# Design Interfaces for High-Level Synthesis: Library Modelling, Netlist Generation and Visualisation

by

# S S Johal

# PhD

# University of Edinburgh

## Abstract

In the fast growing field of high-level synthesis, very little attention has been paid to the areas where core synthesis tools must interact with their immediate environment. Library modelling, netlist generation and design visualisation are the three interfaces that have been neglected at the expense of advances in core synthesis tools. This thesis addresses this problem by looking at these primary interfaces and developing the ideas and tools that are needed to provide significant improvements over and above interfaces used by existing systems.

Most of the results of this work has been embodied in the development of the SAGE high-level synthesis system, whose most significant difference between existing high-level synthesis systems is that the electronic design engineer is able to direct the process of synthesis to a very fine degree of granularity. The main vehicle that has helped achieve this is the visibility of design information through graphical representations with which a designer is able to directly interact. This is in stark contrast to the purely automatic approaches of many synthesis systems, whose only support in heading towards the desired solution tends to be in the form of restarting a synthesis session from scratch.

As well as the interfaces themselves, support tools in the form of sound software building blocks combined with software frameworks around which solid interfaces can be built are equally important. Without them, the interfaces would be concepts without proof in reality. Consequently, an equally important problem that this thesis addresses is the development of the necessary tools that can ensure this can happen.

ii

# Credits

I would like to thank my supervisors Peter Denyer and Peter Grant for their help and support during the preparation of this thesis. I would also like to gratefully acknowledge the direct and indirect support from Abdul Sardharwalla, John Whitelegge, Mike Ginn, Nigel Baldwin, Phil Addison, Jonathon Puddicombe, Martin Ryder, David Mallon, Patrick Seymour, Colin Carruthers, Ross Kennedy, Douglas Chilsom, Allan Tomlinson, Irene Buchanan, David Rees, Tom Kean, Douglas Grant, Iain Findlay, Paul Neil, Gerald Allan and of course Magnus Magnuson.

This is in addition to many thanks to GEC-Marconi Research Centre and the Department of Electrical Engineering at Edinburgh University for supporting me during the development of this thesis.

# Declaration

This thesis has been entirely composed by myself and except where indicated, the majority of the work presented in this thesis is my own.

Subindrao Singh Johal

June 1993

# Table of Contents

| Ab  | strac                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ii                                                                                                                               |

|-----|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| De  | dical                                                                      | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iii                                                                                                                              |

| Cre | edits                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | iv                                                                                                                               |

| De  | clard                                                                      | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iv                                                                                                                               |

|     |                                                                            | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

|     | -                                                                          | igures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|     |                                                                            | bbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

| 1.  | •                                                                          | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

|     | 1.1                                                                        | Problem Domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

|     | 1.2                                                                        | Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

| 2.  | Bac                                                                        | cground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

|     | 2.1                                                                        | Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

|     | 2.2                                                                        | Research High-Level Synthesis Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

|     |                                                                            | 2.2.1 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

|     |                                                                            | 2.2.2 Library Modelling Aspects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|     |                                                                            | 2.2.3 Design Visualisation Aspects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

|     |                                                                            | 2.2.4 Netlist Generation Aspects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                                                                                               |

|     | 2.3                                                                        | Commercial Synthesis Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                                                                                               |

|     | 2.4                                                                        | Development History of SAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                                                               |

|     |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

| 3.  | Lib                                                                        | ary Modelling and Netlist Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 21                                                                                                                             |

| 3.  | Lib:<br>3.1                                                                | ary Modelling and Netlist Generation<br>Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

| 3.  |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                                                                               |

| 3.  |                                                                            | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22                                                                                                                         |

| 3.  |                                                                            | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27                                                                                                             |

| 3.  |                                                                            | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29                                                                                                       |

| 3.  | 3.1                                                                        | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33                                                                                                 |

| 3.  | 3.1                                                                        | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36                                                                                           |

| 3.  | 3.1                                                                        | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37                                                                                     |

| 3.  | 3.1                                                                        | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44                                                                               |

| 3.  | 3.1                                                                        | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46                                                                         |

| 3.  | 3.1                                                                        | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49                                                                   |

| 3.  | 3.1                                                                        | Behavioural Modelling         3.1.1 Temporal Issues         3.1.2 Library Modelling Language         3.1.2.1 Combinatorial Objects         3.1.2.2 Clocked Objects         3.1.2.3 Pipelined Objects         3.1.2.3 Pipelined Objects         3.1.2.1 Creation         3.2.2 Attributing for Netlist Generation         3.2.3 Generation         3.2.3.1 Name Space Problems         3.2.3.2 Generating ELLA                                                                                                                                                                                                                                            | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55                                                             |

| 3.  | <ul><li>3.1</li><li>3.2</li></ul>                                          | <ul> <li>Behavioural Modelling</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64                                                             |

| 3.  | 3.1                                                                        | Behavioural Modelling         3.1.1         Temporal Issues         3.1.2         Library Modelling Language         3.1.2.1         Combinatorial Objects         3.1.2.2         Clocked Objects         3.1.2.3         Pipelined Objects         Structure Modelling         3.2.1         Creation         3.2.2         Attributing for Netlist Generation         3.2.3.1         Name Space Problems         3.2.3.2         Generating ELLA         3.2.3.3         Mapping Schematics                                                                                                                                                          | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64<br>65                                                 |

| 3.  | <ul><li>3.1</li><li>3.2</li></ul>                                          | Behavioural Modelling         3.1.1 Temporal Issues         3.1.2 Library Modelling Language         3.1.2.1 Combinatorial Objects         3.1.2.2 Clocked Objects         3.1.2.3 Pipelined Objects         3.1.2.3 Pipelined Objects         Structure Modelling         3.2.1 Creation         3.2.2 Attributing for Netlist Generation         3.2.3 Generation         3.2.3.1 Name Space Problems         3.2.3.2 Generating ELLA         3.2.3.3 Mapping Schematics         Matchmaking and Unification         3.3.1 Match Searching                                                                                                             | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64<br>65<br>65                                           |

| 3.  | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                              | Behavioural Modelling.         3.1.1 Temporal Issues.         3.1.2 Library Modelling Language         3.1.2.1 Combinatorial Objects         3.1.2.2 Clocked Objects         3.1.2.3 Pipelined Objects         3.1.2.3 Pipelined Objects         Structure Modelling.         3.2.1 Creation         3.2.2 Attributing for Netlist Generation         3.2.3 Generation         3.2.3.1 Name Space Problems.         3.2.3.2 Generating ELLA         3.2.3.3 Mapping Schematics         Matchmaking and Unification         3.3.1 Match Searching         3.3.2 Unification                                                                               | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>65<br>65<br>66                                           |

|     | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                              | Behavioural Modelling         3.1.1         Temporal Issues         3.1.2         Library Modelling Language         3.1.2.1         Combinatorial Objects         3.1.2.2         Clocked Objects         3.1.2.3         Pipelined Objects         Structure Modelling         3.2.1         Creation         3.2.2         Attributing for Netlist Generation         3.2.3         Generation         3.2.3.1         Name Space Problems         3.2.3.2         Generating ELLA         3.2.3.3         Mapping Schematics         Matchmaking and Unification         3.3.1         Match Searching         3.3.2         Unification             | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64<br>65<br>65<br>66<br>71                               |

|     | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>Des</li></ul>                  | Behavioural Modelling.         3.1.1 Temporal Issues.         3.1.2 Library Modelling Language         3.1.2.1 Combinatorial Objects         3.1.2.2 Clocked Objects         3.1.2.3 Pipelined Objects         3.1.2.3 Pipelined Objects         Structure Modelling.         3.2.1 Creation         3.2.2 Attributing for Netlist Generation         3.2.3 Generation         3.2.3.1 Name Space Problems.         3.2.3.2 Generating ELLA         3.2.3.3 Mapping Schematics         Matchmaking and Unification         3.3.1 Match Searching         3.3.2 Unification         gn Visualisation                                                      | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64<br>65<br>65<br>65<br>66<br>71<br>72                   |

|     | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>Des 4.1 4.2</li> </ul>     | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>65<br>65<br>65<br>66<br>71<br>72<br>75                   |

|     | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>Des 4.1 4.2 4.3</li> </ul> | Behavioural Modelling         3.1.1 Temporal Issues         3.1.2 Library Modelling Language         3.1.2.1 Combinatorial Objects         3.1.2.2 Clocked Objects         3.1.2.3 Pipelined Objects         3.1.2.3 Pipelined Objects         3.1.2.4 Creation         3.2.5         3.2.7 Creation         3.2.8 Attributing for Netlist Generation         3.2.3 Generation         3.2.3.1 Name Space Problems         3.2.3.2 Generating ELLA         3.2.3.3 Mapping Schematics         Matchmaking and Unification         3.3.1 March Searching         3.3.2 Unification         gn Visualisation         Visualisation         SAGE Data Model | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64<br>65<br>65<br>66<br>71<br>72<br>75<br>77             |

|     | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>Des 4.1 4.2</li> </ul>     | Behavioural Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22<br>25<br>27<br>29<br>33<br>36<br>37<br>44<br>46<br>49<br>55<br>64<br>45<br>65<br>65<br>65<br>71<br>72<br>75<br>77<br>80 |

|     |       | 4.4.1          |        | Graph Categories        |  |

|-----|-------|----------------|--------|-------------------------|--|

|     |       | 4.4.1          |        | Invisibility            |  |

|     |       | 4.4.1          |        | Nodes                   |  |

|     |       | 4.4.1.         |        | Arcs                    |  |

|     |       | 4.4.1.         |        | Constraints             |  |

|     |       |                |        |                         |  |

|     | 4.5   |                |        | and Undirected Graphs   |  |

|     |       |                |        | thod for Breaking Loops |  |

|     |       |                |        | er Application          |  |

|     | 4.6   |                |        | adsads                  |  |

|     | 4.7   |                |        |                         |  |

|     | 4.8   |                |        | ation                   |  |

|     | 4.8   |                |        |                         |  |

|     |       |                |        | ode                     |  |

|     |       | 4.8.2 Kesot    |        | Time Graphs<br>Zones    |  |

|     |       | 4.8.2          |        | Call Shape              |  |

|     |       | 4.8.2          |        | Mapping                 |  |

|     |       |                |        | low Graphs              |  |

|     |       |                |        | Graphs                  |  |

|     | 4.9   |                |        | -                       |  |

| 5.  | Ero   |                |        |                         |  |

| Э.  |       |                |        |                         |  |

|     | 5.1   |                |        | sions                   |  |

|     | 5.2   |                |        |                         |  |

|     | 5.3   |                |        | 38                      |  |

|     | 5.4   | Drawing Mod    | del    |                         |  |

|     | 5.5   | Attribute Mar  | nage   | ment                    |  |

|     | 5.6   | User Interface | e Ma   | nagement Services       |  |

|     |       | 5.6.1 Progra   | атп    | ers UI Interface        |  |

|     |       | 5.6.2 Rubbe    | erba   | 1ding                   |  |

| 6.  | Fou   | ndations       | •••••  |                         |  |

|     | 6.1   | Lists          | •••••  |                         |  |

|     | 6.2   | Trees          | •••••• |                         |  |

|     | 6.3   |                |        | ement                   |  |

|     | 6.4   |                |        | -                       |  |

|     | 6.5   |                |        | ger                     |  |

|     | 6.6   |                |        |                         |  |

| 7.  | Res   |                |        |                         |  |

|     | 7.1   |                |        |                         |  |

|     | 7.2   |                |        |                         |  |

|     | 7.3   |                |        |                         |  |

| 8.  | Con   |                |        |                         |  |

|     |       |                |        |                         |  |

|     |       |                |        |                         |  |

|     |       |                |        |                         |  |

| лpţ | renal | A              | •••••  |                         |  |

# List of Figures

| Figure 1-1.  | Typical SAGE Design Session                                                | 3  |

|--------------|----------------------------------------------------------------------------|----|

| Figure 1-2.  | Major Interfaces to Synthesis Tools                                        | 5  |

| Figure 1-3.  | Thesis Structure/Breakdown - Main Chapters                                 | 7  |

| Figure 2-1.  | Major High-Level Synthesis Systems                                         | 12 |

| Figure 3-1.  | Example of Modelling a Combinatorial Device                                | 27 |

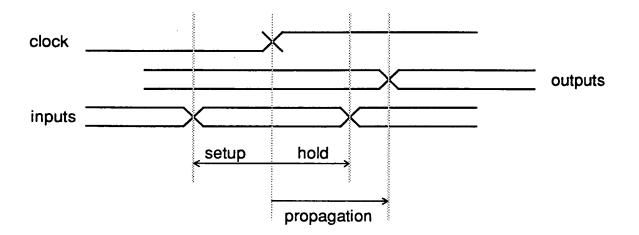

| Figure 3-2.  | Setup, Hold and Propagation Model                                          | 30 |

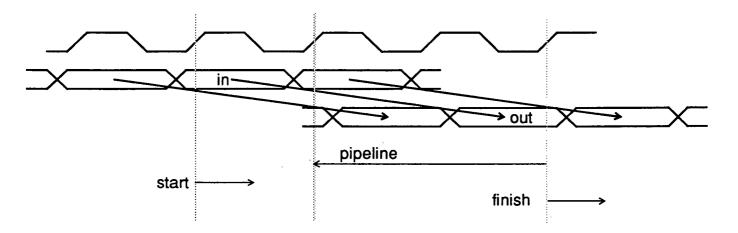

| Figure 3-3.  | Pipeline Model                                                             | 31 |

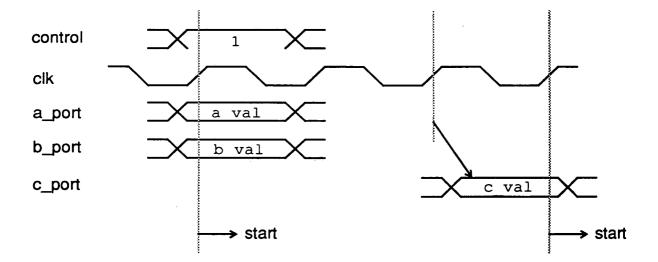

| Figure 3-4.  | Example of Modelling a Clocked Device                                      | 31 |

| Figure 3-5.  | LML Example of a Clocked Device                                            | 33 |

| Figure 3-6.  | Starting State for Pipeline Example                                        | 34 |

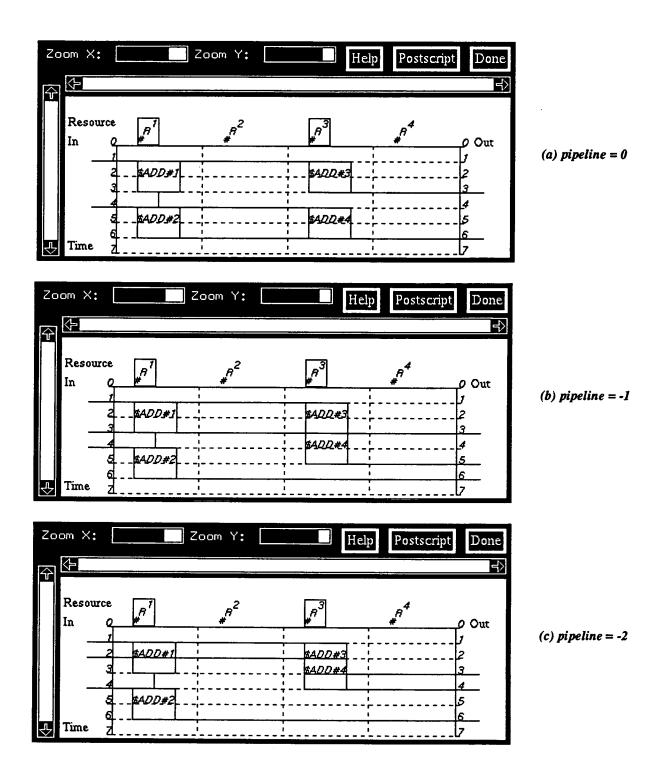

| Figure 3-7.  | Pipeline Figure Combinations                                               | 35 |

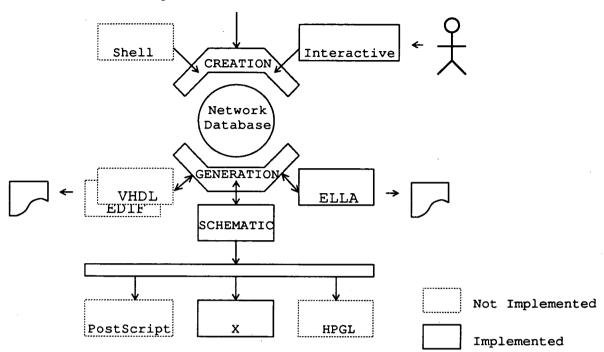

| Figure 3-8.  | Overall Context for Creation and Netlist Generation Activities             | 37 |

| Figure 3-9.  | Creation Procedural Interface                                              | 43 |

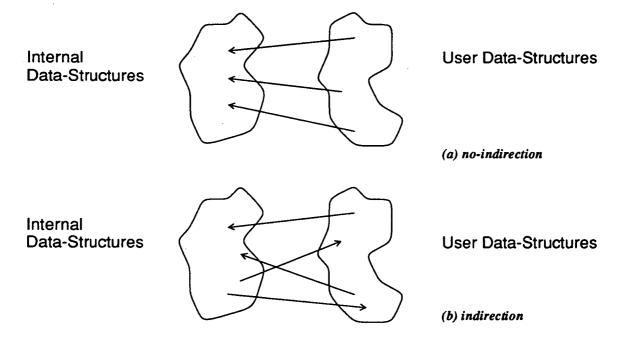

| Figure 3-10. | Indirection and No-Indirection Comparison                                  |    |

| Figure 3-11. | Generic Outline for Indirection Support                                    |    |

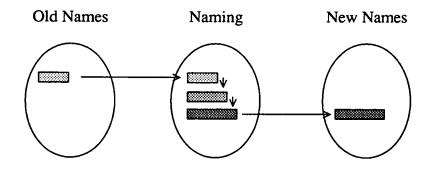

| Figure 3-12. | ELLA names package                                                         | 50 |

| Figure 3-13. | Name Mapping Example, Using Target Case Sensitivity<br>and Case Directives | 52 |

| Figure 3-14. | The 3 Databases Used in Unique Name Generation                             |    |

| Figure 3-15. | Functions and Procedures present in Names Generic                          |    |

| Figure 3-16. | Examples of Unique Name Generation                                         |    |

| Figure 3-17. | Names Database Management                                                  |    |

| Figure 3-18. | ELLA Types                                                                 |    |

| Figure 3-19. | Netlist Generation Primitives: Buffer, Mux and Ram                         |    |

| Figure 3-20. | Different ELLA Views of Tri-state Buffers                                  |    |

| Figure 3-21. | ELLA Bit Resolution Algorithm                                              |    |

| Figure 3-22. | The FNSET bit_bus Macro                                                    |    |

| Figure 3-23. | Connection Types                                                           |    |

| Figure 3-24. | IO -> IO Connections at Node and Instance Levels                           |    |

| Figure 3-25. | Unused Inputs, Outputs and IOs Consumer                                    |    |

| Figure 3-26. | ELLA Controller MACRO                                                      |    |

| Figure 3-27. | Generated ELLA Netlist Structure                                           |    |

| Figure 3-28. | Untouched Automatically Generated ELLA Example                             |    |

| Figure 3-29. | Example of Leaf Level Mappings in Generated ELLA                           |    |

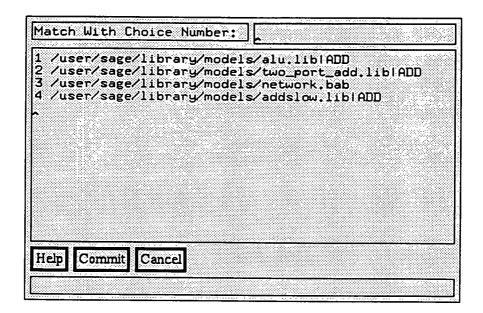

| Figure 3-30. | Matchmaking Selection Panel.                                               |    |

| Figure 3-31. | Unification Program                                                        |    |

| Figure 3-32. | Unification Example                                                        |    |

| Figure 3-33. | Run of Unification Example                                                 |    |

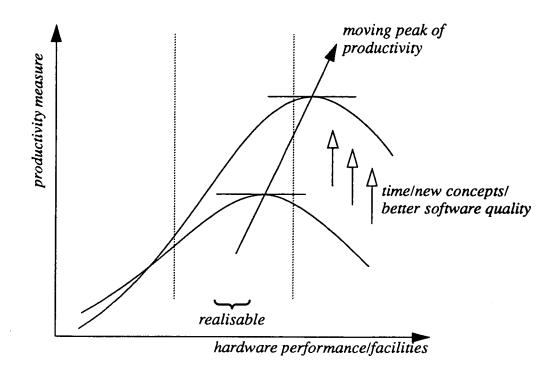

| Figure 4-1.  | Productivity vs Software vs Hardware                                       |    |

| -            | -                                                                          | -  |

| Figure 4-2.  | Design Loop                                                | 76  |

|--------------|------------------------------------------------------------|-----|

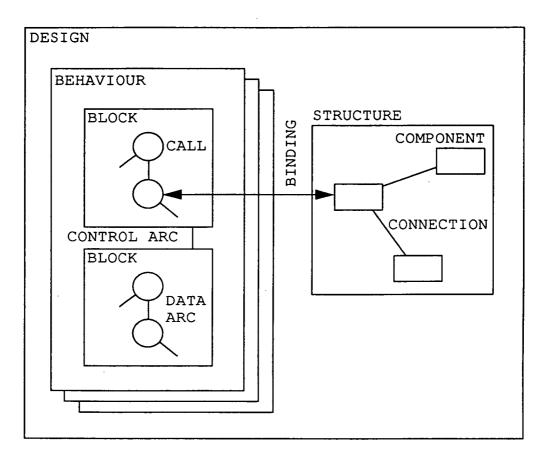

| Figure 4-3.  | Basic SAGE Data Model Objects and their Interrelationships |     |

| Figure 4-4.  | Graph Categories                                           | 83  |

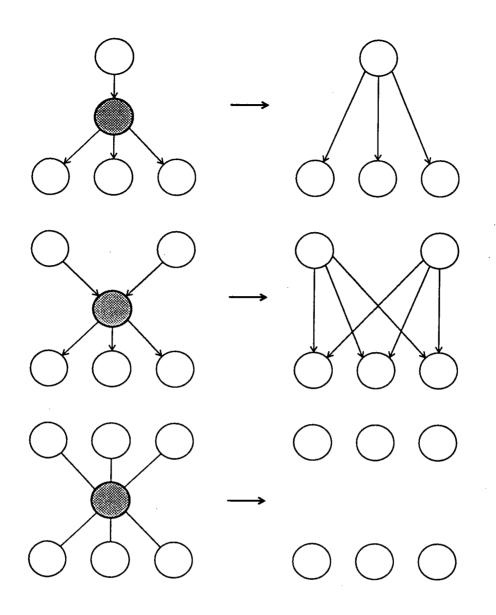

| Figure 4-5.  | Examples Demonstrating Invisibility                        | 85  |

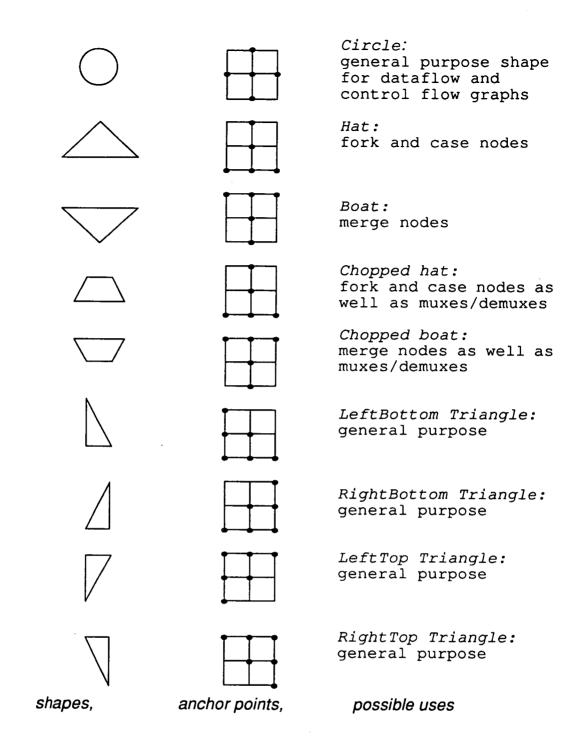

| Figure 4-6.  | Shapes and their Anchor Points                             | 87  |

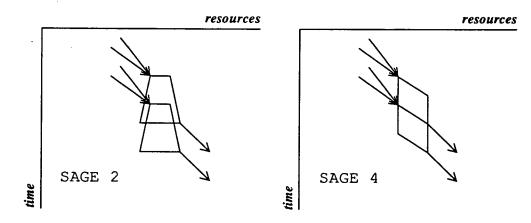

| Figure 4-7.  | Pipelining Representation in SAGE 4, compared to in SAGE 2 | 88  |

| Figure 4-8.  | Highlighting Text Items                                    | 92  |

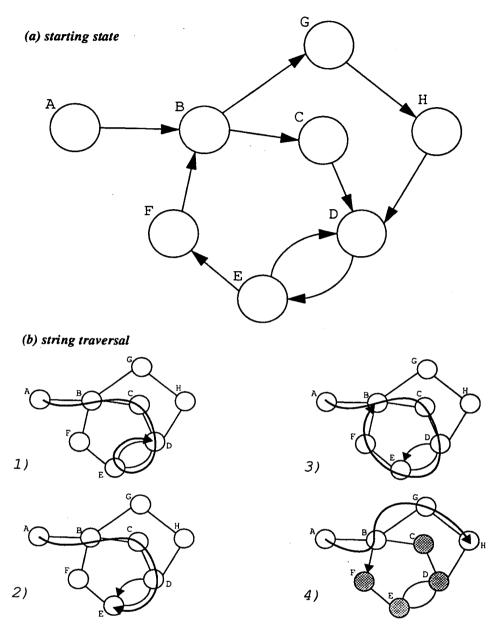

| Figure 4-9.  | Example to Illustrate the String Method                    | 94  |

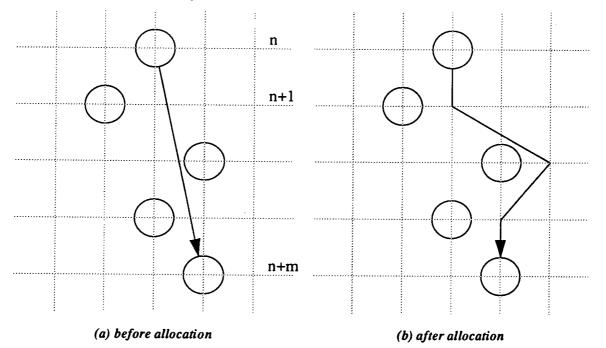

| Figure 4-10. | Space Allocation for Arcs                                  | 96  |

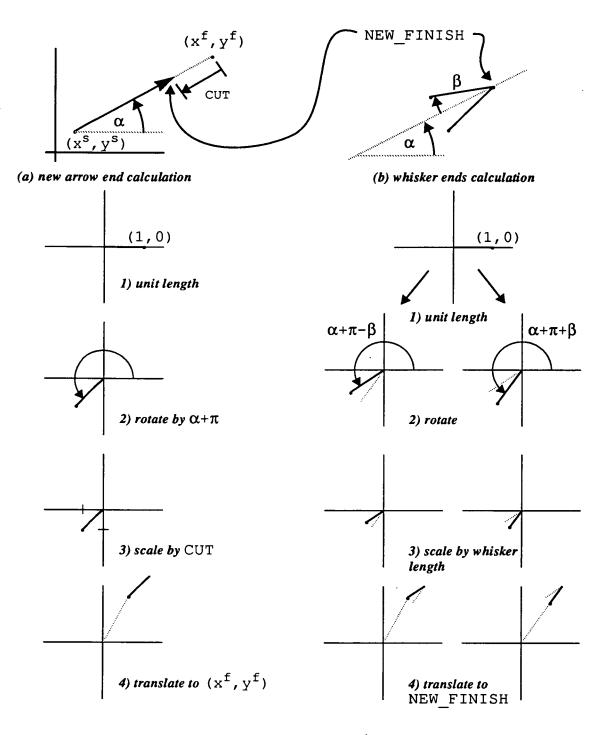

| Figure 4-11. | Transformations for Arrow Heads                            | 98  |

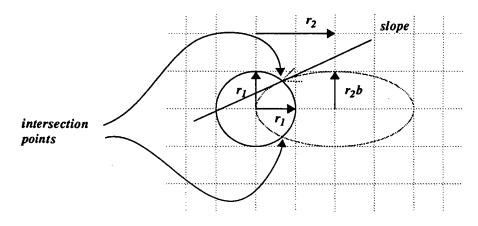

| Figure 4-12. | Local Loops                                                | 99  |

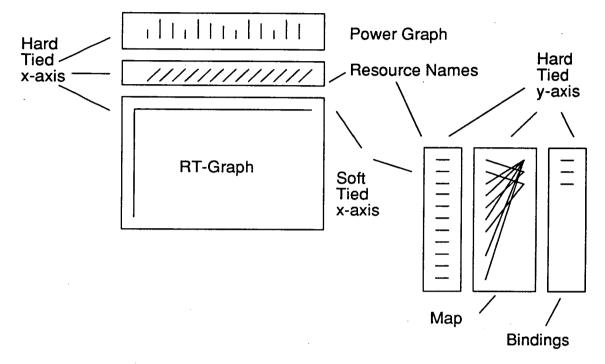

| Figure 4-13. | Example Illustrating Hard and Soft Combined Axis           | 101 |

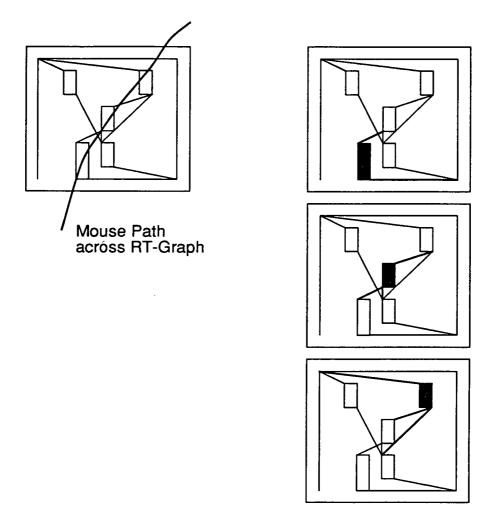

| Figure 4-14. | Dynamic Visualisation in Action                            |     |

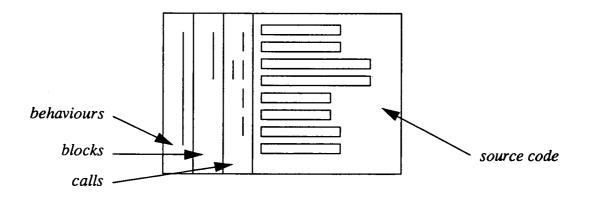

| Figure 4-15. | General Layout of the Source Code                          | 104 |

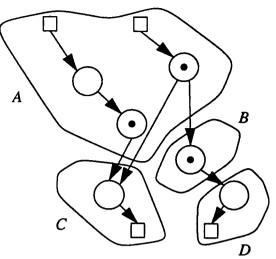

| Figure 4-16. | Zone Identification Example                                | 106 |

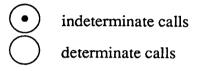

| Figure 4-17. | Zones in a Resource-Time Graph                             | 107 |

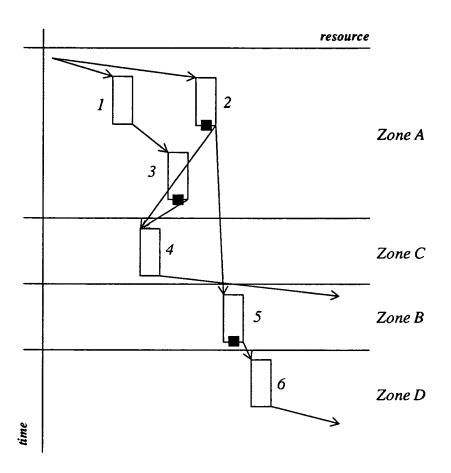

| Figure 4-18. | Supported Call Classes                                     | 108 |

| Figure 4-19. | Call Classes and their Children                            | 108 |

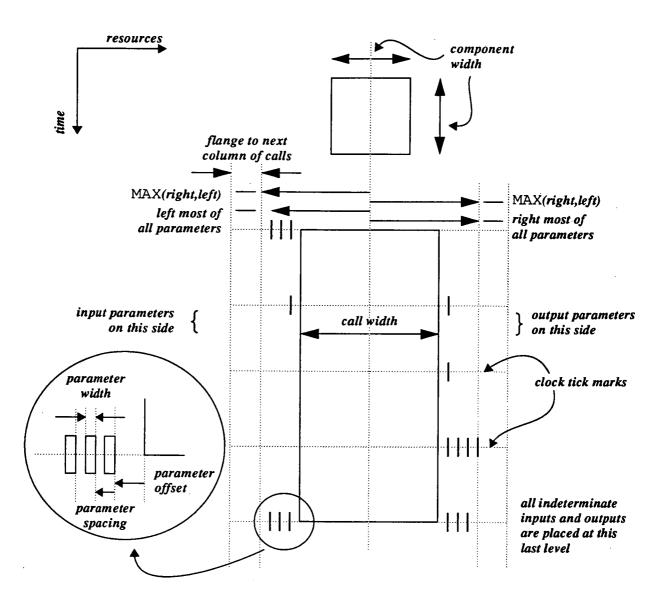

| Figure 4-20. | How a Call Looks Close Up                                  | 110 |

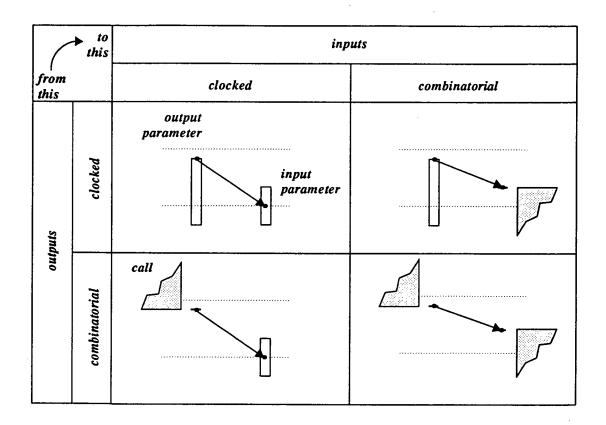

| Figure 4-21. | Arc Alignment, Depending on the Nature of the Call.        | 111 |

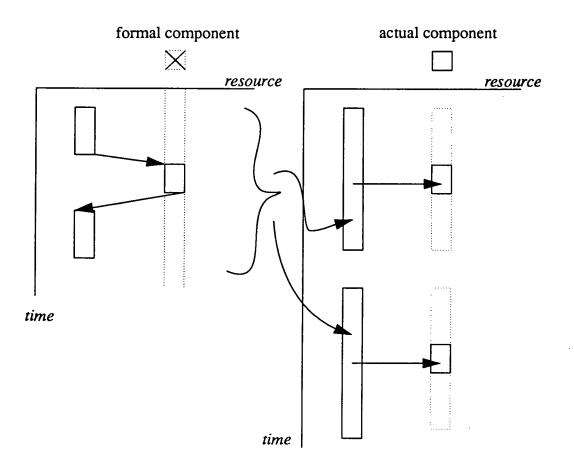

| Figure 4-22. | Mapping Example                                            | 113 |

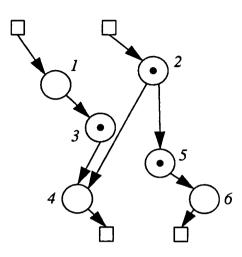

| Figure 4-23. | Control Node Categories                                    | 114 |

| Figure 4-24. | The Three Grids for Schematic Routing                      |     |

|              | (Pins, Components and Routing)                             | 116 |

| Figure 4-25. | Navigation Panels                                          |     |

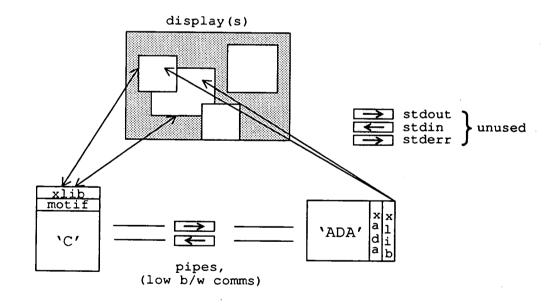

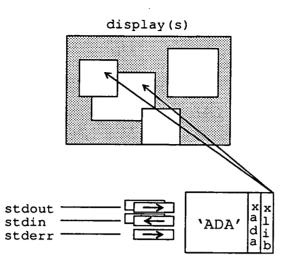

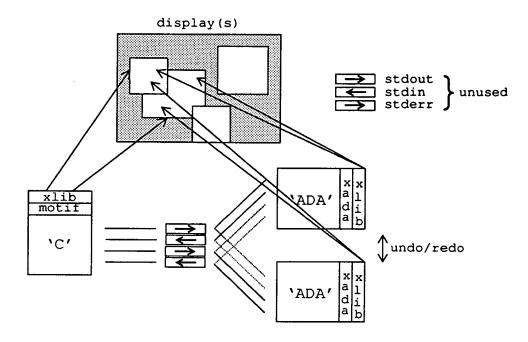

| Figure 5-1.  | Stylised SAGE Process Model                                | 122 |

| Figure 5-2.  | Process Model - Normal Operation                           |     |

| Figure 5-3.  | Process Model - Debug/Test Operation                       | 125 |

| Figure 5-4.  | Process Model - Dual Process Operation                     | 127 |

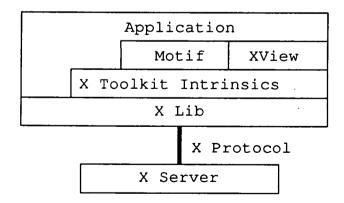

| Figure 5-5.  | X Window System Conceptual Layers                          | 129 |

| Figure 5-6.  | PRAGMA and REPRESENTATION Clause Example                   | 131 |

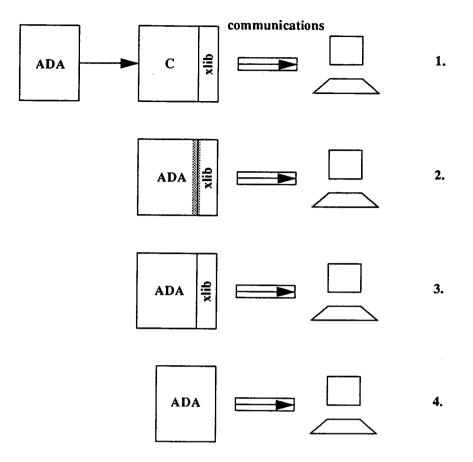

| Figure 5-7.  | X-ADA Binding Scenarios                                    | 132 |

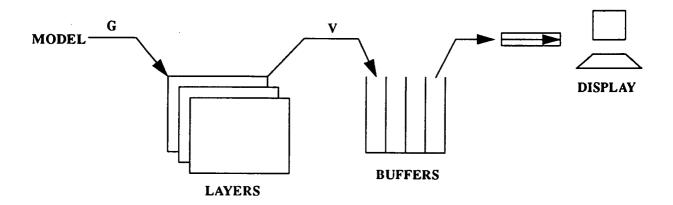

| Figure 5-8.  | Rendering Model Overview                                   | 135 |

| Figure 5-9.  | Composite Objects Through Hierarchical Construction        | 136 |

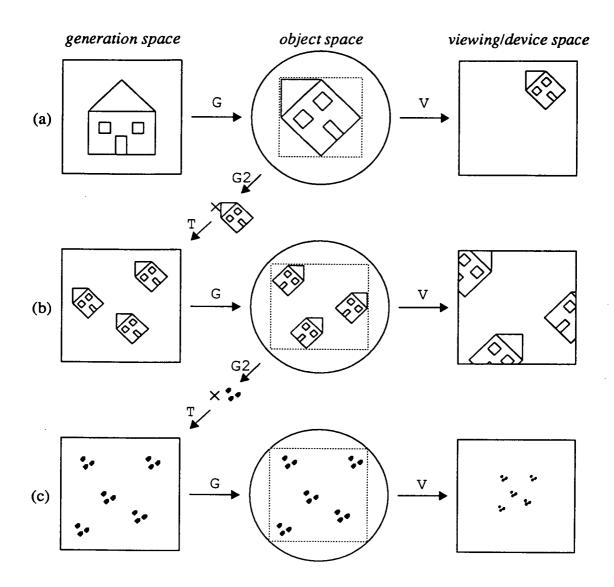

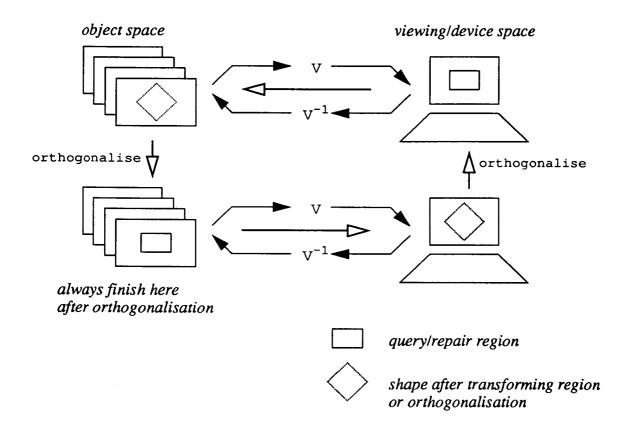

| Figure 5-10. | Region Mapping in Device and Object Spaces,                |     |

|              | for Non Orthogonal Mappings                                |     |

| Figure 5-11. | Clip and Search Regions                                    |     |

| Figure 5-12. | Picture Attributes Example                                 | 141 |

| Figure 5-13. | Two Level Hashing Attribute Management                     |     |

| Figure 5-14. | 36 Ways to Draw Text                                       |     |

| Figure 5-15. | Rotated Bitmap Text                                        |     |

| Figure 5-16. | User Interface Component Construction Example              | 146 |

}

| Figure 5-17. | Stylised Message Construction Example                    | 148 |

|--------------|----------------------------------------------------------|-----|

| Figure 5-18. | Registering Software                                     | 149 |

| Figure 5-19. | Typical Output                                           | 151 |

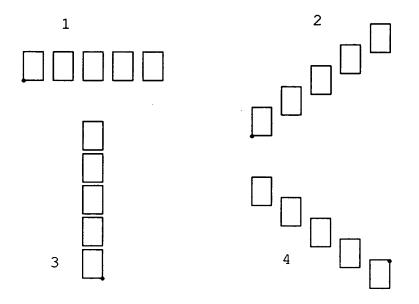

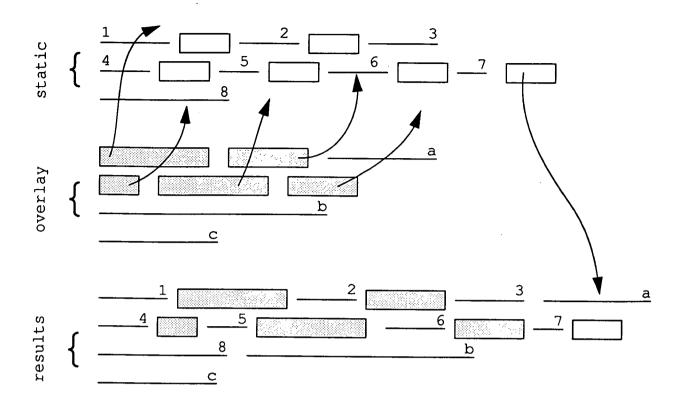

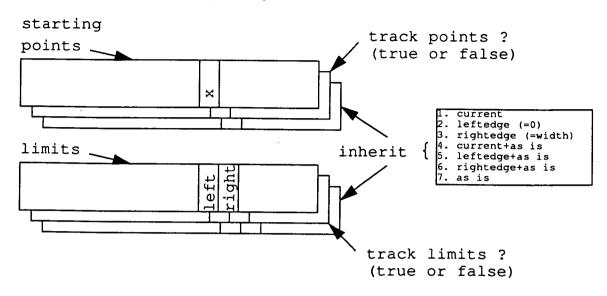

| Figure 5-20. | Tracking, Inheritance and Limits for the x Ordinate      | 153 |

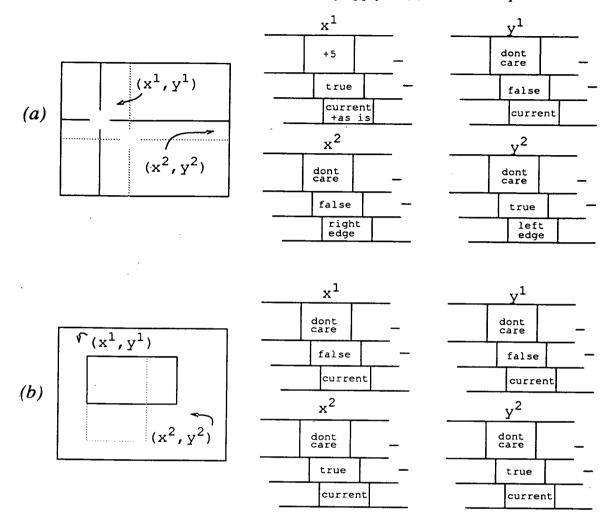

| Figure 5-21. | Rubberbanding Cross-Hairs and Box Examples - Points Only | 154 |

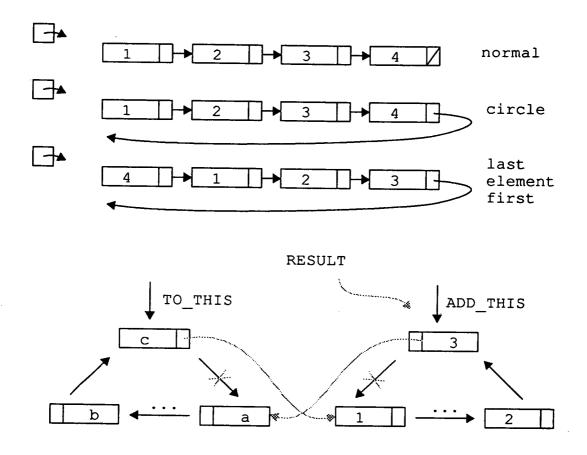

| Figure 6-1.  | List Forms and O(1) Symmetric List Combine               | 158 |

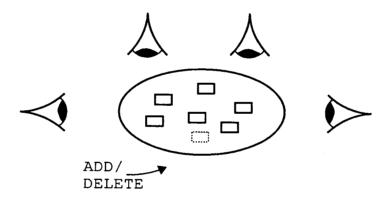

| Figure 6-2.  | Multi View Stability                                     | 159 |

| Figure 6-3.  | SAGE vs Booch iteration                                  | 160 |

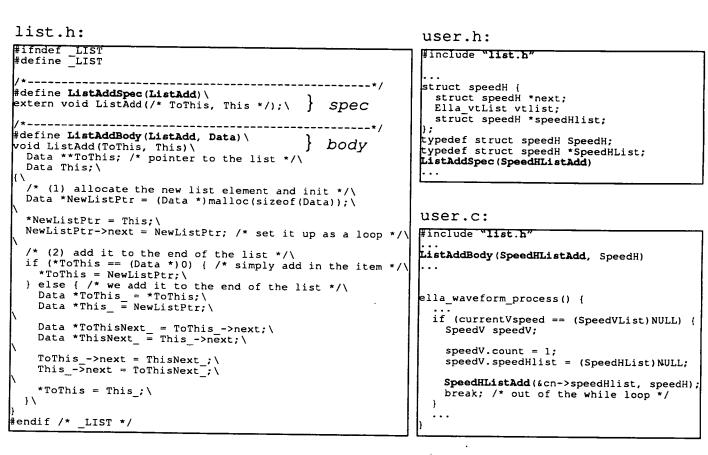

| Figure 6-4.  | Generics in C                                            | 161 |

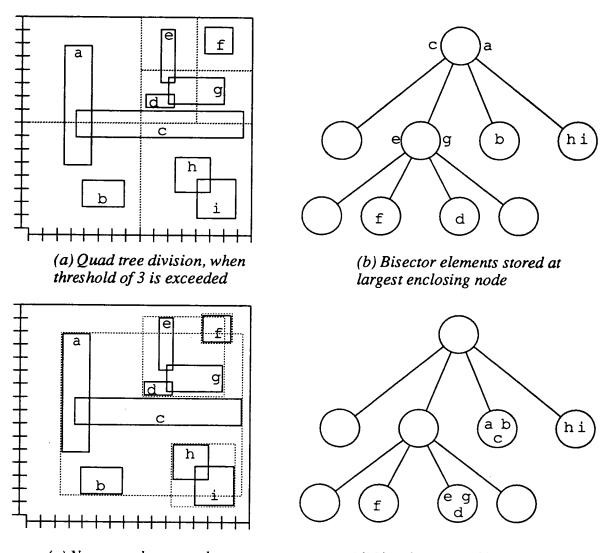

| Figure 6-5.  | Quad Tree Storage - Bisector Element Management          | 164 |

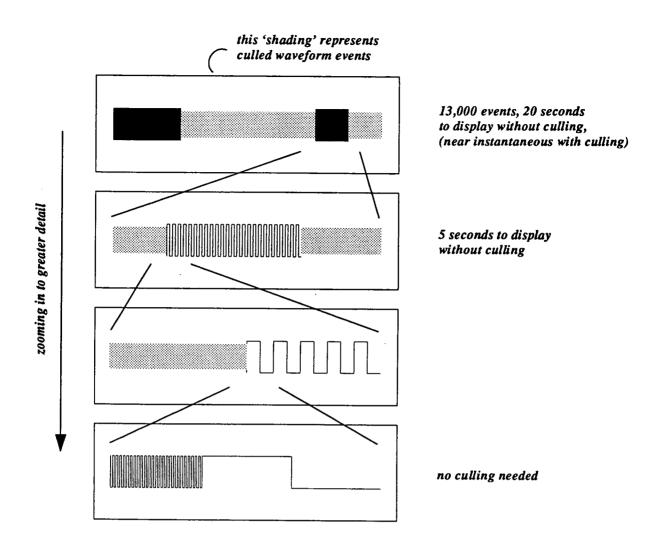

| Figure 6-6.  | Waveform Culling Using The Rectangle Manager             | 167 |

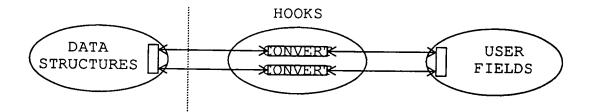

| Figure 6-7.  | Complex Conversion Management of Data References         | 171 |

| Figure 6-8.  | Convert Generic                                          |     |

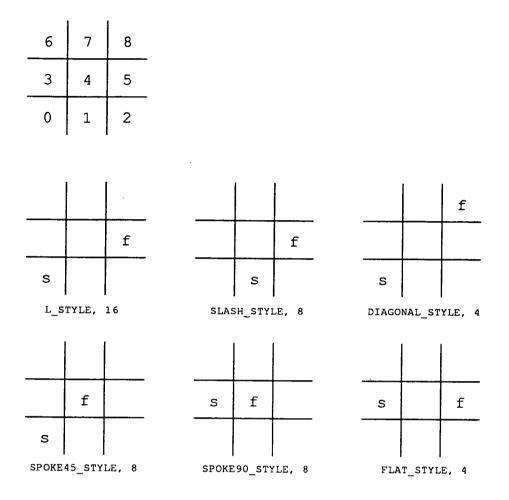

| Figure 6-9.  | NCN Line Starting Points - Shown by Shading              | 173 |

| Figure 6-10. | SAGE Start and End Line Points                           | 174 |

| Figure 6-11. | FLAT_STYLE Code Snippet For Line Clipping                | 175 |

| Figure 7-1.  | VHDL Package Code                                        | 177 |

| Figure 7-2.  | VHDL Process Code                                        | 178 |

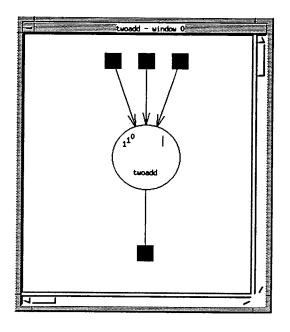

| Figure 7-3.  | Control Flow for TWOADD Example                          | 179 |

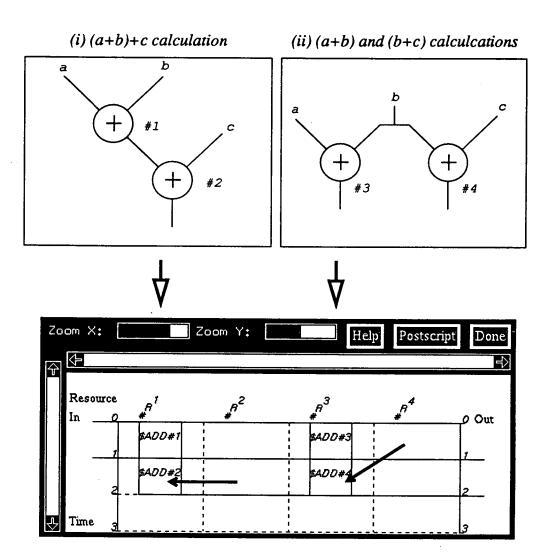

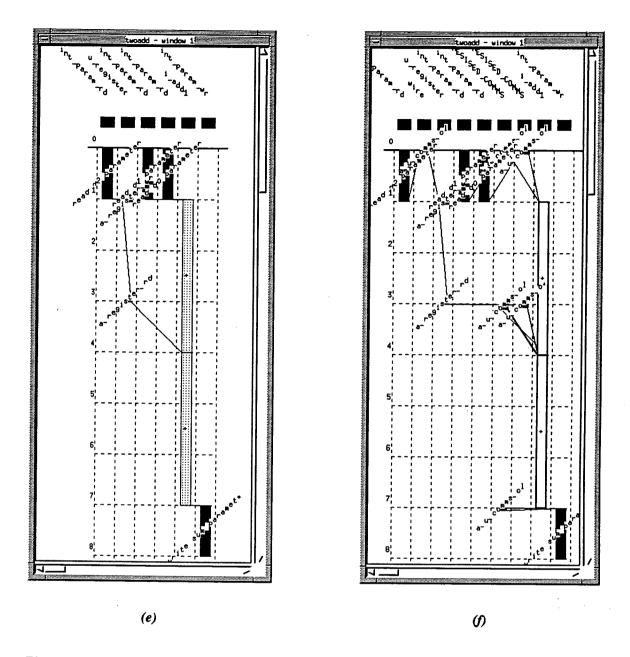

| Figure 7-4.  | Resource-Time Graphs of TWOADD                           |     |

|              | Example During Manipulation                              | 182 |

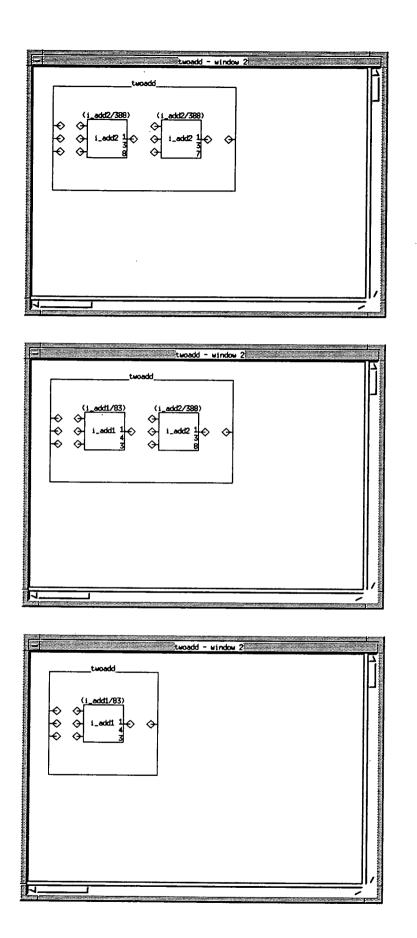

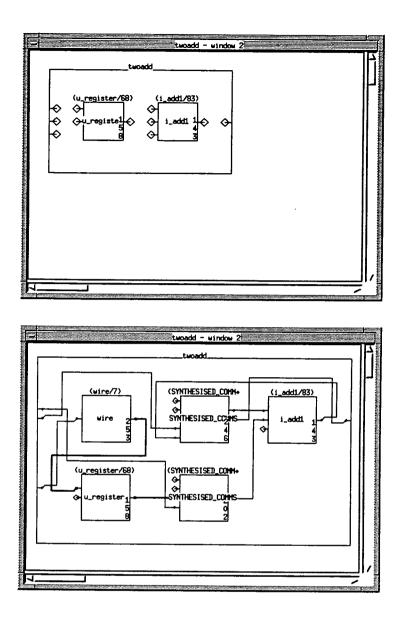

| Figure 7-5.  | Structure Graphs of TWOADD Example During Manipulation   | 185 |

| Figure A-1.  | The Lists Generic                                        | 207 |

| Figure A-2.  | Red-Black Trees Generic                                  | 211 |

| Figure A-3.  | Binary Trees Generic                                     | 213 |

| Figure A-4.  | nary Trees Generic                                       | 215 |

| Figure A-5.  | Rectangle Manager Generic                                | 219 |

| Figure A-6.  | Sets Generic                                             | 221 |

| Figure A-7.  | Union Algorithm                                          | 224 |

# List of Abbreviations

| ALU    | Arithmetic Logic Unit                                |

|--------|------------------------------------------------------|

| ASAP   | As Soon As Possible                                  |

| AVS    | Advanced Visualisation System                        |

| BITBLT | BIT Block Logic Transfer                             |

| BNF    | Backus Naur Form                                     |

| CAR    | head of a list                                       |

| CDR    | tail of a list                                       |

| DPI    | Dots Per Inch                                        |

| EDIF   | Electronic Design Interchange Format                 |

| ELLA   | ELectronic LAnguage                                  |

| FSM    | Finite State Machine                                 |

| GC     | Graphics Context                                     |

| HDL    | Hardware Description Language                        |

| HPGL   | HPs Graphics Language                                |

| IPC    | InterProcess Communication                           |

| LISP   | LISt Processing language                             |

| LML    | Library Modelling Language                           |

| MIMD   | Multiple Instruction Multiple Data                   |

| OOD    | Object Oriented Design                               |

| RCS    | Revision Control System                              |

| PHIGS  | Programmers Hierarchical Interactive Graphics System |

| POSIX  | Portable Operating System Interface                  |

| SAIC   | Science Applications International Corporation       |

| SCCS   | Source Code Control System                           |

| SIMD   | Single Instruction Multiple Data                     |

| UIL    | User Interface Language                              |

| UIMS   | User Interface Management Services                   |

| VHDL   | VHSIC Hardware Description Language                  |

| VTIP   | VHDL Tool Integration Platform                       |

|        |                                                      |

#### LETTERS TO THE EDITOR (The Times of London)

#### Dear Sir,

I am firmly opposed to the spread of microchips either to the home or to the office. We have more than enough of them foisted upon us in public places. They are a disgusting A mericanism, and can only result in the farmers being forced to grow smaller potatoes, which in turn will cause massive unemployment in the abready severely depressed agricultural industry.

Yours faithfully,

Capt. Quinton D'Arcy, J. P. Sevenoaks

# Introduction

The later half of the twentieth century has seen explosive technological achievements in many areas of human endeavour. None so much as in the areas that have arisen from being associated with semiconductor technology. With a symbiotic relationship with software, there has developed a fierce self-feeding loop between hardware and software resulting in continuous improvement - which itself is accelerating. Just as important, if not more so, are the spectacular spin-off benefits which have touched nearly every aspect of mankind. Many examples of such benefits abound, from imaging systems available to physicians, to world wide communication networks that let men and machines communicate with ease and simplicity making the world a smaller place. The systems are as rich in their diversity as they are in their application.

The material presented in this thesis has aimed at being part of this self-feeding loop focusing on the needs of digital electronic design engineers by exploring the tools and ideas that are needed to accelerate and improve the development of new hardware. The problem is simple, namely one of helping designers become more productive. The solution is complex and has started to appear in recent years as a kaleidoscope of many tools and ideas from a variety of university and industrial organisations. What all these developments have in common is the concept of high-level synthesis. In essence, this is the automation of converting concepts into silicon.

The main theme of this thesis is that of the major interfaces that a synthesis tool must have with its environment, and the foundations and framework on which such interfaces must exist in order to operate efficiently and effectively. Section 1.1 looks

at the problem domain addressed by this thesis and places these requirements in a much fuller context.

Most of the work presented in this thesis has arisen from work carried out on a three year collaborative research project hosted by Edinburgh University called SARI -Silicon Architectures Research Initiative. The project had several far-reaching aims, which included the development of tools and ideas in the area of high-level synthesis. The key feature that has differentiated the work of this program from the many previous efforts in the area of high-level synthesis, has been the direct inclusion of the human designer at every possible stage of the synthesis design route. This approach meant that all the creativity and ingenuity a designer possesses is married together efficiently and effectively with a spectrum of brute-force to clever synthesis algorithms. The main vehicle used to achieve this has been the use of graphical representations of a design as it passes from idea to implementation, guided by the human designer.

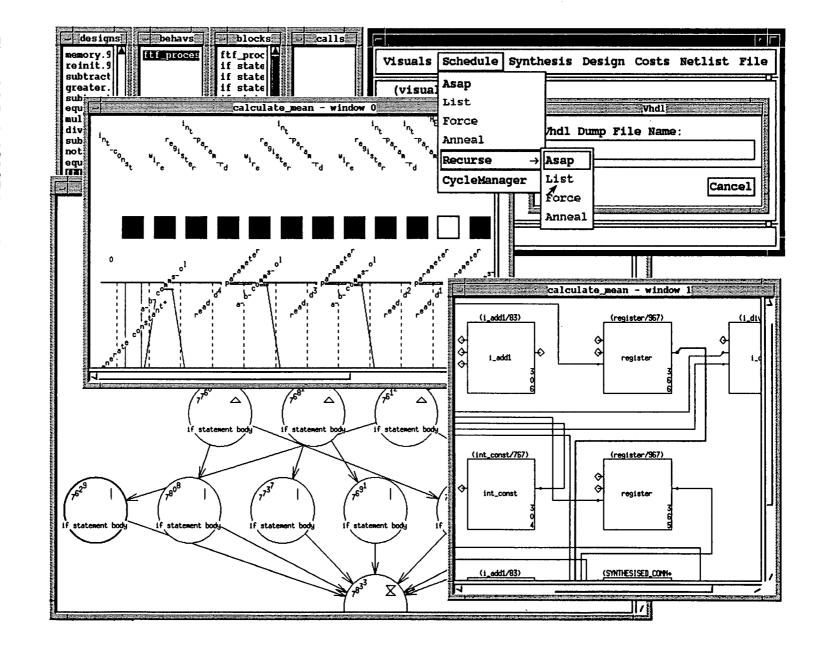

All the ideas developed have been embodied in one toolset, called SAGE [15]. SAGE stands for Sari Architecture GEnerator and as a tool, represents well over thirty man years of effort equating to over a quarter of a million lines of high level code. The toolset has been through a number of generations, the latest being SAGE 4. In its present from, the toolset represents an early snapshot of many ideas that are only now beginning to appear in more mature and stable environments in the form of commercially viable systems. The screen dump given in figure 1-1 shows a snapshot of a typical session with the SAGE system, illustrating some of the panels and graphs that a SAGE user sees and interacts with.

Figure 1-1. Typical SAGE Design Session.

ω

The material presented in this thesis assumes a core understanding of several current systems. In particular, the ELLA hardware description language [34], the X Window System with its programming environment [57, 55] and the ADA programming language [3, 4, 5]. The following section starts by explaining in greater detail the problem domain that has been addressed by this thesis, and is then followed by section 1.2 which gives an overview of the material presented, and how it has been structured.

## **1.1 Problem Domain**

High level synthesis compared with the problem of logic synthesis, usually involves starting with a high-level system description expressed in terms of data flow and control flow structures which precisely defines the system to be implemented. Such structures are similar to those found in most software languages, and have in recent years been incorporated into hardware description languages like VHDL [31, 32] and ELLA. Such descriptions involve time or temporal dependence, unlike the case with logic synthesis, where the focus is generally on purely combinatorial functions.

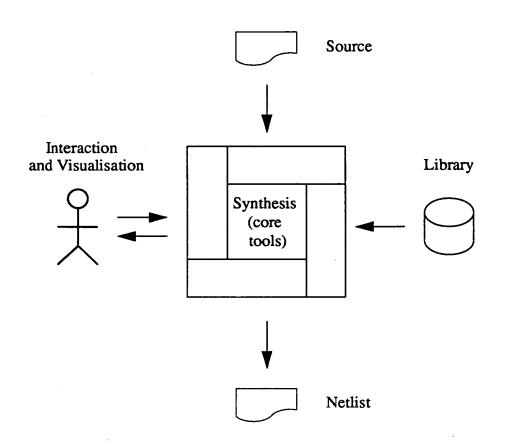

Figure 1-2 shows the high-level information flow of a highly stylised synthesis system. The structure of this diagram is representative of most synthesis systems. In simple terms, the overall order of operations starts with the input of source code and the target library information. Then, with the guidance of a user and the application of automatic core synthesis tools the aim is to produce a technology specific netlist as output. This thesis focuses on three of these four interfaces, namely library modelling, netlist generation and user interaction mostly aided by design visualization. Although a very important area, the problem of source code compilation has been largely obviated by the use of a commercial compilation system called VTIP [45]. In fact, this general approach of using existing tools to build upon, has been used wherever the existing tools have strongly satisfied the conditions of being either excellent or compliant with an existing or emerging industry standard.

#### Figure 1-2. Major Interfaces to Synthesis Tools

Design automation tools to date have concentrated on empowering the user by providing highly focused or point tools that handle one or two concepts very well. Though this approach *does* provide solutions for designers, the tools tend to be too focused in their application. Additionally, this emphasis on the point tools has been at the expense of developments in the interfaces. In other words, this focus hides the richness of opportunity in carefully considered interfaces. By an examination of many existing interfaces, it becomes clear that a great deal more can be done to improve the integration of design automation tools within existing design flows, as well as meshing in closer with the natural requirements of a designer. The improvement of these interfaces is a large part of the problem area addressed by this thesis.

As well as the interfaces themselves, support tools in the form of sound software building blocks combined with software frameworks around which solid interfaces can be built are equally important. Without them, the interfaces would be concepts without proof in reality. Consequently, an equally important problem that has been addressed by this thesis is the development of the necessary tools that can ensure this can happen. The aim has been towards general and complete solutions that could be used without loss of generality in many other novel tool development problems.

### **1.2 Thesis Outline**

This thesis consists of eight chapters. After this introduction, chapter 2 begins with a detailed look at a large number of university developed high-level synthesis systems, and how they compare with the SAGE system, particularly with regards to the material presented in this thesis. The background also looks at the current state of play of commercial synthesis systems. With the multi-million pound research budgets that many commercially driven companies have had in recent years at their disposal, many of the technological developments are coming in larger and larger parts from within industry itself and therefore commercial systems are becoming much more representative of technological leaders in the field. The final part of the background chapter gives a historical perspective of the SAGE system as presented in this thesis.

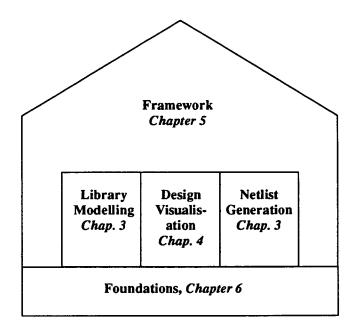

Chapters 3 to 6 contain the core material presented in this thesis. The organisation and the inter-relationship of this material is illustrated pictorially in figure 1-3 by analogy with the core constituents of a building. Chapters 3 and 4, address the areas of design interfaces, showing several key new ideas that are in advance in many ways over existing approaches. Chapters 5 and 6, concentrate on what could be described as software structural foundations and frameworks respectively, without which many of the ideas in chapters 3 and 4 would not have been possible to explore or develop. With a practical basic approach, the broad contribution made by the material in chapters 5 and 6 has been that of an attention to thoroughness, completeness and accuracy in the development of enabling facilities and software. As with real buildings, the framework and foundations are very important and must be sound, since they form the support on which things must bind securely to be successful.

Figure 1-3. Thesis Structure/Breakdown - Main Chapters

Chapter 7, on the results takes a step back from the specific ideas presented and after describing a small design example using SAGE, goes critically onto examine the ideas that the SAGE system has tried to support. From this analysis is also presented the many additional ideas that could be further explored and developed. Although the thesis develops many ideas needed by electronic design engineers in the synthesis of complex systems, just as many important issues have been avoided. From testability issues to the special requirements of recently emerging sub-micron and very high speed logic systems, these holes are explored. In many ways, this chapter highlights the never ending room for improvement that always seems to be available in CAD tool development, and, more importantly, is on many occasions demanded by electronic design engineers. The final chapter, chapter 8, provides a summary of the material presented in this thesis.

The final few paragraphs in this introduction take a more detailed look at the material presented in chapters 3 to 6, with a view to highlighting the key contributions to the field of work that this thesis has made.

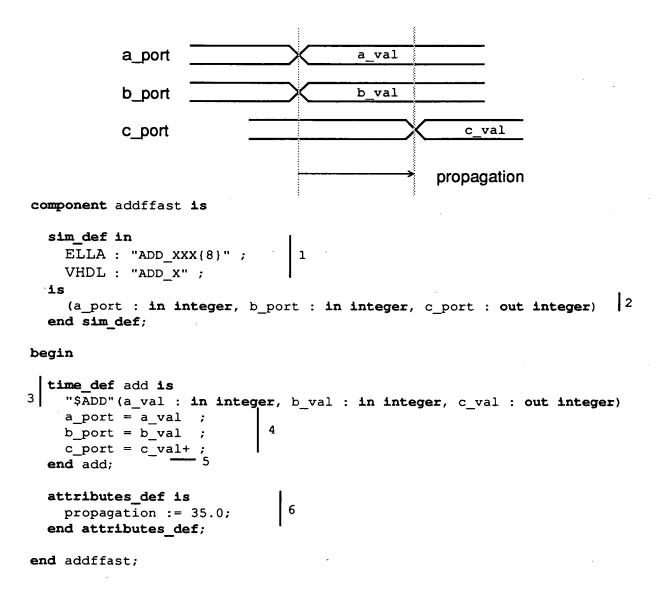

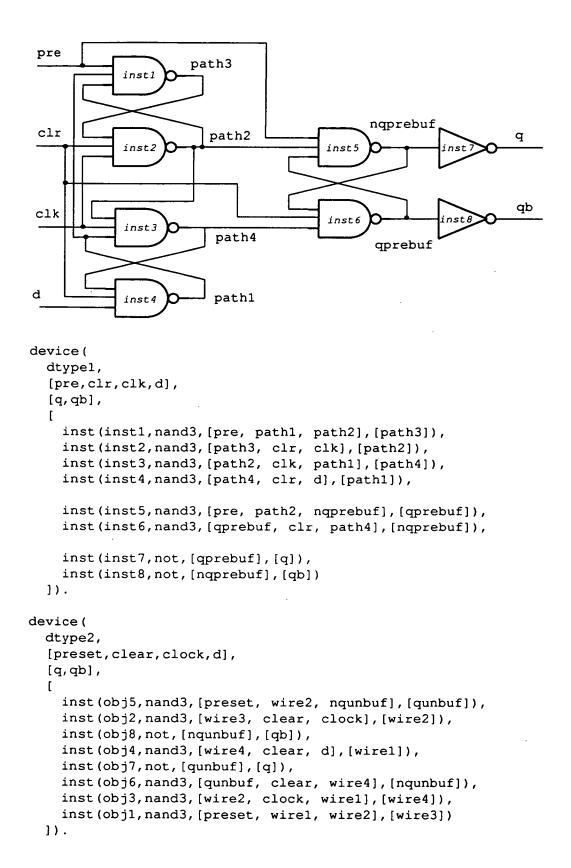

Chapter 3 addresses the problems of library modelling and netlist generation by showing the development of behavioural and structural modelling techniques based

on a formal language called LML. This language supports combinatorial, clocked and pipelined digital devices supporting two levels of timing representation. The structure aspects described in this chapter highlight the concept of creation supported by the technique of attributing netlists to help simplify the process of netlist generation. With these two concepts in place, the section on structure provides a comprehensive solution to the name space problem which is then used as the basis on which netlist generation of ELLA and schematics can happen. Chapter 3 finishes by looking at the services required by core synthesis tools when interfacing with a library of parts, namely matchmaking and unification.

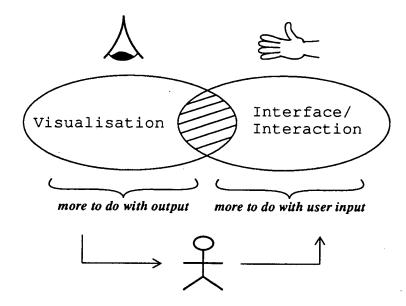

Chapter 4 begins by placing in context the requirements of visualization and then exploring the taxonomy of graphical representations in the form of visuals which can help a designer. From an idealised treatment which views graphs and their properties, the subsequent sections look at how graphs can be effectively drawn. The chapter then explores inter-visual relationships and dynamic visualisation techniques. Following these sections that treat the subject of visualization in a general manner, the chapter looks at the specific development of visuals as used in the SAGE system. The chapter finishes by looking at how a designer is able to interact with these visuals.

Chapter 5 addresses five key areas that are found to be needed to support high-level synthesis in the context of high-performance graphics when the X Window System, ADA and Motif form the key building blocks that have to be used for sound reasons of tool portability and maintainability [97, 98]. These are the process model, language bindings, a rendering model, picture attribute management and user interface management services.

Chapter 6, is primarily a study of object centred software tools that have completeness, accuracy and ease of use as their primary objectives.

An architect's first work is apt to be spare and clean. He knows he doesn't know what he's doing, so he does it carefully and with great restraint.

As he designs the first work, frill after frill and embelöshment after embelöshment occur to him. These get stored away to be used "next time". Sooner or later the first system is finished, and the architect, with firm confidence and a demonstrated mastery of that class of systems, is ready to build a second system.

This second is the most dangerous system a man ever designs. When he does his third and later ones, his prior experiences will confirm each other as to the general characteristics of such systems, and their differences will identify those parts of his experience that are particular and not generalizable.

The general tendency is to over-design the second system, using all the ideas and frills that were cautiously sidetracked on the first one. The result, as Ovid says, is a "big pile". -- Frederick Brooks, "The Mythical Man Month"

# **Background**

This chapter provides an overview of previous work in the area of high-level synthesis. Of particular interest are the interfaces of such systems, and therefore these are examined closely, to help place in context the material presented in this thesis. The background material is in four sections. The first examines the key terminology used in the field. The second is a look at over twenty high-level synthesis systems primarily from universities. The third section examines the current state of the art in commercial synthesis systems. The final section is a historical perspective on the development of SAGE

Although high-level synthesis can be traced back to the 1960's [60, 61, 62], only in recent years have the ideas of high-level synthesis started to take hold as the promised productivity gains of such tools bear fruit. Not only are design times reduced to the order of days for complex systems, but also verification requirements are less due to correctness by construction and a designer is able to work closer to the problem and therefore concentrate on algorithmic problems rather than implementation problems. During this period, the terminology of high-level synthesis has also begun to settle.

## 2.1 Terminology

High-level synthesis, also known as behavioural synthesis, can be defined as translating a behavioural description into a controller description and a network of functional building blocks with their interconnections. The behavioural description is usually specified in terms of high-level operations. These operations are similar to the

data-flow and control-flow constructs found in software programming languages as well as in the behavioural parts of hardware description languages. Examples include assignment and arithmetic functions as data-flow operations, and 'for-loops', 'if-thenelse' and sequencing as control-flow operations. Three broad stages are involved as part of the high-level synthesis process. Finding the functional building blocks to be used is called allocating. Assigning operations to functional building blocks is called binding. Assigning timeslots to each operation is called scheduling. In allocating, scheduling and binding, the target is to minimize one or more cost functions. Such cost functions are usually the area of the functional building blocks or the number of timeslots used. In the literature, the term scheduling is commonly used as the activity of applying all three of these stages optimally. The actual target hardware can range from general purpose functional units to specific hardwired datapaths that require a controller in the form of microinstructions.

Another commonly used term in the literature, is silicon compiler [84]. The broad definition of this term, fully encloses high-level synthesis, by being defined as a program, or set of programs that translates a behavioural description of a system into a chip layout. High-level synthesis, together with logic synthesis and layout form the three main stages of a silicon compiler. The dividing line between high-level synthesis and logic synthesis is not hard and fast. Nevertheless logic synthesis is generally understood to mean the synthesis of combinatorial multi-level or 2-level logic equations.

## 2.2 Research High-Level Synthesis Systems

The broad thrust of work presented in the literature has been that of heuristic solutions to the scheduling problem with relatively little attention to the interfaces that such a tool must provide. The library interface problem has been avoided by synthesis systems allocating complex objects directly. The most common example of this is the presence of the non-deterministic division operation as if it had the characteristics of a deterministic adder. Since most of the synthesis systems are targeted at specific internal logic synthesis and layout systems, the problem of general netlist generation is avoided and therefore this area, and particularly that of name space mapping in netlist generation, has not been addressed in the literature. In the area of user interaction and visualisation, some recent work has started at trying to involve the user, but generally most systems are iterative rather than interactive in nature. The main exception is work done at Carnegie-Mellon University, which, while still no where near as flexible as SAGE, has focused on user directed behavioural transformations similar to those found in software compiler technology.

#### 2.2.1 General

There are now well over thirty major high-level synthesis systems that have been developed at universities or research centres. Figure 2-1 contains a list of most of these synthesis systems with an indication of their origin and main developer. These systems form the basis of the following discussion. The systems which have not been

discussed are generally older systems like MACPITTS, whose functionality is more than addressed by the later systems.

| System                             | Origin                                             | Developer   |

|------------------------------------|----------------------------------------------------|-------------|

| ACE                                | Waterloo University, Canada                        | Buset       |

| ADAM                               | University of Southern California, USA             | Knapp       |

| CATHEDRAL II                       | Inter University Micro Electronics Center, Belgium | De Man      |

| CHIPPE                             | University of Illinois, USA                        | Pangrle     |

| CMU-DA                             | Carnegie-Mellon University, USA                    | Thomas      |

| DAA                                | Carnegie-Mellon University, USA                    | Kowalski    |

| DSL                                | Karlshrue University, Germany                      | Camposano   |

| DSS                                | University of Cincinnati, USA                      | Roy         |

| DTAS                               | California University, USA                         | Dutt        |

| FLAMEL                             | Stanford University, USA                           | Trickey     |

| HAL                                | Carleton University, Canada                        | Paulin      |

| HYPER                              | University of California at Berkeley (UCB), USA    | Chu         |

| LAGER                              | National Chiao Tung University, China & UCB, USA   | Shung       |

| LAMBDA                             | Brunel University, UK                              | Fourman     |

| RLEXT                              | University of Illinois, USA                        | Knapp       |

| MOVIE                              | Lund University, Sweden                            | Andersson   |

| OCCAM TO<br>SILICON                | Meiko, UK                                          | May         |

| OLYMPUS                            | Stanford University, USA                           | DeMicheli   |

| SEHWA                              | University of Southern California, USA             | Park        |

| SCHOLAR                            | University of Southampton, UK                      | Bergamaschi |

| SYSTEM<br>ARCHITECT'S<br>WORKBENCH | Carnegie-Mellon University, USA                    | Thomas      |

| UCB'S SYSTEM                       | UCB, USA                                           | Devadas     |

| ULYSSES                            | Rutgers and Carnegie-Mellon Universities, USA      | Bushnell    |

| VSS                                | University of California at Irvine, USA            | Lis         |

| YSC                                | IBM T.J.Watson Research Centre, USA                | Brayton     |

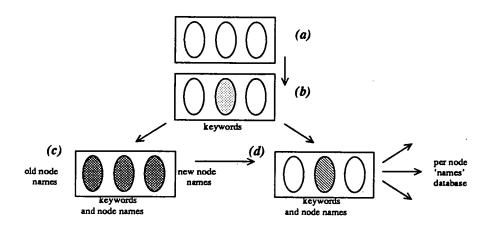

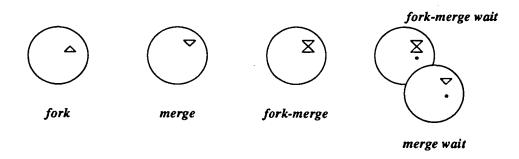

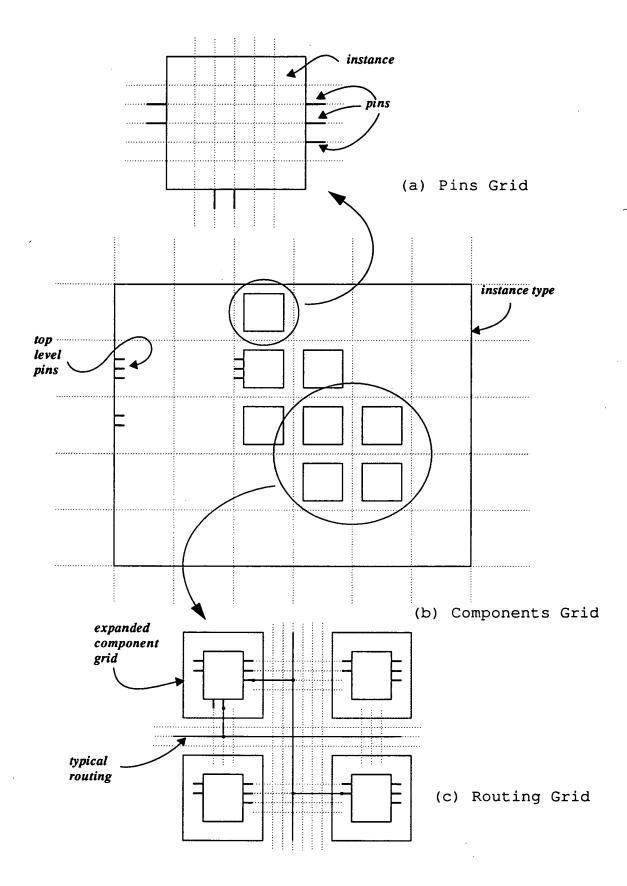

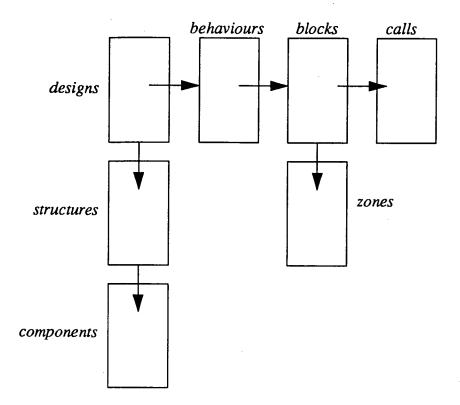

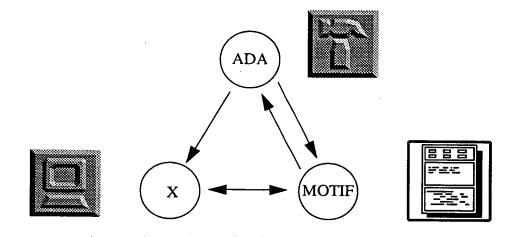

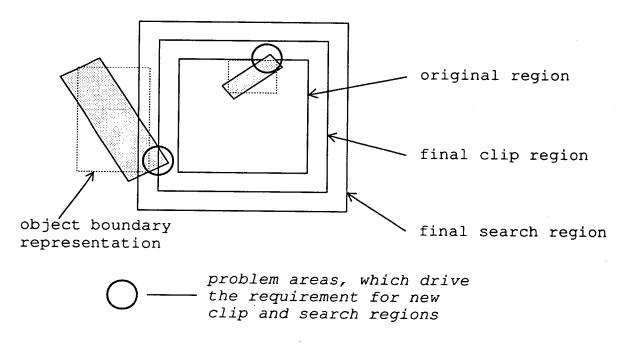

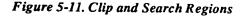

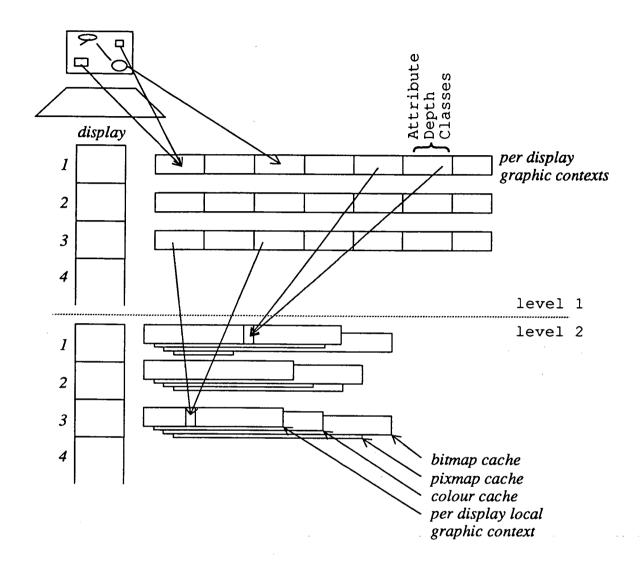

#### Figure 2-1. Major High-Level Synthesis Systems