Computer Aided Design of Printed Wiring Boards

N.A. Rose

Thesis presented for the Degree of Doctor of Philosophy of the University of Edinburgh in the Faculty of Science, April 1970.

ł

| Table | of | Contents |

|-------|----|----------|

|-------|----|----------|

| l.           | Introduction |                                                |        | l  |

|--------------|--------------|------------------------------------------------|--------|----|

|              | 1.1          | Printed Wiring Boards                          |        | 1  |

|              | 1.2          | Objective of Board Layout Design               |        | 2  |

|              | 1.3          | General Method of Layout                       |        | 3  |

|              | 1.4          | Computer System                                | ,<br>, | 4  |

| 2.           | Surv         | ey of Existing Methods of Layout               |        | 7  |

|              | 2.1          | Methods of Component Placement                 |        | 7  |

|              | 2.2          | Methods of Conductor Routing                   |        | 11 |

|              | 2.3          | Topological Methods of Layout                  |        | 15 |

| з.           | Торо         | logical Representation of a circuit            |        | 20 |

|              | 3.1          | Requirements of the Topological Representation |        | 20 |

|              | 3.2          | Elements of the Topological Representation     |        | 21 |

| ,            |              | 3.2.1 Circuit Node                             |        | 21 |

|              |              | 3.2.2 Branch Component                         |        | 22 |

|              |              | 3.2.3 Subgraph Component                       |        | 22 |

|              |              | 3.2.4 Edge Connector                           |        | 24 |

|              | 3.3          | Circuit Data Input                             |        | 25 |

|              |              | 3.3.1 Component Library                        |        | 25 |

|              |              | 3.3.2 Preparation of Circuit Data              |        | 26 |

|              | 3.4          | Data Input Subroutine                          |        | 28 |

| 4 <b>.</b> . | Const        | truction of Planar Graph                       |        | 33 |

|              | 4.1          | Planar Graph Constraints Due to Board Layout   |        | 33 |

|              | 4.2          | Methods of Constructing a Planar Graph         |        | 35 |

|              | 4.3          | Principle of Planarity Algorithm               |        | 36 |

|              |              | 4.3.1 Processing of Planar Graphs              |        | 37 |

|              |              | 4.3.2 Example of Planar Graph Construction     |        | 40 |

|              |              | 4.3.3 Processing of Non-Planar Graphs          |        | 41 |

|              |              |                                                |        |    |

•

|             |      | 4.3.4    | Insertion of Subgraph Components          | page | 45 |

|-------------|------|----------|-------------------------------------------|------|----|

|             | 4.4  | Descrip  | otion of Planarity Subroutine             |      | 45 |

|             |      | 4.4.1    | Search Procedure for Planar Paths         |      | 47 |

|             |      | 4.4.2    | Region Construction                       |      | 49 |

|             |      | 4.4.3    | Further Search Procedures                 |      | 49 |

| 5.          | Inse | rtion of | Non-Planar Branches                       |      | 51 |

|             | 5.1  | Stateme  | ent of the Problem                        |      | 51 |

|             | 5.2  | Princip  | oles of Branch Insertion                  |      | 52 |

|             | 5.3  | Inserti  | on Path Searching                         | •    | 55 |

|             |      | 5.3.1    | Component Branch Search                   |      | 56 |

|             |      | 5.3.2    | Link Branch Search                        |      | 57 |

|             | 5.4  | Path Co  | onstruction                               |      | 58 |

|             | 5.5  | Branch   | Insertion Subroutine                      |      | 60 |

| 6.          | Comp | uter Imp | elementation of Topology Algorithms       |      | 62 |

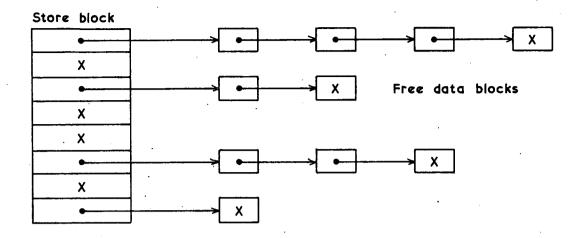

|             | 6.1  | Data St  | corage                                    |      | 62 |

|             | 6.2  | Data St  | ructure                                   | ÷    | 63 |

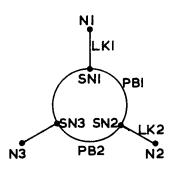

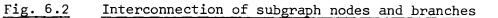

|             |      | 6.2.1    | Interconnection of Nodes and Branches     |      | 64 |

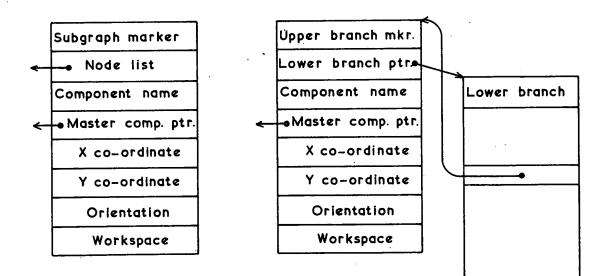

|             |      | 6.2.2    | Subgraph and Branch Components            |      | 66 |

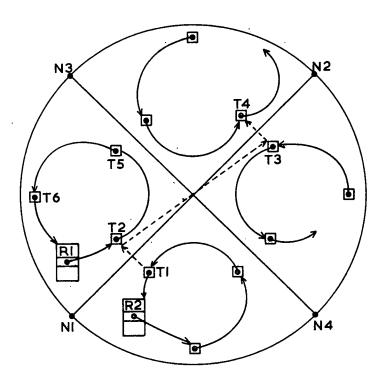

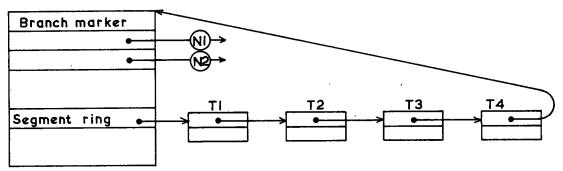

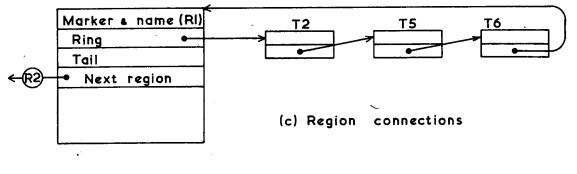

|             |      | 6.2.3    | Branch Segments and Planar Regions        |      | 68 |

|             | 6.3  | Compute  | er Language                               |      | 71 |

| <b>7.</b> . | Plac | ement an | nd Routing of Board Layout                |      | 74 |

|             | 7.1  | Conside  | eration of Layout Methods                 |      | 74 |

|             |      | 7.1.1    | Objectives of Board Layout Method         |      | 75 |

|             |      | 7.1.2    | Force-Field Method of Layout Construction |      | 76 |

|             | 7.2  | Princip  | ole of Layout Algorithm                   |      | 77 |

|             |      | 7.2.1    | Aims of Layout Algorithm                  |      | 79 |

|             | 7.3  | Slot De  | evelopment and Sorting                    |      | 80 |

|             |      | 7.3.1    | Development of Nodes and Conductors       |      | 82 |

.

|   |    |               |                                    |                 | •    |

|---|----|---------------|------------------------------------|-----------------|------|

|   |    |               | 7.3.2 Orientation and Spacing of   | Components pag  | e 85 |

|   |    |               | 7.3.3 Counting of Slot Contents    |                 | 89   |

|   |    |               | 7.3.4 Sorting of Slot Contents     |                 | 91   |

|   |    | 7.4           | Placement and Routing              |                 | 94   |

|   |    |               | 7.4.1 Component and Conductor' Pl  | acement         | 95   |

|   |    |               | 7.4.2 Placement of Crossing Cond   | uctors          | 98   |

| • |    |               | 7.4.3 Processing of Base List El   | ements          | 103  |

|   |    |               | 7.4.4 Routing of Conductors        |                 | 107  |

|   |    | 7.5           | Overall Layout Algorithm           |                 | 111  |

|   |    |               | 7.5.1 Selection of Slots           |                 | 111  |

|   |    |               | 7.5.2 Description of Flow Diagra   | m               | 113  |

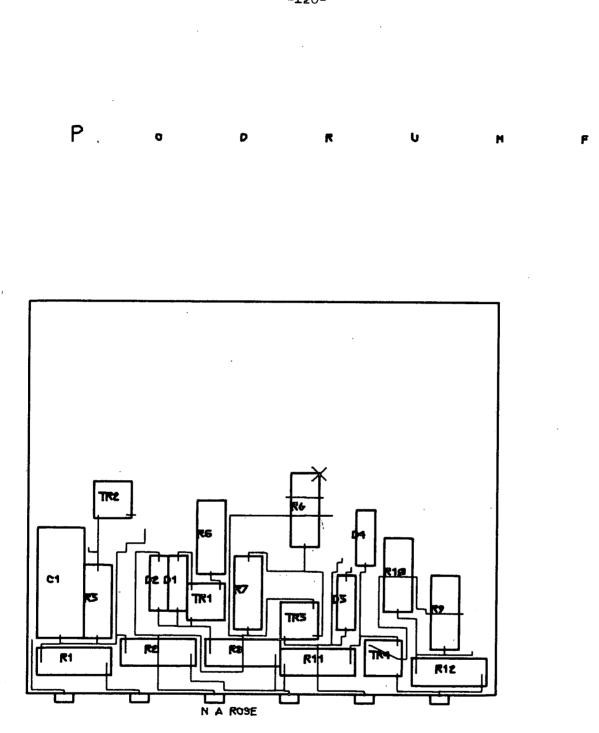

|   | 8. | Inte          | raction With Board Layout          |                 | 118  |

| · |    | 8.1           | Objectives of Interaction          |                 | 118  |

|   |    | 8.2           | Generation of Display              |                 | 119  |

|   |    | 8.3           | Interaction Facilities Provided    |                 | 123  |

|   | ·  |               | 8.3.1 DELETE Mode                  | · ·             | 123  |

|   | r  |               | 8.3.2 ORIENTATE Mode               |                 | 125  |

|   |    |               | 8.3.3 PULL Mode                    |                 | 127  |

|   |    |               | 8.3.4 MODIFY Mode                  |                 | 128  |

|   |    |               | 8.3.5 RESET, UNCHANGE and FINISH   | Modes           | 129  |

|   |    | 8.4           | Modifications to Layout Algorithm  | for Interaction | 130  |

| • |    |               | 8.4.1 Reconstruction of Layout     |                 | 130  |

| • |    |               | 8.4.2 Insertion of Slot Modifica   | tions           | 131  |

|   | 9. | Comp          | uter Implementation of Layout Algo | rithm           | 134  |

|   |    | 9.1           | Data Structure                     |                 | 134  |

|   |    | .9 <b>.</b> 2 | Free Storage System                |                 | 137  |

|   |    | 9:3           | Measurement System of Layout       |                 | 139  |

|   |    | 9.4           | Output of Board Layout             |                 | 141  |

•

| 10. Resul | ts of Layout Procedures                    | page 143 |

|-----------|--------------------------------------------|----------|

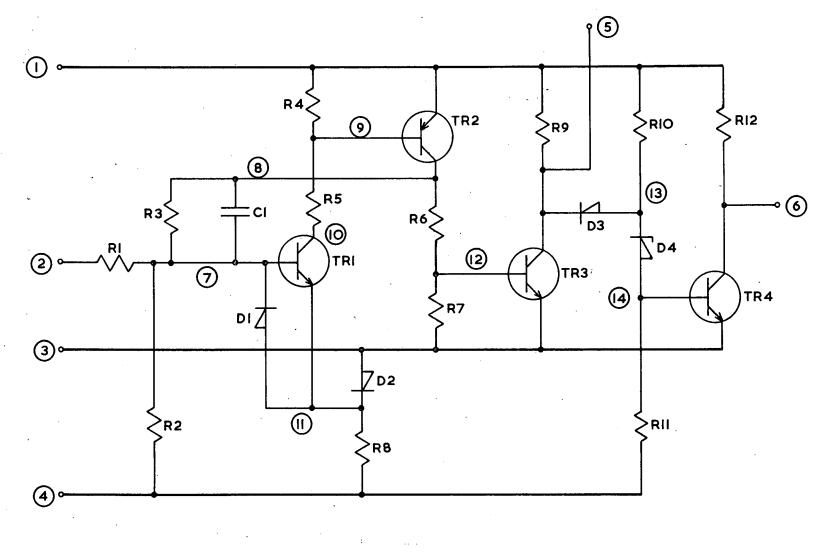

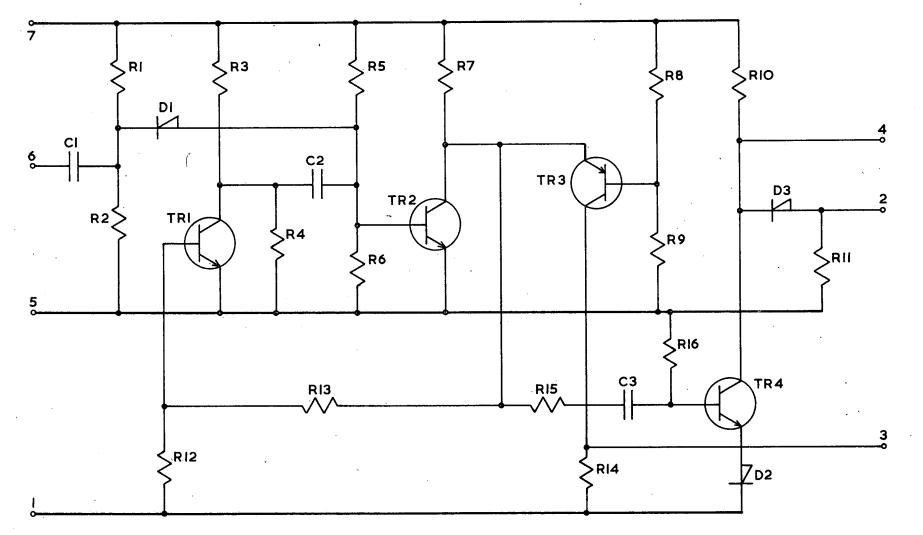

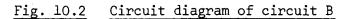

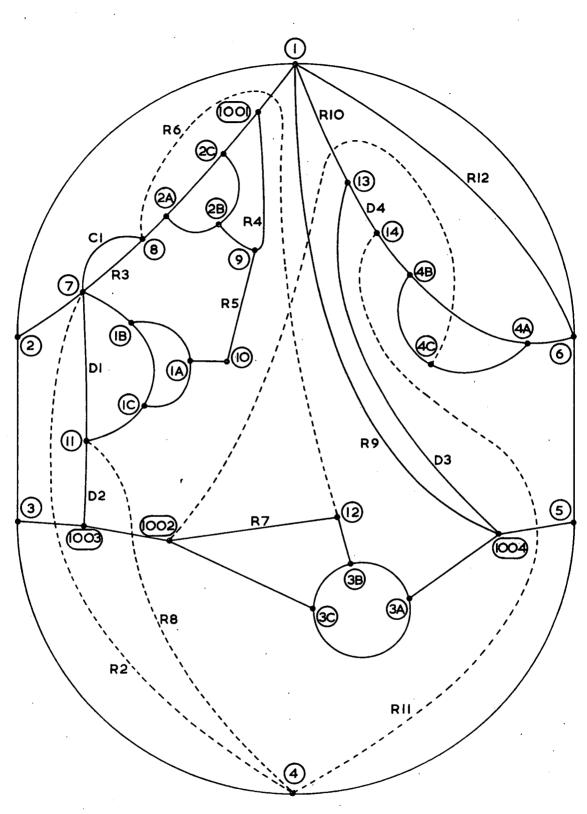

| 10.1      | Description of Circuits                    | 143      |

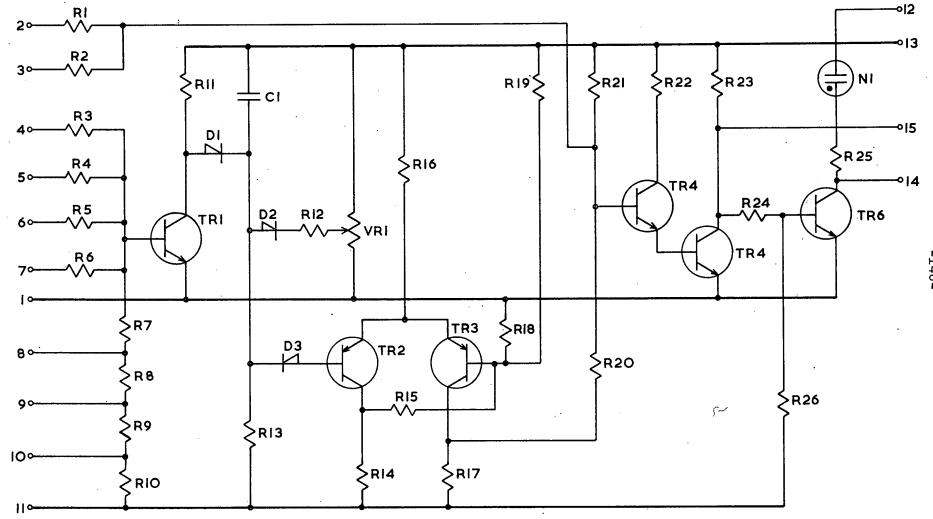

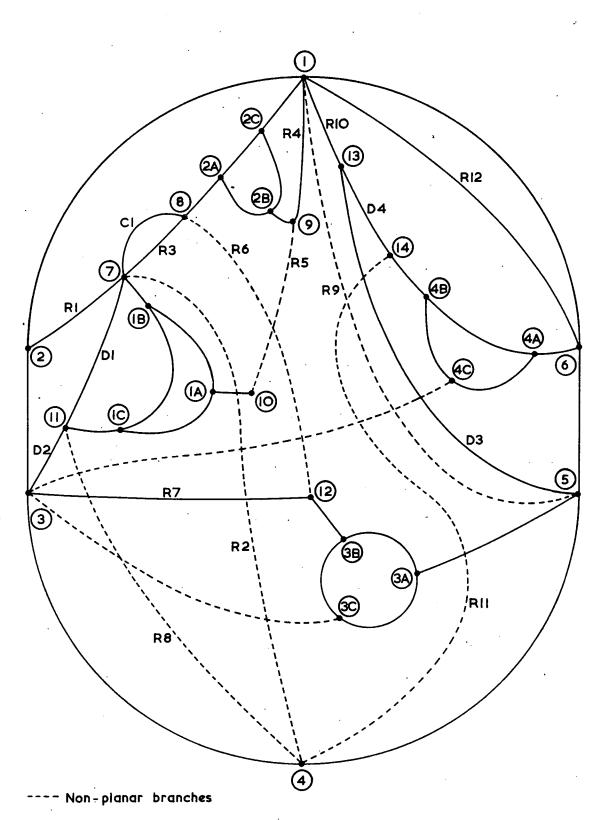

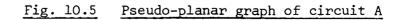

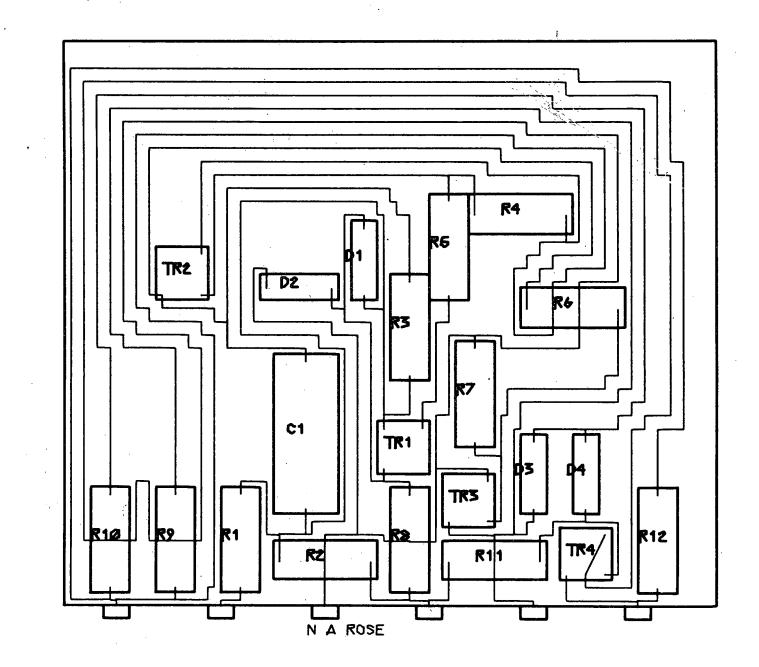

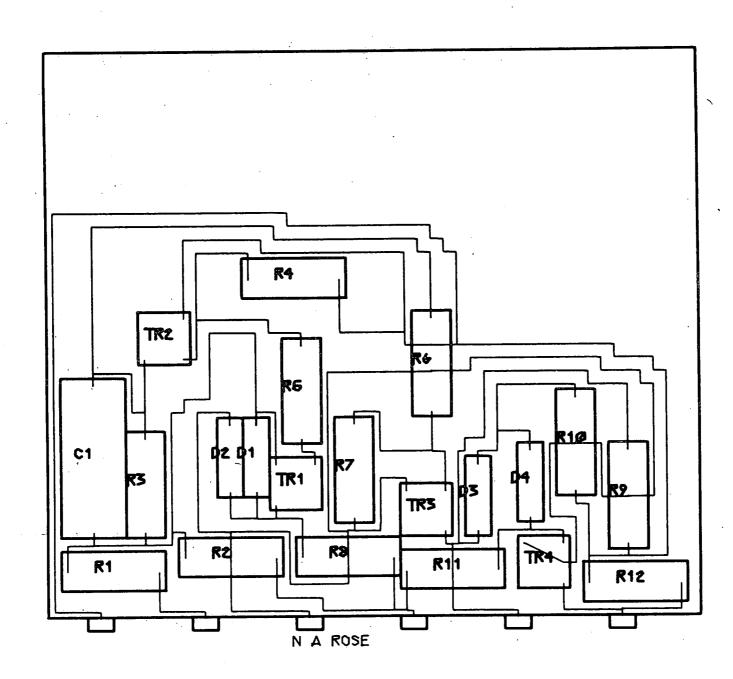

| 10.2      | Construction of Pseudo-Planar Graph        | 147      |

|           | 10.2.1 Construction of Planar Graph        | 147      |

|           | 10.2.2 Insertion of Non-Planar Branches    | 149      |

|           | 10.2.3 Comparison of Circuits              | 151      |

| 10.3      | Construction of Layouts                    | 152      |

|           | 10.3.1 Layout of Circuit A                 | 152      |

|           | 10.3.2 Layout of Circuit B                 | 154      |

|           | 10.3.3 Layout of Circuit C                 | 155      |

|           | 10.3.4 Comparison of Computer Requirements | 157      |

| 10.4      | Results of Interaction                     | 157      |

|           | 10.4.1 Interaction With Circuit A          | 158      |

|           | 10.4.2 Interaction With Circuit B          | 159      |

|           | 10.4.3 Interaction With Circuit C          | 161      |

|           | 10.4.4 Comparison of Interaction Results   | ·161     |

| 10.5      | Comparison With Manually-Generated Layout  | 162      |

| ll. Discu | ssion of Method and Improvements '         | 171      |

| 11.1      | Improvements to Topological Algorithm      | . 171    |

| 11.2      | Improvements to Layout Algorithm           | 175      |

| 11.3      | Improvements to Interaction                | 179      |

| 11.4      | Improvements to Computer Organisation      | 182      |

| 11.5      | Extension to Double Sided Boards           | 184      |

| 11.6      | Integration With an Industrial Environment | 185      |

| 11.7      | Discussion of General Points               | 187      |

|           |                                            | 1 t.     |

|           |                                            | ÷        |

|           |                                            |          |

· · ·

| · · · · · · · · · · · · · · · · · · · | <b>~</b> |

|---------------------------------------|----------|

| 12. Conclusion                        | page 189 |

| Acknowledgements                      | 190      |

| Appendix A Use of Macro Processor     | 191      |

| Appendix B Display Software           | 196      |

| Glossary of Terms                     | 204      |

| References                            | 210      |

|                                       |          |

.

· · · ·

. .

.

•

#### Chapter 1

## Introduction

Printed wiring boards are used by nearly all manufacturers of electronic equipment in the construction of their products. The design of a printed wiring board is a process which takes a considerable amount of the designer's time and is prone to errors. It is therefore desirable to develop a computer program which will quickly and accurately design printed wiring board layouts.

-1-

The design of a layout is a complex problem and many of the steps are performed intuitively by a human designer. The writing of a computer program to automatically design a layout is thus a difficult task, and many different methods have already been attempted. A method is described here which uses the principles of graph theory in designing a layout. It also enables the user to interact with the computer to improve the results.

## 1.1 Printed Wiring Boards

A printed wiring board is a thin board of insulating material upon which an electronic circuit is constructed. Each component of the circuit has a number of terminal wires or <u>pins</u> which pass through holes drilled in the board. The electrical connections required to form the circuit are printed onto the surface of the board as a set of copper paths or <u>conductors</u>. The board provides insulation between adjacent conductors but does not allow conductor paths to intersect, except where a connection is intended. The arrangement of component positions and conductor paths on a board is termed a layout.

Printed wiring board layouts may take a number of different forms. Some circuits consist of components of varying types and sizes such as resistors, capacitors, transistors, etc. termed discrete components. Other circuits consist of integrated circuit components, all the same size and shape and arranged in a fixed matrix of positions on the board. Other circuits still, contain a mixture of discrete components and integrated circuits, such as an integrated circuit amplifier with a number of feedback components.

The conductors of a printed wiring board may be placed on one side of the board, termed a <u>single sided board</u>, or on both sides, termed a <u>double sided board</u>. In some cases a board may be constructed as a set of laminations containing as many as twelve layers of conductors. The reason for using more than one layer of conductors is that on a closely packed board there may be insufficient area for all the required conductors on one side of the board. Also, it is often theoretically impossible to route all the conductors of a circuit without intersections on one side of the board. Electrical connections between the two sides of a double sided board are made by copper lined holes through the board, called through-plated holes.

External connections to the printed circuit board may be made by connecting wires to terminal pins on the board. More generally, however, all the external connections of the circuit are brought to a set of gold-plated conductors on one edge of the board, termed the <u>edge connector pins</u>. This edge of the board then plugs into a multi-way socket to make connections to external signals and power supplies.

## 1.2 Objective of Board Layout Design

The objective of this project is the development of a computer program to lay out printed wiring boards. The type of boards to be considered are single sided boards with an edge connector along one side of the board. The components placed on the board are to be

-2-

discrete components of any number of pins, including integrated circuits. There is considerable interest in laying out this type of board as the majority of electronic circuits use discrete components and many circuits may readily be constructed on single sided boards. Single sided boards have an advantage over double sided in that they cost less to produce. The program is not intended to lay out boards containing only integrated circuits in a fixed matrix of positions. This problem is preferably solved by other methods, some of which are described in chapter 2.

Ideally the program should be completely automatic in its operation so as to produce results in a minimum of time. It has, however, been found virtually impossible to specify an algorithm which will satisfy all of the constraints and conditions required by a general purpose layout program. The program therefore includes facilities for human interaction with the layout process by means of a graphical display and light pen. This enables the experience and skill of the user to be included in the design process whilst relieving him of the task of having to accurately draw the detail of the layout.

## 1.3 General Method of Layout

Most computer methods of board layout already in use divide the problem into two independent parts. These are the placement of components on the board, followed by the routing of conductors. Some of these methods are reviewed in chapter 2. The disadvantage of this approach is that there is no form of feedback from the conductor routing to the component placement stages. There is, for example, no re-arrangement of adjacent components to allow an extra conductor to pass between, such as a

-3-

designer would try in a practical case. This often means that the routing algorithm spends considerable time searching for conductor paths which are topologically impossible to complete.

The method of layout described here attempts to resolve this difficulty by constructing a topological representation of the circuit first, before the layout is constructed. This means that during component placement, due space may be allowed for the conductor paths on the board.

As the conductors are to be routed on a single side of the board, all conductor crossings must be eliminated from the layout. A topological model of the layout is constructed by the use of graph theory so as to remove all crossovers. Its method of construction is described in chapters 3 to 6. The circuit topology is then known so the physical layout may be constructed by a series of logical operations. The layout algorithms constructs small sections of the layout in turn, working from one edge of the board across to the opposite edge. Any special constraints required are incorporated into the layout by means of graphical interaction. The construction of the layout and the use of interaction are described in chapters 7 to 9. The results and possible improvements to the method are discussed in chapters 10 and 11 respectively.

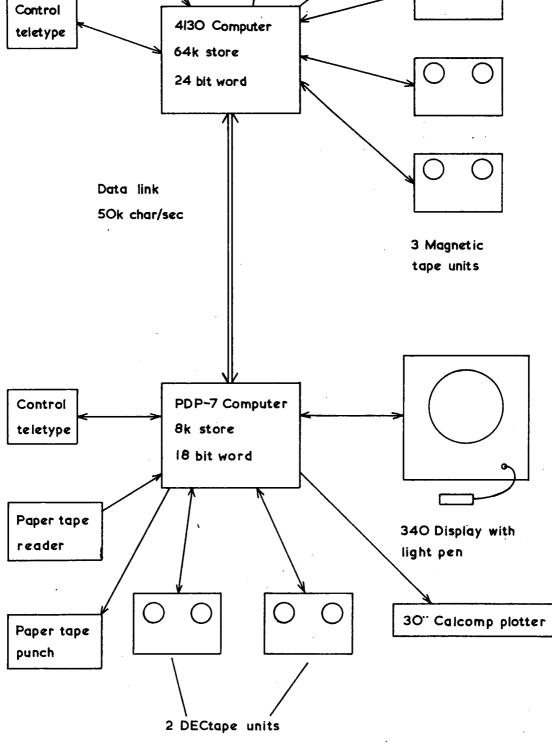

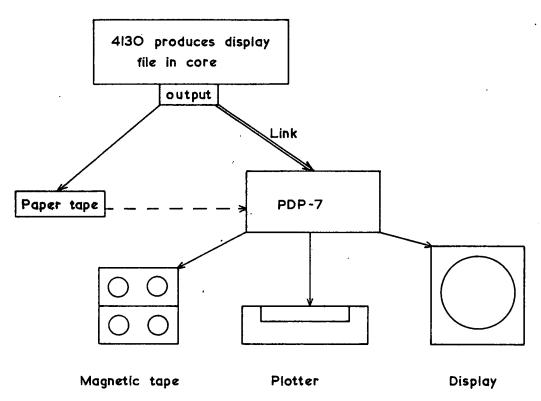

#### 1.4 Computer System

The computer system on which the layout program has been developed is described here as it has, in several ways, influenced the manner in which the program has been written. A diagram of the system is shown in Fig.1.1. The computer used for the major part of the computation is an ICL 4130. It has the usual peripherals of paper tape readers and punches, control teletype, line printer and

-4-

Computer\_Installation

-5-

2 Paper tape readers

three magnetic tape units. It is connected by a high speed data link to the PDP-7 computer. The link allows communication in both directions between the two computers at rates of up to 50,000 characters/second.

The PDP-7 computer deals with the maintenance of the display and the servicing of light pen interrupts during interaction. The Type 340 display with light.pen operates asynchronously with the computer but shares its core store for storage of display file. The useful area of the display is  $9\frac{1}{2}$  inches square with a resolution of 1024 points along each axis. The other peripherals of the computer include a paper tape reader and punch, a control teletype, two DECtape magnetic tape units and a 30 inch wide drum type Calcomp plotter.

The ICL 4130 computer is programmed in FORTRAN IV using the magnetic tape based FORTRAN system. Due to the limitations of core space and the maximum allowable number of subroutines, the overall layout program is split into two parts and run as two consecutive programs. These are the topological part and the board layout part. No special programming is required for the PDP-7 computer as previously developed display and interaction software is used (see Appendix B).

A note is appropriate here on the use of the words "topological" and "graphical". "Topological" is used to describe the abstract structure, or graph, of the circuit to be laid out before it has been given physical dimensions. "Graphical" is used to describe the visual display of the board layout whilst it is being constructed. These two words will be used in the sense just given to avoid any confusion of terms.

-6-

Chapter 2 Survey of Existing Methods of Layout

This chapter presents a survey of some of the known methods of laying out printed wiring boards by computer. Most methods tend to divide the problem into two separate parts; placement of components followed by routing of conductors. Some topological methods of constructing layouts have been proposed but none of them appear to have been put into practice.

## 2.1 Methods of Component Placement

Most of the papers published on board layout tend to concentrate on circuits in which all the components are integrated circuits of the same size and shape. This means that the board may be divided into a fixed matrix of positions such that each component occupies one position. The component placement problem then resolves itself into one of deciding into which position to place each component. The criterion of a good placement is usually taken to be one which gives a minimum total conductor length. The desired result is to reduce conductor congestion on the board and to reduce the effects of capacitance between adjacent conductors. Conductor lengths are assumed to be the point - to - point distances between connected components as the actual conductor paths are not known at this stage.

The method described by Rutman (30) uses the idea of "unconnected sets" of components. The components are given an initial placement on the board, either randomly or manually. They are sorted into a number of unconnected sets such that none of the components within a set are interconnected. An unconnected set of components is then removed from the board and each component in the set is systematically placed in every vacant space on the board in turn. The total length of interconnections between the component

-7-

and those already on the board is calculated at each point. As the component belongs to an unconnected set, its length of interconnections is independent of the remaining components in the set. A matrix of all the component positions and conductor lengths for the set is constructed. From the matrix, the optimum placement solution for the set is calculated such that the total wire length is a minimum. The procedure is repeated for all of the unconnected sets. The layout solution is further improved by interchanging the positions of connected components in an attempt to reduce the lengths of the longest wires. The method should result in a compact layout but it is only feasible for circuits in which all the components are of the same size. Also, the method takes no account of the topology of conductor connections.

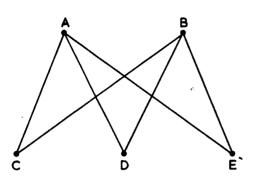

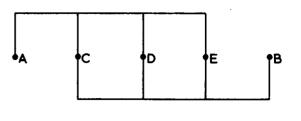

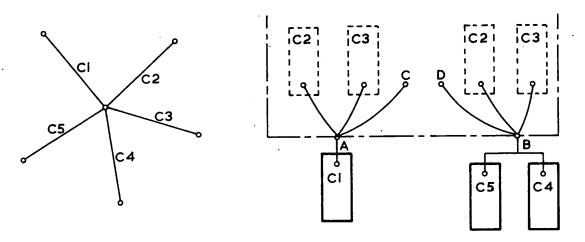

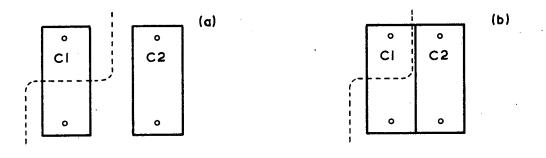

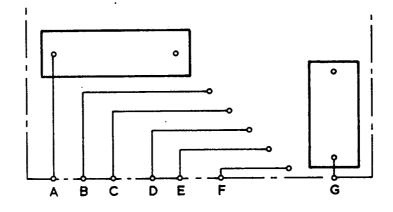

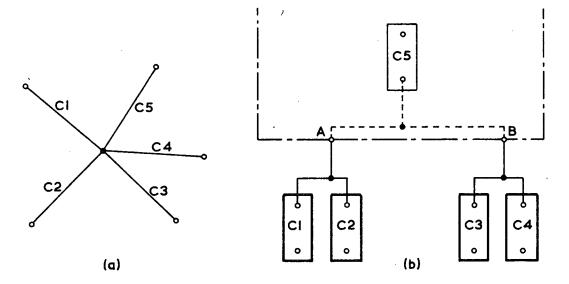

The method described by Mamelak (22) is used for the placement of computer logic modules. From the logic diagram of the circuit to be laid out, a connection matrix of components, or logic modules, is constructed. The components may be divided into a set of "chains" such that each chain consists of an interconnected group of components, two of which are connected at least to the remaining components of the group. A chain is illustrated in Fig. 2.1(a), where components A and B are the two "vertices" of the chain and the remaining components C, D and E are the "base points" of the chain. One property of a chain is that it may be rearranged as shown in Fig. 2.1(b) to reduce the number of conductor intersections.

A permutation procedure is used to divide the components into a set of chains such that each chain may be placed on one row of positions of the board. The row chosen for each chain depends

-8-

(a) Basic chain

(b) Placement in row of board

#### Fig.2.1 Chain of Components

on the total length of interconnections with other chains. Thus the y co-ordinate of each component is determined and the connections between the components of a chain may be made in the x direction on one layer of the board with a minimum number of intersections. A similar procedure is used to assign an x co-ordinate to each component and to reduce the number of intersections between conductors in the y direction on the second layer of the board. Although this method is only suitable for integrated circuit layouts, it does take some account of the wiring topology by attempting to reduce the number of intersections.

The method described by Case (6) is used to assign the positions of small circuit cards on a large "mother board". The method allows an engineer to specify the positions of selected cards. Of the remaining cards, one is selected and tried in every vacant position on the board. The total length of conductors between the card and the already assigned cards is calculated at each position. The card is placed in the position that gives minimum conductor length, and the procedure is then repeated with

-9-

each of the remaining cards. It does not give an optimum placement of components so a further procedure is used to improve the placement. The second procedure attempts to interchange the position of each card with every other card on the board. If an interchange results in a reduction of total wire length, the card positions are reassigned. Again, this method produces a compact layout with low total wire length but does not consider the wiring topology.

The method described by Dunne (7) constructs a layout in stages rather than attempting component interchanges as described in the previous methods. The algorithm selects a location on the board which is nearest to the components which have already been placed. (Initially only the edge connector is placed.) From the list of components to be placed, the one which has the greatest number of connections to the already-placed layout is selected. The algorithm then attempts to route the conductors to the component, using a double sided board. If the routing is not successful, further components are tried in the given board location. If a solution still cannot be found, a new board location is chosen. The procedure is repeated for each component in turn. The method has only been used for integrated circuit components but could possibly be modified for discrete components. It gives the first solution encountered and does not attempt to find the optimum solution. The method does, however, check that all conductor paths can be routed to a component before placing it.

The one method encountered which deals specifically with discrete components is the ACCEL program (9). Component positions are assigned by a "force placement" method. Each conductor of a circuit is assumed to be an "elastic wire" such that it exerts a force of

-10-

attraction, proportional to its length, on the component at either end. The effect of this force is to group together components which are closely connected. In addition, forces of repulsion exist between adjacent components to prevent component overlap. The conductors also exert a "torque" upon components in order to select the best orientation for each component.

The components are given an initial arbitrary placement. The program then operates in an iterative manner, summing the forces on each component in turn and moving it towards an equilibrium position. The forces of attraction are initially high and the forces of repulsion low so as to rapidly improve the layout. After a number of iterations, the components are constrained to a vertical or horizontal position, whichever is nearest to the current component orientation. The forces of repulsion are increased to prevent component overlap and the iterations are continued until component movements are negligible. The method thus gives a good placement of different-sized components. Although closely connected components are grouped together to reduce the total conductor length, no account is taken of conductor topology. The method of conductor routing is described in the next section. A similar method is used by Leevers (20) for the placement of integrated circuits. In the final stages of this method, components are forced onto the nearest allowable board positions.

## 2.2 Methods of Conductor Routing

Nearly all methods of conductor routing start with the assumption that the components have already been placed. The problem is thus one of connecting together pairs of terminals.

-11-

The connecting paths must be routed so that no paths intersect and it is desirable that the total conductor length is a minimum. Most methods assume that a double sided printed wiring board is used.

The classic method for constructing conductor paths is Lee's algorithm (19). The board is divided into a grid of squares. Those which contain obstacles such as component terminals or conductors are marked as being occupied. The two squares to be connected together, the start and target squares, are specially marked. All unoccupied squares around the start square are marked with a '1'. All the unoccupied around these are marked with a '2' and so on. A wave of marked squares thus spreads out from the start square until the target square is reached. It is then a simple matter to trace a path back to the start square. The algorithm is generally modified because the search wave spreads in all directions from the start square, involving unnecessary computing time. Secondly, the algorithm will find all the paths of equal length between two points but has no way of distinguishing between the different paths.

The ACCEL method of conductor routing (9) uses a novel topographical model of the layout for routing. The board is divided into a grid of squares, each of which may be assigned an "altitude". Initially all the squares are set to zero altitude. Any obstacles such as component pins or holes in the board are assigned an altitude so as to form a "peak". The edges of the board are represented by a ridge around the layout. To find a path between two pins, the target peak is depressed to a negative altitude. A modified version of Lee's algorithm is then used to find the most downhill path from the start to the target pin.

-12-

The program has several phases of operation. Firstly, all paths are routed simultaneously for a number of iterations. Paths successfully completed are inserted as ridges in the topographical model so as to repel conductors routed in later phases and avoid congestion on the board. Secondly,the procedure is repeated with all the remaining conductors routed simultaneously. Thirdly, the procedure is repeated with the remaining conductors, routing one conductor at a time. The method can be used for either single or double sided boards. In the case of a double sided board, the whole procedure is performed on one side of the board, then repeated for the remaining conductors on the second side of the board.

Other modifications may be made to Lee's algorithm in order to improve its efficiency, as illustrated by Mikami and Tabuchi (24). In this method a double sided board is used with all horizontal conductors routed on one side and all vertical conductors routed on the other side. This avoids the problem of crossing conductors but restricts the conductor paths which may be formed. The board is again divided into a grid but instead of searching square-by-square, the search is performed line-by-line. From the start square, four lines, limited in length by existing obstacles, give the possible directions of the search. Each of these lines may pass through the board at a number of through-plated holes. Each of the throughplated holes may therefore be developed into two more lines on the opposite side of the board. The procedure is continued until the target square is reached. The line-by-line method of searching is considerably faster and uses less storage space than Lee's algorithm.

Two methods of conductor routing on double sided boards are described by Kodres and Lippmann (13). The first approach sorts sets

-13-

of interconnected pins, or nets, into a list of decreasing net size. The size of a net is defined by the perimeter of the rectangle surrounding all pins in the net. To route a given net, the pins furthest apart are connected by a path which uses the least number of through holes. The remaining pins of the net are then connected onto the path already routed. Paths are only chosen which lie within the rectangle of the net and which use less than a specified number of through holes. These constraints help to reduce board congestion. When all of the nets have been processed, any remaining conductors are routed by using Lee's algorithm to search exhaustively for a path.

The second approach divides the board into a grid of squares and assigns a congestion cost to each square. A square is given a high cost if it can be used by many nets, so that conductor paths will tend to avoid congested parts of the board. The nets are connected one at a time in order of increasing conductor length. For each connection, the path is chosen which has the lowest congestion cost and which uses the least number of through holes. The two methods described avoid the problem of conductor crossings by routing conductors horizontally on one side of the board and vertically on the other side.

A method of conductor routing for double sided boards, using graphical interaction, is described by Leevers (20). A graphical display and light pen are used to display and modify one side of the board at a time. Each conductor is initially displayed as a Straight line joining two end points. Near-vertical conductors are assigned to one side of the board and near-horizontal to the other

-14-

to the other although the assignment may later be altered if desired. Low level routing facilities allow conductors to be routed around obstacles by the insertion of intermediate corners, and diagonal conductors to be replaced automatically by conductors of horizontal and vertical sections. Higher lever facilities attempt to automatically route each conductor in turn by application of the low level facilities. The program initially attempts automatic routing and usually succeeds with many of the conductors. In cases where a path cannot be found, the operator intervenes and uses the low level facilities, by means of the light pen, to re-order part of the layout. The skill of the operator is thus used to assist the program in difficult parts of the layout. In later stages of the layout, the method relies heavily on the operator to find conductor paths.

There are a number of advantages and disadvantages of splitting the layout problem into the separated parts of placement and routing. These are discussed further in Chapter 7.1.

## 2.3 Topological Methods of Layout

The principle of the topological methods of layout is to minimise either the number of conductor crossings or the number of conductors removed from the layout to eliminate crossings. Several algorithms have been programmed but none appear to have been taken to the stage of actually producing a layout.

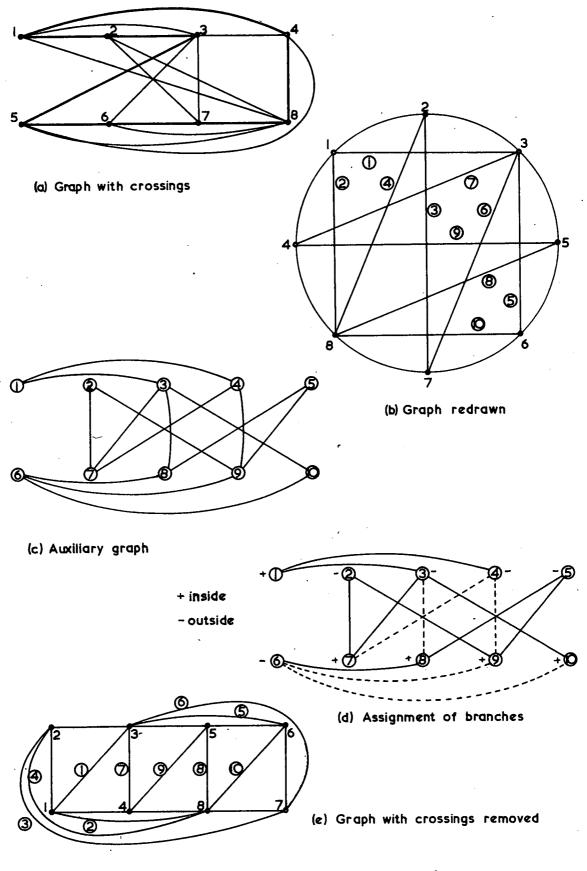

In the method described by Bader (1), the branches of a graph are re-arranged, and some removed, so as to eliminate all crossings. An example from the paper is shown in Fig. 2.2. The graph is searched for a closed circuit which includes as many of the nodes as possible; in this case all the nodes, as shown in

-15-

# Fig.2.2 Construction of a Planar Graph

p.

Fig. 2.2(a). The graph is redrawn with the circuit on the outside edge and the remaining branches within as shown in Fig. 2.2(b). An auxiliary graph is then drawn, Fig. 2.2(c), whose nodes correspond to the branches on the inside of Fig. 2.2(b). Pairs of branches which conflict in Fig. 2.2(b) are represented by branches joining the corresponding nodes in the auxiliary graph. The branches of Fig. 2.2(b) may be assigned to either the inside or the outside of the closed circuit in order to remove crossings. The assignment is made by starting with an arbitrary node in Fig. 2.2(c), node 1, and assigning it to the inside. Adjacent nodes are then assigned to the outside and so on, as shown in Fig. 2.2(d). If the graph is non-planar, branches are removed at this stage. The graph may then be redrawn without crossings as shown in Fig. 2.2(e). The method has been further developed and programmed for computer by Fisher and Wing (8). A matrix method is used to process the graph so that nonplanar branches are identified and removed from the graph.

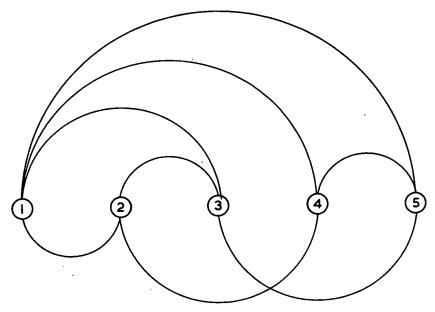

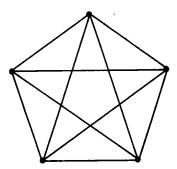

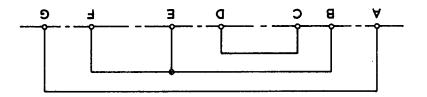

The algorithm described by Nicholson (26) minimises the number of crossings in a graph, rather than deleting non-planar branches. In this method, the modes of the graph represent components and the branches represent interconnections. The nodes are arranged in a straight line and the branches are drawn as semicircles above or below the node line as shown in Fig. 2.3. The graph may then be described by a permutation of the order of nodes and the direction of the branch semicircles. An initial permutation is constructed by selecting an initial node then adding the node which has the most connections to the existing part of the permutation. This is repeated for all nodes, inserting each one into a position which gives least crossings. An iterative procedure

-17-

then changes the order of nodes in the permutation in an attempt to further reduce the number of crossings.

Fig.2.3

Permutation Representation of a Graph

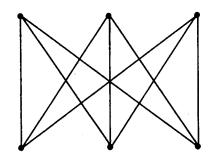

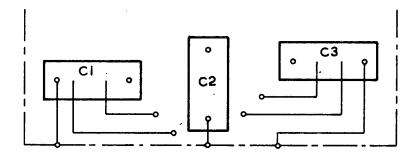

A method of constructing a planar graph of components and interconnections is described by Rowley (29). The circuit is defined by a list of components and a list of interconnections. A set of branches is selected so that a "tree" of all the components may be constructed. Each new component added to the tree is connected by one branch only as shown in Fig. 2.4. A "tree list" of all the component pins in order around the tree is made as shown by the dotted path in Fig. 2.4. Any other interconnection in the circuit will divide the tree list into two parts at the points of connection. Two branches are in conflict if the two parts of the tree list formed by one branch each contain a node of the other branch. A matrix of all the branch conflicts is then constructed. From the matrix, a set of conductors is selected such that the number of non-planar branches removed from the graph is a minimum. The resultant graph is not necessarily the optimum planar graph as it is dependent on the branches selected for the

-18-

Fig.2.4 Formation of Tree List

initial tree.

The advantages and disadvantages of the topological methods described above are discussed further in Chapter 4.2.

#### Chapter 3 Topological Representation of a Circuit

Any computer program that generates a printed wiring board layout must have a method of representing the layout within the computer. This chapter describes how the topological representation of a circuit is constructed from the computer input data. The representation is later used to construct a topological model of the layout. The ways in which the circuit representation is actually programmed are described in Chapter 6.

## 3.1 Requirements of the Topological Representation

The groups of data required for the construction of a layout are the circuit diagram, the physical dimensions of the components and the dimensions of the board. The circuit diagram basically describes the types of components used and the way in which they are interconnected. The information on the circuit diagram should therefore be coded into a suitable format for input to the computer.

The first part of the layout method described here deals with the construction of a topological model of the layout. In developing this model, the circuit is investigated for planarity by examining the way in which components are connected together. The topological representation should therefore indicate the order in which components are connected, without being concerned with the physical co-ordinates of components and conductors.

There are two widely-used methods of representing, within a computer, the interconnections of a graph. The first method is a matrix representation of the graph. Usually, the rows and columns of the matrix represent the nodes and branches respectively. Each element of the matrix is then marked to indicate the incidence, or non-incidence,

-20-

of a given node and branch. The second method of representing a graph uses a ring data structure in which data blocks are used to represent nodes and branches. Pointers between the data blocks indicate the interconnections between nodes and branches.

The method of representation chosen for the layout algorithm is the ring data structure. Although an electronic circuit often has a large number of nodes and branches, there are generally few branches connected to each node. A matrix representation would therefore require a large matrix in which most of the elements were empty. A data structure provides direct pointers from, say, a branch to its two nodes. To obtain the same information from a matrix, the whole branch column of the matrix would have to be searched. A further advantage of the data structure is that additional data such as component name, type of branch, or display file may readily be associated with each data block.

## 3.2 Elements of the Topological Representation

The graph of an electronic circuit is constructed from a number of different types of nodes and branches. Circuit nodes have a corresponding node in the graph but components have a different representation depending on whether they have two, or more, pins. The circuit elements and their corresponding graph representations are described below.

## 3.2.1 Circuit Node

A circuit node is a point of common electrical connection of two or more components. The corresponding node in the graph has no physical representation. It merely fulfils the function of listing all the components connected to a common point, or to a given

-21-

conductor on the board.

## 3.2.2 Branch Component

A component with two connecting wires or pins such as a resistor or a capacitor is termed a branch component. It is represented in the graph by a <u>component branch</u> and is connected between two nodes. Each of the nodes is the abstract representation of a connection. A component branch is therefore physically equivalent to the component together with part of the conductor paths at each end of the component.

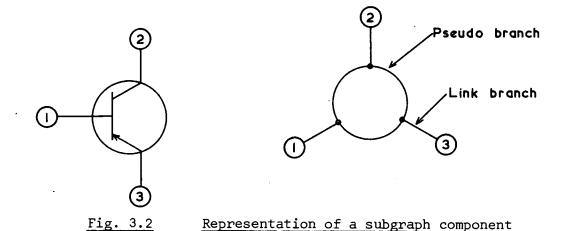

#### 3.2.3 Subgraph Component

In representing a component with more than two pins, such as a transistor or an integrated circuit, several problems arise. The first problem is due to the physical dimensions of the component and the fact that each component pin is connected to a circuit node. In constructing a planar graph of a circuit it may happen that a number of branches, or conductors, have to pass between two particular nodes. If the nodes are connected to two pins of a component, it is quite probable that there would be insufficient space for the conductors to physically pass between the pins. To prevent such an occurrence, each pin of the component is connected to its two adjacent pins by a pseudo branch. Also, each pin of the component is represented by a subgraph node so that every pseudo branch is connected between two subgraph nodes. The pseudo branches initially prevent any conductors from passing between the component pins and they keep all the pins of the component together in a closed planar region. Because of these functions, pseudo branches may never be removed from the graph.

-22-

Assuming that multi-pin components are represented by a ring of pseudo branches, a planar graph of the circuit could be constructed, containing these components as subgraphs. A second problem which is not resolved by some other methods is that all of the subgraph components must have the same orientation in the planar graph. The physical analogy is that all the components are mounted on the same side of the board. Defining a component as a ring of pseudo branches readily enables the orientation of a component to be checked during the planarity algorithm.

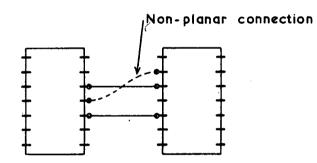

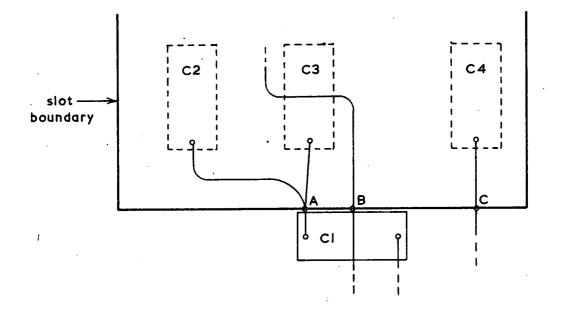

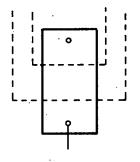

The third problem in representing a multi-pin component lies in the deletion of non-planar branches between closely connected components. An example of two closely connected integrated circuits is shown in Fig. 3.1. A connection has to be removed to make the

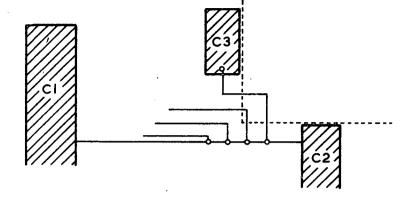

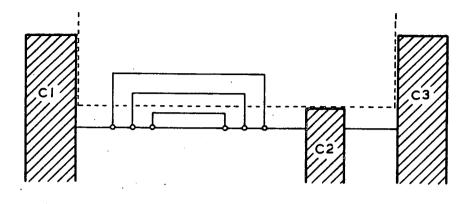

## Fig. 3.1 Closely connected components

graph planar. No pseudo branches can be removed however, because the planarity of the component pins would be lost. Each subgraph node has a <u>link branch</u> connecting it to the corresponding circuit node. The physical representation of a link branch is a length of conductor connecting the component pin to the rest of the circuit node. In the event of a non-planarity, one or more of the component link branches may be removed. The circuit diagram of a transistor

-23-

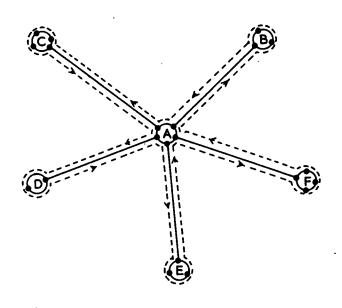

and its corresponding topological representation are shown in Fig. 3.2 as an example.

The complete set of subgraph nodes, pseudo branches and link branches for a component is termed a <u>subgraph component</u>, or subgraph. The nodes and branches of a subgraph are represented by a set of node and branch data blocks. They could be represented more compactly by a single data block. The graph structure would then no longer be compatible with circuit nodes and branch components however, and programming would thus be more difficult.

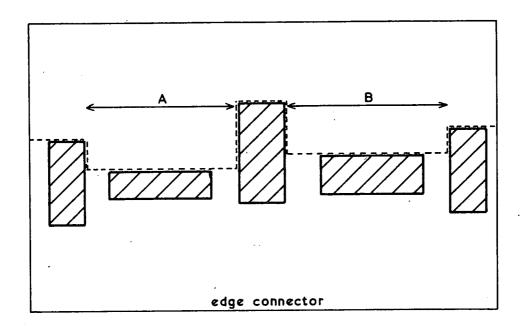

## 3.2.4 Edge connector

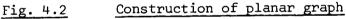

The edge connector of a printed wiring board consists of a row of pins or terminals along one edge of the board. As no conductors can pass between the edge pins, their corresponding nodes in the graph must be adjacent to each other. This is ensured by connecting the nodes into a path by a series of pseudo branches, the order of nodes in the path being the same as the order of edge pins on the board. A further pseudo branch is connected between the first and last nodes of the path, thus forming it into a closed loop. This pseudo branch therefore represents the outside edge of

-24-

of the board, apart from the edge connector. The closed loop of pseudo branches serves as a boundary within which the topological model must lie.

## 3.3 Circuit Data Input

The first step in generating a layout is to prepare the circuit data in a suitable format for input to the computer. Two groups of data are required for the construction of the topological model of a layout. The first is a library of component data which may be common to all circuits laid out. The second is a list of components and their interconnections for the particular circuit to be laid out.

## 3.3.1 Component Library

When constructing a layout, certain data is required for each component, such as its physical dimensions and its number of connecting pins. Most circuits contain several instances of each different type of component. The most economic way to describe the components therefore is to give each one a type number then associate one full description of a component with each different type number. In other words, a library of component descriptions is generated. In a manufacturing organisation this information would probably be stored as part of a data bank which would hold a list of all the types of components ever used together with their electrical and physical characteristics. For the purposes of the method described here, an elementary component library is associated with the circuit data.

The data for each type of component is stored in a <u>master</u> <u>component block</u>. The master component blocks are held together in a list and each one is given a unique name. For example, the blocks representing  $\frac{1}{4}$  watt resistors,  $\frac{1}{2}$  watt resistors and transistors may

-25-

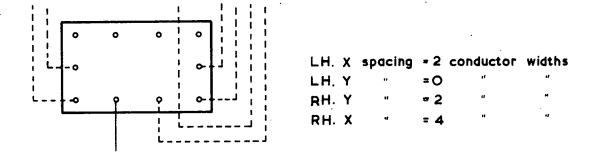

be called RES1, RES2 and TRAN respectively. The size of a component is defined by a boundary rectangle. It allows space for the component itself, space for connections and fixings and clearances for component spacing. This simplifies board layout as component rectangles may then be placed directly adjacent to each other without further computation of clearances. A master component block stores data on the dimensions of the component rectangle, the number of component pins and the co-ordinates of each pin relative to the component rectangle. Several dummy master component blocks are used to indicate certain functions during data input. These are described in the next section.

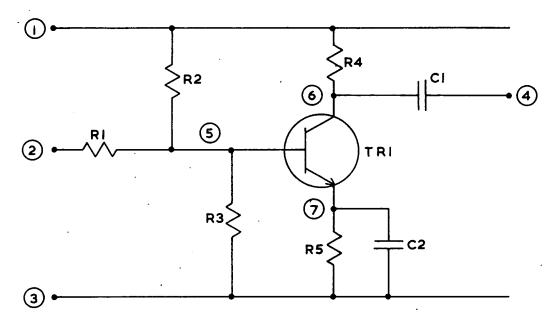

## 3.3.2 Preparation of Circuit Data

To prepare data from a circuit diagram, each electrical node is first labelled with a unique positive integer. A simple example is shown in Fig. 3.3(a). The connections of each component may therefore be described by listing the nodes to which it is connected. The correct orientation of component connections is ensured by adopting a convention of node numbering. Two pin components with a marked pin of polarity such as diodes or electrolytic capacitors are listed with the marked pin as the first node number. Multi-pin components have their pins ordered in a clockwise direction, looking from the conductor side of the board. The first pin in the node list corresponds to the first pin co-ordinate in the master component block.

To code the data from a circuit diagram, each component is described by its name and a list of its node numbers. An example of data coding is illustrated in Fig. 3.3(b); the component library is not shown. Components of the same type are listed consecutively in

-26-

· (a) Circuit diagram

7

| RES       |     |     |

|-----------|-----|-----|

| RI        | 2   | 5   |

| R2        | 1   | 5   |

| R3        | · 3 | 5   |

| <b>R4</b> | I   | 6   |

| R5 ·      | 3   | 7   |

| R.        | - 1 | -1  |

| CAP       |     |     |

| CI        | 4   | 6   |

| C2        | 3   | 7   |

| С         | -1  | - 1 |

| TRAN      |     |     |

| TRI       | 6   | 5   |

| TR        | I   | 1   |

| EDGE      |     |     |

|           | 1   |     |

|           | 2   | -   |

|           | 3   |     |

|           | 4   |     |

|           | -1  |     |

| STOP      |     |     |

(b) Data input format

<u>Fig. 3.3</u>

Preparation of circuit data

-27-

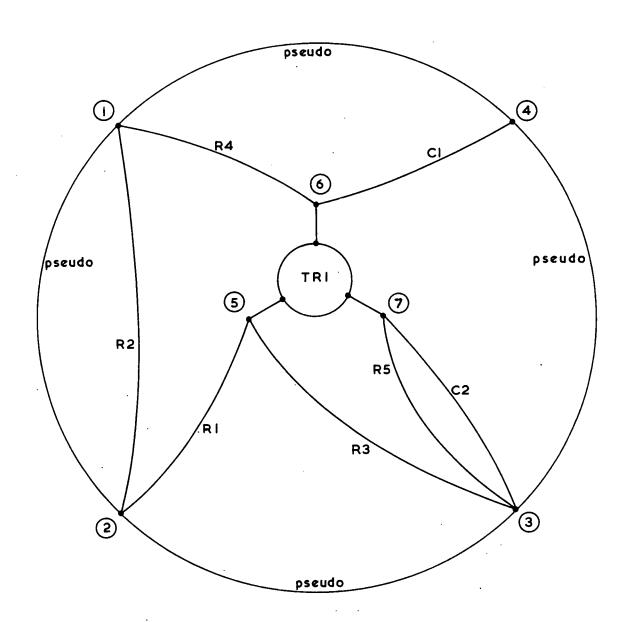

a group. Each group is preceded by the name of its master component block and is terminated by a dummy component with negative node numbers. This method is used because of the difficulties of reading in data under FORTRAN FORMAT statements. Two additional dummy master component block names are used. The name EDGE indicates that the following node numbers are the nodes of the edge connector, in the correct order. The list of edge nodes is terminated by a negative node number. The name STOP indicates that all of the circuit data has been specified. An example of a topological representation of the circuit shown in Fig. 3.3 is illustrated in Fig. 3.4.

## 3.4 Data Input Subroutine

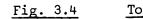

A FORTRAN subroutine called DATAIN has been developed to read in the component library and circuit data and to construct the corresponding data structure. The flow diagram of the subroutine is shown in Fig. 3.5 and the type of data structure constructed is described in detail in Chapter 6.

The subroutine starts by reading in the component library data. As each component type is read in, a new block is created and added to the list of master component blocks. The master component name, the number of pins and the component dimensions are stored in the block. This is followed by a list of the pin co-ordinates. A master component with one pin is used to indicate the edge connector. One with no pins is used to signify the end of the library data and its name, STOP, indicates the end of the circuit data.

Following the component library, the name of the next component group is read in. The component library is searched to find the master component block with the same name. The block then gives the

-28-

# Topological representation of circuit

# Fig. 3.5 Flow diagram of data input subroutine

number of pins of each component in the group. If no corresponding master component block can be found, an error message is printed out and the program stops.

For groups of two pin components, each component name and its two node numbers are read in turn. A list of nodes is kept in the data structure and this list is searched to find the two nodes of each component. If either of the nodes does not yet exist in the list, a new hode block is created and added to the list. The data blocks for a branch component are then created and linked to the existing data structure in the manner described in Chapter 6. The procedure is repeated with each component until the dummy component at the end of the group is encountered. The subroutine then reads in the name of the next component group.

For groups of components with more than two pins, the subroutine reads in the name and appropriate number of nodes for each component. Any new nodes are added to the node list. The required data blocks of subgraph nodes, pseudo branches and link branches are then created for the component and linked into the existing data structure. The subroutine is designed to deal with subgraph components of any number of pins. The appropriate number of pins is merely obtained from the component library. The procedure is repeated for each component in '.

The component group name called EDGE indicates that the next group of numbers is a list of edge connector nodes. The node numbers are read into an array until the dummy end node is reached. Each node is then connected to the next by a pseudo branch in the data structure. The last node is connected to the first by a further pseudo branch. The subroutine then reads in the next component group name.

-31-

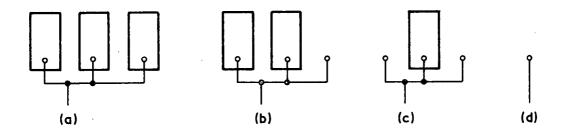

The component group name called STOP indicates that the circuit data input is complete. An elementary check on the data is then performed. Each node in the circuit node list is checked to ensure that it has at least two connected branches. Any node which has only one connected branch causes an error message to be printed. This check detects some coding and typing errors. The data structure now contains all the data related to the interconnection of circuit components.

#### Chapter 4

#### Construction of Planar Graph

The type of board layout considered consists of a set of components placed on one side of the board, a set of conductor paths on the second side and a set of connection pins along one edge of the board. The main objective in producing a board layout is to arrange the components and their interconnecting conductors so that no conductor paths intersect. It has already been shown that a graph may be developed to represent the interconnections of a circuit. This chapter describes an algorithm by which the branches of the graph are ordered, and some removed, so as to produce a planar graph with no branch intersections. Chapter 5 then describes a method by which the non-planar branches are inserted back into the graph.

## 4.1. Planar Graph Constraints Due to Board Layout

A planar graph is defined as one which may be drawn on a plane in such a way that its branches intersect only at their end points. The plane which is of interest in the board layout problem is the conductor side of a printed wiring board. It therefore follows that the graph representing a circuit must be planar to avoid the intersection of conductors in the physical layout.

When using the graph of a circuit as the topological model of its board layout, a number of problems arise. The first major problem is that the graph of a circuit is seldom planar. A nonplanar graph can only be made planar by removing a number of branches although there are usually many alternatives in deciding which branches to remove. A set of branches, preferably a minimum number of branches, has therefore to be identified and removed from

-33-

the graph in order to make it planar. The second major problem is that a graph is a topological entity and that planarity is an internal property of the graph. This means that a graph may be given any number of geometrical representations by drawing it on a plane. Having ensured that a graph is planar therefore, the problem still remains in constructing a geometrical representation which has no branch intersections.

The requirements of representing a board layout impose further constraints on the processing of the original graph and on the construction of a planar graph. These constraints are discussed below.

- (a) Only component branches and link branches may be removed from the graph in order to make it planar. Pseudo branches must remain in the graph to hold the pins of subgraph components in their correct order and spacing.

- (b) All the subgraph components must be connected into the planar graph in the same orientation. This corresponds to all the components being placed on the same side of the printed wiring board.

- (c) The nodes and pseudo branches of the edge connector represent the outside edge of the board. They should therefore lie on the outside edge of the planar graph.

(d) The connection pins on each component are connected together in the inethe graph by either one component branch or several pseudo branches. This prevents conductors from passing between adjacent component pins in a planar graph representation of the layout. In the physical layout however, it is possible

-34-

for a limited number of conductors to pass between adjacent pins, depending on the component and conductor dimensions. This limitation on conductor paths in the planar graph eliminates the problem of checking clearances between adjacent pins although it usually causes a greater number of non-planar branches to be removed. The constraint is later relaxed and the non-planar branches re-inserted into the graph by the method described in the next chapter.

## 4.2 Methods of Constructing a Planar Graph

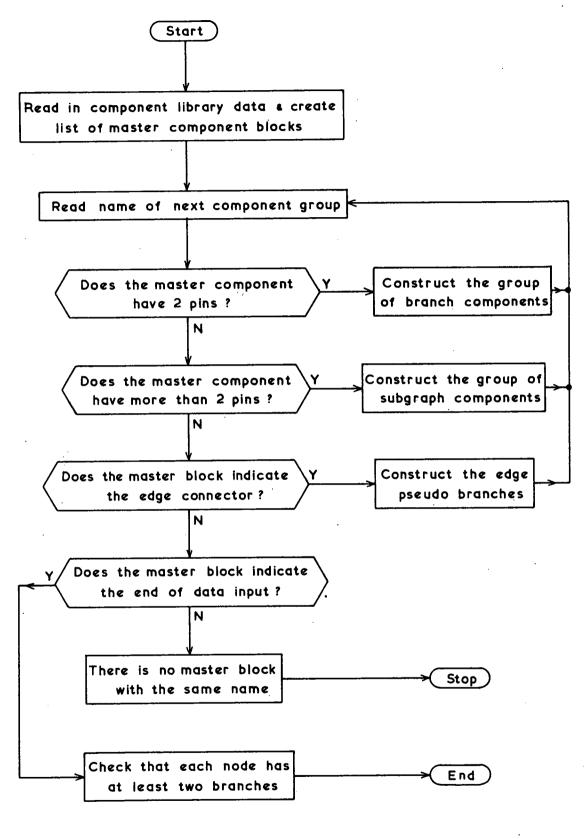

Classical graph theory concentrates on finding the conditions necessary for a graph to be planar rather than devising methods for constructing such a graph. The elegant theorem due to Kuratowski (16) states that a graph is planar if, and only if, it contains neither of the two graphs shown in Fig. 4.1 as subgraphs. The

Fig. 4.1

Kuratowski subgraphs

Kuratowski subgraphs may be well hidden within a graph so it is not practicable to search for them in a graph of many nodes and branches. Whitney (31) proves that a necessary and sufficient condition for a graph to be planar is that it has a dual graph. Again, this offers no practical solution to the construction of a planar graph. A planar graph drawn on a plane without branch intersections divides the plane into a number of non-overlapping regions. Each region is bounded by a <u>circuit</u>, or closed path of branches. MacLane's theorem (21) states that a graph is planar if, and only if, the graph contains a complete set of circuits such that each branch appears in no more than two of the circuits. This theorem is used in the planarity algorithm described in the next section.

Several other methods of constructing the graph of an electronic circuit have been described in Chapter 2.3. These methods suffer several disadvantages, however, in the practical case of producing a board layout. The algorithm for constructing a planar graph described by Bader works satisfactorily for branch components. It is, however, difficult to implement with subgraph components due to the need to preserve correct component orientations. In addition, it is not possible to arrange all the nodes of the edge connector on the outside edge of the graph.

The method due to Nicholson uses a permutation procedure to minimise the number of crossings in a graph. Each component, however, is represented by a node in the graph so that with multition pin components it is not possible to select the correct order of connections to each component. Rowley's algorithm is particularly suited to circuits containing multi-pin components although part of the procedure involves setting up a matrix for all conflicting branches. This can lead to excessive computer storage and time requirements for a large circuit.

#### 4.3 Principle of Planarity Algorithm

The objective of the planarity algorithm is to construct a planar subset of the graph representing an electronic circuit.

-36-

The planar graph should contain no branch intersections and should be subject to the constraints described in section 4.1. Non-planar branches are removed from the graph as they are encountered and no attempt is made to minimise the number of non-planar branches removed. This approach simplifies the planarity algorithm and is justified because non-planar branches are re-inserted into the planar graph at a later stage.

An important assumption upon which the planarity algorithm depends is that every node of the graph is of order two or more. This means that the planar graph may be described by a set of closed paths of branches, each path being the boundary of a planar region. The following circuit and topological conditions show that the assumption is valid for the graph representing a circuit.

- (a) Every circuit node, except the edge connector pins, connects at least two components together.

- (b) Each edge connector node is connected by two pseudo branches to its adjacent edge nodes.

- (c) Similarly, un-used pins on multi-pin components are connected by pseudo branches to their adjacent subgraph nodes.

- (d) Separate circuits or components on the board have the edge connector pseudo branches in common with the remainder of the circuit.

## 4.3.1 Processing of Planar Graphs.

Given a planar graph, G, the planarity algorithm is required to re-arrange G into a second planar graph, H. The nodes and branches of graph H are to be ordered so that a geometrical representation

-37-

of the graph may be drawn without branch intersections. Graphs G and H have a one-to-one correspondence between their nodes and branches. The difference is that additional information in graph H enables the required geometrical representation to be drawn. Graph H is constructed as a series of <u>subsets</u> of its nodes and branches. An initial set of nodes and branches is chosen so that a planar region is formed, with no branch crossings. Subsequent subsets of the graph are constructed by adding further planar regions to the previous subset such that no branch crossings are introduced.

A path that is known to form a planar region with no branch crossings is the set of pseudo branches representing the edge connector and the outside edge of the board. This path is termed  $P_1$  and is used to form the initial subset of graph H, i.e.,

$H_1 = P_1$

When the elements of this subset, or any subsequent subset, are subtracted from graph G, the nodes and branches remaining in G are termed <u>free nodes</u> and <u>free branches</u> respectively. The outside edge of path  $P_1$  forms the boundary of the first planar region of graph H. The region on the inside edge of  $P_1$  is termed the <u>free</u> <u>region</u> as it contains all of the free nodes and branches from graph G which have not yet been defined as part of graph H. In the general case of the nth subset of graph H,

Contents of Free Region =  $G - H_n$

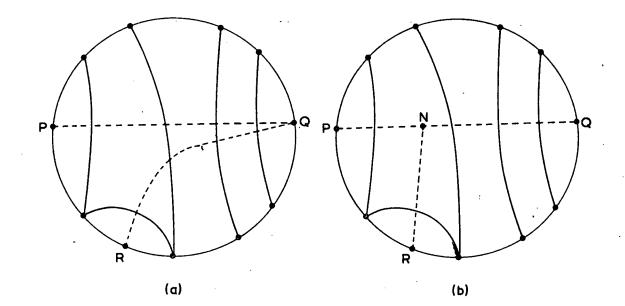

Each branch on the edge of the free region has previously been defined as part of a planar region which is adjacent to the outside edge of the free region. Applying MacLane's theorem to the planar graph, there must be a second planar region, on the inside edge of the free region, which is adjacent to the given branch. The boundary of this second region is defined by a closed path,  $P_n$ , which includes the given branch. This path will be comprised of a number of free branches together with part of the free region edge. The node at which the path leaves the edge of the free region is termed the <u>start node</u>; the corresponding node where it returns to the free region edge is termed the <u>target node</u>. It follows that the start and target nodes each lie on the edge of the free region and each have at least one attached free branch.

To add a planar region to the graph  $H_n$ , an arbitrary node on the edge of the free region, with a free branch attached, is selected as a start node. The next node on the edge of the free region with a free branch attached is selected as the target node. Starting from the free branches on the start node, a search is made to find the shortest path through the free region to the target node,  $P_{n+1}$ . The shortest path is defined as the one with a minimum number of free branches. The path  $P_{n+1}$  is then joined to the start and target nodes to form a new planar region. The boundary of the new region consists of one side of the path together with the edge of the free region between the two nodes. The remainder of the free region edge and the second side of the path are redefined as the new free region edge. A new subset of the graph H is thus defined by:

# $H_{n+1} = H_n + P_{n+1}$

Repeating the procedure with each node on the edge of the free region in turn yields further planar regions of the graph H. The algorithm is terminated when there are no remaining free branches. The free region itself then becomes the final region to be added to the graph.

-39-

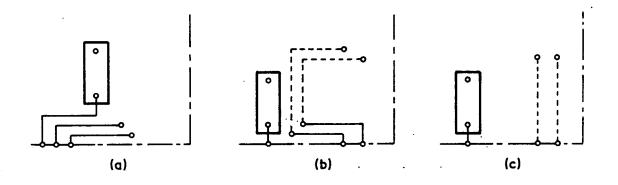

#### 4.3.2 Example of Planar Graph Construction

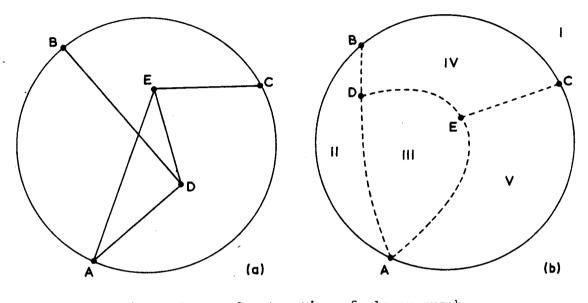

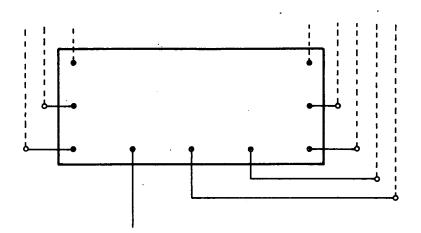

A simple example of the planarity algorithm operating upon a planar graph is shown in Fig. 4.2. The initial geometrical representation of the graph shown in Fig. 4.2(a) contains a branch crossing. The objective of the algorithm is to produce a geometrical representation of the graph with no branch crossings as illustrated by Fig. 4.2(b).

The path of pseudo branches representing the edge connector, ABCA, is taken as the first planar subset of the graph. The outside edge of the path forms the boundary of the first planar region, region I. The inside edge of the path forms the boundary of the initial free region. Node A is arbitrarily selected as the first start node and node B as the target node. A search through the free region for the shortest path from A to B gives the path ADB. Region II is thus defined as the next planar region of the graph and the edge of the free region is redefined as the path ADBCA... Node A remains the start node because it still has a free branch, AE, attached. Node D is then selected as the new target node

-40-

nearest to the start node. A search through the free region gives AED as the next path between start and target nodes, giving ADEA as region III.

All of the branches connected to node A are now defined as parts of the planar graph so a new start node, E, is arbitrarily selected from the edge of the free region. The next node on the edge of the free region with any free branches, node C, is chosen as the new target node. The shortest path through the free region from nodes E to C consists of the single branch EC. The edge of the free region between the start and target nodes, DBC, together with branch EC therefore form region IV. The edge of the free region is then defined as CAEC. As there are no free branches remaining in the free region, CAEC becomes the final region V. The branches of the planar graph are thus ordered so as to eliminate all branch crossings.

#### 4.3.3 Processing of Non-Planar Graphs,

It will generally be found that the graph of a circuit contains a number of non-planar branches. There are several different strategies for removing such branches from a graph in order to make it planar. One strategy used both by Bader (1) and by Rowley (29) involves making an exhaustive search for all branch conflicts in the graph. From the list of conflicting branches, an optimum set of non-planar branches is selected such that the number of branches removed is a minimum.

A second strategy, which is used here, deals with each branch conflict as it is encountered. When two branches are found to conflict, one of them is immediately removed from the graph although the result will not generally give a minimum set of non-planar

-41-

branches. A branch may be unnecessarily removed from the graph if all the branches it conflicts with are themselves later removed. As another algorithm is later used to insert non-planar branches back into the graph, selection of an optimum set of non-planar branches is not critical. The main advantages of this strategy are its speed and simplicity of computation. Each branch conflict is resolved as it is found, instead of having to process a list of many conflicts. Also, in searching the free region of the graph for further planar regions, the number of free branches to examine becomes progressively smaller as more regions are defined.

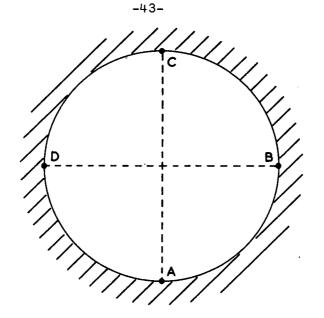

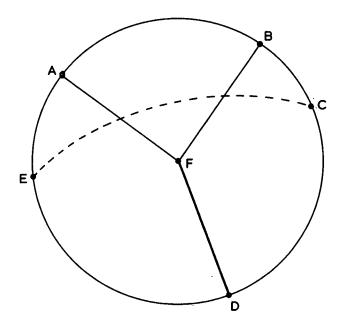

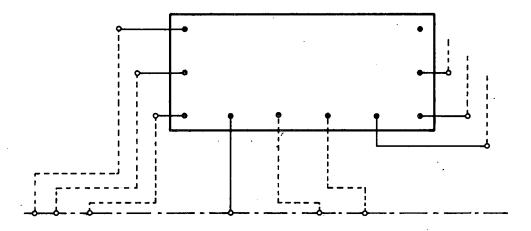

Any free branch, or path of free branches, that crosses the free region divides the edge of the free region into two parts,  $E_1$  and  $E_2$ at the nodes of connection. A conflict of branches occurs when a second branch or path crossing the free region has one end connected to part  $E_1$  and the other end connected to part  $E_2$ . In such a case it follows that the nodes on the edge of the free region, adjacent to the start node of the first path, will belong to the second path. There cannot therefore be a planar path between a start node and either of its two adjacent target nodes.

An example of conflicting branches is shown in Fig. 4.3. Branches AC and BD are in conflict as no path exists within the free region from the starting node A to either of its adjacent target nodes B and D. Neither branch may be drawn around the outside edge of the free region, ABCDA, as the outside has already been defined as part of a planar graph. One of the two branches therefore must be removed in order to make the graph planar.

The algorithm for creating a planar subset of a non-planar graph is an extension of that described in section 4.3.1. A search

-42-

#### Fig. 4.3 Non-planar branches

is made for planar paths from a start node to each of its two adjacent target nodes in turn. Every time a new planar region is defined, the free region is redefined, a new target is defined, and the search procedure is repeated. Any free branches remaining on the start node that do not yield a planar path after a search are either non-planar branches or bridge branches. Non-planar branches are immediately removed from the graph; the procedure for dealing with bridge branches is described below.

A <u>bridge branch</u> is defined as a branch which is the only connection between the edge of the free region and a subset of the graph G which has not yet been defined in the graph H. This state occurs when successive connections to the subset are removed as non-planar until only the bridge branch connection remains. It is essential that no subset of graph G becomes completely disconnected from the remainder of the graph. If this were to happen, the search procedure for constructing the planar graph would never encounter the subset by searching from the edge of the free region. The subset would thus not be defined as part of the required planar graph. This same reason also explains the fact, mentioned at the beginning of section 4.3, that every node of the graph must be of order two or more. A bridge branch is thus inserted into the planar graph to prevent a subset from being completely disconnected from the rest of the graph.

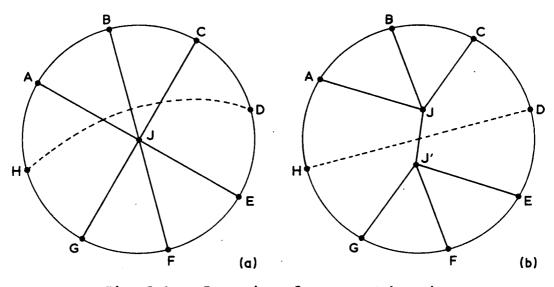

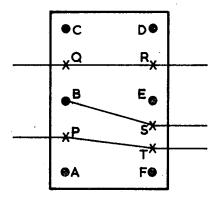

An example of the detection of non-planar branches and bridge branches connected to a node is shown in Fig. 4.4. Node A is taken

# Fig. 4.4 Detection of non-planar and bridge branches

as the start node and its two adjacent target nodes on the edge of the free region are B and D. The first search from node A to target node B yields branch AB as a planar branch so it is inserted into the graph. Two further searches to targets B and D do not yield planar branches so the branches AC and AE on node A must be either non-planar or bridge branches. In order to determine which type they are a search is made from the end of each branch in turn to see if a path exists to any other node on the edge of the free region. If a path does exist, as in the case of branch AC, the branch must be in conflict with another so it is removed as nonplanar. If a path does not exist, as in the case of AE, the branch represents the only connection to a particular subset of the graph

-44-

so it is retained in the graph as a bridge branch.

## 4.3.4 Insertion of Subgraph Components

Each planar region of a graph is defined by an ordered ring of branches around its boundary. The method of definition is described in detail in Chapter 6. By convention, the branch order around every region is described in an anticlockwise direction. A subgraph component consists of a planar region bounded by a ring of pseudo branches and by convention these are also defined in an anticlockwise direction.

In searching through the free region of a graph for a planar path, the target node is always arranged by convention to be in an anticlockwise direction around the edge of the free region from the start node. When a subgraph node is encountered, the search proceeds only along the pseudo branch in a clockwise direction from the subgraph node. The conventions of region definition and search direction thus ensure that all subgraph components are inserted into the graph with the same orientation.

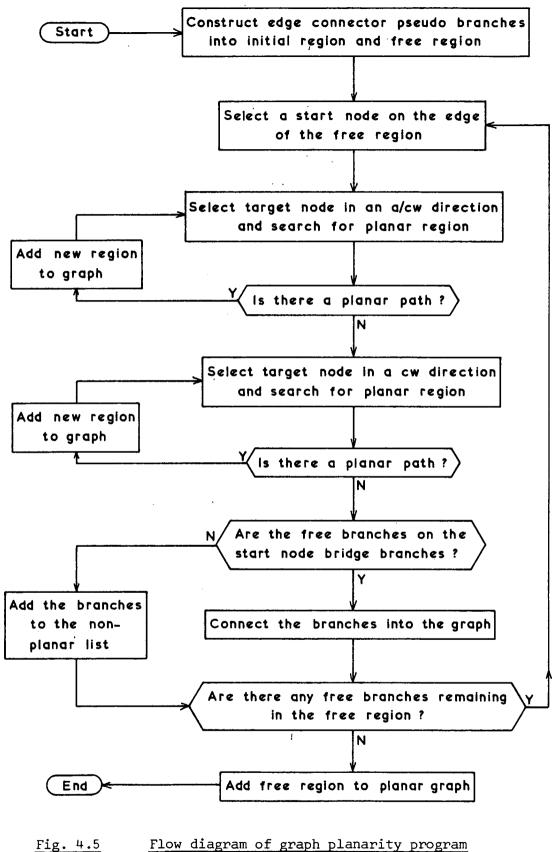

## 4.4 Description of Planarity Subroutine

A subroutine, called PLANAR, has been written to implement the planarity algorithm; its flow diagram is shown in Fig. 4.5. The subroutine starts by connecting the pseudo branches of the edge connector into a closed path. The outside edge of this path bounds the first planar region of the graph and the inside edge of the path is the boundary of the initial free region. The method of linking the branches into a region is detailed in Chapter 6. An arbitrary node with free branches attached, on the edge of the free region, is selected as the first start node. The next node with free branches

-45-

Flow diagram of graph planarity program

in an anticlockwise direction from the start node is taken as the target node. A search is then made for a planar path between the start and target nodes.

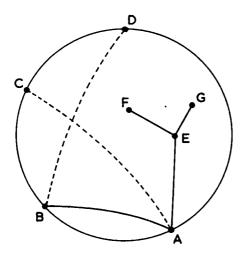

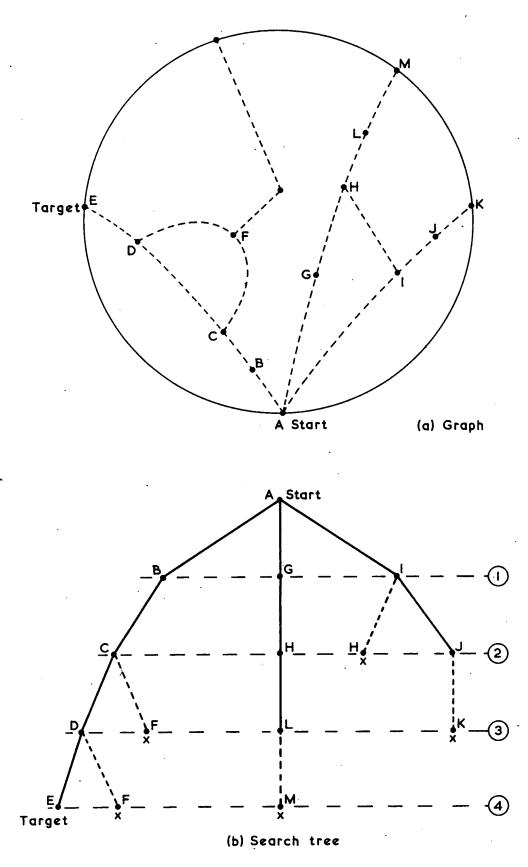

## 4.4.1 Search Procedure for Planar Paths

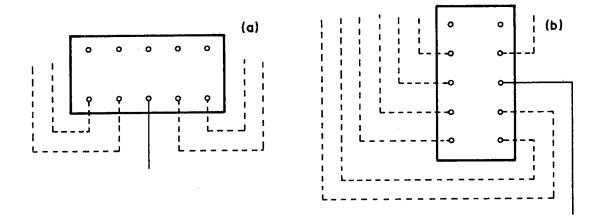

The search procedure for finding a planar path is designed to find the shortest path from start to target node. A tree search method is employed, as illustrated by Fig. 4.6. The free branches connected to the start node enable a set of the free nodes adjacent to the start node to be obtained. This set of free nodes represents the first level of the tree search. The nodes in the first level of the tree are connected by further free branches to another set of free nodes which go to make up the second level of the tree. The tree may thus be built up in successive levels until the target nodec is reached. All the possible nodes in one level of the tree are found before developing the next level. This ensures that the path found to the target node is of minimum length.

Each node is allowed to appear in the search tree once only. This prevents any part of the search from looping continually around a closed ring of branches. Node H in Fig. 4.6(b) for example, is reached from node G first so it is not listed as a successor to node I. No planar path is allowed to cross the free region and thus divide it into two separate regions, apart from a path between the start and target nodes. If a node on the edge of the free region is encountered during the tree search, node K for example, that part of the search is not continued.

When a subgraph component is encountered, CFDC for example, the tree search proceeds only in a clockwise direction from the

-47-

Fig. 4.6

Planar path search

-48-

subgraph node, node C. The correct subgraph component orientation is thus preserved in the graph. Similarly, only one pseudo branch of the subgraph is allowed in the search path. This prevents any subgraph nodes with free branches attached from becoming embedded within a planar region. In the computer data structure representing the tree, each node is given a pointer back to its predecessor in the tree. When the target node is found, the path back to the start node may thus be directly traced. If the tree is constructed as far as is possible without reaching the target node, the branches on the start node are either non-planar or bridge branches.

## 4.4.2 Region Construction

When a planar path is found between the start and target nodes of a graph, the branches of the path are connected in the computer data structure as two segments of region boundaries, corresponding to the two sides of the path. The edge of the free region is divided at the start and target nodes into two separate parts. The two parts of the free region edge and two parts of the planar path are joined to form a new planar region and a redefined free region edge. If the planar path contains any subgraph nodes, the remainder of the subgraph components are also added to the graph as new planar regions.

#### 4.4.3 Further Search Procedures

Each time a new planar region is added to the graph, a new target node is found in an anticlockwise direction from the start node. When no further planar paths can be found, the search is continued by selecting target nodes in a clockwise direction from the start node. In this case, the search for a planar path is actually made from the target to the start node so as to preserve

-49-

the correct orientation of path search.

Any branches remaining on the start node after the planar path search is exhausted are checked for non-planarity. A tree search is made from the node at the other end of the branch under consideration. If the search encounters any node on the edge of the free region, the branch is non-planar and is removed from the graph. If the search is exhausted before reaching a free region edge node, the branch is a bridge branch and so is inserted into the planar graph.

The next node with free branches in an anticlockwise direction from the start node is taken as the new start node and the search for planar regions is continued. The process is terminated when there are no free branches left in the free region. The free region itself is then added to the planar graph as the final region. The result of the planarity subroutine is thus a set of regions describing a planar graph and a list of non-planar branches. The list of nonplanar branches may contain several planar branches, as the branches with which they conflicted have also been removed from the graph.

~50-

#### Chapter 5

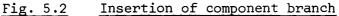

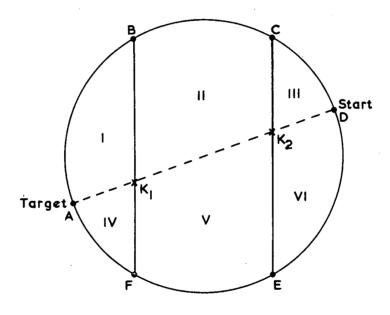

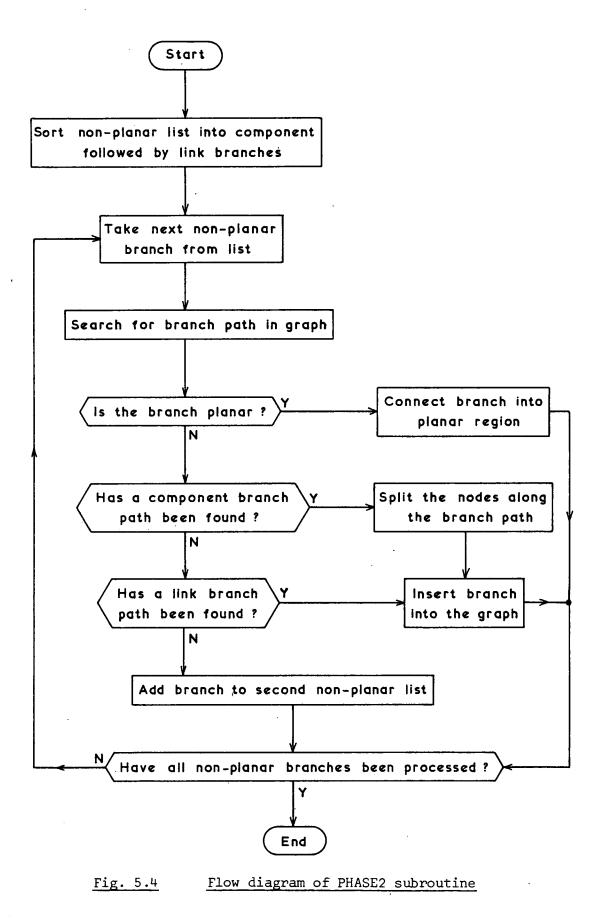

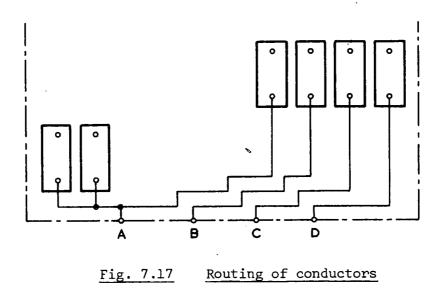

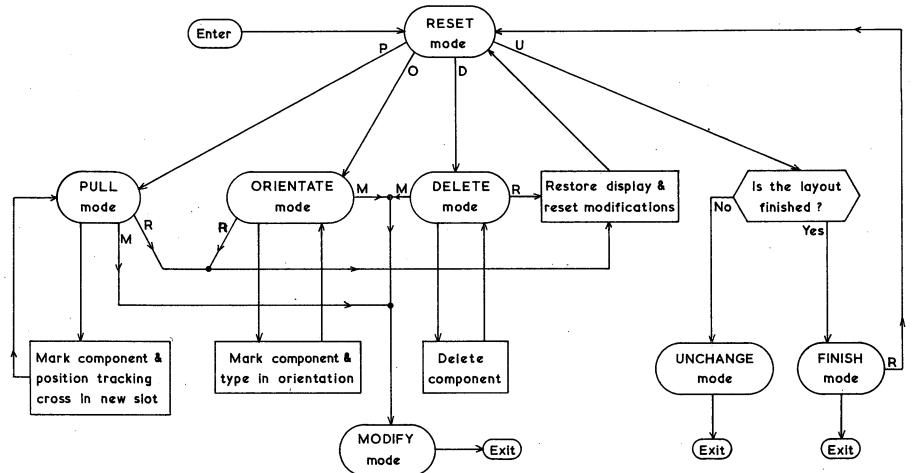

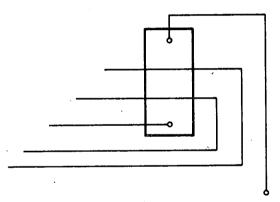

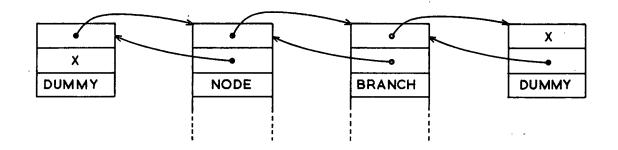

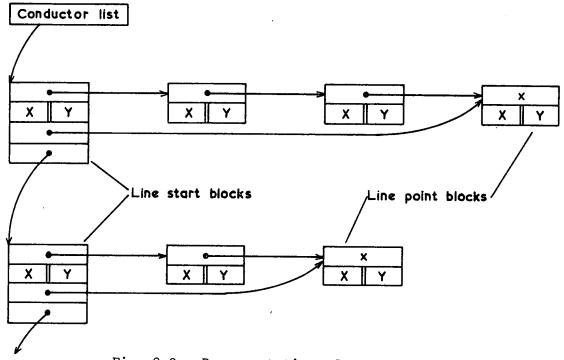

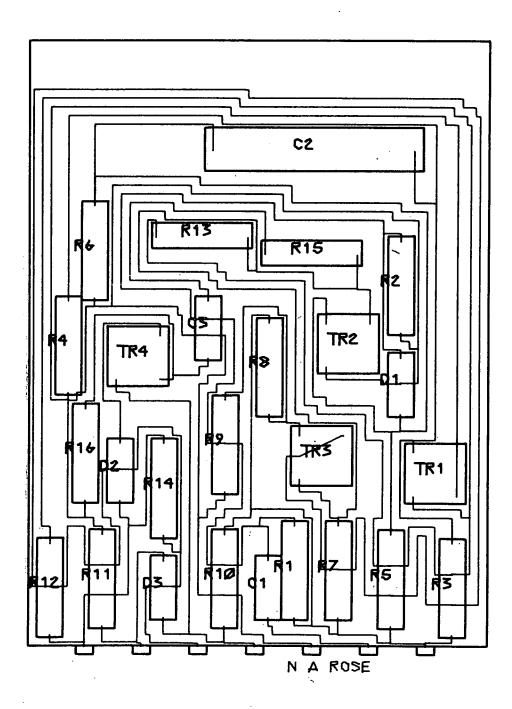

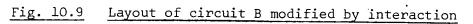

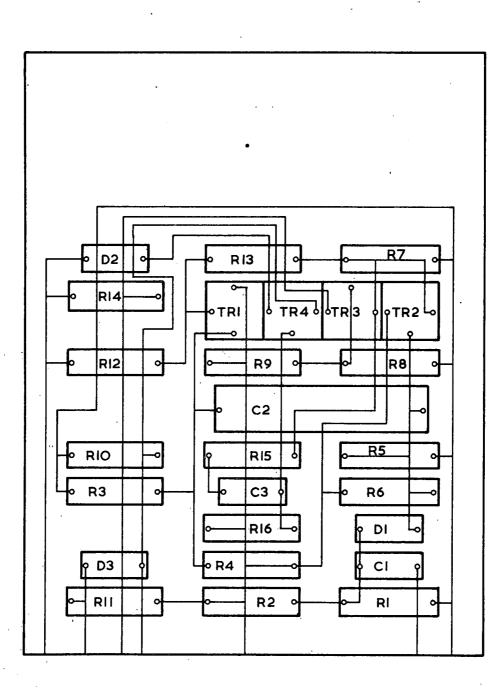

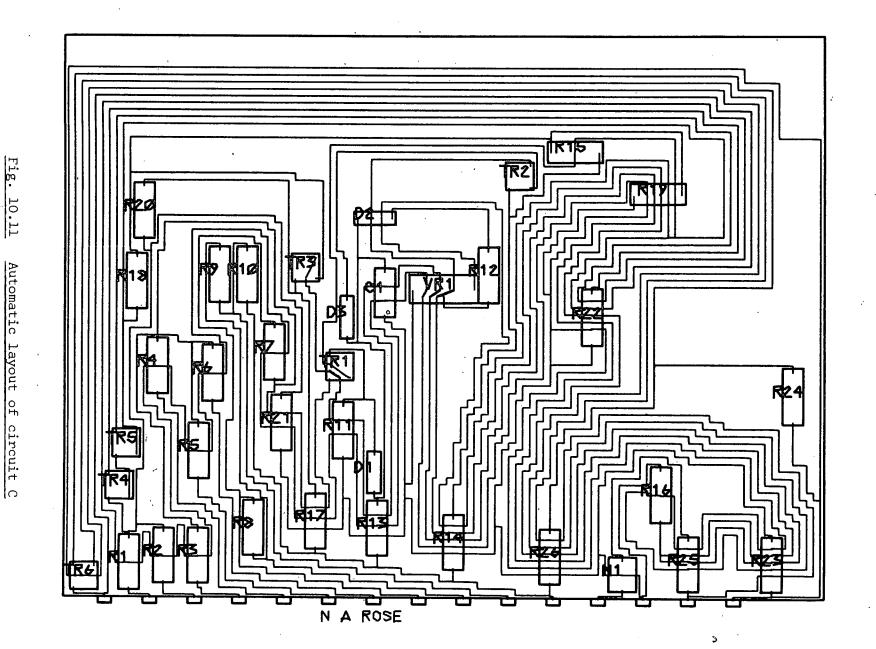

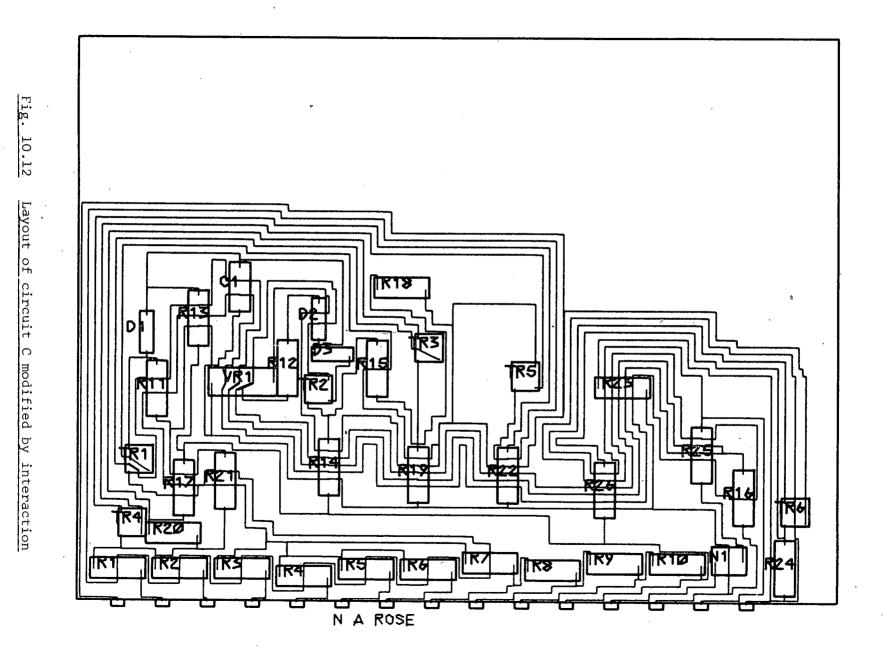

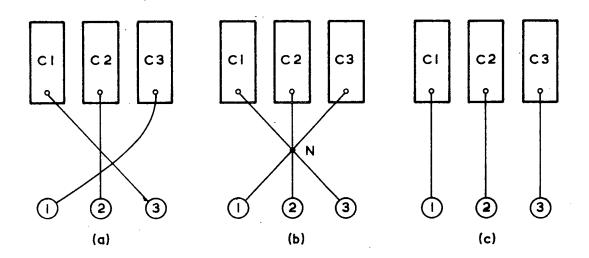

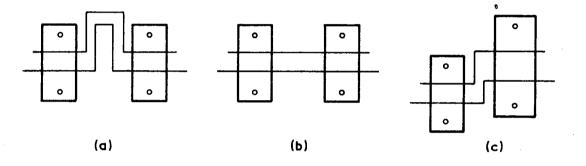

## Insertion of Non-Planar Branches