# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Mapping Parallelism to Heterogeneous Processors

Kiran Chandramohan

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2016

# Abstract

Most embedded devices are based on heterogeneous Multiprocessor System on Chips (MPSoCs). These contain a variety of processors like CPUs, micro-controllers, DSPs, GPUs and specialised accelerators. The heterogeneity of these systems helps in achieving good performance and energy efficiency but makes programming inherently difficult. There is no single programming language or runtime to program such platforms.

This thesis makes three contributions to these problems. First, it presents a framework that allows code in Single Program Multiple Data (SPMD) form to be mapped to a heterogeneous platform. The mapping space is explored, and it is shown that the best mapping depends on the metric used.

Next, a compiler framework is presented which bridges the gap between the high -level programming model of OpenMP and the heterogeneous resources of MPSoCs. It takes OpenMP programs and generates code which runs on all processors. It delivers programming ease while exploiting heterogeneous resources.

Finally, a compiler-based approach to runtime power management for heterogeneous cores is presented. Given an externally provided budget, the approach generates heterogeneous, partitioned code that attempts to give the best performance within that budget.

# Lay Summary

The world is witnessing an ever increasing demand for computational resources. The industry has responded by building huge centralised data-centers and increasing computational capabilities of embedded devices. To improve performance, these platforms also adopted multicore architectures where there are many processors of the same kind. Power is often a limiting factor in both these cases. Computer architects have long realised this and have added specialised processors for a particular kind of task. The presence of specialised processors improves the power efficiency but makes it very difficult to create software for these platforms. It is not clear how to partition work among all the processors, unlike homogeneous multicores, where work could be divided uniformly. Also, programming languages and libraries previously used for programming homogeneous multicore processors become ineffective in the presence of heterogeneous specialised processors. Finally, due to thermal effects, all the processors cannot be powered on simultaneously.

This thesis looks at how OpenMP, a programming language extension typically used for programming homogeneous multicore processors, can be used for heterogeneous processors and examines how work can be partitioned among the heterogeneous processors. It also presents methods for achieving good performance in the presence of power budgets.

# Acknowledgements

First, I would like to acknowledge the guidance of my PhD supervisor Prof. Michael O'Boyle. He has given me excellent advice on which problems to solve and what areas to concentrate on. He was also a great source of ideas, many of which helped form the research described in this thesis. Last, but not the least, is the air of positivity that he brings to the table, which has helped me tide over many dead-ends and disappointments.

Next, I would like to thank Robert Clark of Redhat and Suman Anna of Texas Instruments. I cannot imagine setting up the framework without the help of these two people. I would also like to thank Prof. Bjorn Franke, Oscar Almer, Chris Thompson, Volker Seeker, Erik Tomusk and Jos van Eijndhoven for sharing their knowledge about Heterogeneous Systems and Power Measurement. Thanks to Prof. Vijay Nagarajan for being a part of my committee, and providing constructive feedback on my work. Thanks to Dr. Zheng Wang for helpful discussions and letting me use his OpenMP to OpenCL translator. Thanks also to Chris Margiolas, Alberto Magni, Vasilios Porpodas, Wen Yuan, and Stan Manilov for discussions about compilers, runtime and GPUs. Thanks to Andrew McPherson for many discussions about memory consistency, compilers and UK/Scotland.

I would like to thank Bharghava Rajaram and Murali Emani for all the help during the time I settled in and also for very useful technical discussions. Thanks also to Karthik, Govind, Konstantina Mitropolou, Praveen Tamanna, Ursula Chalita, George, Luna Ferrari and Rui Li for many discussions.

Finally, I am grateful to my family for being understanding and supportive for the entire duration of the PhD degree.

# Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. The material presented in this thesis has been published in the following papers.

- Kiran Chandramohan, Michael O'Boyle, Zheng Wang. "Power Constrained Heterogeneous Code Generation". Under submission, in Chapter 6.

- Kiran Chandramohan, Michael O'Boyle. "A compiler framework for automatically mapping data parallel programs to heterogeneous MPSoCs", In International Conference on Compilers, Architecture and Synthesis for Embedded Systems(CASES), October 2014, in Chapter 5.

- Kiran Chandramohan, Michael O'Boyle, "Partitioning Data-parallel Programs for Heterogeneous MPSoCs: Time and Energy Design Space Exploration", In SIGPLAN/SIGBED Conference on Languages, Compilers and Tools for Embedded Systems(LCTES), June 2014, in Chapter 4.

(Kiran Chandramohan)

# Contents

| 1 | Intr | Introduction |                               |    |  |  |  |  |  |

|---|------|--------------|-------------------------------|----|--|--|--|--|--|

|   | 1.1  | Proble       | ems                           | 4  |  |  |  |  |  |

|   |      | 1.1.1        | Partitioning                  | 4  |  |  |  |  |  |

|   |      | 1.1.2        | Compiler Framework            | 5  |  |  |  |  |  |

|   |      | 1.1.3        | Power Budget                  | 5  |  |  |  |  |  |

|   | 1.2  | Contri       | butions                       | 6  |  |  |  |  |  |

|   | 1.3  | Thesis       | Organisation                  | 7  |  |  |  |  |  |

|   | 1.4  | Summ         | ary                           | 8  |  |  |  |  |  |

| 2 | Bacl | kground      | d                             | 9  |  |  |  |  |  |

|   | 2.1  | Multip       | processors                    | 9  |  |  |  |  |  |

|   | 2.2  | Hetero       | ogeneous Systems              | 10 |  |  |  |  |  |

|   |      | 2.2.1        | Single ISA                    | 10 |  |  |  |  |  |

|   |      | 2.2.2        | Multiple ISA                  | 10 |  |  |  |  |  |

|   | 2.3  | Paralle      | el Programming Models         | 13 |  |  |  |  |  |

|   |      | 2.3.1        | Data Parallel Model           | 13 |  |  |  |  |  |

|   | 2.4  | Paralle      | el Programming Frameworks     | 14 |  |  |  |  |  |

|   |      | 2.4.1        | POSIX threads                 | 14 |  |  |  |  |  |

|   |      | 2.4.2        | OpenMP                        | 15 |  |  |  |  |  |

|   |      | 2.4.3        | OpenCL                        | 16 |  |  |  |  |  |

|   |      | 2.4.4        | Comparison                    | 18 |  |  |  |  |  |

|   | 2.5  | Compi        | iler                          | 18 |  |  |  |  |  |

|   |      | 2.5.1        | Uniprocessors                 | 18 |  |  |  |  |  |

|   |      | 2.5.2        | Homogeneous Multiprocessors   | 18 |  |  |  |  |  |

|   |      | 2.5.3        | Heterogeneous Multiprocessors | 19 |  |  |  |  |  |

|   |      | 2.5.4        | Clang/LLVM                    | 19 |  |  |  |  |  |

|   | 2.6  | Measu        | irements                      | 19 |  |  |  |  |  |

|   |      | 2.6.1        | Runtime                       | 20 |  |  |  |  |  |

|   |      | 2.6.2 Energy                                             | 20 |

|---|------|----------------------------------------------------------|----|

|   | 2.7  | Benchmarks                                               | 21 |

|   | 2.8  | Summary                                                  | 22 |

| 3 | Rela | ted Work 2                                               | 23 |

|   | 3.1  | Heterogeneity                                            | 23 |

|   |      | 3.1.1 Single ISA heterogeneity                           | 24 |

|   |      | 3.1.2 Multiple ISA heterogeneity                         | 24 |

|   |      | 3.1.3 Prototyping Heterogeneity                          | 25 |

|   | 3.2  | Programming Languages                                    | 26 |

|   |      | 3.2.1 Compiler                                           | 27 |

|   |      | 3.2.2 OpenMP to SPMD                                     | 27 |

|   | 3.3  | Mapping Parallelism                                      | 27 |

|   |      | 3.3.1 Partitioning                                       | 27 |

|   |      | 3.3.2 Scheduling Tasks                                   | 28 |

|   | 3.4  | Memory Management                                        | 29 |

|   |      | 3.4.1 Multiple Address Spaces                            | 29 |

|   |      | 3.4.2 Cache Coherence                                    | 30 |

|   | 3.5  | Power/Energy                                             | 30 |

|   |      | 3.5.1 Power                                              | 30 |

|   |      | 3.5.2 Energy Efficiency                                  | 32 |

|   | 3.6  | Summary                                                  | 33 |

| 4 | Part | itioning Data-parallel Programs for Heterogeneous MPSoCs | 35 |

|   | 4.1  | Introduction                                             | 35 |

|   | 4.2  | Motivation                                               | 38 |

|   |      | 4.2.1 Time                                               | 38 |

|   |      | 4.2.2 Energy                                             | 39 |

|   | 4.3  | Programming Model                                        | 40 |

|   |      | 4.3.1 Data Parallelism and SPMD                          | 40 |

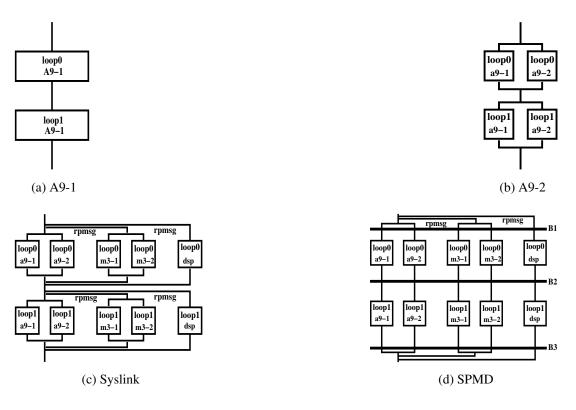

|   |      | 4.3.2 The OMAP model                                     | 42 |

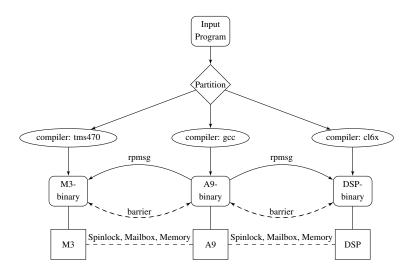

|   |      | 4.3.3 Mapping SPMD programs to OMAP 4                    | 13 |

|   |      | 4.3.4 Code Generation                                    | 14 |

|   | 4.4  | Partitioning Policies                                    | 15 |

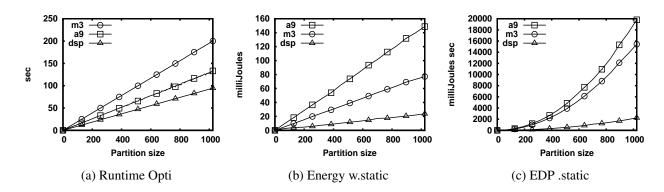

|   | 4.5  | Metrics                                                  | 18 |

|   |      | 4.5.1 Energy                                             | 18 |

|   |     | 4.5.2 Two energy measures          | 49 |

|---|-----|------------------------------------|----|

|   |     | 4.5.3 Runtime and EDP              | 50 |

|   | 4.6 | Experimental Setup                 | 50 |

|   |     | 4.6.1 Benchmarks                   | 50 |

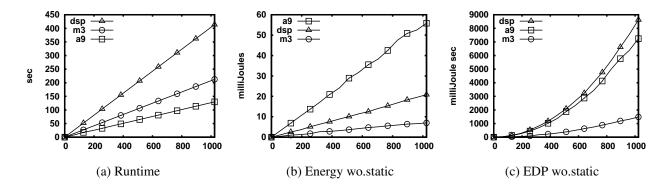

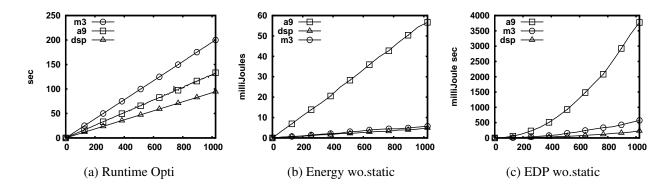

|   | 4.7 | Matrix Multiplication Case Study   | 50 |

|   |     | 4.7.1 Individual Processor         | 51 |

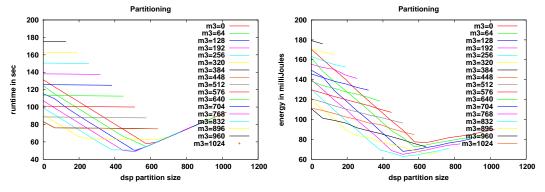

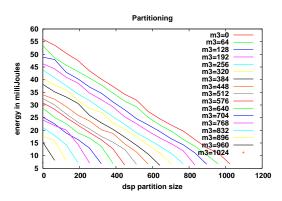

|   |     | 4.7.2 Partitioning                 | 53 |

|   | 4.8 | Partitioning Policy Results        | 54 |

|   |     | 4.8.1 Runtime                      | 55 |

|   |     | 4.8.2 Energy                       | 56 |

|   |     | 4.8.3 Analysis of Results          | 57 |

|   | 4.9 | Summary                            | 58 |

| 5 | Con | piler Framework                    | 59 |

|   | 5.1 | Introduction                       | 59 |

|   | 5.2 | Motivation                         | 61 |

|   | 5.3 | Target Architecture and Runtime    | 63 |

|   | 5.4 | Programming models                 | 64 |

|   |     | 5.4.1 OpenMP                       | 64 |

|   |     | 5.4.2 Syslink Model                | 65 |

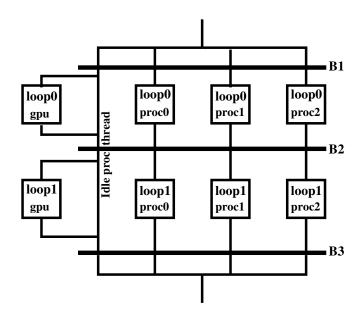

|   |     | 5.4.3 SPMD                         | 66 |

|   |     | 5.4.4 Example                      | 66 |

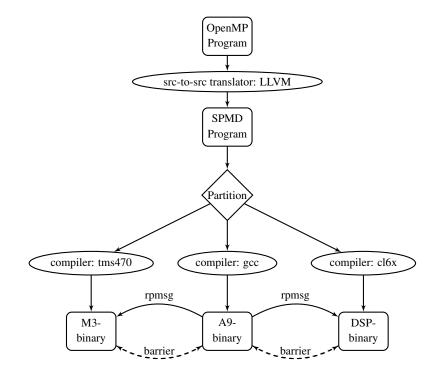

|   | 5.5 | SPMD as a bridging model           | 66 |

|   |     | 5.5.1 Mapping OpenMP to SPMD       | 67 |

|   |     | 5.5.2 Mapping SPMD to MPSoC        | 67 |

|   | 5.6 | Compiler Algorithm                 | 68 |

|   |     | 5.6.1 Data partition               | 68 |

|   |     | 5.6.2 Data bounds per processor    | 69 |

|   |     | 5.6.3 Computation Partitioning     | 69 |

|   |     | 5.6.4 Cache Flush                  | 70 |

|   |     | 5.6.5 Code Generation              | 70 |

|   | 5.7 | Shared Memory on an MPSoC          | 71 |

|   | 5.8 | Compiler Implementation            | 72 |

|   |     | 5.8.1 Source to Source Translation | 72 |

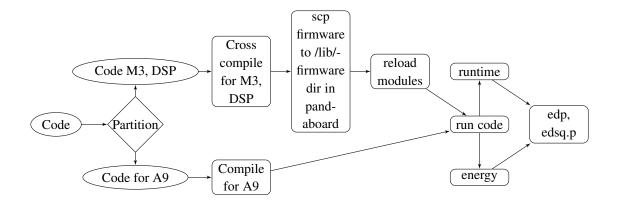

|   | 5.9 | Setup                              | 75 |

|   |      | 5.9.1   | Benchmarks                                | 75  |

|---|------|---------|-------------------------------------------|-----|

|   |      | 5.9.2   | Measurement                               | 75  |

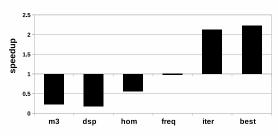

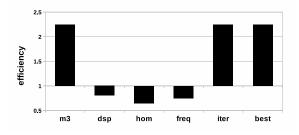

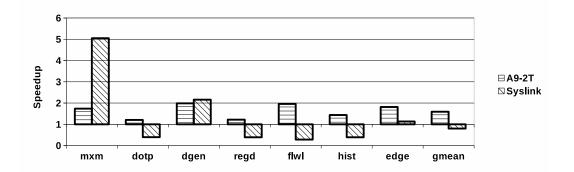

|   | 5.10 | Experin | ments                                     | 76  |

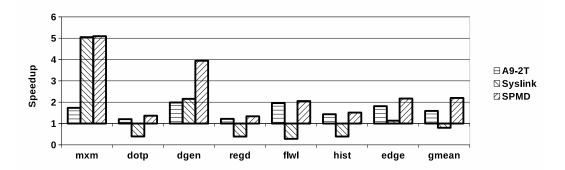

|   |      | 5.10.1  | Syslink and OpenMP Model                  | 76  |

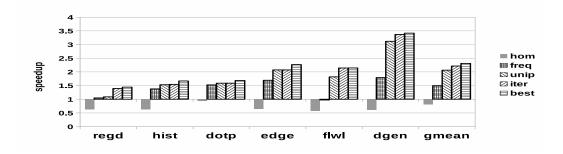

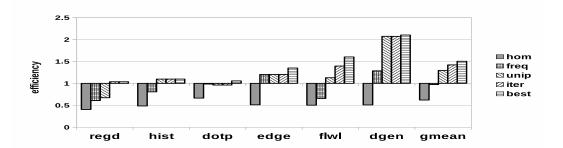

|   |      | 5.10.2  | Our SPMD approach                         | 76  |

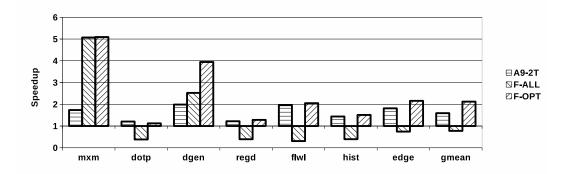

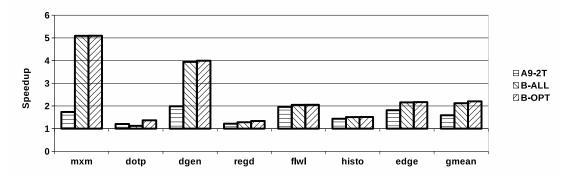

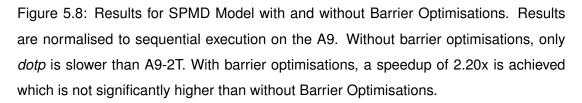

|   |      | 5.10.3  | SPMD Barrier optimisations                | 77  |

|   |      | 5.10.4  | Comparison Summary                        | 78  |

|   |      | 5.10.5  | Energy and EDD                            | 78  |

|   |      | 5.10.6  | Limit Study                               | 80  |

|   | 5.11 | Summa   | ary                                       | 80  |

| 6 | Pow  | er Cons | trained Code Generation                   | 83  |

|   | 6.1  | Introdu | letion                                    | 83  |

|   | 6.2  | Motiva  | tion                                      | 85  |

|   | 6.3  | Our Ap  | pproach                                   | 86  |

|   |      | 6.3.1   | Compile-time                              | 87  |

|   |      | 6.3.2   | Runtime                                   | 87  |

|   | 6.4  | Code g  | eneration                                 | 88  |

|   |      | 6.4.1   | OpenMP                                    | 88  |

|   |      | 6.4.2   | Hybrid SPMD                               | 89  |

|   |      | 6.4.3   | Memory Management                         | 90  |

|   | 6.5  | Power   | Constrained Model                         | 91  |

|   |      | 6.5.1   | Objective                                 | 91  |

|   |      | 6.5.2   | Selecting a configuration                 | 92  |

|   |      | 6.5.3   | Policies                                  | 92  |

|   | 6.6  | Setup   |                                           | 95  |

|   |      | 6.6.1   | Benchmarks                                | 95  |

|   |      | 6.6.2   | Platforms                                 | 95  |

|   |      | 6.6.3   | Policies evaluated                        | 96  |

|   |      | 6.6.4   | Methodology                               | 97  |

|   | 6.7  | Results | 3                                         | 97  |

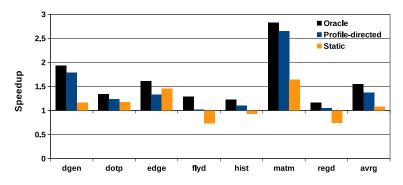

|   |      | 6.7.1   | Comparison against <i>DVFS</i> and Oracle | 97  |

|   |      | 6.7.2   | Comparison to Naive and Core selection    | 99  |

|   |      | 6.7.3   | Speedup Summary                           | 103 |

|   |      | 6.7.4   | Over/Under Shooting                       | 105 |

|    | 6.8    | Summa        | ary                        | 106 |  |  |

|----|--------|--------------|----------------------------|-----|--|--|

| 7  | Con    | nclusion 109 |                            |     |  |  |

|    | 7.1    | Contrib      | outions                    | 109 |  |  |

|    |        | 7.1.1        | Partitioning               | 109 |  |  |

|    |        | 7.1.2        | Compiler Framework         | 110 |  |  |

|    |        | 7.1.3        | Power Budget               | 110 |  |  |

|    | 7.2    | Critical     | Analysis                   | 110 |  |  |

|    |        | 7.2.1        | Common Issues              | 111 |  |  |

|    |        | 7.2.2        | Partitioning               | 111 |  |  |

|    |        | 7.2.3        | Compiler Framework         | 112 |  |  |

|    |        | 7.2.4        | Power Budget               | 112 |  |  |

|    | 7.3    | Future       | work                       | 112 |  |  |

|    |        | 7.3.1        | Scale                      | 112 |  |  |

|    |        | 7.3.2        | Partitioning               | 113 |  |  |

|    |        | 7.3.3        | Oracle Computation         | 114 |  |  |

|    |        | 7.3.4        | Multiple Programs          | 114 |  |  |

|    |        | 7.3.5        | Mobile Devices             | 114 |  |  |

|    | 7.4    | Summa        | ary                        | 115 |  |  |

| Α  | Exp    | eriments     | s with Snapdragon Platform | 117 |  |  |

|    | A.1    |              | agon                       | 117 |  |  |

|    |        | A.1.1        | Hardware                   |     |  |  |

|    |        | A.1.2        | Runtime                    | 117 |  |  |

|    |        | A.1.3        | Programming Model          | 118 |  |  |

|    | A.2    |              | ments                      |     |  |  |

|    | A.3    |              | ary                        |     |  |  |

| D  | n      |              |                            |     |  |  |

| B  | Bug    | fix in Li    | inux Kernel                | 121 |  |  |

| Bi | bliogi | aphy         |                            | 123 |  |  |

## **Chapter 1**

# Introduction

Ever since the birth of microprocessors, there has been a demand for more computation speed. Historically, this demand has been met by improvements in computer architecture design and clock frequency. Some of the improvements in computer architecture seen over the years include pipelining, branch prediction, superscalar processors, out of order execution, speculative execution, etc. The first Intel 4004 microprocessor released in 1971 had a clock frequency of 740 kHz. Thirty years later, the Intel Pentium 4 had clock frequencies more than 2 GHz. These improvements were possible due to advancements in process technology and miniaturisation of transistors which ensured that more and more transistors could be packed on a chip. For e.g., the Intel 4004 was built with 10µm technology and had around 2,300 transistors while the Intel Pentium 4 was built with 180nm and had around 42 million transistors. The increase in transistor count happened approximately in line with Moore's law[84] which predicted a doubling in the number of transistors every year. At the same time, Dennard's scaling [44] predicted that the power density will remain constant as the transistor size reduces. Hence, Dennard's scaling and Moore's law allowed uni-processors to exponentially improve the performance in an energy efficient manner.

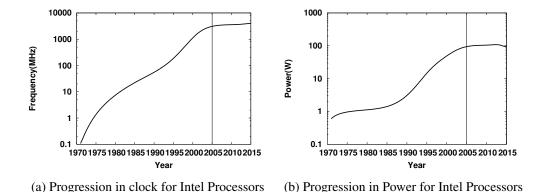

However, this well-scripted success story for uni-processors began to break down at the beginning of this century. The difference in the clock frequency of the memory and processor increased and soon memory speed became the bottleneck. Improvements in performance from Instruction Level Parallelism diminished as not enough parallel instruction could be found in a single thread. Increasing frequency led to high power consumption and heat generation. Figure 1.1 shows that the exponential increase in frequency and power has tapered off around 2005 indicating a transition. Hence, at the turn of this century, the processor industry witnessed a major transition from uni-processors to multicore processors. The processor designers concentrated

Figure 1.1: Note the flattening of the curves beginning around 2005.

on obtaining improved performance by increasing the number of cores. Multicore processors are well suited for data-parallel applications and parallel workloads. Researchers suggested adding multiple cores to a system and processors with even a thousand cores[68] have been discussed. In the industry also there has been a proliferation of homogeneous multicores. The high-performance Intel Xeon Processor E7-8880 v3 has 18 cores.

But the success with homogeneous multicores also seems to be short-lived. As process technology improved, Dennard's scaling broke down which caused a huge increase in power densities. It is no more possible to switch on all the transistors simultaneously without causing thermal safety issues. Thus, due to power and thermal limitations, not all portions of the chip can be switched ON at the same time. The portions that cannot be powered ON are called Dark Silicon. When only a subset of the cores can be active at the same time, it is better to have cores of different types than the same type. The presence of heterogeneous cores provides opportunities to match a task with the most efficient core for that task and thus leads to better usage of the power budget. Hence, Dark silicon leads us to heterogeneous multicore processors. Heterogeneous processors differ from homogeneous processors in that the cores are all not of the same type. The difference among cores can be in the ISA or micro-architecture. Research[64] has shown that heterogeneous multicores are better when considering energy delay trade-offs. A multi-core heterogeneous architecture can support a range of execution characteristics not possible in a single-core processor. It is beneficial for workloads with different characteristics. By having processing units with different characteristics, computation can be mapped to specialised devices that perform a specific type of task more efficiently than other devices. Thus, heterogeneous computing systems can deliver better energy-delay trade-offs [64], [66]. Recently, with the rise of GPGPU (general-purpose computing on GPUs), heterogeneous computing has become more mainstream. An example for a commercial heterogeneous multicore processor is big.LITTLE[18]. It consists of a big (Cortex A15) and a small (Cortex A7) processor. The embedded systems world has also adopted heterogeneous systems. OMAP[6] from TI, Snapdragon[13] from Qualcomm and Tegra[14] from NVIDIA are examples of popular heterogeneous multicores in the mobile embedded systems market.

Heterogeneous processors are found in both the general purpose as well as the embedded space. The design of embedded Multiprocessor System on Chips (MPSoCs) has been largely application driven with specialised units such as ASICs and DSPs targeting media decoding or digital signal applications. Embedded applications developers are typically expert programmers, where the cost of porting and tuning can be amortised across many shipped devices. Because of this, the programming models supported by MPSoCs typically tend to be application driven and change from one platform or generation to the next. The design of general-purpose heterogeneous many-cores has been, by contrast, more conservative. Large scale parallelism is supported, but there is considerably less diversity amongst cores. Same-ISA different scale systems such as big.LITTLE or GPU accelerator approaches have dominated. The reason is that general-purpose programmers require higher-level programming interfaces as the systems are less domain specific. The relative cost of programming is higher and cannot be amortised over many shipped devices

Energy and power have been the driving force behind the gradual convergence of two communities: embedded and general-purpose computing. Both have moved to parallel platforms containing specialised processors. The embedded community were early adopters of such platforms called MPSoCs as they provided cost-effective performance and are energy efficient. The general-purpose community has only recently adopted such platforms, now described as heterogeneous many-cores, as they provide high performance within acceptable power densities. The embedded world has led in system diversity, and it is likely that tomorrow's general-purpose heterogeneous many-core platforms will resemble the MPSoCs of today. This thesis is concerned with connecting these two worlds: the high-level mapping approaches supported in the general-purpose world with MPSoCs. This has the potential to provide today's MP-SOC programmers with a portable programming environment and allow the general-purpose programming of tomorrow's heterogeneous many-cores.

Though there are advantages for heterogeneous multicores, they are very difficult

to program. The difficulty arises due to lack of high-level programming models, multiple address space, lack of cache coherence and the fact that cores have different ISAs. Hence, it remains to be seen whether running programs on heterogeneous processors provides performance or energy improvements. To obtain benefits from multicores, the programs have to be parallelised. Parallelising a program to achieve performance benefits on multicore processors is a difficult task, and there are several papers dedicated to this task. This thesis deals with the relatively simpler case of data-parallel programs. In particular, this thesis considers data-parallel OpenMP[42] programs. Since the parallelism is already explicitly provided by the OpenMP programs, the most important task is to map the parallelism to the heterogeneous cores.

The next section presents the problems that have to be solved to map data-parallel programs to heterogeneous multicores processors.

#### **1.1 Problems**

The following sections present problems to be solved for effectively using heterogeneous multicore processors for data-parallel programs.

#### 1.1.1 Partitioning

The programs are data-parallel. Hence, mapping involves partitioning the work among the processors. So, the first question to answer is how to partition the data-parallel programs such that performance and energy benefits can be obtained. If the target architecture is homogeneous multicores, then a uniform partitioning is desirable. However, with heterogeneous multicores, it is not clear how to partition a program. For best runtime performance it is obvious that work has to be partitioned among the processors but what is not clear is the amount of work to be assigned to each processor. The heterogeneous processors can have different clock frequencies, ISAs, different strengths in processing and different memory configuration.

For energy, the folklore [130] is that running the fastest is best for energy. Since heterogeneous multicores provide opportunities for energy-delay trade-offs, it is not clear whether this property still holds. Is it best to run everything on the fastest processor, or is it best to choose the partition giving the best runtime, or is it best to run on the most efficient processor.

To evaluate partitioning, a runtime framework has to be built to overcome the obstacles posed by heterogeneous processors. Since the address spaces of processors are different, pointers are not portable. The runtime framework has to perform some address translation so that all the processors can work on different partitions of an array. If the caches are not coherent, then the runtime should provide API to flush or invalidate caches so that processors read the updated values.

#### **1.1.2 Compiler Framework**

Once the partitioning problem is solved, the next task is to develop a compiler framework to automatically map data-parallel OpenMP programs to heterogeneous processors. OpenMP is a popular high-level parallel programming model and is widely supported on parallel hardware. Programmers only need to express parallelism without concern as to the mapping and scheduling of work to the underlying platform. Due to the wide availability of OpenMP libraries, it also offers some degree of performance portability. OpenMP, however, is not directly supported on heterogeneous systems, due to lack of coherent shared memory and multiple operating systems. Exploiting heterogeneity is avoided, and only the CPUs are utilised by the OpenMP runtime. The standard method of accessing non-CPU cores is to use them as accelerators accessed via platform specific libraries. This style of programming requires the application to be first split into separate tasks that fit the library API. The main CPU then acts as a coordinator using a Master/Slave programming model. Although this approach means that the programmer does not have to deal with different operating systems and manage memory coherence, it is highly system specific and may introduce excessive data traffic. Furthermore, it requires the programmer to perform platform-specific lowlevel partitioning of work into parallel activities. While this approach may work for specialised applications, it is not suitable for general data-parallel programs.

#### 1.1.3 Power Budget

Power is a first class constraint in modern processor design. It is the driving force behind the shift to multi-cores in today's computing systems. Ever-higher clock frequency scaling is unsustainable due to power-density and thermal limitations [105]. Parallel programming on multiple cores has the potential for increased performance without increased power. Power is also the reason for increased processor heterogeneity. Dark silicon [45] suggests that as it will not be possible to simultaneously power-up all the cores on a chip, cores should be specialised to best utilise the available power.

Simple heterogeneous GPU based systems are now common-place. More challenging heterogeneous platforms are likely to become more prevalent in the future like TI OMAP4430 [6] and Samsung Exynos 5422 [3] platforms which contain heterogeneous CPUs, heterogeneous GPUs and DSP cores. The non-CPU processors in these platforms are generally used for offloading to improve power efficiency/performance. These processors have different micro-architecture, memory hierarchy and/or Operating Systems. There is no single programming language, library or runtime to program these platforms. Hence, these are highly challenging to program but offer the potential for excellent power and performance.

Given that, it is not possible to run all cores at their maximum clock rate frequently for long periods; runtime power-management is needed to keep within the thermal constraints[105]. Such power management is the responsibility of the operating system or hardware which uses *DVFS* or power gating to reduce power at the expense of performance. This approach works well with homogeneous multi-cores or single-ISA heterogeneous cores as there is no need to modify the binaries. However, if, due to dark silicon [45] there are diverse cores each with their own ISA and specialised behaviour, there is no straightforward approach to using the right cores based on program suitability and available power budget. The task is to select the cores and the hardware settings that meet the budget and give the best performance and then allocate the appropriate amount of work to each core.

#### **1.2** Contributions

This thesis presents the following contributions.

- Develops a framework for manually mapping data parallel programs to OMAP4, a highly heterogeneous systems. It presents a detailed energy measurement methodology. It explores a partitioning design space and shows its dependency on optimisation goal: energy vs time. A straightforward partitioning approach is presented and evaluated. It is shown that improvements can be obtained by partitioning programs for heterogeneous systems.

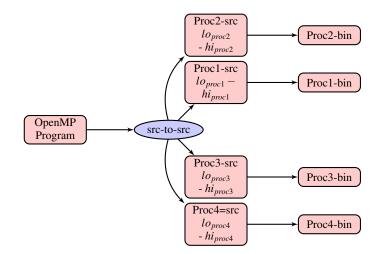

- 2. Develops a Clang/LLVM based compiler approach to map OpenMP programs to MPSoCs. This compiler framework bridges the gap between the high-level programming model of OpenMP and the heterogeneous resources of MPSoCs. It takes OpenMP programs and generates code which runs on all the processors. It delivers programming ease while exploiting heterogeneous resources. The compiler is based on a Single Program Multiple Data model where data layout is explicitly determined, allowing reasoning about memory coherence and synchronisation placement. This compiler approach achieves significant performance improvements over existing approaches on the TI OMAP4.

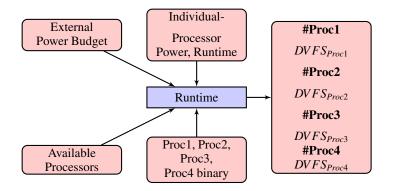

- 3. Develops a compiler-based approach to runtime power-management for hetero-

geneous cores. Given an externally provided power budget, it generates heterogeneous, partitioned code that attempts to give the best performance within that budget. At runtime, it selects parameters determining the workload on each core. A number of different selection policies that combine program and system information are presented. This approach is applied to parallel OpenMP benchmarks on the OMAP 4430 and Exynos 5422 platforms.

### **1.3** Thesis Organisation

The thesis is organised as follows.

- **Chapter 2** presents the background necessary to understand the work presented in this thesis. This chapter presents an introduction to Multiprocessors and then discusses details, examples and challenges of heterogeneous multicores. Compiler issues in heterogeneous multicores are presented next. And finally, details of the measurements and benchmarks used in the experiments in the thesis are discussed.

- Chapter 3 presents a survey of related work. Work related to mapping parallelism, Programming and Compilers for heterogeneous programming and Energy measurements are discussed.

- **Chapter 4** presents a design space exploration in the partitioning of data-parallel programs for heterogeneous multicore processors. Through the exploration, it is shown that the best partitioning varies with optimisation criteria and benchmarks. A straightforward method for partitioning programs is also presented.

- **Chapter 5** presents a compiler framework for mapping data-parallel programs to heterogeneous MPSoCs. It is shown that smart insertion of cache flushes is necessary to attain good performance in a non-cache coherent heterogeneous multicore processor.

- **Chapter 6** explores issues in code generation for heterogeneous processors in the presence of a power budget. Typically, the OS or hardware changes the volt-age/frequency using DVFS to meet the power budget. Heterogeneity provides another dimension for meeting the power budget. This work presents an approach for code generation in the presence of a power budget for heterogeneous multicore processors.

**Chapter 7** concludes this thesis and presents the main contributions. The chapter also includes a critical analysis of the solutions presented as well as discusses possible future work.

### 1.4 Summary

This Chapter provided an introduction to the work presented in this thesis. The Chapter provided a brief overview of the problems in mapping parallelism to heterogeneous multicores and also summarised the contributions of this thesis. Finally, it also provided the organisation of the Chapters of this thesis.

The next Chapter provides background reading for understanding the work presented in this thesis.

## **Chapter 2**

# Background

This chapter presents the technical background necessary to understand the material presented in this thesis. The first Section 2.1 introduces multiprocessors. Section 2.2 covers heterogeneous multiprocessors which is the focus of this thesis. Parallel programming frameworks which can be used for programming multiprocessors are introduced in Section 2.3. Compiler issues relevant to heterogeneous processors are described in Section 2.5. Section 2.6 describes issues in runtime and power measurements. Finally, Section 2.7 briefly discusses the various benchmarks used in the experiments presented in this thesis.

#### 2.1 Multiprocessors

There is always a demand for increased computation speed from processors. Microprocessor architects have traditionally met this requirement by increasing processor frequency, improvements in memory hierarchy (like caching), pipelining, compilers/processors exploiting instruction level parallelism, etc. However, there has been greatly diminished gains in processor performance because of limited instruction level parallelism, difference in speeds of the memory and processor, and an exponential increase in power consumption for every small increase in frequency. Due to the diminishing returns, processors makers have adopted a different approach to improving a computers performance by adding extra processors. A multiprocessor is a processor which contains more than one processor core.

These multiprocessors can directly address and access all the memory in the system. However, depending on the location/speed of memory access, the Multiprocessors are generally categorised into two types. In **Uniform Memory Access (UMA)** machines, all processors require the same time to access any memory location. The multicore systems used on the desktops/workstations and the MPSoCs used in embedded systems fall under this category. In **Non Uniform Memory Access (NUMA)** machines, a processor can access the memory associated with it quickly, but to access memory associated with another processor it requires to wait for more time. In this thesis, the focus is on UMA machines.

Depending on the kind of processors involved, Multiprocessors can also be categorised into two, **Homogeneous** and **Heterogeneous**. If all the processors in a multiprocessor are of the same kind, then it is a homogeneous processor. Otherwise, it is a heterogeneous multiprocessor. Most of the processors in desktops and workstations are homogeneous.

#### 2.2 Heterogeneous Systems

The term Heterogeneous Systems encompasses a wide variety of processor systems. The term is commonly used to define multiprocessor systems where the processors have different capabilities and architecture. Heterogeneous processors provide better power-performance trade-offs. This is advantageous when a program has sections of code with different characteristics or if the workload consists of programs with different characteristics. Heterogeneous systems can be classified into two types based on ISA viz. single ISA and multiple ISA.

#### 2.2.1 Single ISA

Single ISA heterogeneous systems are systems which have processors with a single-ISA but different micro-architecture. e.g., big.LITTLE processors from ARM.

#### 2.2.2 Multiple ISA

Multiple ISA heterogeneous systems are systems which have processors with different ISAs. There are mainly two types of Multiple ISA systems that are commonly seen, CPU-GPU systems and MPSoCs. e.g., Intel IvyBridge and Samsung Exynos.

#### **CPU-GPU Systems**

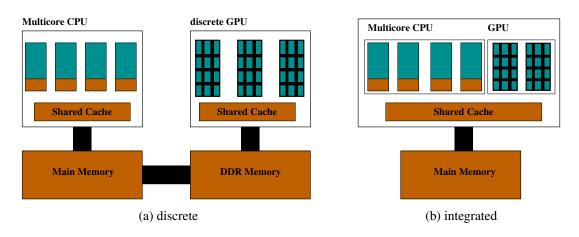

The most common heterogeneous systems are CPU-GPU systems. CPU-GPU systems, as the name suggests, are heterogeneous systems with a multicore CPU and a GPU. Traditionally, the GPUs were used for graphics processing. But over the years, the GPUs were found to be suitable for programming data-parallel applications. These GPUs are composed of a number of Stream Processors/Shader cores. Each core has many hardware threads with a single program counter and works as a Single Instruction Multiple Data (SIMD) machine. CPU-GPU systems can either be discrete or

integrated. In discrete systems (Figure 2.1a), GPUs sit on an external card which is connected to the CPU through the PCI bus. Recently, the GPUs have been integrated (Figure 2.1b) on the same chip like in Intel Ivy Bridge, AMD Fusion and many Embedded MPSoCs like Samsung Exynos. Generally, the CPU is used for computing code with control, and the GPU is used to compute code which has lot of data-parallelism.

Figure 2.1: GPU

#### **MPSoCs**

Multiprocessor System on Chip (MPSoC) is a VLSI system that integrates all of the systems required to run an application on a single chip. It contains several processors that are specialised for various purposes. MPSoCs are widely used in the embedded systems world particularly in cellphones, network and signal processing, and multimedia. MPSoCs started off as homogeneous systems, but later, due to performance and power requirements, these became heterogeneous. A survey of the history of MP-SoCs can be found in [124]. In this section two MPSoCs, viz. OMAP and Exynos are discussed in detail.

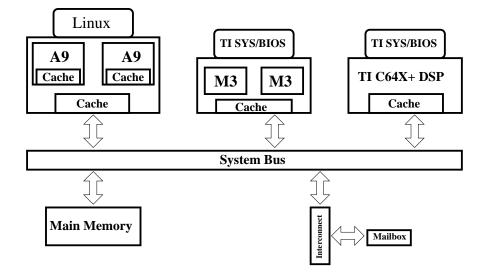

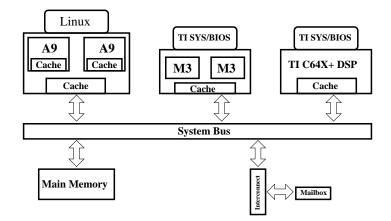

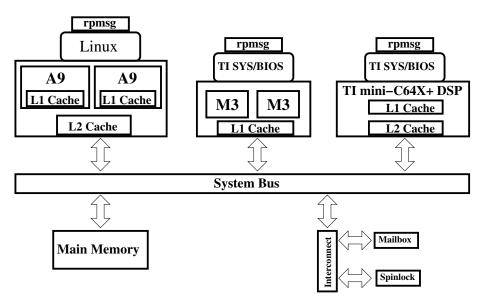

The TI OMAP4430[7] is a typical mobile application MPSoC consisting of various subsystems including general purpose processors, a programmable multimedia engine plus graphics and image accelerators. Figure 2.2 shows the components of the OMAP4430 relevant to this thesis. A dual core ARM Cortex-A9 provides general purpose computing. Both processors share a common L2 cache and address space. There are two smaller ARM Cortex-M3s available for smaller and lower power tasks. Both share a common L1 cache and are responsible for controlling the graphics and image accelerators. There is also distinct programmable multimedia engine based on a TI mini-C64X+ DSP. The PowerVR GPU cannot be currently programmed, since the

Figure 2.2: OMAP4 block diagram

OpenCL driver is not publicly available, and is not considered in our study.

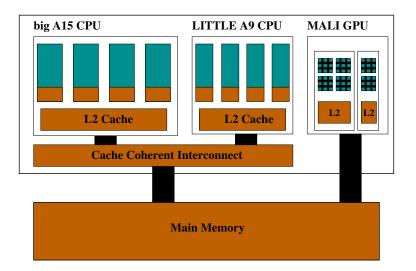

The Exynos 5422[3] is a Samsung platform consisting of 4 ARM Cortex A15 big CPUs, 4 ARM Cortex A7 big little CPUs and 1 Mali T628 MP6 GPU. The Mali T628 consists of 2 devices: one with 4 shader cores, the other with 2. Also, there are 20 DVFS levels available on the A15s, 15 on the A7s and 6 on the Mali. A program can run on any combination of the processors. Figure 2.3 shows the components of Exynos platform relevant to this thesis.

Figure 2.3: Exynos block diagram

#### **2.3 Parallel Programming Models**

Parallel programming models are abstractions for modelling parallelism in applications. There are various kinds of parallel programming models like data-parallel model, task parallel model, stream parallel model, pipeline parallel model etc. This thesis focuses on data-parallel model.

#### 2.3.1 Data Parallel Model

In data-parallel model, the same operation is performed on different sections of an array at the same time. This kind of parallelism is normally found in array based programs with corresponding parallel loops. These are programs where individual elements of an array/data structure can be independently computed. Such programs are widely found in embedded systems applications.

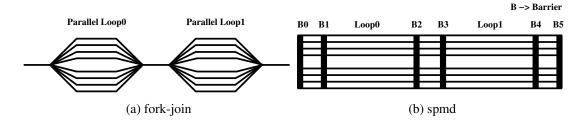

The focus of this thesis is data-parallel programs. There are many ways to implement data-parallelism. Two methods, fork-join and SPMD are discussed in the next two paragraphs. These two methods are pictorially represented in Figure 2.4.

#### fork-join

In the fork-join model, execution starts as a single master thread and on reaching a parallel region, threads of execution are forked off and later these threads join at a point and sequential execution resumes. By default, the number of threads forked is equal to the number of available processors. However, systems implementing fork-join model typically provide features to control the number of threads. The number of threads are not fixed for the whole program and can vary for different parallel regions. Fork-join model provides ease of programming since it is necessary to only specify the parallel regions. Fork-join does not require the data/work to be partitioned in advance. Work partitioning is implicit in the fork-join model, and typically it is the job of the runtime to partition work among the available processors. Since partitioning is performed by the runtime, the work distribution can adapt to the workload. However, presence of a runtime for partitioning and forking and joining of threads introduces overheads which can negatively impact system performance. eg. OpenMP.

#### SPMD

The Single Program Multiple Data (SPMD) model of parallelism is well known and used in a variety of settings. In SPMD, parallel tasks run the same program but operate on independent sections of an array. It is a data-centric approach where data is first partitioned and scheduled to processors. Computation is then partitioned and sched-

Figure 2.4: Programming Models

uled in accordance with this data allocation. Nearly all schemes use an owner-compute or local-write rule where the code executed on a processor is restricted to write to just local data. Unlike the fork-join model, there is no master thread. At program start itself, all the threads start running in parallel. The number of threads correspond to the number of processing elements and are fixed throughout the execution of a program. Synchronisation is not associated with the beginning or end of parallel loops but whether or not there is a cross-processor data dependence i.e., data written on one processor is read on a different processor. Barriers are inserted to honour such dependences. e.g., Unified Parallel C (UPC) is an extension of the C language which uses the SPMD model.

#### 2.4 Parallel Programming Frameworks

To take advantage of the multiprocessors, a parallel programming framework should be used. A parallel programming framework implements one or more of the parallel programming model described in the previous section. The frameworks are usually implemented as language extensions and libraries on top of existing programming languages like C/C++, Fortran, etc. In this section, we take a look at some relevant parallel programming API/libraries, pthreads, OpenMP and OpenCL.

#### 2.4.1 POSIX threads

POSIX threads (or pthreads)[85] is a portable standard for threads. pthreads API is available for many operating systems like Linux, FreeBSD and MacOS. The API provides functions for creating and manipulating threads. Threads are created using pthread\_create and pthread\_join is used to wait for termination of threads. The API also provides for mutual exclusion and synchronisation between threads. There are also functions for signalling and waiting on condition variables. An example for vector addition using pthreads is given in Listing 2.1. The function *vector\_add* is executed by each thread.

```

struct thread_params {

int start_indx ;

int end_indx ;

};

void *vector_add(void* t)

struct thread_params* tp = (struct thread_params*)t ;

int i ;

for (i=tps->start_indx ; i<tps->end_indx ; i++) {

C[i] = A[i] + B[i] ;

}

return NULL ;

void vector_add_threads()

pthread_t thread[NUM_THREADS] ;

thread_params tp[NUM_THREADS] ;

int unit_size = N/NUM_THREADS ;

int cur_start = 0;

for (int i=0 ; i < NUM_THREADS ; i++) {

tp[i]->start_indx = cur_start ;

tp[i]->start_indx = cur_start + unit_size ;

pthread_create(&thread[i], NULL, vector_add,

(void*)&tp[i]);

cur_start += unit_size ;

}

for (int i=0 ; i < NUM_THREADS ; i++) {

pthread_join(thread[i], NULL) ;

```

Listing 2.1: pthread vector addition

#### 2.4.2 OpenMP

OpenMP[42] is a widely used high-level shared memory pragma based programming language. The popularity of OpenMP is due to its ease of use and wide availability. OpenMP consists of a set of compiler directives in the form of comment like pragmas. These are used to mark parallel loops and tasks. There are also directives for specifying scheduling of work, declaration of both shared and private variables and critical sections. OpenMP supports the *fork-join* programming model. In this model, a program starts as a single master thread. When an OpenMP parallel construct is reached a team of threads is *fork*ed. These threads co-operatively perform the work in parallel. At the end of the construct all the threads *join* and only the master thread continues. Rather than creating and destroying threads at the start and end of parallel regions, most implementations have a pool of threads available which are used and synchronised as

needed. An example for OpenMP vector addition is given in Listing 2.2.

```

#define N 100

void vector_add()

{

int i ;

#pragma omp parallel for

for (i = 0; i < N; i++)

{

C[i] = A[i] + B[i] ;

}

return 0 ;

}</pre>

```

#### 2.4.3 OpenCL

OpenCL is a programming framework for heterogeneous devices. It has gained a lot of popularity for programming GPU devices. In the OpenCL hardware architecture, there is a host which controls various Compute Devices. The Compute Device is composed of many Compute Units, and each Compute Unit is further composed of Processing Elements.

The code that runs on the host is called the host code and that which runs on the device is called kernel code. The host code is responsible for setting up the OpenCL environment, command queues, buffers and launching the kernel. The OpenCL buffers are different from the memory that can be accessed by the host device. So the data from the memory has to be copied to the device buffer before computation can begin and copied back after computation. If the copy overhead has to be overcome then the flag *CL\_MEM\_USE\_HOST\_PTR* has to be used when creating OpenCL buffers. The host code performs all these operations using OpenCL API. Command queues have to be created for each compute device. These queues can then be used for submitting OpenCL kernels for execution on the compute devices. The OpenCL kernels execute in parallel on the Processing Elements.

```

//file: vector_add.cl

__kernel void vector_add(__global int* A,

__global int* B,

__global int* C)

{

int i = get_global_id(0) ;

C[i] = A[i] + B[i] ;

return 0 ;

}

```

```

int main( int argc, char* argv[] )

cl_int err ;

// Create OpenCL queue, context, program etc

cl_kernel = clCreateKernel(program, "vector_add",&err) ;

// Size, in bytes, of each vector

size_t bytes = N*sizeof(int) ;

size_t globalSize = N ;

// Device input and output buffers

cl_mem dA = clCreateBuffer(context,CL_MEM_READ_ONLY, bytes,NULL,NULL) ;

cl_mem dB = clCreateBuffer(context,CL_MEM_READ_ONLY, bytes,NULL,NULL);

cl_mem dC = clCreateBuffer(context,CL_MEM_WRITE_ONLY, bytes,NULL,NULL) ;

// Copy the contents of arrays A and B to device memory

err = clEnqueueWriteBuffer(queue,dA,CL_TRUE,0,bytes,A,0,NULL,NULL) ;

err |= clEnqueueWriteBuffer(queue,dB,CL_TRUE,0,bytes,B,0,NULL,NULL);

// Set kernel arguments

err = clSetKernelArg(kernel,0, sizeof(cl_mem),&dA) ;

err |= clSetKernelArg(kernel,1,sizeof(cl_mem),&dB) ;

err |= clSetKernelArg(kernel,2,sizeof(cl_mem),&dC) ;

// Execute the vector_add_kernel

err = clEnqueueNDRangeKernel(queue, kernel, 1, NULL,& globalSize, NULL, 0, NULL, NULL);

// Wait for kernel to finish execution

clFinish(queue) ;

// Copy results from the device

clEnqueueReadBuffer(queue, dC, CL_TRUE, 0, bytes, C, 0, NULL, NULL);

// release OpenCL resources

clReleaseMemObject(dA) ;

clReleaseMemObject(dB) ;

clReleaseMemObject(dC) ;

//Free kernel, queue, context, program etc

return 0 ;

```

Listing 2.3: OpenCL vector addition

A single unit of the OpenCL kernel is called a work-item. Work-items are arranged in an n-dimensional space, and the number of dimensions and the number of work-items in each dimension is specified in the launch command. An example for OpenCL vector addition is given in Listing 2.3. Here *vector\_add* is the kernel that gets executed on each processing element. API calls for obtaining the platform and device IDs, creating and destroying the context, creating and destroying the program and building the program

are omitted for brevity.

#### 2.4.4 Comparison

Table 2.1 compares the characteristics of pthreads, OpenMP and OpenCL parallel programming frameworks. For all these frameworks the parallelism has to be explicitly specified. While partitioning is explicit for OpenMP, it is implicit for pthreads and OpenCL. OpenCL follows the SPMD model whereas pthreads and OpenMP follows the fork-join model.

|              | pthreads  | OpenMP    | OpenCL   |

|--------------|-----------|-----------|----------|

| Parallelism  | Explicit  | Explicit  | Explicit |

| Partitioning | Explicit  | Implicit  | Explicit |

| Model        | fork-join | fork-join | SPMD     |

Table 2.1: Characteristics

### 2.5 Compiler

Computers are programmed using high-level programming languages. Using programming languages helps raise the abstraction level and makes the programmer more productive. Compilers help hide the details of the microarchitecture of the computer and translate the code in a high-level language to machine code. The Compiler ensures that the code generated is correct and the code generated matches the behaviour of the high-level source code. In multiprocessor systems, the compiler converts the code in a parallel programming framework and maps it to the various processors. The following subsections discuss the role of compilers in various kinds of processors.

#### 2.5.1 Uniprocessors

In traditional single processor systems, besides correctness, it is the job of the compiler to optimise the generated code. The optimisation criteria is generally performance, but in embedded systems it can be size of the generated code or energy consumption.

#### 2.5.2 Homogeneous Multiprocessors

Compiler generates code which works along with a runtime to run threads on different processors. Since all the processors are identical, the processors run the same code on all the processors. Since the performance of all the processors are identical, work can be uniformly partitioned and allocated to each of the processors.

#### 2.5.3 Heterogeneous Multiprocessors

Heterogeneous multiprocessors bring new challenges of its own. And the challenges vary depending on the kind of heterogeneity involved. Since the processors behave differently, code cannot be uniformly partitioned for all the processors. The other option is to use dynamic partitioning. But dynamic partitioning has increased overhead. This might also introduce additional complications for insertion of barriers and cache flushes in non-cache coherent architectures. The following paragraphs discuss issues that a compiler for heterogeneous processors has to deal with.

#### ISA

If the ISA is the same as in big.Little Processors, then the same binary can run on all the processors. If the ISA is different as in OMAP Processors, then different binaries are required. This issue is overcome by using a source to source translator to convert the code into intermediate form and then using separate compilers for each processor.

#### **Cache coherency**

If the caches are not coherent, then, a processor will not be able to read the values updated by another processor. Hence, if there are inter-processor dependencies in the code, it is the job of the compiler to insert flushes so that the processors read the updated values.

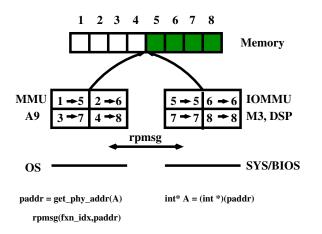

#### Address space

If address space is not the same for all the processors, then pointers are not portable. Hence, support is required from the runtime to convert the address so that all processors have access to the same arrays/memory locations.

#### 2.5.4 Clang/LLVM

LLVM [4] is a compiler framework. Clang is the frontend which does all the type checking and converts the input code into intermediate format. The LLVM optimiser then does optimisations on this IR and then a backend converts the optimised IR to machine code.

#### 2.6 Measurements

The experiments in this thesis mainly measure two quantities, runtime and power. This section dives briefly into the measurement of runtime and power.

#### 2.6.1 Runtime

Runtime is measured separately for each core and the entire system. Runtime is measured by using the *gettimeofday* system call. Calls are made to this function before and after the execution, and the runtime is the difference of the times. All the runtime measurements are made on the CPU side. System calls form part of any communication between the processors. Hence, the runtime of these calls has to be included in our runtime measurement. An API function which measures the system time as well as user time is required. For these reasons, the *gettimeofday* API function is used. This function is called before forking off the threads and after the threads join. The difference in time between these two calls is the execution time.

#### 2.6.2 Energy

Energy is the sum of power over time. Measuring power and hence energy is highly non-trivial. This section describes in detail the methodology used to accurately measure power and discusses how it should be accounted for.

Power consumption is found by measuring the current consumed by the processor and multiplying by the supply voltage. The current consumption cannot be directly measured from the whole board supply since it is very noisy and hence is not accurate enough to distinguish between partition decisions. Also, the individual consumption of each processor has to be measured. Hence, each processor's power consumption is separately measured. The power consumed by the memory has to be measured. To measure the current, a resistor is found in the path of these power rails and the voltage drop across the resistor is measured and divided by the resistance. This method is described in detail by Jos [115].

#### **Power variation**

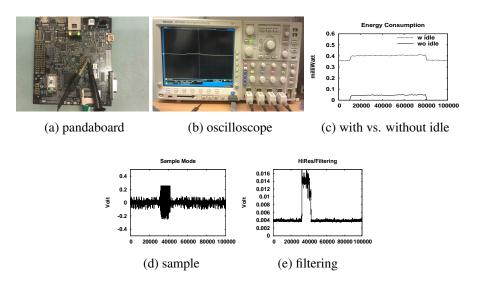

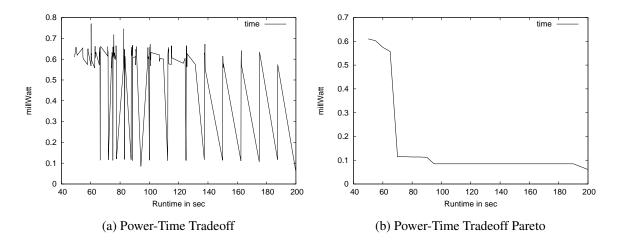

The method described gives a good insight into the power consumption. However in programs with phases, synchronisation and heterogeneous loops, the power consumption varies during the execution of an application. Hence, the voltage has to be continuously monitored. For this purpose, an oscilloscope is used, and readings are taken every millisecond. Figure 4.7a shows the pandaboard with probes attached to one pair of pins to take energy measurements. Figure 4.7b shows the oscilloscope with a measurement of the processor to which the probes are attached in Figure 4.7a. The resistance is measured using a digital multimeter. For our experiments, a Tektronix MSO4104 oscilloscope and Agilent 34410A digital Multimeter is used. Figure 4.7d shows a voltage reading from the oscilloscope in the regular sampling mode for the CPU when running the floydwarshall benchmark on the pandaboard. As can be seen, there is significant noise in the measurement. This can be overcome using either post-filtering using software or using the High Resolution measurement mode of the oscilloscope. Figure 4.7e shows the same measurement after filtering. All the rails are measured separately and summed up to find the total power/energy consumption.

### 2.7 Benchmarks

| Benchmark             | Short Name | Arrays                         | Suite     |

|-----------------------|------------|--------------------------------|-----------|

| Matrix Multiplication | mxm        | A[1024][1024], B[1024][1024],  | DSPstone  |

|                       | matm       | C[1024][1024]                  |           |

| Dotproduct            | dotp       | A[4194304], B[4194304]         | DSPstone  |

| Edgedetect            | edge       | image_buffer1[2048][2048],     | UTDSP     |

|                       |            | image_buffer2[2048][2048],     |           |

|                       |            | image_buffer3[2048][2048]      |           |

| Histogram             | hist       | image[4096][4096]              | UTDSP     |

| Doitgen               | dgen       | A[64][64][64], sum[64][64][64] | Polybench |

| Regdetect             | regd       | diff[64][64][2048],            | Polybench |

|                       |            | sum_diff[64][64][2048],        |           |

|                       |            | mean[64][64], path[64][64]     |           |

| FloydWarshall         | flwl       | path[512][512]                 | Polybench |

Table 2.2: Benchmarks

The benchmarks that are used in this thesis are data-parallel benchmarks taken from DSPstone[113], UTDSP[70] and Polybench [92]. These benchmarks are parallelised by annotating with OpenMP pragmas and then used for our experiments. Table 2.2 shows the name of the benchmark, short name used in the diagrams, the size and name of the arrays partitioned and the benchmark suite it belongs to.

Matrix Multiplication and Dotproduct are from the DSPStone benchmark. Matrix Multiplication multiplies two matrices and stores the result in a third matrix. Dotproduct multiples two vectors and stores the result in a third vector. Dotproduct has a reduction. Edgedetect and Histogram are from the UTDSP benchmark suite. Edgedetect is an edge detection algorithm for images; it has a few convolutions and application of a threshold. Histogram computes the histogram of an image and uses the histogram to make a grayscale mapping and finally uses the mapping to create the output image. Doitgen, Regdetect and FloydWarshall are from the Polybench suite. Doitgen is a multiresolution analysis kernel, and it contains some matrix operations. Regdetect is a regularity detection algorithm for 2D images. FloydWarshall is the all-pair shortest path algorithm.

### 2.8 Summary

This Chapter presented the necessary background for understanding the work presented in this thesis. The next Chapter presents a survey and commentary of published work related to the work in this thesis.

### Chapter 3

# **Related Work**

There is a large amount of related work in various areas associated with mapping parallelism for heterogeneous systems. A survey and discussion of the related work are presented in this Chapter. Section 3.1 presents a survey of work in heterogeneous multicore architecture. Related work in the area of Programming Languages for heterogeneous multicores is presented in Section 3.2. Section 3.3 presents related work in mapping parallelism. Section 3.4 presents an overview of work related to memory management issues. Finally, Section 3.5 presents an overview of work related to power and energy.

### 3.1 Heterogeneity

Multicore processors have now become ubiquitous in desktops and workstations. At the same time, these processors consume a lot of power. For e.g., Intel Core i7-5960X Extreme Edition based on Haswell-E Micro-architecture using 22 nm technology at 3 GHz with 8 Cores consumes around 140 W. Research in the last decade has advocated using heterogeneous multicores to get better power efficiency. Heterogeneous multicores are also widely seen in the Industry. In this section, prior research on heterogeneous multicore architectures is surveyed. Heterogeneous processors can be broadly classified into two categories, single ISA and multiple ISA. As the name suggests, the cores in a multiple ISA heterogeneous multiprocessor have different ISA while that on a single ISA heterogeneous multiprocessors by showing that they are more efficient. Single-ISA heterogeneous architectures are easier to program, and the runtime scheduling is also simplified because the same binary can be scheduled on different processors.

#### **3.1.1** Single ISA heterogeneity

Different applications have different resource requirements. Using the same processor architecture for different applications does not seem to be optimal. Even different sections of a single application have different resource requirements. Based on this argument, Kumar et.al[65] advocated single ISA heterogeneous processors for power efficiency. Single ISA heterogeneous processors are composed of cores which have the same ISA but different micro-architectural features or parameters. Single ISA Heterogeneity can be accomplished primarily by two methods. i) Varying the hardware on-board. For e.g., varying the issue-width, size of caches, reorder buffer, register file, etc. ii) Varying the frequency of the cores by DVFS. Lukefahr et.al[80] showed that using heterogeneous cores is better than DVFS.

While designing heterogeneous single ISA processors, there are many questions to answer. The space for a design space exploration is large, and it is not possible to exhaustively search. Metrics are also needed to measure and compare the various hardware configurations. Tomusk et.al[108] argues that choosing heterogeneous cores is a difficult task since the optimality of cores varies with programs. Various metrics (flexibility, non-uniformity, gap overhead, set overhead and generality) for evaluating heterogeneous processors are presented in [110] and [109].

#### 3.1.2 Multiple ISA heterogeneity

Multiple ISA heterogeneity has been widely investigated, and there exist many proposals to implement heterogeneity. One such way is to add specialised cores to the system. Traditionally, microprocessors were designed with a goal to achieve the best performance for 90% of the workloads. This makes these processors less energy efficient. 10x10[32] is a heterogeneous architecture which splits the workload into 10 different categories and design specialised cores for each of these 10 categories. GreenDroid[49] is a heterogeneous architecture where a processor is augmented with several cores specific to the applications.

Many research groups have explored multiple ISA heterogeneity by creating a heterogeneous system by combining more than one type of processors. Pangaea[125] is a heterogeneous chip multiprocessor with tightly coupled IA32 CPU cores and nonIA32 GPU cores. Marisabel et.al[53] explores the design space of a heterogeneous mix of server-class Xeon processors and mobile-class Atom processors and finds an optimal balance that achieves performance and energy-efficiency. Guo et.al[55] presents a heterogeneous architecture combining a LEON3 host processor and a Data Parallel Coprocessor (DPC). Twin Peaks[128] is a hardware-software co-designed heterogeneous multicore virtual machine which is an architecture with a wide in-order core and a narrow out of order core. Chung et.al[36] reports greater energy efficiency by combining traditional processors with unconventional cores like custom logic, FPGAs, or GPGPUs.

Another approach is to create heterogeneity by having a shared reconfigurable logic along with uniform cores. ReMAP[122] is a reconfigurable heterogeneous multicore architecture. In this architecture, a multicore is augmented with some reconfigurable logic. This reconfigurable logic is shared by all the cores. The cores can be separately augmented with additional functionality using this shared reconfigurable logic. The reconfigurable logic can also be used for inter-core communication and synchronisation.

The industry has also widely adopted heterogeneous multicore processors. Cell[62] was an early example of a heterogeneous multicore architecture which contained two types of processors, the Power Processing Element (PPE) and the Synergistic Processing Element (SPE). The PPE acts as a controller for the SPEs. A common kind of heterogeneity that is found is CPU-GPU systems such as Intel Ivy Bridge and AMD Fusion. An extreme example of heterogeneity is Xilinx Ultrascale MPSoC[15] which has ARM Cortex-53 cores, ARM Mali GPU, ARM Cortex R5 micro-controllers and programmable logic. The Embedded systems community has been the champions of Heterogeneous Processors. OMAP[6] from TI, Snapdragon[13] from Qualcomm, Exynos[3] from Samsung and Tegra[14] from NVIDIA are popular examples.

This thesis focuses on compiler approaches for using heterogeneous systems. In this work, TI OMAP and Samsung Exynos are used for experiments.

#### 3.1.3 **Prototyping Heterogeneity**

A framework for quickly prototyping heterogeneous computers is presented in [33]. Bakker et.al [20] presents a study where the Intel Single Chip Cloud Computer can be used for modelling a heterogeneous MPSoC and making power and runtime measurements. Fabscalar[35] is a toolset for composing heterogeneous RTL cores in a canonical superscalar template. HaDes[112] is an efficient approach for synthesis of dark silicon heterogeneous chip multiprocessors. The HaDes system determines the number of cores of each type such that the power and area budgets are met, and performance is maximised.

## **3.2 Programming Languages**

There are many programming frameworks and APIs for heterogeneous systems. This section surveys a few of these.

Cuda[2] and OpenCL[10] are APIs for CPU-GPU systems and use a master/slave accelerator model. These languages have special features to express task and dataparallelism. C++ Accelerated Massive Parallelism (AMP)[50] from Microsoft is a new C++ language feature and an STL like library for writing programs that execute efficiently on data-parallel hardware like GPUs. Open Accelerators (OpenACC)[9] developed by a consortium of Cray, CAPS, Nvidia, and PGI is an API for parallel computing for heterogeneous CPU/GPU systems. The code is annotated with pragmas/compiler directives to identify parallel regions of code that should be accelerated. A study[41] shows that even though languages like C++ AMP and OpenACC raise the abstraction level, they do not yet offer enough flexibility to extract the required performance.

Cell-Ss[21] exploits task level parallelism and requires source annotations as input, for identifying parallelism. OmpSs[8] is a programming model that supports asynchronous parallelism and heterogeneity. OmpSs is designed by combining features from OpenMP and the StarSs[90] Model. MAPS[103] is a compiler framework for programming MPSoCs using the streaming programming Model. It provides extensions to the C language for supporting Process Networks. Multicore Asynchronous Runtime Environment (MARE)[5, 96] from Qualcomm is a C++ API for parallel programming. It provides features for taking advantage of the full power (use all processors) of a heterogeneous system. The API provides features for creating tasks and setting dependencies between them. OpenCL code which can be run on GPUs can be wrapped in a task.

OptiML[29] is a Domain Specific Language (DSL) for machine learning which can be used to program heterogeneous systems. With this DSL, the domain knowledge can be used to express implicit parallelism.

This thesis chooses OpenMP as the source language. OpenMP is a widely used parallel API for programming shared memory multiprocessors. It is also a very easy to use API. OpenMP cannot be directly used on heterogeneous multicore processors. In this thesis, OpenMP is converted to SPMD form to run on heterogeneous multicore processors.

#### 3.2.1 Compiler

Compilers and runtimes for heterogeneous processors have to perform additional work. There are two main issues that have to be considered by the compiler. i) Often the parallelism present is not suitable for execution on a heterogeneous processor. Hence, it has to be transformed to a form that is suitable. In the work presented in this thesis, an OpenMP data-parallel program is converted to SPMD form. ii) Some heterogeneous processors do not have a cache coherent system. For these systems, it is the job of the compiler to handle coherency in software.

#### 3.2.2 OpenMP to SPMD

Liu et.al[78] presents a method for the translation of OpenMP Code into SPMD style with Array Privatisation. The translation is performed for use on High Performance Computing with uniform cores and a shared coherent address space. SPMD code consists of a set of threads that synchronise at barriers. To improve performance, the number of barriers has to be minimised. Prior work[111], [87] discusses techniques for reducing the number of barriers. This thesis builds on techniques presented in these papers for synchronisation and cache coherence.

# 3.3 Mapping Parallelism

Mapping parallelism present in a program to the underlying hardware architecture is a challenging task. The best mapping varies with architecture and is also dependent on program properties. Parallelism mapping can be broadly categorised into partitioning and scheduling.

#### 3.3.1 Partitioning

Bodin et.al[23] and Agarwal et.al[17] present theoretical frameworks for automatically partitioning parallel loops to minimise cache coherency traffic on shared-memory multiprocessors. Michel et.al [48] uses ILP to partition software for energy efficiency. MAPS[72] deals with programming for MPSoCs. The MAPS system extracts parallelism from sequential applications by partitioning and generates tasks for parallel execution on MPSoCs. Ravi.et.al[95] looks at offloading some work to be executed on a co-processor. In one of the techniques they discuss, sub-offload, they partition a loop for execution on a co-processor for better performance.

#### **CPU-GPU Systems**

Grewe et.al[52] presents a machine learning based method for partitioning programs between CPUs and GPUs. A two level predictor is employed where the first predictor decides whether the program has to be partitioned and the second predictor decides the ratio of partitioning. Qilin[79], constructs linear performance models at runtime. These performance models are sensitive to the size of the tasks also. The model is constructed by running a portion of the program on the CPU and the GPU. Jiang et.al.[60] and Shirahata et.al[104] runs tasks on both the CPU and the GPU to compute the individual runtime the first time a task is run. The observed runtimes are then used to proportionally partition the work between the CPU and the GPU. Mitra et.al[93] also partitions programs based on linear performance models and individual runtimes. In addition, they also calculate the degradation in performance of the CPU when running in parallel with the GPU and vice-versa. The work presented in this thesis also uses individual throughput(derived from runtime) of the processors to calculate the partitioning. Our work differs from the others in the following ways. 1) Rather than computing partitions on a per-kernel basis we partition the whole program. 2) The presence of inter-processor communication introduces overheads and hence affects the partitioning. We capture this aspect in our partitioning formula. 3) Our partitioning method is generalised for a set of heterogeneous processors and is not restricted to CPU-GPU systems.

#### 3.3.2 Scheduling Tasks

Prior work has explored runtime scheduling of tasks compared to compile time partitioning. Bower et.al[24] advocates tackling the heterogeneity at the OS scheduler level. Most other proposals involve a runtime.

Judit et.al[91] presents a Self Adaptive framework for choosing different versions of code at runtime for heterogeneous processors. In work presented in [106], phase transition points are marked and the application is switched to another core at these transition points for better performance. Kwon et.al [69] discusses issues in virtualisation on heterogeneous systems and presents a hypervisor scheduler which is heterogeneity aware and achieves improvement in performance. Whare-map[82] presents scheduling techniques for scheduling applications in a heterogeneous warehouse. The presented technique solves the mapping problem by formulating as an optimisation problem. The optimisation process uses profiling information.

Cong et.al[38] discusses energy efficient scheduling techniques for heterogeneous

multicore architectures. They develop a regression model to predict the energy consumption of each processor and use it along with code instrumentation and static analysis to perform scheduling at runtime. ACCESS[61] is a smart scheduling method for asymmetric cache CMPs. Applications with a small working set size and those which are streaming do not need a large size cache. Higher energy efficiency can be achieved by scheduling such applications on the cores with the smaller cache, switching off larger caches on lighter loads and running the processor at a lower voltage since the smaller cache can be operated at a lower voltage. Twin Peaks[128] dynamically chooses either a wide in-order machine or a narrow out of order machine for execution to achieve higher energy efficiency. The scheduling algorithm uses current and historical performance data. Raghunathan et.al[94] presents results which show that the best cores to choose vary with the job arrival rate.

This thesis deals with partitioning of data-parallel programs, and the focus is on minimising runtime, energy and meeting a power budget. Dynamic scheduling based approaches suffer from overheads particularly on cache incoherent systems and systems with multiple address spaces.

## **3.4** Memory Management

The main issues in memory management for heterogeneous systems are multiple address spaces and handling non-cache coherent systems.

#### 3.4.1 Multiple Address Spaces

Gelado et.al[47] suggests maintaining shared logical memory space for CPUs to access objects in the accelerator physical memory but not vice-versa. This method has the disadvantage that pointers from CPUs cannot be passed to the GPUs. Heterogeneous Systems Architecture (HSA)[98] is a standard developed for seamless integration of CPUs, GPUs and hardware accelerators. Traditionally, CPUs and GPUs have different address spaces, but in HSA-compatible systems, the GPUs can access the CPU virtual addresses. This enables passing of pointers between CPUs and GPUs. It also provides for optional coherence between the CPU and GPU through acquire and release instructions.

This thesis overcomes multiple address spaces issue by allocating memory in contiguous memory and appropriately mapping to each processor. The details of the method are discussed in Section 5.7.

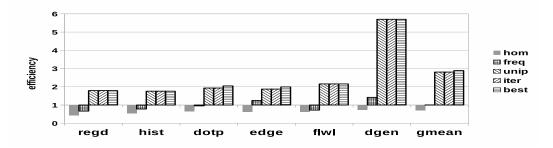

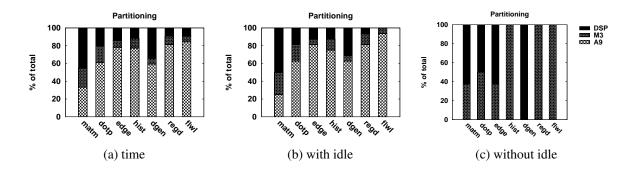

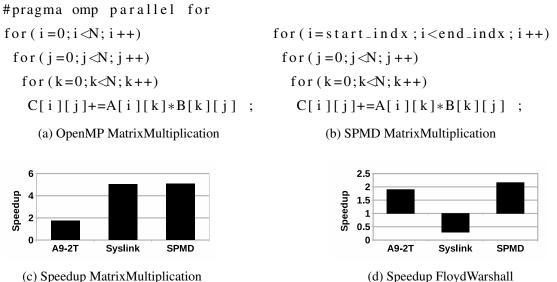

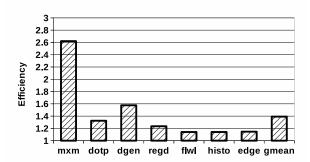

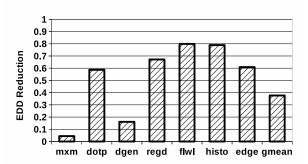

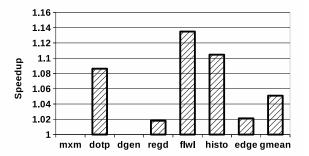

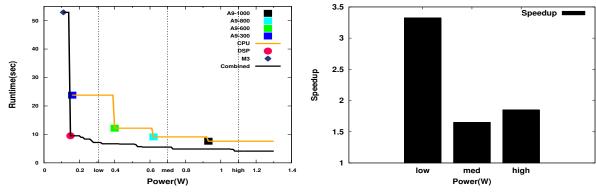

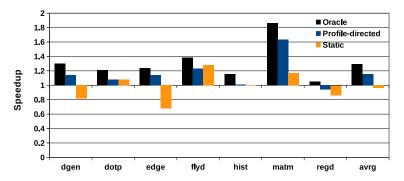

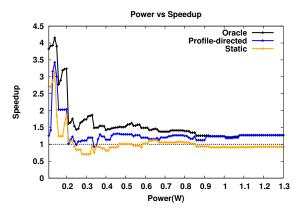

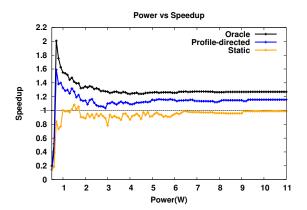

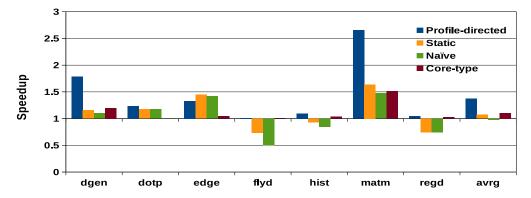

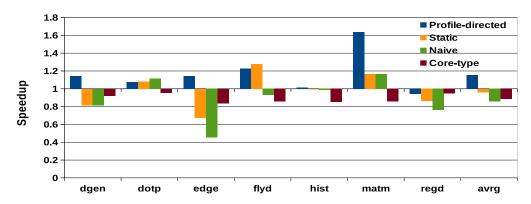

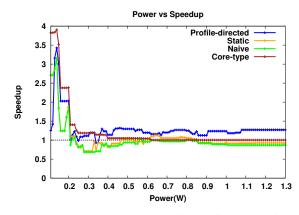

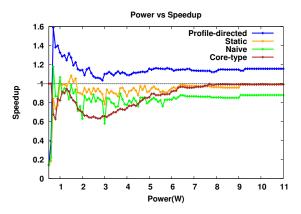

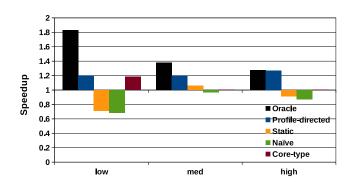

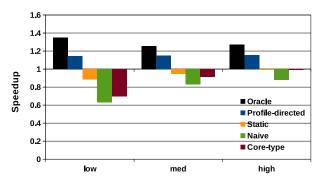

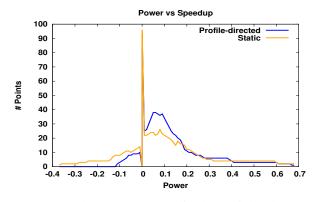

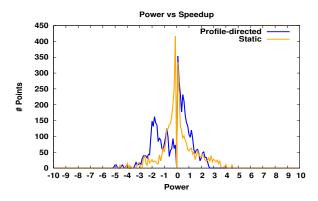

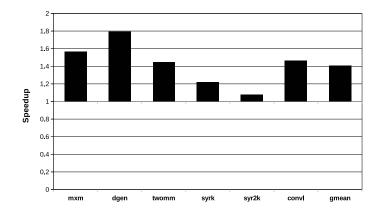

#### 3.4.2 Cache Coherence