# **Simulated Annealing Based Datapath Synthesis**

John Paul Neil

A thesis submitted for the degree of

Doctor of Philosophy

to the Faculty of Science of the University of Edinburgh.

1994

#### **Abstract**

The behavioural synthesis procedure aims to produce optimised register-transfer level datapath descriptions from an algorithmic problem definition, normally expressed in a high-level programming language. The procedure can be partitioned into a number of subtasks linked by a serial synthesis flow. Graph theoretic algorithms can be used to provide solutions to these subtasks. Many of these techniques, however, belong to a class of algorithm for which there is no exact solution computable in polynomial time. To overcome this problem, heuristics are used to constrain the solution space. The introduction of heuristics can cause the algorithm to terminate in a local cost minimum.

This thesis supports a global formulation of the behavioural synthesis problem. An algorithm which can avoid local minima, simulated annealing, forms the basis of the synthesis system reported.

A modular software system is presented in support of this approach. A novel data structure enables multiple degrees of optimisation freedom within the datapath solution space. Synthesis primitives, tightly coupled to a solution costing mechanism directed towards the prevalent datapath implementation technologies, form the core of the system. The software is exercised over small and large-scale synthesis benchmarks. The synthesis paradigm is extended by the provision of optimisation routines capable of supporting the generation of functional pipelines.

# **Declaration of Originality**

Except where noted in the text, the research recorded in this thesis is the original and sole work of the author.

John Paul Neil May 1994

# Acknowledgements

I wish to thank Professor Peter Denyer for providing a stimulating environment in which to work, and for his advice and direction during the course of the research recorded in this thesis. The financial support for this work was provided by the Science and Engineering Research Council and The University of Edinburgh; I am indebted to both institutions.

I acknowledge the support of the engineers seconded to the Silicon Architectures Research Initiative, notably Martin Ryder, David Mallon, Colin Carruthers, Ross Kennedy and Douglas Chisholm. My fellow research students, Douglas Grant and Iain Finlay have also been a source of great encouragement.

I would like to thank Dr. Edward McDonnell for proofreading this thesis.

Finally, my heartfelt thanks go to Janet for her love and support during the preparation of this thesis.

# **Contents**

| Abstract                                          | ii  |

|---------------------------------------------------|-----|

| Declaration of Originality                        | iii |

| Acknowledgements                                  | iv  |

| Contents                                          | v   |

| 1 Introduction                                    | 1   |

| 1.1 ASIC Design Domains                           | 2   |

| 1.2 Synthesis Tool Evolution                      | 3   |

| 1.3 Behavioural Synthesis Tools                   | 4   |

| 1.4 Summary of Research                           | 7   |

| 1.5 Thesis Structure                              | 9   |

| 2 Behavioural and Structural Models for Synthesis | 11  |

| 2.1 Two Alternative Behavioural Representations   | 12  |

| 2.1.1 Discussion                                  | 15  |

| 2.2 Data Flow Semantics                           | 18  |

| 2.3 Data Flow Syntax                              | 22  |

| 2.4 A Structural Notation                         | 23  |

| 2.4.1 A Processor Model                           | 24  |

| 2.4.2 A Memory Model                              | 25  |

| 2.4.3 A Communications Model                      | 26  |

| 2.4.4 Input and Output Ports                      | 27  |

| 2.5 Interlude - A Naive Mapping                   | 27  |

| 2.6 A Control Model                               | 28  |

| 2.7 Summary                                       | 31  |

| 3 Datapath Synthesis Techniques                   | 32  |

| 3.1 Scheduling Techniques                         | 33  |

| 3.1.1 Iterative Scheduling Schemes                   | 33 |

|------------------------------------------------------|----|

| 3.1.2 State Transformation Scheduling                | 42 |

| 3.1.3 Integer Linear Program Scheduling (ILP)        | 43 |

| 3.1.4 Discussion                                     | 44 |

| 3.2 Allocation Techniques                            | 47 |

| 3.2.1 Graph Theoretic Algorithms for Allocation      | 48 |

| 3.2.2 The Left Edge Algorithm.                       | 52 |

| 3.2.3 Bipartite Matching                             | 53 |

| 3.2.4 Edge Colouring                                 | 54 |

| 3.2.5 Expert System/Greedy Allocation Schemes        | 55 |

| 3.2.6 Other Techniques                               | 57 |

| 3.2.7 Discussion                                     | 57 |

| 4 Combinatorial Optimisation and Simulated Annealing | 59 |

| 4.1 Nomenclature and Definitions                     | 60 |

| 4.2 Searching The Solution Space                     | 62 |

| 4.3 The Simulated Annealing Algorithm                | 64 |

| 4.3.1 Cooling Schedule Techniques                    | 67 |

| 4.4 The Class NP and Behavioural Synthesis           | 72 |

| 4.5 Simulated Annealing and Behavioural Synthesis    | 73 |

| 4.6 Discussion                                       | 76 |

| 5 Simulated Annealing Based Synthesis Techniques     | 77 |

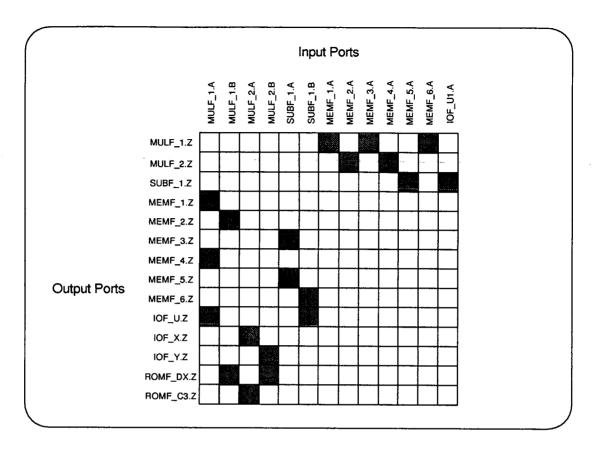

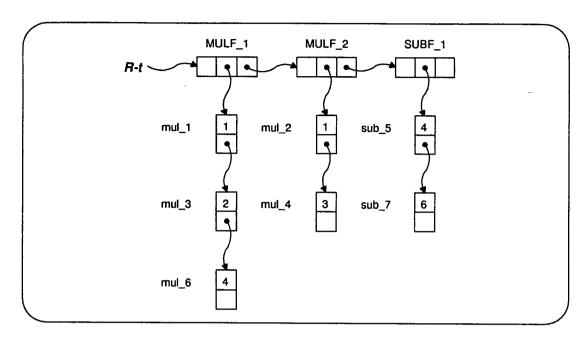

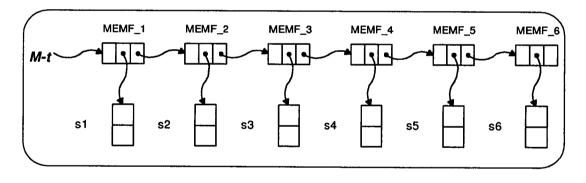

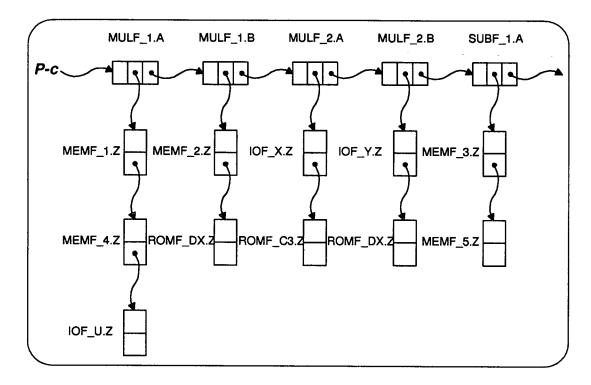

| 5.1 Data Structures                                  | 78 |

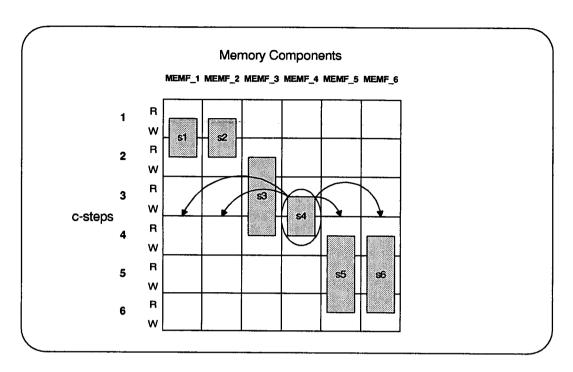

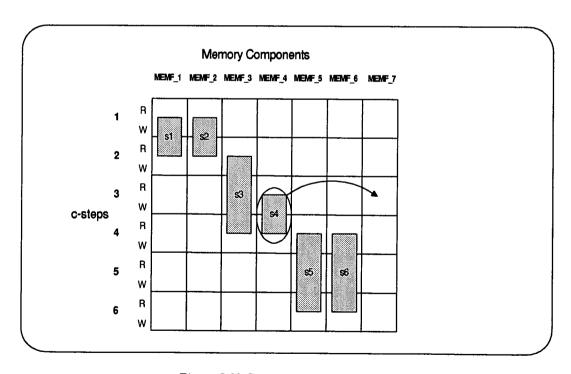

| 5.1.1 Resource-time Space                            | 79 |

| 5.1.2 Memory-time Space                              | 79 |

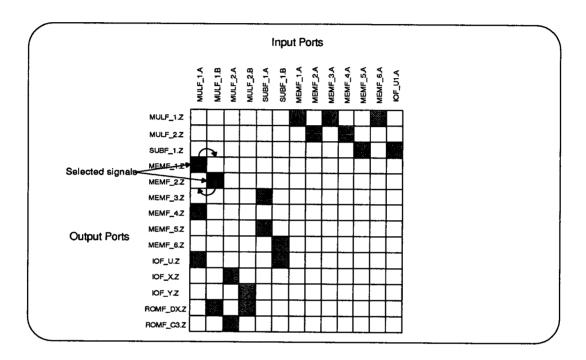

| 5.1.3 Port-connection Space                          | 80 |

| 5.1.4 Implementation Details                         | 81 |

| 5.2 Core Synthesis                                   | 84 |

| 5.2.1 Initial Control Parameter Value                    | 85  |

|----------------------------------------------------------|-----|

| 5.2.2 State Generation                                   | 85  |

| 5.2.3 Attaining Thermal Equilibrium                      | 86  |

| 5.2.4 Control Parameter Update                           | 87  |

| 5.2.5 Stopping Criterion                                 | 87  |

| 5.3 Datapath State Generation Move Sets                  | 88  |

| 5.3.1 Scheduling and Allocation                          | 88  |

| 5.3.2 Memory Optimisation                                | 92  |

| 5.3.3 Optimising P-c Space                               | 92  |

| 5.4 Solution Quality Assessment                          | 96  |

| 5.4.4 A Datapath Costing Model                           | 99  |

| 5.4.5 A Novel Cost Multiplier System                     | 100 |

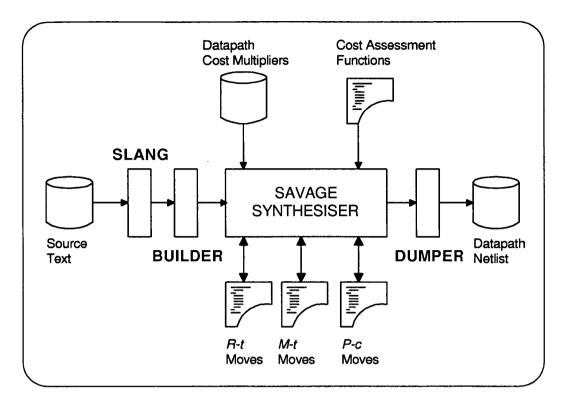

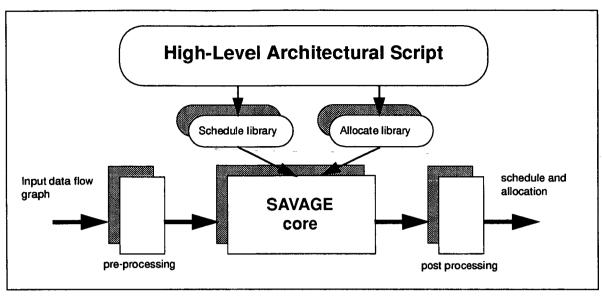

| 5.5 The SAVAGE Toolset                                   | 101 |

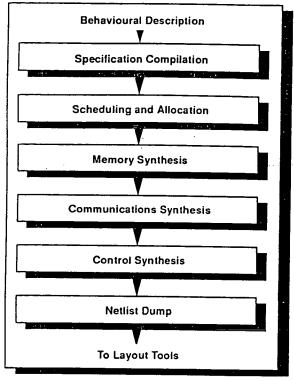

| 5.5.1 SAVAGE Synthesis Flow                              | 102 |

| 5.5.2 BUILDER                                            | 103 |

| 5.5.3 Datapath Verification and Validation               | 104 |

| 5.6 A Worked Example - Differential Equation Solver      | 104 |

| 5.6.1 A Maximum Speed Solution                           | 105 |

| 5.6.2 A Minimum Area Solution                            | 108 |

| 5.7 Summary                                              | 110 |

| SAVAGE Case Studies                                      | 111 |

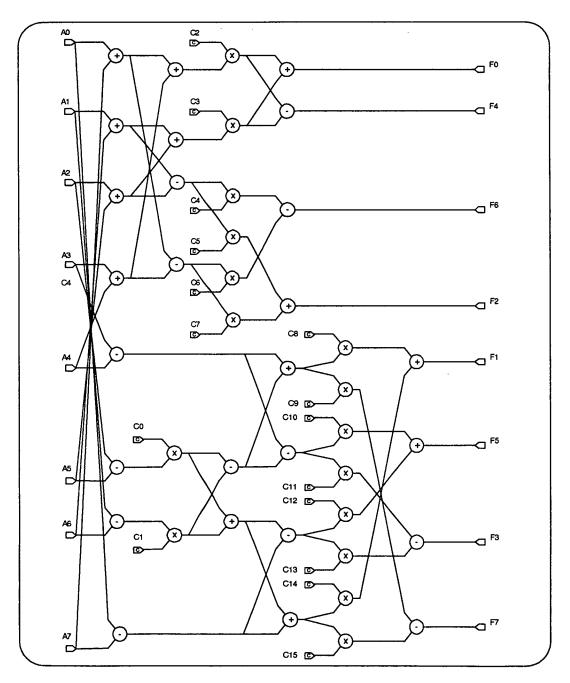

| 6.1 1-Dimensional 8 point Fast Discrete Cosine Transform | 112 |

| 6.1.1 A Resource Constrained Datapath                    | 115 |

| 6.1.2 A High Speed Solution                              | 119 |

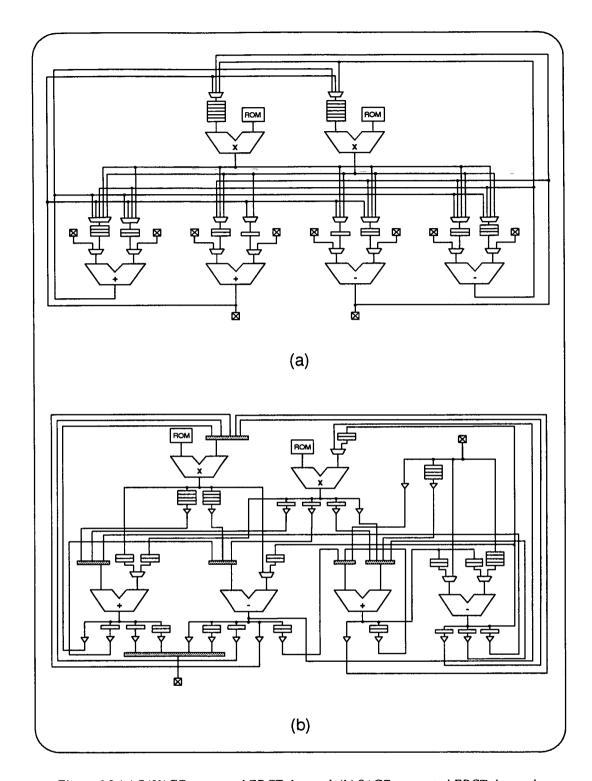

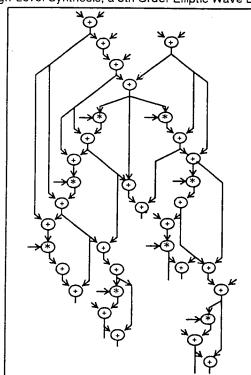

| 6.2 5th Order Wave Digital Filter                        | 121 |

| 6.2.1 Resource Constrained Datapaths                     | 122 |

| 6.2.2 A Maximum Speed Solution                           | 129 |

| 6.3 Discussion and Conclusion                            | 131 |

6

| 7 Synthesis of Functional Pipelines                       |     |

|-----------------------------------------------------------|-----|

| 7.1 Pipelining Nomenclature and Definitions               | 132 |

| 7.1.1 Structural Pipelining                               | 133 |

| 7.1.2 Functional Pipelining                               | 135 |

| 7.2 A General-Purpose Functional Pipelining Algorithm     | 136 |

| 7.2.1 A SAVAGE Implementation                             | 138 |

| 7.3 Examples                                              | 141 |

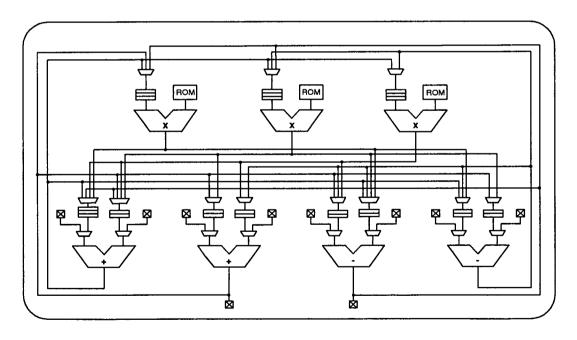

| 7.3.1 A Pipelined Fast Discrete Cosine Transform Datapath | 142 |

| 7.3.2 A Pipelined Wave Digital Filter Datapath            | 145 |

| 7.4 Discussion                                            | 147 |

| 8 Summary and Conclusions                                 | 149 |

| 8.1 Further Work                                          | 151 |

| 8.1.1 A Route to Silicon                                  | 151 |

| 8.1.2 Synthesis using Structural Input                    | 152 |

| 8.1.3 Design for Testability                              | 153 |

| 8.1.4 An Architectural Script-based Design Paradigm       | 154 |

| References                                                | 156 |

| A Differential Equation Datapath                          | 169 |

| B SAVAGE Optimisation Move Sets                           | 173 |

| B.1 R-t Optimisation Code                                 | 173 |

| B.2 M-t Optimisation Code                                 | 177 |

| B.3 P-c Optimisation Code                                 | 179 |

| C Publications                                            | 182 |

# 1 Introduction

The last decade has seen enormous leaps in the complexity of Integrated Circuits (ICs). Correspondingly, the design process associated with these circuits has grown lengthy and expensive.

Whereas the first ICs had typical complexities ranging from a few tens to a few hundreds of discrete logic structures, current devices have complexities ranging from many thousands to, in the case of dynamic Random Access Memory (RAM) designs, millions of logic structures. This increased complexity has arisen through advances in process technology and shrinking mask geometries. Moore's law [Moore79] states that the number of discrete components that can be placed on a single substrate will double every eighteen months. This affords engineers greater opportunities to increase the levels of integration within their designs, towards the level of total system integration on a single substrate.

A good example of this effort is the evolution of a single-chip fingerprint recognition system [Anderson91] developed at the University of Edinburgh. In its original conception, the system was composed of two Application Specific Integrated Circuits (ASICs) executing the recognition algorithm, an imaging subsystem, and two printed circuit boards containing interface and support logic. Subsequently, the recognition algorithms together with the imaging array were successfully integrated onto a single substrate [Anderson93].

While advances in process technology will ultimately be limited by fundamental physical constraints, the potential increase in functionality offered by shrinking mask geometries will act as a significant incentive to systems engineers to realise their designs in silicon for some time to come.

## 1.1 ASIC Design Domains

An ASIC may be specified in four separate domains:

- (i) **Behavioural.** Here the specification captures the *functionality* of the final circuit at a high level, but contains no details of the circuit *implementation*. The ideal behavioural specification is a number of sentences describing function of the circuit, but most behavioural specifications are captured using a high level programming language, such as VHDL, Verilog, C, or ADA.

- (ii) Macroarchitecture. This specification describes the circuit in terms of the functional blocks required to implement the circuit behaviour (communally known as a *datapath*), their interconnection, and the sequencing of the target algorithm on the datapath. This specification level is known as the *Register-Transfer Level* (RTL).

- (iii) Microarchitecture. The circuit microarchitecture models the diversity of implementation of the macroarchitecture at a gate level. For example, an adder block can be implemented in a number of different forms, e.g. ripple, carry lookahead, carry propagate, Manchester chain, and so on.

- (iv) **Physical.** The physical specification of the circuit takes place at the transistor level. The gate level description of the design is translated to a transistor level netlist containing sizing and connectivity information.

These domains suggest an ordering of the ASIC design process, with the functionality of a device captured first, followed by datapath macro- and microarchitectural development, prior to any physical implementation. Historically, however, successive generations of Computer Aided Design (CAD) tools have operated first in the physical domain, followed by the datapath microarchitectural level, and finally at the datapath macroarchitectural level. Current research efforts are focused on the development of CAD tools operating in the behavioural domain. Automatic translation between the design domains is termed *synthesis*.

# 1.2 Synthesis Tool Evolution

The first synthesis tools were targeted at the physical domain. During the design cycle of early ICs, each mask layer was specified separately, with engineers undertaking all the layout effort.

The advent of regular layout technologies such as standard cell logic and gate array structures, together with the development of physical design tools for block placement and routing, have enabled circuit engineers to concentrate on the development of a small number of primitive cells. These primitives can then be instanced many times to form the logic structures required. In the case of cell-based designs, logic gates are

defined in terms of fundamental building blocks (or *standard cells*). For gate array-based designs, logic structures are defined as the metalisation layers required to connect pre-instantiated gates.

Translation between the microarchitectural level and the physical domain exploits these regular layout technologies and the software tools supporting them. Logic gates can be specified in terms of Boolean equations [Brayton84] or entered in a schematic form and optimised prior to compilation into layout.

Translation between the macroarchitectural level and the physical level yielded the first software tools to be called *Silicon Compilers* [Johan78]. Typically, a functional circuit description was mapped into a template datapath architecture. The FIRST silicon compiler [Denyer82] was targeted towards bit-serial architectures. Similarly, research efforts at IMEC and Leuven University yielded the CATHEDRAL series of silicon compilers. The range of architectural templates included bit-serial (CATHEDRAL-I [Clae86]), communicating multiprocessor (CATHEDRAL-II [DeMan88]) and bit-sliced datapath (CATHEDRAL-III [Note88]). The quality of solution achieved in these systems is dependent on the mapping between the input algorithm and the architectural template.

# 1.3 Behavioural Synthesis Tools

Current CAD research is directed towards achieving a successful translation between the behavioural and macroarchitectural domains. Interest in high-level synthesis is motivated by the advantages of such an approach:

(i) Specification of an ASIC at a high level allows rapid functional verification. This should be contrasted with the gate-level verification required when a design is captured at the ASIC microarchitecture level.

- (ii) A high-level approach allows engineers to rapidly evaluate design alternatives at an early stage in the ASIC project cycle. Indeed Broderson [Broder89] argues that the true gains of realising a system in silicon arise through the selection of appropriate silicon architectures.

- (iii) High-level tools are *correct by construction*. The use of behavioural and logic synthesis to realise a design removes the possibility of errors introduced during manual translation between the design domains outlined above.

- (iv) High-level synthesis tools represent an *enabling technology*. By abstracting the design process away from the physical domain, the need for detailed circuit implementation knowledge is removed. Thus, ASIC technology becomes more accessible to system-level engineers.

The advantages offered by the use of behavioural synthesis tools address the problems imposed by market pressures described previously.

McFarland [McFarl88] defines the behavioural synthesis procedure:

"The synthesis task is to take a specification of the behaviour required of a system and a set of constraints and goals to be satisfied, and to find a (datapath) structure that implements the behaviour while satisfying the goals and constraints."

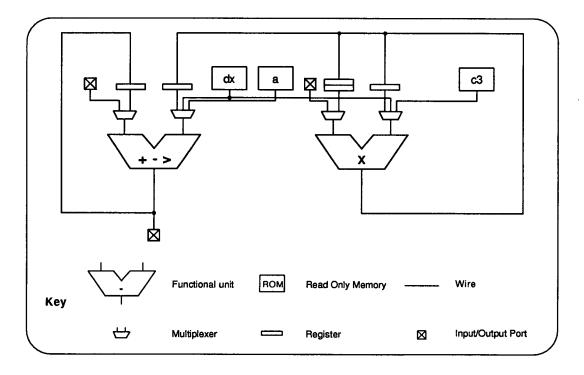

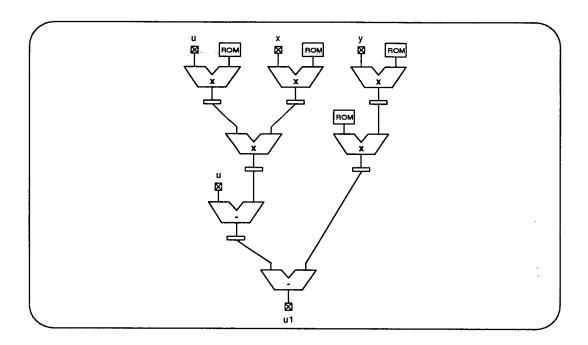

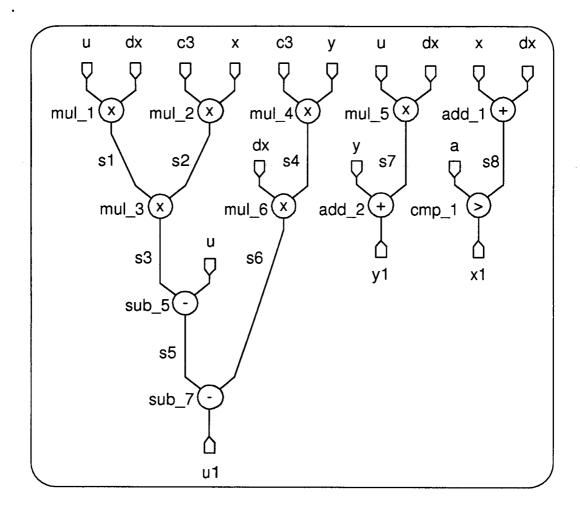

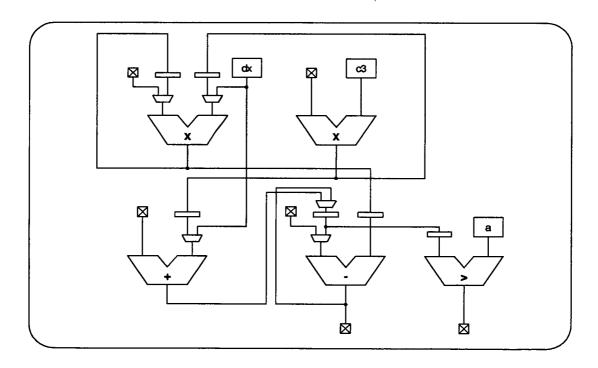

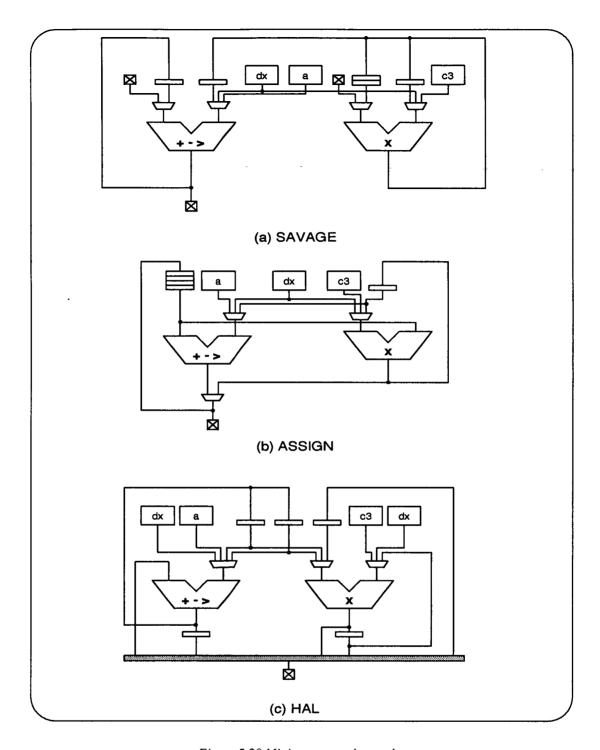

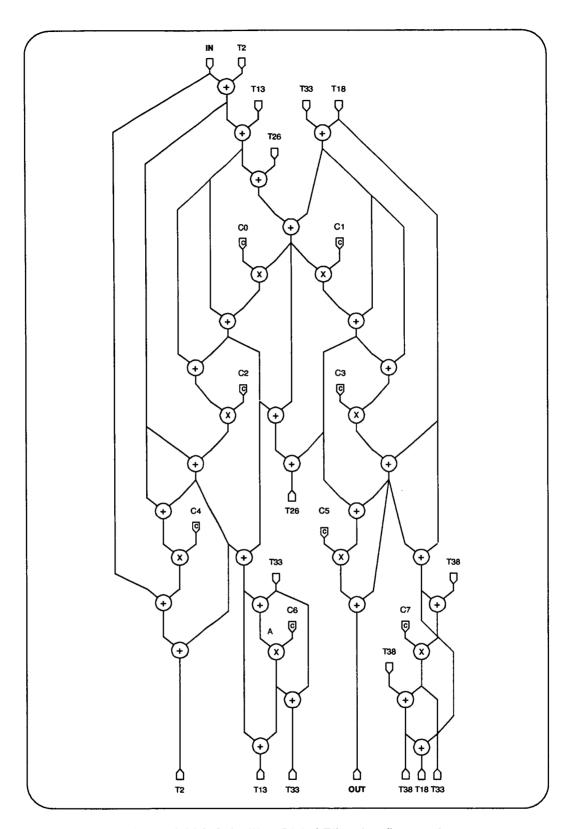

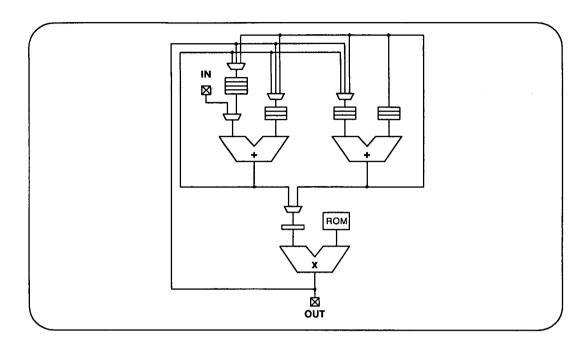

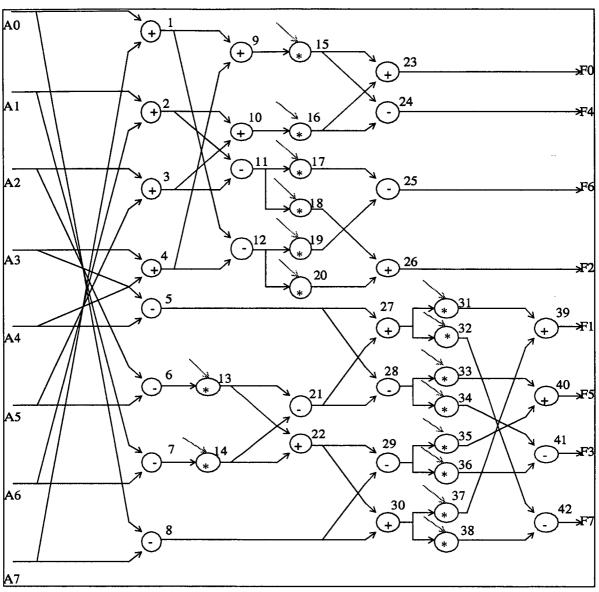

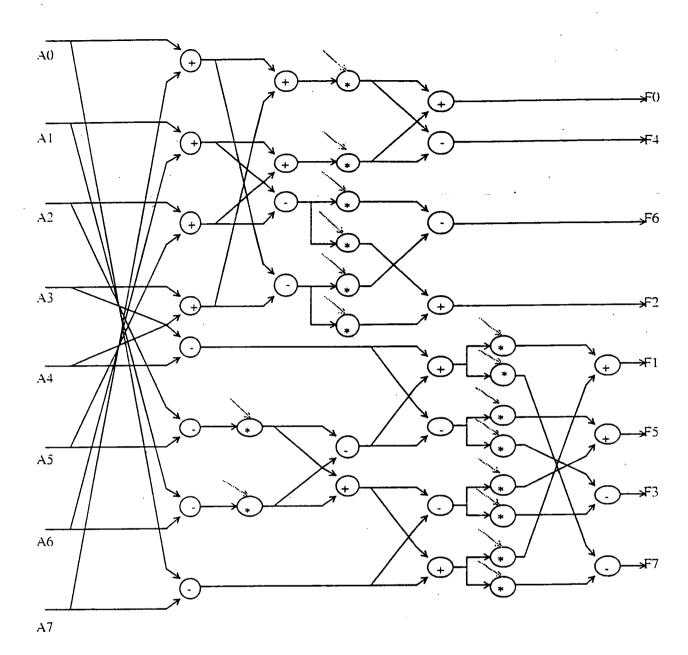

A typical behavioural specification is given in figure 1.1. A datapath optimised to offer a minimum area solution is shown in figure 1.2.

```

procedure DIFF_EQ (X, U, Y : in out INTEGER; A : in INTEGER) is

X1,Y1,U1 : INTEGER;

DX,C3 : CONSTANT;

begin

while (X < A) loop

X1 := X + DX;

U1 := U - (3*X*U*DX) - (3*Y*DX);

Y1 := Y + (U*DX);

X := X1; U := U1; Y := Y1;

end loop;

end DIFF_EQ;</pre>

```

Figure 1.1 Behavioural specification.

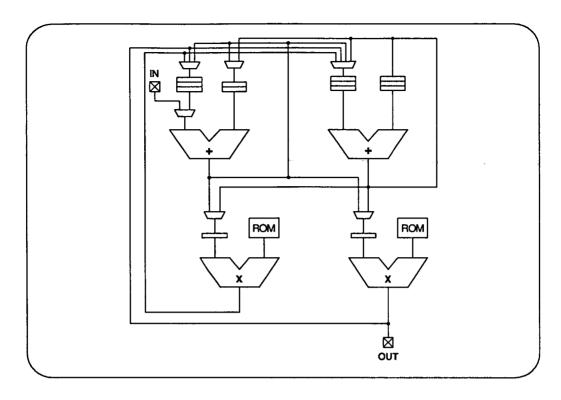

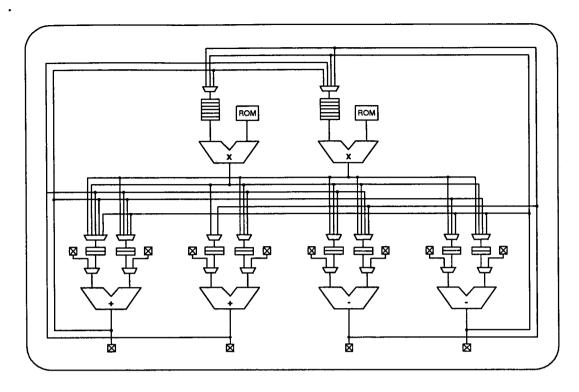

Figure 1.2 Datapath synthesised from specification shown in figure 1.1.

The behavioural synthesis procedure may be partitioned into the following subtasks:

(i) Translation of the behavioural description into some suitable

intermediate format. This data representation must retain all the characteristics of the original description, whilst presenting the data in a suitable and recognisable form. It is at this stage that compiler-like optimisations take place, such as loop unrolling (partial or complete) and dead code elimination [Aho86].

- (ii) Operator scheduling. This corresponds to the assignment of a control step value to each operation. A *control step* (c-step) corresponds to a single state of a finite state machine.

- (iii) **Processor allocation.** This step assigns individual operations to execute on particular hardware resources. These resources may be specialised (e.g. adders, multipliers and subtractors) or generic ALU-type structures.

- (iv) Memory allocation. An appropriate set of memory components must be synthesised to store intermediate results and input/output values.

- (v) Interconnect optimisation. A communications infrastructure is synthesised which connects all modules allocated in steps (iii) and (iv), and completes the datapath topology.

- (vi) Controller synthesis. This final phase generates a controller capable of sequencing all the operations and data transfers as defined in stages (ii) (v).

The research presented in this thesis is concerned with datapath synthesis techniques (i.e. tasks (ii) - (iv)).

## 1.4 Summary of Research

The partitioning of the behavioural synthesis procedure presented above, and the serial synthesis flow it suggests, has allowed optimisation techniques drawn from algorithmic graph theory [Gibbons87] to be used to solve the subtasks. In many cases, however, the solution algorithm belongs to a class of algorithms for which there is no

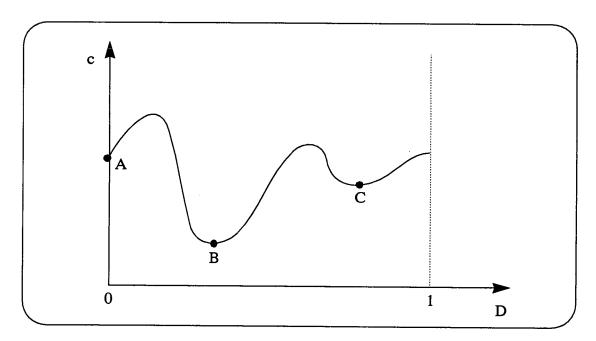

exact solution computable in polynomial time [Garey79]. The introduction of heuristics overcomes this problem by constraining the solution search space. The use of heuristics can, however, lead to the algorithm terminating in a local cost minimum, thus degrading the quality of the solution.

A global formulation of the behavioural synthesis procedure which avoids local minima is proposed in this thesis. A solution algorithm, *simulated annealing*, drawn from the field of statistical physics is used to control the search through the datapath solution space.

A suite of software tools is presented in support of this approach. Innovative features include:

- A multiple-plane data model which provides support for global optimisation of tasks (ii) - (v) above.

- A solution quality assessment procedure targeted towards the production of datapaths amenable to implementation in standard cell and gate array technologies.

- A cost multiplier mechanism which allows the engineer to influence the overall datapath architecture without *direct* synthesis intervention.

- The application of external system constraints is enabled through the use of synthesis directives or pragmas<sup>1</sup>.

Further, a general purpose algorithm for the generation of functional pipelines, which is suited to a simulated annealing-based implementation is presented.

<sup>1.</sup> This term was first introduced in [Clae86].

#### 1.5 Thesis Structure

Chapter 2 develops two related models, pre-requisite to any discussion of the behavioural synthesis procedure or its subtasks. Following a comparison of two differing models of behaviour, the semantics and syntax of a suitable representation are described. Similarly, a structural notation for datapaths is also presented. A review of controller and timing issues concludes the chapter.

The solution techniques for the synthesis subtasks described in section 1.3 above are considered in chapter 3. The scheduling strategies reviewed are split into three categories: iterative, state transformational and integer linear programming (ILP). The merits and demerits of each are discussed. Allocation techniques for the solution of subtasks (iii) - (v) in the synthesis flow above are then reviewed. Graph theoretic algorithms form the core material presented in this section, which concludes with a brief discussion of expert system-based approaches to allocation.

Chapter 4 proposes a global approach to the behavioural synthesis problem and suggests a formulation of the synthesis task as a combinatorial optimisation problem. Local and global search techniques are presented, and the termination of local search algorithms in a non-optimum state is demonstrated. The simulated annealing algorithm is introduced as a global technique capable of escaping from local minima. The cooling schedule techniques associated with the simulated annealing algorithm are then reviewed. A brief survey of NP-complete algorithms used as solution techniques for the synthesis subtasks concludes this section. This is followed by a review of a simulated annealing-based high-level synthesis system developed at the University of California at Berkeley.

Chapter 5 introduces a set of software tools (the SAVAGE system) capable of

transforming a behavioural description into an optimised RTL datapath structure. Central to the method presented is a multi-dimensional data structure capable of supporting simulated annealing-based optimisation in each plane. A review of the core synthesis routines precedes the presentation of the optimisation primitives used to generate the datapath solution states. A solution quality assessment procedure is developed, and a novel system allowing the engineer to assign cost multipliers to the individual cost function components is presented. The synthesis tools are then exercised on a small-scale benchmark.

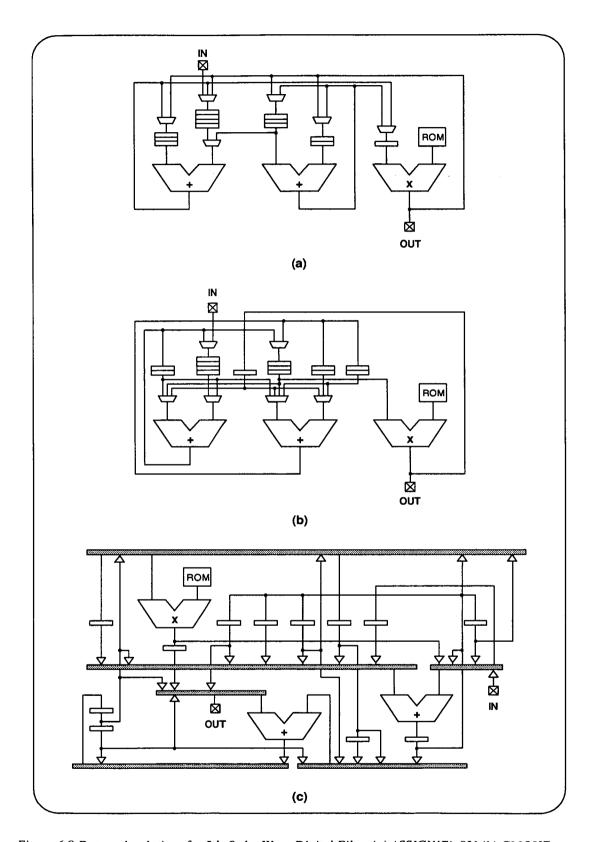

Two large-scale comparative studies are presented in chapter 6. The first, a Fast Discrete Cosine Transform kernel, permits a comparison between the synthesis method reported in this thesis and an interactive synthesis tool developed at the University of Edinburgh. The second benchmark, a Wave Digital Filter, allows comparisons to be drawn between the simulated annealing-based approach and a greater number of behavioural synthesis tools.

A general-purpose algorithm for the generation of functional pipelines, and its integration into the synthesis system reported herein, forms the core of chapter 7. Structural and functional pipelining techniques are reviewed and metrics for the assessment of pipeline performance defined prior to the introduction of the pipelining algorithm. Extensions to the SAVAGE system are described, and datapaths from the large-scale benchmarks of chapter 7 are re-synthesised to demonstrate the approach.

Finally, chapter 8 summarises the work presented in this thesis, and suggests extensions to the research.

# 2 Behavioural and Structural Models for Synthesis

This Chapter describes two related models germane to the behavioural synthesis task. In the first instance, a suitable behavioural representation must be developed. This representation must accurately capture the functionality of the source text, while its internal form should remain amenable to manipulation by the various synthesis procedures.

A notation that describes datapath structure must also be developed. To remain technology independent, the notation should not contain any physical attributes, but should at the same time contain enough meaningful information to allow the synthesis tools to optimise the datapath topology. This implies a level of abstraction between the RTL notation and the compiled gate-level description of the datapath. For example, rather than measure delay through an adder in terms of nanoseconds, the delay can be abstracted into multiples of the system clock (or *control steps*). Similarly, area

measurement does not take place in square microns, rather in notional gate equivalents. By building this level of abstraction into the structural model, it can be ensured that the output RTL descriptions are technology independent.

Following a brief discussion on two alternative representations of behaviour, the data flow semantics and syntax used throughout the work described in this thesis are presented. Closely linked to that is the development of a structural notation which supports the abstraction described above.

As a brief interlude, a naive mapping (or *binding*) between behavioural and structural domains based on a rudimentary set of axioms is considered. This binding contains no sequencing or control information. The synthesis of a suitable controller lies outside the scope of the work described in this thesis, but a simple control and timing model is developed and presented.

# 2.1 Two Alternative Behavioural Representations

Consider the addition of two integer variables, a and b. This addition can be represented by the following equation:

$$x = a + b$$

where x is the integer variable containing the result of the addition. The lexical convention observed here is known as infix notation. Here, the operands (a and b) are separated by the operator (+), thus:

The equality symbol in the equation represents the assignment operator. (The brackets noted above indicate the operator precedence).

Similarly, the addition of a and b could be represented in *prefix* notation. Here, the operator precedes both operands (in the case of non-commutative operations, the ordering of operands becomes important). Thus:

$$= x + a b$$

Both notations are valid and functionally equivalent. The difference between infix and prefix notation hints at the alternative representations of behaviour.

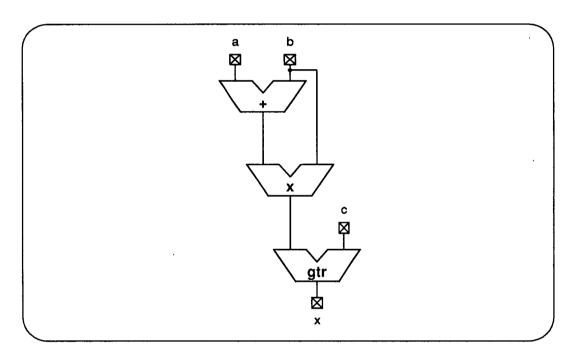

Consider the following, more complex, expression<sup>1</sup> in infix notation.

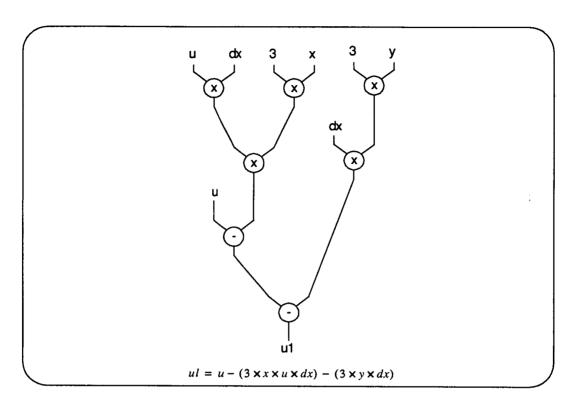

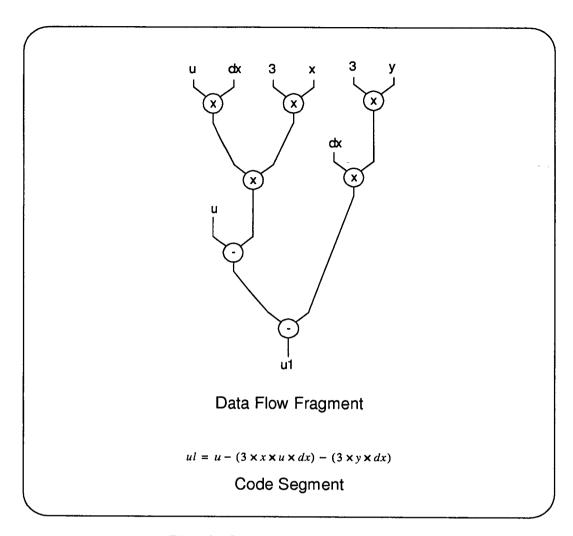

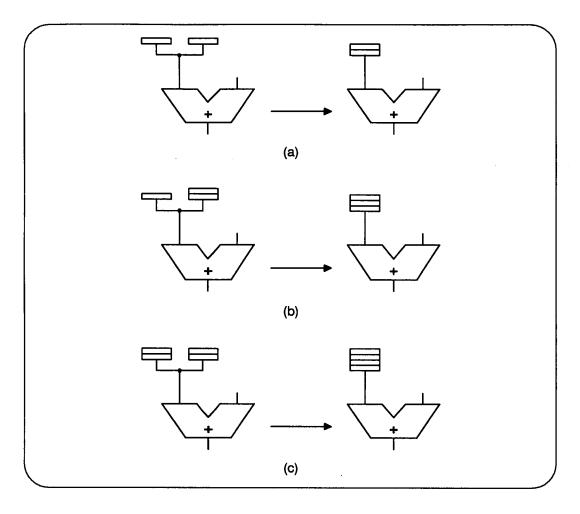

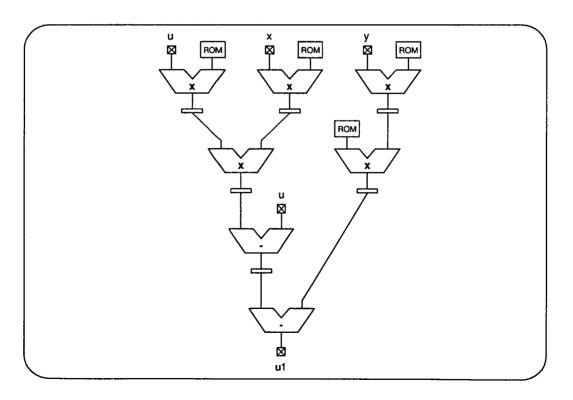

$$ul = u - 3xudx - 3ydx$$

A graphical representation can be created by parsing through the expression left to right, observing operator precedence and replacing operators with vertex tokens whose input arcs correspond to the operands associated with the operator. The graphical representation for the infix expression is shown in figure 2.1 below.

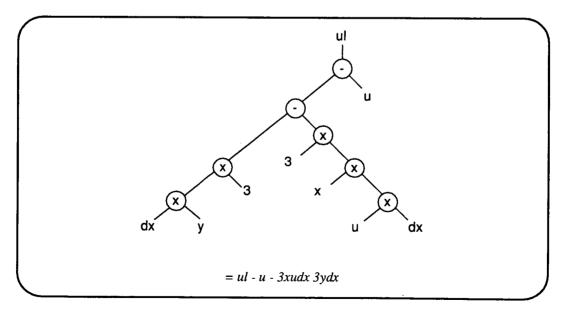

Consider the same expression in prefix notation:

$$= ul - u - 3xudx 3ydx$$

Here the graphical representation is derived by parsing left to right through the

<sup>1.</sup> This expression forms the basis of Paulin's seminal differential equation example [Paulin89b], and is used as an illustration throughout this thesis.

expression creating a tree-like structure whose vertices are the operators, with the operands represented by leaf nodes. This is shown in figure 2.2.

Figure 2.1 Infix-based graphical representation.

Figure 2.2 Prefix-based graphical representation.

In both representations, the assignment operator has been removed, as assignment is implicit.

These two representations are functionally equivalent. It is the axiom used to construct each that differentiates between the two. The first axiom is the more intuitive (as a result of infix notation predominating in mathematics teaching), while the second forms the basis of expression evaluation within many programming language compilers.

The first graphical representation is a data flow graph, with the second known as a parse tree.

#### 2.1.1 Discussion

At an intuitive level, a flow graph provides the most straightforward engineering representation. Indeed, Broderson [Broder89] argues that most electronic engineers begin the design process with a basic data flow representation. For an in-depth discussion of the flow graph, readers are directed to [Orail86]. From an automated standpoint, however, it can be argued that parse trees generated directly from the input expressions are also a suitable representation of behaviour.

For many synthesis tool designers, the choice of behavioural representation is decided by the availability of compilers for the input language. Bearing this in mind, language issues are now discussed.

#### Language Issues

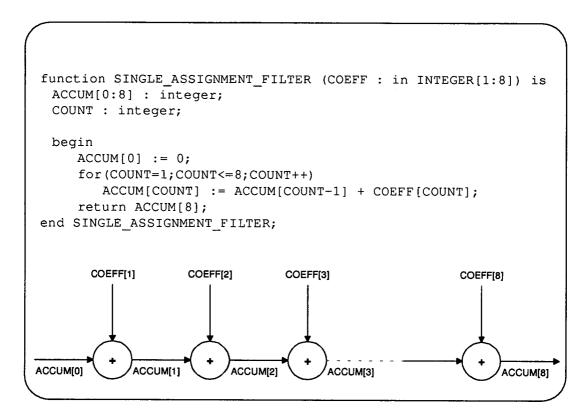

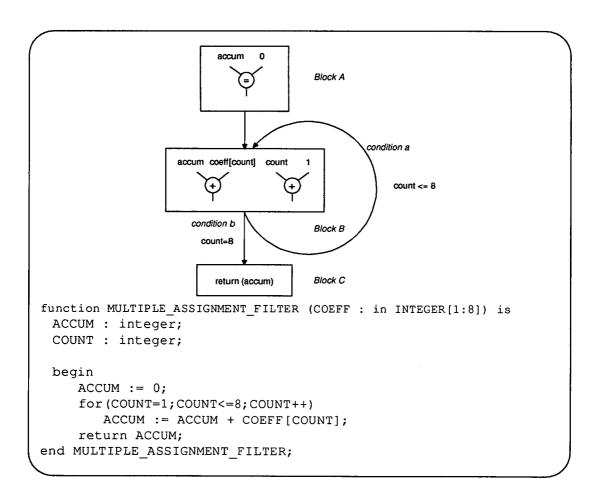

In selecting a high level language for behavioural input, a tool designer has to choose between using a standard procedural language or a specialised language which uses a more explicit data flow representation. Probably the single most important difference between the two types is the use of multiple assignment of a single variable. Consider the descriptions of the filter shown in figures 2.3 and 2.4.

Figure 2.3 Single variable assignment.

The description shown in figure 2.3 permits single assignment of variables only. That is, each intermediate result is specified explicitly in the loop body (hence the requirement for an array of result variables). This description is an accurate representation of true data flow. Probably the best known of all data flow languages, SILAGE [Hilfin84], has been tailored specifically for Digital Signal Processing (DSP) applications. Bit delays, decimation and interpolation constructs are present in the language syntax.

```

function MULTIPLE_ASSIGNMENT_FILTER (COEFF : in INTEGER[1:8]) is

ACCUM : integer;

COUNT : integer;

begin

ACCUM := 0;

for(COUNT=1;COUNT<=8;COUNT++)

ACCUM := ACCUM + COEFF[COUNT];

return ACCUM;

end MULTIPLE_ASSIGNMENT_FILTER;</pre>

COEFF[I]

ACCUM

```

Figure 2.4 Multiple variable assignment.

Against the 'naturalness' of the signal flow description, procedural languages such as PASCAL, C and ADA enjoy a well-established user base. Advances in compiler technology, specifically loop unrolling, have enabled multiple assignment, as shown in figure 2.4, to be detected and replaced with single assignment constructs, preserving the natural data flow within the intermediate representation. The use of multiple  $\nu s$ . single assignment then becomes a matter of designer preference when using a procedural language. As a caveat, however, it should be noted that this detection and replacement strategy is only valid for loop structures with finite limits.

The intuitive nature of the data flow description, together with the availability of a data flow based compiler (SLANG [Sey89]) during the course of the work described in this thesis ultimately prompted the adoption of a data flow model. The semantics and syntax of the model are now formalised.

### 2.2 Data Flow Semantics

A data flow graph is defined as a tuple, D=(V,E), where  $V=\{V_1,V_2,...,V_n\}$  is a finite set of vertices and  $E=\{E_{ij}; i,j=1,2,...,n\}$  is a set of edges connecting elements of V. E is a set of directed arcs; data cannot be consumed before it is produced. Thus, E contains both precedence constraints and connectivity information. The vertices within V can be partitioned into two main types:

**Transformational:** This vertex type performs a transformation on the input data. It is most readily associated with the arithmetic and logical operators found within the instruction set of a typical microprocessor. Further, associated with each vertex is a tuple, P = (I,O) where  $I = \{I_1,...,I_n\}$  is a set of input ports and  $O = \{O_1,...,O_n\}$  is a set of output ports. These port sets provide a mechanism whereby the commutative law can be exercised during optimisation.

**Boundary:** This class of vertex is a synchronisation mechanism allowing external data to be input to and output from the data flow graph.

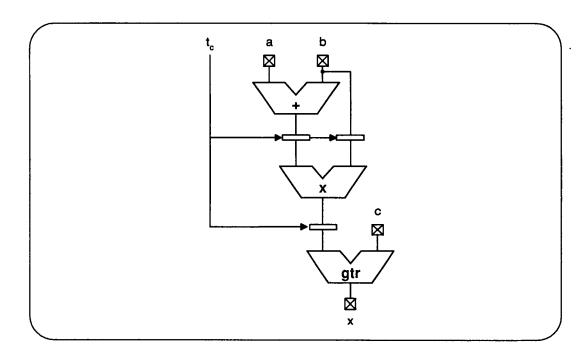

This partial definition allows the specification of straight line code segments, as shown in figure 2.5.

Figure 2.5 Straight line code representation.

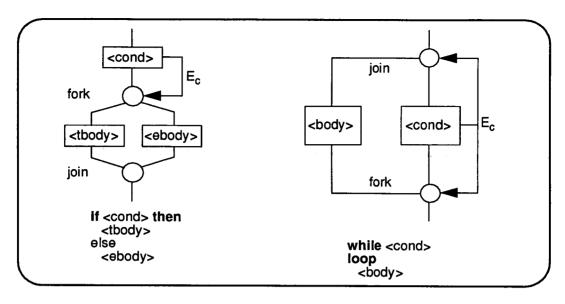

It can be seen, however, that if the high level behavioural constructs, including conditions (If <cond> then else <ebody>) and looping (while <cond> loop <body>) are to be accommodated, then further refinement of this definition is required.

Two further vertex types,  $fork_n$  and  $join_n$  are specified. They perform one-to-many and many-to-one edge mappings respectively, according to the value of a control edge,  $E_c$ . Loop and conditional statements may then be represented as shown in figure 2.6.

Figure 2.6 Representing conditional and loop structures.

The definition of these types leads to an important classification issue within data flow representation.

If the  $fork_n$  and  $join_n$  nodes are associated with the vertex set, V, and the control edges,  $E_c$ , are incorporated into the data edge set, E, then the resulting data/control flow graph is said to be *combined*. The EASY system [Stok88] models both control and data flow in a single graph. A similar representation is the 'value trace' concept [Thomas87], developed for the CMU-DA system. Value trace groups combine control and data flow nodes to form 'vtbodies'; a direct analogue of the software subroutine.

If, however, the new vertices and edges form a graph,  $C=(V,E_c)$ , then the resulting graph pair, G=(C,D) represent separate control and data flow graphs. Camposano [Campos89] uses such a representation to synthesise datapaths from behavioural VHDL descriptions.

This graph-pair notation can be extended to permit the definition of a procedural

hierarchy within the behavioural specification. If, instead of a single data flow graph, a multiplicity of data flow graphs is defined, one for each segment of straight line code, then each data flow graph is said to represent a *basic block*. These basic blocks are inserted as nodes within the control flow graph, much as the <body> instances are shown in figure 2.6. Thus, a procedure call may be represented as a multiple instance of a basic block corresponding to the procedure body within the control flow graph. This representation is used in [Lis88]. The code fragment from figure 2.4 is shown in a basic block structure illustrated in figure 2.7.

Figure 2.7 A basic block structure.

i

## 2.3 Data Flow Syntax

A textual representation<sup>2</sup> for the data flow semantics described above is now developed. A data flow graph is encapsulated as a *network*. A network contains all data flow information associated with the compiled source code. This is restricted to a single basic block in keeping with the definition above. Correspondingly, a network contains no control information.

The textual representation for a network is given below:

```

network <identifier>

-- vertex and edge definitions

end <identifier>

```

Each vertex in the data flow graph is represented as an operation:

```

operation <identifier> <type> <A> <B> <Z> end

```

The operation.type field indicates the type of transformation carried out by the data flow vertex. Typically these are: add, subtract and multiply. Further types are permissible provided that they constitute dyadic operations and that they are supported in the library of hardware functions available to the synthesis tools. The operation.A and operation.B fields correspond to the input data edges. For commutative operations, the ordering of input data on the data edges is unimportant, but for non-commutative operations, ordering is important if the operation is to remain functionally correct. For non-commutative operations, the ordering is A <op> B (e.g. A-B, A/B etc.). The operation.Z field is the output edge.

<sup>2.</sup> The syntax used here is a subset of the BABBLE language [Ryder89] used as input to the SARI Architecture Generator (SAGE) [Denyer89].

Edges within the data flow graph are represented as signals:

```

signal <identifier> <type> end

```

The signal type field is defined as one of input, output, constant or local. Input and Output types correspond to signals whose source or sink is a boundary vertex within the flow graph. The local type is used to classify signals whose source and sink vertices are internal to the current network definition. Finally, the constant type is used to represent signals having a single pre-computed value which may be replicated throughout the network definition.

As an analogy, the signal types may be best thought of as parameters passed to a software procedure, and local variables declared within that procedure.

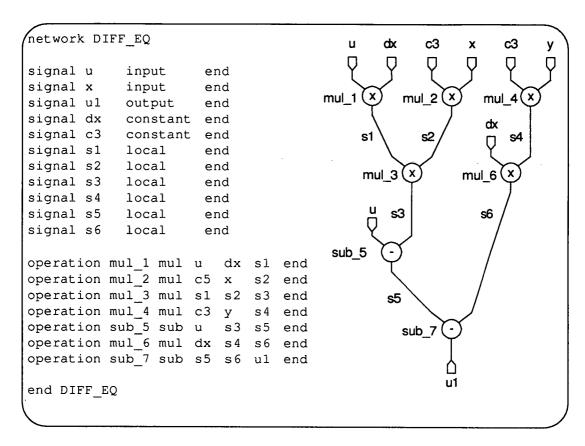

Figure 2.8 shows a portion of the network description of Paulin's differential equation example.

#### 2.4 A Structural Notation

The most basic notion of structure in the context of the work described in this thesis is that of the *datapath*. A datapath can contain four types of component, namely: processors, memories, communication structures (hereafter referred to as *nets*) and I/O ports.

The syntax specifying a single datapath is given below:

```

datapath <identifier> begin

-- processor, memory, net and I/O instances.

end datapath <identifier>;

```

Figure 2.8 Differential equation flow graph and network description.

#### 2.4.1 A Processor Model

The processors defined here are combinational units capable of performing simple arithmetic and logical operations. They are restricted to two input ports and a single output port (the Z port). In order to preserve non-commutative, the input ports are labelled A and B. The most commonly used non-commutative operation, subtraction, is restricted to A-B.

The syntax for a processor is given below:

```

processor <identifier> begin

attributes <attribute_list>;

type <operation_type_list>;

commutative <boolean>;

ports   A source <net>;

B source <net>;

```

```

Z sink <net>;

end processor <identifier>;

```

The processor attribute field contains processor specific information, such as layout area, processor latency and reuse time. The processor type field contains a list of valid operation types that may be executed on this processor. In most cases, this will be a single type, but this type specification allows for the definition of generic ALU structures. The processor.commutative field is a flag for the synthesis tools to determine whether a port swap is a valid optimisation move.

#### 2.4.2 A Memory Model

The structural description supports three types of memory, namely ROM (Read Only Memory), single registers and multiple registers grouped together in a register file. Associated with each register file there is decoding logic for register selection. The extra complexity associated with register files is accounted for in the datapath quality assessment (see Section 5.3).

The syntax for a memory component is given below:

```

memory <identifier> begin

attributes <attribute_list>;

type <ROM | register | file>;

case<sup>3</sup> type of

ROM | file => locations <integer>;

end case;

ports

case type of

register | file => A source <net>;

end case;

Z sink <net>;

case type of

```

<sup>3.</sup> In this notation, the case statement affords the opportunity to conditionally instance component fields. For example, a ROM will have no A port connection, only a Z port connection.

```

register | file => signals <signal_list>;

end case;

end memory <identifier>;

```

The memory attributes field holds memory specific information such as layout area. This is used during the synthesis procedure. The memory locations field gives an indication of the cardinality of the instanced component. This corresponds to the number of registers contained in a single file or the number of values held in a ROM. The data stored in the memory component is appended to the memory signals field.

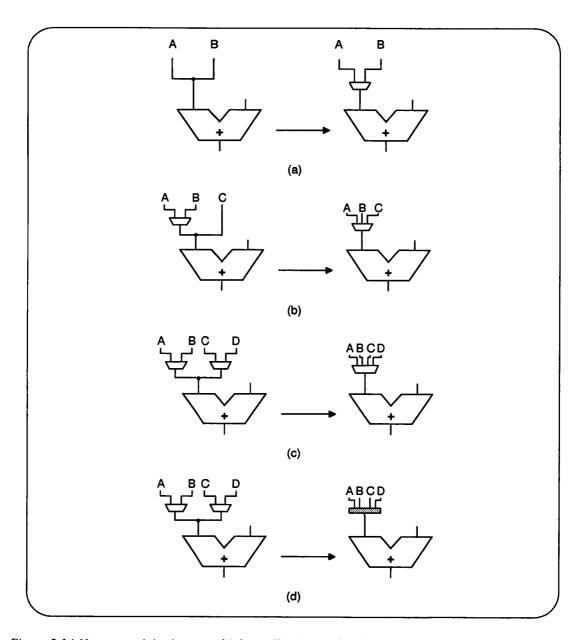

#### 2.4.3 A Communications Model

The structural model fully supports point-to-point (wire), multiplexer and bus based communications strategies. All of these components are classed as nets. Table 2.1 summarises the port connection options associated with each communications component.

| Component | Source   | Sink     |

|-----------|----------|----------|

| Wire      | Single   | Single   |

| Mux       | Multiple | Single   |

| Bus       | Multiple | Multiple |

Table 2.1 Net source and sink options.

#### The syntax for a net is given below:

```

net <identifier> begin

type <wire | mux | bus>;

case type of

mux | bus => cardinality <integer>;

end case;

source <port_list>;

sink <port_list>;

end net <identifier>;

```

#### 2.4.4 Input and Output Ports

The input and output ports provide a means of external communication with the datapath. The syntax for an I/O port is given below:

```

I/O <identifier> begin

type <in | out | bid>;

case type of

in => A sink <port_list>;

out => Z source <port_list>;

bid => A sink <port_list>;

Z source <port_list>;

end case;

end I/O <identifier>;

```

The case statement is used here to instance I/O connections relevant to the port type.

# 2.5 Interlude - A Naive Mapping

Having developed both behavioural and structural models, a naive mapping between the two domains is offered, based on the following axioms:

- (i) Operations should be mapped onto processors capable of executing the operation type.

- (ii) Where a signal traverses a c-step boundary, a memory element will be instanced to preserve the signal state between control steps.

- (iii)Each signal should be mapped to a wire or bus connecting the source and sink modules.

- (iv)Instance I/O ports of the appropriate type where the signal.type field is either input or output

- (v) Instance a ROM where the signal type field is constant.

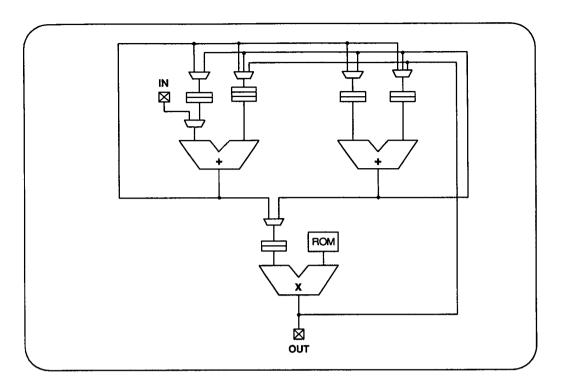

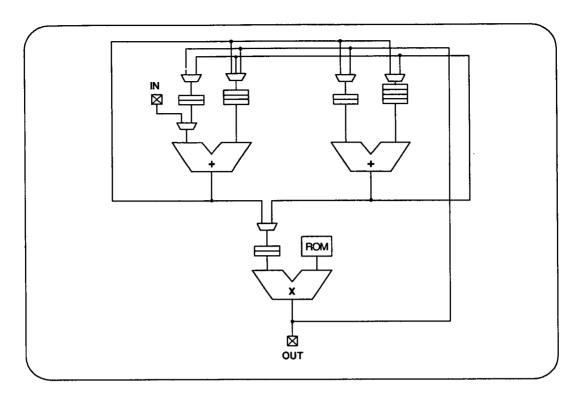

Thus, the code fragment of figure 2.1 can now be mapped to a simple datapath structure as shown in figure 2.9. (The datapath description is presented in Appendix A).

Figure 2.9 Naive differential equation datapath.

This solution offers particularly poor resource utilisation (the RTL description of this datapath produced using the structural notation is presented in Appendix A). The axioms yield a low-quality datapath with replicated hardware components. Possibly the only benefit of such a solution is that it entails zero control overhead, and produces a solution after three cycles of the system clock. The synthesis techniques in the following chapter, together with the tools presented in chapter 5, describe methods of optimising the datapath topology.

#### 2.6 A Control Model

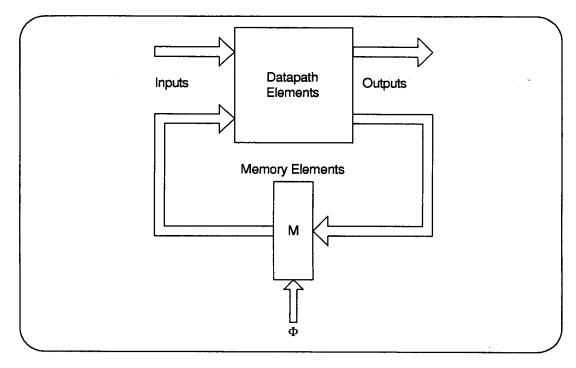

Consider the execution of a typical data flow operation. The data is retrieved from memory or the input ports of the datapath, operated on by the datapath element, then placed back in memory or made available externally via the datapath output ports.

The combination of processor and memory elements is a synchronous sequential machine corresponding to the Mealy model [Mealy54], as shown in figure 2.10.

Figure 2.10 Synchronous sequential machine (with potential race)

The composition of the memory elements holding the current state, M, is critical. In order to avoid race hazards [Seitz80] latches and edge triggered flip-flops *must* be avoided. The transparent mode of the latch prevents any state being retained, and the model shown above becomes an unpredictable asynchronous system. Edge-triggered flip-flops are also unsatisfactory because it can not be guaranteed that all elements of M will latch their input data simultaneously. Some memory elements may latch marginally early; changes on the outputs of M could then loop round through the combinatorial datapath to the input and produce an unwanted race condition.

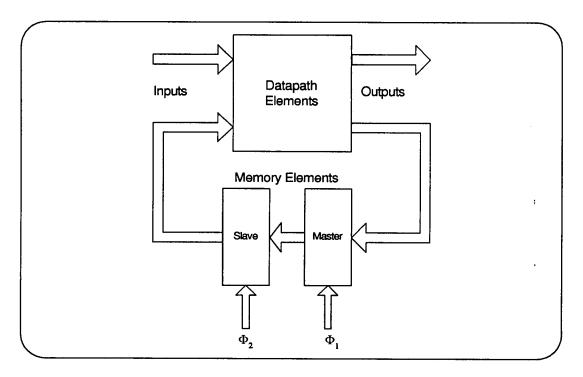

To avoid the race problem, M should be based upon a *master-slave* latch structure, as shown in figure 2.11. When the master clock is high, the outputs of the combinatorial datapath network are stored in the master latches. During this time, the slave latch

maintains consistent data at the inputs to the datapath network. When the slave clock is high, data is transferred from the master to the slave latch, and thus the input data to the datapath network is changed safely. To ensure correct operation, the master clock  $(\Phi_1)$  and the slave clock  $(\Phi_2)$  are defined so as to be non-overlapping (an overlap between  $\Phi_1$  and  $\Phi_2$  would cause both latches to go into transparent mode, again causing the critical race problem).

Figure 2.11 Synchronous sequential machine with master-slave memory structure.

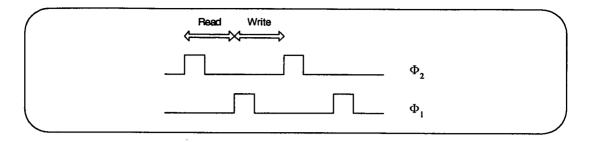

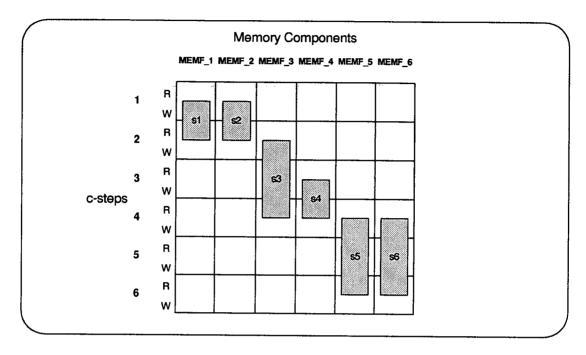

Relating this timing model to the execution of the dataflow operation, the *read* phase of a control step (i.e. the fetching of datapath input data from memory or the datapath input ports) can be specified as the time interval between  $\Phi_2$  and  $\Phi_1$ , and the *write* phase of a control step (i.e. the placing of datapath output data in memory or at the datapath output ports) as the time interval between  $\Phi_1$  and  $\Phi_2$ . This is shown in figure 2.12.

Figure 2.12 Read and Write phase timing.

## 2.7 Summary

Following a review of behavioural representation, this Chapter has developed behavioural and structural models suitable for high-level synthesis. Subsequently, a naive binding between the behavioural and structural domains based on greedy heuristics was produced. This binding yielded a particularly low quality solution. The next Chapter considers techniques designed to optimise the binding quality.

## 3 Datapath Synthesis Techniques

The previous chapter introduced behavioural and structural models capable of supporting the synthesis operations described in section 1.3. This chapter reviews the algorithmic techniques currently used to produce an optimised register-transfer description of a datapath from this intermediate representation.

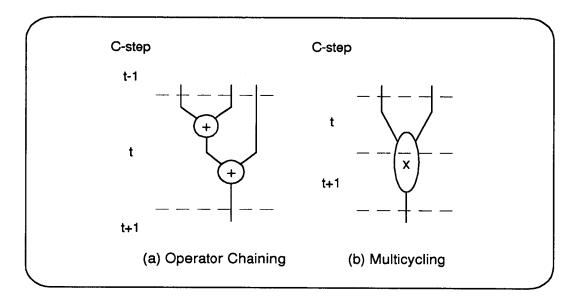

Techniques for solving the scheduling subtask are considered separately from those techniques applicable to the processor, register and interconnect allocation subtasks. The complex inter-relationship between the various synthesis subtasks, and an indication of the drawbacks of a serial synthesis flow is exemplified by considering the essential dichotomy that exists between the scheduling and processor allocation subtasks.

#### The Scheduling and Allocation Dichotomy

The scheduling subtask aims to assign execution times to all nodes in a data flow graph. Without knowledge of the number of processors available during scheduling,

however, an optimal solution is impossible to derive.

Similarly, the number of processors needed to execute all data flow graph nodes is dependent on the amount of parallelism within the graph at any particular control step. This information is generated by the scheduler. Thus, there is a cyclic relationship.

From this basic observation, it may be deduced that any synthesis flow where the scheduling and allocation operations are disjoint (regardless of the order in which the subtasks are performed) may ultimately compromise the quality of the datapath solution.

## 3.1 Scheduling Techniques

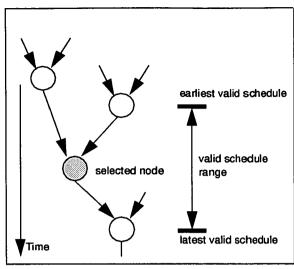

The three major classes of scheduling strategy are discussed in this section. The first, and largest class of scheduling algorithm is known as iterative scheduling. This class operates on a node-by-node basis, and is characterised by the order in which the nodes are visited. An important subclass is the distribution-based scheduler, which is examined in some detail. The second major class uses serialising and parallelising transformations on unary and fully serial schedules. Finally, a small class of synthesis systems formulate the scheduling as an integer programming problem.

## 3.1.1 Iterative Scheduling Schemes

The first class of iterative scheduling scheme constitutes the base scheduling strategies, where no hardware bound is placed on the resource set available to the scheduler. In effect, this class of scheduler operates independently of any allocation system. The most common base schedules are: AS-SOON-AS-POSSIBLE (ASAP) and AS-LATE-AS-POSSIBLE (ALAP). More unusual variations, such as AS-FAST-AS-POSSIBLE (AFAP [Campos90]) do exist, but are not in common use.

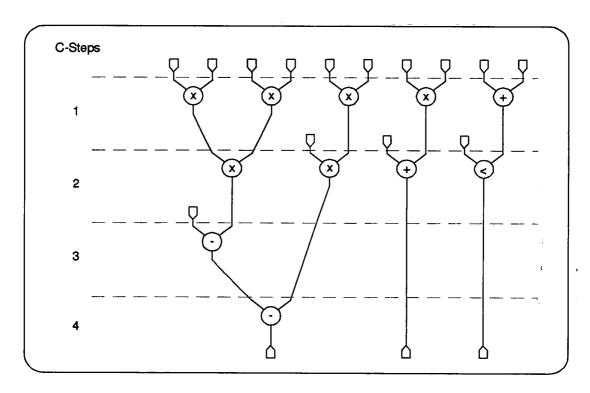

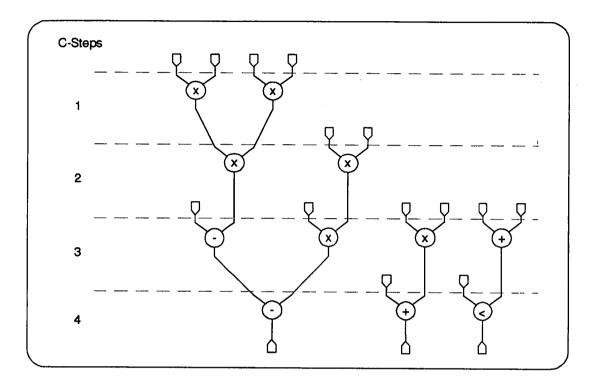

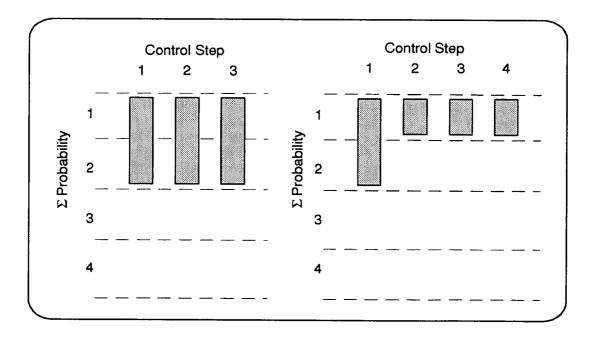

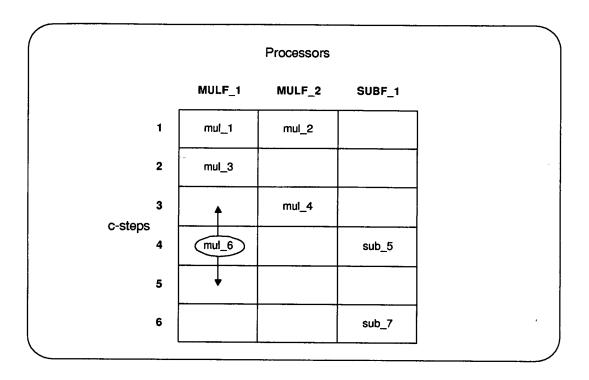

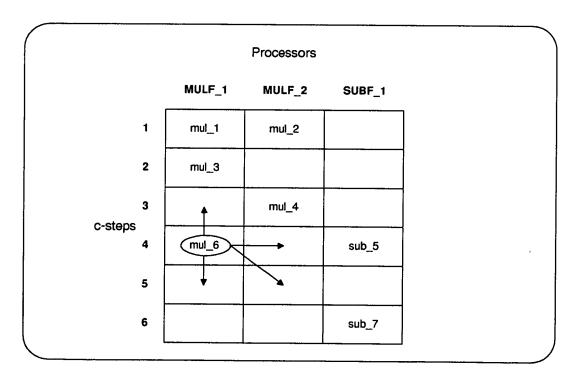

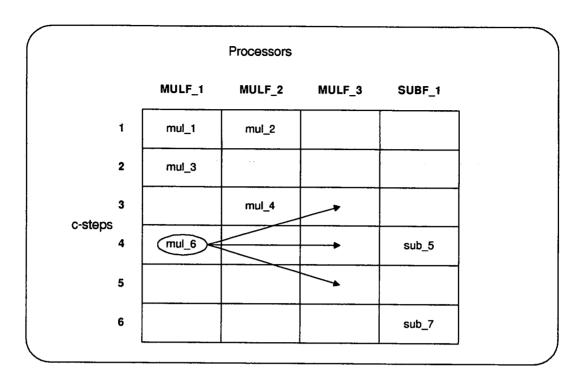

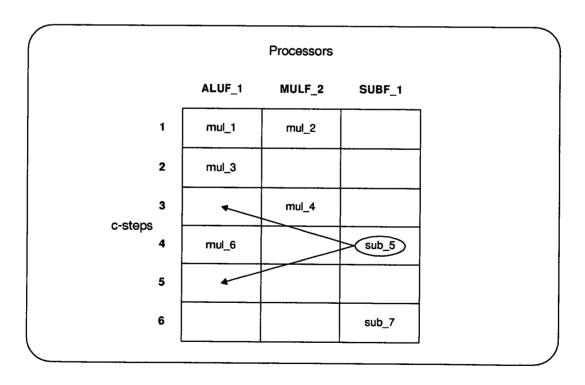

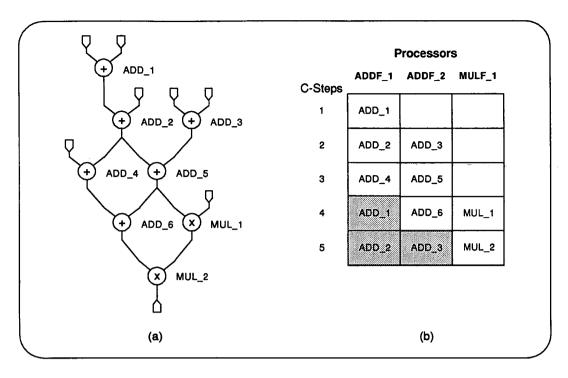

In ASAP schedulers, nodes are scheduled to occur as soon as their input data are available. Similarly, in ALAP schedules, nodes are scheduled to occur in the control step preceding the earliest consumption of their output data. The effects of ASAP and ALAP schedules are shown in figures 3.1 and 3.2.

Figure 3.1 As Soon As Possible (ASAP) Scheduling Strategy.

These strategies, while producing high speed solutions can be wasteful in terms of the excess hardware required to realise the data flow graph. As can be seen from figure 3.1, the ASAP schedule requires 4 multipliers executing concurrently, while the ALAP schedule (figure 3.2) requires only 2, at no overall execution time penalty. Consequently, these base schedules are not generally employed on their own within synthesis systems.

While the base schedules simply correspond to an ordering of the input data flow graph subject only to the data flow constraints themselves, constraining the number of available processors *a priori* necessitates the maintenance of a 'ready list'. This list

contains details of all operations capable of being scheduled at a particular control step.

Figure 3.2 As Late As Possible (ALAP) Scheduling Strategy.

The scheduler processes the data flow graph a control step at a time, removing operations from the ready list and scheduling them according to a prioritising function. This prioritising function resolves resource conflicts when the amount of operational parallelism present in the flow graph exceeds the processor parallelism. The most common form of prioritising function assigns a weight to each data flow graph node. This weight is then used as a selection criterion which determines the node or nodes to be scheduled next, or identifies suitable candidate nodes for deferment.

The simplest prioritising scheme schedules nodes on the critical path of the data flow graph to execute first. In the scheme described above, this may be viewed as a binary weighting. The ATOMICS [Goosse87] scheduler in the CATHEDRAL-II system is

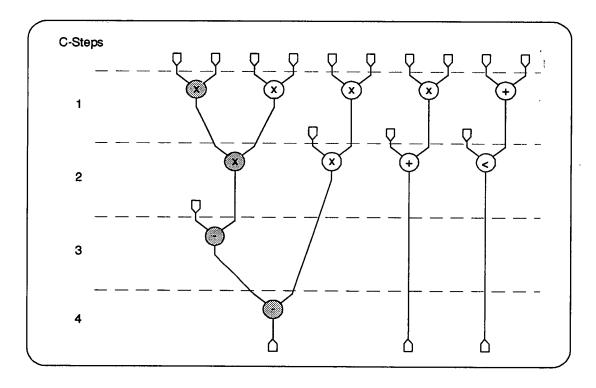

based around this strategy. Parker [Parker86] refines this by determining the *freedom* for all remaining operations once the operations present on the critical path have been scheduled. The operation freedom is defined as the difference between the ASAP and ALAP schedules for that operation, less the propagation delay of the processor executing that operation. For operations executing on the critical path, the node freedom is zero. This approach emphasises the interrelation of the scheduling and allocation subtasks. The effects of critical path and operator freedom based scheduling are illustrated in figures 3.3 and 3.4.

Figure 3.3 Critical Path Analysis (Shown in gray).

Girczyc [Girczyc85] uses node urgency as a selection criterion. Node urgency corresponds to the minimum number of control steps required to execute all operations between the current operation and the nearest timing boundary (e.g. system output, or basic block boundary.) Nodes with the greatest urgency function are given the highest priority during scheduling. This is shown in figure 3.5.

Figure 3.4 Operator Freedom Analysis

Splicer [Pangrle87, Pangrle88] uses node freedom (called node *mobility*) as a primary selection mechanism. Where resource conflicts occur, and node mobility values do not differentiate between schedulable operations, a secondary selection mechanism operates. Here, the node to be scheduled is selected based upon the length of path remaining to the nearest timing boundary. The node with the longest path is selected.

The SEHWA system [Park88] uses two urgency based schedulers. The first, which orders the data flow graph without hardware constraints establishes the *maximal* schedule. A second urgency scheduler is executed on a hardware constrained system to produce the *feasible* schedule. If the maximal schedule is better than the feasible schedule, then a third, exhaustive, scheduler is applied to produce a shorter feasible schedule. If the converse is the case, then the original feasible schedule is used.

Figure 3.5 Node Urgency Analysis

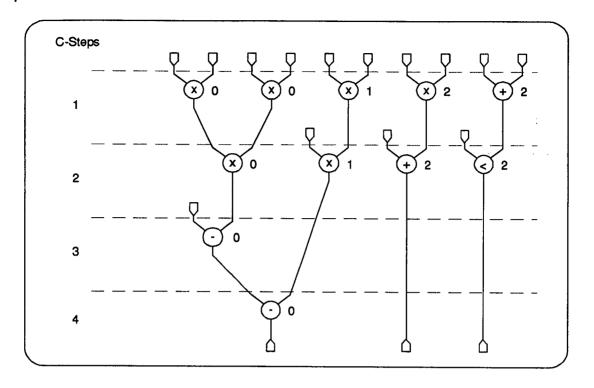

#### Balancing operator concurrency: force-directed scheduling

Paulin [Paulin89b] developed an important class of scheduler which aims to balance the operational concurrency within a data flow graph on a control-step to control-step basis. This class of scheduler is referred to as *force-directed* scheduling. The algorithm is partitioned into three main stages:

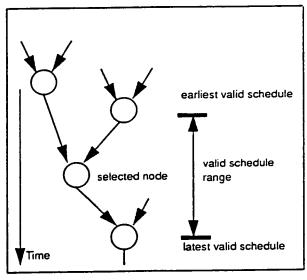

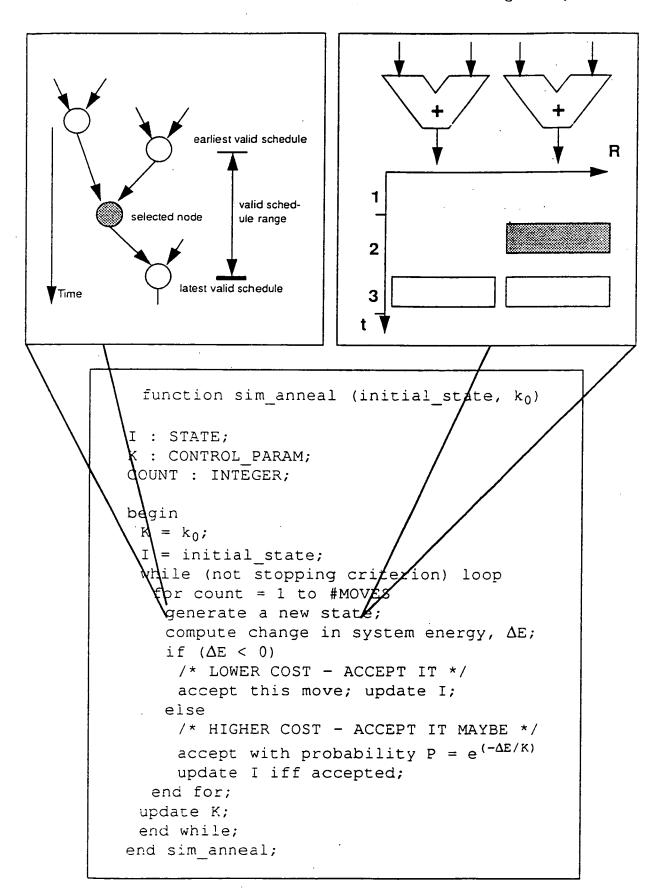

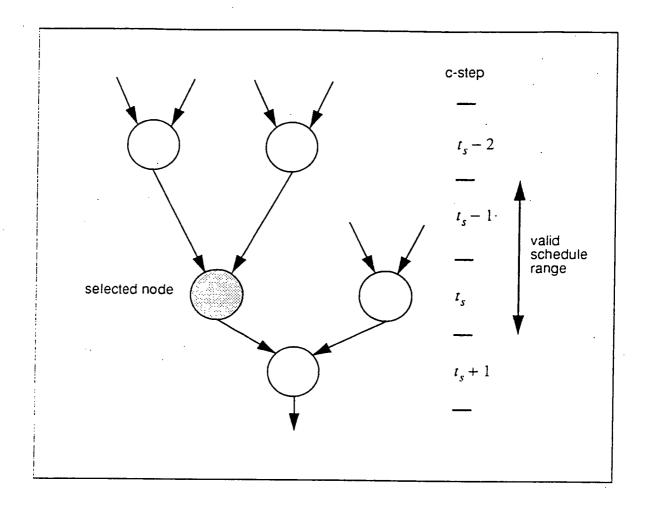

Determination of Time Frames. During this step, ASAP and ALAP schedules are generated for an individual node. This determines the feasible schedule range, and is similar in form to the notion of operator freedom, as introduced by Parker [Parker86].

Creation of Distribution Graphs. For each control step, a summation of the probabilities that individual operations of a similar class will execute in that

control step is formed. The resulting distribution graph (DG) represents an indication of the concurrency of similar classes of operation for a particular control step, and is defined:

$$DG(i) = \sum_{Op-class} P(Op,i)$$

[3.1]

where i is the current control step under consideration, and P(Op,i) is the probability of the selected operation occurring during that control step.

Calculate Forces. Here, the force associated with assigning an operation to a particular control step is determined, and is defined as the difference between the Distribution Graph value associated with the trial assignment and the average DG values over the time frame of the operations. Thus:

$$F(j) = DG(j) - \sum_{i=t_1}^{t_2} \left[ \frac{DG(i)}{(t_2 - t_1 + 1)} \right]$$

[3.2]

where F(j) is the force associated with assigning the selected operation to control step j, and the time frame of the operation runs from time  $t_1$  to time  $t_2$ .

Further, *indirect force* is defined as the force associated with the implicit assignment of control step values to nodes which have direct data dependencies on the initial trial node, *j*. Once the calculation of direct and indirect forces is completed for an operation, the control-step assignment is selected yielding the lowest total force. By definition, this balances the concurrency most effectively for a particular operation.

This force-directed scheduling technique produces datapaths capable of satisfying fixed timing constraints, but does not address the problem of scheduling under resource constraints.

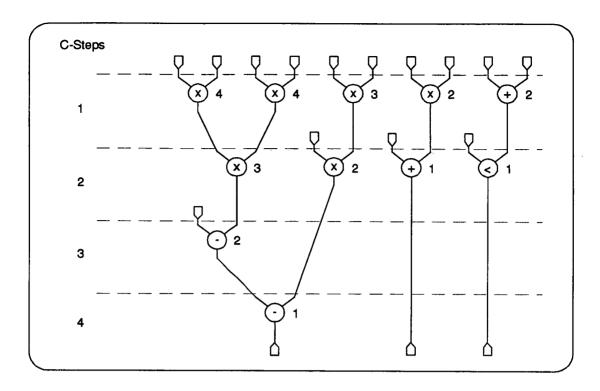

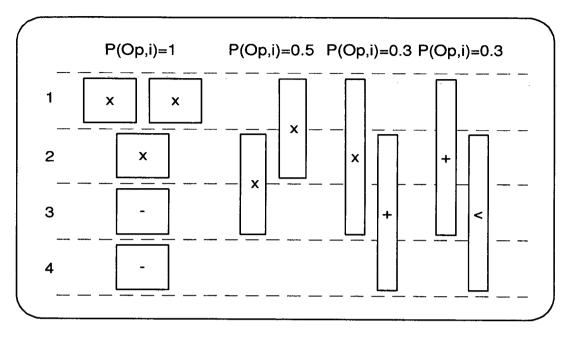

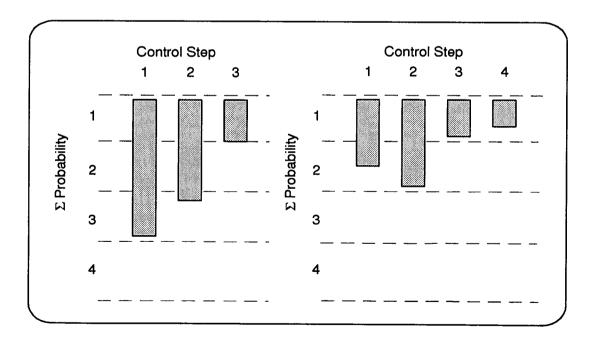

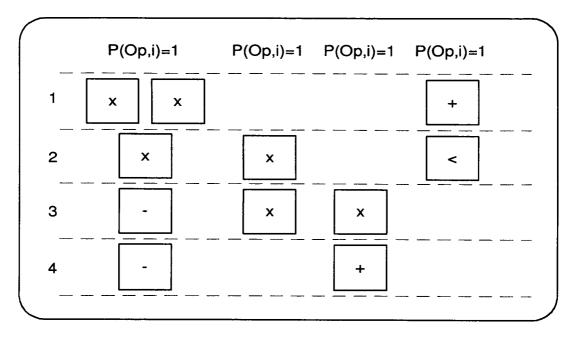

Figures 3.6-3.8 illustrate the use of the force-directed technique for the differential equation example.

Figure 3.6 Initial time frames for differential equation example (after [Paulin89b]).

Figure 3.7 Initial distribution graphs for multiply (left) and add, subtract and compare.

Figure 3.8 Final time frames for differential equation example.

Figure 3.9 Final distribution graphs for multiply (left) and add, subtract and compare.

#### **Force-Directed List Scheduling**

In common with other list scheduling approaches, the FDLS algorithm sorts the dataflow graph nodes according to data and control dependency. Those operations put onto the 'ready list' are capable of being assigned to the first control step. In the case when operational parallelism exceeds the amount of parallel hardware available during a particular control step, then one or more of the 'ready' operations must be deferred to subsequent control steps. As detailed above, operations are selected according to a prioritising function. The FDLS algorithm selects the operation from the ready list which has the lowest total force value associated with it, i.e. the operation to control step assignment producing the lowest global increase in concurrency.

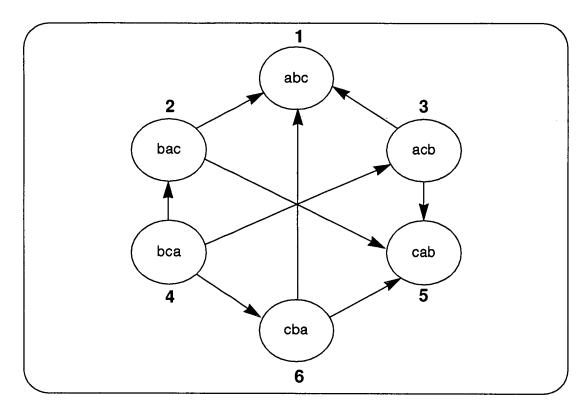

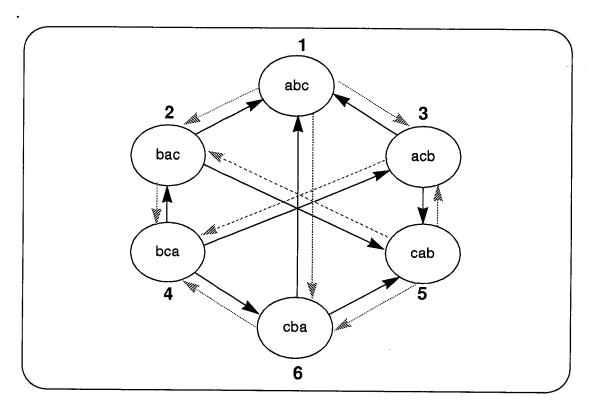

#### 3.1.2 State Transformation Scheduling

This class of scheduler operates under a resource-constrained regime. State transformations on the initial schedule are governed by two factors: data dependency and resource availability.

#### **State Merging Transformations**

In this case, a fully serial schedule is transformed by merging those operations in adjacent control steps, subject to data dependency and resource availability. Pseudo code for the algorithm is given in figure 3.10.

#### **State Splitting Transformations**

This algorithm begins with a unary schedule (i.e. a schedule where all operations occur in a single control step, thereby violating data dependency constraints). Once again, subject to data dependency and resource availability, extra control steps are added, and operations assigned to them until no further constraints are violated. This process is illustrated in figure 3.11. Both the Yorktown Silicon Compiler (YSC) [Brayton88] and the Linköping CAMAD [Peng86, Peng87] systems use this approach.

```

function STATE_MERGE (g : graph);

begin

for (all nodes in g)

assign node to differing csteps;

repeat

select (cstep);

if (merge-possible) then

merge(adjacent csteps);

until no merges possible;

end STATE_MERGE;

```

Figure 3.10 State Merging Transformations.

```

function STATE_SPLIT (g : graph);

begin

for (all nodes in g)

assign node to single cstep;

repeat

select (cstep);

if (split-possible) then

split(cstep);

until no splits needed;

end STATE_SPLIT;

```

Figure 3.11 State Splitting Transformations.

## 3.1.3 Integer Linear Program Scheduling (ILP)

Lee [Lee89] formulates the scheduling problem as an integer linear programming problem. Consider a data flow graph containing n operations. Each operator,  $O_i$ , has pre-computed ASAP and ALAP schedules,  $S_i$  and  $L_i$ , respectively. If a resource constraint is added stating that there are m types of processor of type  $t_i$ , each having a cost  $C_{ti}$ , then  $M_{ti}$  denotes the number of processors of type  $t_i$  required. The decision variables,  $x_{i,j}$  are set to 1 if  $O_i$  is scheduled in control step j, and zero otherwise.

The scheduling problem is formulated thus:

$$\min \sum_{i=1}^{m} C_{ti} M_{ti}$$

[3.3]

Equation 3.3 states that the object is the minimisation of the total processor cost. This is subject to the following constraints:

$$\sum_{i=1}^{n} x_{ij} - M_{tk} \le 0 \qquad 1 \le j \le n \qquad 1 \le k \le m$$

[3.4]

This ensures that the resulting schedule has no more than  $M_{tk}$  functional units of type t in any one control step.

$$\sum_{j=S_i} x_{ij} = 1 \qquad 1 \le i \le n$$

[3.5]

This constraint ensures that  $O_i$  is scheduled between the precomputed ASAP and ALAP schedules. Finally, for the data flow dependencies to be satisfied, equation 3.6 must be applied.

$$\sum_{j=S_{i}}^{L_{i}} jx_{ij} - \sum_{j=S_{k}}^{L_{k}} jx_{kj} \le -1$$

[3.6]

for all nodes  $O_i$  and  $O_k$  constrained by data flow dependencies.

For the differential equation example, with a multiplier cost of 5 ( $C_{tmult} = 5$ ) and an ALU cost of 1 ( $C_{tALU} = 1$ ) (values taken from Lee [Lee89]), the problem formulation and resulting schedule are shown in figures 3.12 and 3.13.

#### 3.1.4 Discussion

Most of the scheduling schemes described above operate on a flattened segment of the data flow graph, consistent with the basic block representation described in Section 2.2. For datapath dominated designs (i.e. designs where the amount of data flow

contained in individual basic blocks is significant compared to the amount of control flow), the deferral-based scheduling schemes are appropriate.

```

minimise (5 x M<sub>mult</sub> x M<sub>alu</sub>) subject to :

x_{1,1} + x_{2,1} + x_{6,1} + x_{8,1} - M_{mult} <= 0;

x_{3,2} + x_{6,2} + x_{7,2} + x_{8,2} - M_{mult} <= 0;

x_{7,3} + x_{8,3} - M_{mult} <= 0;

x_{10.1} - M_{aiu} <= 0;

x_{9,2} + x_{10,2} + x_{11,2} - M_{alu} <= 0;

x_{4,3} + x_{9,3} + x_{10,3} + x_{11,3} - M_{alu} \le 0;

x_{1,1} = 1; x_{2,1} = 1; x_{3,2} = 1;

x_{4.3} = 1; x_{5.4} = 1;

x_{6,1} + x_{6,2} = 1; x_{7,2} + x_{7,3} = 1;

X_{8,1} + X_{8,2} + X_{8,3} = 1; X_{9,2} + X_{9,3} + X_{9,4} = 1;

X_{10.1} + X_{10.2} + X_{10.3} = 1;

X_{11,2} + X_{11,3} + X_{11,4} = 1;

x_{6.1} + 2x_{6.2} - 2x_{7.2} - 3x_{7.3} < = -1;

x_{8.1} + 2x_{8.2} + 3x_{8.3} - 2x_{9.2} - 3x_{9.3} - 4x_{9.4} <= -1;

x_{10,1} + 2x_{10,2} + 3x_{10,3} - 2x_{11,2} - 3x_{11,3} - 4x_{11,4} <= -1;

```

Figure 3.12 ILP formulation of differential equation example.

Conversely, for control dominated designs, those scheduling schemes may yield suboptimal results. Potkonjak [Pot89] describes a hierarchical scheduling scheme which relates more closely to the behavioural synthesis paradigm (i.e. the ability to describe an algorithm in a high level programming language). This hierarchical method does require extensive traversal of the synthesis hierarchy and backtracking.

In terms of individual scheduling techniques, the iterative schemes are capable of producing optimised results when operating in conjunction with an appropriate allocation algorithm. Force-directed list scheduling produces marginally better quality results than the other list based scheduling approaches at a negligible increase in computational complexity.

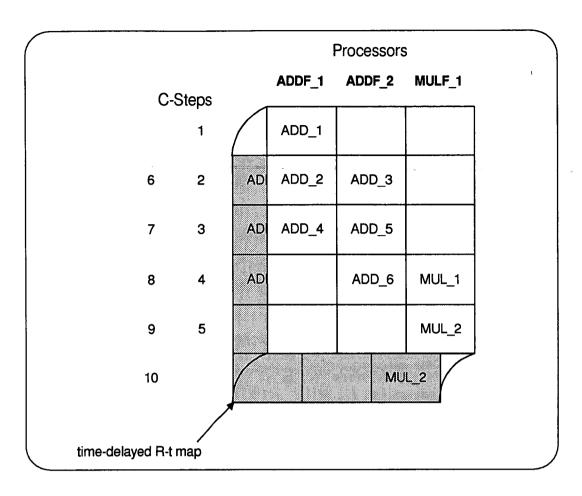

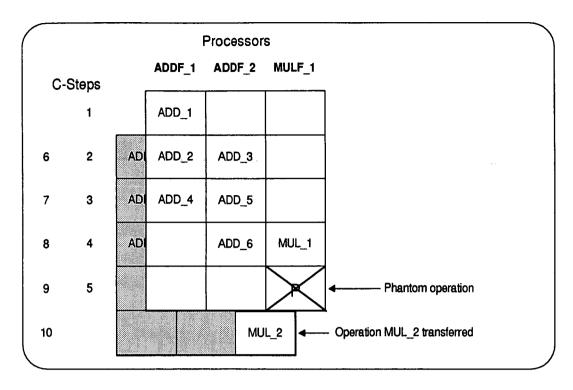

Figure 3.13 ILP Scheduling solution.

The transformational schemes benefit from the fact that both algorithms are easily implemented. In both cases, however, the order in which nodes are merged into control steps, or split into new ones is arbitrary, and in many cases, this scheme produces low quality solutions [Fin92].

ILP techniques have only successfully been applied on problem instances of no practical significance [Lee89]. The solution of the decision matrix requires large amounts of compute time, even for modestly sized problems, and the formulation of the problem may prove unwieldy. Attempts have been made to partition the overall ILP scheduling problem on a control-step by control-step basis. These are reported in Huang [Huang90a]

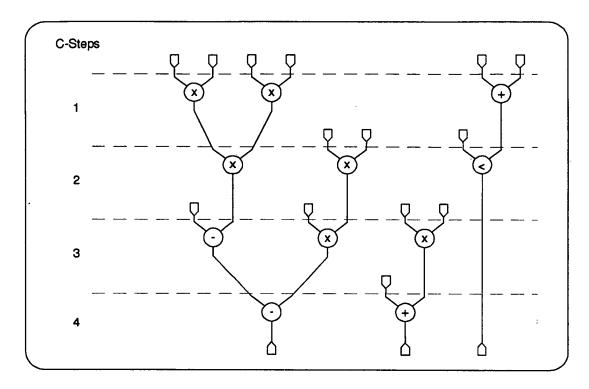

In most cases, the scheduling techniques described can be modified to include multicycling (i.e. operators requiring more than one control step to execute), operator chaining (i.e. combinatorial operators occurring within a single control step), and functional pipelining, as illustrated in figure 3.14.

Figure 3.14 Operator chaining and multicycling.

## 3.2 Allocation Techniques

Data path allocation corresponds to stages (iii) - (v) in the behavioural synthesis design flow outlined in Section 1.3. These subtasks are grouped together in this case to emphasise the inter-relationship between the subtasks, and to establish an informal taxonomy of algorithms suitable for their solution.

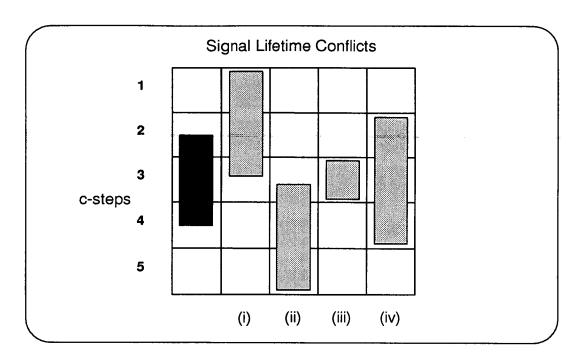

The discussion of the scheduling and allocation dichotomy revealed the relationship between the operator schedule and processor allocation. To reiterate, for effective processor allocation, the degree of parallelism within the data flow graph must be known for every control step. Compounding this problem, the need to use generic alu structures may cause allocation clashes in individual control steps.

Further, only once the schedule has been fixed can the register allocation subtask be completed. Completing the operator scheduling specifies a set of tuples,  $L_{\nu}$

comprising of the signal value and its corresponding life time. A signal life time is defined as the length of time between the production of a value, and its latest consumption time. Resource clashes can also occur on registers where data is written to a particular unit before the previous value has been read. Correspondingly, a further component of the register allocation subtask is the grouping of registers.

Again, this grouping affects the final allocation subtask: interconnect allocation. The ultimate aim is to provide a set of data transfer tuples,  $D_t$ , comprised of source and destination modules (either registers or processors) and the value transferred. From this tuple set, a suitable communications infrastructure can be synthesised.

Unlike the algorithms developed to solve the scheduling subtask, allocation algorithms are of a more diverse nature. (In the survey of scheduling algorithms, it was shown that most scheduling schemes are constructed from two elements: a base scheduling strategy, and a conditional deferment, or prioritising, function.) Broadly, however, algorithms solving the allocation subtask can be partitioned into two main types. The first is based on algorithms designed to solve graph theoretic problems, and rely on the formulation of the problem as a simple, undirected graph. The second type uses expert system and greedy iterative techniques. The former category benefits from the fact that all three subproblems, as outlined above, can be formulated in a similar way for solution, while the latter allows incremental construction of a solution datapath.

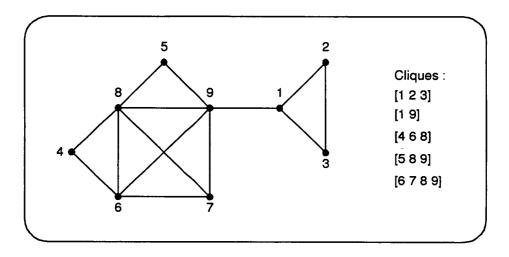

## 3.2.1 Graph Theoretic Algorithms for Allocation

These algorithms formulate the allocation procedure as an undirected graph. Johnson [Johns76] defines a clique as a "maximal, completely connected subgraph of a simple undirected graph". This is illustrated in figure 3.15. Johnson develops a family of programs capable of generating all the cliques of a graph. This family of programs is used throughout the survey of clique based algorithms.

Figure 3.15 Cliques of a graph (after [Johns76]).

#### **Clique Partitioning**

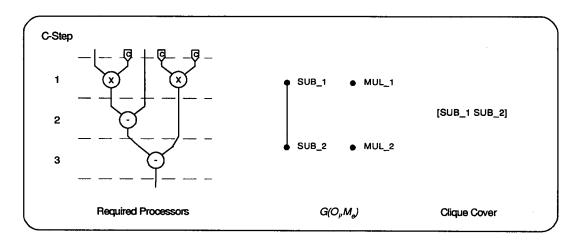

**Processor Allocation:** A graph is defined  $G(O_i, M_e)$ , where the vertex set,  $O_i$ , represents all the operations present in the schedule. The edge set,  $M_e$ , contains all those edges that represent mutually exclusive operations of the same type (i.e. operations which do not execute concurrently therefore they can share the same processor). Thus adjacent vertices can execute on the same processor. Introducing a clique coverage maximally groups operations to processors. This operation is repeated for all operation classes, and is shown in figure 3.16.

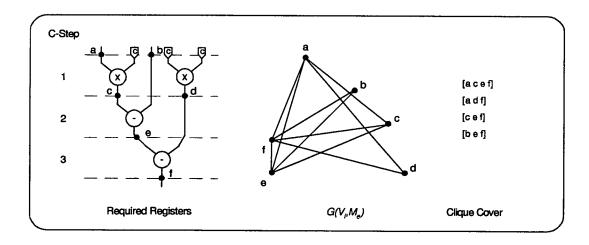

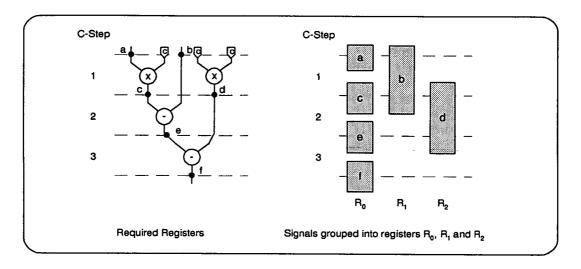

Register Allocation: A graph is defined  $G(V_i, M_e)$  where the vertex set,  $V_i$  represents all values that require storage. The edge set,  $M_e$ , contains all those edges between vertices that represent mutually exclusive values (i.e. the two values do not overlap in the schedule therefore they can be stored in the same register). Thus, adjacent vertices can be stored in the same register. By introducing a clique coverage, values can be maximally grouped into registers. This process is shown in figure 3.17.

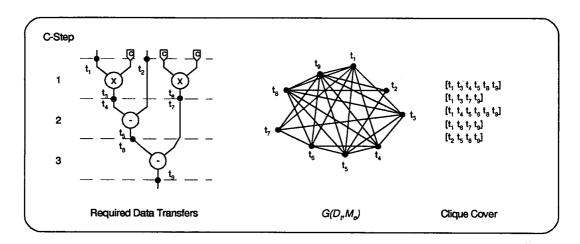

Interconnect Allocation: A graph is defined  $G(D_t, M_e)$ , where the vertex set,  $D_t$ , represents all data transfers present throughout the schedule. The edge set,  $M_e$ ,

contains all those edges that represent mutually exclusive transfers (i.e. the transfers take place at different times in the schedule therefore the transfers can use the same interconnect).

Figure 3.16 Processor allocation by clique coverage.

Thus adjacent vertices can use the same interconnect. Introducing a clique coverage maximally groups data transfers to interconnect. This process is shown in figure 3.18.

Figure 3.17 Register allocation by clique coverage.

#### **Selecting Appropriate Clique Coverage**

In many cases, there is no definitive clique cover. Rather, a group of cliques is produced. Introducing a heuristic selection technique [Tseng86] can eliminate non-

optimal cliques. In the case of the register allocation, Tseng uses a heuristic which selects the maximal clique, thus maximising the register utilisation.

Figure 3.18 Interconnect allocation by clique coverage

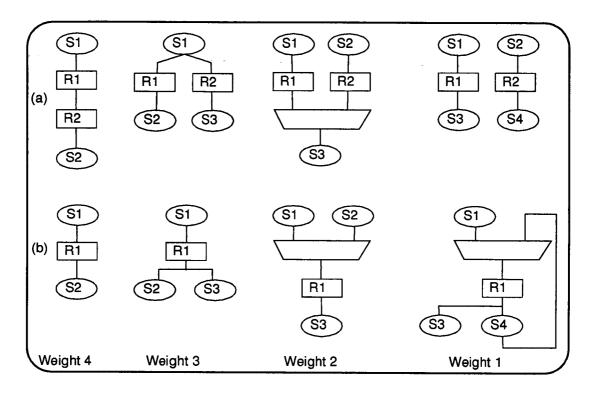

A more common approach is to use weighted clique coverage. Tseng advocates this approach during processor allocation an interconnect allocation in the FACET toolset. In both instances, a hierarchical weighting scheme is adopted. For processor allocation, a four level weight is introduced according to the degree of similarity in the source and destination units for each vertex (a high weighting is assigned to inputs and outputs with the same source and destination; correspondingly, a low weighting is given to dissimilar sources and destinations). This scheme is also used in the interconnect allocation for data transfer source and destinations. The HAL system [Paulin89c] uses weighted clique partitioning to perform register allocation. Paulin computes the weighting values as a function of the saved interconnect area after register merging. This is shown in figure 3.19.

A general clique coverage technique has been examined which can be applied to all datapath allocation stages. It is important to note, however, that in Tseng's original treatise, the order in which the various allocation subtasks are completed is specified: register allocation, processor allocation, and finally interconnect allocation. This

ordering allows the heuristic weighting scheme to operate as the weights are derived directly from the register allocation.

Figure 3.19 Register merging, before (a), and after (b). (after [Paulin89c])

## 3.2.2 The Left Edge Algorithm.

Kurdahi and Parker [Kurdahi87] have shown that the register allocation problem can be modelled as channel routing. In this representation, the goal is to assign values (wires) to registers (tracks) using the minimum number of registers. This is a well understood problem, and is documented in Hasimoto [Hasimoto71]. The left edge algorithm will always produce the minimum number of registers required, but does *not* guarantee optimal value grouping within those registers. Its operation is shown in figure 3.20.

Figure 3.20 Left-Edge register allocation.

Values are allocated to register on a "first available basis" as shown. The lifetime analysis which this graph provides has been incorporated in a further graph theoretic algorithm for register allocation.

#### 3.2.3 Bipartite Matching

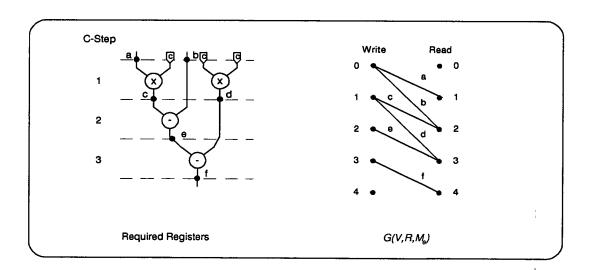

A graph is defined  $G(V,R,M_e)$  whose vertex sets V and R represent the values to be stored and the available registers, respectively. R is determined via a lifetime analysis derived from the left edge algorithm outlined above. Edges are added between values and register if and only if there are no lifetime conflicts on that register, as shown in figure 3.21. In effect, this matching enumerates all value-register combinations as opposed to the first available matching given by the left edge algorithm.

Once again, however, heuristics must be employed to select the most appropriate allocation. In Huang [Huang90b], the heuristics estimate the number of similar interconnects for source and destination pairs.

Figure 3.21 Bipartite register allocation.

#### 3.2.4 Edge Colouring

Stok [Stok90a, Stok91] defines a data path allocation scheme which deals explicitly with the register grouping problem.

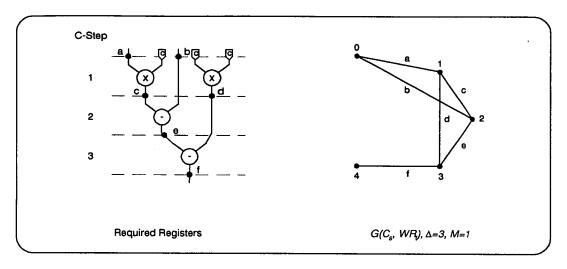

A graph is defined  $S(C_s,WR_t)$ , where the vertex set,  $C_s$ , represents all control steps present in the schedule. The edge set,  $WR_t$ , contains edges which represent the read and write times for storage values. Vizing's theorem [Vizing64] for general graph colouring problems states that for a graph of degree  $\Delta$  (maximum number of edges incident to a node) and multiplicity M, (maximum number of edges joining any two vertices), then:

$$\Delta \le \Psi_e(G) \le \Delta + M \tag{3.7}$$

where  $\Psi_e(G)$  is the number of colours required to colour the graph edges<sup>2</sup>. Therefore, in the register grouping problem, equation 3.7 states that the variables may be grouped into, at most,  $\Delta+1$  register files. This is shown in figure 3.22.

<sup>1.</sup> The graph colouring problem is concerned with finding a partition of the set of vertices into a minimum number of independant sets. Such a partition is called a *colouring*.

<sup>2.</sup> In this application of Vizing's theorem, there is no meaningful interpretation where M > 1.

Figure 3.22 The edge-colouring algorithm for register grouping.

Introducing a two phase clocking scheme produces a bipartite graph, Vizing's theorem can be reduced to:

$$\Psi_e(G) = \Delta \tag{3.8}$$

This is shown in figure 3.23.

Figure 3.23 Bipartite edge colouring.

## 3.2.5 Expert System/Greedy Allocation Schemes

The expert system approach to the allocation problem applies rules generated by an

expert designer on an initial allocation of processors, register and interconnect. After applying a decision criterion, the inference engine of the expert system will apply further predicates aimed at minimising the overall objective function.

JACK-THE-MAPPER [Goosse88] is a three level expert system embedded within the CATHEDRAL II system. The outer level is a standard expert system shell interface, with the intermediate level containing predefined predicates capable of performing specific algorithmic tasks, such as bus merging. The rule base itself contains over 100 transformation rules. These transformations allow the modelling of multiplication as shift and add operations, and the generation of counters for loop structures, for example.

As with all expert system approaches, significant user interaction is required, with the design engineer producing the processor allocation manually. Registers and interconnect are allocated initially, one per value and data transfer, respectively. JACK-THE-MAPPER then performs the optimisation transformations. The designer can influence these translation steps by writing architectural pragmas in the input SILAGE description. The allocation is completed during the scheduling phase with the Atomics tool.

Greedy allocation algorithms select operations from the data flow graph. Processors, register and interconnect are all allocated when needed. In most cases, the algorithm aims to locally optimise the cost of introducing operations into the existing datapath.

The node selection order and the local costing criteria characterise greedy allocation schemes. Nodes may be selected at random, via some prioritising function (e.g. critical path analysis), or in the order determined by the schedule. The MABAL system [Kucukc89] selects operations using the latter technique. A more global analysis may

be adopted, with all data flow nodes considered, regardless of scheduled order. This approach is typified by EMUCS [Thomas88], part of the System Architect's Workbench. The EMUCS cost function selects the functional unit with the lowest binding cost (i.e. the cost of adding operations) per operation. Similarly, the MABAL system determines local cost via an analysis of the partial architecture already generated. The MABAL system improves the accuracy of the cost function by formulating the register and functional unit allocations problems together.

#### 3.2.6 Other Techniques

Branch and bound allocation schemes have been developed and implemented [Pangrle88, Marwed86]. They search through datapath components already instanced to provide an allocation solution. The search depth of branch and bound is generally controlled by passing the scheduled data flow graph on a control step by control step basis.

ILP techniques have been applied to the various allocation subtasks [Hafer83], but are restricted to impractical problem instances.

#### 3.2.7 Discussion

The graph theoretic algorithms presented provide the most elegant solution to the allocation subtasks. Based on well established theory, a number of efficient algorithms have been developed for their solution. In the case of clique coverage and bipartite matching, however, the introduction of heuristics will degrade the performance of the algorithms in a restricted subset of applications.

Viewing the allocation task as a series of separated problems produces solution schemes where one component of the allocation task dominates. Indeed, interconnect

and memory based optimisation approaches have been developed [Stok91, Park89, Grant 90a]. The EASY system [Stok88] uses correlated clique coverage to try and account for the effects of the other allocation phases.

The rule based and greedy allocation approaches allow incremental datapath construction. Expert system based allocation is slow, and requires a large rule base. Without efficient backtracking, this approach is more likely to produce solutions based on local minima. The experience of JACK-THE-MAPPER, and Kowalski's DAA [Kowal85] indicate that for a restricted application area, this approach is applicable. Greedy allocation is strongly dependent on the order in which the optimisation takes place, and yields poor quality results.

Finally, the branch and bound and ILP formulations have proved too computationally expensive to implement for practical problem instances.

# 4 Combinatorial Optimisation and Simulated Annealing