# CMOS VLSI CIRCUITS FOR IMAGING

Wang Guoyu

A thesis submitted to the Faculty of Science, University of Edinburgh for the degree of Doctor of Philosophy August 1993

#### **Declaration**

Unless otherwise stated, the material contained herein was researched and composed entirely by myself in the Department of Electrical Engineering, University of Edinburgh between December 1987 and May 1993.

Wang Guoyu (G. Wang)

# Acknowledgements

I am grateful to my supervisors, Dr. D. Renshaw and Professor P. B. Denyer, for their unsparing support and constant encouragement during the course of this work.

A special word of thanks must go to M. Lu for her invaluable cooperation in the development of the project.

I also wish to thank my parents for their understanding of my staying abroad.

I conclude with acknowledgement to SERC, the Chinese Educational Commission, the University of Edinburgh, and VLSI Vision Ltd., for their funding and financial support.

#### **Abstract**

MOS technology is very attractive for achieving low-cost miniature cameras. It also permits the inclusion of the sensor with other control and processing functions on the same chip. However, this technique has never been developed to the point at which MOS sensor performance matches that of CCD cameras.

The objective of this project has been to develop design techniques to achieve single chip video cameras, in unmodified CMOS processes, with improved performance (aimed to match the performance of CCD cameras) and enhanced functionality.

In this thesis, following an overview of solid state image sensors, the fundamentals and basic sensor array structure suitable for CMOS implementation is presented. The pixel structure and sensor array, the sense amplifier, scan circuitry, and the output amplifier and buffer are described. Noise analysis is also presented with the main noise sources highlighted and compensation schemes proposed. Other useful on-chip techniques including auto-exposure control, gain control, and data conversion are then discussed. A successfully designed device, named ASIS-1011 which incorporates all these circuit techniques, is finally reported. This design shows that the aim of achieving good picture quality and incorporating sensors and control logic on one chip can be achieved.

# **Table of Contents**

|           | Declaration |                                                         |        |  |

|-----------|-------------|---------------------------------------------------------|--------|--|

|           |             |                                                         |        |  |

|           | Abstract    |                                                         |        |  |

|           | Table       | e of contents                                           | ii     |  |

| Chapter 1 | Intro       | duction                                                 |        |  |

|           | 1.1         | Project background                                      | 1      |  |

|           | 1.2         | Project review                                          | 5      |  |

|           | 1.3         | Thesis structure                                        | 7      |  |

| Chapter 2 | Solid       | 1 State Image Sensors: An Overview                      | 9      |  |

|           | 2.1         | Introduction                                            | 9      |  |

|           | 2.2         | CCD image sensors                                       | 11     |  |

|           | 2.3         | CID image sensors                                       | 16     |  |

|           | 2.4         | MOS image sensors                                       | 21     |  |

|           | 2.5         | Comparison of CCD, CID, and MOS image sensors           | 29     |  |

|           | 2.6         | New photo-element structures                            | 31     |  |

|           | 2.7         | Chapter summary                                         | 36     |  |

| Chapter 3 | Basic       | Architecture                                            | 37     |  |

|           | 3.1         | Sensor array                                            | 38     |  |

|           |             | 3.1.1 Charge storage operation of the photodiode        | 38     |  |

|           |             | 3.1.2 Pixel structure and operation                     | 39     |  |

|           | 3.2         | Sense amplifiers                                        | 41     |  |

|           |             | 3.2.1 Structure and transfer function of sense amplific | ers 41 |  |

|           |       | 3.2.2           | High gain amplifier43                                |

|-----------|-------|-----------------|------------------------------------------------------|

|           |       | 3.2.3           | Performance                                          |

|           | 3.3   | Output          | amplifier and buffer                                 |

|           |       | 3.3.1           | Output amplifier46                                   |

|           |       | 3.3.2           | Output buffer                                        |

|           | 3.4   | Scannin         | g circuitry50                                        |

|           |       | 3.4.1           | Horizontal register                                  |

|           |       | 3.4.2           | Vertical shift register                              |

|           | 3.5   | Control 1       | logic53                                              |

|           | 3.6   | Chapter         | summary54                                            |

|           |       |                 |                                                      |

| Chapter 4 | Noise | Analysis,       | Noise Elimination and Compensation 55                |

|           | 4.2   | Rando           | m noise55                                            |

|           |       | 4.2.1 I         | First sensing stage56                                |

|           |       | 4.2.2 \$        | Second sensing stage59                               |

|           |       | 4.2.3           | Dominant random noise61                              |

|           | 4.3   | Fixed           | Pattern Noise                                        |

|           |       | 4.3.1 I         | Parameter mismatch                                   |

|           |       | <b>4.3.2.</b> 1 | Digital pattern interference65                       |

|           |       | 4.3.3 N         | Main sources of FPN66                                |

|           | 4.4   | Reduci          | ng fixed pattern noise                               |

|           |       | 4.4.1 H         | Eliminating speckles caused by access transistors 67 |

|           |       | 4.4.2           | Compensating vertical stripes67                      |

|           |       | 4.4.3 \$        | Sense amplifier calibration70                        |

|           |       | 4.4.4 F         | Reducing interference between digital and analogue   |

|           |       |                 | circuitry73                                          |

|           | 4.5   | Reduci          | ng random noise                                      |

|           | 4.6   | Chapte          | r summary                                            |

|           |       |                 |                                                      |

| Chapter 5 |       |                 | Improve Dynamic Range: Auto-exposure & Auto-gain     |

|           | 5.1   |                 | ction                                                |

|           | 5.2   |                 | nic aperture                                         |

|           |       | 5.2.1 Algorithm                                       | 77      |

|-----------|-------|-------------------------------------------------------|---------|

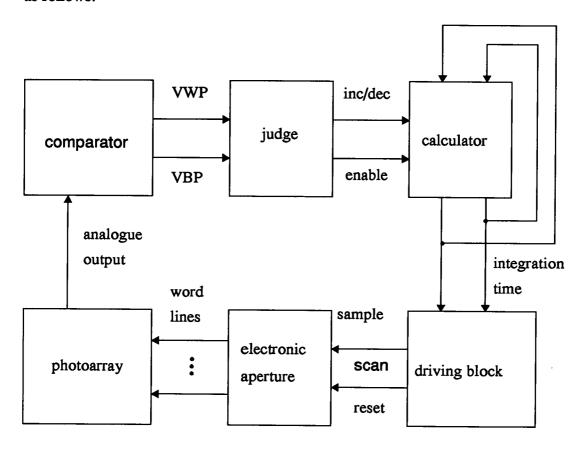

|           |       | 5.2.2 Circuitry                                       | 79      |

|           | 5.3   | Electronic exposure controller                        | 79      |

|           |       | 5.3.1 Algorithm                                       | 80      |

|           |       | 5.3.2 Circuitry                                       | 81      |

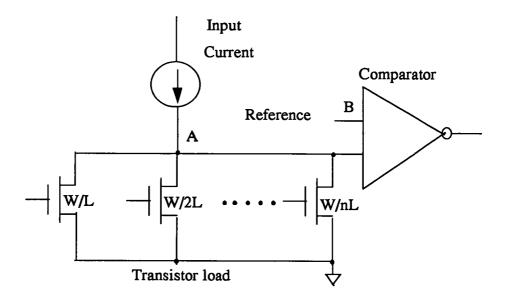

|           | 5.4   | Gain setting circuitry                                | 82      |

|           |       | 5.4.1 MDAC circuit                                    | 82      |

|           |       | 5.4.2 Gain setting                                    | 83      |

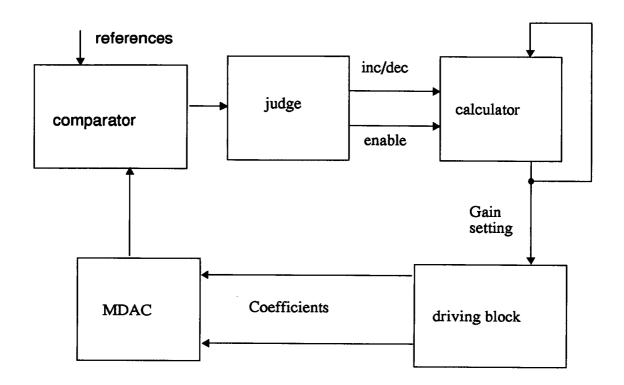

|           | 5.5   | Auto-gain control                                     | 84      |

|           |       | 5.5.1 Algorithm                                       | 84      |

|           |       | 5.5.2 Circuitry                                       | 85      |

|           | 5.6   | Chapter summary                                       | 86      |

|           |       |                                                       |         |

| Chapter 6 | Othe  | er Techniques                                         | 87      |

|           | 6.1   | Data conversion                                       | 87      |

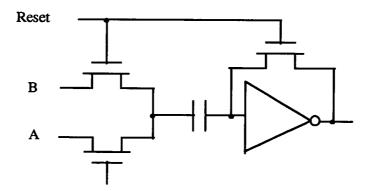

|           |       | 6.1.1 Approximation sequence                          | 87      |

|           |       | 6.1.2 AEC and AGC with the conversion                 | 88      |

|           |       | 6.1.3 Comparator                                      | 88      |

|           | 6.2   | Black level calibration                               | 89      |

|           | 6.3   | γ correction                                          | 91      |

|           | 6.4   | Simple solution for test                              | 94      |

|           |       | 6.4.1 Principle                                       | 94      |

|           |       | 6.4.2 Word-line Test                                  | 96      |

|           |       | 6.4.3 Bit-line (Associated Sensing & Read-out Circuit | s) Test |

|           |       |                                                       | 98      |

|           |       | 6.4.4 Pixel Test                                      | 98      |

|           | 6.5   | Chapter summary                                       | 99      |

|           |       |                                                       |         |

| Chapter 7 | Imple | ementation: A Single-chip Video Camera                | 100     |

|           | 7.1   | Introduction                                          |         |

|           | 7.2   | Main features                                         |         |

|           |       | 7.2.1 Fixed pattern noise                             | 102     |

|           |       |                                                       |         |

|         |        | 7.2.2 Automatic Exposure Control (AEC)   | 103 |

|---------|--------|------------------------------------------|-----|

|         |        | 7.2.3 Automatic Gain Control             | 103 |

|         |        | 7.2.4 Automatic Black-level Calibration  | 104 |

|         | 7.3    | Analogue circuit and layout              | 104 |

|         | 7.4    | Characterization                         | 110 |

|         | 7.5    | Remaining problems                       | 112 |

|         | 7.6    | Chapter summary                          | 112 |

| Chapte8 | Future | Research Opportunities and Conclusions   | 113 |

|         | 8.1    | Future research opportunities            | 113 |

|         |        | 8.1.1 Further reduce fixed pattern noise | 113 |

|         |        | 8.1.2 High gain                          | 114 |

|         |        | 8.1.3 Better y correction                | 114 |

|         |        | 8.1.4 Single bright vertical bar         | 115 |

|         | 8.2    | Conclusions                              | 116 |

|         | Refe   | erences                                  | 119 |

|         | Appe   | endix 1 HSPICE simulation input files    | 125 |

|         | Ap     | pendix 2 ASIS-1011 pads list             | 128 |

|         | App    | endix 3 Publications                     | 131 |

# Chapter 1 INTRODUCTION

## 1.1 Project Background

The research and development of solid state silicon image sensors has attracted and maintained considerable interest.

The driving forces behind this are the increased video camera market and widespread potential for electronic vision applications. Examples include:

- consumer camcoders and still cameras.

- television broadcast cameras,

- telecommunications (video telephones),

- security cameras,

- image capture for personal computers.

- bar-code and text readers.

- biometric verification (fingerprint, faces, etc.),

- production line inspection,

- military use (target tracking, etc.),

- traffic control,

- robot visions, and automotive applications,

- smart toys, etc.

All these applications are sensitive to cost, size, and power consumption. Commonly they use commodity camera modules and image processing hardware and/or software. These systems can hardly be described as miniature, and usually, their cost, size, and power consumption are limitations for wider applications. The camera module itself is one of the dominant limiting factors.

It is well known that silicon can act as an excellent photoreceptor over the visible

spectrum. One of the most significant developments leading to the realization of a practical solid-state image sensor was the utilization of the p-n junction photodiode operating in an integration mode. Charge-storage operation is based on the principle that, if a p-n junction is reverse-biased and then isolated, the charge stored on the depletion layer capacitance decays at a rate proportional to the incident illumination level [Sze, 1981; Middelhoek, 1989; Haskard, 1988].

Compared with vacuum video tubes solid-state image sensors have obvious advantages. They are small, lightweight, of low power consumption, require little maintenance, and have a long life. Solid-state image sensors come in several technologies, including CCD (Charge Couple Device), MOS (Metal Oxide Semiconductor), and CID (Charge Injection Device). All these sensors use the p-n junction as the photoreceptor. The difference among them is in the readout techniques utilized [Wechder, 1965; Tseng, 1965; Chamberlain, 1986]. The majority of solid-state cameras today use CCD technology which, over two decades, has been highly refined to optimize its performance. However, cameras and vision systems addressed by today's CCD technology are still power-hungry and expensive, and fall short of the highest level of integration.

On the other hand, MOS technology, as a popular VLSI technology, is very attractive for achieving low-cost miniature cameras. Another important factor is that MOS technology, especially CMOS, permits the inclusion of the sensor with other control and processing functions on the same chip, to achieve smart vision application systems. Despite encouraging results, however, this technique has never been developed to the point at which MOS sensor performance matches that of CCD cameras.

Noise remains a fundamental problem which limits the development of MOS sensors and MOS vision systems. In fact, it is a limitation which hampers the huge potential application and market of MOS image sensors. The main emphasis has been on reducing the noise and improving the picture quality. The research work of our project is a contribution to this.

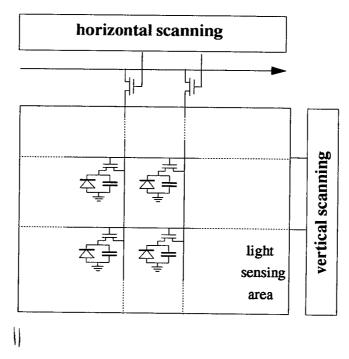

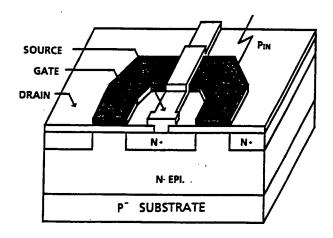

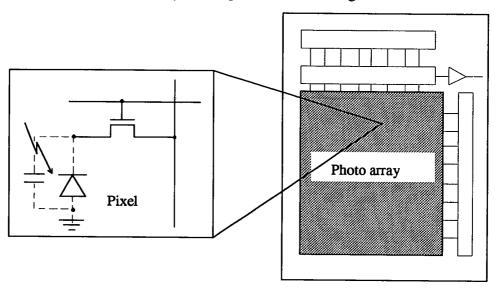

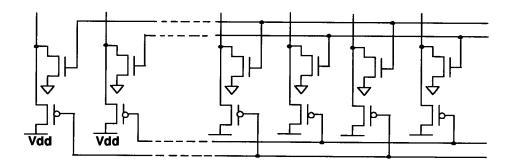

In the normal structure of MOS sensors (Figure 1.1), the signal charge is usually read out through the column line with large parasitic capacitance. Commonly, the column lines are gated through an analogue multiplexer to a single external charge sense amplifier. The requirements of this amplifier are daunting considering that wide dynamic range and high-speed must be achieved from a charge packet in the pixel which may be of the order of fC.

Figure 1.1 Normal structure of MOS sensors

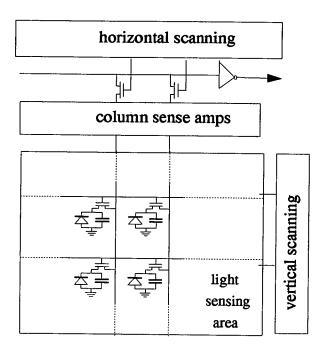

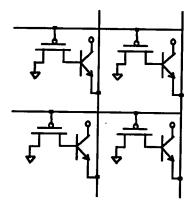

Accordingly a scheme was proposed by Professor P. B. Denyer to overcome this problem [Denyer, 1989]. The novel feature of the scheme is the integration of analogue CMOS charge sensing amplifiers at the top of every bit line, as shown in Figure 1.2. The benefits are that these amplifiers need not work so quickly, since their activation frequency is equal to the line rate rather than the pixel rate; and they are situated as close as possible to the pixel array so the line capacitance is reduced.

Figure 1.2 New structure of MOS sensors

A prototype was designed and fabricated in unmodified CMOS ASIC technology. Although the design itself, as a final year student project, is very basic, the image is surprisingly better than expected. The image signal is not drowned by the noise, due to the on-chip amplifiers, even in the dark.

Although the picture quality is far from perfect, the prototype did show that, with the amplifiers on the top of the array, the readout of the MOS sensor array became easier. Therefore, further development along this direction looked worthwhile. The objective of such work could include:

- Modification of sense amplifiers to optimize their function;

- Addition of an output buffer to improve the driving ability;

- Increased resolution;

- Integration of the control logic with the sensor array;

- Implementation of more camera functions on chip;

- Noise sources should be investigated and the chip should be more carefully designed to minimize the noise.

### 1.2 Project review

I have taken part in the project since the end of 1987. The project was then supported by the Science & Engineering Research Council (Grant GR/F 36538 IED2/1/1159, Augest/1989-July/1992) with Dr. D. Renshaw and Professor P. B. Denyer as principal investigators [Renshaw, 1992]. I registered as a part-time Ph.D. student in October, 1989.

The objective of my project has been to develop design techniques to achieve single chip video cameras, in unmodified CMOS process, with improved performance (aimed to match the performance of CCD cameras) and enhanced functions.

The first task facing me was to reduce noise so that picture quality of MOS image sensors improves. The work involved was to investigate all noise sources, highlight the main ones, and then eliminate them, or reduce them to an acceptable level. Only if this could be achieved without special requirements for process modification or external circuitry, can it be realistic to develop viable single chip video cameras implemented entirely in commodity ASIC CMOS technology.

The second task of the research was then to integrate a photodiode array together with all the necessary sensing, addressing and amplifying circuitry, as well as control logic on the same substrate. A subsequent aim was to achieve some enhanced functionality on chip, such as automatic exposure control, automatic gain control, analogue to digital

conversion, using CMOS design techniques.

With cooperation from another researcher and informative instructions from my supervisors, the objectives of this research have been met. We have developed unique CMOS circuit design techniques to realize single chip video cameras, in unmodified CMOS technology, which match and in some respects exceed the performance of CCD cameras and enjoy unprecedented reductions in size, cost and power consumption.

The main technical achievements are summarized as follows:

- Fixed pattern noise has been reduced to 40dB, by automatically compensating each sense amplifier to give near zero offset.

- Automatic exposure control has been implemented on chip, enabling the use of a single fixed-aperture lens. Control is achieved by varying the integration time prior to reading photo-pixels, giving a total exposure range of 40,000:1, wider than that of most commercial cameras.

- Gain control is implemented through putting a digitally controlled MDAC (Multiplying Digital to Analogue Converter) as an adjustable load. It extends sensitivity in low ambient light so that a dim image can became more visible on a monitor and more detail is retained in data conversion. The MDAC also supports successive approximation analogue to digital conversion.

- Digital control logic such as TV-formatting, exposure control, and gain control have been integrated on the same substrate to implement single chip video cameras.

Other technical features include auto-calibrated video black level, a simple method to implement γ correction and a solution for wafer stage test.

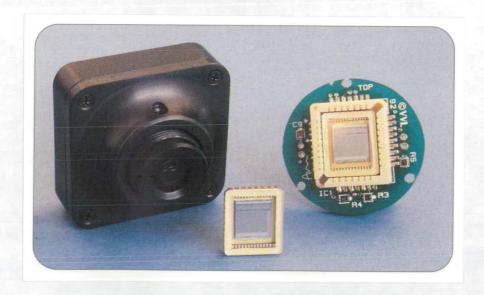

Six different designs of single chip CMOS video cameras have been completed during the past 4 years, including 3 commercial products [Wang, 1988-1992]. These designs have proven that three technical barriers which most greatly influence new product development: namely cost, power consumption and size, can all be dramatically reduced when compared with today's solid-state camera technologies.

Nine technical papers have been published [see publications], of which one paper entitled "CMOS Video Cameras", won the "Best Circuit Award" in the conference of EURO ASIC 91. Another paper entitled "On-chip Automatic Exposure Control Technique" won the "Best Paper Award" in the conference of ESSCIRC'91. There was also an "Award for Innovative Technology", at the International Fire and Security Conference at Olympia in 1992, granted for a remote alarm verification system which is based on a customized image sensor chip developed by us [Watts, 1992; Wang 1990].

The most immediate commercial benefit and probably the most significant outcome of this research has been that it has successfully engendered a new line of business, with the foundation of VLSI Vision Ltd. This is a company set up to trade in CMOS image sensor and sensor-processor designs and techniques, and has over the three years of its existence profitably developed products for third parties from British and overseas industry. This has lead to quantifiable benefits to the research programme, the University and the wider academic, research and commercial communities.

#### 1.3 Thesis structure

In this thesis, following the first chapter of introduction is a chapter of overview which reviews the evolution and present status of research and development in the field of solid state image sensors. Three category sensors (CCD, CID, and MOS) are introduced with the comparison between them. Some new photo-element structures aimed at future high definition television applications are also mentioned.

The fundamentals and architecture of an array sensor suitable for CMOS implementation are introduced in the third chapter. The pixel structure and the sensor array, the sense amplifier, the scan circuitry, and the output amplifier and buffer are covered.

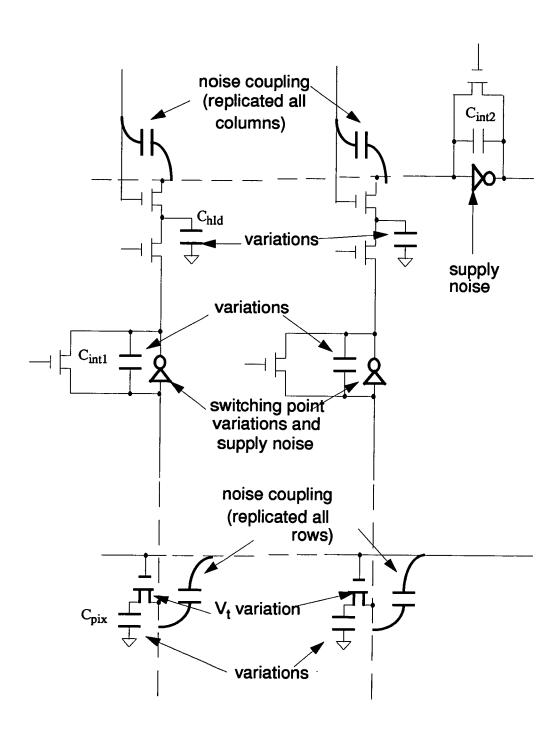

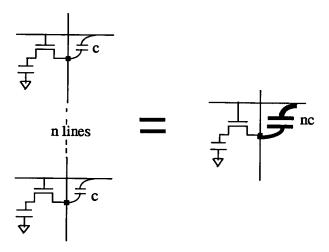

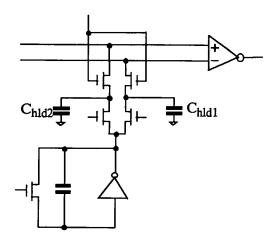

The fourth chapter is on noise. The analysis is carried out for both random noise and fixed pattern noise, with main noise source highlighted. A compensation scheme to eliminating fixed pattern noise caused by mismatch of sense amplifiers is presented. Other techniques to reduce noise are also discussed.

The fifth chapter discusses dynamic range. On-chip automatic exposure control and on-chip automatic gain control are introduced with both algorithm and circuitry covered.

Other techniques such as on-chip data conversion, on-chip black level calibration, on-chip  $\gamma$  correction, and wafer stage testing are then described in the sixth chapter.

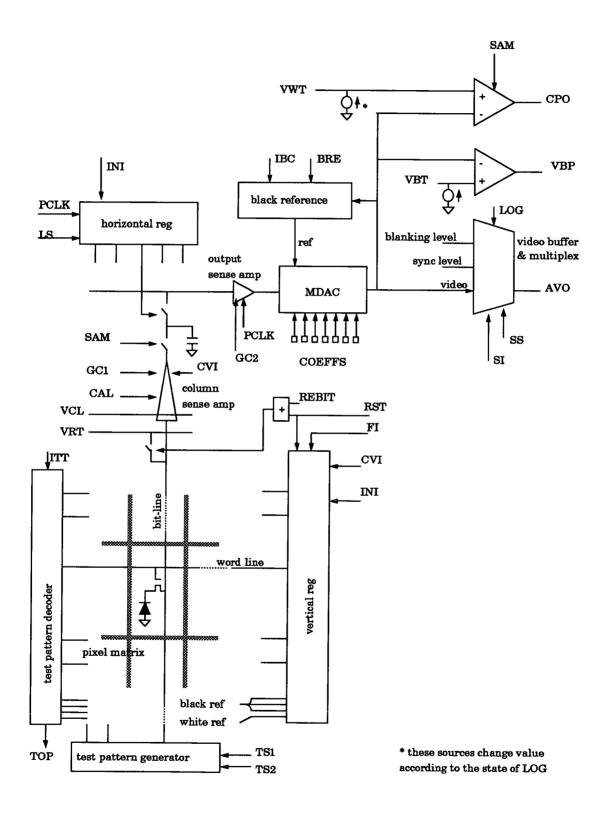

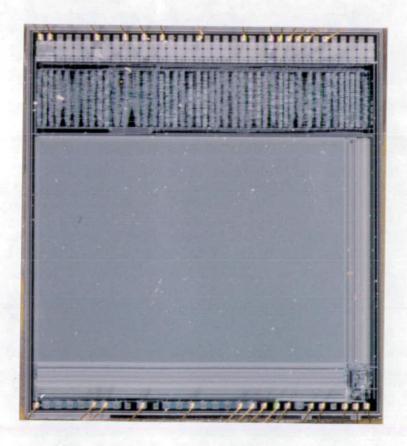

As a design example, the seventh chapter presents a single chip video camera, named ASIS-1011, which we believe is the smallest commercial video camera in the world. The features, the design, and the characterization of the device are covered in details.

The last chapter contains some discussions on remaining problems, recommendations for future work, and conclusions.

# Chapter 2 SOLID STATE IMAGE SENSORS: AN OVERVIEW

#### 2.1 Introduction

Work on solid state image sensors was started in 1960s, with the aim of replacing vacuum tube image sensors. The obvious disadvantages of vacuum devices are the large amount of space required for the electronics and coils, and big power consumption. On the other hand, solid state image sensors offer significant advantages: much greater compactness, low voltage and power reduction, reliability and expected cost reduction. Also, digital scanning provides a geometric accuracy of scan and a versatility of addressing. These advantages could introduce many new applications which were not feasible for vacuum image devices. During the course of the past two decades, solid state image sensors have experienced a tremendous amount of development due to the huge commercial success of home-video cameras, as well as security and industrial applications.

It is well known that silicon can act as an excellent photoreceptor over the visible spectrum. One of the most significant developments leading to the realization of a practical solid-state image sensor was the utilization of the p-n junction photodiode in integration mode. Charge-storage operation is based on the principle that, if a p-n junction is reverse-biased and then isolated, the charge stored on the depletion layer capacitance decays at a rate proportional to the incident illumination level [Sze, 1981; Middelhoek, 1989; Haskard, 1988; Sequin, 1975]. Therefore, a phododiode array can be used to produce electronic signals corresponding to a focused image. To electronically "read" this picture, each pixel on the array is selected in the sequence, controlled by the scan circuitry along both y-direction and x-direction. The image, in the form of electronic charge, can be restored by display devices such as TV monitor and computer terminal.

The entire function of image sensors may be likened to a single-transistor DRAM (Dynamic Random Access Memory) module, except data is written optically. Both

devices have a cell array constructed in a regular two-dimensional format, plus address and amplification circuitry. However, the design of sensors is more difficult than that of DRAM, in that sensors deal with analogue signals whist RAMs only have to store and output digital signals. The challenge of the sensor design is how to achieve rapid, low-noise detection of the tiny charge within each pixel.

Solid state image sensors are classified into three main categories: CCD (Charge Couple Device), MOS (Metal Oxide Semiconductor), and CID (Charge Injection Device). In fact, all these sensors work on the principle of charge storage, employing essentially the same photodiode structure to sense incident light and convert it into an electric signal. The main difference is in the way they read out signals. CCD devices transfer the signal charge by manipulation of MOS potential wells. It shifts the signal charge in series to an output sensing node. CID devices transfer the collected signal charge within an individually addressed pixel, and sense displacement values across the electrodes at the site. MOS devices transfer the signal charge by multiplexing the photoarray, using a digital scanner, in the way similar to RAM readout. Each of these technologies has its merits as well as drawbacks. They all have come a long way from the first primitive forms to their present structures [Wechder, 1965; Tseng, 1985; Chamberlain, 1986; Hobson, 1978; Michon, 1973; Sun, 1988; Tompsett, 1973].

There are appreciable advantages to be gained by building color image sensors using solid state sensors instead of vacuum tubes. In color cameras using vacuum tubes, the incident light from the scene is separated into the red, green and blue components by a prismatic assembly located immediately behind the camera lens. The three color components are then sensed separately by three tubes. Great care has to be taken to ensure that the three beams sweep with nearly perfect mutual registration. In replacing these tubes with solid state sensors, the discreteness and precision geometry of the integration sites and the clock controlled readout can automatically ensure linear and mutually aligned tracking of the scan in all three sensors, once the initial mechanical positioning has been done.

Solid state cameras have the advantage of geometric scan accuracy. This makes it possible to make compact color cameras only using one sensor array. This is achieved

by depositing color stripes directly onto the photo-array, making 3 neighbour pixels produce different color information. The resolution of the array for the use of color cameras will have to be 3 times that of monochrome cameras. The reduction in yield associated with a larger devices and problems with the fabrication of the color stripes have been solved. Today, color solid state cameras with TV standard resolution are in wide use.

Compared to monochrome solid state image sensors, color sensors require higher resolution, higher sensitivity, and more complicated circuitry for balancing and combining 3 color components. Other than this, basic design techniques are the same as for monochrome sensors. So far as the market is concerned, there still are big requirements for monochrome cameras where the color of the picture is not important and the cost is of more concern. Examples of these requirements are security application and production line inspection. The research reported in this thesis concerns monochrome devices only.

This chapter will review the evolution and the present status of research into three main categories of solid state image sensors: CCD image sensors, CID image sensors, and MOS image sensors. Comparison will be made between them. Following this is an introduction to some new photo-element structures which are being investigated for future high definition television applications.

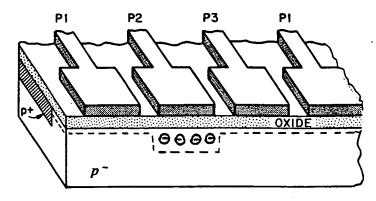

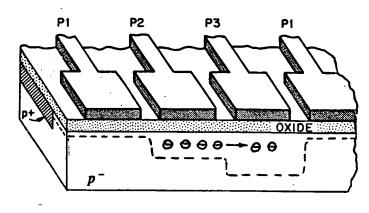

# 2.2 CCD image sensors

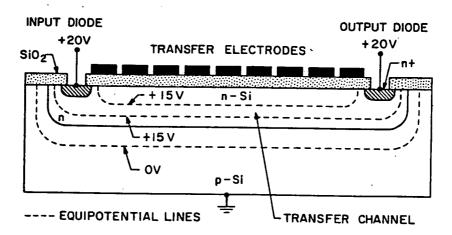

In the simplest implementation, CCDs consist of closely spaced capacitors on an isolated surface of a semiconductor, as shown in Figure 2.1[Tseng, 1985; Chamberlain, 1986; Amelio, 1974]. Figure 2.1a shows the potential well during integration and storage when only one electrode is turned on. During charge transfer, with two adjacent electrodes simultaneously turned on to the same potential, the charge packet will distribute uniformly underneath the two electrodes. When the first electrode is turned off, the charge will be pushed completely to the second one (Figure 2.1b). To continue

this charge transfer, the following electrode is pulsed to a high potential, and so on.

(a) during integration and storage

(b) during charge transfer

Figure 2.1 Basic cell of a 3-phase CCD

The device is referred to as a surface channel CCD if it transfers and stores the signal charge in the potential wells at the interface between the silicon and silicon dioxide. The interaction of the signal charge with interface states imposes certain lower limits on transfer inefficiency and transfer noise. These limitations can be alleviated by using a bulk channel device, which involves the use of an epitaxial or ion implanted silicon layer (or both) of opposite polarity to that of the substrate. This shifts the maximum

potential of the wells away from the interface and into the bulk, as shown in Figure 2.2.

Figure 2.2 Longitudinal cross section through a bulk channel CCD

Whenever charge is transferred from one gate to the next in a CCD a fixed fraction of the signal charge is left behind. Charge Transfer Efficiency(CTE) is a parameter measuring the amount of charge transferred from one cell to the next, and is expressed as a number between 0 to 1. CTE values can range anywhere from 0.9995 to 0.99999. Thus, CCD is a nearly ideal analog shift register.

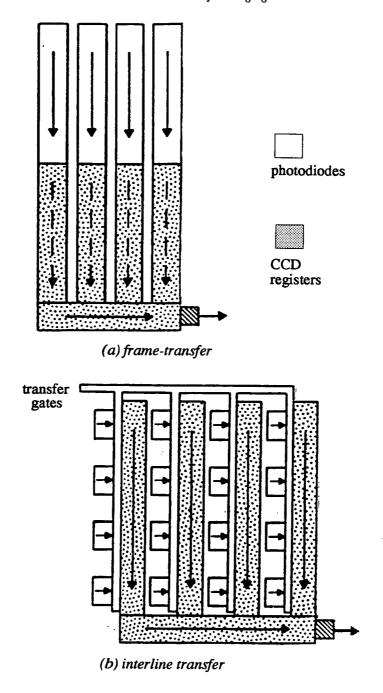

Two readout organizations have been developed for area image sensors. They are frame-transfer structures and interline transfer structures, as shown in Figure 2.3. Figure 2.3a shows the frame-transfer structure, in which, a separate shielded storage area is needed. After integration, the charge packets collected in the sensing area are shifted rapidly into the storage area. Signal charge packets in the storage area are then read out line by line, while the sensing area is integrating the next field. Figure 2.3b shows an interline structure, in which a separated shielded vertical CCD register is needed along each column of sensing cells. After integration, the charge packets in the sensing cells are transferred into the vertical shift register in parallel. Vertical shift registers then transfer the charge into the horizontal readout register one line at a time, while the photo pixels are integrating the next field.

Figure 2.3 Readout organization of CCD

The development of CCD began in 1969 at Bell Labs. A prototype of color camera was demonstrated in early 1970 which uses three small resolution CCD sensor chips. In

1978 a prototype of color camera using only one CCD sensor chip was reported [Dillon, 1978]. Since then, CCD image sensors have been highly refined to improve picture quality, increase the resolution and sensitivity, reduce the pixel size and chip area, and optimize their performance. Today, 2/3 inch and 1/2 inch CCD sensors with the resolution of around  $256 \times 256$  and  $512 \times 512$  are widely used. In fact, the majority of present solid state cameras use CCD sensors [E. Martin, 1990].

However, efforts to improve all features including higher resolution, and lower cost have never stopped. Recent trends are toward small size and high resolution. For this purpose, 1/3 inch format CCD sensors with around 250K pixels have been developed [Kuriyama, 1991; Hojo, 1991; Losee, 1989; Matsunaga, 1991; Akimoto,1991]. Miniaturization of CCD cameras keeps making progress. On the other hand, CCD sensors with million of pixel have been developed [Blouke,1985; Akiyama, 1986; Stevens, 1987; Oda,1989; Yonemoto,1990; Nobusada, 1988]. These sensors are aimed for the future high definition television(HDTV) system which requires much higher resolution than that for the current standard television systems [Crooijmans,1991; Geiger, 1991].

The diagonal of the image area for 1/2 and 1/3-in image sensors are respectively 8.0 and 6.0 mm. A 1/3 inch format will reduce the chip area to approximately 60% of conventional 1/2 inch devices, along with cost reduction and power consumption reduction. However, the pixel size is essentially reduced if the resolution is the same. This causes degradation in performance (mainly photo sensitivity). To tackle this problem, either on-chip microlenses are implemented and/or a high sensitivity amplifier is used [Kuriyama, 1991; Hojo, 1991, Furukawa, 1992].

The recent advances in the miniaturization of CCD cameras is related to the trend to reduce size, weight and power in hand-held camcorders for the consumer market. A Japanese company, Sony, launched its first camcorder, light weight video camera, in 1989. It then has shrunk the size and cost of its products through development of the tape mechanism and optical subsystems. Smaller lenses in turn require smaller and more sensitive image array. [Wilson, 1992]

Improved sensing and signal amplification techniques have enabled Sony to increase optical sensitivity at the same time as reducing the sensor area. This has been achieved by increasing the number of pixels per unit area and improving the sensitivity of pixels with new charge amplifiers. The sensitivity has been increased by a factor of four while reducing sensor array size from 1/2 inch to 1/3 inch. Sony's 1/2 inch CCD contains 440K pixels while 1/3 inch CCD has achieved 290K (figure of 1992) and Sony believes it can improve this figure further.

It is a challenge to achieve CCD sensors for HDTV. It requires not only high resolution (1920 × 1035 pixels), but also very high operational speed (74.25 MHz). It is difficult to reduce pixel size and to increase the operational speed both by such a large amount, while maintaining a wide dynamic range, and high signal-to-noise ratio. As feasibility research for future HDTV cameras, a 1-in format, 2 million pixel, interline CCD image sensor has been reported [Oda,1989], which adapts to the 16:9 aspect ratio, 1125 scanning lines, 60 fields, and 2:1 interlace HDTV system proposed at CCIR'86. In order to follow up ultrahigh-speed, the device uses a dual channel horizontal CCD register configuration and hybridize a bipolar buffer transistor chip in the same package as the sensor chip.

A 4 million pixel CCD has previously been developed [Blouke,1985], it is only applicable to a slow-scanning television system and only usable for capturing still images. [Akiyama, 1986; Stevens, 1987] reported one million pixel CCD image sensors, applicable to special-use systems. [Sakakibara, 1991] reported a 1-inch format 1.5M pixel CCD image sensor for an HDTV camera system. To achieve a low smear ratio while maintaining a high level of sensitivity, they developed a new impurity profile of a buried p+ layer and an on-chip micro lens array whose material is a deep-UV resist. Other papers reporting 2M pixel HDTV image sensors include [Manabe,1988; Negishi, 1991, Harada, 1992; and Shibata,1992].

# 2.3 CID image sensors

The development of charge injection device (CID) image sensors started in the early 70's at General Electric [Michon, 1973; Sun, 1988; CIDTEC; Williams]. CID use the

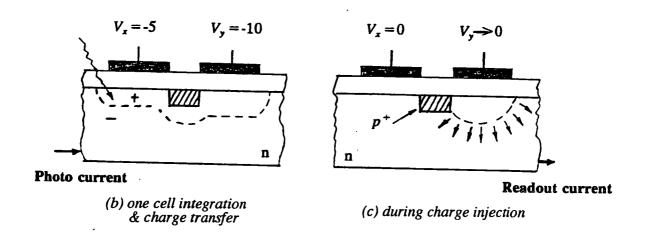

same type of potential well minority carrier storage as CCD does but charge transfer can only occur between two cells. The transfer can occur in either direction but otherwise the pair of cells are isolated from other cells. Basically the CID consists of a two dimensional matrix with a pair of adjacent MOS capacitors at each crosspoint (Figure 2.4a). As long as at least one of these two electrodes is biased on, the photogenerated charge can be stored. Alternatively it can be shuffled back and forth repeatedly between these capacitors (Figure 2.4b). When both capacitors are pulsed to zero simultaneously, the potential well collapses, and the charge is injected into the substrate, where it recombines (Figure 2.4c).

This is the process of charge injection. A corresponding charge flow occurs in the external circuit and it can be sensed through the column bias line. However, the recombination process may take many microseconds in the high lifetime material which is required to give low dark current, and thus the minority carriers may spread into neighbouring elements, or the signals of subsequently read elements may be mixed together. To overcome these problems, most CID image sensors are fabricated on epitaxial material. The epitaxial junction, which underlies the imaging array acts as a buried collector for the injected charge.

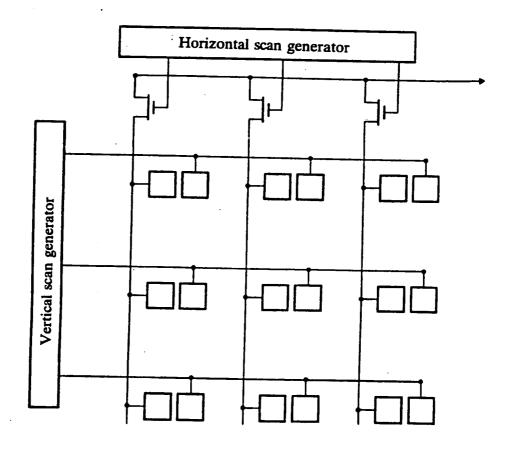

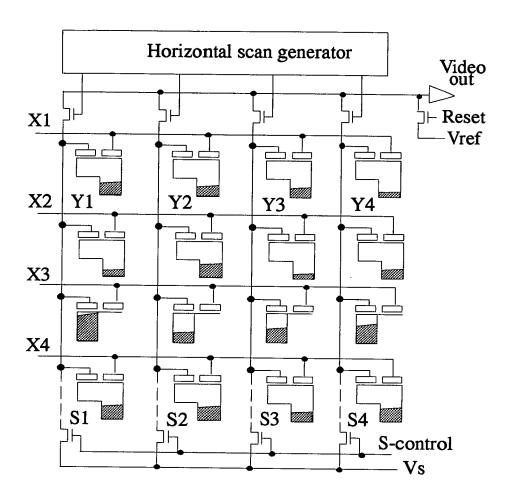

Readout can also be implemented by measuring charge transfer between two storage capacitors of each pixel. The transfer can be performed on all sensing sites along a row in parallel. Each row can also be cleared of signal charge by performing the injection operation in parallel at all pixels in the selected row. This readout technique has been termed "parallel injection". A diagram of a 4 × 4 array using parallel injection is illustrated in Figure 2.5 with the relative surface potential and signal charge included. At the beginning of a line scan, all rows have voltage applied and the column lines are reset to a reference voltage, Vs by means of switches S1 though S4 and then allowed to float. A row (X3 in Figure 2.5) is selected for readout, causing the signal charges at all pixels of that row to transfer to the column electrodes. The voltage on each floating column line then changes by an amount equal to the signal charge divided by the column capacitance. The horizontal scanning register is then operated to scan all column voltage.

(a) basic readout organization

Figure 2.4 Charge injection device (CID)

Figure 2.5 A  $4 \times 4$  CID array designed for parallel-injection readout

At the end of each line scan all charges in the selected row can be injected simultaneously by driving all column voltage to zero through switches S1 to S4. Alternatively, the injection operation can be omitted and voltage reapplied to the row after readout, causing the signal charge to transfer back under the row electrodes. This action retains the signal charge and constitutes a nondestructive readout operation.

Generally speaking, CID cameras are not competitive with CCD cameras. The main reason is fixed pattern noise and high video line capacitance which make image quality

poor, especially in the low light conditions. The other drawback is the requirement for an epitaxial substrate which is not compatible with standard VLSI ASIC processes. The epitaxial layer also causes loss of sensitivity due to absorption of photons by the layer.

On the other hand, CID has its merits such as nondestructive readout, contiguous pixel structure, and better anti-blooming performance. While CCD cameras are dominating the home video and commercial security markets, CID development is taking a different tack. Targeting system automation, CID sensors focus on achieving complete, accurate, and distortion-free image data acquisition for computer processing with fast, flexible timing and function control.

Nondestructive readout techniques enhance user control of light integration and image readout, useful for low-light applications. Integration may proceed for milliseconds or up to hours with the addition of sensor cooling, applied to retard accumulation of thermally-generated dark current. Camera readout may continue at video rates, but charge injection is inhibited, so the developing image can be viewed on a TV monitor as integration proceeds. This real-time exposure control is especially useful for resolving faint details in low-light scientific applications, significantly expanding dynamic range.

Blooming is a condition when excessive charges spill from over-saturated elements to adjoining pixels or the charge transfer paths. It will eradicate portions of the image. CID sensors are more tolerant to intense light due to the epitaxial layer which draws the excessive charges. This inherent anti-blooming performance ensures accurate image details even under extreme lighting conditions, making CID cameras particularly effective for testing and measurement (especially laser analysis), missile tracking, and a wide variety of other applications where reflections and the appearance of specular light intensities give rise to over-saturated regions within a properly exposed image.

The contiguous pixel structure of CID arrays further contributes to accurate imaging because there are virtually no opaque areas between pixels where image detail can be lost. This attribute is important for applications where precise dimensional data is critical. Examples include the determination of object edges for inspection,

measurement, positioning, and tracking. It is also essential for applications where complete data is crucial, as in particle analysis where illuminated particles may disappear if they fall into opaque regions.

Pixels in the CID array can be addressed individually. This makes flexible readout and processing options possible. For maximum flexibility random access CID is currently under development. The random access CID incorporate address decoders instead of sequential shift registers to provide programmable access to individual pixels in any sequence for readout and special charge manipulation routines.

# 2.4 MOS image sensors

The predecessor of the MOS image sensor can be dated back in 1965 when the first monolithic integrated photodiode array structure was announced [Wechder, 1965; Tseng, 1985; Chamberlain, 1986]. It consists of 200 photodiodes, each associated with an MOS FET. The gates of MOS FETs are individually driven by an external scan generator. However, this structure wasn't developed further at that time because MOS technology was in its infancy. Instead, a phototransistor structure was pursued. It was thought to be better due to the transistor gain. The major disadvantages and factors which eventually returned the photodiode to favour, were the random variations in transistor gain and the low level threshold due to the emitter offset. Only after MOS technology was developed (in particular silicon gate technology was developed), the marriage between MOS technology and the photodiode array operating in storage mode has resulted in today's MOS image sensor.

MOS sensors use a digital scanner to multiplex signal charges from photo pixels to the output, in the way similar to RAM readout. A typical structure of MOS sensors has been shown in Figure 1.1.

The light sensing area consists of a diode array matrix, schematically indicated by the columns and rows of individual photo-pixels. The photodiodes are pre-charged to a fixed bias voltage and then isolated. This results in a fixed charge being stored on the associated junction capacitance. The photodiodes are then left isolated for a suitable

exposure time. During this time, incident light upon each pixel partially discharges the junction capacitance. The rate of discharge is proportional to the incident light level. The final charge retained on the capacitor, after a fixed time interval, will represent the light intensity at that point of the image. The pixel signal is read out by opening the gate, connecting the photodiode to the MOS transistor drain. All of the drains in each column are connected in common and only one row is read at any time. The column lines are then gated through an analogue multiplexer to a single external charge sense amplifier.

The attraction of MOS sensors is that it is this technology, especially CMOS, that is the dominant technology for VLSI chips. Therefore, this technology is more easy-access and cost effective. More importantly, this technology has the advancing capability, permitting the integration of control and process logic on the same substrate. A smart vision system may be implemented on a single chip with the advantages of both solid state image sensors and VLSI systems.

Other virtues include the full inherent sensitivity, low voltage driving, custom pixel structure, and flexible readout scheme. Unlike CCD or CID pixel structure, MOS sensors require no surface electrode on the top of discrete photodiodes so that there is no interference pattern or light loss. Like all MOS devices, The sensors only require a single low voltage driving (normally 5 volt).

Other than a photodiode and an access transistor on each pixel, extra transistors can be put in to enhance the function of the pixel. For example, a transistor connecting the photodiode to ground may be added to increase the anti-blooming ability [Renshaw, 1991]. Another example is a image-motion detection device [Chong, 1992]. A pixel of this device consists of a photodiode, a switch, and a cell called current-mirror differentiator which detects the light current variation of the pixel.

The sensor array can be read out in the normal sequence or in other scan out scheme. One example is a CMOS image sensor chip for fingerprint verification [Anderson, 1991]. The addressing and read out circuits have been modified to allow local two dimension smoothing  $(3 \times 3)$  to take place as the image data is scanned out. Just by changing the readout scheme, the required low-pass filtering is implemented without

any hardware overhead.

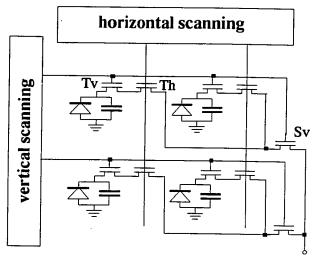

Hitachi is the leading company to develop MOS sensors. It introduced color video cameras in 1981 and camcorders in 1985 [Noda, 1986; Asano, 1988]. A array structure called TSL (Transversal Signal Line) structure, as shown in Figure 2.6, was developed by the company.

Figure 2.6 TSL structure

Compared with the normal structure of Figure 1.1, a new MOS switch is added to each pixel and the signal readout line is laid out horizontally. The information stored in each photodiode is read out in the following manner: the vertical shift register turns on the Tv and readout transistor (Sv), and the horizontal shift register turns on Th by transferring information to the external. The essence of this structure is that electric charges from each pixel stay only a short time on the signal line so that smear noise is suppressed. The normal structure may suffer from smear noise from overcharging of the vertical signal lines during the horizontal scanning period.

However, MOS sensors suffer a significant problem: high noise. The big video line capacitance results in the high random noise. The process nonuniformity results in the high fixed pattern noise. Most commercial MOS cameras (such as Hitachi's) at present

do not integrate control logic together with the sensor array. They usually consist of a X-Y addressable MOS photoarray chip, along with boards of components. One reason is that MOS sensors are so noisy that complicated off-chip sense and amplification circuits are needed. Another reason is that although the digital circuitry can be put on chip, the digital interference causes a big problem. The cameras assembled in this way do not enjoy the real virtue of the MOS technology, integration. They can not compete with CCD cameras because of the inherent high noise.

On the other hand, even through the image quality may not be as good as that of CCD, it is still very attractive to include a sensor array with other control and processing functions on the same chip. There are many applications where the image quality may not be so crucial but other matters such as cost, volume, power consumption, and system integration are more important.

One early example is a one-dimensional motion detector [Tanner, 1984] which consists of an array of photodiodes for detecting the light pattern, a storage array for the image, circuitry to compute the correlation between the stored image and the current one, decision circuitry to determine where the correlation is greatest, and a self timed controller to sequence the entire system.

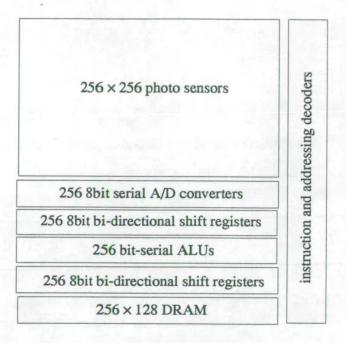

Another example is a matrix array picture processor which can handle image processing tasks such as sensing, digitization and data reduction. [Forchheimer, 1990]. The device contains a 256 × 256 photosensor array, 256 8-bit serial A/D converters, 256 bit-serial processors and a 256 × 128 memory. Two 256 × 8 bi-directional shift registers are used for communication between processor elements and I/O (Figure 2.7). This chip is aimed at pre-processing of gray level images and binary images, eliminating the bottleneck of sequential image read-out that characterizes conventional systems. It is suitable in applications demanding high-frame rate digital image processing with greatly reduced I/O bandwidth, complexity and system cost. [Gibertoni, 1991] also reported a smart image sensor for computer vision. The chip comprises a grid of light sensitive pixels and a set of processors operating in parallel.

Figure 2.7 a matrix array picture processor

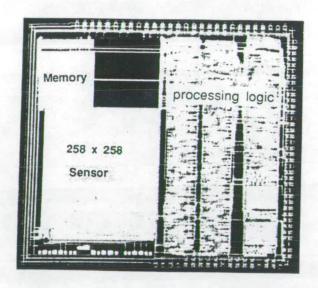

Figure 2.8 a sensor chip for fingerprint verification

Our group also implemented a smart image sensor chip for fingerprint verification [Anderson, 1991]. Other than a 258  $\times$  258 pixel array, it includes image preprocessing

and quantisation circuitry to form a normalised binary image, 64-cell 2000 M op/sec correlator array, post-correlation decision logic, 16K bits RAM, and 16K ROM (Figure 2.8). With the aid of two external devices (one 64Kbit RAM and one 8052 microcontroller), this device performs all of the image sensing and processing functions necessary to capture and verify a fingerprint against a stored reference print within one second. It shows that challenging imaging applications, such as fingerprint verification, can become possible within a few tens of cubic inches, consuming a few watts of power if MOS technology is used. This is perhaps the best example to show how powerful a single chip MOS vision system can be.

Noise remains a fundamental problem which limits the development of MOS sensors and MOS vision systems. In fact, it is a limitation which hampers the huge potential application and market of MOS image sensors. The main emphasis has been on reducing the noise and improving the picture quality. The research work of our project is a contribution to this.

In the normal structure of MOS sensors (Figure 1.1 as well as Figure 2.6), the signal charges are usually read out through the sense line with large parasitic capacitance and amplified by an external charge sense amplifier. The requirements of this amplifier are daunting considering that wide dynamic range and high-speed must be achieved from a charge packet in the pixel which may be of the order of fC.

Accordingly a scheme was proposed in 1987 by Professor P. B. Denyer to overcome this problem [Denyer, 1989]. The novel feature of the scheme is the integration of analogue CMOS charge sensing amplifiers at the top of every bit line (Figure 1.2). The benefits are that these amplifiers need not work so quickly, since their activation frequency is equal to the line rate rather than the pixel rate; and they are situated as close as possible to the pixel array so the line capacitance is also reduced. The sense time can be as short as a few pixel clock periods so that smear noise is suppressed too. The common lines are then connected to bias voltage to prevent blooming. Their sole constraints are the need to achieve a good dynamic range and to be realised within the

pixel pitch (of the order of 10-20 µm).

A prototype was designed and fabricated in unmodified CMOS ASIC technology in 1987 [Suen, 1987]. It comprises a  $128 \times 128$  pixel array, and includes basic address, sense and amplification circuitry. The chip works from a single 5 volt power supply and a 1M Hz clock source, and delivers a sequentially-scanned, low-impedance analogue output of 1 volt peak-to-peak.

Actually, the design itself, as a final year student project, is very basic. Other than the top sense amplifier array and an output amplifier, there are no special considerations about reducing noise, even without protection to the analogue circuit and analogue signals. However, the image, captured by a frame grabber is surprisingly better than expected. The image signal has not been swamped by the noise, due to the on-chip amplifiers, even in the dark. This shows that with the amplifiers on the top of the array, the readout of the MOS sensor become easier. The main problem is still noise, especially fixed pattern noise. We learnt later that one source of the fixed pattern noise is from the sense amplifiers themselves. Process nonuniformity causes the mismatch of the amplifiers.

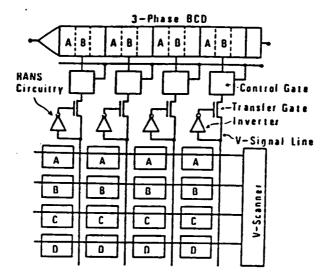

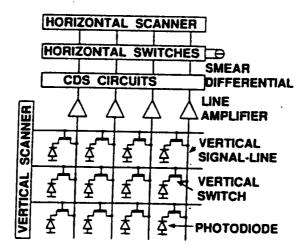

The idea to place amplifiers at each bit common signal line was also reported by Japanese researchers. Their first report was a device which combines a MOS pixel array and a horizontal bulk charge-transfer device (BCD) [Ando, 1985]. The device has noise suppression (RANS) cells on the top of each bit line, as shown in Figure 2.9. [Ozaki, 1991] proposed and analysed another scheme, close to ours, as shown in Figure 2.10. The paper expected this scheme to improve signal to random noise ratio, but fixed pattern noise will remain a problem. However, they didn't actually design and fabricate any such devices.

Figure 2.9 A device with a MOS array, a BCD, and RANS cells

Figure 2.10 A device with line amplifiers on the top of the array

Fixed-pattern -noise is a common issue to photo array and analogue image storage circuits fabricated in unmodified ASIC process. [Franchi, 1992] reported a analogue frame buffer for early vision. The device has 6K analogue memory cells. The measurement result shows the main limiting factor to the higher precision is FPN induced by parameter mismatches, while the errors caused by different charge injection

and by charge decay during the retention time are not critical. This is in consistent with our results. A mismatch-compensation scheme was then developed.

# 2.5 Comparison between CCD, CID, and MOS image sensors

Compared with other solid state image sensors, CCD sensors have been developed to the most advanced state. Today, CCD cameras are being widely used, mainly due to their low noise characteristics. However, CCD technology has the following disadvantages:

- Expensive production cost due to complicated fabrication process;

- Less flexibility of design compared with other types of sensors;

- Not compatible with standard VLSI process;

- Poor quantum efficiency and spectral response for multi-layer gate structures;

- CCD transfer path needs extra area, this become more severe for high resolution.

Of these disadvantages, high production cost and non-compatability with VLSI process are the most important. These explain why commercial CCD cameras are so expensive and so complicated.

On the other hand, MOS sensors have the advantage of

- cheap technology;

- compatible with standard VLSI process.

Therefore, smart vision application systems can be integrated only using MOS sensor arrays along with control logic and processing circuitry. With today's advanced MOS

technology, such system can achieve both high scale integration (near million devices) and low cost (about one pound per chip in mass production).

### Other advantages are:

- small volume;

- low power consumption;

- single power supply (5 volt);

- simple pixel structure suitable for high resolution;

- design flexibility (custom pixel structure and custom readout scheme).

The main drawback of MOS sensors is high noise due to high video line capacitance and process nonuniformity. This has been hampering the development of MOS sensors.

### CID sensors also suffer from

- Fixed pattern noise;

- High video line capacitance;

### Other drawbacks of CID sensors include:

- Requires an epitaxial substrate, which is not compatible with standard VLSI processes;

- Loss of sensitivity due to absorption of photons by epitaxial layer;

- Poor spectral response due to absorption of long wavelength photons by polysilicon gates.

It seems that CID is the poorest technology for solid state image sensors because it has both main drawbacks of CCD and MOS sensors, i.e., not compatible with standard VLSI process and high noise. However, CID has its unique advantages:

- Flexibility of operation (with nondestructive readout mode);

- Random access readout;

- Low blooming due to expitaxial structure;

- Entire active area is sensitive to light;

- Opaque region between adjacent pixels is very small.

It is these merits that make CID sensors survive. In fact, CID sensors have their own market, focusing on achieving complete, accurate, and distortion-free image data acquisition for computer processing with fast, flexible timing and function control.

# 2.6 New photo-element structures

To realize future HDTV image sensors, other new photo-element structures are also being investigated since it is difficult to meet the more stringent requirements with present day techniques. There are several approaches which use photocells with a charge gain built into them in order to increase the light sensitivity when the size of the pixel sensing area is reduced [Yusa, 1986; Hynecek, 1988; Ogata, 1991; Matsumoto, 1991; Tanaka, 1989; Nakamura, 1991]. Here we look at some examples.

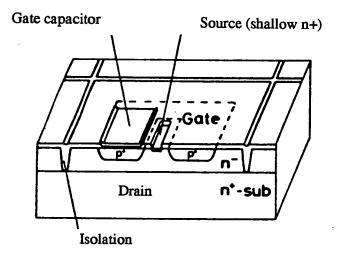

Figure 2.11 shows the cell structure of the device using a static induction transistor(SIT) [Yusa, 1986]. The n- epitaxial layer is grown on the n+ source substrate that acts as the SIT drain. A shallow n+ source region is formed on the epitaxial layer, so that the p+ gate region surrounds the source. An MOS capacitor is formed on the gate, and the gate pulse is applied through this capacitor. When the gate is reverse biased, a depletion layer forms outside the gate. If hole-electron pairs are generated by incident light in this region, electrons are swept away to the source or to the drain, while holes are stored on

Figure 2.11 SIT structure

The drain-source current is modulated by this voltage change, and an amplified light-dependent signal is obtained. Image sensors consisting of  $170 \times 124$  pixels were fabricated using a combined SIT and MOS process. The signal current from the cell is 18 times larger than that of normal MOS cells having same pixel area. The main problem is nonuniformity. One primary cause is the lack of uniformity on the SIT I-V characteristics. This produces nonuniformity of output offsets.

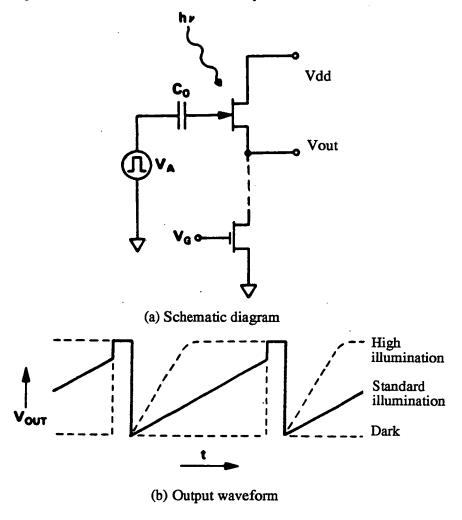

Figure 2.12 shows the cell structure of the device called floating gate array(FGA) [Hynecek, 1988]. The cell consists of a n-channel JFET connected as a source follower with its gate floating and capacitively coupled to an address line. The pull-down transistor in the diagram is common to a column of pixels. The function of this circuit can be understood from the output waveform shown in the diagram in Figure 2.12(b). An arbitrary pulse V<sub>A</sub> presets the circuit and charges the capacitor C<sub>O</sub>. The floating gate remains fully reverse biased if no light injected into it. On the other hand, if there is light, the photogenerated carriers partially discharge the capacitor and increase the potential of the gate. The source potential follows the gate potential and the waveforms corresponding to different light intensities can be observed, as shown in Figure 2.12(b). The photogenerated signal can then be obtained by measuring the output voltage

difference before and after the preset pulse. The layout shape of pixels is an equilateral hexagon with an enclosed gate and the source in the center. It holds promise for smaller cells and much larger arrays that are needed for future high-resolution image sensors. However, this structure still places strict requirements on the geometry tolerances and process parameter controls. The nonuniformity of a test device is around 2%.

Figure 2.12 FGA structure

The cell structure for a charge modulation device (CMD) [Nalamura, 1986; Ogata;1991; Matsumoto, 1991] is shown in Figure 2.13. The device is built on an n-type epitaxial layer which is on the top of p-type substrate. The gate electrode polycrystalline silicon is deposited and then patterned to an annular shape. The n+

source is inside the gate and the n+ drain is outside. The positively biased drain region between the pixels acts as an optical isolator. The gate electrodes are negatively biased with respect to both source and drain during charge collection periods, so that the surface of the semiconductor beneath the gate electrodes is depleted of carriers.

Figure 2.13 CMD structure

The p- substrate is also negatively biased, preventing the holes in the substrate from flowing to the surface. The incident light travels through the semi-transparent gate electrode structure and is absorbed in the Si bulk beneath the gate electrode. The holes generated near the surface drift to the Si/SiO<sub>2</sub> interface under the gate, where they are stored until removal by the image reset process. On the other hand, the holes, generated deeper down, drift to the p- substrate. The stored holes increase the surface potential, thus lowering the potential barrier height for electrons. Therefore, the electron current flows in accordance with the number of stored holes, and an amplified light-dependent current is obtained. When a positive bias is applied to the gate electrode, the stored holes are swept away to the p- substrate, resulting in the surface channel having a ready supply of electrons from the source region.

An experimental chip has been fabricated. The signal to noise ratio is limited by fixed pattern noise which originates mainly from exposure nonuniformity in the wafer

An experimental chip has been fabricated. The signal to noise ratio is limited by fixed pattern noise which originates mainly from exposure nonuniformity in the wafer fabrication process. The FPN in the dark is 5% of the saturation signal. The adjacent pixel nonuniformity is roughly 2%.

There is another pixel structure called base-stored image sensor (BASIS) [Tanaka, 1989; Nakamura, 1991]. The pixel is composed of an NPN bipolar transistor and a PMOS switch, as shown in Figure 2.14. The pixel is operated through the control gate of the switch. The pixel is first reset by applying a negative voltage to the gate of PMOS switch. The device is then off, isolating the base of bipolar transistors. The voltage level of base node of the bipolar transistor will be determined by the light intensity during storage operation when both base and emitter are floating. During readout operation, the emitter is connected to a load. The voltage of emitter will follow that of base because it now works as a emitter follower. In order to reduce fixed pattern noise, nonuniformities of bipolar parameters such as  $h_{\rm FE}$  and  $C_{\rm bc}$  should be made as small as possible.

Figure 2.14 BASIS structure

These new structures all have achieved high gain built into pixels, and are thus affected less by noise originating from readout circuitry and are therefore expected to offer a high signal to noise ratio. However, nonuniformity of pixels causes fixed pattern noise, a common problem which requires solutions.

# 2.7 Chapter summary

The evolution and present status of solid state image sensors have been reviewed. Three categories, CCD, CID, and MOS, have been covered with comparisons made between them. New photo-element structures aimed at future high definition television applications have also been described.

Although CCD image sensors have the most advanced development, MOS sensors have potential to implement smart vision application system with higher scales of integration and lower cost. This is an area worthy of further research efforts.

# Chapter 3 BASIC ARCHITECTURE

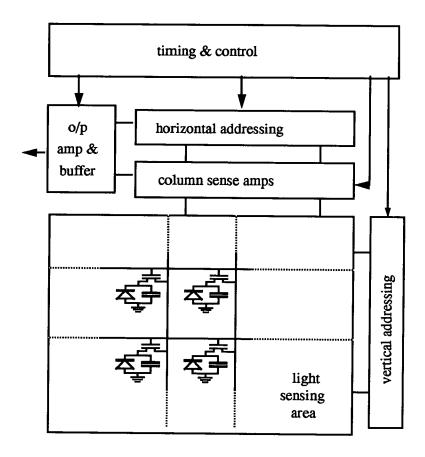

The fundamentals and architecture of an array sensor suitable for CMOS implementation are introduced in this chapter. The pixel structure and the sensor array, the sense amplifier, the scan circuitry and the output amplifier and buffer are all covered.

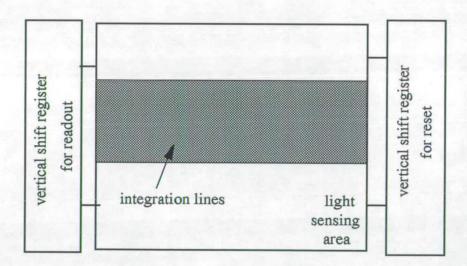

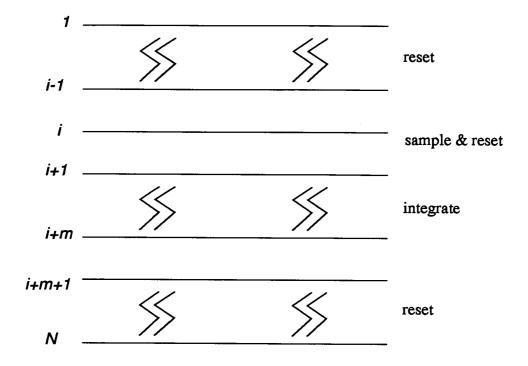

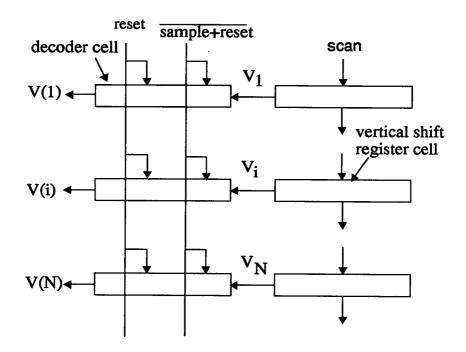

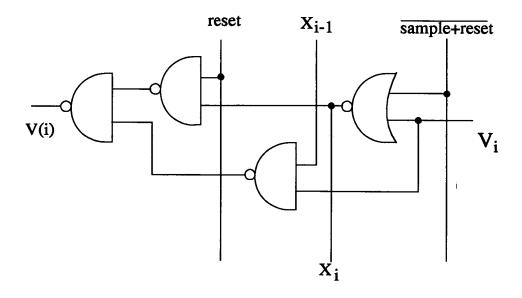

Figure 3.1 Basic architecture of MOS image sensors

The basic architecture of the image sensor is shown in Figure 3.1. The light sensing area consists of a diode array matrix, schematically indicated by the columns and rows of individual photodiodes. The photodiodes are accessed on the basis of sequential selection of each row, along y-direction, through a vertical shift register. At the top of

each column is a sense amplifier. The sensed information is read out sequentially, along the x-direction, under control of a horizontal shift register. At the end of the signal amplification path there is an output amplifier and a buffer. The operation of these cells is coordinated by on-chip timing and control logic.

# 3.1 Sensor array

# 3.1.1 Charge storage operation of the photodiode

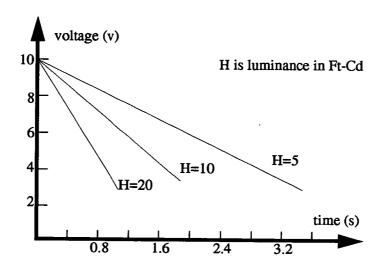

One of the most significant developments leading to the realization of a practical solid state image sensor is the utilization of the p-n junction photodiode in an integrating or storage mode [Sze, 1981; Middelhoek, 1989; Haskard, 1988; Sequin, 1975]. Charge storage operation is based on the principle that, if a p-n junction is reverse biased and then isolated, the charge stored on the depletion layer capacitance decays at a rate proportional to the incident illumination level.

Figure 3.2 Voltage decay of an illuminated p-n junction

In the dark, only generation recombination current (dark current) is available to discharge the depletion layer capacitance; since both depletion layer capacitance and generation recombination current are directly proportional to area, the time constant is

independent of area. In the dark at room temperature, time constants of seconds may be attained for most standard MOS processes.

Figure 3.2 shows decay characteristics of a diode for several illumination levels [Tseng, 1985]. The photon-generated current is directly proportional to the illumination level and therefore the amount of charge removed in a given interval of time is directly proportional to the integral of illumination, taken over that interval. Thus, the final charge retained on the junction, after a fixed time interval, will represent the light intensity at that point of the image.

The charge storage operation mode has a few advantages.

- The integration of the incident illumination results in improved sensitivity;

- Electronic exposure control can be implemented by varying the integration time.

In a standard ASIC CMOS process there are three possible photodetector device structures available: photoconductor, photodiode and photo-transistor. Factors affecting the choice of device include device area, response time, and gain. Photoconductors are unsuited to use in array sensor devices, due to large area and slow response time. Comparing photodiode with phototransistor, the photodiode has advantages of simpler structure, smaller area and faster response time. The phototransistor benefits from greater gain but its use in array device is complicated by inevitable device and operating condition variation. For these reasons the photodiode is the basic sensing element used in our designs.

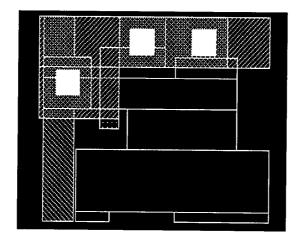

# 3.1.2 Pixel structure and operation

In common with others we use a photodiode array comprising MOS transistors, one per pixel, as shown in Figure 3.3. The photodiode is implemented by extending the source

region of the transistor. The layout of a pixel is shown in Figure 3.4.

Figure 3.3 Pixel structure

Figure 3.4 Pixel layout

In operation, the photodiode is reset to a voltage reference level  $V_{ref}$  by opening the MOS transistor gate. This stores a fixed charge package on the p-n junction capacitor of the source area of that transistor. The p-n junction is then isolated. The photocurrent,

produced by the effect of photons impinging on the diode, discharges the capacitor. The rate of discharge is proportional to the photocurrent, which is in turn proportional to the incident light level. The final charge retained on the capacitor, after a fixed time interval will represent the light intensity at that point of the image. The pixel is read by opening the gate, connecting the photodiode to the MOS transistor drain. All of the drains in each column are connected in common and only one row is read at any time.

# 3.2 Sense amplifiers

# 3.2.1 Structure and transfer function of sense amplifiers

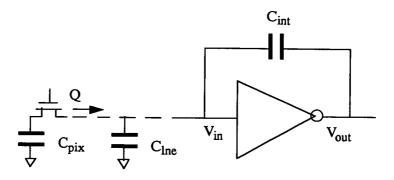

Commonly, as stated in the first chapter, the column lines of the sensor array are gated through an analogue multiplexer to a single external charge sense amplifier(Figure 1.1). The requirements of this amplifier are daunting considering that high-speed and wide dynamic range must be achieved from a charge packet in the pixel which may be of the order of fC.

A novel feature of our design is the integration of a sense amplifier at the top of every column line (Figure 1.2). These amplifiers need not work so quickly, since their activation frequency is equal to the line rate rather than the pixel rate and they are situated as close as possible to the pixel array. Their sole constraints are the need to achieve a good dynamic range and to be realised within the pixel pitch.

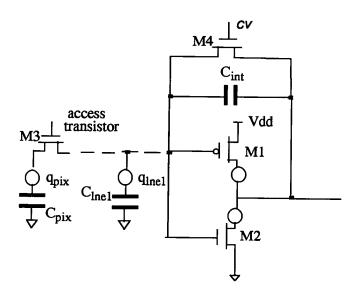

A charge integrator is used as a sense amplifier. Its function is analysed as follows with reference to Figure 3.5.

The capacitor  $C_{lne}$  indicates the bit line capacitance, and capacitor  $C_{pix}$  indicates the photo-diode junction capacitance. The capacitor  $C_{int}$  is the integration capacitor.

Figure 3.5 A charge integrator

Assume everything starts w.r.t. a notional zero and Q is the signal charge stored on  $C_{\rm pix}$ . When a pixel is selected this charge Q is injected into the bit line and redistributed over capacitors  $C_{\rm lne}$ ,  $C_{\rm pix}$ , and  $C_{\rm int}$ . The equation describing the distributed charge is

$$V_{in} \times (C_{lne} + C_{pix}) + (V_{in} - V_{out}) \times C_{int} = Q$$

Eq(3.1)

Using the equation for the gain of the inverter;

$$V_{out} = -A_v \times V_{in}$$

Eq(3.2)

to eliminate V<sub>in</sub> and solving for V<sub>out</sub> yield,

$$V_{out} = \frac{-Q}{C_{int} + \frac{C_{lne} + C_{pix} + C_{int}}{A_{v}}}$$

Eq(3.3)

Assume  $C_{lne}$  is much bigger than  $C_{pix} + C_{int}$ , then

$$V_{out} = \frac{-Q}{C_{int} + \frac{C_{lne}}{A_{v}}}$$

Eq(3.4)

If  $A_v$  is high enough to make  $\frac{C_{lne}}{A_v}$  much less than  $C_{int}$ , thus

$$V_{out} = \frac{-Q}{C_{int}}$$

Eq(3.5)

Furthermore, because  $Q = C_{pix} \times V_{pix}$  ( $V_{pix}$  is the voltage level remained on photodiode), we get

$$V_{out} = \frac{-C_{pix} \times V_{pix}}{C_{int}}$$

Eq(3.6)

This equation shows that to first order the gain of ideal integrators is determined by the ratio of two capacitors.

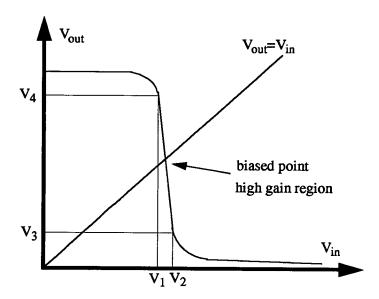

### 3.2.2 High gain amplifier

High gain amplifiers are key elements to achieve good performance charge integrators. However, the realisation of such high gain amplifiers within a narrow pixel pitch presents an engineering challenge. CMOS inverters, the simplest possible amplifiers, have been chosen for this purpose.

It is known that the transfer characteristics of CMOS inverters, especially near the switching region, is largely depending on a second order effect, called channel-length modulation. Figure 3.6 shows the transfer characteristic of CMOS inverters. As a result, it is possible to obtain a linear high gain region providing the input of the inverter is restricted to the voltage value between  $V_1$  to  $V_2$ .

Figure 3.6 Transfer characteristic of CMOS inverters

This condition is ensured by self biasing the inverters, such that  $V_{out} = V_{in}$ , each time before photodiodes are to be sensed. The self biasing is implemented by turning on a transistor across the input and the output. This operation is called "balance".

The balance enable signal for sense amplifiers is *cv*, which is the clock signal driving vertical shift register (see section 3.4: scanning circuitry).

# 3.2.3 Performance

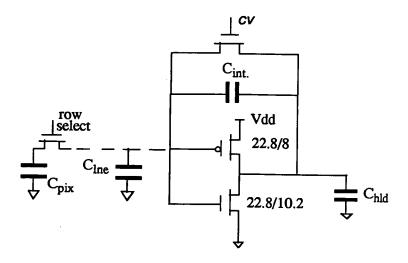

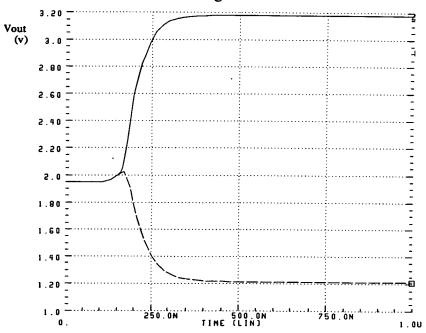

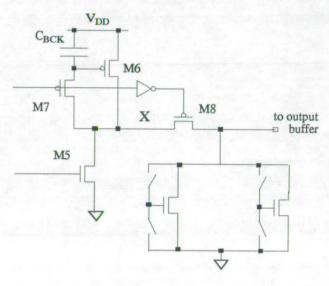

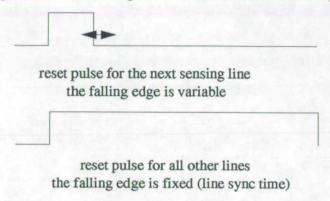

Figure 3.7 shows the detailed diagram of the first sensing stage: from the pixel, through the sense amplifier, to the hold capacitor. The activation of sense amplifiers is coordinated with the vertical shift register, under the control of line clock cv. The sense amplifier balances when cv is high, and then samples a selected line. The voltage representation at the output is stored on a capacitor  $C_{hld}$ .

Figure 3.7 The first sensing stage

SPICE simulations have been carried out to optimize the performance of the sense amplifiers. The sense amplifier gives a low impedance 2 v analogue representation of the pixel charge. The sensing time is approximately 300 ns. Figure 3.8 shows the simulation results for both black and white light conditions.

Figure 3.8 Simulation result of the first sensing stage

The single parameter of concern for this simple circuitry is the fixed pattern noise from mismatches between these amplifiers. This effect can be eliminated by implementing an offset compensating phase during idle period, which will be discussed in Section 4.2.

# 3.3 Output amplifier and buffer

# A

### 3.3.1 Output amplifier

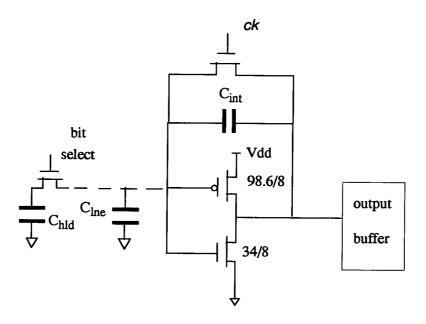

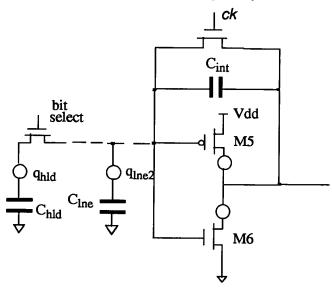

The output amplifier has the same structure as sense amplifiers, shown in Figure 3.9, to implement the second stage of amplification. The difference is that the output amplifier needs bigger transistors (bigger width to length ratio) because it works at the pixel rate which is much faster than the line rate. Fortunately, there are no constraints on layout area, such as pixel pitch match. Secondly, there are no problems of matching multiple amplifiers, as all pixels are sequentially read out through the same output stage.

Figure 3.9 The second sensing stage

The balance enable signal for the output amplifier is *ck*, which is the clock signal driving horizontal shift register (see section 3.4: scanning circuitry).

Analysing the output amplifier in a similar manner to the column sense amplifier gives

$$V_{out} = \frac{-Q}{C_{int} + \frac{C_{lne} + C_{hld} + C_{int}}{A_{...}}}$$

Eq(3.7)

where, Chld is a capacitor storing the signal amplified by the first sensing stage. If Av

is high enough to make  $\frac{C_{1ne} + C_{h1d} + C_{int}}{A_{v}}$  much less than  $C_{int}$ , thus

$$V_{out} = \frac{-Q}{C_{int}}$$

Eq(3.8)

Furthermore, because  $Q = C_{h1d} \times V_{h1d}$  (V<sub>hld</sub> is the voltage level storing on the capacitor  $C_{hld}$ ), we get

$$V_{out} = \frac{-C_{hld} \times V_{hld}}{C_{int}}$$

Eq(3.9)

This shows that to first order the gain is determined by the ratio of two capacitors.

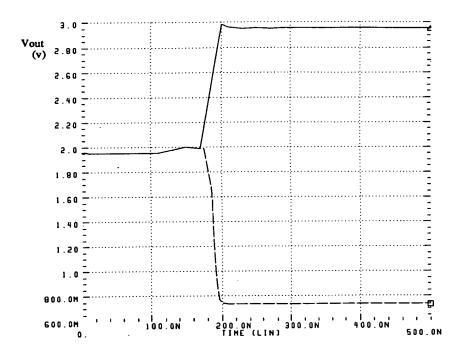

Figure 3.10 show the SPICE simulation results of output amplifier for both black and white light conditions. The sensing time is about 50 ns.

Figure 3.10 Simulation result of the second sensing stage

However, if the output amplifier directly drives a pad, the readout speed will deteriorate. Further more, the balance/amplification operation mode will result in thick vertical stripes, when displayed on a video monitor. Thus, an output buffer is needed to drive the output pad and implement sample/hold functions to improve picture quality.

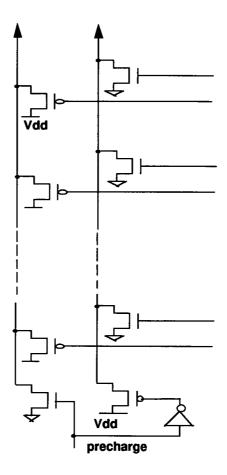

### 3.3.2 Output buffer

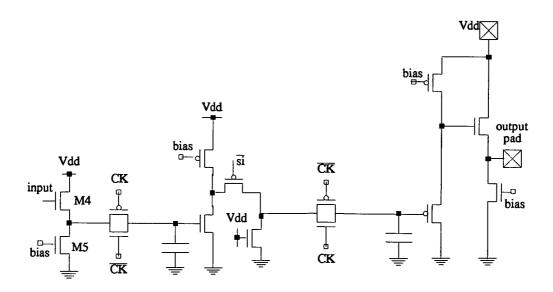

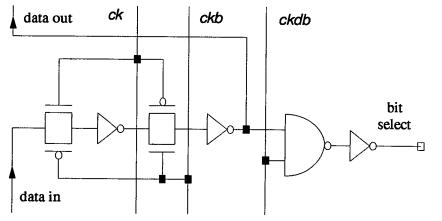

Figure 3.11 shows an output buffer which has been implemented to improve the drive ability and picture quality. It works well at 6 MHz clock, making it possible to achieve a reasonable video rate readout. It has two sample/hold stages to get rid of vertical stripes arising from balance of the output amplifier.

Figure 3.11 an output buffer

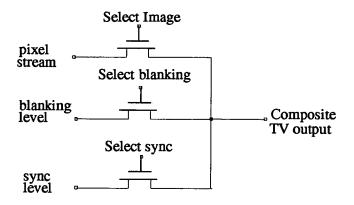

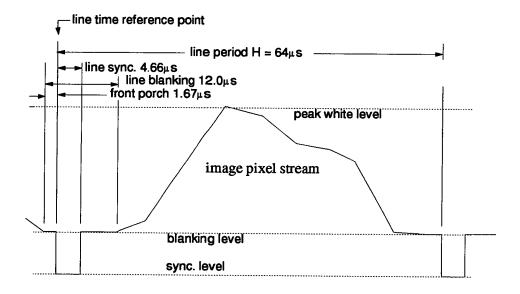

For applications requiring a composite video waveform it is relatively easy to format at this stage. Let us briefly review the format of composite TV signal (CCIR) [Grob, 1984; Bohlman, 1990]. It takes 25 frames a second. Each frame consists of 2 fields with a theoretically infinite horizontal resolution, and 312.5 lines per field vertically. Each field consists of a vertical retrace interval plus about 287 worthwhile lines of video data. Each line is composed of a sync signal, a blanking period, plus actual video. The vertical sync is a longer version of the horizontal signal. The sync, blanking, and video signals can be encoded in an analog voltage multiplexing scheme, as shown in Figure 3.12. Figure 3.13 shows the composite video waveform.

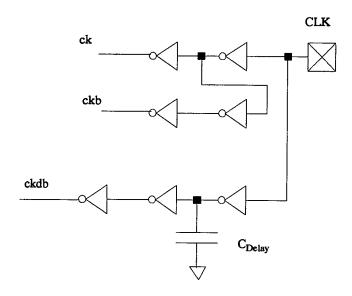

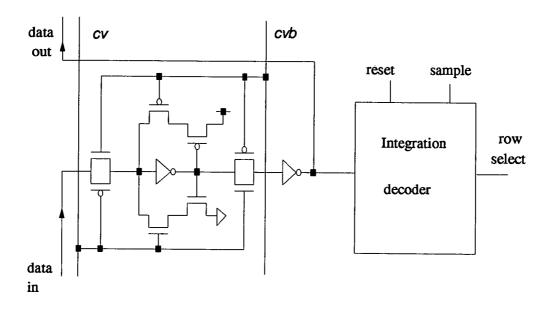

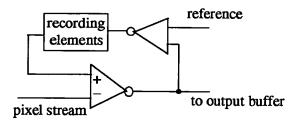

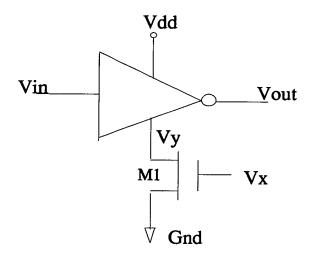

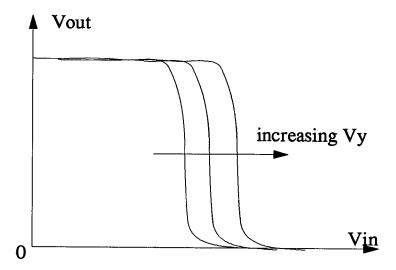

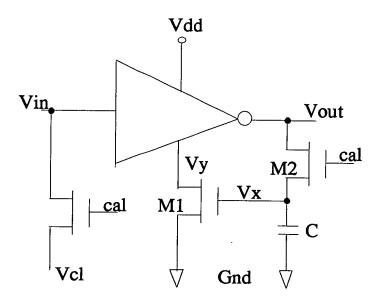

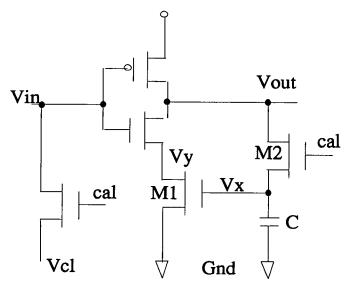

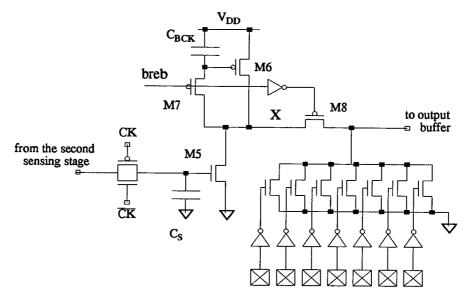

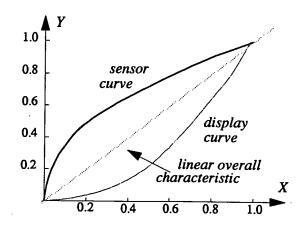

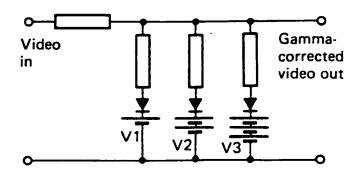

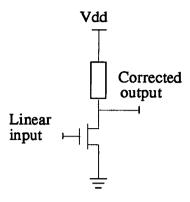

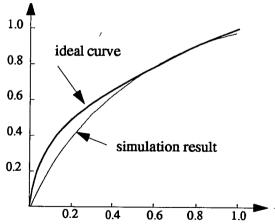

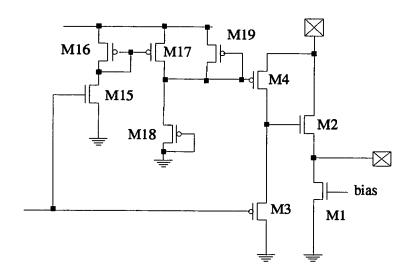

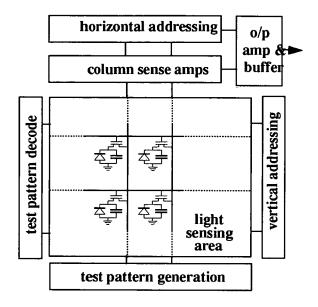

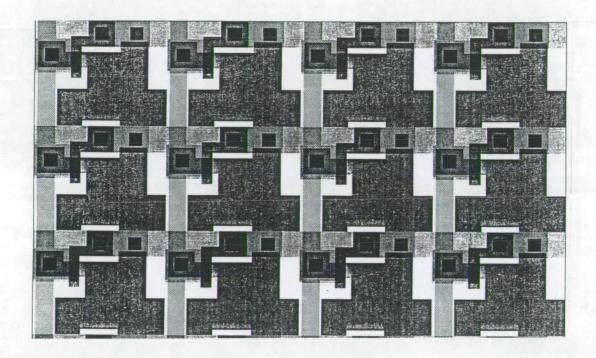

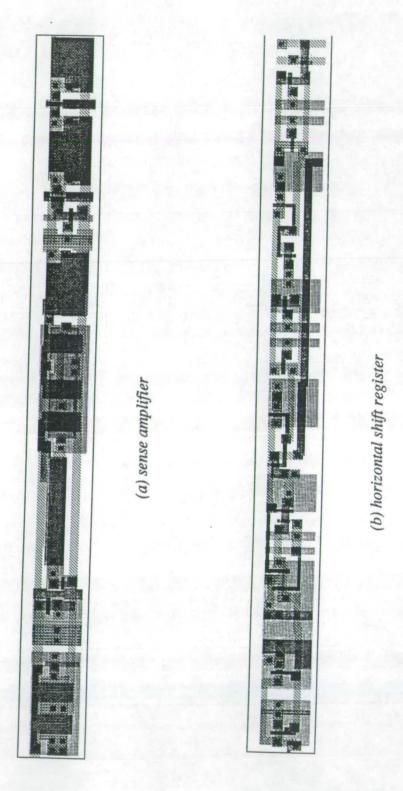

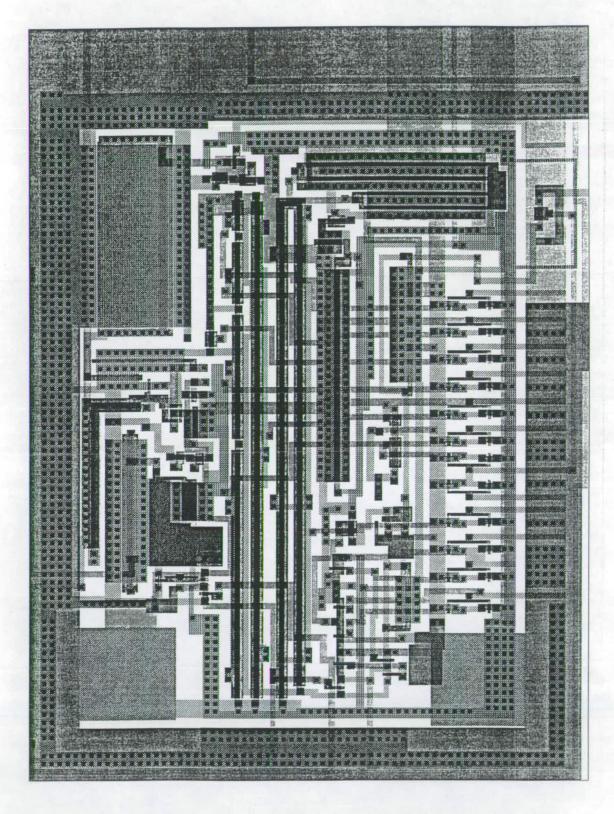

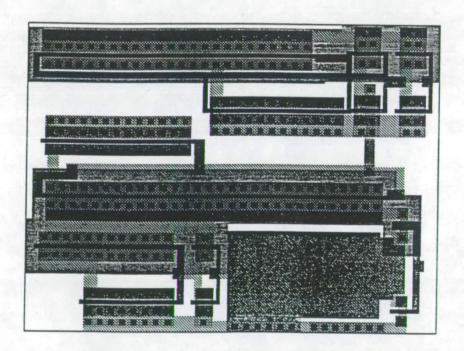

Figure 3.12 An multiplexer for formatting Composite TV output