## CONTENT ADDRESSABLE MEMORY:

## Design and usage for general purpose computing

by

## Gerard Miles Blair

#### Abstract

This thesis considers a Content Addressable Memory (CAM), from its MOS VLSI circuit design and successful fabrication, to its inclusion in a novel computer architecture. The design has a bit-serial, word-parallel configuration, implemented by semi-static shift registers, with multiple tags which also provide for freespace designation and retrieval. The contention through multiple responders is resolved using novel dynamic circuitry. The basic CAM design is enhanced with a natural fault tolerance and a scheme for hierarchical decomposition leading to a practical proposal for wafer scale The potential impact of Content Addressability, both in software engineering and in system design, is discussed in terms of its affinity to common abstract data types. After examining previous attempts to render innovative hardware accessible to the general programmer, the thesis develops a full programming environment for the CAM component within a novel variation to the von Neumann architecture which can be programmed through a tractable set of extensions to conventional high level language syntax.

## CONTENT ADDRESSABLE MEMORY:

Design and usage for general purpose computing

by

Gerard Miles Blair

A thesis submitted to the Faculty of Science,

University of Edinburgh, for the degree of

Doctor of Philosophy.

Department of Electrical Engineering

1986

## Declaration of Originality:

The material contained herein was researched and composed entirely by myself in the Department of Electrical Engineering, University of Edinburgh between October 1983 and July 1986.

## Acknowledgements:

It is with pleasure, however, that I acknowledge the encouragement and guidance of my supervisors Dr Peter Denyer and Dr Gordon Brebner, and the assistance and conversation of the members of the Integrated Systems Group especially Dr David Renshaw and Dr William Blackley. I am also grateful to the staff of the Edinburgh Microfabrication Facility for accommodating my requests so readily.

Finally I wish to thank my Amy for understanding those evenings I spent with her only rival: the computer.

# Ad Majorem Dei Gloriam

## **CONTENTS**

| 1 BACKGROUND AND MOTIVATION                   | 1   |

|-----------------------------------------------|-----|

| To begin at the beginning                     | 1   |

| Content Addressable Memory History            | 4   |

| CAM as a Software tool                        | 11  |

| 2 COMPONENT DESIGN                            | 22  |

| Design Criteria                               | 22  |

| The Abstraction                               | 24  |

| Fundamental Organization                      | 27  |

| The Addressing Circuitry                      |     |

| Control Circuitry                             | 36  |

| Resultant Structure                           | 43  |

| Fault Tolerance                               | 45  |

| Look Ahead                                    | 49  |

| Expansion                                     | 51  |

| 3 PROTOTYPE REALIZATION                       | 60  |

| Computer Aided Design and Testing             |     |

| Test criteria                                 |     |

| Actual testing                                |     |

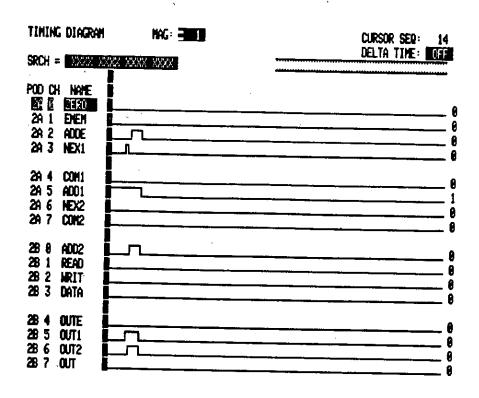

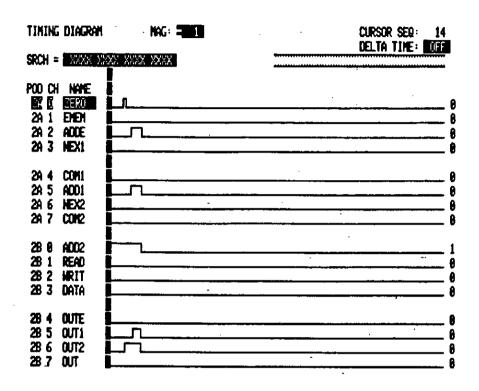

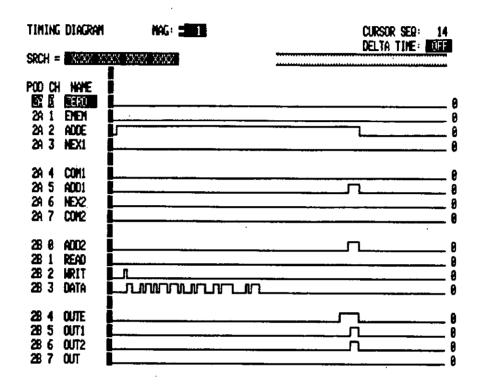

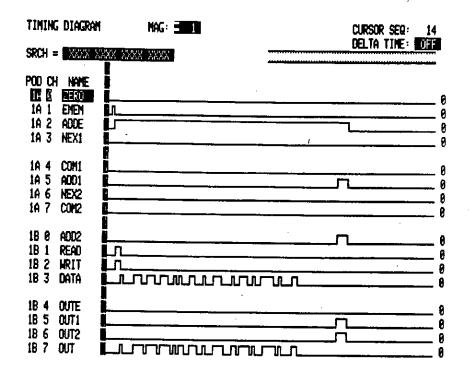

| DAS output                                    |     |

| 4 COMPONENT CHARACTERISTICS                   | 83  |

| CAM Hardware Operations                       | 83  |

| A Software Development                        | 89  |

| System Design                                 | 92  |

| Associons                                     | 96  |

| Assessment                                    | 99  |

| 5 PROGRAMMING LANGUAGES AND COMPUTER HARDWARE | 100 |

| Introduction                                  | 100 |

| Programming Languages for Computer Hardware   | 104 |

| VLSI Hardware for Programming Languages       | 112 |

| 6 THE CONTEXT FOR LANGUAGE DESIGN     | 118 |

|---------------------------------------|-----|

| Triplet Machine Architecture          | 118 |

| An Abstract Computational Form        | 129 |

|                                       |     |

| 7 HIGH LEVEL LANGUAGE DESIGN          | 136 |

| Strategy                              | 136 |

| Methodology                           | 137 |

| Bag names                             | 140 |

| Basic Operations                      | 141 |

| Scope and iterations                  |     |

| Removal of CAM words                  | 146 |

| Field specification                   |     |

| The type 'cword'                      |     |

| An Example                            |     |

| 8 CONCLUDING REMARKS                  | 160 |

| · · · · · · · · · · · · · · · · · · · | ¥00 |

| REFERENCES                            | 162 |

•

.

## Chapter 1

## **BACKGROUND AND MOTIVATION**

This is a project on Content Addressable Memory (CAM). It considers a minimal component for the storage and retrieval of data according to the results of a masked comparison, and in this context examines Content Addressability across a wide spectrum of computing: from transistor level hardware, through computer architectures, to programming language development. It details a development of the question: what if we alter the computer's mode of addressing?

## 1.1 To begin at the beginning

In the "First Draft of a Report on the EDVAC"[1] in 1945, von Neumann delimited five parts of "the functioning of the contemplated device": central arithmetical, central control, memory, and input and output with the outside recording medium. Of the "memory part" he wrote: "While it appeared, that various parts of this memory have to perform functions which differ somewhat in their nature and considerably in their purpose, it is nevertheless tempting to treat the entire memory as one organ, and to have its parts even as interchangeable as possible". Subsequently, developers have indeed yielded to this temptation. The successors of EDVAC have all realized memory as fixed length binary storage locations which are addressed by their physical position; despite von Neumann's early flirtation with the neural studies of Pitts and MacCulloch. By 1946 the idea of a memory hierarchy was established[2], in 1949 the Manchester University group conceived of the index modification of addresses which lead to the virtual memory

concept, and in 1958 the stack was invented by Barton. These contributions are early examples of software abstractions over the memory realization: abstractions which have lead to the "conventional" programming languages of today. They have ensured, by their successful development on the EDVAC model, that the singular nature of the "memory part" has remained unchallenged within the von Neumann architecture.

The architecture itself, however, is much criticized. With the potential offered by the increasing complexity of Integrated Circuits, Computer Architects have used distributed processing to distance themselves from the von Neuman model – however, little consideration has been given to modest changes in architectural design. Specific problems have quite rightly received specific architectural solutions, but the development of general computing machines is still dominated by refinements to von Neumann's EDVAC. Alternatives such as dataflow and reduction machines are promising but as yet unproven, and these too retain the established addressing mode for the "memory part". Separate processors were developed in the 1950's to handle input and output so freeing the "central control part" from the most fundamental operations, co-processors, pipelined and finally hardwired special purpose arithmetic units have enhanced the "central arithmetical part" (culminating in "super computers" such as the Cray series) – but the model remains the same.

From EDVAC onwards, memory has been addressed by a "memory location number". An alternative is to address memory by content: to direct words according to what they have become, rather than where they were placed. This project investigates that alternative.

The motivation for this topic stems from the observation that Content Addressability would:

assist software development by providing a new medium for the design of data structures and algorithms

and through its affinity with certain data types

provide a general component to facilitate system design for innovative computer

architectures and programming languages.

To corroborate this observation, this thesis sets out to describe the design of a suitable CAM component and to prescribe its inclusion in an example, full programming language environment. This approach was adopted because it is the author's belief that a component can only be correctly designed in the context of a parallel development of its projected environment. In this case, that philosophy dictates the development of a full programming environment which provides access to the CAM component in its role as a medium for software engineering.

The example considers the CAM in an enhancement to the von Neumann model: the "memory part" is altered. We could consider replacing the RAM with a CAM, and simulating the desirable RAM features using the CAM; however, we will consider instead an architecture which includes both modes of addressing implemented by their respective memory components. We will consider a general purpose computer architecture in which the central control interacts with both a RAM and a CAM, and we will call it the CAM-CPU-RAM Triplet model. With both types of memory available, the software engineer can choose the more efficient medium for the implementation of a data type. The questions we will consider are: the design of a CAM, the characterization of a CAM, the Triplet architectural organization, and the development of programming languages which render the CAM accessible to the general programmer.

This chapter continues with an historical survey of CAMs and an examination of the application of content addressability to basic computer programming. Chapters 2 and 3 consider the development of a VLSI design from a minimal specification, through the design, fabrication and testing of two prototype components, to a proposal for a natural extension into a wafer scale design. Chapter 4 considers the characteristics and possible role of the resulting component. In chapter 5, we look at the relationship between innovations in hardware and software in general, to discern how each has developed to accommodate the other, and so seek to establish guide lines to facilitate the development the full programming environment for the CAM component. We attempt, in chapter 6, to characterize the CAM in the context of the *Triplet* architecture and then as a computational abstraction — so that chapter 7 can demonstrate that these perspectives may be practically combined by a high level programming language.

## 1.2 Content Addressable Memory History

This section presents a brief review of content addressable memories and current MOS realizations; more comprehensive reviews can be found in Parhami[3] and Kohonen[4].

### 1.2.1 What is CAM?

Content Addressable Memory consists of storage locations divided into words which are addressed, and so directed, according to the results of a masked comparison. This operation is performed by a comparison between a specified comparand and each word in memory over those bits which correspond to the masked bits in a specified mask word. Thus an address is defined by a comparand and a mask word, and an address defines zero of more words in memory. In general the comparison may be made

according to a variety of relations: equality, inequality, greater-than, less-than, etc..

Elsewhere the term Content Addressable Memory is used to include a variety of SIMD processors and even "neural" networks: this thesis restricts itself to the design and use of a memory device. The stage at which a memory with distributed logic becomes a processor is, however, difficult to specify. This stems from the development of CAM in the context of logic distribution among the memory elements, in which comparison is seen as the simplest logic in a scheme which can include word specific ALU functions and inter-word communications — this has lead to a variety of Content Addressable Parallel Processors[5], including Batcher's Massive Parallel Processor[6] which was designed for image processing at NASA. We will consider only the hardware design and usage which is necessary to the address operation itself and exclude devices with additional local processing and communications; this rules out the various array processors with CAM capability, and also content driven special purpose hardware such as hardwired concurrent bubble sorts[7].

The only established use of CAM in commercial computing systems is in the implementation of virtual memory, first developed in the IBM system 360 mainframe series. The technique is to maintain a memory hierarchy whereby the sections (or pages) of memory which are currently being used by the programme are loaded into a faster (more expensive) forward memory device (or cache), and the words are accessed there rather than in the slower (cheaper) secondary storage. To provide a mapping to the memory locations in the cache, a content addressable store is maintained which maps the page address to a cache offset if that page is already present. This CAM realization was possible since the required component need perform only a limited set of operations, and need not be large since the cache address space is limited by the cost of the cache itself.

## 1.2.2 Categories and distinctive features

Even restricted to purely memory devices, CAMs offer a wide variety of possible architectures and operations. The fundamental categorization reflects the degree of parallelism inherent in the logic distribution within the memory store; other distinctions arise from the different solutions to common problems.

#### Parallelism

Content Addressable Memory requires that a comparison operation be performed on every stored word in memory, and the various CAM designs may be usefully categorized by the degree of parallelism used in this operation. The first examples can be found in multi-track disc access systems such as CASSM[8] and RAP[9]. These systems were seen as data base subsystems to the main computer and were generally supported by considerable local data base processing. The idea is that comparison and access logic is associated with long serial tracks of memory, and the design is geared to fast serial processing of specific operations. The parallelism stems from the simultaneous use of several disc tracks, and the cost of serial processing is offset by the 'tuned' design of hardware logic and choice of technology. Modern proposals include memories in CCD shift registers, bubble memories, magneto-optics, and holographs.

Integrated circuit CAMs differ in that the comparison and memory logic are both implemented in the same technology, and thus are designed with one of the four possible degrees of parallelism according to whether the words and/or bits are compared serially or in parallel. The complexity of the matching logic can vary from the implementation of a simple masked comparison to a range of boolean operations.

Full parallelism is the extreme view achieved by distributing processing logic to each memory bit cell. In these systems the comparison is performed simultaneously at each bit with the mask, comparand and control signals being distributed to each word.

The use of a bit-serial word-parallel configuration has the advantage that the cell size can be reduced to a storage element, with the comparison logic removed to one location for each word. A bit-parallel word-serial configuration similarly allows for a reduced bit cell size but, with a sequential processing of the memory words, it is severely limited in its access time by the size of memory. A fully serial configuration is even less attractive for the same reason.

## Location addressing

Some CAM designs include the concept of location address producing a hybrid memory[10] where the portion of memory over which a comparison is to be performed is limited by the degree to which the physical location has been specified. This allows the memory to function in either location or content address mode. One advantage is with pointer driven programming systems, such as LISP, where the dual address mode allows the existence of pointers to a specific cell location to be deduced from a comparison over the pointer fields[11].

There are three consequences of the hybrid architecture:

- The memory space may be divided into different regions by the software. This allows different search spaces to be defined by the physical division of the memory rather than by a conceptual division through the dedication of a CAM field (thus saving memory space).

- The result of a comparison may be given as a physical address by which the word is subsequently directed, rather than using controlled access according to a tag store.

The word-length of CAM may be increased if the comparison can be performed

with reference to the result of the previous comparison on a physically adjacent

word[12].

As an example of the latter, consider doubling the word length: firstly set all the result tags on each of the even addressed words in memory and compare with the first half of the new virtual word resetting the tag on a mismatch, then transfer that result into the next physically adjacent result store and perform the comparison on each odd addressed word with the second half of the virtual word – the tags which remain set indicate the address of the second half of each matching virtual word.

## Multiple Responders

The main difference between addressing by content rather than by location is that in CAM the number of responders to any address is not fixed but rather is a function of the state of the computation. Thus there may be zero, one, or many words which are addressed as a result of a comparison. For some operations, such as write and remove, this can be used to advantage by performing the operation on all responders in parallel. With the read operation in word parallel architectures, however, this raises the problem of contention on the output data bus.

The problem is avoided in some CAM designs which are targeted at a specific system whose operation ensures that there is no more than one match for any valid address. For example, when using CAM as a fast lookup of cache memory addresses, an entry is only made if that page address was not found by the proceeding comparison. In such systems there is no multiple response, and therefore no contention. In general, however, some logic must be devoted to resolving this conflict. There are essentially two options: access one responder only, or access each responder in turn.

In the former case, some system must be devised whereby other responders can be accessed as the result of performing the search again. This can be implemented by setting a marker either in the word or in the hardware which prevents the already accessed word from responding again.

In the latter case, the scheme requires some form of local storage of the results of the comparison, and signal switching so that the 'first' responder is affected by subsequent memory operations. There must also be a mechanism whereby the 'first' responder can be passed to allow the next responder to be directed. A major problem is the delay in the propagation of the addressing signal through the memory. With a large number of words, this becomes prohibitive. There are two approached to this problem: the use of look ahead circuitry on the same principles as the Manchester Carry Chain Adder, or the use of a modular hierarchy with logic to prevent the addressing signal from descending along paths which lead to modules without a responding word.

#### Garbage collection

Free locations pose two problems: how is free space addressed, and how is assigned space returned to free space? The identification of empty words has received scant attention in previous designs. There are two approaches: unused words are identified by a bit field in the memory word by which they can be addressed (by its content), or alternatively some systems keep all the assigned words together. A recent scheme[13] was designed in which the (one if any) matching word is immediately read and removed. The memory system maintains a "depth of memory" pointer to which new words are written, and when a word is removed, the word at the bottom of memory is rewritten into the space vacated, and the pointer is reset accordingly. A similar design has been implemented[14] in which the memory is constructed as a bit parallel stack. Words are entered by pushing them onto the stack, and vacated space is filled by shifting upwards those words further down.

## 1.2.3 Previous MOS Designs

The majority of proposals for MOS CAMs have been fully parallel so as to take full advantage of the processing potential of the technology, despite the restriction on component capacity imposed by the large resulting bit size. Bit-serial word-parallel designs have been proposed mostly for the implementation of more complicated functions such as ordered retrieval[15].

The standard CAM cell design for a fully parallel system is based on a static RAM latch with additional circuitry for performing the masked comparison (for example, see Lea[16]). Commonly the comparison is performed by discharging a precharged word reference line through transistors associated with the mismatching bits. This design leads to a large cell size which was quickly recognized as a severe limitation. The use of dynamic storage nodes was seen as a partial solution to this problem. A four transistor bit cell was proposed by Mundy[17] which is based upon two storage nodes for each bit cell, and which allows for the storage of a "don't care" state in the actual memory cell as well as the normal use of an external mask. The design requires three distinct voltage levels, and the use of current flow is suggested as an analogue counter of the number of responding words. A half cell of the same design was proposed by Lea[18] as a memory which matches against only one logical value. A recent paper by Wade and Sodini[19] modified the Mundy cell by cross-coupling the bit lines to preserve better noise margins.

#### 1.3 CAM as a Software tool

Let us now return to the observation that CAM will provide a new medium for software engineering. Conventional software techniques have evolved to counter the difficulties which have been found in computing with the von Neumann model. We will apply the topics from a standard text on computer algorithms and data structures, to a memory system which is addressable by its content; and so present CAM alternatives to techniques which "underpin much of today's computer programming"[20]. The CAM is used to implement common abstract data types in a manner which is usually simpler, more efficient, and often more powerful than the RAM equivalent.

We will leave the development of a precise terminology of CAM programming until chapter 6, and use instead the model of a number of fixed length words which are each conceptually subdivided into named fields. We will assume that the memory is 'sufficiently' large for the following abstract overview of CAM applications, and that the configuration is word-parallel so that the timing of a comparison operation is independent of the number of words in memory. The 'value' of a memory field may be considered as data or as address or as both. The use of field identifiers is similar to that in record structures of conventional RAM programming except that CAM words are addressed by the values of (some of) its fields rather than by the pointer identifiers which address records.

In the following, the CAM word will be referred to in terms of the field names associated with a particular problem. Thus

[field1 | field2 | field3 ]

depicts the CAM word as having three fields. However, this does not imply that only one convention may be extant in memory, since

[ convention\_field | field1 | field2 | field3 ]

could be a software convention for supporting several sub-conventions simultaneously.

This flexibility is, of course, bought only by smaller virtual word sizes since some bits must be dedicated to the convention field.

## 1.3.1 RAM simulation

We start with the trivial observation that a CAM may simulate a RAM by the convention:

[ address | data ]

RAM is normally accessed by passing the address through hardware decoders; CAM distributes the 'address', and 'decoding' is achieved by a comparison over the address field. The obvious disadvantage is the use of storage area to describe the address, but this inefficiency is in no way daunting since we should not expect CAM to surpass RAM direct through mimicry; the virtues of CAM will be found in exploiting its own characteristics.

A RAM may simulate a CAM, but the free specification of the mask word necessitates that the simulation is performed by a sequential search through all the memory words. Thus, although the CAM-CPU model is "computationally equivalent" to the RAM-CPU model, the RAM's simulation of CAM is of a higher time complexity – this disparity is due to the parallel processing inherent in the CAM model.

The value of the address field need not, however, be equivalent to a RAM memory location number. Instead it could be a representation of the variable's identifier from the high level programming language. To allocate storage in RAM, a compiler must translate a programme's variable names into numerical location addresses. A Fortran compiler makes all allocations before run time, while that of a recursive language must

specify storage in terms of an offset from a 'data frame base' address. If the memory were a CAM, the compiler could use the variable names from the high level language to generate symbolic addresses whose uniqueness, in any one procedure, is ensured by the programme semantics. By adding a procedure identifier to each symbolic address, a Fortran compiler could perform all allocation without counting storage cells. If a recursion level field were also included:

[ unique\_identifier | level | data ]

the compiler of a recursive language could perform allocation without stack maintenance.

This is a possible approach for implementing the conventional languages on a Triplet machine, but the use of CAM alters some of the basic features of the programming environment which have directed their evolution. For instance, block structured scope rules reflect the attributes of the stack which provides structure to RAM usage; but with CAM the access to "non-local" variables can be no more expensive than to local ones. It thus seems likely that new 'CAM orientated' languages would evolve to reflect the new features which CAM provides.

So far we have seen that anything RAM can do, CAM can do also, and that CAM can do certain things better than RAM. We proceed by considering CAM-specific implementations of some basic abstract data types. In general, the point is not that CAM surpasses RAM, but rather that CAM provides a comparable implementation with distinctive features which a software programmer might wish to exploit; however, in some cases the data type's correspondence to the CAM itself affords a superior implementation in CAM than in RAM.

## 1.3.2 Vectors

Vectors do not fit into the unique naming scheme since the word to be addressed is normally determined during run time and so the compiler can not assign a unique name before hand. However, the same calculation of an "offset" value, as found with RAM, could be employed in a CAM implementation. The scheme:

[identifier | offset | data ]

implements the vector data type, with slightly different features from the RAM implementation. For instance, this representation would accommodate the storage of large 'sparse' matrices, where only the (few) significant entries are stored. A RAM implementation of this technique requires the overheads of a pointer mesh, the CAM implementation is the same as for 'full' matrices.

A vector has two basic properties: an ordering of its elements (implicit in an order relation on the offset domain), and also an association under the common vector name. If order is required it can be provided explicitly: in the offset field. The number of elements so ordered is limited not by the vector size but only by the range of the assigned field — repeat entries are also possible. An ordering in CAM can be found in the necessarily sequential storage and reading of addressed words, but this is a feature of the hardware and not of the CAM model — any use made of this ordering must be described in terms of the specific design and thus is not valid testimony in support the general CAM.

However, vectors are sometimes used in programming for association alone, and the offset only assists in programmer maintained RAM allocation — in such cases the offset field is redundant in CAM: association follows directly under a common identifier.

## 1.3.3 Lists, Trees and Queues

Lists and trees are traditionally built out of pointer structures where the pointer is the 'address' of a topologically adjacent word, and like vectors they too provide both order and association. By replacing the address with a CAM word identifier, these structures may be realized with a CAM through mimicry of the RAM technique. An implementation of lists could use the fields

[ identifier | next\_identifier | data ]

and this idea can easily be developed into tree building. A significant advantage of the CAM implementation is that 'backward chaining' is immediate without the need for extra storage space and maintenance of reverse pointers.

However, CAM has distinctive features which allow different concepts to be used in algorithmic design: the free choice of address 'names' allows the programmer to develop naming conventions so that the 'name' itself contains information. For instance, a binary tree can be specified by a binary code where the root is 1, its two branches are 10 and 11, the next level is 100, 101, 110, and 111, and so on. Similarly, queuing may be supported through a circular buffer by the data structure

[counter | data ]

where the counter field is an integer maintained with addition modulo the field's range.

#### 1.3.4 Hash tables

Deep in the folk-lore of RAM programming lurks the hash table. Even before FORTRAN, programmers needed a large table which could be quickly updated or searched for a specific entry, to assist the translation of symbolic names from assembler code; and so they devised the hash table. The implementation of the hash table in RAM

requires the permanent allocation of a large array (necessarily larger than the maximum possible number of entries), a judicious choice of 'key' calculating algorithms, and the choice of strategies to accommodate collisions involving heap storage maintenance or key recalculation. Despite these difficulties, hash tables are so widespread that some even advocate their inclusion in machine code instruction sets[21].

CAM is a hardware solution to the problem. Lookup is performed by addressing the word directly (according to any field), and update is lookup followed by writing. There is full utilization of memory with constant access times, no complicated hashing function, and no lists or incrementing of the index to handle collisions.

## 1.3.5 Graphs

A natural way to store graphs using fixed fields is according to the edges defined by their end nodes:

This is ideal for a (possibly costed) digraph, and non-directed graphs can be implemented by either recording an edge in both directions or searching both fields in the software. The most significant feature here is the closeness of this representation to its mathematical specification: there are no supporting data structures beyond the graphs actual definition.

#### 1.3.6 Sets

We will consider the implementation of sets in some detail to provide a heuristic appraisal of CAM features necessary to support an efficient implementation of this data type. With RAM memory, sets and set functions are supported using hash tables, lists,

or complex tree structures, yet a set is simply an association of its members under a common identifier. A CAM could use the data structure:

## [ set\_identifier | item ]

to provide this association, allowing a set to be addressed directly by its identifier without any supporting data structures. In considering the implementation of set functions, however, we immediately encounter memory design issues.

Consider how to implement a copy function: create a set B with the same elements as set A. This requires that the set A be addressed by a comparison operation over the set\_identifier field and each responder read (non-destructively) in turn and written to free space in memory with an updated set\_identifier. If the comparison logic is involved in designating the free space, the write can not be performed without either destroying the results of the previous comparison, or using different comparison logic. One solution would be to place the result of the first comparison (the words addressed as set A) into an external buffer, and then to write the buffer to free space after a further use of the comparison logic — this is unattractive since it requires a large amount of mostly redundant circuitry. An alternative is to make the addressing of free space independent of the comparison logic used to address set A.

Consider now the *Union* of two sets: create set C which contains all the members of sets A and B, but without repetition. This can be performed by copying set A to C and then copying to C those members of B which are not in C already (or A). To do this, there must be some method for performing a comparison on each element of B against the elements in A without affecting the comparison which is addressing B. Again one solution would be to buffer the elements of B, and the alternative is to provide logic to interrogate the members of set A which is independent of the comparison addressing B.

Assuming the second solution in both cases, the standard set functions may be implemented as follows:

**UNION(A,B,C)**:: copy A to C; while reading B, test each word for occurrence in A; if not in A, write that word to C. Timing is O(|A|+|B|).

INTERSECTION(A,B,C):: while reading A, test each word for occurrence in B; if present in B, write word to C. Timing is O(|A|).

**DIFFERENCE**(A,B,C):: while reading A, test each word for occurrence in B; if not present in B, write word to C. Timing is O(|A|).

MEMBER(x,A), MAKENULL(A), INSERT(x,A), DELETE(x,A), and FIND(x) are all obvious and performed with one addressing of memory.

The boolean EQUAL(A,B) is achieved by performing DIFFERENCE(A,B,\$) and DIFFERENCE(B,A,\$) until an assignment is made to \$, or both functions are finished. Timing is O(|A|+|B|).

The function MIN(A) returns the least member of a set where there is some ordering defined on its members. The simple CAM implementation is to address the set A and then cycle through its members performing a comparison with a 'currently minimum' value: timing is O(|A|). However, if the values are non-negative integers, the techniques mentioned in the next paragraph lead to an O(m) algorithm where m is the number of bits in the order field.

## 1.3.7 Sorting

As we have already seen, it is possible to impose an ordering on the elements of a CAM through the inclusion of an order field – however, this is effecting (through software) a property which is implicit in RAM and so is not evidence of CAM's claims over RAM for data structures which do not derive other benefits from CAM implementation. Sorting relies entirely on order and will, generally, be better implemented in RAM. However, there is a special case when the memory bits are interpreted as non-negative integers. The algorithms were described originally by Falkoff[22], and depend upon the partitioning of the binary tree inherent in the bit representation itself, through the manipulation of the comparand and the mask word. With these techniques, a sort of N values specified in a field of m bits requires time of O(Nm) – a fuller explanation appears in chapter 4.

#### 1.3.8 Algorithms

The above is an example of a CAM specific algorithm, relying on subtle manipulation of the addressing mechanism. However, we might expect algorithmic design to be affected more generally by the use of CAM.

Consider the following algorithm for the traversal of a digraph, using the edge representation above and two sets ('visited' and 'to\_do') with the associated set operations.

Procedure Traversal(start\_node)

{INSERT(start\_node, visited)

INSERT(start\_node, to\_do)

while 'to\_do' is not empty

{select\_node from 'to\_do'

DELETE(selected\_node, to\_do)

foreach edge with tail\_node = selected\_node

{if NOT MEMBER(head\_node, visited)

{INSERT(head\_node, visited)

INSERT(head\_node, to\_do)}}}

Each node of the graph is visisted once by this procedure. The set 'to\_do' is an unordered set of visited nodes adjacent to those which might not yet have been visited. The order in which the graph is traversed is unspecified. The algorithm is trivial — but, in CAM, so too is its implementation since the implicit data types map directly onto the memory architecture.

An order may be imposed on the traversal by including an index field with the node entries in the 'to\_do' set to store the value of an incremented counter, thus numbering the members of that set to form a queue. The search is then breadth\_first or depth\_first according to whether the queue is FIFO or LIFO respectively. The same queues can be found in the least time programming in RAM where depth\_first search is performed using the stack as a LIFO queue, and breadth\_first search requires explicit FIFO queue construction — but in RAM this symmetry is obscured. The CAM version hides no complex structure and needs no implicit system (stack) maintenance; the mapping from the abstract algorithm to physical memory component is more direct with CAM than with RAM.

## 1.3.9 Assessment

CAM is a useful memory design. It is capable not only of mimicking RAM but also of surpassing it in some of RAM's most popular uses. Further since current techniques assume and accommodate a RAM architecture, a CAM based programming system can be expected to promote a new approach to programming which exploits the distinctive features.

## Chapter 2

## **COMPONENT DESIGN**

This chapter considers the design of a suitable Content Addressable Memory component. After stating the design criteria, we develop from an abstract definition of the CAM component into a description of its features; this construction being sufficient rather than necessary. A circuit level realization is then advanced from a general overview to the details of a specific chip's organization. This is followed by two modifications, providing fault tolerance and an increase in operating speed, and a projection of methods by which small CAMs may be configured into a large memory component.

## 2.1 Design Criteria

From the history of previous designs and the observed requirements of common abstract data types, we now consider the criteria with which a suitable CAM component may be designed.

## 2.1.1 Minimality

In the EDVAC report[1], von Neumann exhorted that: "The device should be as simple as possible, that is, contain as few elements as possible" and this emphasis on minimal hardware is perhaps the best explanation of the model's continuing success: a simple framework allowing diverse development. The effectiveness of minimality in VLSI systems is most forcefully advocated by the RISC school of designers who

originally set out "to obtain as much performance for as little complexity as possible" [23] and produced "a single-chip CPU that rivals board level designs" [24]. With this in mind, the CAM design was kept as simple as possible — whilst remaining useful.

The aim is to produce a general purpose memory component. The approach is to refrain from including complex processing and to use only those features which are necessary to that aim. The reasoning is that the simple design is likely to be both realizable and broadly applicable, and that by proving the kernel of possible components, we will implicitly approve them all. As will be seen however, once the basic design was fixed, the resulting component was both flexible and easily ramified.

## 2.1.2 Utility

The utility criterion will be interpreted as an efficient implementation of the data structures and algorithms described in chapter 1 since these cover the fundamental aspects of software engineering practice. In section 1.3.6, we found that an efficient implementation of sets requires:

- a write\_new\_word operation.

- a boolean test which determines whether or not there is a word in memory

addressed by a specified content.

- a search\_and\_queue operation such that the queue of results is maintained whilst

either of the other two operations are executed.

This is also sufficient for the other data types considered. These are the minimal functional requirements to implement sets, but 'design' minimality is approached by reducing the number of distinct functions to be implemented. The boolean test

operation requires the same search to be made of memory as in the search\_and\_queue operation and so may be implemented by a second independent search\_and\_queue operation. These two operations must maintain their respective queues independently from each other and also from the execution of the write\_new\_word operation. The boolean test can be resolved according to the existence of words on a queue.

Having decided to include a second search\_and\_queue operation, we could proceed to include even more since the design effort involved in two may trivially be extended in more than two. However, two such operations (and an independent write\_new) are sufficient to implement sets, and also the other data structures which we have considered, and so, invoking minimality, we will settle on two as a basis for the prototype design.

#### 2.2 The Abstraction

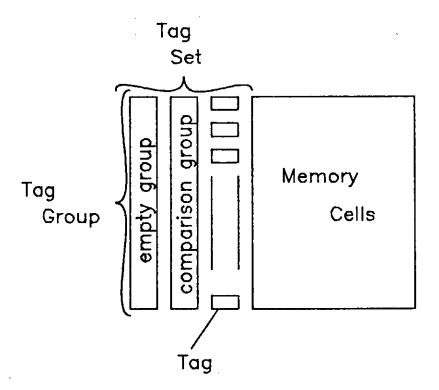

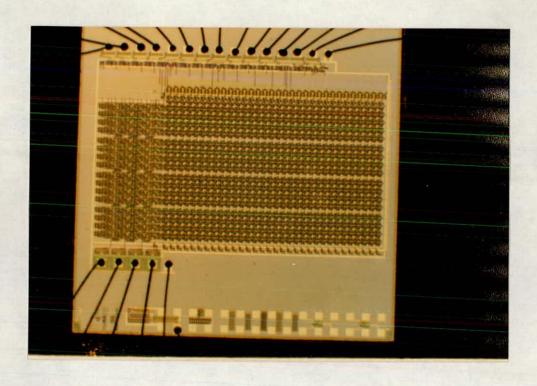

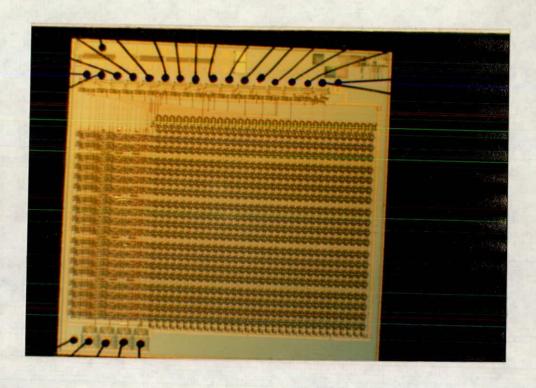

With these criteria in mind, let us develop a specification of the component's organization; the resulting floor plan is shown in figure 2.1.

- Content Addressable Memory is storage addressed according to a subset of its contents.

- To realize this concept in physical storage space, there must be a comparison between the relevant bits of each memory word and the corresponding bits of an addressing comparand, according to which the addressed (matching) words may be accessed.

Figure 2.1: the structural floor plan

- To designate which bits of a word are relevant to the address, there is a mask word whose ONE bits denote relevance, and whose ZERO bits denote irrelevance, to the comparison of the corresponding bits in the comparand and memory words.

- The results of a comparison may be stored to avoid contention from multiple responders, and to allow controlled access. This storage must be associated with the corresponding word. The storage location with each word is known as a tag. A tag is said to be active if the word is addressed by the comparand, or passive otherwise.

- If the results of n (> 1) comparisons are required together there must be n independent groups of tags: n tags associated with each word. A word is said to have a set of tags associated with it.

- A word is manipulated by addressing a tag group and thereby addressing one of the words whose tag in that group is active. Such a word is said to be currently addressed. If there is no active tag in the group, a signal is output when the group is addressed.

- Further words with active tags in the group may only be addressed by making passive the active tag, in that group, of the currently addressed word.

- A currently addressed word may be written or read.

- The concept of a tag group is extended to address empty words: those whose contents are undefined or no longer desired to be addressed by a comparison. This tag group is not available to store the results of a comparison. It is known as the empty tag group, while the other groups are comparison tag groups.

- A word which is empty can not have active tags in its comparison tag set: in any set, an active empty tag implies that all the comparison tags are passive.

- The CAM is initialized, or emptied (re-initialized), by making all tags in the empty group active. The content of empty CAM words is undefined.

- When a word in memory is written, its contents are defined and the empty tag in its tag set becomes passive.

- A currently addressed word may be made undefined by making its empty tag

active this necessarily makes its comparand tags passive.

## 2.3 Fundamental Organization

This section presents the overall design decisions which determined the general organization of the hardware component.

## 2.3.1 Bit-serial Word-parallel Architecture

The operations described above occur only at word level: the addressing mechanism defines words, and so the addressing logic need only be distributed to the word level. With the comparison logic at word (rather than at bit) level, the bits of a word must be fed through the comparison logic sequentially and the operation may be performed in parallel on all words in memory.

By moving the logic from the bit to the word level, a smaller memory cell design is possible but the comparison can only be performed one bit at a time. This is a trade-off between the speed of operations and the size of the associated circuitry. Other advantages in making the chip bit-serial are that the data may be distributed to the words

as it arrives at the chip without local buffering, and that the (potentially large) number of pins is reduced.

### 2.3.2 Rotating Word Model

The comparison operation occurs at all words simultaneously as the whole of memory is rotated through a word cycle. I/O operations require the rotation of only one word, but by using the addressing mechanism as a communication switch between the data buses and the addressed memory word, the bulk memory rotation may still occur.

This leads to the design model of circulating memory words which may be implemented either as actually rotating storage locations: using shift registers, or by cyclically addressing a static configuration: using, for instance, bit slice addressing with standard RAM-like circuitry. The latter may eventually lead to higher bit densities with dynamic storage but this is not necessarily advantageous because the word pitch is also limited by the word dense addressing and comparison mechanism which requires static logic and so seems to set the lower limit.

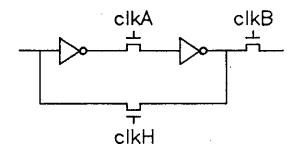

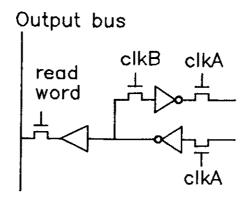

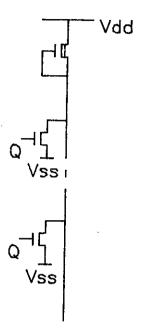

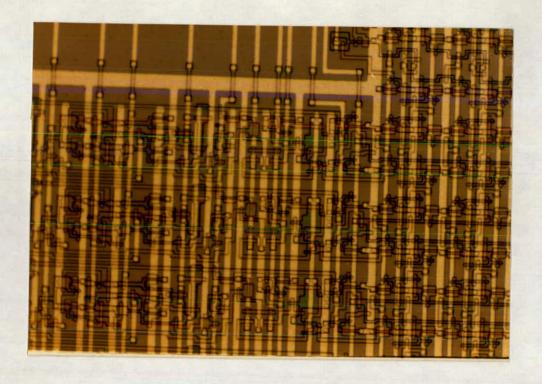

For a practical realization, semi-static shift registers were used (see figure 2.2). With clock H off, clocks A and B form a dynamic shift register configuration and allow the memory word to rotate; with clocks A and H on and clock B off, the bits are statically held. This has a speed advantage over RAM in that there is no delay associated with charging a word line since the current bit is always in the cell adjacent to the switching logic. Also the shift registers lead to a very compact layout.

Figure 2.2: a semi-static shift register bit cell

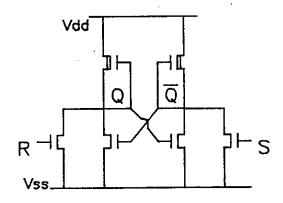

Figure 2.3: the latch realization of a tag

## 2.4 The Addressing Circuitry

We now consider specific circuitry for the realization of the abstract model. The major feature is the addressing mechanism which is to be based upon the value of tags associated with each word of memory; the problem is how to cope with multiple words matching on a comparison operation.

### 2.4.1 The Tag

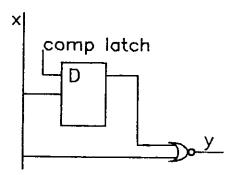

The tag storage of a comparison's result is realized as a reset latch (figure 2.3). The value of the latch corresponds to Q: the latch is active if Q is high, and passive if  $\overline{Q}$  is high. The value is switched by pulling the high arm to ground through the corresponding pass transistors: R or S. The value is changed either by commands acting on a single addressed word, or by the comparison and CAM initialization operations.

## 2.4.2 The Comparison

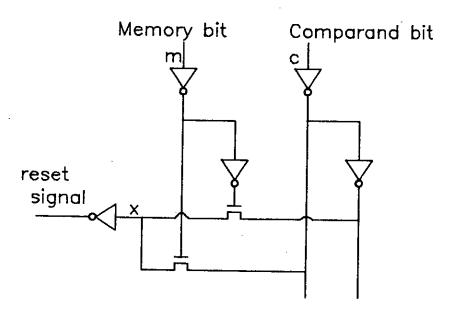

The primary function of the tag is to record the result of a comparison: the tag is active after a comparison if the corresponding word matches the comparand at all the masked bits. This may be translated into a practical algorithm as the tag becomes passive after a masked mismatch.

The bit-serial comparison operation begins by making all the tags in a group active. The masking of the comparison is performed by clocking the reset circuitry with a signal which occurs if and only if the corresponding mask bit is set. The reset signal at each memory word is generated from the comparand and word bits according to the logic in figure 2.4. The signal is high for a mismatch and low for a match, for instance: if m is high, the node x is connected to the arm with the value of c making x high if c matches

Figure 2.4: the comparison logic

m and low if not. To perform the comparison, the comparand bits and their compliments are broadcast sequentially as the memory words are rotated and the reset signal is clocked in the selected comparison tag group for those bits which are masked. The tag becomes passive on the first masked mismatch; that is, the tag is active at the end of the sequence if and only if there was no masked mismatch to reset it to passive.

#### 2.4.3 Addressing Logic

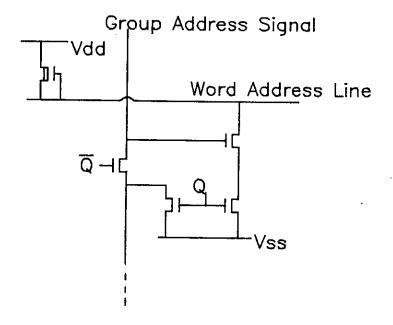

A tag group consists of active and passive tags. When a tag group is addressed, one word with an active tag in that group is currently addressed. This is realized by using the latch values to pass a signal through the latches until the first active tag is reached. The circuitry at each word is shown in figure 2.5. The tag group is addressed by raising the group address signal line. If the tag is passive,  $\overline{Q}$  is high and the pass transistor is on allowing the signal to propagate down the line. If the tag is active, this pass transistor is off and the isolated lower section of the group address line is pulled low since Q is high.

The word associated with the first active tag is then currently addressed as the word address line is pulled low through the two transistors gated by the latch value Q and the group address signal line. The word address line may be pulled low by any of the tag groups. Some operations on the word are performed by signals which affect only a word whose word address line is low: by design there is only one such word for each addressed tag group, and in normal usage only one tag group will be addressed at a time.

Addressing another word in that group is achieved by making the selected tag passive and then allowing the group address signal to propagate to the next active tag. This operation is initiated by a signal rather than automatically since there are various

Figure 2.5: the addressing logic

(Group address signal assisted by restoring buffers every four stages)

operations which may be performed on the addressed word. This scheme is effectively daisy-chain addressing where each site is polled in succession until one responds, and the polling continues when the responding site has finished the required operations.

If there are no active tags in the group, the signal emerges at the end of the addressing line and is output from the chip.

#### 2.4.4 Non-cascading signals

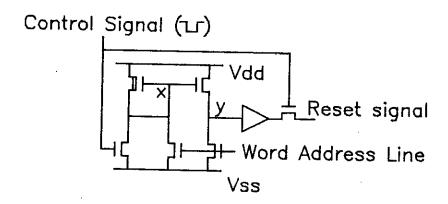

If the tag, by which a word is currently addressed, is made passive the group addressing signal propagates to the next active tag. There is here a potential race hazard since the signal to make the tag passive must be removed before the next word becomes currently addressed or its tag also will be made passive. The dynamic circuitry shown in figure 2.6 prevents this cascading. It was verified both by SPICE simulation and by fabrication as a small test structure before inclusion in the full design.

The control signal is generally high. If the word is not currently addressed the word address line is also high, making node x low, and connecting node y to Vss. A pulse on the control signal does not effect the node values. If the word address line then becomes low, y is isolated and discharged. If the control signal is subsequently lowered, node x rises and node y is connected to Vdd. The pass transistor beyond the buffer is off, since the control signal is low, and so the reset signal still remains low. When the control signal is raised, this pass transistor becomes on and the reset signal rises. Also the node x becomes low and node y is isolated but charged, dynamically maintaining the high input to the buffer. The circuit is self timing in that the reset signal remains high until the tag is made passive which in turn raises the word address line so discharging node y and lowering the reset signal. Thus, the system returns to the initial configuration.

Figure 2.6: the non-cascading unit

#### 2.4.5 The empty tag group

The idea of addressing the words in memory according to the setting of an associated tag is extended to overcome the problems of identifying free-space and garbage collection. A solution with similar features has been published independently by Ogura[25].

The empty tag operates without reference to a comparison operation. The whole group is made active by a signal to initialize the memory and an empty tag must be made passive when a word is written to its associated memory word. Thus the write operation is used to make passive the empty tag of the currently addressed word. An empty tag may be made active again to allow a word to be made unaddressable and so effectively erased, thus allowing explicit garbage collection to be performed through the control signals.

If a word's empty tag is active, the memory bits contain undefined data. To ensure that this does not lead to an undefined word being addressed through a (random) matching comparison, the comparison tags are constantly reset by the value of the empty tag. Thus the comparison tags of an empty word are never active.

#### 2.5 Control Circuitry

To design an actual component requires the specification of the overall control logic. The following is one possible realization: the design is built using standard digital circuits and the two phase non-overlapping clock normally associated with NMOS shift registers. Other technologies or other realizations of the rotating word model might require different control techniques.

#### 2.5.1 Internal Control Summary

Each comparison tag group has the control lines:

Reset: making all the tags active as the first part of the comparison operation.

Mask: clocks the reset of all the tags according to the value of the mask word during the comparison.

Next: resets the tag of the currently addressed word to passive using the non-cascading control unit.

Address: addresses the tag group.

The empty tag group has the control lines:

Empty: making all the empty tags active.

**Defined:** a non-cascading unit signal which is completed at the end of a write operation.

Remove: making the empty tag of the currently addressed word active and so undefining that word.

Address: addresses the tag group.

And the remaining general functions are:

Read: to output the contents of the currently addressed word.

Write: to input data into the currently addressed word.

#### 2.5.2 Clock and input organization

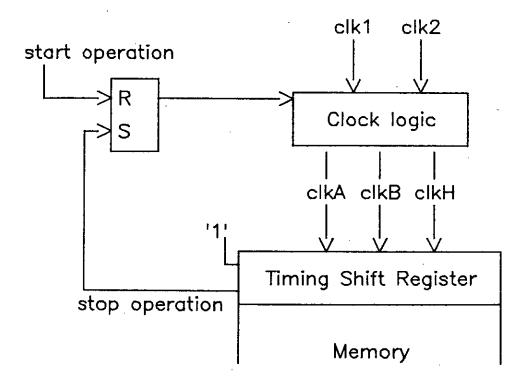

The chip is driven by a two phase non-overlapping clock: clk1 and clk2. The memory word is held static until an operation on the memory bits is initiated so avoiding a word synchronization delay and (with some technologies) also saving power. The three clock signals for the memory cells (clkA, clkB and clkH) are controlled according to the value of an RS flip-flop (see figure 2.7). After start operation, clkA and clkB follow clk1 and clk2 respectively and clkH is low thus driving the shift register memory words; after stop operation, clkA and clkH are high and clkB is low to hold the data values in static latch configuration.

The timing of an operation is achieved by a special shift register driven by the same clocks as the memory cells. When the memory is static, this register is initialized to zero on all its cells; when the memory is rotated, a one is propagated through the register and becomes the *stop operation* signal when the word cycle is complete. The logic is self timing in that the signal causes the clock control RS flipflop to reset and the clocks to alter accordingly which thus initializes the special shift register and so removes the *stop operation* signal.

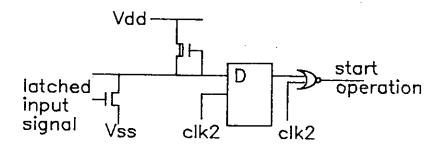

All input signals to the chip, including the data buses, are passed through D-flipflops clocked by clk1. Whatever the appropriate value of the internal signal, the input signal is designed to be significant on being raised to high. The start operation signals is designed to allow the longest possible time for the resetting of the clock control logic and the discharging of the clock lines which are held high in the static phase, before the remaining internal clock (clkB) rises. Thus the stop operation signal is generated on the falling edge of clk2 — figure 2.8 shows the logic design. As an input

Figure 2.7: the clock organization

Figure 2.8: the start operation signal

signal is latched on clk1, the latch signal which is correspondingly raised is used to discharge a signal line whose value is subsequently clocked into a D-flipflop according to clk2. The value of this delay element can not be used directly as the start operation signal since this would cause clkB to begin to charge while clkA and clkH were still high; thus the signal is input, with clk2, into a NOR gate so that the resulting start operation signal is only raised when clk2 is lowered. This scheme implies that the memory rotation commences on the clock cycle following the initiating control signal.

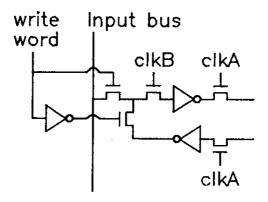

The read and write operations are performed by switching the data buses into the addressed memory word through pass transistors activated by a control signal gated with the word address line. Figures 2.9 and 2.10 show the read and write interfaces respectively. The control signal is sent by lowering the control line which is combined with the word address line through a NOR gate, and so only the currently addressed word is affected. The signal must be held throughout the operation, and this is achieved by driving the internal read or write control signal from an RS-flipflop which is set at the beginning of the operation and reset by the *stop operation* signal. Recall that the transfer of data from one cell to the next occurs on the clk2/B signal. The input data signal thus has from the beginning of clk1 to (nearly) the ending of clkB to become fully established. The output signal is not clocked on the chip and therefore has a full clock period to establish itself on the output bus, starting at clkB or at the setting of the RS-flipflop after clkA on the first bit.

The comparison operation is initialized through the mask data input, by the setting of an internal RS-flipflop – subsequent inputs represent the mask which is gated with clkB to form the clock signal for the comparison latch reset logic. The RS-flipflop is again reset by the *stop operation* signal.

Figure 2.9: the read interface

Figure 2.10: the write interface

The defined signal is taken from the write signal together with a non-cascading unit. Since the effect of the non-cascading unit occurs when the signal returns to high, the compliment of the internal write signal is used in making passive the empty tag of the currently addressed word. Thus the word remains addressed throughout the operation and becomes defined at the end, as is required.

There is also an *empty memory* signal which ensures that the RS-flipflops are initialized appropriately, by sending the *stop operation* signal, and that all the empty tags are active.

#### 2.6 Resultant Structure

This completes the basic design of the minimal CAM component and the remainder of the chapter considers some practical enhancements which render it a viable computing component. The basic design leads to a simple but powerful configuration (see figure 2.11). On each word operation, all memory words rotate together. The details such as the number of tag groups and the memory word realization are independent from each other and so can be easily changed within the design.

At each word the current bit is boosted and so available to the output bus and the word specific comparison logic. The comparison operation is effectively a conditioned reset in a tag group and this occurs by sequentially providing the comparand on the comparison bus and the mask data on the selected tag group(s). The word address line spans the addressing logic of each word and may be lowered by any of the tag groups, to gate the word addressed operations. Input and Output are achieved by listening to or breaking into the rotating bits on the addressed word.

Figure 2.11: the basic word structure

#### 2.7 Fault Tolerance

The size of an Intergrated Circuit is a compromise between the designers desire to fit as much logic as possible onto a contiguous area of silicon and the manufactures inability to prevent defects. The system designer seeks to minimize the delay in propagating signals, which is smaller within an IC than between them. On the other hand, the manufacturer is constrained by the yield of his product: a circuit is defective if it overlaps with a defective region on the wafer and the probability of this occurring increases exponentially with the size of the circuit.

#### 2.7.1 Memory Defects

Defects in the wafer are of two major types: regional and point defects. The former results from processing effects where either the variation of the functional parameters has gone beyond the tolerance limits, or there are misalignments due to shrinkage or expansion of the wafer during fabrication. These global effects can only be minimized by either improved fabrication techniques or by more tolerant layout design rules.

Point defects are small localized faults which commonly are caused either by dust or other particles reaching the wafer or the lithography masks, or by isolated spikes or pinholes in the deposited films. These defects may be countered if the effected logic can be isolated from the operation of the IC. This is achieved in RAMs by incorporating redundancy[26]: extra word and bit lines are included into the design to replace lines which are found to be defective. The replacement of good for bad lines is achieved by blowing fuses in the addressing circuitry either by using lasers or by applying a high voltage across a high resistance. This post-manufacturing yield enhancement has made large RAM chips more feasible.

#### 2.7.2 CAM Fault Tolerance

The possibility of including fault tolerance into CAM has often been mentioned in the literature, but little has been written concerning actual implementation. In RAM the addressing logic has to be changed so that the entire address space corresponds to functioning memory; in CAM the problem is more simply to eliminate defective words. This may be done by making the words unaddressable. In the same way that an active empty tag renders the comparison tags unaddressable by a hardwired reset, the signal from a further latch can be used to make the address tags passive.

The testing of a memory word is performed by checking that the word recalled is the same as the word stored. CAM already has the distributed logic for performing this test. If the same word is stored at every memory location and a comparison performed on the entire word, the comparison tag of each correctly recalled word will be active. Thus the value of the comparison latches may be used to set a latch which will eliminate defective words.

The fault recording logic at each word is shown in figure 2.12: the corresponding word is eliminated when the line y is high. The input to the D-flipflop is taken from the setting of the tag in one of the comparison groups: high if the tag is active, and low if the tag is passive implying that the comparison had failed. When x is high, the word is addressable as normal since the output y of the NOR gate is low. When x becomes low, the D-flipflop retains the value of its current input and y is subsequently held at that value's compliment.

The test pattern depends upon the realization of the memory. For shift registers it is sufficient to show that any sequence of bits with at least one 0 and one 1 can be stored and recalled. The test sequence is thus:

Figure 2.12: the fault tolerance logic

raise x line

empty memory

address empty tag group

while memory not full write pattern

perform comparison pattern

lower x line.

Only correctly functioning shift register words will be addressable so long as the x line is maintained low.

If the memory is realized using bit-sliced RAM cells, it is necessary to show that each cell can store and recall both 1 and 0. The test sequence is performed as above with an arbitrary pattern and then followed by:

empty memory

address empty tag group

while memory not full write compliment of pattern

perform comparison compliment of pattern

raise line x

lower line x.

Words which failed the second comparison will be removed as the D-flipflop is "clocked" by the x line. Words which failed the first part of the test will remain unaddressable since their comparison tags will necessarily be passive at the end of the second comparison.

This method of fault elimination has the advantage that it is effective against faults which develop after the component has been released by the manufacturer, it has the disadvantage that the test must be performed each time the component is powered up. However if the component is deemed to be fully functional, the test does not have to be performed when the component is used; an input may be tied to maintain the x line high and the component will operate as if there were no fault tolerance logic.

### 2.8 Look Ahead

The main limitation on operating speed is the time delay associated with the purely sequential nature of daisy-chain addressing. The signal is delayed both by the pass transistors and by the necessary booster gates. The system using the component is delayed for the time it takes for the signal to pass completely around the chain, which is proportional to the number of words. To allow for system growth, there must be a mechanism for avoiding some of this delay.

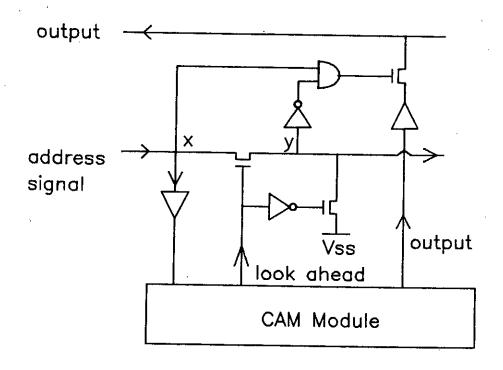

A simple circuit enhancement allows a lookahead signal which provides the output of the daisy-chain address signal without the inherent delay: it is high if and only if there are no active tags. The modification is to include a single metal line running parallel to the addressing line, which is pulled high by a depletion transistor unless pulled low by the output of one of the tags (see figure 2.13). Thus it can be determined if all the tags are passive without charging up the group addressing line.

This enhancement is very significant in the context of the functional operation of the CAM. Any addressed operation on memory must be performed by charging the address line and proceeding if, and only if, there is a word addressed. With lookahead, this decision may be taken without the addressing delay which, therefore, does not affect cases where there are no active tags (no words addressed by the comparison). In cases where there are active tags, the delay is reduced since the addressing may be initiated while the lookahead output is being interrogated by the controlling processor.

Figure 2.13: the look-ahead line

### 2.9 Expansion

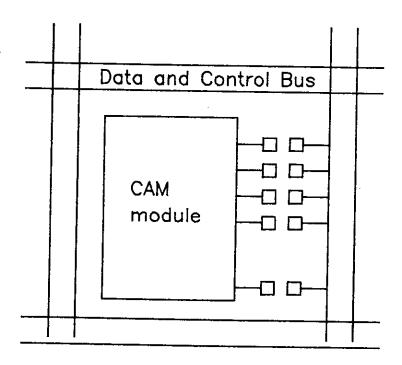

The limitations on IC size necessitate that large CAMs are built from modules of small CAMs. This applies both to bread-boarding and to producing large ICs containing small units which may be isolated if defective.

### 2.9.1 Monolithic

The first approach is to combine several components in a series forming a single extended address bus by connecting the address outputs of each component to the corresponding inputs of the next. The address signal thus travels along the extended daisy-chain with the same organization as that of a single component, with more words than are practically possible due to the IC size constraints, but with additional off-chip delays.

The disadvantages of this scheme are that lookahead (and the associated delay savings) involves two extra ports and a ripple delay, and that the addressing delay is directly proportional to the number of words in the monolith which could seriously impede the performance of large memory systems.

## 2.9.2 Hierarchical

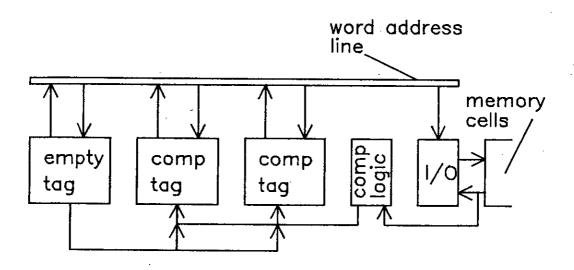

A better approach can be designed with a hierarchical address bus by using the lookahead output to bypass subtrees with no active tags. The CAM has three categories of signals:

All but one type of input signals can be broadcast to the whole system. Those

which affect all words can obviously be broadcast. Those which affect only the

currently addressed word can also be broadcast since the signal is gated with the

word address line and the daisy-chain group addressing ensures that there is only one such word per group.

- The group address signals follow a sequential path through the memory words.

- The output from a memory word when it is read.

The approach is to broadcast all the signals for which it is possible, use lookahead to minimize the actual path of the daisy-chain address signal, and to use the address signal to switch the output of a memory word along a path of the same minimized length. The logic for the addressing and switching is shown in figure 2.14. When the addressing signal reaches x, it enters the module. If the look ahead signal is high (implying that there are no active tags), the signal continues through the pass transistor without delay; if the lookahead is low, the address signal is stopped and the address line beyond the pass transistor is pulled low. The output switch uses the fact that output can only occur if there is a currently addressed word within the module, which would imply that x is high and y is low; otherwise the module is isolated from the output line.

By including a lookahead line with this level of the addressing logic, it is possible to build modules of modules. Worst case delays are then a function of the sum of the path lengths for each level of the hierarchy, and not of the full size of memory.

### 2.9.3 Bread Boarding

The hierarchical approach may be applied to bread board assembly by designing a switching chip using the above logic. For each memory module attached to it, there are two pads for each group: address input and lookahead, a further pad for each comparison group: mask input, and one pad for the output signal. If any of these modules are unattached, the switch will continue to function correctly if the lookahead

Figure 2.14: the switching logic

pad is tied high. The remaining pads on the switching chip form the address input, and data and lookahead output, of the resultant memory module which therefore has the same interface as its own submodules. Thus modules composed by a switching chip may themselves be connected into larger modules by the same switching chip design.

### 2.9.4 Wafer Scale Integration

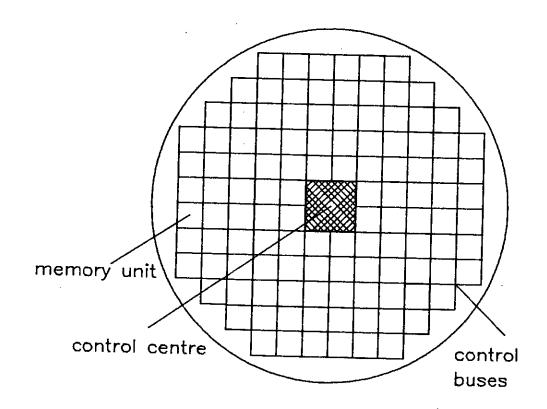

Rather than bread boarding small packages, let us now consider the production of a large memory system on a contiguous wafer. The main advantages of wafer scale integration are the higher speeds, reliability and packing densities which are achieved by eliminating the need for packaging "chip size" components individually. The problem is that the defects arising in the manufacturing process limit the size of integrated circuits which could be produced with any reasonable yield. The solution is to design wafer scale components with small independent and testable sub-circuits which can be configured into a working system after testing. The configuration can be effected by either eliminating or establishing interconnections, by the use of lasers, fuses, further fabrication layers, or test and routing.

A wafer scale CAM has been proposed using test and routing[27]. This scheme routes a signal path incrementally through the good components by testing each potential addition to the path through the "known to be good" signal path that is already established. The disadvantage is that the signal path establishes a monolithic expansion of the CAM component and hence a long address delay — let us consider a different approach which will allow us to retain the hierarchical expansion.

Discretionary wiring dates from the late '60s. The technique is to test the components on a wafer and to use the results to define a further (unique) mask set for a final layer of metal to form appropriate interconnections between functioning units[28].

This scheme is now more attractive due to the development of E-beam direct write on wafers, and higher reliability in the fabrication of the final layers.

Content Addressable Memory in general is a suitable candidate for wafer scale integration because:

- There is no critical dimension in producing a working component. A general wafer scale system must have at least one correctly functioning circuit for each of its sub-units, a RAM must have sufficient words to fill the full address space; a CAM functions with whatever logic it can.

- The number of pins for the wafer is the same as for a single memory unit and does not follow the observed (so called "Rent's Law") relationship of increasing in proportion to the number of gates raised to the power of 0.6.

The CAM design of this thesis is particularly suitable because:

- Most signals are distributed on global buses.

- The expansion logic produces a modular hierarchy to distribute the address line and switch the output bus.

- The fault tolerance in the memory units allows the automatic isolation of defective words, and hence a larger practical size of sub-circuit.

- The modular design allows for isolation of a defective sub-circuit. This is achieved by tying the look ahead output of that module to high during the testing.

The only critical area is the control centre.

The distribution network of signals (see figure 2.15) requires at least a process with two metal layers because of signal delays. Global signals are broadcast over the network, and the addressing and output signals are laid along the same paths. The actual decomposition of the modules depends upon the optimal numbers of modules to be included in each level of the hierarchy which in turn depends upon timing equations using the parameters of the chosen fabrication process. The control centre may be best placed at the actual centre of the wafer since this is the region least affected by regional processing defects.

The elimination of defective submodules requires the testing and possible modification of the fabricated wafer. The functioning of each independent unit must be verified, and the lookahead input to each switch connected by discretionary wiring either to the lookahead output of its subtree (if the subtree is correct) or to logical high (if defective). The salient features are that the proposed wafer consists of several units (the CAMs and the switches) which can operate independently, and that a defective unit may be isolated by tying the lookahead nodes of its communication bus to the power rail. If the units where designed with a probe pad on either side of a break in each connection to the control bus (see figure 2.16), an automatic tester could be used to verify each unit since they are each unconnected to the remainder of the circuits. If the unit functions correctly, the corresponding probe pads are connected by the further layer of metal; if the unit is defective, the lookahead inputs to the communications bus are connected to the power rail. The fabrication of this metal layer would require only a comparatively 'course' process, since it need only cross a purely substrate terrain between the two probe pads, and there is no significant advantage in using narrow tracks. A similar verification and isolation could be performed at each level of the switching network.

Figure 2.15: the signal distribution logic

Figure 2.16: a discretionary wiring scheme

## 2.9.5 Silicon Wafer Packaging

While CAM is particularly suited, in comparison to other logic, to wafer scale integration there remain problems. The metal tracks of standard processes have a significant RC delay and power consumption when laid over such a network; the testing and commissioning stage requires the production of an extra, unique mask for each wafer or a unique programming for E-beam direct writing.

A middle, practical course is to produce the distribution network on an independent silicon wafer to which tested CAM units may be bonded. This allows the fabrication of the network using thick films for increased interconnection speed and low power consumption[29] without limiting the choice of technology for the memory units. The expansion logic is laid down with the network and the memory and control units are fabricated separately. Test structures may be included on the bonding wafer to check for regional defects at the bonding sites. The yield on the bonding wafer will be very high since there is very little active logic and the metal tracks have negligible sensitivity to point defects.

## Chapter 3

#### PROTOTYPE REALIZATION