# APPLICATION OF ANALOGUE CHARGE-COUPLED DEVICES TO ADAPTIVE SIGNAL PROCESSING

by

#### C.F.N. Cowan

Thesis submitted for the degree of Doctor of Philosophy to the Faculty of Science,

University of Edinburgh

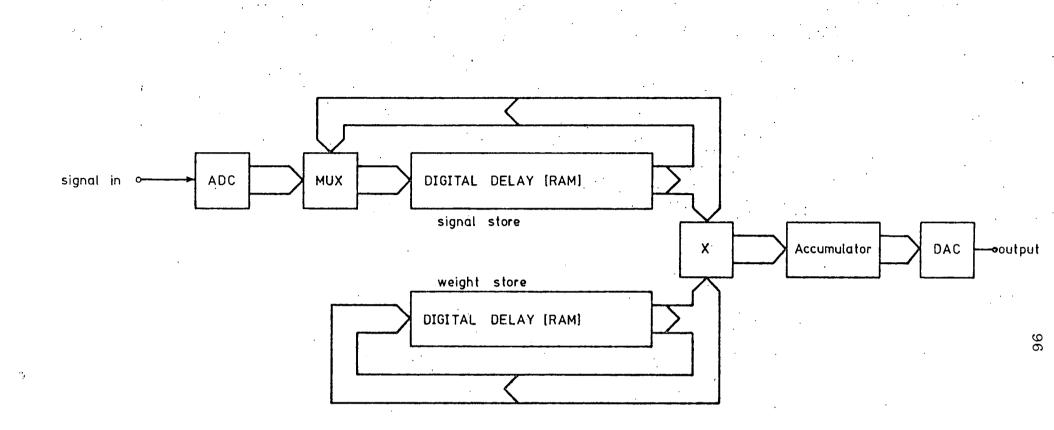

### DECLARATION OF ORIGINALITY

This thesis, composed entirely by myself reports work conducted in the Department of Electrical Engineering at the University of Edinburgh exclusively by myself, with the exception of the section mentioned below.

The result presented in section 6.6 is reproduced by kind permission of Dr. J.W. Arthur and H.M.M. Reekie.

signed

C.F.N. Cowan date: 21 July 1980

#### ACKNOWLEDGEMENTS

The author would like to express his gratitude for the supervision of Dr. J. Mavor; his help and encouragement have been invaluable during the course of this work.

Thanks are also due to many friends and colleagues in the Department of Electrical Engineering and the Wolfson Microelectronics Institute, in particular Dr. J.W. Arthur and Mr. P.B. Denyer. I would also like to mention the help supplied by J.F. Dickson and J.N. Gooding of Plessey Research Ltd, the Northern Ireland Dept. of Education for their financial help and Hewlett Packard Ltd., South Queensferry, who supplied a telephone line simulator for use in the experiments described here.

Finally, thanks are due to my wife and family for their patience and constant support over the last three years.

(iv)

(v)

## CONTENTS

|                            |                                | Pa  | ge no. |

|----------------------------|--------------------------------|-----|--------|

| Title page                 |                                |     | (i)    |

| Abstract                   | •                              | • • | (ii)   |

| Declaration of originality |                                | (   | iii)   |

| Acknowledgeme              | nts                            |     | (iv)   |

| Contents                   |                                | • . | (v)    |

| List of abbre              | viations                       | ( v | iii)   |

| · · · ·                    |                                |     |        |

| CHAPTER 1 IN               | TRODUCTION                     |     | 1      |

| 1.1 Si                     | gnal processing with charge-   |     |        |

| co                         | oupled devices                 |     | 2      |

| 1.2 La                     | yout of thesis                 |     | 10     |

| • • •                      |                                |     |        |

| CHAPTER 2 CC               | D CIRCUITS                     |     | 13     |

| 2.1 Ch                     | arge transport mechanism       |     | 13     |

| 2.2 Si                     | gnal input techniques          |     | 21     |

| 2.3 Ta                     | pped delay line implementation |     | 24     |

| 2.4 SP                     | S delay line implementation    |     | 28     |

| 2.5 Pr                     | ogrammable transversal filter  |     |        |

| im                         | plementation                   |     | 33     |

| · ·                        |                                |     |        |

| CHAPTER 3 OP               | EN LOOP SYSTEMS                |     | 43     |

| 3.1 Li                     | near regression analyser       |     | 43     |

| 3.1.1                      | Theoretical analysis           |     | 46     |

| 3.1.2                      | System implementation          |     | 50     |

| 3.1.3                      | Experimental results           |     | 58     |

| 3.1.4                      | Summary                        |     | 64     |

|       | 3.2          | Adaptive noise cancellation in an    |                 |

|-------|--------------|--------------------------------------|-----------------|

|       |              | SPS delay line                       | 65              |

|       | 3.2          | 2.1 System implementation            | <sub>.</sub> 66 |

|       | 3.2          | 2.2 Experimental results             | 69              |

|       | 3.3          | Summary                              | 72              |

|       |              |                                      |                 |

| CHAPT | rer 4        | CLOSED LOOP SYSTEMS                  | 74              |

|       | 4.1          | General adaptive systems             | 74              |

| -     | 4.2          | Adaptive algorithms                  | 78              |

|       | 4.3          | Adaptive filter applications         | 79              |

|       | ·            |                                      |                 |

| CHAPT | <u>rer 5</u> | SYSTEM IMPLEMENTATIONS               | 89              |

|       | 5.1          | Variants of the LMS adaption         |                 |

|       |              | algorithm                            | 89              |

|       | 5.2          | Adaptive system architectures        | 92              |

|       | 5.3          | Experimental realisations            | 100             |

|       | 5.3          | 3.1 64-point adaptive filter         |                 |

|       |              | prototype                            | 102             |

|       | 5.3          | 3.2 64-point digital adaptive filter |                 |

|       |              | prototype                            | 107             |

|       | 5.4          | Adaptive recursive filters           | 111             |

|       |              | ·                                    |                 |

| CHAPT | TER 6        | ADAPTIVE ERROR CORRECTION            | 116             |

|       | 6.1          | Analogue system errors               | 116             |

|       | 6.2          | Charge transfer efficiency effects   | 117             |

| ·-    | 6.3          | Reference signal decay               | 120             |

|       | 6.4          | Multiplier errors                    | 121             |

| •         |                                       | Page no. |

|-----------|---------------------------------------|----------|

| 6.5       | General error correction mechanism    | 123      |

| 6.6       | Experimental verification of error    |          |

|           | correction                            | 124      |

|           |                                       |          |

| CHAPTER 7 | EXPERIMENTAL RESULTS                  | 131      |

| 7.1       | Convergence time characteristics      | . 131    |

| 7.2       | Cancellation characteristics          | 138      |

| 7.3       | Matched and inverse filtering         | 143      |

| 7.        | 3.1 Matched filtering characteristics | s 143    |

| 7.        | 3.2 Inverse filtering characteristics | s 150    |

| 7.4       | Self-tuning filter characteristics    | 159      |

| 7.5       | Summary                               | 161      |

| · • •     |                                       |          |

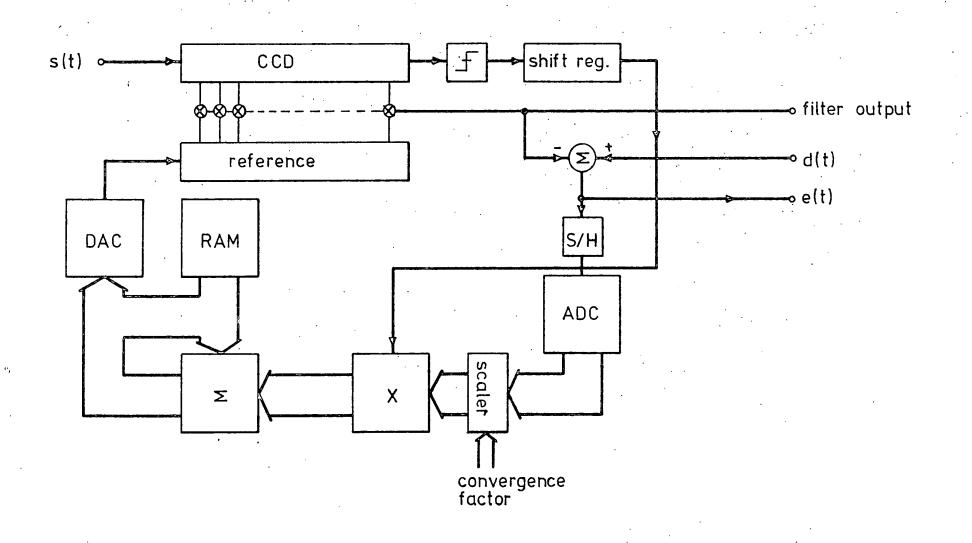

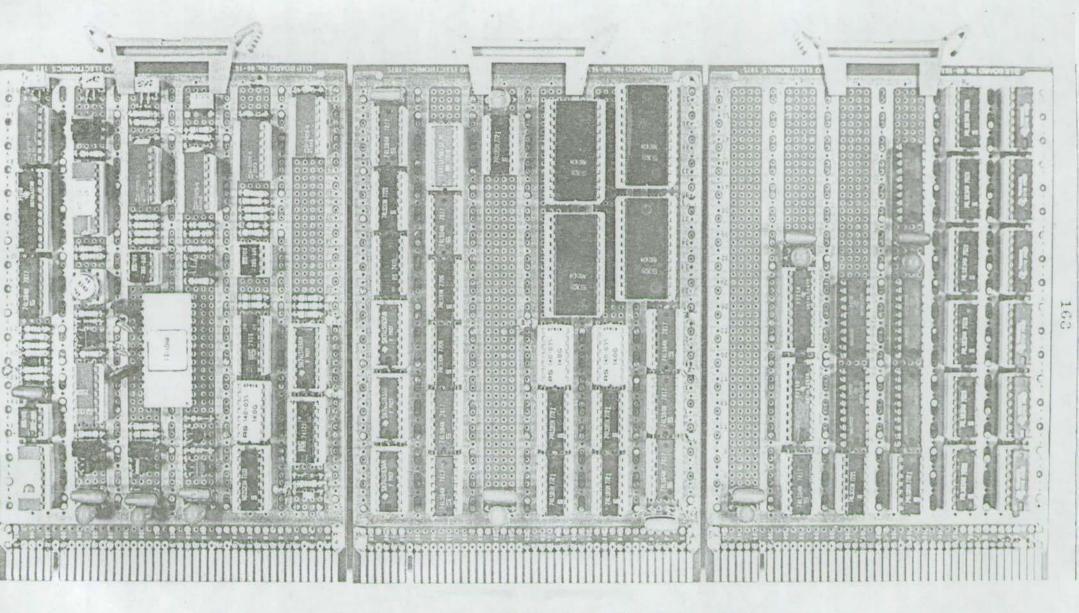

| CHAPTER 8 | 256-POINT ADAPTIVE FILTER             | 162      |

| 8.1       | 256-point system implementation       | 163      |

| 8.2 | Convergence characteristics        | 167 |

|-----|------------------------------------|-----|

| 8.3 | Cancellation characteristics       | 171 |

| 8.4 | Matched and inverse filter results | 175 |

| 8.5 | Summary                            | 181 |

CHAPTER 9 CONCLUSIONS 183

| REFERENCES      |                 |        |              | 190 |

|-----------------|-----------------|--------|--------------|-----|

| APPENDIX A 256  | -point adaptive | filter | construction | 199 |

| APPENDIX B Rele | evant publicati | ons    |              | 208 |

(vii)

(viii)

### LIST OF ABBREVIATIONS

| ADC  | Analogue to Digital Converter     |

|------|-----------------------------------|

| agc  | automatic gain control            |

| ARAM | Analogue Random Access Memory     |

| BBD  | Bucket Brigade Device             |

| CCD  | Charge Coupled Device             |

| CMOS | Complementary Metal Oxide Silicon |

| CTD  | Charge Transfer Device            |

| CZT  | Chirp-Z Transform                 |

| DAC  | Digital to Analogue Converter     |

| DCT  | Discrete Cosine Transform         |

| FFT  | Fast Fourier Transform            |

| FIR  | Finite Impulse Response           |

| FM   | Frequency Modulation              |

| LCD  | Liquid Crystal Display            |

| LED  | Light Emitting Diode              |

| LSB  | Least Significant Bit             |

| LSI  | Large Scale Integration           |

| MOS  | Metal Oxide Semiconductor         |

| MSB  | Most Significant Bit              |

| SNR  | Signal to Noise Ratio             |

| prf  | pulse repetition frequency        |

| PT   | Prime Transform                   |

| PTF  | Programmable Transversal Filter   |

| RAM  | Random Access Memory              |

| rms  | root mean square                  |

| ROM  | Read Only Memory                  |

| SAW  | Surface Acoustic Wave        |

|------|------------------------------|

| SPS  | Serial Parallel Serial       |

| TDL  | Tapped Delay Line            |

| TDI  | Time Delay and Integrate     |

| TTL  | Transistor Transistor Logic  |

| VLSI | Very Large Scale Integration |

- ----

· · ·

. ~

#### CHAPTER 1: INTRODUCTION

A key element in many signal processing applications is one which is capable of delaying signals in a controlled manner. Until the invention of the charge-coupled device  $(CCD)^{(1,2)}$  in 1970 the circuit techniques used to do this were digital shift registers, or bucket-brigade devices (BBD) in the analogue domain. The CCD provided an efficient, compact technique for the production of analogue signal delays on a single integrated circuit which opened the way to effective analogue implementations of convolvers and correlators at baseband frequencies.

It is the use of analogue CCD convolutional processors applied to analogue signal processing which is addressed in this thesis. The particular type of systems considered here may be generally grouped under the heading of adaptive signal processing<sup>(3)</sup> modules since, in all the experimental systems described in this thesis, the general aim is to make use of particular measured statistical properties of an incoming signal in order to determine some form of filtering or decision function. This class of system has been chosen because of the possibility of enhanced performance<sup>(4)</sup> which could be available when the filtering characteristics are not fixed (ie variable or self-varying).

#### 1.1 Signal processing with charge-coupled devices

One of the most important characteristics of the CCD is its formation as a straightforward analogue delay line. In this form it finds uses in such diverse areas as  $audio^{(5)}$  and  $video^{(6)}$  delay lines and simple noise integrators<sup>(7)</sup> and comb filters.

The applicability of this type of delay is strictly limited unless the signal may be accessed at a number of points along the delay line and then weighted and summed to form a so-called transversal filter structure. Two types of transversal filter have been previously advocated which will be divided into the two groups of committed and uncommitted filtering.

(1) Committed filtering: Here the filtering function is fixed at the processing stage. The commonest type of committed filtering function is the split-gate filter<sup>(8)</sup>, in which the individual weights are implemented by physically dividing the CCD transfer electrode into two portions. The ratio of the lengths of the two portions determines the tap weight for that particular electrode. The signal under each electrode is extracted (non-destructively) and weighted by a current sensing technique<sup>(9)</sup> and the summation of the weighted signal values is then simply achieved by using a common summing node and current-to-voltage conversion. This is one of the commonest types of fixed filter implementation

using CCD's and some typical applications for these devices will be considered later.

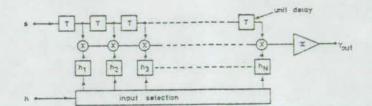

(2) Uncommitted filtering: In this case the filter architecture used is again that of the transversal filter but with the difference that the filter weighting function is not specified at the time of device manufacture, ie the filter is programmable. Three basic structures have been used to implement this approach and these structures are illustrated in figure 1.1.

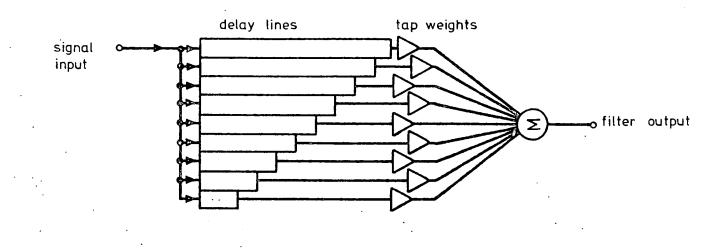

(a) the 'organ-pipe' structure (10): This structure basically uses a number of CCD delay lines of different lengths which have a common input node. The delay line outputs then yield values of the input signal at various delay times. These outputs may then be weighted using a resistor summing network or an array of multipliers (cf. figure 1.1(a)). This structure is unwieldy due to repetition of identical delay paths many times in the overall filter.

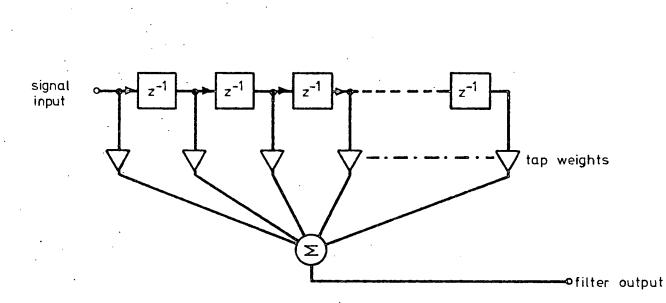

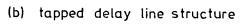

(b) the tapped delay line<sup>(11)</sup> structure (TDL): In this structure only one delay line is used and the signals are made available for weighting by the use of non-destructive tapping<sup>(12)</sup> of the delay line which replicates the signal under an electrode without destroying the charge packet. The resulting signal samples may again be weighted by resistive summing networks or by the use of multipliers (cf. figure 1.1(b)). This structure does have the disadvantage of requiring extra silicon area to accommodate the tapping amplifiers

(a) organ-pipe structure

(c) time delay and integrate structure

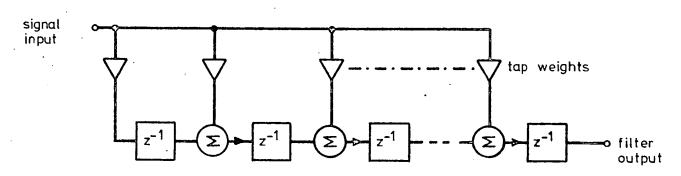

Figure 1.1 : Block diagrams of three alternative schemes for programmable transversal filter implementation.

and the resulting tapped delay lines do tend to have slower clocking rates than the other two alternatives. This structure does however make more efficient use of silicon area than the 'organ-pipe' structure.

(c) time delay and integrate  $(TDI)^{(13)}$ : The TDI structure works by reversing the order of operations considered in the previous two cases. All inputs are taken as being common but signal weighting is done before entry into the CCD. Each input then occurs at successive delay points with the charge packet from the previous stage being added in one clock cycle later so that the weighted input signals progressively accumulate (or integrate) with the filter result being available on the final transfer electrode (cf. figure 1.1(c)). This structure does have the requirement of a progressive increase in size of transfer electrodes due to the accumulating size of the charge packets and this yields the characteristic triangular shape of the TDI. This particular characteristic provides an upper limit on the length (ie. the time-bandwidth product) of the TDI.

Although the TDI and 'organ-pipe' structures have faster clocking rates (due to the fact that they have no tapping points in their structure) than the TDL structure they are not so suitable for long filters since the TDL size increases by a factor of 1/N for each successive filter stage added (N = the total number of filter stages) whereas the TDI and 'organ-pipe' size increases by a

factor of 2/N and the overall area is proportional to  $N^2/2$  against the TDL area which is proportional to N. It is therefore clear that the TDL structure is more suited to long (high time-bandwidth product) filters with relatively low bandwidths as it makes more economical use of silicon area than either of the above alternatives.

Two distinct types of uncommitted filter may be identified and these have been termed as field programmable<sup>(10)</sup> filters. The field programmable filter is typified by a TDL with a resistive weighting function, where the filter characteristics may only be changed by altering the resistor values, this type of system is then directly comparable to a split-gate filter where the weights are readily programmed by the user. The real-time programmable filter may be defined as a filter in which the tap weights may be altered at a rate similar to the clock rate of the CCD. This is done by weighting with multipliers using coefficients stored on some external circuit (RAM or ROM usually). Many possible schemes have been proposed for this type of structure (which will be referred to as a programmable transversal filter or PTF) which use either analogue multipliers (14, 15) or multiplying digital to analogue converters<sup>(16)</sup> (MDAC's) to perform the weighting function.

A great deal of work has been done on the filtering structures just described with particular reference to

their application in a number of areas.

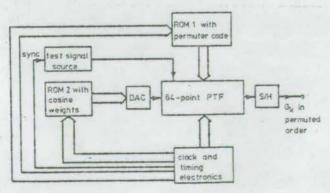

(1) Spectrum analysis: The CCD has made a significant contribution in the area of spectrum analysis, particularly to the implementation of the chirp-z transform (CZT) using split-gate chirp filters<sup>(17)</sup>. Efforts have also been made to implement the prime transform algorithm<sup>(18)</sup> and more recently PTFs have been applied to yield a very efficient realisation of the discrete cosine transform<sup>(19)</sup> (DCT).

(2) Frequency filtering: This is an area almost entirely dominated by the split-gate CCD filter which has been used to implement anti-aliasing filters<sup>(20)</sup> and band-pass filters for use in spectrum analyser filter banks and vocoders<sup>(21)</sup>.

(3) Matched filtering and pulse compression: In this area the CCD based PTF has found application to pulse compression of sonar return pulses<sup>(22)</sup> and matched filtering in spread spectrum communications equipment<sup>(23)</sup>. The small size and low power consumption of the CCD has made it a most attractive alternative to digital solutions in this application area.

(4) Adaptive filtering<sup>(3)</sup>: It is in this particular application that the PTF has its most important role since it is essential here that the filter tap weights should be updated at the CCD clock rate. This area is a relatively new one but a few schemes for adaptive filter implementation have been published<sup>(24-27)</sup>.

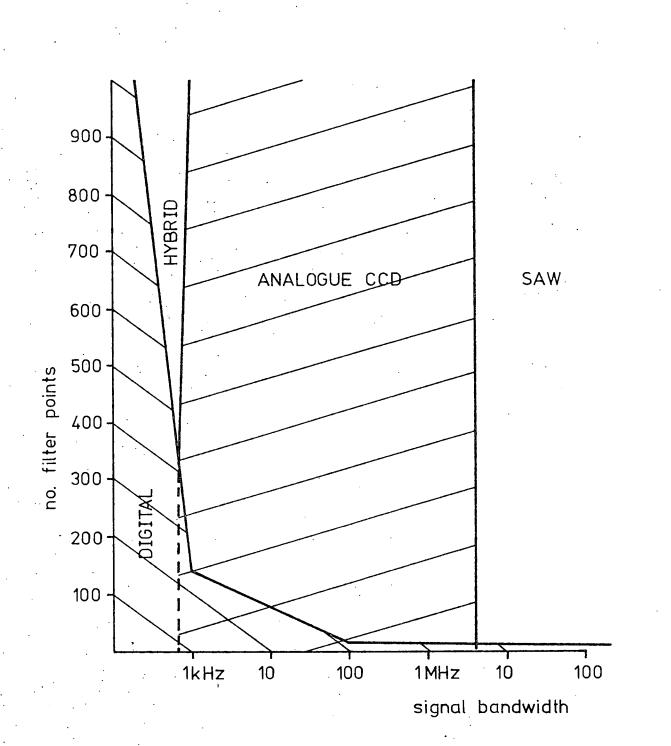

Many of the applications mentioned above are being approached using entirely digital circuit techniques and with the ever shrinking size and cost of digital components it appears more and more likely that they will be used in prefernce to the more elegant CCD solutions in many areas of signal processing. This is particularly true when the poor temperature stability and difficult 'setting-up' procedures of contemporary CCDs is taken into account. It would then appear that the CCD will only be used in areas where space and power are primary considerations or where the structures involved are insensitive to temperature drift due to the inherent systematic structure.

This is the specific category of system which is considered in this thesis under the general heading of adaptive signal processors. Two classes of processor are considered: (1) open loop adaptive systems which have specific tasks assigned to them, and (2) closed loop or true adaptive systems which are much more general purpose machines.

The open loop processor is one in which a number of a priori assumptions are made about an incoming signal sequence and the filtering function is in fact fixed. The first is a statistical analyser module (28) which is capable of measuring the statistics of an incoming signal and then making a decision, with a defined confidence

level, on the presence or absence of a signal peak. This processor was specifically conceived as a decision making circuit to follow a sonar matched filter in an environment where size and power consumption are of primary consideration.

The second module was a noise canceller<sup>(7)</sup> used to cancel unwanted fixed pattern noise on the output of a serialparallel-serial (SPS) delay line. The technique used was a simple coherent integration technique. The important point here was that the canceller should be implemented in a technology which was compatible with the SPS delay line to permit integration on the same integrated circuit and CCD techniques therefore had to be used.

Although both the processors just described were necessarily implemented using CCD circuits the stability of both systems was not entirely satisfactory. This prompted the construction of the second system type mentioned above, the closed loop adaptive filter.

Four experimental adaptive filter modules were constructed, two of which were based around a monolithic 64-point CCD  $PTF^{(14)}$ . These two prototypes<sup>(27,29)</sup> demonstrated the basic feasibility of using CCD elements for adaptive filtering. However, quantitative measurements were difficult to perform on these modules due to their lack of controllability. The third prototype<sup>(30)</sup> which was based

around a monolithic 256-point PTF<sup>(31)</sup> was constructed, which incorporated the necessary controllability and therefore allowed a quantitative comparison of filter performance with theoretical predictions. The fourth prototype was an all-digital module<sup>(32)</sup> which was used to provide a comparison with results obtainable using conventional technology. The results generated with the 256-point adaptive filter in particular may be readily compared with theory to demonstrate the quality of performance available using CCD based adaptive systems. An additional adavantage of the closed loop system is that it is insensitive to temperature drift effects and a corresponding decrease in 'setting-up' procedure complexity is achieved.

#### 1.2 Layout of thesis

A number of integrated circuits not commonly available commercially were used in the construction of the experimental systems just described. A brief description of the more important characteristics of these devices is given in chapter 2 together with an overview of the basic operating principles of the charge-coupled device.

Chapter 3 deals with the theory and construction of the two open loop systems described in the last section. Experimental results from the two prototype systems are also presented which demonstrate the principles of

operation of these systems.

The remainder of the thesis is devoted to a description of the closed loop experimental systems. Chapter 4 introduces the basic principles of the operation of an adaptive filter and describes some of their possible applications. In chapter 5 a number of solutions to the problem of adaptive filter implementation are presented with particular reference to specific circuit techniques. System architectures which are specifically suited to analogue and digital implementation are advocated and the actual system structures used in the construction of the three 64-point adaptive filter prototypes are described.

One of the most intriguing possibilities with an adaptive filter structure is that of inherent correction of errors within the filter itself. This aspect of adaptive filter operation is investigated theoretically in chapter 6 with specific reference to error sources such as charge transfer inefficiency, tap gain errors and multiplier inaccuracies. Experimental verification of some of the theoretical predictions in this chapter is also included in the last section of this chapter.

Chapter 8 is devoted to a description of the 256-point adaptive filter prototype (full details of the construction of this module are given in Appendix A). Experimental results for this module are also presented in

chapter 8 demonstrating the high degree of predictability of this processor from theoretically ideal models.

Chapter 9 contains a discussion of the results presented in the previous chapters and the author's conclusions.

#### CHAPTER 2: CCD CIRCUITS

In the work described in the following chapters a number of novel charge-coupled device integrated circuits were used which are not commercially available. A large part of this chapter is, therefore, devoted to an explanation of the particular operational aspects of these devices which are relevant to the work considered. In addition, the following two sections briefly review the basic operation of the charge-coupled device in terms of charge transfer and, input and output mechanisms.

#### 2.1 Charge transport mechanisms

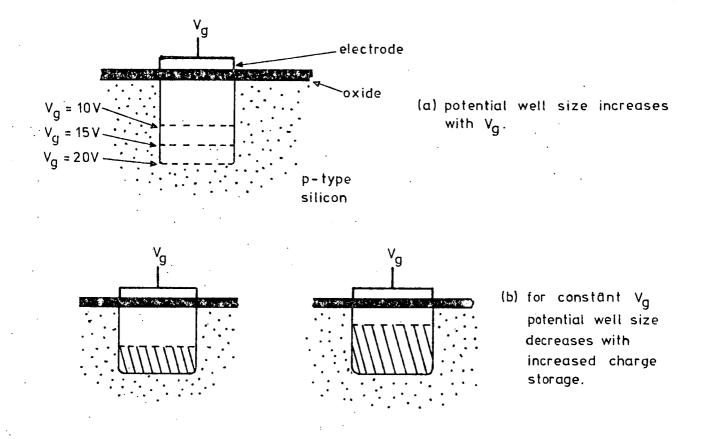

The basic function of the CCDs considered in this section is that of delay of sampled analogue data. In a CCD, analogue data samples are stored as charge packets held in the depletion region under an electrode with a positive voltage bias (for an n-channel device). If it is first assumed that no signal charge is available then the depletion region may be conveniently viewed as a potential 'well' of a depth which is proportional to the gate bias applied to the CCD electrode. Introducing a signal charge packet into this well causes the well to fill up, with a resulting drop in the surface potential. This is illustrated diagramatically in figure 2.1 which shows how the depth of the potential well decreases as the amount of signal charge stored under the electrode increases<sup>(33)</sup>.

Figure 2.1: Diagram illustrating the potential well concept

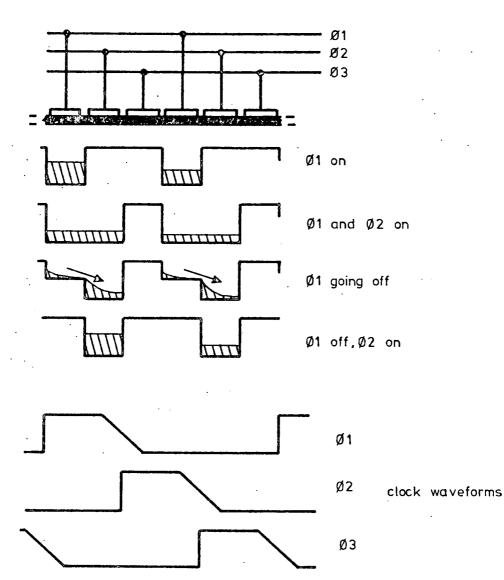

Figure 2.2: Transfer of charge using a 3-phase CCD clocking structure.

The transfer of charge packets from one potential well to another may be achieved in a number of ways, usually described in terms of the clock structure needed to perform a unit delay. In this section two charge transfer schemes will be described, one using a 3-phase clock structure and the other using a 2-phase clock structure. In the following discussion the word 'phase' will be replaced by the symbol '0'.

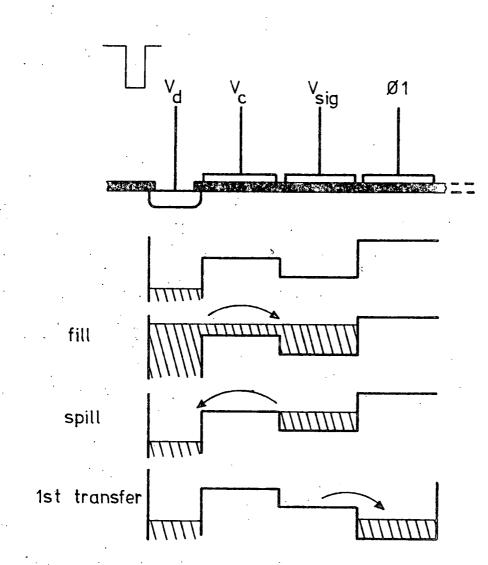

Charge transfer with a  $3\emptyset$  clock structure is achieved by the use of 3 successive CCD electrodes forming a single delay 'cell'. With reference to figure 2.2, the signal charge packet is initially stored under electrode 1 and its corresponding clock Ø1 is therefore on (positive potential) while the other two electrode clocks, Ø2 and  $\emptyset$ 3, are off (zero volts). The second clock,  $\emptyset$ 2, now comes on so that the signal charge is shared between electrodes 1 and 2,  $\emptyset$ 1 now switches off and the charge remaining under electrode 1 spills into the well under electrode 2. No reverse charge flow occurs since  $\emptyset 3$  is off during this transfer sequence and charge flow therefore occurs from left to right only. The charge transfer is completed by transferring the signal charge packet from electrode 2 to electrode 3, following the same procedure as that described above for transfer between electrodes 1 and 2.

The main reason for employing this  $3\emptyset$  clock structure is to prevent the reverse flow of charge along the delay line.

It is clearly demonstrated how this is achieved with the 3Ø structure in figure 2.2 since a barrier, in the form of at least one transfer electrode in the off state, always exists between adjacent transfer cells.

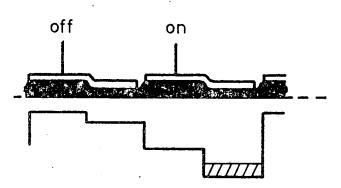

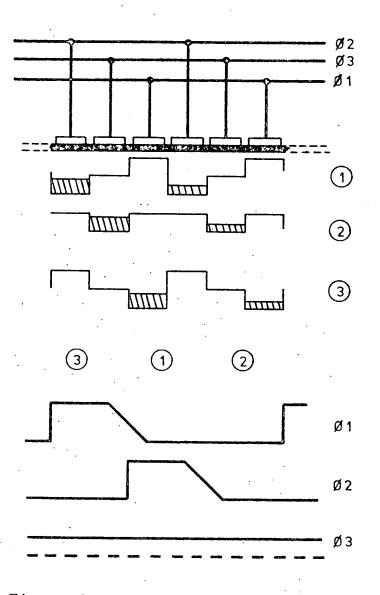

Charge transfer using only 2 clock phases may however be achieved by the use of implanted barriers or stepped oxide thickness. The stepped oxide thickness technique will be the one described here. The important point here is that the threshold voltage of two adjacent electrodes differs, so that when they are switched on together the depth of the potential well under a given electrode pair is stepped. This is shown in figure 2.3, where the threshold voltage difference is achieved by using a thick and then a thin oxide layer covered by one electrode.

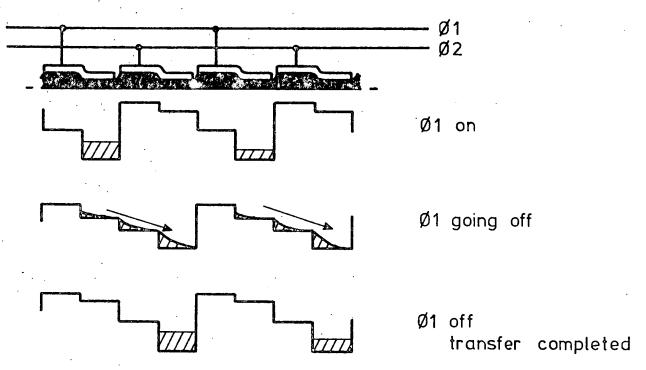

The transfer of a charge packet from one well to the next is shown in figure 2.4 where the charge is initially held under the second half of the  $\emptyset$ 1 electrode with  $\emptyset$ 1 on and  $\emptyset$ 2 off. As  $\emptyset$ 2 comes on and  $\emptyset$ 1 goes off the charge is dumped over the first potential barrier under the  $\emptyset$ 2 electrode and accumulates in the lower part of the 'step'. In this way backward flow of charge is minimised in a 2 $\emptyset$ CCD structure, as long as the signal charge packet size is significantly smaller than the size of the potential step between the two half-electrodes.

Despite the structural and clocking details just described

Figure 2.3: 20 CCD structure illustrating stepped well sizes due to different oxide thickness.

Figure 2.4: Transfer of charge in a 20 CCD structure.

backward flow can still occur in both 20 and 30 structures and this leads to the phenomenon known as charge transfer inefficiency (34). This is the incomplete transfer of a signal charge packet from one CCD electrode to the next. An additional factor which leads to transfer inefficiency is the existance of surface trapping states under an electrode. Charge carriers are trapped by these states and remain until the next charge packet is transferred in. The overall effect is that when a charge packet is transferred a small proportion  $\xi Q$  (where Q represents the signal charge and  $\xi$  is a constant usually between  $10^{-3}$  and  $10^{-4}$ ) is left behind and combines with the following charge packet. All the charge eventually leaves the delay line but the signal is distorted or 'smeared' by the inefficiency effect. The only way in which charge is actually destroyed is by carrier recombination in the semiconductor bulk material.

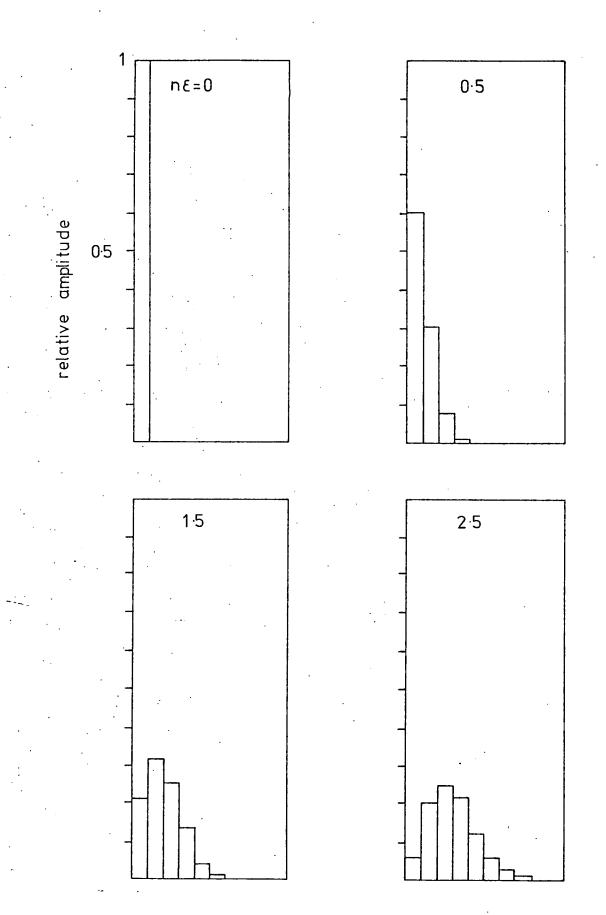

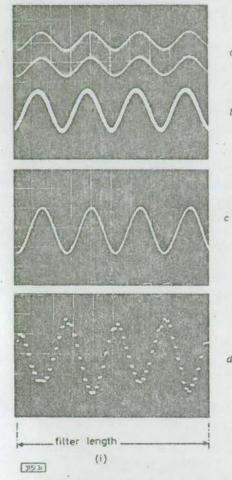

An overall figure of merit used to describe the charge transfer inefficiency is the n $\xi$  product, where n is the total number of transfers which take place in the delay line. The effect of transfer inefficiency is illustrated in figure 2.5 where the input to the CCD is a single pulse and the form of the delay line output is shown for progressively larger n $\xi$  products. This effect clearly imposes an upper limit on the length of delay achievable for acceptable signal distortion.

Figure 2.5: Output of a CCD delay line with a unit pulse input for varying n $\xi$  product.

#### 2.2 Signal input techniques

A variety of signal input techniques may be used with CCD structures of which two will be described in this section; diode cut-off<sup>(35)</sup> and 'fill and spill'<sup>(36)</sup>.

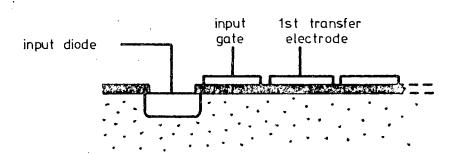

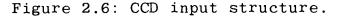

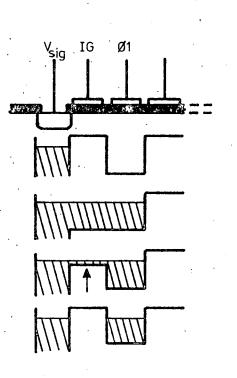

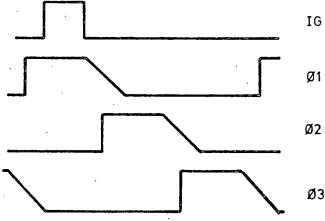

The structure at the CCD input is similar for both input techniques and is shown in figure 2.6. This consists of an implanted diode followed by a gate electrode immediately preceding the first transfer electrode. In the diode cut-off technique the input signal is applied directly to the diode. Initially the  $\emptyset 1$  clock is on, therefore a potential well exists under the  $\emptyset 1$  electrode. However, no charge is transferred from the input diode as long as the input gate clock remains off. When the input gate is pulsed high an amount of charge proportional to the signal amplitude is dumped under the  $\emptyset$  electrode and the input gate is switched off before the  $\emptyset 1$  to  $\emptyset 2$ transfer takes place, therefore isolating the input diode from the transfer process. This technique is illustrated in figure 2.7. Diode cut-off does result in some nonlinearity due to the fact that when the input gate switches off the charge under it tends to divide between the input diode and the  $\emptyset$ 1 transfer well resulting in an inaccuracy in the amount of the charge injected.

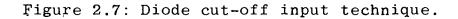

The fill and spill technique is shown in figure 2.8, where it can be seen that the arrangement of electrodes

1 clock waveforms 2

Ø3 ·

Figure 2.8: Fill and spill input technique.

at the input differs from that described above. The input signal voltage is actually applied to a second gate electrode immediately before the first transfer electrode. The first input gate is held at a constant potential to form a potential barrier between the input diode and the input gate. With  $\emptyset$ 1 held off the diode is pulsed on, filling the potential well under the input gate (this potential well depth is proportional to the input voltage). When the diode goes off the excess charge under the input gate spills back over the first gate barrier leaving a charge packet proportional in size to the input signal. Normal charge transfer may then take place to the  $\emptyset 1$  electrode position. Since there is no cut-off applied here there can be no forward spillage of charge into the input gate potential well and this input technique therefore provides a more linear input scheme than the diode cut-off.

#### 2.3 Tapped delay line implementation

In the previous sections the basic mechanisms for charge input and transfer in a CCD were considered; in this section a technique for non-destructively sensing the amount of charge under an electrode is described. The reason for doing this is to form a tapped delay line structure which is the basic element required to form a programmable transveral filter (as described in chapter 1).

Two tapped delay line devices were used in the work described here both of which used a floating gate reset<sup>(12)</sup> (f.g.r.) tapping circuit implementation. One of the devices used a 30 clocking structure (the M55 tapped delay line) with two complete delay stages between each tapping point while the other was a 20 structure with 1 delay stage between each tapping point (the WM2010 tapped delay line).

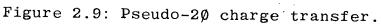

The mechanism of f.g.r. tapping will be described here with reference to the 30 clocking structure used in the M55 TDL. The basic technique relies on the use of a slightly different transfer mechanism than that already stated, in that one of the clock phases is held at a constant voltage about half way between the on and off levels. For the M55 device an electrode is on when +25V is applied to it and off at +2V, the intermediate voltage used on the tapping electrode was about +15V. The charge transfer mechanism using this arrangement is shown in figure 2.9 for a group of 3 electrodes showing the pseudo-20 operation now obtained.

The charge is sensed while under this second electrode using the circuit shown in figure 2.10. The potential on the sense electrode is reset during the  $\emptyset$ 2 phase by pulsing high the gate of the reset transistor with  $\emptyset$ 2. When the transfer of charge from the  $\emptyset$ 2 to the sense electrode takes place the sense electrode is floating and

---

. . .

· · · ·

· ·

Figure 2.10: Floating-gate-reset charge sensing.

its potential is modified by the signal charge packet transferred under it. This modified electrode potential is sensed by the source follower shown in figure 2.10 and a voltage proportional to the signal size may be measured at the sense amplifier output.

The main disadvantage with this sensing technique is that the dynamic range of signals is halved since the shallow potential well under the sense electrode now determines the maximum signal size. The main characteristics of the two TDLs described in this section are summarised in table I.

#### 2.4 SPS delay line implementation

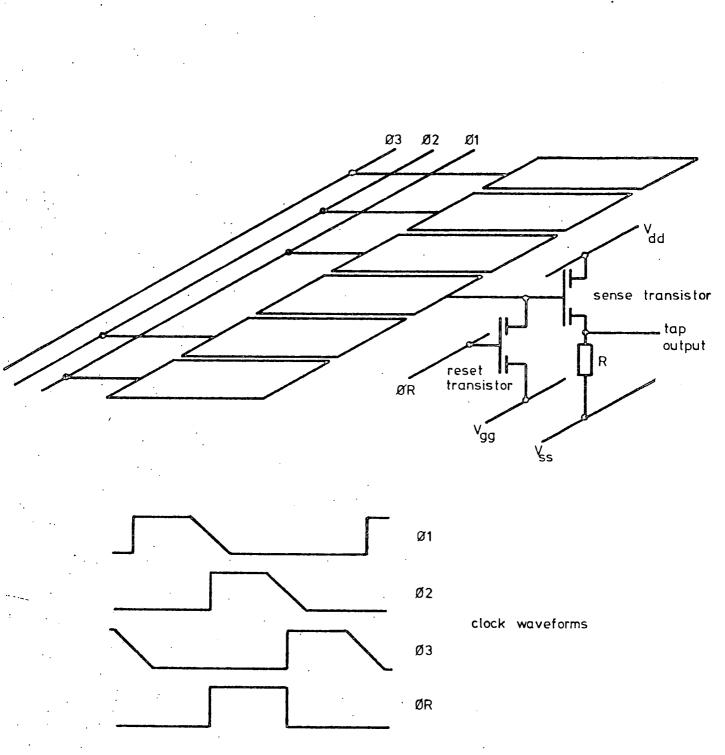

The serial-parallel-serial<sup>(36)</sup> configuration of delay line is the one most commonly used to implement long delays, usually associated with the storage of digital information. If a normal linear CCD delay were to be used in this application P delay stages would be required to store P bits of data with a resultant inefficiency product of P $\xi$ . With P $\approx 10^3$  this inefficiency product becomes unacceptable and some other technique for delaying signals must be found.

The SPS realisation is shown diagramatically in figure 2.11. This consists of a set of N parallel delay lines each of lenght M delay stages. The inputs to these delay

|                               | M55   | WM2010    |

|-------------------------------|-------|-----------|

| delay stages                  | 32    | 32        |

| clock phases                  | 3     | 2         |

| maximum sampling<br>frequency | 100 1 | kHz 2 MHz |

| delay cells/tap               | 2     | 1         |

| dynamic range                 | 50 0  | dB 50 dB  |

Table I: Tapped delay lines characteristics.

**:**٦.

lines are supplied from N parallel outputs on an N stage delay line which has a clock rate N times faster than the parallel delay line clocks. Therefore a set of N input signals are clocked into the first serial delay line at clock rate  $f_c$  and are then transferred into the N parallel delay lines. The signals are clocked along these parallel lines at a clock rate of  $f_c/N$ . At the end of these delay lines the signals are transferred into another N point serial delay line and clocked out at clock rate  $f_c$ . The total delay for any given signal is then N.M stages but total number of transfers is only N + M.

Although signal distortion due to transfer inefficiency is reduced to a minimum using this architecture the effects of dark current noise are accentuated. Dark current<sup>(37)</sup> noise arises from thermally generated minority carriers which are injected into the signal charge packet. At the output of the CCD the contribution from dark current is indistinguishable from the actual signal charge.

In a linear CCD this noise source does not usually present a serious problem provided that the device clocks operate at a constant rate. This is because each signal packet will accumulate the same amount of dark current generated charge during its passage along the delay line resulting in only an extraneous d.c. bias at the output. This, however, is not the case in an SPS device since a signal charge packet may be transferred along any one of N

Figure 2.12: Photomicrograph of the Plessey M67 SPS delay line.

different delay paths. Differences in device structure such as local stacking faults and carrier concentration which tend to vary across the device surface mean that each delay path will have a different dark current contribution. Therefore at the SPS output the signal appears with an additive noise component which repeats every n clock cycles.

In chapter 3 a scheme for the cancellation of this fixed pattern noise is presented (29). The SPS delay line used was a Plessey M67 SPS delay line which is a 4028 stage delay arranged as a 32 x 128 stage SPS block with a specified maximum clock rate of 2 MHz. A photograph of the M67 integrated circuit is shown in figure 2.12.

# 2.5 Programmable transversal filter implementation

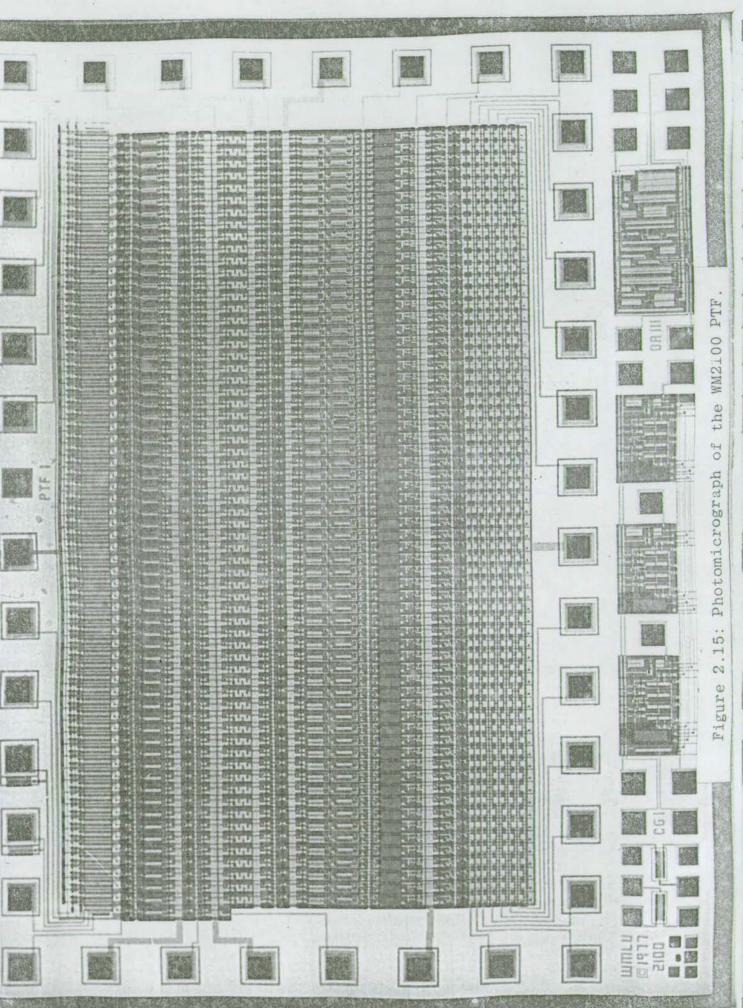

Two monolithic CCD programmable transversal filter realisations were used in the work described in chapters 5 to 8. These were the WM2100 64-point  $PTF^{(14)}$  and the WM2110 256-point  $PTF^{(31)}$ . In this section the basic operational characteristics of each of these devices are described with particular attention being paid to the method of weight multiplication.

Both of the PTF circuits mentioned above were of the TDL type described in section 1.1 with analogue weight storage where the weighting operation is achieved using a

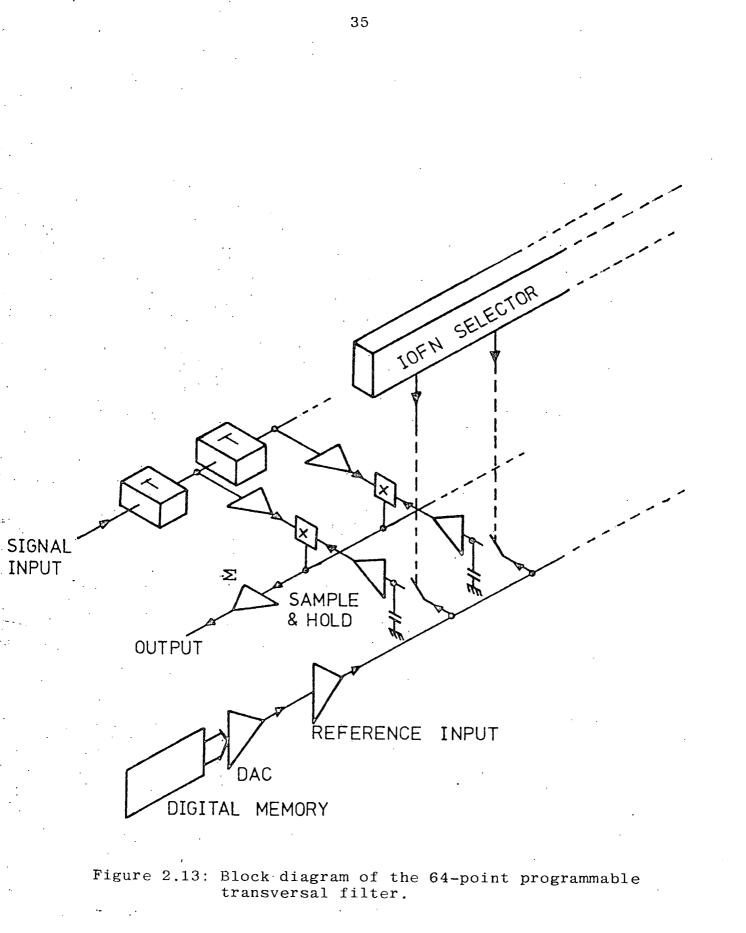

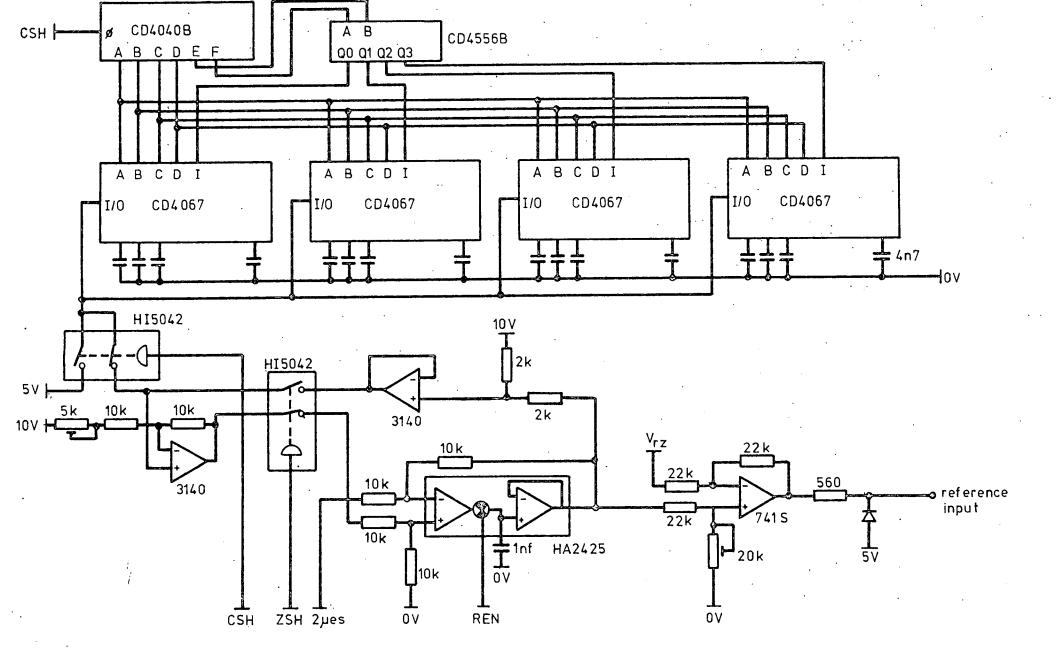

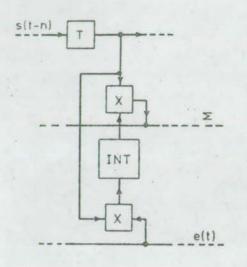

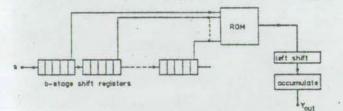

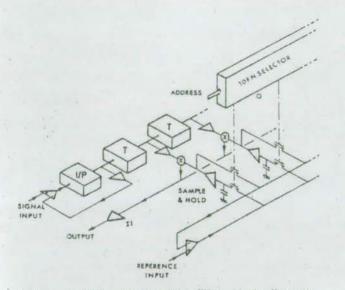

set of parallel analogue multipliers. In the case of the WM2100 device the TDL structure was essentially a 64-point 30 structure of the same type as that used in the M55 TDL. A block diagram of the 64-point PTF is shown in figure 2.13. Storage of the 64 weight coefficients was achieved using a set of 64 storage capacitors linked by MOS switches to a common analogue input bus. Any one of these switches could be opened, at random, by the application of a 6 bit address code to the input function decoder. However, once read into the sampling sites it was impossible to retrieve the information again due to the fact that the capacitance of the input bus line was approximately 100 times greater than the storage capacitance. It is therefore necessary to store the filter weight values on some external medium, usually digital RAM or ROM.

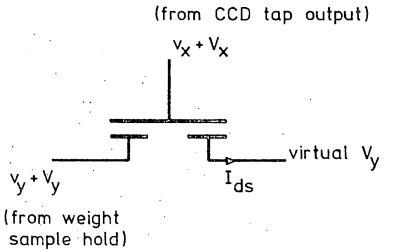

The signal weighting was achieved using a single MOS multiplying transistor at each CCD tap output, connected as shown in figure 2.14. The signal at the CCD tap output comprises the signal  $v_x$  plus a constant bias voltage  $V_x$  and the weighting signal, or reference, applied to the transistor drain was comprised of the weighting signal  $v_y$  plus a constant bias  $V_y$ . The source of each transistor provides an output current  $I_{DS}$  where:

For any given set of reference weights  $v_y$  does not change and the bracketed term in equation (2.2) can be viewed as a constant d.c. offset at the output. All  $I_{DS}$  currents are summed by connecting the transistor sources to a common summing bus to yield the result

One technique which was used to subtract the unwanted d.c. term in equation (2.2) was to form the convolution sum described in equation (2.3) and store this result for half a clock cycle on a sample and hold circuit at the output of the device. On one of the following CCD reset clock cycles the CCD sense gate was forced to a constant voltage equal to  $V_x$ . The filter output was sampled again at this point yielding the result:

$$v_0 = \sum (kv_y - \frac{1}{2}v_y^2) \dots (2.4)$$

Subtracting equation (2.4) from equation (2.3) yields the required output  $\sum v_v v_v$ .

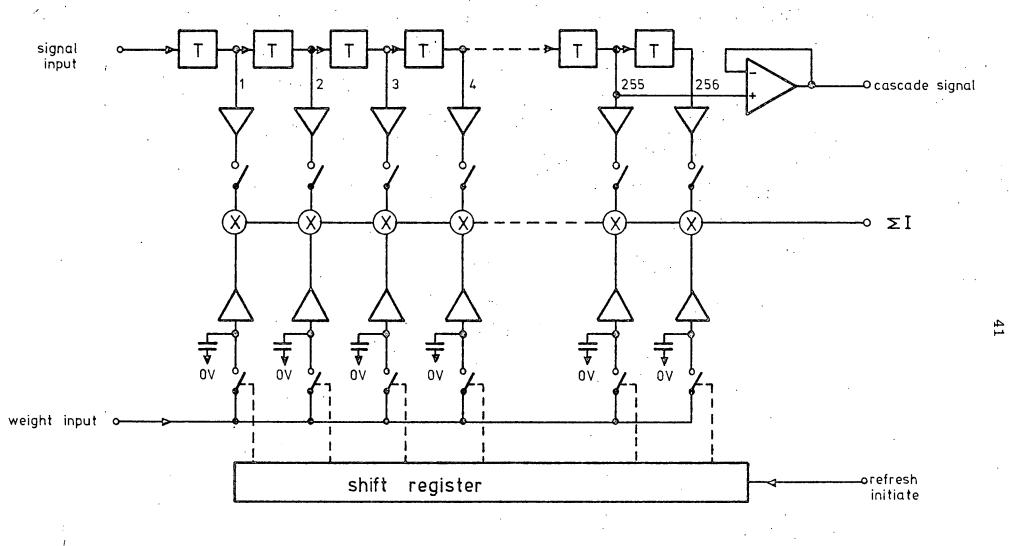

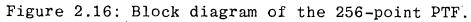

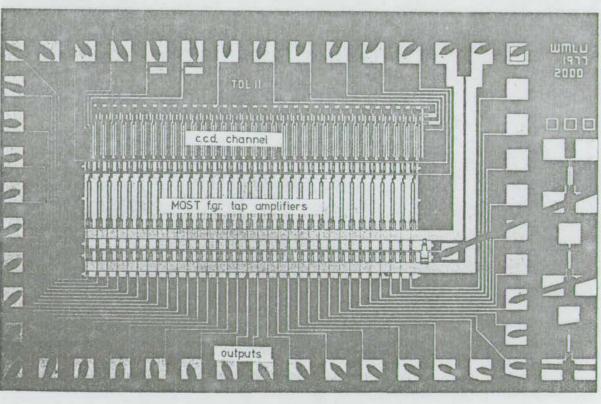

It was possible to use this zeroing technique with the WM2100 PTF since the CCD tap amplifiers were coupled directly to the multiplier transistor gates. However, with the WM2110 PTF this was not possible since each CCD tap output was sampled at the tap amplifier output to allow a larger amount of time for output amplifier settling. The WM2110 device was based on a 256-point 20 TDL of the same type as the WM2010 TDL. It differed in a few significant ways from the WM2100 PTF. A block diagram of the 256-point PTF chip is shown in figure 2.16. The weighting sample and holds were implemented in the same way as the WM2100 but here the sampling switches were activated by a pulse propagating along a 256 stage shift register rather than by the random access technique used in the WM2100.

As mentioned before the CCD tap outputs are all sampled on the chip and the zeroing technique described above could not therefore be used. The mechanism by which the residual d.c. errors caused by this are compensated for in an adaptive system is described in section 6.4. The reason for not including the facility for zeroing in this chip was that in many filtering applications d.c. terms on the PTF output are not used and the excess d.c. offset shown in equation (2.3) may be nulled simply by a.c. coupling the filter output. However, in the implementation of adaptive systems d.c. terms on the output must be used and a.c. coupling would result in a failure to converge.

A comparison of the characteristics of the WM2100 and the WM2110 PTF devices is given in table II.

|                        | WM2100  | WM2110 |

|------------------------|---------|--------|

| no. of filter points   | 64      | 256    |

| tap weight update mode | random  | serial |

| CCD clocking           | ЗØ      | 2Ø     |

| delay stages/tap       | 2       | 1      |

| Max. CCD sampling rate | 100 kHz | 2 MHz  |

| Max. weight update     | 1 MHz   | 5 MHz  |

| Harmonic distrotion    | -40 dB  | -50 dB |

| output dynamic range   | 65 dB   | 70 dB  |

# Table II: Programmable transversal filter characteristics.

۰,

Figure 2.17: Photomicrograph of the WM2110 PTF.

#### CHAPTER 3: OPEN LOOP SYSTEMS

In this chapter two systems are considered under the broad definition of open loop signal processing systems. This means that the processor has a fixed, and therefore predictable, response to any input signal and a certain number of a-priori assumptions must be made about the form of incoming signals. The two systems considered are:-

(1) A statistical analyser module which is capable of detecting signal peaks immersed in noise by the use of an adaptive thresholding technique.

(2) A noise canceller used to eliminate the fixed pattern noise associated with the output of a CCD serial-parallel-serial delay line; the delay line used was described in chapter 2.

The systems described above are adaptive in that they are capable of adjusting their characteristics to suit any situation in a given set of possibilities. However the filtering functions used are fixed, ie. no feedback to filter tap weights is provided, and therefore the systems are described as open loop.

## 3.1 Linear Regression Analyser Module

A common problem encountered in signal processing is that of detecting a signal against a background of noise. If the expected signal waveform is known then matched

filtering techniques may be used, and if the expected signal is a precisely known pattern (eg. a PN-sequence) then the optimum detection technique is correlation. However, if relatively little information is available about the expected signal (that is, it is restricted within a certain frequency band but may assume any combination of frequency components within that bandwidth) then the problem becomes more complex. For instance, for the events in the time domain using conventional filtering and thresholding techniques the threshold must be matched to the noise level which can vary making the set threshold invalid, and a slowly varying baseline also adds to this problem.

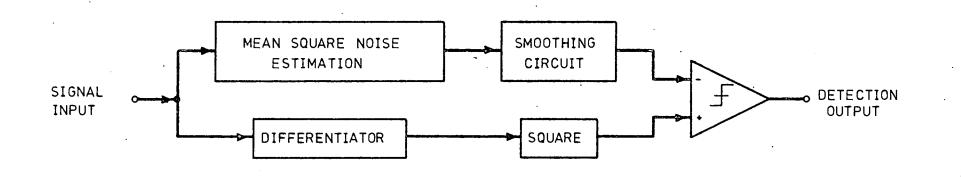

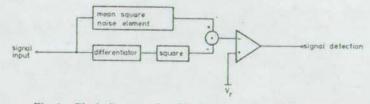

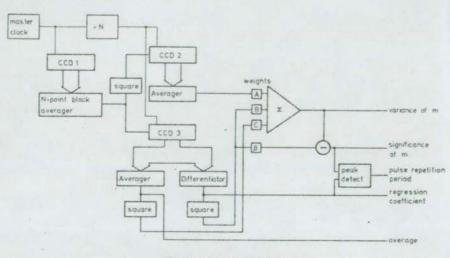

The ideal system would be one which is capable of evaluating the mean-square noise level and using this figure to automatically adjust the thresholding level to attain a constant error rate<sup>(39)</sup>. A slowly varying baseline would still lead to detection problems but this could be overcome by evaluating the signal validity from its derivative rather than its amplitude, in which case d.c. and low-frequency noise would have no effect on the detection system. A block diagram of this basic, idealised system is shown in figure 3.1.

This type of signal analysis is ideally suited to the use of statistical techniques and the system presented in this section is based on linear regression analysis<sup>(40)</sup>.

5

Figure 3.1: Block diagram of an idealised adaptive threshold detection system.

NB. It should be noted that where the signal is known exactly, beforehand, matched filtering is still the optimum filtering technique. This type of filter is really only valid where a pulse of unknown form occurs within specified limits.

This technique<sup>(41)</sup> has been used before in the form of a computer program for the 'non real-time' analysis of experimental data. The system described here, based on analogue charge-coupled device (CCD) tapped delay lines, implements similar algorithms providing a 'real-time' output at the sampling rate<sup>(39)</sup>. Certain restrictions on bandwidth and accuracy do exist using this method and these are described in greater detail in section 3.1.2, devoted to systems design.

#### 3.1.1 Theoretical Analysis

A slowly varying signal, y, having values  $y_n$  at times  $t_n$ may be estimated over a given interval by the equation,  $y = mt_n + c$ ; where m and c are the derivative and average of the signal, respectively. The error in the value of y, at any given time, may be expressed as:

$$e_n = y_n - y$$

$$= y_n - (mn\tau + c)$$

where the samples are evenly spaced in time by intervals. $\tau^{-}$ The sum of the squared errors over a fixed number of samples (2p + 1) is then given by:

$$S^{2} = \sum_{n=-p}^{p} e_{n}^{2} = \sum (y_{n} - (mn\tau + c))^{2} \dots (3.1)$$

Using the least-squares method, the best estimates of the quantities m and c are given by minimising the sum of the errors squared  $e_n^2$ . That is:

$$\frac{\partial S^2}{\partial m} = \frac{\partial S^2}{\partial c} = 0$$

Hence:

$$m = \frac{\sum_{n=-p}^{p} n\tau y_{n}}{\sum_{n=-p}^{p} (n\tau)^{2}} = y' \dots (3.2)$$

The minimised form of equation (3.1) is then:

$$S^{2} = \sum y_{n}^{2} - m^{2} \sum (n\tau)^{2} - c^{2}(2p + 1) \dots (3.4)$$

where m and c are given by equations (3.2) and (3.3).

Assuming the data to be normal with standard deviation  $\sigma$ ,

then  $\sigma^{2}$  may be estimated by:

$\sigma^2 = \frac{\sum (y_n - y)^2}{2p}$

and the variances of  ${\tt m}$  and  ${\tt c}$  are given by:

$$\sigma_{\rm m}^2 = \frac{\sum (n\tau)^2 \sigma^2}{\left(\sum (n\tau)^2\right)^2} = \frac{\sigma^2}{\sum (n\tau)^2}$$

$$\sigma_{c}^{2} = \frac{\sum \sigma^{2}}{(2p+1)^{2}} = \frac{\sigma^{2}}{2p+1}$$

Hence:

$$\sigma_{c}^{2} = \frac{p+1}{2} \left\{ \frac{1}{p(p+1)} \left[ (\overline{y^{2}}) - c^{2} \right] - \frac{\tau^{2} m^{2}}{3} \right\} \dots (3.5)$$

$$\sigma_{\rm m}^2 = \frac{3}{2p} \left\{ \frac{1}{p(p+1)\tau^2} \left[ (\overline{y^2}) - c^2 \right] - \frac{m^2}{3} \right\} \dots (3.6)$$

$$\overline{y^2} = \frac{1}{2p+1} \sum_{n=-p}^p y_n^2.$$

where

That is, the variances of m and c are connected simply by a factor of proportionality,  $\frac{1}{3}p(p + 1)\tau^2$ .

Intuitively, it may be argued that the value of  $m^2$  must be greater than its probable error  $\sigma_m^2$  to register a significant rate of change in the data, and hence the presence of a signal (see figure 3.1). More rigorously, the significance of the regression coefficient m may be determined by the application of the 'Student-t' test of significance to the derivative. That is:

$$t = m \left[ (2p - 1) \sum (n\tau)^2 / \sum (y_n - y)^2 \right]^{\frac{1}{2}}$$

$$\sum (y_n - y)^2 = \frac{m^2 (2p - 1) \sum (n\tau)^2}{t^2}$$

or

where the value of t may be found from the Student-t  $\binom{40}{40}$  table, dependent on the chosen level of significance. Using equation (3.4) an inequality:

$$T(m,\beta) = \frac{1}{p(p+1)^2} \left[ (\overline{y^2}) - c^2 \right] - (\beta + 1) \frac{m^2}{3} < 0 \quad (3.7)$$

may be determined which indicates when a signal is significant at the chosen level. Equation (3.7) is similar to (3.6) except for the factor  $\beta$  where:

$$\beta = \frac{2p - 1}{t^2}$$

This test is independent of the value of  $\tau$ , which may be arbitrarily set at unity. We now have a test which yields a signal detection system which automatically compensates for the noise level, the function which can not be carried out using conventional filtering and thresholding techniques.

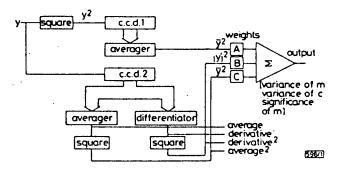

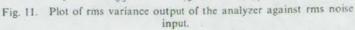

A number of output parameters may be readily evaluated from the well known results. For instance, it can be predicted that the averager and differentiator frequency responses will closely follow the sinc(x) function and its derivative. Further, the averager response will have a maximum at d.c. and its first null when one complete cycle is stored in the CCD register (ie. at  $1/27f_c =$  $0.037 f_c$ , where  $f_c$  is the sampling rate of the 27 point delay lines used in this experiment).

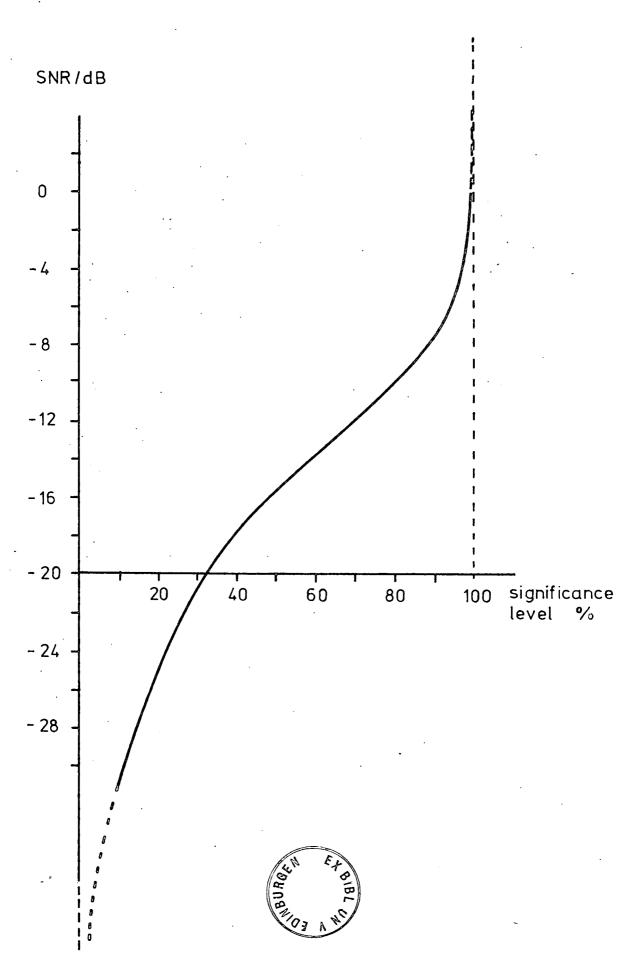

It is also a simple matter to calculate the maximum processing gain (minimum signal to noise ratio) for the system by the choice of two distinct waveforms representing maximum signal and maximum noise respectively. Furthermore, if the noise signal is chosen so that it affects only the  $y^2$  value and the signal has no effect on the variance then the calculation is greatly simplified. Examination of the relevant variance and significance formulae confirms that these criteria are satisfied for the case where the noise signal is a Nyquist-rate square wave and the signal is another square wave at less than 0.018 f<sub>c</sub> (ie. well within the range where the variance

output is not affected). The processing gain may then be evaluated for various levels of significance. Figure 3.2 shows a plot of minimum signal to noise ratio against significance level for the stated case. It should be noted that the processing gain is critically dependent on the signal and noise spectral characteristics and the case presented here is for maximum processing gain.

In all instances shown in figure 3.2, where the minimum signal to noise ratio is less than 0 dB, a white noise background may not be used since components of the noise spectrum in the signal detection region will yield a significant output. Therefore, for a white noise background it is necessary to use a value of  $\beta$  which gives a minimum signal to noise ratio of 0 dB, or greater, at the input. In the example stated in section 3.1.2 the significance level used was the 1% level and hence the noise spectrum was limited to about 0.04 f<sub>c</sub>, upward.

In the case where a white noise background may be used the components of noise in the signal region both add and subtract from the actual signal. Therefore, to ensure signal detection the minimum signal to noise ratio is raised to about 3 dB.

# 3.1.2 System Implementation

The implementation of the system described in the

Figure 3.2: Graph of minimum signal to noise ratio plotted against theoretical significance level.

previous section is dependent on the ability to store several successive samples of the incoming data, and make them available for manipulation simultaneously, to aid the speed of operation. In addition, the accuracy of the system is dependent on the number of samples used, and the bandwidth of detectable signals is dependent on the sampling frequency and the number of samples N, such that:

Bandwidth  $\alpha f_{c}/N$

Accuracy a/N

Therefore to make a fast, versatile system with potentially programmable bandwidth the following attributes are required:

- (i) Variable sampling rate;

- (ii) The availability of several successive samples simultaneously (ie. serial-to-parallel operation); and

- (iii) The ability to process varying numbers of samples.

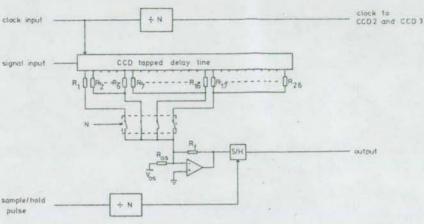

One circuit which offers all of these features is the CCD analogue tapped delay line, which was the basic circuit element used to implement the experimental system.

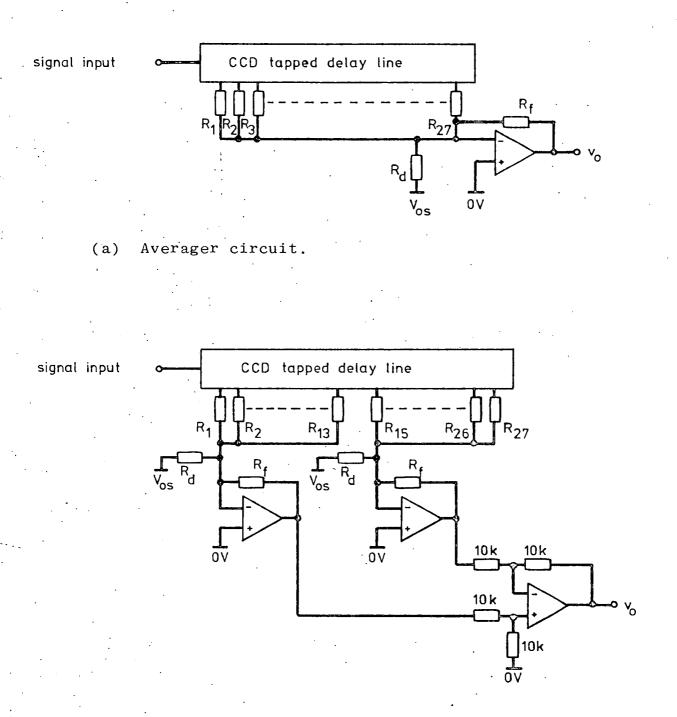

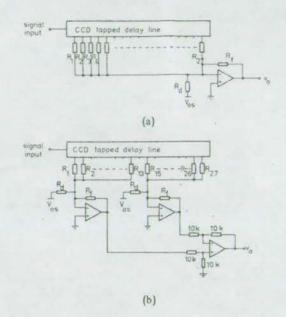

The delay lines used in the experimental system to be described here were the M55 CCD tapped delay lines described in chapter 2, with 27 separately accessible taps. The use of these devices means that the averaging and differentiating function described mathematically in

equations (3.2) and (3.3) may be implemented directly by weighting the tap outputs and summing. Circuit diagrams demonstrating the circuits used to implement these functions are shown in figure 3.3. The register values  $R_1$  to  $R_{27}$  may be evaluated directly from equations (3.2) and (3.3). In figure 3.3(a) the averager weighting resistors are all identical and the differentiator weights in figure 3.3(b) form a linear ramp with  $R_{14}$  being the centre point, not contributing.

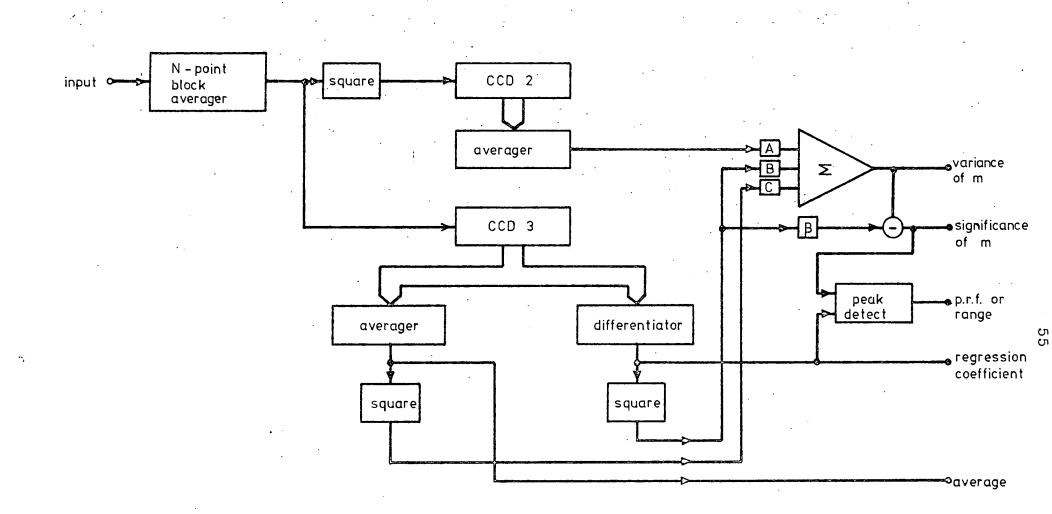

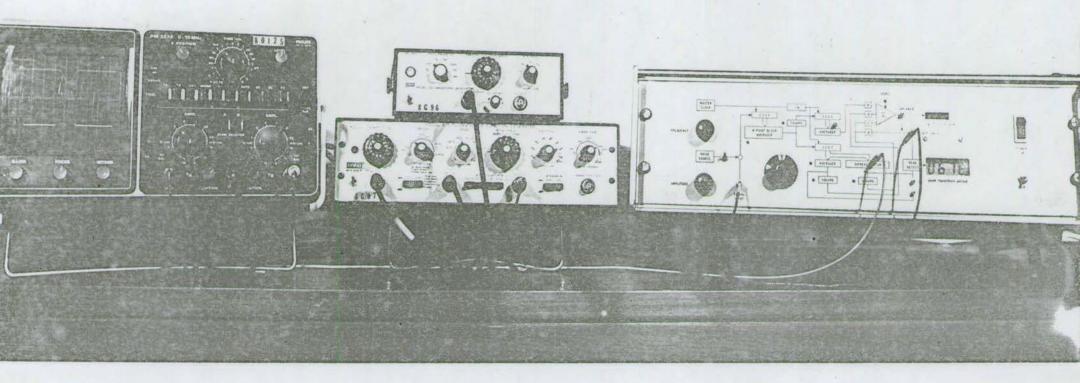

A complete block diagram of the experimental system is shown in figure 3.4. It can be seen from this that the system is a literal interpretation of the variance and significance formulae, making system performance exactly predictable. However, the variance output is filtered before application to the significance testing circuit to eliminate variance errors. This means that the variance is averaged over a greater number of data points than the basic 27 and the significance testing circuit now more closely resembles a 'Chi-square' test than a 'Student-t' test of significance. Nevertheless, equation (3.7) may still be applied and in this case for 27 data points at the 1% significance level the value of  $\beta$  is approximately 4.2.

Although the significance output gives a positive indication of a valid signal at the input, it conveys only the information that a significant derivative is

# (b) Differentiator circuit.

Figure 3.3: Schematic diagrams of the CCD averager and differentiator circuits.

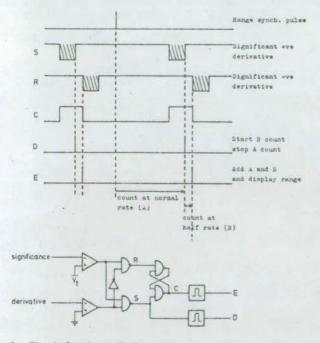

present, whilst no information on the polarity of that derivative is available. If however, the significance output is used in conjunction with the derivative output then significant positive and negative derivatives may be separately resolved. This information may then be applied to indicate the presence of a significant signal peak.

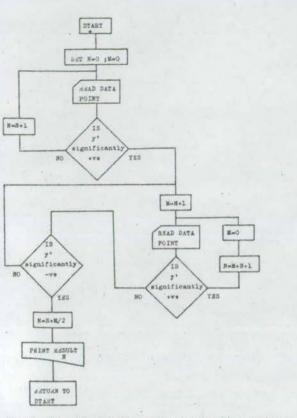

Information derived from this circuit may further be used to find the peak position<sup>(41)</sup> and the peak repetition period. In the experimental system the peak position was taken as the point half-way between the last significant positive derivative and the first significant negative derivative. The peak repetition period may then be calculated by counting between these values. It is possible to initiate this count sequence from any arbitrary point so if the peak position with reference to an arbitrary synch. pulse were required (ie. a range figure) then the algorithm could be easily modified to provide this facility.

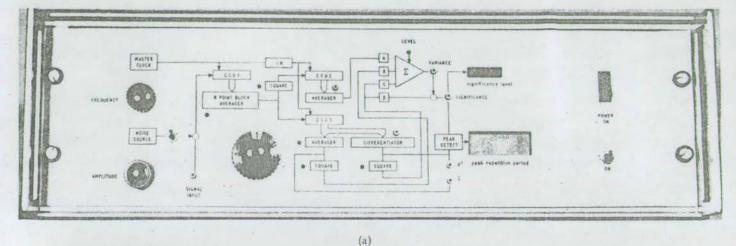

The experimental system was constructed as a modular system in a 19" rack: figure 3.5 shows a photograph of the system. The complete system as described had overall power requirement of 12 Watts, however, the CCD processing elements individually consume 500 mW. It is estimated that an equivalent digital realisation would require 50 times as much power (i.e. in the region of 500W).

Figure 3.5: Photograph of the experimental system.

### 3.1.3 Experimental Results

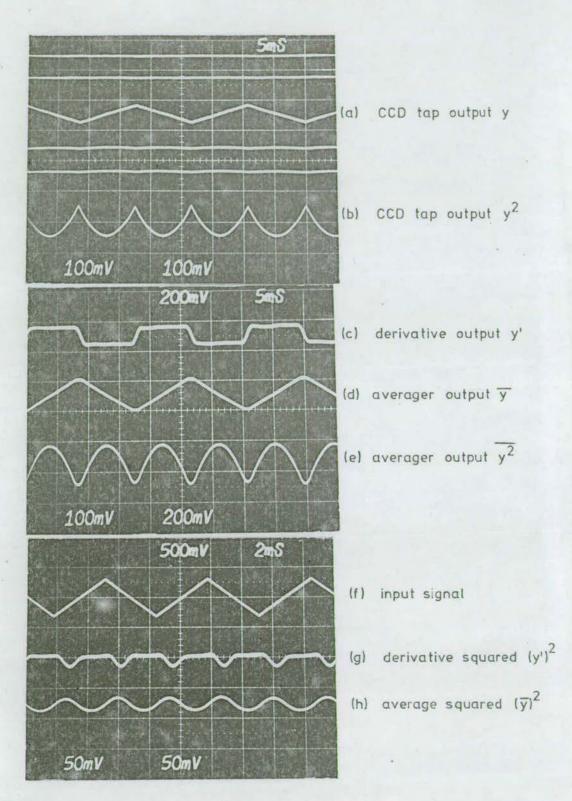

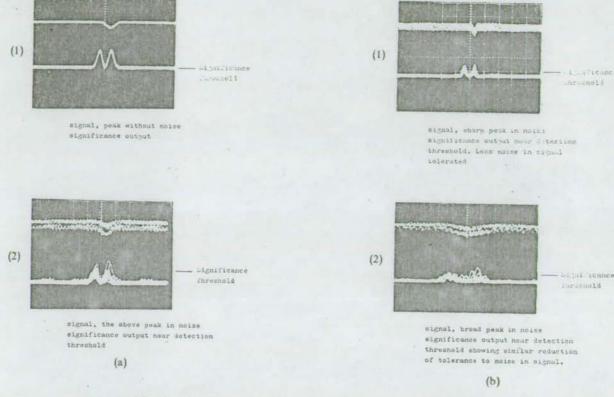

Figure 3.6 shows a series of photographs demonstrating the basic system outputs for a triangular wave input. It should be noted that the differentiator weighting does not make full use of the possible system bandwidth but is rather a least-square estimate.

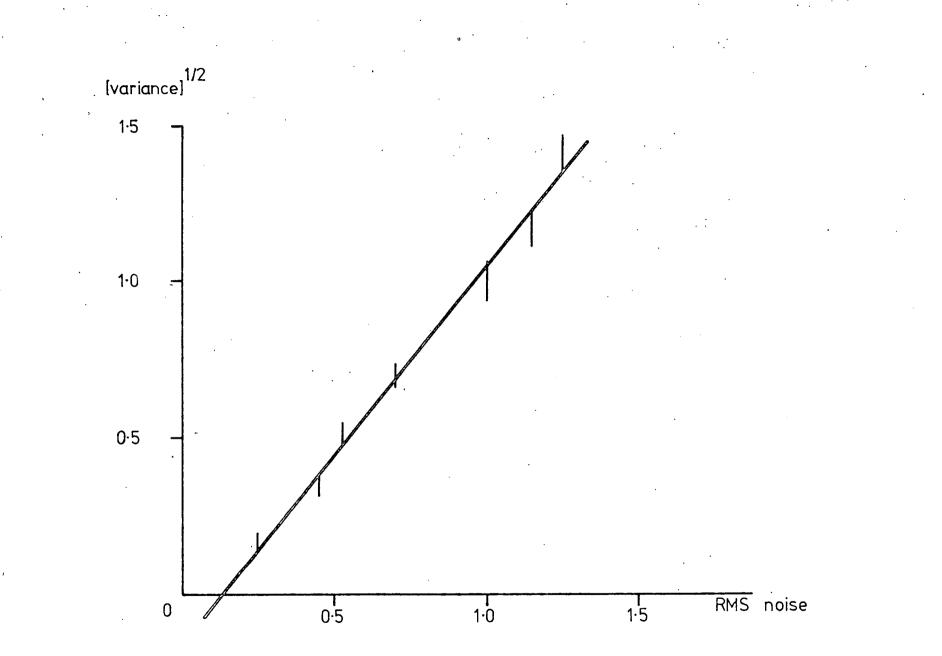

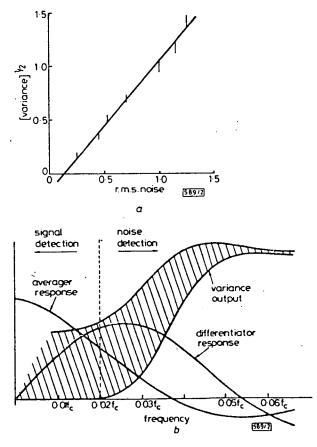

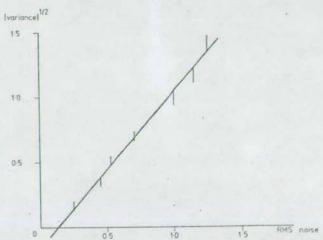

Since the variance is (by definition) the mean-square variation of the signal, then a graph of the square root of the variance plotted against the rms noise input should yield a linear relationship. This was plotted using a 31bit pseudo-random sequence as the noise source and the result is shown in figure 3.7. It can be seen that, within the limits of reading error, a linear relationship was maintained.

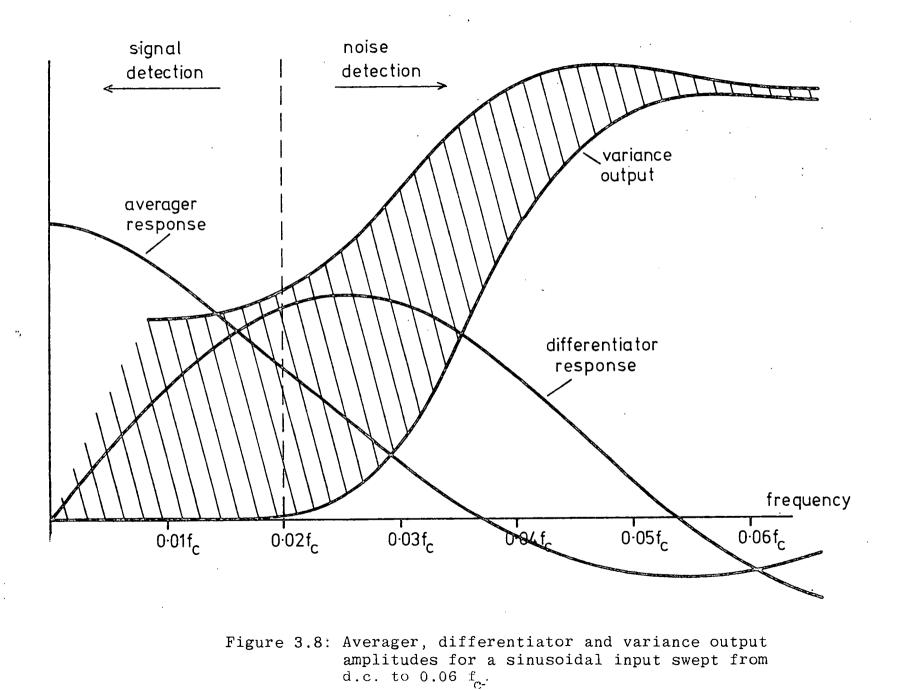

Figure 3.8 shows a plot of averager and differentiator frequency responses for a sine wave swept from d.c. to 0.06  $f_c$ , approximately. These responses display the expected sinc(x) shape and its derivative (cf. section 3.1.1).

Also shown in figure 3.8 is the envelope of the unfiltered variance output, for the same input, demonstrating a relatively constant output above about  $0.04 f_c$ . Hence, frequencies above this point are detected as noise yielding a predictable d.c. offset at the

Figure 3.6: Basic system outputs for a triangular waveform input.

۰,

Figure 3.7: Plot of the square root of the variance output against input signal to noise ratio.

variance output and signals below this frequency are regarded as valid signals (weighted according to their derivative).

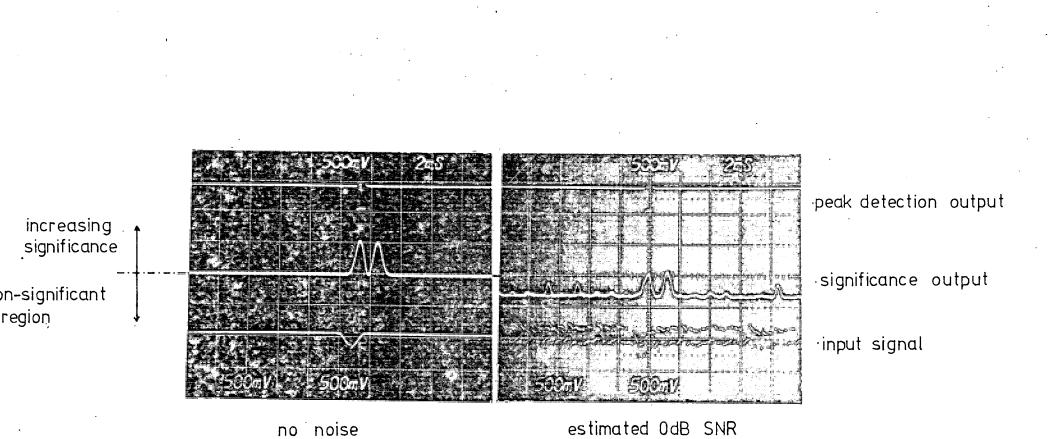

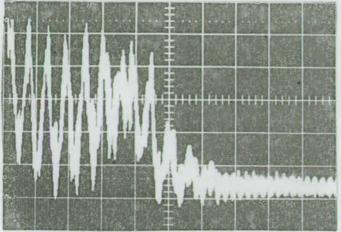

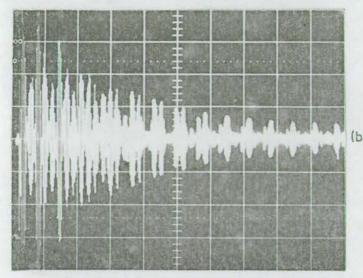

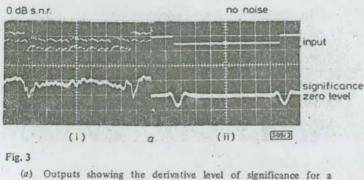

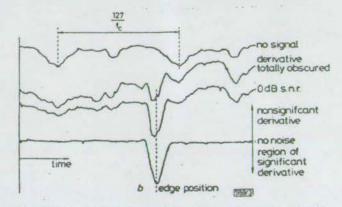

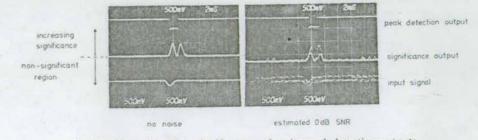

Figure 3.9 shows some typical significance outputs for a triangular pulse, first with no noise and then with an estimated 0 dB signal to noise ratio. In this case the noise source used was a 127-bit pseudo-random sequence filtered to give about 10 dB rejection at 0.04  $f_c$ . Therefore noise components are present in the signal region and these may be clearly seen in figure 3.9 although they never reach the detection threshold level. It can be seen from these outputs that even with a considerable noise background the significant peaks still reach above the set threshold level and a consistent peak detection output is available.

A major brawback in the system described here was a low dynamic range which was measured to be about 25 dB at the input. This is due mainly to the fact that the signal is squared before entering CCD2 which results in halving the available input dynamic range (the range of the CCD register is approximately 50 dB)<sup>(42)</sup>. That is, for normal operation the dynamic range;

20  $\log_{10}(\frac{A}{B}) = 50 \text{ dB}$ but for the case where the signal is squared

$20 \log_{10} (\frac{A'}{B'})^2 = 50 \text{ dB}$

Therefore, at the input the dynamic range is approximately

25 dB.

#### 3.1.4 Summary

It has been demonstrated in principle that it is feasible to apply statistical analysis technique to the problem of non-matched filtering, and that the use of these techniques have certain basic advantages over more conventional methods. These advantages mainly concern the automatic, noise controlled, thresholding technique and the exclusion of low frequency noise from the signal by the use of derivative detection rather than by the more normal amplitude detection.

In addition, it had been shown that charge-transfer devices provide a suitable basic building block for such a system providing for easy adjustment of the system characteristics. A small, low power system of this type is ideally suited to use as a constant false alarm rate decision module following a noise reduction system, in particular communications receiver applications (eg. sonarreturn processing). Applications to scientific instruments used inherently in 'noisy' experiments is also a possibility, replacing non real-time techniques<sup>(41)</sup>.

A major problem associated with the processor described here is that of stability. This is due to the high dependence of the processor on d.c. levels produced at the

output of various analogue squaring and filtering circuits. It was found that the outputs tended to drift to unacceptable levels for quite small temperature changes, of the order of 1 or  $2^{0}$  C. This type of behaviour is clearly unacceptable in a module of this type since drifts of this kind seriously affect the accuracy of pulse detection.

# 3.2 Cancellation of fixed pattern noise in SPS delay lines

The basic operation of a serial-parallel-serial (SPS) CCD delay line has been discussed in chapter 2. Although the structure does have the advantage of reducing the overall charge-transfer inefficiency involved in the total delay it does tend to accentuate the problems associated with dark current noise<sup>(43)</sup>. This is due to the fact that an incoming signal may be transferred over any one of 32 separate delay paths (using the M67 SPS delay line described in section 2.4). Each of these delay paths will contribute different amounts of dark current to the signal charge packet due to differences in the device structure, such as local stacking faults and carrier concentration variations in the silicon substrate. The overall effect is a fixed pattern noise which is added to the output signal.

The one fact which is known about this noise pattern is its repetition period which is fixed at 32 clock cycles

for the M67 device since there are only 32 individual signal paths within the device. This means that it is possible to coherently integrate over the period of the fixed pattern noise and then cancel it at the SPS delay line output. In this section the design of such a canceller is described and some typical results are presented to demonstrate the operation of the experimental canceller.

# 3.2.1 System Implementation

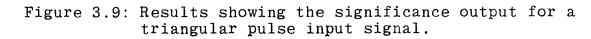

It is important if a system such as this is to be commercially viable that the noise cancellation scheme should be physically compatable with the technology used in the SPS device manufacture and should be simple enough to enable integration on the same chip as the SPS device.

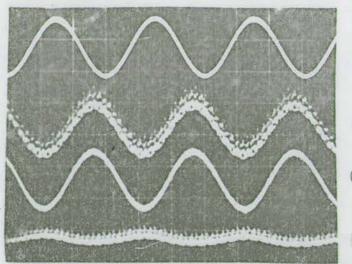

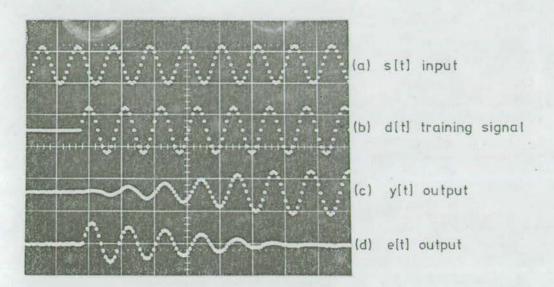

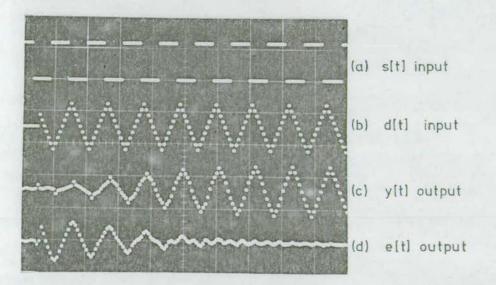

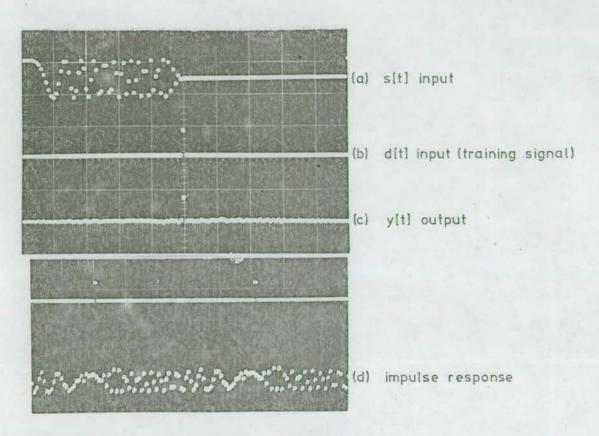

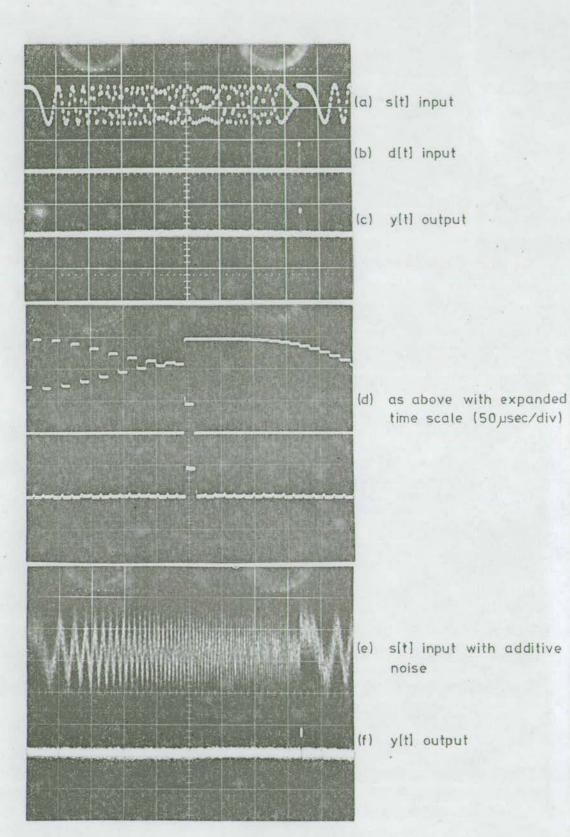

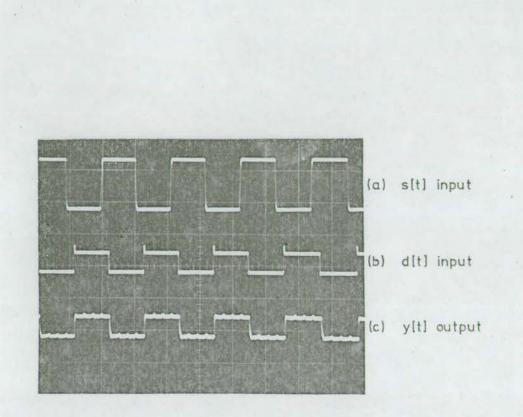

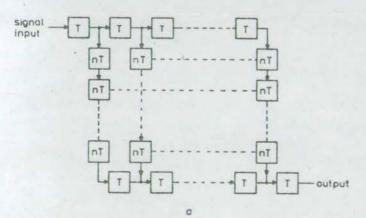

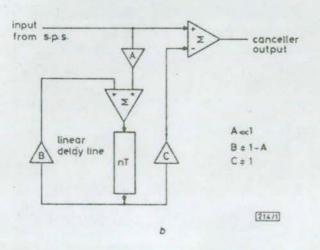

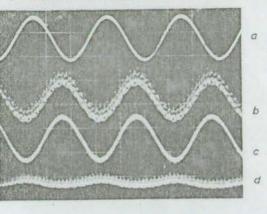

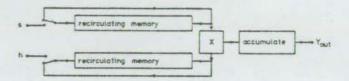

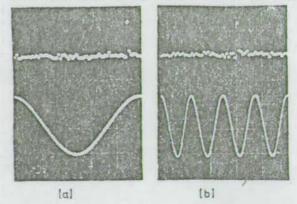

The cancellation scheme chosen for the experimental system is shown in figure 3.10. The principle of operation is that the output of the SPS device is integrated by the linear (n stage) CCD delay line loop so that a replica of the output noise pattern builds up in the linear CCD. The pattern is then subtracted from the SPS output. The result shown in figure 3.11 shows a typical output from the experimental integration loop (which was constructed using the WM2100 TDL described in chapter 2) when the input to the SPS delay line was grounded. The trace shown in figure 3.11(b) shows the

1.32.

Figure 3.10: Block diagram of the experimental noise canceller.

Figure 3.11: Result demonstrating the canceller performance for a zero signal input.

integrated version of the SPS noise pattern and figure 3.11(c) shows the canceller output which may be seen to be relatively noise free, in comparison with the original output.

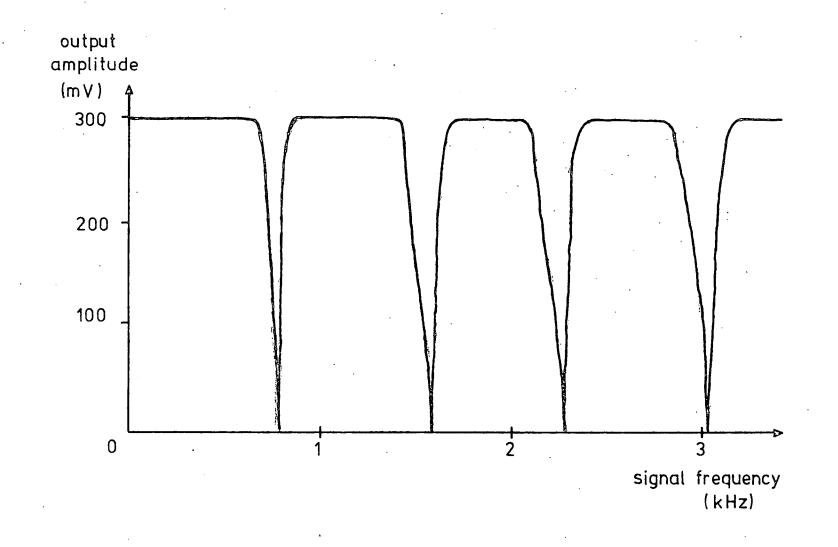

One defect which does occur using this cancellation scheme is that the integration loop imposes a comb filter response on the output with nulls at frequencies which are integer multiples of  $f_c/n$ . However for speech or video signals it will be assumed that truly periodic signals do not exist for long enough for a notch to form at the canceller output. The graph shown in figure 3.12 illustrates the measured frequency response of the system when the input signals are pure sinusoids.

#### 3.2.2 Experimental Results

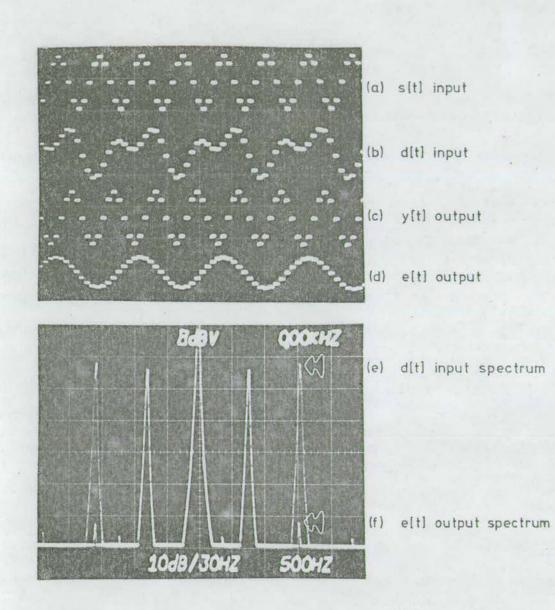

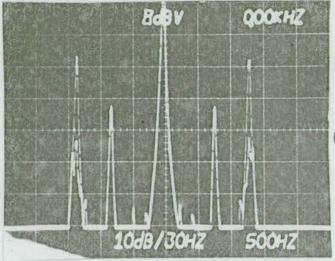

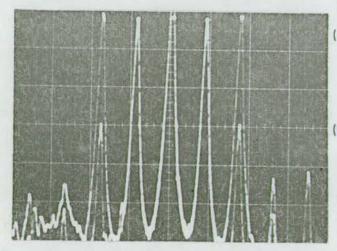

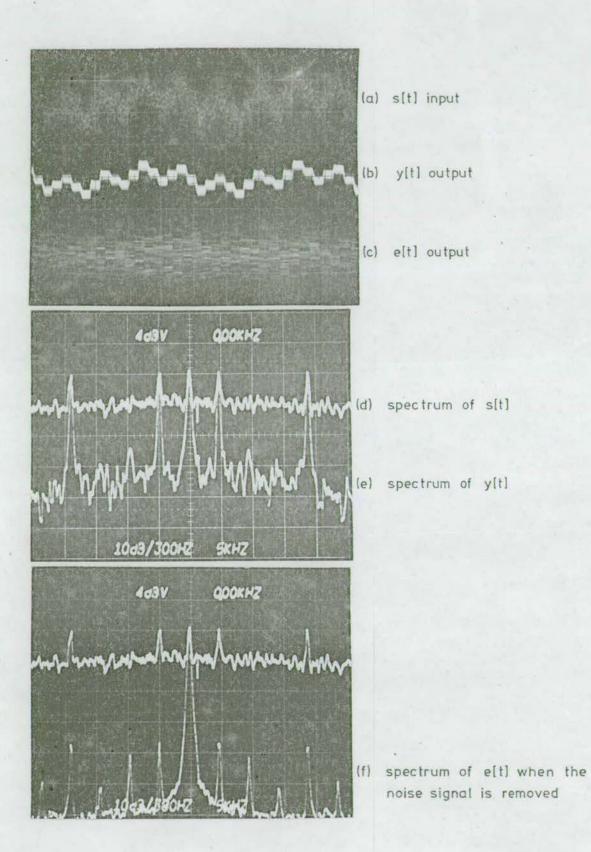

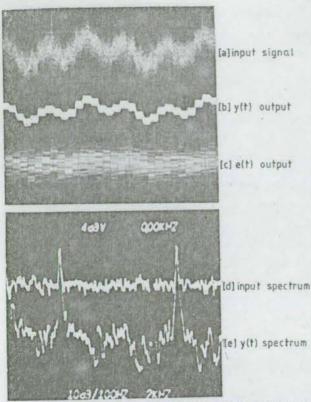

The result shown in figure 3.13 is for a sinusoidal input to the SPS device (figure 3.13(a)). The SPS output is shown in figure 3.13(b) and the effect of dark current fixed pattern noise is clearly visible here.

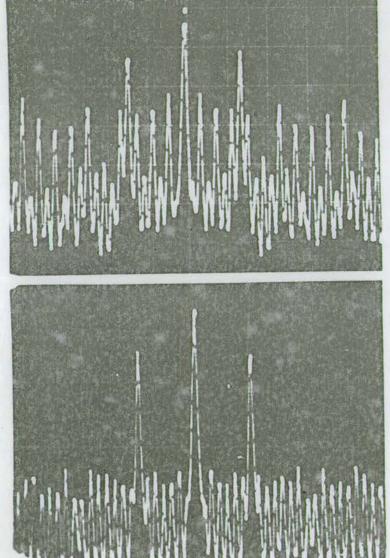

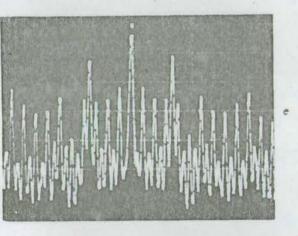

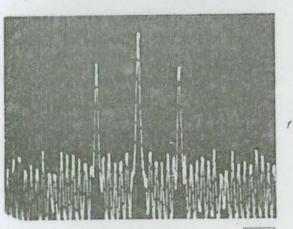

The integrated noise pattern in shown in figure 3.13(d) and the actual canceller output is shown in figure 3.13(c). From the frequency spectra shown in figure 3.13(c) and (f) the improvement in effective signal to noise ratio is approximately 20 dB.

$\gamma_{j}$

A signal input

71

- B SPS output

- C canceller output

- D integrated noise

E input signal spectrum

10 dB/div 2 kHz/div

F canceller output

Figure 3.13: Result showing fixed pattern noise carcellation in the presence of a sine wave input signal. A certain amount of signal distortion was obvious in the test signals used mainly due to the relatively high values of the gain A necessary at the integrator input. This high gain was necessary due to the cumulative transfer inefficiency in the noise integrator meaning that integration had to take place over a relatively short period of time. This situation could be improved either by using a buried channel CCD in the integrator (the experimental module used a surface channel device), or by using a simple transfer inefficiency compensation filter<sup>(34)</sup>

#### 3.2.3 Summary

The feasibility of SPS fixed pattern noise cancellation has been demonstrated showing that it is possible to considerably enhance the effective signal-to-noise ratio of a signal at the output of an analogue SPS delay line. Potential future developments of this concept are:

(1) Monolithic integration: This circuit could be integrated monolithically with the SPS device, since the technology for the cancellation scheme is compatible and all gains in the integration loop are less than unity. Thus simple MOS buffers and charge manipulation techniques may be employed to complete the cancellation loop.

(2) Overall feedback: The present cancellation system is an open loop processor depending on externally applied gains. A desirable system would

be a closed loop system employing signal feedback to minimise dependence on loop gains.

(3) Alternative cancellation schemes: Such as the use of delta-modulation at the CCD output to cancel fixed noise components with minimal effect on required signal components.

Again the major problem found here was that of stability due to the d.c. terms in the CCD integration loop. This problem could be solved to some extent here by a.c. coupling of signals around the integration loop, but a more attractive solution would be to use the averaging techniques advocated by Traynar and Beynon<sup>(44)</sup> which suffer from none of the inherent stability problems of recursive filter structures.

#### CHAPTER 4: CLOSED LOOP SYSTEMS

In the previous chapter the processing systems under consideration were so called 'open loop' systems, meaning that no continuous dynamic control is available over their operating gain and bias levels. In the following chapters the systems which will be considered are closed loop; i.e. some form of external feedback is applied around the filtering device to provide continuous dynamic optimisation of gain and bias parameters. This means that the closed loop system may be designed to be stable and free from drift due to temperature changes. An added advantage is a reduction in the required accuracy of 'setting-up' procedures due to the inherent ability of the closed loop system to adjust its own bias levels. These characteristics will be demonstrated theoretically and experimentally in the following chapters.

# 4.1 General adaptive systems

In general a closed loop filtering system is known as an adaptive filter and it involves several fundamental differences in overall operation from a conventional open loop processing system. With a normal open loop system the statistics of incoming signals and any accompanying noise or distortion must be known a-priori. It is then necessary to define exactly how the noise and/or distortion may be optimally reduced and this a-priori

information must be used in the design of a dedicated processing system.

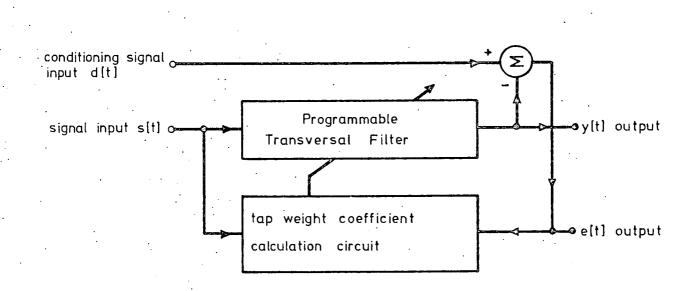

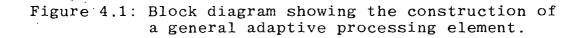

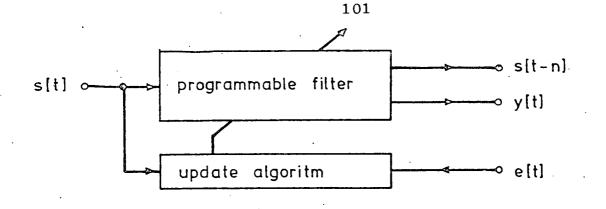

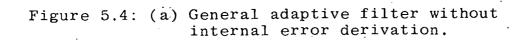

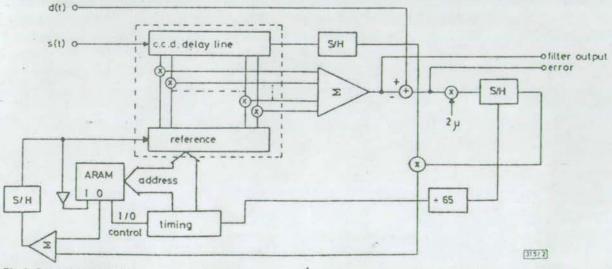

However, with a true adaptive system an absolute minimum of a-priori information is necessary about the incoming signal. This is because the adaptive filter operates by measuring the statistics of the incoming signal and adjusting its own impulse response in such a way as to minimise some cost function. This cost function may be derived in a number of ways depending on the intended application but normally it is derived by the use of a second signal source (see the general block diagram in figure 4.1). This secondary signal input d(t) may be defined as the desired output of the filter, in which case the task of the adaptive algorithm is to adjust the weights in the programmable filter device in such a way as to minimise the difference between the filter output and the secondary d(t) input.

It can be shown that when the filtering device is a finite impulse response transversal filter the optimum weight vector is the Weiner<sup>(45)</sup> solution given by:

$\underline{H}_{W} = \underline{R}^{-1} \underline{P} \dots (4.1)$ where  $\underline{H}_{W}$  is a column vector of the weight values supplied to the transversal filter;

$$\underline{\mathbf{R}} = \mathbf{E}\left(\underline{\mathbf{SS}}^{\mathrm{T}}\right)$$

Where E() denotes the expected value, <u>S</u> is a column vector of signal samples stored in the filter and the

superscripted T represents the transpose of the matrix; and

$$\underline{P} = E(d(t) \underline{S})$$

One of the earliest true adaptive systems was designed by Gabor<sup>(46)</sup> and used a complex analogue computer system with a capability to adaptively adjust 18 filter weight coefficients so that the output approached as closely as possible to some target function.

Many of the later developments in adaptive filter structures were aimed specifically at the equalisation of telephone channels for digital data transmission. This class of system is typified by the filters designed by Lucky<sup>(47)</sup> which used a least-mean square criterion to minimise the error function. The least-mean square technique was later refined and developed by Widrow<sup>(48-50)</sup> et al at Stanford and later work by Moschner<sup>(51)</sup> investigated the effects of simplifying the Widrow algorithm.

Most of the work carried out at this point was primarily on the theoretical aspect of the adaptive filter and one of the first attempts at a realistic implementation of the Widrow algorithm was undertaken by Neissen<sup>(52)</sup> and also by Morgan and Craig<sup>(53)</sup>using an 8 tap analogue transversal filter with digital circuitry used to update and store the weight values. Although this work proved

successful, the size and power consumption of the adaptive filter module was to prevent its general use. Later attempts at realising these systems, notably the systems designed by  $\operatorname{Corl}^{(54)}$ , White<sup>(24)</sup> and Copeland<sup>(25)</sup>, were concentrated on minimising the size and power consumption of the adaptive filter by the use of CCDs and LSI techniques. However, in the work mentioned above no attempt was made to optimise the design technique by examination of the error sources within the analogue devices used in the various realisations. This thesis represents the first realistic attempt to evaluate the effect of CCD error sources on the operation of a CCDbased adaptive processor.

### 4.2 Adaptive algorithms

It is clearly possible to calculate the value of  $\underline{H}$  given by equation 4.1 directly, however this would involve a processor of considerable complexity and power. Many algorithms have been proposed which approximate the result and a considerable effort has gone into the theoretical evaluation of these algorithms both by the use of analytical techniques and computer simulations. Using the techniques of direct calculation of  $\underline{H}$  described above is to return essentially to the use of an open loop processor; therefore, by definition, the method of calculation of  $\underline{H}$  to be used in this work was restrained to being an iterative closed loop technique. It was

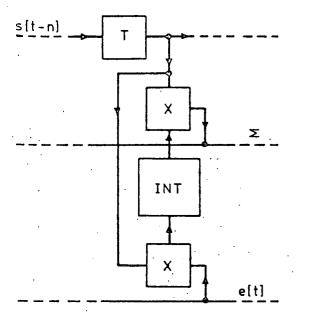

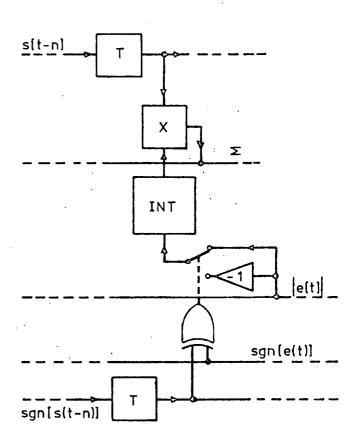

additionally required that the computation needed in order to implement the algorithm should be as simple as possible. The basic algorithm chosen to implement the CCD-based adaptive filter was the Widrow least-mean square (LMS) adaption algorithm<sup>(48)</sup> given by:

$H(t + 1) = H(t) + 2\mu e(t)S(t) \dots (4.2)$

where

e(t) = d(t) - y(t);

y(t) is the filter output; and

$\mu$  is a convergence factor which controls the stability and rate of convergence of the algorithm.

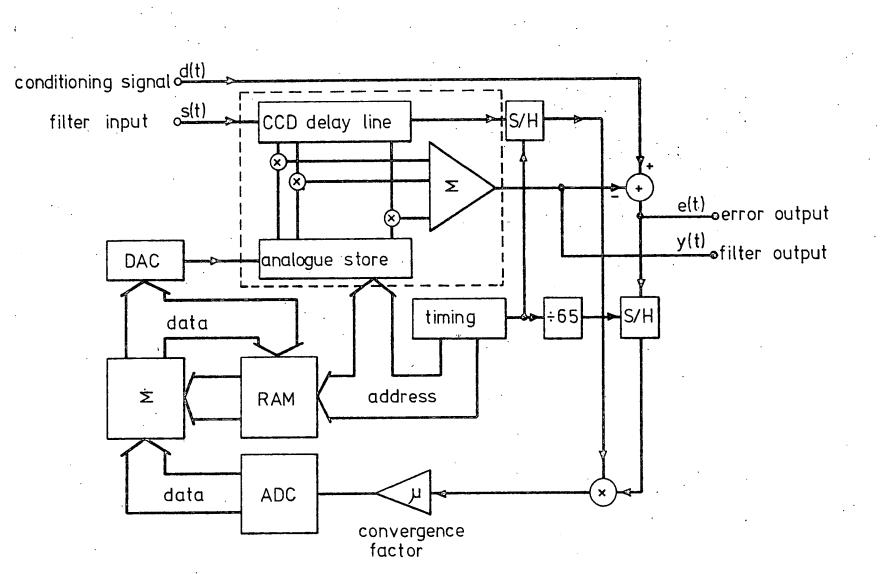

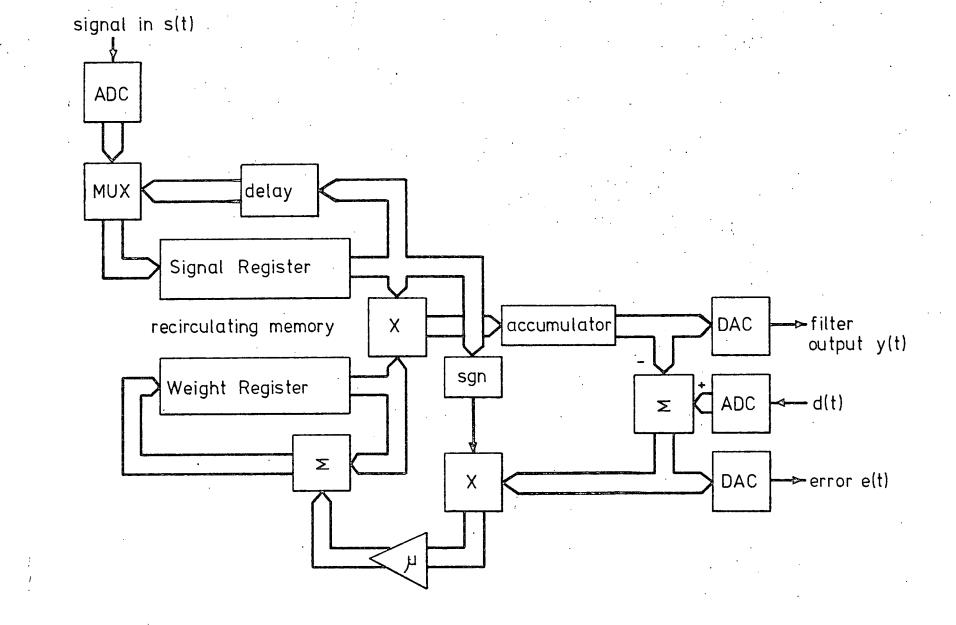

This algorithm uses a single value of the error e(t) to estimate the gradient of a parabolic error surface and then uses this gradient estimate to reduce the error (in a least-mean square sense) by descending towards the minimum point of the error surface: the rate of descent and the eventual accuracy of the result being dependent on the size of  $\mu$ , the convergence factor. A full derivation of the Widrow LMS algorithm may be found in reference 48 and a general block diagram of this system is shown in figure 4.2.

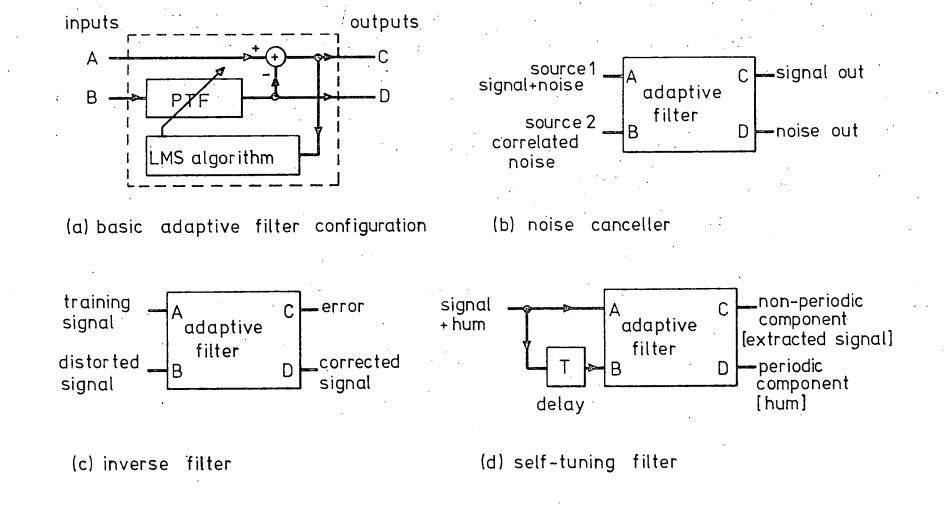

### 4.3 Adaptive filter applications

The same basic adaptive filter unit may be used in many important application areas essentially by changing only the way in which the input and output ports are used. These applications principally involve situations where it

Figure 4.2: Block diagram of an adaptive transversal filter using the linear Widrow LMS adaption algorithm.

:--

is impossible to predict the characteristics of the environment through which a signal must travel.

There are two basic characteristics of an adaptive filter which must be considered when such a system is applied in a practical manner:

(1) Any component of the s(t) input correlated with any component of the d(t) input will be reproduced at y(t) in such a way to subtract coherently from d(t). Any component of s(t) uncorrelated with d(t) will be suppressed by the filter. Any component of d(t)uncorrelated with s(t) will remain at the e(t) output.

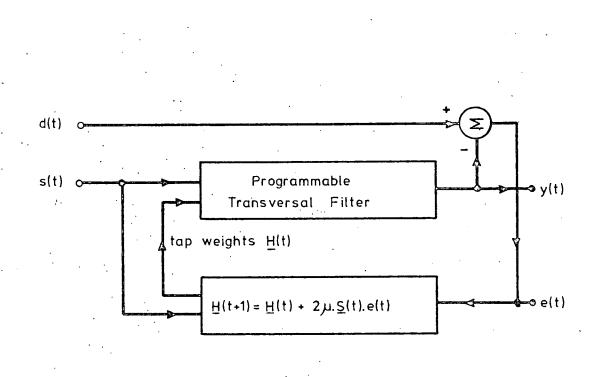

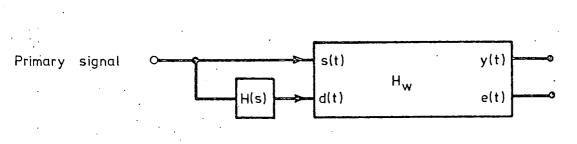

(2) Many applications essentially use the system modelling ability of the filter (see figure 4.3). That is, if there is only one primary signal which is the input to an unknown system and both input and output of this system are available, then if s(t) is the primary signal source and d(t) is the system output the optimum adaptive filter impulse response is the same as that of the unknown system. If s(t) is the unknown system output and d(t) the primary input signal then the optimum adaptive filter transfer function is the inverse of that of the unknown system.

Using these two basic characteristics we may now consider some of the major application areas to which the adaptive filter may be applied.

(A) Medical electronics: This was one of the first areas

$H_w = H(s)$

Figure 4.3: Configuration of the idealised adaptive filter in the two system modelling modes of operation.

in which adaptive filters were applied (48), principally in the role of noise cancellers (see figure 4.4(b)). In this configuration the primary signal (that containing the desired information) is applied to the d(t) input. This signal is contaminated by a spurious signal from a secondary source. A sample of this secondary signal may be obtained from another source (uncontaminated by the required signal) which is correlated with the interference on the primary signal. This correlated signal is applied to the s(t) input and the filter forms an impulse response which yields an output y(t) which subtracts coherently the unwanted component from d(t) leaving the desired signal on the e(t) output.

An example of the use of this technique is in the monitoring of foetal heartbeat, where the primary signal is obtained from a transducer array on the mother's abdomen. There transducers yield a signal containing the foetal heart signal heavily masked by the mother's heartbeat. The secondary signal registering only the mother's heartbeat is then obtained from a transducer array on the mother's chest. The adaptive filter then models the distorting path from the chest to the abdominal transducers to produce the signal which coherently subtracts from the abdominal signal.

(B) Speech processing: Here the major impact (aside from communications processing) occurs when speech is contaminated by periodic (or pseudo-periodic) signals or

Figure 4.4: Use of an adaptive filter in three basic applications

$\mathbf{v}_{i}$

by so-called 'convolutional' noise<sup>(55)</sup>. The first problem occurs for instance in trying tc record speech in a room where music is being played (the musical tones in general last long enough to be considered periodic) or where constant interference exists (eg. hum or whistle on HF radio reception). This type of problem may combated by the use of the self-tuning filter configuration shown in figure 4.4(c). Here the delay between the d(t) and the s(t) inputs is sufficient to decorrelate any non-periodic signal existing at the input. The filter then suppresses the non-periodic signal leaving the periodic component on the y(t) output, which subtracts coherently from the d(t) output. The speech may be viewed as an essentially non-periodic random signal and can therefore be stripped of interfering hum or musical tones by using this configuration of adaptive filter.

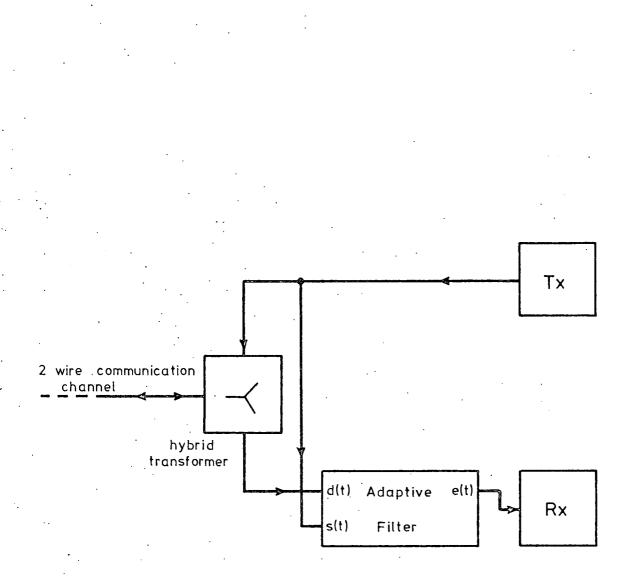

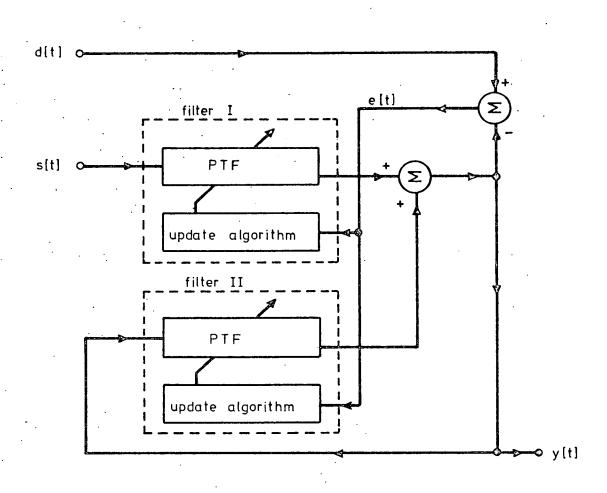

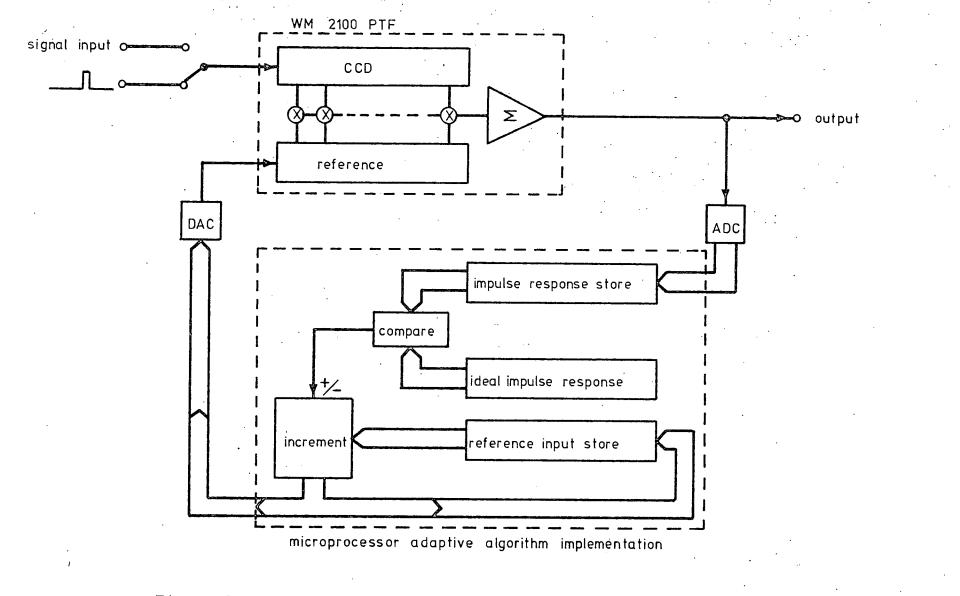

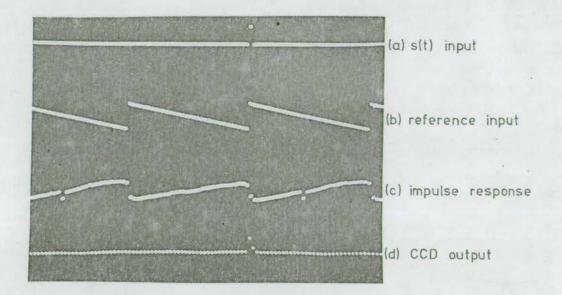

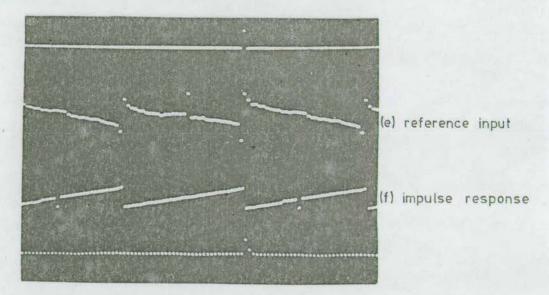

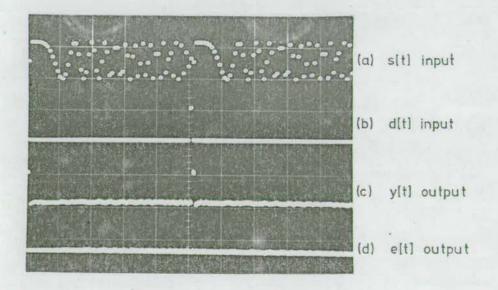

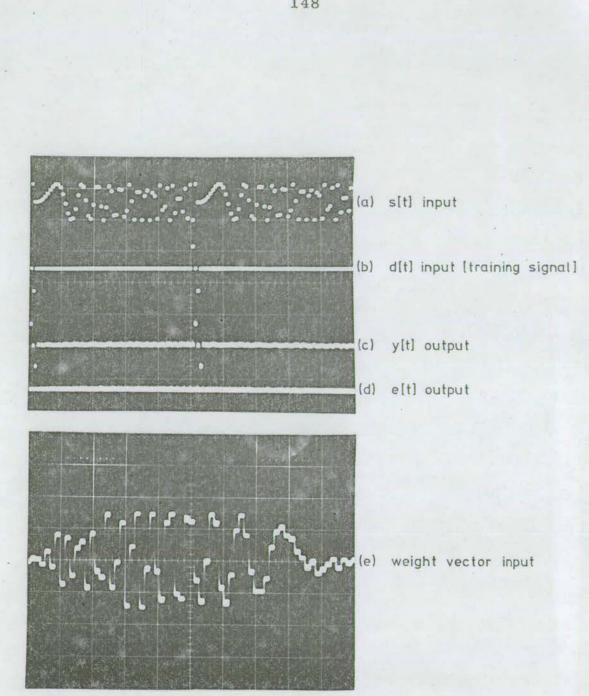

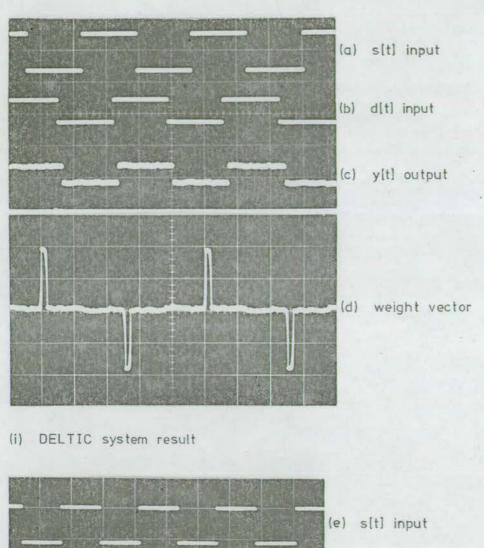

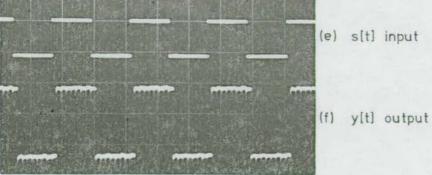

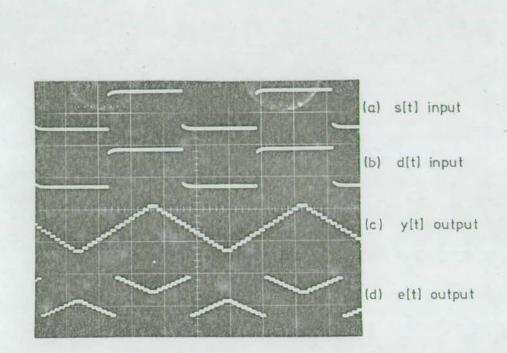

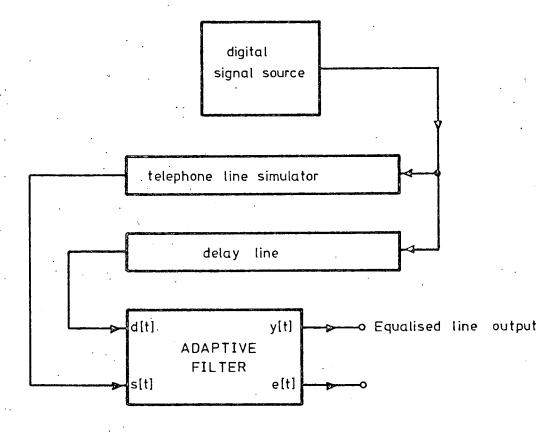

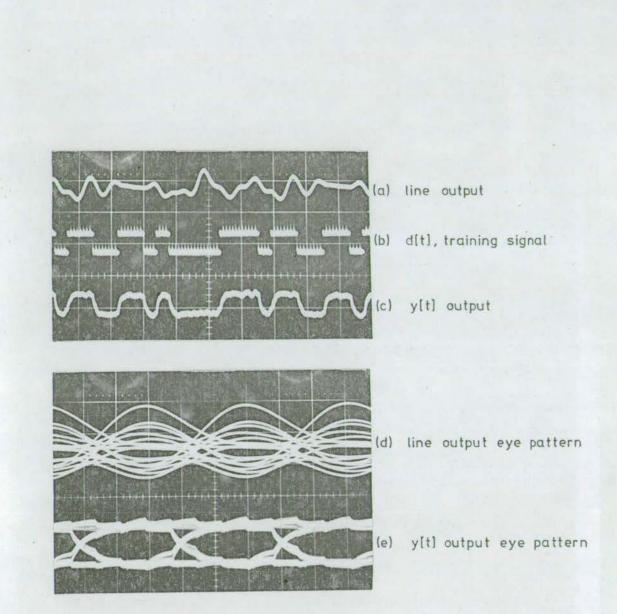

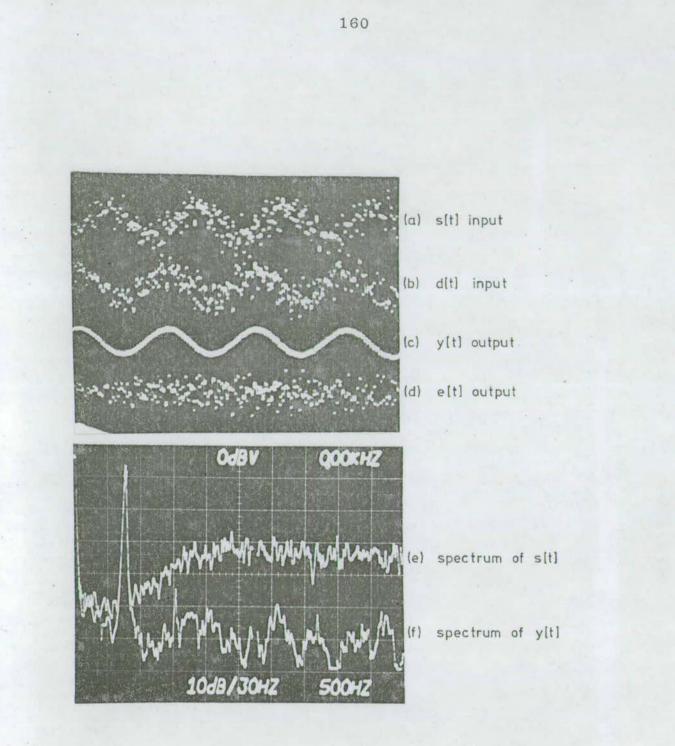

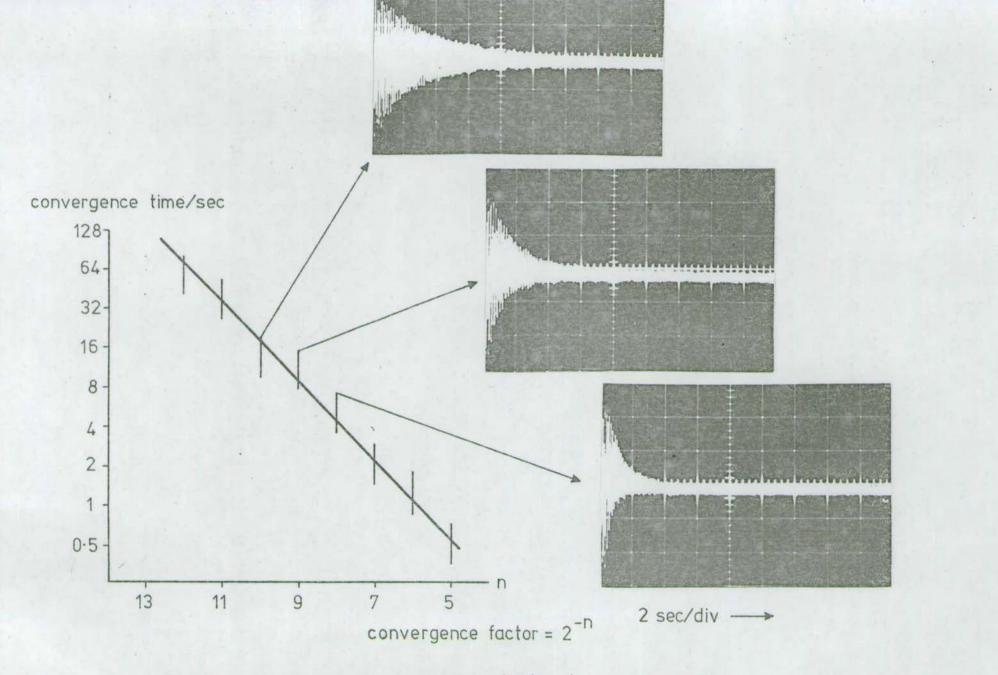

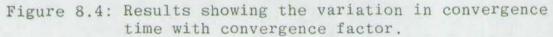

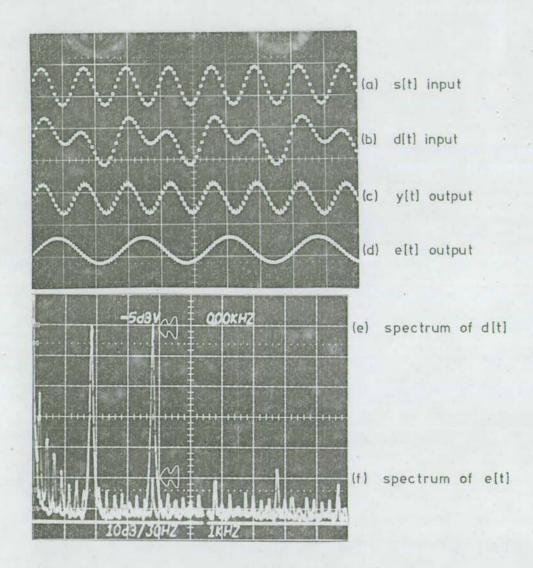

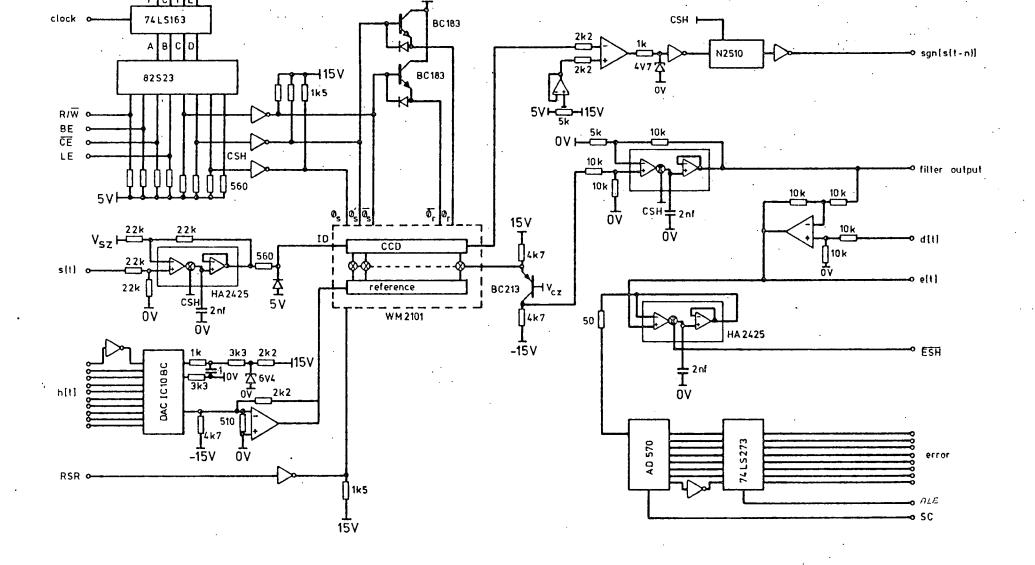

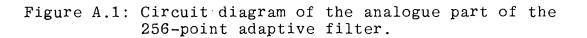

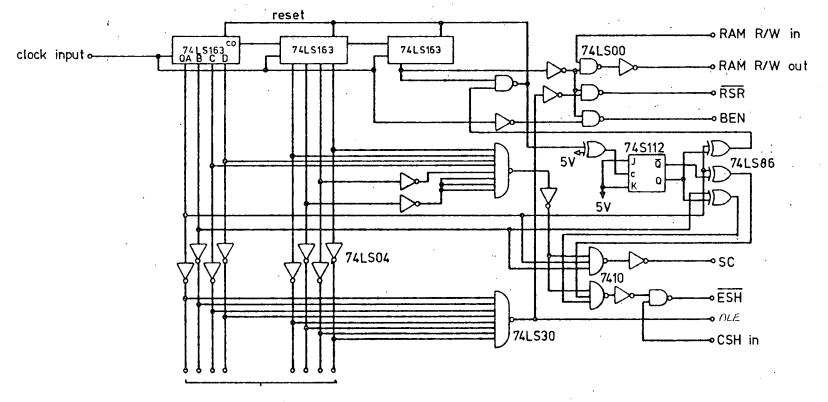

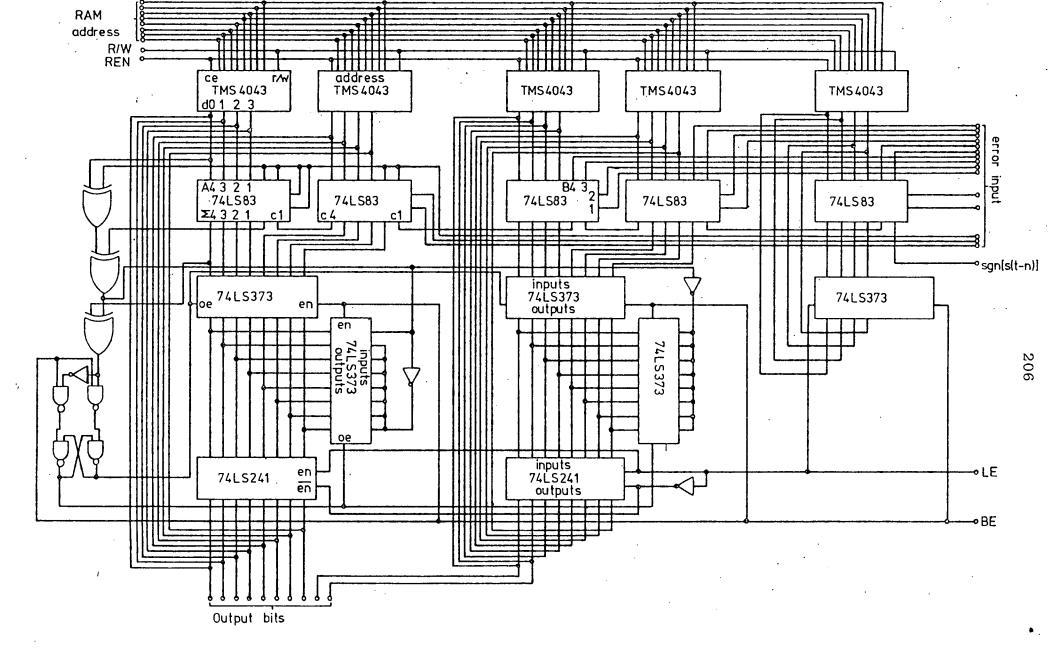

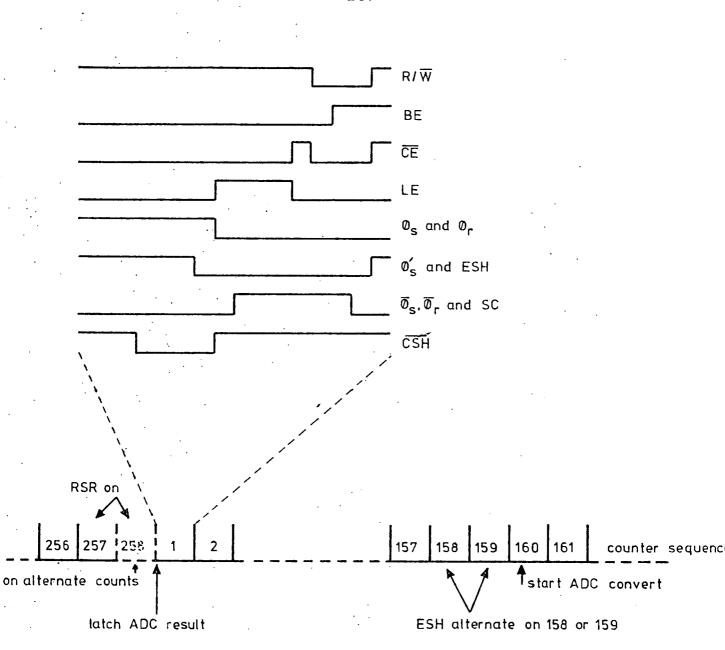

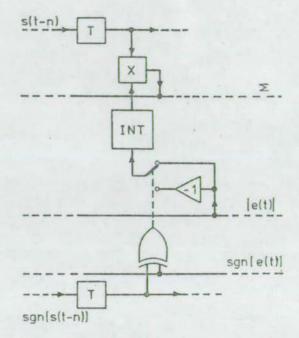

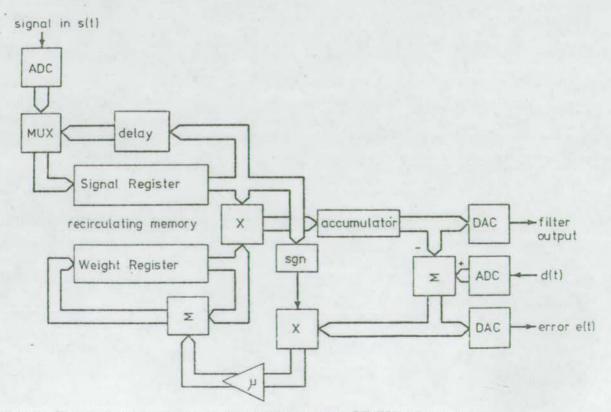

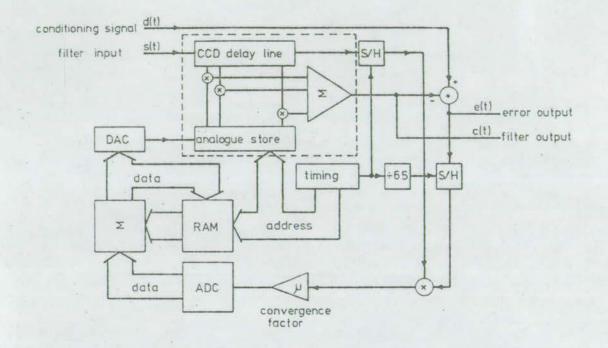

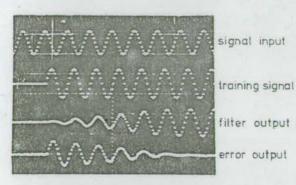

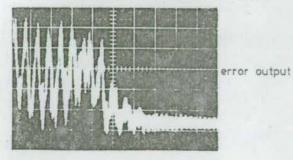

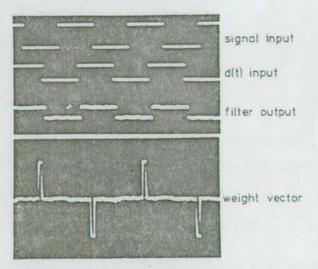

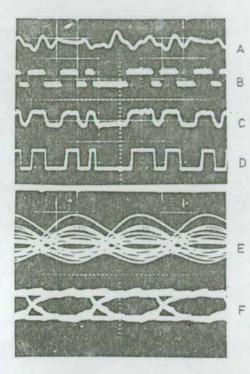

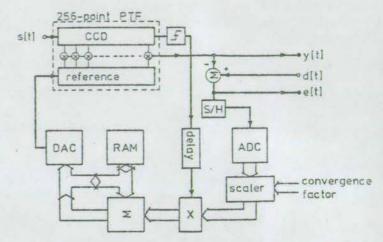

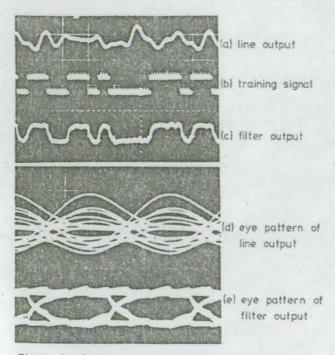

(C) Communications processing: Applications for adaptive filtering in communications processing exist mainly in the field of digital data transmission over switched voice-bandwidth telephone lines (47,52,56). The specific problems encountered are those of echo and distortion. With fixed telephone links these effects are not really problematical since fixed equalisers may be constructed to compensate for a known data link. However, when the switched network is used each reconnection results in a different set of distortion and echo parameters. It is therefore necessary to use an adaptive equalisation scheme which is capable of learning the optimum