# The Design of a Sparse Vector Processor

# T.M. Hopkins

# Ph.D.

University of Edinburgh

1993

#### Abstract

This thesis describes the development of a new vector processor architecture capable of high efficiency when computing with very sparse vector and matrix data, of irregular structure.

Two applications are identified as of particular importance: sparse Gaussian elimination, and Linear Programming, and the algorithmic steps involved in the solution of these problems are analysed. Existing techniques for sparse vector computation, which are only able to achieve a small fraction of the arithmetic performance commonly expected on dense matrix problems, are critically examined. A variety of new techniques with potential for hardware support is discussed. From these, the most promising are selected, and efficient hardware implementations developed.

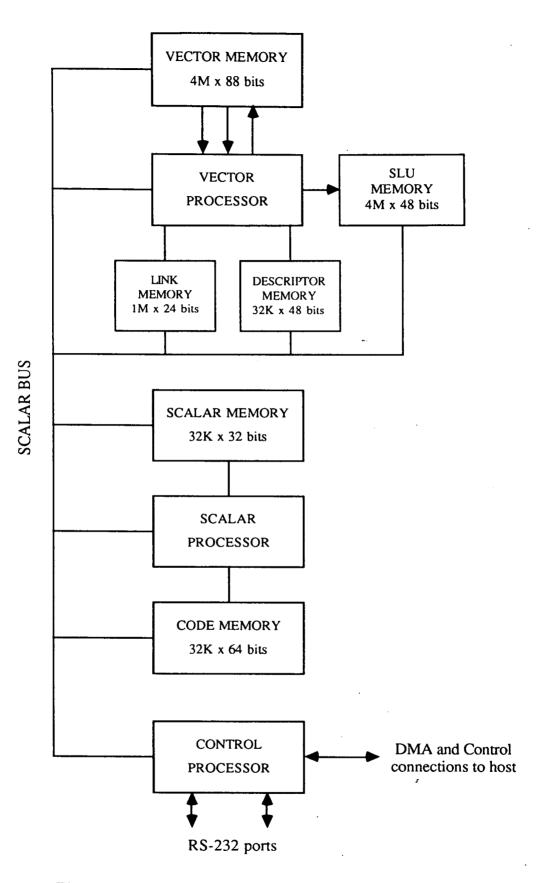

The architecture of a complete vector processor incorporating the new vector and matrix mechanisms is described – the new architecture also uses an innovative control structure for the vector processor, which enables high efficiency even when computing with vectors with very small numbers of non-zeroes. The practical feasibility of the design is demonstrated by describing the prototype implementation, under construction from off-the-shelf components.

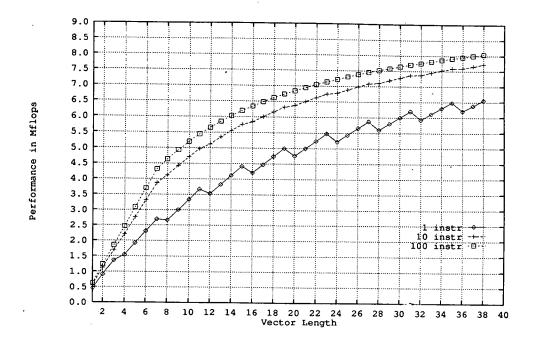

The expected performance of the new architecture is analysed, and simulation results are presented which demonstrate that the machine could be expected to provide an order of magnitude speed-up on many large sparse Linear Programming problems, compared to a scalar processor with the same clock rate. The simulation results indicate that the vector processor control structure is successful – the vector half-performance length is as low as 8 for standard vector instruction loop tests. In some cases, simulations indicate that the performance of the machine is limited by the speed of some scalar processor operations.

Finally, the scope for re-implementing the new architecture in technology faster than the prototype's 8MHz is briefly discussed, and particular potential difficulties identified.

# Declaration

I hereby declare

- that this thesis has been composed by myself; and

- that the work described herein is my own, except where stated in the text.

T.M. Hopkins 22nd January 1993

### Acknowledgements

Many thanks are due to my supervisor, Roland Ibbett, for his advice, patience, and friendly encouragement of this work, and for setting up and managing the ESP project. The weekly meetings of the group working on ESP have provided many useful ideas, and other members of the group have also been of great help. Ken McKinnon, in particular, carried out the Linear Programming simulation study, and through conversations with him, many useful changes have been made to the ESP architecture. On the machine itself, Rainer Thonnes has carried out the detailed circuit design, and Peter Lindsay is wiring the many thousands of connections. Two students in the Department of Computer Science, Alisdair Manning and Goh Boon Seng, contributed greatly by developing further simulations of the ESP architecture.

The author's research work was for a time supported by the Science and Engineering Research Council, who, together with High Level Hardware Ltd., have also supported the construction of the prototype machine. All other facilities for this research have been provided by the Department of Computer Science.

# Table of Contents

| 1. | Intr              | roduction                                   |                                                |                            |  |  |

|----|-------------------|---------------------------------------------|------------------------------------------------|----------------------------|--|--|

|    | 1.1               | Superc                                      | computer architectures                         | 1                          |  |  |

|    |                   | 1.1.1                                       | Vector processing                              | 2                          |  |  |

|    |                   | 1.1.2                                       | Parallel processing                            | 4                          |  |  |

|    |                   | 1.1.3                                       | Using vector and parallel machines             | 6                          |  |  |

|    | 1.2               | Sparse                                      | e matrix problems                              | 7                          |  |  |

|    |                   | 1.2.1                                       | Use of vector processors for sparse problems   | <b>9</b> .                 |  |  |

|    |                   | 1.2.2                                       | Use of parallel processors for sparse problems | 10                         |  |  |

|    | 1.3               | The E                                       | dinburgh Sparse Processor project              | 11                         |  |  |

|    |                   |                                             |                                                |                            |  |  |

| 2. | Spa               | rse Ma                                      | atrix Algorithms                               | 14                         |  |  |

| 2. | <b>Spa</b><br>2.1 |                                             | atrix Algorithms<br>uction                     | <b>14</b><br>14            |  |  |

| 2. | -                 | Introd                                      |                                                |                            |  |  |

| 2. | 2.1               | Introd                                      | uction                                         | 14                         |  |  |

| 2. | 2.1               | Introd<br>Direct                            | uction                                         | 14<br>15                   |  |  |

| 2. | 2.1               | Introd<br>Direct<br>2.2.1                   | uction                                         | 14<br>15<br>16             |  |  |

| 2. | 2.1               | Introd<br>Direct<br>2.2.1<br>2.2.2          | uction                                         | 14<br>15<br>16<br>17       |  |  |

| 2. | 2.1               | Introd<br>Direct<br>2.2.1<br>2.2.2<br>2.2.3 | uction                                         | 14<br>15<br>16<br>17<br>17 |  |  |

.

.

|    |     | 2.2.7   | Size and sparsity of typical problems                        | 20 |

|----|-----|---------|--------------------------------------------------------------|----|

|    | 2.3 | Iterati | ve solution of linear equations                              | 21 |

|    | 2.4 | Linear  | Programming                                                  | 22 |

|    |     | 2.4.1   | The simplex method                                           | 22 |

|    |     | 2.4.2   | Computational steps in the revised simplex method            | 25 |

|    |     | 2.4.3   | Size and sparsity of typical LP problems                     | 28 |

|    | 2.5 | Summ    | ary                                                          | 29 |

| 3. | Imp | olemen  | ting Sparse Matrix Computation                               | 31 |

|    | 3.1 | Introd  | uction                                                       | 31 |

|    | 3.2 | Array   | storage for vectors                                          | 32 |

|    | 3.3 | The o   | rder vector mechanism                                        | 34 |

|    |     | 3.3.1   | Handling fill-in in the order vector method                  | 36 |

|    | 3.4 | The ir  | ndex/value array mechanism                                   | 37 |

|    |     | 3.4.1   | In-phase scan implementations of arithmetic                  | 38 |

|    |     | 3.4.2   | Scatter/gather implementations of arithmetic                 | 39 |

|    |     | 3.4.3   | Comparison of in-phase scan and scatter/gather methods $\ .$ | 42 |

|    | 3.5 | The ir  | ndex/value list mechanism                                    | 43 |

|    | 3.6 | Assoc   | iative memory storage                                        | 44 |

|    | 3.7 | Other   | data structure candidates                                    | 47 |

|    |     | 3.7.1   | Tree structures                                              | 48 |

|    |     | 3.7.2   | Hash table based structures                                  | 49 |

|    | 3.8 | Data s  | structures for whole matrices                                | 50 |

|    | 3.9 | A vect  | tor storage mechanism for ESP                                | 51 |

.

.

| 4. | Spa | rse Ma  | atrix Mechanisms in ESP                                        | 56 |

|----|-----|---------|----------------------------------------------------------------|----|

|    | 4.1 | The a   | rray form                                                      | 56 |

|    | 4.2 | The lis | st form                                                        | 57 |

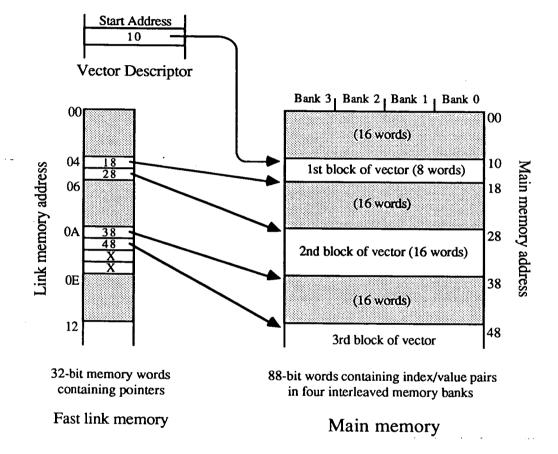

|    |     | 4.2.1   | Implementing linked lists in a single-level memory environment | 59 |

|    |     | 4.2.2   | Implementing linked lists in a hierarchical memory environ-    |    |

|    |     |         | ment                                                           | 60 |

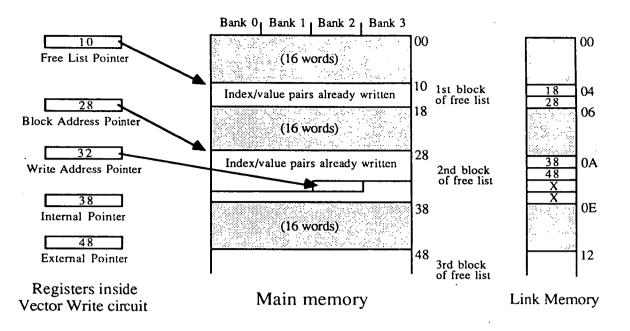

|    |     | 4.2.3   | Writing list vectors                                           | 64 |

|    |     | 4.2.4   | Freeing list vector space                                      | 65 |

|    | 4.3 | Indired | ction and vector registers                                     | 68 |

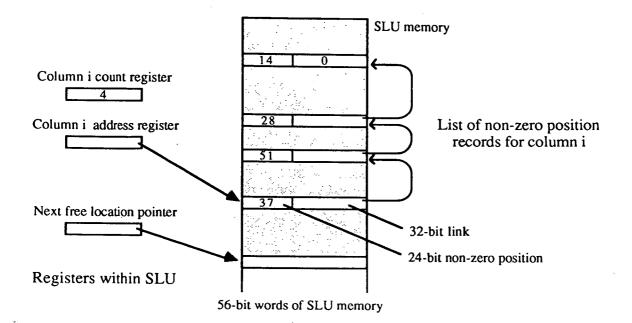

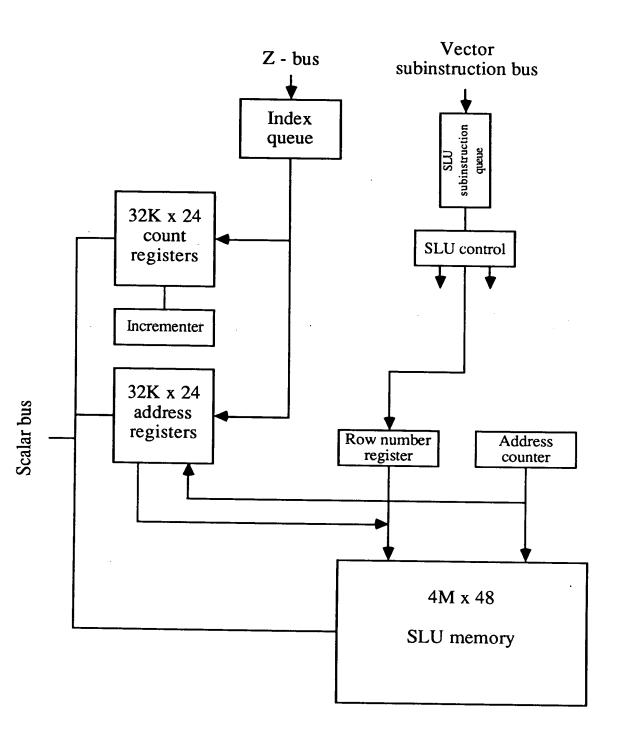

|    | 4.4 | The Si  | ideways List Unit                                              | 69 |

|    | 4.5 | Summ    | ary                                                            | 72 |

| 5. | The | Archi   | tecture of ESP                                                 | 73 |

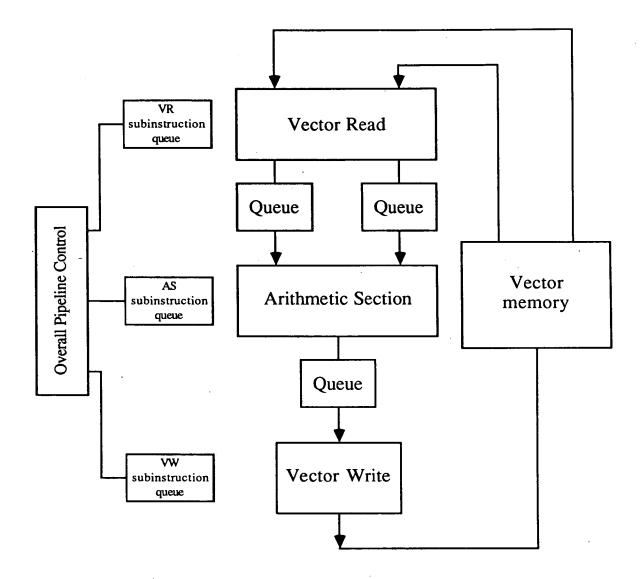

|    | 5.1 | Genera  | al structure                                                   | 73 |

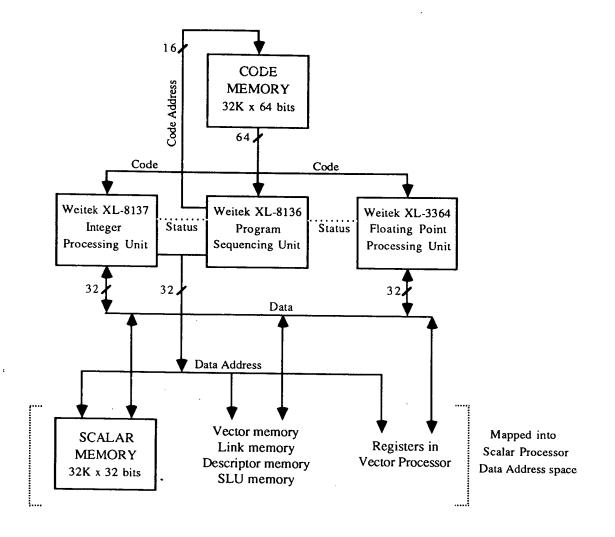

|    | 5.2 | The sc  | calar processor and associated memories                        | 77 |

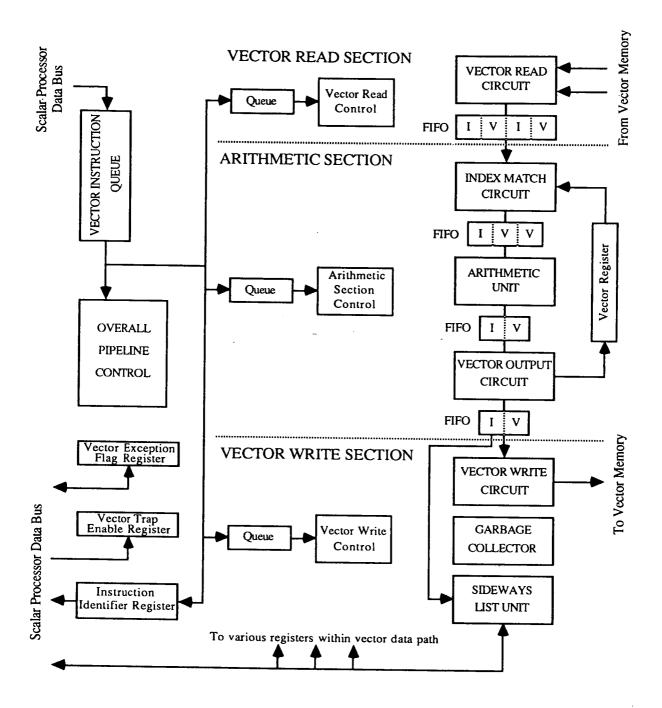

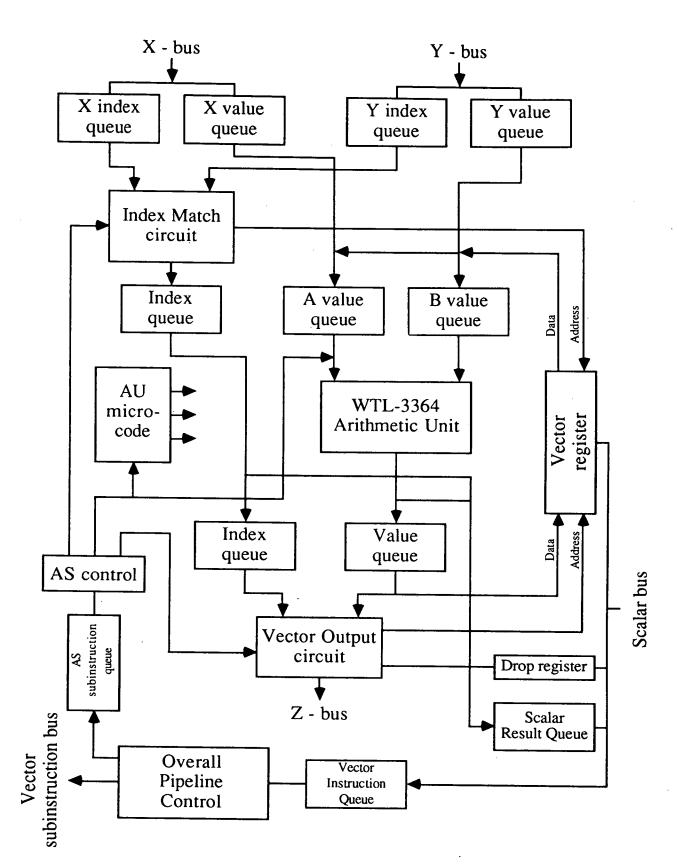

|    | 5.3 | The ve  | ector processor                                                | 78 |

|    |     | 5.3.1   | Vector instructions                                            | 79 |

|    |     | 5.3.2   | Instruction decode and control                                 | 83 |

|    |     | 5.3.3   | The Vector Read circuit                                        | 84 |

|    |     | 5.3.4   | The Index Match circuit                                        | 85 |

|    |     | 5.3.5   | The Arithmetic Unit                                            | 86 |

|    |     | 5.3.6   | The Vector Output circuit                                      | 87 |

|    |     | 5.3.7   | The Vector Write circuit                                       | 87 |

|    |     | 5.3.8   | The Garbage Collection circuit                                 | 88 |

|    |     | 5.3.9   | The Sideways List Unit                                         | 88 |

.

,

•

|    | 5.4            | The ir | nterface between the scalar and vector processors $\ldots$ $\ldots$ $\ldots$ | 89  |

|----|----------------|--------|------------------------------------------------------------------------------|-----|

|    |                | 5.4.1  | Instruction transfer                                                         | 89  |

|    |                | 5.4.2  | Synchronisation between the scalar and vector processors .                   | 90  |

|    |                | 5.4.3  | Data transfer between the processors                                         | 91  |

|    |                | 5.4.4  | Vector exceptions                                                            | 91  |

|    | 5.5            | The co | ontrol processor                                                             | 92  |

|    | 5.6            | The ir | struction set                                                                | 93  |

| 6. | $\mathbf{The}$ | Imple  | ementation of ESP                                                            | 96  |

|    | 6.1            | Introd | uction                                                                       | 96  |

|    | 6.2            | Basic  | design decisions                                                             | 96  |

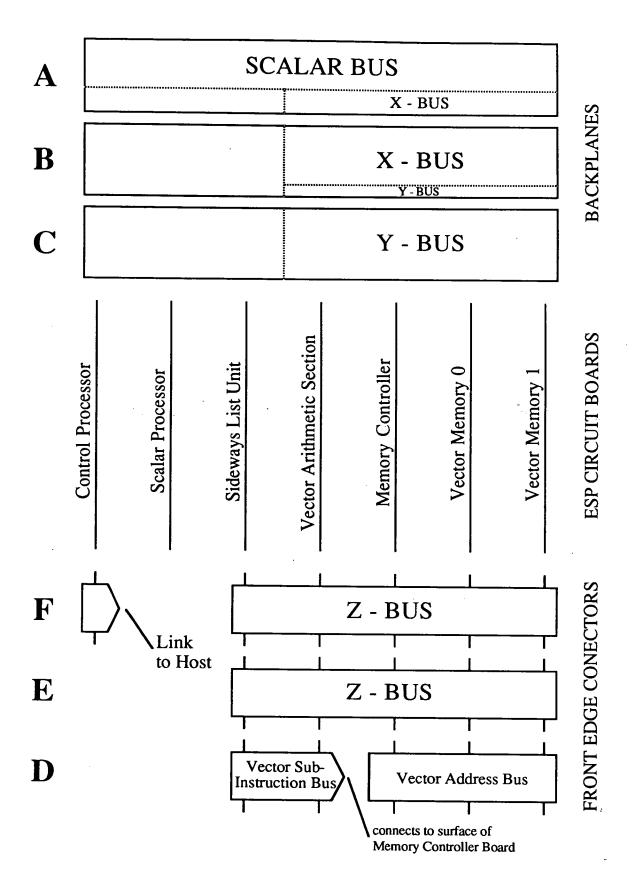

|    | 6.3            | Physic | cal partitioning of the machine                                              | 98  |

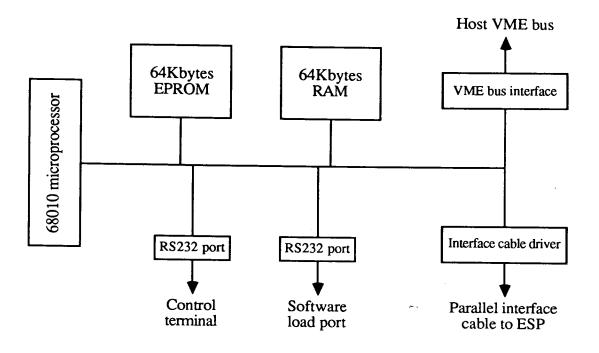

|    | 6.4            | The h  | ost interface board                                                          | 101 |

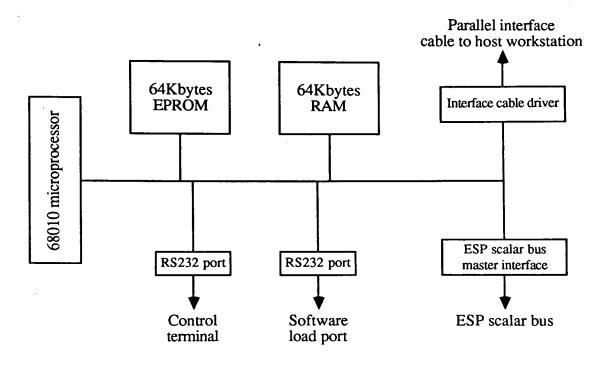

|    | 6.5            | The co | ontrol processor                                                             | 103 |

|    |                | 6.5.1  | The scalar bus                                                               | 104 |

|    | 6.6            | The h  | ost interface software                                                       | 105 |

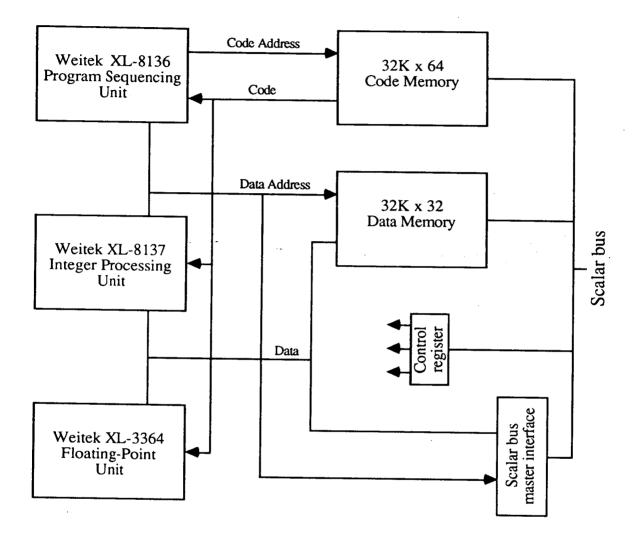

|    | 6.7            | The so | calar processor                                                              | 105 |

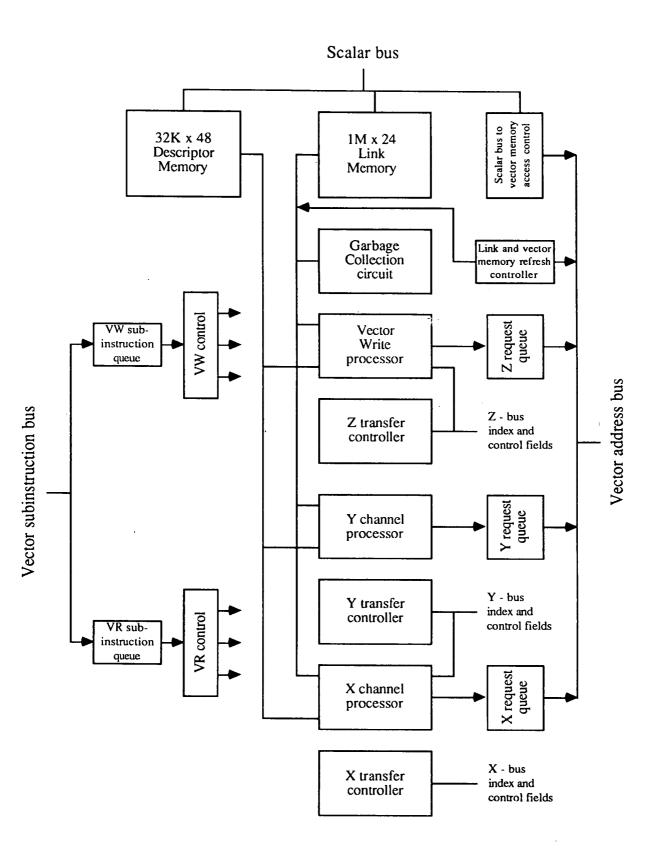

|    | 6.8            | The m  | emory controller                                                             | 107 |

|    |                | 6.8.1  | The Vector Read circuitry                                                    | 109 |

|    |                | 6.8.2  | The Vector Write circuitry                                                   | 111 |

|    |                | 6.8.3  | The Garbage Collection circuitry                                             | 112 |

|    |                | 6.8.4  | Vector memory request arbitration                                            | 113 |

|    |                | 6.8.5  | The data transfer controllers                                                | 114 |

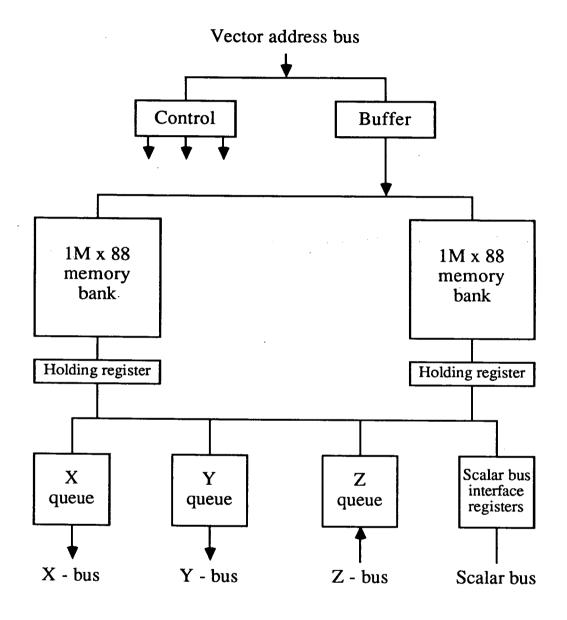

|    | 6.9            | The ve | ector memory                                                                 | 116 |

|    | 6.10           | The ve | ector Arithmetic Section                                                     | 119 |

.

|    |      | 6.10.1          | The Index Match circuit               | 120 |

|----|------|-----------------|---------------------------------------|-----|

|    |      | 6.10.2          | The Arithmetic Unit                   | 122 |

|    |      | 6.10.3          | The Vector Output circuit             | 123 |

|    | 6.11 | The Sid         | leways List Unit                      | 123 |

|    | 6.12 | Testing         | ESP                                   | 124 |

| 7. | The  | Perform         | mance of ESP                          | 127 |

|    | 7.1  | Introdu         | ction                                 | 127 |

|    | 7.2  | The LP          | simulation study                      | 130 |

|    |      | 7.2.1           | The model                             | 130 |

|    |      | 7.2.2           | The results                           | 131 |

|    | 7.3  | The firs        | t SIM++ simulation study              | 134 |

|    |      | 7.3.1           | Γhe model                             | 134 |

|    |      | 7.3.2           | The results                           | 136 |

|    | 7.4  | The sec         | ond SIM++ simulation study            | 138 |

|    |      | 7.4.1           | The model                             | 138 |

|    |      | 7.4.2 I         | Results for vector instruction loops  | 139 |

|    |      | 7.4.3 H         | Results for Gaussian elimination      | 142 |

|    | 7.5  | Summar          | y                                     | 144 |

| 8. | Sum  | mary a          | nd Conclusion                         | 147 |

|    | 8.1  | Evaluati        | on of the ESP architecture            | 148 |

|    |      | 8.1.1 7         | The sparse vector handling mechanisms | 149 |

|    |      | 8.1.2 T         | The Sideways List Unit                | 149 |

|    |      | 8.1. <b>3</b> 7 | The vector pipeline control strategy  | 151 |

|             | 8.1.4     | The scalar processor/vector processor interface | 151 |

|-------------|-----------|-------------------------------------------------|-----|

|             | 8.1.5     | The implementation                              | 152 |

|             | 8.1.6     | Scalability of the design                       | 153 |

| 8.2         | 2 Evalua  | tion of the design methodology                  | 154 |

| 8.3         | 3 Furthe  | r work on ESP                                   | 156 |

| 8.4         | 4 Conclu  | ision                                           | 157 |

| Bibli       | ography   |                                                 | 159 |

| <b>A. T</b> | he Vecto  | r Processor Instruction Set                     | 164 |

| А.          | 1 Vector  | Read circuit instructions                       | 165 |

|             | A.1.1     | Two operand output modes                        | 165 |

|             | A.1.2     | Single operand output modes                     | 166 |

|             | A.1.3     | Null mode                                       | 166 |

|             | A.1.4     | Instruction termination                         | 166 |

| A           | .2 Index  | Match circuit instructions                      | 167 |

|             | A.2.1     | I/V/V triple output modes                       | 167 |

|             | A.2.2     | I/V pair output modes                           | 168 |

|             | A.2.3     | Instruction termination                         | 169 |

| A           | .3 Arithr | netic Unit instructions                         | 169 |

|             | A.3.1     | Data movement operations                        | 170 |

|             | A.3.2     | Arithmetic operations                           | 171 |

|             | A.3.3     | Logical operations                              | 174 |

|             | A.3.4     | Special operations                              | 175 |

|             | A.3.5     | Instruction termination                         | 175 |

-

.

| . в | 8. Rep | orint of | published paper                 | 179 |

|-----|--------|----------|---------------------------------|-----|

|     |        | A.5.2    | Instruction termination         | 178 |

|     |        | A.5.1    | Sideways List Unit instructions | 178 |

|     | A.5    | Vector   | Write circuit instructions      | 177 |

|     |        | A.4.1    | Instruction termination         | 176 |

|     | A.4    | Vector   | Output circuit instructions     | 176 |

.

# Chapter 1

# Introduction

# **1.1** Supercomputer architectures

Most of the largest and most time-consuming numerical computer applications involve data in the form of vectors and matrices. Computing with such data requires large numbers of arithmetic operations, each acting on single elements of the vectors or matrices involved. The standard way of coding such a computation in, for example FORTRAN (most scientific and engineering programs have, since the 1960's, been written one or another version of FORTRAN), is as a nest of DO loops indexing through FORTRAN ARRAYs of one or more dimensions, and this coding implies sequential execution of the elemental arithmetic operations. However, these arithmetic operations can to a very large extent be carried out in any order, without affecting the result, or they can be done simultaneously, and thus these algorithms exhibit a degree of potential parallelism. The finest-grained parallelism, between the elemental parts of a single vector operation, is homogenous, in the sense that each of the parallel operations is identical, although each operates on different data. Many numerical computations also exhibit potential parallelism at higher levels, between separate vector operations, and between even larger chunks of code. This coarser-grained parallelism is often heterogenous - it involves different operations, which can be carried out in parallel.

Conventional computers are often able to overlap individual instructions, and in some cases this process is assisted by executing instructions in a slightly different order from that defined by the program code itself. The maximum speed of most conventional machines is limited by the fact that they can issue at most

1

one instruction per clock cycle, although the latest superscalar architectures are able to average less than one cycle per instruction. However, all these standard scalar processors are unable to take advantage of any of the levels of parallelism described above. As there appears to be no limit to the size of numerical problem which scientists and engineers can find good reason to solve (even on the fastest machines available today, crucial numerical problems in fundamental physics take months to solve), much effort has been spent, over three decades, in developing improved computer architectures which can solve these problems faster. To do so requires extra hardware, and that hardware has been arranged in one of two general ways. Vector processors incorporate a pipeline of hardware elements for executing, in sequence, each step of a single vector elemental operation (address calculation, data fetch, arithmetic and data store). Several elemental operations may be in execution simultaneously, in different stages of the pipeline, and this design takes advantage of the finest-grained parallelism described above. Parallel processors contain a number of identical processing units. Depending on the control arrangement, a parallel processor may be able to exploit fine- or coarse-grained parallelism in an algorithm.

#### 1.1.1 Vector processing

Early examples of vector processors were the STAR-100 [24], later redeveloped into the CYBER-205 [12], and the CRAY-1 [43]. The vector pipeline in these machines is split into several tens of stages, through which a vector elemental operation flows, one stage per clock cycle. When the pipeline is fully busy, a different vector elemental operation is in execution in each pipeline stage, and one elemental operation is completed per clock cycle. With this number of pipeline stages, each stage can be kept simple, and the clock cycle is correspondingly fast. An entire vector arithmetic operation is performed as a result of the issue of a single vector instruction, which specifies the whereabouts of the vector operands, the elemental operation to be performed (add, scalar product, etc), and the number of elemental operations to be performed. The circuits required to perform a floating-point add and a floating-point multiply are different, and separate add and multiply units are therefore provided (each of which is split over several pipeline stages). Vector processors can therefore include vector instructions which use both these arithmetic units, to implement vector operations requiring both multiplication and addition (eg scalar product), and so, on these instructions, the peak floating point performance of a single vector processor is two floating point operations (one add and one multiply) per clock cycle.

In practice, it is difficult to obtain anything approaching this peak performance from a vector processor, for two principal reasons. Firstly, although once a vector instruction has got started, it proceeds at the rate of one elemental operation completed (one or two floating-point operations performed) per clock cycle, the instructions take a considerable time to start up. The instruction must be decoded, the vector processor must be configured, and the first elemental operation must pass through the length of the pipeline, before the first result is produced. The start-up time for the CRAY X-MP [13] (the successor to the CRAY-1) is around 50 cycles, while for the CYBER-205 it is closer to 100 [25]. As a result, the overall performance of a vector instruction is only close to the peak performance if the vector operands are long; if the operands have the same number of elements as the number of cycles start-up time, for example, the overall floating point performance of a vector instruction can be no more than half the peak.

The second reason that processor performance may be much less than the theoretical peak is that application programs do not consist entirely of operations on vectors; much of the code involves operations on single scalar values, and control operations. As a result, the vector processing hardware may be idle much of time, while the machine executes scalar instructions. (The fact that the speed-up available through the use of a vector processor is limited by the fraction of the code which must execute on the scalar processor is known as "Amdahl's law" [6].) This problem can be alleviated by careful algorithm design, including the use of optimised hand-written assembler code, but it is also important that the processor is able to carry out scalar operations fast enough to balance the vector processor speed. The biggest failing of the commercially unsuccessful STAR-100 design, corrected in its successor, the CYBER-205, was the poor scalar performance.

The mechanisms used to synchronise the execution of scalar and vector instructions are also important in this respect.

Since the introduction of the first commercial vector machine, the CRAY-1, in 1976, vector processing has been highly successful, with vector machines in widespread use for numerically demanding applications. Other successful machines include the CDC CYBER-205, the CRAY X-MP, CRAY Y-MP and CRAY-2 ranges, Japanese machines such as the Fujitsu FACOM series, the Hitachi HITAC and the NEC SX1 and SX2 (described in [25]), and the vector processor version of IBM's mainframe series, the IBM 3090VF [10]. More recently, however, there has also been much interest in the parallel processing alternative.

### 1.1.2 Parallel processing

Parallel numerical processing involves the use of more than one arithmetic processor simultaneously. However, parallel machines differ in their number of processors, in the way in which instructions are issued to the separate arithmetic units, and in the way that memory access is organised.

#### Array processors

One way of organising the use of parallel identical arithmetic units is to build them into a processor which fetches a single stream of instructions which operate on replicated data structures, such as vectors and matrices, but in which the arithmetic operation(s) for each element in the operand structures are performed in a different processor. Execution of the elemental operations proceeds in parallel. The number of processing units may be a hundred or more, and each accesses data from its own memory. Vectors/matrices are distributed through the memory banks in a suitable way before computation commences, and instructions cause all the processing units to operate simultaneously. A limited degree of variation in instruction execution between different processors is usually supported – a flag in each processor may disable instruction execution, on a processor by processor basis, or an address register in each processor may allow different processors to carry out the same instruction on data stored at different addresses. These machines are commonly known as array processors or SIMD (Single Instruction Multiple Data) parallel processors. The first such machine to be built was the ILLIAC IV [18], an experimental design. The Burroughs BSP [8] was developed in the light of experience with the ILLIAC IV, but was not exploited commercially, while commercial array processors include the ICL DAP [40] and its successor, the AMT mini-DAP from Active Memory Technology Ltd., and the Thinking Machines CM-1 [23] and CM-2. In the DAP and CM machines, the individual arithmetic units are much slower than those used in vector processors. The high level of parallelism, however, (the CM-1 can be configured with 65,536 processors) means that very high overall arithmetic rates can be achieved, but only on vectors/matrices with very large numbers of elements. Also, the distribution of data must be carefully arranged, and hence programming is more difficult than for the vector processors.

#### **Multiprocessors**

Other parallel processors fetch a separate instruction stream for each processor – the processors are executing separate program threads, but can communicate data, and synchronise with each other. These machines are commonly called *multiprocessors* or *MIMD* (Multiple Instruction Multiple Data) machines. In machines with a small number of processors, the processors may share a common memory; examples include the **IBM** range of mainframe multiprocessors, and the **Sequent Balance** series (described in [27]). Access to the shared memory soon becomes a bottleneck as the number of processors is increased, and so machines with more than a few processors use large caches or local memory for each processor, in addition to the shared memory. Alternatively, all the memory may be physically distributed at the processors, but with each processor's memory mapped into the other processors' address spaces, and accessible via a high-bandwidth interconnection, as in the **BBN Butterfly** [41]. Other multiprocessor machines use no shared memory at all – each processor operates with program and data held in a local memory, and a communication network allows processors to synchronise and exchange data. Examples of these *distributed memory* MIMD machines include systems based on the **INMOS Transputer** [29] range of microprocessors, such as the **Meiko Computing Surface** series [27]. Distributed memory MIMD parallel machines may contain several hundred processors.

## 1.1.3 Using vector and parallel machines

The early popularity of vector processors was no doubt because they provided a performance boost of perhaps ten times (compared to conventional scalar processors of the same technology), at reasonable extra cost in hardware, and because existing programs could easily be adapted to run on them. However, the full performance of these machines is only available on problems which are sufficiently *vectorisable*, *ie* the vectors must be long enough, and the algorithm must be capable of expression as vector code without serious scalar bottlenecks. On the other hand, for *highly* parallel problems, such as matrix multiplication, the peak performance of a vector machine is limited by the limited degree to which the parallelism of the problem is exploited in the single vector pipeline.

Parallel processors with many arithmetic units are in theory able to reach much higher peak performance, but at the cost of more difficult programming. Single instruction stream array processors, even more than vector processors, are only utilised efficiently on problems with a sufficient degree of fine-grained homogenous parallelism, and the increased speed then provided by the multiple processing units makes scalar bottlenecks more likely on array processors. These machines also present the programmer with the additional problem of data distribution.

MIMD multiprocessors can be effective on any problem which can be decomposed into parallel parts, even if the decomposition is heterogenous (*ie* different processors are carrying out different subtasks) – this class of problems includes many which cannot make efficient use of vector or array architectures. However, the programmer has the often difficult task of finding a problem decomposition which will fit the machine architecture in such a way that each processor has a similar amount of work to do, and such that synchronisation and data communication between processors does not delay processing inordinately.

The vector processor and parallel processor approaches to performance improvement are not exclusive alternatives. Some commercial vector machines, such as the **CYBER-205** and the **NEC SX-2**, can incorporate up to four vector pipelines, and divide the elemental parts of a vector operation between the pipelines, thus combining the vector and array approaches. Peak performance is four times greater, but vectors must be four times longer to obtain the same percentage of that peak.

There is potentially more to be gained from combining the vector and MIMD multiprocessor approaches. The processors in an MIMD machine are usually relatively loosely coupled, in the sense that synchronisation and data communication between processors takes many cycles – this is particularly true of the larger, distributed memory systems. Because of this, MIMD machines are more suited to exploiting the coarser-grained parallelism in an algorithm. An MIMD machine consisting of a number of vector processors can simultaneously exploit parallelism at different levels of granularity in many large-scale numerical problems, and combines the performance advantages of each class of machine. Many vector processors are available in small parallel MIMD configurations, with a shared memory architecture supporting up to four processors. Examples include the CRAY X-MP, Y-MP and CRAY-2 series of machines, and the IBM 3090VF (in which the maximum number of processors is six).

## 1.2 Sparse matrix problems

Sparse matrices are those in which many of the matrix elements have the value zero. They arise naturally in the formulation of problems in application areas such as design, simulation and optimisation, and in finite approximation methods for solving differential equations. In all cases, the matrix is sparse because most or all of the linear equations in the formulation involve only a small subset of

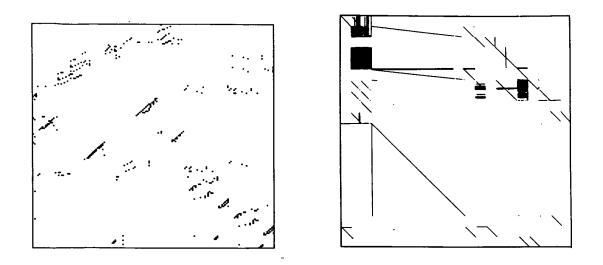

Figure 1-1: Irregular sparse matrices arising from a chemical plant model (left) and from an economic model (right), from [16]

the variables. This reflects the nature of the physical problem modelled – in a structural model, each piece of the structure usually connects only to a few other pieces; in a large optimisation problem, most of the constraints involve only a few of the variables; in a finite element formulation of a differential equation problem, each element is affected only by adjacent elements. In the last example, the regular pattern of elements and the fact that each 'connects' only to adjacent elements mean that the pattern of non-zeroes in the resulting matrix is regular (often a band along the diagonal), while for the other examples, the pattern reflects the pattern of 'connections' between the elements of the model, and can be very irregular (figure 1-1).

Many useful engineering or optimisation problems involve matrices which are very large (tens of thousands of rows) and very sparse (the constraint matrix for a large Linear Programming problem might typically have 5 to 7 non-zero elements per column). Clearly such matrices must be treated specially – a matrix of order 20,000 is much too large to handle on a computer if it were stored as an ordinary, 'dense' matrix. These large sparse problems can only be solved because the matrices can be stored in a compressed form with the zeroes removed, and because arithmetic need only be performed on the non-zero elements. The amount of arithmetic required to solve a sparse problem depends on the number of nonzeroes in the matrix, but the arithmetic operations themselves tend to create new non-zeroes as the computation proceeds – a process known as *fill-in* of the matrix. The amount of fill-in which occurs depends very greatly on the order in which computation is carried out, and thus sparse problems require special algorithmic techniques to ensure a computation order which keeps fill-in to the absolute minimum.

Sparse matrix computation researchers over the last three decades have developed a variety of ways of minimizing fill-in, and have experimented with a number of data structures for sparse matrices which support rapid identification and execution of the required arithmetic operations. Much of the sparse matrix software developed over this period has been for conventional *scalar* processor architectures; little use has been made of vector processors, which are designed specifically to operate on dense vector data structures. However, interest in vector and parallel solution of sparse matrix problems has grown over the past few years, partly as a result of the introduction of vector processor instructions which can, to a limited extent, operate on sparse vectors stored in compressed form, and partly as a result of the increasing availability of MIMD parallel machines able to take advantage of coarser-grained parallelism in sparse matrix problems.

#### 1.2.1 Use of vector processors for sparse problems

Vector processor instructions are designed to operate on dense vectors stored as arrays – the elements of the vector are all present in memory, and occupy consecutive memory locations. In some sparse problems, where the non-zero structure of the original matrix is regular (as it is in matrices arising from finite element methods, for example), or where the matrix can be permuted to bunch together the non-zeroes, dense vector data structures can be used for that small part of each vector which contains the non-zeroes, and implementations can take then advantage of vector processor facilities. Many problems, however, involve a highly irregular pattern of non-zeroes, and the vectors must necessarily be stored in some compressed form on which standard vector instructions will not operate.

In recognition of this problem, some vector processor developers have considered ways of providing vector instructions which operate on sparse vector operands stored in compressed form. This work was pioneered by the designers of the CYBER-205 [12], who introduced in that machine two sets of novel instructions, operating on sparse vectors stored in two different forms: the "order vector" form and the "index vector" form. These mechanisms are discussed in chapter 3, and for reasons explained there, the "order vector" mechanisms were not a success. The "index vector" mechanisms actually comprised two operations only, called "scatter" and "gather", which carry out subparts of a common implementation of vector arithmetic on compressed sparse vectors. Using the scatter and gather vector instructions, an addition operation between two sparse vectors stored in compressed form can be implemented by a sequence of eight vector instructions, and this can be considerably faster than a scalar implementation of the same vector arithmetic. The scatter and gather operations have been used in successfully in sparse matrix software [19,16], and have become a standard feature on vector processors (all Cray models from the X-MP/48 onwards have incorporated them, as do the Japanese machines and the IBM 3090VF). Because, even with scatter and gather instructions, a sparse vector arithmetic operation requires a sequence of several vector instructions, most of which involve data rearrangement, not arithmetic, the overall arithmetic rate obtainable from a vector processor on sparse vector arithmetic operations remains far below that obtainable from the same processor on dense vectors.

### 1.2.2 Use of parallel processors for sparse problems

Of the two classes of parallel machine with substantial parallelism, the SIMD array and MIMD multiprocessor, only the array processor has been available for applications research for any length of time. Attempts have been made to mount sparse matrix problems on such machines [39,37], but these have run into similar difficulties as those arising with conventional vector architectures – the machines work well on dense vectors stored as arrays, but are hard to adapt to problems involving arithmetic on compressed sparse vector data structures.

MIMD parallel processors (with a reasonable degree of parallelism) have only become available for widespread research on program design in the past five years, and parallel implementations of sparse matrix problems are thus at an earlier stage of experimentation [7,14,34,45,51]. Nevertheless, it seems likely that the parallelism of such machines can be exploited in many sparse problems, although the best parallel decomposition of program and data is likely to be machine architecture dependent. One MIMD parallel machine, the  $(SM)^2$ -II [3,4,5] has been developed specifically for sparse matrix problems, and a small prototype is under evaluation.

As with dense matrix code, the parallelism exploitable on MIMD architectures is coarser grained than that exploitable by vector processors, and research into the implementation of sparse matrix software on both these classes of machine remains potentially fruitful.

# **1.3** The Edinburgh Sparse Processor project

The Edinburgh Sparse Processor (ESP) project developed out of research on the MU6V machine carried out at Manchester University [47,33,26]. In its final form, MU6V was an MIMD parallel machine, designed for vector and matrix applications, and each processor in the parallel machine was itself intended to be a vector processor, with an instruction set which included vector instructions to operate on sparse vectors, as well as the usual dense vector instructions. The focus of research, however, was on the MIMD parallelism, and in the prototype each vector processor was emulated using scalar code running on a Motorola 68010 microprocessor. A mechanism was proposed for implementation of sparse vector storage and arithmetic, based on the CYBER-205 "index vector" mechanism, but with more flexibility, but the sparse vector operations were never implemented in the emulated vector processor, and the sparse mechanism was not developed. However, the **MU6V** proposal had suggested that it might be possible to build a vector processor capable of executing the full set of vector arithmetic instructions directly on sparse vectors stored in compressed form. If so, the result would be a performance improvement on sparse vector arithmetic, compared to scalar processor implementations, at least as great as that provided by conventional vector processors for dense vector arithmetic.

The aims of the author's research were to investigate the feasibility of efficiently supporting sparse vector arithmetic in a vector processor, and, if feasible, to develop an architecture for a machine incorporating sparse vector instructions: the Edinburgh Sparse Processor. ESP was intended to be a single vector processor machine, although it was expected that, if the design was successful, an MIMD parallel version, built by replicating the ESP architecture, would give even higher performance on large sparse problems. The development of a prototype of the machine has been supported by High Level Hardware Ltd., of Oxford, and the UK Science and Engineering Research Council.

Specific objectives of the research described in this thesis were:

- to identify the vector and matrix operations which must be implemented efficiently to support chosen target applications;

- to identify mechanisms for storage of sparse vectors and matrices of a wide range of sizes and densities, and for computation with those vectors and matrices, including mechanisms for all standard vector operations, plus any other operations identified as necessary for the target applications; to examine the feasibility of hardware support for those mechanisms, and to evaluate their resulting efficiency;

- to develop a vector processor architecture capable of high performance on the target applications, incorporating suitable sparse vector mechanisms and supporting a full vector instruction set, based on that developed for MU6V, plus any additional instructions identified as required for the target applica-

tions, and with each instruction able to operate efficiently, where appropriate, with dense vector or sparse vector operands, or a mixture of the two;

• to evaluate the technical feasibility of the new architecture, by designing an implementation using off-the-shelf components, and to examine the effectiveness of the architecture by analysis, by simulation, and by building and testing a prototype.

# Chapter 2

# Sparse Matrix Algorithms

### 2.1 Introduction

The principal chosen target application for ESP is Linear Programming (LP). This is an application of great commercial interest, for example in the manufacturing, transport and communications industries, and is also of importance as a subproblem of non-linear optimisation problems. Many LP problems are large and sparse, and the availability, from a local research group, of a variety of real problems of different characteristics assists in the evaluation of the architecture and of the machine. However, in developing the architecture of ESP, the simpler problem of the direct solution of sparse systems of linear equations by Gaussian elimination was also targetted, as this problem is both in itself an important application area, and is a sub-problem of the most commonly used LP algorithm.

This chapter presents a general description of the methods currently used to solve these sparse matrix problems, concentrating on the operations which must be performed at matrix and vector level.

# 2.2 Direct solution of linear equations

There are two classes of method for solving

$$\mathbf{A}\mathbf{x} = \mathbf{b}$$

- direct solution methods, and iterative techniques (the latter are considered in section 2.3 below). Direct methods for the solution of linear equation systems are based on the *Gaussian elimination* algorithm. The basic principle is to reduce the matrix  $\mathbf{A}$  (or some permutation of it) to upper triangular form by subtracting multiples of each row from the rows below it, each time zeroing out a column in the lower triangle. The same subtractions may be performed on the right hand side  $\mathbf{b}$ , as the solution proceeds, leaving a system of the form

$$\mathbf{U}\mathbf{x} = \mathbf{b}'$$

which is solved by back substitution of the elements of  $\mathbf{x}$ . Alternatively, the sequence of subtraction multipliers may be stored, yielding an explicit factorisation  $\mathbf{L}\mathbf{U} = \mathbf{A}$ , which may be used to solve the equations for multiple right hand sides, by forward-substitution to solve  $\mathbf{L}\mathbf{y} = \mathbf{b}$ , then back-substitution to solve  $\mathbf{U}\mathbf{x} = \mathbf{y}$ . (The related *Gauss-Jordan* method diagonalises the original matrix in one calculation, by applying the row subtractions to rows above the diagonal as well as below it. It is not widely used in practice, as it involves more arithmetic operations than the Gaussian method.)

An intermediate stage in Gaussian elimination is illustrated in fig. 2–1. The principal operation required is vector subtraction:

$$\mathbf{A'_{i\bullet}} \leftarrow \mathbf{A'_{i\bullet}} - s_i * \mathbf{A'_{p\bullet}}$$

where  $\mathbf{A}'$  is the current, partially triangularised, version of  $\mathbf{A}$ . Using this operation repeatedly, the lower part (*ie* the part below the diagonal) of a column of  $\mathbf{A}'$  is zeroed by subtracting suitable multiples of row p from all the rows i beneath it.  $s_i$  is a scalar chosen for each row i so that the subtraction zeroes the pth element

Figure 2-1: Gaussian elimination

of the row.  $A'_{p\bullet}$  is known as the *pivot row*, and  $A'_{\bullet p}$  is the column of which the lower part is being zeroed, and is called the *pivot column*. Element  $a'_{pp}$  is called the pivot element, and  $s_i$  is given by:

$$s_i = a_{ip}'/a_{pp}'$$

#### 2.2.1 Choice of pivot element

In the basic Gaussian elimination algorithm described above, the pivot elements are the diagonal elements of the matrix, and are used in order from top to bottom. This is often unsatisfactory, however, because when a diagonal element is used as the pivot its value may be relatively very small compared to the elements below it in the pivot column, and this will necessitate subtraction of very large multiples of the pivot row. Because of the limited precision of floating point number representations, the size of such subtracted row element multiples may swamp the original matrix entries, and the resulting error in the calculation will render it useless. It is therefore normal to select the element to be used as pivot at each stage of the elimination, either by exchanging rows to replace the diagonal pivot element with the largest element in the pivot column (this operation is known as *partial pivoting*), or by exchanging rows and columns to make the pivot the largest element in the submatrix remaining to be triangularised (full pivoting). The overall effect is the same as applying row and column permutations to A before factorisation, and then pivoting down the diagonal, but the pivot choices must be made during factorisation, as the values of the relevant elements change during the calculation. In practice, partial pivoting almost always provides sufficient numerical stability, and full pivoting is not normally used.

In the special cases where the matrix  $\mathbf{A}$  is symmetric and positive definite, or diagonally dominant, pivoting can proceed down the diagonal, without permutation, as the factorisation will always be numerically stable.

#### 2.2.2 Gaussian elimination on sparse matrices

Sparse systems of linear equations arise for example from engineering models, where structures to be modelled often consist of (or may be approximated by) many parts sparsely interconnected, from optimisation problems, and from difference methods for solving partial differential equations. All of these problem areas can generate very large matrices, of order  $10^4$  or larger, but the problems differ in the typical patterns of distribution of the non-zeroes through the matrix.

#### 2.2.3 Sparse matrices with regular structure

Sparse matrices arising from partial differential equation solution by finite differences, and from many finite element methods, generally have a regular, banded structure. The band is relatively dense, and there are no non-zeroes outside it. If Gaussian Elimination proceeds using pivots on the diagonal, no fill-in will occur outside the band. Partial pivoting will result in, at most, a doubling of the width of the upper half of the band, without affecting the width of the lower half.

Obviously, only the parts of the rows within the band need be processed, and it is efficient to store and process the band alone, as a set of *dense* vectors, using the vector arithmetic mechanisms of an ordinary vector processor.

### 2.2.4 Sparse matrices with irregular structure

Matrices arising from engineering or optimisation problems often have an irregular distribution of non-zeroes, reflecting the inherent structure of the original problem (see fig. 1-1). Algorithms exist to permute matrices to band structured matrices with minimised band width - the resulting matrices may then be solved using dense vector operations on the band. However, it is often not possible to permute the non-zeroes into a dense enough band to make this method efficient.

In such a case, it is better to work on the matrix in its sparse form. To solve large problems of this kind, the non-zeroes, and information about their positions, must be stored in compressed form, but in such a way that the elimination and pivot choice steps of the Gaussian elimination algorithm can proceed efficiently.

The elimination step (*ie* the subtraction of multiples of a single pivot row from other rows in the matrix) here involves the subtraction of one sparse vector from another  $(\mathbf{x} \leftarrow \mathbf{x} - \mathbf{y})$ , and will generally involve *fill-in* of the vector  $\mathbf{x}$  – if the positions of the non-zeroes in  $\mathbf{y}$  do not coincide with the non-zeroes in  $\mathbf{x}$ , the updated vector  $\mathbf{x}$  will contain more non-zero elements after the subtraction. The storage scheme for the vectors must be able to deal with this.

If the matrix is sparse, it is only necessary to subtract the pivot row from those rows in the matrix with a non-zero in the pivot column – the storage scheme must therefore allow fast identification of the position of the non-zeroes in each column of the updated matrix, as the elimination proceeds, or the time spent searching for these will dominate the solution time. In order to calculate the scalar multiple of the pivot row to be subtracted, the actual values of the non-zeroes in the pivot column must also be rapidly accessible.

#### 2.2.5 Pivot choice in sparse Gaussian elimination

The overall computation time will depend on the total number of non-zeroes processed, and this number is increased by fill-in of the as yet unfactorised part of the matrix, caused by previous pivot row subtractions. The amount of fill-in depends on the chosen sequence of pivots, because the more non-zeroes there are in the chosen pivot row, the more fill-in is likely to occur in each row from which the pivot row is subtracted, while the more non-zeroes there are in the pivot column, the more such rows there will be. A second requirement, the need to minimize fill-in, must therefore guide the choice of pivots in the sparse case, in addition to the requirement to choose pivots which do not upset the numerical stability of the calculation.

The most common criterion for pivot choice to minimise fill-in is known as the *Markowitz criterion* [36]. It consists of choosing as pivot the element in the unfactorised sub-matrix with the minimum product of number of non-zeroes in its row, and number of non-zeroes in its column. To find such an element efficiently requires rapid assessment, at each stage of the factorisation, of the number of non-zeroes currently in each row and column of the matrix.

The usual way of combining the requirements of numerical stability and minimal fill-in is known as *threshold pivoting* [11]. The element to be used as the pivot is chosen on fill-in grounds, using the Markowitz criterion, and its magnitude is then checked against all other elements in its row (or alternatively, all other elements on or below the diagonal in its column). If the selected pivot is too much smaller than the largest element in its row, it is rejected, and another candidate chosen on fill-in grounds.

#### 2.2.6 Pivot choice on sparsity grounds only

In special cases, for example where the matrix is symmetric and positive definite, any permutation may be applied to it before factorisation, without risking numerical instability. It is therefore normal practice to determine a permutation which will minimise fill-in, before factorisation starts. (This can be done before factorisation because the amount of fill-in depends on the choice of pivots and the non-zero structure of the original matrix, but, ignoring the rare possibility of cancellation of a matrix entry to zero during a subtraction step, not on the *values* of the nonzeroes.) Finding the optimal sequence of pivots is provably NP-complete, but

**Figure 2-2:** Typical pattern of non-zeroes in the factors  $L \setminus U$  of a sparse matrix. In this case, the original matrix was symmetric, and  $U = L^{T}$  (from [16]).

heuristic methods based on a graph representation of the non-zero structure are fast and work well [11]. Factorisation can then proceed without further checking of pivots on sparsity or stability grounds.

#### 2.2.7 Size and sparsity of typical problems

In [17], Duff *et al.* list a set of typical problem matrices, which they used to compare different implementations of Gaussian elimination. These vary in order from 156 to 5300, while the number of non-zeroes ranges from 371 for the order 156 matrix, to 21842, for the matrix of order 5300, with most matrices averaging fewer than ten non-zeroes per row. As Gaussian elimination proceeds, fill-in accumulates, so that the resulting factors L and U become increasingly dense towards the bottom right-hand corner (see Fig. 2–2). The amount and pattern of fill-in obviously depend on the structure of the original matrix, but, typically, the unfactorised submatrix might be 25% full after 70% of the pivots have been used, and 50% full after 80% of the elimination steps are done [15].

# 2.3 Iterative solution of linear equations

If  $\mathbf{x}_0$  is an inaccurate solution to  $\mathbf{A}\mathbf{x} = \mathbf{b}$ , then the accurate solution is

$$\mathbf{x} = \mathbf{x}_0 + \mathbf{A}^{-1}(\mathbf{b} - \mathbf{A}\mathbf{x}_0)$$

If  $\tilde{\mathbf{A}}^{-1}$  is a sufficiently close approximation to  $\mathbf{A}^{-1}$ , then the iterative sequence

$$\mathbf{x}_{n+1} = \mathbf{x}_n + \tilde{\mathbf{A}}^{-1}(\mathbf{b} - \mathbf{A}\mathbf{x}_n)$$

(2.1)

will converge to an accurate solution.

The trick is to choose  $\tilde{\mathbf{A}}^{-1}$  to minimize the computation involved in evaluating (2.1), while achieving fast convergence. If  $\mathbf{A}$  is partitioned into its diagonal  $\mathbf{D}$ , the part below the diagonal  $\mathbf{A}_L$ , and the part above the diagonal  $\mathbf{A}_U$ , so that  $\mathbf{A} = \mathbf{A}_L + \mathbf{D} + \mathbf{A}_U$ , then the Jacobi method chooses  $\tilde{\mathbf{A}}$  to be  $\mathbf{D}$ , so that (2.1) may be re-written

$$\mathbf{D}\mathbf{x}_{n+1} = -(\mathbf{A}_L + \mathbf{A}_U)\mathbf{x}_n + \mathbf{b}$$

The right-hand side uses (most of) the original matrix, and takes full advantage of its sparsity;  $\mathbf{D}\mathbf{x} = \mathbf{y}$  is trivial to solve.

The Gauss-Seidel method uses  $\tilde{\mathbf{A}} = \mathbf{A}_L + \mathbf{D}$ , so that

$$(\mathbf{A}_L + \mathbf{D})\mathbf{x}_{n+1} = -\mathbf{A}_U\mathbf{x}_n + \mathbf{b}$$

Again, full advantage is taken of the sparsity of A;  $(A_L + D)x = y$  is solved by forward-substitution.

Both the above methods are certainly convergent if A is diagonally dominant, while Gauss-Seidel also converges if A is symmetric and positive-definite. The convergence of the Gauss-Seidel method may be improved by *relaxation* - in this variant,  $\tilde{\mathbf{A}}$  is chosen to be  $\omega^{-1}(\omega \mathbf{A}_L + \mathbf{D})$  with  $\omega$  a factor chosen by experience and dependent on the problem type.

An alternative choice for  $\tilde{\mathbf{A}}$  is to use an approximation to the LU factorisation of  $\mathbf{A}$ ,  $\tilde{\mathbf{A}} = \tilde{\mathbf{L}}\tilde{\mathbf{U}}$  [16]. The factors  $\tilde{\mathbf{L}}$  and  $\tilde{\mathbf{U}}$  are generated by setting to zero any matrix entries smaller than a chosen threshold encountered during the Gaussian elimination of  $\mathbf{A}$ , and are thus much sparser than accurate factors. Evaluating the product term on the right hand side of (2.1) is done by forward- and backsubstitution using the sparse approximate factors.

Other, more sophisticated iterative methods, such as the *conjugate gradient* method [9] may be used; these methods also take good advantage of the sparsity of **A**, while converging faster than the simpler methods above. However, one often cannot be sure in advance that iteration will converge satisfactorily, and in practice this has restricted the use of iterative methods to special cases where convergence is known to be good and where a good initial approximation is known. In any case, these iterative algorithms are computationally relatively straightforward, and the sparse vector operations required to implement them are included in the set required to be supported by ESP for other applications which have been considered in detail. For these reasons, iterative methods are not considered further.

# 2.4 Linear Programming

#### 2.4.1 The simplex method

The general Linear Programming (LP) problem consists of finding a set of values for a number of variables (represented here as an *n*-element vector  $\mathbf{x}$ ) which maximizes a given linear function of those variables (known as the *objective* function):

$$f = \mathbf{c}^T \mathbf{x}$$

subject to linear constraints:

$$l_i \le \mathbf{A}_{i\bullet} \mathbf{x} \le u_i \qquad \qquad 1 \le i \le m \tag{2.2}$$

$$l_{m+j} \le x_j \le u_{m+j} \qquad \qquad 1 \le j \le n \qquad (2.3)$$

Each constraint inequality defines a pair of hyperplanes in the *n*-dimensional  $\mathbf{x}$  space, between which any solution must lie. The inequalities together define a convex region (simplex) in which the solution must lie (if the problem is feasible, ie there are values of  $\mathbf{x}$  which satisfy all the constraints, such a region will certainly exist, and in a well-behaved problem it will be bounded). The maximum value of the objective function will be attained at one (or more than one) corner of the simplex. The simplex method consists of first finding a corner of the simplex, then moving around the corners step by step, improving the value of the objective function at each step, until no further improvement is possible.

The simplex method usually involves converting the problem set out in (2.2) and (2.3) into a form in which all the inequality constraints refer to a single variable only. This is done by introducing a unique extra variable into each of the inequalities in (2.2), so that the inequality,

$$l_i \leq a_{i1}x_1 + a_{i2}x_2 + \dots + a_{in}x_n \leq u_i$$

becomes:

$$a_{i1}x_1 + a_{i2}x_2 + \dots + a_{in}x_n + x_{n+i} = 0$$

$$-u_i \le x_{n+i} \le -l_i$$

The newly introduced variables are known as *logical*, or alternatively *slack* or *surplus* variables.

Applying this transformation to each inequality converts the problem set out in (2.2) and (2.3) into the standard form for the simplex method:

Maximize  $f = \mathbf{c}^T \mathbf{x}$ , subject to:

$$\mathbf{A}\mathbf{x} = \mathbf{b} \tag{2.4}$$

$$l_i \le x_i \le u_i \qquad \qquad 1 \le i \le n+m$$

With the introduction of the logical variables, x and c are now n+m long (the elements of c corresponding to the logical variables are zero). A is m by n+m, and includes the m by m identity matrix.

There are *m* independent equations in (2.4), so if *n* components of **x** are fixed, (2.4) uniquely determines the remaining *m* components. If **x** is partitioned into *n* components which are fixed (the 'independent' variables), written  $\mathbf{x}_I$ , and the remainder (the 'dependent' variables),  $\mathbf{x}_D$ , equation (2.4) and the objective function may be rewritten:

$\mathbf{A}_D \mathbf{x}_D + \mathbf{A}_I \mathbf{x}_I = \mathbf{b}$  $f = \mathbf{c}_D^T \mathbf{x}_D + \mathbf{c}_I^T \mathbf{x}_I$

$\mathbf{x}_D$  and f may be determined from  $\mathbf{x}_I$ :

$$\mathbf{x}_D = \mathbf{A}_D^{-1} \mathbf{b} - \mathbf{A}_D^{-1} \mathbf{A}_I \mathbf{x}_I \tag{2.5}$$

$$f = \mathbf{c}_D^T \mathbf{A}_D^{-1} \mathbf{b} - (\mathbf{c}_I^T - \mathbf{c}_D^T \mathbf{A}_D^{-1} \mathbf{A}_I) \mathbf{x}_I$$

(2.6)

If an initial feasible solution (*ie* a solution which satisfies all the constraints)  $\mathbf{x}$ , and partition  $\mathbf{x}_D | \mathbf{x}_I$ , are chosen such that each of the *n* independent variables in  $\mathbf{x}_I$  is at one of its bounds, this will correspond to a corner of the feasible simplex, and the value of  $\mathbf{x}_D$  will indicate the distances from the remaining bounds. Moving to an adjacent corner of the simplex corresponds to setting one of the  $\mathbf{x}_D$  components to a bound, while allowing one of the  $\mathbf{x}_I$  components to come off its

bound, and thus involves altering the  $\mathbf{x}_D \mid \mathbf{x}_I$  partition by making one dependent variable independent, and *vice versa*.

Each iteration of the simplex method involves choosing an independent variable to move off a bound, and a dependent variable which will reach a bound. The equations (2.5) and (2.6) must then be updated to reflect the new partition. The value of  $\mathbf{A}_D^{-1}\mathbf{b}$  can easily be updated at each step, while the standard simplex method also updates  $\mathbf{A}_D^{-1}\mathbf{A}_I$  at each step. However, for problems of significant size (n > 100), the revised simplex method is substantially faster. This involves storing  $\mathbf{A}_D^{-1}$  in a form which is easy to update as the  $\mathbf{x}_D | \mathbf{x}_I$  partition changes, and from which  $\mathbf{c}_D^T \mathbf{A}_D^{-1}$  and (the required part of)  $\mathbf{A}_D^{-1} \mathbf{A}_I$  is calculated at each step.

### 2.4.2 Computational steps in the revised simplex method

In the revised simplex method (also called the *product form of inverse (PFI)* simplex method), the inverse matrix  $\mathbf{A}_D^{-1}$  is stored as a list of matrices whose product is the inverse matrix. Each of these matrices has the form of the unit matrix, with one special column:

| $\left( 1\right)$ | 0 | ••• | $\eta_1$     | ••• | 0 | 0) |

|-------------------|---|-----|--------------|-----|---|----|

| 0                 | 1 | ••• | $\eta_2$     | ••• | 0 | 0  |

|                   |   |     | •            |     |   |    |

|                   |   |     | •            |     |   |    |

|                   |   |     | •            | •   |   |    |

| 0                 | 0 | ••• | $\eta_{m-1}$ | ••• | 1 | 0  |

| 0                 | 0 | ••• | $\eta_m$     | ••• | 0 | 1) |

These matrices are usually known as the  $\eta$ -matrices, and the interesting column of the matrix as the  $\eta$ -vector.

A single iteration of the simplex method replaces one column of  $A_D$  with a column from  $A_I$ , and applying the old inverse matrix to this new  $A_D$  would result in a unit matrix with one filled column. The inverse matrix can therefore be

updated by adding one extra  $\eta$ -matrix to the front of the list, chosen so as to reduce the extra column to a single entry, value 1, without affecting the other columns. The  $\eta$ -matrix list thus grows by one entry per iteration of the algorithm.

#### Choosing the variables to update

At each iteration, to choose the independent variable to be moved off its bound, the effect on the objective function of changes in the value of each independent variable must be known. This is given by the term in brackets in equation (2.6) above. At each iteration  $\mathbf{A}_D^{-1}$  changes, and  $\mathbf{c}_D^T \mathbf{A}_D^{-1}$  must be calculated anew. Its value is given by:

$$\mathbf{c}_D^T \mathbf{E}_j \mathbf{E}_{j-1} \cdots \mathbf{E}_1$$

where the **E** are the  $\eta$ -matrices described above.

If k is the column position of the vector  $\eta$  within the matrix **E**, then  $\mathbf{c}^T \mathbf{E}$  is simply the vector

$$(c_1, c_2, \ldots c_{k-1}, (\mathbf{c}.\boldsymbol{\eta}), c_{k+1}, \ldots c_m).$$

Thus  $\mathbf{c}_D^T \mathbf{A}_D^{-1}$  may be calculated via a sequence of scalar products, the result of each of which updates a single element of **c**. The result is called the *price* vector  $\pi$ , and this calculation, which must be redone at every iteration, is called the *BTRAN* operation.

Assessment of the effect on the objective function of a change to a single independent variable now requires a scalar product of the price vector with the corresponding column of  $A_I$  (refer to equation (2.6) above). The independent variable chosen to move from its bound is the one for which the rate of increase in the objective function is largest, although when solving a large problem, it is usually sufficient to make the choice from a subset of the independent variables at each iteration (some versions of the algorithm, eg DEVEX [21], use slightly ł

different criteria for choosing the variable). The calculation of the required scalar products is known as the *pricing* operation.

To calculate how far the chosen independent variable can move off its bound, it is necessary to ascertain which of the dependent variables reaches a bound first, as the value of the independent variable changes.

The effect on  $\mathbf{x}_{D}$  of changes in a single independent variable is given by a single column of  $\mathbf{A}_{D}^{-1}\mathbf{A}_{I}$  (refer to equation (2.5) above). Once the independent variable to be changed has been chosen at the pricing step, this column can be calculated from the corresponding column in the original matrix A, by:

$$\mathbf{E}_{j}\mathbf{E}_{j-1}\cdots\mathbf{E}_{1}\mathbf{A}_{\bullet i}$$

As matrix multiplication is associative, this can be evaluated from right to left, and the result of pre-multiplying a vector  $\mathbf{a}$  by the specially structured matrix  $\mathbf{E}$ is given by:

$$\mathbf{a} + a_k \eta$$

where k is the position of the interesting column  $\eta$  within the matrix E. The calculation of the required column of  $\mathbf{A}_D^{-1}\mathbf{A}_I$  can therefore be implemented as a sequence of scaled vector addition steps. This calculation is known is the *FTRAN* operation.

Once the *FTRAN* operation is complete, the resulting vector gives the rate of change of each dependent variable with change in the chosen independent variable, and, as the current values of the dependent variables are known, it is easy to ascertain which reaches a bound first. The step in the independent variable is then fixed, and all the dependent variables may be updated. The dependent variable which is now on a bound becomes 'independent', while the independent variable which was moved off a bound becomes 'dependent'. The result of the *FTRAN* operation is also used to generate the new  $\eta$ -matrix to update the representation of  $\mathbf{A}_D^{-1}$ , because it corresponds to the result of applying the existing  $\mathbf{A}_D^{-1}$  to the

new column introduced to  $A_D$  when the  $x_D | x_I$  partition is updated. The extra  $\eta$ -matrix, which is added to the front of the list (*ie* becomes  $E_{j+1}$  in the notation used above), effects the subtraction steps required to clear out this column to a single 1.

#### The Re-invert Step

The product form of the inverse  $\mathbf{A}_D^{-1}$  described above represents of a list of Gauss-Jordan elimination steps, each with its pivot chosen as described above. After a large number of iterations of the revised simplex method, this representation of the inverse matrix becomes prone to excessive fill-in, because the order of pivot choice ignores sparsity. Many implementations of the simplex method therefore use a slightly modified representation of the inverse matrix  $\mathbf{A}_{D}^{-1}$ , in which the inverse is still represented as a product of elementary matrices of the form of the  $\eta$ -matrices described above (thus the BTRAN and FTRAN steps remain as described above) but where those elementary matrices are initially generated by directly factorising the matrix  $\mathbf{A}_D$ , choosing pivots by a method which minimises fill-in and ensures stability, such as the threshold method described in section 2.2.5 above. This product form of the inverse is updated at each iteration (the exact method used to update the factors differs between implementations), and as the updates proceed, the number of non-zeroes in the  $\eta$  columns grows. It is therefore worthwhile to regenerate the inverse from time to time, by re-inverting the current matrix  $A_D$ . This re-invert step comprises a Gaussian elimination operation on the very sparse  $A_D$ , and is typically carried out every 100 or so iterations.

### 2.4.3 Size and sparsity of typical LP problems

The matrix A in a typical commercial problem might have 500 rows and 1500 columns [37] - the three to one shape is typical for large problems. Problems with more than 1000 constraints are very common, while some have 10000 or more. However, in a typical large problem, there are only a small number (perhaps 6

to 10) non-zeroes in each column, thus a model with a few thousand constraints would only be around 0.1% full.

At the very start, therefore, the  $\eta$  vectors are correspondingly sparse, but fillin caused by the application of the product-form inverse results in the columns of  $\mathbf{A}_D^{-1}\mathbf{A}_I$  typically being around 20% full for most of the computation. This is therefore the density of most  $\eta$  vectors added after a re-invert. The re-invert step will typically reduce the  $\eta$  density to around 1%.

During *BTRAN*, the original vector  $\mathbf{c}_D^T$ , which is usually very sparse, fills to reach a density of around 20% or more during the *BTRAN* operation – the final density of the price vector is problem dependent. During *FTRAN*, the column of **A** being updated fills rapidly to about 20% full [37].

Although in theory the number of iterations required to solve an LP problem can be exponential in the size of the problem, in practice the number of iterations required is usually roughly proportional to problem size, typically a small factor (1 to 10) times the number of constraints [11], *ie* many thousand iterations on a large problem. In practical implementations, it is found that the most computationally intensive parts of the revised simplex algorithm are the *BTRAN*, pricing and *FTRAN* steps - taking perhaps 30%, 35%, and 20% respectively of the total solution time for a large sparse problem, while the re-invert step might consume 5% of the time [37,19].

## 2.5 Summary

From the descriptions given above, a set of vector and matrix operations which must be efficiently supported by the new machine can be identified. For the Gaussian elimination algorithm, efficient subtraction of a multiple of one sparse vector from another is required, and the implementation must be able to handle the fill-in which occurs. In addition, for pivot choice by the Markowitz criterion, there must be a way of rapidly finding the number of non-zeroes in each row and in each column of the updated matrix. Rapid access to the non-zeroes in the chosen

#### Chapter 2. Sparse Matrix Algorithms

pivot row is required, in order to check the chosen pivot (if using the threshold pivoting method), and rapid access to the non-zeroes in the chosen pivot column is needed to calculate the scalar multipliers for the subtraction step.

For fast implementation of Linear Programming, the machine must also support efficient implementation of the *BTRAN*, pricing and *FTRAN* operations.

If mechanisms can be developed which support all of the above operations efficiently, in addition to sparse versions of the standard set of vector arithmetic operations provided by a vector processor, then the resulting machine could be expected to support well a wide range of problems involving sparse vectors and matrices. In practice, it is also likely that the use of a machine offering new facilities will develop in unexpected ways, as programmers exploit the new features to solve problems in ways unanticipated by the designers of the architecture.

## Chapter 3

## Implementing Sparse Matrix Computation

## 3.1 Introduction

One of the aims of the ESP development was to develop an architecture for a processor supporting a general set of vector instructions, such as might be found on many vector processor machines, but with the facility to work with sparse vector, and mixed sparse/dense vector operands. A second aim was to ensure that the architecture supports all the operations required for the Gaussian elimination and Linear Programming algorithms described in chapter 2, and does so in a balanced way – that is, there should be no 'holes' in the support for the algorithm, which would result in the time for one step dominating the execution time. This requirement has led to the development of new vector instructions, and to hardware to support not just vector operations, but operations on complete matrices.

Close examination of the operations which need to be performed on vectors during sparse matrix computation reveals that there are three basic suboperations which need to be implemented efficiently:

1. Access to all of the non-zero indices, and often the values as well, in sequence. Sometimes the sequence is required to be in order of ascending index.

- 2. Access to the value of a single element, given its index.

- 3. Insertion of new non-zero elements, and updating of the value of existing non-zeroes.

This chapter examines the ways in which a variety of data structures for sparse vectors can support these suboperations so as to provide efficient implementations for the required vector and matrix operations. These data structure operations may be implemented in software, on conventional scalar and vector processors, or by using special-purpose hardware additions to standard processor architectures.

Large sparse matrix problems require matrix storage in compressed form – a suitable choice of data structure depends on a balance between the need to minimise the memory space used, and the requirement for fast implementation of vector and matrix operations. All representations save space by discarding the zero values, and, because the memory location of a non-zero in the vector no longer implies its index position, information about the index positions of the non-zeroes must be represented in some other way.

Existing implementation techniques, both software and hardware, are discussed in this chapter, and other options are examined.

## **3.2** Array storage for vectors

The standard data structure for storing a *dense* vector is what will be referred to here as the  $array^1$  – a vector with *n* elements, whose elements are each held in *m* memory locations, is stored in *mn* consecutive locations starting at the location

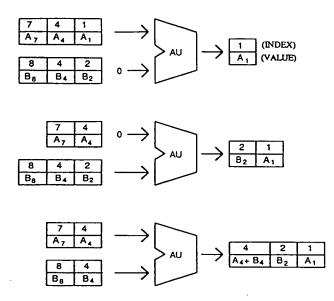

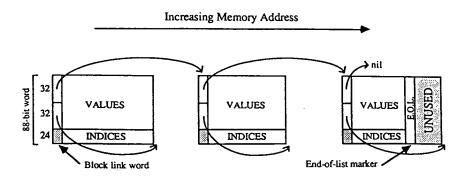

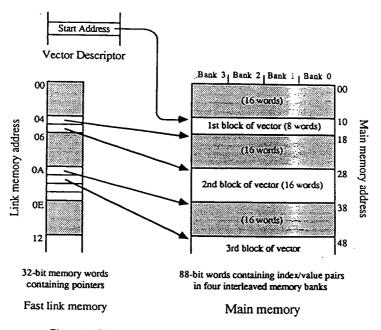

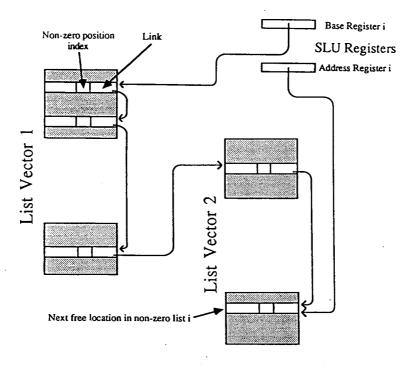

<sup>&</sup>lt;sup>1</sup>Many publications concerned with vector processing use the term *vector* to refer to both the mathematical entity involved in the computation, and its concrete representation in the memory of the computer. This is confusing when dealing with sparse vectors, for which a variety of concrete representations is possible, even for the same vector at different times within a single program. The term *vector* will here be used exclusively