# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## Automatic Test Pattern Generation for Asynchronous Circuits

Dilip P. Vasudevan

Doctor of Philosophy

Institute of Computing Systems Architecture

School of Informatics

University of Edinburgh

2011

#### **Abstract**

The testability of integrated circuits becomes worse with transistor dimensions reaching nanometer scales. Testing, the process of ensuring that circuits are fabricated without defects, becomes inevitably part of the design process; a technique called design for test (DFT). Asynchronous circuits have a number of desirable properties making them suitable for the challenges posed by modern technologies, but are severely limited by the unavailability of EDA tools for DFT and automatic test-pattern generation (ATPG).

This thesis is motivated towards developing test generation methodologies for asynchronous circuits. In total four methods were developed which are aimed at two different fault models: stuck-at faults at the basic logic gate level and transistor-level faults. The methods were evaluated using a set of benchmark circuits and compared favorably to previously published work.

First, ABALLAST is a partial-scan DFT method adapting the well-known BALLAST technique for asynchronous circuits where balanced structures are used to guide the selection of the state-holding elements that will be scanned. The test inputs are automatically provided by a novel test pattern generator, which uses time frame unrolling to deal with the remaining, non-scanned sequential C-elements. The second method, called AGLOB, uses algorithms from strongly-connected components in graph graph theory as a method for finding the optimal position of breaking the loops in the asynchronous circuit and adding scan registers. The corresponding ATPG method converts cyclic circuits into acyclic for which standard tools can provide test patterns. These patterns are then automatically converted for use in the original cyclic circuits. The third method, ASCP, employs a new cycle enumeration method to find the loops present in a circuit. Enumerated cycles are then processed using an efficient set covering heuristic to select the scan elements for the circuit to be tested. Applying these methods to the benchmark circuits shows an improvement in fault coverage compared to previous work, which, for some circuits, was substantial. As no single method consistently outperforms the others in all benchmarks, they are all valuable as a designer's suite of tools for testing. Moreover, since they are all scan-based, they are compatible and thus can be simultaneously used in different parts of a larger circuit.

In the final method, ATRANTE, the main motivation of developing ATPG is supplemented by transistor level test generation. It is developed for asynchronous circuits designed using a State Transition Graph (STG) as their specification. The transistor-level circuit faults are efficiently mapped onto faults that modify the original STG. For each potential STG fault, the ATPG tool provides a sequence of test vectors that expose the difference in behavior to the output ports. The fault coverage obtained was 52-72 % higher than the coverage obtained using the gate level tests.

Overall, four different design for test (DFT) methods for automatic test pattern generation (ATPG) for asynchronous circuits at both gate and transistor level were introduced in this thesis. A circuit extraction method for representing the asynchronous circuits at a higher level of abstraction was also implemented.

Developing new methods for the test generation of asynchronous circuits in this thesis facilitates the test generation for asynchronous designs using the CAD tools available for testing the synchronous designs. Lessons learned and the research questions raised due to this work will impact the future work to probe the possibilities of developing robust CAD tools for testing the future asynchronous designs.

#### **Acknowledgements**

I would like to extend my sincere gratitude to my supervisor Dr. Aristides Efthymiou for his patience and guidance during my research endeavor. I am very thankful to him for mentoring and supporting during these years. I would like to take this opportunity to thank my second supervisors Prof. Nigel Topham, Dr. Murray Cole and Prof. D.K. Arvind for their continuous guidance.

I would like to thank my postdoctoral mentors Prof. Michel Schellekens and Dr. Emanuel Popovici during my Thesis writing periods. Their support was invaluable and I would like to acknowledge their guidance for my smooth transition in to next stage of my academic career. I would like to thank my external examiner and my internal examiner for providing very helpful and guiding recommendations.

I would also like to thank Prof. Parag K. Lala and Prof. Patrick Parkerson who introduced me to research career during my postgraduate studies.

I would like to acknowledge the support offered by Engineering and Physical Sciences Research Council EPSRC and School of Informatics for my three years of study. I would like to thank UK ASYNC Forum for providing me a platform to network with other Asynchronous Design researchers.

I am grateful to my parents and my brother for their loving support. I would like to extend my sincere thanks to all my friends, relatives and acquaintances who played significant part in keeping me going during my PhD years.

I would like to extend my thanks to the Edinburgh Tango Society, which helped me spend my leisure time embarking something creative.

Finally, I would like to acknowledge my sincere thanks to the comments and reviews of all the blind reviewers of my conference papers, who made me a stronger and stronger academic writer and researcher.

### **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Dilip P. Vasudevan)

## **Contents**

| 1 | Intr | oductio      | n                                           | 1  |  |  |  |  |  |  |  |  |  |

|---|------|--------------|---------------------------------------------|----|--|--|--|--|--|--|--|--|--|

|   | 1.1  | Introdu      | action                                      | 1  |  |  |  |  |  |  |  |  |  |

|   |      | 1.1.1        | Past work                                   | 1  |  |  |  |  |  |  |  |  |  |

|   |      | 1.1.2        | Motivation                                  | 2  |  |  |  |  |  |  |  |  |  |

|   |      | 1.1.3        | Asynchronous Design and Testing in Industry | 4  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Contril      | butions                                     | 5  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Publica      | ations                                      | 8  |  |  |  |  |  |  |  |  |  |

|   |      | 1.3.1        | Thesis Overview                             | 8  |  |  |  |  |  |  |  |  |  |

|   | 1.4  | Summa        | ary                                         | 11 |  |  |  |  |  |  |  |  |  |

| 2 | Bacl | kground      | l                                           | 12 |  |  |  |  |  |  |  |  |  |

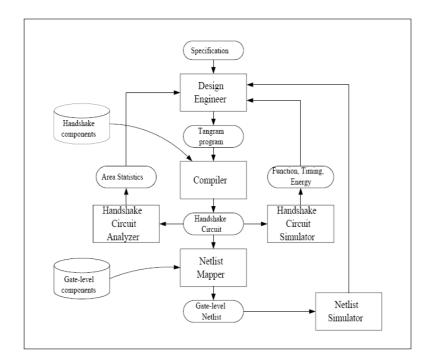

|   | 2.1  | Asyncl       | hronous Design                              | 12 |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.1        | Introduction                                | 12 |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.2        | Gates and Delay Models                      | 13 |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.3        | Types of circuits                           | 14 |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.4        | Logic Synthesis and Simulation:             | 15 |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Testing      | · · · · · · · · · · · · · · · · · · ·       | 17 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.1        | Introduction                                | 17 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.2        | Fault Modeling                              | 17 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.3        | Terminologies                               | 19 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.4        | Automatic Test Pattern Generation           | 19 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.5        | ATPG Algorithms                             | 20 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.6        | Scan Design                                 | 25 |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.7        | Partial Scan Design                         | 26 |  |  |  |  |  |  |  |  |  |

|   | 2.3  | Summa        | ary                                         | 27 |  |  |  |  |  |  |  |  |  |

| 3 | Rela | Related Work |                                             |    |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Introdu      | action                                      | 29 |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Related      | d Work                                      | 30 |  |  |  |  |  |  |  |  |  |

|   |      | 3.2.1    | Design For Test                                                        | 30 |

|---|------|----------|------------------------------------------------------------------------|----|

|   |      | 3.2.2    | Scan Testing                                                           | 33 |

|   |      | 3.2.3    | Synthesis For Testability                                              | 36 |

|   |      | 3.2.4    | Testing C-element                                                      | 37 |

|   |      | 3.2.5    | Test Pattern Generation for Asynchronous Circuits                      | 38 |

|   |      | 3.2.6    | Random Testing                                                         | 42 |

|   |      | 3.2.7    | Offline Testing                                                        | 44 |

|   |      | 3.2.8    | Functional Testing                                                     | 45 |

|   |      | 3.2.9    | Fault Simulators and Test methods                                      | 46 |

|   |      | 3.2.10   | Fault Modelling                                                        | 50 |

|   |      | 3.2.11   | Switch/Transistor Level Testing                                        | 52 |

|   |      | 3.2.12   | Self Testing Asynchronous Designs                                      | 53 |

|   |      | 3.2.13   | Critical Analysis                                                      | 54 |

|   | 3.3  | Conclu   | sion                                                                   | 56 |

| 4 | Auto | omatic T | Test Pattern Generation for Asynchronous Circuits: A Comparative       |    |

|   | Stud | ly       |                                                                        | 57 |

|   | 4.1  | Introdu  | action                                                                 | 57 |

|   | 4.2  | Autom    | atic Test Pattern Generation based on Symbolic Reachability Analysis . | 58 |

|   |      | 4.2.1    | Definition                                                             | 58 |

|   |      | 4.2.2    | Synchronous Abstraction of the Circuit State                           | 59 |

|   | 4.3  | Scan L   | atch Insertion Based Test Generation                                   | 61 |

|   | 4.4  | Compa    | urison of results                                                      | 63 |

|   |      | 4.4.1    | Example                                                                | 63 |

|   |      | 4.4.2    | Analysis                                                               | 64 |

|   |      | 4.4.3    | Factors affecting the fault coverage                                   | 70 |

|   | 4.5  |          | ision                                                                  |    |

|   |      |          |                                                                        |    |

| 5 |      |          | I-Asynchronous Circuit Test Generation based on Balanced Structures    |    |

|   | 5.1  | Introdu  | action                                                                 | 73 |

|   |      | 5.1.1    | Problem statement                                                      |    |

|   |      | 5.1.2    | Motivation                                                             | 74 |

|   | 5.2  | Backgr   | ound                                                                   | 74 |

|   |      | 5.2.1    | Cyclic and Acyclic Circuits                                            | 74 |

|   |      | 5.2.2    | Loops in circuit                                                       | 75 |

|   |      | 5.2.3    | BALLAST                                                                | 76 |

|   |      | 5.2.4    | Circuit topology                                                       | 76 |

|   | 53   | Test M   | ethodology                                                             | 83 |

|   |      | 5.3.1 Special Case - Cyclic circuits without C-elements                        |

|---|------|--------------------------------------------------------------------------------|

|   | 5.4  | Algorithms                                                                     |

|   |      | 5.4.1 Circuit Topology Description                                             |

|   |      | 5.4.2 Cycle detection                                                          |

|   |      | 5.4.3 Cyclic to Acyclic Conversion                                             |

|   |      | 5.4.4 ABALLAST                                                                 |

|   | 5.5  | Evaluation methodology                                                         |

|   |      | 5.5.1 Choice of Benchmarks                                                     |

|   |      | 5.5.2 Methods Evaluated                                                        |

|   |      | 5.5.3 Metrics used for Evaluation                                              |

|   | 5.6  | Results and Analysis                                                           |

|   |      | 5.6.1 C-element                                                                |

|   |      | 5.6.2 Benchmark "chu150"                                                       |

|   |      | 5.6.3 Results                                                                  |

|   | 5.7  | Conclusion                                                                     |

|   |      |                                                                                |

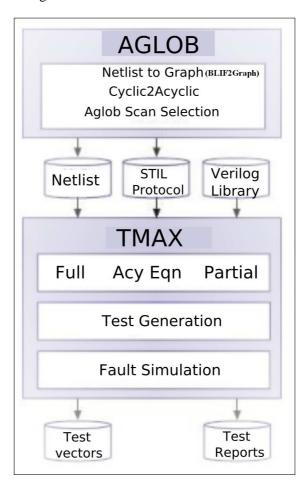

| 6 |      | OB - Asynchronous Circuit Test Generation Based on Breaking Global Loops 122   |

|   | 6.1  | Introduction                                                                   |

|   | 6.2  | Background                                                                     |

|   | 6.3  | Test Methodology                                                               |

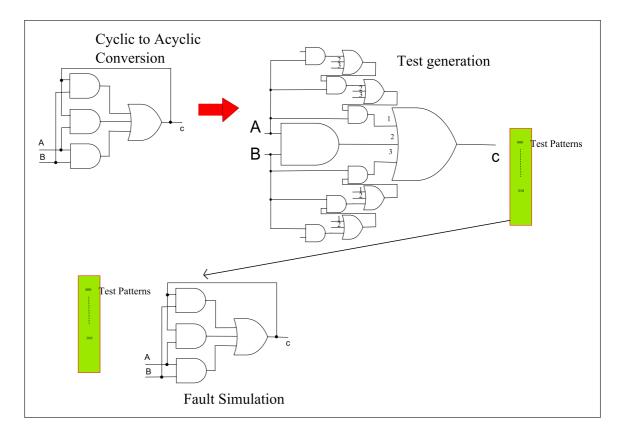

|   |      | 6.3.1 Cyclic-to-Acyclic Conversion                                             |

|   | 6.4  | Algorithms                                                                     |

|   |      | 6.4.1 Global loop breaking                                                     |

|   |      | 6.4.2 Cyclic-to-Acyclic Conversion                                             |

|   | 6.5  | Working Example and Results                                                    |

|   |      | 6.5.1 c-element                                                                |

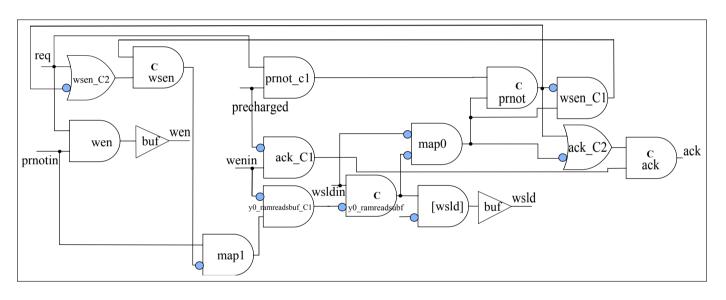

|   |      | 6.5.2 ram-read-sbuf                                                            |

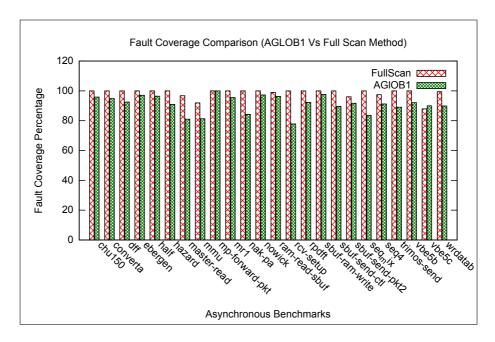

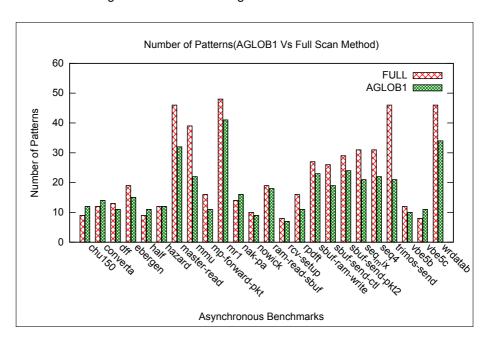

|   |      | 6.5.3 Experiments and Results                                                  |

|   | 6.6  | Conclusion                                                                     |

| 7 | ASC  | P - A Set Covering Problem based Test Generation for Asynchronous Circuits 143 |

| , | 7.1  | Introduction                                                                   |

|   | 7.2  | Preliminaries                                                                  |

|   | 7.3  | Algorithms                                                                     |

|   | , .5 | 7.3.1 Cycle enumeration                                                        |

|   |      | 7.3.2 SCP algorithm                                                            |

|   | 7.4  | Methodology                                                                    |

|   |      | Experiments and Results                                                        |

|   |      |                                                                                |

|   | 7.6                                                                                       | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54                                                                                |

|---|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 8 | ACL                                                                                       | ARION - High level circuit extraction for Asynchronous Circuit Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                                |

|   | 8.1                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56                                                                                |

|   | 8.2                                                                                       | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57                                                                                |

|   |                                                                                           | 8.2.1 Clarion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57                                                                                |

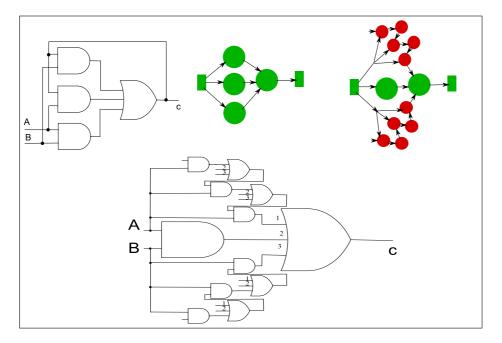

|   | 8.3                                                                                       | High Level Circuit Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58                                                                                |

|   |                                                                                           | 8.3.1 Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                |

|   | 8.4                                                                                       | Register clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                |

|   |                                                                                           | 8.4.1 Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63                                                                                |

|   | 8.5                                                                                       | Combinational logic clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72                                                                                |

|   | 8.6                                                                                       | Fanout clustering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76                                                                                |

|   |                                                                                           | 8.6.1 Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                   |

|   | 8.7                                                                                       | Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80                                                                                |

|   | 8.8                                                                                       | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   |

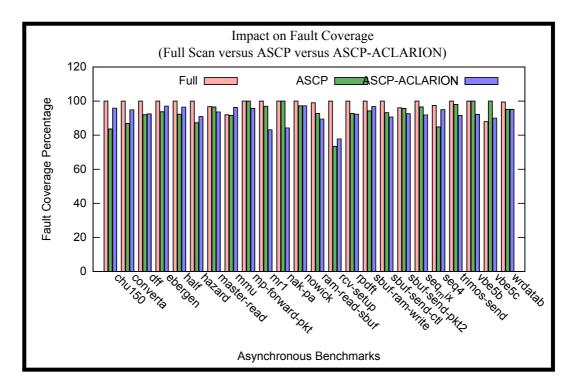

|   |                                                                                           | 8.8.1 Impact on Fault Coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87                                                                                |

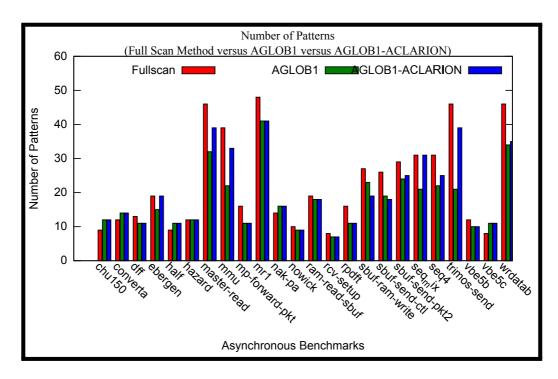

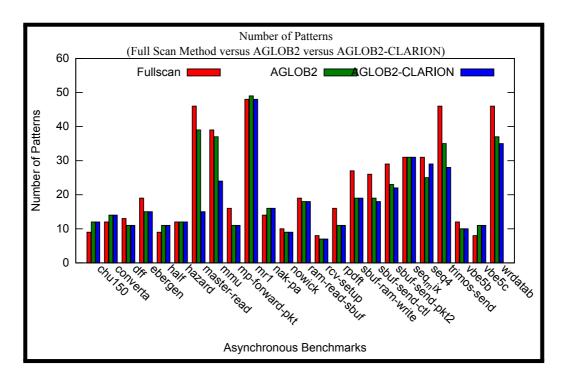

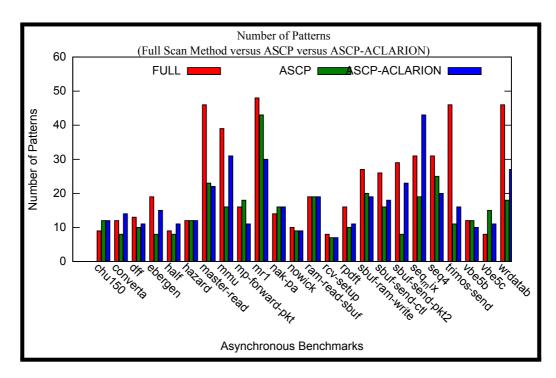

|   |                                                                                           | 8.8.2 Impact on Number of patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                                                                |

|   | 8.9                                                                                       | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92                                                                                |

|   |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                   |

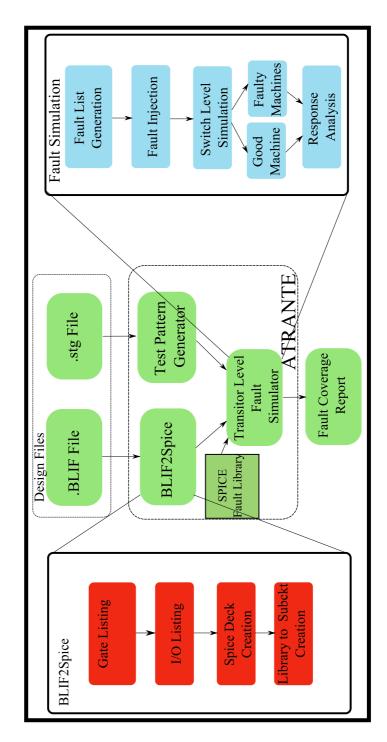

| 9 | ATR                                                                                       | ANTE - Transistor Level Test Generation for Asynchronous Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96                                                                                |

| 9 | <b>ATR</b> 9.1                                                                            | ANTE - Transistor Level Test Generation for Asynchronous Circuits  Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                   |

| 9 |                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96                                                                                |

| 9 |                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96<br>97                                                                          |

| 9 | 9.1                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>98                                                                    |

| 9 | 9.1                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>98<br>98                                                              |

| 9 | <ul><li>9.1</li><li>9.2</li></ul>                                                         | Introduction199.1.1 Motivation: Why transistor level testing?19Background199.2.1 Asynchronous Circuit Representation19Problem Statement20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96<br>97<br>98<br>98                                                              |

| 9 | <ul><li>9.1</li><li>9.2</li></ul>                                                         | Introduction199.1.1 Motivation: Why transistor level testing?19Background199.2.1 Asynchronous Circuit Representation19Problem Statement20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96<br>97<br>98<br>98<br>00                                                        |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li></ul>                                             | Introduction199.1.1 Motivation: Why transistor level testing?19Background199.2.1 Asynchronous Circuit Representation19Problem Statement209.3.1 Motivating Example20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96<br>97<br>98<br>98<br>00<br>00                                                  |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li></ul>                                             | Introduction199.1.1 Motivation: Why transistor level testing?19Background199.2.1 Asynchronous Circuit Representation19Problem Statement209.3.1 Motivating Example20Test Method20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03                                      |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li></ul>                                             | Introduction199.1.1 Motivation: Why transistor level testing?19Background199.2.1 Asynchronous Circuit Representation19Problem Statement209.3.1 Motivating Example20Test Method209.4.1 Fault Model20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06                          |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li></ul>                                             | Introduction       19         9.1.1 Motivation: Why transistor level testing?       19         Background       19         9.2.1 Asynchronous Circuit Representation       19         Problem Statement       20         9.3.1 Motivating Example       20         Test Method       20         9.4.1 Fault Model       20         9.4.2 Test Algorithm       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06<br>07                    |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li><li>9.4</li></ul>                                 | Introduction       19         9.1.1 Motivation: Why transistor level testing?       19         Background       19         9.2.1 Asynchronous Circuit Representation       19         Problem Statement       20         9.3.1 Motivating Example       20         Test Method       20         9.4.1 Fault Model       20         9.4.2 Test Algorithm       20         9.4.3 Fault Simulation       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06<br>07                    |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li><li>9.4</li></ul>                                 | Introduction       19         9.1.1 Motivation: Why transistor level testing?       19         Background       19         9.2.1 Asynchronous Circuit Representation       19         Problem Statement       20         9.3.1 Motivating Example       20         Test Method       20         9.4.1 Fault Model       20         9.4.2 Test Algorithm       20         9.4.3 Fault Simulation       20         Experiment Results       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06<br>07<br>09              |

| 9 | <ul><li>9.1</li><li>9.2</li><li>9.3</li><li>9.4</li></ul>                                 | Introduction       19         9.1.1 Motivation: Why transistor level testing?       19         Background       19         9.2.1 Asynchronous Circuit Representation       19         Problem Statement       20         9.3.1 Motivating Example       20         Test Method       20         9.4.1 Fault Model       20         9.4.2 Test Algorithm       20         9.4.3 Fault Simulation       20         Experiment Results       20         9.5.1 Test Generation and Fault Simulation       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06<br>07<br>09              |

|   | <ul><li>9.1</li><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li><li>9.6</li></ul>         | Introduction       19.1.1 Motivation: Why transistor level testing?       19.1.1 Background         9.2.1 Asynchronous Circuit Representation       19.2.1 Asynchronous Circuit Representation         Problem Statement       20.2.1 Asynchronous Circuit Representation         Problem Statement       20.2.1 Asynchronous Circuit Representation         9.3.1 Motivating Example       20.2.1 Asynchronous Circuit Representation         10.2 Test Method       20.2.1 Asynchronous Circuit Representation         9.4.1 Fault Model       20.2.2 Asynchronous Circuit Representation         9.4.2 Test Algorithm       20.2.2 Asynchronous Circuit Representation         9.4.1 Fault Model       20.2.2 Test Algorithm         9.4.2 Test Algorithm       20.2.2 Test Algorithm         9.4.3 Fault Simulation       20.2.2 Test Generation and Fault Simulation         9.5.1 Test Generation and Fault Simulation       20.2.2 Analysis         9.5.2 Analysis       20.2.2 Summary          2 Summary       20.2.2 Summary | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06<br>07<br>09<br>09        |

|   | <ul> <li>9.1</li> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> <li>Conc</li> </ul> | Introduction       19         9.1.1 Motivation: Why transistor level testing?       19         Background       19         9.2.1 Asynchronous Circuit Representation       19         Problem Statement       20         9.3.1 Motivating Example       20         Test Method       20         9.4.1 Fault Model       20         9.4.2 Test Algorithm       20         9.4.3 Fault Simulation       20         Experiment Results       20         9.5.1 Test Generation and Fault Simulation       20         9.5.2 Analysis       2         Summary       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 96<br>97<br>98<br>98<br>98<br>00<br>00<br>03<br>05<br>06<br>07<br>09<br>10<br>112 |

| 10.3 Conclusion | <br> | <br> | <br> | <br> | <br> |  |  |  |  |  | 219 |

|-----------------|------|------|------|------|------|--|--|--|--|--|-----|

| Bibliography    |      |      |      |      |      |  |  |  |  |  | 221 |

## **List of Figures**

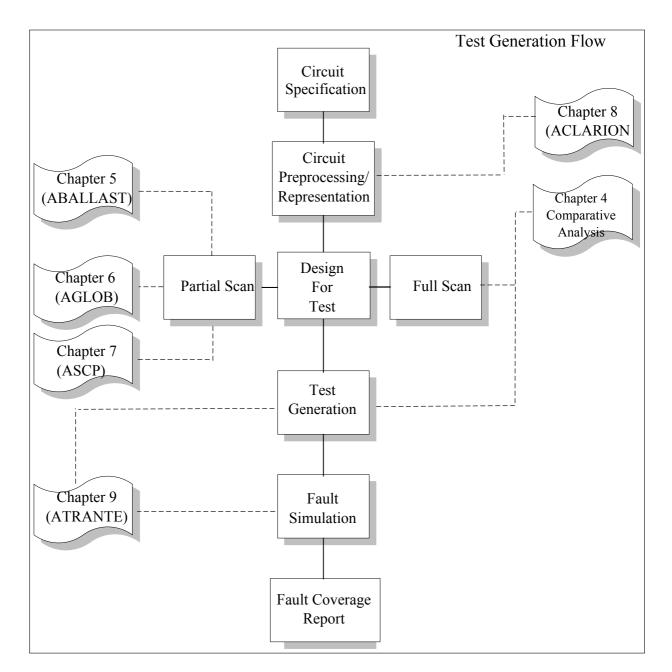

| 1.1  | Contributation of the Thesis                                          | 7  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | Organization of the Thesis                                            | 10 |

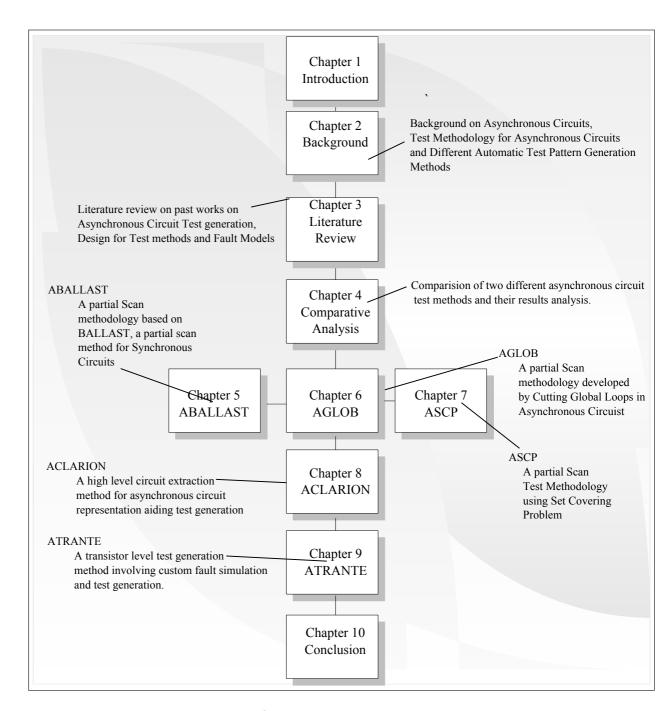

| 2.1  | Asynchronous Design                                                   | 13 |

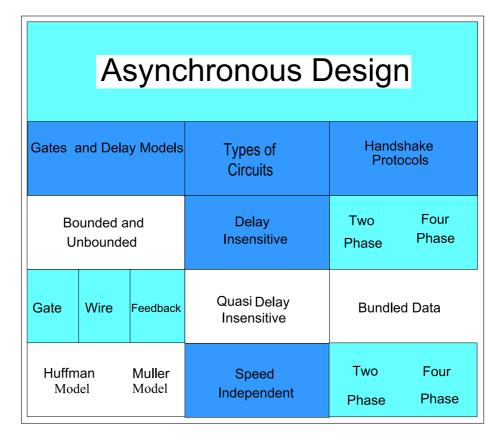

| 2.2  | Asynchronous Design Flow - language based [KF91]                      | 15 |

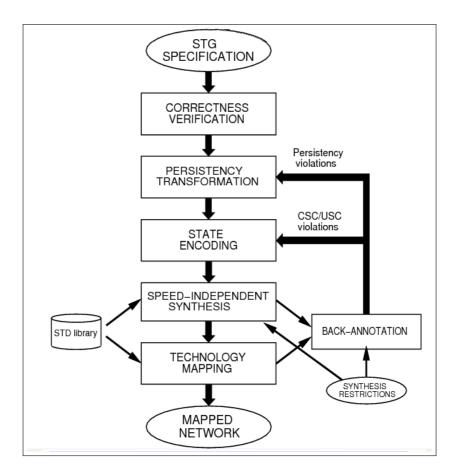

| 2.3  | Asynchronous Design Flow: Graph based(Derived from petri net) [E.P97] | 16 |

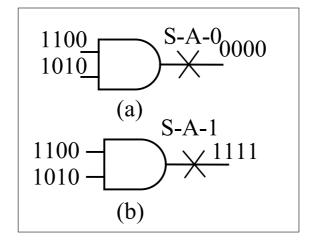

| 2.4  | Stuck-at Faults                                                       | 18 |

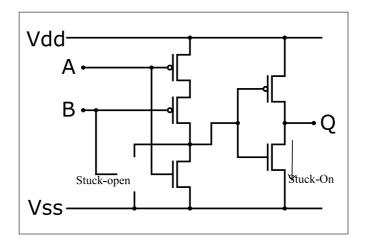

| 2.5  | Stuck-Open/Close Faults                                               | 18 |

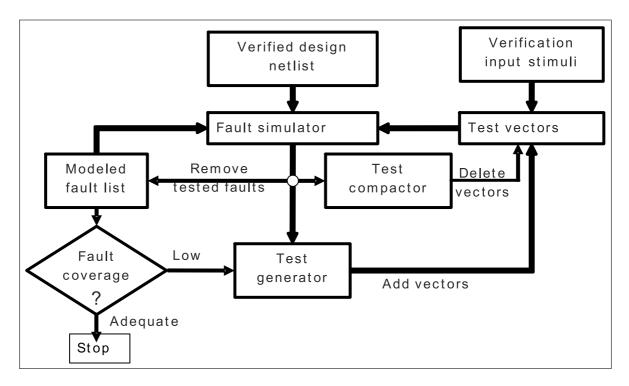

| 2.6  | An ATPG System in a VLSI Design Process [MV00]                        | 20 |

| 2.7  | D-Algorithm [[MAF90]]                                                 | 22 |

| 2.8  | PODEM Algorithm [[MAF90]]                                             | 24 |

| 2.9  | FAN Algorithm[[MAF90]]                                                | 25 |

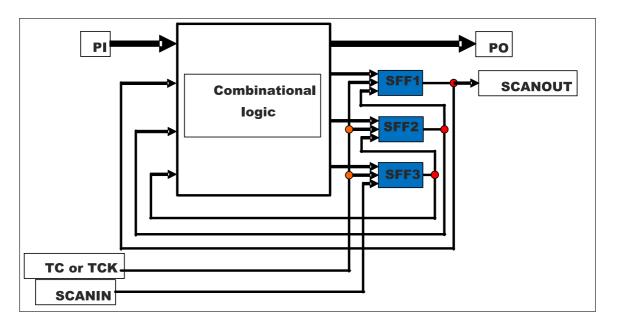

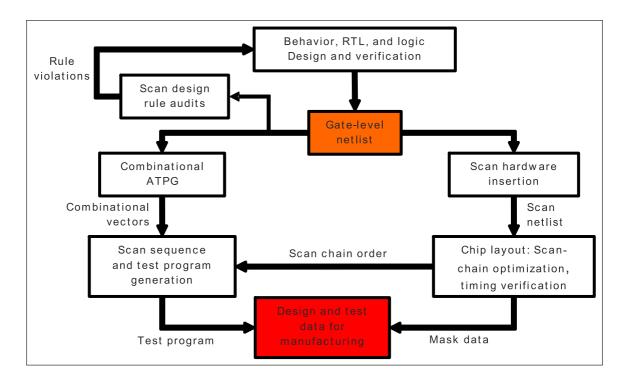

| 2.10 | Full Scan Architecture [MV00]                                         | 26 |

| 2.11 | Automated Scan Design [MV00]                                          | 27 |

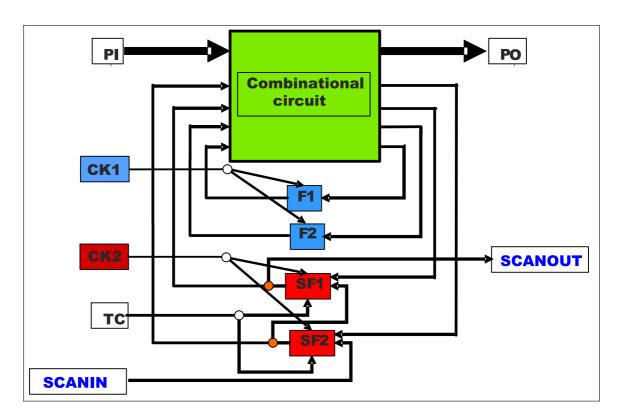

| 2.12 | Partial Scan Architecture [MV00]                                      | 28 |

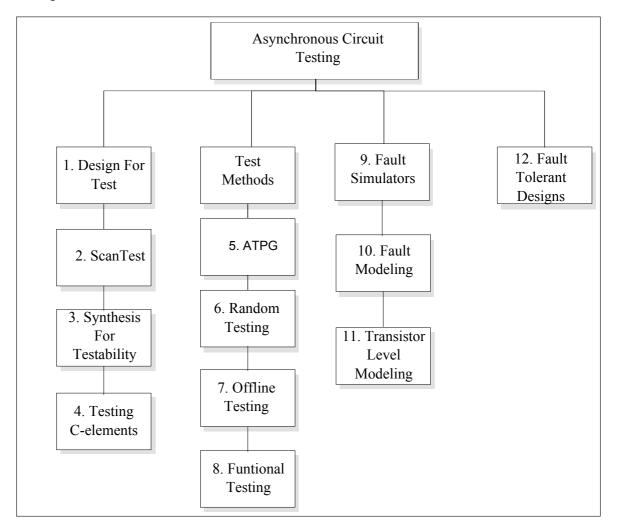

| 3.1  | Asynchronous Circuit Testing - A Short Review                         | 30 |

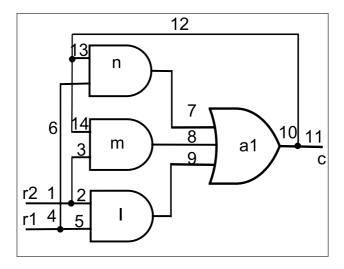

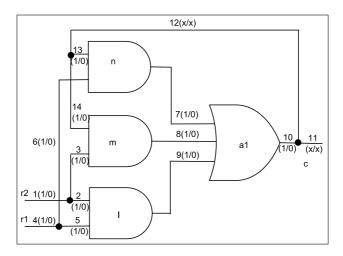

| 4.1  | Majority Gate Based C-Element                                         | 59 |

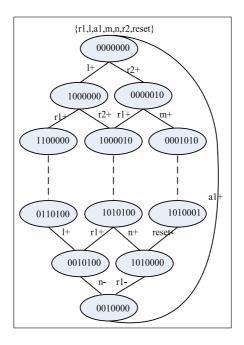

| 4.2  | State Graph                                                           | 60 |

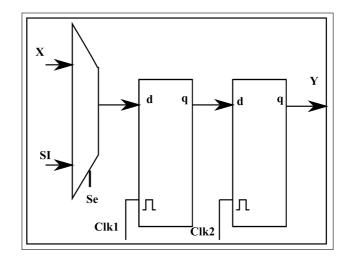

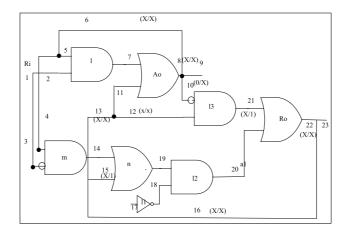

| 4.3  | LSSD Latch Desgin                                                     | 62 |

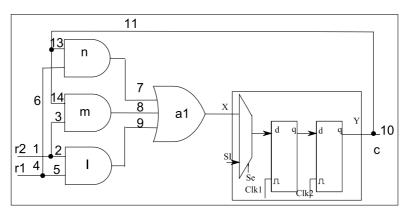

| 4.4  | Celement Design with LSSD Latch                                       | 62 |

| 4.5  | C-element-Faults detected by testify                                  | 63 |

| 4.6  | Half-Faults detected by testify                                       | 64 |

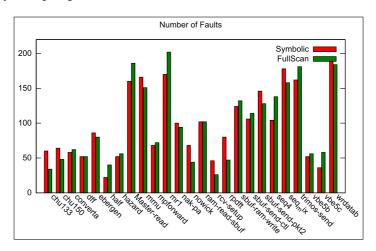

| 4.7  | Total number of Faults - Symbolic versus Full Scan                    | 67 |

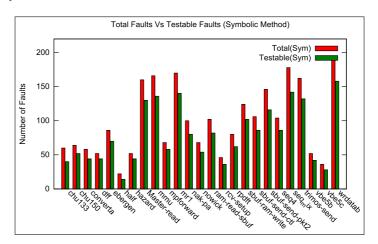

| 4.8  | Total Faults Vs Testable Faults - Symbolic Method                     | 68 |

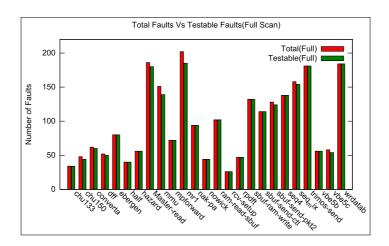

| 4.9  | Total Faults Vs Testable Faults - Full Scan Method                    | 68 |

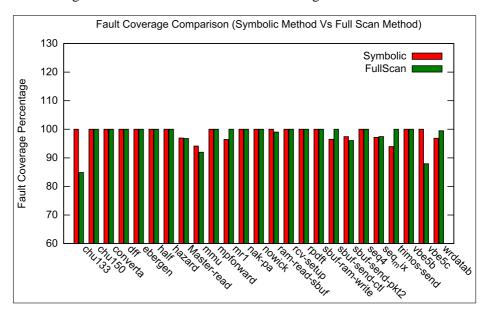

| 4.10 | Fault Coverage Comparision - Symbolic Vs Full Scan                    | 69 |

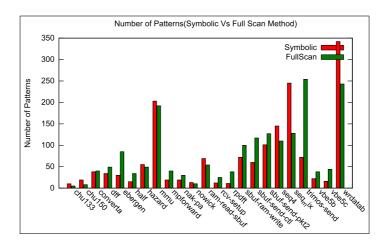

| 4.11 | Comparision of Test Patterns - Symbolic Vs Full Scan                  | 70 |

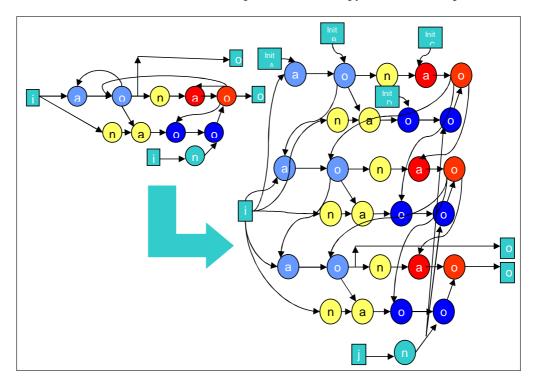

| 5.1   | C-element - Cyclic to Acyclic Conversion                                         |

|-------|----------------------------------------------------------------------------------|

| 5.2   | Benchmark "half" - Cyclic circuit and equivalent acyclic circuit                 |

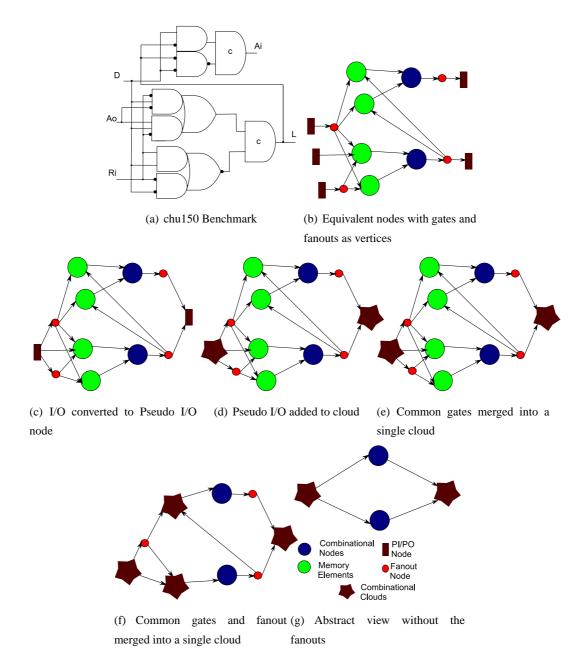

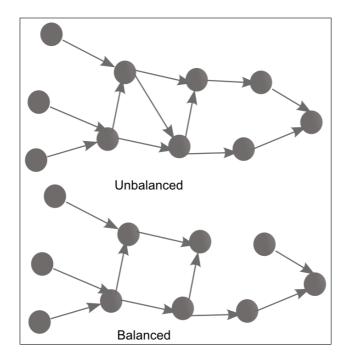

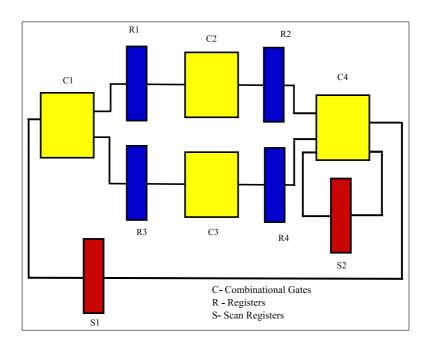

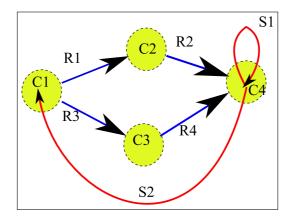

| 5.4   | Unbalanced and Balanced structures                                               |

| 5.5   | Partial Scan Circuit using Balanced structures                                   |

| 5.6   | Example Circuit - Graph Representation                                           |

| 5.7   | BALLAST Method Example                                                           |

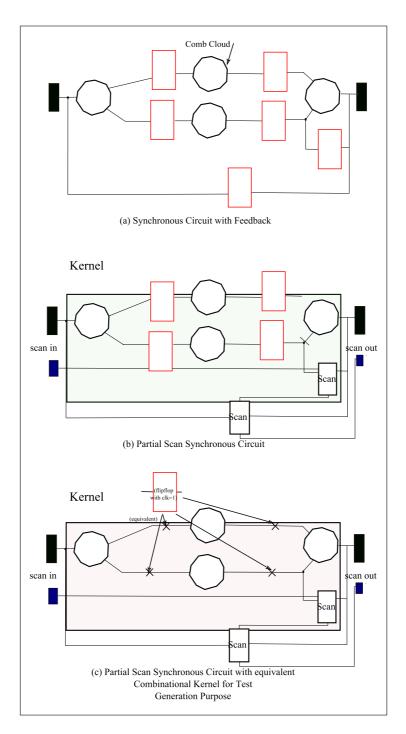

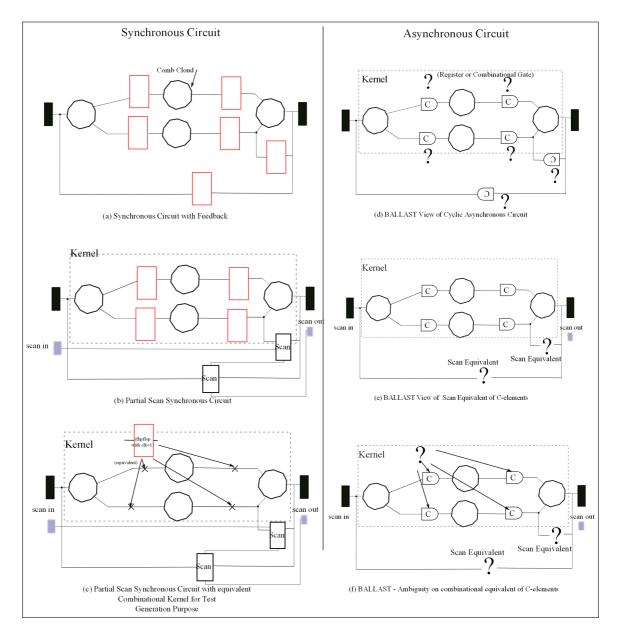

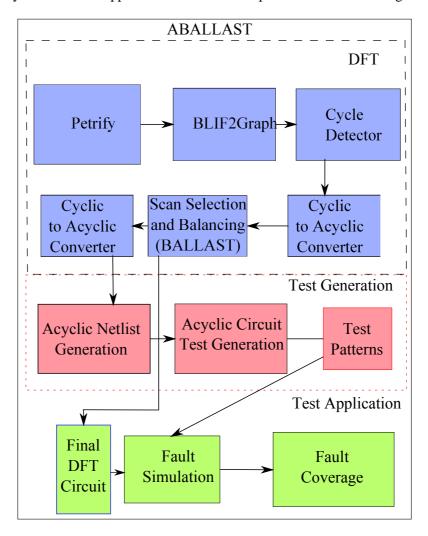

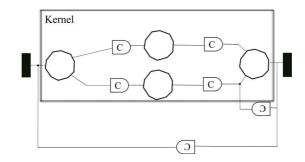

| 5.8   | BALLAST Method on Synchronous and Asynchronous Circuits 83                       |

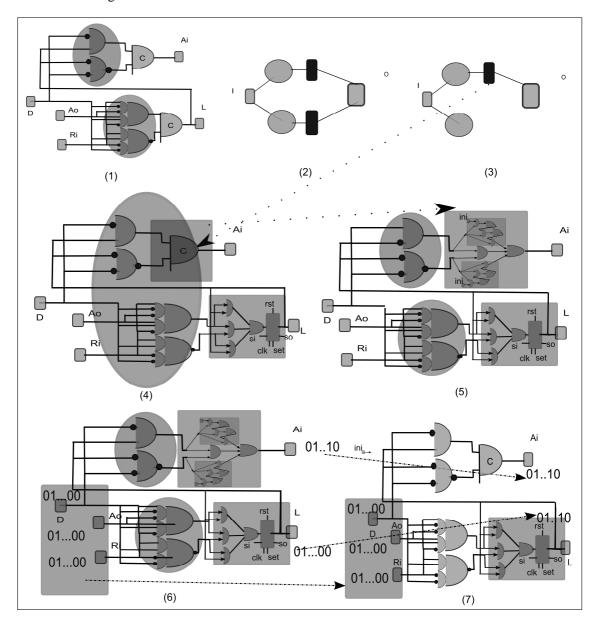

| 5.9   | Test Methodology                                                                 |

| 5.10  | Optional caption for list of figures 1                                           |

| 5.11  | Test generation for cyclic circuit without state holding elements                |

| 5.12  | Cyclic to Acyclic conversion - C-element                                         |

| 5.13  | Graph traversal in GR procedure                                                  |

| 5.14  | Ordered Vertex Sequence                                                          |

| 5.15  | C-element -Majority Gate Implementation                                          |

| 5.16  | Test Generation for chu150                                                       |

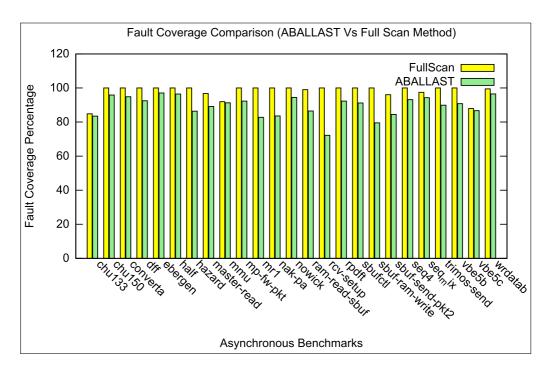

| 5.17  | Fault Coverage comparison - ABALLAST vs Full scan                                |

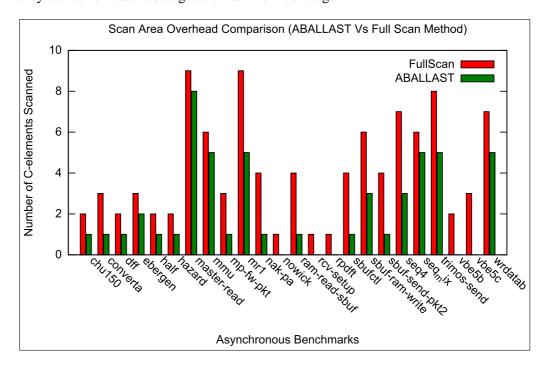

| 5.18  | Scan area overhead comparison                                                    |

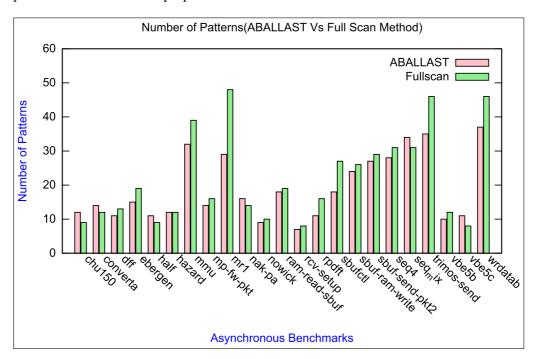

| 5.19  | Comparison of Number of Patterns Generated -ABALLAST Vs Full Scan 105            |

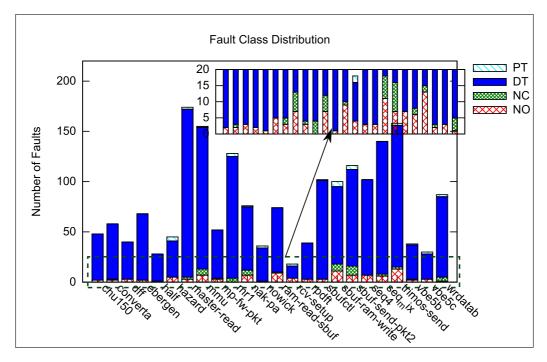

| 5.20  | Distribution of different fault classes, PT- Possible Detected, DT- Detected, NO |

|       | - Not observable, NC - Not Controllable                                          |

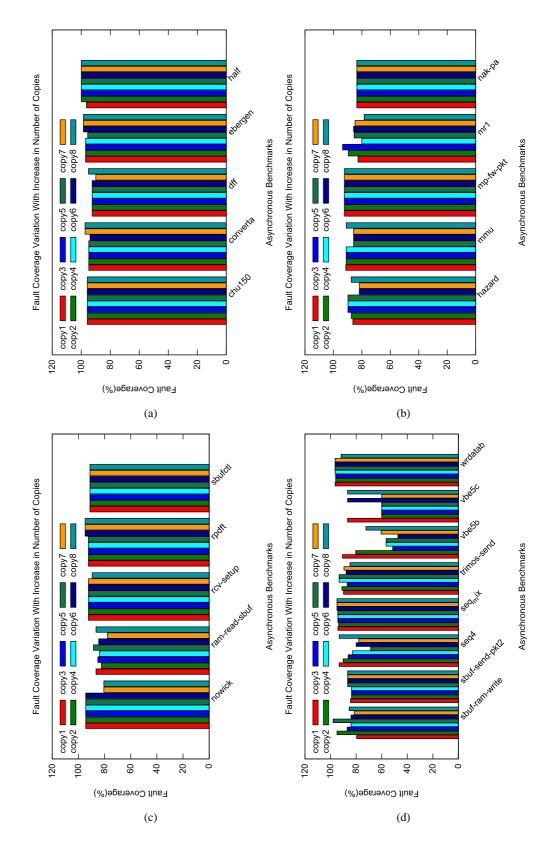

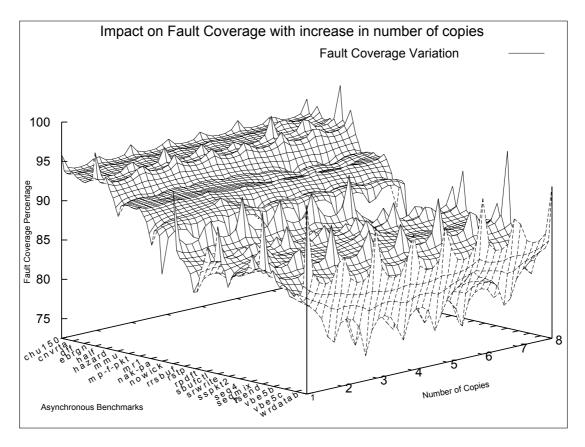

| 5.21  | Fault Coverage of Benchmarks with copies 1 to 8                                  |

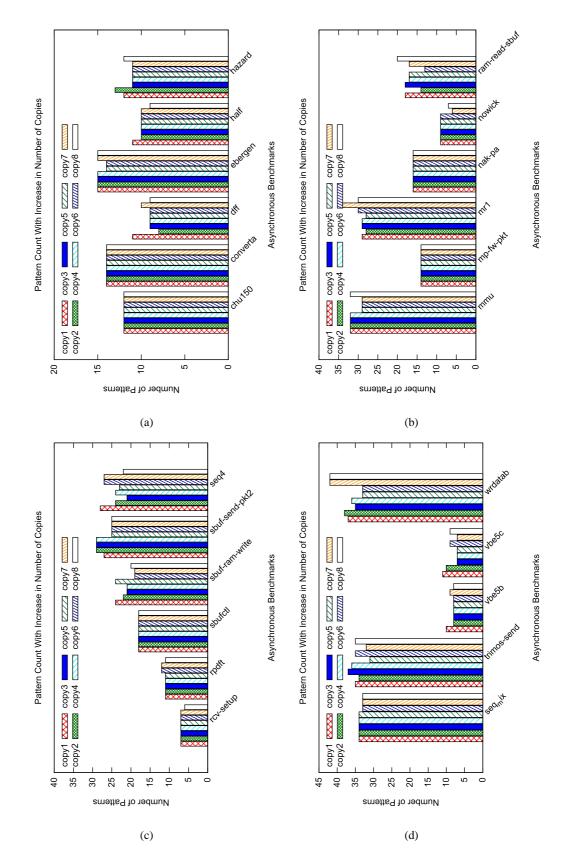

| 5.22  | Number of Test Patterns for Benchmarks with copies 1 to 2                        |

| 5.23  | 3D Plot depicting the impact on fault coverage                                   |

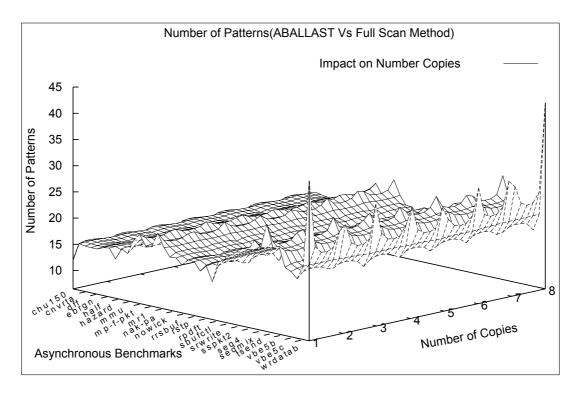

| 5.24  | 3D Plot depicting the impact on number of patterns                               |

| 6 1   | Test Methodology                                                                 |

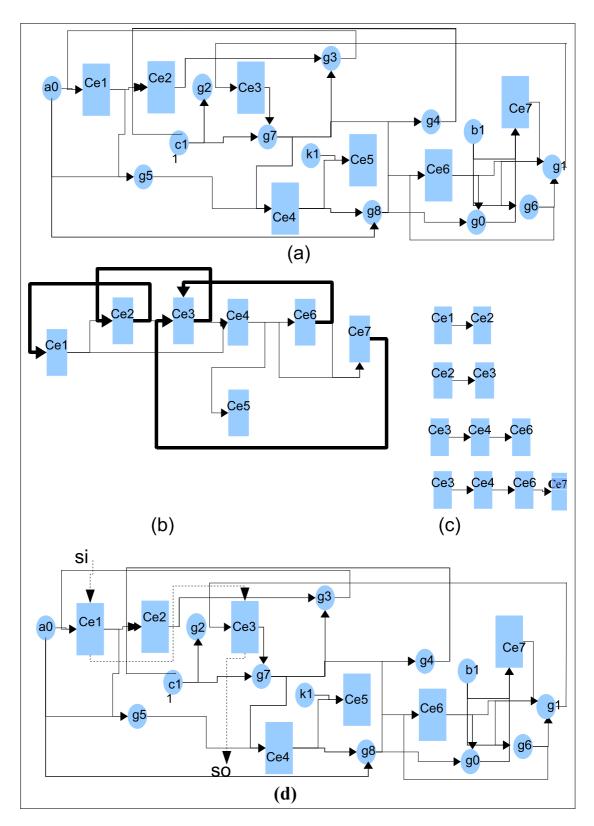

| 6.2   | Scan Selection         127                                                       |

| 6.3   |                                                                                  |

| 6.4   | C-element Cyclic to Acyclic Conversion                                           |

| 6.5   | Benchmark "ramreadsbuf"                                                          |

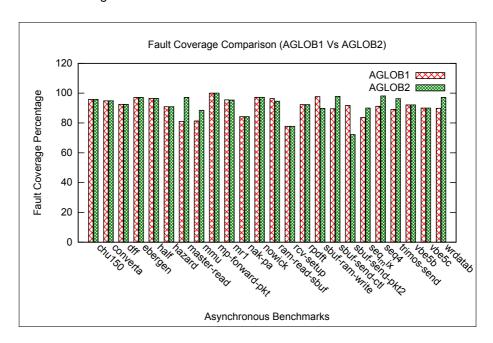

| 6.6   | Fault Coverage - Full Scan Vs AGLOB1                                             |

| 6.7   | Number of Patterns - Full Scan versus AGLOB1                                     |

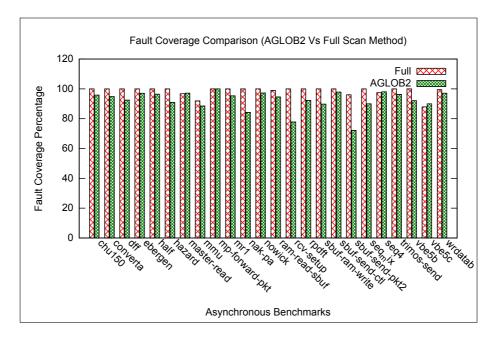

| 6.8   | Fault Coverage - Full Scan versus AGLOB2                                         |

|       |                                                                                  |

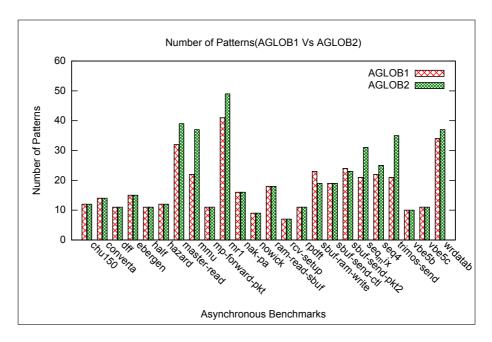

| 6.9   | Number of Patterns - AGLOB1 vs AGLOB2                                            |

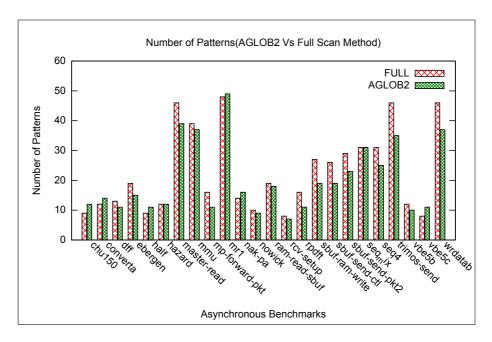

|       | Number of Patterns - Full Scan vs AGLOB2                                         |

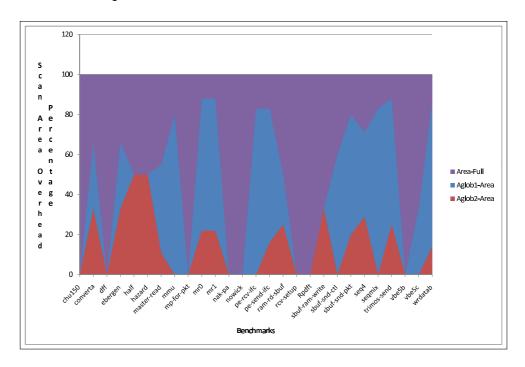

|       | Results - Area Overhead comparison                                               |

| 11 1/ | NENDOS - ALEA CIVELDEAD COMUNICIONO                                              |

| 7.1  | Function - EnumPath                                                           |

|------|-------------------------------------------------------------------------------|

| 7.2  | Function - Wscp                                                               |

| 7.3  | Greedy Heuristic                                                              |

| 7.4  | Function - Optimize                                                           |

| 7.5  | Algorithm: ASCP                                                               |

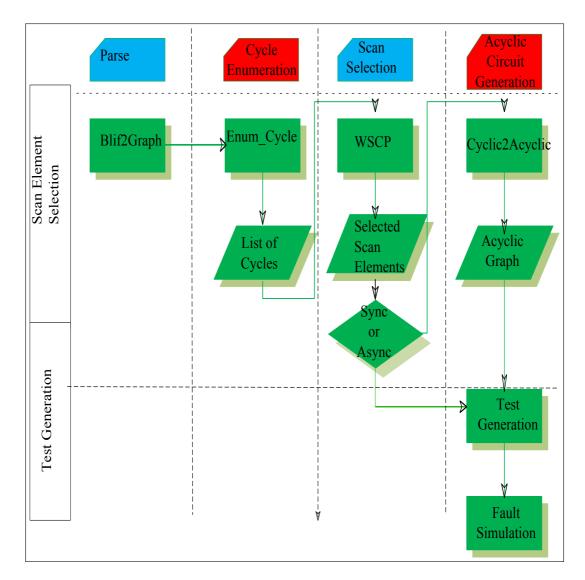

| 7.6  | Test Methodology                                                              |

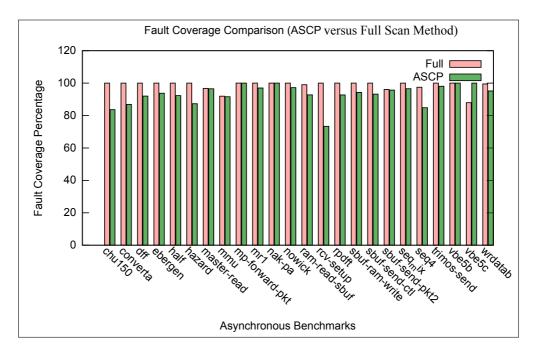

| 7.7  | Fault Coverage Comparison - ASCP versus Full Scan Method                      |

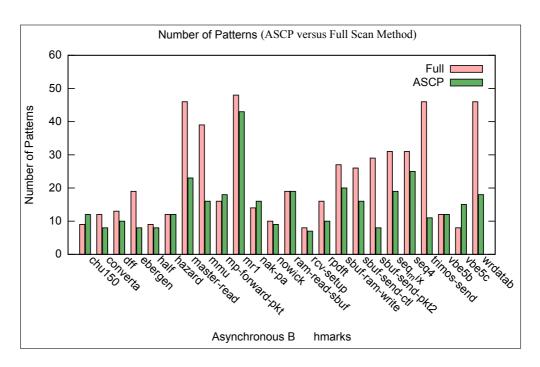

| 7.8  | Number of Patterns - ASCP versus Full Scan Method                             |

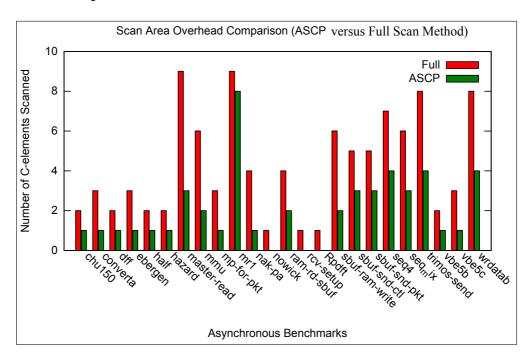

| 7.9  | Comparison of number of scanned C-elements for 27 benchmarks (X-axis=Circuit  |

|      | name, Y-axis = Scan Area Overhead Percentage)                                 |

| 8.1  | Function Span                                                                 |

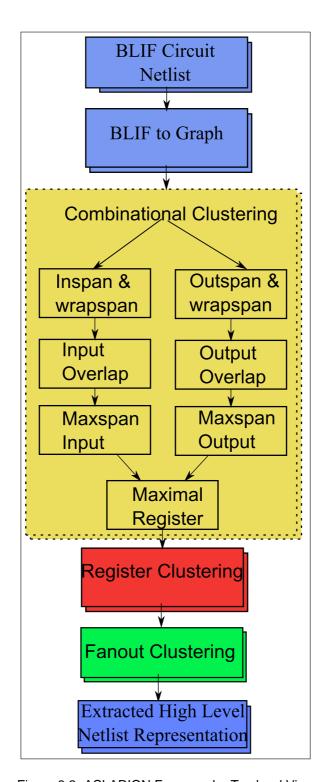

| 8.2  | ACLARION Framework - Top-level View                                           |

| 8.3  | Function:Overlap                                                              |

| 8.4  | Function:Outspan and Output WrapSpan                                          |

| 8.5  | Function:Input Spand and Input WrapSpan                                       |

| 8.6  | Function:Output Overlap                                                       |

| 8.7  | Function:Input Overlap                                                        |

| 8.8  | Function: Maxspan Output                                                      |

| 8.9  | Function:Maxspan Input                                                        |

| 8.10 | Function:Maximal Register                                                     |

| 8.11 | Function:CLU Clustering - part1                                               |

| 8.12 | Function:CLU Clustering:part 2                                                |

| 8.13 | Function Fanout Clustering - part 1                                           |

| 8.14 | Function Fanout Clustering - part 2                                           |

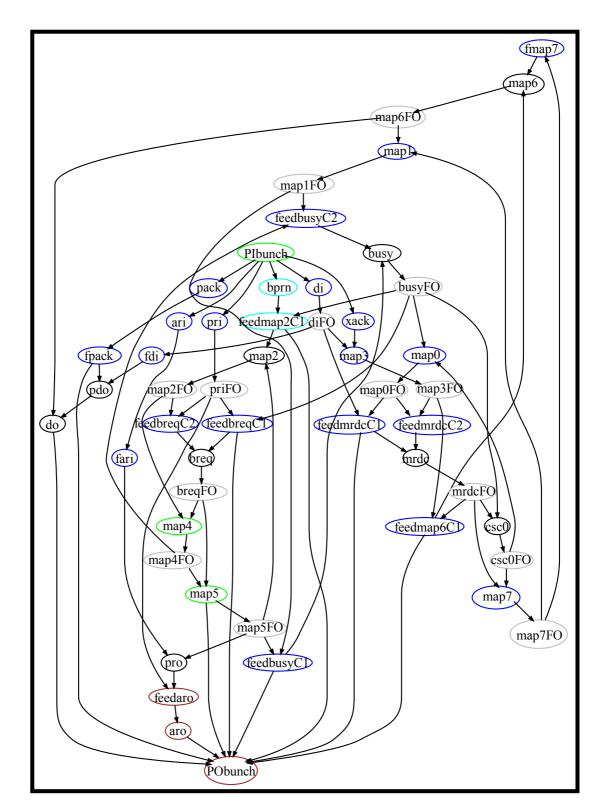

| 8.15 | Master-read Benchmark                                                         |

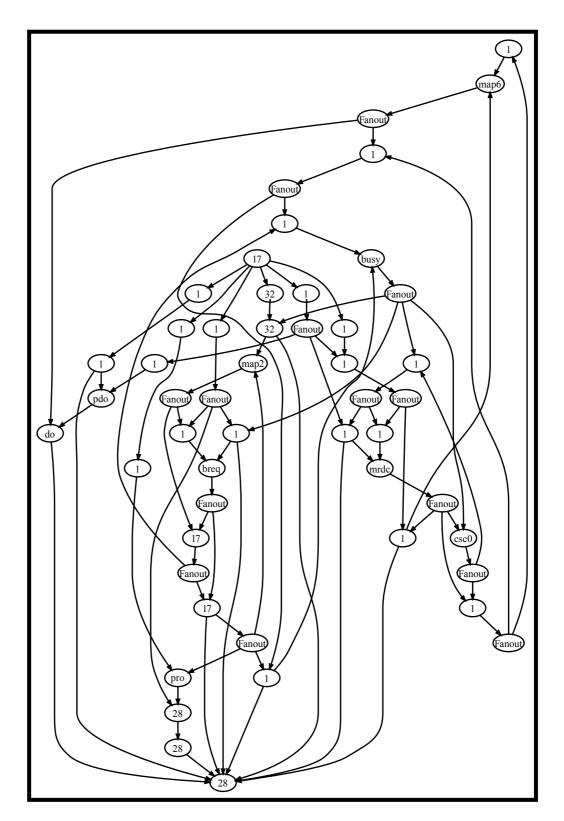

| 8.16 | master-read benchmark - numbered clouds                                       |

| 8.17 | Extracted High Level View - master-read benchmark                             |

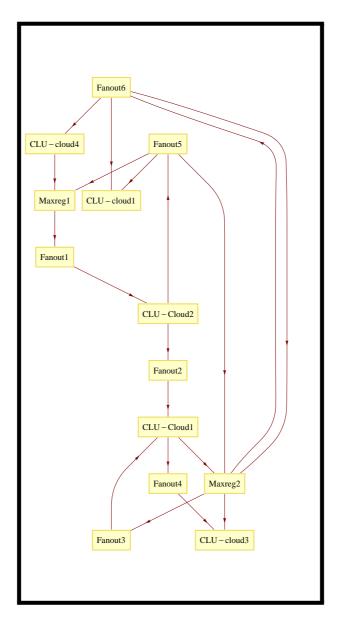

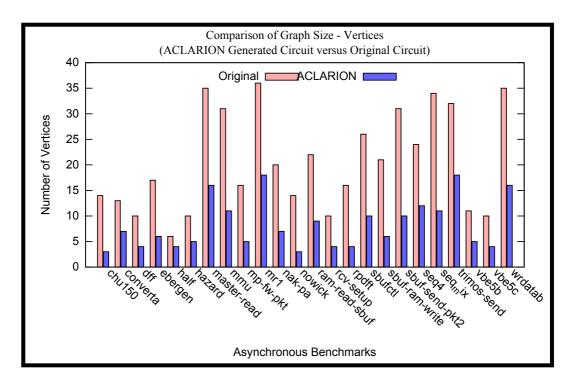

| 8.18 | Graph Size Comparision - Vertices                                             |

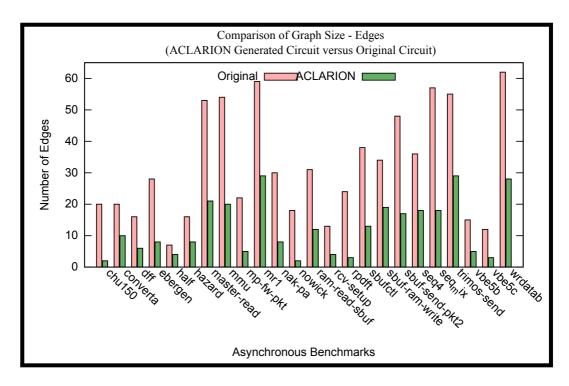

| 8.19 | Graph Size Comparision - Edges                                                |

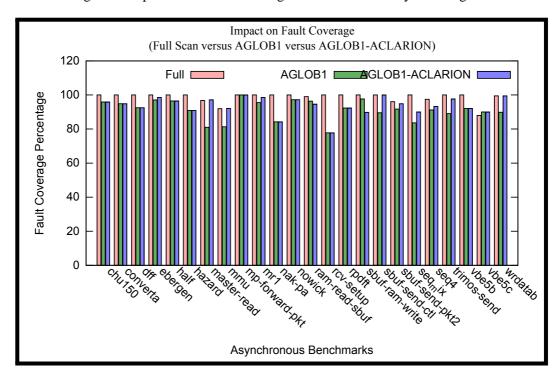

| 8.20 | Impact on Fault Coverage - Full Scan versus AGLOB1 versus AGLOB1-ACLARION188  |

| 8.21 | Impact on Fault Coverage - Full Scan versus AGLOB2 versus AGLOB2-ACLARION189  |

| 8.22 | Impact on Fault Coverage- Full Scan versus ASCP versus ASCP-ACLARION . 190    |

| 8.23 | Impact on Number of Patterns - Full Scan versus AGLOB1 versus AGLOB1-         |

|      | ACLARION                                                                      |

| 8.24 | Impact on Number of Patterns - Full Scan versus AGLOB2 versus AGLOB2-         |

|      | ACLARION                                                                      |

| 8.25 | Impact on Number of Patterns - Full Scan versus ASCP versus ASCP-ACLARION 193 |

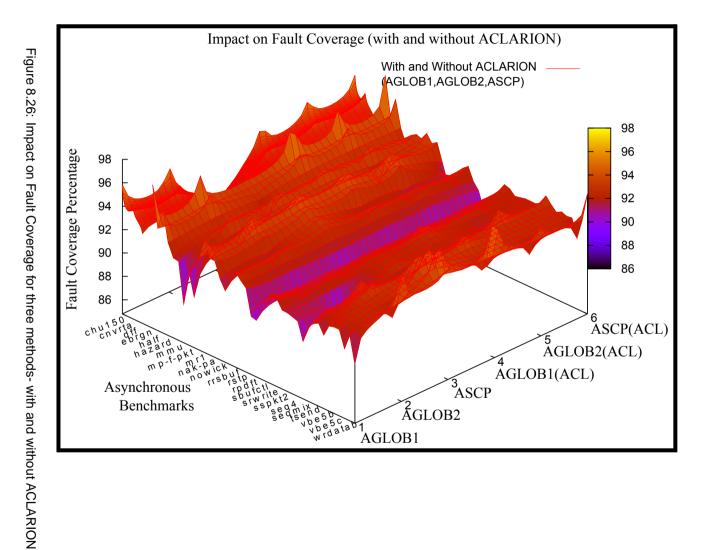

| 8.26 | Impact on Fault Coverage for three methods- with and without ACLARION 194       |

|------|---------------------------------------------------------------------------------|

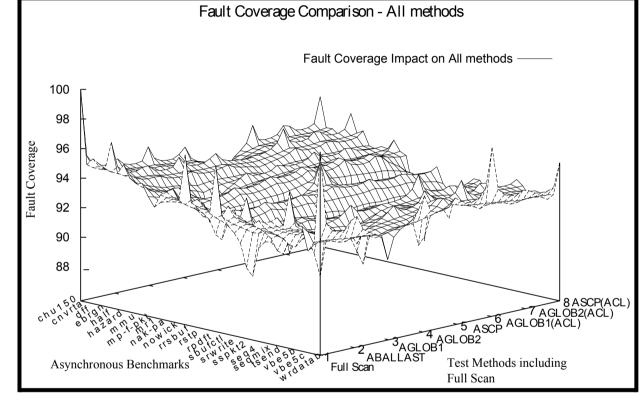

| 8.27 | Fault Coverage Comparison - All methods                                         |

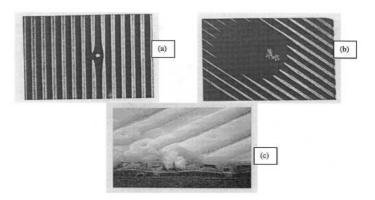

| 9.1  | Open Defects. a) A foreign particle causing a line to open and a line thinning, |

|      | b) A contaminating particle causing 7 line opens, c) Defect which caused an     |

|      | open in metal 2 and short in metal 1. [RM00]                                    |

| 9.2  | Stuck-at-false fault and Stuck-at-true fault                                    |

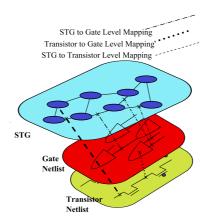

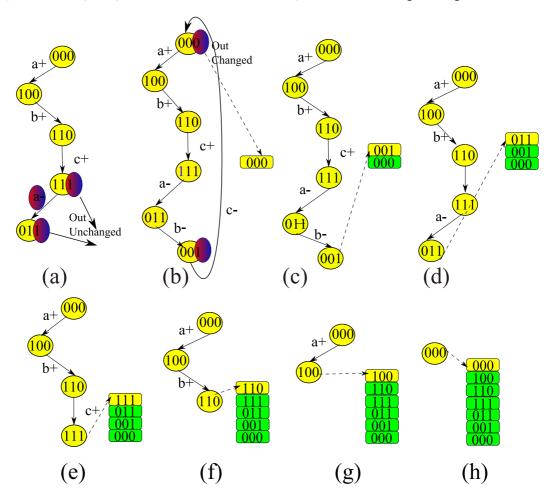

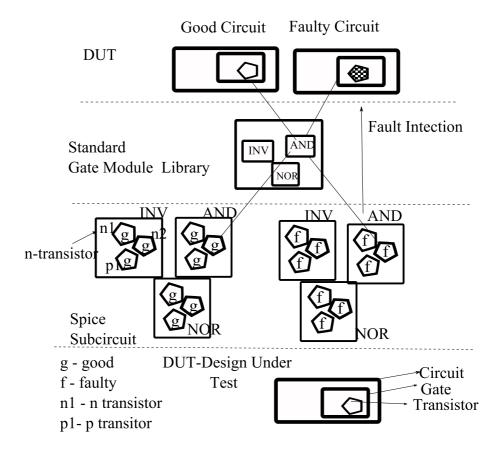

| 9.3  | Fault Mapping in STG based asynchronous circuit netlist                         |

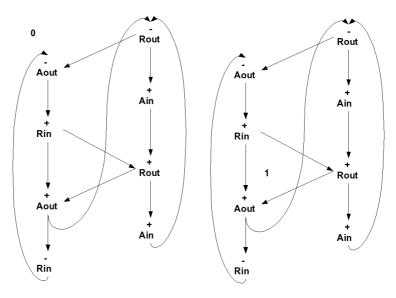

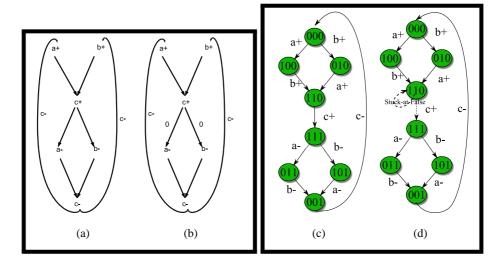

| 9.4  | SG and STG for faulty circuit with transistor P3 Stuck-on fault shown in (a),   |

|      | (b), (c), (d)respectively                                                       |

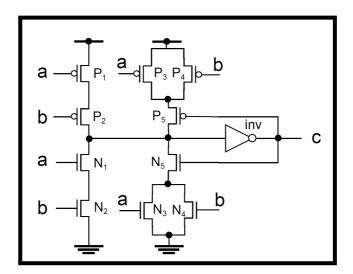

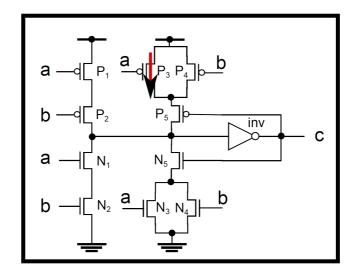

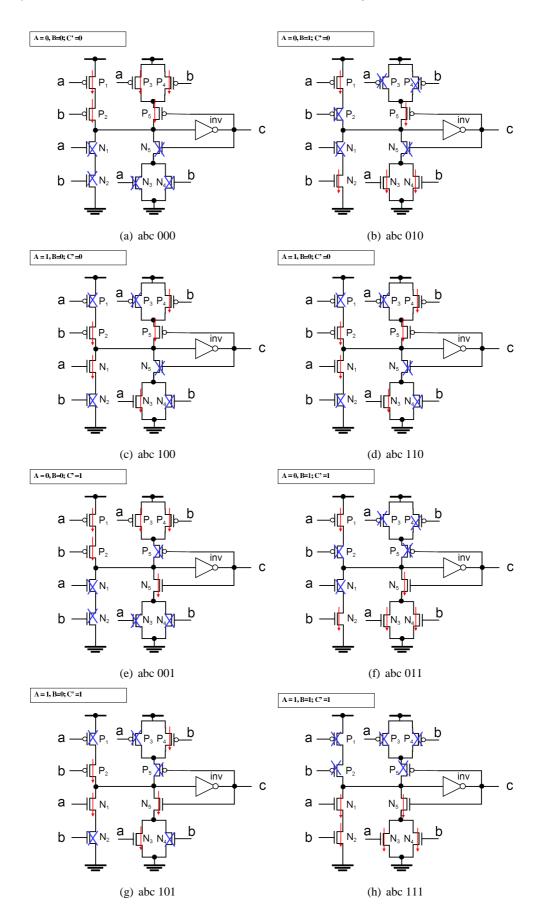

| 9.5  | C-element Design                                                                |

| 9.6  | Transistor P3 Stuck-on fault in the C-element                                   |

| 9.7  | Test Methodology                                                                |

| 9.8  | Test Generation Example                                                         |

| 9.9  | Fault Injection                                                                 |

| 9.10 | Optional caption for list of figures                                            |

| 9.11 | Optional caption for list of figures 1                                          |

## **List of Tables**

| 4.1  | Fault Coverage using Symbolic Method                                            |

|------|---------------------------------------------------------------------------------|

| 4.2  | Fault Coverage for Scan Insertion based method                                  |

| 5.1  | Fault Classes in Tetramax                                                       |

| 5.2  | Fault Sites and Detection Results                                               |

| 5.3  | Fault Coverage                                                                  |

| 5.4  | Result – Fault Coverage Comparison                                              |

| 5.5  | Scan Area Overhead                                                              |

| 5.6  | Number of Patterns                                                              |

| 5.7  | Fault Class Distribution                                                        |

| 5.8  | Undetectable Fault Locations                                                    |

| 5.9  | Fault Coverage Comparison of proposed method using 1 to 8 copies of forward     |

|      | path during acyclic conversion                                                  |

| 5.10 | Comparision of Number of patterns generated for the circuits with 1 to 8 copies |

|      | of forward path during acyclic conversion                                       |

| 6.1  | Fault Coverage Comparison                                                       |

| 6.2  | Comparison of Number of Patterns                                                |

| 6.3  | Area Overhead - expressed as percentage of extra scan elements                  |

| 7.1  | ASCP Versus Full Scan - Fault Coverage Comparison                               |

| 7.2  | Comparison of Number of Patterns                                                |

| 8.1  | Circuit Extraction Results                                                      |

| 9.1  | MOS Gate Output Table[JA85]                                                     |

| 9.2  | Truth Table for $Good(G)$ and $Faulty(F)$ machine                               |

| 9.3  | Transistor Level Circuit Characteristics                                        |

| 9.4  | ATRANTE Test Generator Results                                                  |

| 9.5  | Fault Coverage Results from Fault Simulator                                     |

## **Chapter 1**

## Introduction

#### 1.1 Introduction

Synchronous circuit design has been considered the standard for industrial practice due to the availability of advanced CAD tools and testing strategies. At deep sub micron levels, global clock synchronization, power consumption and noise factors are affecting the design performance, as a result asynchronous circuit design is gaining its momentum currently over its synchronous counterpart. On the other hand, asynchronous circuits need thorough research on CAD tool development for the whole design flow with test generation [BE00]Asynchronous designs are classified into speed independent, delay insensitive, and quasi delay insensitive circuits. Thus it has different models and architectures to be designed with and each of them has its own circuit models and delay assumptions. Significant efforts have been taken to develop CAD tools for synthesis of asynchronous circuits which lead to several tools like Petrify [CKK+96b], Tangram[KP01], Balsa [BE00] etc.,. Currently, very few tools (commercial tool from [Han]) are available for test generation for asynchronous circuits. Testing is essential for the designed systems, as the fabrication and component aging will cause defects in the circuits.

#### 1.1.1 Past work

Several attempts to generate tests for asynchronous circuits have been made in the recent years. Some of the methods involved test generation based on the STG (State Transition Graph) specification of the design. The test methods were introduced mostly by traversing through states of the state transition graph of the circuit. Some attempts have been made to generate test patterns for these circuits at the gate level. Also the test generation was specifically based on DFT methods, which makes the test generation methods dependent on the design methodology of the circuits. Several methods for generating acyclic circuit(circuits without feedback) from cyclic circuits.

cuits(circuits with feedback) have been introduced lately [Edw03],[Mal93],[Wei72],[Niv04]. But the methods are restricted for the cyclic circuit without state holding elements and which does not oscillate. But oscillations are predominant in asynchronous cyclic circuits and also presence of state holding elements like c-elements are common in them. Full scan based test generation for the circuits have been proposed in [Bee03]. Partial scan based method for selftimed circuit was proposed in [KB95]. The work in [BCR96] introduces a synchronous test generation to generate test for asynchronous circuits. A STG(State Transition Graph) based approach of test pattern generation was carried out in [RCPP97]. Test pattern generated were applied synchronously to test the target asynchronous circuits. A test generation method for testing redundant circuits in asynchronous designs was introduced in [LKL94] which used a method called "Variable Phase Splitting" to generate test patterns for these NCL circuits which is acyclic. A partial scan based delay fault testing of asynchronous circuit was acclaimed in [KKL<sup>+</sup>98]. An algorithm similar to the proposed algorithm on this paper was used to test path delay faults. The work in [KSS02] introduced a test method for a subclass of asynchronous circuits called NCL(Null Convention Logic). This method is also based on partial scan test generation by breaking feedback loops. A partial scan test generation method for asynchronous SOC interconnect was presented in [ABE05]. The method focused on generating test for asynchronous interconnect named CHAIN. In [Ron94], a partial scan test generation method for DCC error corrector was provided. A fault simulator called FSIM was used for fault simulation. Micropipelines form the vital components in AMULET processor design and Scan testing for these micropipelines was introduced in [PF95b]. Lately a systematic scan insertion technique was introduced to test Asynchronous interconnects [SO08]. Also a recent work on automating test generation for asynchronous NCL circuits was published in [WA08]. This method promises near 100% test coverage for most of the NCL libraries used to design the NCL circuits. A detailed literature review on related works is given in chapter 3.

#### 1.1.2 Motivation

Most commonly used testing methods for testing digital circuits are structural and functional testing. Both these methods have its own pros and cons.

#### Structural Vs Functional