# A Generic Low Power Reconfigurable Distributed Arithmetic Processor

Liu Zhenyu

A thesis submitted for the degree of Doctor of Philosophy.

The University of Edinburgh.

May 2008

To my wife Ni Yuanyuan and my parents Liu Ziheng, Piao Xueqin

For their love, affection and support.

### Abstract

Higher performance, lower cost, increasingly minimizing integrated circuit components, and higher packaging density of chips are ongoing goals of the microelectronic and computer industry. As these goals are being achieved, however, power consumption and flexibility are increasingly becoming bottlenecks that need to be addressed with the new technology in Very Large-Scale Integrated (VLSI) design.

For modern systems, more energy is required to support the powerful computational capability which accords with the increasing requirements, and these requirements cause the change of standards not only in audio and video broadcasting but also in communication such as wireless connection and network protocols. Powerful flexibility and low consumption are repellent, but their combination in one system is the ultimate goal of designers.

A generic domain-specific low-power reconfigurable processor for the distributed arithmetic algorithm is presented in this dissertation. This domain reconfigurable processor features high efficiency in terms of area, power and delay, which approaches the performance of an ASIC design, while retaining the flexibility of programmable platforms. The architecture not only supports typical distributed arithmetic algorithms which can be found in most still picture compression standards and video conferencing standards, but also offers implementation ability for other distributed arithmetic algorithms found in digital signal processing, telecommunication protocols and automatic control.

In this processor, a simple reconfigurable low power control unit is implemented with good performance in area, power and timing. The generic characteristic of the architecture makes it applicable for any small and medium size finite state machines which can be used as control units to implement complex system behaviour and can be found in almost all engineering disciplines. Furthermore, to map target applications efficiently onto the proposed architecture, a new algorithm is introduced for searching for the best common sharing terms set and it keeps the area and power consumption of the implementation at low level. The software implementation of this algorithm is presented, which can be used not only for the proposed architecture in this dissertation but also for all the implementations with adder-based distributed arithmetic algorithms. In addition, some low power design techniques are applied in the architecture, such as unsymmetrical design style including unsymmetrical interconnection arranging, unsymmetrical PTBs selection and unsymmetrical mapping basic computing units. All these design techniques achieve

### Abstract

extraordinary power consumption saving. It is believed that they can be extended to more low power designs and architectures.

The processor presented in this dissertation can be used to implement complex, high performance distributed arithmetic algorithms for communication and image processing applications with low cost in area and power compared with the traditional methods.

# Declaration of originality

| I hereby declare that the research recorded in this thesis and the thesis itself was composed |

|-----------------------------------------------------------------------------------------------|

| and originated entirely by myself in the School of Engineering and Electronics at The         |

| University of Edinburgh, except when otherwise stated.                                        |

|                                                                                               |

|                                                                                               |

|                                                                                               |

|                                                                                               |

|                                                                                               |

|                                                                                               |

|                                                                                               |

|                                                                                               |

| Zhenyu Liu                                                                                    |

|                                                                                               |

### Acknowledgments

My foremost thank goes to my supervisor, Prof. Tughrul Arslan, for giving me a big chance to go to the door of top level research which leads me to the success of the work in this dissertation. His valuable comments were instrumental in shaping the direction of the research. Prof. Tughrul Arslan built a harmonious academic environment in which I could discuss and exchange ideas with members in the lab friendly. I thank him also for leaving enough academic space for me to cultivate the ability to carry out research independently, which leads me to success.

This work was supported in part by the David Mayes Scholarship. I wish my successful work can be a solid prove for the rightness of setting up this scholarship, which is also the best gift to Dr Davis Mayes.

It was a valuable experience to work in System-Level Integration group. Many thanks go to Dr. Ahmet T. Erdogan for being so patient and helping in sharing with me technical knowledge whenever I needed help. His help and support contributed greatly to my work and publications, which is deeply appreciated. I sincerely thank all of the current and former members of the group for their precious time, helpful advice and friendship over the last four years. Here, I would like to mention just a few in particular: Sami Khawam, Yi Ying, Erfu Yang, Han Wei, Ming-Lang Lin, Zhan Cheng, Mark Muir, Yutian Zhao, Jichuan Zhao. Specially, I would like to thank Miss Yuanyuan Ni and Prof. Lili Wang for their suggestions and help in editing this manuscript.

A big thank also goes to Miss Ning Wei for her company during my time in Edinburgh. I thank her for her caring, patience and encouragement that made my tough life easier and carried me on through the difficult times. Her support and understanding is greatly appreciated.

Lastly, and most importantly, I would like to express my deepest gratitude to my parents for their forever love, unconditional sacrifices, endless encouragement and continual support (financial and moral) throughout my academic years. They are always my loyal, ultimate and strong backing which carried me forward and I'm forever in debt to them.

I would express my sincere gratitude to all of you again. This dissertation is only made possible with the love and support from the various people in my life,

# Table of Contents

| Chapter I   | Introduction                                                     | 1  |

|-------------|------------------------------------------------------------------|----|

| I.1 Intr    | oduction                                                         | 1  |

| I.2 Sig     | nificance of This Work                                           | 3  |

| I.3 Org     | ganisation of the Thesis                                         | 4  |

| Chapter II  | Review of Reconfigurable and Low-power Architecture              | 7  |

| II.1 Ove    | erview                                                           | 7  |

| П.1.1       | Reconfigurable Architecture                                      | 8  |

| II.1.2      | FPGA devices                                                     | 9  |

| II.1.3      | Domain-specific Processor                                        | 10 |

| II.2 FPC    | GA Architecture                                                  | 11 |

| II.2.1      | Fine-grain FPGA Architecture                                     | 11 |

| II.2.2      | Problems with Fine-grain FPGA Architecture                       | 13 |

| II.3 Fin    | e-grain Architecture                                             | 14 |

| II.4.1      | National Semiconductor's Adaptive Processing Architecture (NAPA) | 15 |

| II.4.2      | Garp: Gate Array Processor                                       | 16 |

| II.4.3      | Chimaera Architecture                                            | 17 |

| II.4 Coa    | nrse-grain Architecture                                          | 18 |

| II.4.1      | Pleiades Architecture                                            | 18 |

| II.4.2      | RaPiD: Reconfigurable Pipelined Datapath                         | 20 |

| II.4.3      | MorphoSys                                                        | 21 |

| II.4.4      | Chameleon                                                        | 22 |

| II.4.5      | RAP                                                              | 23 |

| II.3 Inte   | erconnection Structure                                           | 25 |

| II.4.1.     | Symmetrical Interconnection Network                              | 25 |

| II.4.2.     | Hierarchical Interconnection Network                             | 26 |

| II.4.3.     | Binary (Fat) Interconnection Tree                                | 27 |

| II.4 Lov    | w Power Technology                                               | 28 |

| II.5 Co     | nclusion                                                         | 30 |

| Chapter III | Review of Distributed Arithmetic Algorithm and its Applications  | 31 |

| III.1 Overview                                          | 31 |

|---------------------------------------------------------|----|

| III.2 Distributed Arithmetic Algorithm                  | 32 |

| III.2.1. DA Algorithms                                  | 32 |

| III.2.2. ROM Based DA                                   | 33 |

| III.2.3. Adder-Based DA                                 | 34 |

| III.3 Distributed Arithmetic Implements                 | 35 |

| III.3.1 Architecture for Distributed Arithmetic         | 36 |

| III.3.2 Memory Reduced DA Architecture                  | 37 |

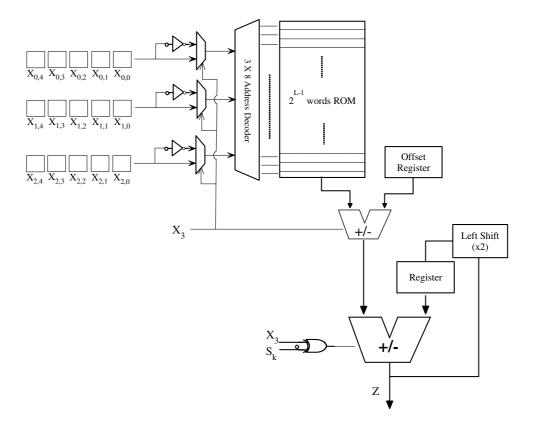

| III.3.3 Offset Binary Coding Architecture               | 43 |

| III.3.4 Parallel DA Architecture                        | 47 |

| III.4 Applications of Distributed Arithmetic            | 49 |

| III.5 Conclusion                                        | 50 |

| Chapter IV Low Power Reconfigurable Architecture for DA | 51 |

| IV.1 Overview                                           | 51 |

| IV.2 Related Work                                       | 52 |

| IV.3 Reconfigurable DA Architecture                     | 54 |

| IV.4 Architecture of Algorithm Logic Unit               | 57 |

| IV.4.1. Algorithm of Proposed Architecture              | 58 |

| IV.4.2. Two-level Adder Structure                       | 59 |

| IV.4.3. Wallace tree multiplier Matrix                  | 60 |

| IV.4.4. Interconnection Network                         | 61 |

| IV.4.5. Memory for Reconfigure Bits                     | 68 |

| IV.4.6. Architecture Implementation:                    | 71 |

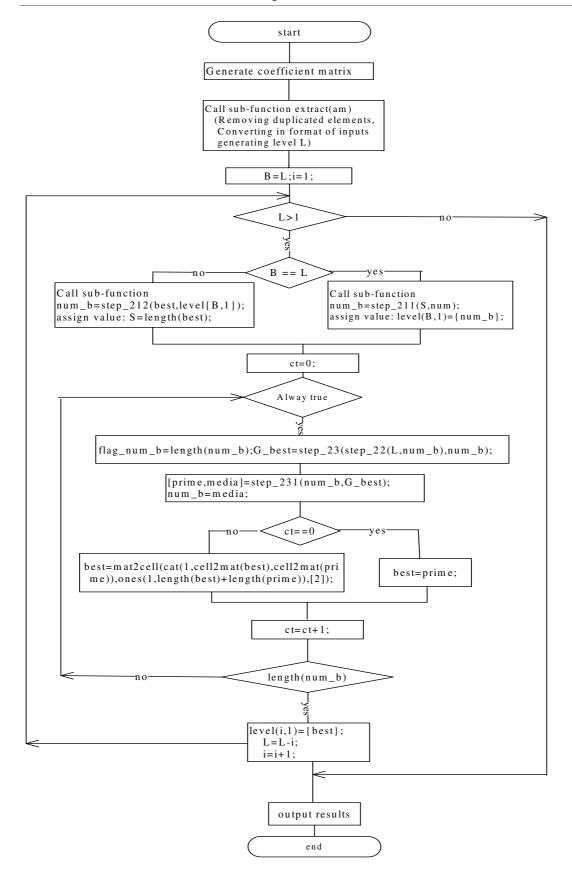

| IV.5 Algorithm Searching for Optimal Scheme             | 72 |

| IV.5.1. Common Term Sharing Availability Analysis       | 73 |

| IV.5.2. Dimidiate Tree                                  | 75 |

| IV.5.3. Crossing Forest and Targeted Problem            | 77 |

| IV.5.4. Algorithm Searching for Best Set                | 78 |

| IV.5.5. Software Implementation                         | 81 |

| IV.6 Co   | mparison with Subexpression Sharing in CSD                                 | .85 |

|-----------|----------------------------------------------------------------------------|-----|

| IV.7 Co   | nclusion                                                                   | .87 |

| Chapter V | Reconfigurable Control Unit                                                | .89 |

| V.1. Ov   | erview                                                                     | .89 |

| V.2. Ba   | ckground                                                                   | .92 |

| V. 2.     | 1. Definition of FSM                                                       | .92 |

| V. 2. 2   | 2. Three Categories of FSM                                                 | .93 |

| V. 2. 3   | 3. State Transition Graph and State Transition Table Representation of FSM | .94 |

| V. 2.     | 4. Decomposition of FSM                                                    | .95 |

| V.3. Im   | plementation of FSMs                                                       | .97 |

| V.3.1.    | Extraction of FSM Implement FSM with Hardware Platforms                    | .99 |

| V.3.2.    | FSM Operation on Reconfigurable Device                                     | 100 |

| V.3.3.    | Reconfigurable Hardware Platform for FSMs Implementation                   | 101 |

| V.4. Ex   | isting FSM Hardware Implementation Architectures                           | 102 |

| V.4.1.    | PLD Hardware Platform for FSMs Implementation                              | 102 |

| V.4.2.    | CPLD Hardware Platform and Xilinx CoolRunner XPLA3 CPLD                    | 103 |

| V.4.3.    | Limitation of CPLD.                                                        | 104 |

| V.4.4.    | Existing Customer-specific Reconfigurable Architecture                     | 105 |

| V.5. Re   | configurable FSM Architectures                                             | 106 |

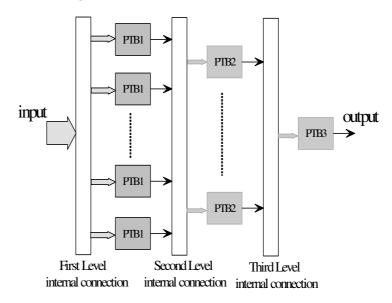

| V.5.1     | Reconfigurable FSM Architecture Overview                                   | 106 |

| V.5.2     | Functional Sections in the Architecture                                    | 107 |

| V.5.3     | Architecture of Logic Block and Sequential Block                           | 108 |

| V.5.4     | Construction of PTB                                                        | 108 |

| V.6. Lo   | w Power Implementation                                                     | 109 |

| V.6.1     | A typical Interconnection Network                                          | 109 |

| V.6.2     | Interconnection Network                                                    | 110 |

| V.6.3     | Function of PTB                                                            | 112 |

| V.6.4     | Mapping of PTB                                                             | 112 |

| V.7. Ex   | perimental Results and Evaluation                                          | 113 |

| V.7.1       | Experimental Platform                                 | 114 |

|-------------|-------------------------------------------------------|-----|

| V.7.2       | Experimental Data Pre-process                         | 115 |

| V.7.3       | Power consumption Comparison                          | 120 |

| V.7.4       | Area & Delay Comparison                               | 122 |

| V.7.5       | Power Consumption, Area and Delay after Decomposition | 127 |

| V.7.6       | Relationship between Power, Area and Delay            | 127 |

| V.8. Cor    | nclusion                                              | 128 |

| Chapter VI  | Implementation of DA Application                      | 130 |

| VI.1. D     | CT Implementation                                     | 130 |

| VI.1.1      | . DCT Algorithm                                       | 131 |

| VI.1.2      | . 2-D DCT and its Implementations                     | 132 |

| VI.1.3      | . Control Path Implementation                         | 133 |

| VI.1.4      | . Registers Matrix Implementation                     | 135 |

| VI.1.5      | . Algorithm Logic Unit Implementation                 | 135 |

| VI.1.6      | . Performance & Evaluation                            | 142 |

| VI.1.7      | . Summary                                             | 147 |

| VI.2. D     | FT Implementation                                     | 147 |

| VI.2.1      | . DFT Algorithm                                       | 149 |

| VI.2.2      | . FFT Algorithm                                       | 150 |

| VI.2.3      | . Overview of FFT Implementation                      | 154 |

| VI.2.4      | . Algorithm logic Unit Implementation                 | 155 |

| VI.2.5      | . Performance & Evaluation                            | 158 |

| VI.3. C     | onclusion                                             | 159 |

| Chapter VII | I Conclusion and Future Work                          | 161 |

| VII.1. C    | onclusion                                             | 161 |

| VII.2. E    | valuation of Results and Contributions                | 162 |

| VII.2.      | 1.Novel and Efficient Points of the Work              | 162 |

| VII.2.2     | 2.Limitations                                         | 163 |

| VII.3. Fu   | uture Work                                            | 164 |

# List of Figures

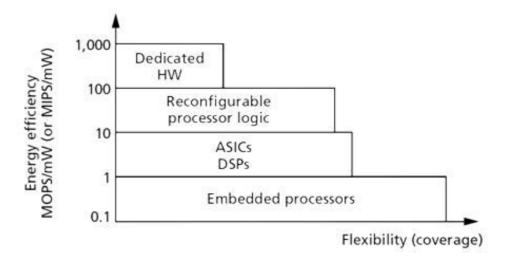

| Figure I-1: Flexibility versus energy trade-off in implementation [1]                | 2  |

|--------------------------------------------------------------------------------------|----|

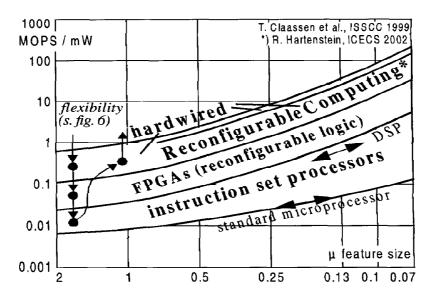

| Figure I-2: Energy efficiency vs. flexibility including reconfigurable computing [2] | 3  |

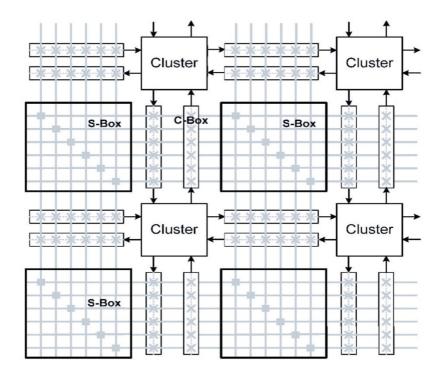

| Figure II-1 : Architecture of FPGA                                                   | 12 |

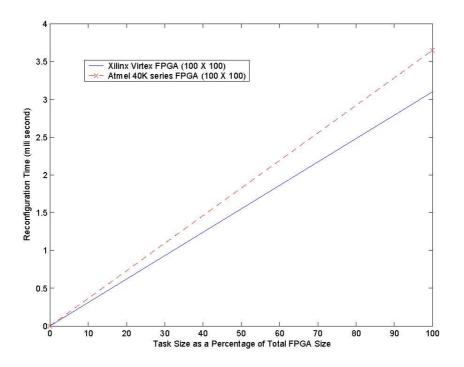

| Figure II-2: Reconfiguration time of two FPGA devices                                | 13 |

| Figure II-3: NAPA processor structure [20]                                           | 15 |

| Figure II-4 : Garp block diagram [23]                                                | 16 |

| Figure II-5 : Overall Chimaera architecture [6]                                      | 17 |

| Figure II-6: Overall Pleiades architecture [9]                                       | 19 |

| Figure II-7: Abstract view of the Rapid architecture [34]                            | 20 |

| Figure II-8 : The MorphoSys Architecture [38]                                        | 22 |

| Figure II-9: The logic in D-Fabrix ALU and Switchbox pair [52]                       | 24 |

| Figure II-10 : An example of generalized hierarchical interconnection                | 27 |

| Figure II-11: A fat binary tree                                                      | 28 |

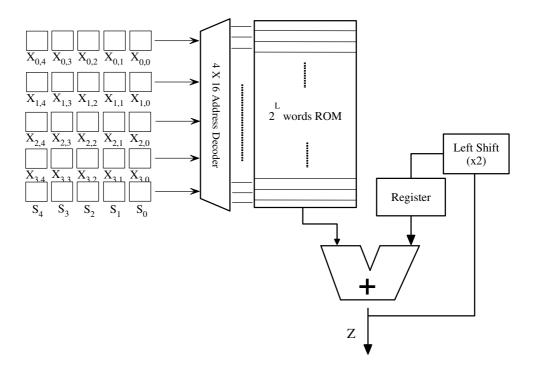

| Figure III-1 : General architecture for DA                                           | 36 |

| Figure III-2 : Memory reduced DA architecture I                                      | 39 |

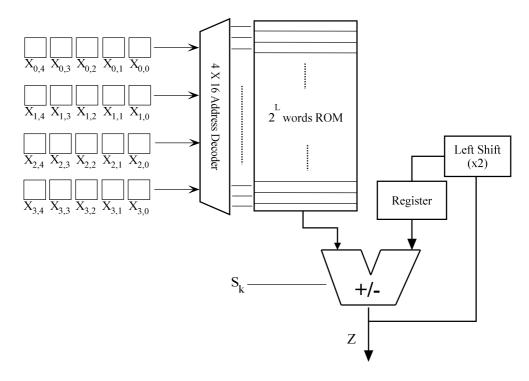

| Figure III-3 : Memory reduced DA architecture II                                     | 46 |

| Figure III-4: A typical parallel DA architecture                                     | 48 |

| Figure IV-1 : Reconfigurable DA architecture                                         | 54 |

| Figure IV-2 : Architecture of address coding                                         | 55 |

| Figure IV-3 : The architecture of algorithm logic unit                               | 57 |

| Figure IV-4 : Example of adder-based DA                                              | 59 |

| Figure IV-5: Adder followed by 2-input multiplexer                                   | 60 |

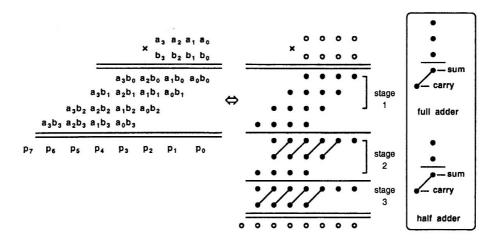

| Figure IV-6: Operation of the Wallace tree multiplier [74]                           | 61 |

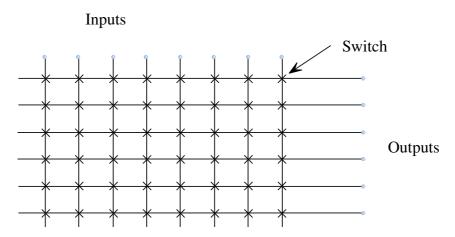

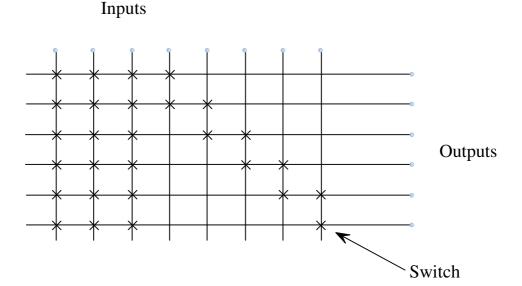

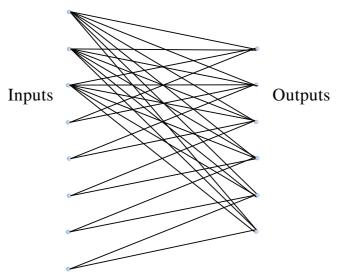

| Figure IV-7: An 8x6 full crossbar                                                    | 62 |

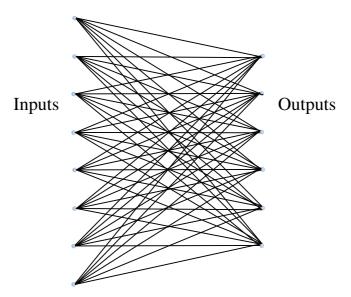

| Figure IV-8: 2-sided switch block                                                    | 63 |

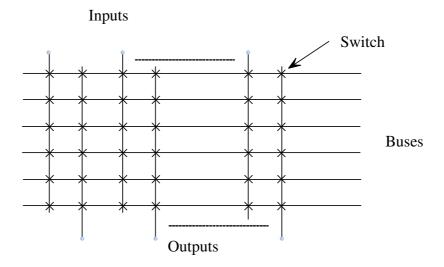

| Figure IV-9 : Multiple-bus interconnection                                           | 64 |

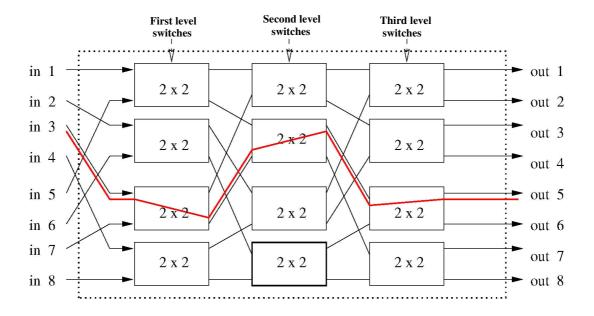

| Figure IV-10: An omega network [78]                                                  | 65 |

| Figure IV-11 : A partial 8x6 crossbar                                    | 67  |

|--------------------------------------------------------------------------|-----|

| Figure IV-12 : A 2-sided switch block for partial crossbar               | 68  |

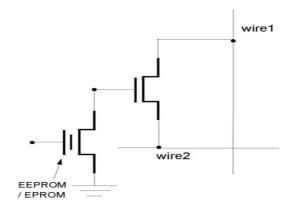

| Figure IV-13: EEPROM/EPROM programmable switch                           | 69  |

| Figure IV-14: A simple 6-transistor SRAM cell                            | 69  |

| Figure IV-15: SRAM switch based full crossbar                            | 70  |

| Figure IV-16: SRAM programmable switch application                       | 70  |

| Figure IV-17 : Examples of dimidiate tree                                | 75  |

| Figure IV-18 : Different format for the same dimidiate tree              | 76  |

| Figure IV-19: Example of crossing forest                                 | 78  |

| Figure IV-20: Coefficient (P <sub>h,k</sub> ) matrix                     | 80  |

| Figure IV-21 : Design flow chart                                         | 83  |

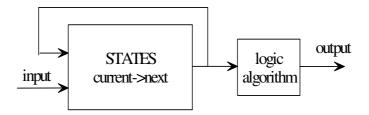

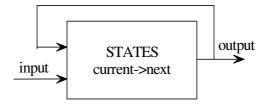

| Figure V-1: Mealy machine                                                | 93  |

| Figure V-2: Moore machine                                                | 93  |

| Figure V-3: FSM with internal states as outputs                          | 93  |

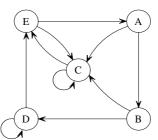

| Figure V-4: State transition graph for two-bit counter                   | 92  |

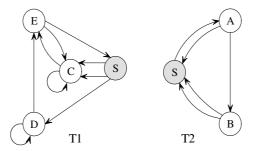

| Figure V-5: Generic FSM decomposition                                    | 96  |

| Figure V-6: State transition graph of an example FSM                     | 96  |

| Figure V-7: State transition graph after decomposition                   | 96  |

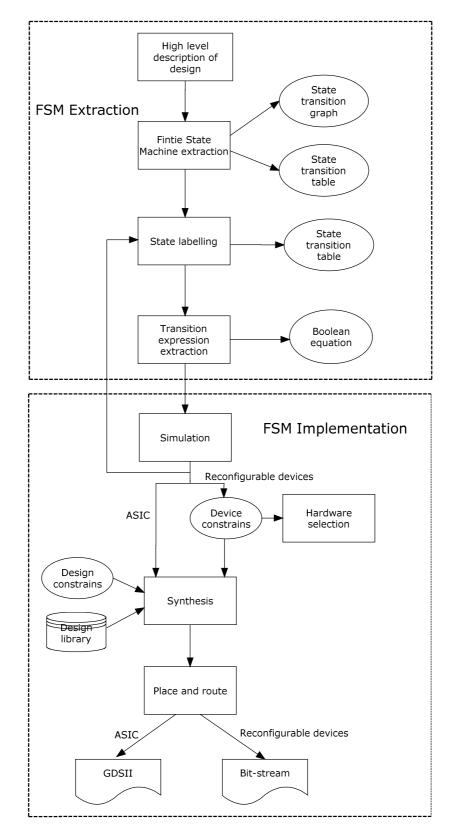

| Figure V-8: FSM design flow                                              | 98  |

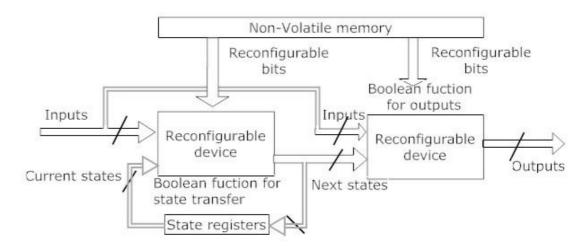

| Figure V-9: General reconfigurable hardware implementation of FSMs       | 99  |

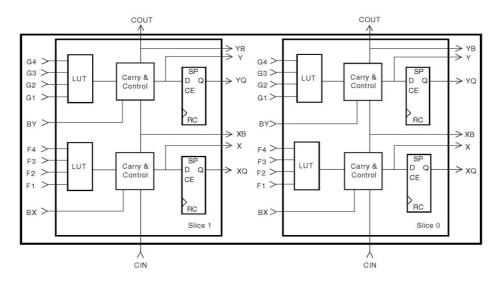

| Figure V-10: CLB of Xilinx Virtex-E FPGA [10]                            | 100 |

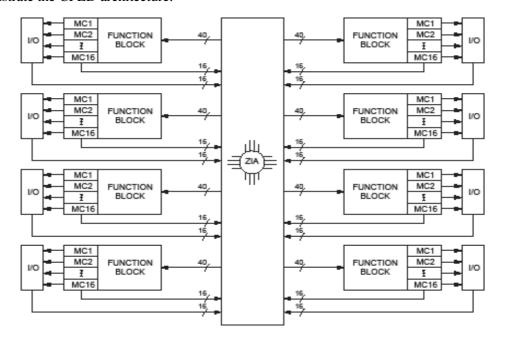

| Figure V-11: Xilinx XPLA3 CPLD architecture [101]                        | 103 |

| Figure V-12 : The architecture of a reconfigurable FSM                   | 106 |

| Figure V-13 : The architecture of a logic block                          | 108 |

| Figure V-14: A typical FPGA interconnection network                      | 110 |

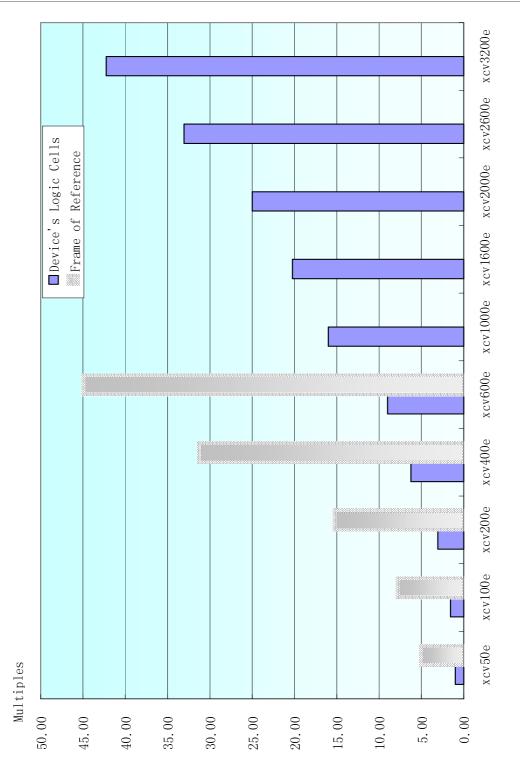

| Figure V-15: The illustration of comparison in size between FPGA devices | 118 |

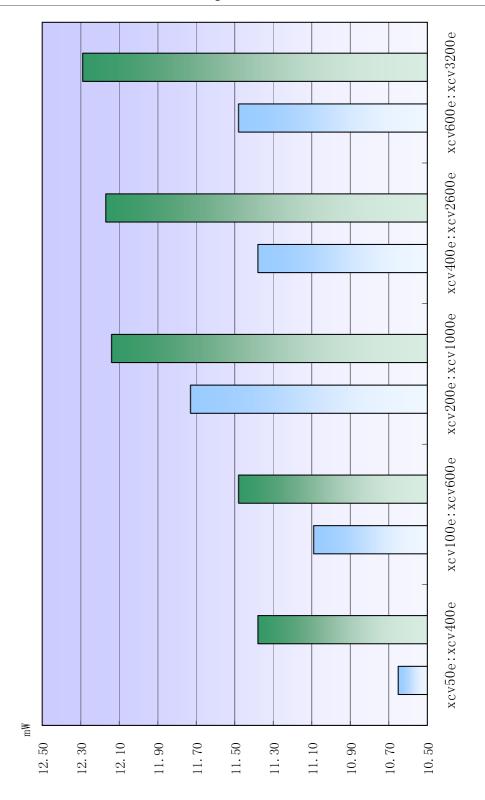

| Figure V-16: The power consumption comparison of FPGA device pairs       | 119 |

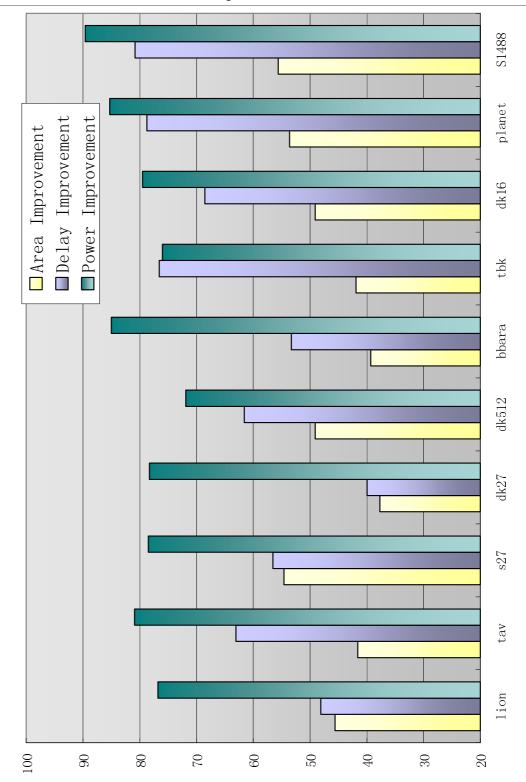

| Figure V-17 : The improvements compared with the FPGA device             | 124 |

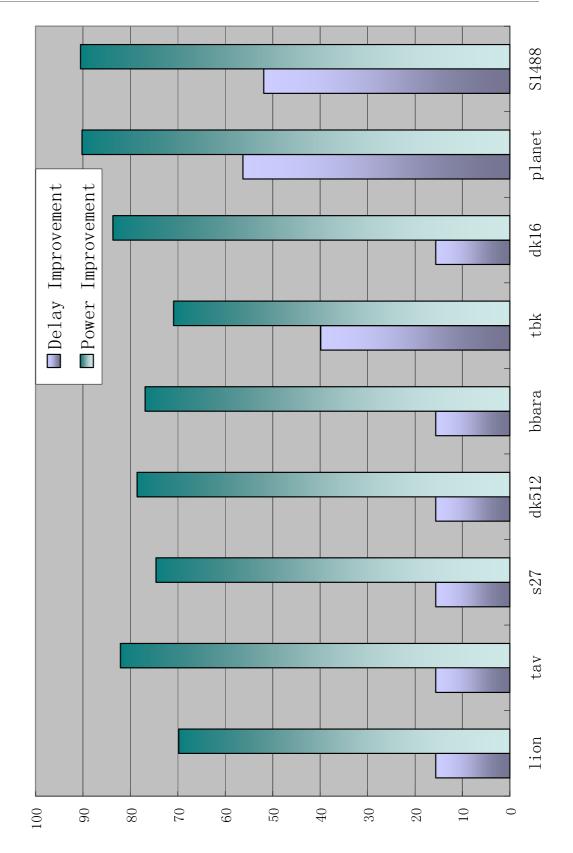

| Figure V-18: The improvements compared with the CPLD device              | 126 |

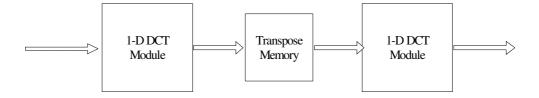

| Figure VI-1 : A general row-column 2-D DCT implementation                      | 133 |

|--------------------------------------------------------------------------------|-----|

| Figure VI-2 : Registers matrix                                                 | 134 |

| Figure VI-3 : $F_k(i)$ in 2's complement format                                | 136 |

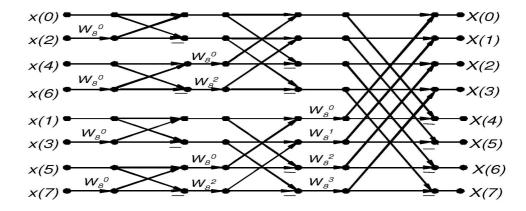

| Figure VI-4 : Data flow graph of an 8-point radix-2 decimation-in-time FFT     | 151 |

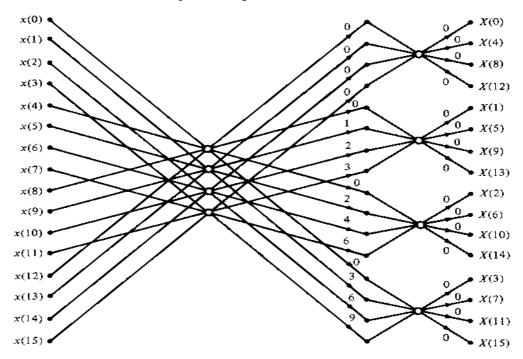

| Figure VI-5 : Data flow graph of 16-point, radix-4 decimation-in-frequency FFT | 153 |

| Figure VI-6 : Twiddle factors of 4-point FFT                                   | 157 |

# List of Tables

| Table III-1: The content in the ROM of original DA architecture    | 8 |

|--------------------------------------------------------------------|---|

| Table III-2: The content in the memory reduced DA architecture II  | 0 |

| Table III-3: Transform between Table III-1 and Table III-2         | 1 |

| Table III-4: The content in the ROM of reduced DA architecture III | 2 |

| Table III-5: Transform between Table III-2 and Table III-4         | 2 |

| Table III-6: Expansion of Equation (III-25) fo • r the case        | 5 |

| Table IV-1: Availability analysis of common term sharing           | 4 |

| Table V-1: State transition Table of the case 9:                   | 5 |

| Table V-2: Test cases and their characterizations                  | 4 |

| Table V-3: Selected FPGA devices                                   | 6 |

| Table V-4: Experimental results for power consumption              | 0 |

| Table V-5: Normalized power consumption of FPGA and CPLD           | 1 |

| Table V-6: Experimental results for area and delay                 | 2 |

| Table V-7: Normalized area and delay of FPGA and CPLD              | 3 |

| Table VI-1 : Eight coefficient matrixes in format of input vectors | 7 |

| Table VI-2 : Unique terms of DCT                                   | 8 |

| Table VI-3: R'h sets for DCT                                       | 9 |

| Table VI-4 : First $P_{h,k}$ coefficient matrix for DCT            | 0 |

| Table VI-5 : Second $P_{h,k}$ coefficient matrix for DCT           | 1 |

| Table VI-6: Performances of some existing designs and ours         | 6 |

| Table VI-7: Workload for a 4096 point FFT using different radices  | 2 |

| Table VI-8: Mixed-radix algorithms for different FFT sizes         | 4 |

### Glossary / Acronyms

ALP Adaptive Logic Processor

**ALU** Arithmetic Logic Unit

**AVC** Advanced Video Coding

**ASIC** Application Specific Integrated Circuit

**BRASS** Berkeley Reconfigurable Architecture System and Software

**CAVLC** Context Adaptive Variable Length Coding

**C-Box** Connection Boxes

**CDMA** Code Division Multiple Access

CIO Configurable I/O

**CLB** Configurable Logic Block

**CMOS** Complementary metal–oxide–semiconductor

**CORDIC** COordinate Rotation DIgital Computer

**CPLD** Complex Programmable Logic Device

**CPU** Central Processing Unit

**CSD** Canonic Signed-Digit

**DA** Distributed Arithmetic

**DCT** Discrete Cosine Transform

**DFT** Discrete Fourier Transform

**DES** Data Encryption Standard

**DHT** Discrete Hartley Transform

**DIF** Decimation-In-Frequency

**DIT** Decimation-In-Time

**DoSP** Domain Specific Processor

**DMA** Direct Memory Access

**DPU** Data Path Unit

**DSP** Digital Signal Processor

**DVB-H** Digital Video Broadcasting – Handheld

**DVB-T/DAB** Digital Video/Audio Broadcasting

**DWT** Discrete Wavelet Transform

**EDA** Electronic Design Automation

**EEPROM** Electrically Erasable Programmable Read-only Memory

**EPROM** Erasable Programmable Read-only Memory

**FFT** Fast Fourier Transform

**FIFO** First In, First Out

**FIP** Fixed Instruction Processor

**FIR** Finite Impulse Response

**FPGA** Field Programmable Gate Arrays

**FSM** Finite State Machine

**GPP** General Purpose Processor

**GPU** Graphics Processing Units

**GRM** General Routing Matrix

**GSM** Global System for Mobile communications

**HDL** Hardware Description Language

JPEG Joint Photographic Experts Group

**IDCT** Inverse Discrete Cosine Transform

**IOB** Input/output block

LAN Local Area Network

**LUT** Look-Up-Tables

LSB Least Significant Bit

MAC Multiply and Accumulate

MCD MultiCarrier Demultiplexing

MIMO Multiple-Input Multiple-Output

MIPS Microprocessor without Interlocked Pipeline Stages

MP3 MPEG-1 Audio Layer 3

MPEG-4 Moving Picture Experts Group standard 4

MSB Most Significant Bit

NAPA National Semiconductor's Adaptive Processing Architecture

NRE NonRecurring Engineering

**OBC** Offset Binary Coding

**OFDM** Orthogonal Frequency Division Multiplex

VLSI Very Large-Scale Integrated

PAL Programmable Array Logic

**PE** Processing Element

**PDA** Personal Digital Assistant

**PGA** Programmable Gate Array

PLA Programmable Logic Array

**PLD** Programmable Logic Device

**PMA** Pipeline Memory Array

**PTB** Product-Term Block

**QoS** Quality of Service

**RAM** Random Access Memory

**RAP** Reconfigurable Algorithm Processor

**RaPiD** Reconfigurable Pipelined Datapath

**RISC** Reduced Instruction Set Computer

**ROM** Read Only Memory

**RPC** Reconfigurable Pipeline Controller

**RTL** Register Transfer Level

**S-Box** Switch Boxes

**SDA** Serial Distributed Arithmetic

**SIMD** Single Instruction, Multiple Data

**SP** Simple Profile

**SoC** System-on-Chip

**SRAM** Static Random Access Memory

SMA Scratchpad Memory Array

STG State Transition Graph

**STT** State Transition Table

**TBT** Toggle Bus Transceiver

**TD-SCDMA** Time Division-Synchronous Code Division Multiple Access

VCEG Video Coding Experts Group

VHDL Verilog hardware description language

VLSI Very Large-Scale Integrated

**VLIW** Very-Long Instruction-Word

WCDMA Wideband Code Division Multiple Access

**WFTA** Winograd Fourier Transform Algorithm

WLAN Wireless Local Area Network

**XPC** External Memory Controller

**XPLA** eXtended Programmable Logic Array

**ZIA** Zero-power Interconnect Array

# Chapter I

### Introduction

### I.1 Introduction

Higher performance, lower cost, increasingly minimizing integrated circuit components, and higher packaging density of chips are ongoing goals of the microelectronic and computer industry. As these goals are being achieved, however, power consumption and flexibility are increasingly becoming bottlenecks that need to be addressed with the new technology in Very Large-Scale Integrated (VLSI) design.

Both powerful computing ability and long running time are the key features of the handheld and portable devices such as wireless communication terminals, personal digital assistants (PDAs), laptops, etc. The outstanding system performance requires more energy to support powerful computational capability. However, high power consumption directly shortens the running time of portable devices which, in a sense, directly determines the future of devices in the market. Therefore, the success of low-power techniques not only implies battery life in mobile system will be extended, but also reliability in high-performance systems will be improved.

The powerful processing ability of modern system accords with the increasing requirements which cause the change of standards not only in audio and video broadcasting but also in communication such as wireless connection and network protocols. The frequent updates in media and communication standards raise higher requirements in flexibility to support changes. Generally speaking, the more complex the system is, the more power is consumed. Powerful flexibility and low consumption are repellent, but their combination in one system is the ultimate goal of designers.

Programmable solutions such as Field Programmable Gate Arrays (FPGA) devices have become more popular among the applications in multimedia and communication because of their low design cost and fast time-to-market. However, compared with Application Specific Integrated Circuit (ASIC) solutions, there is a large power and delay overhead for these programmable solutions.

Despite the common notion of FPGA's large power consumption, Jan Rabaey has shown in [1] that, for certain type of digital signal processing applications, the energy efficiency of FPGAs is orders of magnitude better than that of general purpose processors. This observation is shown in Figure I-1. Although ASICs or hardwired solutions provide the best energy-efficiency, their longer design cycles make the time-to-market unacceptable for a business company besides their high design costs.

Figure I-1: Flexibility versus energy trade-off in implementation [1]

Reconfigurable System-on-Chip (SoC) technology emerged to meet the simultaneous demands for flexibility and efficiency. Compared with general SoC, one or more programmable arrays are embedded in the reconfigurable system. The reconfigurable arrays can be programmed to adapt to different applications so that the efficiency of the hardware and the flexibility of the whole system are improved. A typical reconfigurable SoC architecture consists of general purpose processor, memory, system bus, control modules and reconfigurable arrays which handle specific complex functions.

From the developing trends in reconfigurable logic and computing, it is found that the reconfigurable computing consumes higher power (roughly a factor of 10) when compared to ASICs. But compared with standard microprocessors the energy-efficiency is about two orders of magnitude better [2], as shown in Figure I-2. Therefore, introduction of reconfigurable architecture can lead to significant energy savings when compared with processor solutions only [2].

Figure I-2: Energy efficiency vs. flexibility including reconfigurable computing [2]

This thesis presents a hybrid solution between ASICs and general-purpose programmable platforms to fill up this gap. This solution is an application-specific reconfigurable processor targeting on distributed arithmetic algorithm, which approaches the performance of an ASIC design, while retaining the flexibility of programmable platforms.

### I.2 Significance of This Work

The contributions of this research are stated as follows, including five key aspects:

• A novel domain-specific reconfigurable architecture for the distributed arithmetic algorithm is demonstrated. The architecture not only supports the typical distributed arithmetic algorithm, discrete cosine transform, which can be found in most still picture compression standards and video conferencing standards, but also offers implementation ability for other distributed arithmetic algorithms such as discrete Fourier transform, finite impulse response, and discrete Hartley transform.

- To achieve the best hardware efficiency, the concepts of dimidiate tree and crossing forest are introduced. A new algorithm is accordingly developed for searching for the best common sharing terms set when the target application is implemented with the proposed architecture. The algorithm can find out the best set for implementation so as to achieve the most efficient consumption of area and power.

- The software implementation of the algorithm for searching for the best common sharing terms set is demonstrated, which can be used not only for the architecture presented in this dissertation but also for all the implementation of adder-based distributed arithmetic algorithm.

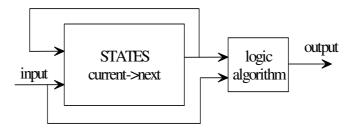

- A reconfigurable control unit is introduced, which is not only the key part of proposed architecture. The core part of it, reconfigurable finite state machine architecture, can be applied in any small and medium-sized finite state machines which are the control units to implement complex system behaviour and can be found in almost all engineering disciplines.

- Low power design techniques such as unsymmetrical interconnection arranging, unsymmetrical product-term blocks (PTBs) selection and unsymmetrical mapping basic computing units are presented in this dissertation, which can improve area and power efficiency significantly.

### I.3 Organisation of the Thesis

This section describes the organization of this dissertation by introducing main points of each chapter.

Chapter II presents reviews of literature related to this work including basic concepts of reconfigurable architecture, the classification of the architectures, a brief introduction to interconnection network applied in reconfigurable architecture and low power design technology. In addition, the implementations of fine-grain and coarse-grain architectures are described. Typical reconfigurable coarse-grain architectures are also presented and compared in detail.

Chapter III first introduces basic concept of distributed arithmetic algorithm and its definition. Two basic distributed arithmetic algorithms, Read Only Memory (ROM) based distributed arithmetic and adder based distributed arithmetic, are then addressed after the summarization of the distributed arithmetic concept development. Several serial and parallel architectures for distributed arithmetic are described. The advantages of these architectures and the problems facing them are also proposed in this chapter. At the end of this chapter, distributed arithmetic applications in signal processing and communication fields are described briefly.

A domain-specific low power reconfigurable distributed arithmetic architecture and its implementation are addressed in Chapter IV. The overview architecture is described first and then the descriptions of the algorithm logic unit are detailed. To achieve the best hardware efficiency, the concepts of dimidiate tree and crossing forest are introduced and defined in this chapter. An algorithm is accordingly developed and presented in the chapter as well, which makes the architecture mapped with the best efficiency.

The control unit of proposed processor will be described separately in Chapter V because if its complexity and unique function. Based on the analysis of traditional reconfigurable architecture given at the beginning of this chapter, a simplified one is presented with less flexibility, but high efficiency in terms of area, power and delay. In this chapter, the performance of the reconfigurable control unit architecture in area, power and delay of control unit will be evaluated and analyzed as well.

After the full description of the proposed processor in Chapter IV and V, the implementations of two typical distributed arithmetic applications, discrete cosine transform and discrete Fourier transform, are introduced in Chapter VI for functionality verification and performance evaluation. The implementations with the target architecture include the configurations of control path, register matrix and algorithm logic unit specified according to the requirements of the application. Additionally, the common term sharing scheme is demonstrated in this chapter by applying dimidiate tree and the algorithm to search for optimal scheme.

Finally, Chapter 7 concludes the thesis by discussing the contributions of the dissertation, limitations of the proposed architecture and directions for future research.

# Chapter II

# Review of Reconfigurable and Lowpower Architecture

### II.1 Overview

The traditional ASIC approach has become very expensive due to large design time and increasing photolithography cost. In addition, the relatively rapid changes in algorithms make an ASIC tend to execute partial reuse of the chip, which has resulted in this approach being widely considered a financially infeasible solution for most applications. This can be overcome by adding flexibility and programmability to ASICs, which allows making changes to the design after fabricating. Thus, design errors are greatly reduced; updated standards are better supported and the system is better able to overcome run-time constraints. Besides, the flexibility helps the system adapt to run-time constraints by adopting dynamic reconfiguration. Currently, such flexibility is realized through software solutions with processors and digital signal processors (DSPs).

However, it is not beneficial in portable devices with performance-critical application such as Moving Picture Experts Group standard 4 (MPEG-4) and Advanced Video Coding (AVC) whose complexity demand high operating frequency and power consumption of DSP to achieve the high throughput required.

Efforts of researchers to find better architectures for future devices have resulted in several novel systems on which the current work presented in this thesis is based. Existing and established architectures like DSPs, FPGAs and ASICs were described previously. Features of typical emerging and reported reconfigurable architectures will be demonstrated in the rest of this chapter. As will be compared later, each architecture has its own pros and cons

and only a few of them can potentially function with high performance and low-power consumption.

This chapter first explores reconfigurable logic structures and reconfigurable computing architectures. Since programmable interconnects contribute greatly to flexibility of reconfigurable systems, a considerable part of this work focuses on the interconnections. The second part of this chapter overviews the existing programmable interconnection topologies. The last part of the chapter describes low power technologies briefly.

### **II.1.1 Reconfigurable Architecture**

For a given application set or domain, there are generally two implementation methods: ASICs and general purpose programmable/reconfigurable platform including Programmable Logic Device (PLD) and general purpose processor (GPP).

Because the functionality of the architecture is fixed, ASIC platform has exactly one-to-one correspondence between application and architecture. This fixed construction has no redundant parts, which makes the ASIC platform the most efficient in area, power and the least delay among all possible implementation platforms. But its Nonrecurring Engineering (NRE) cost is very high. The mask cost is over millions pounds for the 60-nm technology and the design cost runs into as high as tens of millions of pounds as the dimensions of chips approach nano-scales. Besides, time to discover the design failures and repair them would be long, making time-to-market of product uncertain, which is even a more important factor than other cost and may lead to product failure regardless of its high performance.

PLD is an electronic device containing reconfigurable digital circuits which can be programmed for targeted applications by users. GPP is a processor in which the programs stored in the integrated memory can be easily modified according to the requirements of applications and drive GPP to realize the desired function. PLD and GPP rise naturally to deal with today's multimedia and communication applications. These applications are becoming larger and larger, making the chip real estate more and more costly. They can be easily found in smart phone integrating multiple cell phone standards (e.g., Global System for Mobile communications (GSM), Wideband Code Division Multiple Access (WCDMA),

CDMA2000, Time Division-Synchronous Code Division Multiple Access (TD-SCDMA)), wireless Local Area Network (LAN), Bluetooth, MPEG-1 Audio Layer 3 (MP3), MPEG-2, MPEG-4, Digital Video Broadcasting - Handheld (DVB-H), digital camera/camcorder, graphics, games, etc. The PLD devices and programs stored in the memory of a GPP can be easily programmed according to the changes of applications. Under the semiconductor technology trend that the increase of memory density is outpacing that of transistor, storing multiple programs is more cost-effective than fabricating much larger chips.

Furthermore, even for a single application, there has been a tendency that complexity is growing rapidly. Historically, the growing complexity of applications has triggered the digitization revolution in the 90's of the last century and has changed most aspects of human life. Now the further growing complexity, mainly dynamics this time, will very likely introduce another "softwarization revolution" in the next decade. One piece of evidence is the prevalence of embedded processors. Another famous step is the Software-Defined Radio [3]. A typical embedded processor is Graphics Processing Units (GPU) which emerged in graphics and games application domain. It evolved from special ASIC blocks to domain-specific processors with their own C-like high-level programming languages and even larger than GPPs [4].

Compared with ASIC platforms, there are also other reasons for preferring a programmable platform. Firstly, a programmable solution greatly saves NRE cost [5]. It reduces not only mask cost but also the design cost since design efforts would shift from expensive hardware design to relatively cheap software design if the programmable platform is available. Secondly, programmable solution reduces uncertainty and risk. Software design takes less time than hardware design and its failure takes less time to discover and repair than hardware. This greatly reduces the time-to-market which is an even more important factor than cost.

### II.1.2 FPGA devices

The general way to implement reconfigurable architecture is to adopt a PLD style core in the SoC design [6-9]. There are two basic architectures, namely, Complex PLD (CPLD) and FPGA. Using an embedded PLD is the mainstream method for a reconfigurable SoC.

Most FPGA devices are traditionally homogenous arrays of fine-grain, such as [10] and [11], which give the most possible flexibility. In fine-grain reconfigurable architectures the functionality of the hardware is specified at the bit-level or bits-level (less than four) and the programmable interconnection is manipulated as individual wire. The flexibility of fine-grain architecture comes at the cost of additional silicon area and this overhead hampers the performance of word-level algorithms like multiplications. Fine-grained architectures are efficient for bit-level masking and filtering or complex bit-oriented computations. Therefore word-level operations will become relatively large and slow when they are implemented with fine-grained architectures. To cover the gap between fine-grained FPGA devices and coarse-grained (word-level) reconfigurable architectures, 6-input Look-Up-Tables (LUT) based FPGA devices from Xilinx Virtex-5 family [12] are developed to meet the requirements of large complex applications for heavy load.

Compared with 4-input LUT fine-grained FPGA devices, Xilinx Virtex-5 FPGA devices show their merits in area and power efficiency for the computing-intensive digital signal processing applications. Such applications often require Random Access Memory (RAM)/ First In, First Out (FIFOs), mass of adder, subtracter, accumulator and multiplication, all of which are just integrated in Xilinx Virtex-5.

#### II.1.3 Domain-specific Processor

Compared with the poor configuration flexibility of ASIC platform, the flexibility of GPP platform will never be a problem. Actually the processor could implement any target application along with corresponding programs. But GPP platform really suffers from its abundant flexibility and thus is limited to several categories such as superscalar, Very-Long-Instruction-Word (VLIW), multithread, etc., which have been proved hard to maintain the annual performance increase of 50% [13].

More and more, power consumption and flexibility are becoming bottlenecks in VLSI design.

Domain Specific Processor (DoSP) technology emerged to meet the simultaneous demands for flexibility and efficiency. The appropriate constraints imposed onto application sets can

release the architecture from the burden caused by the unnecessarily abundant flexibility, thus opening much larger design space for higher performance than GPP.

The lower flexibility in DoSP necessitates larger configuration bits (e.g., 8 contexts per plane for MorphoSys) compared with one 32-bit instruction for X86 and longer time (e.g. thousands to millions of cycles for FPGA) compared with one cycle for ARM in order to change the configuration. Of course, longer-lasting configuration set makes DoSP work more efficiently and reduce the cost of changing the configuration, which could be achieved by carefully optimizing the configuration set. This type of processor is a sort of reconfigurable architecture by definition. From the above, we observe that DoSP inherently leads to reconfigurable architectures either fine-grained (e.g., FPGA) or coarse-grained (e.g., MorphoSys), and vice versa.

GPP reconfigurable platforms can be roughly divided into fine grain architecture and coarse grain architecture in term of granularity which is determined by the width of the components in its datapath. Generally, an architecture is considered as fine-grain one when its datapath width is four bits or less [14]. Otherwise, it is considered coarse-grain architecture. In the following three sub-sections, fine-grain FPGA Architecture, typical fine-grain and coarse-grain architectures are discussed briefly.

### II.2 FPGA Architecture

### II.2.1 Fine-grain FPGA Architecture

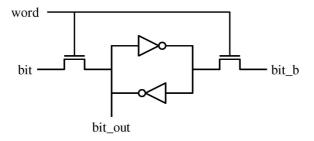

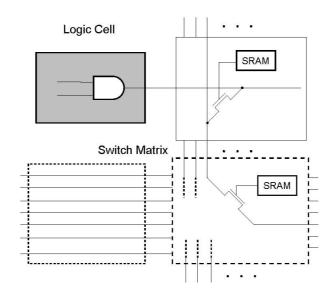

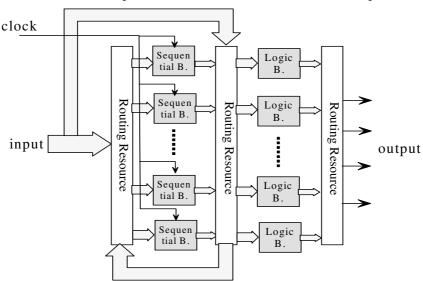

The architecture model of FPGA is shown in Figure II-1. In this model, the reconfigurable hardware platform consists of three basic elements: Configurable Logic Blocks (CLBs), Connection Boxes (C-Box), and Switch Boxes (S-Box). The operational elements in CLBs of FPGA are mainly LUTs with 16 single bit inputs, which store the truth tables of user-defined combinational logic functions. These inputs are controlled by bits from the configuration memory which makes it possible to build any 4-input logic function by changing the content of the Static Random Access Memory (SRAM) configuration memory [15]. A combinational logic function is realized by looking up the value stored in the LUT that is addressed by the corresponding gate inputs. The programmable elements also have the

ability to optionally register their outputs. Furthermore, a mesh of programmable interconnects is available to connect the CLBs together to build bigger circuits.

Figure II-1: Architecture of FPGA

Implementing a logic network requires connecting CLBs by selecting the desired signal wire linked to the routing tracks through horizontal and vertical wiring channels located between two neighbouring rows or columns. A connection block can attach the signals to the logic block and the switch box nearby. The connections in the switch boxes make the input signal either pass through the switch box on its track or change its routing direction. To enhance the connectivity for connecting various CLBs, it is possible to use various types of wires with different lengths which are separated by variable numbers of blocks [14]. For example, in Xilinx's Virtex FPGAs, there are two types of routing devices, C-Box and S-Box, which route the signal flows among CLBs and wires. C-Box route the inputs and outputs of a CLB to the adjacent wires. S-Box connects horizontal and vertical crossing wires. The single-lines connect adjacent CLBs, while 16 lines connect CLBs that are three or six blocks apart [10].

The fine-grain aspect of FPGAs makes them extremely flexible and suitable for a very wide range of applications. Hence, FPGA chips are produced in large quantities which make their usage come with greatly reduced NRE costs. This high flexibility is obtained at the cost of very high power consumption which prohibits the deployment of FPGAs in portable applications.

### II.2.2 Problems with Fine-grain FPGA Architecture

One problem with fine grain FPGAs is the high reconfiguration time. Take Atmel 40K40 as an example, which is a 48 by 48 FGPA and it needs 42063 8-bit words for full reconfiguration with maximum 8 MHz reconfiguration clock [16]. Therefore it can be fully reconfigured in 5.26 milliseconds. Similarly, Xilinx Virtex-E FPGA family has the array size of 64 by 96 with 766042 bits bitstream for full reconfiguration. It needs 3.1 milliseconds for reconfiguration by using a 50MHz clock [10]. The high reconfiguration time can be a restriction if dynamic reconfiguration is adopted in applications where parts of the circuit mapped on the FPGA are idle waiting for another part to finish. Dynamic reconfiguration of the circuit in this case would lead to better use of the available silicon. Besides, FPGAs usually have around 10 times more delays than ASICs.

Figure II-2: Reconfiguration time of two FPGA devices

Figure II-2 gives comparison of reconfiguration times of imaginary Atmel 40K and Virtex-E FPGA with 100 by 100 array size and reconfiguration clock of 50 MHz [17, 18].

In addition to the high reconfiguration overheads, FPGA devices also suffer from high power dissipation. In an FPGA chip, the energy dissipated in interconnects is about 65% of the total energy consumption, while 30% are dissipated in programmable clock-routings and I/O blocks. For example, the power consumption of an XC4085 chip running at a system clock of 50 MHz is approximately 6W [19]. Therefore, the high power consumption of FPGA is a limiting factor in energy-sensitive domains for the hand-held and portable devices such as wireless communication terminals, personal digital assistants (PDAs), laptops, etc. High power consumption directly shortens the running time of portable devices which, in a sense, directly determines the future of devices in the market.

As the size of the application becomes larger, the size of FPGAs has been growing steadily over the past decade and will stay on this path. This has been made possible by staying at the forefront in terms of the process technology. The combined effect of smaller feature sizes and larger die area is that more and more transistors are integrated on a die. The resulting increase in power density and total power dissipation will have an adverse effect even in the power insensitive domains, due to the advanced packaging and the cooling techniques required [19].

### II.3 Fine-grain Architecture

Fine-grained architectures can make designers to take the benefit for implementing bit manipulation tasks flexible without wasting reconfigurable resources. The fine granularity of such architectures makes the implementation of large and complex calculations consuming numerous Processing Element (PEs). This results in slower clock rate when the applications are implemented with fewer, coarse-grained PEs.

To author's opinion, the number of fine-grain architectures is limited so it is difficult to classify them. Though each has its specific characters that differentiate them from others, they have a lot in common. Thus three popular architectures are randomly selected and introduced in this section. It is not intended to detail all industrial reconfigurable systems and

research projects; instead it is to show the overall characters of fine-grain architectures by introducing selected systems.

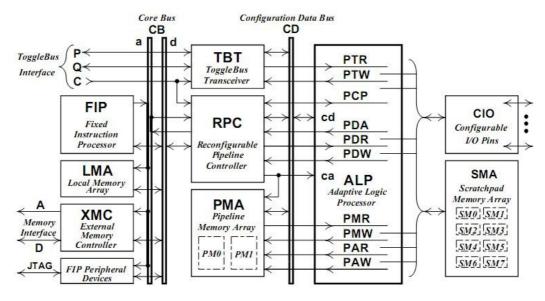

### II.4.1 National Semiconductor's Adaptive Processing Architecture (NAPA)

NAPA [20-22] was developed by National Semiconductors USA. Adaptive Logic Processor (ALP) in the architecture couples a standard processor on-chip, 32-bit Reduced Instruction Set Computer (RISC) core (Compact RISC) called the Fixed Instruction Processor (FIP), with a reconfigurable array of fine-grained logic elements. Both ALP and FIP can access the same memory space and ALP, therefore, retains complete generality. The structure of NAPA processor is shown in Figure II-3. Additionally, the ALP has exclusive access to a set of configurable I/O pins and on-chip memory resources and a general external memory interface. This increased flexibility in interfacing and memory allocation are greatly helpful for adaptive computing effectively, especially in embedded systems.

To overcome the problems of consistency and synchronization between ALP and FIP, there are synchronization mechanisms such as standard status flags and interrupts with two programming modes for FIP and ALP threads to rejoin. In the first mode, FIP initiates the ALP operation and suspends afterwards. Once the work is done, the ALP reactivates FIP by an interrupt. In the second mode, the FIP is free to perform computation loaded after having initiated ALP.

Figure II-3: NAPA processor structure [20]

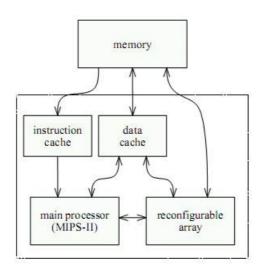

### II.4.2 Garp: Gate Array Processor

Garp was developed by Berkeley Reconfigurable Architecture, System, and Software (BRASS) group at UC Berkeley, USA [23-25]. It is reserved for tasks such as interrupting the main processor, array-initiated memory accesses, and register transfers with the host processor. The Garp processor architecture, as shown in Figure II-4, combines a standard Microprocessor without Interlocked Pipeline Stages II (MIPS-II) processor with a two-dimensional reconfigurable array such as FPGA-like blocks available from Xilinx, Altera and other manufacturers. The reason to classify this processor into fine-grain architecture is 2-bit operands in size at most for each computing element in the reconfigurable array which is used to accelerate certain computations. Garp's main processor executes an extended MIPS-II instruction set and the reconfigurable array in it exchanges data between memory and the main processor through 4 memory buses which is vertical through the rows. In Data Encryption Standard (DES), image dithering, and a sorting algorithm, Garp processor runs at 133 MHz and speeds up from 2 to 24 over a 167 MHz UltraSPARC processor.

Figure II-4: Garp block diagram [23]

The main problem is a lack of memory to store intermediate data inside the reconfigurable array. There are flip-flops only inside the logic elements, which can be used for memory resources. The intermediate data generated in reconfigurable array must be written back to the data cache. Due to the caching mechanism, accesses to intermediate data may cause

misses and stall array execution. Besides, large amount of data caching requires more bandwidth and therefore forms a bottleneck for its limited buses.

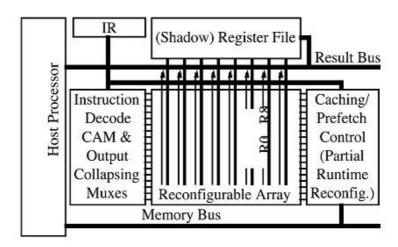

### II.4.3 Chimaera Architecture

The Chimaera [6, 26, 27] architecture was developed by Scott Hauck and other researchers at Northwestern University first and University of Washington later. Figure II-5 demonstrates the overall Chimaera architecture. It consists of tightly coupled fine-grain reconfigurable functional units (FPGA blocks) and microprocessor for hardware caching. This integration was intended to eliminate the communications bottleneck between the two and allow the acceleration of a broad class of functions as opcodes. Functions loaded into the FPGA by the host processor operate speculatively on every clock cycle, with the results written back to a register file only for those functions explicitly invoked by the processor.

Figure II-5 : Overall Chimaera architecture [6]

The execution model is that of bit-slice data which spreads horizontally across the array, propagating downward as row-wise operations are applied. Kernels corresponding to operating codes take up entire contiguous rows. Hence, the array is partially reconfigurable by the row. Logic blocks have multiple LUTs and multiple inputs/outputs, allowing data forwarding while computing. Special carry-propagation logic propagates critical paths along each row. Horizontal wires of various reaches are available, but limited. In order to simplify context switching, there are no pipeline registers apart from the logic block's ability to

read/write the register file of the host processor. Besides, there are not pipelining latches in the reconfigurable array.

### II.4 Coarse-grain Architecture

Coarse-grained reconfigurable architectures contain word-level function units, such as multipliers, Arithmetic Logic Units (ALUs) or PE which can perform a limited number of 16-bit or 32-bit operations as configured. One characteristic of coarse-grain architectures is the large size of PE and limited functions available in it. Compared with fine-grain architectures, coarse-grain architectures will consume less power, but it also suffers from the difficulty in implementing the control logic which is operated at bit level.

Generally, Coarse-grained architectures require less configuration data than fine-grained architectures because of their short configuration time. A survey of coarse grain architectures can be found in [28, 29]. The reconfiguration overhead of the coarse architectures is less than that of the fine grain architectures [30].

Coarse-grain architectures share certain features as introduced above while each has its own differentiating characters. Given their limited number and varied functions, it is difficult to systematically classify coarse-grain architectures. Thus five coarse-grain architectures are selected randomly as examples, which could make overall characters of coarse-grain architectures better revealed.

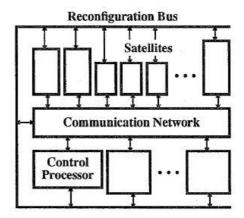

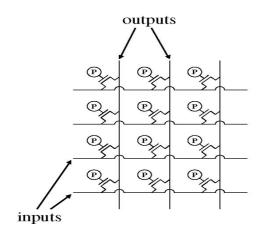

#### II.4.1 Pleiades Architecture

Pleiades [31] is an important vision for InfoPad project by Jan Rabaey's group at Wireless Research Centre at the University of California in Berkeley, which works toward multimedia on the mobile unit of computing services available from a high-bandwidth backbone network of computers, in which the driving need was to perform many different computationally intense tasks with low power.

The architecture, as shown in Figure II-6, consists of a general-purpose microprocessor for controlling and a surrounding heterogeneous array of coarse grain satellites. The main processor executes control-dominated sections of the program while satellites execute data-

dominated computations. The system is distributed in a sense that every satellite has its own instruction fetch and execution. The satellites communicate between each other through dedicated interconnects. The satellite processors could be arithmetic modules such as multipliers, memory modules, address generators or reconfigurable arrays [9, 32].

Because the configurable modules are function-specific, the paradigm is based on an ASIC flow. However, the control core processor is linked to satellite processors of varying degrees of specialization through a reconfigurable communication network. The task of architecture design and the decision of which satellites to use have to be done manually. Although dynamically configurable fine grain programmable gate array (PGA) satellites could accelerate functions, they cannot warrant special-purpose satellites and are less efficient than specialized circuits in the satellites. At partitioning stages the designer decides which loops of the full high-level program need to speed up using reconfigurable fabric; then the decision of which satellites to be deployed is made and their design started.[33]

Interconnects and the type/number of satellites can be parameterized to provide limited reconfigurability according to the requirements in applications. But programming the satellites requires writing low-level netlists. This technique can make the architecture efficient; however, they become too specific for diverse targeted applications.

Figure II-6 : Overall Pleiades architecture [9]

#### II.4.2 RaPiD: Reconfigurable Pipelined Datapath

The RaPiD (Reconfigurable Pipelined Datapath) architecture [34], developed in 1996 at the University of Washington, USA, is a one-dimensional array of cells. It is aimed at speeding up highly repetitive, computationally-intensive tasks in multimedia and digital signal processing domain by implementing deep, application-specific computation pipelines to form a mostly linear pipeline in the RaPiD architecture.

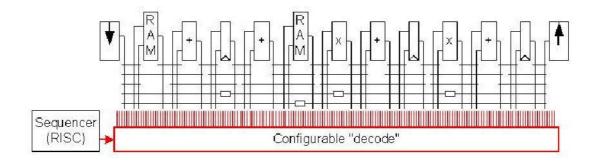

An abstract view of the Rapid architecture is shown in Figure II-7. For RaPid-1prototype, each cell comprises an integer multiplier, three integer ALUs, six general purpose datapath registers and three local memories with 32 entries. Cells are connected by segmented buses with built-in pipeline registers and FIFOs at each end. The registers, the RAM, the ALU and all datapath operate on 16-bit data types. The multiplier performs a 16 x 16 to 32 multiplication and outputs the 32-bit result as two 16-bit words. The ALUs can be cascaded for double-precision operations. The data-path registers can be used to store constants or temporary values, to implement additional multiplexers, to support routing, and for additional pipeline delays. Each memory has a specialized datapath register featuring an incrementing feedback path. A RaPiD array is constructed by replicating identical cells from left to right, forming a linear computing pipeline. The array can consist of hundreds of cells, such as multipliers, adders, and comparators.[35-37]

Figure II-7: Abstract view of the Rapid architecture [34]

RaPiD is the only architecture that defines a broad architectural approach and provides a heterogeneous computation fabric/array. For configuration, the RaPiD architecture uses a

mix of static configuration and dynamic control, which brings plenty of flexibility for designers to configure it for their target domain.

Mapping applications onto RaPiD needs a non-standard programming language, RaPiD -B language, and compiler tool set, RaPiD -B compiler. All this causes the architecture to be considerably weak. Compared to an FPGA or MATRIX routing architecture, RaPiD restricts the connectivity among the processing elements to a linear segmented bus. This places the designer at a significant disadvantage when the architecture is configured for the target applications.

#### II.4.3 MorphoSys

Morphosys [38] is a reconfigurable processor that is a parallel system on one chip comprising a software programmable processing unit and a reconfigurable hardware unit from UC Irvine. It is targeted at the applications with inherent parallelism and a high level of granularity, which can be accelerated by the reconfigurable part. The granularity of the Morphosys processing elements is the highest among the family of reconfigurable processors. The performance of the Morphosys architecture on MPEG2, Motion Estimations, Discrete Cosine Transform (DCT) and Viterbi is around a 5-10 times improvement over normal Central Processing Units (CPUs) [39, 40].

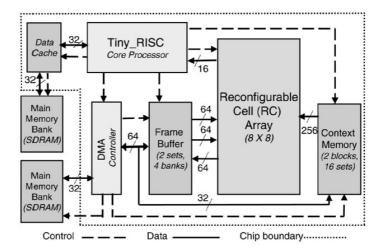

The complete MorphoSys architecture, as shown in Figure II-8, consists of a MIPS-like TinyRISC core processor, a frame buffer, a Direct Memory Access (DMA) controller, a context memory, and an 8x8 reconfigurable array. The main component of Morphosys is the reconfigurable array of 8 by 8 which has a 28 bit, fixed point ALU (with a 16 x 12 multiplier) and a register file, and is configured through a 32-bit context word. The ALUs run on RISC instructions and the instruction set has load and store instructions for manipulation of the DMA controller and the reconfigurable array. The context word is loaded into a register in every execution cycle from the context memory, which is used to store the configuration data for the reconfigurable array including the functionality of the ALU (the instruction fetch and decode phase) and the network connections for that ALU. The frame buffer is used as data cache to store internal data for blocks of intermediate results.[41-43]

Figure II-8: The MorphoSys Architecture [38]

The processor uses a hierarchical routing architecture, and is therefore capable of providing good routing flexibility. It follows that the Single Instruction, Multiple Data (SIMD) model and all the functional units in the same row or column execute the same operation with different data. Hence the array is only useful for data-parallel operations such as pixel parallel-data operations. In addition to its preference for word-level applications, which is caused by the coarse granularity of the processing elements, the architecture is also flexible enough to support bit level operations such as control operations which are executed by the RISC.

The Morphosys approach is well suited to some regular computation patterns but it does little to address the increasingly irregular patterns in the latest media standards, such as MPEG4. The regularity and simplicity of the reconfigurable array have limitations on implementation of some media processing algorithms and the applications with time-varying computation patterns. For example, an implementation of FIR on such an array is likely to cause excessive stalls and repeated-redundant context reloading. Besides, the architecture was not designed to be customised in spite of its synthesisable core.

#### II.4.4 Chameleon

The Chameleon reconfigurable processor [44], developed in University of Twente, Netherlands, is a heterogeneous reconfiguration architecture in combination with a Quality of Service (QoS) driven operating system.

It provides a platform for high-performance telecommunication and data communication applications. Chameleon reconfigurable processor is a general processor-based reconfigurable architecture, in which a 32-bit RISC core, the reconfigurable fabric, a fast bus, the local memory system, Programmable Logic Arrays (PLAs) for the control path and I/O are built in a single chip. [45]

The RISC core is employed as a host processor which schedules computation intensive tasks onto the programmable logic. The programmable logic is the main computing engine in the fabric, which is a 32-bit array of 108 data path units (DPUs). These DPUs are also capable of parallelling 16-bit operations and can be dynamically reconfigured between one and eight instruction execution. The main computational block within the DPU is an ALU capable of two's complement arithmetic and bitwise Boolean operations. It can simultaneously monitor and flag a number of relational and arithmetic conditions. The ALU is fed by two operand paths with optional Boolean masking, shifting, and registers for pipelining or storing constants. Input muxes select the operands from buses driven by other DPUs. Data can be read/written to/from the adjacent SRAM; each SRAM memory has one read port and one write port on the fabric side which can be used by the executing kernel. The SRAM memories can be chained together into a contiguous address space.[46-49]

A configuration bit stream is stored in the main memory and loaded onto the fabric at runtime by DMA. The programme logic can be configured at running time by bits stored in the memory. There are two kinds of planes in the DPUs: active and back planes. An active one executes the working bit stream and a back one contains the next configuration bit stream. It only takes one cycle to switch from the back plane to the active one. Therefore, the back plane can be treated as a cache for loading configurations.

#### **II.4.5 RAP**

The Reconfigurable Algorithm Processor (RAP) [50-52], originally developed by Bristol-based Elixent Ltd, is a coarse-grain reconfigurable platform designed for DSP and multimedia applications. The reconfigurable hardware, known as the D-fabrix, is made up of an array of hundreds of 4-bit ALU's and register/buffer blocks that can be cascaded together

to accommodate larger data lengths. This allows the fabric to operate on the 8-24 bit data lengths common in multimedia applications. The ALU's are arranged in a chessboard style, alternating with switchboxes which can act as a cross-point switch or 64 bits of configuration memory.

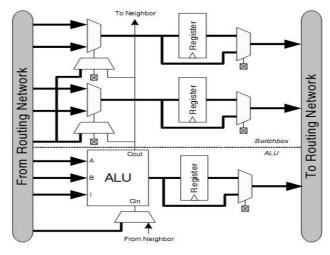

The D-Fabrix architecture is an extension of the Chess project [53] which is developed by Hewlett-Packard Laboratories. The logic in D-Fabrix ALU and Switchbox pair is shown in Figure II-9. Each basic 4-bit processing element of it has two 4-bit data inputs, one 4-bit data output, 1-bit carry input and carry output terminals to create carry chains linking between ALUs for wider words processing and a 4-bit instruction input. Besides, the array also contains 256-byte memory blocks dispersed around the array. The choice of nibble sized ALU's means that only a few bytes of memory are required to configure each ALU allowing rapid reconfiguration and improved density. The large amount of on-chip memory also allows ALUs to be fed by instruction streams generated within the array reducing off-chip memory traffic to improve overall performance.

Multiplexers are adopted in the switchbox in D-Fabrix, which is used to construct 2-input logic gates. One of the input ports of the multiplexer are connected to the control input and the other port is connected to data inputs. Although one of the four available data bits is used, the adoption of multiplexers achieves good performance in terms of area and speed compared with ALUs because of its efficient construction for simple Boolean logic implementation.

Figure II-9: The logic in D-Fabrix ALU and Switchbox pair [52]

The RAP is targeted at multimedia and wireless base-station applications and they have shown a speed-up of 238x against a 32-bit DSP processor and 38x against an FPGA in Joint Photographic Experts Group (JPEG) compression application.

#### II.3 Interconnection Structure

Reconfigurable interconnection networks are the important underlying hardware infrastructures of reconfigurable system. They not only provide the whole system with powerful flexibility to meet the requirements from applications, but also affect the area, time, and power efficiency. Reconfigurable interconnection networks implement required connections among functional blocks or components through reconfiguring programmable switches and basically consist of programmable switches and wire segments or channels [54].

In this section, three typical interconnection structures are evaluated which are symmetrical interconnection network, hierarchical interconnection network and binary (Fat) interconnection tree.

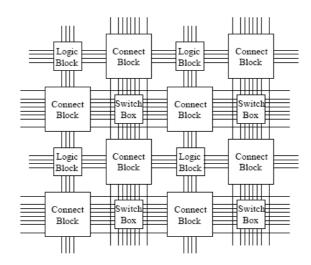

#### **II.4.1. Symmetrical Interconnection Network**

FPGA devices employ non-distinctive logic blocks which are embedded in a mesh of routing sea consisting of switch boxes and connect boxes. Each function module in FPGA devices including Boolean and routing function modules are the same. The routing network is organized in symmetrical and balanced style.

Logic blocks in FPGA are separated by vertical and horizontal channels. There are prefabricated parallel wire segments running between each pair of adjacent logical blocks in both the vertical and horizontal channels. A switch block is located at each intersection of a vertical and horizontal channel. When an FPGA is used to implement a Boolean function, a partitioning algorithm is used to decompose the Boolean function into some smaller subfunction so that each of them can be implemented by a single logic block. Then a placement and routing algorithm is employed to select a logic block for each sub-function, and the wire segments and switches are chosen to connect the selected logic blocks.

During the whole processing, the selection of logic block, switch box and connect box is no distinction except the limitation caused by the requirement of delay.

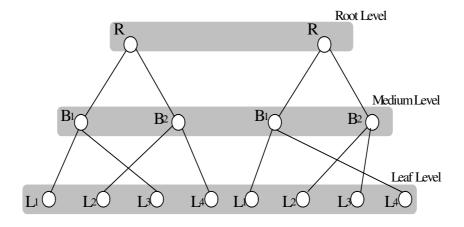

#### II.4.2. Hierarchical Interconnection Network

While being effective for local connections, the symmetrical interconnection network has the disadvantage caused by the coarse granularity architecture that distant routing wires make communication slow and expensive since a large number of programmable switches have to be traversed. This leads to the concept of the hierarchical interconnection network, which continues to exploit locality while reducing the cost of the long connections.

Hierarchical interconnection network is focused on the interconnection between the coarse block elements such as Pleiades architecture (see sub-section II.4.1) and tries to overcome the routing problems caused by blocks with different area sizes. It is useful in applications where data locality is high and only a few signals need to be sent across the chip.

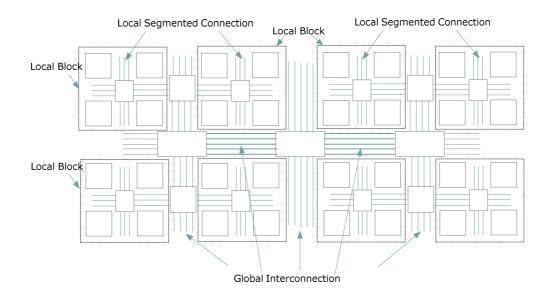

The interconnection network is composed of two types of connections: global interconnects and local segmented mesh structure. Global interconnects provide long distant connection between any two parts of the array. Furthermore, switching activities of the lines are transmitted for long distances. Local segmented mesh structures in local blocks improve overall global interconnects as shown in Figure II-10, but it is difficult for them to adapt to heterogeneous arrays, for a 2D regular grid has to be found. The disadvantage of hierarchical interconnection network is that their switching elements are less generic than symmetrical interconnection network. Besides, the complexity of two routing methods in their respective partitions always makes mapping distribution hard to achieve an optimal status as originally expected.

Figure II-10: An example of generalized hierarchical interconnection

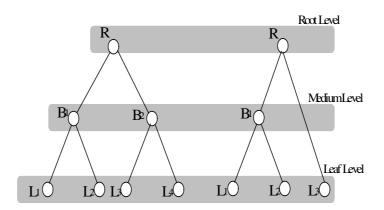

#### II.4.3. Binary (Fat) Interconnection Tree

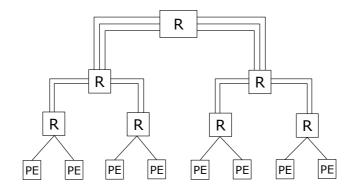

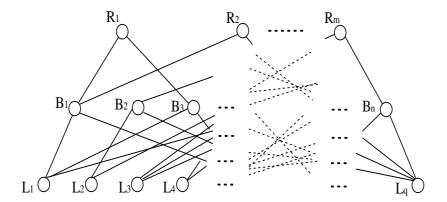

The binary interconnect tree is a useful alternative to the hierarchical segmented mesh, which is also presented by the "fat tree". The hierarchical synchronous reconfigurable array used in the BRASS project [55] is such an interconnection which is a network based on a complete binary tree and the shared bus when logic block to logic block connections are needed. Binary trees have favourable features such as constant node degree, small node degree, scalability, etc. An example of such a network is shown in Figure II-11, in which, functional logic blocks, represented by the symbol PE, are located at the terminals of the network, like leaves on a tree. The routing nodes are represented by Rs. The number of buses per channel increases with the levels of the tree. For the communication between two local logic blocks, signals are transferred without the assistance of stem network bus which is in the upper level. The fat tree is more like a real tree, in which the branches get thicker toward the top.

The advantage of this architecture is that the number of switches used to route the signal grows logarithmically with the distance, which means that the overall delays introduced by the switches are lower.

Figure II-11: A fat binary tree

#### **II.4 Low Power Technology**

Traditionally, low-power VLSI design techniques have been focussed on improving energy efficiency. As the issue of low-power VLSI design techniques becomes more pervasive, the researches to minimize power consumption in VLSI design have been carried out on multiple lines: semiconductor technology, circuit design, system architecture, application design, design automation tools and operating system. Energy awareness is now gaining more and more attention in the mainstream VLSI design affecting all aspects of the design process.

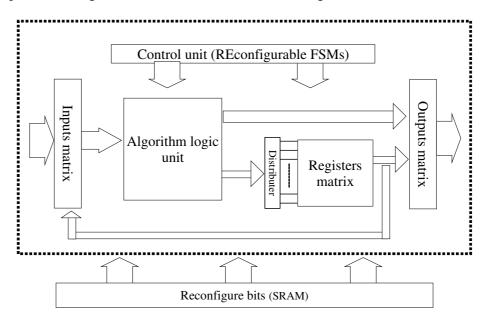

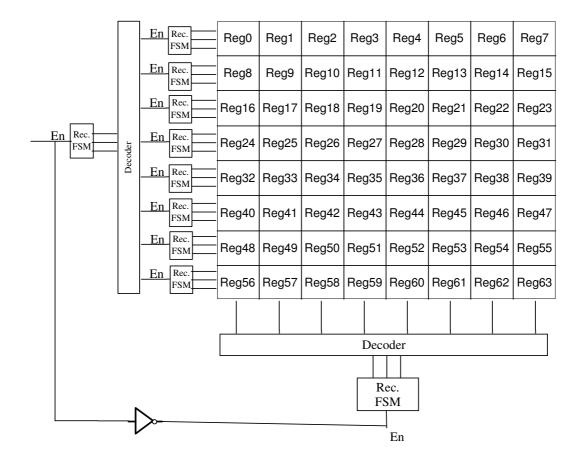

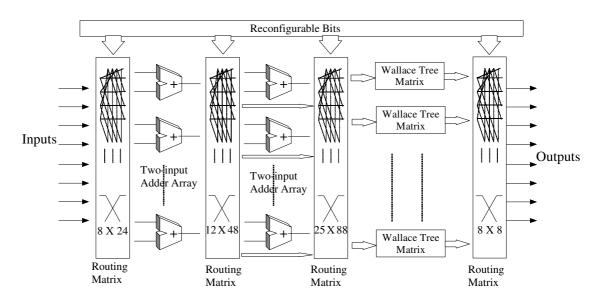

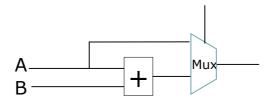

Currently, most components in VLSI design are fabricated using CMOS technology. The reason for this bias is low cost and, inherently, efficient power consuming of Complementary metal—oxide—semiconductor (CMOS) technology compared with other technologies. There are two main components of power dissipation in a CMOS circuit: dynamic power and static power. During normal operation, the power dissipation of a CMOS circuit is determined by the dynamic power which is the switching energy consumption spent in charging and discharging of circuit nodes. The leakage currents of the circuit are orders of magnitude less than the operating currents when devices are switching and are negligible therefore. The dominant factor of energy consumption in CMOS is dynamic power consumption, which is linear with the effective switch capacitance, the square of supply voltage, and the frequency of operations.