# Low Power JPEG2000 5/3 Discrete Wavelet Transform Algorithm and Architecture

Kay-Chuan Benny Tan

A thesis submitted for the degree of Doctor of Philosophy. The University of Edinburgh.

November 2004

## Abstract

With the advances in VLSI digital technology, many high throughput and performance imaging and video applications have emerged and increased in usage. At the core of these imaging and video applications is the image and video compression technology. Image and video compression processes are by nature very computational and power consuming. Such high power consumption will shorten the operating time of a portable imaging and video device and can also cause overheating. As such, ways of making image and video compression processes inherently low power is needed.

The lifting based Discrete Wavelet Transform (DWT) is increasingly used for compression digital image data and is the basis for the JPEG2000 standard (ISO/IEC 15444). Even though the lifting based DWT has resulted in several implementations of this algorithm, there is no work on the low power realisation of such an algorithm. Recent JPEG2000 DWT implementations are pipelined data-path centric designs and do not consider the issue of power. This thesis therefore sets out to realise a low power JPEG2000 5/3 lifting based DWT hardware architecture and investigates whether optimising at both algorithmic and architectural level will yield a lower power hardware. Besides these, this research also ascertains whether the accumulating Arithmetic Logic Unit (ALU) centric processor architecture is more low power than the feed-through pipelined data-path centric processor architecture.

A number of novel implementation schemes of the realisation of a low power JPEG2000 5/3 lifting based DWT hardware are proposed and presented in this thesis. These schemes aim to reduce the switched capacitance by reducing the number of computational steps and data-path/arithmetic hardware through the manipulation of the lifting-based 5/3 DWT algorithm, operation scheduling and alteration to the traditional processor architecture. These resulted in a novel SA-ALU centric JPEG2000 5/3 lifting based DWT hardware architecture that saves about 25% of hardware with respect to the two presented existing 5/3 DWT lifting-based architectures.

The proposed SA-ALU centric architecture also allows innovative scheduling and a novel embedded extension algorithm to be incorporated into its main operation. The embedded extension algorithm saves more than 50% of memory and power by doing away with explicit data extension operations entirely. Optimisation at architectural level also results in a novel addressing architecture called the dyadic multi-segments multi-level one-hot addressing architecture (MSML-OHA). The MSML-OHA reduces power by 20% through reducing switched capacitance by isolating and confining switching activities into a small local area by segmentation. A further reduction of 59% is achieved in the dyadically structured MSML-OHA (DMSML-OHA) when this is combined with the shared address lines architecture bought about by innovative scheduling.

## Publication

#### **Refereed Journal Papers**

K. C. B. Tan and T. Arslan, Low Power Embedded Extension Algorithm for the Lifting based Discrete Wavelet Transform in JPEG2000, IEE Electronic Letters, Vol. 37, No.22, pp. 1328-1330, Oct. 2001.

#### **Refereed Conference Papers**

K. C. B. Tan and T. Arslan, *An Embedded Extension Algorithm for the Lifting based Discrete Wavelet Transform in JPEG2000*, 2002 IEEE International Conference on Acoustics, Speech, and Signal Processing (ICASSP 2002), Vol: 4, pp. 3513-3516, May 2002.

K. C. B. Tan and T. Arslan, *Shift-accumulator ALU Centric JPEG2000 5/3 Lifting based Discrete Wavelet Transform Architecture*, 2003 IEEE International Symposium on Circuits and Systems (ISCAS 2003), Vol:5, pp. 161-164, May 2003.

#### **Submitted Papers**

K. C. B. Tan and T. Arslan, Low Power Multi-segment Sequential One-hot Addressing Architecture, accepted to be published in the IEE Proceedings of Circuits, Devices and Systems.

K. C. B. Tan and T. Arslan, Low Power JPEG2000 5/3 Lifting Based Discrete Wavelet Transform Architecture, submitted to IEEE transactions on Integrated Circuits and Systems I.

## Declaration of originality

I hereby declare that the research recorded in this thesis and the thesis itself was composed and originated entirely by myself in the Institute of Integrated Micro and Nano Systems, School of Engineering and Electronics at The University of Edinburgh.

Kay-Chuan Benny Tan

## Acknowledgements

Firstly, I would like thank my Supervisor Dr. Tughrul Arslan for giving me his guidance and this opportunity to do this PhD.

I would also like to especially thank my second supervisors Dr. John Hannah for his kind and invaluable advices, guidance and support for the last 3 years.

Thanks also go to Dr. Ahmet Erdogan for his expert advice on digital hardware design and tool.

I would like to thank Prof. Steve McLaughlin for giving me the occasional but necessary sanity checks. Thanks also to Dr. David Renshaw for making my 3 years interesting by kindly letting me demonstrate in the 2nd year project laboratory.

Many thanks to all those in the Department of Electronics and Electrical Engineering at the University of Edinburgh who made the last 3 years both rewarding and enjoyable.

And most important of all, I like to thank GOD for all He had done.

This thesis and the research project have been kindly supported by EPSRC under grant number N08322.

## Contents

|   |                                               | Public                                                                                    | ation                                                      | iii                                                    |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------|

|   |                                               | Declar                                                                                    | ration of originality                                      | iv                                                     |

|   |                                               | Ackno                                                                                     | wledgements                                                | v                                                      |

|   |                                               | Conter                                                                                    | nts                                                        | vi                                                     |

|   |                                               | List of                                                                                   | figures                                                    | x                                                      |

|   |                                               | List of                                                                                   | tables                                                     | xiv                                                    |

|   |                                               | Acron                                                                                     | yms and abbreviations                                      | xvii                                                   |

|   |                                               | Nomer                                                                                     | nclature                                                   | xx                                                     |

| 1 | Intr                                          | oductio                                                                                   | n .                                                        | 1                                                      |

|   | 1.1                                           | Introdu                                                                                   | uction                                                     | 1                                                      |

|   | 1.2                                           | Motiva                                                                                    | ations                                                     | 2                                                      |

|   | 1.3                                           | Contri                                                                                    | bution                                                     | 3                                                      |

|   | 1.4                                           | Thesis                                                                                    | Structure                                                  | 4                                                      |

|   | 1.5                                           | Summ                                                                                      | ary                                                        | 6                                                      |

|   |                                               |                                                                                           |                                                            |                                                        |

| 2 | Low                                           | Power                                                                                     | Digital CMOS System and Circuit Design                     | 7                                                      |

| 2 | <b>Low</b><br>2.1                             |                                                                                           | Digital CMOS System and Circuit Design                     | <b>7</b><br>7                                          |

| 2 |                                               | Introdu                                                                                   |                                                            | -                                                      |

| 2 | 2.1                                           | Introdu                                                                                   | uction                                                     | 7                                                      |

| 2 | 2.1                                           | Introdu<br>Power                                                                          | Consumption Sources of Complementary MOSFET (CMOS) Circuit | 7<br>8                                                 |

| 2 | 2.1                                           | Introdu<br>Power<br>2.2.1<br>2.2.2                                                        | Inction                                                    | 7<br>8<br>11                                           |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2                                                        | Auction                                                    | 7<br>8<br>11<br>14                                     |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Pe                                              | Inction                                                    | 7<br>8<br>11<br>14<br>16                               |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Pe<br>2.3.1                                     | Inction                                                    | 7<br>8<br>11<br>14<br>16<br>16                         |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Po<br>2.3.1<br>2.3.2<br>2.3.3                   | action                                                     | 7<br>8<br>11<br>14<br>16<br>16<br>28                   |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Po<br>2.3.1<br>2.3.2<br>2.3.3                   | action                                                     | 7<br>8<br>11<br>14<br>16<br>16<br>28<br>29             |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Po<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4          | action                                                     | 7<br>8<br>11<br>14<br>16<br>16<br>28<br>29             |

| 2 | 2.1<br>2.2                                    | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Pe<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5 | action                                                     | 7<br>8<br>11<br>14<br>16<br>16<br>28<br>29<br>30       |

| 2 | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Introdu<br>Power<br>2.2.1<br>2.2.2<br>Low Pe<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5 | action                                                     | 7<br>8<br>11<br>14<br>16<br>16<br>28<br>29<br>30<br>30 |

|   |                                                                                          | 2.4.3                                                                                                | Limitation of Existing Power Evaluation Tool            | 37                                                                                                                     |

|---|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   | 2.5                                                                                      | Summ                                                                                                 | ary                                                     | 38                                                                                                                     |

| _ | _                                                                                        | _                                                                                                    |                                                         |                                                                                                                        |

| 3 |                                                                                          | -                                                                                                    | pression                                                | 40                                                                                                                     |

|   | 3.1                                                                                      |                                                                                                      | uction                                                  | 40                                                                                                                     |

|   | 3.2                                                                                      | Image                                                                                                | Compression Techniques                                  | 41                                                                                                                     |

|   |                                                                                          | 3.2.1                                                                                                | Discrete Cosine Transform (DCT) Coding                  | 42                                                                                                                     |

|   |                                                                                          | 3.2.2                                                                                                | Sub-Band Coding                                         | 43                                                                                                                     |

|   | 3.3                                                                                      | Discre                                                                                               | te Wavelet Transform (DWT) Algorithm and Implementation | 45                                                                                                                     |

|   |                                                                                          | 3.3.1                                                                                                | Discrete Wavelet Transform (DWT)                        | 46                                                                                                                     |

|   |                                                                                          | 3.3.2                                                                                                | Conventional Convolution Based DWT Implementation       | 49                                                                                                                     |

|   |                                                                                          | 3.3.3                                                                                                | Lifting Based DWT Algorithm and Implementation          | 51                                                                                                                     |

|   | 3.4                                                                                      | Image                                                                                                | Compression Standards                                   | 57                                                                                                                     |

|   |                                                                                          | 3.4.1                                                                                                | Discrete Cosine Transform (DCT) Based Standards         | 58                                                                                                                     |

|   |                                                                                          | 3.4.2                                                                                                | Discrete Wavelet Transform (DWT) Based Standards        | 60                                                                                                                     |

|   | 3.5                                                                                      | Comp                                                                                                 | Itational Load of Image Compression                     | 60                                                                                                                     |

|   | 3.6                                                                                      | Summ                                                                                                 | ary                                                     | 63                                                                                                                     |

|   |                                                                                          |                                                                                                      |                                                         |                                                                                                                        |

| 4 | JPE                                                                                      | G2000 :                                                                                              | 5/3 Lifting Based DWT Implementation                    | 64                                                                                                                     |

| 4 | <b>JPE</b><br>4.1                                                                        |                                                                                                      | 5/3 Lifting Based DWT Implementation                    | <b>64</b><br>64                                                                                                        |

| 4 |                                                                                          | Introdu                                                                                              |                                                         |                                                                                                                        |

| 4 | 4.1                                                                                      | Introdu                                                                                              | action                                                  | 64                                                                                                                     |

| 4 | 4.1                                                                                      | Introdu<br>JPEG2                                                                                     | oction                                                  | 64<br>65                                                                                                               |

| 4 | 4.1                                                                                      | Introdu<br>JPEG2<br>4.2.1<br>4.2.2                                                                   | action                                                  | 64<br>65<br>65                                                                                                         |

| 4 | 4.1<br>4.2                                                                               | Introdu<br>JPEG2<br>4.2.1<br>4.2.2                                                                   | action                                                  | 64<br>65<br>65<br>67                                                                                                   |

| 4 | 4.1<br>4.2                                                                               | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos                                                         | action                                                  | 64<br>65<br>65<br>67<br>71                                                                                             |

| 4 | 4.1<br>4.2                                                                               | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1                                                | action                                                  | 64<br>65<br>65<br>67<br>71<br>73                                                                                       |

| 4 | 4.1<br>4.2                                                                               | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1<br>4.3.2                                       | action                                                  | <ul> <li>64</li> <li>65</li> <li>65</li> <li>67</li> <li>71</li> <li>73</li> <li>73</li> </ul>                         |

| 4 | 4.1<br>4.2                                                                               | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                     | action                                                  | <ul> <li>64</li> <li>65</li> <li>67</li> <li>71</li> <li>73</li> <li>73</li> <li>77</li> </ul>                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                            | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Archite          | action                                                  | <ul> <li>64</li> <li>65</li> <li>65</li> <li>67</li> <li>71</li> <li>73</li> <li>73</li> <li>77</li> <li>78</li> </ul> |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>              | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Archite<br>Summa | action                                                  | 64<br>65<br>67<br>71<br>73<br>73<br>77<br>78<br>85<br>86                                                               |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>Emb</li> </ul> | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Archite<br>Summa | action                                                  | 64<br>65<br>67<br>71<br>73<br>73<br>77<br>78<br>85<br>86                                                               |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>Emb</li> </ul> | Introdu<br>JPEG2<br>4.2.1<br>4.2.2<br>Propos<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Archite<br>Summa | action                                                  | 64<br>65<br>65<br>67<br>71<br>73<br>73<br>73<br>77<br>78<br>85<br>86                                                   |

|   |     | 5.2.1   | Symmetric Extension                                                  | 90  |

|---|-----|---------|----------------------------------------------------------------------|-----|

|   |     | 5.2.2   | JPEG2000 5/3 Data Extension                                          | 90  |

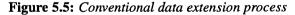

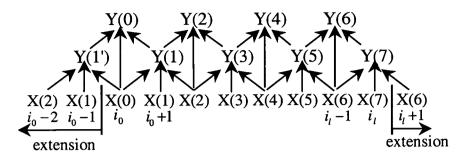

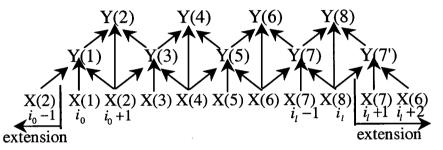

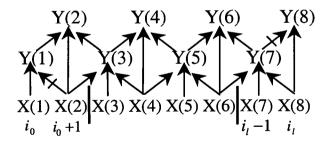

|   |     | 5.2.3   | Conventional Implementation of JPEG2000's Data Extension             | 91  |

|   | 5.3 | Embeo   | dded Data Extension Algorithm                                        | 92  |

|   | 5.4 | Power   | Analysis of Embedded Extension Algorithm                             | 95  |

|   |     | 5.4.1   | Power Consumption of Explicit Data Extension's Hardware              | 96  |

|   |     | 5.4.2   | Analytical Results                                                   | 99  |

|   |     | 5.4.3   | Discussion                                                           | 101 |

|   | 5.5 | Summ    | ary                                                                  | 101 |

| 6 | Pow | er Anal | lysis of Shifter-Accumulator Arithmetic Logic Unit Centric Processor | 103 |

|   | 6.1 | Introdu | uction                                                               | 103 |

|   | 6.2 | Proces  | sor Architecture                                                     | 104 |

|   |     | 6.2.1   | Pipelined Data-path Centric Processor Architecture                   | 104 |

|   |     | 6.2.2   | Area Consumption of Processors                                       | 107 |

|   | 6.3 | Power   | Analysis                                                             | 108 |

|   |     | 6.3.1   | Power Evaluation                                                     | 108 |

|   |     | 6.3.2   | Analysis                                                             | 116 |

|   | 6.4 | Discus  | sion                                                                 | 124 |

|   |     | 6.4.1   | New Criteria for Power Evaluation                                    | 125 |

|   |     | 6.4.2   | Better Low Power Design with Better Power Evaluation                 | 126 |

|   | 6.5 | Summ    | ary                                                                  | 130 |

| 7 | Low | Power   | Multi-Segment One Hot Addressing                                     | 132 |

|   | 7.1 | Introdu | uction                                                               | 132 |

|   | 7.2 | Sequer  | ntially Addressed Memory                                             | 133 |

|   |     | 7.2.1   | Conventional Sequential Addressing Hardware                          | 133 |

|   |     | 7.2.2   | One-Hot Addressing Architecture                                      | 134 |

|   | 7.3 | Multi-S | Segment Multi-Level OHA (MSML-OHA)                                   | 137 |

|   |     | 7.3.1   | Double-Segment Double-Level OHA (DSDL-OHA)                           | 137 |

|   |     | 7.3.2   | Triple-Segment Double-Level OHA (TSDL-OHA)                           | 141 |

|   |     | 7.3.3   | Triple-Segment Triple-Level OHA (TSTL-OHA)                           | 143 |

|   |     | 7.3.4   | Dyadic Multi-Segment Multi-Level OHA (DMSML-OHA)                     | 146 |

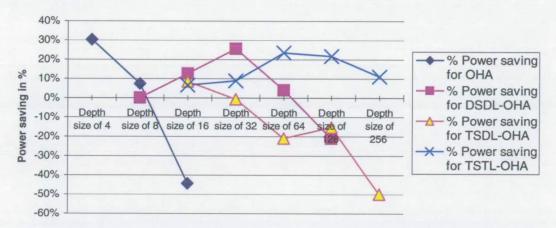

|   | 7.4 | Power   | Evaluation Results                                                   | 147 |

•

|    |       | 7.4.1   | ОНА                                     | 148 |

|----|-------|---------|-----------------------------------------|-----|

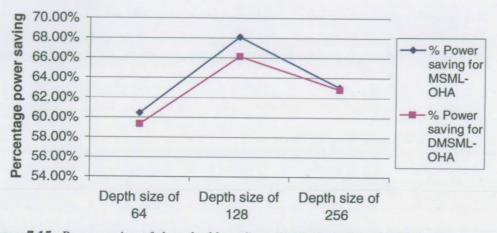

|    |       | 7.4.2   | Multi-Segment Multi-Level OHA           | 149 |

|    |       | 7.4.3   | Dyadic Multi-Segment Multi-level OHA    | 152 |

|    |       | 7.4.4   | Summary                                 | 153 |

|    | 7.5   | Discus  | ssion                                   | 154 |

|    | 7.6   | Summ    | ary                                     | 155 |

| 8  | Sum   | mary a  | and Conclusion                          | 157 |

|    | 8.1   | Introdu | uction                                  | 157 |

|    | 8.2   | Conclu  | usions                                  | 157 |

|    | 8.3   | Achiev  | vements                                 | 160 |

|    | 8.4   | Future  | Work                                    | 161 |

|    | 8.5   | Final C | Comments                                | 162 |

| Ą  | Eucl  | idean A | Algorithm                               | 163 |

| B  | Pseu  | do-Asso | emble Code for Row and Column Processor | 165 |

| С  | FSM   | l Mappi | ing Process                             | 171 |

| D  | Test  | Images  |                                         | 172 |

| Re | feren | ces     |                                         | 174 |

•

# List of figures

٠

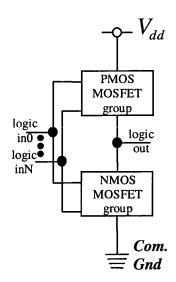

| 2.1 | Generic make-up of a CMOS logic gate circuit                                     | 8  |

|-----|----------------------------------------------------------------------------------|----|

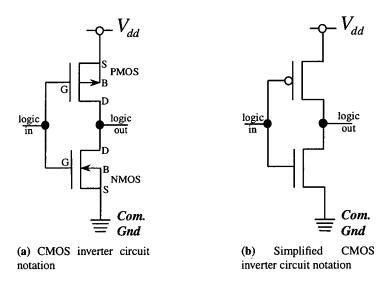

| 2.2 | Diagrams of CMOS inverter circuit                                                | 9  |

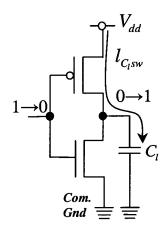

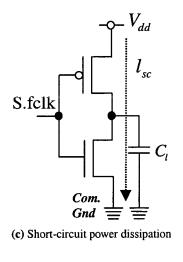

| 2.3 | Diagrams of CMOS inverter circuit power dissipation                              | 10 |

| 2.4 | Voltage values at the terminals of a turned-off NMOS                             | 12 |

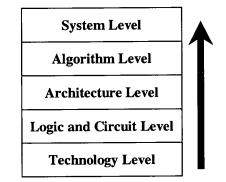

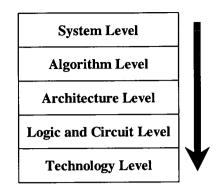

| 2.5 | Power reduction design abstraction hierarchy                                     | 18 |

| 2.6 | Bottom-up design flow approach                                                   | 30 |

| 2.7 | Top-down design flow approach                                                    | 31 |

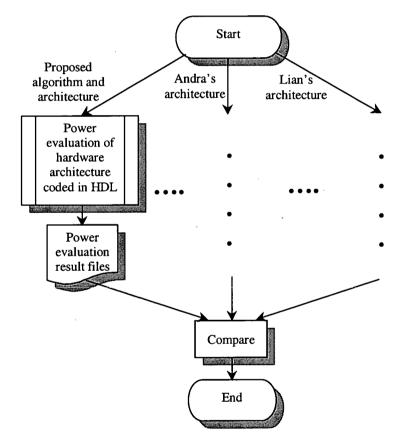

| 2.8 | Flowchart for power evaluation of different algorithm and architecture           | 33 |

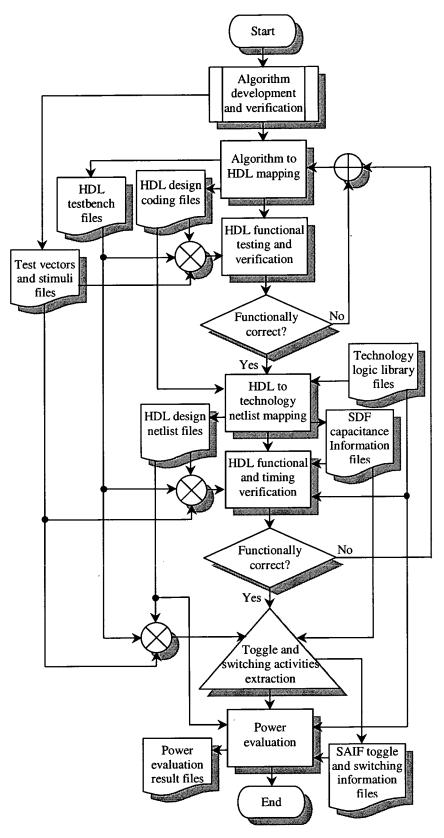

| 2.9 | Flowchart of the system hardware implementation and coding                       | 35 |

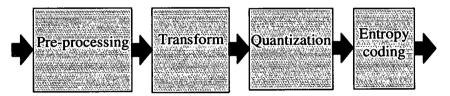

| 3.1 | Generic image compression core process blocks (Modified from [1])                | 41 |

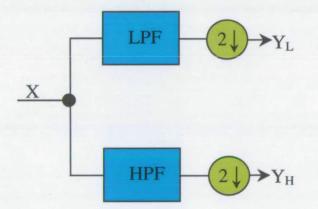

| 3.2 | Two bands (low and high band) sub-band coding structure                          | 44 |

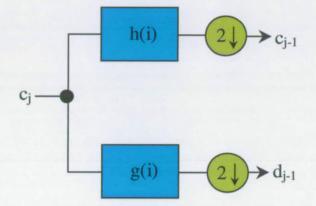

| 3.3 | One stage of the iterated filter bank structure of wavelet transform             | 49 |

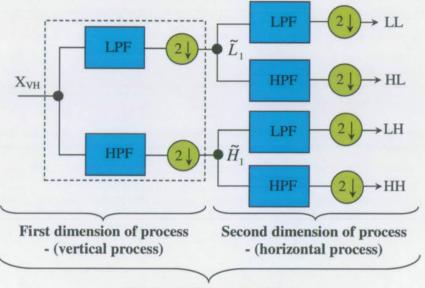

| 3.4 | Conventional convolution-based two-dimensional DWT process flow                  | 50 |

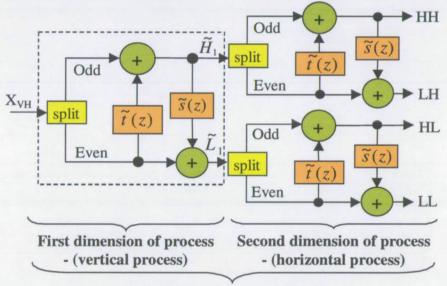

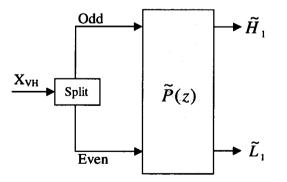

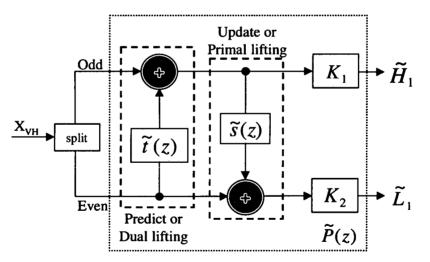

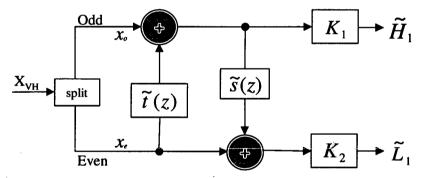

| 3.5 | Lifting-based two-dimensional DWT process flow                                   | 51 |

| 3.6 | Discrete Wavelet Transform using polyphase matrix                                | 53 |

| 3.7 | Lifting-based DWT diagram                                                        | 54 |

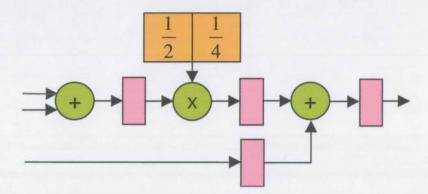

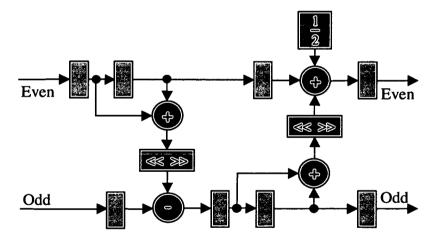

| 3.8 | Lifting-based DWT implementation diagram                                         | 57 |

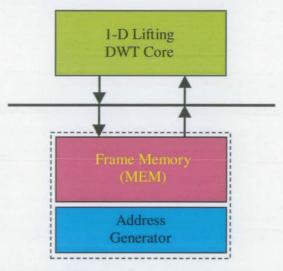

| 4.1 | Simplified Andra's lifting based 5/3 DWT processor architecture modified         |    |

|     | from [2]                                                                         | 68 |

| 4.2 | Andra's lifting based DWT overall architecture block diagram [2]                 | 69 |

| 4.3 | Andra's JPEG2000 lifting based DWT overall dataflow diagram modified from [2]    | 69 |

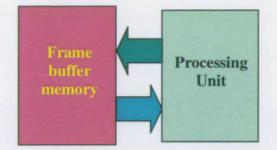

| 4.4 | Simplified Lian's lifting based 5/3 DWT processor architecture modified from [3] | 70 |

| 4.5 | Simplified Lian's JPEG2000 lifting based DWT overall architecture block          |    |

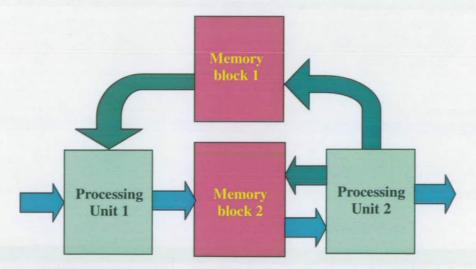

|     | diagram modified from [3]                                                        | 70 |

| 4.6 | Lian's JPEG2000 lifting based DWT overall dataflow diagram                       | 71 |

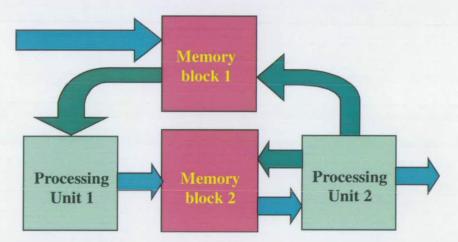

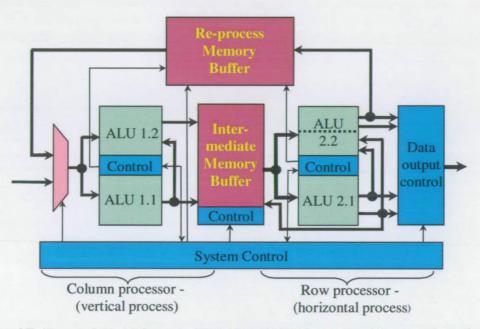

| 4.7 | Proposed SA-ALU centric JPEG2000 5/3 DWT overall architecture block              |    |

|     | diagram                                                                          | 72 |

| 4.8 | Proposed SA-ALU centric JPEG2000 5/3 DWT overall dataflow diagram                | 72 |

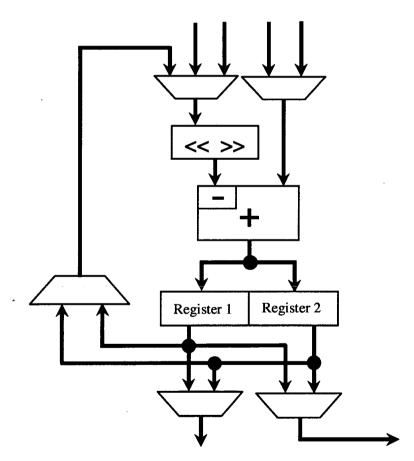

| 4.9  | Simplified SA-ALU architecture                                                         | 74       |

|------|----------------------------------------------------------------------------------------|----------|

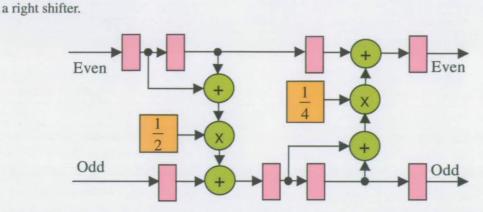

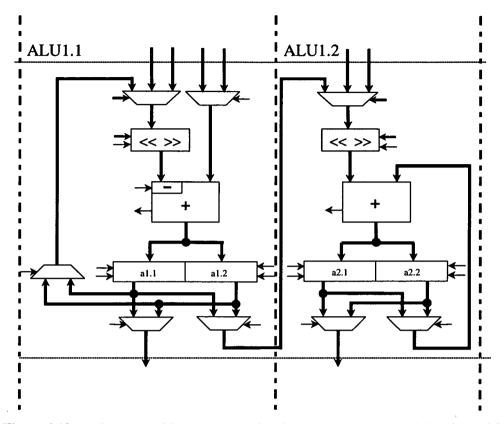

| 4.10 | Architecture of SA-ALU vertical (column) processor - ALU1.1 and ALU1.2                 | 76       |

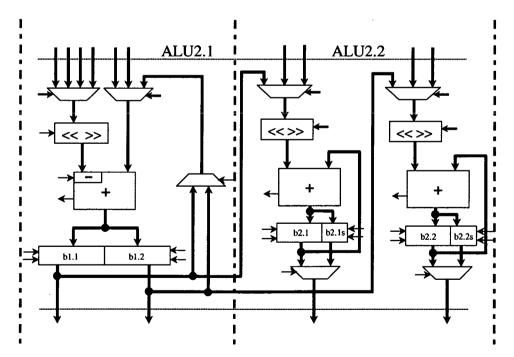

| 4.11 | Architecture of SA-ALU horizontal (row) processor - ALU2.1 and ALU2.2 $\ . \ .$        | 76       |

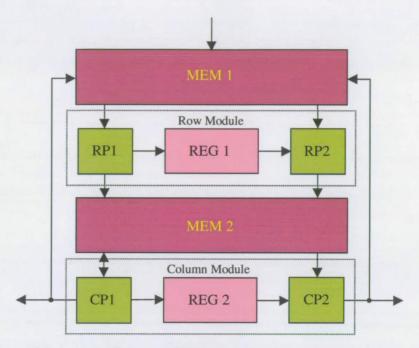

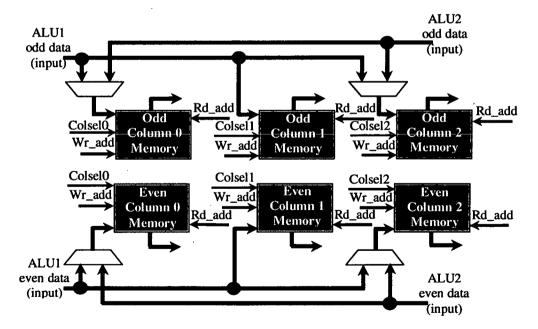

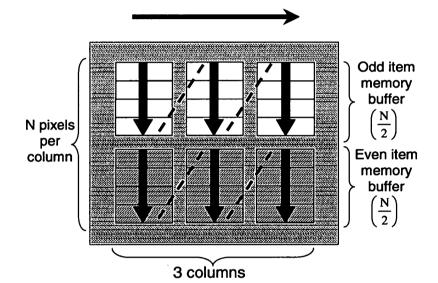

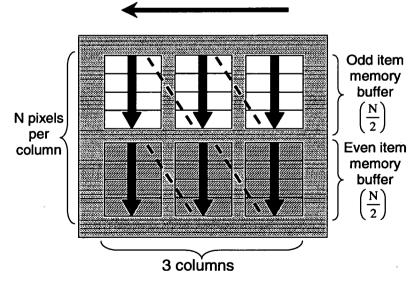

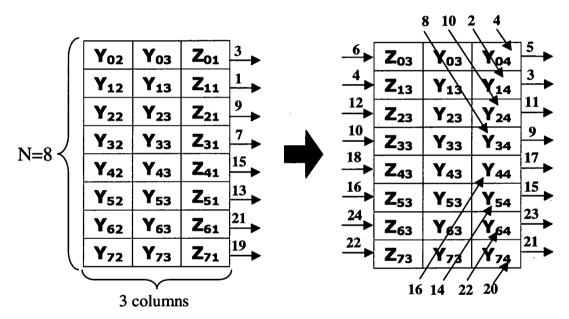

| 4.12 | SA-ALU architecture's intermediate memory (INMEM) structure                            | 77       |

| 4.13 | Pseudo-instruction code of the column and row processor (both in Normal                |          |

|      | process) for system scheduling                                                         | 79       |

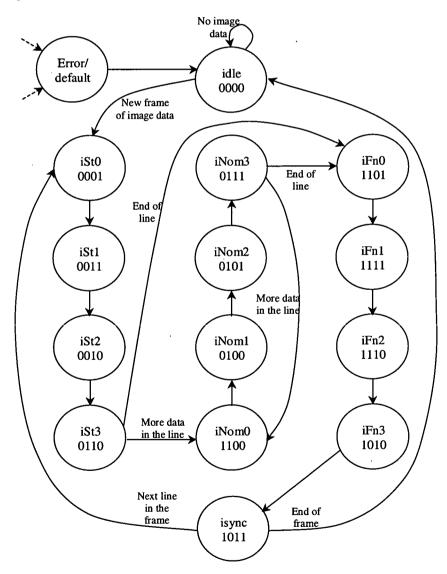

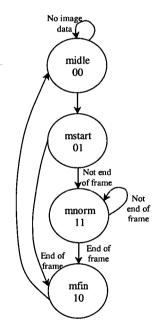

| 4.14 | FSM states transition diagram of Vertical (Column) processor                           | 80       |

| 4.15 | FSM states transition diagram of Horizontal (Row) processor                            | 81       |

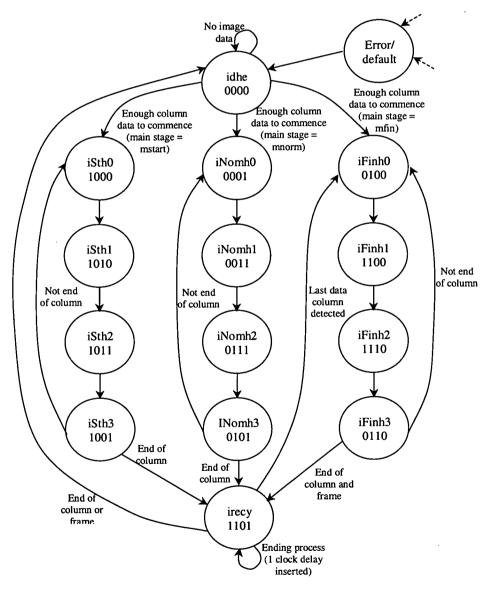

| 4.16 | Main states transition diagram of Horizontal (Row) processor state register            | 82       |

| 4.17 | INMEM write access from left to right                                                  | 83       |

| 4.18 | INMEM write access from right to left                                                  | 83       |

| 4.19 | Tandem write-read-write access sequence of INMEM                                       | 84       |

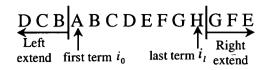

| 5.1  | Original input data complex                                                            | 90       |

|      | Original input data samples                                                            |          |

| 5.2  | Half sample (HS) extension                                                             | 90       |

| 5.3  | Whole sample (WS) extension                                                            | 90<br>01 |

| 5.4  | JPEG2000's symmetric data extension                                                    | 91<br>01 |

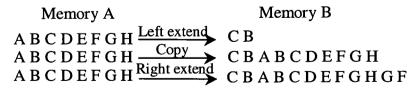

| 5.5  | Conventional data extension process                                                    | 91       |

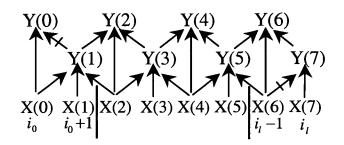

| 5.6  | Data dependence graph of JPEG2000's 5/3 DWT data extension with even                   | 02       |

| c =  | numbered start term and odd numbered ending term                                       | 93       |

| 5.7  | Data dependence graph of JPEG2000's 5/3 DWT data extension with odd                    |          |

|      | numbered start term and even numbered ending term                                      | 93       |

| 5.8  | Data dependence graph of JPEG2000's 5/3 DWT embedded data extension with               |          |

|      | odd numbered start term and even numbered ending term                                  | 93       |

| 5.9  | Data dependence graph of JPEG2000's 5/3 DWT embedded data extension with               |          |

|      | even numbered start term and odd numbered ending term                                  | 94       |

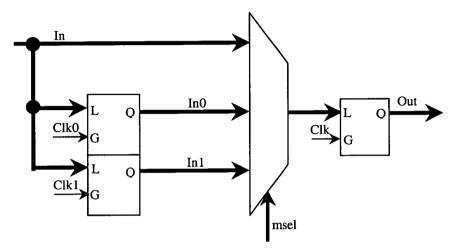

|      | Explicit data extension hardware                                                       | 96       |

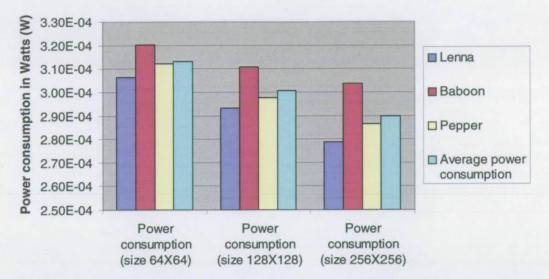

| 5.11 | Graph of explicit data extension power consumption of test image Lenna,                |          |

|      | Baboon, Pepper at image size of $64 \times 64$ , $128 \times 128$ and $256 \times 256$ | 98       |

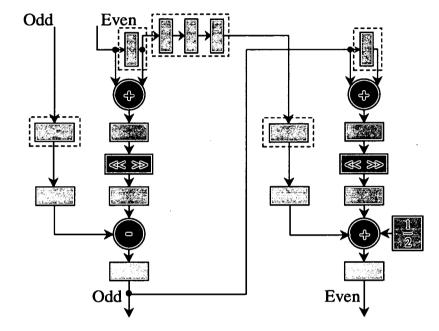

| 6.1  | Simplified and modified 1-D Andra's lifting based 5/3 DWT processor                    |          |

|      | architecture for both odd and even term                                                | 105      |

| 6.2  | Simplified and modified 1-D Lian's lifting based 5/3 DWT processor                     |          |

|      | architecture for both odd and even term                                                | 106      |

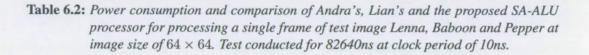

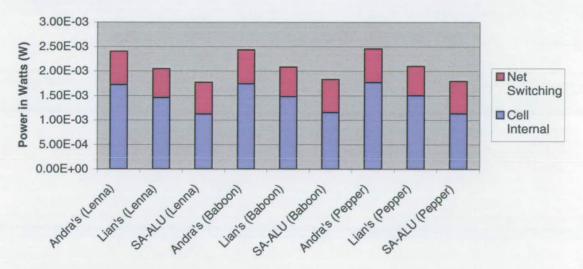

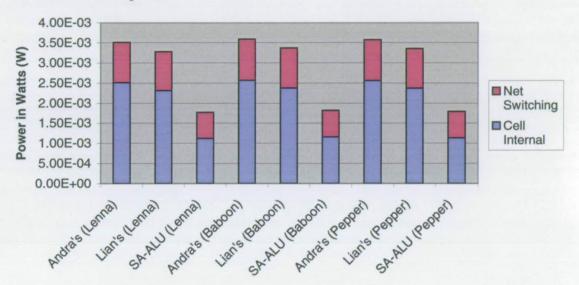

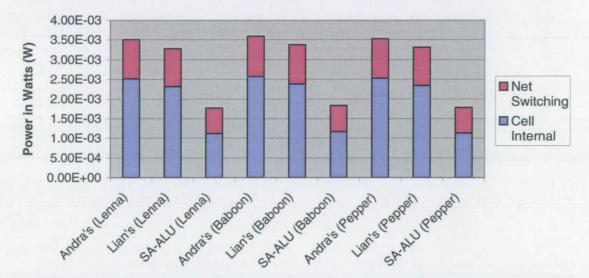

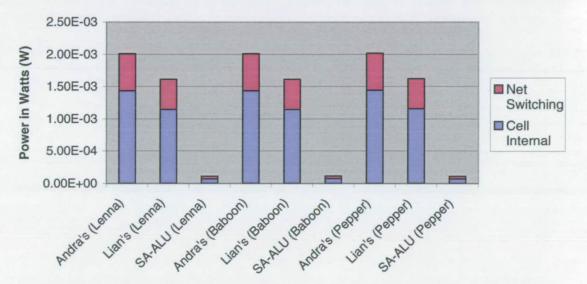

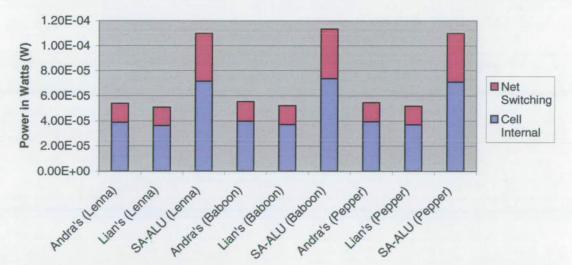

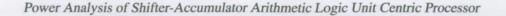

| 6.3 | Power consumption graph of Andra's, Lian's and the proposed SA-ALU                         |

|-----|--------------------------------------------------------------------------------------------|

|     | processor for processing a single frame of test image Lenna, Baboon and                    |

|     | Pepper at image size of $64 \times 64$ for duration of 82640ns at clock period of 10ns 110 |

6.5 Power consumption graph of Andra's, Lian's and the proposed SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper at image size of  $64 \times 64$  at actual process completion time with clock period of 10ns . . 114

6.6 Power consumption graph of Andra's, Lian's and the proposed SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper at image size of  $128 \times 128$  at actual process completion time with clock period of 10ns . 115

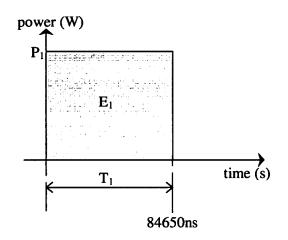

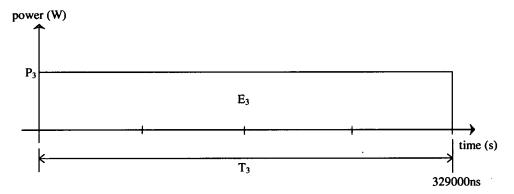

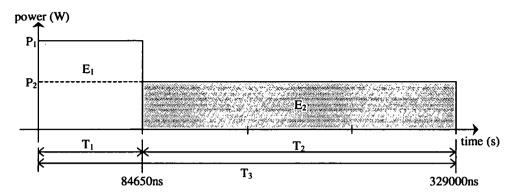

- 6.7 Graphical representation of the average power consumed by Andra's processor for processing an 128 × 128 image at its process completion time of 84650ns at clock period of 10ns

- 6.8 Graphical representation of the average power consumed by Andra's processor for processing an 128 × 128 image after 329000ns at clock period of 10ns . . . 117

- 6.9 Graphical representation of the power consumption profile of Andra's processor for processing an  $128 \times 128$  image after 329000ns at clock period of 10ns.  $E_1 + E_2$  is total energy consumed.  $P_1$  is 3.52mW.  $T_1$  is the Andra's processor process completion time of 84650ns.  $E_1$  is the energy associated with  $P_1$ .  $P_2$ is the power consumed for the remaining time  $T_2$  after the process completion time.  $E_2$  is the energy associated with  $P_2$ . The value for  $P_2$  is 1.85mW. . . . . 118

- 6.10 Power consumption graph of Andra's, Lian's and the proposed SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper at image size of 128 × 128 for duration of 5.5555ms at clock period of 10ns . . . . . . 121

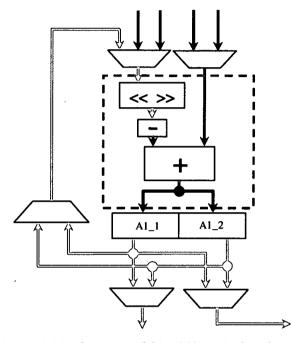

- 6.11 Switching activities hot-zone of SA-ALU vertical (column) processor ALUA1 123

- 6.12 Power consumption break-down of SA-ALU vertical (column) ALUA1 processor124

- 6.13 Power consumption graph of Andra's, Lian's and the proposed SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper at image size of 128 × 128 with clock gating for duration of 5.5555ms at clock period of 10ns

| 6.14 | Power consumption graph of Andra's, Lian's and proposed SA-ALU processor        |

|------|---------------------------------------------------------------------------------|

|      | for a single frame of test image Lenna, Baboon and Pepper at image size of      |

|      | $128 \times 128$ for duration of 329000ns at clock period of 38.8457ns for both |

|      | Andra's and Lian's processor and at clock period of 10ns for proposed SA-ALU    |

|      | processor                                                                       |

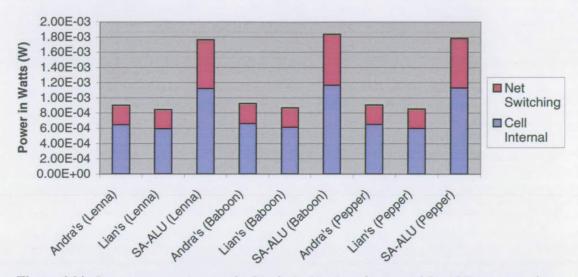

| 7.1  | Conventional counter-decoder (CCD) architecture                                 |

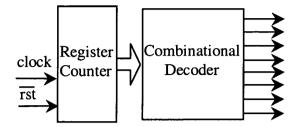

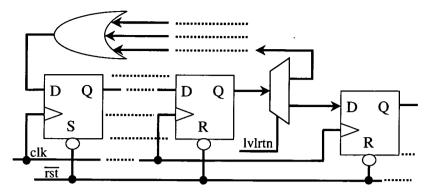

| 7.2  | One-hot shift-register                                                          |

| 7.3  | Verilog code of an equivalent OHA                                               |

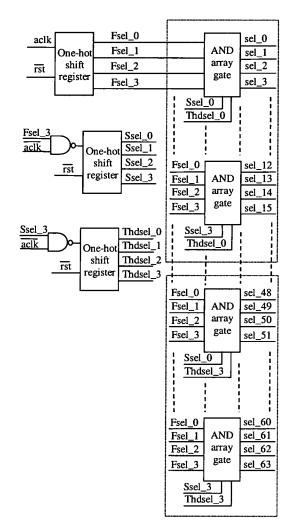

| 7.4  | DSDL-OHA 4x4 architecture                                                       |

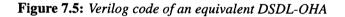

| 7.5  | Verilog code of an equivalent DSDL-OHA                                          |

| 7.6  | AND gate array                                                                  |

| 7.7  | Verilog code of an equivalent 2-input AND gate array                            |

| 7.8  | TSDL-OHA 4x4x4 architecture                                                     |

| 7.9  | Verilog code of an equivalent TSDL-OHA                                          |

| 7.10 | TSTL-OHA 4x4x4 architecture                                                     |

| 7.11 | Verilog code of an equivalent TSTL-OHA                                          |

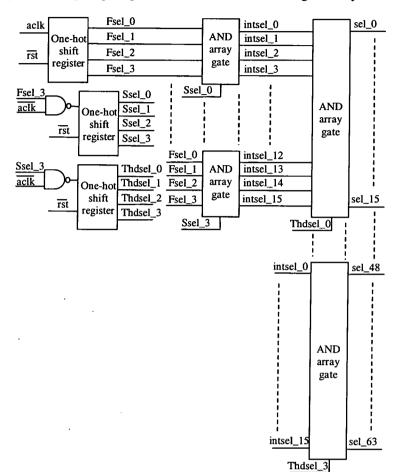

| 7.12 | Dyadic MSML-OHA (DMSML-OHA)                                                     |

| 7.13 | Dyadic 'turn around' logic                                                      |

| 7.14 | Best case power saving (with respect to CCD) at different depth size 153        |

| 7.15 | Power saving of shared address lines DMSML-OHA and MSML-OHA                     |

|      | compared to CCD at address depth size of 64, 128 and 256                        |

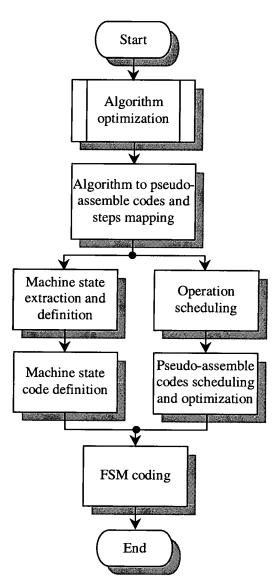

| C.1  | FSM mapping flowchart                                                           |

| D.1  | Test image 'Lenna'                                                              |

| D.2  | Test image 'Baboon'                                                             |

| D.3  | Test image 'Pepper'                                                             |

.

xiii

## List of tables

| 4.1 | 5/3 DWT tap coefficient value                                                                  |

|-----|------------------------------------------------------------------------------------------------|

| 4.2 | Data-path arithmetic hardware comparison table                                                 |

| 5.1 | Number of extension terms both even and odd starting and ending term                           |

| J.1 |                                                                                                |

|     | specified by JPEG2000 standard 91                                                              |

| 5.2 | Power consumption table of the explicit data extension's data-path hardware 97                 |

| 5.3 | Power consumption table of the control logic of explicit data extension                        |

|     | hardware at image size of $64 \times 64$ , $128 \times 128$ and $256 \times 256$               |

| 5.4 | Area requirement table of explicit data extension hardware at image size of                    |

|     | $64 \times 64, 128 \times 128$ and $256 \times 256 \dots 99$                                   |

| 5.5 | Analytical result of memory and operation usage and saving at per line                         |

|     | extension process basis                                                                        |

| 6.1 | Area consumption table of Andra's, Lian's and proposed SA-ALU column                           |

|     | processor                                                                                      |

| 6.2 | Power consumption and comparison of Andra's, Lian's and the proposed                           |

|     | SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper                     |

|     | at image size of $64 \times 64$ for duration of 82640ns at clock period of 10ns 110            |

| 6.3 | Power consumption and comparison of Andra's, Lian's and the proposed                           |

|     | SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper                     |

|     | at image size of $128 \times 128$ for duration of 329000ns at clock period of 10ns 111         |

| 6.4 | Process completion time Andra's, Lian's and the proposed SA-ALU processor                      |

|     | for a single frame of test image at image size of $64 \times 64$ and $128 \times 128$ at clock |

|     | period of 10ns                                                                                 |

| 6.5 | Power consumption and comparison of Andra's, Lian's and the proposed                           |

|     | SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper                     |

|     | at image size of $64 \times 64$ at actual process completion time with clock period            |

|     | of 10ns                                                                                        |

|     |                                                                                                |

·

-

| 6.6  | Power consumption and comparison of Andra's, Lian's and the proposed                      |

|------|-------------------------------------------------------------------------------------------|

|      | SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper                |

|      | at image size of $128 \times 128$ at actual process completion time with clock period     |

|      | of 10ns                                                                                   |

| 6.7  | The idle period power consumption $(P_2)$ of Andra's, Lian's and the proposed             |

|      | SA-ALU processor with null input value for an evaluation duration of 329000ns             |

|      | at clock period of 10ns                                                                   |

| 6.8  | Power consumption and comparison of Andra's, Lian's and the proposed                      |

|      | SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper                |

|      | at image size of $128 \times 128$ for duration of 5.5555ms at clock period of 10ns 121    |

| 6.9  | Power consumption and comparison of Andra's, Lian's and the proposed                      |

|      | SA-ALU processor for a single frame of test image Lenna, Baboon and Pepper                |

|      | at image size of $128 \times 128$ with clock gating for duration of 5.5555ms at clock     |

|      | period of 10ns                                                                            |

| 6.10 | Power consumption and comparison of Andra's, Lian's and the proposed                      |

|      | SA-ALU processor for a single frame of test image Lenna, Baboon and                       |

|      | Pepper at image size of $128 \times 128$ for duration of 329000ns at clock period of      |

|      | 38.8457ns for both Andra's and Lian's processor and at clock period of 10ns               |

|      | for the proposed SA-ALU processor                                                         |

| 7.1  | Output of OHA versus number of clock tick                                                 |

| 7.2  | Dyadic decoder's output with respect to the dyadic level and clock signal $\ldots$ 146    |

| 7.3  | Power evaluation results of OHA                                                           |

| 7.4  | Power evaluation results of multi-segment OHA at depth size of 8, 16 and 32 $$ . 149      |

| 7.5  | Power evaluation results of multi-segment OHA at depth size of 64 and 128 $\ . \ . \ 150$ |

| 7.6  | Power evaluation results of multi-segment OHA at depth size of 256 $\ldots$ 151           |

| 7.7  | Power evaluation results of dyadic multi-Segment OHA at depth size of 64, 128             |

|      | and 256                                                                                   |

| 7.8  | Power consumption of AND gate compared with D-type flip-flop 155                          |

| B.1  | Pseudo-Assemble code of Start, Normal and End process of the Vertical                     |

|      | Processor when Horizontal Processor is at Start process                                   |

| B.2  | Pseudo-Assemble code of Start, Normal and End process of the Vertical                     |

|      | Processor when Horizontal Processor is at Normal process                                  |

•.

# Acronyms and abbreviations

| 1-D       | One-Dimensional                                                 |

|-----------|-----------------------------------------------------------------|

| 2-D       | Two-Dimensional                                                 |

| ABITS     | Advance Bus-invert/Transition Signalling Coding                 |

| ADCVSL    | Adiabatic Differential Cascode Voltage Switch Logic             |

| ALU       | Arithmetic Logic Unit                                           |

| AVC       | Advance Video Coding                                            |

| BITS      | Bus-invert/Transition Signalling Coding                         |

| CAD       | Computer Aided Design                                           |

| CCD       | Conventional Counter-decoder                                    |

| CGC       | Control Generated Clocks                                        |

| CPL       | Complementary Pass-gate Logic                                   |

| CMOS      | Complementary Metal Oxide Semiconductor                         |

| COM       | (Electrical) Common                                             |

| CWT       | Continuous Wavelet Transform                                    |

| DCT       | Discrete Cosine Transform                                       |

| DFT       | Discrete Fourier Transform                                      |

| DG-MOSFET | Double Gate Metal Oxide Semiconductor Field-Effect Transistor   |

| DG-SOI    | Double Gate Silicon On Insulator                                |

| DPCM      | Differential Pulse Code Modulation                              |

| DSDL-OHA  | Double-Segment Double-Level One-Hot Addressing Architecture     |

| DSP       | Digital Signal Processor                                        |

| DTMOS     | Dynamic-threshold MOSFET                                        |

| DMSML-OHA | Dyadic Structured Multi-Segments Multi-Level One-Hot Addressing |

|           | Architecture                                                    |

| DVD       | Digital Versatile Discs                                         |

| DWT       | Discrete Wavelet Transform                                      |

| EMC       | Electromagnetic Compatibility                                   |

| ES        | Elementary Stream                                               |

| FDCT      | Fast Discrete Cosine Transform                                  |

|           |                                                                 |

.

| FET    | Field-Effect Transistor                                           |

|--------|-------------------------------------------------------------------|

| FIFO   | First In First Out                                                |

| FinFET | Fin Field-Effect Transistor                                       |

| FIR    | Finite Impulse Response                                           |

| FSM    | Finite State Machine                                              |

| GALS   | Globally Asynchronous Locally Synchronous                         |

| GCD    | Greatest Common Divisor                                           |

| GND    | (Electrical) Ground                                               |

| HDL    | Hardware Description Language                                     |

| HFET   | Heterostructure Field-Effect Transistor                           |

| НН     | 2-D DWT High-High sub-band output                                 |

| HL     | 2-D DWT High-Low sub-band output                                  |

| HP     | High Pass                                                         |

| HPF    | High Pass Filter                                                  |

| HS     | Half Sample                                                       |

| IEC    | The International Electrotechnical Commission                     |

| INMEM  | Intermediate Memory                                               |

| IP     | Intellectual Property                                             |

| ISO    | International Organisation for Standardization                    |

| ITU    | The International Telecommunications Union                        |

| ITU-T  | The International Telecommunication Union, Telecommunication      |

|        | Standardization Sector                                            |

| ITRS03 | International Technology Roadmap for Semiconductors, 2003 Edition |

| KLT    | Karhunen-Loeve Transform                                          |

| JPEG   | Joint Photographic Experts Group                                  |

| LH     | 2-D DWT Low-High sub-band output                                  |

| LL     | 2-D DWT Low-Low sub-band output                                   |

| LP     | Low Pass                                                          |

| LOP    | Low Operating Power                                               |

| LPF    | Low Pass Filter                                                   |

| LSTP   | Low Standby Power                                                 |

| NMOS   | N-channel Metal Oxide Semiconductor Field-Effect Transistor       |

| NUDC   | Source-to-Drain Non-uniformly Doped Channel                       |

|        |                                                                   |

| MJ2      | Motion-JPEG2000                                                    |

|----------|--------------------------------------------------------------------|

| MMC      | Multi-Module Chip                                                  |

| MPEG     | Moving Picture Expert Group                                        |

| MOBILE   | Monostable-Bistable Transition Logic Element                       |

| MOP      | Million Operation                                                  |

| MOSFET   | Metal Oxide Semiconductor Field-Effect Transistor                  |

| MRA      | Multi-Resolution Analysis                                          |

| MSML-OHA | Multi-Segments Multi-Level One-Hot Addressing Architecture         |

| MSB      | Most Significant Bits                                              |

| OD       | Object Description                                                 |

| OHA      | One-Hot Addressing Architecture                                    |

| PC       | Personal Computer                                                  |

| PMOS     | P-channel Metal Oxide Semiconductor Field-Effect Transistor        |

| PDA      | Personal Digital Assistant                                         |

| RF       | Radio Frequency                                                    |

| RPMEM    | Re-process Memory                                                  |

| RTD      | Resonant Tunnel Diodes                                             |

| RTL      | Register Transfer Level                                            |

| SA-ALU   | Shift-Accumulator Arithmetic Logic Unit                            |

| SAIF     | Switching Activity Interchange Format                              |

| SCCMOS   | Super Cut-off Complementary Metal Oxide Semiconductor              |

| SDF      | Standard Delay Format                                              |

| SiGe     | Silicon Germanium                                                  |

| SOC      | System-On-a-Chip                                                   |

| SOI      | Silicon On Insulator                                               |

| TSDL-OHA | Triple-Segment Double-Level One-Hot Addressing Architecture        |

| TSTL-OHA | Triple-Segment Triple-Level One-Hot Addressing Architecture        |

| UTB-SOI  | Ultra-Thin Body Silicon On Insulator                               |

| VCD      | Video Compact Disc                                                 |

| VTCMOS   | Variable Threshold Voltage Complementary Metal Oxide Semiconductor |

| VQ       | Vector Quantisation                                                |

| WS       | Whole Sample                                                       |

|          |                                                                    |

.

~

·

## Nomenclature

| $C$ Electric charge unit (Coulomb) $C_l$ Load capacitance $C(n)$ l-D DCT boundary condition correcting factor $C(u)$ 2-D DCT row boundary condition correcting factor $C(v)$ 2-D DCT column boundary condition correcting factor $c_{j-1}(i)$ Present DWT level low pass output coefficients $D_n$ Electron diffusion coefficient $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DTT bl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DWT5/3_{256}$ Computational load of 2-D D/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ms with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ms with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with its clock period stretched from<br>iOns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $f_0$ Output coefficients of 2-D DCT $f_0$ The maxima of the square of the elementary signal in fourier domain                                                   | Α              | Electric current unit (Ampere)                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------|

| C(n)1-D DCT boundary condition correcting factorC(u)2-D DCT row boundary condition correcting factorC(v)2-D DCT column boundary condition correcting factorc_{j-1}(i)Present DWT level low pass output coefficientsc_j(m)Previous DWT level low pass output coefficientsDnElectron diffusion coefficientDCT cl256Computational load of 2-D DCT processing a 256 × 256 imageDVT5/3256Computational load of 2-D DCT processing a 256 × 256 imageDWT5/3256Computational load of 2-D DCT processing a 256 × 256 imagedj-1(i)Present DWT level high pass output coefficientsE00°Band-gap energy of a semiconductor at 0° KevinE1Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650nsE2Energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000nsEcgEnergy consumed by Andra's processor with clock gatingEpsaEnergy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000nsEcgEnergy consumed by Andra's processor with clock gatingEpsaEnergy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457nseNatural number (Value = 2.718281828)F(n)Output coefficients of 1-D DCTF(u, v)Output coefficients of 2-D DCT                                                                                                 | C              | Electric charge unit (Coulomb)                                                 |

| C(u)2-D DCT row boundary condition correcting factorC(v)2-D DCT column boundary condition correcting factorc_j-n(i)Present DWT level low pass output coefficientsc_j(m)Previous DWT level low pass output coefficientsDnElectron diffusion coefficientDCT cl256Computational load of 2-D DCT processing a 256 × 256 imageDCT cl2556Computational load of 2-D DCT processing a 256 × 256 imageDWT5/3256Computational load of 2-D DCT processing a 256 × 256 imageDWT5/3256Computational load of 2-D 5/3 DWT processing a 256 × 256 imagedj-n(i)Present DWT level high pass output coefficientsEooBand-gap energy of a semiconductor at 0° KevinE1Energy consumed by Andra's processor for processing a 128 × 128 imageat clock period of 10ns with process completion time of 84650nsE2Energy consumed by Andra's processor for processing a 128 × 128F2,gEnergy consumed by Andra's processor for processing a 128 × 128E2,gEnergy consumed by Andra's processor for processing a 128 × 128E2,gEnergy consumed by Andra's processor with clock gatingE2,gEnergy consumed by Andra's processor with clock period stretched from<br>image at clock period of 10ns with process completion time of 329000nsE1,gEnergy consumed by Andra's processor wi | $C_l$          | Load capacitance                                                               |

| $C(v)$ 2-D DCT column boundary condition correcting factor $c_{j-1}(i)$ Present DWT level low pass output coefficients $c_j(m)$ Previous DWT level low pass output coefficients $D_n$ Electron diffusion coefficient $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DWT5/3_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                               | C(n)           | 1-D DCT boundary condition correcting factor                                   |

| $c_{j-1}(i)$ Present DWT level low pass output coefficients $c_j(m)$ Previous DWT level low pass output coefficients $D_n$ Electron diffusion coefficient $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DCT cl_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $DWT5/3_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with clock gating $E_{sck}$ Energy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                           | C(u)           | 2-D DCT row boundary condition correcting factor                               |

| $c_j(m)$ Previous DWT level low pass output coefficients $D_n$ Electron diffusion coefficient $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DWT5/3_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor in idle period of 244350ns $E_3$ Average energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with its clock period stretched from<br>ins to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                                                         | C(v)           | 2-D DCT column boundary condition correcting factor                            |

| $D_n$ Electron diffusion coefficient $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image $DCT cl_{256}$ Computational load of 2-D DCT processing a 256 × 256 image<br>with 16 × 16 blocking $DWT5/3_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                                                                                                                                                                      | $c_{j-1}(i)$   | Present DWT level low pass output coefficients                                 |

| $DCTcl_{256}$ Computational load of 2-D DCT processing a $256 \times 256$ image $DCTclb_{256}$ Computational load of 2-D DCT processing a $256 \times 256$ image $DWT5/3_{256}$ Computational load of 2-D $5/3$ DWT processing a $256 \times 256$ image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at $0^o$ Kevin $E_1$ Energy consumed by Andra's processor for processing a $128 \times 128$ image<br>at clock period of 10ns with process completion time of $84650ns$ $E_2$ Energy consumed by Andra's processor for processing a $128 \times 128$<br>image at clock period of 10ns with process completion time of $329000ns$ $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor for processing a $128 \times 128$<br>image at clock period of 10ns with process completion time of $329000ns$ $E_{sck}$ Energy consumed by Andra's processor with clock gating $e_{sck}$ Energy consumed by Andra's processor with clock period stretched from<br>iOns to $38.8457ns$ $e$ Natural number (Value = $2.718281828)$ $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                            | $c_j(m)$       | Previous DWT level low pass output coefficients                                |

| $DCTclb_{256}$ Computational load of 2-D DCT processing a 256 × 256 image<br>with 16 × 16 blocking $DWT5/3_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor in idle period of 244350ns $E_3$ Average energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor for processing a 128<br>× 128 at clock period of 10ns with process completion time of 329000ns $E_{sck}$ Energy consumed by Andra's processor with clock gating $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                                                                                                                                                                  | $D_n$          | Electron diffusion coefficient                                                 |

| with $16 \times 16$ blockingDWT 5/3256Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor in idle period of 244350ns $E_3$ Average energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by Andra's processor for processing a 128<br>× 128 at clock period of 10ns with process completion time of 329000ns $E_{sck}$ Energy consumed by Andra's processor with clock gating $E_{sck}$ Energy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u,v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                                                                                                                                      | $DCTcl_{256}$  | Computational load of 2-D DCT processing a $256 \times 256$ image              |

| $DWT5/3_{256}$ Computational load of 2-D 5/3 DWT processing a 256 × 256 image $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor in idle period of 244350ns $E_3$ Average energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by the proposed SA-ALU processor for processing a 128<br>× 128 at clock period of 10ns with process completion time of 329000ns $E_{sck}$ Energy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u, v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $DCTclb_{256}$ | Computational load of 2-D DCT processing a $256 \times 256$ image              |

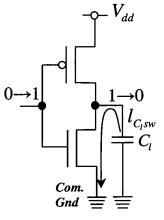

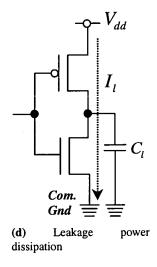

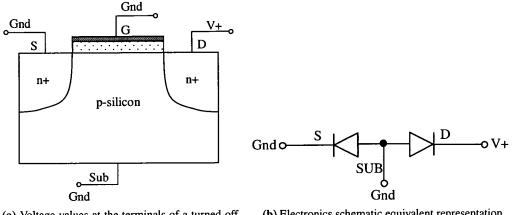

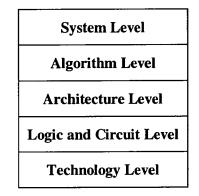

| $d_{j-1}(i)$ Present DWT level high pass output coefficients $E_{0^o}$ Band-gap energy of a semiconductor at 0° Kevin $E_1$ Energy consumed by Andra's processor for processing a 128 × 128 image<br>at clock period of 10ns with process completion time of 84650ns $E_2$ Energy consumed by Andra's processor in idle period of 244350ns $E_3$ Average energy consumed by Andra's processor for processing a 128 × 128<br>image at clock period of 10ns with process completion time of 329000ns $E_{cg}$ Energy consumed by Andra's processor with clock gating $E_{psa}$ Energy consumed by the proposed SA-ALU processor for processing a 128<br>× 128 at clock period of 10ns with process completion time of 329000ns $E_{sck}$ Energy consumed by Andra's processor with its clock period stretched from<br>10ns to 38.8457ns $e$ Natural number (Value = 2.718281828) $F(n)$ Output coefficients of 1-D DCT $F(u,v)$ Output coefficients of 2-D DCT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | with $16 \times 16$ blocking                                                   |