# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Instruction Scheduling Optimizations for Energy Efficient VLIW Processors

Vasileios Porpodas

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2013

#### Abstract

Very Long Instruction Word (VLIW) processors are wide-issue statically scheduled processors. Instruction scheduling for these processors is performed by the compiler and is therefore a critical factor for its operation. Some VLIWs are clustered, a design that improves scalability to higher issue widths while improving energy efficiency and frequency. Their design is based on physically partitioning the shared hardware resources (e.g., register file). Such designs further increase the challenges of instruction scheduling since the compiler has the additional tasks of deciding on the placement of the instructions to the corresponding clusters and orchestrating the data movements across clusters.

In this thesis we propose instruction scheduling optimizations for energy-efficient VLIW processors. Some of the techniques aim at improving the existing state-of-theart scheduling techniques, while others aim at using compiler techniques for closing the gap between lightweight hardware designs and more complex ones. Each of the proposed techniques target individual features of energy efficient VLIW architectures.

Our first technique, called Aligned Scheduling, makes use of a novel scheduling heuristic for hiding memory latencies in lightweight VLIW processors without hard-ware load-use interlocks (Stall-On-Miss). With Aligned Scheduling, a software-only technique, a SOM processor coupled with non-blocking caches can better cope with the cache latencies and it can perform closer to the heavyweight designs. Performance is improved by up to 20% across a range of benchmarks from the Mediabench II and SPEC CINT2000 benchmark suites.

The rest of the techniques target a class of VLIW processors known as clustered VLIWs, that are more scalable and more energy efficient and operate at higher frequencies than their monolithic counterparts.

The second scheme (LUCAS) is an improved scheduler for clustered VLIW processors that solves the problem of the existing state-of-the-art schedulers being very susceptible to the inter-cluster communication latency. The proposed unified clustering and scheduling technique is a hybrid scheme that performs instruction by instruction switching between the two state-of-the-art clustering heuristics, leading to better scheduling than either of them. It generates better performing code compared to the state-of-the-art for a wide range of inter-cluster latency values on the Mediabench II benchmarks.

The third technique (called CAeSaR) is a scheduler for clustered VLIW architectures that minimizes inter-cluster communication by local caching and reuse of already received data. Unlike dynamically scheduled processors, where this can be supported by the register renaming hardware, in VLIWs it has to be done by the code generator. The proposed instruction scheduler unifies cluster assignment, instruction scheduling and communication minimization in a single unified algorithm, solving the phase ordering issues between all three parts. The proposed scheduler shows an improvement in execution time of up to 20.3% and 13.8% on average across a range of benchmarks from the Mediabench II and SPEC CINT2000 benchmark suites.

The last technique, applies to heterogeneous clustered VLIWs that support dynamic voltage and frequency scaling (DVFS) independently per cluster. In these processors there are no hardware interlocks between clusters to honor the data dependencies. Instead, the scheduler has to be aware of the DVFS decisions to guarantee correct execution. Effectively controlling DVFS, to selectively decrease the frequency of clusters with slack in their schedule, can lead to significant energy savings. The proposed technique (called UCIFF) solves the phase ordering problem between frequency selection and scheduling that is present in existing algorithms. The results show that UCIFF produces better code than the state-of-the-art and very close to the optimal across the Mediabench II benchmarks.

Overall, the proposed instruction scheduling techniques lead to either better efficiency on existing designs or allow simpler lightweight designs to be competitive against ones with more complex hardware.

### Lay Summary of Thesis

Nowadays computing technology is more widespread than ever before. Many computers, in the form of consumer electronic devices, are mobile. People carry these computers on them as they aid them in their everyday life. Mobile devices have to be cheap, high performance and energy efficient so that they are affordable to everyone and they perform complex tasks without draining the battery. To achieve these goals, improvements have to be made across all levels of the stack starting from the program developer, the programming languages, the tools used to transform the programs into machine code (compiler tools), all the way down to the computer architecture and the low level hardware design.

This thesis focuses on improving the compiler tool, which stands between programs and computer architecture. The processors considered follow the Very Long Instruction Word (VLIW) design philosophy, which aims at lower hardware complexity at the cost of higher compiler (software) complexity. In more detail, any task that could be done efficiently off-line (in advance) by the the compiler tool, should be done by the tool (in software), not by the processor (in hardware). VLIW processors are in general: i) cheaper to build (by being less complex to design and requiring less hardware components) ii) as well performing as more complex designs and iii) more energy efficient. These benefits, however, require advanced compiler optimizations.

This thesis proposes new and improved optimizations for the compiler tool, to better support this class of high performance yet energy efficient processors. Our techniques let the compiler generate more efficient programs to run on these processors with benefits in performance or energy. The experimental evaluation of the proposed techniques shows that our techniques outperform the state-of-the-art.

#### Acknowledgements

I would like to thank my supervisor, Marcelo Cintra, for guiding me through my PhD and teaching me to stay focused and avoid chasing "crazy" ideas.

Living in "New Texas" (a.k.a. office 1.05, Informatics Forum) for the past 4 years, I met a good number of nice people. Many of them have been kind enough to help me with my work by explaining things to me, providing valuable feedback and giving me advice. Andrew J. McPherson, Chris Fensch, Christos Margiolas, George Stefanakis, George Tournavitis, Luis Fabricio Wanderley Goes, Karthik Thucanakkenpalayam Sundararajan, Kiran Chandramohan, Konstantina Mitropoulou, Vijay Nagarajan, Nikolas Ioannou, Polychronis Xekalakis, Zheng Wang, just to name a few.

I would finally like to thank my family and friends for their support.

## Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following papers:

- "UCIFF: Unified Cluster assignment Instruction scheduling and Fast Frequency selection for heterogeneous clustered VLIW cores"

Vasileios Porpodas, and Marcelo Cintra

International Workshop on Languages and Compilers for Parallel Computing (LCPC), 2012

- "LUCAS: Latency-adaptive Unified Cluster Assignment and instruction Scheduling"

Vasileios Porpodas, and Marcelo Cintra

Conference on Languages, Compilers and Tools for Embedded Systems (LCTES), 2013

- "CAeSaR: unified Cluster-Assignment Scheduling and communication Reuse for clustered VLIW processors"

Vasileios Porpodas, and Marcelo Cintra International Conference on Compilers Architecture and Synthesis for Embedded Systems (CASES), 2013

- "Aligned Scheduling: Cache-efficient Instruction Scheduling for VLIW Processors"

Vasileios Porpodas, and Marcelo Cintra

International Workshop on Languages and Compilers for Parallel Computing (LCPC), 2013

(Vasileios Porpodas)

# **Table of Contents**

| 1 | Intr | oduction                                                             | 1  |

|---|------|----------------------------------------------------------------------|----|

|   | 1.1  | Aligned Scheduling: Exploiting MLP to hide cache-miss latencies on   |    |

|   |      | VLIWs                                                                | 3  |

|   | 1.2  | Latency-adaptive Unified Clustering and Scheduling (LUCAS)           | 3  |

|   |      | 1.2.1 Clustered architectures                                        | 3  |

|   |      | 1.2.2 LUCAS                                                          | 5  |

|   | 1.3  | Cluster Assignment, Scheduling and Communication Reuse (CAeSaR)      | 5  |

|   | 1.4  | Unified Clustering, Scheduling and Fast-Frequency selection for Het- |    |

|   |      | erogeneous Clustered VLIW (UCIFF)                                    | 6  |

| 2 | Bac  | kground                                                              | 7  |

|   | 2.1  | VLIW Machine Model                                                   | 7  |

|   | 2.2  | Basic Terminology                                                    | 9  |

|   | 2.3  | Compiler Structure                                                   | 12 |

|   | 2.4  | Instruction Scheduling                                               | 13 |

|   | 2.5  | Scheduling Regions                                                   | 15 |

|   | 2.6  | Clustered VLIW Machine Model                                         | 17 |

|   | 2.7  | Heterogeneous Clustered VLIW                                         | 19 |

|   | 2.8  | Cluster Assignment                                                   | 20 |

|   | 2.9  | Load Scheduling                                                      | 24 |

| 3 | Alig | ned Scheduling                                                       | 27 |

|   | 3.1  | Introduction                                                         | 27 |

|   | 3.2  | Motivation                                                           | 30 |

|   |      | 3.2.1 Hoisting of Low-Priority Loads (HLPL)                          | 32 |

|   |      | 3.2.2 Lowering of Low-Priority Loads (LLPL)                          | 34 |

|   |      | 3.2.3 Discussion                                                     | 36 |

| 3.3         | Aligned Scheduling                                                                       |

|-------------|------------------------------------------------------------------------------------------|

|             | 3.3.1 Overview                                                                           |

|             | 3.3.2 Aligned Scheduling driver                                                          |

|             | 3.3.3 Aligned Scheduling selection                                                       |

|             | 3.3.4 Complexity Analysis and Comparison                                                 |

| 3.4         | Experimental Setup                                                                       |

| 3.5         | Results and Analysis                                                                     |

|             | 3.5.1 Case study: cjpeg                                                                  |

|             | 3.5.2 All benchmarks                                                                     |

| 3.6         | Conclusion                                                                               |

| 4 LU        | CAS 57                                                                                   |

| 4.1         | Introduction                                                                             |

| 4.2         | Motivation                                                                               |

|             | 4.2.1 Clustering Heuristics                                                              |

|             | 4.2.2 Scheduling                                                                         |

| 4.3         | LUCAS                                                                                    |

|             | 4.3.1 Algorithm                                                                          |

|             | 4.3.2 Algorithmic Complexity                                                             |

| 4.4         | Experimental Setup                                                                       |

|             | 4.4.1 Architecture                                                                       |

|             | 4.4.2 Compiler                                                                           |

|             | 4.4.3 Evaluation                                                                         |

| 4.5         | Results and Analysis                                                                     |

|             | 4.5.1 Performance                                                                        |

|             | 4.5.2 Instruction Distribution                                                           |

| 4.6         | Conclusion                                                                               |

| 5 CA        | eSaR 81                                                                                  |

| 5 CA<br>5.1 | Introduction                                                                             |

| 5.2         | Motivation         81           Motivation         85                                    |

| 5.2         | CAeSaR                                                                                   |

| 5.5         | 5.3.1       High Level Overview       89                                                 |

|             | 5.3.1       Inight Level Overview       89         5.3.2       CAeSaR Main Body       89 |

|             | 5.3.2       CAesar Main Body       89         5.3.3       Compute ICCs       91          |

|             | 1                                                                                        |

|             | 5.3.4 Clustering Heuristic                                                               |

|   |      | 5.3.5 ICC Reuse                           | 94 |

|---|------|-------------------------------------------|----|

|   |      | 5.3.6 Register File Coherence             | 95 |

|   |      | 5.3.7 ICC Reuse Across Scheduling Regions | 96 |

|   |      | 5.3.8 Complexity Analysis                 | 96 |

|   | 5.4  | Experimental Setup                        | 98 |

|   | 5.5  | Results and Analysis                      | 00 |

|   |      | 5.5.1 Overview                            | 00 |

|   |      | 5.5.2 ICC Overhead                        | 00 |

|   |      | 5.5.3 Performance                         | 03 |

|   |      | 5.5.4 Phase-ordering                      | 05 |

|   | 5.6  | Conclusion                                | 06 |

| 6 | UCI  | 7F 10                                     | 07 |

| U | 6.1  |                                           | 07 |

|   | 6.2  |                                           | 09 |

|   | 0.2  |                                           | 09 |

|   |      |                                           | 10 |

|   | 6.3  | -                                         | 10 |

|   |      |                                           | 12 |

|   |      |                                           | 13 |

|   |      |                                           | 21 |

|   |      |                                           | 22 |

|   | 6.4  | Experimental Setup                        | 24 |

|   | 6.5  | Results                                   | 25 |

|   |      | 6.5.1 Accuracy of Frequency Selection     | 26 |

|   |      | 6.5.2 UCIFF code quality                  | 27 |

|   |      | 6.5.3 UCIFF runtime                       | 29 |

|   | 6.6  | Conclusion                                | 30 |

| 7 | Pala | ted Work 13                               | 31 |

| , | 7.1  |                                           | 31 |

|   | 7.1  |                                           | 32 |

|   | 7.3  |                                           | 33 |

|   | 7.4  |                                           | 35 |

|   | 7.5  |                                           | 36 |

|   | 7.6  | -                                         | 37 |

|   |      | o                                         |    |

| 8 | Con | clusions | and Future Work                                     | 141 |

|---|-----|----------|-----------------------------------------------------|-----|

|   | 8.1 | Summa    | ary of Contributions                                | 141 |

|   | 8.2 | Future   | Work                                                | 142 |

|   |     | 8.2.1    | Unifying Register Allocation                        | 142 |

|   |     | 8.2.2    | Bigger Regions and Loop Scheduling                  | 143 |

|   |     | 8.2.3    | Hardware Reconfiguration and Scheduling at Run-Time | 144 |

|   |     |          |                                                     |     |

#### Bibliography

145

# **List of Figures**

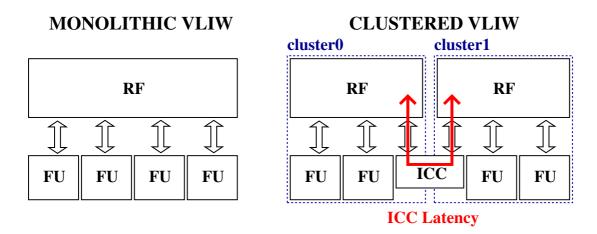

| A 2-cluster VLIW architecture. The red arrow shows the Inter-Cluster      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copy (ICC) Latency.                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

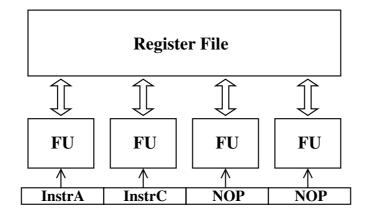

| The VLIW architecture                                                     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

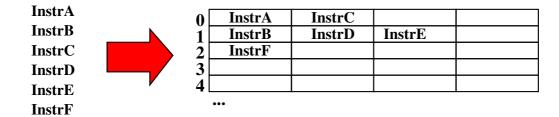

| Priority, ASAP, ALAP and Mobility. Each node in the DFG has a delay       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| of 1 cycle                                                                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

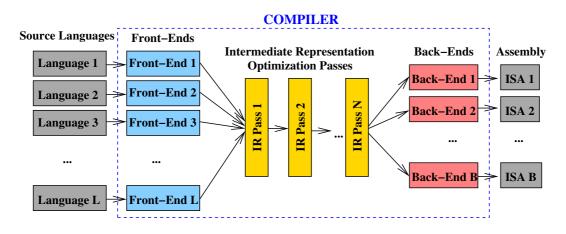

| A modern retargetable compiler                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Major target-specific passes.                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

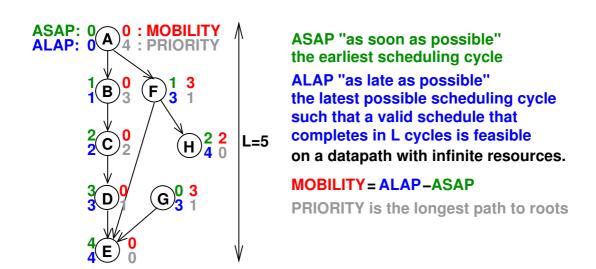

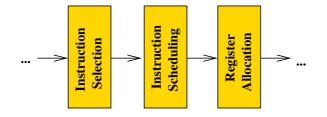

| A Data Flow Graph (DFG) with the nodes tagged with their priority.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| All instructions have a latency of 1 cycle (not shown)                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

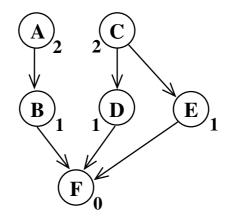

| Various scheduling regions on a CFG. The region is marked by the          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| dashed blue lines. The control edges are tagged with their % profile      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| probability and they are colored accordingly (red is high, black is low). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| The single-BB regions are not shown.                                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A Clustered VLIW architecture with 2 clusters                             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

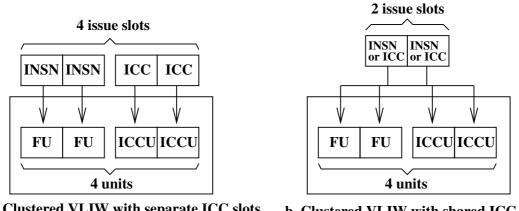

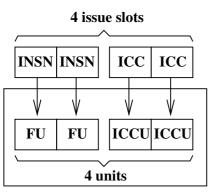

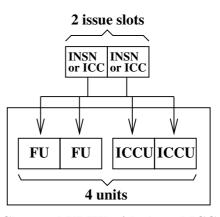

| Two different ways of treating ICC instructions.                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

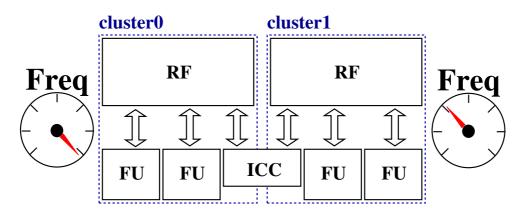

| A Heterogeneous Clustered VLIW architecture with 2 clusters. Cluster      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 operates at the maximum frequency, while cluster1 operates at $1/3$     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| of the maximum frequency.                                                 | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Heuristic values calculated on schedules                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

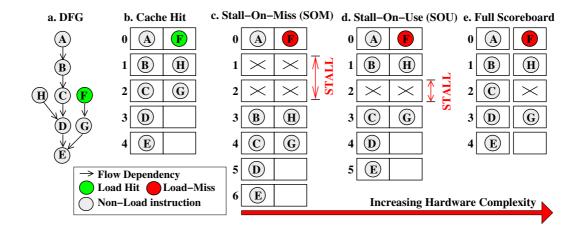

| Dynamic schedules on architectures with Load stall semantics of in-       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| creasing hardware complexity.                                             | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

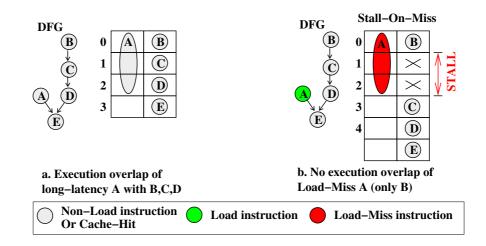

| The VLIW semantics of a regular long-latency instruction (a) versus a     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| cache-miss instruction (b) on a Stall-On-Miss architecture                | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

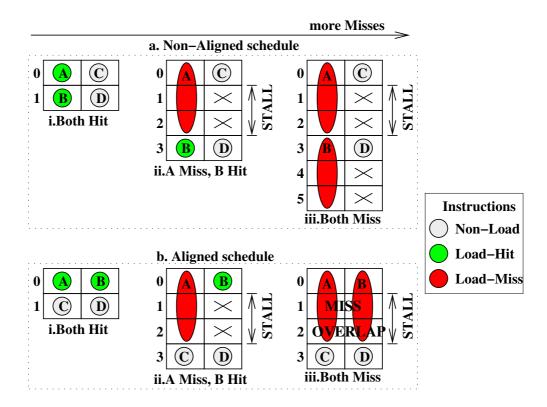

| Two different schedules (a) and (b) under increasing miss conditions.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Schedule (b) (Aligned) exhibits miss-overlapping under heavy miss         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| conditions (b.iii).                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                           | Copy (ICC) Latency.The VLIW architecture.Priority, ASAP, ALAP and Mobility. Each node in the DFG has a delayof 1 cycle.A modern retargetable compiler.Major target-specific passes.A Data Flow Graph (DFG) with the nodes tagged with their priority.All instructions have a latency of 1 cycle (not shown).Various scheduling regions on a CFG. The region is marked by thedashed blue lines. The control edges are tagged with their % profileprobability and they are colored accordingly (red is high, black is low).The single-BB regions are not shown.A Clustered VLIW architecture with 2 clusters.Two different ways of treating ICC instructions.A Heterogeneous Clustered VLIW architecture with 2 clusters. Cluster0 operates at the maximum frequency, while cluster1 operates at 1/3of the maximum frequency.Heuristic values calculated on schedules.Dynamic schedules on architectures with Load stall semantics of in-creasing hardware complexity.The VLIW semantics of a regular long-latency instruction (a) versus acache-miss instruction (b) on a Stall-On-Miss architecture.Two different schedules (a) and (b) under increasing miss conditions.Schedule (b) (Aligned) exhibits miss-overlapping under heavy miss |

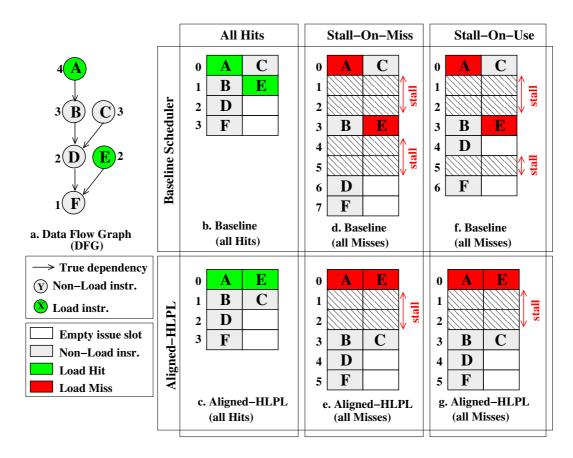

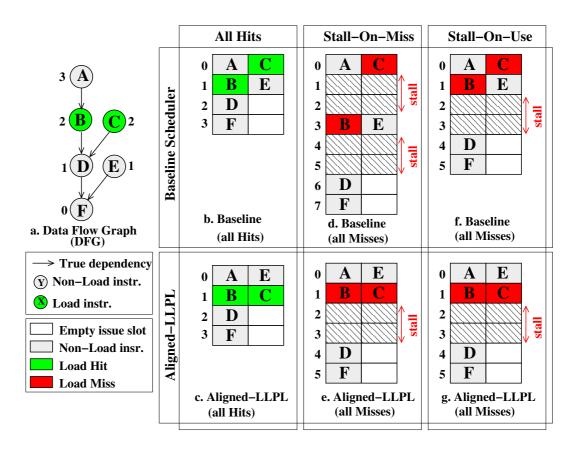

| 3.4  | The instruction schedule of the DFG (a), under baseline (b, d and f) and Aligned-HLPL Scheduling (c, e and g). The dynamic schedule in the event of two consecutive Load-misses on a Stall-On-Miss and a Stall-On-Use architecture is listed in (d and e) and (f and g) for the Baseline and Aligned-HLPL, respectively              | 33 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | The instruction schedule of the DFG (a), under baseline (b, d, and f)<br>and Aligned-LLPL Scheduling (c, e and g). The dynamic schedule<br>in the event of two consecutive Load-misses on a Stall-On-Miss and<br>a Stall-On-Use architecture is listed in (d and e) and (f and g) for the<br>Baseline and Aligned-LLPL respectively. | 35 |

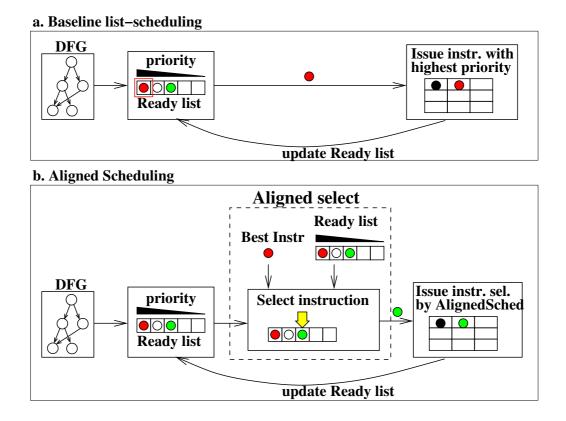

| 3.6  | Overview of scheduling algorithms.                                                                                                                                                                                                                                                                                                   | 37 |

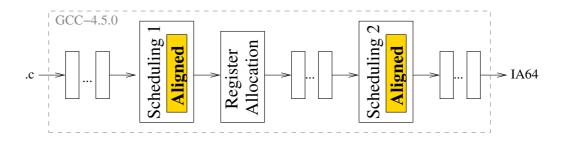

| 3.7  | The compilation flow.                                                                                                                                                                                                                                                                                                                | 45 |

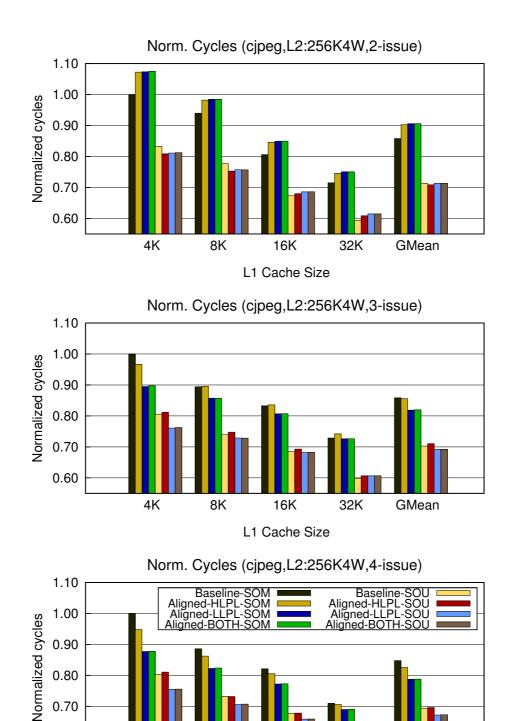

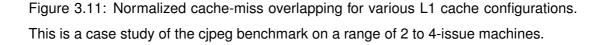

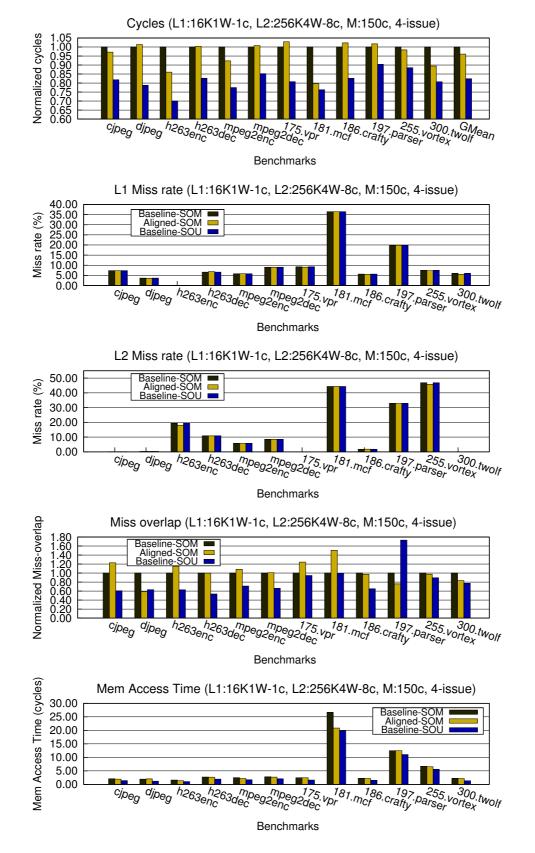

| 3.8  | Normalized Cycle count of the Baseline list scheduler and the vari-<br>ous Aligned Scheduling optimizations for both SOM and SOU stall<br>semantics, over various L1 cache configurations. This is a case study<br>of the cjpeg benchmark on a range of 2 to 4-issue machines                                                        | 47 |

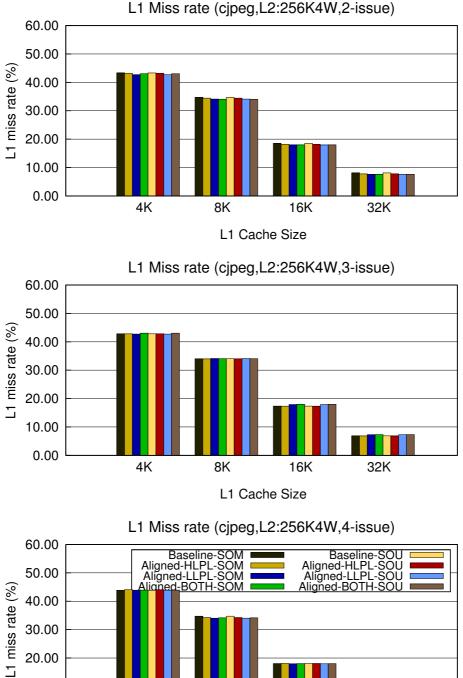

| 3.9  | L1 cache-miss rate for various L1 cache configurations. This is a case study of the cjpeg benchmark on a range of 2 to 4-issue machines                                                                                                                                                                                              | 48 |

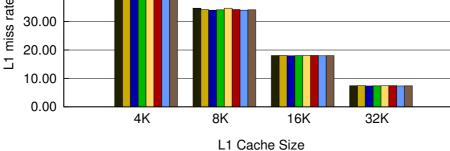

| 3.10 | L2 cache-miss rate for various L1 cache configurations. This is a case study of the cjpeg benchmark on a range of 2 to 4-issue machines                                                                                                                                                                                              | 49 |

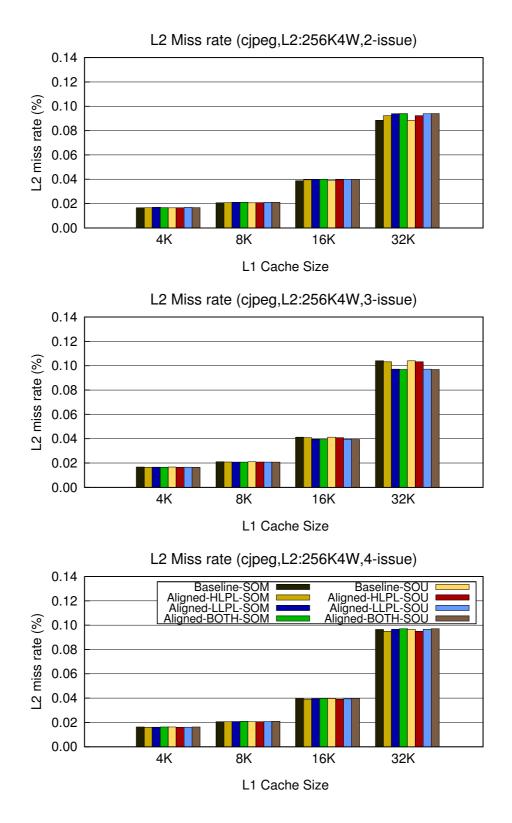

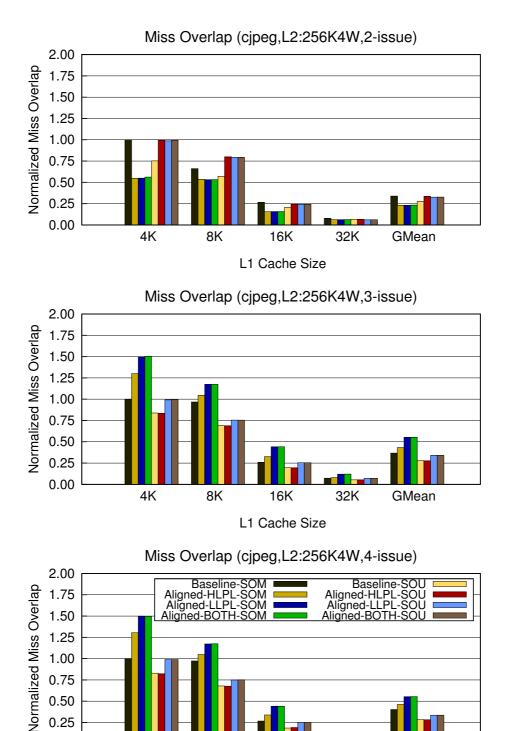

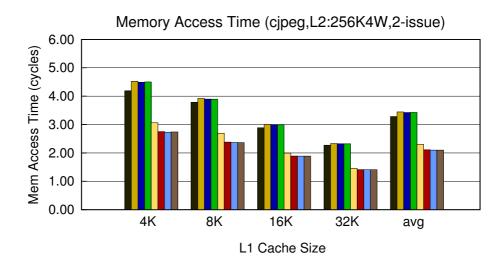

| 3.11 | Normalized cache-miss overlapping for various L1 cache configura-<br>tions. This is a case study of the cjpeg benchmark on a range of 2 to<br>4-issue machines.                                                                                                                                                                      | 50 |

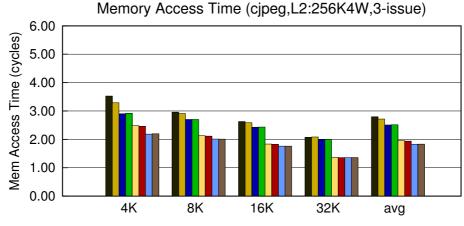

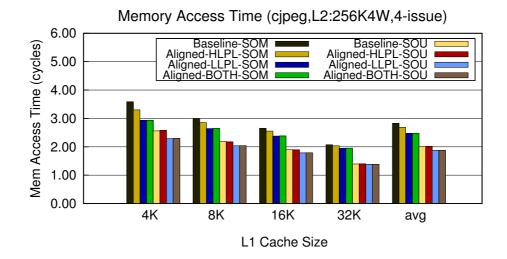

| 3.12 | Memory Access Time (i.e., the average Load latency) for various L1 cache configurations. This is a case study of the cjpeg benchmark on a range of 2 to 4-issue machines.                                                                                                                                                            | 51 |

| 3.13 | Normalized Cycle count, Miss Rates, Miss overlaps and average Mem-<br>ory Access Time for 6 of the Mediabench II and the SPEC CINT2000<br>benchmarks.                                                                                                                                                                                | 54 |

| 4.1  | A 4-cluster 4-issue clustered VLIW architecture (a). The instruction schedule in (b) corresponds to the code in (c).                                                                                                                                                                                                                 | 58 |

|      |                                                                                                                                                                                                                                                                                                                                      |    |

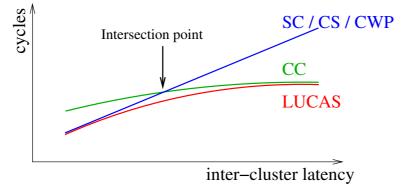

| 4.2  | Qualitative performance comparison of clustering heuristics under in-                                                                        |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | creasing inter-cluster latency: Start-Cycle (SC) [27, 41], Critical-Successor                                                                | r   |

|      | (CS) [96], Completion-weighted Predecessor (CWP) [72], Completion-                                                                           |     |

|      | Cycle (CC) [27] and the proposed heuristic used in LUCAS                                                                                     | 60  |

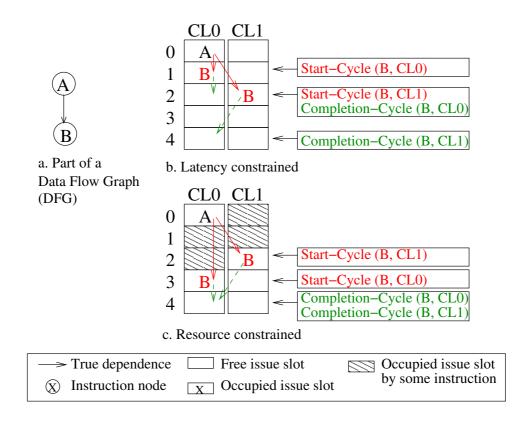

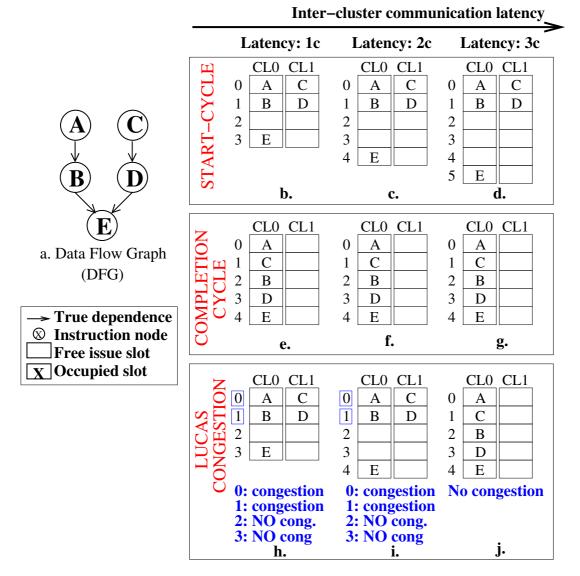

| 4.3  | Motivating example 1. Schedules for the instructions in the Data Flow                                                                        |     |

|      | Graph (DFG) (a) on a 2-cluster 2-issue clustered architecture, for the                                                                       |     |

|      | Start-Cycle, Completion-Cycle and LUCAS-Cycle-Congestion clus-                                                                               | ()  |

|      | tering heuristics. The inter-cluster delay ranges from 1 to 3 cycles                                                                         | 62  |

| 4.4  | Motivating example 2. Schedules for the instructions in the Data Flow                                                                        |     |

|      | Graph (DFG) (a) on a 2-cluster 2-issue clustered architecture, for the                                                                       |     |

|      | Start-Cycle, Completion-Cycle and LUCAS-Mobility clustering heuris-<br>tics. The inter-cluster delay ranges from 1 to 3 cycles. Each node in |     |

|      | the DFG is tagged with its mobility number                                                                                                   | 63  |

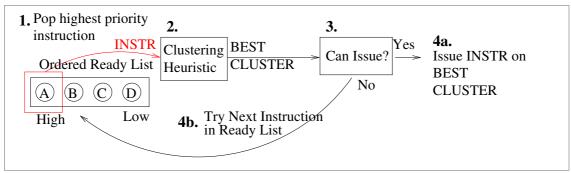

| 4.5  | The two variants of embedding the clustering heuristic into the instruc-                                                                     | 02  |

| 4.5  | tion scheduler. The numbers denote the order of execution of each step.                                                                      | 64  |

| 4.6  | Visualization of the Congestion Threshold.                                                                                                   | 67  |

|      | -                                                                                                                                            | 69  |

| 4.7  | The fully-connected point-to-point interconnect.                                                                                             |     |

| 4.8  | The compilation flow.                                                                                                                        | 70  |

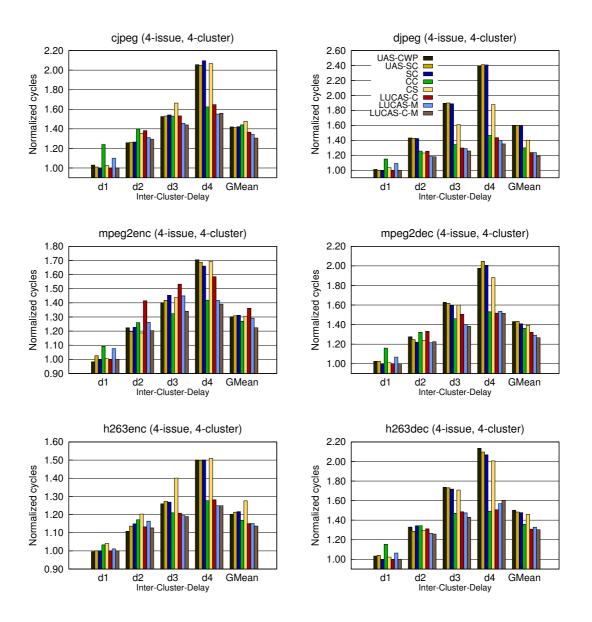

| 4.9  | Normalized cycles of the 4-issue, 4-cluster configuration for inter-                                                                         | = 0 |

|      | cluster delay 1 to 4, normalized to Start-Cycle (SC), delay 1                                                                                | 73  |

| 4.10 | Normalized cycles of the 8-issue, 4-cluster configuration for inter-                                                                         |     |

|      | cluster delay 1 to 4, normalized to Start-Cycle (SC), delay 1                                                                                | 74  |

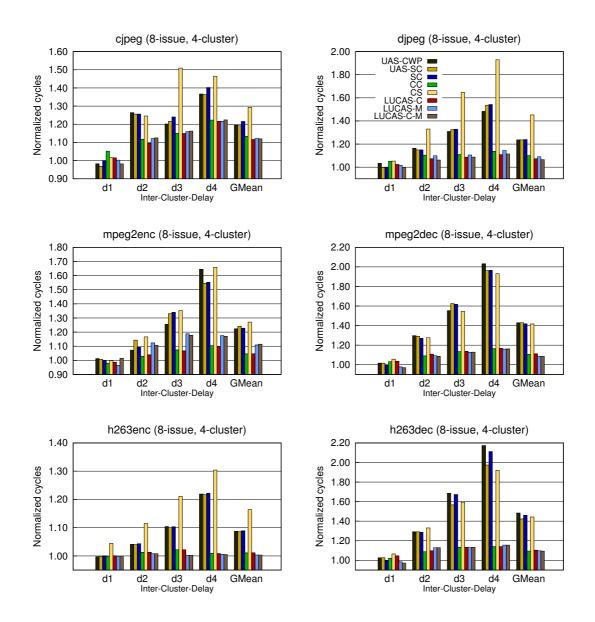

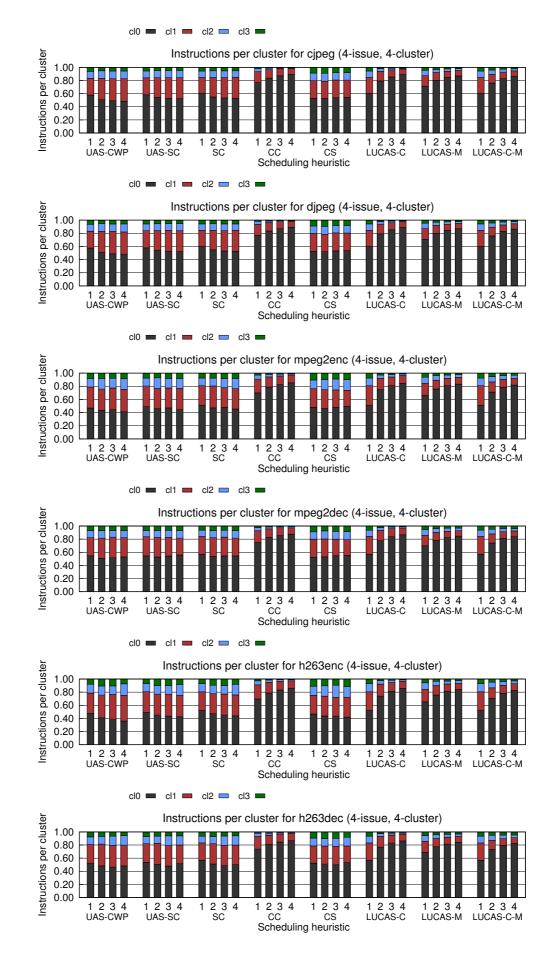

| 4.11 | Distribution of instructions on each cluster, for all clustering heuristics                                                                  |     |

|      | and for delays ranging from 1 to 4. This is for the 4-issue 4-cluster                                                                        |     |

|      | machine                                                                                                                                      | 77  |

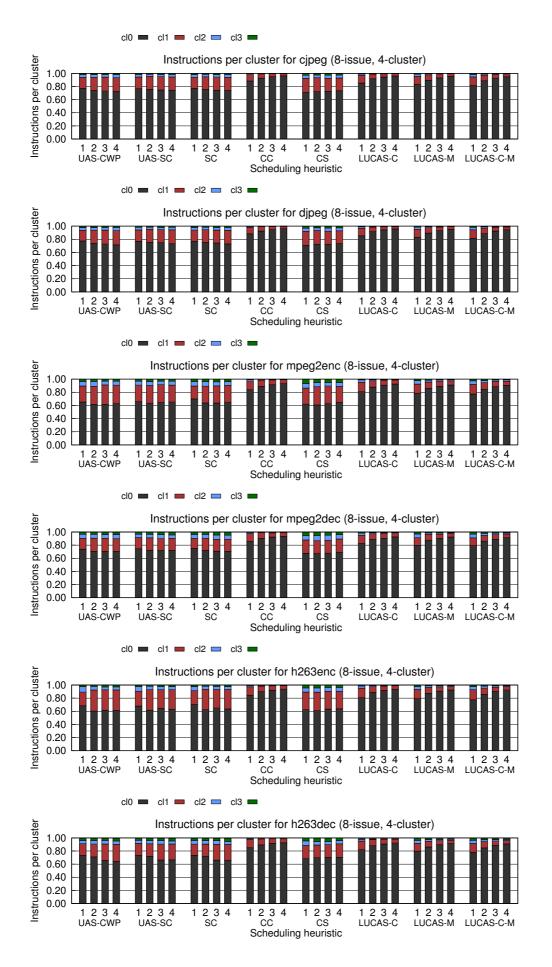

| 4.12 | Distribution of instructions on each cluster, for all clustering heuristics                                                                  |     |

|      | and for delay ranging from 1 to 4. This is for the 8-issue 4-cluster                                                                         | 70  |

|      | machine and just for the mpeg2 benchmarks.                                                                                                   | 78  |

| 5.1  | A 4-cluster 4-issue clustered VLIW architecture (a). The instruction                                                                         |     |

|      | schedule in (b) corresponds to the code in (c)                                                                                               | 82  |

| 5.2  | Two different ways of treating ICC instructions.                                                                                             | 84  |

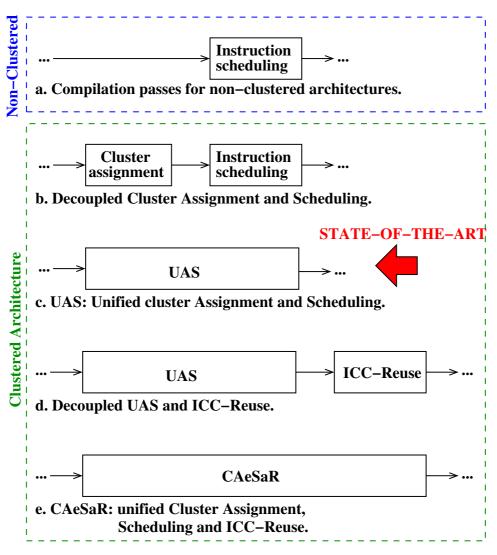

| 5.3  | The various compilation pipelines.                                                                                                           | 86  |

|      |                                                                                                                                              |     |

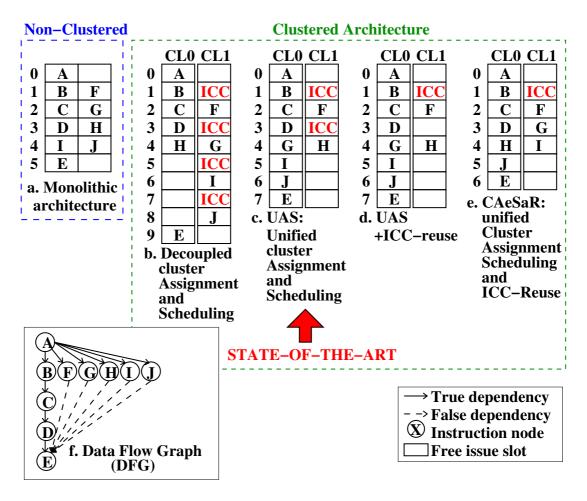

| 5.4  | Instruction schedules for the Data Flow Graph (DFG) in (f), based on             |     |

|------|----------------------------------------------------------------------------------|-----|

|      | various scheduling algorithms. The first one (a) is on a monolithic non-         |     |

|      | clustered VLIW architecture. The rest are on a clustered architecture:           |     |

|      | (b) Decoupled Cluster Assignment and Scheduling, (c) Unified As-                 |     |

|      | signment and Scheduling (UAS), (d) UAS + ICC-reuse optimization,                 |     |

|      | (e) CAeSaR (proposed)                                                            | 87  |

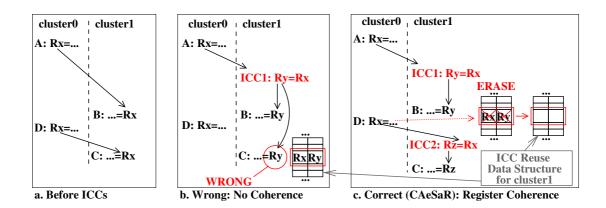

| 5.5  | The Register File Coherence.                                                     | 95  |

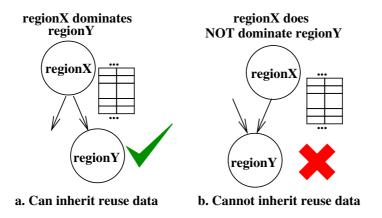

| 5.6  | The ICC reuse challenges across scheduling regions.                              | 96  |

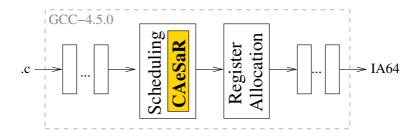

| 5.7  | The compilation flow.                                                            | 98  |

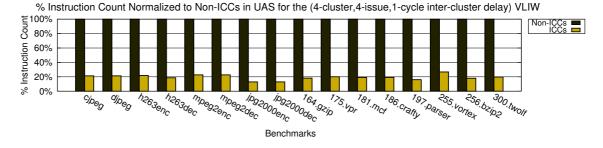

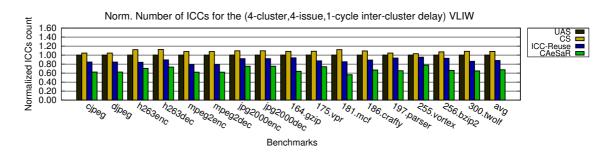

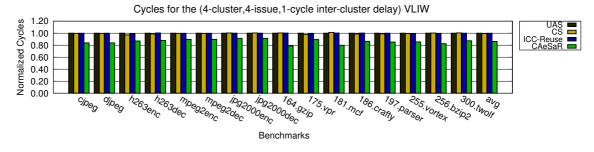

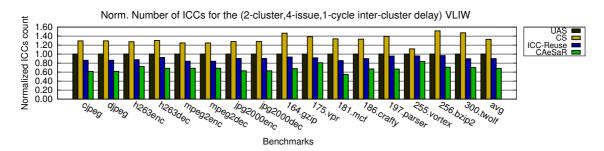

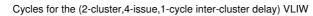

| 5.8  | Measurements for the 4-cluster, 4-issue, 1-cycle inter-cluster delay             |     |

|      | VLIW machine                                                                     | 101 |

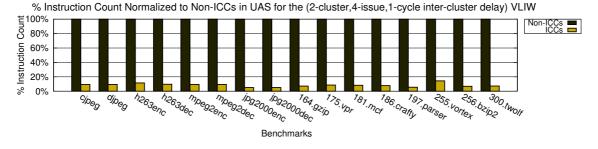

| 5.9  | Measurements for the 2-cluster, 4-issue, 1-cycle inter-cluster delay             |     |

|      | VLIW machine                                                                     | 102 |

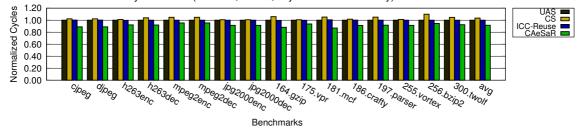

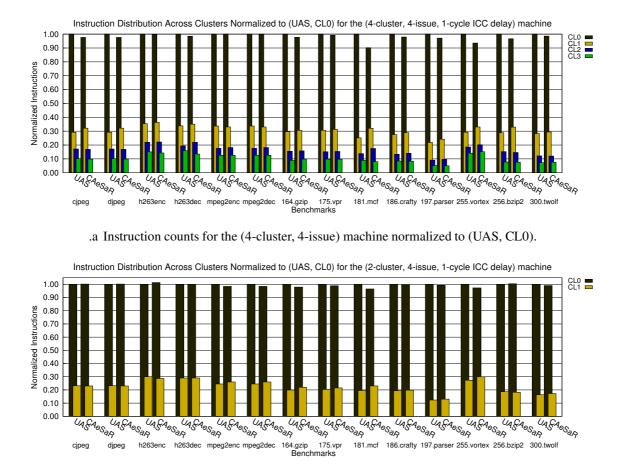

| 5.10 | Distribution of original instructions across clusters for both 4-cluster         |     |

|      | and 2-cluster machines                                                           | 104 |

| 6.1  | Under-utilized cluster1 can have half the frequency with no perfor-              |     |

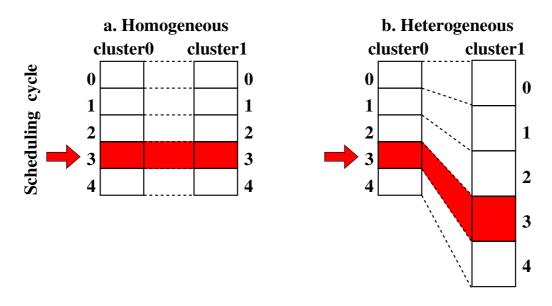

|      | mance loss and possible energy gains.                                            | 109 |

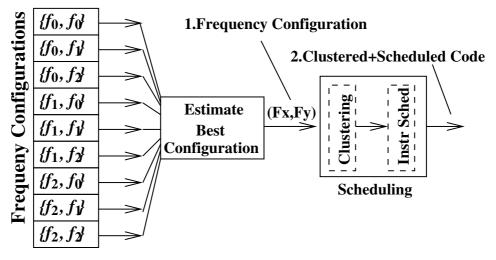

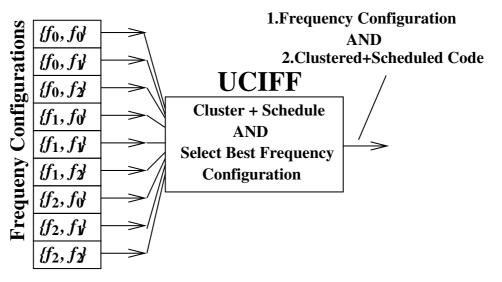

| 6.2  | The two-phase scheduling of the current state-of-the-art (a). The pro-           |     |

|      | posed unified approach (b) is free of this phase-ordering problem                | 111 |

| 6.3  | The scheduling problem of misaligned cycle boundaries for the hetero-            |     |

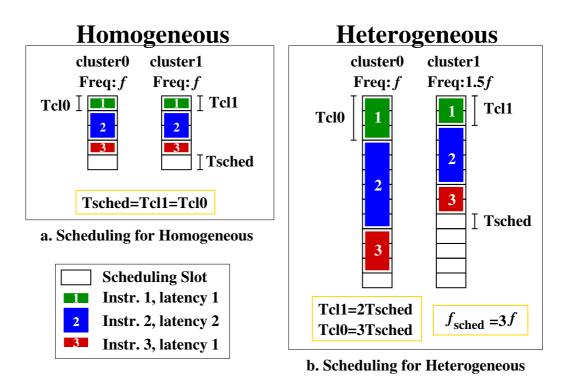

|      | geneous processor.                                                               | 112 |

| 6.4  | The scheduler's internal clock period $T_{sched}$ compared to the periods of     |     |

|      | the two clusters $T_{cl0}$ and $T_{cl1}$ , for a homogeneous (a) and a heteroge- |     |

|      | neous (b) architecture.                                                          | 113 |

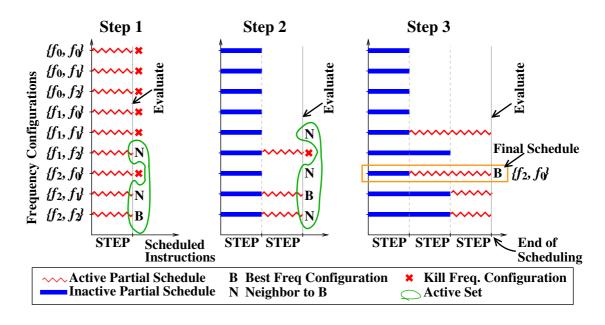

| 6.5  | Overview of the UCIFF gradual hill climbing algorithm for a schedule             |     |

|      | that consists of three steps.                                                    | 115 |

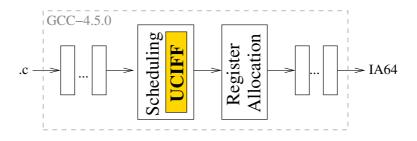

| 6.6  | The compilation flow.                                                            | 124 |

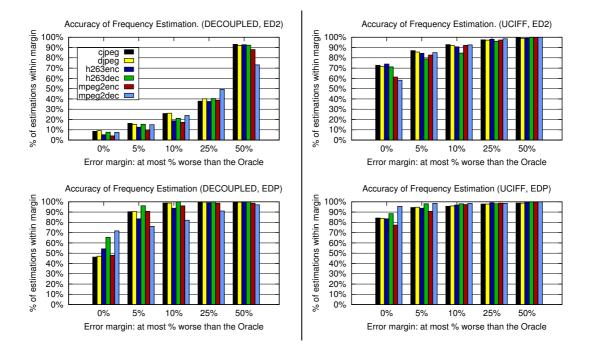

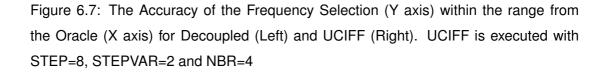

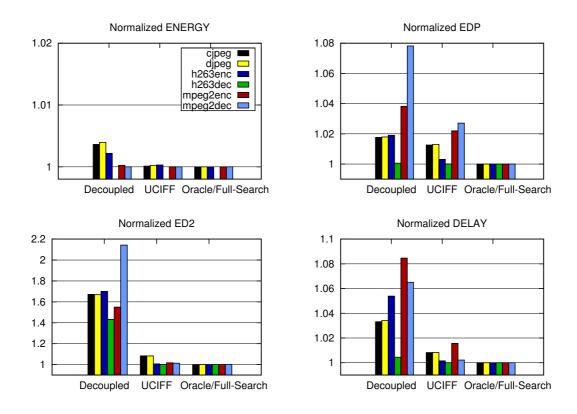

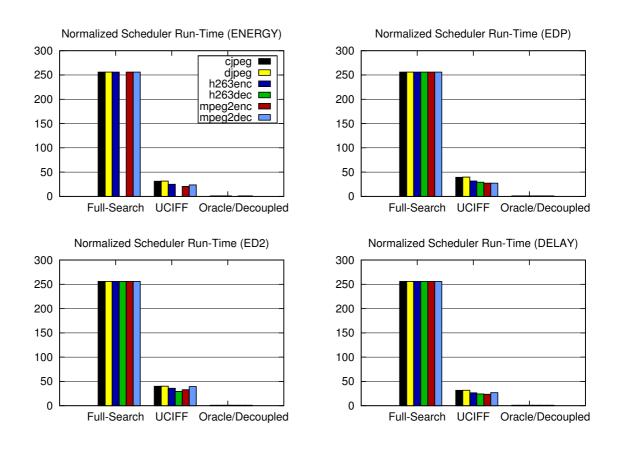

| 6.7  | The Accuracy of the Frequency Selection (Y axis) within the range                |     |

|      | from the Oracle (X axis) for Decoupled (Left) and UCIFF (Right).                 |     |

|      | UCIFF is executed with STEP=8, STEPVAR=2 and NBR=4                               | 127 |

# **List of Tables**

| 3.1 | Complexity comparison.                                           | 43  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | Processor configuration.                                         | 45  |

| 3.3 | Benchmarks                                                       | 45  |

| 4.1 | Processor configuration.                                         | 69  |

| 4.2 | Evaluated schemes.                                               | 71  |

| 5.1 | Complexity of UAS (baseline) and CAeSaR algorithms               | 97  |

| 5.2 | Target Architecture Configuration.                               | 99  |

| 5.3 | Benchmarks                                                       | 99  |

| 6.1 | Formulas for energy calculation.                                 | 120 |

| 6.2 | Some features of the algorithms under comparison                 | 126 |

| 7.1 | Summarized features of LUCAS, CAeSaR, UCIFF and other cluster-   |     |

|     | ing schedulers in the literature                                 | 137 |

| 7.2 | Summarized comparison of memory-aware instruction schedulers for |     |

|     | VLIW                                                             | 139 |

# **Chapter 1**

# Introduction

We are now in the mobile era. With the widespread adoption of mobile devices, highperformance and low power embedded processors are becoming the focus of the computing industry. Energy consumption in terms of performance per watt has become a primary design goal. Both architecture and compiler techniques that improve efficiency are the focus of research in both academia and industry.

The compiler's role in improving performance has recently become particularly important. In the past, one would get large performance and energy improvements without changing the software, thanks to advances in silicon scaling. Nowadays, however, this is no longer true since silicon scaling has got very close to its physical limits and further improvements are harder and more expensive than ever before. Therefore any improvements at that level will come from either the hardware design, the microarchitecture, or the compiler. In contrast to the first two, compiler optimizations require no additional chip real estate, they do not consume any extra energy at run-time and they can apply immediately even to existing chips by a recompilation of the workload.

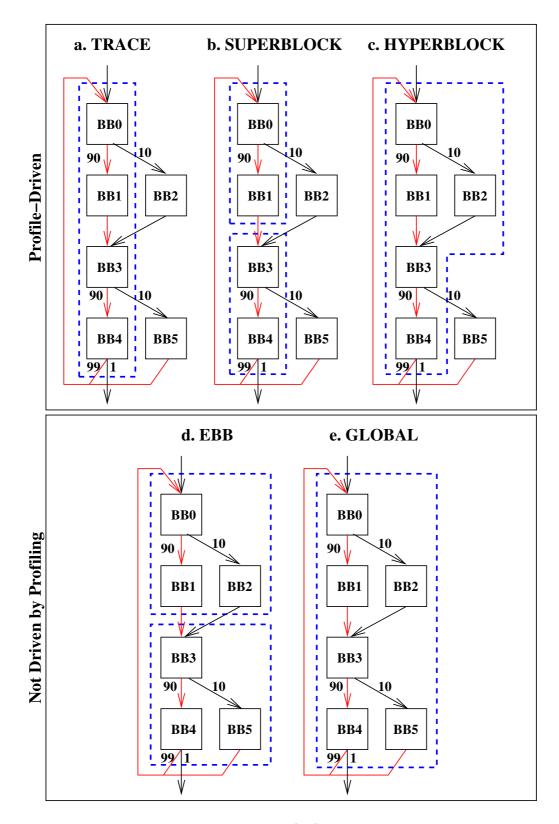

The Very Long Instruction Word (VLIW) design philosophy is about reducing hardware complexity in the expense of a more advanced compiler. This is nicely summarized by Joseph Fisher in the phrase "A smart compiler and a dump machine" [31]. This design philosophy is particularly important nowadays that energy consumption is a major design constraint. The compiler back-end for VLIWs offloads code generation work from the micro-architecture hardware to the compiler back-end. The back-end tasks are instruction selection, instruction scheduling and register allocation, all of which are specifically tuned for the target architecture. The VLIW design allows for simple, more energy efficient, wide-issue designs. However, the performance of such architectures depends highly on the quality of the code generated by the compiler.

According to the VLIW design philosophy, the processor hardware is to be kept simple. Optimizations that can be done in the compiler instead of the hardware, should be done there, whenever this is practical and beneficial. For example VLIW machines rely on the compiler to perform instruction scheduling. This is practical because a large portion of the data dependencies between instructions can be fully analyzed and determined by the compiler. This includes register dependencies and a part of the memory dependencies that can be determined with the help of the compiler's alias analysis. It is often beneficial too, since compile-time scheduling leads to simpler hardware designs, with fewer and less complicated hardware interlocks, and with wide issue widths that can operate at higher clock frequencies and consume less energy. Therefore, instruction scheduling done at compile time is both beneficial and practical compared to a hardware-only solution (like that of dynamically scheduled superscalar processors).

Deciding which micro-architectural tasks should be offloaded to the compiler is a complicated design trade-off. There are several factors that have to be taken into account, such as the target operating energy-performance point, the workloads, the other micro-architectural components used (e.g., the size/type/design of cache) and others. It is common for all VLIWs to offload instruction scheduling to the compiler, therefore static scheduling is one of the identifying features for VLIWs.

In this thesis we propose new or we improve existing instruction scheduling optimizations following the VLIW design philosophy. We firstly present a scheduling technique that allows a lightweight VLIW processor without load-use hardware interlocks (Stall-On-Miss) to effectively hide cache-miss latencies (Chapter 3). In Chapter 4, we present a high-performance scheduler for clustered VLIWs powered by a novel clustering heuristic that adapts to a wide range of inter-cluster delays. Next, in Chapter 5 we present a novel high-performance instruction scheduler for clustered VLIW processors that caches and reuses data transmitted to clusters, thus decreasing the intercluster communication more than any existing solution. Finally, we present a novel scheduling algorithm with DVFS capabilities. It accurately determines the voltagefrequency points of each cluster of a clustered VLIW, while performing instruction scheduling (Chapter 6).

In the following Sections (1.1, to 1.4) we introduce each of these techniques and we discuss how they advance the state-of-the-art.

# 1.1 Aligned Scheduling: Exploiting MLP to hide cachemiss latencies on VLIWs

Traditional VLIW processors were connected directly to the memory, with no caches in between. Later, as the gap between logic and memory increased, cache memories were introduced. Caches, however, lead to statically unpredictable memory latencies, since a memory access can either be a cache-hit or a cache-miss. With no extra control logic hardware support, a Load-miss will stall the processor, causing a pause in the computation, degrading performance. For this reason several hardware techniques have been proposed to overlap computation with outstanding misses, typically for dynamically scheduled processors. Such techniques track the instruction data dependencies and cause a stall only if the value of the missing load is about to be consumed. These mechanisms are usually referred to as "load-use interlocks".

In Chapter 3, we propose a compiler-only approach to improve the performance caused by cache-misses, without resorting to the use of load-use interlocking. We call this approach "Aligned Scheduling" since it relies on aligning independent Load instructions on the same VLIW cycle. The technique targets VLIW processors and is in harmony with the VLIW design philosophy of performing work at compile-time rather than at run-time (in hardware). This is the first compiler technique of this nature that targets VLIW processors with no memory interlocks. The experimental results show that it manages to improve the performance of the processor significantly and to bring it closer to the hardware solution, particularly in cases with many cache-misses.

# 1.2 Latency-adaptive Unified Clustering and Scheduling (LUCAS)

#### 1.2.1 Clustered architectures

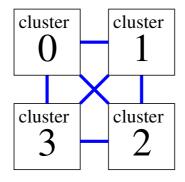

Clustered designs for Instruction Level Parallelism (ILP) were introduced as a solution to the poor performance and energy scalability of wide-issue ILP processors. This is done by partitioning the design into smaller sections called clusters (as shown in Figure 1.1). Within the cluster, data transfers between the register file and functional units are fast and energy efficient, while across clusters there is a performance and energy penalty. On the contrary, monolithic (non-clustered) architectures have some

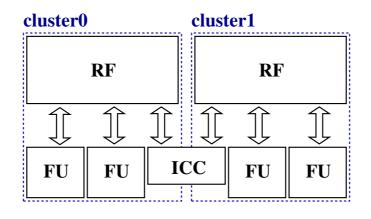

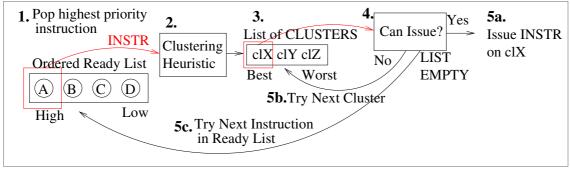

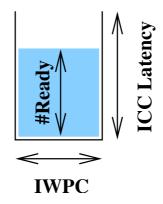

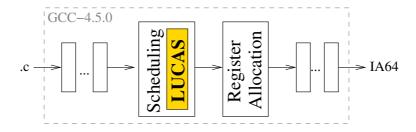

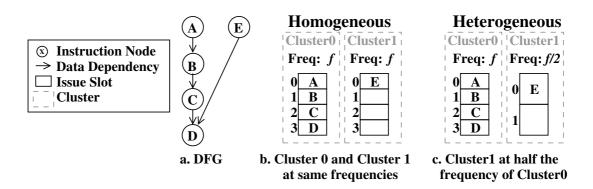

Figure 1.1: A 2-cluster VLIW architecture. The red arrow shows the Inter-Cluster Copy (ICC) Latency.

bulky resources (such as the register file) that are shared across many functional units and therefore do not exploit the opportunity to improve performance or to save energy whenever global communication is not required. A clustered design, on the other hand, does exactly that as its resources are partitioned into smaller, locally accessible chunks. Each cluster usually contains a portion of the register file tightly connected to a small number of other resources (e.g., functional units). In this way any local communication within the cluster is fast and efficient while any inter-cluster communication comes at the extra cost, close to that of a monolithic design. It is this partitioning of the global resources and its localization within a cluster that gives the clustered design an advantage in both energy and operating frequency [92].

Clustered VLIW processors are designed to be more scalable than their monolithic counterparts and more energy efficient, while achieving higher operating frequencies [92]. They operate at an attractive power/performance ratio point. The Texas Instruments C64xx family is an example of a clustered VLIW architecture.

The clustering algorithm, regardless of whether it is implemented in hardware or in the compiler, makes use of some data-flow information and assigns the instructions to clusters. The cluster selected is the one suggested by the clustering heuristic, which has a major impact on performance.

An important parameter of the clustered design is the Inter-Cluster Copy (ICC) latency. It signifies the time needed for data to be communicated between clusters (red arrow in Figure 1.1). The longer the ICC latency, the more the penalty of offloading instructions to distant clusters.

The techniques that follow (Sections 1.2, 1.3, 1.4 and Chapters 4, 5, 6, all target

clustered VLIW processors.

#### 1.2.2 LUCAS

The Inter-Cluster Copy delay (ICC delay) of a clustered VLIW architecture is an important parameter. It is the extra latency needed for some cluster to bring in data to its own register file from a distant one. This is important because it controls how effectively the clusters can be utilized: a high ICC delay makes it harder for the clusters to be utilized fully, since any communication between the clusters is followed by additional latency, the ICC delay.

Our target being a statically scheduled architecture, it is up to the instruction scheduler, and more specifically to the cluster assignment algorithm, to effectively utilize the clusters. The scheduler must be aware of the ICC delay to generate an effective schedule. The problem that the scheduler solves is where in space (i.e., cluster) and time (i.e., cycle) each instruction of the program should be scheduled at such that the final schedule is of minimum length.