# The Performance Mapping of a Class of Fully Decoupled Architecture

Alan W.R. Crawford

M.Phil.

The University of Edinburgh

1998

# **Declaration**

I, the undersigned, hereby declare that the contents of this thesis have been composed solely by myself, and that the work described herein is entirely my own.

Date: 27<sup>th</sup> May 1998.

#### Acknowledgements

I would like to acknowledge the vital contribution of my supervisor, Dr. Nigel Topham, without whose continuing guidance, advice, comments, suggestions, criticism and encouragement I would never have finished this thesis. I would also like to thank my second supervisor, Prof. Roland Ibbett, and Muriel Mewison, of the SHIPS project, who provided the LOD frequency information that greatly helped to reduce the amount of work required in Chapter 7. Many thanks also to Dr. Rob Pooley and Dr. Tony Fields, the examiners, for their feedback, suggestions and constructive criticism. Particular thanks to Rob for his tolerance and all his help during this past year.

Credit is also due to Trident Systems, my former employer, for allowing me the use of their computing facilities during the period 1995-1997.

Finally, many thanks to my ex-wife Jenni for all she put up with during the period when I was working on my research and thesis.

#### Abstract

Fully decoupled architectures present a possible solution to the problems posed by the growing disparity between memory and processor speeds. In this thesis the performance of this class of fully decoupled architectures is examined in detail. The causes and effects of both access/execute and control decoupling are investigated using simulation and modelling, and techniques for their more efficient exploitation are proposed. A similar investigation is made of losses of decoupling (LODs), which eliminate many of the advantages of decoupling, and particular attention is given to a number of methods for the removal of LODs or the reduction of their effects. Finally, a number of architectural techniques to enhance the performance of this class of architectures is presented.

# **Table Of Contents**

| 1. | Overvi  | ew                                                 | 1  |

|----|---------|----------------------------------------------------|----|

| 2. | Introdu | ection                                             | 3  |

|    | 2.1 Th  | e Problem                                          | 3  |

|    | 2.2 La  | tency Reduction                                    | 3  |

|    | 2.3 La  | tency Tolerance                                    | 4  |

|    | 2.4 No  | n-Blocking Stores                                  | 5  |

|    | 2.4.1   | Non-Blocking Loads                                 | 6  |

|    | 2.4.2   | The CDC 6600 Address Unit                          | 6  |

|    | 2.4.3   | Cache Preloading                                   | 7  |

|    | 2.4.4   | Dataflow                                           | 10 |

|    | 2.4.5   | Context Flow And Multi-Threading                   | 11 |

|    | 2.      | 4.5.1 Pessimistic Multi-Threading                  | 11 |

|    | 2.      | 4.5.2 Optimistic Multi-Threading                   | 14 |

|    | 2.4.6   | Decoupling                                         | 16 |

| 3. | Decou   | pled Architectures                                 | 18 |

|    | 3.1 Ac  | cess/Execute Decoupled Architectures               | 18 |

|    | 3.1.1   | Single instruction stream architectures            | 20 |

|    | 3.1.2   | Dual instruction stream architectures              | 21 |

|    | 3.1.3   | Decoupled loads and stores                         | 23 |

|    | 3.1.4   | Inter-unit transfers                               | 26 |

|    | 3.1.5   | The problems of distributed control.               | 27 |

|    | 3.2 Fu  | lly Decoupled Architectures                        | 27 |

|    | 3.2.1   | MIQ and CFQ design issues                          | 30 |

| 4. | The M   | odelling And Simulation Of Decoupled Architectures | 33 |

|    | 4.1 An  | Analytical Model                                   | 35 |

|    | 4.2 A   | Simulation Model                                   | 39 |

|    | 4.3 An  | Architectural Simulator                            | 42 |

|    | 4.3.1   | The Source Annotator                               | 46 |

|    | 4.3.2   | The Simulator Structure                            | 50 |

|    | 4.3.3   | The Simulated Architecture                         | 58 |

|    | 4.:     | 3.3.1 The Level 1 Architecture                     | 58 |

|    | 4.      | 3.3.2 The Level 2 Architecture                     | 60 |

| 4.3.3.3 The Level 3 Architecture                       | 62  |

|--------------------------------------------------------|-----|

| 5. Decoupling                                          | 64  |

| 5.1 Access/Execute Decoupling                          | 64  |

| 5.1.1 Experiments 1 & 2: Load streaming                | 64  |

| 5.1.2 Unit stride accesses                             | 66  |

| 5.1.3 Random accesses                                  | 74  |

| 5.1.4 Conclusions                                      | 76  |

| 5.1.5 Experiment 2: Is the LAQ really necessary?       | 78  |

| 5.1.6 Conclusions                                      | 81  |

| 5.1.7 Experiment 3: Store streaming                    | 84  |

| 5.1.8 Conclusions                                      | 92  |

| 5.1.9 Experiment 4: The SAXPY loop                     | 94  |

| 5.1.10 Comparisons with the simulated model            | 103 |

| 5.1.11 Conclusions                                     | 106 |

| 5.1.12 Access/execute decoupling - a summary           | 106 |

| 5.2 Control Decoupling                                 | 110 |

| 5.2.1 Experiment 5: The SAXPY loop again               | 110 |

| 5.2.1.1 Increasing The Available Decoupling            | 115 |

| 6. Losses Of Decoupling                                | 118 |

| 6.1 Losses Of A/E Decoupling                           | 118 |

| 6.1.1 Causes                                           | 118 |

| 6.1.2 Effects                                          | 119 |

| 6.1.3 Solutions                                        | 120 |

| 6.1.3.1 Code replication                               | 120 |

| 6.1.3.2 Address SP self-load and self-store operations | 128 |

| 6.1.3.3 Strip Decoupling                               | 128 |

| 6.1.3.4 Code motion                                    | 136 |

| 6.1.4 Conclusions                                      | 136 |

| 6.2 Losses Of Control Decoupling                       | 138 |

| 6.2.1 Causes                                           | 138 |

| 6.2.2 Effects                                          | 138 |

| 6.2.3 Solutions                                        | 139 |

| 6.2.3.1 Code Replication                               | 139 |

| 6.2.3.2 Guarding                                       | 140 |

| 6.2.3.4 Guarded meta-instructions                                | 150<br>150<br>153<br>154 |

|------------------------------------------------------------------|--------------------------|

| 6.2.3.6 Performance of meta-instruction level guarding           | 150<br>153               |

| 6.2.3.7 Decoupling-specific guarding techniques                  | 153                      |

|                                                                  | 154                      |

| 624 Canalysians                                                  |                          |

| 8.2.4 Conclusions                                                | 156                      |

| 7. The Decoupling Behaviour of Real Programs                     |                          |

| 7.1 The problems of simulating the execution of real programs    | 156                      |

| 7.1.1 Trace reduction techniques                                 | 157                      |

| 7.2 Decoupling behaviour at the program level                    | 160                      |

| 7.2.1 Results                                                    | 163                      |

| 7.2.2 Conclusions                                                | 173                      |

| 7.2.2.1 An alternative to program-level simulation               | 175                      |

| 8. Conclusions & Future Work                                     | 177                      |

| 8.1 Conclusions                                                  | 177                      |

| 8.2 Some possible future work                                    | 179                      |

| 8.2.1 Instruction caching mechanisms for decoupled architectures | 179                      |

| 8.2.1.1 Multi-threaded decoupling                                | 183                      |

| 8.2.1.2 Scheduling                                               | 186                      |

| 8.2.1.3 Non-specialised decoupled processing                     |                          |

# **List Of Figures**

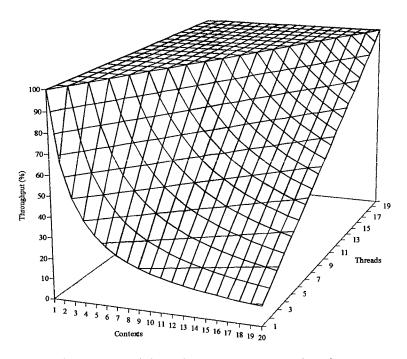

| Figure 1 - Total throughput vs. contexts vs. threads                                  | 12 |

|---------------------------------------------------------------------------------------|----|

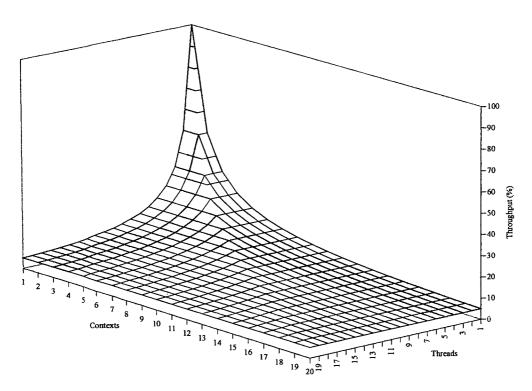

| Figure 2 - Per thread throughput vs. contexts vs. threads.                            | 14 |

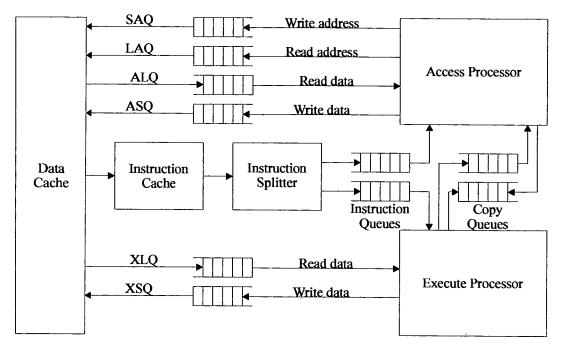

| Figure 3 - The Astronautics ZS-1 CPU.                                                 | 20 |

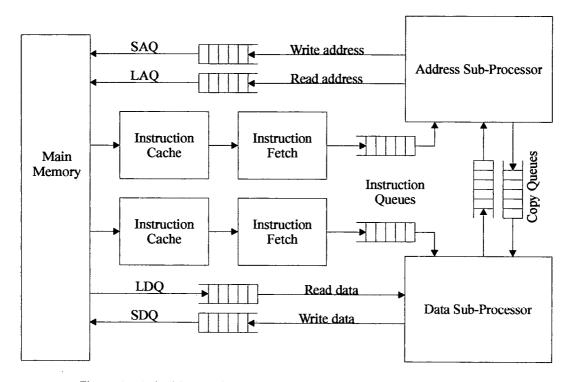

| Figure 4 - A dual instruction stream access/execute decoupled architecture.           | 22 |

| Figure 5 - A simple instruction dispatch mechanism.                                   | 28 |

| Figure 6 - A meta-instruction dispatch mechanism.                                     | 29 |

| Figure 7 - Two possible meta-instruction formats.                                     | 30 |

| Figure 8 - Load path queueing model.                                                  | 37 |

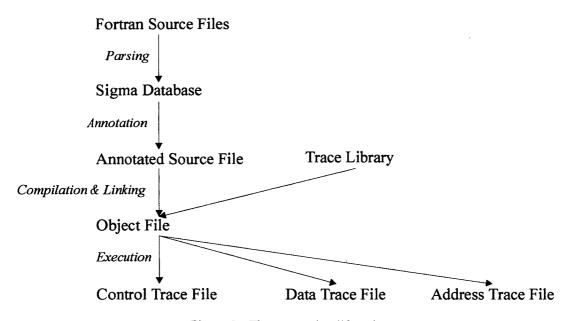

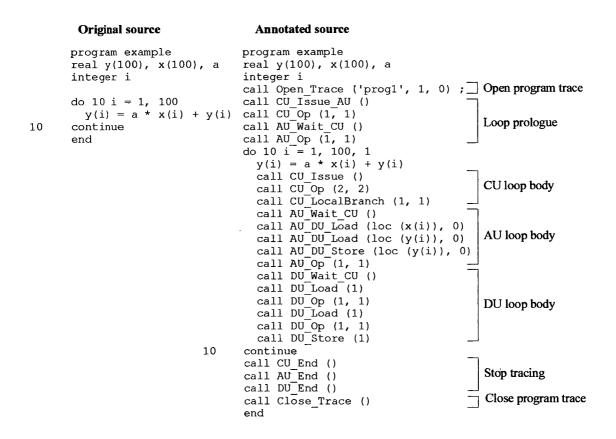

| Figure 9 - The annotation lifecycle.                                                  | 48 |

| Figure 10 - A sample source annotation.                                               | 49 |

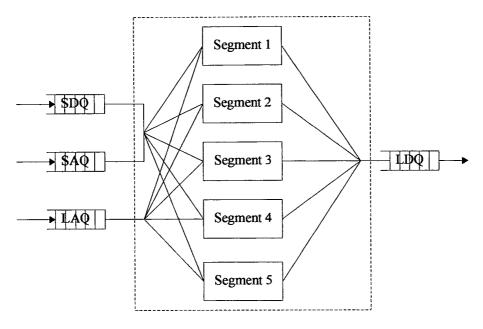

| Figure 11 - The simulated memory subsystem structure (5 segments)                     | 51 |

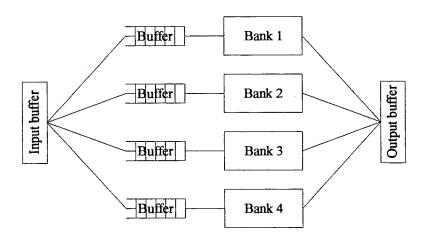

| Figure 12 - The simulated memory segment structure (4 banks).                         | 52 |

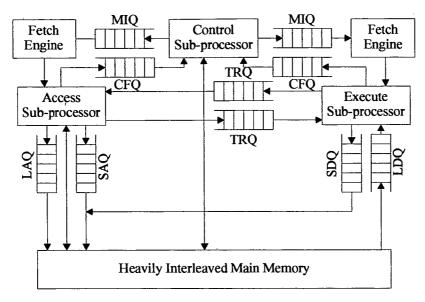

| Figure 13 - Level 1 architecture.                                                     | 59 |

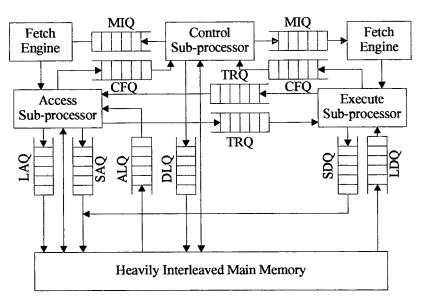

| Figure 14 - Level 2 architecture.                                                     | 61 |

| Figure 15 - Level 3 architecture.                                                     | 62 |

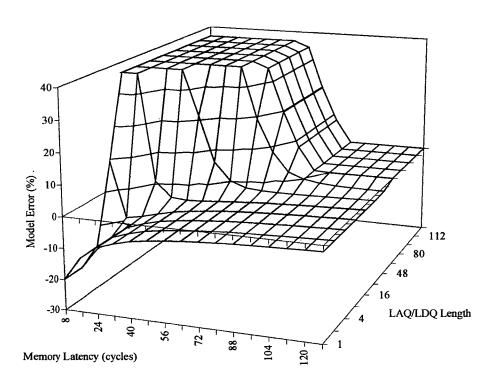

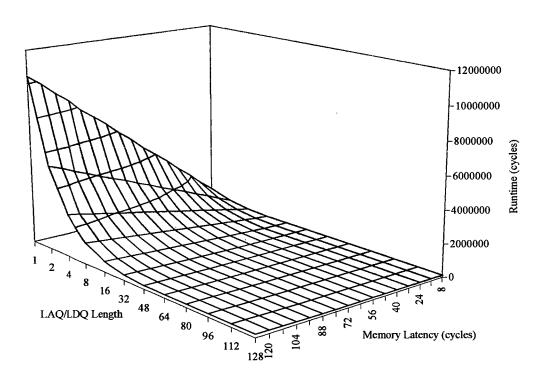

| Figure 16 - Normalised model runtime error. (Ex. 1)                                   | 66 |

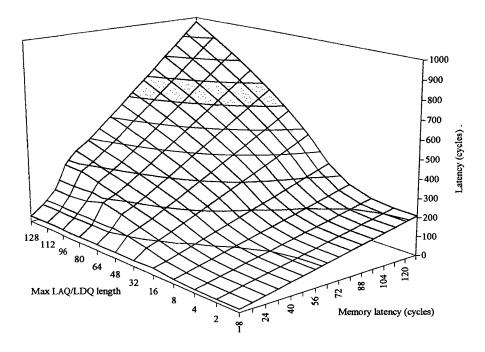

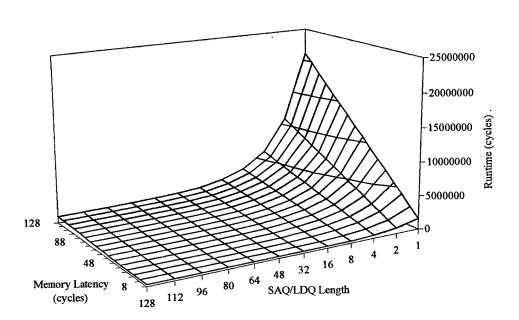

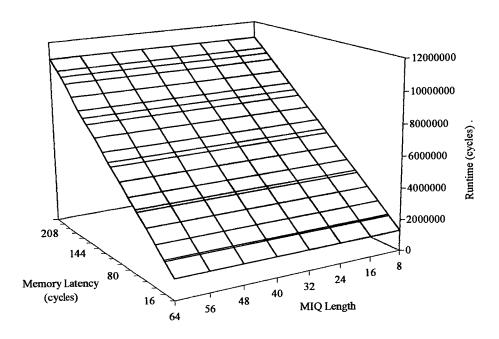

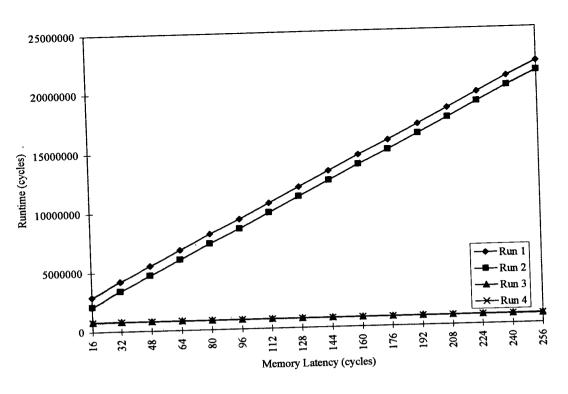

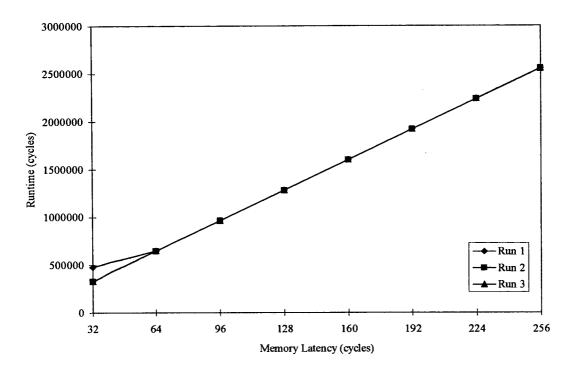

| Figure 17 - Total runtime. (Ex. 1)                                                    | 67 |

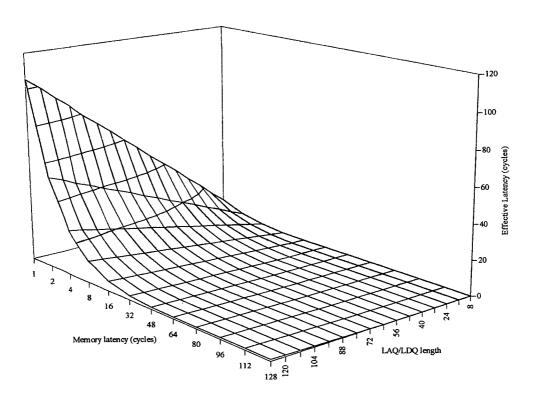

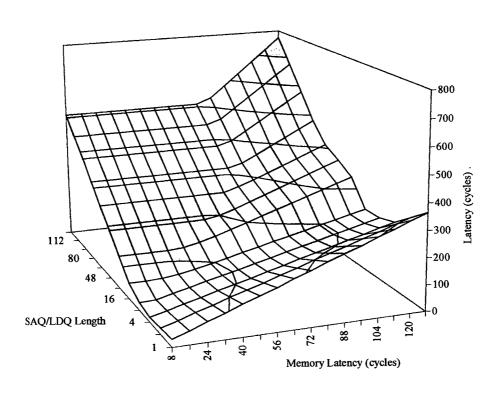

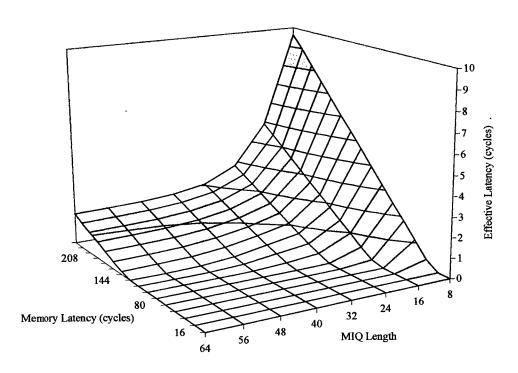

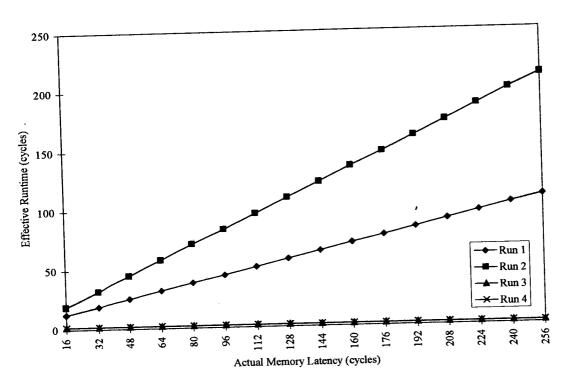

| Figure 18 - Effective load latency with unit stride (Ex. 1)                           | 69 |

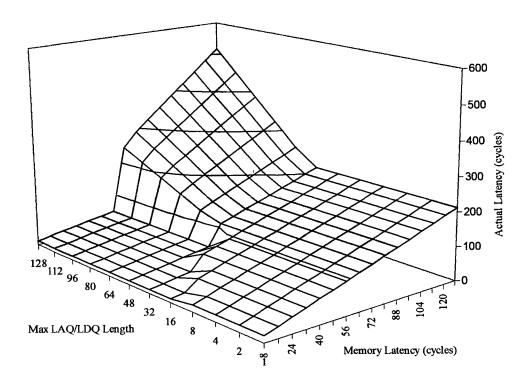

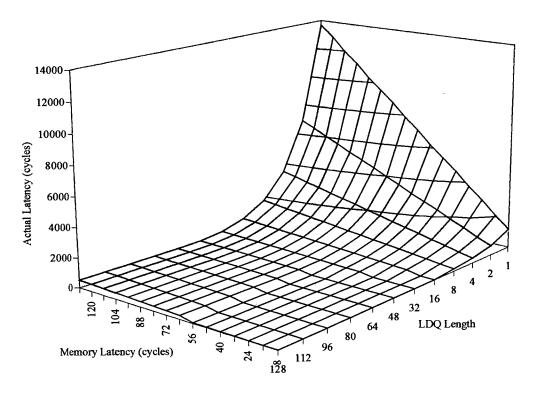

| Figure 19 - Actual load latency with unit stride. (Ex. 1)                             | 70 |

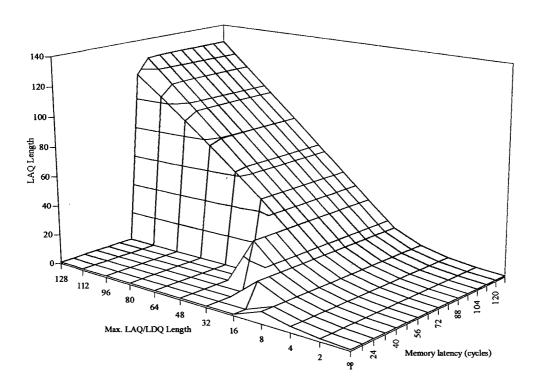

| Figure 20 - Average LAQ length with unit stride for simulator. (Ex. 1)                | 71 |

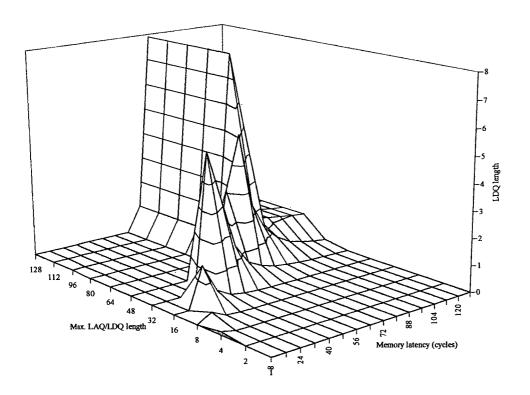

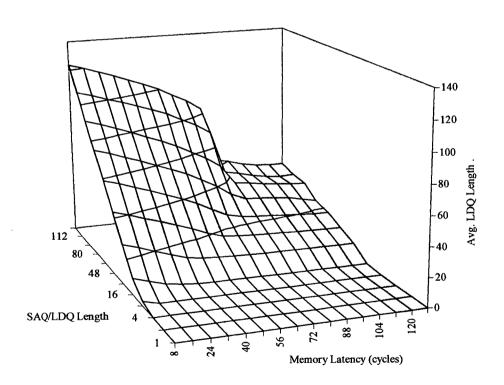

| Figure 21 - Average LDQ length with unit stride for model. (Ex. 1)                    | 72 |

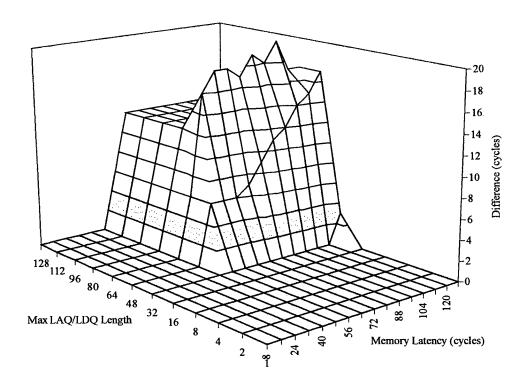

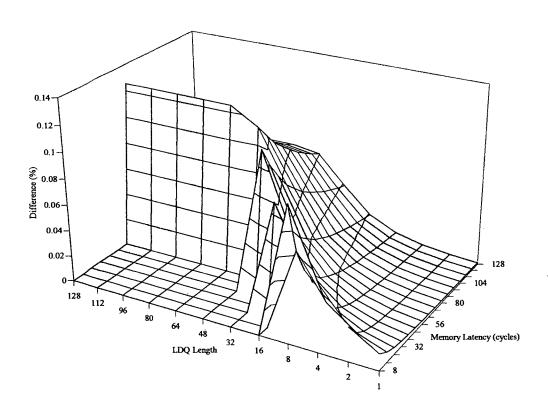

| Figure 22 - Difference in runtime between random and unit stride accesses. (Ex. 1)    | 74 |

| Figure 23 - Difference in actual latency for unit stride and random accesses. (Ex. 1) | 75 |

| Figure 24 - Actual latency for model with random stride. (Ex. 1)                      | 76 |

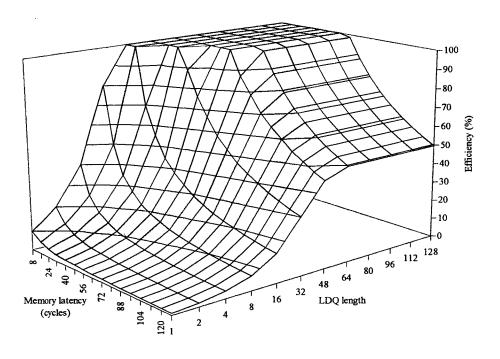

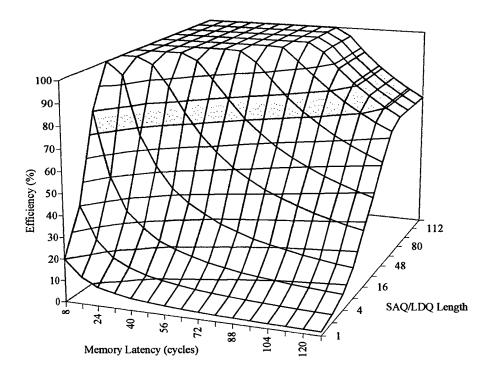

| Figure 25 - Sub-processor efficiency. (Ex. 2)                                         | 78 |

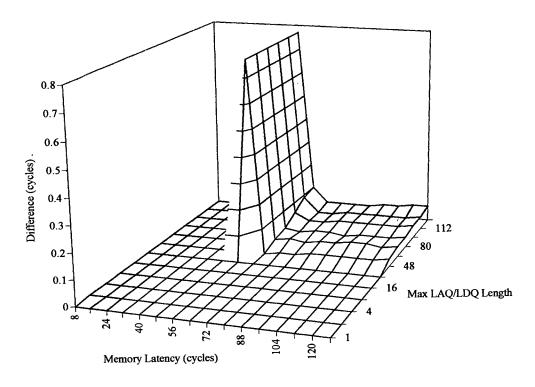

| Figure 26 - Difference in simulated AU efficiency for LAQ lengths 1 and 128. (Ex. 2)  | 79 |

| Figure 27 - Modelled runtime difference. (Ex. 2)                                      | 80 |

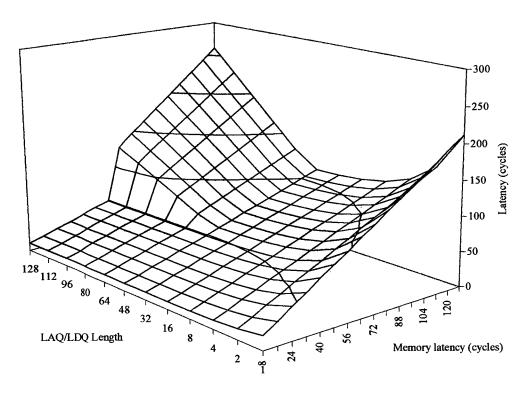

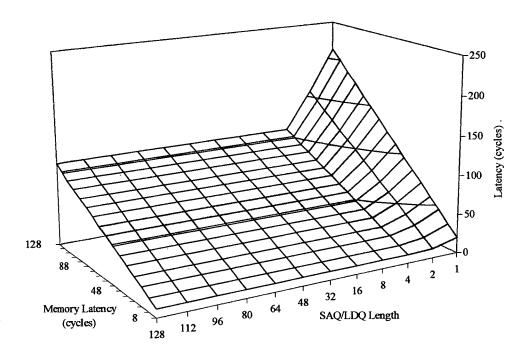

| Figure 28 - Simulated actual latency for LAQ length 1. (Ex. 2)                        | 81 |

| Figure 29 - Simulated actual latency for LAQ length 128. (Ex. 2)                      | 82 |

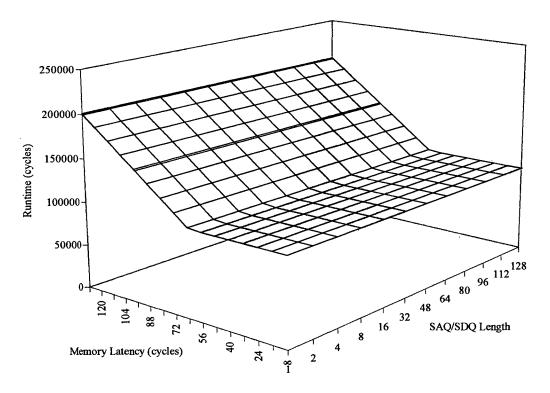

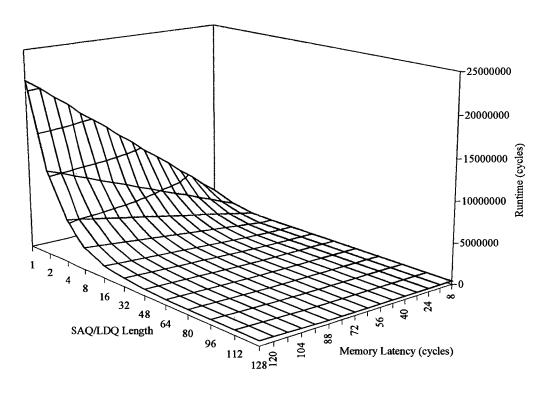

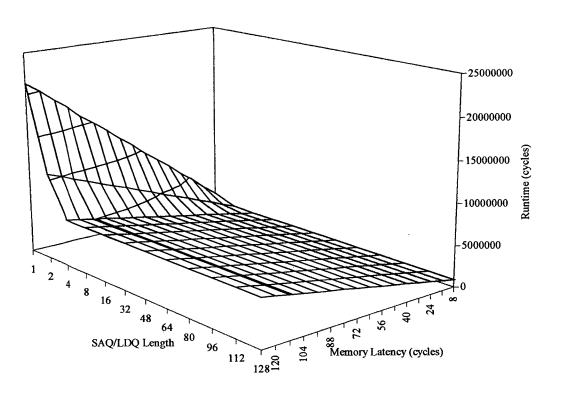

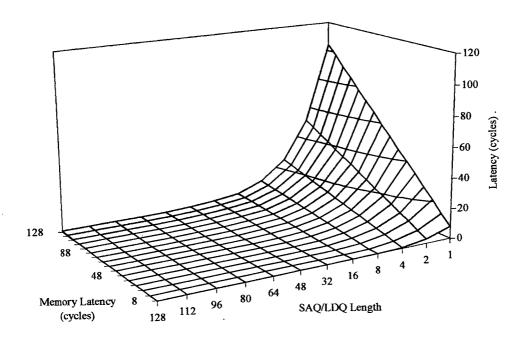

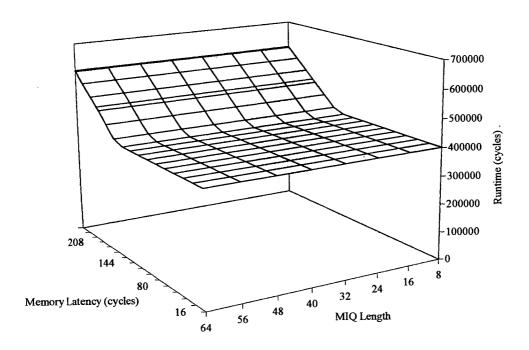

| Figure 30 - Simulated runtime. (Ex. 3)                                                | 84 |

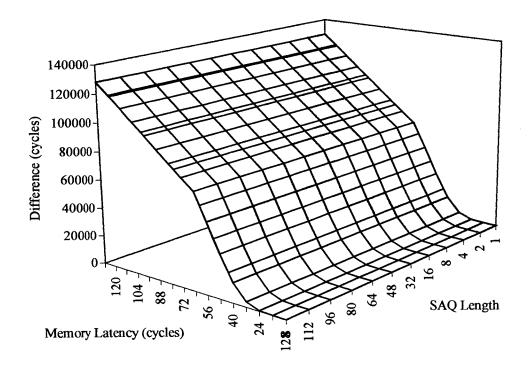

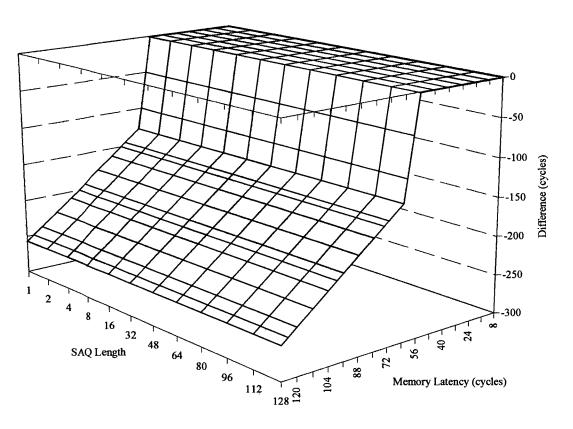

| Figure 31 - Runtime difference for SDQ lengths of 1 and 128. (Ex.3)                   | 85 |

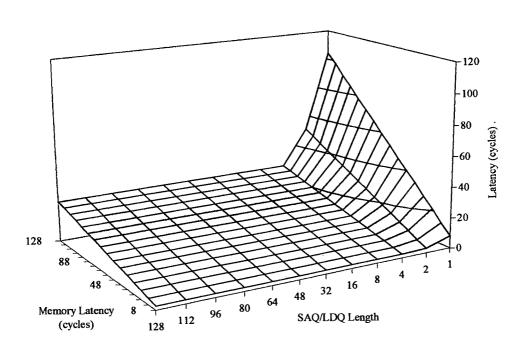

| Figure 32 - Difference between model and simulator runtime. (Ex. 3)                   | 86 |

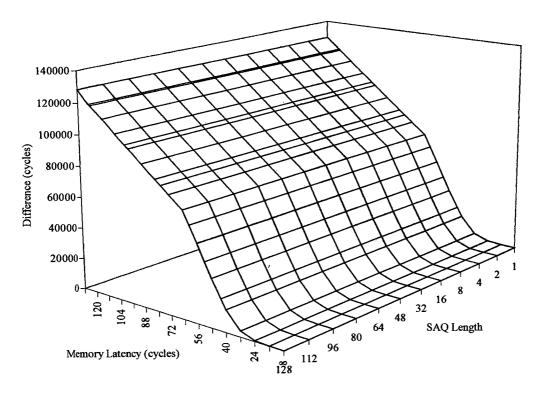

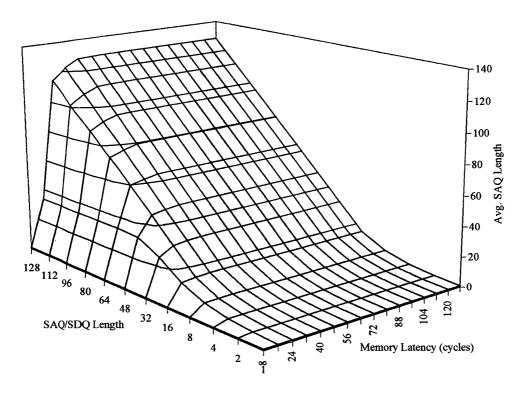

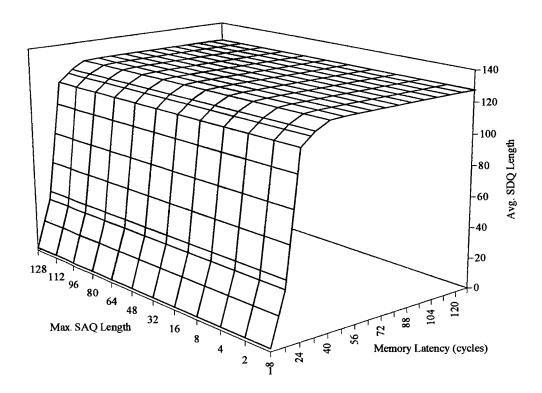

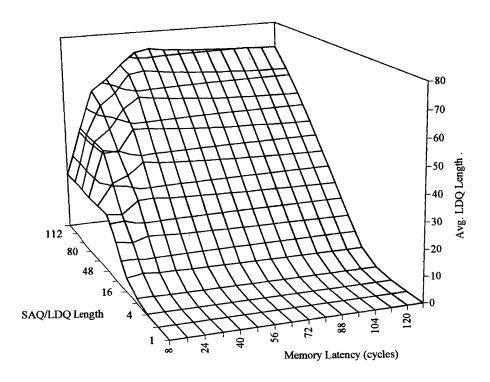

| Figure 33 - Simulator average SAQ length. (Ex. 3)                                   | 87  |

|-------------------------------------------------------------------------------------|-----|

| Figure 34 - Model average SAQ length. (Ex. 3)                                       | 88  |

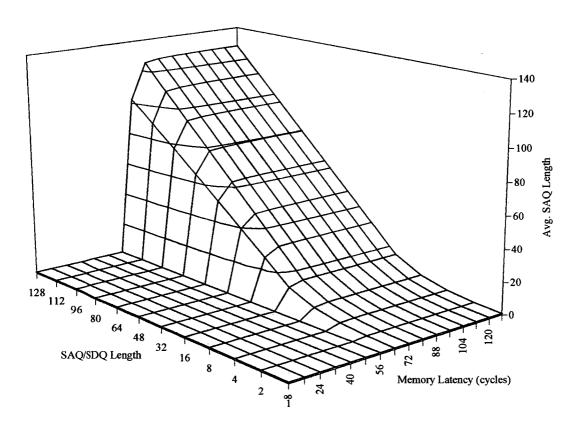

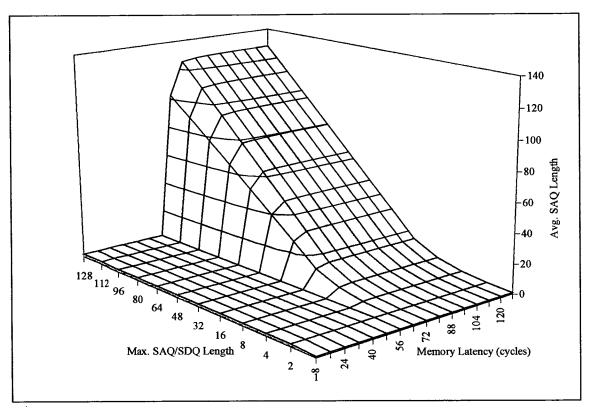

| Figure 35 - Simulated SDQ length when SAQ and SDQ lengths are varied. (Ex. 3)       | 89  |

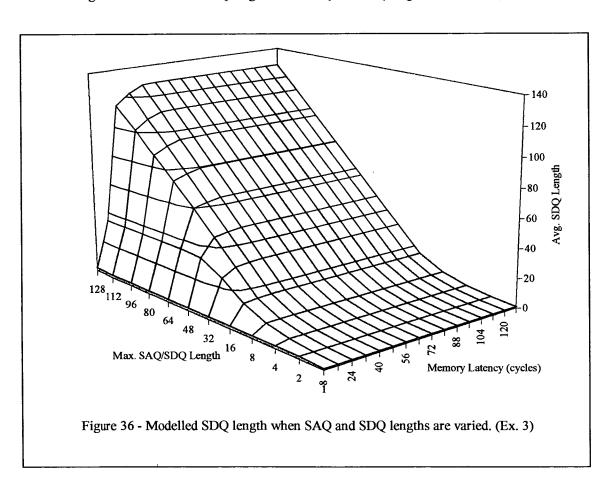

| Figure 36 - Modelled SDQ length when SAQ and SDQ lengths are varied. (Ex. 3)        | 89  |

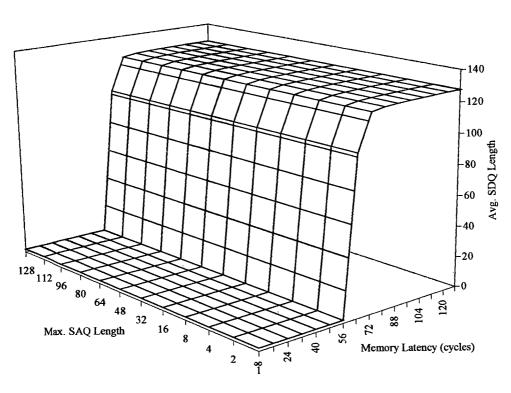

| Figure 37 - Simulated SDQ length when SDQ size is 128. (Ex. 3)                      | 90  |

| Figure 38 - Modelled SDQ length when SDQ size is 128. (Éx. 3)                       | 91  |

| Figure 39 - Data sub-processor runtime for first and second. (Ex. 4)                | 94  |

| Figure 40 - Data sub-processor runtime for third run. (Ex. 4)                       | 95  |

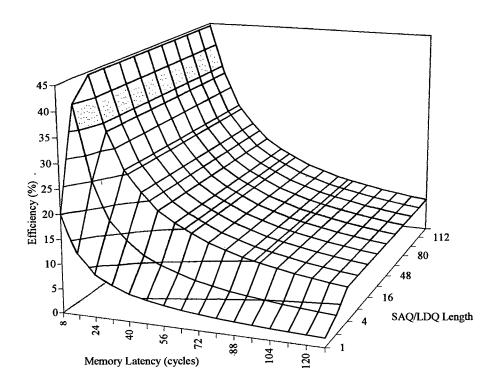

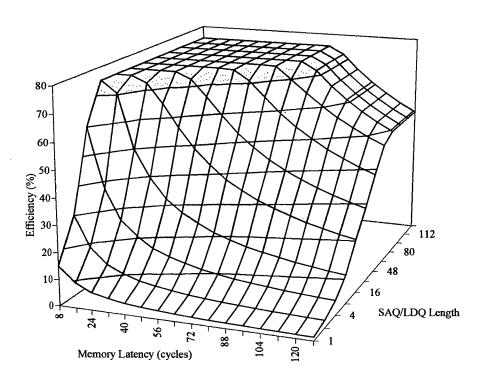

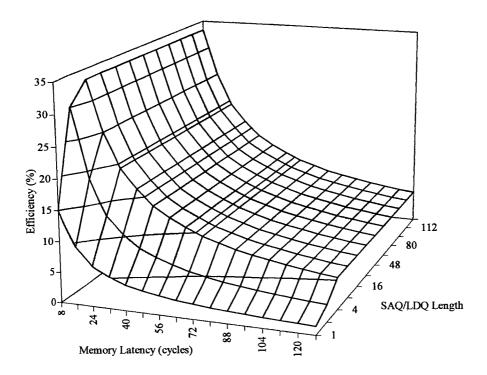

| Figure 41 - Data sub-processor efficiency for first and second runs (Ex. 4)         | 96  |

| Figure 42 - Data sub-processor efficiency for third run (Ex. 4).                    | 97  |

| Figure 43 - Address sub-processor efficiency for first and second runs. (Ex. 4)     | 98  |

| Figure 44 - Address sub-processor efficiency for third run. (Ex. 4)                 | 99  |

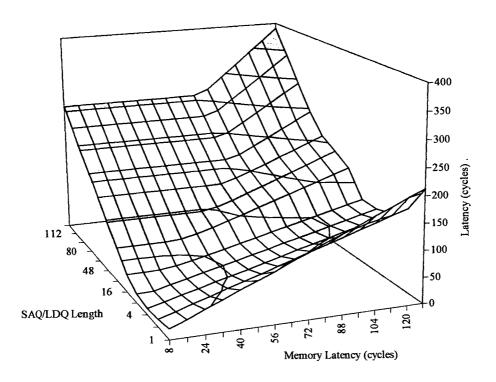

| Figure 45 - Actual memory latency for first run. (Ex. 4)                            | 100 |

| Figure 46 - Actual memory latency for second run. (Ex. 4)                           | 100 |

| Figure 47 - Actual memory latency for third run. (Ex. 4)                            | 101 |

| Figure 48 - Effective memory latency for first and second runs. (Ex. 4)             | 102 |

| Figure 49 - Effective memory latency for third run. (Ex. 4)                         | 102 |

| Figure 50 - LDQ length for first and second runs. (Ex. 4)                           | 103 |

| Figure 51 - Modelled data sub-processor runtime. (Ex. 4)                            | 104 |

| Figure 52 - Modelled LDQ length for all three runs (Ex. 4)                          | 105 |

| Figure 53 - Fully decoupled pseudocode for SAXPY loop.                              | 110 |

| Figure 54 - Data sub-processor runtime for first and second runs. (Ex. 5)           | 111 |

| Figure 55 - Data sub-processor runtime for third run. (Ex. 5)                       | 112 |

| Figure 56 - Data sub-processor effective latency for first and second runs. (Ex. 5) |     |

| Figure 57 - Data sub-processor runtime with hardware loop mode. (Ex. 5)             | 117 |

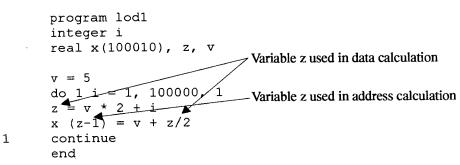

| Figure 58 - Kernel code. (Ex. 6)                                                    | 121 |

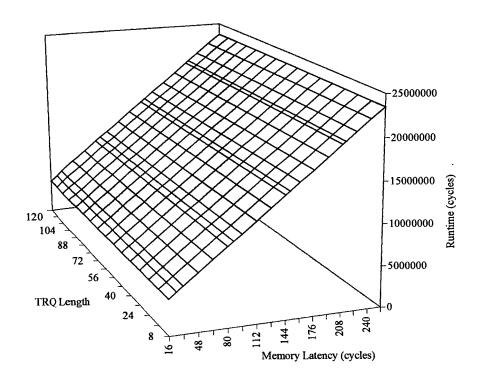

| Figure 59 - Total runtime for first run. (Ex. 6)                                    | 123 |

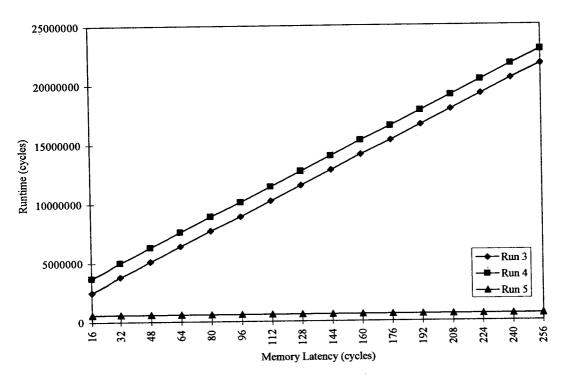

| Figure 60 - Total runtime for runs 3-5. (Ex. 6)                                     | 124 |

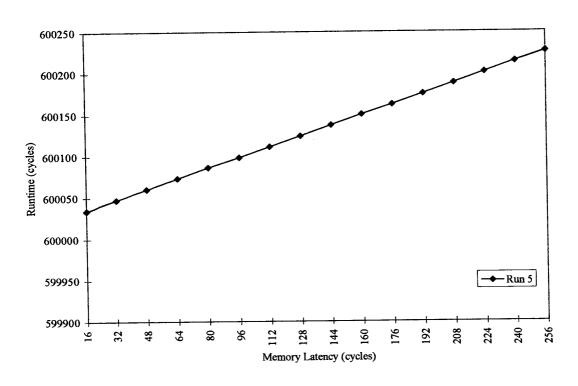

| Figure 61 - Total runtime for run 5. (Ex. 6)                                        | 124 |

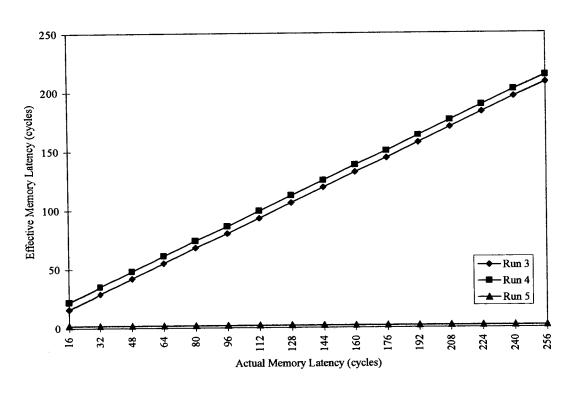

| Figure 62 - Effective latency for runs 3 to 5. (Ex. 6)                              | 126 |

| Figure 63 - Indirection in a Fortran loop.                                          | 127 |

| Figure 64 - Strip decoupling.                                                       | 130 |

| Figure 65 - Total runtime. (Ex. 7)                                                  | 132 |

| Figure 66 - Effective memory latency. (Ex. 7)                                       | 134 |

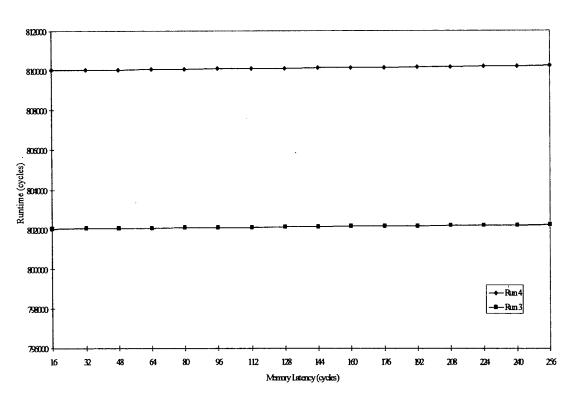

| Figure 67 - Total runtime for runs 3 and 4. (Ex. 7)                            | 135 |

|--------------------------------------------------------------------------------|-----|

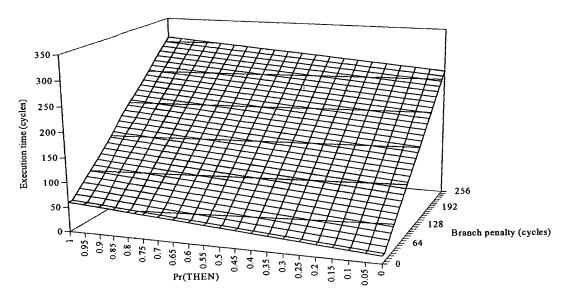

| Figure 68 - Execution time for conditional branch.                             | 142 |

| Figure 69 - Data sub-processor runtime for first run (Ex. 8)                   |     |

| Figure 70 - Data sub-processor runtime for second run (Ex. 8).                 | 146 |

| Figure 71 - Data sub-processor runtime for third run (Ex. 8).                  | 147 |

| Figure 72 - Data sub-processor runtime. (Ex. 9)                                | 152 |

| Figure 73 - Guarded pseudo-code for nested IF-THEN-ELSE                        |     |

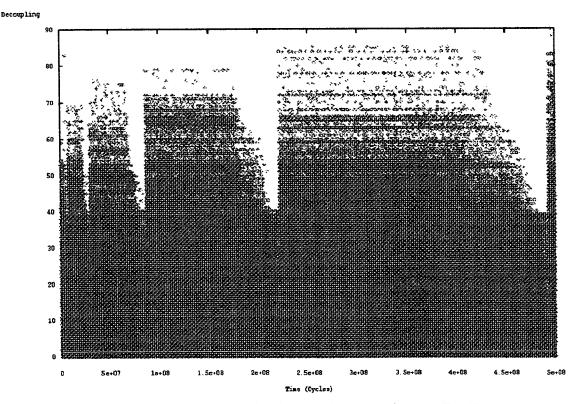

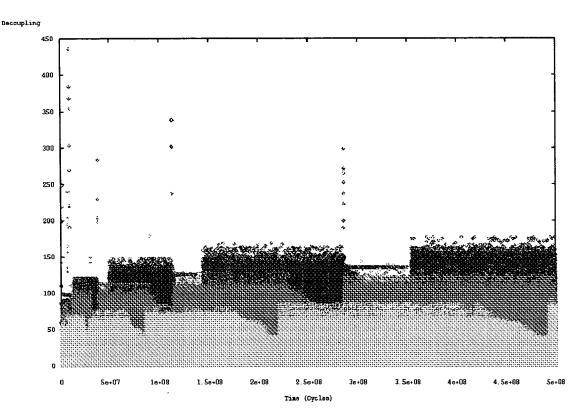

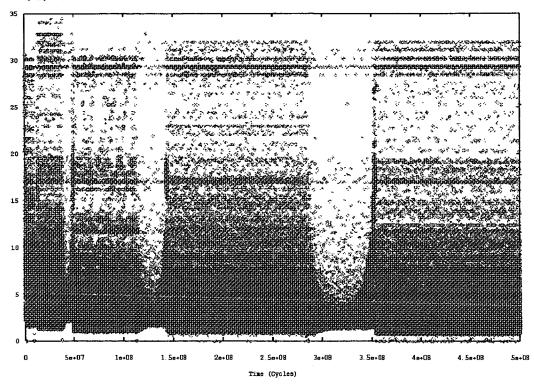

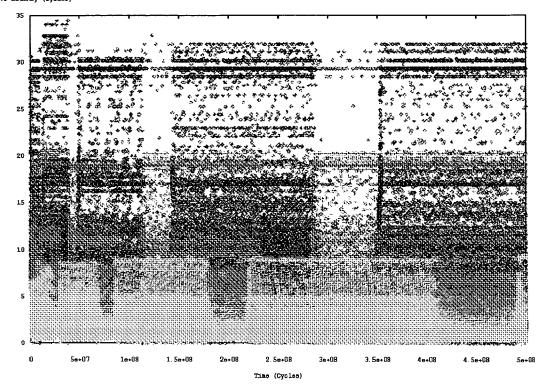

| Figure 74 - Degree of decoupling for 16 cycle memory latency. (Ex. 10)         | 163 |

| Figure 75 - Degree of decoupling for 32 cycle memory latency. (Ex. 10)         | 164 |

| Figure 76 - Degree of decoupling for 48 cycle memory latency. (Ex. 10)         | 165 |

| Figure 77 - Degree of decoupling for all three runs. (Ex. 10)                  | 166 |

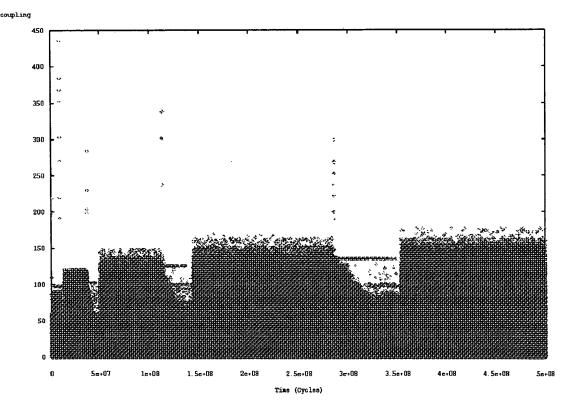

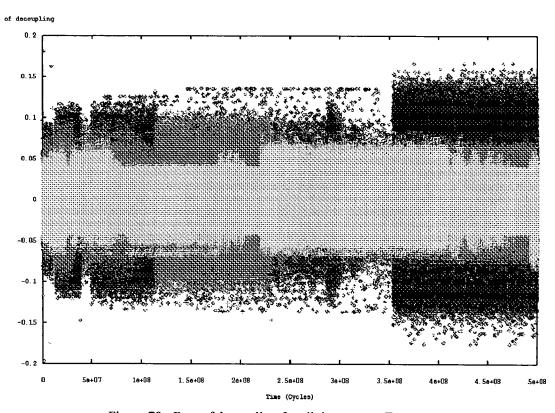

| Figure 78 - Rate of decoupling for all three runs. (Ex. 10)                    | 168 |

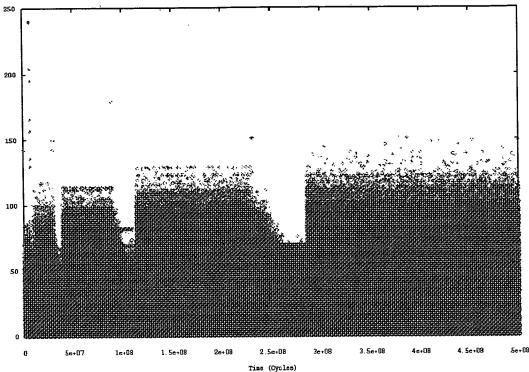

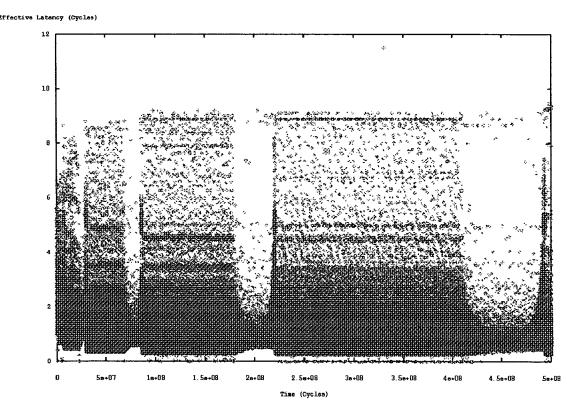

| Figure 79 - Effective latency for 16 cycle memory latency. (Ex. 10)            |     |

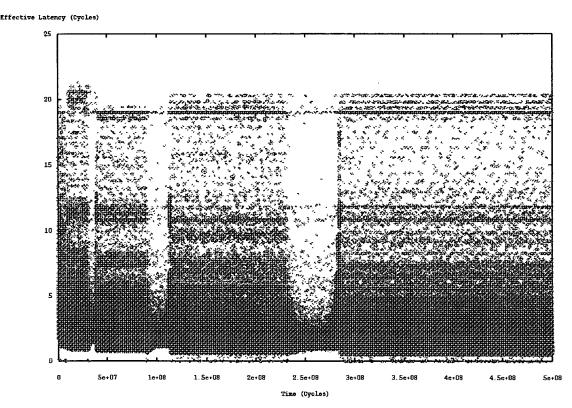

| Figure 80 - Effective latency for 32 cycle memory latency. (Ex. 10)            | 170 |

| Figure 81 - Effective latency for 48 cycle memory latency. (Ex. 10)            | 171 |

| Figure 82 - Effective memory latency for all three runs. (Ex. 10)              | 172 |

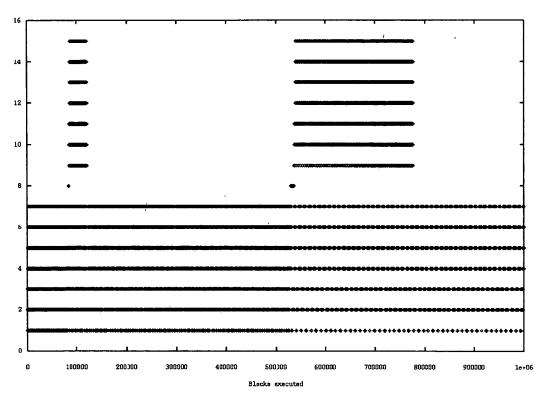

| Figure 83 - Block execution activity for Ex. 10                                | 174 |

| Figure 84 - An instruction cache preload mechanism.                            | 181 |

| Figure 85 - Deadlock in a multi-threaded dual load path decoupled architecture | 187 |

| Figure 86 - NDSP processing element                                            | 191 |

#### 1. Overview

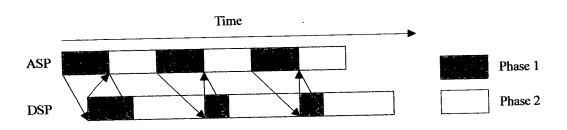

Fully decoupled processor architectures present one possible solution to the problems posed by the growing disparity between memory and processor speeds. Full decoupling is a fusion of two separate architectural techniques - access/execute decoupling and control decoupling.

The first of these separates program execution into two distinct sub-tasks - the access of data and the execution of arithmetic operations upon the data - and allows these sub-tasks to run asynchronously on dedicated processing units. This can in principle allow the access sub-task to run ahead of the execution sub-task, fetching data from memory sufficiently far in advance of the point in time at which it will be needed that memory latency can be hidden.

Control decoupling applies a similar asynchrony to the sub-tasks of control and calculation. In a control decoupled system, a dedicated processing unit traverses the program's control flow graph, attempting to determine the path that program execution will take sufficiently far in advance of the calculation sub-task that instructions can be fetched far enough in advance to hide their memory latency.

When both techniques are combined they can, in theory at least, produce a processor architecture with a high tolerance for long memory latencies, where the pre-fetching permitted by decoupling hides the latency of memory accesses for both instructions and data.

In this thesis I illustrate the capabilities of this class of architectures, examining which architectural parameters affect performance most strongly, and highlighting potential weaknesses in the architecture.

In Chapter 2 the problems associated with high memory latencies are examined, and a number of existing architectural techniques that aim to either hide or reduce memory latency are discussed. Chapter 3 presents the ideas behind both access-execute and control decoupling in more detail. Chapter 4 examines a number of possible techniques for modelling the behaviour of decoupled architectures, including analytical modelling, simulation, and a fusion of both techniques. The

model derived in this chapter is put to use in Chapter 5, in which a series of experiments are performed to determine the architectural parameters which most strongly influence the degree to which a decoupled processor can exploit both access/execute and control decoupling. A number of techniques to enhance decoupling, both software- and hardware-based, are presented.

Chapter 6 addresses the problem of loss of decoupling, a phenomenon whereby the two decoupled sub-tasks must resynchronize and thus temporarily lose their ability to mask memory latency. A further series of detailed experiments is performed to determine the causes and effects of loss of decoupling, as well as to examine the potential of a number of software- and hardware-based techniques to remove or reduce the impact of losses of decoupling.

The decoupling experiments in Chapters 5 and 6 were based upon the examination of a number of program kernels, short segments of code that illustrate some fundamental behaviour characteristic of certain classes of program. In Chapter 7 these results are validated in the context of real programs, by conducting a series of experiments based upon full-sized programs. The decoupling behaviour of these is analyzed with respect to the fundamental behaviours examined in the previous two chapters.

Finally, in Chapter 8, conclusions are drawn as to the potential of fully-decoupled architectures as well as their drawbacks, and several possible avenues for future research are described.

### 2. Introduction

#### 2.1 The Problem

As the 1990s have progressed the disparity between processor and main memory performance has increased inexorably. While the speed of main memory has risen for a number of reasons, this has been more than offset by the increased demands made of it by modern high-performance processors.

The improvements in memory performance are due to a number of factors. A fortuitous side effect of the drive for ever larger capacity memory ICs is a decrease in feature size which has in turn reduced memory cycle times. Page-mode dynamic RAM chips which allow sequential data to be accessed more efficiently have become commonplace, and DRAMs have also appeared which incorporate small internal caches of fast static memory.

At the same time, however, processor clock speeds have risen considerably. High-end microprocessors are at the time of writing typically clocked at somewhere between 300 and 400 MHz, and projections for the end of the 1990s show a steady climb towards clock speeds in the 500-700 MHz range. These high clock speeds place a heavy load on memory in terms of the instruction and data memory bandwidth required. Add to this the emergence of superscalar instruction issue, with several instructions being initiated per processor cycle and potentially issuing multiple requests to memory for data, and the gap between the low memory latencies that processors require and what a realistic memory system can provide becomes wider still.

A number of solutions have been proposed to deal with this problem. Most of these fall into two distinct categories: memory latency reduction and memory latency tolerance.

#### 2.2 Latency Reduction

Up until now the main thrust of research into improving computer performance has been closing the processor-memory gap, largely through the use of memory hierarchies such as caches. These work on the principle that, due to spatial and temporal locality in memory reference patterns, the vast majority of memory requests will be met by a fast, local cache. A penalty will be paid when there is

a cache miss, but these are sufficiently infrequent in most cases to have little effect on performance. The concept of caches and their behaviour are well understood and have been covered in detail in the literature, so the topic will not be covered in any depth here. Detailed coverage of the issues involved in cache design can be found in Chapter 8 of Hennessy and Patterson's *Computer Architecture: A Quantitative Approach* [HP90] and also in Hennessy, Horowitz and Przybylski's paper on cache design tradeoffs [Pr88] amongst others [Smth82].

The usefulness of caches is limited, however, since Amdahl's Law places a strict bound on the performance gains that can be obtained. Some proportion of memory accesses will always miss the cache and, as the gap between processor and memory speeds widens, the effect of these cache misses on overall performance increases. Even if the proportion of accesses that cause cache misses were to remain constant (which is by no means certain when dealing with shared memory multiprocessors and their requirements for cache coherency), processor performance will become increasingly limited by the disparity between processor and memory speeds due to the effects of these cache misses.

#### 2.3 Latency Tolerance

Most current techniques to close the gap in speed are, alas, only partially successful in treating the symptoms of this disparity. Also, these techniques attempt only to reduce the symptoms, not to cure the problem itself. In fact, it appears that no complete cure is yet possible, unless an unexpected technological breakthrough leads to a drastic reduction in memory latencies. There is another approach to the problem though - the development of processor architectures which are "immune" to long memory latencies. Heavily-interleaved memory systems are, once up to speed, quite capable of providing sufficient memory bandwidth to keep a modern processor supplied. The problem lies in creating a situation in which this high potential bandwidth can be reliably exploited, and the high latency (which no amount of interleaving can remove) of memory accesses has little or no effect on processor performance.

One way of achieving this is to dispense with the idea that a memory access is atomic. In most conventional modern processors, a load is a single indivisible operation, from the placing of the

address on the address bus to the arrival of the requested data on the data bus. If the data is not immediately available, the processor must stall until it arrives. Thus the latency of a load operation is directly determined by the latency of memory and it is through this method that the effects of slow memory are transmitted directly into the most immediate measure of processor performance, program execution time.

Similarly, when a store operation is initiated the processor waits for it to complete before proceeding. This is due to the need to prevent any subsequent store instruction from changing the contents of the address and/or data bus before the current store has completed.

The use of a cache mitigates these effects somewhat, since with a reasonably efficient (write-back rather than write-through) cache, most loads and stores complete within a cycle or two. However, on those loads that miss the cache and those stores that force a write-back (or all stores in a system with a write-through cache) the full latency of these operations becomes apparent and the processor is stalled, wasting many processor cycles that could conceivably have been used to perform other operations. By overlapping the load or store latency with other subsequent operations and thus hiding or masking the latency, its effect on the program's execution time could be reduced considerably.

Historically, a number of approaches have been tried that attempt to do this. They vary considerably, but all rely on the use of some form of non-blocking or *decoupled* load or store.

#### 2.4 Non-Blocking Stores

The idea of non-blocking stores is far from new, and is frequently encountered in the form of write buffers. In a system with a write buffer, the store address and data are placed in a temporary buffer until the store has been committed to memory. The processor can continue unhindered while the store completes. It is only necessary for the processor to stall if it tries to execute a load from the same memory location as the pending store (which would cause a read-after-write hazard) or if a second store is attempted before the first has completed.

However, even these two situations can be exploited in certain circumstances. A load attempting to access a location to which a store is still pending can take its data directly from the buffer, eliminating the need to stall. A second store to the same memory location can overwrite the value in the buffer, since no reads of the old value have been performed in the intervening time. By substituting a queue for the simple buffer and thus allowing multiple stores to be pending at any one time, stalls on stores can be eliminated in the vast majority of cases, although the need to compare any subsequent loads with the addresses of all pending stores requires additional hardware and also makes it difficult for a load to take its data directly from the buffer should a pending store to the same location be present.

The benefits of write buffers are particularly apparent in systems with write-through caches. In these systems the processor can potentially be stalled for a considerable amount of time, since all stores go directly to main memory as well as the cache. However, even in systems with a write-back cache the presence of a write buffer can help to mask the high latency of a cache miss. As will be seen later, the techniques used to mask store latencies in fully decoupled architectures are a natural extension of the write buffer concept.

#### 2.4.1 Non-Blocking Loads

The techniques that have been used to mask load latencies are more varied than those used to mask store latencies although, presumably due to the prevalence of caches, the area has been less widely explored. Historically, a number of approaches have been tried and these are briefly surveyed.

#### 2.4.2 The CDC 6600 Address Unit

Perhaps the simplest form of latency masking load appeared as long ago as the late 1960s, in the Control Data Corporation's CDC 6600 supercomputer [Ibb82]. This architecture implicitly split each load into two decoupled operations by virtue of its unconventional approach to memory accesses. The CDC 6600 possessed three distinct sets of registers. The A (address) registers were used, as their name suggests, for specifying addresses for memory accesses, although the method by which this was accomplished was unusual. The X (operand) registers were used to store the

operands for arithmetic operations, while the B (index) registers were used as offsets to memory accesses.

Loads were performed by storing an address (with an optional offset specified by a B register) into one of a certain subset of the A registers. This initiated the load operation, and the requested value appeared in the corresponding X register some number of cycles later (that is, write to A1 and the value at the address specified by A1 will eventually appear in X1). In the meantime, other operations could be performed, hiding the latency of the load. The register scoreboarding mechanism used in the CDC 6600 ensured that any instruction attempting to read the contents of a register in the process of being loaded from memory would stall until the access had completed.

A similar mechanism was used for stores, whereby storing an address to a certain subset of the A registers would cause the contents of the corresponding X register to be written to memory. Again, the scoreboard prevented either of the registers involved being overwritten before the operation had completed while allowing other operations that did not use those registers to proceed unhindered.

#### 2.4.3 Cache Preloading

In more recent times similar techniques [Sk92] [Smth82] [Chen95] has been employed by a number of architectures to preload data into the data cache. While this is not quite the same as decoupling a load into two distinct parts (the generation of the address and the fetching of the data), it does give similar benefits.

Preload instructions are statically inserted in the instruction stream some time before the data they access will actually be needed. Hopefully this will lead to the requested data being present in the data cache by the time it is needed.

This approach falls midway between reducing the *actual* latency through the use of a cache and reducing the *effective* latency by hiding the true latency of a possible cache fill underneath other operations. As such it combines elements of both latency reduction and latency tolerance and attempts to use some techniques commonly associated with the latter to improve the performance of the former.

An architecture that employs cache preloading may still occasionally block. There is no guarantee that the requested data will be fetched in time or, indeed, that it will be fetched at all. However, if the preload operation can be started sufficiently far in advance of the point at which the data is needed, the increased latency that might result from a cache miss and subsequent cache line fill will be hidden underneath any instructions executed between the issuing of the preload operation and the execution of the operation that will use the preloaded data.

This approach has both advantages and disadvantages. The primary advantage is, of course, the decrease in the number of visible cache misses and the subsequent reduction of the average effective latency. The technique also has the rather less obvious benefit of having no effect on the semantics of the load operation. There is no requirement that a memory access be preceded by a preload operation, which is little more than a hint to the memory system that the specified data is likely to be accessed in the near future and should be fetched into the data cache if possible. Preloads may be safely ignored without any change in program semantics. The only effect of ignoring a preload is a change in the effective memory latency.

This makes it practical to build a family of processors with the same instruction set architecture [A92] where, depending on how much money the customer wishes to spend on their processor, the preload operation may result in nothing happening at all, in a preload to cache being attempted, or in the specified data being moved up a single level in a multi-level memory hierarchy.

Those architectures which currently implement cache hints of this sort (such as Digital's Alpha architecture and the PA-RISC architecture from Hewlett Packard) tend to use them to provide an approximation of vector registers using the data cache. The preload operation (FETCH in the Alpha) optionally loads an aligned block around a specified address into cache which can then be accessed by the processor at cache speeds.

However, if the data cache has limited associativity or limited size problems can arise when preloading large data structures, such as long vectors or even fairly modest matrices. If the preload operation is executed sufficiently far in advance of the time at which the data will be required, a later

preload operation might cause data loaded by the first preload to be overwritten before it has been used. When the instructions that use the first preloaded data are reached not only will the full memory latency be visible, but the reloading of that data due to the cache miss may also result in the data that had been loaded by the second preload being overwritten before it is needed, necessitating that *that* data also be reloaded.

On the face of it, this may seem to be no worse than the well known situation in which two regularly accessed memory addresses cause a cache to "thrash" due to insufficient associativity. However, on closer inspection it can be seen that preloading means that each cache line would be loaded not once but twice per access, wasting considerable amounts of memory bandwidth and severely reducing performance. For this reason, the effectiveness of preloading is limited by the need to ensure that cache contention of this sort will not occur frequently, since in some cases the use of cache preloading can actually *reduce* performance.

The cache thrashing problem reveals another limitation of preloading. The need to ensure that cache contention or thrashing does not occur make it necessary that programmers or compilers take upon themselves the responsibility for explicitly managing the cache. This requires an awareness of the physical structure of the cache, such as the line size, number of lines, and associativity, and even then is likely to produce sub-optimal results due to the effects of non-preloaded cache accesses and those memory access characteristics that cannot be determined at compile time.

In addition, carefully tweaked code that goes to great pains to prevent cache contention may, if run on a machine with a larger or smaller cache (or even one with a differing degree of associativity), either fail to take advantage of the greater cache size or perform poorly. It could even be suggested that an architecture employing preloading would be better to dispense entirely with the notion of a separate cache and instead use an explicitly mapped and accessed area of fast scratchpad RAM, with data being loaded into the scratchpad by a decoupled load of the form described in Section 2.4.2.

A further limitation of cache preloading centres around the required distance between the preload instruction itself and the first use of preloaded data. It is frequently impossible to move the preload

far enough from the first use for the latency to be completely masked. For example, the Alpha architecture manual recommends that there should be no fewer than 64 unrelated instructions between a FETCH instruction and the first operation that uses the prefetched data. While it is true that this high figure is at least partly due to the Alpha FETCH operation preloading data in blocks of 512 bytes, it still illustrates the general principle that the required distance between preload and use may be large.

The problems this can cause are particularly noticeable in the case of tight loops. A tight program loop may result in it being impossible to separate a preload from the first use of the preloaded data by more than a handful of instructions, greatly reducing the usefulness of the technique. Techniques such as loop unrolling can reduce the effects of this problem but cannot always eliminate them. There will always be some cases in which there just are not enough instructions available between initiating the preload and the data being required to keep the processor busy.

#### 2.4.4 Dataflow

Finding plenty of instructions to execute is, however, the forte of dataflow architectures [Arv91]. These machines are, by their very nature, tolerant of long-memory latencies. Rather than instructions fetching their operands, the availability of operands results in the execution of instructions that act upon those operands. An instruction *cannot* wait for a value to return from memory in a dataflow architecture, since the instruction will not even be activated until its operands become available.

On the surface it would seem that dataflow, with its ability to exploit parallelism to the full and tolerate slow memory is the solution to all the problems of long memory latencies. However, this is not the case in practice. For one thing, the apparently non-existent memory access latency for instructions is due more to cleverly restating the problem than actually eliminating the latency. Also the complexity of dataflow architectures, both from an implementation and programming viewpoint, means that to date dataflow has failed to move beyond the realm of research and into the commercial sphere.

#### 2.4.5 Context Flow And Multi-Threading

Another architectural technique which has yet to be fully commercially exploited, but which at the time of writing seems to be a topic of considerable research interest in both industry and academia, is variously known as context flow or multi-threading [Dub94].

Multi-threaded architectures aim to obtain high throughput with the processor consistently running at near peak performance. They do this through the use of multiple independent processor contexts (each corresponding to one hardware thread of execution) which can be rapidly switched should the currently-running thread run into a possible delay. By the use of multiple threads, the processor can be kept busy until the cause of the delay (the latency of a memory access, or an inter-instruction dependency) has passed. Analogies can be drawn between the decoupled load mechanism of the CDC 6600 (where the gap between load initiation and completion is filled with instructions from the same process) and loads on a multi-threaded architecture where the gap between load initiation and completion is filled with instructions from a number of other, independent, threads.

Exactly what constitutes a "possible delay" can vary from architecture to architecture. At the pessimistic end of the spectrum, the assumption is that every single instruction can potentially cause a delay and that an implicit context switch should occur between each instruction regardless of whether any delay actually exists. More optimistically, there are architectures where context switches happen only on memory accesses or branches and the delays due to inter-instruction dependencies are tolerated. Both approaches have advantages and disadvantages [Lau94].

#### 2.4.5.1 Pessimistic Multi-Threading

The pessimistic approach can potentially achieve very high throughput if sufficient threads of execution are available. By ensuring that no two instructions in the processor pipeline are from the same context, delays due to inter-instruction dependencies are eliminated. Conditional branch penalties also vanish, since each instruction is completed before the next starts, which makes the architecture very suitable for superpipelining [Jou89]. Even memory latencies are hidden, as threads that are waiting for values to return from memory are suspended until such time as their data becomes available. From the point of view of a single thread, all memory accesses have zero latency.

As long as sufficient threads are available to keep the pipeline full, the processor can be kept busy continuously. This can be seen graphically in Figure 1, which shows the theoretical maximum throughput of a context-flow architecture for various numbers of available threads and hardware contexts. Note that when the number of threads exceeds the number of available contexts, throughput levels out onto a high plateau. The model used to produce this graph relies on the assumption that no thread will experience a delay longer than c cycles, where c is the number of hardware contexts available, but the general principle is clearly illustrated.

Figure 1 - Total throughput vs. contexts vs. threads

The pessimistic approach to multi-threading has two major shortcomings. The first is in the amount of silicon real-estate taken up by the large number of contexts. Since a context switch occurs between each and every instruction it is imperative that the switch be performed as quickly as possible [Gru96]. This rules out context switching techniques in which the thread's register set is completely or even partly written out to memory and reloaded when the context is next switched in. Generally the only practical way of implementing multiple contexts with no time penalty is through the use of a large partitioned register set. The implicit context switching would be implemented by associating a unique numeric tag with each hardware context. This tag would follow each

instruction from that context down the pipeline and also follow each memory reference to memory. It would be prepended to any register identifiers specified in the instruction to specify the appropriate partition of the register file to access. When sent to memory it would be used to reassociate a returning value from memory with the appropriate context.

If there were 64 hardware contexts, each of which had access to 32 64-bit general purpose registers, the register file would contain no less than 2048 64-bit registers. While this not inconsiderable size is well within the reach of mid-90s technology it is open to question as to whether this is a good use to put such a large area of silicon, especially since the register file utilisation will remain constant regardless of how large it becomes.

The second shortcoming is not a technical one but a result of the architecture's semantics. By ensuring that no single process has more than one instruction in the processor pipeline at any time, we ensure that at best each thread can only use a small fraction of the processing power available. On a processor with n pipeline stages and t hardware contexts, each thread can at best use only  $\frac{1}{n}$  th of the processor's total throughput, in the case where exactly n threads monopolise the processor and no delay is greater than n cycles. In the worst case, where there are more software threads than hardware contexts, each context can use only  $\frac{1}{n}$  th of the total throughput available (assuming that t > n) with the available throughput per software thread dropping in inverse proportion to the increase in the number of software threads competing for the available contexts.

So, while the throughput of the architecture as a whole may be high, no individual thread can attain more than a fraction of this performance. Thus, unless the application that is being run is inherently highly parallel, peak performance will be difficult to achieve, since a reduction in the number of runnable software threads will not produce a corresponding increase in per-thread performance.

Although a typical workstation may be running many processes at a time (user shells and applications, a window manager, assorted daemons) these heavyweight processes would be unable to exploit multi-threading, other than internally, since their enlarged contexts would contain additional

information such as cache TLB entries, which would have to be switched in the conventional manner. To obtain high performance from a multi-tasking system would also require that each of the processes was itself multi-threaded.

Figure 2 - Per thread throughput vs. contexts vs. threads.

If the number of active threads in a multi-threaded processor drops below the length of the processor pipeline, bubbles will form due to the one instruction per thread restriction. The effect of this on per-thread performance is illustrated in Figure 2. This shows the proportion of total throughput available to a single thread as the number of hardware contexts and runnable software threads are varied. No account has been taken here of the additional performance penalty that would be incurred by having to save and restore hardware contexts in the conventional sense when there are more threads than contexts, and it is also assumed that the processor has a CPI of 1, and is thus capable of 100% throughout. For this reason, Figure 2 actually gives an optimistic estimate of per-thread throughput.

#### 2.4.5.2 Optimistic Multi-Threading

An optimistic approach to multi-threading overcomes many of the shortcomings of pessimistic multithreading, at the expense of additional complexity. Exactly what constitutes "optimistic" can vary, but the general guideline is that a context switch should be performed only when necessary. It is in the precise definition of "necessary" and the measure of what constitutes an unacceptable delay in execution that variations arise.

In the most extreme form of optimistic multi-threading, contexts are switched whenever a real delay, of whatever kind, is encountered. This has the advantage over pessimistic multi-threading that contexts are switched only when real, rather than potential, delays are encountered. The restriction on the number of active instructions from a single context is relaxed, allowing several instructions from the same context to be in the processor pipeline at any one time, as long as none but the last will cause any pipeline stalls.

This means that, as long as delay-causing instructions do not occur too frequently, it should be possible to keep the pipeline full with a smaller number of active threads, and for each of those threads to potentially use a greater proportion of the total processor throughput. This in turn means that fewer hardware contexts may be required. In an extreme case, a single thread with no instructions that cause delays can utilise 100% of the processor throughput if all the other threads are stalled for some reason.

While the optimistic approach to multi-threading is undoubtedly more flexible than the pessimistic one, there are costs associated with this added flexibility. The pipeline requires some form of scoreboard to identify inter-instruction dependencies and switch contexts as necessary, as well as a mechanism for switching contexts on a cache miss and restarting the delaying instructions when the hazard or delay has passed. It may also be necessary to provide some form of pre-emptive switch between contexts (in addition to any higher level pre-emptive multi-tasking), otherwise a number of threads with long runs of non-delaying instructions could monopolise the processor, starving the other threads.

There are, of course, a number of variations in between the extremes of "switch context on every potential delay", "switch context on every real delay" and "do not switch context at all". Since delays can be caused by a number of events (an instruction dependency, a branch in control flow, a

long latency memory access) and these delays all have differing costs, it may be desirable to choose from the three possibilities listed above.

An architecture may ignore the delays due to inter-instruction dependencies and conditional branches and allow pipeline bubbles to form, since the delays due to these are usually short, while switching context whenever a memory access instruction is encountered. Alternatively, it may ignore the delays due to inter-instruction dependencies, always switch contexts when a conditional branch is encountered, but only switch contexts if a memory access results in a cache miss. There are many possible combinations.

A detailed examination of multi-threading is, however, outside the context of this thesis. There is, however, much in the literature on this topic, ranging from discussion of multi-threading in multi-processors [Kur91] to more rigourous analytical examinations of the performance aspects of multi-threading [Dub94].

It should be stressed that multi-threading is being examined here only as an alternative latency tolerance technique. It is by no means considered inferior to the latency tolerance technique with which this thesis is primarily concerned, namely decoupling. The not-inconsiderable volume of research underway in the multi-threading field in the mid-90s is ample evidence of the technique's potential and, as we will see later, there is no reason that multi-threading cannot be combined with decoupling.

#### 2.4.6 Decoupling

The concept of decoupling is far from new. As described in Section 2.3.3., the CDC 6600 architecture used a form of decoupled memory access to provide some tolerance of high memory latencies. Several contemporary architectures have also introduced some form of decoupling between the integer and floating point (FP) units of the processor, to "smooth out" differing rates of integer and FP computation and prevent integer operations being delayed by unrelated high latency floating point instructions.

The architectures with which this thesis is concerned use two forms of decoupling - control decoupling and access/execute decoupling. The combination of these two is known as full decoupling. These are described in detail in Chapter 3. Simply stated, the first of these separates the task of traversing a program's control flow graph from the actual computation that occurs at each node of that graph. One processor follows the flow graph, dispatching high-level descriptions of the code to be executed at that node in the graph to "work processors" which execute the code itself.

Access/execute decoupling [Ben91], on the other hand, separates the work allocated by the control processor into the task of generating the addresses for memory accesses and that of performing the actual computation. Both of these provide a natural method of extracting low-level parallelism and, as will be shown, are possible sources of latency tolerance for instruction and data memory accesses respectively [Kur94].

While fully decoupled architectures are a novelty (only one, the ACRI-1, has begun development to date [Top95] [Bird93], machines using access/execute decoupling are not a new development.

The origins of access/execute decoupled architectures can be traced to the early 80s with the PIPE architecture [Goo85] [You88] [Far91] and its successor MISC [Tys92], and the work of James E. Smith at the University Of Wisconsin, who wrote several seminal papers on the subject [Smit82] [Smit84]. This research eventually gave rise to the Astronautics ZS-1, an access/execute decoupled mini-supercomputer. Although this is amply described in the literature ([Smit87] [Smit89] [Mang91]) this architecture, being the only decoupled architecture to reach full commercial production to date, is worthy of closer examination and will be discussed in some detail in the next chapter. More recent access/execute architectures include the Rockwell/DARPA funded research into the HiDISC architecture at the University of Southern California [Cra96] and W.A. Wolf's WM architecture [Wol92].

# 3. Decoupled Architectures

#### 3.1 Access/Execute Decoupled Architectures

Access/Execute decoupled architectures, as their name suggests, exploit the relatively independent nature of the memory access and data manipulation (or execution) tasks that make up a program. By separating, or decoupling, these tasks and running them concurrently, considerable performance gains can be obtained.

The first of these, the access task, is responsible for generating the memory address of data that is to be used by the execute task and either initiating the loading of that data from memory or providing the store address for a store operation. The generation of memory addresses may be straightforward, requiring only that the access task send the address of a scalar variable to memory, or it may be complex and require additional computation to convert the indices of a multi-dimensional array into a linear offset which, when added to the base address of the matrix, gives the actual address of the memory location to be accessed.

The second of these tasks, the data task, takes data arriving from memory, performs operations on it, then stores the result to memory. Since, for the most part, these two tasks are relatively independent and require very little in the way of inter-task communication, they provide an excellent source of low-level parallelism. In an access/execute architecture, each task runs on a separate specialised sub-processor, a processing unit that has much of the functionality of a conventional processor yet is unable to function without its companion sub-processor. These sub-processors may be further optimised for their role, with the mixture of available functional units and the design of their internal data path and instruction set reflecting their role. They are also likely to include certain specialised architectural structures which will be described shortly.

The splitting of a program into access and execute tasks is a relatively straightforward process, since the two tasks are naturally partitioned. This is not, however, immediately obvious from conventional architectures since these typically arbitrarily mix together instructions from the two tasks. This lack of separation of the two tasks can even inhibit performance, since it complicates the scheduling of instructions on today's superscalar architectures [Far93]. However, superscalar instruction issue and access/execute decoupling are by no means mutually exclusive. There is no reason why the two subprocessors of an A/E decoupled machine cannot themselves be superscalar, and it is possible that the separation of the two tasks might even allow a greater degree of low-level parallelism to be extracted from them.

The main benefits of access/execute decoupling are that it allows the easy exploitation of this natural low-level parallelism, and that since the two tasks are now running (almost) independently and asynchronously, the access sub-processor can run ahead of the data sub-processor and fetch operands from memory before they are actually needed. This is particularly advantageous when the system's memory latency is high, since it allows the address sub-processor to fetch data sufficiently far in advance that the required data is delivered to the data sub-processor before it actually needs it. The data sub-processor is thus able to use it immediately, with no noticeable delay due to memory latency. The memory latency is thus hidden and, as long as the address sub-processor can run sufficiently far ahead of its companion, the architecture exhibits latency tolerance.

This characteristic is valuable in high performance uniprocessors, where the processor clock cycle may be considerably smaller than the memory cycle time. For example, a mid-90s high performance processor may have a processor cycle time of 3ns or lower yet still use 60ns DRAM for its main memory. Latency tolerance is also of use in multiprocessor systems, where accesses to memory that is not local to a processing node may have a very high latency due to it having to traverse an interconnection network.

At the time of writing, access/execute architectures represent the state of the art with regard to the commercial use of decoupling. Although fully decoupled architectures, which will be described in the next section, have been designed, only access/execute decoupling has reached the marketplace so far, albeit with little commercial success.

Figure 3 - The Astronautics ZS-1 CPU.

Two distinct families of access/execute decoupled architectures have emerged. These differ primarily in the degree to which they separate the address and data sub-processors.

#### 3.1.1 Single instruction stream architectures

The first of the two families of access/execute decoupled architectures considers the two subprocessors to be little more than functional units of a conventional processor, or even just a particular partitioning of the functional units of a conventional processor. The resulting processor appears relatively conventional externally, with a single instruction data path. However, it splits the instruction stream internally and routes each instruction to either the address or the execute unit.

The Astronautics ZS-1 (discussed briefly in Chapter 2) is the most important example of this type of "instruction-splitting" decoupled A/E architecture. This machine, shown in Figure 3, has a single instruction stream. Instructions are fetched from a small 16K instruction cache (which in turn fetches them from a larger 64K unified cache) and fed into an instruction splitter. This decodes the instruction opcode and routes it to one or the other of the units, depending upon the operation to be performed. Compare instructions also set a branch bit in the splitter unit, allowing later conditional branch instructions to test the value before splitting occurs. The various queues allow decoupled

loading and storing, loading and storing directly to/from the access unit and the transfer of data between the two units.

The primary advantage of this particular form of decoupled A/E architecture is that it can exploit the parallelism and latency tolerance inherent in access/execute decoupling, whilst appearing relatively conventional externally. The only oddity in the ZS-1 instruction set is the unconventional approach to load and store operations, whereby the load instruction implicitly stores a value in the appropriate queue on the access unit with loaded data being accessed explicitly via top-of-queue registers on the execute unit. There is, however, no reason that a processor of this type could not use the instruction set of an existing processor. Additional decoding of loads and stores in the splitter unit would result in appropriate instructions being placed in the instruction queues and copies between address and data registers could be achieved via the copy queues (again by decoding and splitting internally). Architectures with unified, general purpose register files would present a problem, although it is possible that some form of run-time dependency analysis along with a register renaming scheme could work around the possible implicit inter-unit dependencies that might result.

One problem with this approach, however, is that the use of a single instruction stream severely limits the degree to which the two units can decouple, with the inter-unit asynchrony (or, to use the term coined by Smith, dynamic slippage) being limited by the size of the internal instruction queue. Dual instruction stream architectures represent one way of increasing the degree to which decoupling can be exploited.

#### 3.1.2 Dual instruction stream architectures

The second approach to access/execute decoupling separates the two tasks more completely and is illustrated in Figure 4. Rather than treating the two units as functional units of a single processor, they become more independent. Each has its own instruction stream and the asynchrony is bounded not by the size of internal queues but by dependencies within the program itself. These dependencies occur when the two units must communicate. This can happen if the address unit requires a data value for one of its calculations (e.g. indirection, list following) or if a control decision must be made. The control decision can either be made by collaboration between the two instruction fetch

units (which handle control flow) or on the sub-processors themselves. In the majority of cases only one of the two units will make the control decision, however, and the result of this decision must be communicated to the other sub-processor.

Figure 4 - A dual instruction stream access/execute decoupled architecture.

If the sub-processor making the decision is the address unit, this is not a problem. This unit will typically attempt to run ahead of the data unit providing latency tolerance. Should it be responsible for making a control decision such as evaluating the branch at the end of a loop, it will pass the result of this to the other unit. This incurs no performance penalty, although the degree of decoupling may be limited by the size of the queues via which this information is transferred.

However, if the control decision has to be made on the data unit, such as breaking out of a loop when a particular value is encountered, this information has to be communicated to the address unit. This will typically require the address unit to stop and wait until the data unit "catches up". This is known as a loss of decoupling (LOD) and, as we will see later, is the major drawback of decoupled architectures. Loss of decoupling appears to be less of a problem in single stream architectures, since control decisions are made before the decoupling point and all instructions in the instruction queues

can be safely executed without a LOD occurring. However, since there is less decoupling in a single stream architecture anyway, no performance improvement is obtained.

The other main disadvantage of dual instruction stream architectures concerns the instruction fetch mechanism. Surprisingly, instruction bandwidth is not one of them, since instructions (other than those involved with memory accesses) appear in one or other of the instruction streams, but rarely both. Some code bloat is inevitable, but the increase in object code size is not prohibitive. However, the instruction fetch hardware itself must be duplicated and the memory access patterns produced by the fetching of instructions are less predictable than those of, for example, a dual-issue superscalar architecture. This can be mitigated somewhat through the use of separate instruction caches for each unit but this once again increases the complexity of the architecture.

#### 3.1.3 Decoupled loads and stores

Having stated that decoupled loads and stores are a good thing, they will now be described and details given of exactly why this is the case.

Before beginning, however, some terminology will be introduced. The two parts of a decoupled processor can be referred to by a number of names. Each part is known either as a *sub-processor* or a *unit*. The two terms are interchangeable although the former is preferable when discussing an architecture with multiple instruction streams and the latter is used only for brevity. The sub-processor concerned with generating memory addresses is known as the *address* or *access* sub-processor, while the other is known as the *data* or *execute* sub-processor. Generally the former term (which describes the type of data processed by the unit) is preferable, although the latter (which describes the task it performs) is also acceptable.

Memory accesses are known as *memory packets* and are split into two types. The address subprocessor generates *load packets* which contain the memory address to be accessed as well as other information, the purpose of which will be described later. When a load packet reaches memory the address is used to fetch the appropriate data and a *load response packet* is generated containing the data and other information (some of which may be copied from the first packet). A *store packet* contains data and an address and is "absorbed" by memory.

It should be noted that the use of the term "packet" in no way implies that the memory sub-system uses packet switching. In practice this may well be the case, especially if the processor is part of a multi-processor system, but the term has been chosen chiefly because in most cases the data or address is accompanied by additional information, the whole forming a "packet" of information.

The ideas behind non-blocking loads were discussed in Section 2.4.1. By splitting a load operation into two parts - one that generates the address and one that uses the fetched data - a processor need not necessarily stall while waiting for data to arrive from memory. If the first part of the operation can be issued sufficiently far ahead of the second, the memory latency can be hidden entirely from the "receiving" instruction. In a decoupled access/execute architecture, the two parts of the operation execute on different sub-processors, and in a "good" program the address generating part of the operation can be issued far in advance of the time at which the other unit will need the data. Since the two units run asynchronously, the address sub-processor can potentially initiate many such loads ahead of the time at which the data will be required. Since all of these could complete before the data sub-processor executed its part of even the first load, queues are necessary to buffer load packets that have arrived but not yet been used.

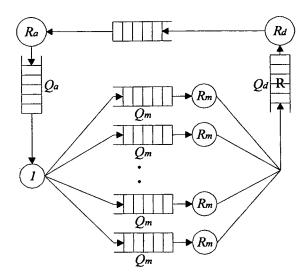

Two queues are used (see Figure 4). The first, the Load Address Queue or LAQ, is part of the address sub-processor and is used to store load packets that are waiting to be sent to the memory sub-system. This provides some degree of decoupling between the address sub-processor and the memory sub-system should, for one reason or another, the memory be incapable of accepting load packets as quickly as the address sub-processor can produce them. The second queue is known as the Load Data Queue or LDQ. This is part of the data sub-processor and stores load packets that have arrived from memory but which have yet to be used. This decouples the data sub-processor from memory, acting as a buffer when packets arrive too quickly for it to cope.

It can be seen above that the load path in fact consists of two decoupled processes, between address sub-processor and memory and memory and data sub-processor respectively. It is assumed that a well-specified memory sub-system will be capable of accepting load packets at least as fast as they can be produced, if the memory access pattern is reasonably uniform. On a machine with a single load path, this will be one load packet per cycle, or a multiple of this if there are multiple load paths. This is generally achieved through the use of highly banked, interleaved memory where the number of banks matches or exceeds the latency of the individual banks when measured in processor clock cycles. To use the example figures quoted earlier, if the processor has a cycle time of 3ns and memory has a cycle time of 60ns, each memory cycle takes 20 processor cycles to complete. If the address sub-processor generates a load packet on every cycle, it can initiate 20 loads during a single memory latency, which requires that memory be 20-way interleaved if full throughput is to be achieved even if memory accesses are "perfect" and access each bank in sequence. In practice some degree of over-banking will be required to handle the less-than-perfect access patterns typical of real programs.

The two decoupled processes that make up the load path can generally be thought of as a single process as long as the memory is sufficiently well-specified. If it has insufficient bandwidth it is always going to stall the address sub-processor eventually, and the rate of production and consumption of load packets will be bounded by the rate at which the memory subsystem can process them. A well-specified memory sub-system will present no bottleneck to the two sub-processors, with load packets arriving at the data sub-processor at the same rate that they were sent by the address sub-processor.

Two decoupled processes are also involved when data is stored to memory, although there is no "chain" between the two as with loading. When the address sub-processor executes a store instruction, it places the address to which the stored data should be sent in the Store Address Queue (SAQ). Similarly, when the data sub-processor encounters a store instruction, it places the appropriate data into the Store Data Queue (SDQ). The heads of both of these queues are paired and

assembled into a store packet containing both address and data information, which is then dispatched to memory.

Both of the decoupling processes involved here are between a sub-processor and memory. The SAQ decouples the address sub-processor from memory and buffers addresses should they be generated faster than the memory sub-system can accept them, while the SDQ decouples the data sub-processor in a similar fashion. The rate at which store packets are actually dispatched to the memory sub-system is the minimum of the rates at which the two sub-processors generate their respective halves of the store packet. Since the address sub-processor generally runs ahead of the data sub-processor, it will usually be the case that the SAQ will fill until the data sub-processor reaches its first store. At this point stores will begin to be dispatched to memory. This seems to suggest that the SDQ might be redundant, since arriving data will almost always be immediately paired with an address and sent to memory. Whether this is in fact the case will be investigated in the next chapter.

Another design feature that will also be evaluated in a later chapter is one that appeared in the ZS-1 - a dedicated memory path for the address sub-processor. As can be seen in Figure 3, the address sub-processor is connected to memory by two "extra" queues, the ALQ and ASQ, which allow it to load and store data directly from/to memory without requiring the co-operation of the data sub-processor. The standard justification for this design feature is that it allows the address sub-processor to perform such tasks as spilling or reloading registers, performing indirection and list following without causing a loss of decoupling. The alternative would be to perform a decoupled load then pass the value returned to the address sub-processor via the transfer queues, which are described in the next section.

#### 3.1.4 Inter-unit transfers

From time to time it is necessary for information to be passed from one of the sub-processors to the other. There are two ways in which this can be achieved. The most straightforward method, and that employed by both the ZS-1 and the sample dual stream machine shown in Figure 3, is to use architectural queues. These are mapped into the sub-processor's register file and may be accessed as registers in a similar manner to those queues concerned with loading and storing. This method is

easy to use and fast but requires a considerable amount of additional hardware. Two extra queues are needed, and the internal data path of each sub-processor is complicated by the mapping of the queue heads onto register file.

A cheaper alternative, if the address sub-processor has a dedicated path to memory, is to perform inter-unit transfers via memory. For example, to transfer data from the address sub-processor to the data unit, the address sub-processor would first issue a self-store then initiate a decoupled load to the other unit. A transfer in the other direction would be achieved by performing a decoupled store then executing a self-load on the address sub-processor.

### 3.1.5 The problems of distributed control

The main weakness of access/execute decoupling is the need to communicate control information from one sub-processor to the other on each control decision. The single stream architecture only suffers from this problem to a minor extent, since the state information required for control flow decisions can be centralised in the instruction splitter, through which instructions for both units flow. This single locus of control means that control flow decisions are only complicated on those occasions where a decision is made based on information from *both* of the sub-processors.

In a dual stream architecture, however, the distributed nature of flow control is more of a problem. Each control decision must be communicated to the other unit, which can result in a loss of decoupling. One possible solution is to centralise the control. While this will not always eliminate the loss of decoupling, it does have many other advantages. Separating the execution of a program into three separate threads - access, execute and control - results in what is known as a Fully Decoupled Architecture.

# 3.2 Fully Decoupled Architectures

The ideas behind fully decoupled architectures are rather newer than those behind access/execute decoupling. The concept was first proposed by Peter Bird et al in 1991 [Bird91] who termed this a "semantically-driven architecture". This name arose through the partitioning of the program onto specialised processing units closely following the various components of the computing formalism

known as Action Semantics [Moss94]. The control task corresponded closely to the interpretation of the structure of the action semantics "rules", the access task to the binding of variables and the execution task to the semantic evaluation.

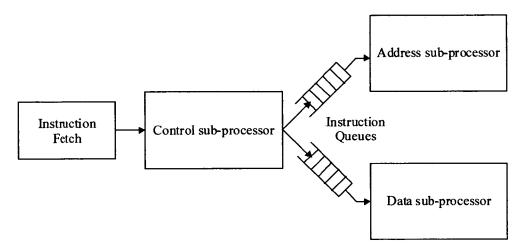

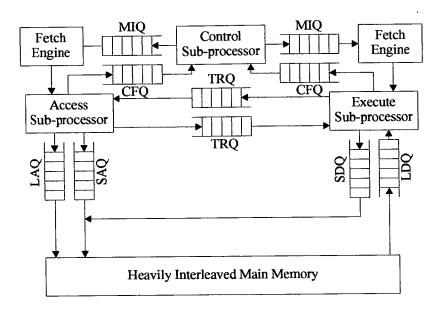

Figure 5 - A simple instruction dispatch mechanism.

A fully decoupled architecture has three sub-processors. Two of these are already familiar from access/execute decoupling, while the control sub-processor performs all control flow decision making and dispatches instructions to the other sub-processors. It can do this in one of two ways. The first, and simplest, is illustrated in Figure 5. All instructions pass through the control unit and are either executed on the control sub-processor directly (control flow instructions) or passed to one of the other two units. In this respect the architecture differs little from the ZS-1, except that the control sub-processor is more complex than a mere instruction splitter and that conditions are evaluated on the other sub-processors then passed back to the control SP to be acted upon.

Given the similarity between this approach to control decoupling and the ZS-1's treatment of access/execute decoupling, it should come as no surprise that this single instruction stream form of full decoupling suffers from the same problem - the available degree of decoupling between the control unit and the other units (and also between the sub-processors themselves) is limited by the size of the instruction queues.

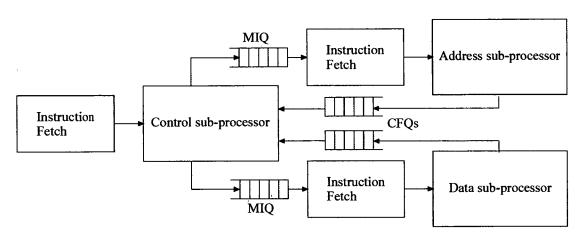

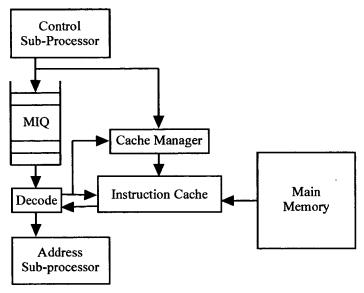

The second approach to control decoupling rectifies this problem. It makes use of the fact that control flow instructions are only a small proportion of the total instructions that make up a program and each control instruction (a branch back to the beginning of a loop, a subroutine call) typically is followed by a sequence of uninterrupted instructions (a basic block). Since reaching a particular node in the control flow graph means that *all* of the instructions directly associated with that node are going to be executed, there is no need for the control processor to individually fetch and dispatch each instruction. Instead, as shown in Figure 6, it places "meta-instructions", high level basic-block descriptors that describe a sequence of sub-processor level instructions, in the meta-instruction queue, or MIQ. This queue does not feed directly into the sub-processor pipeline as with the simpler scheme but instead feeds into a specialised instruction fetch mechanism, or Fetch Engine. This is responsible for removing meta-instructions from the MIQ, decoding them and fetching the instructions which it then feeds to the sub-processor. Thus, a processor using this variety of full decoupling has three separate instruction streams.

Figure 6 - A meta-instruction dispatch mechanism.

The access and execute sub-processors are known collectively as the work units because they do all the work, while the control sub-processor just tells them what to do. They are able to pass results back to the control SP which it then uses to make control flow decisions. This is done via yet another set of queues, the Condition Feedback Queues (or CFQs). These have the usual purpose of allowing some degree of decoupling to be maintained even if the rates at which results are produced and consumed differ.

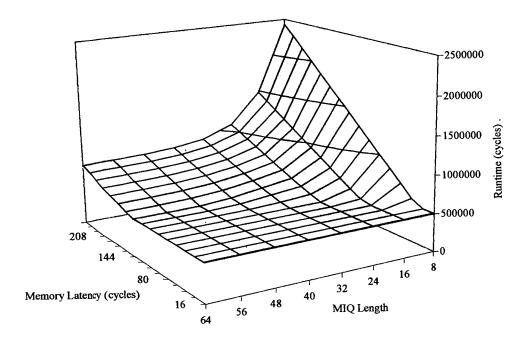

# 3.2.1 MIQ and CFQ design issues

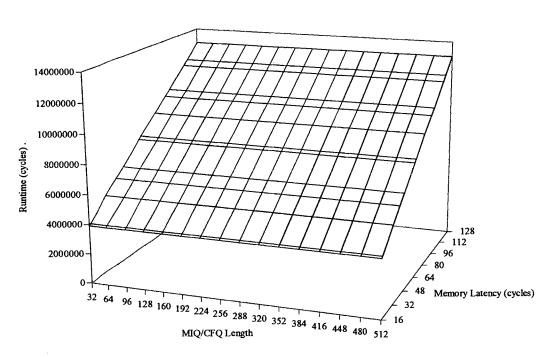

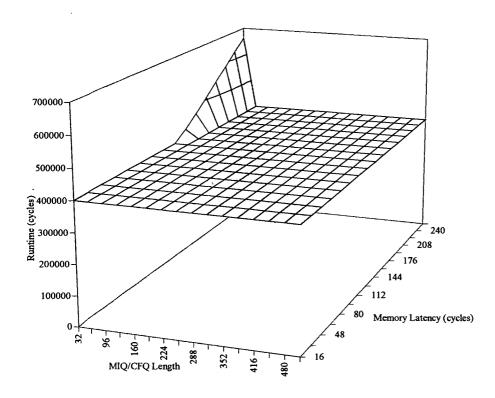

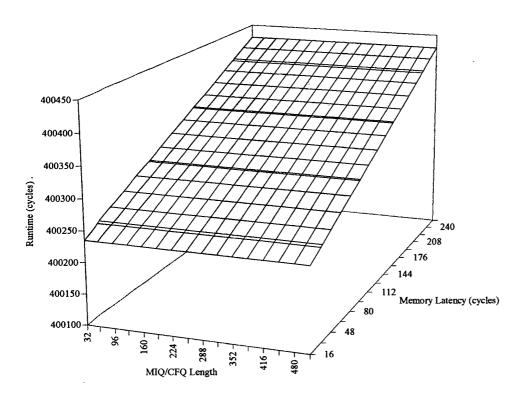

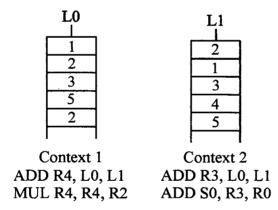

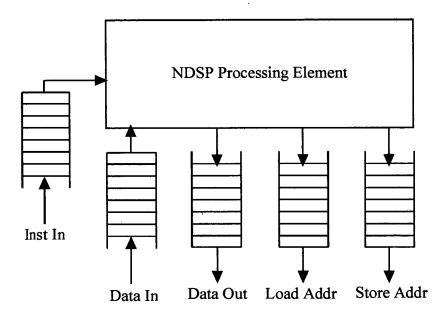

Unlike the other queues discussed so far, where the width has depended entirely upon the data or address size for the particular architecture, the width of the CFQ and MIQ is a design parameter.