# Communication Centric Platforms for Future High Data Intensive Applications

## Balal Ahmad

Thesis submitted for the degree of Doctor of Philosophy.

The University of Edinburgh

March 2009

# **Declaration Of Originality**

| I declare that this thesis is my original work except where stated |

|--------------------------------------------------------------------|

|                                                                    |

| Student Name: Balal Ahmad                                          |

| 2000                                                               |

|                                                                    |

|                                                                    |

| Signed:                                                            |

|                                                                    |

| Date:                                                              |

| <del></del>                                                        |

# **ACKNOWLEDGMENTS**

Pursuing a PhD has been a long and rather unique journey in my life. I would like to take this opportunity to express my gratitude to those who helped me through this journey.

The first person I would like to thank is my supervisor Professor Tughrul Arslan. I have been very fortunate to have Prof. Arslan as my supervisor. I am very grateful to him for giving me a chance to pursue my PhD in Edinburgh University. Without his valuable guidance and support this work would not have been possible. Many thanks Prof. Arslan for everything.

Having had a chance to work on SOCCAD project also brought me in contact with Dr Ali Ahmadinia. I have thoroughly enjoyed working with him. His technical advice and precise suggestions during my PhD are whole heartily appreciated.

I would also like to thank Dr. Ahmet Erdogan who always was available when I needed his advice. I extend a sincere thanks to all members of System Level Integration Group at Edinburgh University for their support and motivation.

I would especially like to thank my cousin Major Majid for his helpful suggestions throughout my University life. I won't be where I am now without his helpful advice and support.

Living at Edinburgh has been a pleasant experience and would not have been possible without the moments I shared with Wahiba, Sadie, Moynaa, Mikhail, Alyas and Omar. Thanks for helping me keep my sanity.

Very special thanks to my parents and their prayers which have supported me throughout my life.

"Tell your heart that the fear of suffering is worse than the suffering itself. And that no heart has ever suffered when it goes in search of its dreams." \_\_\_The Alchemist by Paulo Coelho

# **Publications**

### **Refereed Conferences**

#### On Dynamically Reconfigurable Network on Chip

"Dynamically Reconfigurable NoC with Bus Based Interface for Ease of Integration and Reduced Design Time" – Balal Ahmad, Ali Ahmadinia, Tughrul Arslan. In Proceedings of IEEE NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2008), 22-25 June 2008. European Space Agency, Noordwijk, Netherlands. Pages: 309-314

"Architecture of a Dynamically Reconfigurable NoC for Adaptive Reconfigurable MPSoC" – Balal Ahmad, A. T. Erdogan, S. Khawam. In Proceedings of IEEE NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2006), 15-18 June 2006. Istanbul, Turkey. Pages: 405-411.

"Dynamically Reconfigurable NoC for Reconfigurable MPSoC" - Balal Ahmad, Tughrul Arslan. In the proceedings of IEEE 2005 Custom Integrated Circuits (CICC 2005), 18-21 September 2005. San Jose, USA. Pages: 277-280.

#### On Communication Centric Platforms and systemC modelling

"SystemC-based Reconfigurable IP Modelling for System-on-Chip Design" – Ali Ahmadinia, Balal Ahmad, A T Erdogan, Ahmet T, Tughrul Arslan. In Proceedings of IEEE NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2008),22-25 June 2008. European Space Agency, Noordwijk, Netherlands. Pages: 362-367

"SystemC-based Custom Reconfigurable IP Cores for Wireless Applications" - Ali Ahmadinia, Balal Ahmad, Ahmet Erdogan, Tughrul Arslan. In the Proceedings of Engineering of Reconfigurable Systems and Algorithms (ERSA 2008), 14-17 July 2008. Las Vegas, USA.

"High-Level Power Estimation for Multi-Standard Wireless Systems."- Ali Ahmadinia, Balal Ahmad, Tughrul Arslan. In Proceedings of IEEE Computer Society Annual Symposium on VLSI (ISVLSI 2008), 7-9 April, 2008. Montpellier, France, pp. 275-280.

"Communication Centric Modelling of System on Chip Devices Targeting Multi-Standard Telecommunication Applications" - Ali Ahmadinia, Balal Ahmad, and Tughrul Arslan. In Proceedings of IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 7-9 April, 2008. Montpellier, France, pp. 209-214.

"Communication Centric Platform Based Designs for Future MPSoC" – Balal Ahmad, Ali Ahmadinia, Tughrul Arslan. 6th International Bhurban Conference on Applied Sciences and Technology, 2008. January 2009, CESAT, Pakistan.

"Hybrid Communication Media for Adaptive SoC Architectures" - Balal Ahmad, Ali Ahmadinia, and Tughrul Arslan. In Proceedings of NASA/ESA Conference on

Adaptive Hardware and Systems (AHS 2007), 5-8 August 2007. Edinburgh, U. K., pp. 373-378,.

"System Level Reconfigurable FFT Architecture for System-on-Chip Design." - Ali Ahmadinia, Balal Ahmad, and Tughrul Arslan. In Proceedings of NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2007), 5-8 August 2007. Edinburgh, U. K., pp. 169-175.

"System-level Modelling and Analysis of Embedded Reconfigurable Cores for Wireless Systems." – Ali Ahmadnia, Balal Ahmad, Tughrul Arslan. - In Proceedings of International Conference on Field-Programmable Logic and Applications (FPL 2007). 27-29 August 2007. Amsterdam, Netherlands, pp. 757-760.

# **Abstract**

The notion of platform based design is considered as a viable solution to boost the design productivity by favouring reuse design methodology. With the scaling down of device feature size and scaling up of design complexity, throughput limitations, signal integrity and signal latency are becoming a bottleneck in future communication centric System-on-Chip (SoC) design. This has given birth to communication centric platform based designs.

Development of heterogeneous multi-core architectures has caused the on-chip communication medium tailored for a specific application domain to deal with multi-domain traffic patterns. This makes the current application specific communication centric platforms unsuitable for future SoC architectures.

The work presented in this thesis, endeavours to explore the current communication media to establish the expectations from future on-chip interconnects. A novel communication centric platform based design flow is proposed, which consists of four communication centric platforms that are based on shared global bus, hierarchical bus, crossbars and a novel hybrid communication medium. Developed with a smart platform controller, the platforms support Open Core Protocol (OCP) socket standard, allowing cores to integrate in a plug and play fashion without the need to reprogram the pre-verified platforms. This drastically reduces the design time of SoC architectures. Each communication centric platform has different throughput, area and power characteristics, thus, depending on the design constraints, processing cores can be integrated to the most appropriate communication platform to realise the desired SoC architecture.

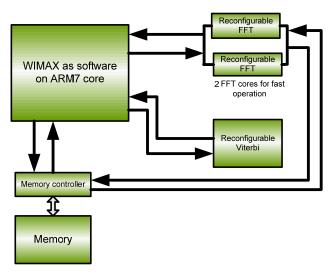

A novel hybrid communication medium is also developed in this thesis, which combines the advantages of two different types of communication media in a single SoC architecture. The hybrid communication medium consists of crossbar matrix and shared bus medium. Simulation results and implementation of WiMAX receiver as a real-life example shows a 65% increase in data throughput than shared bus based communication medium, 13% decrease in area and 11% decrease in power than crossbar based communication medium.

In order to automate the generation of SoC architectures with optimised communication architectures, a tool called SOCCAD (SoC Communication architecture development) is developed. Components needed for the realisation of the given application can be selected from the tool's in-built library. Offering an optimised communication centric placement, the tool generates the complete SystemC code for the system with different interconnect architectures, along with its power and area characteristics. The generated SystemC code can be used for quick simulation and coupled with efficient test benches can be used for quick verification.

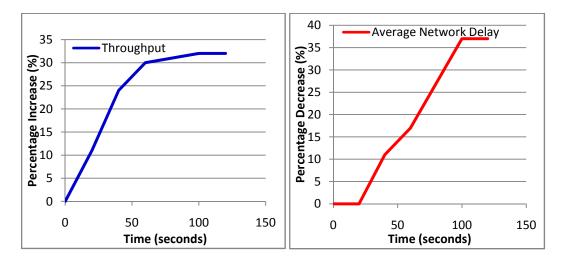

Network-on-Chip (NoC) is considered as a solution to the communication bottleneck in future SoC architectures with data throughput requirements of over 10GB/s. It aims to provide low power, efficient link utilisation, reduced data contention and reduced area on silicon. Current on-chip networks, developed with fixed architectural parameters, do not utilise the available resources efficiently. To increase this efficiency, a novel dynamically reconfigurable NoC (drNoC) is developed in this thesis. The proposed drNoC reconfigures itself in terms of switching, routing and packet size with the changing communication requirements of the system at run time, thus utilising the maximum available channel bandwidth. In order to increase the applicability of drNoC, the network interface is designed to support OCP socket standard. This makes drNoC a highly reuseable communication framework, qualifying it as a communication centric platform for high data intensive SoC architectures. Simulation results show a 32% increase in data throughput and 22-35% decrease in network delay when compared with a traditional NoC with fixed parameters.

# **Table of Contents**

| Chapte | er 1 I | NTRODUCTION                                        | 17 |

|--------|--------|----------------------------------------------------|----|

| 1.1    | Mot    | ivation                                            | 17 |

| 1.2    | Aut    | hor's contribution                                 | 18 |

| 1.3    | Roa    | dmap of thesis                                     | 20 |

| 1.4    | Sur    | nmary                                              | 21 |

| Chapte | er 2 L | ITERATURE REVIEW – Communication Centric Platforms | 22 |

| 2.1    | Intr   | oduction                                           | 22 |

| 2.2    | Bas    | ics of On-chip Communication                       | 24 |

| 2.3    | Bus    | Based On-Chip Communication                        | 26 |

| 2.     | 3.1    | Shared Bus based communication architectures       | 27 |

| 2.     | 3.2    | Commercially developed shared buses                | 30 |

| 2.4    | Hie    | rarchical bus                                      | 33 |

| 2.5    | Cor    | nmunication centric platform                       | 34 |

| 2.     | 5.1    | IBM CoreConnect                                    | 35 |

| 2.     | 5.2    | ARM AMBA                                           | 37 |

| 2.     | 5.3    | Palmchip CoreFrame                                 | 38 |

| 2.     | 5.4    | Sonic's Silicon Backplane                          | 39 |

| 2.6    | Bus    | Features Overview                                  | 40 |

| 2.7    | Per    | formance Metrics                                   | 41 |

| 2.8    | Sur    | nmary                                              | 42 |

| Chapte | er 3 L | ITERATURE REVIEW – Network on Chip                 | 44 |

| 3.1    | Net    | work on chip                                       | 44 |

| 3.2    | Bas    | ic Concept of NoC                                  | 44 |

| 3.3    | Phy    | sical Layer                                        | 46 |

| 3.4    | Arc    | hitecture & Control                                | 46 |

| 3.     | 4.1.   | Data Link Layer                                    | 47 |

| 3.     | 4.2    | Network Layer                                      | 47 |

|        | 3.4.2  | .1 Routing in NoC                                  | 49 |

|        | 3.4.2  | .2 Contention Awareness                            | 51 |

| 3.     | 4.3    | Transport Layer                                    | 52 |

|        | 3.4.3  | .1 Network flow Control                            | 52 |

|   | 3.5    | NoC as Communication Centric Platforms               | 53 |

|---|--------|------------------------------------------------------|----|

|   | 3.6    | Development History                                  | 53 |

|   | 3.7    | Advantages of NoC                                    | 55 |

|   | 3.8    | Analysis of NoC                                      | 56 |

|   | 3.9    | Summary                                              | 57 |

| C | hapter | 4 Proposed Communication Centric Platforms           | 58 |

|   | 4.1    | Introduction                                         | 58 |

|   | 4.2    | Proposed Communication Centric Platform              | 59 |

|   | 4.2    | .1 Platform Controller                               | 61 |

|   | 4.2    | .2 Interfacing                                       | 63 |

|   | 4.2    | .3 Communication media                               | 63 |

|   | 4.3    | System Level Modelling                               | 66 |

|   | 4.3    | .1 Proposed Modelling Level                          | 67 |

|   | 4.3    | .2 Programming Language Choice                       | 69 |

|   | 4.4    | Proposed Communication Centric Platform modelling    | 69 |

|   | 4.5    | Simulation Results                                   | 73 |

|   | 4.5    | .1 Verification of Bus based platform                | 73 |

|   | 4.5    | .2 Verification of crossbar based platform           | 76 |

|   | 4.5    | .3 Verification of Hierarchical and hybrid platforms | 79 |

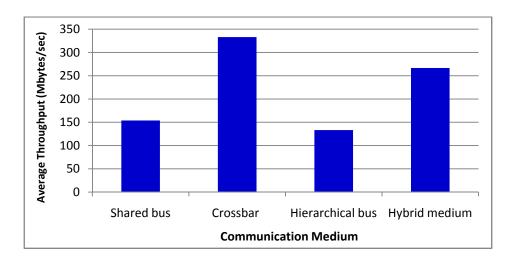

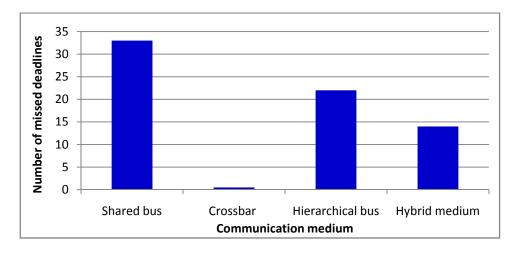

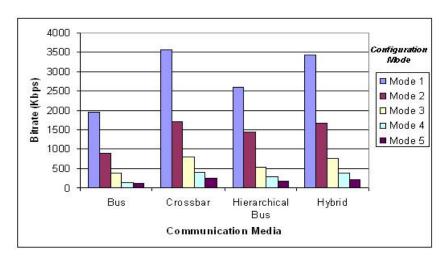

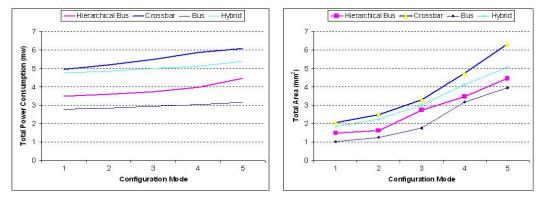

|   | 4.5    | .4 Throughput comparison                             | 81 |

|   | 4.5    |                                                      |    |

|   | 4.6    | Real World Example                                   | 91 |

|   | 4.7    | Summary                                              | 95 |

| C | hapter | 5 SOCCAD Tool                                        | 96 |

|   | 5.1    | Introduction                                         |    |

|   | 5.2    | Current SoC architecture development tools           |    |

|   | 5.3    | SOCCAD Tool                                          |    |

|   | 5.4    | Tool Design Flow                                     |    |

|   | 5.5    | Tool Demonstration with Real life example            |    |

|   | 5.6    | Summary 1                                            |    |

| C | hanter | c 6 Dynamically Reconfigurable NoC                   | 09 |

| _ | 6.1    | Introduction                                         |    |

|   | 6.2    | Proposed dynamically reconfigurable NoC              |    |

|   | 6.3    | Network architecture and Control                     |    |

|   | 6.3    |                                                      |    |

|   |        | •                                                    | 13 |

|        | 5.3.2.1 Routing Algorithm for packet switching | 114 |

|--------|------------------------------------------------|-----|

| 6.     | 3.3 Data Link layer                            | 115 |

| 6.     | 3.4 Physical Layer                             | 116 |

| 6.4    | SystemC Modelling of drNoC                     | 116 |

| 6.5    | Network Analysis                               | 120 |

| 6.6    | Explanation of Simulations                     | 130 |

| 6.7    | Summary                                        | 131 |

|        |                                                |     |

| Chapte | er 7 Conclusion and Future Work                | 132 |

| 7.1    | Introduction                                   | 132 |

| 7.2    | Summary of Thesis                              |     |

| 7.3    | Summary of achievements                        | 134 |

| 7.4    | Conclusions                                    | 135 |

| 7.5    | Future Work                                    | 136 |

|        |                                                |     |

| Refere | nces                                           | 138 |

# **List of Figures**

| Figure 2-1 Global bus architecture with an arbiter [KYE-001]                | 27 |

|-----------------------------------------------------------------------------|----|

| Figure 2-2 Global bus architecture with registers [KYE-001]                 | 28 |

| Figure 2-3 Global bus architecture with Bi-FIFO [KYE-001]                   | 29 |

| Figure 2-4 Crossbar Switch Bus Architecture [KYE-001]                       | 30 |

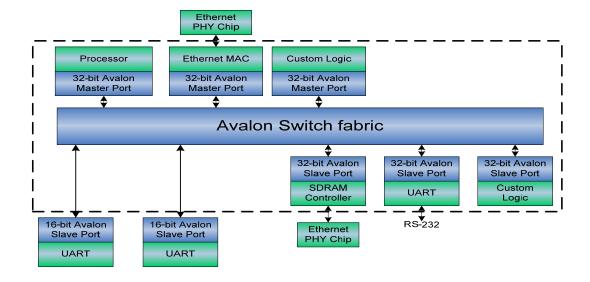

| Figure 2-5 Avalon bus based system [ALT-002]                                | 30 |

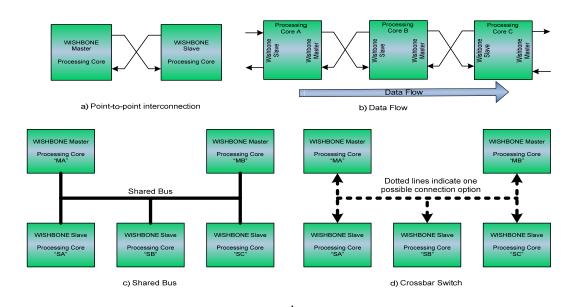

| Figure 2-6 Wishbone interconnections [AYA-001]                              | 31 |

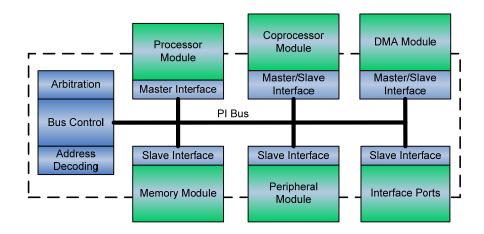

| Figure 2-7 PI (Peripheral interconnect) bus architecture [MIL-001]          | 32 |

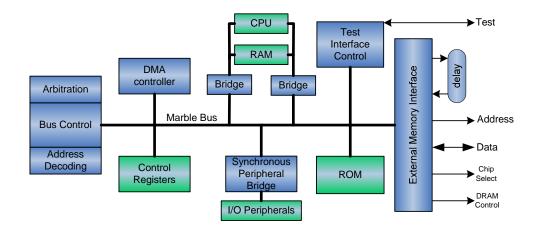

| Figure 2-8 The AMULETH3H System [BAI-001]                                   | 33 |

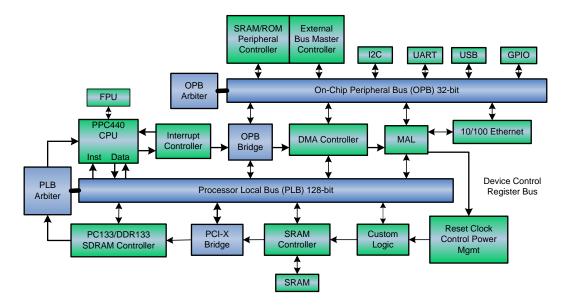

| Figure 2-9 CoreConnect platform architecture [IBM-001]                      | 35 |

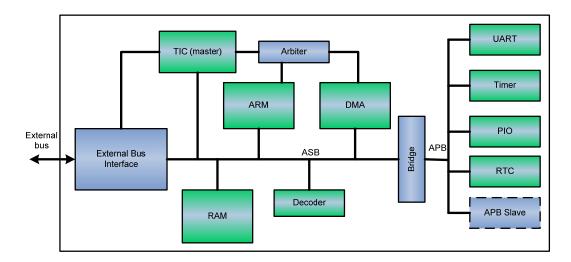

| Figure 2-10 AMBA platform architecture [ARM-001]                            | 37 |

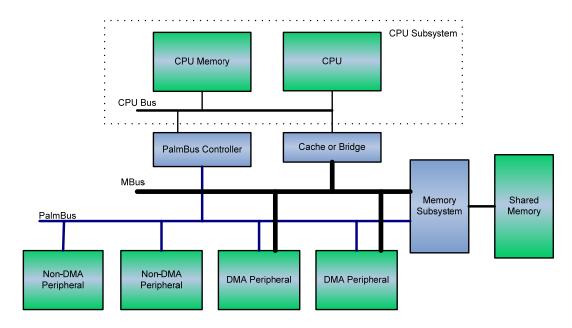

| Figure 2-11 CoreFrame platform architecture [PAL-001]                       | 38 |

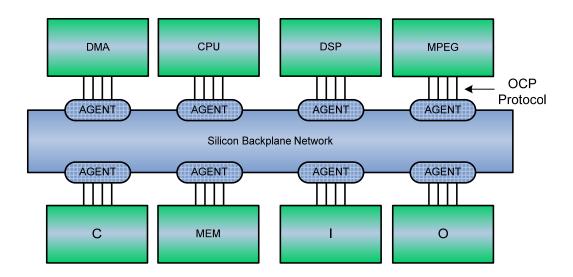

| Figure 2-12 SiliconBackplane platform architecture [SON-001]                | 39 |

| Figure 3-1 Basic NoC architecture                                           | 45 |

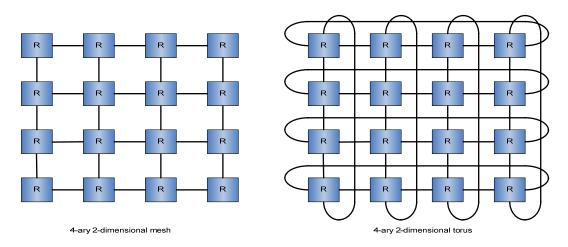

| Figure 3-2 Orthogonal Topology – (Mesh and Torus networks)                  | 48 |

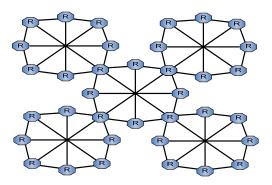

| Figure 3-3 The Octagon Topology                                             | 49 |

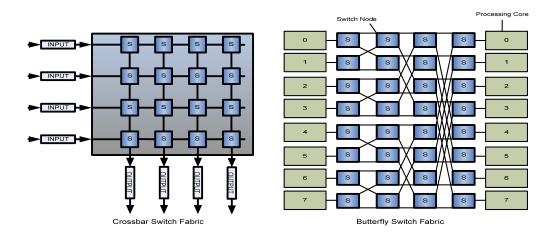

| Figure 3-4 Indirect Network Topologies                                      | 49 |

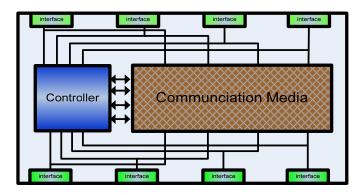

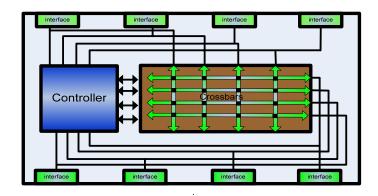

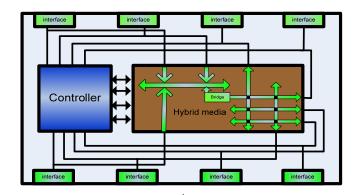

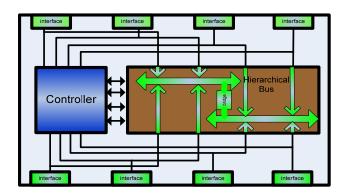

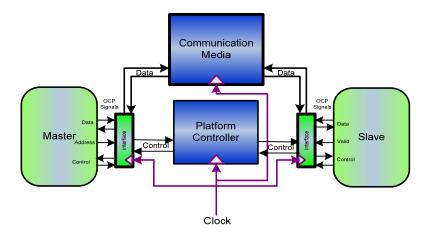

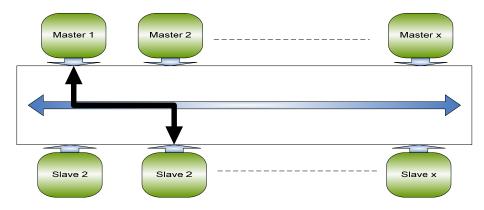

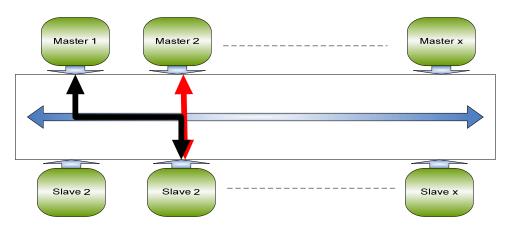

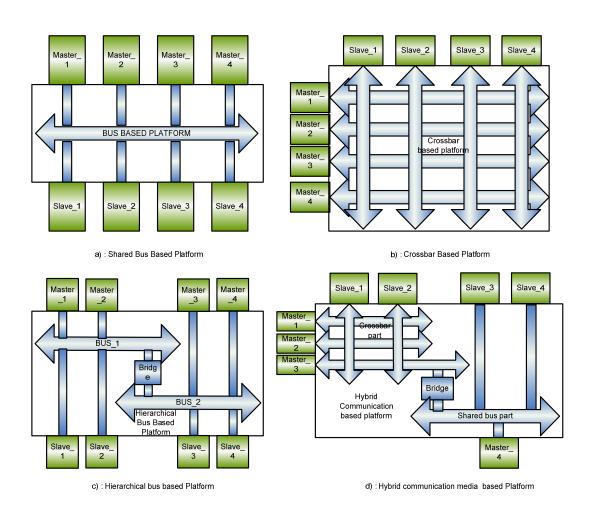

| Figure 4-1 Block diagram of Proposed Platforms                              | 60 |

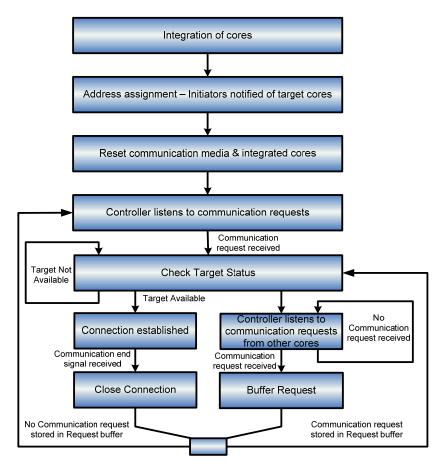

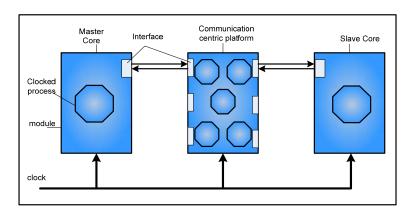

| Figure 4-2 Working of proposed communication-centric platforms              | 61 |

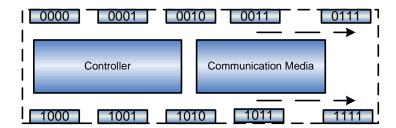

| Figure 4-3 Port address assignment in the proposed platforms                | 62 |

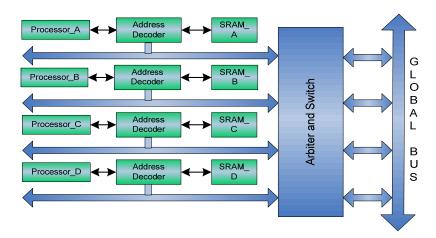

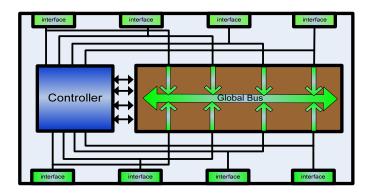

| Figure 4-4 Bus Based Platform                                               | 64 |

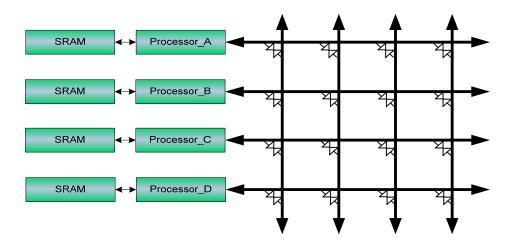

| Figure 4-5 Crossbar Based Platform                                          | 64 |

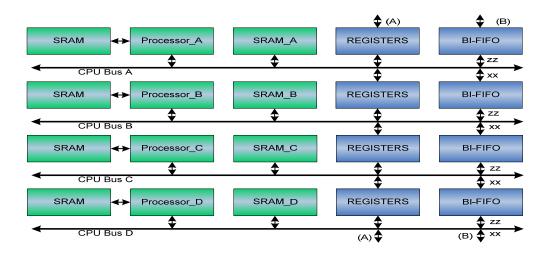

| Figure 4-6 Hybrid communication medium based Platform                       | 65 |

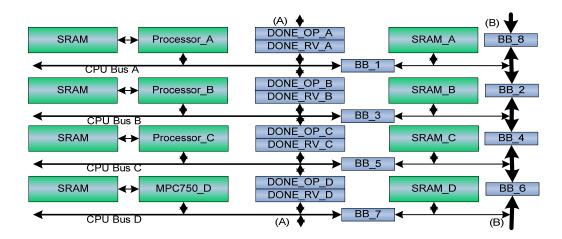

| Figure 4-7 Hierarchical bus based Platform                                  | 66 |

| Figure 4-8 A system showing the proposed modelling level                    | 68 |

| Figure 4-9 Generic model of the proposed platform                           | 69 |

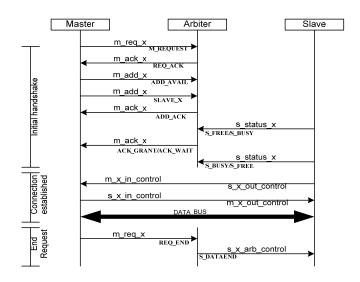

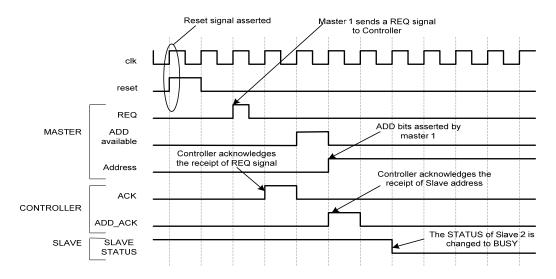

| Figure 4-10 Connection establishment steps                                  | 71 |

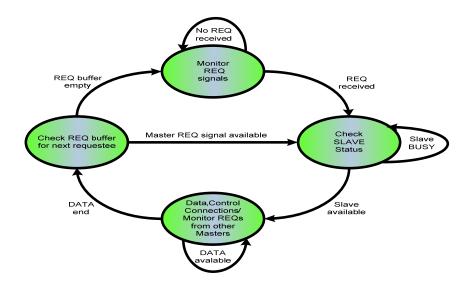

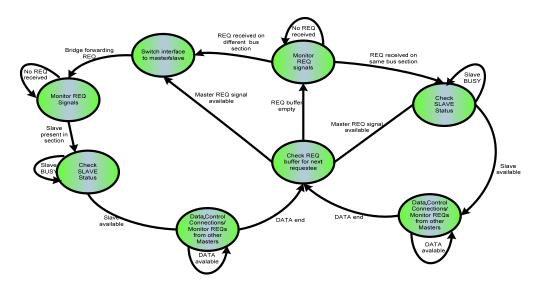

| Figure 4-11 FSM of arbiter for bus/crossbar                                 | 72 |

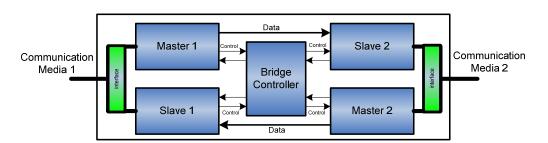

| Figure 4-12 Bridge between two communication media                          | 72 |

| Figure 4-13 FSM of arbiter for hierarchical bus/hybrid communication media  | 73 |

| Figure 4-14 Scenario 1 - one master core communicating with one slave core  | 73 |

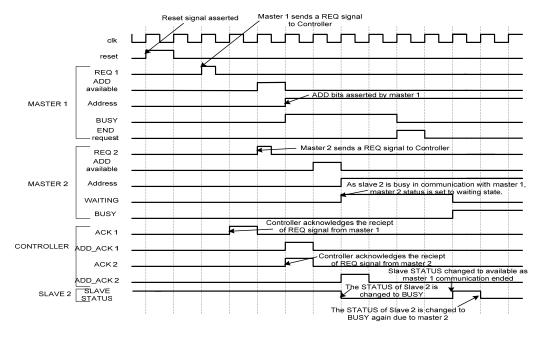

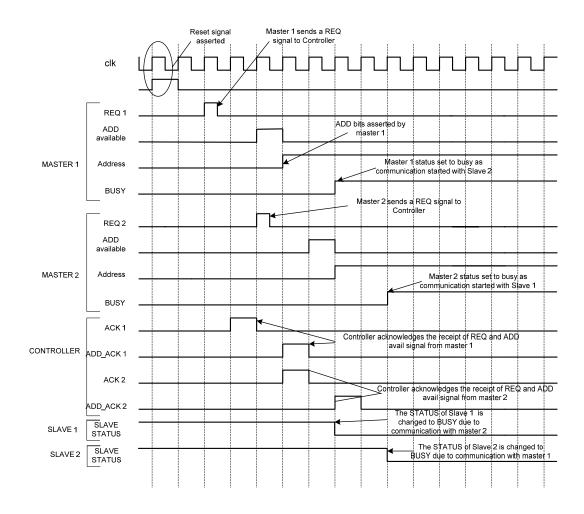

| Figure 4-15 Bus scenario 1 Transaction behaviour                            | 74 |

| Figure 4-16 Scenario 2 - two master cores communicating with one slave core | 75 |

| Figure 4-17 Rus scenario 2 Transaction behaviour                            | 75 |

| Figure 4-18 Scenario 3 - two master cores communicating with two different slave cores 76     |

|-----------------------------------------------------------------------------------------------|

| Figure 4-19 Scenario 1 - two master cores communicating with one slave core77                 |

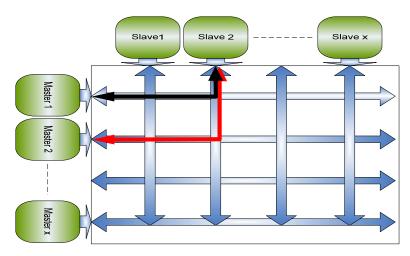

| Figure 4-20 Crossbar scenario 1 transaction behaviour                                         |

| Figure 4-21 Scenario $2$ - two master cores communicating with two different slave cores $78$ |

| Figure 4-22 Crossbar scenario 2 transaction behaviour                                         |

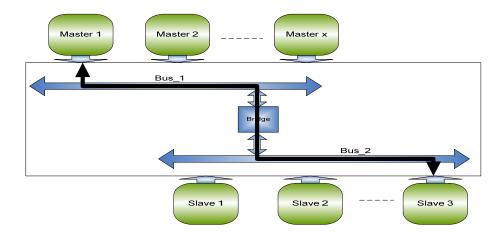

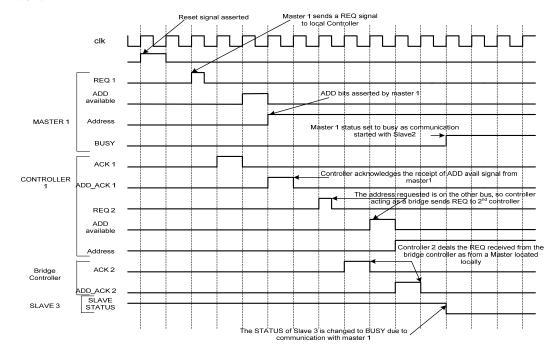

| Figure 4-23 verification of communication across bridge                                       |

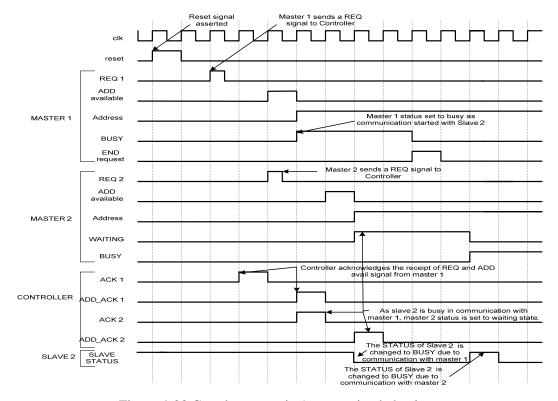

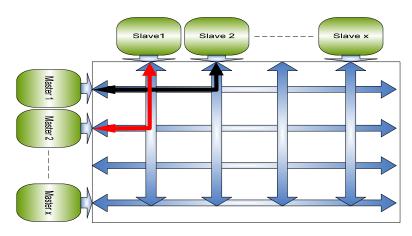

| Figure 4-24 Hierarchical bus transaction behaviour                                            |

| Figure 4-25 Placement of cores for simulations                                                |

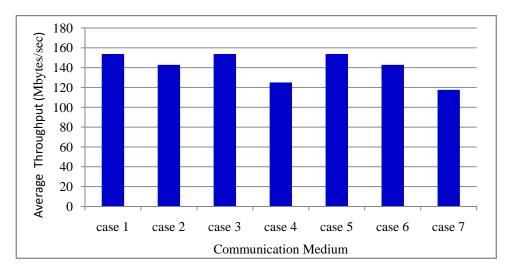

| Figure 4-26 Scenario 1 - Simulation results                                                   |

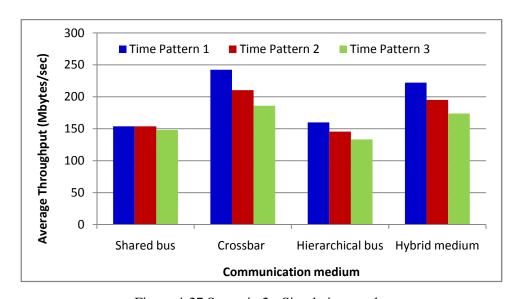

| Figure 4-27 Scenario 2 - Simulation results                                                   |

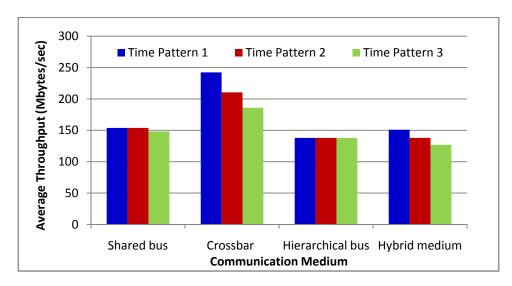

| Figure 4-28 Scenario 3 - Simulation results                                                   |

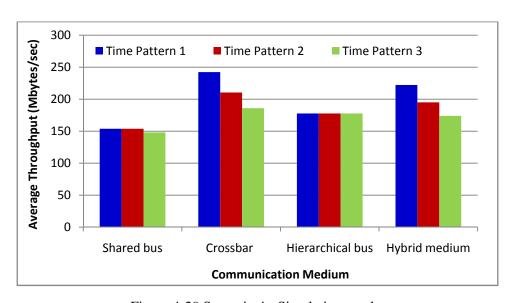

| Figure 4-29 Scenario 4 - Simulation results                                                   |

| Figure 4-30 Scenario 5 - Simulation results                                                   |

| Figure 4-31 Delayed start-up deadlines of different communication media90                     |

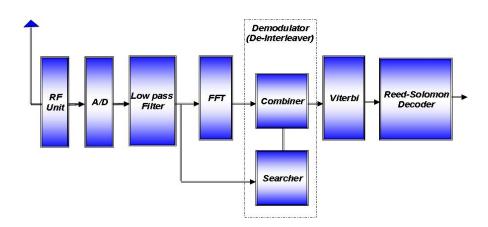

| Figure 4-32 Block diagram of WiMAX reciever                                                   |

| Figure 4-33 Communication links in the WiMAX receiver                                         |

| Figure 4-34 Impact of Communication Centric System-on-Chip Design on WiMAX94                  |

| Figure 4-35 Impact of Communication Centric System-on-Chip Design on WiMAX Power              |

| and Area Consumption94                                                                        |

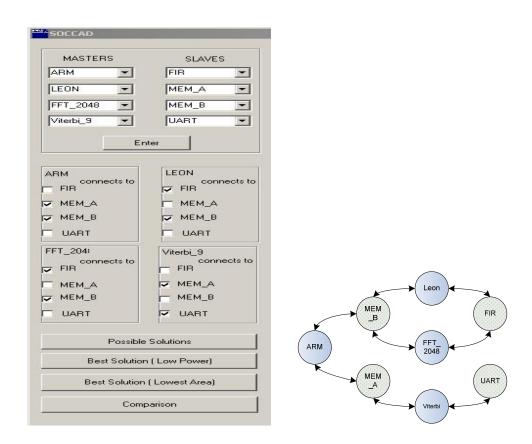

| Figure 5-1 Interface of the SOCCAD tool                                                       |

| Figure 5-2 Design Flow of SOCCAD tool                                                         |

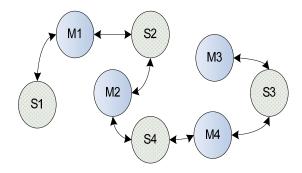

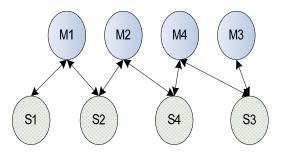

| Figure 5-3 Example of a CTG                                                                   |

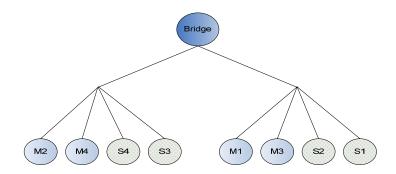

| Figure 5-4 Simplification of CTG for shared bus                                               |

| Figure 5-5 Simplification of CTG for Hierarchical bus                                         |

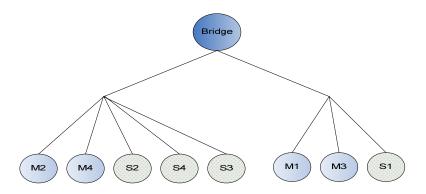

| Figure 5-6 Simplification of CTG for Hybrid medium                                            |

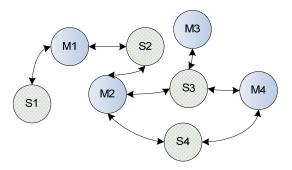

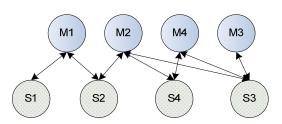

| Figure 5-7 Example 2 CTG                                                                      |

| Figure 5-8 Simplification of Example 2 CTG for Shared bus                                     |

| Figure 5-9 Simplification of Example 2 CTG for Hierarchical bus                               |

| Figure 5-10 Simplification of Example 2 CTG for Hybrid media                                  |

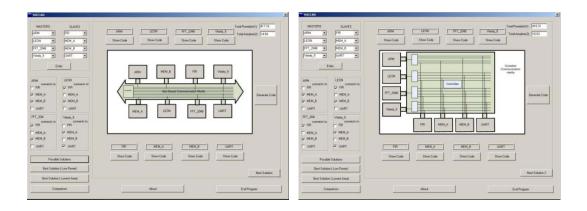

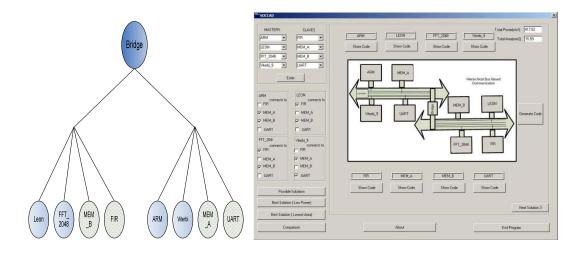

| Figure 5-11 SOCCAD communication input interface and respective CTG105                        |

| Figure 5-12 Shared bus and Crossbar based media implementation by SOCCAD tool $\dots 106$     |

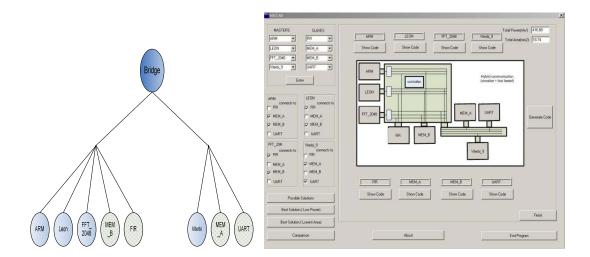

| Figure 5-13 Simplified CTG for hierarchical bus and SOCCAD implementation of system           |

|                                                                                               |

| Figure 5-14 Simplified CTG for hybrid media and SOCCAD implementation of system               |

|                                                                                               |

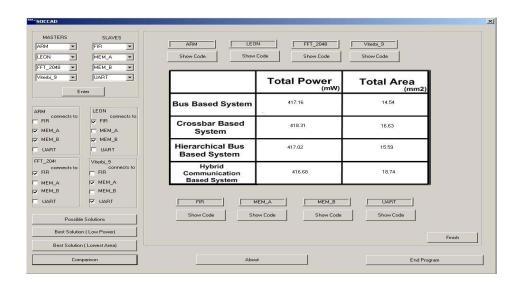

| Figure 5-15 Power & Area results of system generated by SOCCAD tool                           |

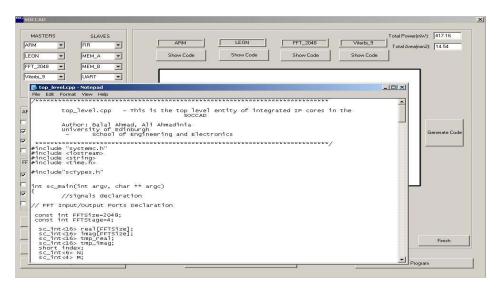

| Figure 5-16 Overall SystemC code generated by SOCCAD tool                                     |

| Figure 6-1drNoC data packet structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

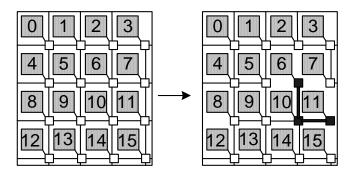

| Figure 6-2 change of packet switching to circuit switching between node 6 and 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 114  |

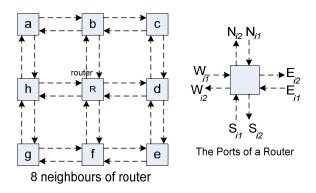

| Figure 6-3 Eight neighbours and ports of a router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 115  |

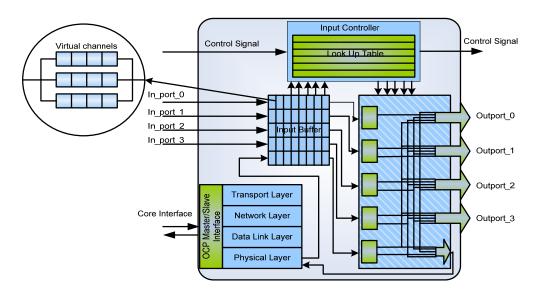

| Figure 6-4 Conceptual model of drNoC Router with OCP interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 117  |

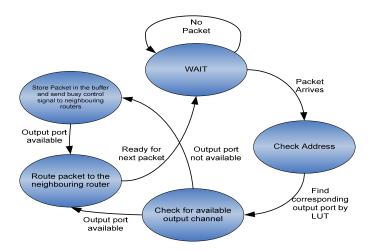

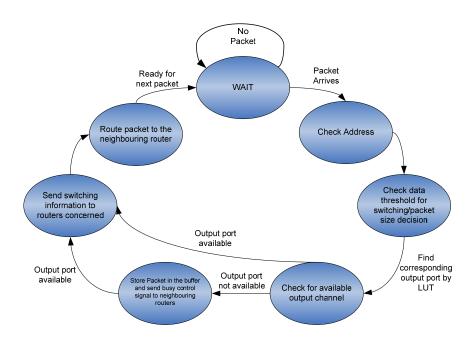

| Figure 6-5 FSM showing basic NoC flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 118  |

| Figure 6-6 FSM showing drNoC flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 119  |

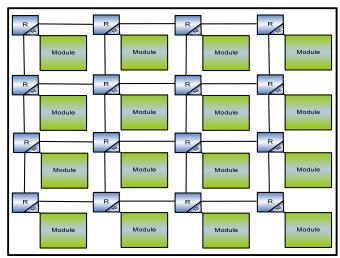

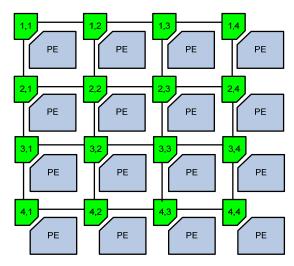

| Figure 6-7 Simulated 4x4 2D Mesh network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 121  |

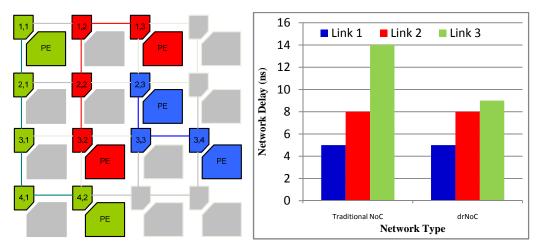

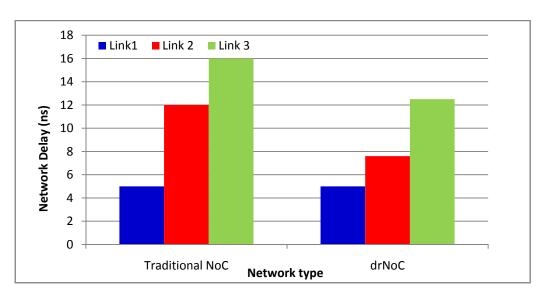

| Figure 6-8 Scenario 1: Network delay results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 122  |

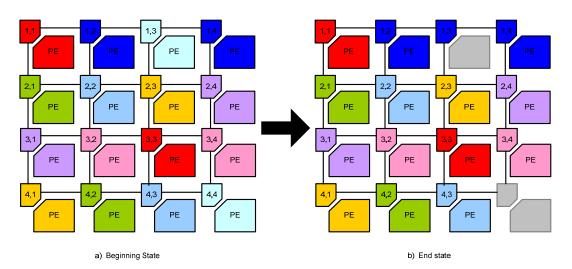

| Figure 6-9 Scenario 2 - Path formation in drNoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123  |

| Figure 6-10 Scenario 2 - Network delay results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123  |

| Figure 6-11 Scenario 3 - Path formation in drNoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 124  |

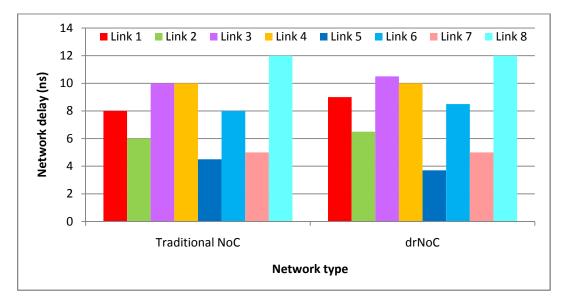

| Figure 6-12 Scenario 3 - Network delay results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 125  |

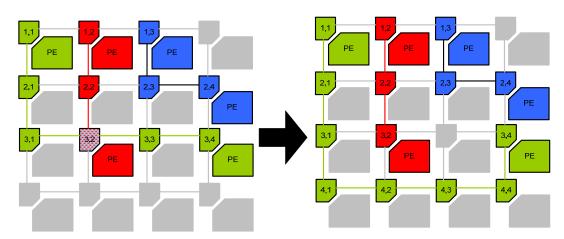

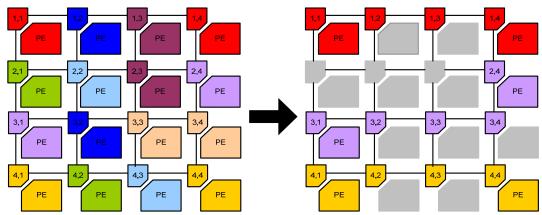

| Figure 6-13 Scenario 4- Path formation in drNoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126  |

| Figure 6-14 Scenario 4 – Percentage Increase in data throughput and decrease in average Increase In | rage |

| network delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 127  |

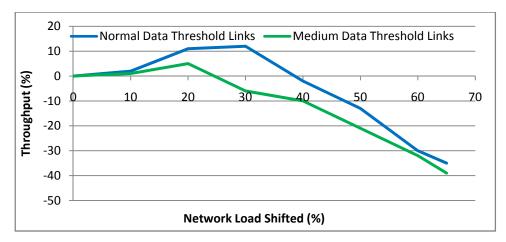

| Figure 6-15 Effect of drNoC path formation on rest of the network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 127  |

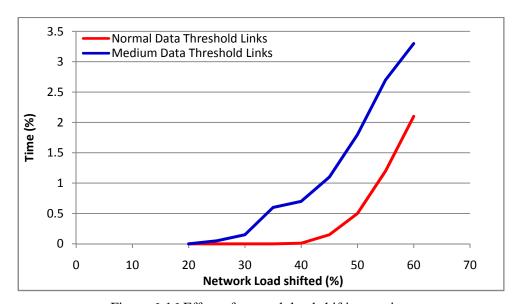

| Figure 6-16 Effect of network load shifting on time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 128  |

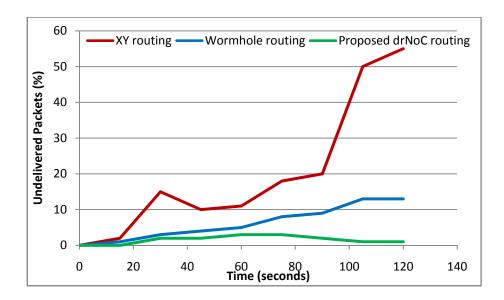

| Figure 6-17 Scenario 5- comparison of routing algorithms on drNoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 130  |

# **List of Tables**

| Table 2-1 SoC Bus Features Overview                                 | 40  |

|---------------------------------------------------------------------|-----|

| Table 3-1 Micro Network Stack [BEN-002]                             | 45  |

| Table 4-1 Platform interface signals                                | 70  |

| Table 4-2 Scenario 1 - Experimental setup                           | 82  |

| Table 4-3 Scenario 2 - master-slave pairs with expected start times | 84  |

| Table 4-4 Scenario 3 - master-slave pairs with expected start times | 86  |

| Table 4-5 Scenario 4 - master-slave pairs with expected start times | 88  |

| Table 4-6 Scenario 5 - master-slave pairs                           | 89  |

| Table 6-1 Smart Network Stack                                       | 111 |

| Table 6-2 Available channel for message routing                     | 115 |

| Table 6-3 Scenario 1: Resource configuration                        | 121 |

| Table 6-4 Scenario 2: Resource configuration                        | 122 |

| Table 6-5 Scenario 3: Resource configuration                        | 124 |

| Table 6-6 Scenario 4: Resource configuration                        | 126 |

| Table 6-7 Scenario 5: Resource configuration.                       | 129 |

# **Acronyms and Abbreviations**

APB Advanced Peripheral Bus

ASB Advanced System Bus

ASIC Application Specific Integrated Circuit

CPU Central Processing Unit

CTG Communication Task Graph

DCR Device Control Register

DMA Direct Memory Controller

DRAM Dynamic Random Access Memory

drNoC Dynamically Reconfigurable NoC

FIFO First In First Out

FPGA Field Programmable Gate Array

GALS Globally Asynchronous Locally Synchronous

**Electronic Design Automation**

GPIO General Purpose Input Output

HW Hardware

**EDA**

NoC Network-on-Chip

OCP Open Core Protocol

OPB On-Chip Peripheral Bus

PCB Printed Circuit Board

PIO Parallel Input Output

PLB Processor Local Bus

QoS Quality of Service

SJF Shortest Job First

SoC System-on-Chip

SW Software

TDMA Division Multiple Access

TLM Transaction Level Modelling

UART Universal Asynchronous Receiver/Transmitter

VC Virtual Component

VLIW Very Long Instruction Word

VSIA Virtual Socket Interface Alliance

# Chapter 1

### INTRODUCTION

#### 1.1 Motivation

According to International Technology Roadmap for Semiconductors, by the end of this decade, System-on-Chips (SoCs), using 50-nm will grow to 4 billion transistors running at 10GHz [ITR-001]. Such growth will be driven by design methodologies supporting component reuse in plug and play fashion. Most quality of service (QoS) matrices will revolve around performance and reliability measures and on-chip interconnections will be the limiting factor for performance and energy consumption [BEN-001].

In today's electronic industry, time to market is one factor that greatly determines the success of the developed product. Re-use design methodologies and ease of integration are seen as the way forward to reduce this time to market constraint. Reconfiguration has not only emerged as an efficient way of development of low power architectures for multistandard applications but also plays an important part in the reuse design paradigm.

The definition of a "system" in "system on a chip" has expanded to cover multiple processors, embedded DRAM, flash memory, application specific hardware accelerators and (Radio Frequency) RF components. This has created a situation where there is a mixture of traffic types utilising the on-chip communication media. The communication network that was traditionally handcrafted to a particular traffic type and constraints has to cope with additional burden now and proves to be a limiting factor in achieving the required performance from the present SoC. This is shifting the design paradigm from computation centric to communication centric design flow.

Due to escalating costs associated with design, verification, manufacture and testing of deep sub-micron chips, it is becoming economically infeasible to build highly customised application specific systems. The notion of platform based design is seen as a

way to tackle this problem. Platform refers to systems consisting of largely pre-designed and verified hardware and software components that can be targeted towards multiple applications, in order to amortise the high cost of platform development over larger markets. Different platform based designs have emerged in the last few years, however, most of the commercially developed platforms support companies' own products and thus, do not provide the facility to easily integrate third party components into the pre-verified platform.

System modelling and electronic design automation (EDA) tools go hand in hand in today's semiconductor industry. With Multi-core SoC being a major part of electronics used in safety critical systems, quick system simulation for verification purposes poses a new challenge for the system designers. Current application specific integrated circuit (ASIC) or conventional field programmable gate array (FPGA) centric design methodologies are unable to cope with the development requirement of present day sophisticated SoC architectures. Especially with the added reconfigurable component integration in system, there is an urgent need for design methodologies and tools that are able to deal with different types of reconfigurable SoC fabrics targeting future reconfigurable SoC architectures.

#### 1.2 Author's contribution

The aim of this thesis is to propose an on-chip communication framework for future high throughput intensive applications and to develop a design methodology for rapid SoC development. The work presented in this thesis targets three crucial areas of SoC design methodology: development of communication media for future heterogeneous multi-core systems, development of communication centric platforms for plug and play integration of components (reconfigurable, fixed and processor based) to facilitate ease of design reuse, and thirdly, development of a tool to automate the generation of SoC architectures with optimised communication media, focussing on custom reconfigurable cores.

Work carried out in the field of on-chip communication varies from bus based systems to complex Network-on-Chip (NoC) architectures. Along with the advantages of a certain communication medium are its drawbacks; no work is done where two different communication structures with different power and throughput characteristics co-exist in single SoC. In this thesis, a novel hybrid communication medium is presented that

combines the advantages of a bus based communication system with a crossbar based communication system and thus both the bus and crossbar co-exist in the same SoC [AHM-001].

NoC is considered to be a solution to the communication demands of future multi-core systems. NoC is generated by choosing a network topology, one of the routing and switching schemes and finding an optimal packet size. However, along with the advantages of any communication parameter in NoC, follows its disadvantages and a compromise has to be reached when choosing these network parameters. This thesis presents a dynamically reconfigurable NoC (drNoC) that eliminates this compromised choice of network parameters and dynamically chooses the best parameter in terms of routing, switching and packet size for the optimised network performance. The proposed drNoC incorporates an Open Core Protocol (OCP) based interface allowing components to be integrated in a plug and play fashion [AHM-002] [AHM-003] [AHM-004].

As mentioned above, platform based design has emerged as an efficient way for rapid development of SoC architectures. This thesis also presents a novel communication centric platform based design flow for future SoC architectures. The proposed platforms have built in controllers, thus making the heterogeneous cores (reconfigurable, fixed, processor based) integrated in a plug and play fashion. This eliminates the need of the dedicated system controller to be integrated or programmed when integrating processing cores to the platform. Four platforms have been developed with different communication media including the hybrid concept mentioned above. Unlike traditional platform based designs, the novelty of the proposed platform lie in its ability to produce SoC architecture in truly plug and play fashion with an optimised communication media [AHM-005].

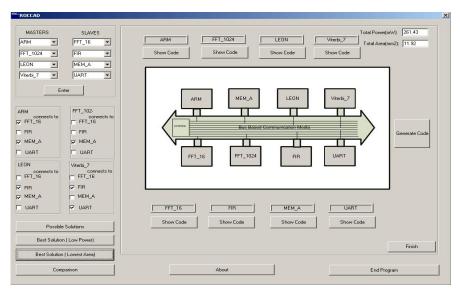

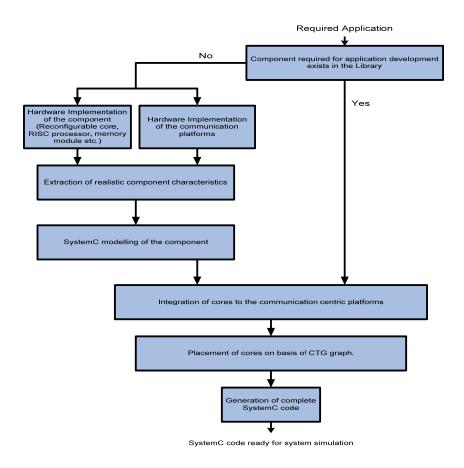

Lastly, bringing the above mentioned work together, a tool called SOCCAD is developed to automate the development of SoC architectures. The novelty of the SOCCAD tool lies in its ability to automate development of SoC architectures integrating custom reconfigurable cores and with optimised communication media. SOCCAD tool has a built-in component library that not only holds SystemC models of communication media but also includes custom reconfigurable cores, processor cores and other peripheral components required to generate complete system architecture for quick simulation and verification. [AHM-006] [AHM-007] [AHM-008] [AHM-009] [AHM-010] [AHM-011].

#### 1.3 Roadmap of thesis

This remaining of this thesis is divided into six chapters and is organised as follows:

- Chapter 2 gives an overview of traditional communication media and communication centric platforms. It introduces the concept of shared communication media and gives an overview of commercially available shared and hierarchical buses. The communication centric platform based approach is then described and performance matrices related to on-chip communication media is listed to conclude the chapter.

- Chapter 3 details the concepts of NoC communication and how it tackles the drawbacks in traditional bus based communication media. This chapter also identifies the expectations from future packet based on-chip communication network and lists performance matrices relating to NoC.

- Chapter 4 presents two important things, firstly, a hybrid communication medium is presented and secondly the proposed communication centric platforms have been discussed. For the purpose of effective on-chip communication, four platforms have been developed. This chapter also details the systemC based communication centric modelling of the proposed platforms and discusses their simulation results. The developed platforms are also evaluated with the help of real life example.

- Chapter 5 presents the developed SOCCAD tool, highlights the communication centric placement and explains the automated generation of communication centric SoC architectures utilising the developed communication centric platforms.

- Chapter 6 presents drNoC, which is developed for SoC architectures with communication requirements of over 10GB/s and explains its architecture and implementation. Simulation results are then listed to demonstrate the effectiveness of proposed drNoC in high data throughput applications.

• Chapter 7 presents a summary of all the previous chapters reiterating the main contributions by the author. It also identifies topics for future research and development.

## 1.4 Summary

On-chip communication is a crucial research area and with the SoC design methodology shifting to communication centric design flow, there is a need for development of new communication architectures to cater for the increasing throughput requirements while providing the required QoS in a reduced design time. This thesis presents two novel communication media, a hybrid communication architecture and a dynamically reconfigurable NoC for future high data intensive multi-core architectures. This thesis also presents novel communication centric platform based approach and a tool for automated generation of SoC architectures that aims at rapid development of SoC architectures. The next chapter gives an overview of traditional communication media and commercially developed communication centric platforms.

# Chapter 2

## LITERATURE REVIEW

# **Communication Centric Platform Based Designs**

#### 2.1 Introduction

This chapter gives an insight of communication centric platform based design. It starts with the definition of term platform and the origin of platform based design. Current on-chip communication media are discussed followed by literature review of communication centric platforms.

During recent years, platform based design, also known as the configure and execute approach is emerging as a powerful SoC design methodology for rapid development of SoC devices. The term "platform" is defined differently by researchers, semiconductor industries and tool vendors.

Sangiovanni-Vincentelli [SAN-001] defines an SoC platform as a "layer of abstraction with two views." The upper view allows an application to be developed without referring to the lower levels of abstraction. Meanwhile, the lower view is a set of rules that classify a set of components belonging to the platform.

The Virtual Socket Interface Alliance's (VSIA) [VIS-001] platform-based design development group defines an SoC platform as "a library of virtual components and an architectural framework, consisting of a set of integrated and pre-qualified software and hardware virtual components (VCs), models, EDA and software tools, libraries and methodology, to support rapid product development through architectural exploration, integration and verification."

Automotive industry pioneered the platform concept in the early 1980s by standardising a common platform across several makes and models. By developing several platforms and sub-platforms, for example, the chassis platform, the interior platform, and

the electrical platform etc., the manufacturer was able to outsource significant segments of automotive hardware, thus reducing production cost and design cycle and improving design quality.

The semiconductor industry embraced the concept of platform based design to cope with the rising pressure of time to market, design and manufacture costs. Platform based designs have been classified into different kinds.

The first kind is called a "full application platform" in which users design full applications on top of hardware and software architectures. Such platforms usually are accompanied by software to support compilation, debugging, simulation and emulation. This speeds up the time to market and gives the designer an advantage of having a working chip, running at real speeds and executing in real environment.

Some Industrial examples of full application platform include Philip's Nexperia including a 32 bit MIPS RISC CPU, a 32 bit VLIW Trimedia processor and three levels of internal buses [PHI-001], Texas Instrument's OMAP multimedia platform including a DSP, an enhanced ARM processor and an inter-processor communication mechanism [TEX -001], and ARM's PrimeXsys wireless platform including ARM 926EJ-S processor core, java acceleration, a multi-layer AMBA bus and a selection of peripherals [ARM-002].

The second type of platform, which is not very common in academic based research, is a "processor centric platform". As the name suggests, in processor based platforms only the processor is reconfigurable but it does not make the whole system. Industrial examples include Improv Systems [IMP-001], ARC [ARC-001] and Tensilica's Xtensa [TEN-001].

The third type is a "communication centric platform" which provides an interconnect architecture but does not provide a processor or a full application. Example includes IBM CoreConnect [IBM-001], ARM's AMBA [ARM-001] Sonic's silicon backplane [SON-001] and Palmchip's CoreFrame architecture [PAL-001].

Finally there is a "fully programmable platform" consisting typically of FPGA logic and a processor core. Examples from industry are Altera's Excalibur [ALT-001], Xilinx Virtex Pro [XIL-001] and Quick Logic's PolarPro [QUI-001].

Due to the importance of communication in the future SoC designs, this chapter focuses on the communication centric platform based designs. In the following sections, the basics of on-chip communication is discussed followed by a literature review of traditional SoC communication including bus based, crossbars, hierarchical bus and finally it moves towards the development of communication centric platforms.

## 2.2 Basics of On-chip Communication

As mentioned earlier, performance of a multi-core SoC is not only determined by the capacity of the processing elements (e.g. CPU speed, cache size, etc.), but it is also limited by the interconnect network. Design and optimization of such interconnect network are critical for system performance. In designing communication architecture for SoC, certain factors have to be considered [LAH-001]:

<u>Appropriate Topology</u>: The topology refers to the way SoC components are connected. It can be in the form of single shared architecture, dedicated communication channels or more complex architectures such as hierarchical buses, token ring or crossbars.

<u>Communication Protocols:</u> The protocol specifies the manner in which communication across the channel takes place. Communication protocols deal with the different types of resource management algorithms used for determination of access right to the shared communication channels. Static-priority, time division multiple access (TDMA), token passing, lottery and code division multiple access (CDMA) are some of the existing communication protocols employed in on-chip communication.

<u>Architectural Parameters</u>: Parameters like bus widths, burst transfer size, priorities etc are also to be defined for the communication channels and associated protocols. Performance of communication media depends highly on these parameters.

<u>Clocking</u>: Clocking can be synchronous or asynchronous. If a single clock is used for the communication medium and its connected cores, the system is referred to as a synchronous system. Asynchronous system in contrast, has no global clock and timing is managed locally. Communication medium synchronisation occurs with the help of handshaking protocol that uses request-acknowledgement signals to ensure that data transfer is completed successfully. Handshaking is also used in synchronous systems for a data