# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## Autotuning Wavefront Patterns for Heterogeneous Architectures

Siddharth Mohanty

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2015

## Abstract

Manual tuning of applications for heterogeneous parallel systems is tedious and complex. Optimizations are often not portable, and the whole process must be repeated when moving to a new system, or sometimes even to a different problem size.

Pattern based parallel programming models were originally designed to provide programmers with an abstract layer, hiding tedious parallel boilerplate code, and allowing a focus on only application specific issues. However, the constrained algorithmic model associated with each pattern also enables the creation of pattern-specific optimization strategies. These can capture more complex variations than would be accessible by analysis of equivalent unstructured source code. These variations create complex optimization spaces. Machine learning offers well established techniques for exploring such spaces.

In this thesis we use machine learning to create autotuning strategies for heterogeneous parallel implementations of applications which follow the wavefront pattern. In a wavefront, computation starts from one corner of the problem grid and proceeds diagonally like a wave to the opposite corner in either two or three dimensions. Our framework partitions and optimizes the work created by these applications across systems comprising multicore CPUs and multiple GPU accelerators. The tuning opportunities for a wavefront include controlling the amount of computation to be offloaded onto GPU accelerators, choosing the number of CPU and GPU threads to process tasks, tiling for both CPU and GPU memory structures, and trading redundant halo computation against communication for multiple GPUs.

Our exhaustive search of the problem space shows that these parameters are very sensitive to the combination of architecture, wavefront instance and problem size. We design and investigate a family of autotuning strategies, targeting single and multiple CPU + GPU systems, and both two and three dimensional wavefront instances. These yield an average of 87% of the performance found by offline exhaustive search, with up to 99% in some cases.

## Lay Summary

Modern computing systems are increasingly becoming hybrid systems consisting of multiple CPU cores and specialized accelerators such as graphical processing units (GPU) that can offload many intensive operations to offer higher processing capability than a single core system. The presence of many CPU and GPU cores allows a large chunk of work to be partitioned into many smaller chunks that can be computed simultaneously or in parallel. Parallel computing can be seen in action in almost every field that requires large scale computation to be carried out as quickly as possible. Its application ranges from handling millions of transactions concurrently in an on line trading platform to making accurate weather forecasts that require massive computation power. IBM Deep Blue and Google data centers are all examples of such systems.

However, programming such hybrid systems is complex. This is because the programmer now has to decompose serial problems into parts that can be computed in parallel. After conceptually decomposing the problem, the programmer is then required to become an expert in multiple, conceptually diverse languages and libraries to implement parallelism, and to integrate these within single applications. An application programmer would prefer not to be bogged down by the low level details of problem distribution across systems and rather focus on the computation. And, even after implementing parallelism, the code needs to run optimally across different types of hybrid architectures so that the programmer does not have to expend time on tuning the application for each architecture.

Our work addresses these two issues of implementing parallelism transparently and making code performance portable across diverse heterogeneous systems. We provide a framework that lets the programmer write application level code while our framework handles the distribution of work across multiple CPU cores and GPU devices. We target a specific class of problems called wavefronts which can be difficult to parallelise due to their internal dependencies that place restrictions on how the problems can be decomposed and distributed. After implementing parallelism, our framework automatically selects high performing configurations for the application so that the programmer does not have to manually port each application to a new system. Our autotuning framework shows promising results based on numerous trials across three different classes of applications and five diverse systems.

## Acknowledgements

Much credit for the research undertaken is due to Dr. Murray Cole who guided and provided valuable inputs to this project over numerous mails and meetings. This research undertaking was possible due to generous grants from the Institute for Computing Systems Architecture (ICSA), Numerical Algorithms and Intelligent Software Centre (NAIS), Ethel Gordon Fund, the University of Edinburgh College Science Fund and the Chalmers Fund. Finally, I would like to thank my family for their unconditional support, my friends for their encouragement and camaraderie and Shishu for always being there for me.

## Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published earlier as follows:

- Siddharth Mohanty and Murray Cole. Autotuning wavefront applications for multicore multi-GPU hybrid architectures. In Proceedings of Programming Models and Applications on Multicores and Manycores, PMAM'14, pages 1:1-1:9, New York, NY, USA, 2014. ACM [77].

- Siddharth Mohanty and Murray Cole. Autotuning wavefront abstractions for heterogeneous architectures. In Applications for Multi-Core Architectures (WAMCA), 2012 Third Workshop on, pages 42-47. IEEE, 2012 [76].

- Siddharth Mohanty. Task farm optimization through machine learning. Diss. Master's thesis, Institute of Computing Systems Architecture, Informatics Department, University of Edinburgh, 2010 [75]. Paraphrased materials from the thesis with additional content have been used in chapter 2 and chapter 7. Specifically, these are subsection 2.2.1, subsection 2.2.2, section 2.3, subsection 2.4.2, subsection 2.4.3, subsection 2.4.4, subsection 2.4.5, subsection 2.4.6, section 2.7, subsection 7.2.3 and the last paragraph of section 7.4.

$Siddharth \ Mohanty$

# **Table of Contents**

| 1        | $\mathbf{Intr}$ | oducti | ion                                                                     | 1  |

|----------|-----------------|--------|-------------------------------------------------------------------------|----|

|          | 1.1             | Hetero | ogeneous Parallelism Challenges                                         | 3  |

|          | 1.2             | Contr  | ributions of this Thesis                                                | 3  |

|          | 1.3             | Struct | ture of the Dissertation                                                | 5  |

| <b>2</b> | Bac             | kgrou  | nd                                                                      | 7  |

|          | 2.1             | Parall | el Computer Architecture                                                | 7  |

|          |                 | 2.1.1  | Opportunities and Challenges of Parallelism                             | 7  |

|          | 2.2             | Parall | el Programming Paradigms                                                | 10 |

|          |                 | 2.2.1  | Message Passing Paradigm                                                | 10 |

|          |                 | 2.2.2  | Shared Address Space (SAS) Paradigm                                     | 11 |

|          |                 | 2.2.3  | Accelerator Programming Paradigm                                        | 14 |

|          |                 | 2.2.4  | Current Parallel Programming Model Advantages and Limitations $\ . \ .$ | 18 |

|          |                 | 2.2.5  | Summary                                                                 | 20 |

|          | 2.3             | Algori | thmic Skeletons                                                         | 20 |

|          |                 | 2.3.1  | Classifying Skeletons                                                   | 21 |

|          |                 | 2.3.2  | Guiding Principles for Skeleton System Design                           | 22 |

|          |                 | 2.3.3  | Tuning of Skeletons                                                     | 23 |

|          | 2.4             | Machi  | ne Learning                                                             | 23 |

|          |                 | 2.4.1  | Need for Machine Learning                                               | 24 |

|          |                 | 2.4.2  | Machine Learning in Program Optimization                                | 25 |

|          |                 | 2.4.3  | Machine Learning Models in Supervised Learning                          | 26 |

|          |                 | 2.4.4  | Linear Regression                                                       | 26 |

|          |                 | 2.4.5  | Support Vector Machines                                                 | 27 |

|          |                 | 2.4.6  | Multi Layer Perceptron                                                  | 28 |

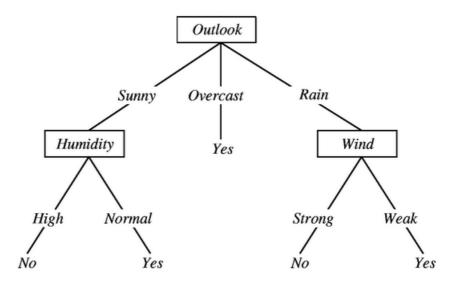

|          |                 | 2.4.7  | Decision Trees                                                          | 29 |

|          | 2.5             | Dynar  | nic Programming Problems                                                | 30 |

|          |                 | 2.5.1  | Wavefront                                                               | 34 |

|          |                 | 2.5.2  | Wavefront Terminology                                                   | 35 |

|   | 2.6        | Wavefront Applications                                                                           | 7 |

|---|------------|--------------------------------------------------------------------------------------------------|---|

|   |            | 2.6.1 Nash Equilibrium $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$ | 7 |

|   |            | 2.6.2 Longest Common Sub-sequence                                                                | 8 |

|   |            | 2.6.3 Lower Upper Triangulation                                                                  | 8 |

|   | 2.7        | Parallel Computing Metrics                                                                       | 0 |

|   | 2.8        | Conclusion                                                                                       | 1 |

| 3 | Wa         | vefront Implementation Strategy 4                                                                | 3 |

|   | 3.1        | Introduction                                                                                     | 3 |

|   | 3.2        | 2D Wavefront Implementation                                                                      | 3 |

|   |            | 3.2.1 Single GPU Implementation and Tuning Points                                                | 3 |

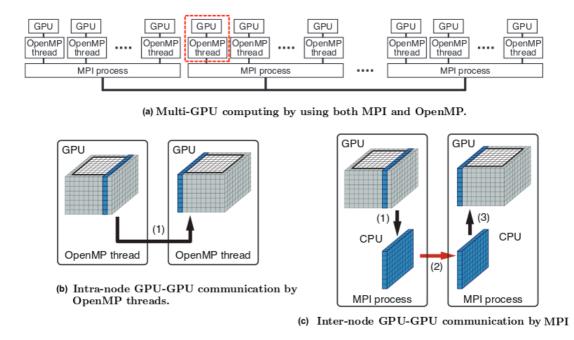

|   |            | 3.2.2 Multiple GPU Implementation                                                                | 5 |

|   | 3.3        | 3D Wavefront Implementation                                                                      | 8 |

|   | 3.4        | Performance Tuning Trade-Offs                                                                    | 0 |

|   | 3.5        | Summary                                                                                          | 3 |

|   | <b>a</b> . |                                                                                                  | _ |

| 4 |            | gle GPU Autotuning : 2D Wavefronts   5                                                           |   |

|   | 4.1        | Introduction                                                                                     |   |

|   | 4.2        | Autotuning Strategy       5         Autotuning Strategy       5                                  |   |

|   | 4.0        |                                                                                                  | 7 |

|   | 4.3        | 0                                                                                                | 0 |

|   |            |                                                                                                  | 0 |

|   |            |                                                                                                  | 4 |

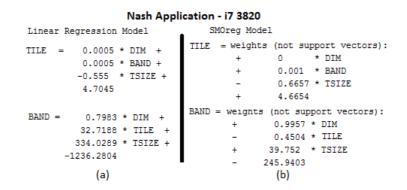

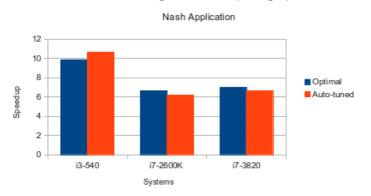

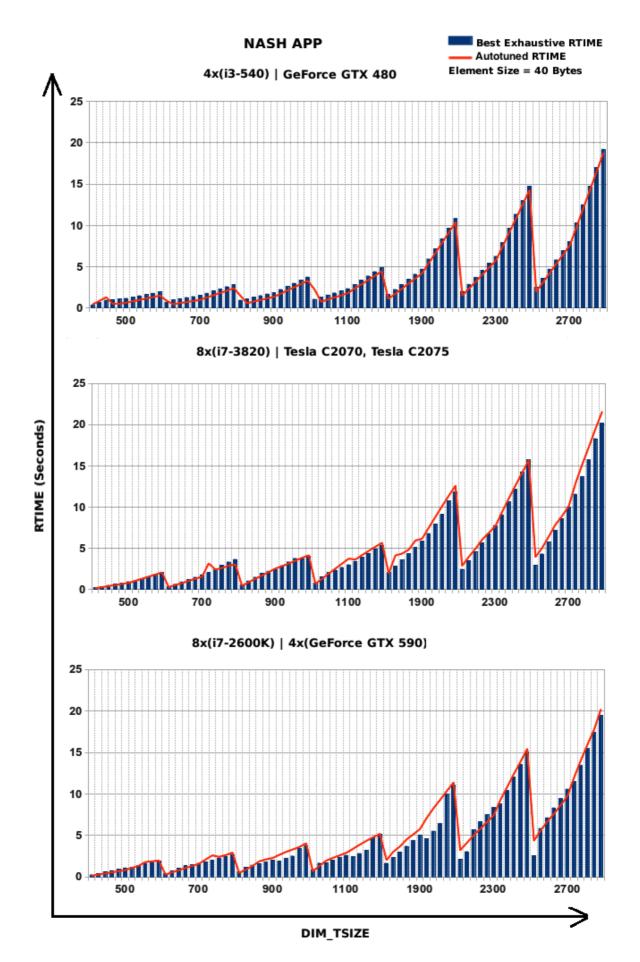

|   |            | 4.3.3 Autotuning Results for Nash Application                                                    |   |

|   |            | 4.3.4 Autotuning Results for Synthetic Application 6                                             | 9 |

|   |            |                                                                                                  | 3 |

|   |            | 4.3.6 Summary                                                                                    | 3 |

|   | 4.4        | Conclusion                                                                                       | 3 |

| 5 | Mu         | ltiple GPU Autotuning : 2D Wavefronts 7                                                          | 7 |

|   | 5.1        | Introduction                                                                                     | 7 |

|   | 5.2        | Experimental Program                                                                             | 7 |

|   |            | 5.2.1 Training Phase                                                                             | 7 |

|   |            | 5.2.2 Evaluation Phase                                                                           | 0 |

|   |            | 5.2.3 Platforms                                                                                  | 0 |

|   | 5.3        | Results and Analysis                                                                             | 1 |

|   |            | 5.3.1 Training : Exhaustive Search Results                                                       | 1 |

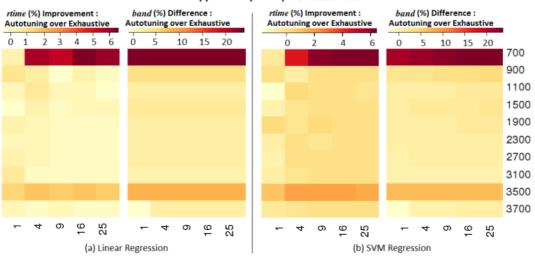

|   |            | 5.3.2 Autotuning : The Learned Model                                                             | 3 |

|   |            | 5.3.3 Autotuning Results : Evaluation                                                            | 8 |

|    | 5.4            | Conclusion                                                      | .00       |

|----|----------------|-----------------------------------------------------------------|-----------|

| 6  | Aut            | totuning 3D Wavefronts 1                                        | 01        |

|    | 6.1            | Introduction                                                    | .01       |

|    | 6.2            | 3D Autotuning Strategy                                          | .01       |

|    | 6.3            | Application Suite and Platforms                                 | .02       |

|    |                | 6.3.1 Lower Triangulation Application                           | .03       |

|    |                | 6.3.2 Experimental Platforms                                    | .04       |

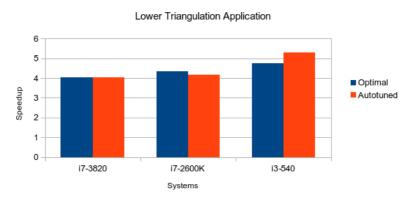

|    | 6.4            | Results and Analysis                                            | .05       |

|    |                | 6.4.1 Exhaustive Search Analysis                                | .05       |

|    |                | 6.4.2 Autotuning Results                                        | .10       |

|    | 6.5            | Conclusion                                                      | .14       |

| 7  | $\mathbf{Rel}$ | ated Work 1                                                     | 15        |

|    | 7.1            | Introduction                                                    | 15        |

|    | 7.2            | Domain Specific Autotuners                                      | 16        |

|    |                | 7.2.1 Wavefront Tuning Frameworks                               | 16        |

|    |                | 7.2.2 Self Tuning Library Generators                            | 18        |

|    |                | 7.2.3 Task Farm Skeleton Frameworks                             | 19        |

|    |                | 7.2.4 Stencil Tuning Frameworks                                 | .20       |

|    | 7.3            | Compiler Space Tuners and Optimization using Machine Learning 1 | .23       |

|    | 7.4            | Dynamic Self Adaptive Tuners                                    | .24       |

|    | 7.5            | Conclusion                                                      | .26       |

| 8  | Cor            | nclusion 1                                                      | <b>27</b> |

|    | 8.1            | Contributions                                                   | 27        |

|    | 8.2            | Critical Analysis                                               | 28        |

|    | 8.3            | Future work                                                     | 29        |

|    |                | 8.3.1 Accelerated Processing Unit                               | .30       |

|    |                | 8.3.2 Many Integrated Core Architecture                         | .30       |

| Bi | ibliog         | graphy 1                                                        | 33        |

# **List of Figures**

| 1.1  | Heterogeneous Computing Architecture          | 2  |

|------|-----------------------------------------------|----|

| 2.1  | The Memory Gap                                | 8  |

| 2.2  | The MPI model                                 | 11 |

| 2.3  | The Pthread model                             | 12 |

| 2.4  | The OpenMP model                              | 13 |

| 2.5  | The OpenCL Model                              | 16 |

| 2.6  | The Task Farm                                 | 22 |

| 2.7  | Learning as Curve Fitting                     | 25 |

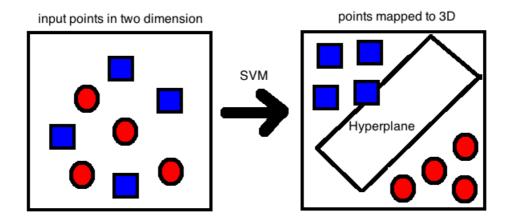

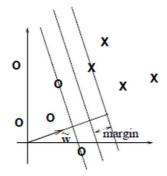

| 2.8  | Support Vector Machine Hyperplane             | 27 |

| 2.9  | The Support Vector Machine model              | 27 |

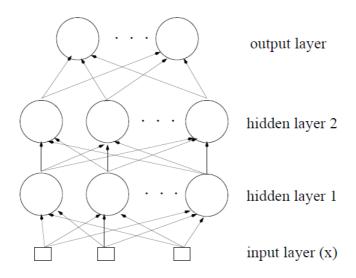

| 2.10 | The Multi layer Perceptron model              | 28 |

| 2.11 | The Decision Tree                             | 29 |

| 2.12 | Limits of tree based learners                 | 30 |

| 2.13 | Serial Monadic DP                             | 32 |

| 2.14 | Non Serial Monadic DP                         | 33 |

| 2.15 | Serial Polyadic DP                            | 33 |

| 2.16 | Non Serial Polyadic DP                        | 34 |

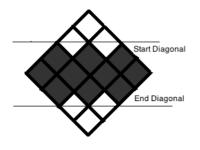

| 2.17 | 2D Waveflow                                   | 35 |

| 3.1  | 2D Tiled Waveflow                             | 44 |

| 3.2  | Wavefront Dependency Array                    | 45 |

| 3.3  | Wavefront Implementation with 3 phases        | 46 |

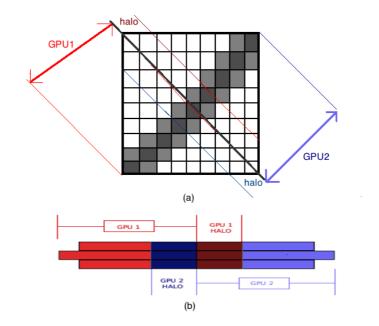

| 3.4  | Dual-GPU division of wavefront diagonals      | 47 |

| 3.5  | 3D Waveflow                                   | 48 |

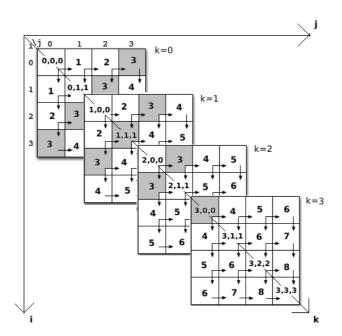

| 3.6  | 3D Wavefront Dependency Array                 | 49 |

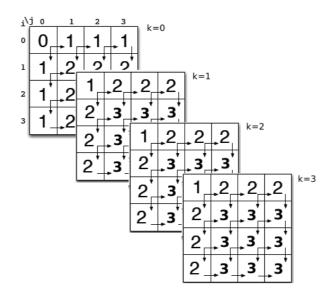

| 3.7  | Linearized 3D Wavefront                       | 51 |

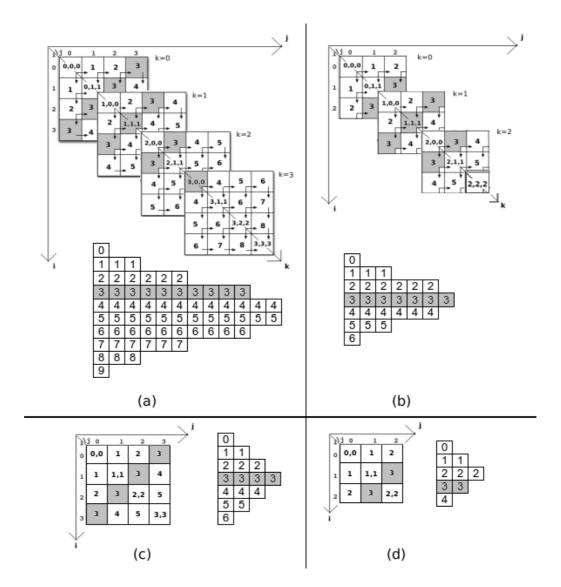

| 3.8  | Diagonal major representation of 2D Wavefront | 52 |

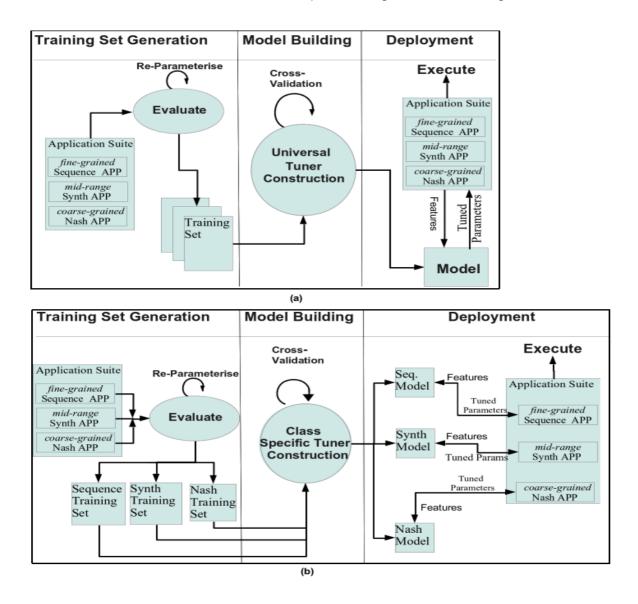

| 4.1  | Single GPU Learning Strategy                  | 56 |

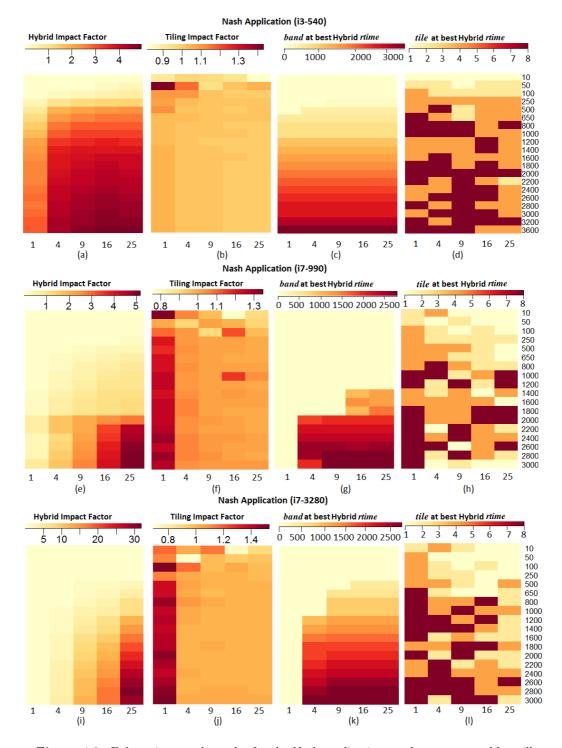

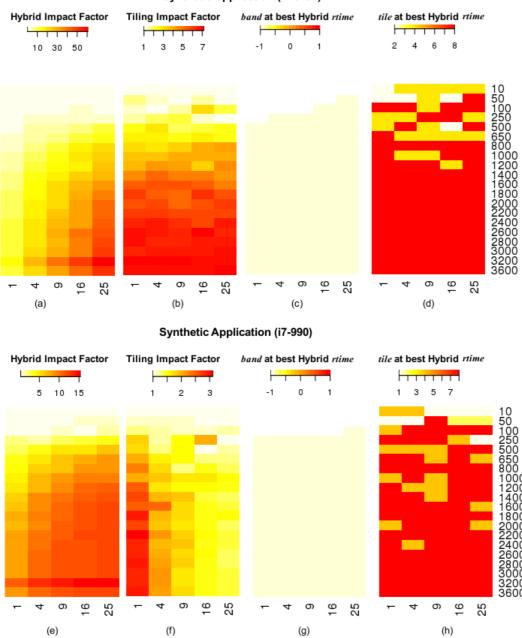

| 4.2  | Exhaustive search results : Nash application                                             | 59  |

|------|------------------------------------------------------------------------------------------|-----|

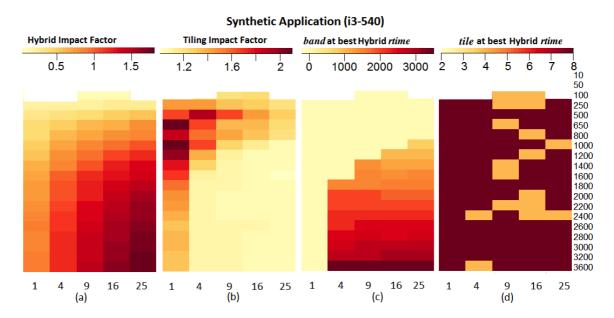

| 4.3  | Exhaustive search results : Synthetic application on i3-540                              | 61  |

| 4.4  | Exhaustive search results : Synthetic application on i7 systems $\ldots \ldots \ldots$   | 62  |

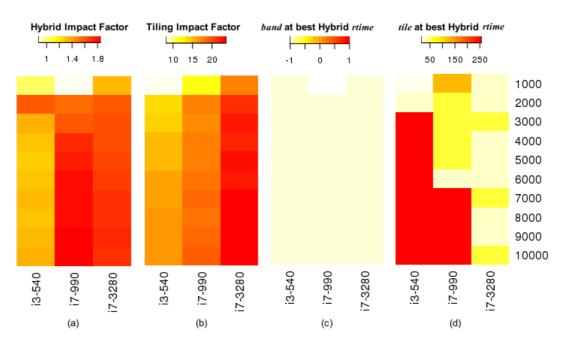

| 4.5  | Exhaustive search results : Sequence Comparison application $\ldots \ldots \ldots$       | 63  |

| 4.6  | Sample <i>tile</i> and <i>band</i> prediction by learners                                | 64  |

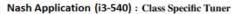

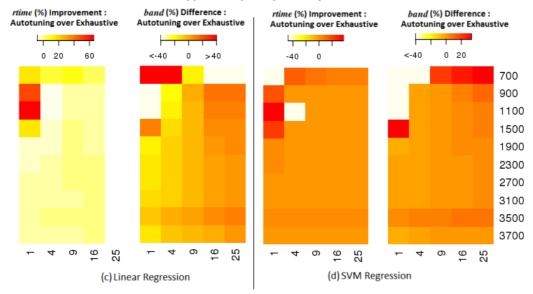

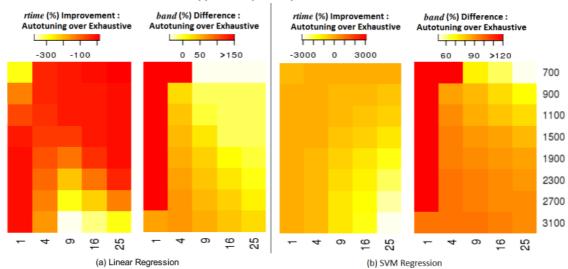

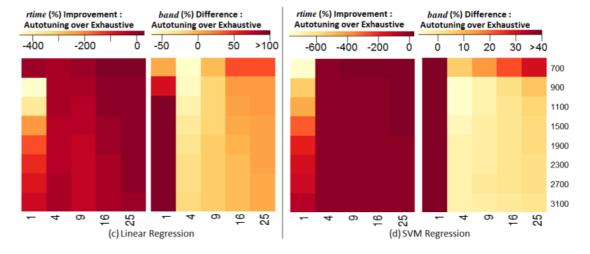

| 4.7  | Autotuning performance : Nash application on i3-540                                      | 66  |

| 4.8  | Autotuning performance : Nash application on i7-3280                                     | 67  |

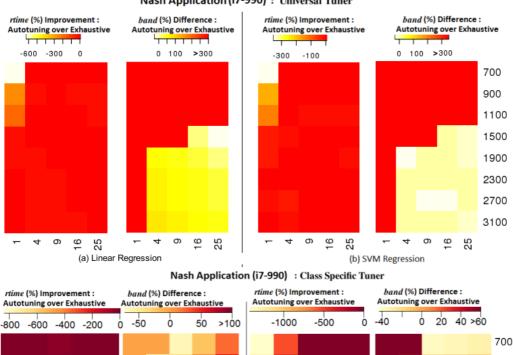

| 4.9  | Autotuning performance : Nash application on i7-990                                      | 68  |

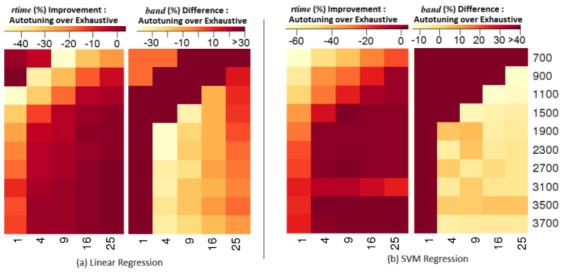

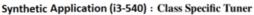

| 4.10 | Autotuning performance : Synthetic application on i3-540                                 | 70  |

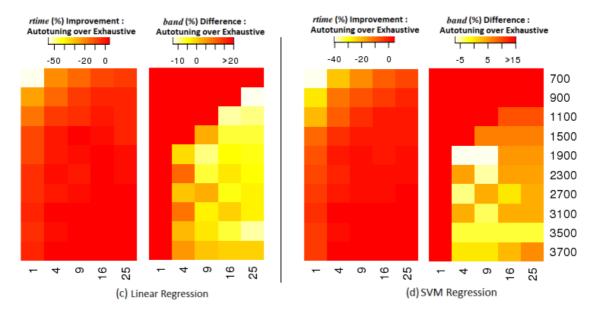

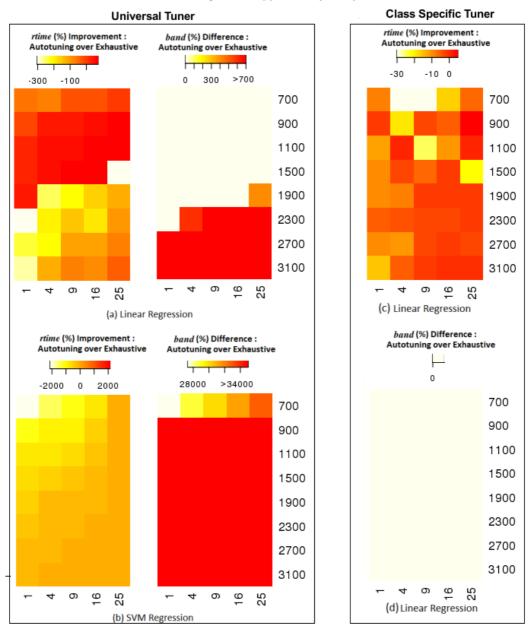

| 4.11 | Autotuning performance : Synthetic application on i7-990                                 | 71  |

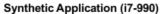

| 4.12 | Autotuning performance : Synthetic application on i7-3280                                | 72  |

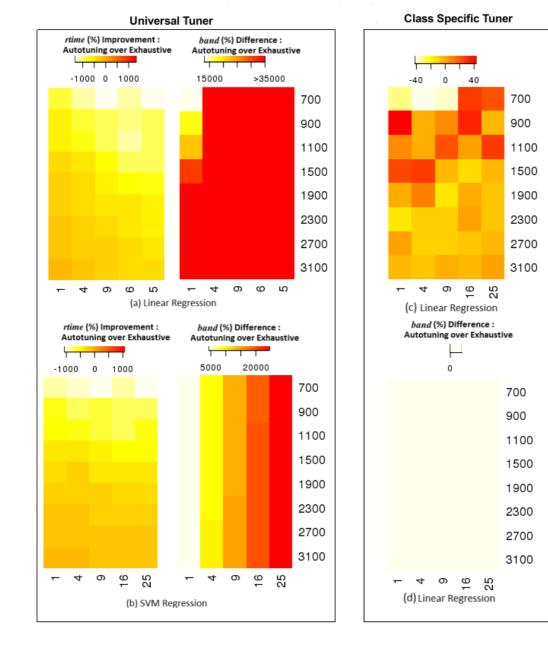

| 4.13 | Autotuning Summary : Universal and Class Specific                                        | 74  |

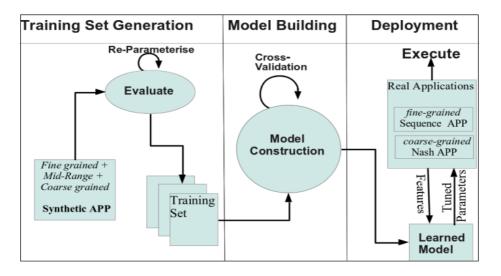

| 5.1  | Learning Strategy based on synthetic application                                         | 78  |

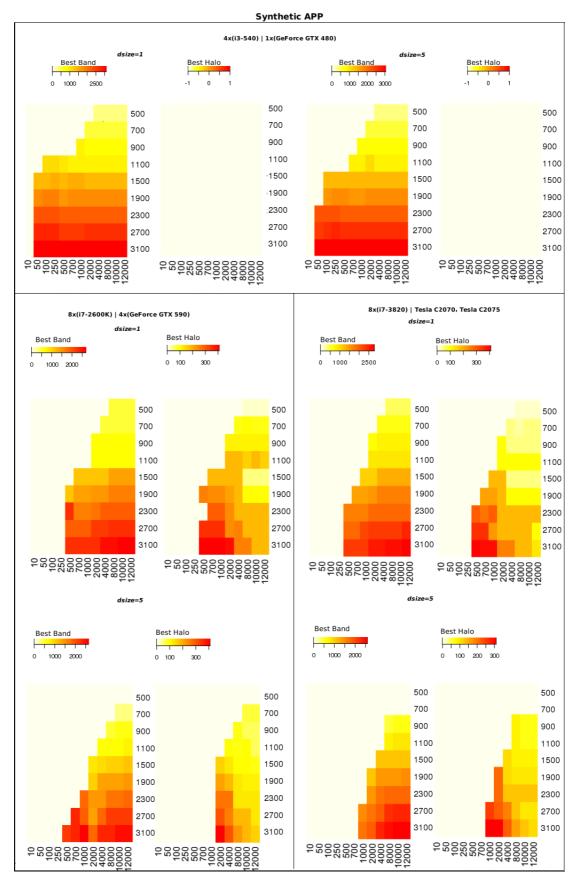

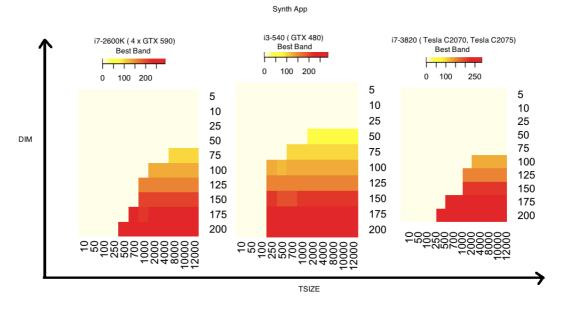

| 5.2  | Exhaustive Search Results : Synthetic application                                        | 83  |

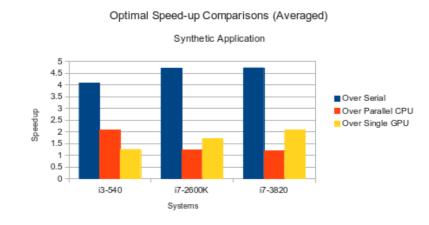

| 5.3  | Synthetic application speedup over baselines                                             | 85  |

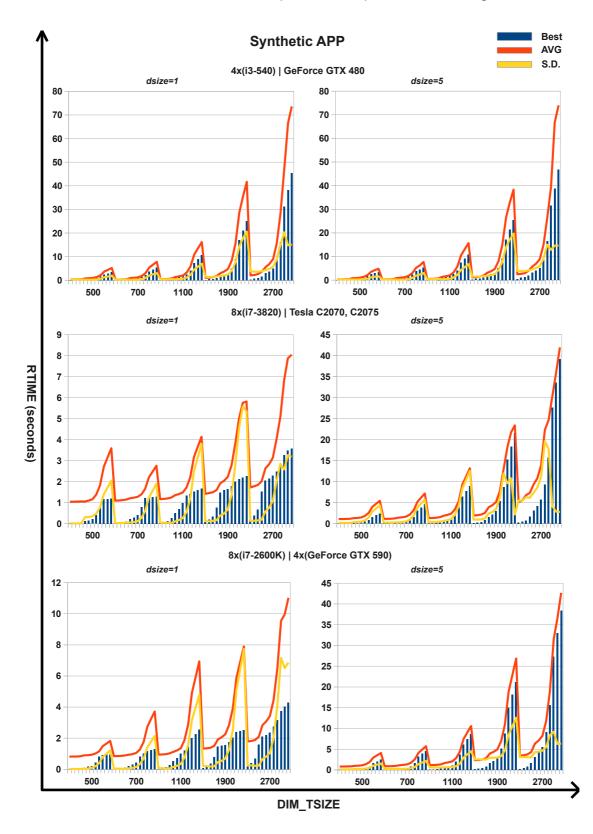

| 5.4  | Average case comparison for Synthetic Application                                        | 86  |

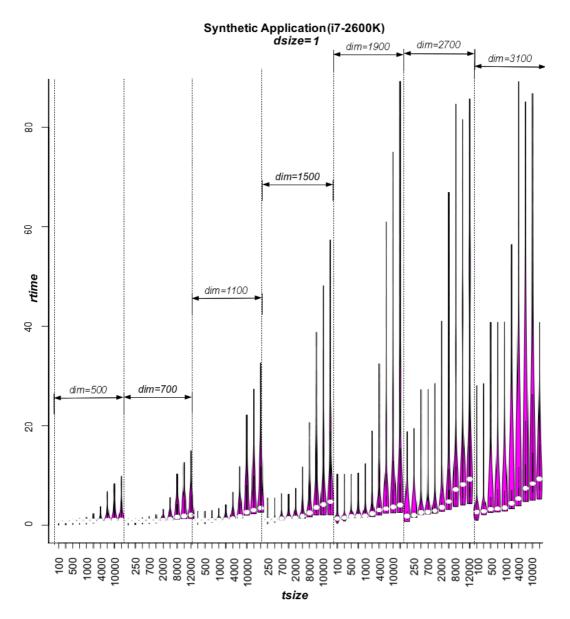

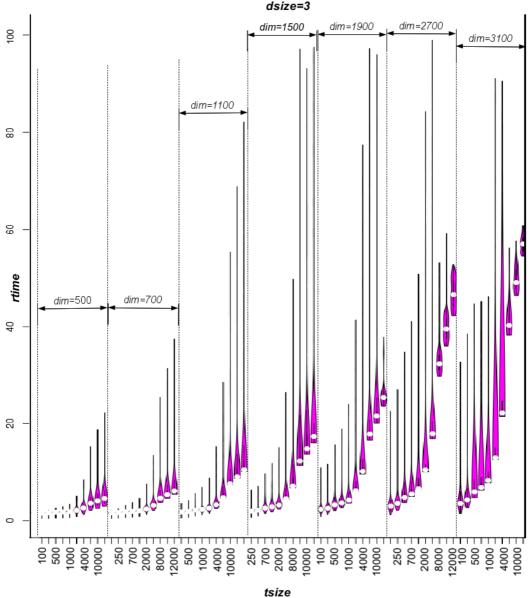

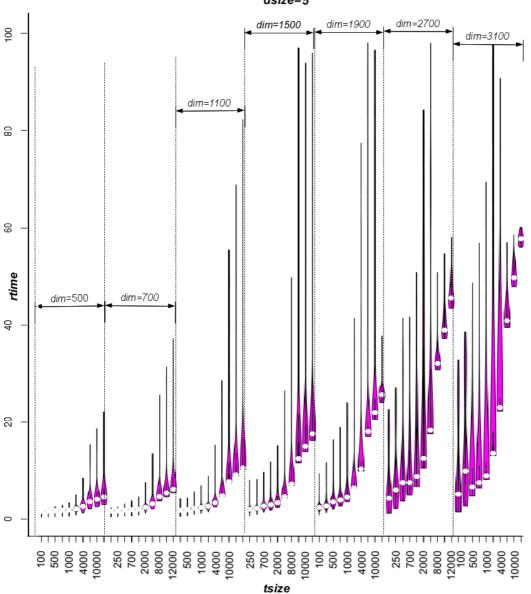

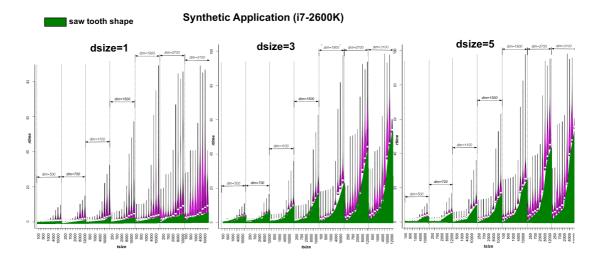

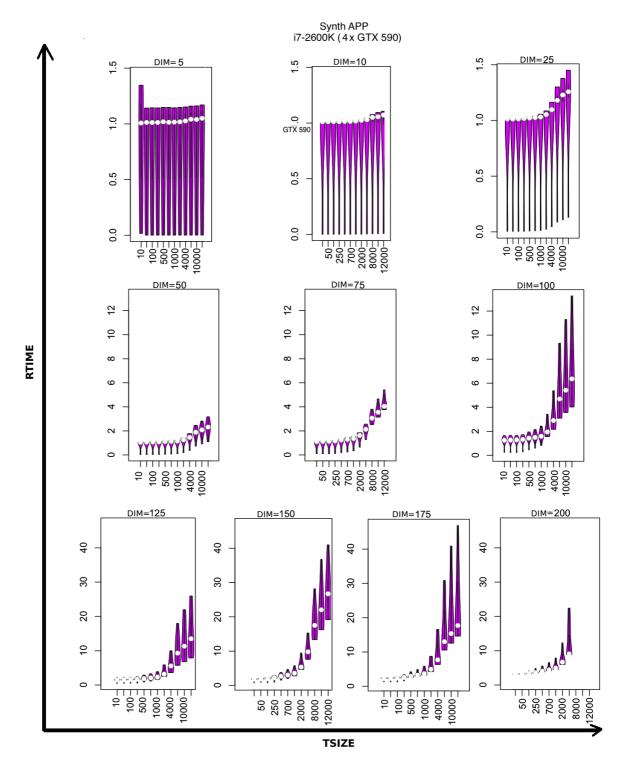

| 5.5  | Synthetic application : Dispersion on i7-2600K, $dsize = 1 \dots \dots \dots \dots$      | 88  |

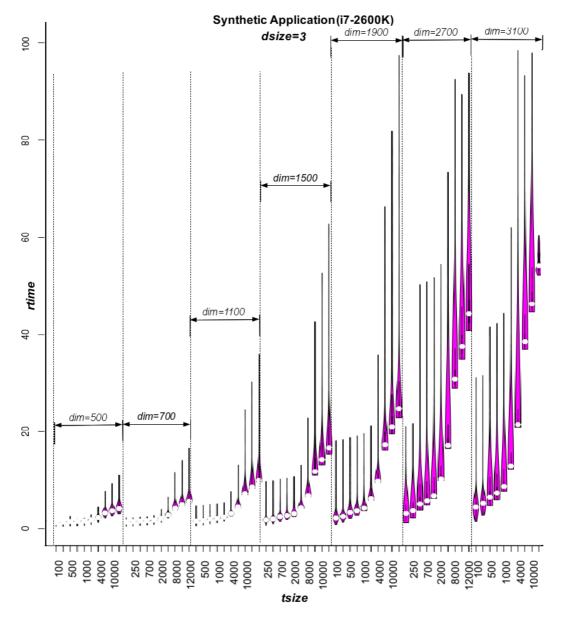

| 5.6  | Synthetic application : Dispersion on i7-2600K, $dsize = 3 \dots \dots \dots \dots$      | 89  |

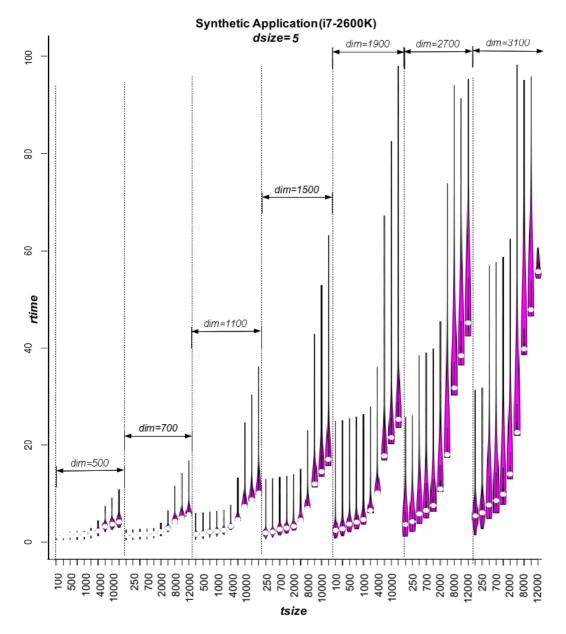

| 5.7  | Synthetic application : Dispersion on i7-2600K, $dsize = 5 \dots \dots \dots \dots$      | 90  |

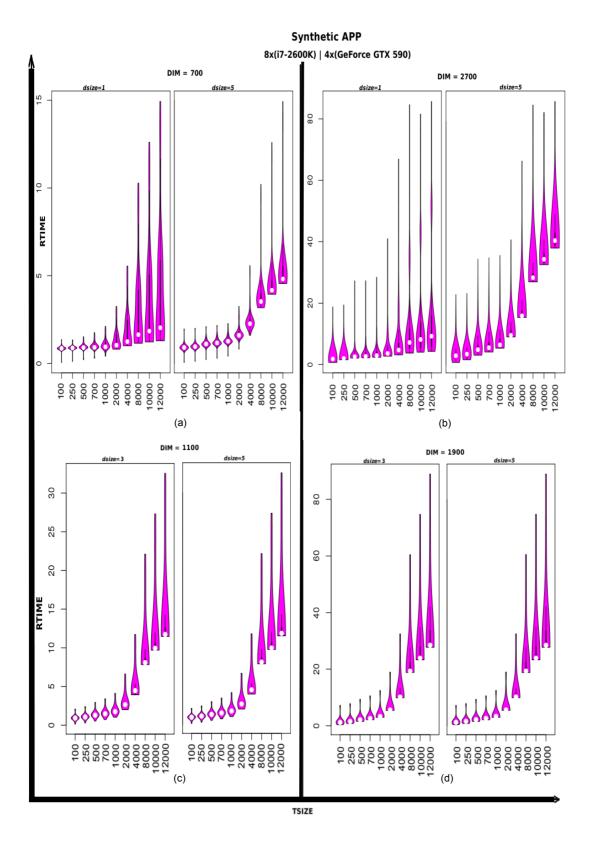

| 5.8  | Synthetic application : Dispersion for boundary and mid range cases                      | 92  |

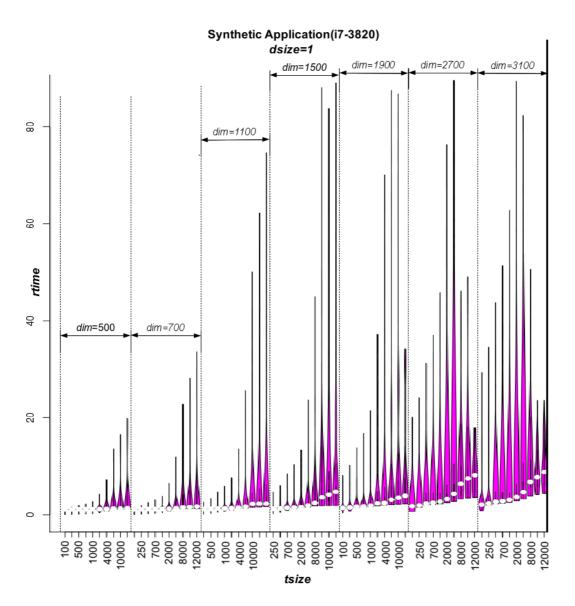

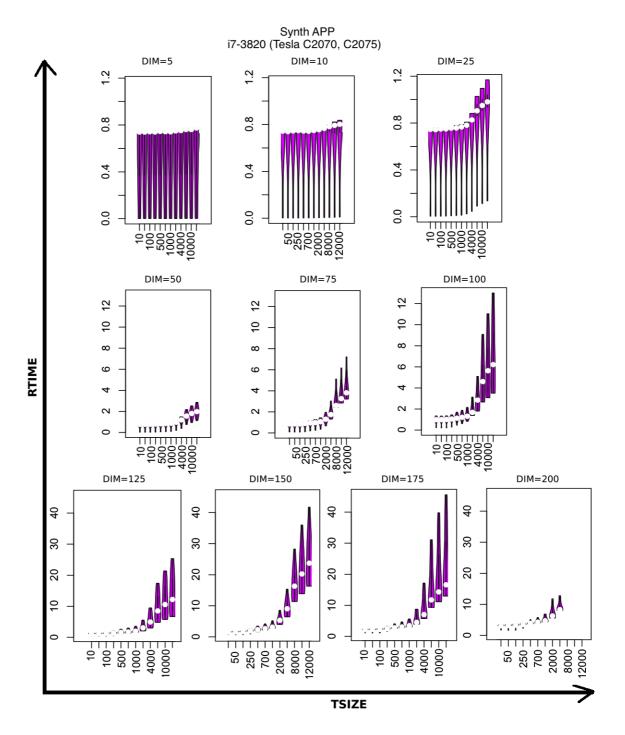

| 5.9  | Synthetic application : Dispersion on i7-3820, $dsize = 1 \dots \dots \dots \dots \dots$ | 94  |

| 5.10 | Synthetic application : Dispersion on i7-3820, $dsize = 3 \dots \dots \dots \dots \dots$ | 95  |

| 5.11 | Synthetic application : Dispersion on i7-3820, $dsize = 5 \dots \dots \dots \dots \dots$ | 96  |

| 5.12 | Saw Tooth distributions                                                                  | 97  |

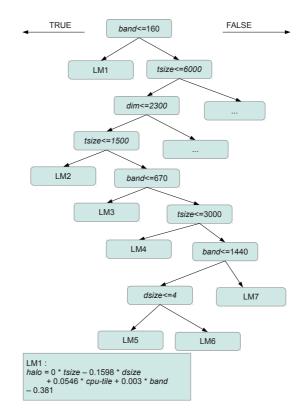

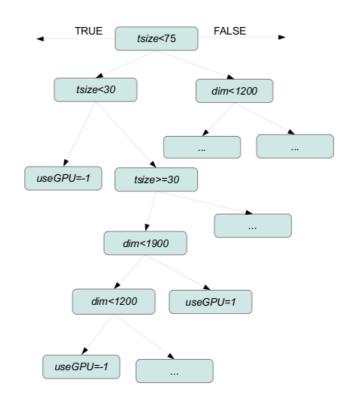

| 5.13 | The M5 pruned tree model                                                                 | 97  |

| 5.14 | Synthetic Speedup Comparisons                                                            | 98  |

| 5.15 | Autotuning performance : Nash application                                                | 99  |

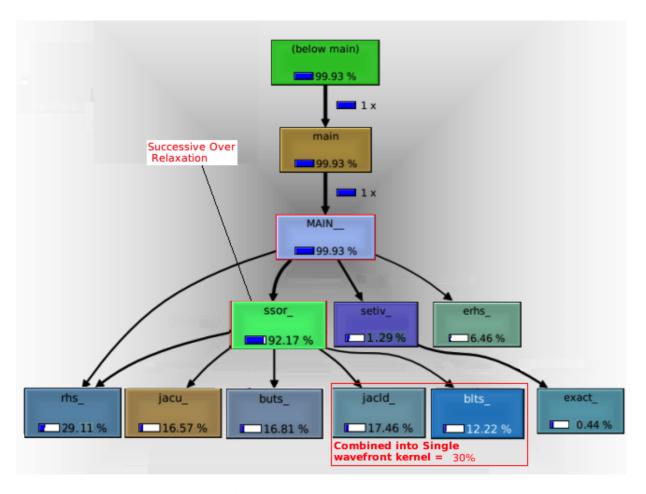

| 6.1  | Call graph of NAS-PB LU application                                                      | 104 |

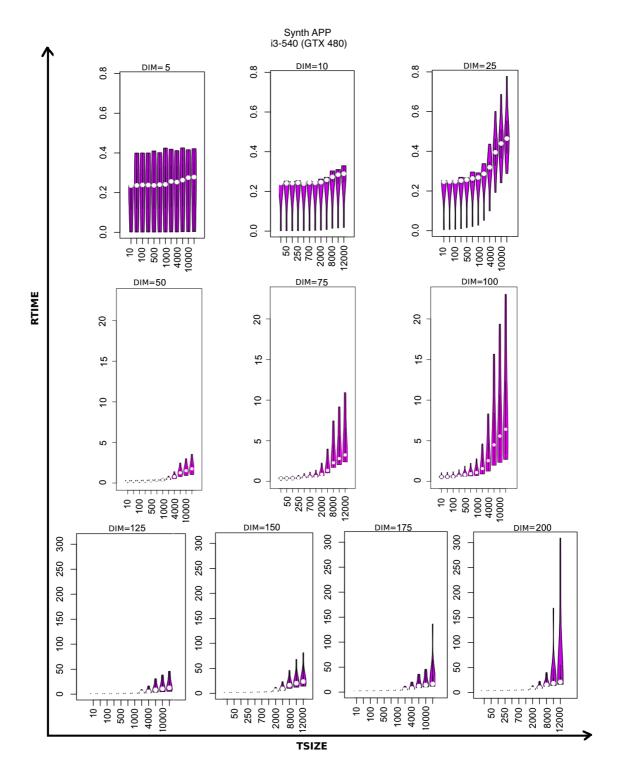

| 6.2  | Exhaustive search results : 3D Synthetic application                                     | 105 |

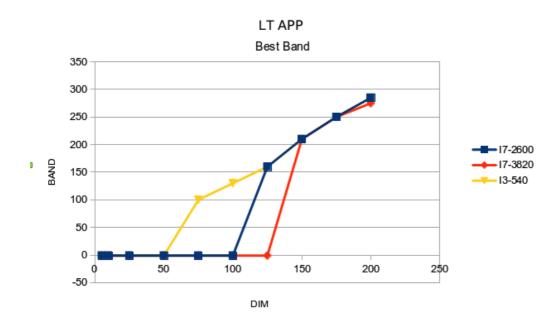

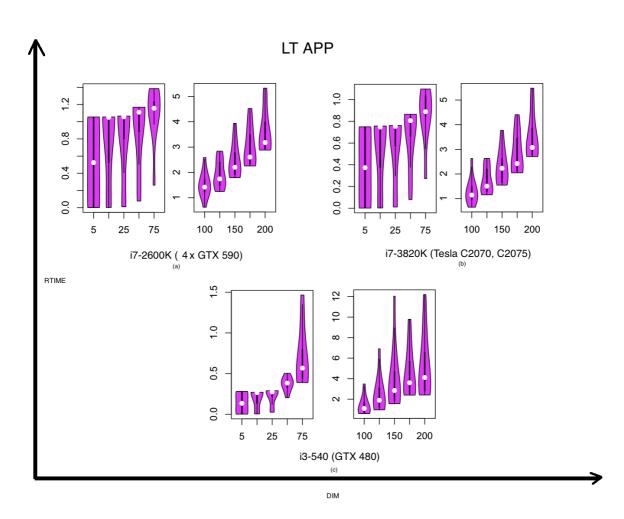

| 6.3  | Exhaustive search results : LT Application                                               | 106 |

| 6.4  | 3D Synthetic application : Dispersion on i7-2600K                                        | 107 |

| 6.5  | 3D Synthetic application : Dispersion on i7-3820                                         | 109 |

| 6.6  | 3D Synthetic application : Dispersion on i3-540                                          | 111 |

| 6.7  | LT application : Results All                                                             | 112 |

| 6.8  | REP Tree Tile Predictor                                                                  | 113 |

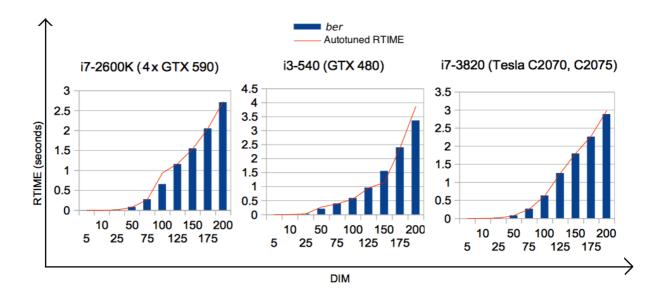

| 6.9  | Detailed autotuning performance : LT application                                         | 113 |

| 6.10 | Averaged autotuning performance : LT application                                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

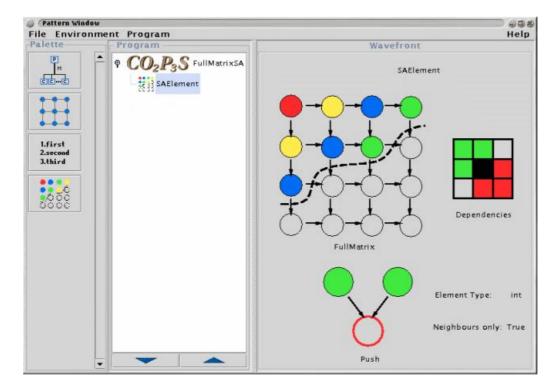

| 7.1  | The $CO_2P_3S$ framework $\ldots \ldots \ldots$ |

| 7.2  | Basic Farm prototype in <i>eSkel</i> library 119                                                                                                                |

| 7.3  | Task Farm in <i>Muesli</i> library                                                                                                                              |

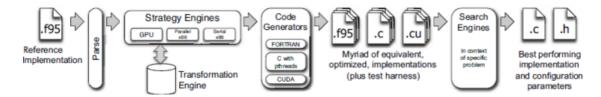

| 7.4  | The Berkeley Tuner framework                                                                                                                                    |

| 7.5  | The 3 tier Stencil Tuning framework                                                                                                                             |

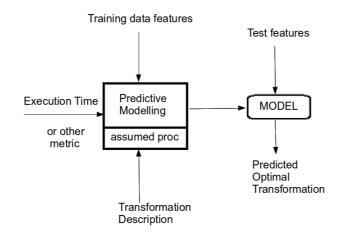

| 7.6  | Predictive Modeling in Compiler Optimization                                                                                                                    |

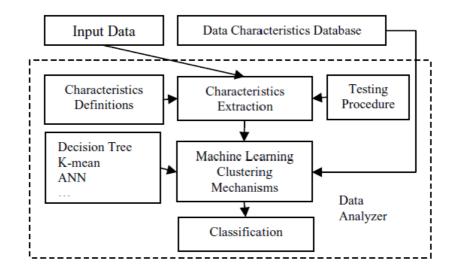

| 7.7  | Active Harmony framework : Data Analyzer                                                                                                                        |

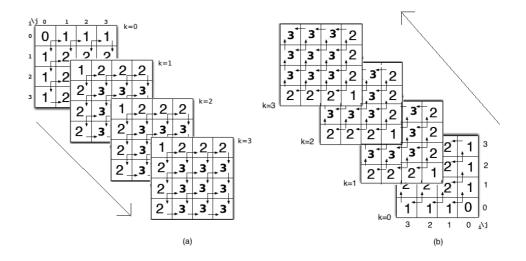

| 8.1  | Dependency Arrays for forward and reverse sweeps                                                                                                                |

# **List of Tables**

| 2.1 | Input Parameters                                         | 36 |

|-----|----------------------------------------------------------|----|

| 2.2 | Payoff Matrix for a Cooperation game in Nash Equilibrium | 38 |

| 3.1 | Tunable Parameters                                       | 47 |

| 4.1 | Experimental Systems                                     | 60 |

| 4.2 | Optimal speed-up across applications and systems         | 73 |

| 5.1 | Parameter Ranges                                         | 78 |

| 5.2 | Experimental Systems                                     | 81 |

## Chapter 1

## Introduction

Parallel computing literally means carrying out computations in parallel, i.e at the same time and encompasses the hardware aspect of dealing with the type and number of processors, and the software side of solving problems through computational models like shared memory or message passing [71].

Parallel computing can be seen in action in almost every field that requires large scale computation to be carried out as quickly as possible. Its application ranges from handling millions of transactions concurrently in an on line trading platform to making accurate weather forecasts that require massive computation power. IBM Deep Blue and Google data centers are all examples of such systems.

One of the earliest definitions of what constituted a parallel processor was provided by Almasi [2] who defined it as "a collection of serial processors which can communicate and cooperate to solve big problems fast". This old world high performance computing (HPC) landscape that envisioned large clusters of single core processors communicating over networks to distribute work and compute in parallel has been extended by heterogeneous architectures consisting of multicore CPUs and diverse accelerators that have made parallelism mainstream [6].

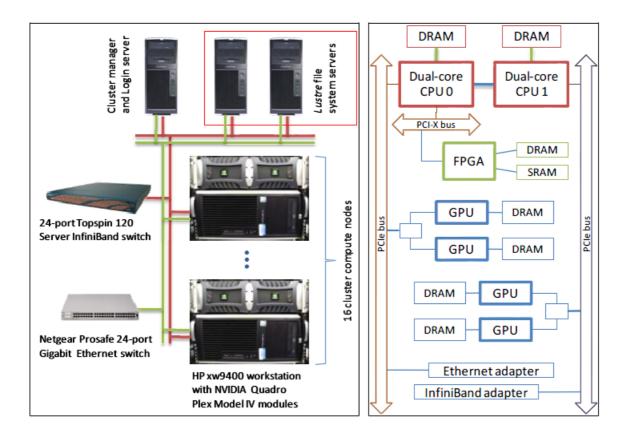

Thus the modern parallel landscape can be thought to be composed of three common forms of parallelism which typically overlap and can be merged in various combinations in real heterogeneous systems. The first form of parallelism is obtained from integration at the chip level such as the chip-multiprocessing as seen on Sun's UltraSPARC T2 Plus 8-core processor [35]. The next form of multiprocessing capability is obtained through clusters of workstations, for example the Beowulf Cluster [96] or the Edinburgh Compute and Data Facility (ECDF) [8] - a high-performance cluster of multicore nodes with 1456 processors that runs a Batch System where a user submits a job and waits in a queue until the resources it requires are available. Other examples of such multicore cluster systems are the CRAY XE6 series of supercomputers [41]. The third form of parallelism is seen in specialized accelerator devices including GPGPUs and FPGAs. A three tier form of parallelism (multicore-cluster-accelerator) can be seen in the system shown in 1.1. The supercomputing facility Tianhe [9] and the CRAY CS series of supercomputers [40] are examples of such clusters of accelerator workstations. There are more numerous examples of heterogeneous systems without the cluster level, such as modern personal computers and Ultrabook laptops that typically comprise of multicores and multiple GPUs. Our experimental systems also had two overlapping forms of parallelism - chip level and accelerator level.

Among accelerators, GPUs are increasingly ubiquitous as they have evolved from being used purely for graphical rendering in computer gaming to being used for non graphical processing for HPC applications. Taking advantage of the parallelism afforded by their hundreds of cores, GPUs have become cost effective alternatives to HPC hardware for applications whose problem structure is inherently data-parallel. Examples of such HPC applications include quantum chromo-dynamics experiments in physics [10], gene-sequencing in bio-informatics [3], competitive game theory problems in financial strategy [104] and incompressible flow computations [97]. However, using these specialized accelerators along with multicores brings its own challenges, as discussed in the next section.

Figure 1.1: Heterogeneous Computing Architecture, taken from [52]

#### 1.1 Heterogeneous Parallelism Challenges

The Heterogeneous Computing paradigm offers challenges in the form of the twin issues of problem decomposition-distribution and performance portability.

• Problem Decomposition and Distribution : MultiCore accelerator architectures pose problems to the application developer and programming and systems tool-chains. Firstly, the developer has to be able to decompose serial problems into parts that can be computed in parallel. After conceptually decomposing the problem, the programmer is then required to become an expert in multiple, conceptually diverse languages and libraries to implement parallelism, and to integrate these within single applications.

To exploit parallelism, an application programmer would prefer not to be bogged down by the low level details of handling communication and cooperation between processes across systems (problem distribution). Instead the primary focus of the programmer should be the computation task at hand. These twin issues can be addressed by an API or application programming interface. Besides getting ease of use from this layer of abstraction, the application programmer would also require this interface to be efficient which means, optimally exploiting all the available resources in the system. This brings up the next issue.

• **Performance Portability** : Performance tuning of such applications is complex, and typically much more architecture specific than in simpler, essentially homogeneous systems. The layer of abstraction that handles problem decomposition and distribution should ideally perform optimally across heterogeneous systems where the three forms of parallelism overlap and this performance portability should be transparent to the end user who should not be tasked with porting an application for each architecture.

Finding a programming methodology and toolchain which can address these challenges is widely recognized as being of major importance, both academically and industrially [14].

### 1.2 Contributions of this Thesis

Pattern-oriented parallel programming has experienced a recent upsurge in interest [72], and offers a promising approach to the twin challenges of heterogeneous parallelism mentioned earlier. Each pattern of interest is abstracted and encapsulated behind an API which requires the programmer to code only application specific aspects. This approach simplifies the programmers task (there is no parallelization "glue" code to write), and presents the system with a constrained optimization challenge of choosing between and tuning internal parameters of a set of pre-existing candidate, heterogeneous parallelizations.

We present a case study in the application of this approach by employing patterns in the form of algorithmic skeletons [20]. We chose skeletons because they are flexible and reusable constructs (skeletons can be nested inside other types of skeletons to create new patterns and they can be highly abstract or detailed). Skeletons handle the communicationsynchronization mechanism of concurrent operations, thus providing transparent problem decomposition and distribution. By being architecture-specifically tunable they also allow performance portability. We have provided background details of skeletons and the advantages of employing skeletons in section 2.3.

Our selected pattern is the *wavefront*, which captures a specific class of dynamic programming problems. We are interested in this pattern because the dependencies inherent in a wavefront make it challenging to parallelize across hybrid settings of multicore CPU processors and GPU accelerators (as compared, for example to embarrassingly parallel stencil patterns). A large number of applications exhibit the wavefront pattern across diverse domains including bio-informatics, financial game theory, particle physics and linear algebra. However, there has as yet been no extensive investigation into the tuning of wavefront patterns across heterogeneous systems. This means tuning wavefronts in such hybrid systems is an important area of research. The relevant background details regarding wavefront dependencies and applications are introduced in detail in subsection 2.5.1.

Our implementation strategy distributes wavefront applications across systems which incorporate a multicore CPU and multiple GPU accelerators. In order to better understand the tuning trade-offs, and to assist in the evaluation of our heuristics, we have performed an exhaustive exploration of an interesting fragment of the tuning space, across a collection of systems comprising a CPU and single or multiple GPUs. Since such an exhaustive search would be impractical in a production system, we have investigated the application of machine-learning strategies to reduce the search time. We have experimented across a range of wavefront applications and heterogeneous systems.

There are two main contributions of this thesis.

### Designing tunable high level parallel programming models for wavefront applications

In many high level parallel programming models employing skeletons, there are several opportunities for optimization. In one study of Intel Threading Building Blocks (TBB) [22], it was reported that increasing the number of cores increases the overhead costs to become as high as 47 percent of the total per-core execution time on a 32-core system. This highlights the need to tune the parameters of these models in order to avoid performance penalties. In this thesis we have identified what parameters can affect the runtime of our wavefront skeleton, and how to tune them.

Demonstrating effectiveness of machine learning for optimizing wavefront ab-

#### stractions on heterogeneous architecture

Many automated optimizations based on prior learning have been done at the low level for applications that are dependent on the hardware. However there are few that target high level parallel programming models. Utilization of these techniques in exploring the parameter space of wavefronts for heterogeneous architectures has provided empirical data showing how effective machine learning is for tuning a high level model like the wavefront.

### **1.3 Structure of the Dissertation**

The remainder of the thesis is structured as follows

- Chapter 2 provides all the background details related to the need for algorithmic skeletons to solve the parallel programming crisis, tuning skeletons through machine learning to enable performance portability, dynamic programming problems and terminologies associated with a special case of dynamic programming problem, the wavefront pattern and its applications.

- Chapter 3 discusses our skeleton or framework implementation strategy for 2D wavefront application in multicore CPU + single GPU and multicore CPU + multiple GPU systems. It then provides the details of implementing a 3D wavefront application in multicore CPU + single GPU systems. It also discusses our experimental setup, performance trade-offs in our framework and how they are tuned by using machine learning techniques.

- Chapter 4 first delves into the tuning strategy of a 2D wavefront application in a multicore CPU + single GPU environment. It then discusses the results of our exhaustive search of the tuning space and the evaluation of machine learning strategies for autotuning.

- Chapter 5 similarly delves into the experimental details of autotuning 2D wavefront applications in a hybrid multicore CPU + multiple GPU environment. The addition of another GPU increases the complexity of tuning with more tunable parameters and decisions to be taken.

- Chapter 6 provides autotuning experience for 3D wavefront applications. The results of an exhaustive search of optimal performing points are analyzed, and machine learning results for our autotuner are presented.

- Chapter 7 discusses related work, comparing our autotuning methodology and results with other similar autotuners.

• Chapter 8 concludes the thesis with a review of our contributions and discusses future work.

## Chapter 2

## Background

This chapter provides background information on topics relevant to our work. These relate to the opportunities and challenges of parallelism, discussed in section 2.1, followed by details of common parallel programming paradigms and their drawbacks in section 2.2. The limitations of commonly used parallel models highlight the need for abstractions. We introduce algorithmic skeletons, their classification, their guiding design principles, and address the issue of performance portability of skeletons in section 2.3. In section 2.4 we explain the need for predictive modeling based on the curve fitting concept, followed by an overview of some machine learning models that have been employed in this thesis. Since the wavefront pattern is a specific class of dynamic programming problem, we provide the necessary background to dynamic programming problems in section 2.5. This section then provides the conceptual details of the wavefront abstraction that forms the core of our thesis. The corresponding wavefront applications used in our work are described in section 2.6. Finally we conclude this chapter with a discussion of the measurement of parallel processing performance in section 2.7.

### 2.1 Parallel Computer Architecture

#### 2.1.1 Opportunities and Challenges of Parallelism

From late 20th century (1970 onwards), CPU processing capability has been steadily improving at exponential rates and is expected to continue until 2020 [85]. This observation is referred to as Moore's law which states transistor counts in integrated circuits double approximately every two years. The resulting increase in clock rates enables single-threaded code to execute faster on every new generation of processors with no modification. However, in 2005 Moore noted that transistors would eventually reach the limits of miniaturization at atomic level [86], i.e. transistor scaling would saturate owing to limited gate metals, limited options for channel material and limited material solutions for reducing source to drain leak-

age. Meanwhile, new computing prototypes such as quantum computing are at experimental stages and are a long way from becoming mainstream [38].

There is also the economic cost to increasing miniaturization. Rock's law states the capital cost of setting up a semiconductor fabrication plant increases exponentially with every new generation of chips [90]. Another constraint to Moore's law of adding more transistors to conventional CMOS chip is related to energy and power dissipation [30]. This is because increased transistor density leads to increased internal processor heat that results in overheating and excess energy use. Recent work in addressing this includes [30], that explores a design space of matching supply voltage with threshold voltage of the transistor to enable energy saving. This design however suffers from performance loss, as measured by the fanout-of-four inverter delay or F04 metric, which is 10 times slower compared to conventional supply voltage design.

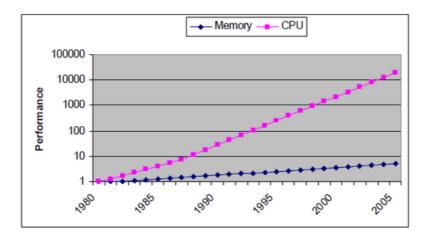

It should also be noted that merely doubling CPU capacity does not automatically improve performance. Memory bandwidth also plays a crucial role based on Von Neumann's limit [81]. So sequential computational performance is subject to the available memory bandwidth. The graph below underscores the increasingly expensive sequential memory access cost.

Figure 2.1: The Memory Gap, taken from [52]

One solution to the costly process of manufacturing faster chips that are energy efficient design and have improved memory bandwidth is to employ parallelism. The overall time taken to compute a large task can be quicker with multiple cheaper, but relatively slower, processors working on parts of the problem rather than one fast expensive processor computing the whole task. Based on our previous discussion of three tiers of parallelism in chapter 1, we discuss how each tier of parallelism can outperform sequential processing and also compare their relative strengths and weaknesses.

#### 2.1.1.1 Multiple Node Architecture

In the traditional HPC parallelism, clusters of nodes form a distributed address space. The distribution of large tasks and chunks of data across nodes reduces the memory load on individual nodes and overcomes sequential bottlenecks. This performance is limited by the network speed but with high speed connections (Infiniband/Ethernet) the traditional HPC based parallelism can outperform sequential processing, subject to Amdahl's law.

#### 2.1.1.2 Shared Memory Architecture

Next we look at shared memory systems consisting of a single node but multiple processing cores that share a single address space. The immediate benefit over a sequential single core system is the greater computing capacity afforded by the multiple cores present on a chip. Compared to traditional HPC clusters, they also do not suffer from network bottlenecks of distributed systems. However, shared memory systems incur the additional architectural overhead of maintaining cache coherency and the programmers are also burdened with understanding the intricacies of relaxed consistency memory models needed for cache coherent (CC) systems. The time and memory cost of scaling the number of cores on a CC system quickly grows beyond a point at which additional cores are not useful in a single parallel problem. This is referred to as the *Coherency Wall* [70].

#### 2.1.1.3 Manycore Architecture

We now look at many core computing or massively multi-core systems which refer to systems having processors numbering hundreds to thousands, with the exception of the traditional distributed systems. These include shared memory systems with high processor counts and accelerator based (GPU, FPGA) systems.

An example of such a shared memory many core system is the 48 core Intel Single Chip Cloud platform [80] which internally implements message passing between its cores and can be considered to possess a hybrid address space.

Accelerator based heterogeneous architectures consist of one or more GPGPUs or FP-GAs. Due to the availability of hundreds of compute units on GPUs, these systems can outperform sequential processing. They also do not suffer from network bottlenecks of distributed systems but global memory contention and data transfer overheads. These systems are also limited to SIMD parallelism (discussed later in subsection 2.2.3) and are constrained by bandwidth limitations of PCI-E. Improvements to PCI-E layout in [68] helps reduce this bandwidth overhead. [16] demonstrates heterogeneous GPGPU parallelism wins over sequential memory access bottlenecks by adding memory layout remapping that takes advantage of concurrent GPU operations while overlapping with PCI-E memory transfer.

### 2.2 Parallel Programming Paradigms

The benefit of parallelism is obtained after problem decomposition has been carried out. This is subject to Amdahl's constraint of parallelism being limited by the sequential parts of the code [53]. Both problem decomposition and the subsequent work load distribution are challenging tasks, but the performance gains with a parallel system are often many times higher than the single core system. Keeping the need for parallelism in mind we now delve into the many conceptually distinct programming models that address parallelism, to illustrate how challenging it is to integrate or port to these very different models. We address those differences by first discussing the two leading programming paradigms for systems based on clusters and multicores - Message Passing (MP) and Shared Address Space (SAS) [92]. Then we discuss the accelerator programming languages for GPUs - CUDA and OpenCL.

#### 2.2.1 Message Passing Paradigm

We begin with the message passing model which gives each process its own address space. The task is to distribute data across these address spaces and provide communication between processes by sending and receiving messages.

In the world of Message Passing, MPI has been enjoying the position of de facto standard since its inception [51]. Even recent programming systems like MPJ Express that target multi-core processors are, nevertheless MPI hybrids having MPI-like libraries [91]. As a distributed memory programming model, MPI is based on explicit control parallelism as defined by the MPI standard [15], making it a language independent communications protocol. It supports point to point communication that involves two processes in a process group and collective communications that involve all processes in a process pool. MPI subroutines can be called from any language that is able to interface with its libraries since MPI uses language independent specifications for calls. Hence there are C/C++, Fortran, Java and Python implementations of MPI.

A sample point to point MPI operation for sending data is as follows : MPI \_Send (start, count, datatype, destination, tag, communicator) in which the message buffer has a starting address, the number of elements in the count and the size of each element as per the datatype. The target process rank (a number between 0 and MPI \_COMM \_SIZE -1 where the latter is the total number of processes in the global MPI communicator) is given by destination and tag can be used to obtain status information or send any additional data.

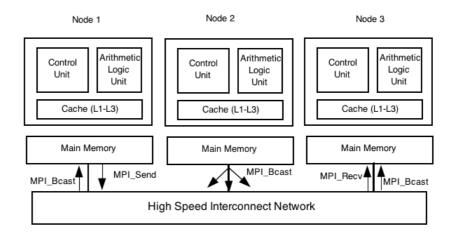

Figure 2.2 shows both point to point communication in the form of MPI \_\_Send, MPI \_\_Receive and the collective operation MPI Broadcast among three nodes in a cluster. MPI \_\_Send enables a process to send a message to another process which receives the sent message through MPI \_\_Receive. The Send-Receive operations can be blocking or asynchronous non

**Figure 2.2:** The MPI model : 3 nodes communicating over a high speed interconnect using point to point communication like MPI\_Send from Node 1, MPI\_Recv to Node 3, and the MPI\_BCAST collective communication from Node 2 to Nodes 1 and 3.

blocking. In MPI collective communications like MPI\_BCAST, every process including the receiver processes of Node 1 and Node 3, have to participate by calling the broadcast routine which has a parameter specifying the *root* or the sender process (Node 2 in the figure).

MPI \_\_Bcast call takes data from one node and sends it across all other nodes in the process group. The data transferred during these operations can be predefined MPI datatypes like MPI \_\_INT, MPI\_\_CHAR or custom defined ones. A key feature of MPI is its dynamic process management, which establishes connection between MPI processes that have been independently spawned. MPI is thus well suited to task parallel applications such as the Task Farm where worker nodes can independently start working on chunks of work and return results to a master node.

#### 2.2.2 Shared Address Space (SAS) Paradigm

The shared address space model allows threads or lightweight processes to directly interact through shared memory locations. This model raises the issue of memory consistency i.e., when and in what order should updates to memory made by one processor become visible to other processors. There are also race conditions to be dealt with, where threads compete against each other for access to the shared resource.

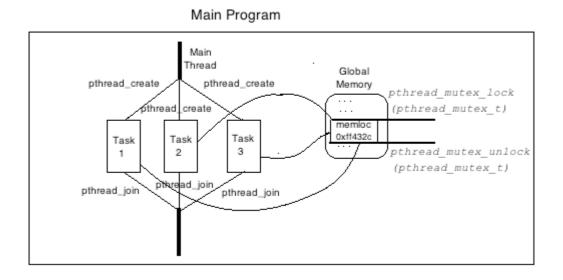

C's POSIX threads or Pthreads [11] form the standard for thread programming in which the main thread/process can start, synchronize and stop other threads of activity within its address space. Pthreads is a standardized model for interleaving the execution of sub-tasks partitioned from a main task. Parallelism is achieved as each thread begins the execution of a given function, which either terminates upon that function's exit or is terminated by another thread. A sample Pthread flow is shown in figure 2.3 where the main thread creates three different threads to work on three sub tasks using pthread \_\_create. This method is of the form

$$pthread\_create(thread, attr, start\_routine, arg)$$

(2.1)

thread refers to a unique identifier for new threads. attr deals with various properties like scheduling policy, parameters and contention, stack size, address etc. The start\_routine is basically a C function pointer. arg deals with arguments to the subroutine, passed by reference as pointer cast of type void. To synchronize the execution of the spawned threads, the main thread calls pthread\_join, which suspends the main caller thread until the spawned thread exits. Once all three subtasks are completed, the caller thread resumes execution. Since all three threads access the same memory location, entry to the critical section is restricted to one thread at a time through mutexes that enforce mutual exclusion with mutex lock and unlocks.

Figure 2.3: Three threads being spawned through pthread \_create to work on 3 subtasks independently, using a mutex to safely access the shared memory location and update shared variables, before being joined to the main spawning thread using the pthread \_join synchronization mechanism

The Pthreads standard specifies concurrency, meaning tasks defined by the programmer can occur before or after another or in parallel, depending on the operating system and the hardware they run on. Thus Pthread programs can run on both single cores and multicores.

The OpenMP [24] application program interface (API) is popular for the SAS paradigm, particularly for multi-cores. It is a portable programming interface in C/C++ or Fortran and supports multi-platform parallel programming on all architectures.

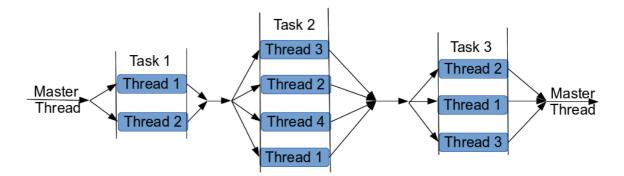

OpenMP implements multi-threading by spawning a specified number of worker threads from a master thread and divides tasks among them. The threads run concurrently and are allocated to different processors by the runtime environment. This is illustrated in Figure 2.4 In OpenMP threads are created using the pragma directive **omp parallel**. OpenMP provides

**Figure 2.4:** Master thread forking worker threads using pragma omp parallel directive and tasks assigned to threads, which are themselves bound to different processors by the runtime. These worker threads synchronize into the master thread without the need for explicit join statements as in pthreads.

work-sharing loop constructs like *omp for* and *omp do* that partition loop iterations among threads. Shown below is a code listing that demonstrates loop splitting among 10 threads using parallel for. Each element in an array of size 10 creates a task which is assigned to implicit OpenMP threads that independently squares that element.

```

// example of loop construct : omp parallel for

#include <omp.h>

void main(int argc, char *argv[]) {

const int NUM_THREADS = 10;

int i, demo[NUM_THREADS];

#pragma omp parallel for

for (i = 0; i < NUM_THREADS; i++)

demo[i] = i * i;

```

}

Unlike Pthreads, here the programmer does not have to worry about explicitly creating and synchronizing the spawned threads. However, OpenMP provides synchronization clauses like static scheduling where threads are allocated loop iterations before executing or dynamic scheduling where smaller number of threads dynamically fetch new iterations after completing their initial allocated iterations. OpenMP also provides data sharing attribute clauses, such as shared data region which is accessible by all threads or private data region where each thread have their own local copies of variables.

Intel's Threading Building Blocks (TBB) [31] is also becoming a popular alternative. It provides easy to use thread safe container classes and templates that abstract out low level details such as multiple thread synchronization and load balancing among processes. Unlike

the low level threading API Pthreads, the TBB library provides high level abstractions in the form of algorithms. Like OpenMP, TBB provides loop templates such as *parallel for*, parallel\_reduce, parallel\_do etc. These loop templates are powered by its runtime engine called the *task scheduler*. TBB operations are treated as tasks that are allocated to multicore processors dynamically by the library's run time engine which efficiently utilizes the CPU cache. Thus, TBB employs logical tasks instead of the usual logical threads that map onto the physical threads of hardware, which are lightweight compared to logical threads. The time taken to spawn and terminate a task has been measured at 18 times faster than the thread creation and termination in Unix systems, and on Windows system the ratio exceeds 100 [69]. The reason for this is logical threads require a local copy of register state, stack and a process identifier (in Linux). TBB tasks in contrast, are small routines which can not be preempted at task level. Besides, thread schedulers typically distribute time slices in a fair round robin fashion as this is a safe strategy that does not require high level understanding of the program structure. Since TBB provides abstractions mapped to algorithms, the tasks have some higher level information which allows the task scheduler to employ a greedy work-stealing algorithm resulting in higher efficiency. The tasks are executed respecting their internal graph dependencies and the scheduler assigns tasks to the underlying threading API (Pthreads in Posix systems), providing efficient load balancing. TBB also provides atomic operations and built in atomic template classes that provide better performance compared to manually enforcing atomicity in OpenMP [28]. A sample parallel\_for is shown in the below code listing.

#include "tbb/tbb.h"

```

void ParallelApplyFoo( float a[], size_t n ) {

parallel_for(blocked_range<size_t>(0,n), ApplyFoo(a));

}

```

The entire iteration space 0 to n-1 represented by the blocked \_\_range construct is divided into subspaces for each processor by the parallel \_\_for loop template. ApplyFoo is the functor (whose implementation is not shown for sake of brevity), that is applied to each resulting sub-range of the array of floats 'a'. With this discussion we conclude the subsection on shared address spaces and move on to the accelerator programming paradigm.

#### 2.2.3 Accelerator Programming Paradigm

While scaling complex CPU cores to hundreds or thousands is hard, there are already thousands of simpler RISC based cores working in a SIMD fashion [61] inside GPUs. Early GPUs were used for graphic processing activities like rendering images, but with heterogeneous computing becoming mainstream, general purpose GPU computing has increased in usage. However, due to the single instruction multiple thread limitation of GPU architectures where a single instruction executes on multiple work-items, having any kind of control flow like if - else blocks means all work-items execute the if block first and then all of them execute the *else* block. This contrasts with pthreads in CPU multi-cores that operate in SPMD (single program multiple data) fashion. A pthread can be assigned to the if block and another to else block and both will execute simultaneously.

Software implementations for programming GPUs are based on either the CUDA programming language, which is specific to NVIDIA graphic cards or OpenCl programming language [34] which is platform agnostic. Another implementation of heterogeneous computing is the Asymmetric Distributed Shared Memory (ADSM) programming model that "maintains a shared logical memory space for CPUs to access objects in the accelerator physical memory but not vice versa" [45]. This allows for light weight implementation, reduced programming effort and increased portability.

OpenCL and CUDA are the two dominant GPU programming languages and our auto tuning framework is built on OpenCL as it is more portable compared to CUDA. It should be noted that CUDA and OpenCL programming models are SIMT or Single Instruction Multiple Thread which is more flexible than SIMD with some additional costs. SIMT has scalar syntax instead of vector syntax, so the code is written for a single thread using standard arithmetic operators, instead of assembly-like opcodes in SIMD loops.

An example of an OpenCL kernel or computation function which is executed inside the GPU is shown below.

```

__kernel void constant_add_gpu (const int num,

__global const float* src_a,

__global float* res

)

{

/* get_global_id(0) returns the ID of the thread in execution */

const int id = get_global_id(0);

/* Now each work-item performs the corresponding computation of adding num to

itself */

res[id] = src_a[id] + num;

}

```

SIMT allows a single instruction to be applied to multiple addresses enabling indirect memory access in the form of a[b[i]] where the index for array a is computed from b[i]. Finally SIMT allows flow divergence. This is explained in the code listing below.

\_\_kernel void constant\_apply\_even (const int len,

```

__global const float* src_vector,

__global float* res

)

{

/* get_global_id(0) returns the ID of the thread in execution */

const int id = get_global_id(0);

/* Now only even work items will compute */

if(id%2==0) //Flow Divergence

res[id] = src_vector[id] + id

}

```

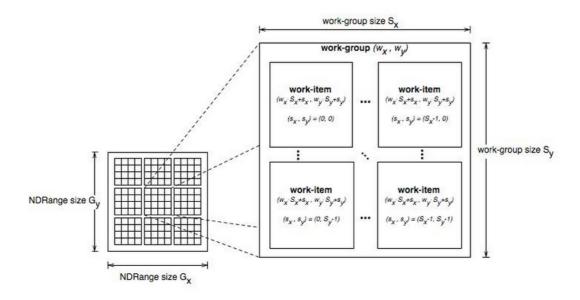

In a GPU, the work item is the smallest entity of execution (analogous to a thread) which has an ID to distinguish the data being computed by it. The programmer specifies the number of work items to be spawned upon launching the kernel and each work item executes the same piece of kernel code. Work items can be synchronized inside work-groups that allow the work items to communicate and cooperate as shown in figure 2.5.

Figure 2.5: Spawned work items organized into a 2D grid of work groups. The number of work groups are specified by the NDRangeKernel which enqueues a command to execute a kernel on a GPU or even CPU device, adopted from [44]

The programmer has to manage transferring data to and from the GPU and firing off GPU kernels on available GPU device on appropriate GPU supporting platforms. These actions form part of the host code which is executed on the CPU. An example of host code listing is shown below.

```

. . .

/*1. Get the Platform */

clGetPlatformIDs(1, platforms, &platforms_count);

/*2. Get the GPU devices, max 10*/

clGetDeviceIDs(NULL, CL_DEVICE_TYPE_GPU, 10, devices, &devices_n);

/*3. Create the CL context inside which compute devices will be available*/

clCreateContext(NULL, devices_count, devices, &pfn_notify, NULL, &_err)

/*4. Create a command queue which will queue kernel calls */

command_queue = clCreateCommandQueue(context, device_id,CL_QUEUE_PROFILING_ENABLE,

&ret);

1

/*5. Create a program from the kernel source */

cl_program program = CL_CHECK_ERR(clCreateProgramWithSource(contexts, 1,

(const char **)&source_str, (const size_t *)&source_size, &ret));

/*6. Build the program */

clBuildProgram(program, devices_count, devices, "", NULL, NULL);

/*7. Create the OpenCL kernels */

cl_kernel sum_kernel= clCreateKernel(program, "constant_add_gpu", &ret);

/*8.Create memory buffers on the device for the vector */

cl_mem lmv_mem_obj=clCreateBuffer(context, CL_MEM_READ_WRITE,

(global_item_size)* sizeof(float), NULL, &ret);

/*9. Load data into the memory buffer*/

float lmv[global_item_size];

initialize(lmv);

clEnqueueWriteBuffer(command_queue lmv_mem_obj, CL_TRUE, 0,

global_item_size* sizeof(float), lmv, 0, NULL, &buffer_completion);

/*10. Set kernel Arguments - num value */

int myNum=10;

clSetKernelArg(sum_kernel, 0, sizeof(int), &myNum));

/* 11. Now execute the kernel by enqueuing it on the NDRange ! */

clEnqueueNDRangeKernel(command_queue,sum_kernel, 1, &start_offset,

&global_item_size,NULL,0,NULL,&kernel_completions);

/*12. Wait for computations to be over*/

clWaitForEvents(1, &kernel_completions);

/*13. Load the results back to CPU after GPU computation is over */

clEnqueueReadBuffer(command_queue, lmv_mem_obj, CL_TRUE, 0,

global_item_size*sizeof(float), lmv], 0, NULL, &readEvent);

/*14. Finally clean the cl buffers*/

clReleaseCommandQueue(command_queue); ....

```

As seen from the code listing, a lot of boiler plate code dealing with loading data to and

from the GPU and executing the actual computation kernel needs to be written on the host side (steps 1 to 10 and 12 to 14).

In the case of simultaneous CPU-GPU processing, it is usual for the sequential control intensive tasks of an application to be executed on the CPU while the data parallel tasks of the application that need to be operated in a SIMT manner are executed by the GPU or accelerator.

#### 2.2.4 Current Parallel Programming Model Advantages and Limitations

We now look at the comparative advantages and limitations inherent in these existing message passing, shared memory and accelerator models.

#### 2.2.4.1 Message Passing

#### Advantages

Most high performance computing codes are written in the message passing paradigm. The advantages of employing message passing are :

- Distributed systems require explicit message passing models and the overall cost of building such clusters is less compared to large shared memory systems.

- Message passing models like MPI are more portable across systems as they can be utilized on both shared memory and distributed architectures

- Message passing models provide better safety because each process has its local copy of variables on which it operates. This prevents any kind of race condition or unexpected change of local variable state.

#### Limitations

MPI is a low level distributed programming model that has its share of drawbacks as mentioned in [94]. These are as follows:

- It places the entire burden on the programmer for being responsible for many low level implementation details, ranging from setting the communication among processes to resolving any deadlocks that may arise.

- The programmer alone has a global view of the problem as the processes themselves are only able to read and write data to their respective local memory. This data is copied and communicated to local memory locations of the processes through method calls making global operations expensive.

- Finally making the programmer responsible for all low level decisions increases the scope for adding bugs to programs.

#### 2.2.4.2 Shared Address Space Programming

#### Advantages

- Shared address space models are easier to program and understand due to readily available loop parallelization constructs that require few lines of code to implement. This also allows maintainability and easier debugging.

- Shared address space models like OpenMP provide flexible parallel coding due to incremental parallelization obtained by adding directives over loops or blocks. The parallel parts of the code can run sequentially on a single core with no modification.

#### Limitations

In case of the Shared Address Space paradigm the ease of programming comes with some drawbacks. They are as follows:

- SAS systems face performance limitations due to poor spatial locality and high protocol overhead. This was observed in [92], where the GeNIMA SVM protocol was used for SAS on a cluster of eight, 4-way SMPs and it was found that using this in place of MPI gave roughly a factor-of-two deterioration in performance for many applications.

- While MPI has extra work upfront, optimization and debugging is easier compared to multi-threaded shared memory systems. So project time to solution can be longer in SAS [70].

- Unlike message passing systems, shared address systems need to deal with race conditions which can be challenging. For example, proving that a shared address space problem using semaphores will be race free, is an NP-complete problem [70].

#### 2.2.4.3 Accelerator Programming

#### Advantages

• Accelerator programming languages like CUDA and OpenCL provide the only means to program GPUs for general purpose computing and offer optimized solutions for exploiting the concurrency from hundreds of GPU cores.

#### Limitations

• Accelerator programming languages suffer from the drawback of being very low level with the application programmer responsible for transforming data based on the memory layout of the accelerator device and handling data transfer between host and accelerator devices.

- The programmer has to learn domain specific libraries that target particular architectures. For example CUDA programming is aimed at NVIDIA based accelerators only. OpenCL is more generic than CUDA but it requires a lot more boiler plate setup code in comparison to CUDA as discussed in subsection 2.2.3.

- The SIMT programming model of CUDA and OpenCL provides flexibility in the way of expressive scalar syntax but has the drawback of maintaining registers to store redundant data items. The indirect memory access is also limited to registers so a[b[i]] can scale to tens of elements, not tens of thousands of elements. This is because indirect memory access is unfeasible at the DRAM level (which is farthest from GPU cores, sitting outside the chip, see figure 1.1 ) since random access is not efficient and even within shared memory random access is slowed by bank contentions[61].

- Divergent flow leads to randomizing of memory access and unlike the SPMD (Single Program Multiple Data) model only one path is executed at a time forcing idle threads to wait for the active thread to complete execution. This makes multiple if else branches expensive and contrasts with pthreads whose SPMD model allows concurrent execution of multiple branches.

#### 2.2.5 Summary

The drawbacks found in current parallel programming models suggest the need for a model that provides a layer of abstraction to handle low level operations while allowing the programmer to concentrate on the problem at hand. Also, the very existence of a multitude of parallel programming models makes integrating them to address heterogeneous parallelism a challenging task. This motivates the case for algorithmic skeletons.

## 2.3 Algorithmic Skeletons

A skeleton is essentially a second order function which accepts functions instead of simple data types as its arguments, and returns functions that accept the details of a specific problem as its results. The arguments passed to a skeleton are methods which are specific to a problem, while the structure of the skeleton would be the overall computation pattern that needs to be applied to the methods passed to it.

#### Advantages

• Algorithmic skeletons address the two fundamental issues of any parallel programming model, i.e. of *problem decomposition*, which is the identification of parallelism, and *distribution*, which is the physical implementation of the parallelism identified by decomposition.

- The distribution and manipulation of data across the processors based on the hardware topology is also handled implicitly by the skeleton. The application programmer has to be only concerned with supplying the arguments and may not even be aware of the implicit parallelism built into the skeleton. The system implementer creates the general computational structure of the skeleton.

- The fragmented programming nature of skeletons allows independent skeletons to coexist, differentiating them from other systems that are either too highly abstract to implement any specific solution, or are restricted to function optimally in a particular hardware setting.

#### Limitations

- There is a restriction placed at the highest level of the structure of the skeleton regarding what computation it can perform. Since the programmers are not aware of the underlying parallel implementation (and they do not have access to it), they are restricted to exploiting parallelism offered by the skeletons without being able to modify the skeletons.

- The restricted structure of skeletons means they are generally not portable across different architectures without tuning some of their components. This is elaborated later in section 2.3.3.

#### 2.3.1 Classifying Skeletons

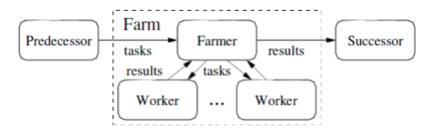

Poldner et al. [54] have classified Skeletons as either Task Parallel or Data Parallel depending on the kind of parallelism used. Task Parallel skeletons are responsible for dynamically setting up the communication among processes and distributing tasks using the concept of nesting. They include the farm or pipeline skeletons [20] among others. Task parallel skeletons, like atomic processes, accept a sequence of inputs and produce a sequence of outputs. This allows them to be nested in any manner. A concrete example of the task parallel skeleton, the Task Farm is shown in figure 2.6. The farmer node distributes tasks to worker nodes in a demand driven manner and then collects results from the workers. Task Farms can have multiple farmer nodes handling many workers, and computation involves an iterative process of the farmer distributing a large task across idle worker nodes, receiving results and assigning the next piece of task and so on, until all tasks are complete. The Data Parallel Skeletons, in contrast to the task parallel ones, perform the same task or operation across a bulk data structure such as an array. Examples of this type of skeleton are Map, Fold, Rotate [25] and the wavefront which will be discussed later in section 2.5.1.

Abstractions are also provided by Intel's Threading Building Blocks (TBB) [31]. This has become popular for multi-core processors by providing easy to use thread safe container

Figure 2.6: The Basic Task Farm, taken from [54]

classes and templates, that abstract out low level details such as multiple thread synchronization and load balancing among processes. In Threading Building blocks skeletons are found in the algorithm templates like pipeline and parallel \_do.

With this overview of different types of algorithmic skeletons we now focus on some practical guiding principles for the design and development of skeletal systems.

#### 2.3.2 Guiding Principles for Skeleton System Design

Research into design patterns for high performance computing stresses the advantages of Object Oriented (OO) languages for implementing skeletons [21]. The convergent experiences of design pattern based and skeleton based systems necessitate sound software engineering principles and motivate four principles which we will follow in our design.

- Minimal conceptual disruption Skeletal programming is neither a completely abstract declarative system based on functional programming nor is it a fully object-oriented one. It should not be restricted to these two concepts rather it should be a bridge to the de facto standard for parallel programming.

- Integrate ad-hoc parallelism Since we cannot expect skeletons to provide complete parallelism, the system should have a well defined process to allow integration of skeletons with ad-hoc parallelism.

- Accommodate diversity The system should not be restricted by its own specification. For example, a pipeline specification requiring each stage to produce one output for each input is too restrictive, as it excludes algorithms that have stages where one input generates many outputs or none at all.

- Show the payback As per the cost benefit analysis, the benefits of adopting a new technology should outweigh the costs. The skeletal programs must outperform conventional implementations with equivalent investment of effort in developing them and they should be easily ported to new architectures with minimal changes to source and with sustained performance.

We have followed these guidelines in designing our wavefront framework. We provide minimal conceptual disruption by providing a C++ library with method and parameter declarations in wavefront terminology (explained in subsection 2.5.2). These can be overridden with custom defined data structures and kernel functions. The methods can also be plugged into existing code, allowing ad-hoc parallelism. We accommodate diversity by providing support for 2D and 3D wavefronts, along with choice of dependent elements up to two preceding diagonals. The payback is demonstrated from the performance gains of employing our autotuning framework.

With this brief discussion of the guiding principles behind designing and implementing skeletons, we now look at the limitation of skeletons regarding performance portability.

#### 2.3.3 Tuning of Skeletons

Skeletons solve the challenge of problem decomposition and distribution but they don't readily address the issue of performance portability when moving from one architecture to another. This can be illustrated by the task parallel Task Farm. In a task farm, there are several opportunities for optimizations that include

- Choosing the correct number of tasks to transfer in a single farmer-worker interaction, i.e. chunks of tasks being communicated.

- Selecting the correct number of workers to prevent bottleneck at either the farmer or worker's end, depending on the size of task.

- Adjusting the size of the data that is being communicated for each task to minimize communication overhead.

- Choosing between single and multiple distributed farmers.

All these parameters may have some impact upon the overall performance by reducing the effect of bottlenecks. They have different optimal settings for different combinations of architecture and the farmed application. These combinations of various input features can, and do produce an enormous number of possibilities.

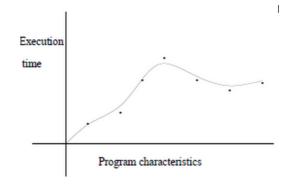

One approach to exploring this space efficiently is to apply machine learning [74] which is introduced in next section.

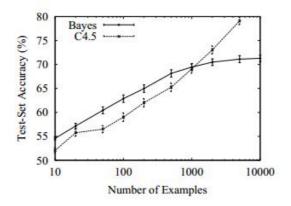

## 2.4 Machine Learning

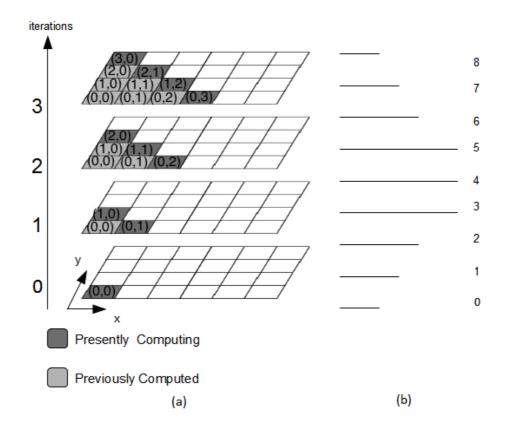

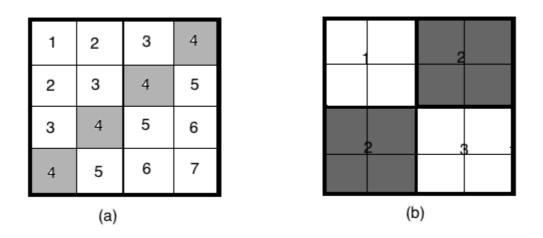

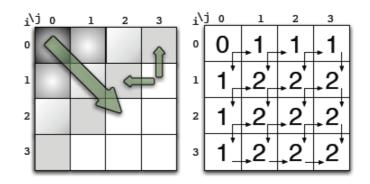

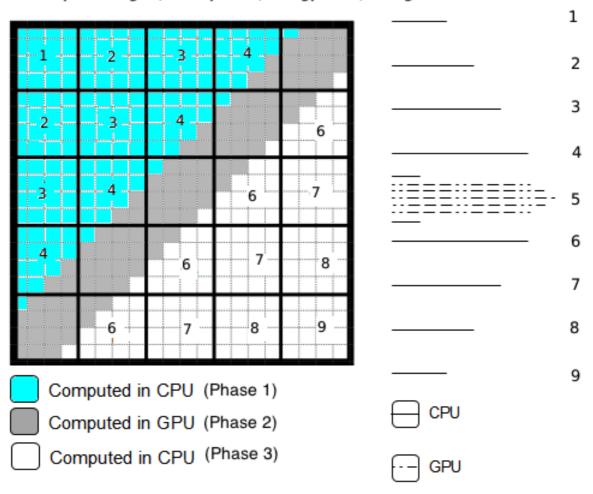

Machine Learning refers to the field of study in computer science and statistics of algorithms that improve from experience without any explicit programming instructions. A formal definition of machine learning in operational terms is provided by Tom Mitchell [74] as "A computer program is said to learn from experience E with respect to some class of tasks T and performance measure P, if its performance at tasks in T, as measured by P, improves with experience E." Based on this definition we can say the purpose of a machine learning algorithm is to improve performance on new unseen tasks after experiencing tasks from a training data set. This training data set consist of values of input features or attributes that define a problem and is representative of the space of occurrences of those problem instances. The learning model trained on this data has to be then general enough to predict desired output values for unseen problem instances with high accuracy.