# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Optimizing Cache Utilization in Modern Cache Hierarchies

Cheng-Chieh Huang

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2015

### Abstract

*Memory wall* is one of the major performance bottlenecks in modern computer systems. SRAM caches have been used to successfully bridge the performance gap between the processor and the memory. However, SRAM cache's latency is inversely proportional to its size. Therefore, simply increasing the size of caches could result in negative impact on performance. To solve this problem, modern processors employ multiple levels of caches, each of a different size, forming the so called memory hierarchy. Upon a miss, the processor will start to lookup the data from the highest level (L1 cache) to the lowest level (main memory). Such a design can effectively reduce the negative performance impact of simply using a large cache. However, because SRAM has lower storage density compared to other volatile storage, the size of an SRAM cache is restricted by the available on-chip area. With modern applications requiring more and more memory, researchers are continuing to look at techniques for increasing the effective cache capacity. In general, researchers are approaching this problem from two angles: maximizing the utilization of current SRAM caches or exploiting new technology to support larger capacity in cache hierarchies.

The first part of this thesis focuses on how to maximize the utilization of existing SRAM cache. In our first work, we observe that not all words belonging to a cache block are accessed around the same time. In fact, a subset of words are consistently accessed sooner than others. We call this subset of words as *critical words*. In our study, we found these critical words can be predicted by using access footprint. Based on this observation, we propose *critical-words-only cache (co cache)*. Unlike the conventional cache which stores all words that belongs to a block, co-cache only stores the words that we predict as critical. In this work, we convert an L2 cache to a co-cache and use L1s access footprint information to predict critical words. Our experiments show the co-cache can outperform a conventional L2 cache in the workloads whose working-set-sizes fit in the conventional L2, we propose the adaptive co-cache (aco-cache) which allows the co-cache to be configured back to the conventional cache.

The second part of this thesis focuses on how to efficiently enable a large capacity on-chip cache. In the near future, 3D stacking technology will allow us to stack one or multiple DRAM chip(s) onto the processor. The total size of these chips is expected to be on the order of hundreds of megabytes or even few gigabytes. Recent works have proposed to use this space as an on-chip DRAM cache. However, the tags of the DRAM cache have created a classic space/time trade-off issue. On the one hand, we would like the latency of a tag access to be small as it would contribute to both hit and miss latencies. Accordingly, we would like to store these tags in a faster media such as SRAM. However, with hundreds of megabytes of die-stacked DRAM cache, the space overhead of the tags would be huge. For example, it would cost around 12 MB of SRAM space to store all the tags of a 256MB DRAM cache (if we used conventional 64B blocks). Clearly this is too large, considering that some of the current chip multiprocessors have an L3 that is smaller. Prior works have proposed to store these tags along with the data in the stacked DRAM array (tags-in-DRAM). However, this scheme increases the access latency of the DRAM cache. To optimize access latency in the DRAM cache, we propose aggressive tag cache (ATCache). Similar to a conventional cache, the ATCache caches recently accessed tags to exploit temporal locality; it exploits spatial locality by prefetching tags from nearby cache sets. In addition, we also address the high miss latency issue and cache pollution caused by excessive prefetching. To reduce this overhead, we propose a cost-effective prefetching, which is a combination of dynamic prefetching granularity tunning and hit-prefetching, to throttle the number of sets prefetched. Our proposed ATCache (which consumes 0.4% of overall tag size) can satisfy over 60% of DRAM cache tag accesses on average.

The last proposed work in this thesis is a *DRAM-Cache-Aware (DCA) DRAM controller*. In this work, we first address the challenge of scheduling requests in the DRAM cache. While many recent DRAM works have built their techniques based on a tagsin-DRAM scheme, storing these tags in the DRAM array, however, increases the complexity of a DRAM cache request. In contrast to a conventional request to DRAM main memory, a request to the DRAM cache will now translate into multiple DRAM cache accesses (tag and data). In this work, we address challenges of how to schedule these DRAM cache accesses. We start by exploring whether or not a conventional DRAM controller will work well in this scenario. We introduce two potential designs and study their limitations. From this study, we derive a set of design principles that an ideal DRAM controller that is based on these design principles. Our experimental results show that DCA can outperform the baseline over 14%.

### Lay Summary

Memory is an essential component of today's computing systems. Computer programs use memory to store the input, output, and also the intermediate values during computation. However, because the speed of today's main memory is significantly slower than the processor speed, modern processors use hardware caches to bridge the performance gap between processor and main memory. Typically, caches are made using SRAM, which is a fast but a low density technology. The low-density of SRAM limits the size of caches due to the limited available chip area. Meanwhile, modern applications such as big data analytics or high-performance computing workloads require more and more memory to complete their tasks. Because the conventional cache cannot scale as the growing memory requirement in these applications, memory becomes the bottleneck in developing a high performance/efficient computing system. Therefore, how to increase cache capacity for applications with larger memory requirement is an important task for developing next-generation computers. In this thesis, we propose techniques to mitigate capacity issue in memory systems. In the first part of the thesis, we try to improve the (SRAM) cache utilization in current memory systems. In the second part of this thesis, we study on how to efficiently enable a larger (DRAM) cache by exploiting emerging die-stacking technology.

### Acknowledgements

I would like to thank my supervisor Vijay Nagarajan for all the help and guidance that he has provided. Coming from an industry background, without a postgraduate degree, I had no idea how to do research at the beginning of my PhD. Vijay helped me build up all the essential skills for doing research work.

I would also like to thank everybody at Institute of Computing Systems Architecture (ICSA) for their support and help. I am thankful to my second supervisor Nigel Topham for reviewing my works in the annual review panel. I would also like to thank Michael O'Boyle for giving me opportunity of being an organizing member in PLDI 2014. Many thanks to my fellow students, Jose Cano, Marco Elver, Priyank Faldu, Arpit Joshi, Rakesh Kumar, Thibaut Lutz, Alberto Magni, Andrew McPherson, Bharghava Rajaram, Erik Tomusk, and Yuan Wen. As an non-native English speaker, they have provided a great support in both improving my writing and research skills.

Finally, and most importantly, I would like to thank my parents for their absolutely unconditional support.

### Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following paper:

- C. Huang and V. Nagarajan, "Increasing Cache Capacity via Critical-words-Only Cache", The 32nd IEEE International Conference on Computer Design (ICCD), Seoul, Korea, October 2014 [1].

- C. Huang and V. Nagarajan, "ATCache: Reducing DRAM Cache Latency via a Small SRAM Tag Cache", The 23rd International Conference on Parallel Architectures and Compilation Techniques (PACT), Edmonton, Canada, August 2014 [2].

(Cheng-Chieh Huang)

## **Table of Contents**

| Ι  | Pre  | eamble  | <del>,</del>                          | 1  |

|----|------|---------|---------------------------------------|----|

| 1  | Intr | oductio | n                                     | 3  |

|    | 1.1  | Overv   | iew                                   | 3  |

|    | 1.2  | Contri  | butions                               | 5  |

|    |      | 1.2.1   | Critical-words-Only Cache             | 5  |

|    |      | 1.2.2   | Aggressive Tag Caching for DRAM cache | 5  |

|    |      | 1.2.3   | DRAM-Cache-Aware DRAM Controller      | 6  |

|    | 1.3  | Thesis  | Structure                             | 6  |

| 2  | Bac  | kgroun  | d                                     | 9  |

|    | 2.1  | Memo    | ory Hierarchy Overview                | 9  |

|    | 2.2  | Cache   | Overview                              | 10 |

|    |      | 2.2.1   | Organization                          | 10 |

|    |      | 2.2.2   | Cache Optimizations                   | 12 |

|    | 2.3  | Dynan   | nic Random Access Memory (DRAM)       | 13 |

|    |      | 2.3.1   | Introduction                          | 13 |

|    |      | 2.3.2   | Terminologies                         | 14 |

|    |      | 2.3.3   | DRAM Accesses                         | 16 |

|    |      | 2.3.4   | Bus Turnaround                        | 18 |

|    | 2.4  | DRAN    | M Cache                               | 19 |

| II | SI   | RAM (   | Cache Optimization                    | 23 |

| 3  | Crit | ical-wo | rds-Only Cache                        | 25 |

|    | 3.1  | Introd  | uction                                | 25 |

|    | 3.2  | Study   | and motivation                        | 29 |

|    |      | 3.2.1   | Critical Words vs Non-critical Words  | 30 |

|   |     | 3.2.2     | Critical Words Predictability                 | 31  |

|---|-----|-----------|-----------------------------------------------|-----|

|   |     | 3.2.3     | Useful Words vs Critical Words                | 33  |

|   | 3.3 | Metho     | dology and Design                             | 33  |

|   |     | 3.3.1     | Critical Words Predictor                      | 35  |

|   |     | 3.3.2     | Co-cache Structure and Implementation         | 36  |

|   |     | 3.3.3     | Adaptive Co-cache                             | 38  |

|   |     | 3.3.4     | Space Overhead                                | 39  |

|   | 3.4 | Evalua    | tion Methodology                              | 41  |

|   |     | 3.4.1     | Co-cache's access latency                     | 42  |

|   | 3.5 | Result    | s                                             | 43  |

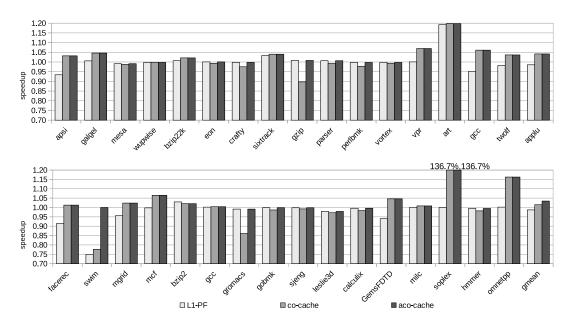

|   |     | 3.5.1     | Performance Evaluation                        | 43  |

|   |     | 3.5.2     | Adaptive Co-cache                             | 44  |

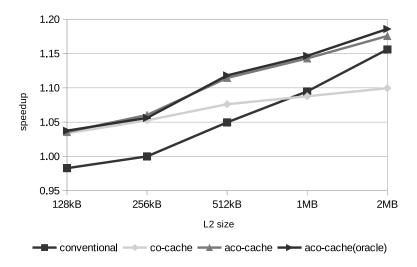

|   |     | 3.5.3     | Sensitivity to L2 Size                        | 45  |

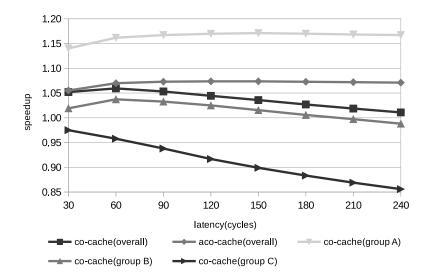

|   |     | 3.5.4     | Sensitivity to Lower Level Latency            | 46  |

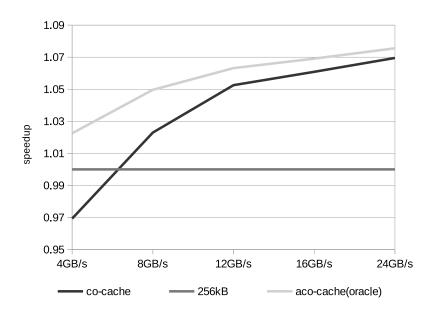

|   |     | 3.5.5     | Sensitivity to Bandwidth                      | 47  |

|   |     | 3.5.6     | Prefetcher Effects                            | 48  |

|   |     | 3.5.7     | Energy Impact                                 | 49  |

|   |     | 3.5.8     | Comparison with Oracle Useful Words Technique | 51  |

|   |     | 3.5.9     | Multi-core Workloads                          | 52  |

|   | 3.6 | Relate    | d Work                                        | 53  |

|   | 3.7 | Conclu    | usion                                         | 54  |

|   |     |           |                                               |     |

| Π | п   | RAM       | Cache Optimization                            | 57  |

|   |     |           |                                               | C I |

| 4 | Agg | ressive ' | Tag Caching for DRAM Cache                    | 59  |

|   | 4.1 | Introdu   | uction                                        | 59  |

|   | 4.2 | Motiva    | ation                                         | 62  |

|   | 4.3 | Metho     | dology and Design                             | 63  |

|   |     | 4.3.1     | Terminology                                   | 63  |

|   |     | 4.3.2     | Locality of tag accesses                      | 64  |

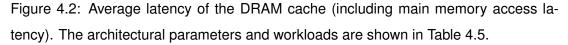

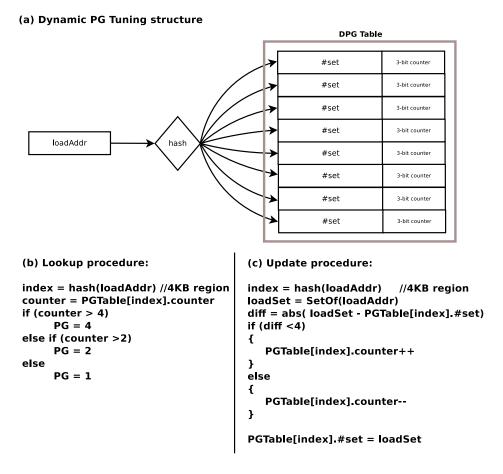

|   |     | 4.3.3     | Cost-effective Prefetching                    | 64  |

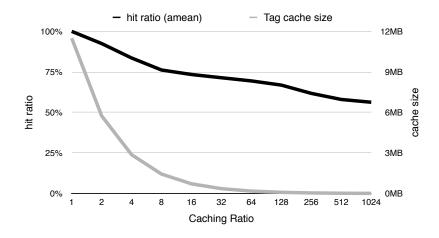

|   |     | 4.3.4     | Size, hit ratio and latency                   | 67  |

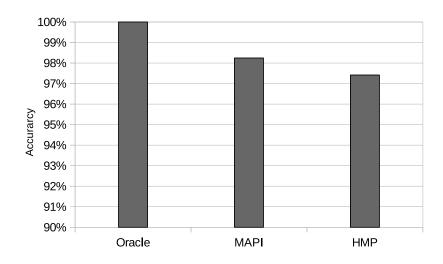

|   |     | 4.3.5     | Integration with miss predictor               | 68  |

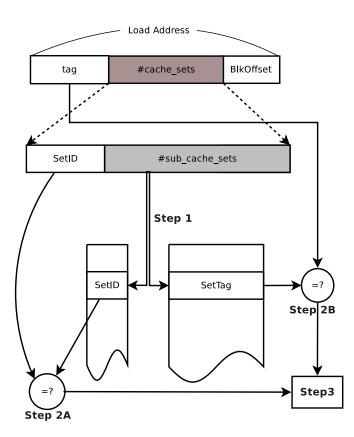

|   |     | 4.3.6     | Design of ATCache                             | 68  |

|   |     | 4.3.7     | Putting it all together                       | 70  |

|   |     | 4.3.8   | Area overhead                       | 71  |

|---|-----|---------|-------------------------------------|-----|

|   | 4.4 | Experi  | mental Methodology                  | 72  |

|   |     | 4.4.1   | Baseline system                     | 72  |

|   |     | 4.4.2   | DRAM cache organizations            | 72  |

|   | 4.5 | Results | s                                   | 74  |

|   |     | 4.5.1   | Performance                         | 74  |

|   |     | 4.5.2   | L2 miss latency                     | 77  |

|   |     | 4.5.3   | Sensitivity towards caching ratio   | 77  |

|   |     | 4.5.4   | Sensitivity towards DRAM cache size | 78  |

|   |     | 4.5.5   | Sensitivity towards PG              | 80  |

|   |     | 4.5.6   | Effect of Dynamic PG tuning         | 80  |

|   |     | 4.5.7   | Multiprogrammed workloads           | 80  |

|   | 4.6 | Related | d Work                              | 82  |

|   | 4.7 | Conclu  | usion                               | 83  |

| 5 | DRA | M-cacl  | he-aware DRAM controller            | 85  |

|   | 5.1 | Introdu | uction                              | 85  |

|   | 5.2 | Motiva  | ntion                               | 88  |

|   |     | 5.2.1   | Basics of DRAM Controller Design    | 88  |

|   |     | 5.2.2   | Accesses in DRAM Cache              | 89  |

|   |     | 5.2.3   | Potential Designs                   | 90  |

|   |     | 5.2.4   | Read-Write Interference             | 94  |

|   | 5.3 | DRAM    | 1-Cache-Aware Controller            | 95  |

|   |     | 5.3.1   | Design Principles                   | 95  |

|   |     | 5.3.2   | Low Priority Read Queue (LPRQ)      | 96  |

|   |     | 5.3.3   | LPRQ Servicing Scheme               | 97  |

|   |     | 5.3.4   | An example                          | 98  |

|   | 5.4 | Experi  | mental Methodology                  | 99  |

|   | 5.5 | Results | s                                   | 100 |

|   |     | 5.5.1   | Performance                         | 101 |

|   |     | 5.5.2   | Turnarounds                         | 102 |

|   |     | 5.5.3   | Associativity                       | 103 |

|   |     | 5.5.4   | Workload Analysis                   | 104 |

|   |     | 5.5.5   | 8-core Workloads                    | 105 |

|   |     | 5.5.6   | Summary                             | 106 |

|   |     |         |                                     |     |

| Bi | bliogr | raphy                                 | 113 |

|----|--------|---------------------------------------|-----|

|    | 6.2    | Future Work                           | 110 |

|    | 6.1    | Summary of Contributions              | 109 |

| 6  | Sum    | mary of Contributions and Future Work | 109 |

|    | 5.7    | Conclusion                            | 107 |

|    | 5.6    | Related Work                          | 106 |

# **List of Figures**

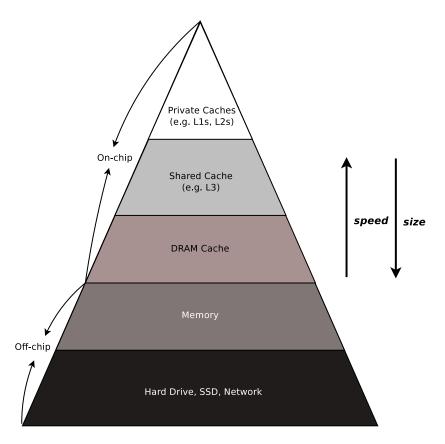

| 2.1  | Memory Hierarchy                                                                   | 9  |

|------|------------------------------------------------------------------------------------|----|

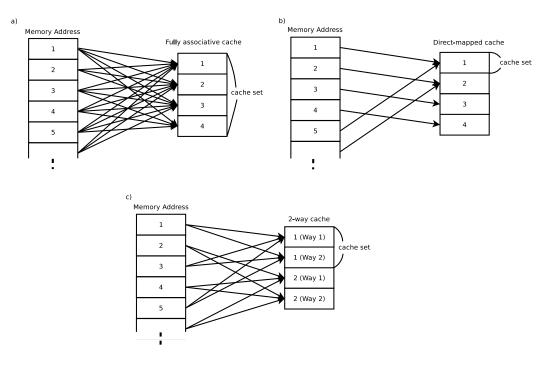

| 2.2  | Memory Mapping in Different Cache Structure                                        | 11 |

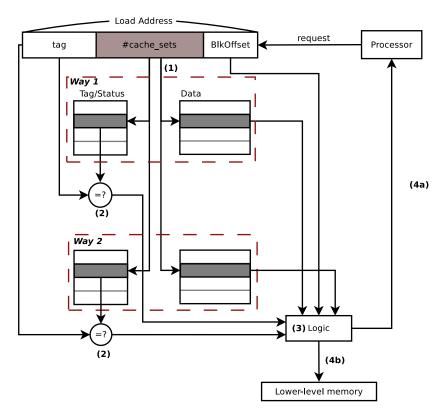

| 2.3  | Cache Organization                                                                 | 12 |

| 2.4  | A dual in-line memory module                                                       | 13 |

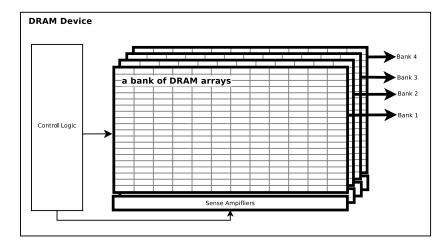

| 2.5  | A DRAM Device in memory system                                                     | 14 |

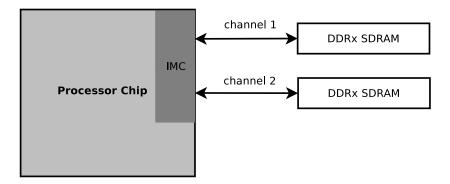

| 2.6  | A DRAM memory system with two channels. (IMC: Integrated Mem-                      |    |

|      | ory Controller.)                                                                   | 15 |

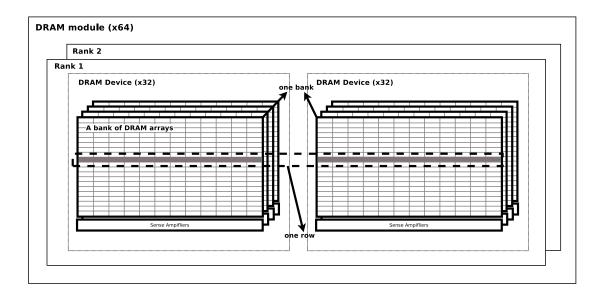

| 2.7  | The diagram of a x64 DRAM module (with 2 x32 DRAM devices)                         | 15 |

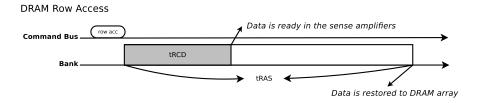

| 2.8  | A row access in DRAM                                                               | 16 |

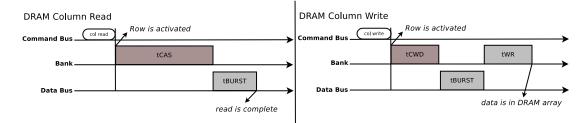

| 2.9  | Column Read/Write in DRAM                                                          | 17 |

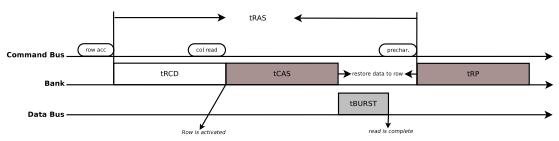

| 2.10 | A complete read access in DRAM                                                     | 18 |

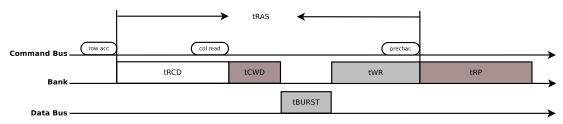

| 2.11 | A complete write access in DRAM                                                    | 18 |

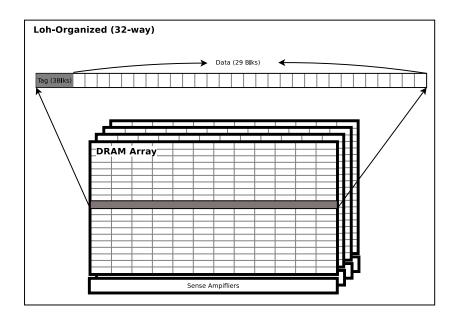

| 2.12 | Block-based DRAM cache in Loh and Hill's work [3]                                  | 20 |

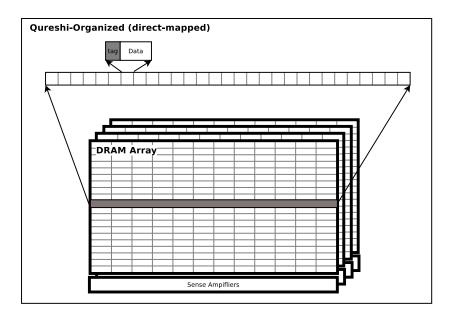

| 2.13 | Block-based DRAM cache in Qureshi and Loh's work [4]                               | 20 |

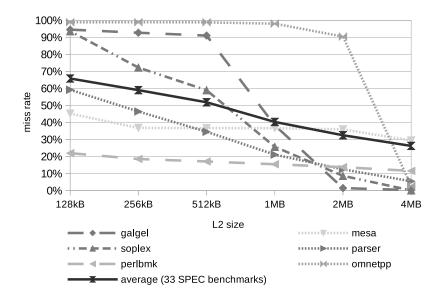

| 3.1  | Miss rate versus L2 cache size: as the size of the L2 cache (8-way) is             |    |

|      | increased from 128 KB through 4 MB, the local miss-rate significantly              |    |

|      | decreases. For this experiment 32 KB (4-way) L1 cache was used                     | 26 |

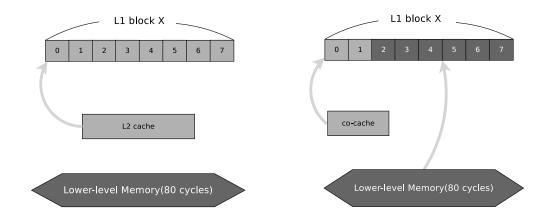

| 3.2  | (left) L1 + conventional L2: (1) $X[0]$ causes a miss in L1 (2) the block          |    |

|      | is fetched from L2 (3) $X[0], X[1]X[7]$ hit in L1. ( <b>right</b> ) L1 + L2 as co- |    |

|      | cache of depth 2: (1) $X[0]$ causes an L1 miss, accessed in both co-cache          |    |

|      | and lower-level (2) The first 2 critical words are fetched from co-cache           |    |

|      | (3) $X[0]$ and $X[1]$ is accessed from L1 (4) The memory returns the full          |    |

|      | block into L1 in time for second iteration of for loop(5) $X[2] \dots X[7]$        |    |

|      | hit in L1                                                                          | 28 |

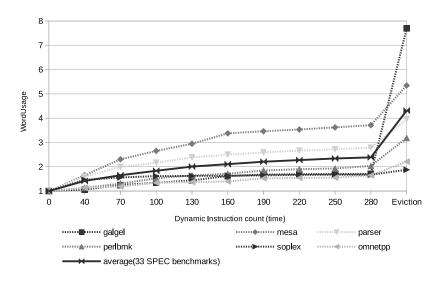

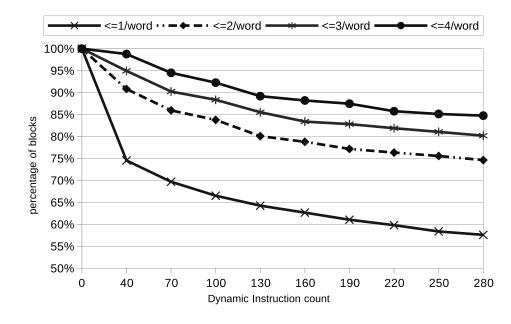

| 3.3  | The word usage in different time intervals (dynamic instruction count);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the time at which the first word is accessed is taken to be 0. Eviction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | in the graph refers to the time in which the block is replaced from L1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30 |

| 3.4  | The percentage of blocks that has accessed less than or equal to N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | words with time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

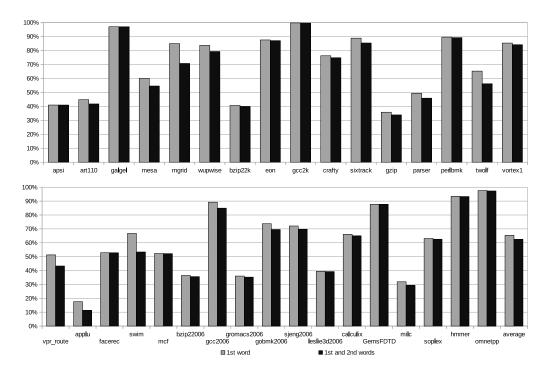

| 3.5  | Predictabilities of the first critical word, and both first and second com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | bined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32 |

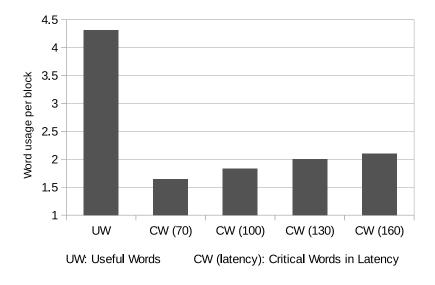

| 3.6  | Useful words filtering versus critical words filtering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

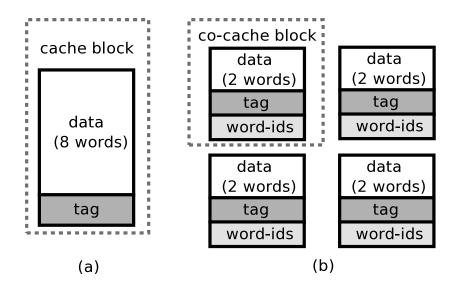

| 3.7  | (a) cache block in a conventional cache (b) 4 blocks in a co-cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

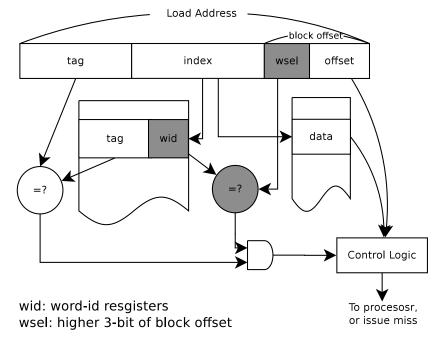

| 3.8  | Accessing a co-cache block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35 |

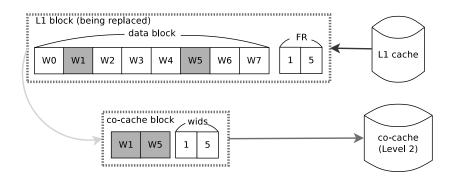

| 3.9  | Block placement – FR: Footprint registers (§ 3.3.1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35 |

| 3.10 | Performance Speedup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42 |

| 3.11 | Benchmark preference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

| 3.12 | Sensitivity to reconfiguration threshold $-0\%$ threshold means always                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|      | use co-cache; 100% means always use conventional cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45 |

| 3.13 | Sensitivity to cache size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

| 3.14 | Performance speedups with different latencies - Group A, B, C are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | defined in Table 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47 |

| 3.15 | Speedup versus Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48 |

| 3.16 | Performance speedups with a stride prefetcher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49 |

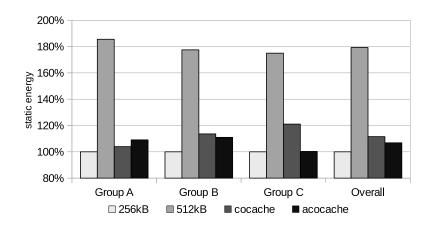

| 3.17 | Static energy comparison (without L3, the lower the better)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50 |

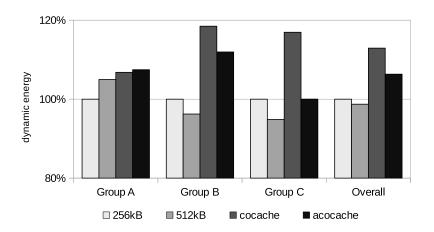

| 3.18 | Dynamic energy comparison (the lower the better)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |

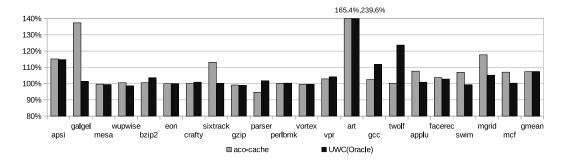

| 3.19 | Performance comparison with oracle useful words filtering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51 |

| 3.20 | Performance improvement in multiprogrammed workloads - Please                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

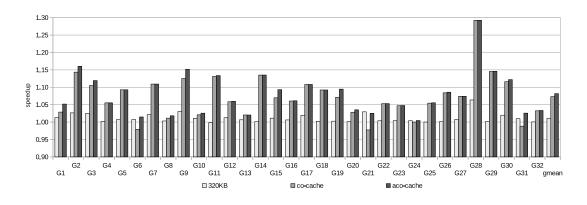

|      | refer to Table 3.3 and Table 3.5 for workloads' information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52 |

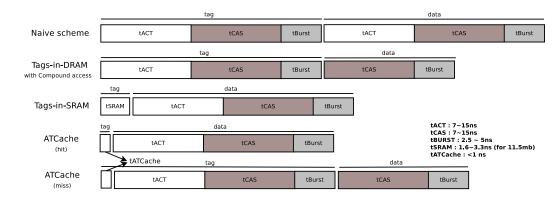

| 4.1  | Access latency of different types of DRAM cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

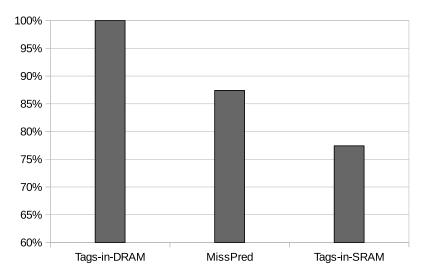

| 4.2  | Average latency of the DRAM cache (including main memory access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | latency). The architectural parameters and workloads are shown in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | Table 4.5.         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <th< td=""><td>60</td></th<> | 60 |

| 4.3  | Miss ratio with various PG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65 |

| 4.4  | Hardware structure of DPGTable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66 |

| 4.5  | Hit ratio, size for different caching ratios.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67 |

| 4.6  | Accuracy of prior proposed predictors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

| 4.7  | The access logic (also refer to Table 4.2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

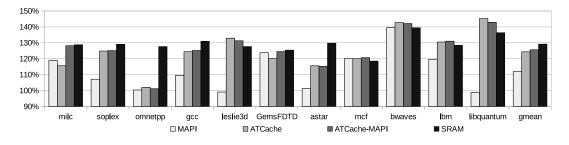

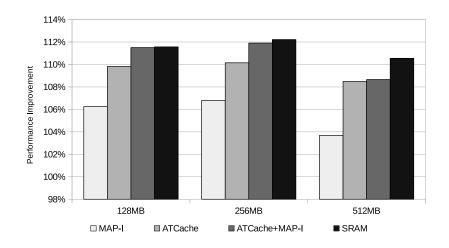

| 4.8  | Performance results.                                                        | 74       |

|------|-----------------------------------------------------------------------------|----------|

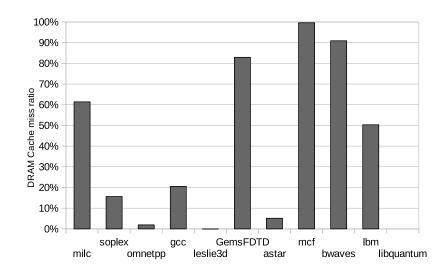

| 4.9  | L3 miss ratio.                                                              | 75       |

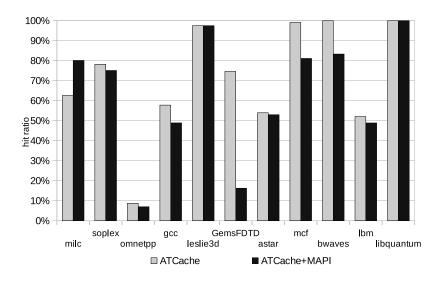

| 4.10 | ATCache hit ratio                                                           | 75       |

| 4.11 | L2 miss latency reduction (higher the better)                               | 77       |

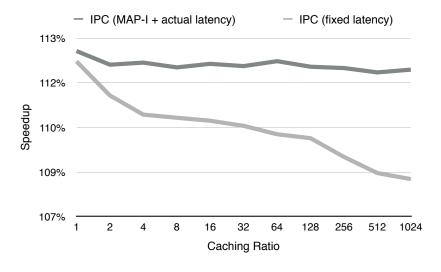

| 4.12 | Performance improvement for different caching ratios. <i>Caching Ratio:</i> |          |

|      | <i>1</i> means a <i>tags-in-SRAM</i> design                                 | 78       |

| 4.13 | Sensitivity study of DRAM cache sizes.                                      | 79       |

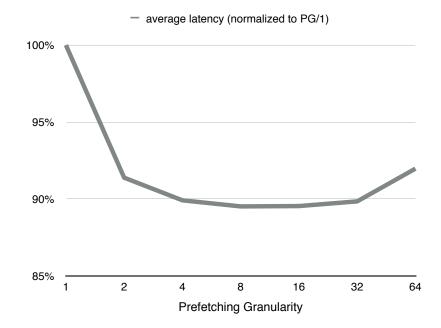

| 4.14 | Sensitivity study to PG (with MAP-I)                                        | 79       |

| 4.15 | Tag Accesses                                                                | 81       |

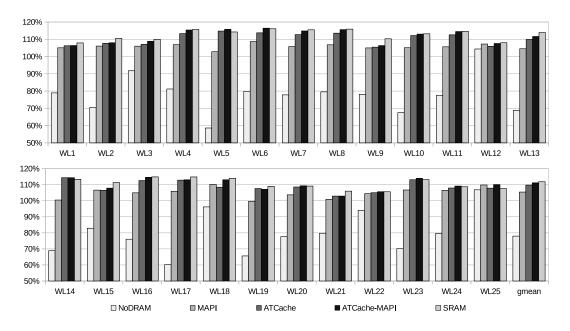

| 4.16 | Performance improvement in multiprogrammed workloads                        | 81       |

| 4.17 | L2 miss latency reduction in multiprogrammed workloads (higher the          |          |

|      | better)                                                                     | 82       |

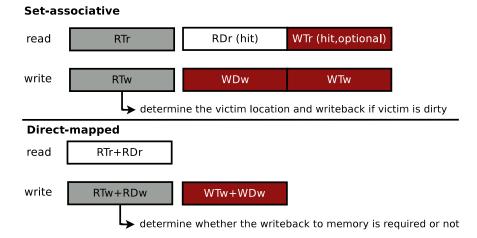

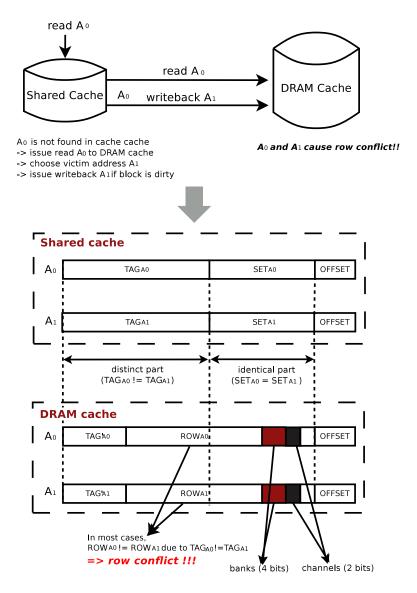

| 5.1  | Accesses in a cache read and a cache writeback                              | 90       |

|      |                                                                             | 90<br>91 |

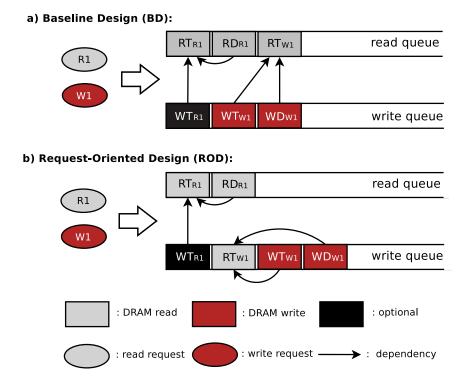

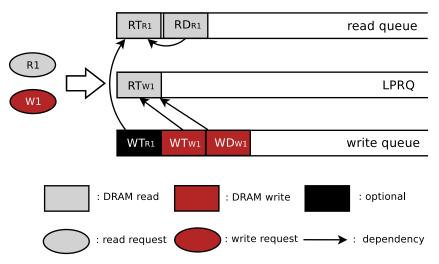

| 5.2  | How the translated accesses map to queues in BD and ROD                     | 91<br>92 |

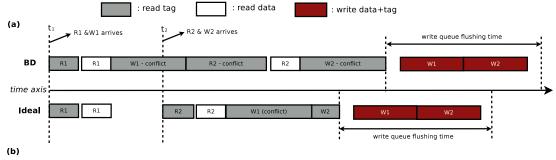

| 5.3  | A case study in baseline design (BD).                                       | 92       |

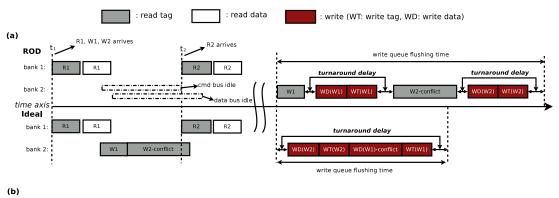

| 5.4  | A case study in Request-Oriented Design (ROD) — please note that            |          |

|      | bank 1 and bank 2 are in the same rank/channel and all queues are           | 02       |

| ~ ~  | using FR-FCFS policy.                                                       | 93       |

| 5.5  | Row conflict in DRAM cache due to shared cache replacement                  | 94       |

| 5.6  | How the translated accesses map to queues in DRAM-Cache-Aware               | 0.6      |

|      | design                                                                      | 96       |

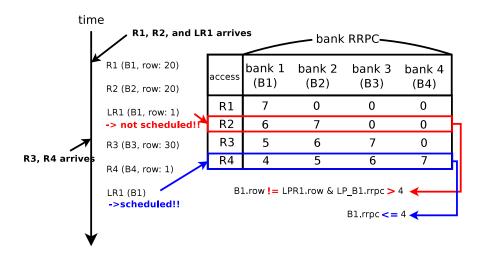

| 5.7  | Working case for Re-Reference Prediction Counter                            | 98       |

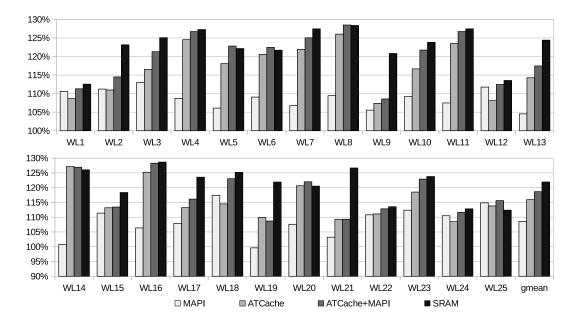

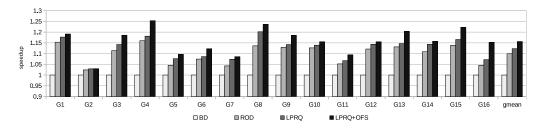

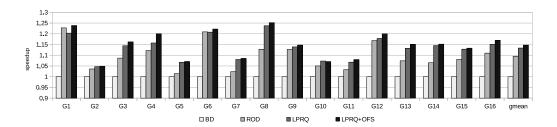

| 5.8  | Performance speedup of all designs (16-way)                                 | 101      |

| 5.9  | Performance speedup of all designs (direct-mapped)                          | 101      |

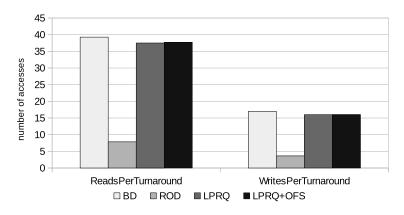

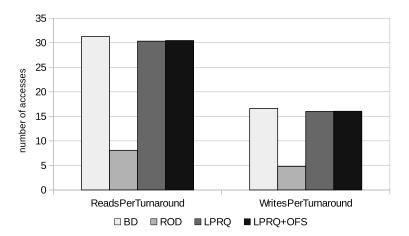

|      | Read/Write accesses per turnaround (the higher the better) $- 16$ -way .    | 102      |

| 5.11 | Read/Write accesses per turnaround (the higher the better) – direct-        |          |

|      | mapped                                                                      | 102      |

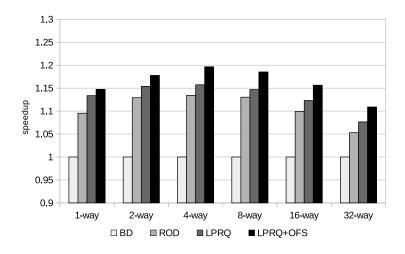

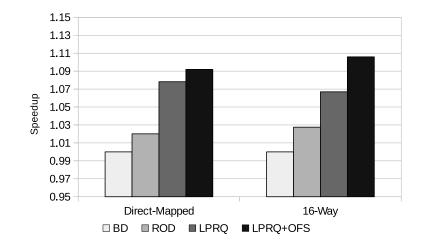

|      | Average speedup in different associativity                                  | 103      |

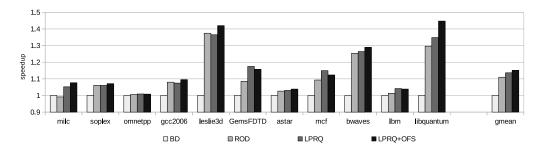

|      | Performance speedup in single workload                                      | 104      |

| 5.14 | Performance speedup in 8-core workload                                      | 105      |

## **List of Tables**

| 2.1 | DRAM Timing Parameters                                                   | 16  |

|-----|--------------------------------------------------------------------------|-----|

| 3.1 | Accessing the co-cache                                                   | 37  |

| 3.2 | Area Overhead                                                            | 39  |

| 3.3 | Architectural Parameters                                                 | 40  |

| 3.4 | L2 miss-rates in different workloads                                     | 41  |

| 3.5 | Workload groupings                                                       | 52  |

| 4.1 | Tag sizes/latencies for different cache sizes.                           | 63  |

| 4.2 | ATCache access procedure (refer to Figure 4.7)                           | 69  |

| 4.3 | Example showing 5 DRAM cache accesses                                    | 70  |

| 4.4 | Overhead for different cache sizes                                       | 71  |

| 4.5 | System parameters                                                        | 73  |

| 4.6 | Workload groupings                                                       | 73  |

| 4.7 | Latency in different caching ratios - caching ratio of 1 equals tags-in- |     |

|     | SRAM (6 cycles)                                                          | 77  |

| 5.1 | System parameters                                                        | 99  |

| 5.2 | Stacked DRAM parameters                                                  | 99  |

| 5.3 | Workload groupings                                                       | 100 |

| 5.4 | 8-core workload groupings                                                | 105 |

| 5.5 | Techniques comparisons                                                   | 106 |

# Part I

# Preamble

## **Chapter 1**

## Introduction

### 1.1 Overview

In modern computer systems, memory has become an overwhelming bottleneck in system performance due to the disparity of speed between the processor and the off-chip memory, otherwise called the *memory wall*. To bridge the performance gap between processor and off-chip memory, modern processors use hardware caches to avoid the penalty of accessing off-chip memory. A hardware cache is a small memory buffer that is usually made of static random access memory (SRAM) and placed on the processor chip. While the access latency of off-chip main memory is around 10 to 100 nanoseconds, the on-chip cache allows the access latency to be in the order of few nanoseconds or less. However, this latency is inversely proportional to its size. Larger SRAM size will result in slower access latency. Therefore, modern processors use multiple levels of caches (each of a different size) in its memory system. Upon a miss, the processor will start to look up the data from the highest level (L1 cache) to the lowest level (main memory). This is known as memory hierarchy.

In addition to multiple levels of caches, most modern processors, ranging from mobile phones to supercomputers, have multiple processing units (cores) in a single physical package, known as the chip multiprocessor (CMP). A CMP chip will typically have multiple small caches for each core (private caches) and a large cache shared among all cores (shared cache). In a typical CMP memory hierarchy, the L1 is usually small and private to match the speed of the processor core. On the other hand, lower level caches such as L2 or L3 are are relatively larger and slower access latency compared to the L1. Furthermore, to enhance the performance of multi-thread programs, the last level cache is usually shared among all cores. Computer programs nowadays require more memory to complete their jobs due to various reasons. For example, huge data sets in big data applications increase the memory footprint in modern computers. On the other hand, total cache size in today's processor chips is restricted by various reasons including the price, power budget, latency, or available die area. For example, we can see an Intel Nehalem processor from 2007 has similar cache settings as Intel Haswell processor from 2013 [5]. With cache sizes not able to match the growing memory requirement in these modern workloads, caches will suffer from excessive cache misses (called *capacity misses*) and lose the purpose of bridging the latency gap between the processor and the off-chip memory. Given that memory is one of the major performance bottlenecks in computer systems, how to maximize cache efficiency is a major challenge for computer scientists and therefore draws a significant amount of research works from the computer architecture community.

In this dissertation, we study how to support higher cache capacity in the CMP processor. In modern processors, most on-chip caches use SRAM as storage. However, SRAM's low packing density limit the available on-chip storage. Therefore, how to use existing SRAM space effectively becomes a fundamental problem for developing a high performance/efficiency processor.

On the other hand, many computer programs in HPC [6] or servers [7] today have working-set-sizes that are over hundreds of megabytes. Clearly, the conventional SRAM cache will not be able to provide enough capacity for such workloads. Recently, 3D-stacking technology has enabled the option of embedding hundreds of megabyte or even few gigabytes DRAM chips onto the processor. Prior studies have proposed using this stacked DRAM as an L4 DRAM cache [8]. Given the huge size, many design questions, such as how to organize data and tag in the DRAM array [3, 4] arise in DRAM cache. Therefore, how to efficiently enable this DRAM cache is another important research problem.

To summarize, we focus on two architectural questions in this dissertation:

- How to effectively use existing SRAM space in memory hierarchy?

- How to effectively enable a large DRAM cache?

### 1.2 Contributions

#### 1.2.1 Critical-words-Only Cache

In the first work, we target the first architectural question that we arise in introduction — *how to effectively use existing SRAM space in memory hierarchy?* Today, most processors have multiple levels of caches. In multi-level cache hierarchies, choosing the right cache size for each level is critical for performance. As we mentioned in the previous section, the first-level cache (L1) is typically small, in order to match the speed of the processor. The lower level caches, on the other hand, are typically large, in order to reduce capacity misses. Ideally, the lower level cache should be large enough to fit workloads' working-set-sizes, but situations may arise in which the size of the cache is lesser than the working-set-sizes of the workload. In that case, this cache could adversely affect the overall system performance.

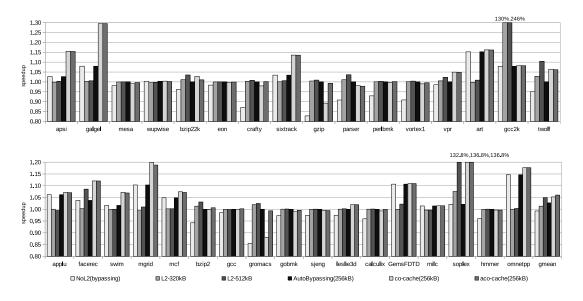

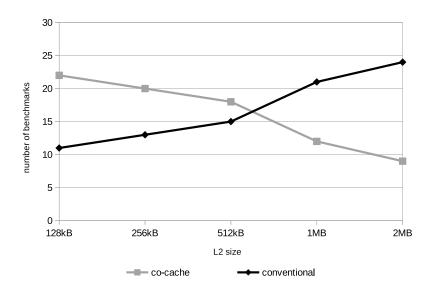

The first work of this thesis proposes a cache design called emphcritical-wordsonly cache (co-cache) for increasing the effective cache capacity. Our approach involves rethinking the notion of cache blocks; instead of storing all the words that belong to a cache block, we only store the critical words, where the critical words are the words that are generally accessed before the others. Our experiments show that with our design a 256 KB L2 performs as well as a 512 KB conventional L2 cache on average.

#### 1.2.2 Aggressive Tag Caching for DRAM cache

As 3D-stacking technology has enabled the chance to support a very large size DRAM cache in the processor chip, *how to effectively enable this DRAM cache* is a major challenge in research works. Because of its large size (a DRAM cache can be on the order of hundreds of megabytes), the total size of the tags associated with it can also be quite large (on the order of tens of megabytes). The large size of the tags has created a problem [3]. Should we maintain the tags in the DRAM and pay the cost of a costly tag access in the critical path? Or should we maintain the tags in the faster SRAM by paying the area cost of a large SRAM for this purpose? Prior works have primarily chosen the former and proposed a variety of techniques for reducing the cost of a DRAM tag access. In this work, we first establish (with the help of a study) that maintaining the tags in SRAM, because of its smaller access latency, leads to overall better performance. Motivated by this study, we ask if it is possible to maintain tags in SRAM

without incurring high area overhead. Our key idea is simple. We propose to cache the tags in a small SRAM tag cache; we show that there is enough spatial and temporal locality amongst tag accesses to merit this idea. We propose the aggressive tag cache (ATCache) which is a small SRAM tag cache. Similar to a conventional cache, the ATCache caches recently accessed tags to exploit temporal locality; it exploits spatial locality by prefetching tags from nearby cache sets. In addition, we also address the high miss latency issue and cache pollution caused by excessive prefetching. To reduce this overhead, we propose a cost-effective prefetching, which is a combination of dynamic prefetching granularity tunning and hit-prefetching, to throttle the number of sets prefetched. Our proposed ATCache (which consumes 0.4% of overall tag area) can satisfy over 60% of DRAM cache tag accesses on average.

#### 1.2.3 DRAM-Cache-Aware DRAM Controller

We also observed many recent DRAM works [3, 4, 9, 10, 11] have built their technique based on a tags-in-DRAM scheme, which means cache tags are stored in the DRAM array itself. Storing these tags in the DRAM array, however, increases the complexity of a DRAM cache request. In contrast to a conventional request to DRAM main memory, a request to the DRAM cache will now translate into multiple DRAM cache accesses (tag and data). In this work, we address challenges of how to schedule these DRAM cache accesses. We start by exploring whether or not a conventional DRAM controller will work well in this scenario. We introduce two potential designs and study their limitations. From this study, we derive a set of design principles that an ideal DRAM controller must satisfy. We then propose a DRAM-cache-aware (DCA) DRAM controller that is based on these design principles. Our experimental results show that DCA can outperform the baseline over 14%.

### 1.3 Thesis Structure

Chapter 2 provides background on memory systems. In this chapter, we first explain the conventional memory hierarchy and the basic structure of a hardware-managed cache. We then show the DRAM terminologies and access protocols which will be used in our DRAM cache works. In the rest of this chapter, we summarize the current state-of-the-art in the DRAM cache. Chapter 2, 3, and 4 are the main contributions of this thesis. **Critical-words-Only Cache** (co-cache, chapter 2) provides an opportunity to increase effective cache capacity when workloads' working-set-sizes are not fitted in the cache size. We describe the problem and evaluation our idea in this chapter. **Aggressive Tag Cache** (ATCache, chapter 3) is used to enhance the access latency of a DRAM cache with the tags-in-DRAM design. ATCache uses a small SRAM cache to the buffer of DRAM cache's tags. Also, we study and use a cost-effective prefetching to avoid prefetching overhead. The last contribution of this thesis is the **DRAM-Cache-Aware** (**DCA**) **DRAM controller** (chapter 2). In this work, we address the problem of how to schedule a DRAM cache's request and propose a controller design that can enhance the scheduling efficiency in DRAM cache.

In chapter 5, we first summarize the key findings and results presented in this thesis. Finally, we describe several potential future works and/or possible further studies related to this thesis.

## **Chapter 2**

## Background

### 2.1 Memory Hierarchy Overview

Figure 2.1: Memory Hierarchy

*Memory wall* is one of major performance bottlenecks in modern computer systems, which is caused by the disparity of speed between the processor and the off-chip memory. To avoid the access of memory, *cache* is used to bridge this latency gap. A

cache is a small memory region that stores partial contents of the main memory. These caches are usually made of static random access memory (SRAM). SRAM provides an access latency that can match the speed of processors. However, as the SRAM speed (latency) is inversely proportional to its size, to match the processor speed, the cache needs to be on the order of tens of kilobytes [12].

To overcome this problem, modern processors use multiple layers of caches. The level 1 (L1) cache, which typically small (e.g. 32KB), can complete the access in a few processor cycles. Lower level caches (level 2 or level 3) are typically larger, ranging from hundreds of kilobytes to few megabytes. Although L2 and L3 caches are usually slower (about 10 to 40 processor cycles) than L1 caches, the larger capacity allows them to further reduce the number of accesses to the off-chip memory, which can incur a penalty of over 100 processor cycles. This multiple layer design is known as *memory hierarchy*.

One disadvantage of SRAM cache is its area cost. SRAM has lower area density compared to other storage media such as dynamic random access memory (DRAM). Because of this, the total size of all on-chip caches is usually under 30 MB. Therefore, to support higher cache capacity, many recent works [3, 13, 14, 15, 4, 9] have proposed using die-stacked DRAM as an L4 cache. This allows the cache size to be over hundreds of megabytes. Figure 2.1 shows an overview of the modern memory hierarchy.

### 2.2 Cache Overview

The *cache* mentioned in this paper is a transparent hardware-managed cache, which means they work independently and the software is not aware of their existence.<sup>1</sup>. In this section, we will show how a conventional cache is organized and some of their optimization techniques.

#### 2.2.1 Organization

Address Mapping and Set-associativity. In the cache, if a given address can be placed in any cache blocks, this is called *fully-associative cache* as shown in Figure 2.2 (a). However, even an L1 cache, which has the smallest size in the cache

<sup>&</sup>lt;sup>1</sup>On the other hand, a software-managed cache is a cache that requires the programmer/OS to decide when to evict the data and where to store the data.

Figure 2.2: Memory Mapping in Different Cache Structure

hierarchy, will have about 1000 of blocks (assumed a 64KB L1 cache, 64B per block). In other words, a single cache access will need to search the given address in about 1000 blocks. The access overhead in a fully-associative cache is huge in both energy and latency perspectives. An extreme solution to this problem is the direct-mapped design, in which a memory address can only be mapped to one cache block (as shown in Figure 2.2(b)). In this case, only one location (block) needs to be checked for a cache access. However, the direct-mapped design gives rise to rise another potential problem. Considering an access sequence that is repeatedly accessing two blocks (address 1 and 5) in Figure 2.2(b), although our cache has space to store 4 data blocks, the accesses will always miss in the direct-mapped cache. These are known as *conflicts misses*<sup>2</sup>. As a trade-off, most caches use a set-associative design. In this design, a memory address can be mapped to multiple blocks (ways) but not all cache blocks. An example of a two-way design is shown in Figure 2.2(c).

Accessing a set-associative cache. Figure 2.3 shows the flow of accessing a setassociative cache. When a processor sends a load request to the cache, the cache controller will use the part of the load address to locate tag/data (1) in the SRAM array. Later, the tag in the SRAM array will be checked (2) with the tag part of the load address. If the check of the tag results in a match, it is a cache hit and the data located

<sup>&</sup>lt;sup>2</sup>On the other hand, cache misses caused by insufficient cache blocks is called *capacity misses*