# Putting Checkpoints to Work in Thread Level Speculative Execution

Salman Khan

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2010

## Abstract

With the advent of Chip Multi Processors (CMPs), improving performance relies on the programmers/compilers to expose thread level parallelism to the underlying hardware. Unfortunately, this is a difficult and error-prone process for the programmers, while state of the art compiler techniques are unable to provide significant benefits for many classes of applications. An interesting alternative is offered by systems that support Thread Level Speculation (TLS), which relieve the programmer and compiler from checking for thread dependencies and instead use the hardware to enforce them.

Unfortunately, data misspeculation results in a high cost since all the intermediate results have to be discarded and threads have to roll back to the beginning of the speculative task. For this reason intermediate checkpointing of the state of the TLS threads has been proposed. When the violation does occur, we now have to roll back to a checkpoint before the violating instruction and not to the start of the task. However, previous work omits study of the microarchitectural details and implementation issues that are essential for effective checkpointing. Further, checkpoints have only been proposed and evaluated for a narrow class of benchmarks.

This thesis studies checkpoints on a state of the art TLS system running a variety of benchmarks. The mechanisms required for checkpointing and the costs associated are described. Hardware modifications required for making checkpointed execution efficient in time and power are proposed and evaluated. Further, the need for accurately identifying suitable points for placing checkpoints is established. Various techniques for identifying these points are analysed in terms of both effectiveness and viability. This includes an extensive evaluation of data dependence prediction techniques. The results show that checkpointing thread level speculative execution results in consistent power savings, and for many benchmarks leads to speedups as well.

## Acknowledgements

I'd like to thank my adviser, Marcelo Cintra, for providing the guidance I needed, but also for letting me find my own path.

I would also like to thank all my colleagues and friends at *ICSA*. I have learned a great deal from them and they have made my time at Edinburgh enjoyable as well as productive. In particular Polychronis Xekalakis and Nikolas Ioannou, who showed exemplary patience while sharing an office with me.

I am grateful to Alasdair for his support and patience throughout my PhD and especially during the preparation of this document. Finally, I'd like to thank my parents who have always encouraged me and have enabled me to get this far. Without them, none of this would be possible.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Salman Khan)

# **Table of Contents**

| Li | List of Figures xi |                              |                                             |    |

|----|--------------------|------------------------------|---------------------------------------------|----|

| Li | st of [            | <b>Fables</b>                |                                             | XV |

| 1  | Intr               | Introduction                 |                                             |    |

|    | 1.1                | Chip N                       | Aultiprocessors and Parallelisation         | 1  |

|    | 1.2                | Contri                       | butions                                     | 2  |

|    |                    | 1.2.1                        | Efficient Checkpointing                     | 2  |

|    |                    | 1.2.2                        | Dependence Prediction                       | 3  |

|    | 1.3                | Structu                      | ıre                                         | 3  |

| 2  | Bac                | kground                      | 1                                           | 5  |

|    | 2.1                | Thread                       | l Level Speculation                         | 5  |

|    |                    | 2.1.1                        | Speculation Mechanism                       | 7  |

|    |                    | 2.1.2                        | Compilation                                 | 10 |

|    | 2.2                | Reducing Wasted Re-execution |                                             | 11 |

|    |                    | 2.2.1                        | Synchronisation                             | 12 |

|    |                    | 2.2.2                        | Checkpointing                               | 13 |

|    |                    | 2.2.3                        | Value Prediction                            | 16 |

|    | 2.3                | Hardw                        | vare Support for Speculative Multithreading | 17 |

| 3  | Che                | ckpoint                      | ing Mechanism                               | 21 |

|    | 3.1                | Creatio                      | on of Checkpoints                           | 21 |

|    |                    | 3.1.1                        | Hardware Requirements                       | 23 |

|   | 3.2 | Efficie  | ent Checkpointing                         | 24 |

|---|-----|----------|-------------------------------------------|----|

|   |     | 3.2.1    | Selective Kills and Restarts              | 24 |

|   |     | 3.2.2    | Memory Optimisation                       | 30 |

| 4 | Che | ckpoint  | t Placement Policy                        | 33 |

|   | 4.1 | Identif  | fying Checkpoint Locations                | 33 |

|   |     | 4.1.1    | Static Checkpoints                        | 33 |

|   |     | 4.1.2    | Stride Checkpoints                        | 34 |

|   |     | 4.1.3    | Checkpointing By Predicting Dependences   | 34 |

|   | 4.2 | Dealin   | ng with Resource Constraints              | 39 |

|   | 4.3 | Check    | point Insertion Policy                    | 40 |

|   | 4.4 | Micro    | architectural Interactions                | 40 |

| 5 | Eva | luation  | Methodology                               | 43 |

|   | 5.1 | Evalua   | ation Metrics                             | 43 |

|   |     | 5.1.1    | Evaluating Dependence Predictors          | 43 |

|   |     | 5.1.2    | Evaluating Checkpointing Schemes          | 46 |

|   | 5.2 | Simula   | ator                                      | 48 |

|   | 5.3 | Bench    | marks                                     | 48 |

| 6 | Res | ults and | l Evaluation                              | 51 |

|   | 6.1 | Depen    | Idence Prediction                         | 51 |

|   |     | 6.1.1    | Address Based Prediction                  | 52 |

|   |     | 6.1.2    | Program Counter Based Prediction          | 55 |

|   |     | 6.1.3    | Hybrid Prediction                         | 60 |

|   |     | 6.1.4    | Comparison of Predictors                  | 64 |

|   | 6.2 | Check    | pointing Scheme                           | 69 |

|   | 6.3 | Sensit   | ivity to Architectural Extentions         | 75 |

|   |     | 6.3.1    | Memory System Modification                | 75 |

|   |     | 6.3.2    | Restart Mechanism                         | 76 |

|   | 6.4 | Using    | Dependence Prediction for Synchronisation | 77 |

| 7  | Related Work |                                             |    |  |

|----|--------------|---------------------------------------------|----|--|

|    | 7.1          | Thread Level Speculation                    | 81 |  |

|    | 7.2          | Checkpointing                               | 81 |  |

|    | 7.3          | Other Schemes for Reducing Wasted Execution | 82 |  |

|    | 7.4          | Data Dependence Prediction                  | 82 |  |

| 8  | Con          | clusions and Future Work                    | 85 |  |

|    | 8.1          | Summary of Contributions                    | 85 |  |

|    | 8.2          | Future Work                                 | 86 |  |

| Bi | Bibliography |                                             |    |  |

# **List of Figures**

| 2.1 | Example of Thread Level Speculation and checkpointing                                                                                  | 14 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparing synchronisation and checkpointing: synchronising around predicted dependences can be problematic. We look at a code snippet: |    |

|     | if <i>cond</i> is true, the store will restart subsequent tasks                                                                        | 15 |

| 2.3 | Example of a simple loop spawn insertion. When the spawn instruction                                                                   |    |

|     | executes, both tasks start at the next instruction. The parent has child                                                               |    |

|     | set to false and the child has it set to true.                                                                                         | 19 |

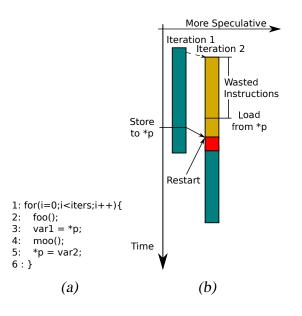

| 3.1 | Intermediate checkpointing showing two iterations                                                                                      | 22 |

| 3.2 | Intermediate checkpoints and selective restart                                                                                         | 25 |

| 3.3 | Restart algorithm showing how restart and kill events are recursively                                                                  |    |

|     | propagated.                                                                                                                            | 27 |

| 3.4 | Example of selective restart using timestamps                                                                                          | 29 |

| 4.1 | Address Predictor in action.                                                                                                           | 35 |

| 4.2 | Address based checkpointing sometimes has trouble identifying de-                                                                      |    |

|     | pendences                                                                                                                              | 36 |

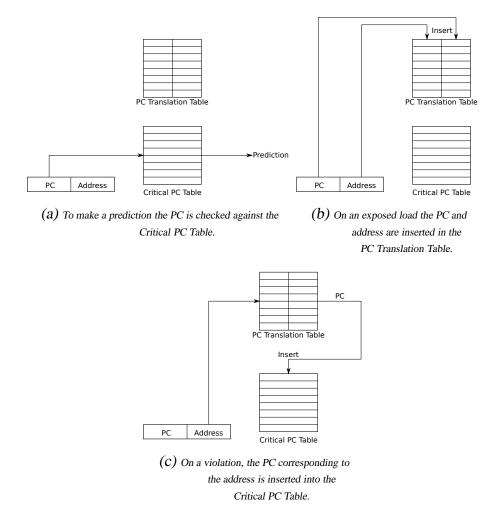

| 4.3 | PC Predictor in action.                                                                                                                | 37 |

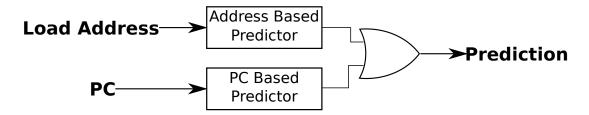

| 4.4 | A hybrid dependence predictor where the outputs of the predictors are                                                                  |    |

|     | ORed                                                                                                                                   | 38 |

| 4.5 | A hybrid predictor. Based on the Program Counter, a meta-predictor                                                                     |    |

|     | selects the prediction to use.                                                                                                         | 39 |

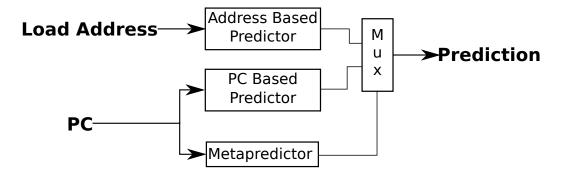

| The instructions before the load from $p$ are not dependent, and are     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| wastefully re-executed. All the instructions from the start of the task  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| to the one immediately preceding the load are <i>wasted instructions</i> | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

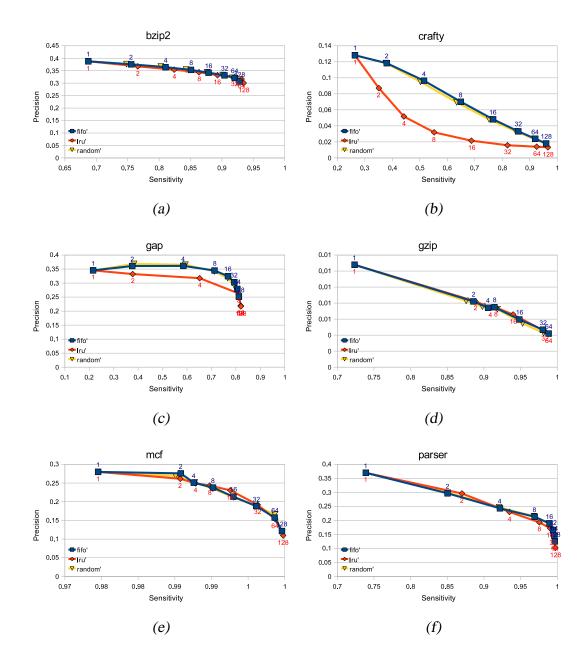

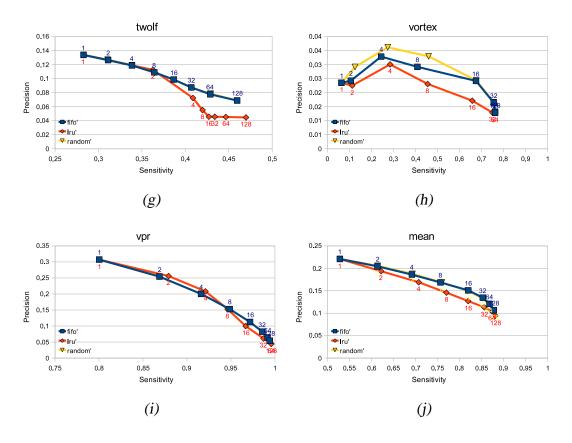

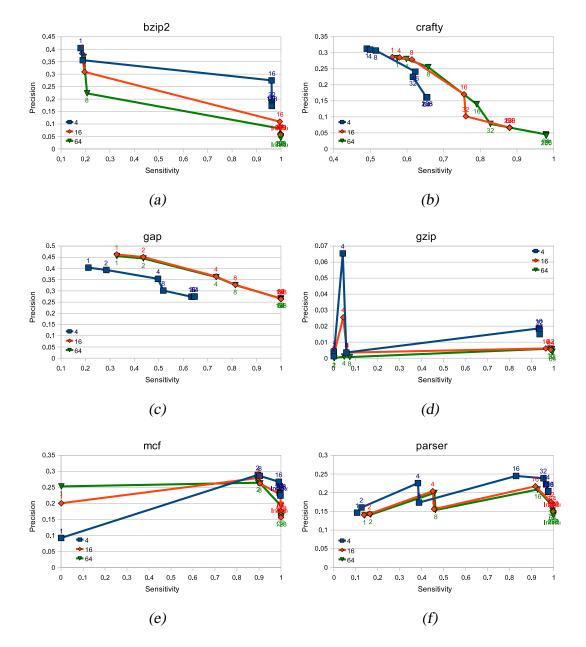

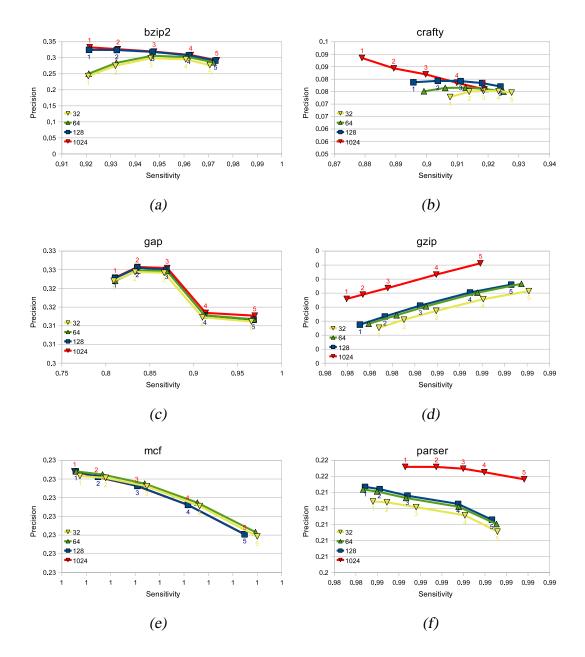

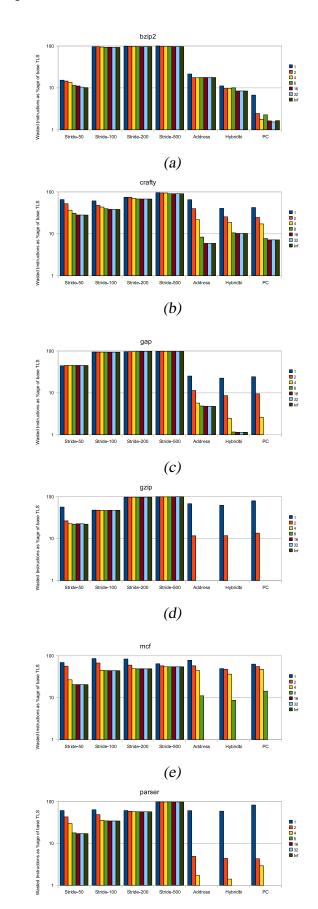

| Sensitivity and Precision for address based dependence predictor with    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LRU, FIFO and Random replacement policies. (Continued on next page)      | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

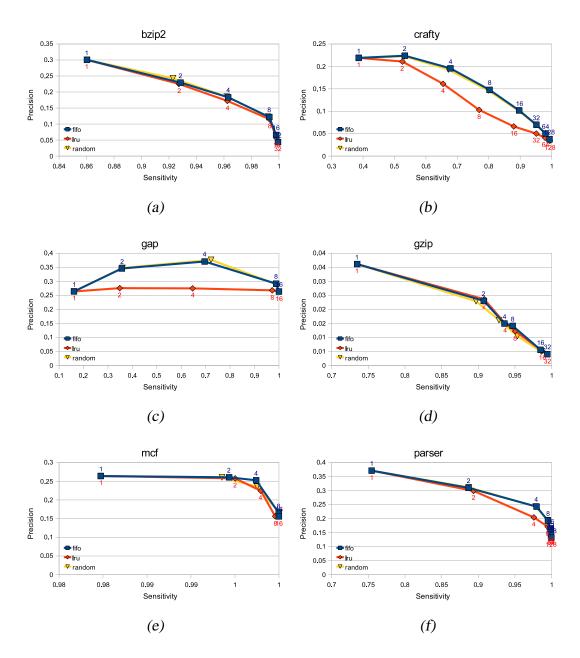

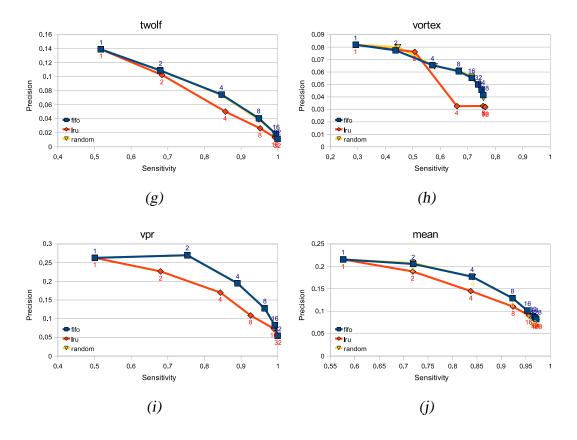

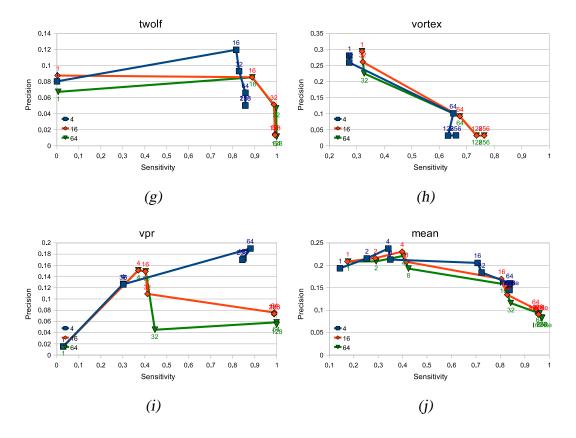

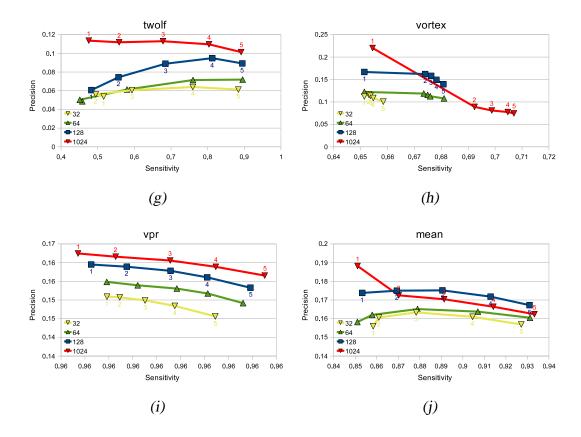

| Sensitivity and Precision for Program Counter based table dependence     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| predictor with LRU, FIFO and Random replacement policies. (Con-          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| tinued on next page)                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sensitivity and Precision for PC based dependence predictor for vari-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ous sizes of PC Translation Table. (Continued on next page)              | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

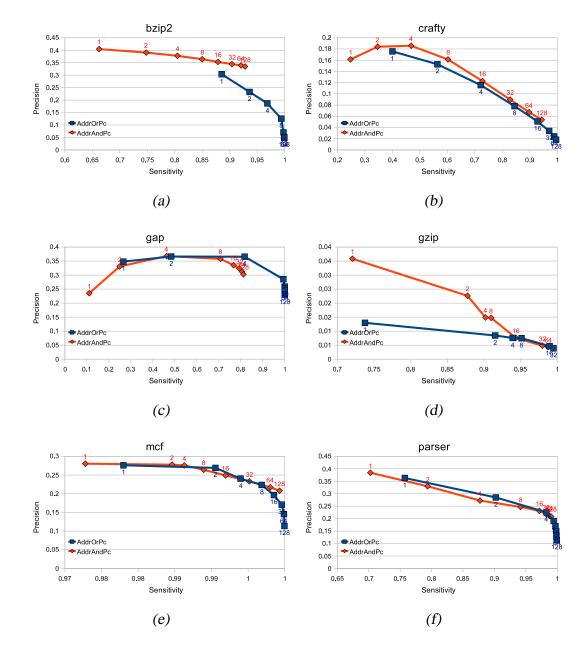

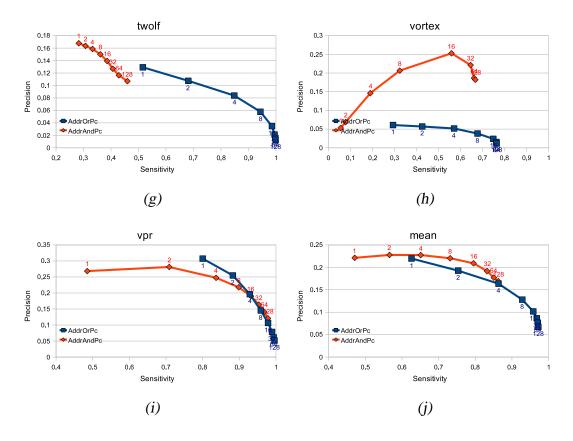

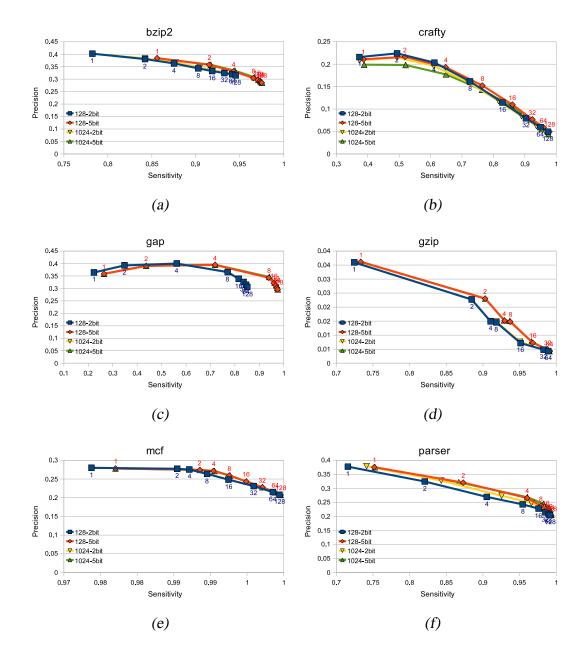

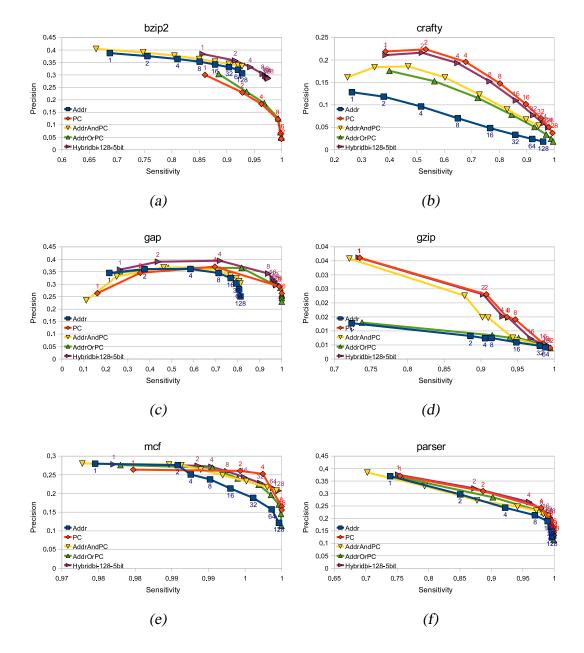

| AND and OR hybrid predictors, varying buffer size for individual pre-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| dictors. (Continued on next page)                                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

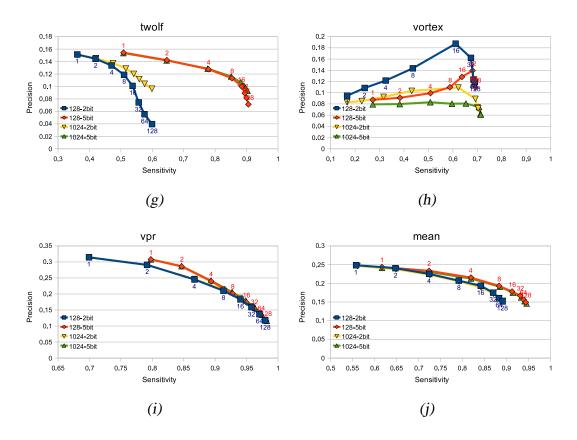

| Hybrid bimodal predictor, varying table size and the number of counter   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bits. (Continued on next page)                                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Hybrid bimodal predictor, varying buffer size for individual predictors. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (Continued on next page)                                                 | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparison of predictor types                                            | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

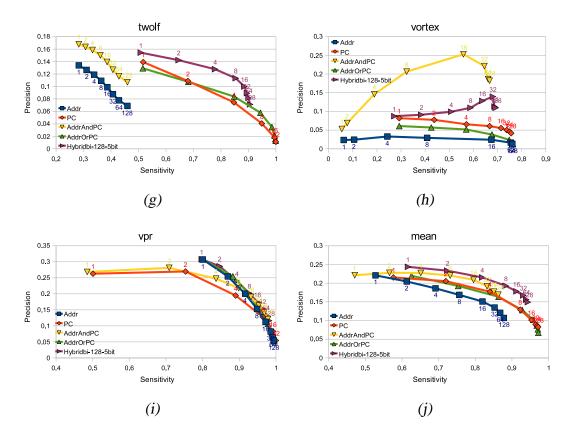

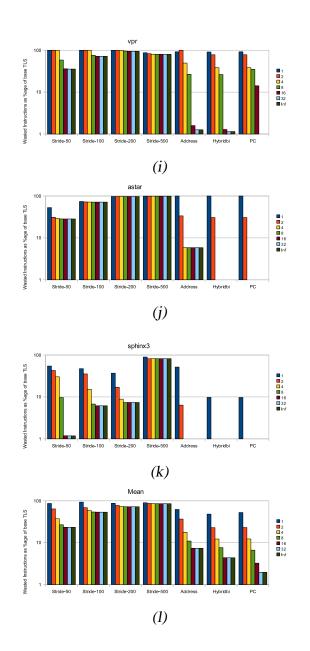

| Change in savings of wasted instructions as the maximum number of        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| checkpoints is changed. (Continued on next page)                         | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

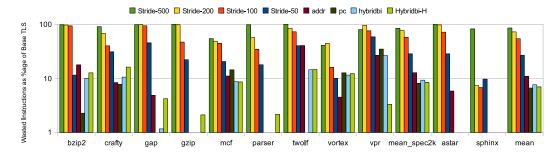

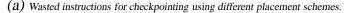

| Unnecessary re-execution as a percentage of TLS with no checkpoint-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ing for different checkpoint placement schemes.                          | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

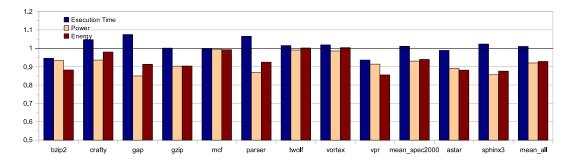

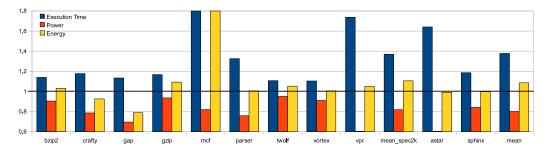

| Checkpointing shows power improvement, resulting in an energy im-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| provement of 7% on average over base TLS                                 | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

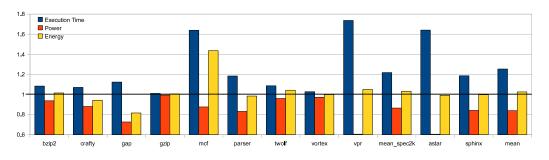

| Checkpointing recovers some of the power lost to speculation while       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| maintaining speedup.                                                     | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

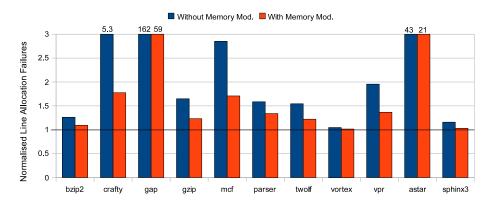

| Number of times allocation of a speculative line fails in checkpointed   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| execution normalised against TLS without checkpointing                   | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

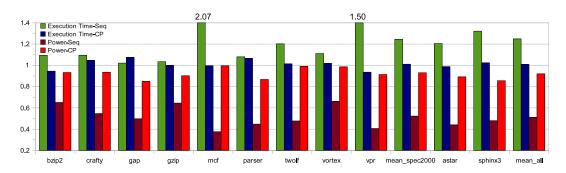

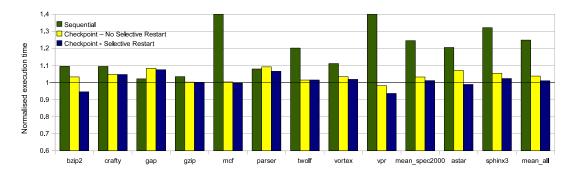

| Execution time for sequential execution and TLS when checkpoint-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ing with and without selective restart, normalised against TLS without   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| checkpoints                                                              | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                          | wastefully re-executed. All the instructions from the start of the task<br>to the one immediately preceding the load are <i>wasted instructions</i><br>Sensitivity and Precision for address based dependence predictor with<br>LRU, FIFO and Random replacement policies. (Continued on next page)<br>Sensitivity and Precision for Program Counter based table dependence<br>predictor with LRU, FIFO and Random replacement policies. (Con-<br>tinued on next page) |

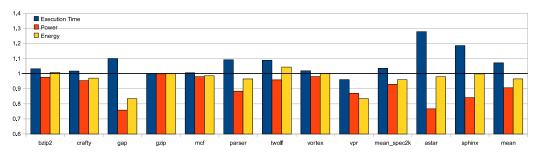

| 6.14 | Effect of synchronisation on execution time, power and energy, nor- |    |

|------|---------------------------------------------------------------------|----|

|      | malised against base TLS execution.                                 | 78 |

# **List of Tables**

| 5.1 | Prediction Outcomes.              | 44 |

|-----|-----------------------------------|----|

| 5.2 | Percentage of Outcomes Known      | 46 |

| 5.3 | Architectural parameters used.    | 49 |

| 6.1 | $F_{\beta}$ values for predictors | 68 |

## **Chapter 1**

## Introduction

## 1.1 Chip Multiprocessors and Parallelisation

Since the early days of microprocessors, designs have evolved from simple, microcoded processors to complex, wide superscalars with multiple levels of cache. This has led to steadily improving performance, but at the cost of extremely complex designs. In the last decade, it has become clear that adding complexity to single processors to achieve greater performance is providing diminishing returns. Meanwhile, the number of transistors available per chip has continued to grow. This has led to Chip Multiprocessors (CMPs) becoming the mainstream design choice for general purpose computing.

In the absence of coarse grained parallelism, the performance potential of Chip Multiprocessors remains unrealised. To improve performance of sequential programs on CMPs, attempts are made to extract thread level parallelism from the sequential program flow. This may be done manually by the programmer or through various compiler techniques. When a sequential program is parallelised conventionally, the programmer or compiler needs to ensure that threads are free of data dependences. If data dependences do exist, threads must be carefully synchronised to ensure that no violations occur. Specially for languages that support pointers, compile time disambiguation is often impossible. This means that compilers are often unable to extract much parallelism from sequential code while still guaranteeing correctness. In the absence of speculation, inter-thread dependences constrain performance and automated thread partitioning seldom results in high performance (17).

Improving the performance of hard to parallelise programs through exploiting the opportunities presented by CMPs has been an area of intense research in recent years. This includes work in three broad categories. First, improved languages and programming models to allow programmers to more easily expose parallelism. Second, improved static analysis so that more parallelism can be extracted at compile time. And third, the area this thesis is concerned with, techniques to speculate on parallelism so that precise static dependence analysis is no longer required. With Thread Level Speculation (TLS), the compiler only needs to divide the code into threads. It does not need to guarantee that the multithreaded code is free of data dependences. If a dependence violation occurs at run-time, the speculation hardware detects the violation and rolls back the violating thread to a safe state. This mechanism allows the compiler to parallelise very aggressively and extract parallel threads from code that would otherwise not be parallelisable.

While Thread Level Speculation has been shown to provide significant performance improvements for hard to parallelise applications, questions remain about the efficiency of speculative execution. Re-execution of misspeculated portions of the program is wasteful in both time and energy. In case of a data dependence violation, TLS mechanisms (discussed in Section 2.1) lead to re-execution of *all* the instructions of the task in question, regardless of whether those instructions are dependent. The focus of this thesis is the reduction of wasteful re-execution. First, it proposes mechanisms for efficient checkpointing. Second, it uses dependence prediction as an effective way of placing checkpointing.

## **1.2 Contributions**

### 1.2.1 Efficient Checkpointing

This thesis presents new ways of addressing the inefficiency of Thread Level Speculative execution by proposing an intermediate checkpointing scheme based on dependence prediction. The idea of checkpointing speculative tasks is not new, however, previous work in the area of checkpointing speculative tasks has left many open questions. This is specially true about checkpoint placement policies. This thesis addresses implementation and policy details that are missing from previous work.

A detailed study is performed of the mechanisms involved in checkpointing and the policy issues that it exposes. Specifically, checkpointing is applied to a state-of-theart TLS system that supports out of order spawning of speculative tasks. Observing task behavior leads to the conclusion that the base TLS protocol is not well suited to checkpointed execution. This motivates extensions in the TLS protocol to allow effective checkpointing. Further, a dependence predictor based policy is used to effectively place checkpoints.

#### 1.2.2 Dependence Prediction

Dependence prediction is an important aspect of placing checkpoints effectively. Dependence predictors of varying levels of sophistication also have uses beyond checkpointing. They are important in synchronising speculative tasks to avoid data dependence violations (7; 42) and in resource management (53). This thesis proposes program counter and hybrid dependence prediction techniques in addition to previous address based ones, and performs a detailed evaluation of all these methods. It also discusses the complexity of constructing these various predictors.

## 1.3 Structure

This thesis is organised as follows.

**Chapter 2** provides background on Thread Level Speculation and techniques for reducing unnecessary re-execution. This includes work in value prediction and in particular intermediate checkpointing. This chapter ends with details on the TLS hardware support assumed for the remainder of the thesis.

**Chapter 3** proposes mechanisms for allowing efficient intermediate checkpointing. First, basic support for inserting intermediate checkpoints is described. Later, ways of making checkpointing more efficient are presented, including a modified restart mechanism and changes to the versioned memory system. **Chapter 4** looks at the policy options for inserting checkpoints. These include previously proposed stride checkpointing, and using dependence prediction to place checkpoints. It goes on to describe and compare various dependence predictors. The effects of overheads on checkpoint placement policy are also discussed.

**Chapter 5** describes the simulator setup and the benchmarks used for evaluation. The metrics used for evaluation are discussed and justified. This includes metrics for dependence prediction and the performance of checkpointing schemes.

**Chapter 6** performs a quantitative evaluation of the techniques described in this thesis. First, there is an extensive evaluation of dependence predictors and a comparison of different schemes. Then, the savings due to checkpointing are evaluated for various placement policies. The effects of the architectural extensions for efficient checkpointing proposed in this thesis are demonstrated. Finally, a brief demonstration is made of applying dependence prediction to synchronisation.

**Chapter 7** looks at related work. This includes other uses of checkpointing, such as early recycling of resources and fault tolerance as well as other schemes for checkpointing speculative execution.

Finally, **Chapter 8** concludes this thesis by summarising the contributions and discussing avenues of future extension.

## **Chapter 2**

## Background

This chapter surveys the background for this work. The first part, in Section 2.1, provides background on work on Thread Level Speculation (TLS), looking at the execution model, the architectural support needed, compiler and task selection issues and the various systems proposed. This section also introduces the terminology associated with TLS, which is employed throughout the rest of the thesis. Then, in Section 2.2 various techniques to address the overhead of wasted re-execution in speculative execution are discussed. Synchronisation aims to avoid speculative overlap when dependences exist. Checkpointing reduces the re-execution required by changing the granularity of task units that need to be restarted on a violation. Value prediction techniques aim to avoid restarts by predicting values for speculative uses which would otherwise have caused a violation. Finally, in Section 2.3 the TLS mechanism assumed in the rest of the thesis is detailed.

## 2.1 Thread Level Speculation

In the absence of coarse grained parallelism, Chip Multiprocessors (CMPs) generally do not match the performance of superscalar processors of comparable die area. To improve performance of sequential programs on CMPs, attempts are made to extract thread level parallelism from the sequential program flow. This may be done manually by the programmer or through various compiler techniques. When a sequential program is parallelised conventionally, the programmer or compiler needs to ensure that threads are free of data dependences. If a data dependence does exist, threads must be carefully synchronised to ensure that no dependence violations occur. In many cases, this cannot be effectively done by compilers. Specially for languages that support pointers, compile time disambiguation is often impossible. This means that compilers are often unable to extract much parallelism from sequential code while providing correctness guarantees. In the absence of speculation, inter-thread dependences constrain performance and automated thread partitioning seldom results in high performance (17).

Under the TLS execution model (also referred to in the literature as Speculative Multithreading), a sequential application is split into threads which are then speculatively executed in parallel with the hope that their concurrent execution will not violate sequential semantics (14; 16; 21; 38; 40). The control flow of the sequential code imposes a total order on the threads. A thread is said to be speculative if it is executing such that it is overlapped with a part of the program that is earlier in sequential order. Threads earlier in the sequential flow are termed less speculative (or *predecessors*) with respect to later threads (successors). The least speculative thread being executed is called the *head* or the *safe thread*. During speculative execution of threads, reads are monitored to detect data dependence violations. Writes may be forwarded from less speculative threads to more speculative ones in order to minimise violations. When executing tasks speculatively in parallel, correct behaviour is maintained by keeping the tasks ordered and making sure that no data dependences are violated. If a data dependence violation is detected, the consumer of the misspeculated data must be squashed along with its successors. A squash can result in a *restart*, reverting the state back to a safe position from which the thread can be re-executed. Alternatively, a thread can be *killed*, where the thread is simply destroyed and no re-execution is attempted. In most schemes a squash rolls the execution back to the start of the thread, but some proposals in the literature use periodic *checkpointing* of threads (8) such that upon a squash it is only necessary to roll the execution back to the closest safe checkpointed state. When the execution of a non-speculative thread completes it commits and the values it generated can be moved to safe storage. To maintain sequential semantics, threads must commit in order. When a thread commits, its immediate successor acquires nonspeculative status and is allowed to commit. When a speculative thread completes it must wait for all predecessors to commit before it can commit. After committing, the processor is free to start executing a new speculative thread.

## 2.1.1 Speculation Mechanism

To provide the desired memory behaviour, the data speculation hardware must provide at a minimum:

- 1. A method for detecting true memory dependences, in order to determine when a dependence has been violated.

- 2. A method for backing up and re-executing speculative loads and any instructions that may be dependent upon them when the load causes a violation.

- 3. A method for buffering any data written during a speculative region of a program so that it may be discarded when a violation occurs or permanently committed at the right time.

Typical ways of achieving these are described below.

#### 2.1.1.1 Tracking Dependences and Detecting Violations

Typically, all data written and read by a task is tracked in order to ensure that any violations are detected. This may be done at different granularities. Some systems do so for each word, others for cache lines.

A write marks a location as dirty. If the size of the write is equal to the granularity of tracking, the location is marked as *protected*. This is done so that dependence violations are not flagged for values that are produced in the same task that consumes them. Any read is marked as an *exposed read* unless it is from a protected location. A data dependence violation occurs when a task writes to a location that has been read by a more speculative task with an exposed read.

Locations can be checked for dependence violations immediately upon a write or dependences can be checked in bulk at the end of a task. Hardware speculation schemes usually perform the checks on each store, while software schemes usually do the checks when a task finishes (6).

#### 2.1.1.2 Buffering State

Speculative tasks generate speculative writes which cannot be merged with the state of the system unless the task commits. These writes are stored separately, typically either in the cache of the processor running the task or in a dedicated speculative store buffer. If the task successfully commits, the state is merged with system state. If it is squashed before it reaches completion, buffered state is discarded. A task only commits if it completes execution *and* becomes non-speculative. This ensures that tasks commit in order, thus preserving sequential semantics. Garzaran et al. (13) provide a taxonomy of buffering approaches along with their respective advantages.

#### 2.1.1.3 Data Versioning

Each task has one version of each datum. If a number of speculative tasks are running on a system, each has a different version of shared data. On commit, versions are merged into system state in task order.

Some proposals allow one version per processor (27), while others support multiversioned caches and hence allow a speculative task to execute on a processor even if commit is still pending for a previously executed task (34). Colohan et al. (8) do not use versioned memory at all in the first level of cache, instead relying on a multiversioned *L*2 cache. To allow efficient execution in the presence of shared data, speculative systems also forward shared data from earlier threads to later threads.

#### 2.1.1.4 Register Passing

TLS systems vary in the degree of direct communication between processors. Multiscalar (38) allows direct communication between processors, allowing passing of live registers to freshly spawned tasks. Other proposals assume CMPs with no direct communication between processors and in these, all communication has to take place through shared memory. If all live registers are transferred from the parent task to the spawned task, there are no complications regarding initial processor state for the speculative task. Otherwise, the issue needs to be addressed in the compiler or runtime by ensuring either that the newly spawned task does not rely on any registers or that register values are transferred.

#### 2.1.1.5 Out-of-Order Spawn

In a TLS system, task ordering has to be maintained at all times. Some TLS proposals can only do this for in-order spawns. This means that tasks can only be created in the same order as sequential execution. This constraint can be enforced by only allowing the most speculative task to spawn another task. This means that each task can spawn at most one task. In-order spawn allows tasks to be spawned for only one loop level. Other systems support out-of-order spawning as well (32; 34). In this case, *any* task can spawn another speculative task. This allows nested tasks to safely be spawned.

Support for out-of-order spawn allows more parallelism to be extracted from nested loops, nested function calls, loops within function calls, etc.

#### 2.1.1.6 Control Speculation

Most of the TLS architectures discussed support only data speculation. This means that speculation can only occur between points that are *execution equivalent* <sup>1</sup>. However, the Superthreaded Architecture (45) supports control speculation, but not data speculation. The Superthreaded compiler (44) can convert data dependences into control dependences, so that they can be enforced even without hardware data speculation support. Mitosis (20; 30) supports both control and data speculation. It does so by speculating between points that are not execution equivalent, but then adding *cancel* instructions on incorrect paths. This ensures that tasks that are created along misspeculated paths are killed.

<sup>&</sup>lt;sup>1</sup>Two locations are said to be execution equivalent when one of them executes if and only if the other does, and they both execute the same number of times.

### 2.1.1.7 Spawn and Commit Mechanism

The hardware must provide a mechanism for starting tasks and for signalling that tasks have reached completion. Typically this is done through special *spawn* and *commit* instructions or through software control handlers supported by some specialised registers in hardware, as in the case of the Hydra CMP (27).

### 2.1.2 Compilation

Thread Level Speculative execution typically requires some compiler support. The compiler can be tasked with one or more of task selection, code generation and TLS specific performance optimisations.

In most proposed systems, task selection is done statically at compile time. One option is to use high level program structure to select tasks. This means constructs such as loops and function calls are candidates for tasks. Proposals that use this approach include the POSH (18) and Spice (31) compilers. Other systems take a more general approach. Mitosis (30) identifies *spawning pairs*, which are pairs of instructions that meet certain conditions of control and data independence. The Min-Cut approach to decomposition by Johnson et al. (15) applies graph theoretic algorithms to the control flow graph, such that all basic blocks and combinations of basic blocks are candidates for tasks. Other proposals that are not restricted to loops and functions for task selection include Multiscalar (48) and the compiler framework by Bhowmik and Franklin (1).

Not every candidate task performs well when speculated on. There are various ways of pruning out inefficient tasks. One possibility is to perform a preliminary task selection and then profile the resulting decomposition (18). Another is to leverage information about dependences between tasks at compile time. When taking static decisions on the quality of task decomposition, dependence relationships between tasks are important. In traditional, non-speculative parallelisation, if pointers are present pointer analysis needs to be performed to guarantee that there are no inter-task data dependences. This can be done by comparing the read and write references between them. Traditional pointer analysis techniques classify points-to relationships into those

that definitely hold and those that may hold. TLS does not require guarantees of tasks being dependence free, but would benefit in performance from information about the likelihood of dependences across tasks. This information can be provided through a dependence profile of the sequential program, or through *Probabilistic Pointer Analysis* (4; 37). Dou and Cintra (9) take a different approach, constructing a model to predict task runtime and then choosing tasks with predicted speedups. Recently, the use of hardware based performance counters to create speculative tasks at runtime has been proposed (19), removing the need for making static compile time and/or profile based decisions.

Further, in systems that do not support register communication between cores, the compiler must ensure correctness by communicating all values between tasks through memory.

Some compilers also perform TLS specific optimisations to make speculative execution more efficient. For instance, Zhai et al. (55) look at identifying dependent scalar use and define pairs and then aggressively scheduling the *USEs* late in the consumer task and the *DEFs* early in the producer task. This increases overlap when synchronisation is being used. In that work, the synchronisation is statically performed at compile time, but the same optimisations can apply to dynamic, hardware guided synchronisation and checkpointing schemes. Steffan et al. (41) have noted that small loop bodies can be made more TLS friendly through loop unrolling. The interaction of loop unrolling with speculative execution is further studied by Wang et al. (50). Software value prediction code may also be inserted at compile time, as by Mitosis (20) and the Superthreaded architecture (44). This is discussed in Section 2.2.3.

## 2.2 Reducing Wasted Re-execution

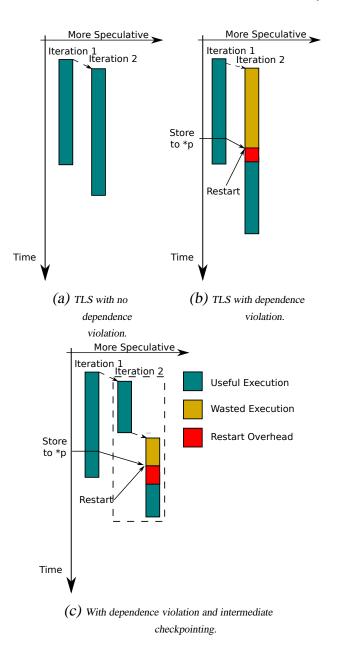

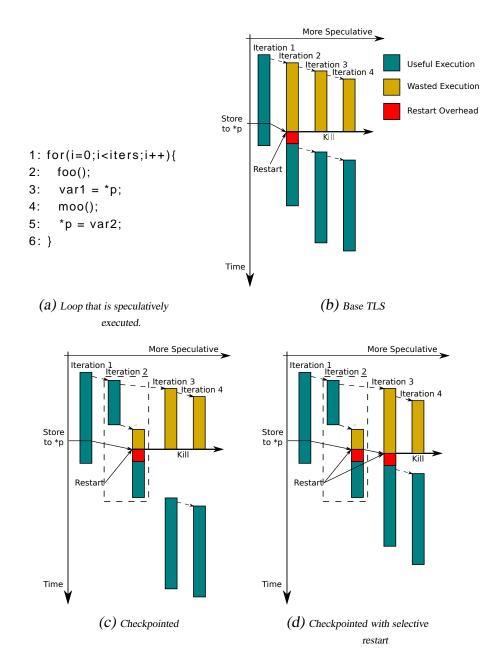

When there are no dependences between tasks, TLS works well to achieve parallelism by overlapping execution of sections of code (Figure 2.1a). However, in many cases violations occur and remove much of the overlapped execution (Figure 2.1b). Dependence violations incur significant overhead. There have been a number of techniques proposed to reduce this overhead. These are discussed below.

### 2.2.1 Synchronisation

Synchronisation aims to avoid dependence violations by serialising parts of execution such that values are not consumed before they are produced. This can reduce wasteful re-execution (7; 25; 42; 54; 55).

In the work of Zhai et al. (54; 55), a compiler based approach is used to synchronise scalar communication between tasks. The compiler identifies communicated scalar values, then inserts *wait* and *signal* instructions, each of which is associated with the scalar through an architected register. The *wait* instruction stalls until the value is produced in the previous task and communicated through a *signal*. In this proposal, since scalar values are explicitly communicated, correct execution depends on maintaining correct synchronisation. This can be achieved trivially by placing all the *signal* instructions at the end of a task and all the *wait* instructions at the start. This has the effect of serialising execution. To achieve overlap, each *signal* is placed as early as possible and the associated *wait* as late as possible. Also, to avoid deadlock, *wait* and *signal* instructions for each synchronised scalar must appear on every possible path. Further, an aggressive instruction scheduling algorithm is used to maximise overlap. The work has also been extended to memory resident values (56). In this case, since the underlying TLS mechanism ensures correctness, the optimisations can be more aggressive.

There have been a number of hardware techniques proposed as well for synchronising speculative tasks. The Multiscalar architecture (12; 25) uses an *Address Resolution Buffer* to automatically synchronise dependent load-store pairs.

The Multiscalar approach relies on very close coupling between processors. In a more general shared memory environment, different techniques have to be employed. Cintra and Torrellas (7) achieve synchronisation by associating states with cache lines. This state information is kept in a *Violation Prediction Table*. If a location sees violations, the system first tries to value predict, and if this fails it falls back on synchronisation. When a task consumes data from a cache line that commonly causes a violation and cannot be value predicted, it is stalled. At what point the consumer continues execution depends on the state of the cache line. In the *Stall&Release* state, it waits for the first write to the line. On the other hand, in the *Stall&Wait* state, it waits for all

possible writers, i.e. until the consumer becomes non-speculative.

A slightly different approach is taken by Steffan et al. (42). This scheme also attempts to value predict in the first instance and falls back on synchronisation when the prediction confidence is low. However, instead of associating states with cache lines, it marks load *instructions* as being hard to predict. If a load instruction leads to violations, it is added to a *violating loads list*. This list is checked whenever a load instruction executes, and if the Program Counter of an executing instruction is found in the list, it is stalled. In this scheme, the load is always stalled until it becomes non-speculative.

### 2.2.2 Checkpointing

Intermediate checkpointing schemes aim to reduce misspeculation penalty by allowing partial rollback (Figure 2.1c). This is done by checkpointing the processor at some point or points during the execution of a task, and upon detecting a violation, only rolling back to the latest checkpoint which allows correct re-execution. Instead of avoiding violations, as synchronisation does, checkpointing aims to reduce the cost of violations.

The effect of checkpointing is quite similar to synchronisation when a violation does occur. In fact synchronisation is more efficient than checkpointing in cases where we can be sure that a violation will occur. On the other hand, if a violation occurs rarely, but at a high cost, then synchronisation may cause unnecessary serialisation, and checkpointing is a better alternative.

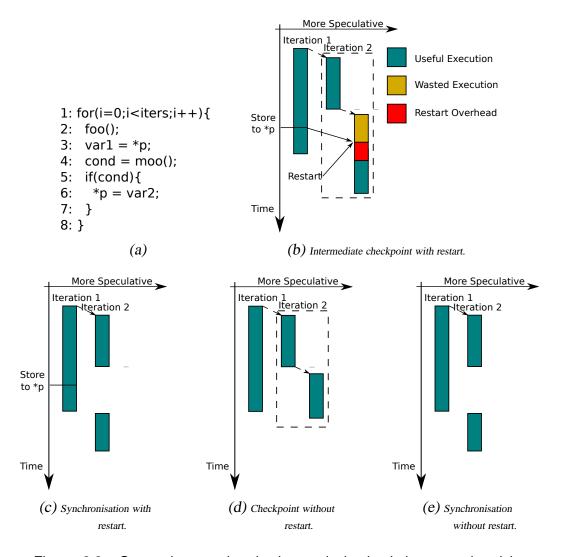

This can be understood better by inspecting the code snippet in Figure 2.3a. Assume that when the *cond* boolean is true, the resulting store in line 6 causes a squash to all subsequent threads, and that when *cond* is false, these threads commit without restart. In Figure 2.3b we can see what happens for the intermediate checkpointing case when speculation fails. The checkpoint is able to save some of the execution, however all the instructions executed after the checkpoint are wastefully executed. By synchronising instead, some power can be saved since the wasteful execution of these instructions is avoided (Figure 2.2c). However, when the store is not performed, and thus all threads commit, intermediate checkpointing is preferable. As is evident from

Figure 2.1: Example of Thread Level Speculation and checkpointing.

Figure 2.2d, we place a checkpoint before the load and proceed as normal. On the other hand, by synchronising on that load, the second thread will have to wait until it becomes safe, since the store which it attempts to synchronise with, is never performed by the less speculative thread (Figure 2.2e). This results in unnecessary serialisation.

From this example it is clear that from a performance point of view intermedi-

Figure 2.2: Comparing synchronisation and checkpointing: synchronising around predicted dependences can be problematic. We look at a code snippet: if *cond* is true, the store will restart subsequent tasks.

ate checkpointing is better (if we disregard the associated overhead of possible extra restarts, which is typically small). In fact, even threads that will have to be killed or restarted can indirectly provide performance benefits by prefetching for safer threads (34; 52). However, in terms of number of instructions executed, and thus energy consumed, synchronisation is typically better.

Checkpointing speculative tasks is studied by Colohan et al. (8). This is done in

the context of supporting efficient speculation for long running database tasks. The workload considered in that study consists of tasks that are often more than 50,000 dynamic instructions in size, and show large numbers of cross-thread dependences. The L2 cache is extended to maintain state for multiple thread contexts. A *sub-thread* is created by checkpointing register state and saving subsequent speculative state in the next thread context.

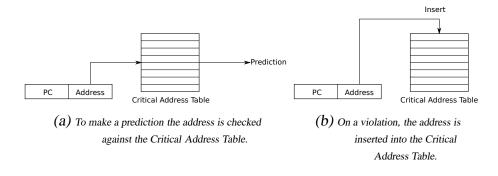

The decision to place a checkpoint can be taken in a variety of ways. Colohan et al. (8) place checkpoints periodically on fixed instruction strides. Waliullah and Stenstrom (49) place intermediate checkpoints in transactions in a Transactional Memory system <sup>2</sup>, guiding checkpoint placement by identifying loads that may cause misspeculation. This is done by maintaining a *Critical Address Buffer*. Whenever a violation occurs, the address of the violating data is inserted into the buffer. The address of every speculative load is checked against this buffer and if it is found, a checkpoint is inserted. Checkpoint placement schemes are explored in detail in Chapter 4.

### 2.2.3 Value Prediction

There have been a number of proposals that include prediction of speculative values so as to avoid dependence violations. Value prediction has been suggested in both software and hardware. Successfully predicting values communicated from less speculative tasks to more speculative ones breaks dependences altogether and allows for more overlap. The Spice proposal (31) splits loop iterations into as many speculative chunks as there are cores available, and inserts code for predicting live-ins for each chunk. The POSH compiler (18) performs value prediction as well, but only for what it identifies as induction variables. Mitosis (20; 30) adopts a much more general method for value prediction, inserting pre-computation slices at the start of speculative sections. This is done by traversing the control flow graph backwards starting at the speculative section. Instructions that produce the live-ins to the speculative section are selected. These selected instructions are then summarised using profile information. For instance, rarely taken control paths are pruned out, as are instructions that the live-ins are infrequently

<sup>&</sup>lt;sup>2</sup>Transactional Memory (TM) is a speculative parallelisation technique related to TLS. TM systems also suffer ineffiency due to wasteful re-execution.

dependant on. These summarised instructions are then duplicated at the start of the speculative section to form a *p-slice*. The live-ins produced by these *p-slices* are validated when the previous task has both ended and become non-speculative.

A number of proposals incorporate hardware value prediction for both register and memory resident values. Cintra and Torrellas (7) propose a framework for learning and predicting violations, and using value prediction in certain states. They only evaluate a simple last value predictor and find that it does not improve performance significantly. Steffan et al. (42) have a similar scheme that throttles value prediction and only employs it under certain circumstances. Values are predicted when the load in question is likely to squash *and* the prediction confidence is high. If the prediction confidence is low, the load is synchronised. This is discussed in Section 2.2.1. The scheme is evaluated with an aggressive hybrid context and stride predictor.

Marcuello et al. (22) evaluate various value predictors on their Clustered Speculative Multithreaded processor. They look at innermost loops in SPECint95 and propose a new predictor targeted specifically toward speculatively multithreaded systems, called a *new value predictor*. They conclude that it is beneficial to value predict register dependences, but that memory value prediction did not lead to much further improvement.

Prior to this, Oplinger et al. (28), as part of a study to identify sources of potential performance improvement using speculative multithreading, observed that return value prediction for procedures and stride value prediction for loops can improve performance.

While synchronisation is an *alternative* to value prediction, checkpointing and value prediction can be *combined*. If a checkpoint is placed when a value is predicted, the misprediction penalty is reduced. Unlike synchronisation, checkpointing does not result in a stall.

## 2.3 Hardware Support for Speculative Multithreading

In this section, the details of the TLS execution model and the hardware to support it are described. These form a baseline model for the rest of the thesis.

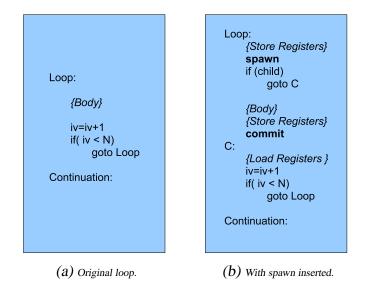

The basic TLS model used is very similar to the one proposed by Renau et al. (32; 34). Data versioning and dependence tracking are handled through having a multiversioned L1 cache. If a task attempts to perform a speculative load and there is no space in the L1 cache to allocate a speculative line, the task cannot continue. In this case, the most speculative task on the processor is restarted in an attempt to free some speculative memory. The L2 cache is shared and only contains non-speculative data. Spawns and commits are performed through explicit instructions. When a spawn instruction is encountered, a new task is spawned off on a different processor, with the Program Counter, Stack Pointer and some task ordering information copied over. No other registers are copied, and hence the compiler is responsible for spilling registers around spawn instructions and ensuring that live-ins for spawned tasks are communicated through memory. Since both the parent and child task start with the same Program Counter, a mechanism needs to exist for each task to execute the correct code. This is done through the spawn instruction returning different values. That is, the standard return value register (r31) holds 0 in the parent and 1 in the child after the spawn. A conditional branch placed by the compiler after the spawn instruction can thus choose the correct code to execute. An example of such a spawn for loop level speculation is shown in Figure 2.3.

Since out-of-order spawn is supported, there are no restrictions on which tasks are allowed to spawn. This support is through splitting task ID ranges as proposed by Renau et al. (34).

During speculative execution, whenever a task performs a store, it is immediately written through the *L*1 cache to the bus, and becomes visible to all other processors. If, for any task more speculative than the task performing the store, the address matches an exposed load, the more speculative task is immediately restarted. Once a task reaches the end of execution (executes a *commit* instruction), it becomes ready to commit. A task cannot actually commit state until it becomes non-speculative. The commit process itself involves propagating all speculatively written data to safe system state <sup>3</sup>, followed by passing the *commit token* to the next more speculative task. This in turn

<sup>&</sup>lt;sup>3</sup>This is done by writing all speculative L1 lines associated with the committing task to the L2 cache, and marking those lines in the L1 cache to be non-speculative.

Figure 2.3: Example of a simple loop spawn insertion. When the spawn instruction executes, both tasks start at the next instruction. The parent has *child* set to false and the child has it set to true.

informs the next task that it is now non-speculative and is allowed to commit.

Restarts are handled by restoring the Program Counter and Stack Pointer values with which the task was spawned and starting execution. Since speculative tasks are not allowed to assume live-ins through registers, the entire register file does not need to be restored.

As an energy optimisation, the number of restarts is limited. If a task receives a violation and restarts three times, it then stalls until it becomes non-speculative before it can continue. This is to prevent tasks with many dependences from wasting too much energy.

# **Chapter 3**

## **Checkpointing Mechanism**

Intermediate checkpointing of speculative tasks requires some architectural support. This chapter describes the mechanisms required to support efficient intermediate checkpointing. First, in Section 3.1, the basic checkpointing support is described, and the hardware requirements enumerated. In Section 3.2, cases are identified in which the basic scheme leads to inefficiencies, and extensions to overcome these problems are described.

## 3.1 Creation of Checkpoints

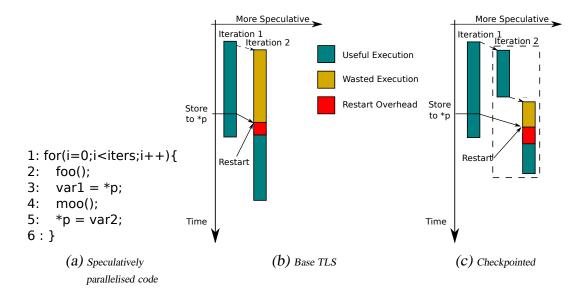

The insertion of checkpoints in the proposed scheme is quite straightforward. When a task is to be *checkpointed*, we simply spawn a new task which is an immediate successor to it. This is a hardware initiated spawn, unlike the compiler inserted spawn instruction mentioned in Section 2.1.1.7. We shall refer to this new task as the *checkpoint*. This process is shown in Figure 3.1, considering a simple case of two iterations of a loop, one of which is executed speculatively. In the base TLS case, the task receiving a violation restarts. In the checkpointing case, a checkpoint is inserted by spawning off a new task. We assume that the checkpoint is inserted just before the read from \*p in line 3. This *checkpoint* then behaves exactly as normal, and restarts upon receiving a violation. The difference is that the *checkpointed* task does not see a violation.

Figure 3.1: Intermediate checkpointing showing two iterations.

Further, we take a snapshot of the register file so that the checkpoint can be restarted<sup>1</sup>. We constrain the newly created checkpoint to remain on the same processor as the checkpointed task. This simplifies the protocol and keeps overheads low because live registers remain available in checkpointed execution. If we allowed checkpoints to be started on a different processor, we would need complex support for communicating live registers across processors. Keeping the checkpoint on the same processor is also the obvious route to take with respect to data locality. Apart from pinning it to the same processor as the parent, the checkpoint only cause a restart to the checkpoint. If a violation affects the checkpoint task, it is restarted and since the checkpoint is a successor task, the checkpoint is killed. Any task can be checkpointed, even if it is a checkpoint. The versioned memory mechanism ensures that tasks have the correct state just as with normal tasks. It is worth observing that if the underlying TLS protocol only allows in-order tasks, only the most speculative task can be checkpointed through this mechanism. Since we use a base protocol that allows out-of-order spawn,

<sup>&</sup>lt;sup>1</sup>In the base TLS protocol, no such snapshot is required when spawning a new task, since it is assumed that there are no live registers and all communication to the new task is through memory. So for non-checkpoint tasks, we only need to store the Program Counter and Stack Pointer in order to allow restarts, as discussed in Section 2.3.

we can checkpoint any task, whether it is the most speculative or not. However, as we demonstrate in Section 3.2 through examples, there are some extensions required to the TLS protocol to allow checkpointing to be effective in improving performance and reducing power consumption.

### 3.1.1 Hardware Requirements

The hardware changes required to allow checkpointing speculative tasks are minimal. The only difference between a normal spawn and a checkpoint is that a checkpoint requires a snapshot of register state. This can be done either by sets of shadow registers in the processor, or by storing these snapshots in memory. If the former route is chosen, snapshots can be taken very quickly, perhaps with no time penalty at all, but the number of checkpoints is limited. Such shadow register files are already supported in processors to allow recovery from branch mispredictions. If, on the other hand, registers need to be transferred to memory for each checkpoint, there is an associated latency. Storing the snapshot in memory need not cause a delay, since this process is not on the critical path and can be buffered and performed lazily. However, rewinding to a checkpoint would incur memory access latency in this case.

It is also possible to envision a hybrid process, which would keep register state for some checkpoints on the processor but allow older checkpoints or those less likely to be used to be moved to memory. If those checkpoints that are more likely to be needed can by successfully identified, this approach could give the best of both worlds.

For the purpose of evaluation in this thesis, checkpointing through shadow register files in the processor is modeled. The effects of supporting varying numbers of checkpoints are evaluated in Section 6.2.

Checkpointing a task and continuing execution of the checkpoint on the same processor presents the question of *when* the checkpoint begins execution. If, on a modern pipelined processor, we wait for the instructions from the checkpointed task to drain from the pipeline, there is a significant cost. There is no need to wait, however, and checkpoint instructions can follow immediately. In fact, once a decision to checkpoint is made, it is even possible to insert a checkpoint at an instruction already in the pipeline. It is important that loads and stores on either side of the checkpoint boundary are marked with the correct task ID in the versioned cache. Also, the register file must be checkpointed at the state after the last instruction of the checkpointed task in sequential execution. This can be achieved by performing the checkpoint in two stages. Once the instruction where the checkpoint is to be placed is identified, mark all memory operations after that in sequential order with the child task ID. Second, when the first instruction in the checkpoint task is ready to commit, take a snapshot of the register file to associate with the checkpoint.

Apart from the mechanism for inserting checkpoints, there has to be hardware support for deciding *when* to insert a checkpoint. This can be done either by having explicit checkpoint instructions or by making the decision at runtime. Policies for checkpoint insertion and the hardware requirements for employing each policy are left for discussion in Chapter 4.

## 3.2 Efficient Checkpointing

Though the minimum support for inserting checkpoints is quite simple, as described above, observing checkpointed execution reveals that this may not be sufficient for checkpointing to be *efficient* in terms of execution time and power consumption. This is demonstrated through examples in the remainder of this chapter and hardware extensions for overcoming these shortcomings are proposed.

### 3.2.1 Selective Kills and Restarts

In TLS execution, a task may spawn a more speculative task and later get killed or restarted. In the base TLS mechanism, when a task is restarted, all the tasks that are more speculative are killed. However, since the task re-executes from the beginning, any tasks it spawned earlier (before restart) are now respawned<sup>2</sup>. Rewinding to a checkpoint may change this behaviour.

We look at this issue by revisiting the program in Figure 2.2. This time, in Figure 3.2, we look at speculating on multiple iterations of the loop, assuming a four

<sup>&</sup>lt;sup>2</sup>This assumes that the spawns are on a control path that is taken each time. If this is not true, the tasks spawned before and after restart may be different.

Figure 3.2: Intermediate checkpointing with four processors and a dependence violation. For simplicity only the first dependence violation is shown, and checkpoints are only shown for the first speculative task.

processor system. In Figure 3.2b, we look at the case without checkpointing. We see that a violating store to p in the safe task 1 (running iteration 1) causes task 2 (running iteration 2) to be restarted and tasks 3 and 4 to be killed. However, the restarted task 2 quickly causes new tasks to be spawned. Now, looking at the case in Figure 3.2c, where the speculative task 2 is checkpointed immediately before the offending load, we see that we save re-execution by only rewinding to the checkpoint. In this case, the processors that are left idle because tasks 3 and 4 are killed remain idle until task 2 finishes executing.

Checkpointing causes this behaviour often since when tasks are not rolled back completely, they do not necessarily respawn child tasks that have been killed. This is specially true of loop iteration speculation where spawns are often at the very start of tasks. This can cause or exacerbate load imbalance. This issue can be *rectified* with some changes to the TLS protocol, which are described below.

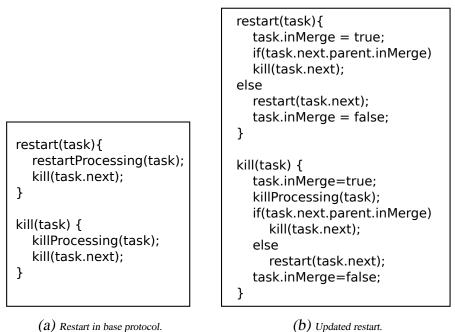

When a task is restarted, we have to be careful to maintain correctness in more speculative tasks. In the base protocol, this is achieved by simply killing all tasks more speculative than a task that is restarted. This is shown in Figure 3.3a. The algorithm there shows that whenever a task receives a restart, it restarts itself, and propagates a kill signal to the next more speculative task<sup>3</sup>. We observe that this is excessively conservative. The only tasks that have to be killed are those that were spawned incorrectly. That is, those tasks that were spawned by execution that turned out to have misspeculated. So, in the updated restart algorithm, we kill each task whose parent (spawning) task has been restarted or killed. Or, to state it differently, for each task that is restarted or killed, all its children are killed. For other tasks that are more speculative than any killed or restarted task, even though they were spawned correctly, it is still possible that they have consumed invalid values forwarded from less speculative tasks. Therefore, we restart all other tasks that are more speculative than any killed or restarted task. This modified restart mechanism is shown in Figure 3.3b. Here, the algorithm is expressed recursively. *inMerge* is used to check if a task's parent has been killed or restarted as part of the current chain of restarts and kills. Each task

<sup>&</sup>lt;sup>3</sup>As described in Section 2.1.1.5, in out-of-order speculation the successor of a task is not necessarily its child, and the predecessor not necessarily its parent. This distinction should be kept in mind during the discussion of restart and kill mechanisms.

(a) Restart in base protocol.

```

restart(task){

kill(task) {

task.inMerge = true;

task.inMerge=true;

if(task.startTime

earliestRestartTime =

> earliestRestartTime) {

max(earliestRestartTime,

earliestRestartTime =

task.startTime);

max(earliestRestartTime,

if(task.next.parent.inMerge)

task.startTime);

kill(task.next);

restartProcessing(task);

else

}

restart(task.next);

if(task.next.parent.inMerge)

task.inMerge=false;

kill(task.next);

}

else

restart(task.next);

task.inMerge = false;

}

```

(C) Updated restart with timestamp comparison.

Figure 3.3: Restart algorithm showing how restart and kill events are recursively propagated.

that is restarted or killed sets *inMerge* to true before passing on a kill/restart token. For any task, *task.next* is the immediately more speculative task. *task.parent* is the parent or spawning task. By checking the value of *inMerge* for the parent of each task, we can ensure that all tasks that were spawned from misspeculated execuation are killed. It is worth noting that the same effect can be achieved by associating a list of task IDs with the kill or restart signal, with the ID of each task being appended to it when it is killed or restarted.

This issue is specific to out-of-order spawn, since if spawns are only in-order, for any given task, all tasks that are more speculative have been spawned by it or its successors. For in-order spawn, the algorithm in 3.3b reduces to killing all tasks more speculative than the restarted one.

If the new restart algorithm is used, we get the situation in Figure 3.2d. The checkpoint for task 2 gets restarted, but the checkpointed task does not receive a restart. This means that the task for iteration 3 now receives a restart instead of a kill since its parent is not in the restart/kill chain, and it immediately spawns off a new task 4. We see that checkpointing is no longer causing processors to remain idle.

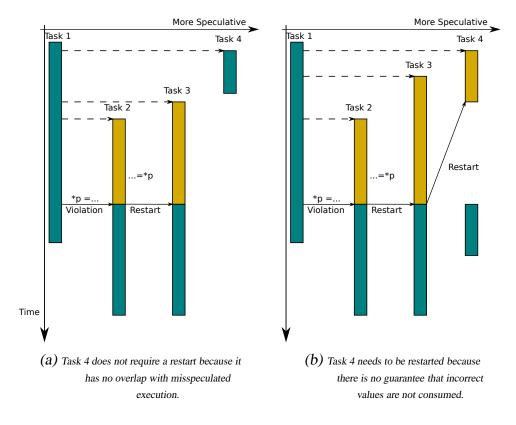

Going further, not all more speculative tasks need to even be restarted. A given task requires a restart only if it has overlap with misspeculated execution<sup>4</sup>. This observation has previously been made by Colohan et al. (8). In that work, timestamps are tracked to compare the start time of a task receiving a violation with the end time of more speculative tasks. A more speculative task is only restarted if its end time is later than the start time of the task receiving the violation.

We now extend the restart/kill mechanism to keep track of task start and end times. To maintain a temporal ordering between tasks, each task is annotated with a *times-tamp*, which is the value of the system clock when the task begins execution. Since the system studied here is a CMP with closely coupled processors, it is assumed that real time is available to each task, and hence a total ordering can be maintained. In situations where a total ordering cannot be established, the notion of *logical time*, as commonly used in distributed systems, can be employed to establish partial orderings.

<sup>&</sup>lt;sup>4</sup>Strictly speaking, a restart is only required if an incorrect value was forwarded from misspeculated execution. The scheme can be made more precise by tracking forwarded values but we avoid the complexity of that here.

Figure 3.4: Example of selective restart using timestamps.

between tasks.