# An Algebraic Approach to Hardware Description and Verification

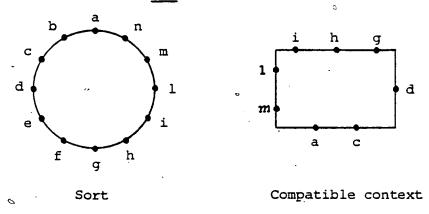

by

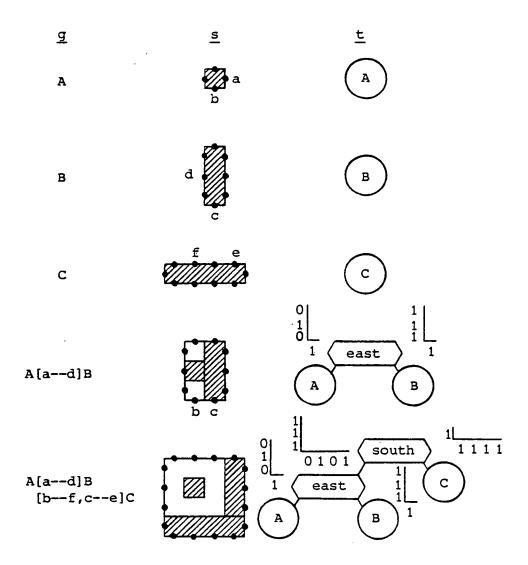

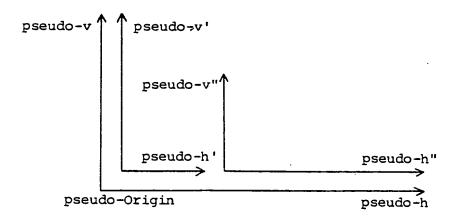

Luca Cardelli

Doctor of Philosophy

University of Edinburgh

1982

#### Abstract

We apply algebraic techniques to various aspects of hardware description and verification, with particular emphasis on VLSI (Very Large Scale Integration) circuit design.

A simple and uniform notation for the description of networks of hardware components is introduced. It is shown how to impose planarity constraints, and how to treat regular and repetitive structures in convenient ways.

The notation is applied to several examples of hardware networks. All these examples constitute different levels of description in the process of translating behavioural specifications into VLSI circuits. A formal semantics is given for the topmost level. Algorithms are given for the translation of purely topological planar stick expressions into metric structures from which layouts can be generated.

The implementation of an experimental VLSI design system is described which uses algebraic concepts to hide detailed geometrical information. Geometric layouts are introduced as an abstract data type in a general purpose functional programming language and considerable advantages over traditional design systems are demonstrated with respect to the user interface.

On the semantic side, two different formal frameworks are defined for the description of systems developing in continuous time. The emphasis is again algebraic, and techniques of both denotational and operational semantics are used. In the operational framework nondeterministic systems can be treated in a natural way, and it is possible to precisely formulate the behaviour of synchronous and asynchronous systems and to study their interactions.

# Acknowledgements

I would like to thank first of all my supervisor, Gordon Plotkin, for his help, encouragement and precise hints in the development of this thesis.

I regard this thesis as much a product of the Edinburgh environment as my own and I find it difficult to sort out all the ideas great and small which have been transmitted to me during these years. I would like to thank Robin Milner and Matthew Hennessy for continual assistance; Mike Gordon, Glynn Winskel, Kevin Mitchell, Igor Hansen and Marc Snir for helpful talks; Jeff Tansley and Irene Buchanan for getting me involved in VLSI; and the "system people" for providing some concreteness and an enjoyable computational environment.

During my stay I have been supported by a scholarship of the Italian National Research Council and a scholarship of the University of Edinburgh.

#### Declaration

This thesis has been composed by myself and the work is my own, under the guidance of my supervisor Gordon Plotkin. Parts of Chapters 1 and 2, produced in different form in collaboration with Gordon Plotkin, appear in [Cardelli 81a]. Chapter 3 is [Cardelli 81b], Chapter 4 is [Cardelli 80] and Chapter 5 is an extended version of [Cardelli 82]. Sections 2.5-2.6 have been submitted for publication.

# Contents

#### 0. Introduction

- 0.1 The Past

- 0.1.1 Microelectronics

- 0.1.2 Design Tools

- 0.1.3 Semantics

- 0.2 This Thesis

# 1. Algebra of Networks

- 1.1 Introduction

- 1.2 Many-sorted Algebras

- 1.3 Net Algebras

- 1.3.1 Sorts

- 1.3.2 Signatures

- 1.3.3 Net Expressions and Laws

- 1.3.4 More on Net Expressions

- 1.4 Net Morphisms

- 1.5 Net Algebras and Flow Algebras

- 1.6 The Initial Net Algebra

- 1.7 Planar Networks

- 1.8 Bunched Networks

- 1.9 Planar Bunched Networks

- 1.10 Molecules, Hypercubes, Mosaics and Klein Bottles

- 1.11 Main Example: The Foster & Kung Pattern Matcher

- 1.12 Appendix: Some Proofs Needed for the Initiality Theorem

# Její

- 2. Hardware Networks for VLSI

- 2.1 Introduction

- 2.2 Layouts

- 2.3 Clocked Networks

- 2.3.1 Clocked Transition Algebra (CTA) Expressions

- 2.3.2 Main Example

- 2.3.3 Formal Semantics of CTA

- 2.3.4 Semantics of the Main Example

- 2.4 Connector-Switch-Attenuator (CSA) Networks

- 2.4.1 The Value Domain

- 2.4.2 Connectors, Switches and Attenuators

- 2.4.3 Basic CSA Circuits

- 2.4.4 Static Semantics of CSA

- 2.4.5 Main Example

- 2.4.6 From CTA to CSA

- 2.5 Stick Networks

- 2.5.1 Sticks

- 2.5.2 Stick Expressions

- 2.5.3 Examples

- 2.6.4 From CSA to Sticks

- 2.6 Grid Networks

- 2.6.1 Grids

- 2.6.2 Discrete Stretch Transformations

- 2.6.3 Normal Grid Composition

- 2.6.4 Grid Expressions

- 2.6.5 Grid Recomposition

- 2.6.6 From Sticks to Grids

- 2.6.7 From Grids to Layouts

# 3. Sticks & Stones

- 3.1 Introduction

- 3.2 Pictures

- 3.2.1 Forms

- 3.2.2 Restriction

- 3.2.3 Renaming

- 3.2.4 Composition

- 3.3 Bunching

- 3.4 Iteration

- 3.5 Paths and Geometric Renaming

- 3.6 Figures

- 3.7 Commands

- 3.8 Modules and Externals

- 3.9 Efficiency

- 3.10 Conclusions

- 3.11 Syntax

# 4. Analog Processes

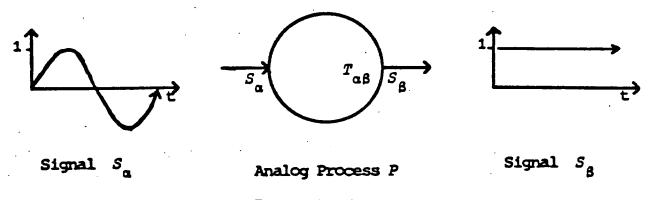

- 4.1 Introduction

- 4.2 Analog Processes

- 4.3 An Algebra of Analog Processes

- 4.3.1 Composition

- 4.3.2 Restriction

- 4.3.3 Renaming

- 4.4 A Denotational Model

- 4.5 Feasibility

- 4.6 Expressibility

- 4.7 Indeterminacy

- 4.8 Flip-Flops

- 4.9 Conclusions

# 5. Real Time Agents

- 5.1 Introduction

- 5.1.1 Methodology

- 5.1.2 The Action Monoid

- 5.1.3 Time

- 5.2 Deterministic Agents

- 5.2.1 Signature

- 5.2.2 Operational Semantics

- 5.2.3 Observation

- 5.2.4 Equivalence

- 5.2.5 Algebraic Laws

- 5.2.6 Determinacy

- 5.3 Nondeterministic Agents

- 5.3.1 Signature

- 5.3.2 Operational Semantics

- 5.3.3 Algebraic Laws

- 5.3.4 Combined Calculus

- 5.4 Communication

- 5.4.1 Restriction

- 5.4.2 Morphisms

- 5.4.3 Delays

- 5.5 Recursion

- 5.6 Indefinite Actions and Delays

- 5.7 Synchronising on Non-Synchronous Input

- 5.8 An Asynchronous Rising Edge Counter

- 5.9 Descriptive Operators

# 6. Conclusions

- 6.1 Achievements and Future Work

- 6.2 The Future

- 6.2.1 VLSI

- 6.2.2 Design Tools

- 6.2.3 Semantics

Appendix I. Syntax Description Notation

Appendix II. Table of Symbols

References

#### 0. Introduction

#### 0.1 The Past

We begin with a review of those recent developments in the fields of microelectronics, design tools and semantics which are relevant to this thesis.

#### 0.1.1 Microelectronics

During the past few years, the steady progress in microelectronics has reached a point where completely untrained people can be taught, in the span of few weeks, to conceive and design highly complex hardware systems.

This fact may come as a great surprise to two categories of people. On the one side professional hardware designers have seen the complexity of systems growing beyond any control, to the point where the technology is clearly more powerful than the ability to use it. It seems then unlikely that untrained people might do better.

On the other side the average (computer) scientist who has been trained to think that "the hardware is made by the engineers", suddenly discovers that in a couple of months he can design and receive, his pet architecture; one the big manufacturers had thoughtfully refused to consider. However, it may seem unlikely that he can really do it if those expert manufacturers would not.

The fact is that, until recently, the problem of managing the complexity of VLSI (Very Large Scale Integration) systems was not adequately considered. Design methodologies were developed which encouraged circuit efficiency at a very low level, often at the expense of global optimisations and disregarding elegance and

structure. The work done by Carver Mead, Lynn Conway and their collaborators [Mead 80] has completely changed this picture. Structured methodologies have proven to be more reliable, to extend smoothly to big systems and in many cases to provide more efficient and totally unexpected solutions. The simplicity reintroduced by structured methodologies allows people to learn quickly and to quickly produce non-optimal but working devices. In many cases the achievements of these newcomers [Conway 80] sound astounding with respect to average industrial products [Steele 80, Rivest 80, Masumoto 80]. Structured methodologies are now beginning to be systematically used by big manufacturers, and the results are equally encouraging [Lattin 81, Mudge 81].

#### 0.1.2 Design Tools

Another key contribution has been the definition of a clean interface between design and fabrication [Mead 80]. While any such interface necessarily introduces some inefficiency, it allows the designer to ignore most of the inessential aspects of the fabrication process. Moreover it seems sensible to expect that in future fabrication processes will be designed to match this kind of interface, so that many of the inefficiencies will disappear [Mikkelson 81].

The coincidence of structured methodologies, clean interfaces and high level of integration, has inspired a sudden and rapidly spreading interest outside the microelectronic environment. It is most fortunate that this sudden "discovery" of VLSI, comes at a moment where the traditional architectures and design techniques used in microelectronics are showing their limits, and where there is a great need for complexity management techniques.

In fact, the management of complexity has always been the main

problem in software engineering and programming language design, and structured methodologies are now simply common sense in those areas. The hope is that as a result of the experience gained in software we shall not have to wait long before getting very effective high level tools for hardware design. A subordinate hope is that we shall be able to completely omit the "batch" and "FORTRAN" stages of design tools.

An interesting parallel can be made between the state of hardware design today and the state of software design in the fifties and early sixties. Layouts (the end-product of any VLSI design activity) have many of the characteristics of machine language programs. They are powerful enough to fully exploit the technology and can lead to great efficiency when used at the lowest level. On the other hand they are inscrutable, and difficult to modify, maintain and debug, and very prone to trivial and repetitive (yet fatal) errors. The information they convey is inflexible and absolute, and in general they encourage programming styles which lack clarity and elegance.

Most of the VLSI design tools today are based on layouts. As a consequence of the low level notations used, many of these are concerned with recovering from errors which have already been made, or with recovering structure which has been lost at some previous stage of design.

For example, design rule checkers are needed because people are allowed to draw wires of the wrong thickness, or to put transistors in the wrong places. Again, electrical rule checkers are needed because the low level of primitives allows designers to combine them in meaningless ways. And again, node extractors are needed because the initial description of the circuit is not semantically structured, or because the structure has been flattened out by some

other tool.

Other tools are hampered by tasks which are not their own.

Graphics editors are sometimes equipped for checking design rules,

or even electrical parameters. Simulators are used in the detection

of errors which are clearly syntactical, such as wires which fall

short of their intended contact points, switches connected in

meaningless ways, transistors introduced by accident, power supply

lines disconnected or wrongly connected, etc.

Recently, "assembly languages" have been devised ([Locanthi 78] and many others), where symbolic names and locations can be used instead of bare numbers. High level control structures can be used and syntactic correctness checks can be performed so that some of the syntactic properties of the output, like wire thickness, are guaranteed to be correct. The primary task of these tools is however to describe layouts, not computations, and they are strongly process (or process-class) dependent because they aim to give full access to the lowest level of description. For this reason they should still be considered to be low-level tools.

Continuing the analogy, why cannot we have compilers? The features of a general purpose silicon compiler are easily listed: it should be process-independent, it should be able to express any range of architectures at the behavioural level, and given a syntactically correct input it should always produce syntactically correct code. We should be able to formally describe the compiler (i.e. no "hacking") and maybe prove its correctness, or at least believe in it!

The production of a silicon compiler is a very complex problem.

We know what the output should be, namely layouts, but we do not know how to produce it and we do not have any clear ideas about what

the input should look like. The choice of a convenient input notation might deeply influence (and maybe simplify) the translation process, and conversely translation techniques may impose restrictions on our notation. It is not clear whether we should first fix the notation or study the translations, or proceed by attempts in both directions until some satisfactory meeting point is reached.

As to the linguistic problems, there is no doubt about the advantages of a high level notation, as far as programming is concerned. For example in many cases high-level language programs can be debugged by typechecking and proof-reading, while "tracing" (which corresponds to simulation) is essential for assembly language programs. Moreover, if we consider the elegance of, for example, a one-pass Pascal compiler with respect to an n-pass macro-assembler, we can also clearly see the implementational advantages of a well structured and powerful notation.

The problem of compiling into two-dimensional structures, even if frequently found in design automation problems, seems to be rather new in formal language and compiler construction theory. There is a little recent interesting work [Floyd 80, Forster 81] at the formal language end. Pioneering work towards full-scale silicon compilers is reported in [Johannsen 79] and [Rupp 81]. Unfortunately the vast literature in hardware routing and placement problems does not seem to apply very directly to VLSI; indeed for compilation it is not enough use techniques like general routers which often only solve 95% of each problem.

On the positive side, a series of remarkable design tools for VLSI has emerged in recent years. Many of these tools share many of the criticisms we have expressed, but they are indisputable milestones in their area.

Some design tools computerise boring hand-drawing activities, by using interactive graphics displays. In this class we can mention, for layouts ICARUS [Fairbairn 78], for stick diagrams STICKS [Williams 78] culminating in REST [Mosteller 81], and for cell composition the Chip Assembler [Tarolli 80].

The prototypical text-oriented system is LAP [Locanthi 78], which embeds a very simple graphical notation [Sproull 80] in a general purpose high-level language (this idea comes from standard graphics techniques [Newman 79]). The crudeness of the graphics primitives is compensated for by the ability to use the control constructs of the language for parameterisation and abstraction, achieving an effectiveness far greater than graphics editors (but with very little user-friendliness).

More ambitious systems try to integrate several tools [Buchanan 80], often into a workstation with special purpose programming languages or packages and sophisticated graphic interfaces. On the layout level we have the LISP-based DPL [Batali 81], and on the sticks level MULGA [Weste 81]. Both these systems are truly remarkable, even if the complexity of the former seems excessive. Many similar systems are now being developed; they mostly use a personal computer together with a high resolution colour display and a pointing device.

#### 0.1.3 Semantics

A very sharp distinction should be made between the means and ends of formal description and formal verification. These two activities are often inversely proportional, in the sense that very powerful description systems can be so detailed and complicated as not to allow any general view of the problems (for example, consider

quantum mechanics as a way of describing an armchair: can we formally verify that the armchair is comfortable?). Conversely we might have verification systems which at a certain level of abstraction allow us to easily verify any property we want, but which are unable to describe part of the realities we are interested in (suppose we have a nice theory of armchairs and soft materials; what happens if we ship the armchair to a black hole?). Unfortunately one can also come up with questions which require both powerful descriptions and flexible theories (if we do send the armchair to the black hole, will it keep being comfortable?), and the problem is then to maximise the usefulness of the whole system, and not just the descriptive or the proof-theoretical part.

In mathematics some sort of optimality has been reached, if we consider for example how analysis merges smoothly into topology. Not so in computer science; the considerable descriptive success of denotational and algebraic semantics has not yet ledî to satisfactory theories of programs (even if it has led to satisfactory theories of models). Properties which are considered obvious to programmers escape, on large programs, any verification or even formalisation.

It is well known that concurrent systems are much more difficult to describe and verify than sequential ones. In this field, denotational and algebraic semantics found descriptive difficulties, while powerful descriptive systems like Petri nets do not seem to offer striking advantages for verification purposes.

From this point of view, hardware systems seem to summarise many difficult problems in semantics; they are of extensively concurrent nature, and the behaviour of even the simplest components is difficult to describe and context-dependent.

Hardware is semantically unexplored at intermediate levels. For low level hardware, the main semantic description available is device physics, which is not very helpful when the number of devices exceeds one. Very powerful techniques have been developed in electronics for the study of analog circuits, but are not of general application to digital circuits. For gate-level hardware, we have satisfactory theories like switching theory (for small combinational systems), and automata theory (for larger sequential systems) which however do not work very well for complex systems built out of many parts, like microprocessors. Very little exists between device physics and switching theory, which is unfortunately exactly what we need for low-level VLSI. Moreover automata theory is not very suitable for studying interconnected networks of processors, which is what we need for high-level VLSI.

Part of these problems, which are common to concurrency problems, have been attacked by the use of operational techniques [Plotkin 81], which can conveniently describe concurrency, algebraic techniques [Milner 80], which lead to flexible proof systems. Recent work on synchronous concurrent systems [Milner 81] (which extends smoothly to asynchronous systems) seem to particularly well suited both to hardware description verification. most hardware 88 systems today are synchronous.

#### 0.2 This Thesis

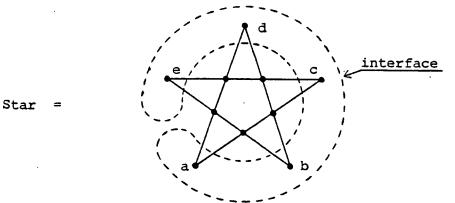

The first chapter of this thesis is dedicated to the task of providing a simple and uniform notation for the description of networks of hardware components. The approach is algebraic in nature and derives from work on the syntax of concurrent systems [Milner 79]. After a general introduction to many-sorted algebras (section

1.2), a "pure" formalism of net expressions is introduced in section 1.3, together with a set of equational laws expressing the equivalence of networks. Networks are regarded as graphs with an interface, and together with net expressions they form what we call a net algebra (net algebras are compared to Milner's flow algebras in section 1.5). In section 1.6 we characterise the initial net algebra in terms of particular kinds of graphs, and we prove soundness, completeness and definability theorems with respect to the net expressions and laws. Some additional structure is then imposed on net algebras in view of the use we shall make of them in chapter 2. Section 1.7 treats planar networks, and sections 1.8 and 1.9 introduce the idea of a bunch (a way of structuring interfaces) which is essential when programming in net algebras. Some bizarre examples of net algebras are given in section 1.10 in order to explore the power of the formalism, while section 1.11 introduces a hardware network which will be used as an example throughout chapter 2.

The second chapter applies the notation developed in the first chapter to several examples of hardware networks. All these examples constitute different levels of description (i.e. different net algebras) in the process of translating behavioural specifications into VLSI circuits. Even if we occasionally attack the problem of algorithmic translations into two-dimensional structures, we concentrate in general on formalisms which can be considered as prototype textual languages for silicon assemblers and compilers, on much the same lines as [Rem 81]. This leaves uncovered a wide area of research, namely graphical languages and graphical interaction. Although it is rather natural to imagine graphical counterparts for some of the textual programming constructs we present, it is not clear how to define purely graphical systems of the same power as

text-oriented systems (see [Trimberger 79] for an effort towards integrated text-graphics systems). This is mostly due to the lack of a good graphical analog for parameterisation. Hence, even if we think that graphical interfaces are essential to easily usable systems, we generally concentrate on textual expressions denoting graphical entities.

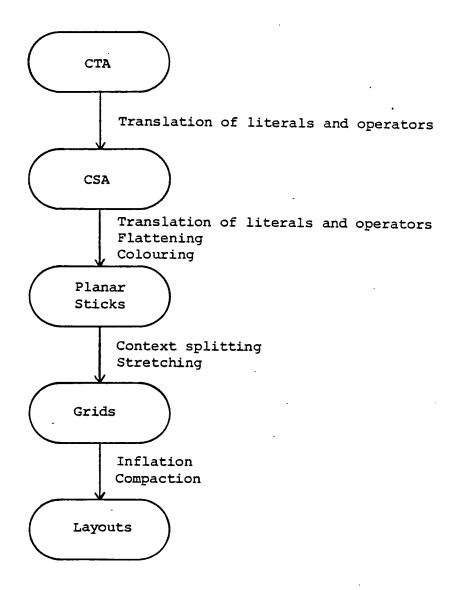

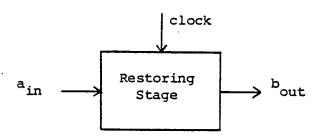

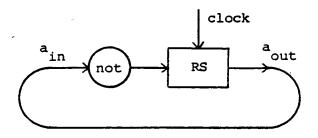

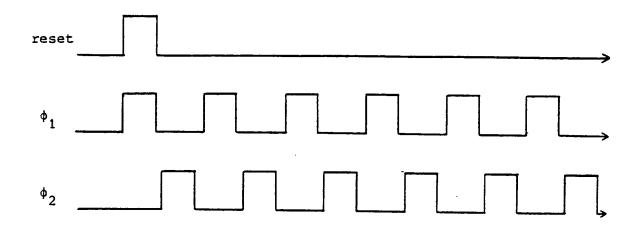

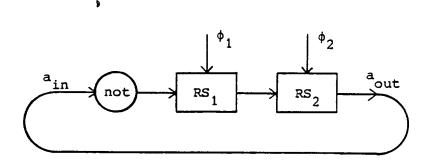

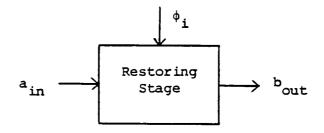

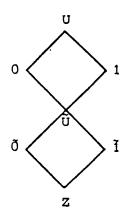

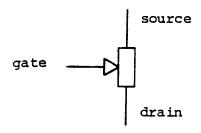

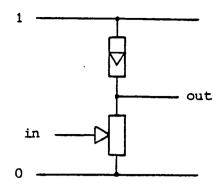

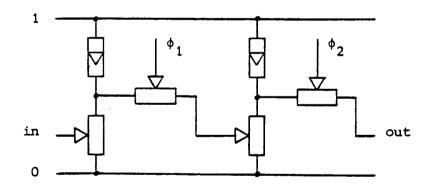

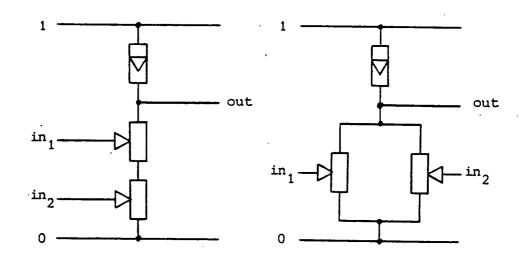

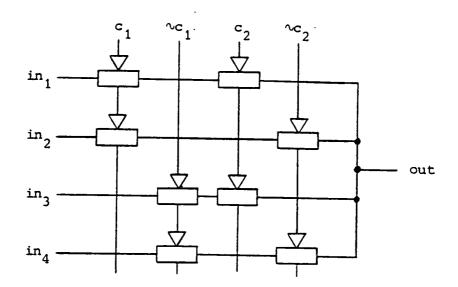

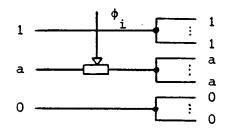

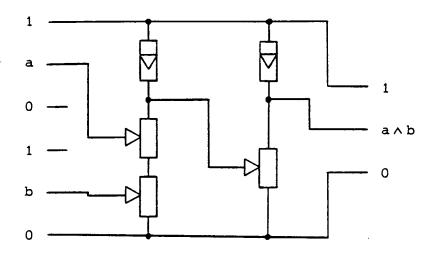

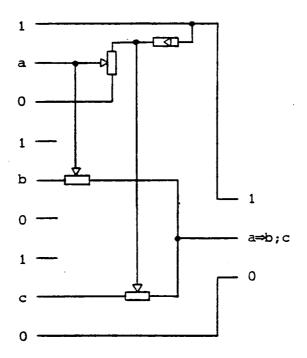

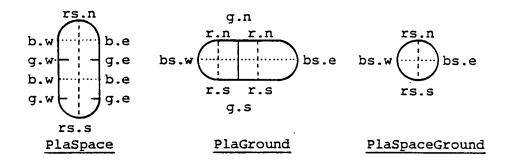

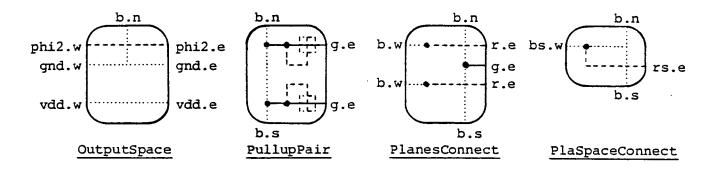

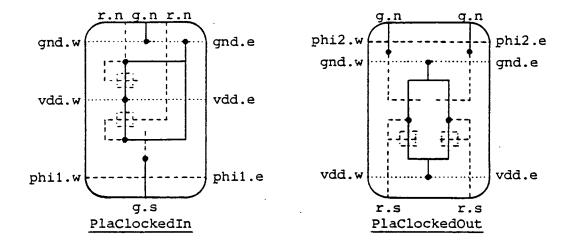

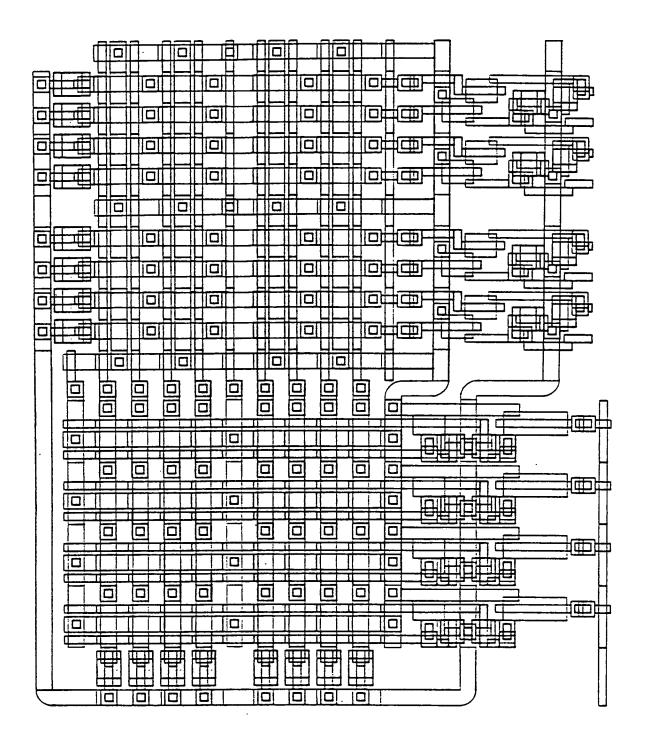

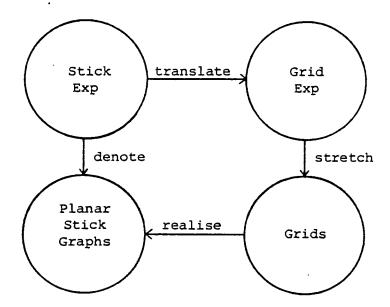

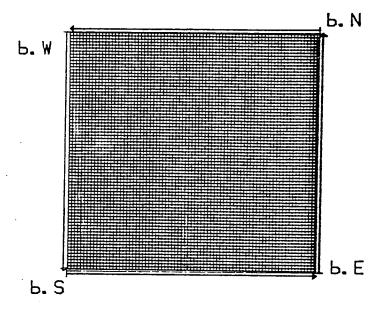

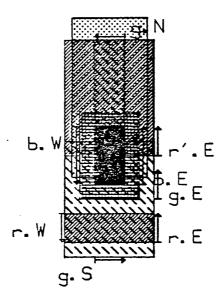

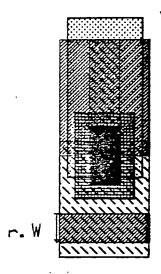

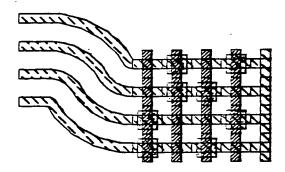

The topmost level of description, called Clocked Transition Algebra (CTA, section 2.3), is concerned with the behavioural specification of synchronous systems. A formal semantics of CTA is given by a translation to Synchronous CCS [Milner 81]. Section 2.4 describes the CSA model of switch-level hardware [Hayes 81, Bryant 81] and gives a semantics to the stable CSA circuits. A translation mapping every CTA expression into a CSA circuit is then shown. In section 2.5 we work with (planar) stick diagrams, showing several examples of net algebra programming activity. A translation from CTA to sticks is briefly sketched. Section 2.6 treats grids, which are stick diagrams disposed on orthogonal lines. The algebra of grids is very important as an intermediate step in the translation of purely topological stick diagrams into geometrical layouts. An efficient stretching algorithm for grids is developed; then a translation from sticks to grids is described, which has the property of always succeeding in every admissible context (a context expresses constraints on the position of connection points on a rectangular boundary). Finally we comment that translations from grids into layouts have already been experimented with (e.g. [Mosteller 81]).

The third chapter describes the implementation of an experimental VLSI design system (constituting what is generally called a <u>silicon</u> assembler) where most of the geometry-related characteristics of layouts are hidden by the use of algebraic operations. In section 3.2 we introduce the basic data type of pictures (layouts), which is

embedded in a general purpose programming language [Gordon 79] allowing parameterisation and conditional assemblies of pictures. Bunches, and their use in association with an iteration construct, are described in sections 3.3 and 3.4. Section 3.5 deals with an interpretation of a net algebra operator which embodies a form of geometrical river routing. The remaining sections describe various aspects of the implementation.

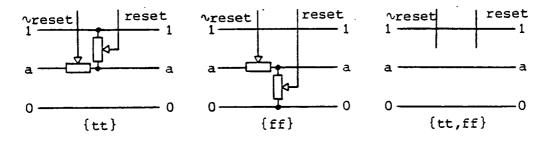

The purpose of the fourth and fifth chapters is to provide a framework where formal proofs concerning the low level behaviour of hardware systems can be carried out. The fourth chapter describes a formalism in which systems developing through continuous time can be expressed. The emphasis is again algebraic, and algebraic laws are formulated which express the behaviour of such systems (section 4.3). Techniques of denotational semantics are used to provide a deterministic model (section 4.4); the attempt to extend the treatment to nondeterministic systems encounters technical difficulties and another approach is used in chapter 5. A discussion about the expressive power of this formalism is contained in sections 4.5, 4.6 and 4.7. Section 4.8 is dedicated to an example (flip-flops) which exhibits metastable behaviour.

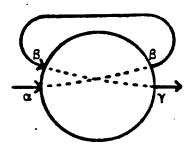

The semantic techniques used in chapter 5 are operational, with the advantage that a semantics can be given to nondeterministic systems in a natural way. This chapter follows [Milner 81] and can be regarded as an extension of that work where a discrete time domain is replaced by a continuous one. Section 5.1 introduces the main ideas and the operational semantics methodology. After a section studying deterministic systems (5.2), nondeterminism is introduced in two orthogonal ways in section 5.3 by a choice operator and an indefinite-duration operator. Communication is treated in section 5.4 and recursion in section 5.5, where some

difficulties due to the density of time have to be solved. The following three sections (5.6, 5.7 and 5.8) discuss the complex interactions between synchronous and asynchronous systems, and section 5.9 gives a way of characterising synchronous, non-synchronous and asynchronous systems.

Appendix I introduces the notation used for expressing the syntax of languages, and appendix II contains a list of the symbols used through this thesis.

# 1. Algebra of Networks

#### 1.1 Introduction

A network is to a first approximation a finite graph. Our main concern is with structured network design, and we are interested in methods and notations for building and analysing networks in a hierarchical fashion. Hence the first problem we have to solve is how to express finite graphs, considered as unstructured sets of arcs, in some orderly and structured way.

The simplest way of exhibiting a graph is of course by displaying it. This kind of presentation is expressive and immediately understandable by humans, but unfortunately it also has several disadvantages.

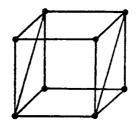

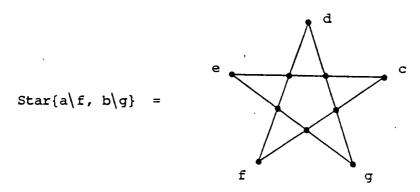

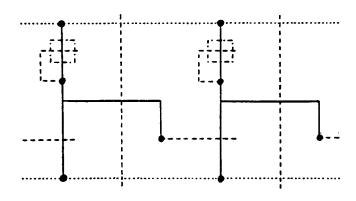

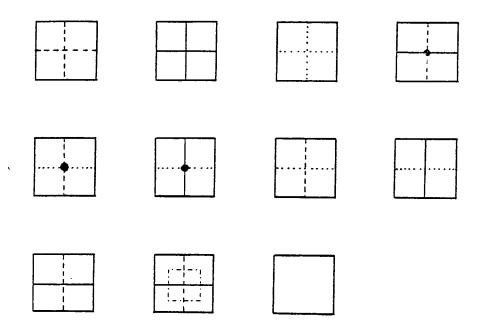

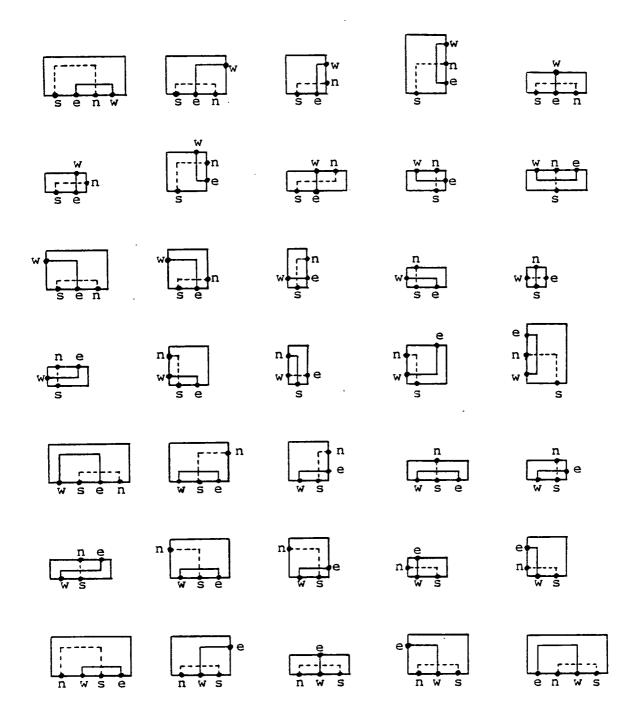

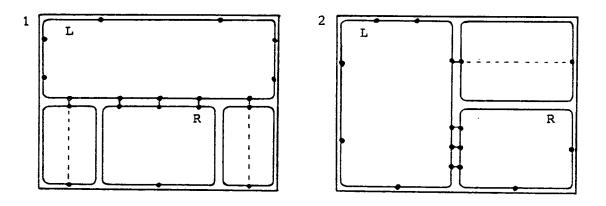

Figure 1.1 A graph

First of all the structure of the graph is not evident in its picture, i.e. we cannot tell how it was built; the mere picture of the graph hides the intended way of looking at a particular graph among the several ways in which the graph can be constructed. Hence some structure (graphical or otherwise) has to be superimposed on the graph in order to understand it in terms of its components.

Figure 1.2 Decompositions

Second, graphical notation is not suitable for direct mathematical manipulation. Mathematical coding has to be used in order to get the benefits of formal treatment, and an effort should be made to keep the coding not too different from the intended structure of the coded object, otherwise an obscure theory will result.

Third, graphical notation does not make a good programming language; not because it is difficult to "type it in" (this can be overcome by graphical editors) but because the usual programming language control structures and parameterisation mechanisms are not easily definable on pictures.

Fourth, and finally, no matter how we express them, graphs may have to be represented in terms of data structures in a computer, and operations have to be carried out upon them; then this is just another aspect of the problem of finding a non-graphical notation for manipulating graphs in useful ways.

Our aim is then to develop a notation for structured graphs which is formally tractable, expressive enough to be used as a programming language, and easily convertible into useful data structures. The central idea is to have an abstract data type of networks over which certain operations can be performed (particularly composition of

subnetworks) and which can be easily translated into different data types for different purposes. We formalise these ideas in an algebraic framework where abstract types are algebras and easy translations are different shades of algebra morphisms.

This chapter is mostly technical; the reader is advised to skim it in case of difficulties and to come back to it when needed while reading chapter 2. Sections 1.10 and 1.11 contain examples which give some motivation for the notation introduced here.

# 1.2 Many-sorted Algebras

An Algebra is a set together with some operations on its elements. Intuitively the base set of an algebra is a data type, and the operations are the basic operations allowed on that data type; other operations can be defined from the basic ones [Gratzer 79].

A many-sorted algebra is an extension of this idea, where we have several sets instead of one (hence several data types) and typed operations which take arguments from and produce results in these sets [Goguen 78]. The extension from single-sorted to many-sorted algebras is conceptually very simple, but makes the technical treatment considerably heavier. In fact operations have to be indexed by their type, and we have to distinguish operators having the same name but belonging to different algebras. All this typing and naming information is gathered into the notions of sort and signature.

A sort is a data-type name; sorts will be denoted by the letter s, sets of sorts by S and lists of sorts by w & S\* (with [] the empty list).

Definition 1.1 A signature  $\Sigma$  is a pair  $\langle S, \Sigma \rangle$  where S is a set (of sorts) and  $\Sigma$  is a family of sets (of operator symbols) indexed by S\*XS. An operator symbol  $a_{w,S} \in \Sigma_{w,S}$  has rank (or functionality) w,s arity w and sort s  $\square$

Example: Boolean  $\Sigma = \langle S = \{bool\}, \\

\Sigma = \{ \Sigma_{[],bool} = \{true,false\}, \\

\Sigma_{bool,bool} = \{ \sim \}, \\

\Sigma_{bool,bool} = \{ \vee, \wedge \}, \\

\Sigma_{w.s} = \emptyset \text{ for any other w,s } \rangle$

We denote by  $X = \{X_s \mid ssS\}$  a set of sets of variables of sort s. Variables are all distinct, and they are distinct from operator symbols and punctuation.

Definition 1.2 A  $\Sigma(X)$ -expression is a syntactic expression built from the operator symbols of  $\Sigma=\langle S,\Sigma\rangle$ , the variables of  $X=\{X_S\mid s\in S\}$  and the distinguished symbols "(", ")" and ","; more precisely, expressions are all and only the strings of symbols obtained by the following rules:

- If x is a variable of sort s, then x is an expression of sort s.

- If  $e_1 cdots e_n$  are expressions of sort  $s_1 cdots s_n$   $(n \ge 0)$

and

$$a_{s_1...s_n,s}$$

$\epsilon \sum_{s_1...s_n,s}$  then:

$a_{s_1...s_n,s}(e_1,...,e_n)$

is an expression of sort s

(where, for n=0, a<sub>[],s</sub>() has sort s)

When there is no ambiguity subscripts are omitted, so that we simply write  $a(e_1, ..., e_n)$ .

Example: Boolean expressions

The following are  $\sum (X)$ -expressions, where  $\sum$  is the boolean signature and  $X = \{X_{bool} = \{x,y\}\}$ .

I

true()

$\sim (\Lambda(x, V(false(),y)))$

We use the following notation for cartesian products of sets:

$$A_{[\cdot]} = \{[\]\}$$

$$A_{w} = A_{s_{1} \dots s_{n}} = A_{s_{1}} \times \dots \times A_{s_{n}}$$

Definition 1.3 A  $\Sigma$ -algebra  $\underline{A}$  (with  $\Sigma = \langle S, \Sigma \rangle$ ) is a pair  $\langle A^*, A \uparrow \rangle$  where  $A^*$  is an S-indexed set of sets  $A_s$  and  $A \uparrow$  is an S\*XS-indexed set of maps  $A_{w,s} \colon \Sigma_{w,s} \longrightarrow (A_w \longrightarrow A_s)$  associating a function  $A_{w,s}(\alpha_{w,s}) \colon A_w \longrightarrow A_s$  with each operation symbol  $\alpha_{w,s} \in \Sigma_{w,s}$  []

Each  $A_s$  is called the carrier of  $\underline{A}$  of sort s; each  $A_{w,s}(a_{w,s})$  is called the operator of  $\underline{A}$  named by  $a_{w,s}$ , and is also denoted by  $\phi_{a_{w,s}}^A$ . When there is no ambiguity  $\phi_{a_{w,s}}^A$  is also written  $\phi_{a_{w,s}}$ ,  $\phi_{a}^A$ ,  $\phi_{a_{w,s}}^A$  or even a.

#### Example:

Expressions are a very important example of algebras:

Definition 1.4  $T_{\Sigma}(X)$  (where  $\Sigma = \langle S, \Sigma \rangle$ ) is the  $\Sigma$ -algebra with:

- Carriers: the set of  $\Sigma(X)$ -expressions of sort seS.

- Operations: the mappings

$$\phi_{\alpha_{s_1...s_n,s}} : e_1...e_n \longrightarrow \alpha_{s_1...s_n,s}(e_1,...,e_n) \quad (n \ge 0)$$

for each  $\alpha_{s_1...s_n,s} \in \Sigma_{\alpha_{s_1...s_n,s}}$

and expressions  $e_1...e_n$  of sort  $s_1...s_n$

(for n=0 we have  $\phi_{\alpha_{[],s}}$ : []  $\longleftrightarrow \alpha_{[],s}()$ )

0

It is easily verified that  $T_{\Sigma}(X)$  is really a  $\Sigma$ -algebra.

We finally include the definition of homomorphism and of signature morphism which are the formal basis for the translations which we shall discuss in Chapter 2 (even if those translations will only approximate the idea of homomorphism).

Definition 1.5 A  $\Sigma$ -homomorphism of  $\Sigma$ -algebras

$$h: \underline{A} \longrightarrow \underline{B}$$

is an S-indexed set of maps  $h_s: A_s \rightarrow B_s$  such that  $h_s(\phi_{\alpha_w,s}^A(a_1,\ldots,a_n)) = \phi_{\alpha_w,s}^B(h_{s_1}(a_1),\ldots,h_{s_n}(a_n))$  for all  $s \in S$ ,  $w=s_1\ldots s_n \in S^*$  and  $a_1 \in A_{s_1},\ldots,a_n \in A_{s_n}$

Definition 1.6 A signature morphism  $\rho$  from  $\langle S, \Sigma \rangle$  to  $\langle S', \Sigma' \rangle$  is a pair  $\langle f, g \rangle$  consisting of a map  $f \colon S \longrightarrow S'$  and a family of maps

$$g_{w,s}: \Sigma_{w,s} \rightarrow \Sigma'_{f^*(w),f(s)} \mathbb{Q}$$

A signature morphism is a (possibly many-to-one) renaming of sorts, together with a compatible (possibly many-to-one) renaming of operator symbols.

Theorem 1.1 For every  $\Sigma$ -algebra A and map h: X  $\longrightarrow$  A (i.e. family  $h_s\colon X_s \to A_s$  for seS) there is a unique  $\Sigma$ -homomorphism  $h^*\colon T_\Sigma(X) \to A$  such that

$$h * o I_X = h$$

where  $I_X: X \to T_{\sum}(X): x \longleftrightarrow x$  is the injection of generators

The above theorem states the existence of a unique homomorphism  $h^*$  from  $\Sigma(X)$ -expressions  $(T_{\Sigma}(X))$  and environments for free variables  $(h: X \to A)$  into any  $\Sigma$ -algebra A. This homomorphism is often called evaluation or interpretation of an expression e in an algebra, and  $h^*(e)$  is called the (because of uniqueness) value of e in A (with respect to an environment).

# 1.3 Net Algebras

Refining our idea of network, we can say that a network is a finite graph with an interface. Interfaces are an abstraction mechanism; they contain all the information about the network which is needed and visible from "outside", while hiding the internal structure. For example, syntactic checks can be performed on network operations on the basis of the information contained in the interfaces they operate onto; operations are guaranteed to be meaningful if they satisfy these syntactic checks.

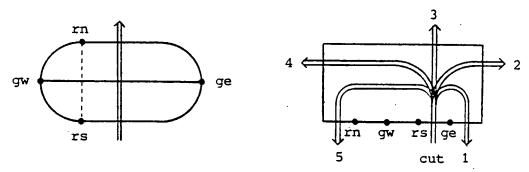

Figure 1.3 A graph with an interface

The interface of a network consists of ports which have a name and a type. Names are used to denote edges of the network (i.e. connection points), and types guarantee the consistency of certain operations. The most important use of interfaces is in joining networks together into larger networks; the join is done by naming the ports to be connected, provided that there are no name clashes and that the types of the connected ports match.

#### 1.3.1 Sorts

Formally, an interface is a sort. Given a set Types of types and a set PortNames of (port) names (with a,b ranging over names and A,B,C ranging over finite sets of names), a sort is a map s:  $A \rightarrow \text{Types with } \lceil s \rceil \stackrel{\triangle}{=} A$ ; hence s(a) shows the type of the port named a. We say that two sorts s,s' are compatible if their common port names have the same type, i.e. if  $s \nmid B = s' \nmid B$ , where  $B = \lceil s \rceil a \lceil s' \rceil$ .

# 1.3.2 Signatures

Networks are built out of a given set L of basic components called literals (nullary operators). Every literal 1  $\epsilon$  L has a sort given by  $\lambda(1)$ .

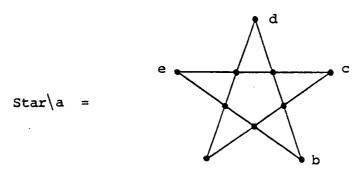

The unary restriction operator, \a, removes the name a from the sort of a network. For every a and s we have an operator \a:  $s \rightarrow s'$

where  $\lceil s' \rceil = \lceil s \rceil \setminus \{a\}$  and s'(a') = s(a') for a' in  $\lceil s' \rceil$ . Restriction is a postfix operator, and we abbreviate  $x \setminus a_1 \dots \setminus a_n$  to  $x \setminus a_1 \dots a_n$ .

Figure 1.4 Restriction

The unary renaming operator,  $\{r\}$ , changes the names of a sort without changing the port types. For every sort s and bijection r:  $\lceil s \rceil \rightarrow A'$  we have an operator  $\{r\}$ :  $s \rightarrow s'$  where  $s' = s \circ r^{-1}$ . Restriction is postfix and we write  $\{a_1 \setminus b_1, \ldots, a_n \setminus b_n\}$  for r when  $\{a_i\} \subseteq A$ ,  $r(a_i) = b_i$  and r(a) = a for a not in  $\{a_i\}$  (hence  $\{\}$  is the identity renaming).

Figure 1.5 Renaming

The binary composition operator,  $| \cdot \rangle$ , composes two networks together identifying and then forgetting their common port names. For every compatible pair of sorts s,s' we have an operator  $| \cdot \rangle$ : s,s'  $\longrightarrow$  s" where s" = s\thetas': A\theta A' (we use \theta for symmetric difference: A\theta A' = (A\A') \(\mathbf{u}(A'\A)\), and s\thetas' = s\(\frac{1}{2}(A\A') \(\mathbf{u} s'\frac{1}{2}(A'\A)\). Composition is an infix operator associating to the left.

A useful derived operation is explicit composition, [r], which composes two networks by linking the ports which are explicitly mentioned in a bijection r. The operator [r]:  $s,s' \rightarrow s''$  with r:  $A \rightarrow A'$ ,  $B=\lceil s \rceil \setminus A$  and  $B'=\lceil s' \rceil \setminus A'$ , is well defined iff

- (i) AC[s] and A'C[s']

- (ii) s(a) = s'(r(a)) for every a in A (type restriction)

- (iii)  $B A B' = \emptyset$  (no name clashes)

Then  $\lceil s'' \rceil = B \cup B'$  and s''(b) is s(b) if  $b \in B$  and s'(b) otherwise.

Under these conditions we define

$$e[r]e' \triangleq e\{ruid_B\}|e' = e|e'\{r^{-1}uid_B\}|e'$$

Explicit composition is infix and left associative; e[r]e' will be written as  $e[a_1-b_1,...,a_n-b_n]e'$  for  $\langle a_i,b_i\rangle$   $\varepsilon$  r.

Figure 1.6 Composition

# 1.3.3 Net Expressions and Laws

From the signature of a net algebra, and for a given set of literals, we can construct a corresponding set of net expressions (ranged over by e):

- literals are expressions

- if e,e' are expressions

then (e/a), (e{r}) and (e|e') are expressions.

Parentheses will often be omitted.

The operators we have so far defined must obey a set of laws

called the net laws, which complete our definition of net algebras. We write  $\sigma(e)$  for the sort of e, and we require the following equations to hold whenever they are well-formed according to our previous remarks.

Derived laws for explicit composition are as follows:

and  $\lceil r'' \rceil = \lceil \sigma(e) \rceil n \lceil \sigma(e') \rceil$

[[]]

$$e[r]e' = e'[r^{-1}]e$$

[[][]]  $(e[id_{A_1}]e')[id_{A_2}uA_3]e'' = e[id_{A_3}uA_1](e'[id_{A_2}]e'')$

whenever all the compositions are well formed

[[][]]  $e[r'or]e' = e[ruid_B][r']e'$

[[][]  $(e[r]e')[a = (e[a)[r](e'[a)) \text{ if } r: A_1 \rightarrow A_2 \text{ and } a \not A_1 uA_2$

[[][]]  $(e'[r]e'')[r'ur''] = (e'[r'ur'_1])[r''oror'_1](e''[r''ur''_1])$

where  $\lceil r \rceil = \lceil \sigma(e) \rceil \backslash \lceil \sigma(e') \rceil, \lceil r' \rceil = \lceil \sigma(e') \rceil \backslash \lceil \sigma(e) \rceil$

# 1.3.4 More on Net Expressions

Net expressions can be used as the kernel of a programming language for networks. We give some definitions which can guide the

implementation of net expressions, particularly regarding their syntactic correctness. A formal syntax for net expressions is introduced, and algorithms are given for checking whether a net expression is well formed and for extracting its sort.

The formal syntax of net expressions is defined here, using the metasyntactic notation of Appendix I:

```

literal ::= ... (depending on the particular algebra)

exp ::= literal |

exp '\' name |

exp '\' {name '\' name / ','} '\' |

exp '\' exp |

exp '\' {name '--' name / ','} '\' exp |

'(' exp ')'

```

Restriction and renaming bind stronger than explicit composition, which binds stronger than implicit composition. Both kinds of composition are left associative.

A sorting e of a net expression e is an assignment of a sort to every subexpression e' of e; for example  $(c_s[a--b]c'_s,)_{s''}$  is a sorting of c[a--b]c'.

A well-sorting of e is a sorting e such that the predicate WellSorted(e) (defined below) is true. We then say that e is well-sorted if it admits a well-sorting e.

٠.

```

WellSorted (1_s) = s = \lambda(1)

WellSorted ((e_s \setminus a)_s, ) = MellSorted(e_s) and s' = s + \lceil s \rceil \setminus \{a\}

```

```

WellSorted ((e_{e}\{a_{i}\}b_{i}\})_{g}) =

WellSorted(e,) and NameBijection({(a,,b,))

and \{a_i\}\subseteq [s] and ([s]\setminus \{a_i\}) \cap \{b_i\} = \emptyset

and s' = (s \downarrow \lceil s \rceil \setminus \{a_i\}) \cup \{\langle b_i, s(a_i) \rangle\}

WellSorted ((e | e',),") =

WellSorted(e,) and WellSorted(e',)

and \forall a \in [s] \cap [s']. s(a) = s'(a)

and s'' = s + (\lceil s \rceil n \lceil s' \rceil) \cup s' + (\lceil s \rceil n \lceil s' \rceil)

WellSorted ((e_s[a_i-b_i]e'_{g'})_{g''}) =

WellSorted(e,) and WellSorted(e',)

and NameBijection(({a;,b;>})

and a, e [s] and b, e [s']

and s(a_i) = s'(b_i) and (\lceil s \rceil \setminus \{a_i\}) \land (\lceil s' \rceil \setminus \{b_i\}) = \emptyset

and s'' = s + (\lceil s \rceil \setminus \{a_i\}) \cup s' + (\lceil s' \rceil \setminus \{b_i\})

NameBijection (\{\langle a_k, b_k \rangle\}) =

i \neq j \Rightarrow a_i \neq a_j, b_i \neq b_i

```

The following procedure, SortOf, computes the sort of a well-sorted net expression. It is easily verified that WellSorted(e) is true, where e is the sorting generated by applying SortOf to all the subexpression of e.

#### 1.4 Net Morphisms

A net morphism is a homomorphism of net algebras. Given two net algebras  $\underline{A}$  and  $\underline{B}$  over the same signature (i.e. over the same set of literals  $\underline{L}$ ), a morphism  $h: \underline{A} \longrightarrow \underline{B}$  is a set of maps

$\{h_s: A_s \rightarrow B_s \mid s \text{ s NetSort}\}$ such that:

# 1.5 Net Algebras and Flow Algebras

Net algebras are modelled on Milner's Flow Algebras [Milner 79]. The main difference is that in flow algebras many-to-many port connections are possible, while in net algebras we have one-to-one connections of ports and connected ports are forgotten in the sort of the result. One-to-one connections seem to reflect more accurately some of our intended applications, particularly in the case of connecting geometric objects. In Chapter 3 for example we define composition so that the connection of two geometric ports does not leave "space" for any other connection, and the connected ports may as well disappear from the sort of the result.

The formal treatment of net algebras shows that the theory and the set of laws we obtain are about as nice as in the case of flow algebras. However, the relationships between the two theories need some further study. On the one hand, it is easy to mimic net algebras in the flow algebra framework; for example the explicit composition e[a-b]e' (with the usual restrictions) is definable in

terms of flow algebra composition, restriction and renaming as (e{c\a}|e'{c\b})\c (with c new) and the net laws are then derivable from the flow laws. On the other hand, net expressions cannot easily define flow algebra expressions because the latter may connect each of their ports to an unlimited number of other ports. A solution could be to define flow algebra composition in the net algebra framework in the following way: any time that we have to connect a port, we first "fork" it into two ports (by composition with a three-port forking literal) and then we connect one of the new ports, leaving the other one free for subsequent connections. Another solution, which might also be useful for different purposes, could be the introduction of net expressions with infinitary sorts: each flow algebra port would be represented by an infinite number of indexed net algebra ports, and composition would take care of always using the "next" available port.

#### 1.6 The Initial Net Algebra

There is a particularly important net algebra, called the initial net algebra, for which the laws []..[{}] only hold and which is unique up to net isomorphism. The initial net algebra is the one that we implicitely have in mind when we talk about "nets", "graphs" or "pictures" and their abstract properties. It turns out that the formalisation is not so intuitive, but it allows us to give a formal justification for our laws and to investigate their darkest details.

The initial net algebra can be built by standard algebraic techniques, quotienting the set of net expressions by the congruence relation generated by the net laws [Gratzer 81]. In this section we look for a more explicit characterisation of the initial net algebra in terms of a suitable kind of graph. The corresponding results for flow algebras can be found in [Milnez 79].

We start with some preliminary definitions:

- PortNames, is the countable set of port names, with a,b ranging over port names and A,B ranging over finite sets of port names;

- Types, is the set of port types;

- L, is the set of literals 1 (nullary operators);

- Sorts, is the set of functions s: PortNames  $\longrightarrow$  Types associating a type to each port name (where  $\lceil s \rceil \triangleq \text{domain}(s)$  is finite);

- $\lambda$ : IL  $\rightarrow$  Sorts, associates a sort to each literal.

#### Definition 1.7

A network is a quintuple  $\langle V, \gamma, A, \pi, E \rangle$ , where:

- V (the set of vertices), is a non-empty finite set, with veV;

- $\gamma$ :  $\forall$   $\rightarrow$   $\mathbb{L}$  (the interpretation mapping), associates a literal to each node of the network;

- A 5 PortNames (the set of port names), is a finite set;

- P is the set of the ports  $\{\langle v,a \rangle \mid v \in V \text{ and } a \in [\lambda(\gamma(v))]\}$ ; where each port is a pair  $\langle v,a \rangle$  (vertex-portname) such that a is a port name of the literal associated with v;

- $\pi$ : A  $\rightarrow$  P (the naming mapping), is 1-1;

- type: P  $\rightarrow$  Types, defined as type(v,a)  $\stackrel{\triangle}{=}$   $\lambda(\gamma(v))(a)$

- B C P X P (the edges), is a relation on ports satisfying:

- 1. E is symmetric and a partial function.

- 2. If  $\langle v,a \rangle E \langle v',a' \rangle$  then  $v \neq v'$  and type (v,a) = type (v',a').

- 3. No  $\langle v,a \rangle$  is both in the domain of E and equal to  $\pi(b)$  for some b.

Condition 1. ensures that connection is symmetric and any port is connected to at most another one. Condition 2. excludes self-loops and ensures type-consistency. Condition 3. ensures that no port is both named (i.e. externally connectable) and connected.

Definition 1.8 A net isomorphism  $\rho: \langle V, \gamma, A, \pi, E \rangle \simeq \langle V', \gamma', A', \pi', E' \rangle$  is an isomorphism  $\rho: V \simeq V'$  such that:

$$\gamma = \gamma' \circ \rho;$$

$$A' = A;$$

$$\pi' = (\rho \# id_A) \circ \pi;$$

$$\langle v, a \rangle E \langle w, b \rangle \Rightarrow \langle \rho(v), a \rangle E' \langle \rho(w), b \rangle$$

$$\square$$

where  $(f \# g) \langle a, b \rangle \triangleq \langle f(a), g(b) \rangle.$

Remark: We do not distinguish between isomorphic networks.

Definition 1.9 The sort of a network N= $\langle V, \gamma, A, \pi, E \rangle$  is s: A  $\rightarrow$  Types with s(a)  $\stackrel{\triangle}{=}$  type( $\pi$ (a)) and  $\lceil s \rceil \stackrel{\triangle}{=} A \rceil$

Definition 1.10 The operations on networks are defined as follows:

1

$$\triangleq$$

$\langle \{1\}$ ,  $1 \circ \rightarrow 1$ , A,  $asA \circ \rightarrow \langle 1, a \rangle$ ,  $\emptyset \rangle$  where  $A = \lceil \lambda(1) \rceil$

$\langle V, \gamma, A, \pi, E \rangle \langle a \triangleq \langle V, \gamma, A \rangle \langle a \rangle$ ,  $\pi \backslash a, E \rangle$

$\langle V, \gamma, A, \pi, E \rangle \{r\} \triangleq \langle V, \gamma, B, \pi \circ r^{-1}, E \rangle$  where  $r:A \rightarrow B$

$\langle V, \gamma, A, \pi, E \rangle \mid \langle V', \gamma', A', \pi', E' \rangle \triangleq \langle V \cup V', \gamma \cup \gamma', A \oplus A', \pi'', E'' \rangle$

where  $C = A \pi A'$

and  $s \downarrow C = s' \downarrow C$

and  $\pi'' = \pi \downarrow (A \backslash C) \cup \pi' \downarrow (A' \backslash C)$

and  $E'' = E \cup E' \cup \{\langle \pi a, \pi' a \rangle, \langle \pi' a, \pi a \rangle \mid asC \}$

where we assume  $V \cap V' = \emptyset$ .

0

Theorem 1.2 The operations are well defined:

- (1)  $\forall 1 \text{s.t.} \langle \{1\}, 1 \rightarrow 1, A, a \in A \rightarrow \langle 1, a \rangle, \emptyset \rangle$ , where  $A = \lceil \lambda(1) \rceil$ , is a network;

- (2) if N is a network, so is N\a;

- (3) if N is a network and r a bijection on [s], then N{r} is a network;

- (4) if N,N' are networks and s,s' are compatible, then N|N' is a network;

- (5) the operations have the correct type.

Proof In Appendix to this chapter [

Every well sorted net expression can be made to denote a network (by interpreting the operations as network operations); the converse is also true:

Theorem 1.3 (Definability)

Every network can be denoted by a well sorted net expression (up to network isomorphism).

Proof In Appendix to this chapter [

The net laws are verified:

Theorem 1.4 (Consistency)

Laws [] .. [{}] are valid up to network isomorphism.

Proof In Appendix to this chapter [

Definition 1.11 Let = be the congruence generated by laws [] .. [{}|] over net expressions. Two net expressions e,e' are convertible iff e=e' []

Lemma 1.1 (Network Substitution Lemma)

Network isomorphism is a congruence with respect to restriction, renaming and composition [

Theorem 1.5 (Soundness)

If e≡e', then e and e' denote isomorphic networks.

Proof

By induction on the proof of e≡e', using the consistency theorem and the network substitution lemma.

Definition 1.12 An atom (at) is an expression of the form

$$at = 1 A \{r\}$$

where 1 is a literal and  $\A$  is multiple restriction over all the a  $\epsilon$

Definition 1.13 A net expression is in normal form (nf) if it has the form

```

nf = at<sub>1</sub> | ... | at<sub>n</sub>

with 1. \forall i, j. s<sub>i</sub> compatible with s<sub>j</sub>

and 2. \forall i, j, k all different. \lceil s<sub>i</sub> \rceil n\lceil s<sub>k</sub>\rceil = \emptyset

where s<sub>i</sub> = \sigma(at<sub>i</sub>)

```

0

Theorem 1.6 (Normal Forms)

Every net expression is convertible to a normal form.

Proof In Appendix to this chapter [

Theorem 1.7 (Completeness)

If e and e' denote isomorphic networks, then e≡e'.

Proof

(1) If nf and nf' denote isomorphic networks, then nf≡nf'.

Suppose  $nf = at_1 | \dots | at_n$  and  $nf' = at_1' | \dots | at_n'$ . By []], []] and condition 2. on normal forms, we can reorder nf and nf' so that there is a bijection between  $at_i$ ,  $at_i'$  and the nodes of the two networks (hence n=n'). Let us assume that nf and nf' are already

properly ordered; by the properties of the isomorphism for each pair of atoms at  $i = l_i \setminus B_i \{r_i\}$  and at  $i = l_i \setminus B_i \{r_i\}$  we have  $l_i = l_i'$ , and  $l_i = l_i'$ . The renamings  $l_i = l_i'$  do not have to be exactly the same, because internal connection can be arbitrarily named. However they must agree on the visible ports, and the internal connections can be renamed as shown in the proof of the normal form theorem. Hence  $l_i = l_i'$ .

(2) Let e denote N and e' denote N' with N  $\simeq$  N'. By the normal form theorem, e and e' have respective normal forms of  $\equiv$  e and of  $\cong$  e'. By soundness of denotes  $\overline{N} \simeq N$  and of denotes  $\overline{N}' \simeq N'$ . Since  $\overline{N} \simeq N \simeq N' \simeq \overline{N}'$ , by (1) we have of  $\cong$  of

Definition 1.14 The net algebra  $N_{IL}$ , (with respect to a set of literals IL) has as carriers the networks of sort s for each s, and as operations the network operations.

Π

Theorem 1.8 (Initiality)

For each net algebra  $\underline{A}$  there is a unique net homomorphism

$$\rho_{\underline{A}} \colon \, \underline{N}_{\underline{1L}} \, \, \xrightarrow{\underline{A}} \, \underline{A}$$

Proof

Let  $e_{\underline{B}}$  be the interpretation of the net expression e in the net algebra  $\underline{B}$ . There is at most one net homomorphism  $\rho\colon \underline{N}_{\overline{A}} \longrightarrow \underline{A}$  which is determined, because of definability, by:

$$-\rho(1) = 1 (\forall 1 \in \mathbb{L})$$

$$-\rho(N\backslash a) = \rho(N)\backslash a$$

$$-\rho(N\{r\}) = \rho(N)\{r\}$$

$$-\rho(N|N') = \rho(N)|\rho(N)$$

i.e. we have

$$\rho(e_{\underline{N}_{\overline{\mathbf{I}}}}) = e_{\underline{\mathbf{A}}}$$

.

We have however to show that  $\rho$  is well defined: if e and e' define N and N' with N = N', then we must show that  $\rho(N) = \rho(N')$ , i.e. that

$e_{\underline{A}}=e'_{\underline{A}}.$  By completeness e=e' and so, as  $\underline{A}$  satisfies the net laws,  $e_{\underline{A}}=e'_{\underline{A}}.$

# 1.7 Planar Networks

In the next chapter we shall often be concerned with planar networks, i.e. with networks whose graph is planar. In those situations it is useful to be able to check syntactically whether an expression denotes a planar network, so that we can define precisely the class of meaningful expressions.

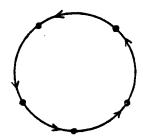

It is possible to characterise planar networks by refining our notion of interface. While an interface is just a set of ports, a planar interface is going to be a cyclically ordered set of ports, hereafter called a cycle.

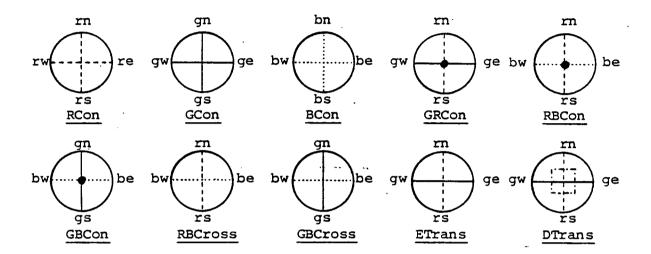

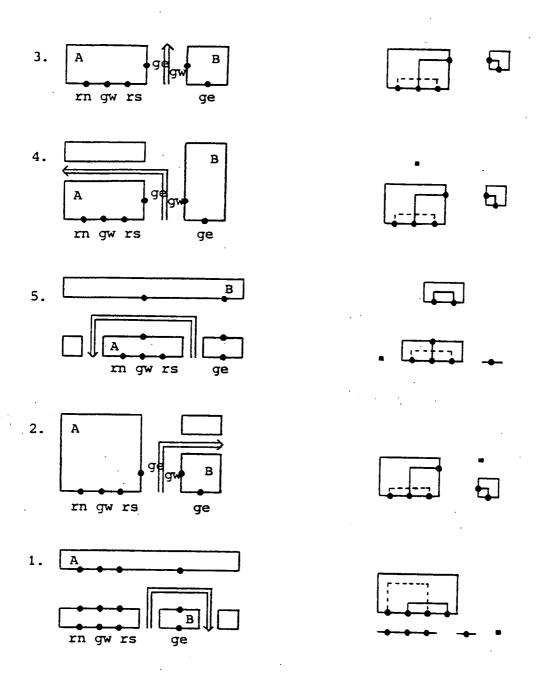

Figure 1.7 A planar interface

Suppose we have a set of planar primitives, with planar interfaces; we need a composition operation preserving planarity and cycles, i.e.

- (i) Composition must take pairs of cycles into cycles.

- (ii) Composition must take pairs of planar graphs into planar graphs.

A first restriction is imposed on composition in order to guarantee condition (i); the presence of cycles then helps enforcing condition (ii). We require:

(i') The ports being connected must be contiguous in both cycles, so that it is possible to form a new cycle by joining the two cycles around the connection area after having dropped the connected ports.

Figure 1.8 Composing cycles

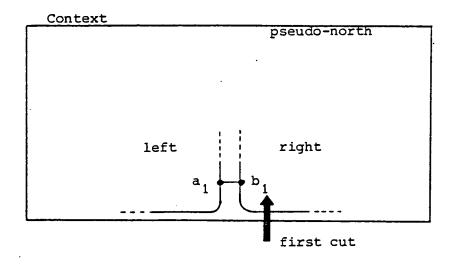

(ii') (Existence) The ports being connected must be inversely ordered in their respective cycles; thus two planar graphs are connected by non-intersecting edges and the result is planar. (Uniqueness) The particular resulting planar graph is not yet completely determined:

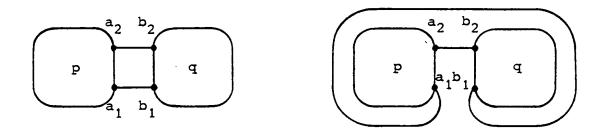

Figure 1.9 Ambiguity of  $p[a_1-b_1,a_2-b_2]q$

We then impose that in a connection  $[a_1-b_1;\ldots;a_n-b_n]$  the oriented arc  $a_{i+1}-b_{i+1}$  be on the "left" of the oriented arc  $a_i-b_i$ , with  $a_{i+1}$  adjacent to  $a_i$  and  $b_{i+1}$  adjacent to  $b_i$  (i a {1..n-1}). Implicit composition is now "plaq" where a is the starting port of the planar composition, which then proceeds anticlockwise on the sort of p.

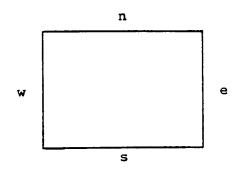

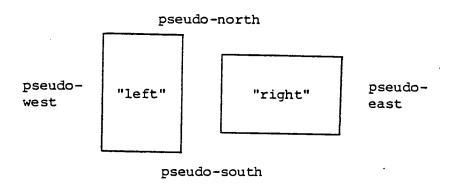

The sort of a Planar Network is a pair

$\langle s: A \rightarrow Types, o: A \rightarrow A \rangle$

where s: A  $\rightarrow$  Types is like the sort of a non-planar network, i.e. it is a mapping from a finite set of port names A into port types. The second component of a sort is used to express planarity

constraints; a cyclic ordering is imposed on A by a bijection  $o: A \cong A$  which is a cyclic permutation of A. We say that a g: A preceeds a' g: A if g: A and that a is adjacent to a' if a preceeds a' or a' preceeds a. The ordering induced by the "preceeds" relation is taken to represent the anticlockwise ordering of ports around a graph.

Two sorts are equal if they associate the same types to the same port names, and if the cyclic ordering of ports is the same.

### 1.8 Bunched Networks

The number of ports contained in a sort can quickly get out of hand when arrays of networks are built. In these cases it is too cumbersome to invent different names for all the ports in a sort, but ambiguities would arise if we allowed repeated names. We therefore introduce bunches as a way of structuring port names.

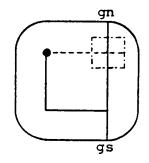

Figure 1.10 Bunches arising in composition

In a bunched sort, the port names are partitioned into a collection of lists, called bunches. Each bunch a is a list containing several copies of the same name, a (each copy denoting a different port):

$$\tilde{a} = [a; ..; a]$$

All the names in a bunch must have the same type. Empty bunches  $\tilde{b}=[]$  are also admitted, meaning that there is no b port.

We can consider a bunched sort as an ordinary sort containing

indexed names  $a_i$  (where  $a_i$  is the i-th item in the list  $\widetilde{a}=[a;..;a]$ ), the advantage of the list notation is that we obtain an automatic re-indexing on bunch operations. Lists are used instead of multisets because ports must not lose their individuality.

A bunch restriction pla cancels the bunch a from the sort of p.

A bunch renaming  $p\{r\}$  (e.g.  $p\{a\backslash b\}$ ) renames uniformly all the elements of the bunches specified by r (i.e.  $\tilde{a}$  becomes  $\tilde{b}$ ). Note that r must still be a bijection of port names.

A debunching operation gives access to the individual elements of a bunch:  $p\{a[i] \mid b\}$  renames part of the bunch a to a new bunch b, provided that b is not already in the sort of p. The list [n] is a list of indexes of a; it can be written as a list of numbers [1;2;5] or a range [3..7] or a combination of them [12;5..7;2;1]. Note that debunching can be used to reorder a bunch: for example if p has a bunch of four ports b, than  $p\{b[4;3;2;1] \mid b\}$  inverts the order of the ports in the bunch.

A cobunching operation is used to merge bunches:  $p\{a;b\c\}$  renames the concatenation of the bunches  $\tilde{a}$  and  $\tilde{b}$  (in that order) to a bunch  $\tilde{c}$ , provided that c is either a, or b, or is not already in the sort of p.

Debunching and cobunching can be generalised to more complex expressions like

$p\{a[3..5];b;c[1]\b, d\e\} =$

$p{a[3..5]b'}{c[1]b"}{b';bb}{b;b"b}{de}$

provided that restrictions similar to the ones discussed above are observed.

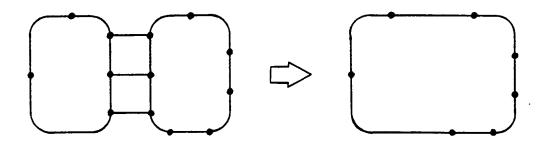

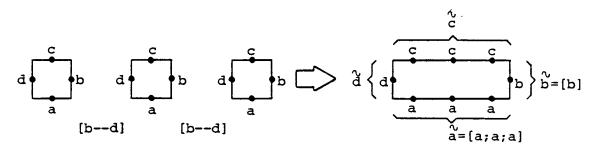

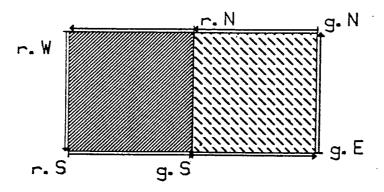

The implicit bunch composition plq connects the bunches of p to the bunches of q having the same name, and the connected bunches disappear from the sort of the result. The usual restrictions apply to bunch composition. Moreover the connection of two bunches is legal only if the bunches have the same number of elements; then the first element of one bunch is connected to the last element of the other bunch, and similarly for all the other elements (this convention turns out to be natural on several occasions, e.g. to connect a bunch on the "west" of a net to a bunch on the "east" of another net, and expecially in the case of planar bunches).

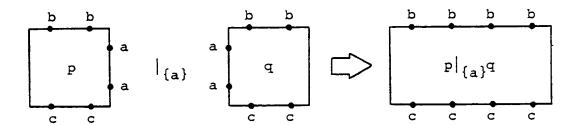

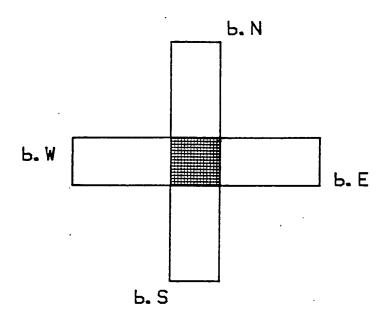

A more general kind of composition is the partial implicit composition  $p|_Aq$ , where A is a subset of the common bunches of p and q. Only the bunches contained in A are connected as described above; the remaining bunches common to p and q are cobunched in pairs of the same name (the ones of p to the left). For example if we imagine to have nets of rectangular shape, we can connect the east bunches of one net to the west bunches of another net, while the south and north bunches of both copies are bunched together.

Figure 1.11 Partial implicit composition

The explicit bunch composition p[r]q connects the bunches of p to the bunches of q according to [r] as with partial implicit composition: we can define [r] as

$$p[r]q \triangleq p|_{\Gamma_{r}}(q\{r^{-1}\})$$

Hence the connected bunches disappear from the sort of the result, and if p has a bunch  $\tilde{a}_{p}$  and q has a bunch  $\tilde{a}_{q}$ , then the cobunching

$\widetilde{a}_p; \widetilde{a}_q$  belongs to the result. This automatic cobunching turns out to be very useful.

Formally, the set PortNames' of a bunched sort is the set PortNames X N, where n s N is the length of each bunch. Let  $\#: A \longrightarrow N$  be the function returning the length of each bunch of a sort based on A, and returning 0 for each port name not contained in A. Moreover, let  $\langle n \rangle \stackrel{\Delta}{=} \{1, ..., n\}$ . Then bunch restriction is defined as:

$$p b \triangleq p \{b, | i \in \langle \#b \rangle \}$$

and bunch renaming as:

$$p\{r:A\cong B\} \triangleq p\{u_{agA}\{a_i \setminus r(a)_i | is \langle \#a \rangle\}\}$$

For debunching we need to introduce the operation  $\partial(i,1)$  which returns the position of the number i in the list of numbers 1.

$p\{a[1]\backslash b\} \stackrel{\Delta}{=} p\{a_i\backslash b_{\partial(i,1)}|is1\} \quad \{a_i\backslash a_{\partial(i,\langle\#a\rangle\backslash 1)}|i\not=1\}$  Cobunching is defined as:

$$p\{a;b\c\} \triangleq p\{a_i\c_i|is\langle\#a\rangle\} \cup \{b_i\c_{\#a+i}|is\langle\#b\rangle\}$$

Finally, partial implicit composition (from which the other compositions can be derived) is defined in terms of the previously described bunch operators and of normal composition:

$$p|_{A}q \triangleq$$

$$(p\{b\backslash b'|beB\} u\{a_{i_a}\backslash a_{\#a-i_a+1}|aeA,i_ae<\#a\rangle\} |$$

$$q\{b\backslash b''|beB\})$$

$$\{b':b''\backslash b|beB\}$$

where  $B = (\lceil \sigma(p) \rceil a \lceil \sigma(q) \rceil) \setminus A$  and b',b" do not occur in the sorts of p and q.

# 1.9 Planar Bunched Networks

A Planar bunched sort is a planar sort with planar bunches; a planar bunch is a bunch  $\tilde{a}=[a_1;...;a_n]$  where the  $a_i$  respect the cyclic order of their sort. Planar bunch operations are similar to their nonplanar versions, except that they must make sense in a planar

framework.

Planar bunch restriction and renaming present no further problems.

Debunching is valid only if the extracted sub-bunch respects the cyclic ordering; note that we can rotate bunches this way, like in  $b[2;3;4;1]\b$  for a 4-bunch  $\tilde{b}$ .

Cobunching needs some further explanation; the planar cobunching of two planar bunches  $\tilde{a}; \tilde{b} \setminus \tilde{c}$  is the bunch  $\tilde{c}$  starting with the first port of  $\tilde{a}$ , containing  $\tilde{a}$  and  $\tilde{b}$ , and respecting the order of the planar sort. Note that if  $\tilde{a}$  and  $\tilde{b}$  are interleaved then  $\tilde{c}$  respects the interleaving, and  $\tilde{c}$  can be rotated in order to start with the desired port of  $\tilde{a}$  or  $\tilde{b}$ .

The various kinds of compositions work much as before. Again the connection of (interleaved) bunches must respect the cyclic ordering and the first port of each bunch connects to the last port of the respective matching bunch. Note that this first-to-last conventions allows us, in most cases, to connect planar bunches without having to rearrange them in order to respect planarity constraints.

# 1.10 Molecules, Hypercubes, Mosaics and Klein Bottles

This section shows some examples of use of net algebras, especially concerning recursive definitions and bunches. The examples suggest some interesting extensions of our notation which are left as open problems.

The first example is a attempt to describe molecules by their chemical bond structure. Chemical elements of valency n are represented by literals with n ports, for example:

H: {h} (hydrogen)

0:{o<sub>1</sub>,o<sub>2</sub>} (oxygen)

C: {c<sub>1</sub>,c<sub>2</sub>,c<sub>3</sub>,c<sub>4</sub>} (carbon)

We can easily compose simple molecules:

Methane

$$\triangle$$

C [c<sub>1</sub>--h] H

[c<sub>2</sub>--h] H

[c<sub>3</sub>--h] H

[c<sub>4</sub>--h] H

CarbonDioxide

$$\stackrel{\Delta}{=}$$

C [ $c_1 - o_1$ ,  $c_2 - o_2$ ] 0

[ $c_3 - o_1$ ,  $c_4 - o_2$ ] 0

$$c_2H_2 \stackrel{\Delta}{=}$$

CH  $[c_2-c_1, c_3-c_3]$  CH

Figure 1.12 Methane, carbon dioxide and benzene

Two molecules are isomers if they have the same number of atoms

of each kind, but "behave" differently. Hence isomerism implies structural difference, which can be expressed in our notation as well as by chemical diagrams. For various reasons, it does not matter which valencies of an atom are connected to another atom, so that the simple interchanges of bonds of a single atom does not produce isomers.

In general we might want to talk about the <u>spacial</u> orientation of valencies, which is important in stereochemistry and cristallography. This suggests a generalisation of planar cycles and sorts to three dimensions, producing what we might call envelopes, i.e. arrangements of ports on the vertices of a polyedrum. Envelopes should characterise legal compositions of polyedra in 3-D space, forbidding copenetration in the same way as cycles forbid over-crossings. We could then equally well describe crystalline structures, mechanical parts or the architecture of buildings in a safe and unambiguous way. This is left as an open problem which might have very interesting applications, but which has little relevance here.

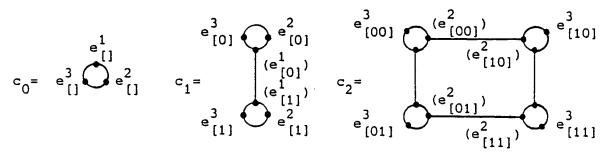

As a second example, let us build an n-dimensional cube starting from a single literal v (vertex) with ports  $e^1 ... e^n$ . In order to avoid name clashes we index the port names  $e^i$  by lists of binary digits (e.g.  $e^3_{[0;1;1;0]}$ ):

$$c_0 \stackrel{\Delta}{=} v\{e^1 \setminus e^1_{[]}, \dots, e^n \setminus e^n_{[]}\}$$

$$c_{i+1} \stackrel{\Delta}{=}$$

$$c_i \{e^{i+1}_{[0..0]} \setminus e^{i+1}_{[0,0..0]}, \dots, e^{i+1}_{[1..1]} \setminus e^{i+1}_{[0,1..1]}, \dots, e^n_{[0..0]} \setminus e^n_{[0,0..0]}, \dots, e^n_{[1..1]} \setminus e^n_{[0,1..1]}\}$$

$$\{e^{i+1}_{[0,0..0]} - e^{i+1}_{[1,0..0]}, \dots, e^{i+1}_{[0,1..1]} - e^{i+1}_{[1,1..1]}\}$$

$$c_i \{e^{i+1}_{[0..0]} \setminus e^{i+1}_{[1,0..0]}, \dots, e^{i+1}_{[1..1]} \setminus e^{i+1}_{[1,1..1]}, \dots, e^n_{[0..0]} \setminus e^n_{[1..1]} \setminus e^n_{[1..1]}\}$$

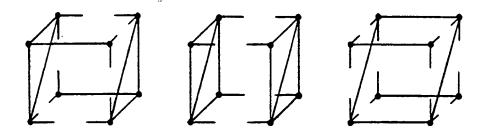

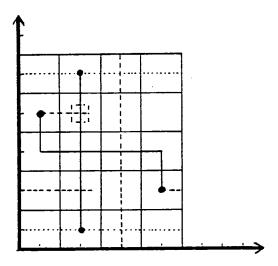

The first three steps in the construction of a three-dimensional cube are illustrated in the next figure:

Figure 1.13 Building a cube

This is a situation where the advantages of bunches are particularly clear, indeed by using bunched sorts and compositions we need only write:

$$c_0 \stackrel{\underline{\Delta}}{=} v$$

$$c_{i+1} \stackrel{\underline{\Delta}}{=} c_i [e^{i+1} - e^{i+1}] c_i$$

Note that the result is really an hypercube, and not a "twisted" version of it (remember that two bunches  $a_1 cdots a_n$  and  $b_1 cdots b_n$  are connected as  $a_1 cdots b_n cdots a_1 cdots b_1 cdots a_n cdots b_1$ ).

Suppose now that we only have a literal v with three ports f,b,e (forward, backward and external) and we still want to make a

hypercube [Preparata 79]. All we have to do is to build up n-ary vertices from ternary ones (for n>1):

$$v_n \stackrel{\Delta}{=} (v\{e \setminus e^1\}[f-b]...[f-b]v\{e \setminus e^{n-1}\})$$

$$[f-b,b-f] v\{e \setminus e^n\}$$

Figure 1.14 An n-ary vertex

and we can then apply our previous definitions.

The third example concerns mosaics on the plane. Suppose we have a literal t (equilateral triangle) with ports b,r,l (base, right and left) organised in this order in a planar sort. The following definition builds a mosaic of triangles which at every steps retains the form of an equilateral triangle. Bunches are used.

$$\begin{array}{lll} m_{0} & \stackrel{\Delta}{=} & t \\ \\ m_{n+1} & \stackrel{\Delta}{=} \\ \\ m_{n} \{b \setminus b', 1 \setminus 1', r \setminus r'\} \\ \\ [b'--b] & m_{n} [1'--1] & m_{n} [r'--r] & m_{n} \end{array}$$

The next figure shows the first three steps in the construction of a mosaic:

$$m_0 = 1 \underset{b}{ } \sum_{b} r$$

$m_1 = r \underset{r}{ } \sum_{1} 1$   $m_2 = 0$

Figure 1.15 Building a mosaic

Note that if we do not use planar sorts triangles are allowed to flip around their connection points, and the result can be a rather complicated three-dimensional graph instead of a planar mosaic.

The fourth example concerns sorts with an infinite number of ports. We can consider a segment  $s_1$  of length 1 in 3-D space, as a literal with uncountably many ports  $p_x$  for  $0 \le x \le 1$ . We can obtain a v-shape by joining two segments at their end point:

$$v \triangleq s_1[p_0-p_0]s_2$$

Figure 1.16 Joining two segments

We can then join two v-shapes by connecting the middle points of the first v-shape to the 0.3-points of the second v-shape. Note the effect of bunches in this case.

$$\mathbf{w} \triangleq \mathbf{v}[\mathbf{p}_{0.5} - \mathbf{p}_{0.3}]\mathbf{v}$$

Figure 1.17 Joining two v-shapes

We can produce more interesting examples with a literal r (representing a "flexible" rectangle in 3-D space) with ports  $n_x$ ,  $s_x$  for  $0 \le x \le 1$  ranging from left to right, and  $e_y$ ,  $w_y$  for  $0 \le y \le 1$  ranging from bottom to top:

Figure 1.18 A flexible rectangle

Here are some interesting objects which can be obtained:

ring

$$\stackrel{\Delta}{=}$$

r  $[e_x - w_x, w_x - e_x \ \forall x]$  r

punched-ring  $\stackrel{\Delta}{=}$  r  $[e_x - w_x, w_x - e_x \ \forall x \in [0..0.1] \ u [0.9..1]]$  r

Note that we do not capture the class of 3-D surfaces modulo continuous transformations; for example we have no way of distinguishing a straight ring from a double-twisted one.

An alternative flexible rectangle may be defined to have four ports n,s,e,w which are uncountable bunches disposed anticlockwise around the perimeter (when bunches are concatenated, they are renormalised to the interval 0..1). This case is particularly

similar to the treatment of ports in Chapter 3.

Note that torus1 is obtained by inserting one ring in parallel inside the other, and then joining the edges, while in torus2 the two rings are composed into a thicker ring which is then bent around to connect its two edges.

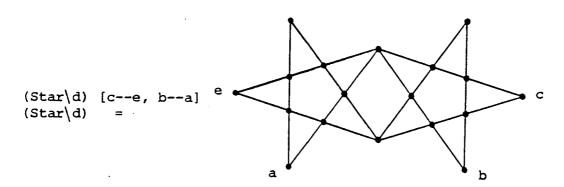

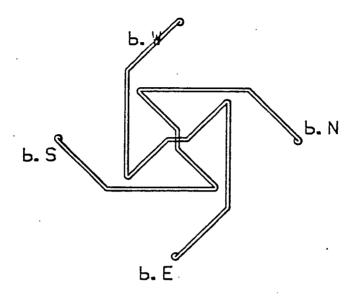

## 1.11 Main Example: The Foster & Kung Pattern Matcher

The Foster & Kung pattern matching hardware algorithm [Foster 80] will be used as an example through chapters 1 and 2. It has a very simple and regular structure, deriving from the systematic hierarchical decomposition of a pattern matching problem, while its behaviour involves flow of data in a double pipeline configuration and is far from obvious.

The problem is to find all the occurrences of a pattern p in a text (string of characters) s, where p may contain the distinguished character '\*'. A pattern p matches a subtext s' of s if p and s':

(i) have the same length and, (ii) either the corresponding characters are equal or the pattern character is '\*'.

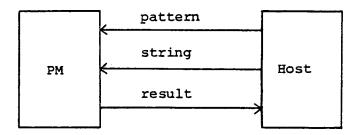

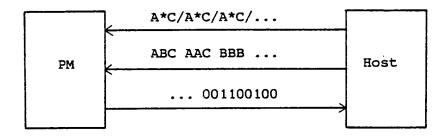

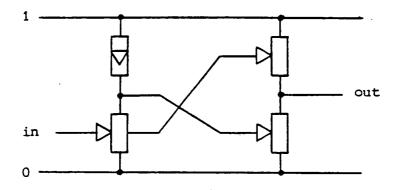

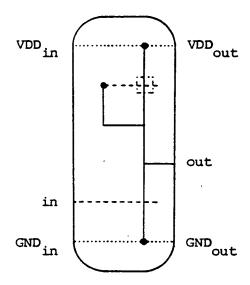

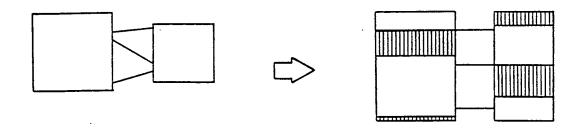

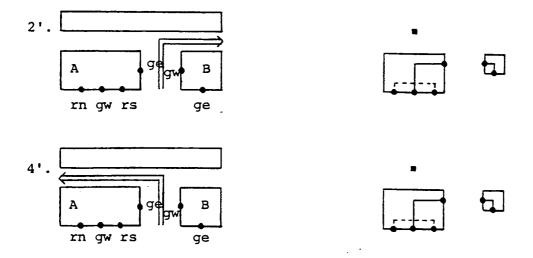

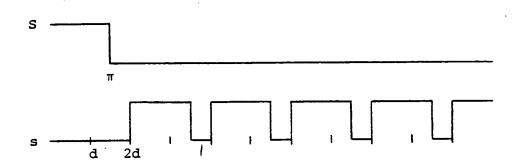

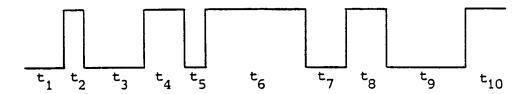

The pattern matcher is implemented as a separate processor, communicating with some host computer; here is the general plan.

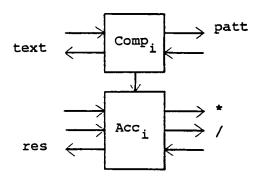

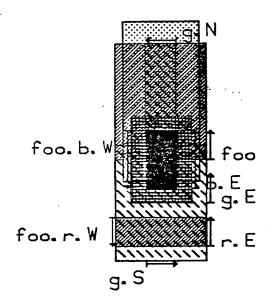

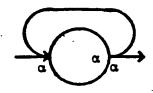

Figure 1.19 The pattern matcher as a processor

Instead of storing the pattern into PM and then supplying the string, it is simpler to implement a on-the-fly pattern matching where the pattern is repeatedly transmitted by the host H together with an indication of the end of the pattern which is encoded in the last character of the pattern.

Figure 1.20 The pattern matcher protocol

The result of the matching is returned as a binary string containing a 1 for each successful match; the position of each 1 corresponds to the position of the last character of a matching subtext.

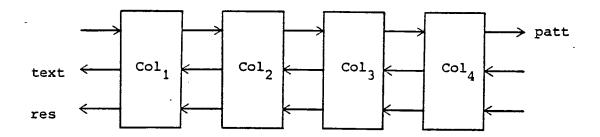

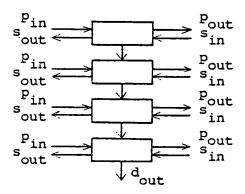

The key architectural idea is the use of a pipeline where text and (repeated) pattern meet head-on.

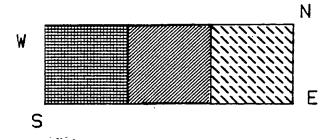

Figure 1.21 Architecture

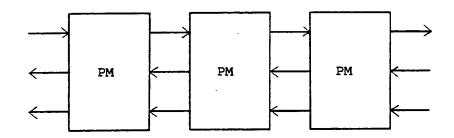

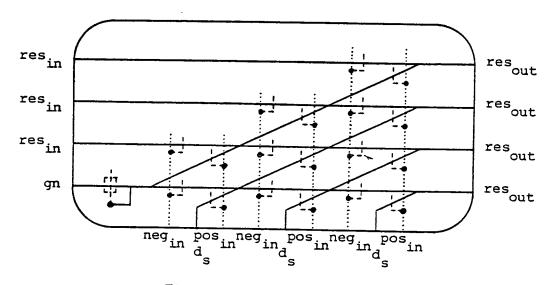

The pipeline should be at least as long as the pattern. This structure is very convenient because makes the matching process time-linear in the text length and space-linear in the pattern length. Moreover, if we want to match a very long pattern we can simply connect several PM processors in a row and all works well.

Figure 1.22 Matching long patterns

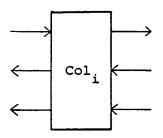

Every stage of the pipeline matches a single character of text to a single character of pattern. The stage produces an output whenever it matches the last char of the pattern, otherwise it transmits forward the output coming from the previous stage.

Consider a single stage: it receives in turn the pattern from the left and the text from the right (retransmitting them unaltered) and it has to remember whether all the previous characters matched, so that at the end of the pattern it can tell whether the pattern as a whole matches the subtext.

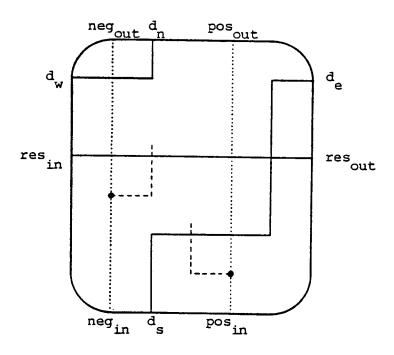

Figure 1.23 A stage of the pattern matcher

If there are  $n_p$  characters in the pattern, a single stage will consider all the substrings of length  $n_p$  starting at multiples of  $n_p$  in the text, ignoring all the other substrings. The other substrings of length  $n_p$  will be considered by the adjacent stages, so that if we have  $n_p$  stages we consider all the substrings of length  $n_p$ . More than  $n_p$  stages will do no harm: the result will simply be overwritten one or more times, but it will still be correct.

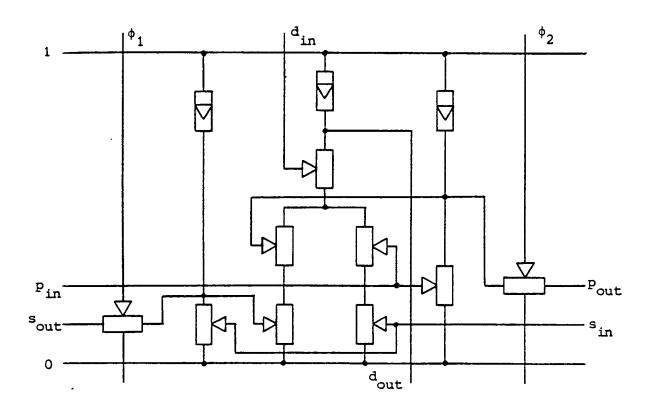

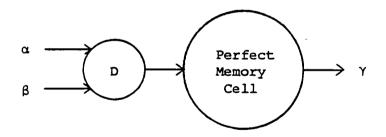

We can further decompose the structure of a single stage by distinguishing a comparator part and an accumulator part.

Figure 1.24 Inner structure of a stage

The comparator takes a string character and a pattern character, and compares them outputting the result to the accumulator. The accumulator accumulates the successive results of the comparator, and when the pattern is complete it produces the final result.

The pattern information is split between comparator and

accumulator. The comparator receives the proper pattern characters, and the accumulator receives: (i) the information that the current pattern character is actually the wild card character (so that it can ignore the result of the comparator) and: (ii) the information that the current character is the last of the pattern (so that it can output the result and reinitialise itself).

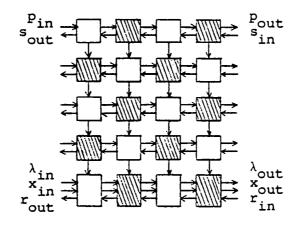

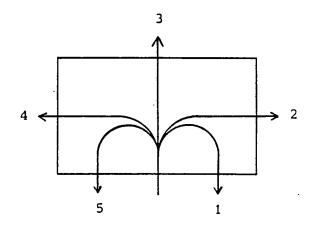

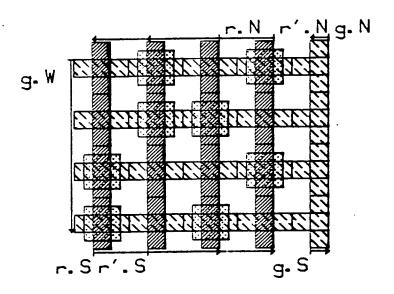

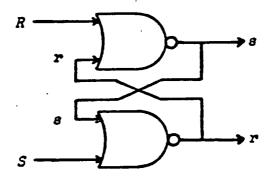

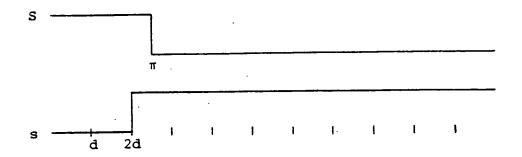

Each character is assumed to be a parallel vector of bits, let us say 4 bits. We can further decompose the comparator into a series of bit comparators, each of them matching a bit of pattern against a bit of string. Having done this, we might just take the boolean and of the results of all the bit comparator and feed it to the accumulator. However, there is a different solution which gives us the opportunity of studying a more interesting kind of architecture, as well as being more elegant for VLSI implementations. We can organise the bit comparators into a pipeline which runs orthogonally to the main string-pattern pipeline; this assumes that the bits constituting the characters are shifted at the input of the pattern matcher and realigned at the output. The net effect is that although a byte comparison takes 4 cycles, the accumulator receives a result at each cycle.

Figure 1.25 Bit comparators

The first bit comparator at the top is connected to "true", and each bit comparator outputs the boolean and of its comparation with the previous result coming from above.

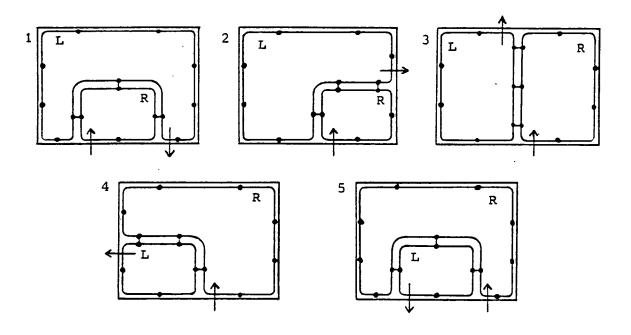

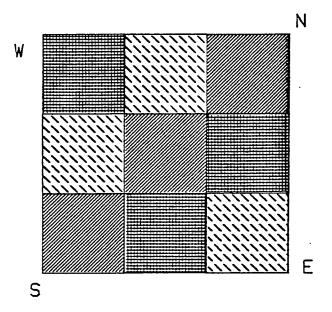

There is a final optimisation to be made. It is convenient to implement each bit comparator by a single inverting stage; this implies that all the outputs will be inverted, and the next comparator (both below and to the left) must be ready to accept an inverted output. This leads to differentiating "positive" and "negative" comparators and accumulators, arranging them into a chess-board pattern. The behaviour of the pattern matcher will not be affected, provided that there are both an even number of stages and an even number of bits in each character.

Figure 1.26 Positive and negative devices

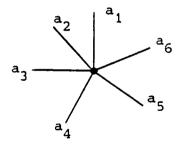

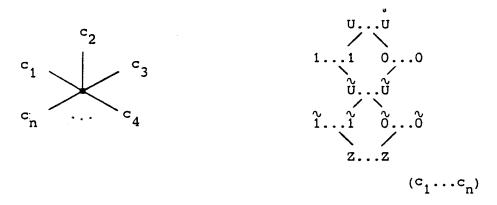

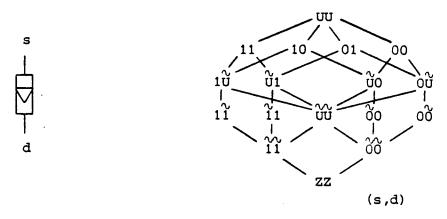

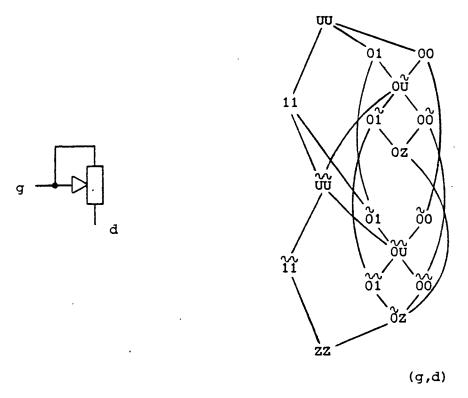

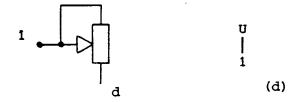

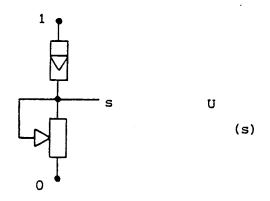

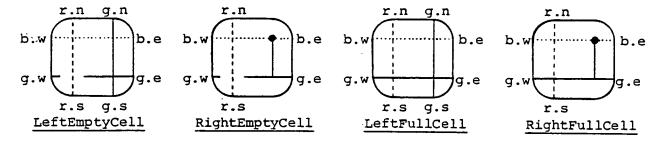

We now show that the structure of the pattern matcher can be expressed as a network. We take the bit comparators and accumulators as black boxes (to be denoted by literals) and we compose them together into the complete system using our network operations. In the next chapter, more refined net algebras will be used to specify the contents of these black boxes according to the descriptive model or technology we want to implement them in. Here we use the following primitives (i.e. literals):

True: {true: match}

False: {false: match}

PosBitComp: {p<sub>in</sub>,p<sub>out</sub>: pattern, s<sub>in</sub>,s<sub>out</sub>: string, d<sub>in</sub>,d<sub>out</sub>: match}

NegBitComp: {pin,pout: pattern, sin, sout: string, din, dout: match}

PosAccum:  $\{\lambda_{in}, \lambda_{out}: endpattern, x_{in}, x_{out}: wildcard, \}$

rin, rout: result, din: match}