# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## On the Simulation and Design of Manycore CMPs

Christopher Callum Thompson

Doctor of Philosophy

Institute of Computing Systems Architecture

School of Informatics

University of Edinburgh

2014

#### **Abstract**

The progression of Moore's Law has resulted in both embedded and performance computing systems which use an ever increasing number of processing cores integrated in a single chip. Commercial systems are now available which provide hundreds of cores, and academics have proposed architectures for up to 1024 cores. Embedded multicores are increasingly popular as it is easier to guarantee hard-realtime constraints using individual cores dedicated for tasks, than to use traditional time-multiplexed processing. However, finding the optimal hardware configuration to meet these requirements at minimum cost requires extensive trial and error approaches to investigate the design space.

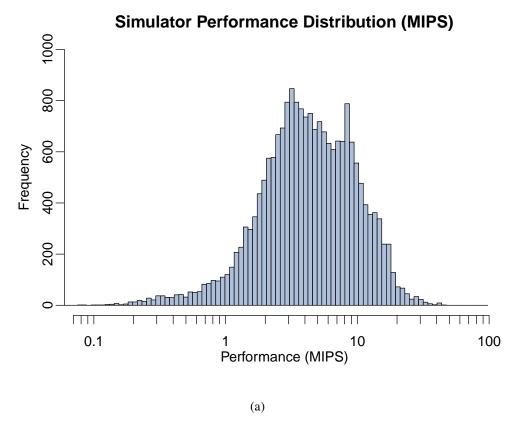

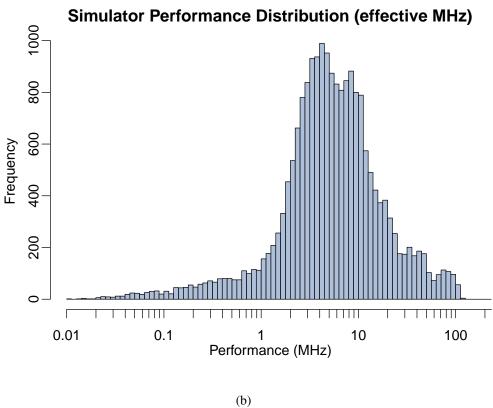

This thesis tackles the problems encountered in the design of these large scale multicore systems by first addressing the problem of fast, detailed micro-architectural simulation. Initially addressing embedded systems, this work exploits the lack of hardware cache-coherence support in many deeply embedded systems to increase the available parallelism in the simulation. Then, through partitioning the NoC and using packet counting and cycle skipping reduces the amount of computation required to accurately model the NoC interconnect. In combination, this enables simulation speeds significantly higher than the state of the art, while maintaining less error, when compared to real hardware, than any similar simulator. Simulation speeds reach up to 370MIPS (Million (target) Instructions Per Second), or 110MHz, which is better than typical FPGA prototypes, and approaching final ASIC production speeds. This is achieved while maintaining an error of only 2.1%, significantly lower than other similar simulators.

The thesis continues by scaling the simulator past large embedded systems up to 64-1024 core processors, adding support for coherent architectures using the same packet counting techniques along with low overhead context switching to enable the simulation of such large systems with stricter synchronisation requirements. The new interconnect model was partitioned to enable parallel simulation to further improve simulation speeds in a manner which did not sacrifice any accuracy.

These innovations were leveraged to investigate significant novel energy saving optimisations to the coherency protocol, processor ISA, and processor micro-architecture. By introducing a new instruction, with the name wait-on-address, the energy spent during spin-wait style synchronisation events can be significantly reduced. This functions by putting the core into a low-power idle state while the cache line of the indicated

address is monitored for coherency action. Upon an update or invalidation (or traditional timer or external interrupts) the core will resume execution, but the active energy of running the core pipeline and repeatedly accessing the data and instruction caches is effectively reduced to static idle power. The thesis also shows that existing combined software-hardware schemes to track data regions which do not require coherency can adequately address the directory-associativity problem, and introduces a new coherency sharer encoding which reduces the energy consumed by sharer invalidations when sharers are grouped closely together, such as would be the case with a system running many tasks with a small degree of parallelism in each.

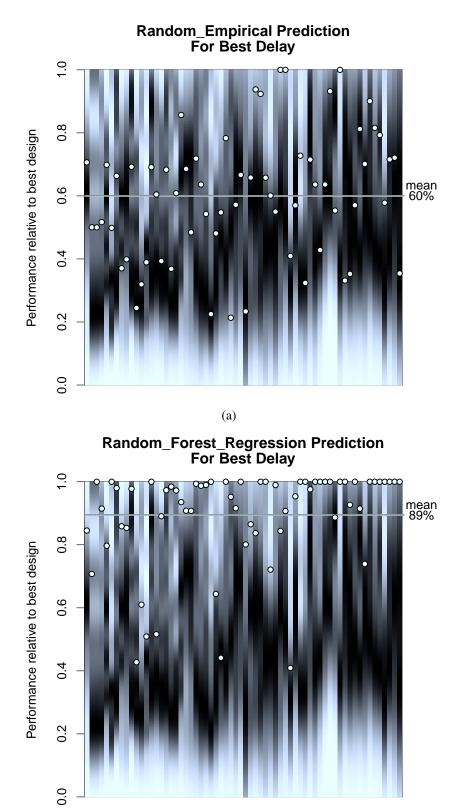

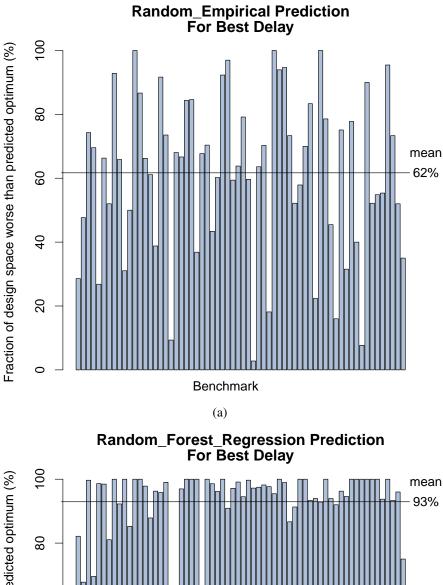

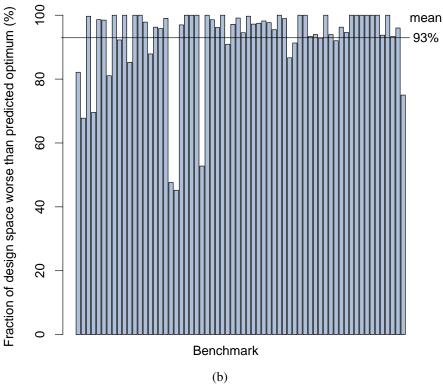

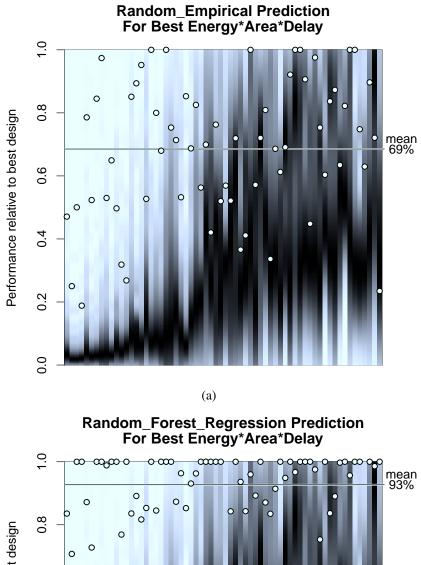

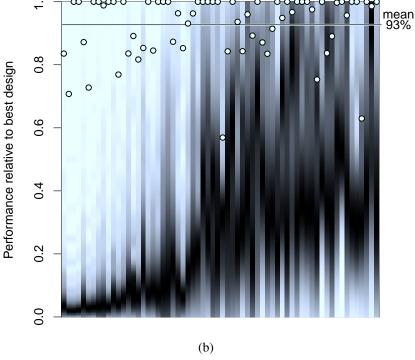

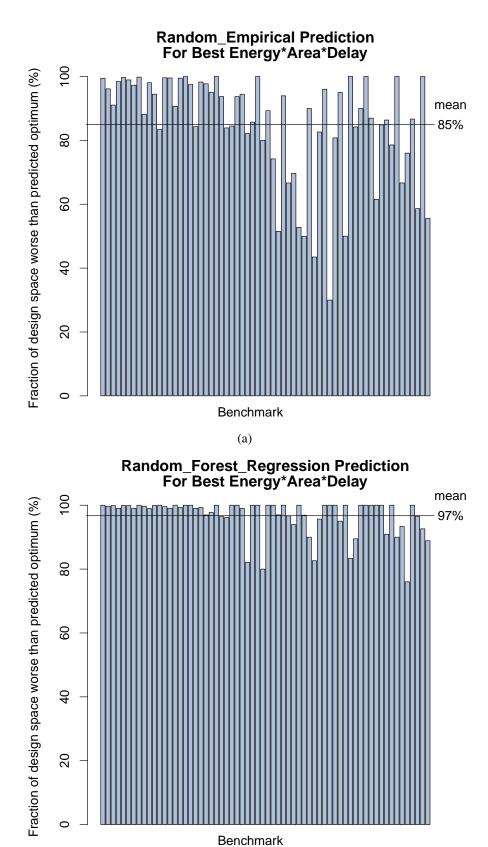

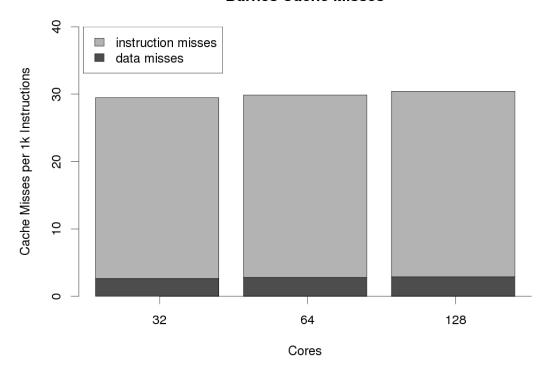

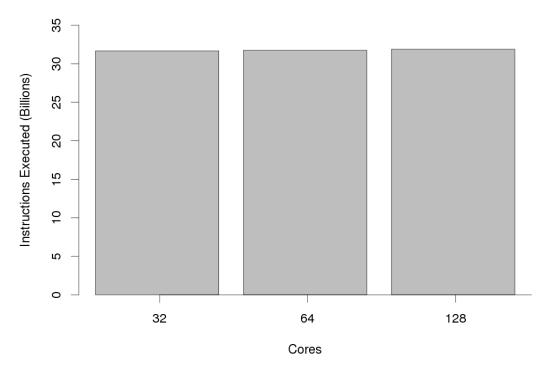

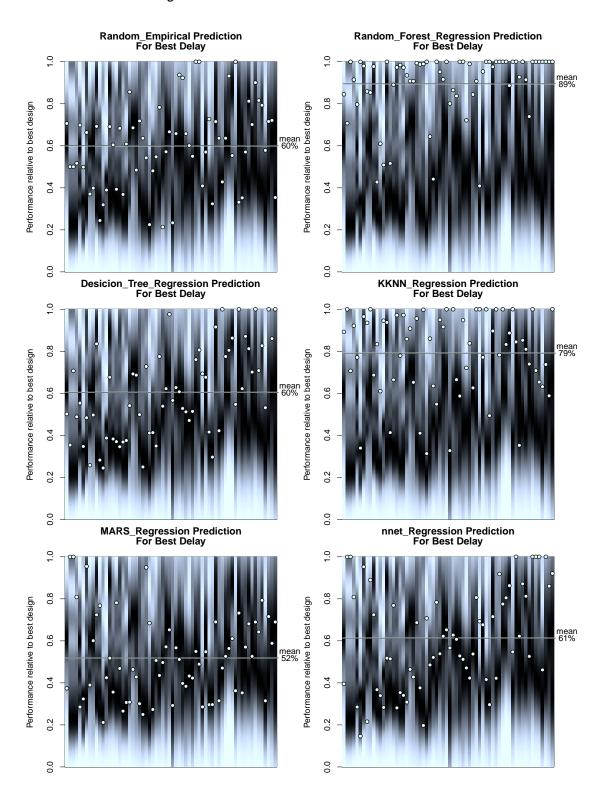

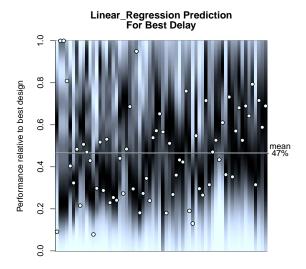

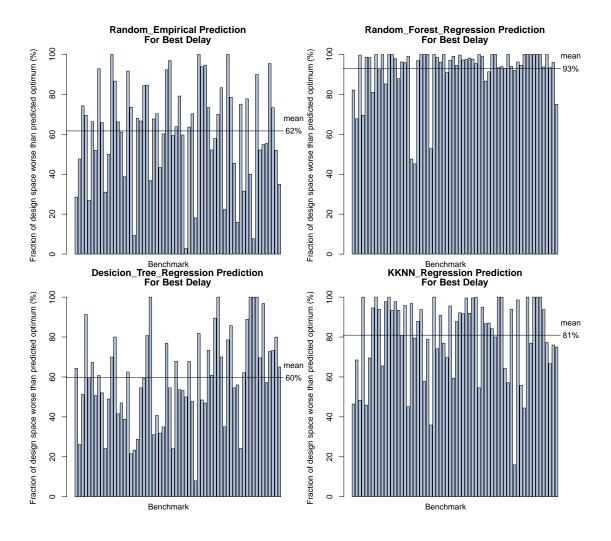

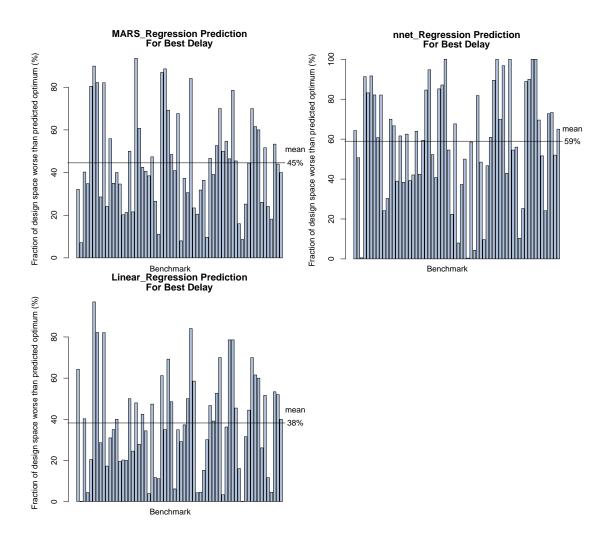

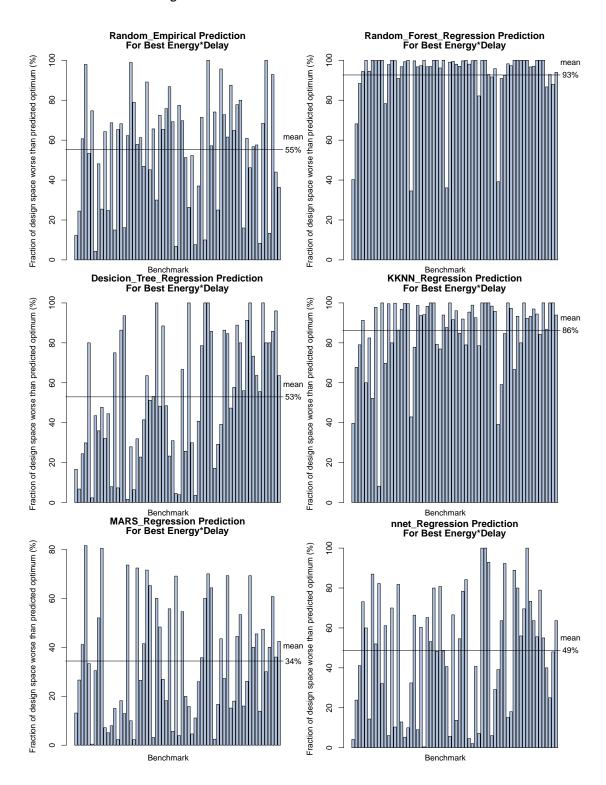

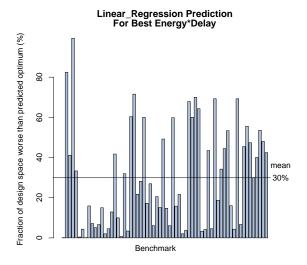

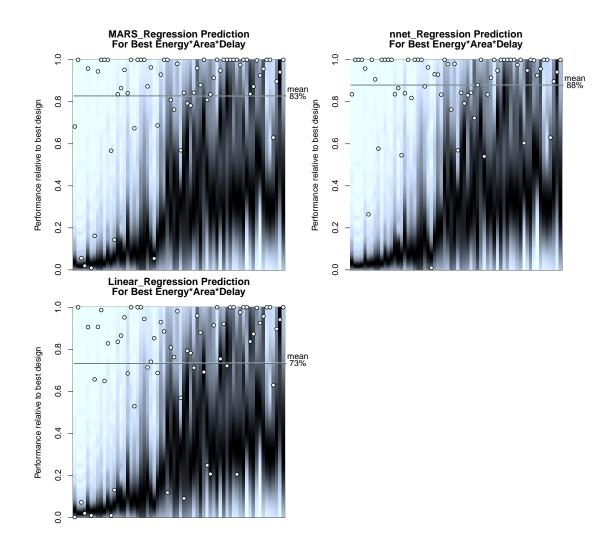

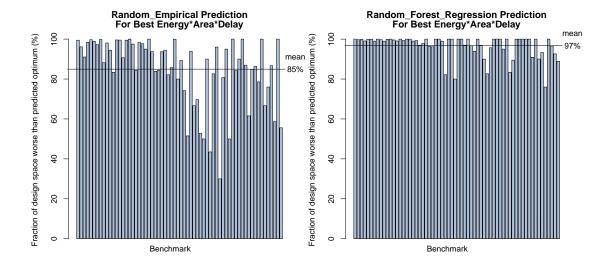

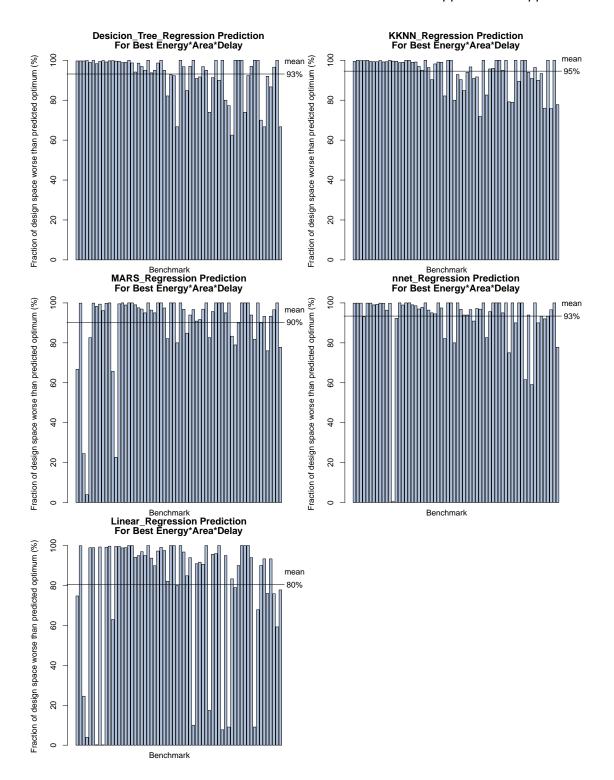

The research concludes by using the extremely fast simulation speeds developed to produce a large set of training data, collecting various runtime and energy statistics for a wide range of embedded applications on a huge diverse range of potential MPSoC designs. This data was used to train a series of machine learning based models which were then evaluated on their capacity to predict performance characteristics of unseen workload combinations across the explored MPSoC design space, using only two sample simulations, with promising results from some of the machine learning techniques. The models were then used to produce a ranking of predicted performance across the design space, and on average Random Forest was able to predict the best design within 89% of the runtime performance of the actual best tested design, and better than 93% of the alternative design space. When predicting for a weighted metric of energy, delay and area, Random Forest on average produced results within 93% of the optimum result.

In summary this thesis improves upon the state of the art for cycle accurate multicore simulation, introduces novel energy saving changes the the ISA and microarchitecture of future multicore processors, and demonstrates the viability of machine learning techniques to significantly accelerate the design space exploration required to bring a new manycore design to market.

## **Lay Summary**

Many tasks performed by computers can be broken down into multiple smaller tasks can be processed independently. These can then be worked on in parallel, by multiple processing cores within the computer. So long as the work can be split into enough independent jobs it is possible to keep increasing the speed at which the whole task is computed by adding more processing cores to the system. The degree to which a task can be split into independent tasks is called the parallelism of the task. It is also possible to make each processing core more powerful, and in turn increase the overall processing rate. However each increase in performance of an individual core comes at ever increasing non-linear cost, in both space and energy, eventually reaching a limit to what is physically possible. Because of this, the best design of computer for a given application depends on the parallelism inherent to the application, and the energy and space constraints in which the application must execute. An extremely parallel application would suite a large number of processors, while one which cannot be parallelised needs the most powerful single-core system available (within the constraints).

This thesis addresses the design of such parallel computing systems from several inter-related directions. Firstly through innovations in the simulations of such systems it enables much greater simulation performance at extremely high levels of detail and accuracy, enabling greater exploration of the performance of an application across a number of design parameters. Secondly it leverages this simulation infrastructure to evaluate the effectiveness of some existing techniques in a new context to address scalability issues with the communication challenges that rise from splitting a problem between hundreds of processing cores. These focus mostly on reducing the exchange of information through tracking the sharing state of memory, and through increasing the energy efficiency of waiting periods during synchronisation. The thesis then presents and evaluates novel contributions to the problem of "cache coherency" at the extreme scale of hundreds to a thousand processing cores in a single processor. Cache coherency is an aspect of the inter-processor communication inherent to the most common way of parallelising programs, where all processing cores can access the data from any other processor working on the same task. The thesis finally evaluates a set of algorithms from the field of Artificial Intelligence called "machine learning" algorithms, to predict the performance of new applications across a large design space of potential embedded computer designs. It finds that existing algorithms can make very good predictions for identifying the best overall design choice, targeting a number of design goals, such as performance, or a balance between energy and design size.

## **Acknowledgements**

Foremost I would like to thank my PhD supervisor, Prof. Nigel Topham, whose guidance, advice, and support has not only helped to inspire my research and articulate my ideas into writing, but has also prevented this PhD from descending into an endless number of only tangentially related, although interesting, side projects. I would also like to thank Dr Björn Franke for his continued support and advice; always interested to talk and quick to volunteer for proof-reading, which always came back with invaluable advice. Additional thanks go to my second supervisor Dr Vijay Nagarajan for the valuable discussions and encouragement.

The colleagues and friends from the CArD and PASTA groups to which I would like to extend my gratitude are too numerous to list, but I would like to give special thanks to those closer friendships I have made and those who's regular discussions were both fruitful and enjoyable. Stephen Kyle, Harry Wagstaff, Matthew Beilby, Volker Seeker, Tom Spink, Tobias Edler von Kock, Oscar Almer, Miles Goulde, Marco Eliver, Igor Böhm, and from outwith the department Jennifer Mankin, have all contributed greatly to this journey.

I would also like to say thank you to Dr Peter Boyle, in the School of Physics and Astronomy, who was the first person to encourage me towards undertaking a PhD.

Thank you to my parents for their endless support in my academic career, and for always pushing me to perform to my fullest, and to set my goals high.

Finally I would like to say thank you to my partner in life Rachael Barton, whose proof reading, tireless support, encouragement, and patience has seen me through the highs and lows of my PhD, and without whom both this thesis, and my life, would most certainly be incomplete.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Christopher Callum Thompson)

## **Table of Contents**

| A۱ | ostrac     | et      |                                  | iii |  |  |

|----|------------|---------|----------------------------------|-----|--|--|

| La | ıy Suı     | nmary   |                                  | v   |  |  |

| A  | cknow      | vledgem | nents                            | vi  |  |  |

| O  | wn W       | ork Dec | claration                        | vii |  |  |

| 1  | Intr       | oductio | n                                | 1   |  |  |

|    | 1.1        | Resear  | rch Goals                        | 4   |  |  |

|    | 1.2        | Contri  | butions                          | 4   |  |  |

|    | 1.3        | Public  | ations                           | 6   |  |  |

|    | 1.4        | Structi | ure of this Thesis               | 7   |  |  |

| 2  | Background |         |                                  |     |  |  |

|    | 2.1        | Paralle | el Computing Systems             | 9   |  |  |

|    | 2.2        | Progra  | mming Models                     | 9   |  |  |

|    |            | 2.2.1   | Message Passing                  | 10  |  |  |

|    |            | 2.2.2   | Shared Memory                    | 10  |  |  |

|    | 2.3        | Cache   | Coherency & Memory Consistency   | 11  |  |  |

|    |            | 2.3.1   | Memory Consistency Models        | 13  |  |  |

|    | 2.4        | Cohere  | ency Mechanisms                  | 16  |  |  |

|    |            | 2.4.1   | Snooping                         | 16  |  |  |

|    |            | 2.4.2   | Directory                        | 19  |  |  |

|    |            | 2.4.3   | Other Sharer-Tracking Mechanisms | 21  |  |  |

|    |            | 2.4.4   | Software Managed Coherency       | 23  |  |  |

|    | 2.5        | Archit  | ecture Scalability               | 24  |  |  |

|    |            | 251     | Ruses and Crosshars              | 24  |  |  |

|   |      | 2.5.2   | Mesh and Tiled Architectures                 | 25 |

|---|------|---------|----------------------------------------------|----|

|   |      | 2.5.3   | Tree and other NoC architectures             | 25 |

|   |      | 2.5.4   | Design Space Exploration                     | 27 |

|   | 2.6  | Simula  | ation                                        | 27 |

|   |      | 2.6.1   | Emulation and Instrumentation                | 27 |

|   |      | 2.6.2   | Single-Core Simulation                       | 28 |

|   |      | 2.6.3   | Serial Simulation                            | 28 |

|   |      | 2.6.4   | Decoupled Simulation                         | 28 |

|   |      | 2.6.5   | Parallel Relaxed System Simulation           | 29 |

|   |      | 2.6.6   | Hardware Accelerated Simulation              | 29 |

|   | 2.7  | Machi   | ne Learning                                  | 29 |

|   | 2.8  | Energy  | Modeling                                     | 30 |

| 3 | Rela | ited Wo | rk                                           | 33 |

|   | 3.1  | Cohere  | ency Components                              | 33 |

|   |      | 3.1.1   | Efficient Directory Storage                  | 33 |

|   |      | 3.1.2   | Invalidation Multicast Energy                | 39 |

|   |      | 3.1.3   | Efficient Coherence Messaging Support        | 41 |

|   |      | 3.1.4   | Tackling the associativity problem           | 43 |

|   |      | 3.1.5   | Software assisted solutions                  | 44 |

|   | 3.2  | Multic  | ore Architectures                            | 45 |

|   |      | 3.2.1   | Intel Research and Products                  | 45 |

|   |      | 3.2.2   | Tilera TilePro/TileGX                        | 48 |

|   |      | 3.2.3   | Rigel                                        | 48 |

|   |      | 3.2.4   | ATAC 1000                                    | 49 |

|   |      | 3.2.5   | Cyclops-64                                   | 51 |

|   |      | 3.2.6   | Godson-T                                     | 52 |

|   |      | 3.2.7   | Cicso Metro, a.k.a. Silicon Packet Processor | 52 |

|   | 3.3  | Simula  | ators                                        | 53 |

|   |      | 3.3.1   | Single Threaded Simulators                   | 53 |

|   |      | 3.3.2   | Tightly Coupled Parallel Simulators          | 56 |

|   |      | 3.3.3   | Parallel Relaxed System Simulators           | 57 |

|   |      | 3.3.4   | Hardware Accelerated Simulation              | 65 |

|   | 3 4  | Machi   | ne Learning based Design Space Exploration   | 67 |

| 4 | Exp  | oiting Cache Incoherence for Fast Parallel MPSoC Simulation          | 69  |

|---|------|----------------------------------------------------------------------|-----|

|   | 4.1  | Introduction                                                         | 69  |

|   | 4.2  | Target Platform                                                      | 71  |

|   | 4.3  | Motivation and Innovation                                            | 75  |

|   | 4.4  | Simulator Implementation                                             | 76  |

|   |      | 4.4.1 Details of the NoC Interconnect                                | 79  |

|   |      | 4.4.2 Modeling the NoC Interconnect                                  | 80  |

|   |      | 4.4.3 Simulation Challenges                                          | 84  |

|   | 4.5  | Performance Evaluation                                               | 85  |

|   | 4.6  | Accuracy Evaluation                                                  | 95  |

|   | 4.7  | Conclusion                                                           | 99  |

| 5 | A Si | mulation Architecture for Cache-Coherent Manycore Systems 1          | 101 |

|   | 5.1  | Introduction                                                         | 101 |

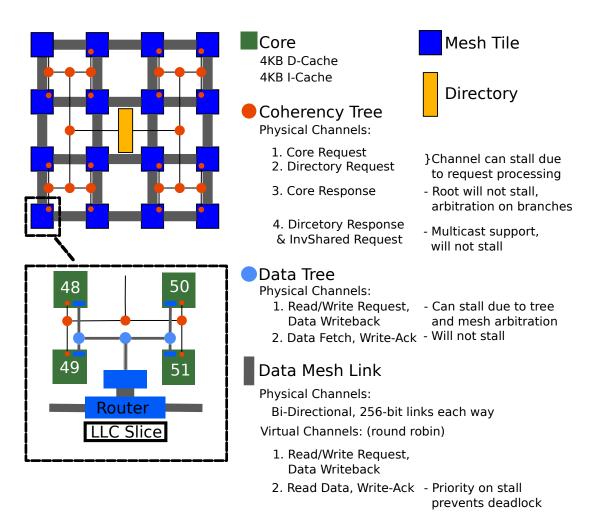

|   | 5.2  | Architectural Summary and Assumptions                                | 101 |

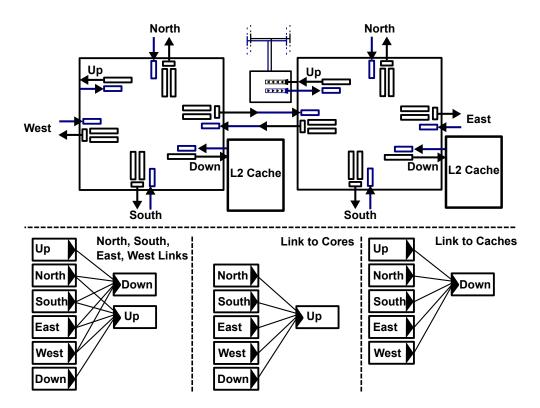

|   | 5.3  | Simulator Construction                                               | 104 |

|   | 5.4  | Instrumentation and Statistics Gathering                             | 105 |

|   | 5.5  | Performance Optimisations                                            | 106 |

|   | 5.6  | Performance Evaluation and Conclusions                               | 109 |

| 6 | A La | tency-Bandwidth Balanced Manycore Architecture 1                     | 115 |

|   | 6.1  | Introduction                                                         | 115 |

|   | 6.2  | Architecture                                                         | 116 |

|   |      | 6.2.1 Design Decisions                                               | 119 |

|   |      | 6.2.2 Data Interconnect                                              | 121 |

|   |      | 6.2.3 Coherency Tree                                                 | 122 |

|   |      | 6.2.4 Coherency Protocol                                             | 123 |

|   | 6.3  | Reducing Bandwidth and Directory Size/Associativity Requirements . 1 | 125 |

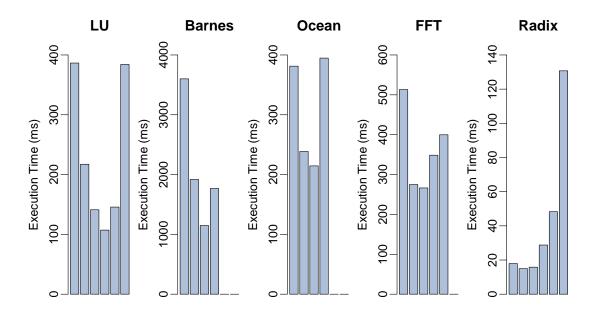

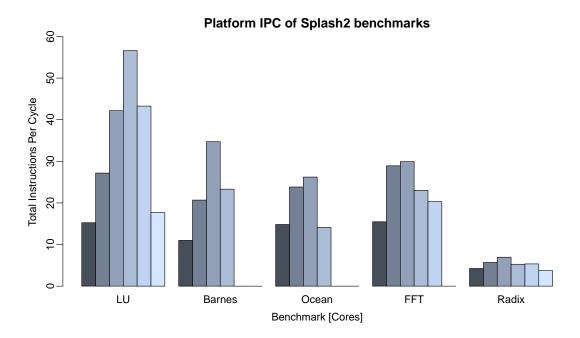

|   |      | 6.3.1 Benchmarks                                                     | 129 |

|   | 6.4  | Architecture Scalability Analysis                                    | 129 |

|   |      | 6.4.1 Performance                                                    | 130 |

|   |      | 6.4.2 Cache Aliasing                                                 | 131 |

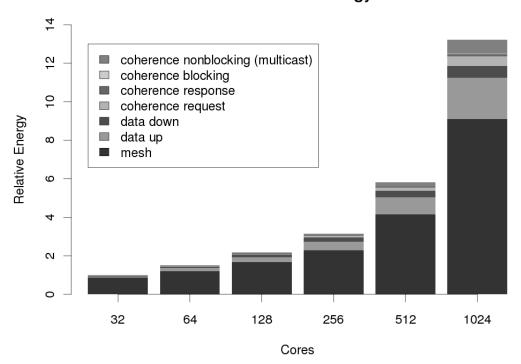

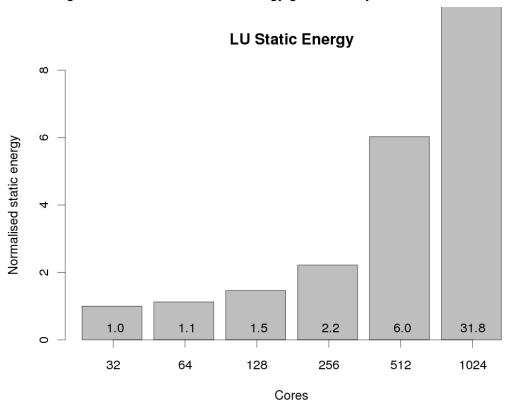

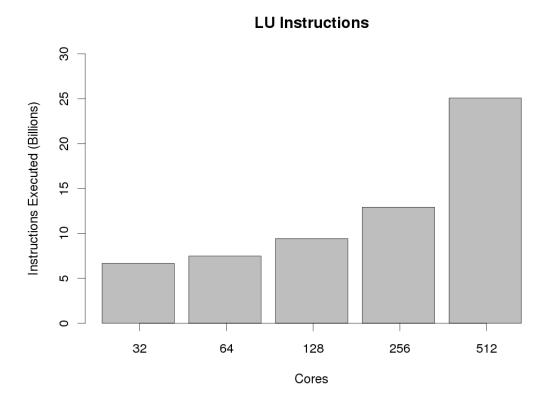

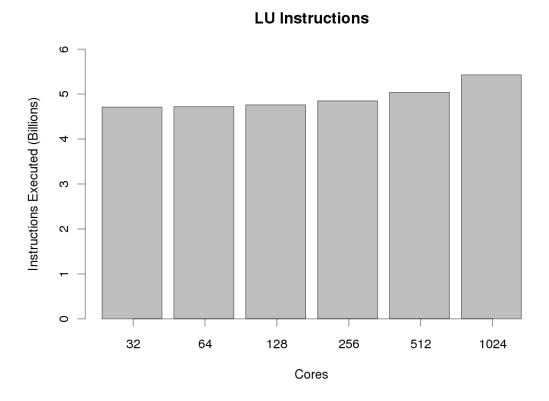

|   |      | 6.4.3 Energy Scalability Analysis                                    | 135 |

|   |      | 6.4.4 Request Latency                                                | 142 |

|   | 6.5  | Page Tracking Results                                                | 143 |

|   | 6.6  | Architectural Conclusions                                            | 150 |

| 7  | Savi   | ng Ene   | rgy in Manycore Processors                  | 151 |

|----|--------|----------|---------------------------------------------|-----|

|    | 7.1    | Introdu  | uction                                      | 151 |

|    | 7.2    | Reduc    | ing Cache Write-Back During Synchronisation | 152 |

|    | 7.3    | Wait-o   | on-Address Hint Instruction                 | 153 |

|    |        | 7.3.1    | Results                                     | 156 |

|    |        | 7.3.2    | Related Work                                | 162 |

|    | 7.4    | Conse    | rvative Tree Encoding                       | 165 |

|    |        | 7.4.1    | Advanced Insertion and Further Extensions   | 169 |

|    |        | 7.4.2    | Synthetic Results                           | 170 |

|    |        | 7.4.3    | Benchmarks                                  | 183 |

|    |        | 7.4.4    | Benchmark Results                           | 183 |

|    | 7.5    | Furthe   | r Work                                      | 184 |

| 8  | A M    | achine   | Learning Based Approach to MPSoC Design     | 187 |

|    | 8.1    | Forewo   | ord                                         | 187 |

|    | 8.2    | Introdu  | uction                                      | 187 |

|    | 8.3    | Relate   | d work                                      | 189 |

|    | 8.4    | Metho    | dology                                      | 189 |

|    |        | 8.4.1    | Hardware Configurations                     | 190 |

|    |        | 8.4.2    | Benchmark Configurations                    | 192 |

|    |        | 8.4.3    | Machine Learning Methods                    | 193 |

|    | 8.5    | Empiri   | ical Evaluation                             | 194 |

|    |        | 8.5.1    | Data Set Generation and Features            | 194 |

|    |        | 8.5.2    | Machine Learning Execution                  | 196 |

|    |        | 8.5.3    | Design Space Transformation                 | 197 |

|    | 8.6    | Result   | s                                           | 197 |

|    | 8.7    | Discus   | ssion and Conclusions                       | 210 |

| 9  | Con    | clusions | S                                           | 211 |

| A  | App    | endix    |                                             | 217 |

|    | A.1    | Archite  | ecture Scalability                          | 217 |

|    | A.2    | Machi    | ne Learning                                 | 230 |

| Bi | bliogi | aphy     |                                             | 241 |

## **Chapter 1**

## Introduction

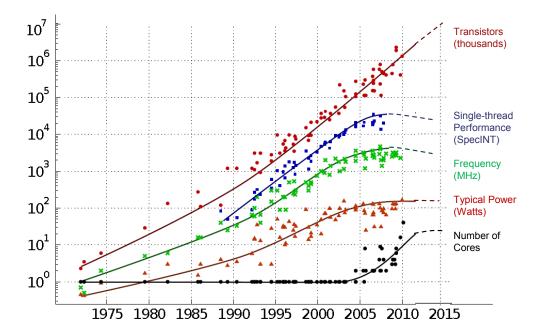

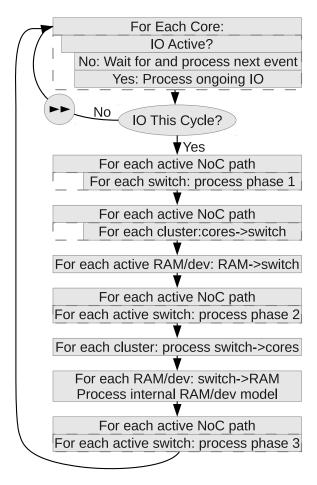

In recent years there have been several factors pushing chip manufacturers to pursue chip-multiprocessors (CMP) with an ever growing number of cores. Moore's Law continues [1], giving us ever more transistors each year, but silicon processes have hit a frequency wall, preventing performance increases by simply raising the operating frequency [2]. There is also very little instruction level parallelism (ILP) left to extract via techniques such as superscalar architectures, known as the ILP wall [3; 4; 2]. These factors are driving chip designers to exploit thread level parallelism (TLP) using both simultaneous multi-threading (SMT) and CMP techniques [5; 6; 7]. These can all be clearly seen from 2005 in the typical Moore's Law graph, Figure 1.1.

On top of this, the power consumed by transistors is no longer scaling down with their size, so while more transistors can still be packed onto a chip, doing so now increases the power consumed, where traditionally the power saved by shrinking transistor sizes would offset the additional transistors used. This means that while extra transistors are available, they cannot be used in power hungry features like those used to aggressively exploit ILP. Simply adding more of the same cores to exploit thread-level parallelism (TLP), without sacrificing per-core performance, will still result in a large increase in power. As a result of the frequency, ILP and power walls, chip designs for applications with significant TLP are looking towards using smaller, energy efficient cores to extract performance. Smaller cores are especially attractive as single core processors scale approximately quadratically in power and area, for linear performance, while an ideal multicore scales linearly in power and area for linear performance gains. This simplified model of course neglects the achievements of features such as clock and power gating to keep single core power consumption low, and the interconnect and synchronisation overheads of multicores. It also ignores the issue of

Figure 1.1: Microprocessor trends from 1970–2010, showing the exponential growth in transistors with Moore's Law. The abrupt end of frequency and single core performance scaling, and growth in power consumption, is clear from 2005 where CMP architectures become popular. Source of illustration: C. Moore (AMD) [8]

Amdahl's Law of parallel speedup [9], assuming that applications are perfectly parallel. As such, the ideal balance between per-core performance and number of cores is highly dependant on the application demands and the constraints of the operating environment. In many cases, from extreme scale super computing to deeply embedded biomedical sensors, there is a delicate balance between providing sufficient performance, while being as energy efficient as possible.

Unfortunately, CMP systems bring new problems which can severely limit the scalability of the system: thread synchronisation, interconnect complexity, and cache coherency.

For small scale CMPs like those in most consumer systems today, which contain between 2 and 8 cores, a simple shared bus or crossbar can connect all of the cores to the shared cache or memory system. This configuration allows for simple snooping coherence protocols, which perform well for such small systems, but are not efficient for more than 8 cores [10]. Manycore processors however (>16 core CMPs), require more scalable interconnects and coherence mechanisms, with the most common interconnects used being the 2D mesh in a tiled architecture, and bi-directional ring bus.

Just because these designs are currently in use, this does not mean they are the optimum choice. The best interconnect may be application dependent, and could borrow elements from multiple interconnect topologies, to provide a balance between the advantages and disadvantages of each. Architectures without a shared bus require more complicated coherence protocols, because memory traffic is not visible to all cores. Less homogeneous multi-core devices such as a multi-processor system-on-chip (MP-SoC), often use less regular interconnects, using network-on-chip (NoC) architectures like Butterfly networks, and may not even support direct core-to-core communication. The best cache coherency protocol is still an open question, and depends very much on the application, the size and design of the underlying architecture, and the memory consistency and programming models to be provided.

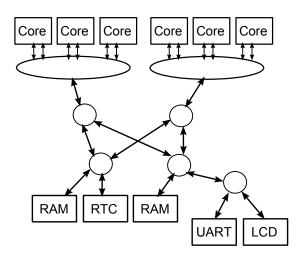

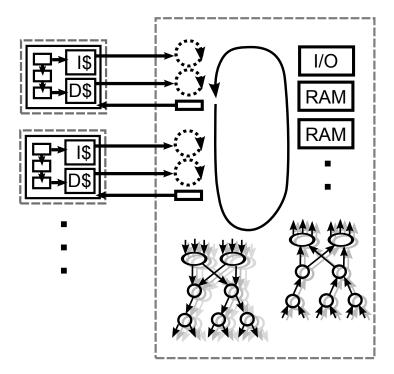

When considering developing a new MPSoC or manycore processor the number of possible design combinations presents a massive design space, such as those in Figure 1.2, with subtle trade-offs and design interactions. To reason about what design is best for a given target application requires detailed simulation of many different possible solutions.

| No.   | ISA             | uArch             | Heterogeneous | s Interconnect | Memory-      | Cache-                        |     |     |

|-------|-----------------|-------------------|---------------|----------------|--------------|-------------------------------|-----|-----|

| Cores | ?               | ?                 | ?             | ?              | Consistency- | <ul> <li>Coherency</li> </ul> | ,   |     |

| ?     | <b>y</b> x86    | Y Interlocked     | Homogeneous   | <b>y</b> Bus y | Model X      | , ?                           | X = | 222 |

| 1 '   | <b>^</b> x86 64 | <b>1</b> In Order | • -uArch      | ີ Ring 🥂       | ` ?          | Software                      | A – |     |

| 2     | ARM             | Super Scalar      | -ISA          | Mesh           | None         | Snooping                      |     |     |

| 100   | ARC             | Out-of-order      |               | -2D            | SC           | Directory                     |     |     |

| 1000  | PPC             | SMT               |               | -Torus         | TSO          | MSI                           |     |     |

|       | SPARC           |                   |               | -3D            | PSO          | MESI                          |     |     |

|       |                 |                   |               | Tree           | RC           | Token                         |     |     |

|       |                 |                   |               | Optical        | C++11        | SCI                           |     |     |

Figure 1.2: Design space state explosion for CMP to manycore processors.

Cycle accurate multicore full system simulation typically is either very slow, requires specialised hardware, or is non-deterministic and lacking in accuracy (i.e. not truly cycle accurate). This means that an architect cannot quickly iterate through different designs to find the optimal solution, and must either settle for a potentially suboptimal solution, or spend many hours waiting on simulation results.

The effort of simulating manycore systems has also left a large number of design issues unsolved, with many issues relating to large scale interconnects and scalable cache coherency mechanisms remaining. Developing a simulator capable of exploring these problems enables the micro-architectural experimentation and analysis required to begin addressing these problems effectively.

#### 1.1 Research Goals

The objective of this thesis was to address three fundamental and interrelated challenges facing the design of future manycore processors: fast and accurate simulation, scalability, and design-space-exploration. One of the most significant impediments to manycore research is the challenge of providing accurate, flexible, and yet high performance simulation models. Without such models, the design of future manycore systems will rapidly become an intractable problem. An initial goal of this research was to advance the state-of-the-art in simulation technologies to significantly increase the simulation speed of truly cycle-accurate models. Using these fast simulation models, the second goal was to investigate issues that constrain the scalability of future manycore processor designs. Key issues in scaling manycore processors include: the interconnect between cores, the coherency protocols used within the interconnect, and the energy efficiency of inter-processor synchronization primitives. One of the aims of this work was to demonstrate that fast models would enable new innovations in these areas to be explored, and to validate the specific novel solutions proposed in this thesis. The third goal of this thesis was to show that fast simulation models can be used to populate machine-learning models, and in turn those models can be used to rapidly search the design space for good manycore architectures.

#### 1.2 Contributions

The primary contributions of this thesis are new techniques which enable much higher simulation rates than have previously been possible for large scale embedded MPSoCs, while maintaining cycle accurate correctness. Using using commodity hardware the results are competitive even against FPGA simulation and prototyping options. Extending this highly accurate simulation platform to explore cache-coherent CMPs, while still improving upon the state-of-the art, this thesis then presents novel techniques for reducing energy consumption of CMPs and demonstrates that scalability concerns of centralised directory architectures can be addressed by extending existing software-hardware coherency techniques. Finally this thesis demonstrates that by applying the high speed, accurate, simulation technologies developed in this thesis to existing machine learning techniques, close to optimal multicore and manycore architectures can be predicted quickly and efficiently for new applications.

Specifically the contributions of this thesis are: Improved simulation performance

1.2. Contributions 5

of multicore, cycle-accurate, simulation through more efficient NoC simulation, by using compact cache friendly data structures, and by tracking packets through NoC regions to reduce the simulation work. Simulation performance has also been improved by increasing the available parallelism in MPSoC simulations, by decoupling the core and interconnect simulation, and exploiting cache-incoherency of embedded architectures to increase the timing slack between simulation threads without sacrificing accuracy. The thesis demonstrates that the combination of these techniques allows for software based cycle accurate simulation rates significantly better than the state of the art, competitive with FPGA based techniques. It also shows that many of these techniques can be used to construct an efficient cache-coherent simulator capable of simulating up to 1024 cores in a fully cycle accurate system, with detailed NoC models, with better accuracy, and higher simulation speeds, than the current state of-the-art in multicore software simulation. This thesis proposes a novel manycore architecture which offers different bandwidth/latency trade-offs, enabling an energy efficient multicast coherency mechanism to address scalability problems with traditional coherency protocols. It demonstrates that existing software-hardware techniques for coherency filtering are capable of addressing the directory-associativity problem without an extravagant hardware directory, reducing pressure on the directory or alternative coherence protocol, reducing the required die space, and reducing energy required to process coherency transactions. This work proposes and evaluates a new hint instruction which can eliminate the dynamic energy used in spin-wait synchronisation primitives, while requiring minimal hardware or program modification. It also proposes an optimisation to the existing atomic-exchange instruction found in many ISAs to reduce cache write-back traffic and cache-line "ping-ponging" for contended mutex's. The thesis then proposes and evaluates a new sharer encoding and multicast scheme which can be used to reduce the interconnect traffic and number of unnecessary cores involved in multicast coherency events, addressing the scalability problem of directory space from the sharer encoding space dimension, and addressing communication bandwidth and latency scalability challenges. Finally the thesis demonstrates that existing machine learning techniques can be applied to the design space of large scale MPSoCs, running mixed program workloads, to enable the rapid identification of near-optimal MPSoC configurations for new workloads.

#### 1.3 Publications

The relevant publications in which the author was primary or co-author are:

- First Author: High Speed Cycle Approximate Simulation for Cache-Incoherent MPSoCs [11] 2013 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XIII)

In this work the author was responsible for all major components of the research, including adding cycle accurate multicore interconnect simulation to Arcsim, developing cache incoherent multi-threaded benchmarks (based on an existing embedded benchmark suite and runtime), and developing NoC models from existing Verilog designs. The author was also responsible for ensuring accuracy against RTL by analysing detailed cycle accurate Verilog based simulation and comparing with cycle by cycle traces from the developed simulator, as well as conducting parallel experiments on FPGA prototype platforms along side the simulator based experiments to verify accuracy of performance counters from full benchmark results. This paper forms the basis of Chaper 4.

- Co-author: Scalable multi-core simulation using parallel dynamic binary translation[12]

2011 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XI)

- Co-author: A Parallel Dynamic Binary Translator for Efficient Multi-Core Simulation[13] 2013 International Journal of Parallel Programming

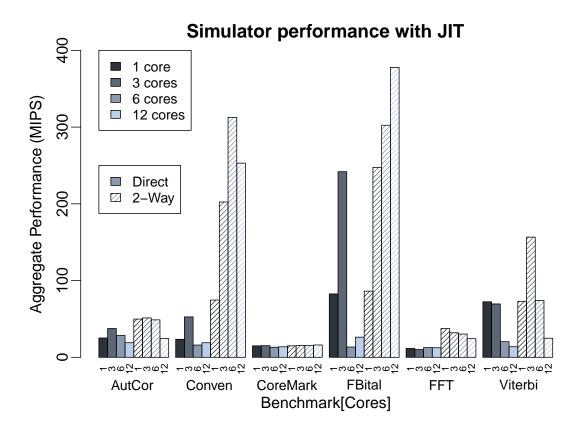

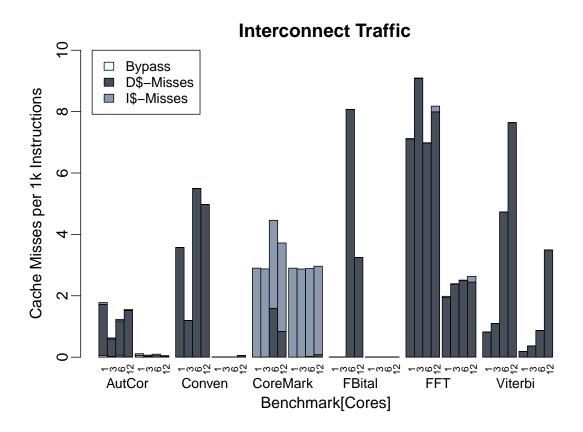

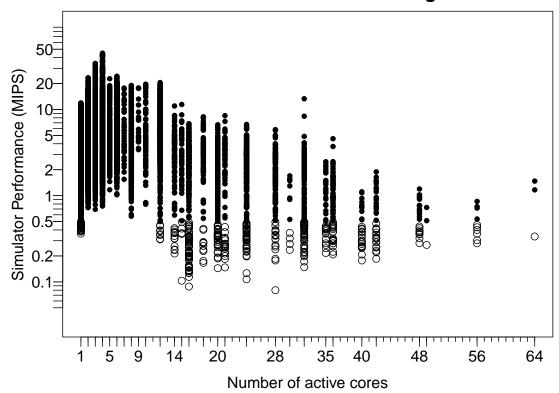

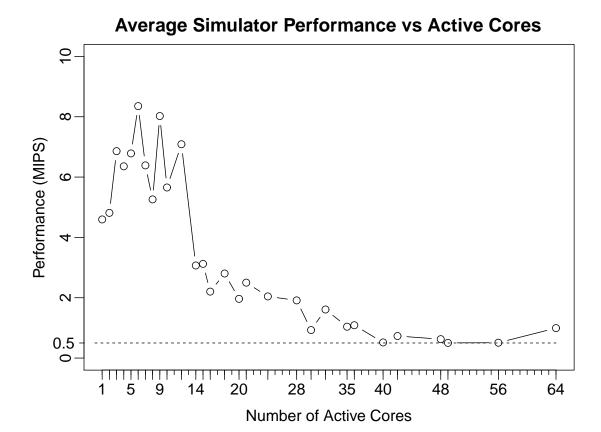

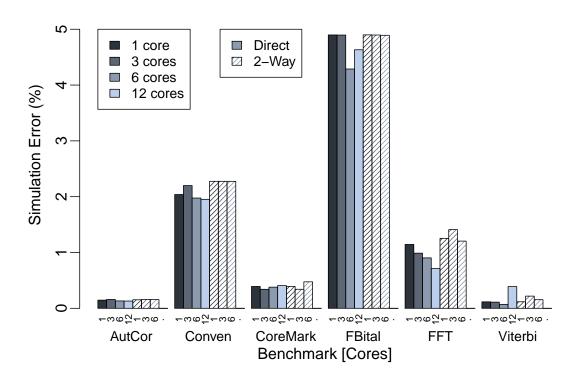

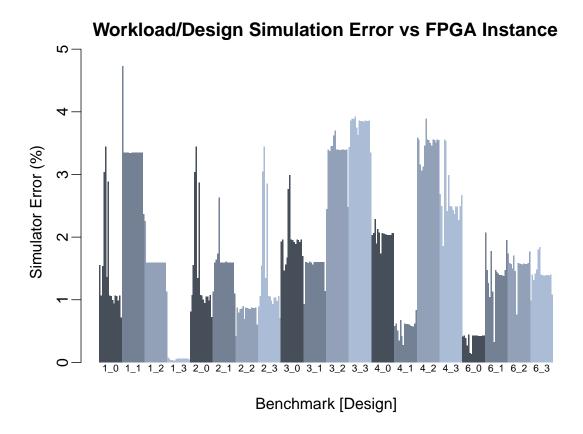

In the above work the author contributed to benchmark porting efforts and analysis of results explaining the unusual performance behaviour as simulations are scaled up and an increasing proportion of the benchmark runtime is spent in synchronisation. The author was also responsible for proposing and implementing a direct-memory-access optimisation for the JIT compiled simulation code, which contributed approximately 30%, on average, to the performance achieved.

#### 1.4 Structure of this Thesis

The remainder of this thesis is structured as follows:

- Chapter 2 presents background information on multicore systems, cache coherency, and system simulation of single and multicore targets.

- Chapter 3 discusses the important related work, relating to each of the sections in Chapter 2 and the work undertaken in this thesis.

- Chapter 4 investigates the simulation of embedded multiprocessor systems, presenting new techniques for increasing the simulation speed and accuracy of multicore simulation.

- Chapter 5 presents the extension of the incoherent simulation work to cache coherent manycore architectures.

- Chapter 6 presents the scalable coherent manycore architecture used in Chapters 5 through 7 of this thesis, along with analysing the scalability of the architecture and the potential for existing software based techniques to address the directory associativity problem often tackled with expensive hardware.

- Chapter 7 presents a novel hint instruction to drastically reduce the energy consumption wasted on synchronisation operations along with another energy saving microachitectural optimisation and novel coherence sharer state compression and multicast scheme, which reduces the energy required to send multicast invalidations, using no more storage overhead than the state of the art.

- Chapter 8 investigates the feasibility of extending previous machine learning based design space exploration techniques to larger manycore embedded systems.

## **Chapter 2**

## **Background**

## 2.1 Parallel Computing Systems

The concept of using multiple processors to increase performance is long-standing within the field. There are a huge variety of parallel computing architectures, with various degrees of coupling between processing elements. The first sections of this chapter look at how programmers can utilise these platforms. Then, because this thesis focuses primarily on integrated single-chip multiprocessors, this thesis looks in more detail at issues which affect shared memory parallelism and on-chip interconnects. The final section of this chapter looks at the challenges of simulating these parallel systems when designing and exploring new architecture and programming options.

## 2.2 Programming Models

Programming these parallel systems usually takes one of two forms, often depending on the underlying architecture of the system:

- 1. Message Passing

- 2. Shared Memory

Ranked in order of increasing coupling, message passing is the most disconnected form of parallel computing. Each processing thread can only communicate with other threads via explicit messages, no thread can inspect or modify another threads' state. In this model, processing elements need only be connected by a form of communication network. This can be a slow network such as TCP/IP, a dedicated on-ship interconnect optimised for the message passing API in use, or an abstraction on top of a

shared memory system, with operating system (OS) provided interprocess communication (IPC). Shared memory systems appear to the running process as if all threads are running in a single, shared, address space. So, if thread A modifies a global variable, all other threads will see this change. The semantics of how soon the new value propagates are dependent on the memory consistency model of the system, discussed in Section 2.3.1.

Both mechanisms have real world implementations scaling from large scale distributed systems, to tightly coupled single chip systems. For example, message passing architectures range from world wide distributed Grid Computing platforms, to exotic dataflow architectures, while shared memory systems can similarly range from large distributed non-uniform memory architecture (NUMA) systems (where different memory regions live on different nodes and must make remote memory requests) down to vector machines (where an array of parallel processing elements operate in a parallel indexed fashion on the same memory space, executing the same program in lockstep, like modern graphics processors (GPUs)). It should be noted that GPU architectures usually do not provide cache coherence for the L1 caches, so there is stronger data coupling in CMP systems, with weaker thread timing synchronisation. Modern GPU systems also relax the thread timing synchronisation, moving closer to a manycore general purpose architecture.

#### 2.2.1 Message Passing

Message passing can be conceptually simpler to program correctly. Data and control flow between the various processing nodes is explicit and clear in the program description, and there are no concerns about data races or mutual exclusion algorithms. The clear separation between local computation and communication makes the programming model much more scalable, and is the predominant means of programming large scale supercomputers (although each individual node may use shared memory parallelism and vector processing).

#### 2.2.2 Shared Memory

Shared memory programming is how most consumer and small scale parallel systems communicate and share information. In the simplest case, all memory is visible to all cores, at the same memory location, so if one thread writes to a variable at address A, any other thread can read from address A and see the new value for that variable.

On modern CMP systems, and older SMP systems with off-chip memory controllers, this is simple because all cores and threads share the same main memory, with cache coherence either enforced by hardware, software, or a mixture of the two. Modern multi-socket machines, and multi-node system, have a less uniform view of the system memory: the address space is partitioned across the different nodes in the system. When a thread needs to access memory, it may need to make a remote memory request, to be served by another node or processor in the system. This is referred to as a non-uniform memory architecture, and the granularity of address space partitioning and allocation, and the protocol for migrating, caching and owning memory regions can vary greatly between different architectures. Because of this, optimisations on a shared memory program for one architecture often do not transfer directly to other shared memory architectures.

## 2.3 Cache Coherency & Memory Consistency

To improve performance, processing cores usually have a small local memory called a cache, which is used to temporarily hold copies of data from main memory, while it is being used by the core. For a single core system, this drastically reduces the time spent fetching data from main memory, but presents a problem when there are multiple processors or cores in a system. Since each core can cache a copy of any data element, it is possible for two or more cores to cache the same element simultaneously, and without any extra hardware or software enforcement, such cores could modify their local copies of the data. The problem here is that there is no way for each core to know if another has modified any data, and if both cores write back their cache lines, one of them will be over written in main memory. The data elements need not even be the same address, so long as they are cached in the same block. This problem is known as cache coherency, and an ideal system should maintain a view of the shared memory space where all cores can see stores from other cores, and accidental writeback masking cannot occur. The term coherency usually refers to the fact that reads and writes from different cores are visible to each other, and Culler et al. [14] provide a more formal definition which explains the property of cache-coherence well:

More formally, we say that a multiprocessor memory system is coherent if the results of any execution of a program are such that, for each location, it is possible to construct a hypothetical serial order of all operations to the location (i.e., put all reads/writes issued by all processors into a total order) which is consistent with the results of the execution and in which:

- 1. operations issued by any particular processor occur in the above sequence in the order in which they were issued to the memory system by that processor, and

- 2. the value returned by each read operation is the value written by the last write to that location in the above sequence.

Fulfilling this definition results in "write-serialization", which means that accesses to a specific memory location (from any processor) are seen in the same order by all processors.

It should be noted that this definition of cache-coherency does not imply any strictness to the ordering of accesses to different memory locations with respect to each other – this is defined instead by the memory consistency model. The stricter the consistency model, the easier it is to reason about program behaviour and write programs. However, the more relaxed models allow for more aggressive hardware optimisations and less hardware coherency synchronisation, giving better performance. Some processors, like the Sun SPARC architecture, allow the user to switch between multiple models, allowing them to pick the balance they would like, while most consumer systems such as x86 and ARM have a fixed model.

Almost all consumer CMPs provide cache coherency, but deeply embedded MP-SoCs forego cache coherency to reduce hardware complexity and power consumption. Because hardware-enforced cache coherency can be expensive, and lead to performance interference between different cores, putting the task of managing memory consistency in the programmer's hands can allow for better control of worst case execution time and a cheaper, more energy efficient end solution. This is a level of programming complexity which most programmers do not want to deal with however, and most software assumes relatively strict cache coherency and memory consistency guarantees. There are also coherence strategies which use only software [15; 16] and can be assisted by the compiler [17].

#### 2.3.1 Memory Consistency Models

When multiple threads of execution on different cores perform a series of memory load and store operations, the memory consistency model defines exactly what orderings are allowed on a given system. These range from the strictest – sequential consistency (SC), to much more relaxed schemes, like release consistency (RC). This section describes a few of the more popular memory consistency models, although a more thorough introduction to these and more memory consistency models may be found in Adve and Gharachorloo's tutorial [18].

#### 2.3.1.1 Sequential Consistency

Sequential consistency (SC) is the strictest of all consistency models. It requires that all threads and cores in the system see the same ordering of all memory operations. This ordering must be equivalent to a possible interleaving of all thread executions on a single time multiplexed in-order core. In other words, the memory accesses are all in program sequential order, with a single global ordering [19].

#### 2.3.1.2 Total Store Order

Total store order (TSO) is the next most relaxed form of consistency, which relaxes SC and allows load operations to be executed in any order. There does not need to be a globally agreed ordering for load operations, however all store operations must complete in a globally agreed ordering – total store ordering [20]. This means that if two cores make a store operation, all cores see them happen in the same order. Memory fences are used on loads to ensure they do not overtake the global store order view, so when a core completes a store operation, a subsequent load cannot see a stale value for a memory location which had a store from another core that committed before its own in the global ordering.

TSO is the memory consistency model found on the x86 processors [21] used in most consumer systems, and is also supported by the Sun SPARC architecture [22].

#### 2.3.1.3 Partial Store Order

Relaxing TSO further, partial store order (PSO) does not guarantee stores from a particular core will appear in memory any particular ordering, with memory barrier instructions required to enforce a particular ordering between two memory operations [22].

#### 2.3.1.4 Release Consistency

Release consistency (RC) is one of the most relaxed consistency models available. Instead of enforcing an order on all load or store operations, it introduces new instructions, with acquire and release semantics. All standard memory operations can appear in any order to other cores, except that on acquire all external stores that were issued before a release are visible, and on a release, all local stores so far are committed and visible. This ensures that the shared memory regions are consistent across memory synchronisations primitives such as a mutex (when to acquire the lock one would involve an acquire instruction, and on release one would similarly involve a release instruction). However, if proper thread synchronisation primitives are not used, there are no guarantees about memory orderings.

#### 2.3.1.5 C++11

The new C++ standard includes a memory consistency specification, allowing for relaxed and atomic memory operations. Programs that need the extra performance of a relaxed memory consistency model can explicitly annotate memory accesses to allow the compiler to avoid emitting memory fences. For memory with extremely relaxed requirements it may be possible to avoid hardware coherency at all (although it may be necessary to track dirty bytes or words in the cache, to prevent over-writing new data with stale, i.e. to provide memory coherency, without the memory consistency or in-cache coherency requirements). How future platforms' coherency and consistency models are adapted to closely model the C++ standard will be an interesting development to watch.

#### 2.3.1.6 Transactional Memory

A completely different approach to parallel programming is encompassed by the concept of transactional memory. This model allows a thread to build up a "transaction" of memory operations, which only finally commit to be visible to the rest of the system if a final condition check is met. This is a popular method for speculative execution, where a thread speculatively takes a lock, operates on a data element, and then commits back the changes if and only if the lock was successful. This allows the internal processor architecture to operate efficiently on the task, while the speculative lock is in flight through the coherency system. An efficient speculative system will kill the thread as soon as the lock returns with a failure, but speedups can still be achieved letting the

thread run to completion if there are enough other cores to take on other speculative tasks. Performing this in software has typically been too expensive, but there have been experimental research platforms such as Atlas [23], and Intel has recently incorporated some hardware transactional memory support into its processors [24]. Transactional memory operations are one area where incoherent memory regions could be used: with a high enough compute-to-data ratio the thread may operate speculatively within an incoherent buffer, then commit back to coherent memory space upon completion. It could also be possible to use large scratchpads or the data-cache as a write-buffer (speculation would have to halt until it was no longer speculative if the cache required a dirty write-back or the scratchpad was full, however).

One form of this transactional memory style operation is a technique called Speculative Lock Elison (SLE) [25] which allows speculative parallel execution of critical sections provided by a mutex lock. SLE begins speculation at the lock acquire instruction sequence, but does not acquire the lock, and continues executing the code path for the critical section until the lock release instruction are reached. If at any point a coherency conflict is detected – a memory location read within the critical section is written to by another processor, or a memory location stored in the critical section is read by another processor – this causes the speculation to abort and either re-attempt speculation, or fall back to actually acquiring the lock and progressing with traditional execution. The processor may attempt to speculate a number of times before resorting to actually acquiring the lock. The speculation must also be aborted if there are insufficient resources to track all memory locations accessed during the speculation, or of the speculation mechanism cannot track any more register changes.

Transactional operations like this can be more efficient than traditional synchronisation because coarse grained locks may protect multiple sensitive memory locations, depending on the control flow within the critical section (such as a lock on a hash-map), and fine-grained locks can incur more significant overheads in terms of synchronisation impact of acquiring these locks, and memory space for storing them (along with the cache-affects of how and where these locks are stored relative to the data they guard and other locks in the code). By speculatively executing through the critical section coarse grained lock regions can be effectively executed in parallel, and only abort and serialise when a true dependency is encountered, speculating fine grained lock regions can remove much of the synchronisation overhead while still providing correctness. SLE is an effective transactional approach because it can be applied to existing code without any changes (and in some cases can be automatically be applied by

the hardware without re-compilation). The fact that critical sections are often short (a requirement to avoid lock contention) means that the resources needed in the processor to speculatively execute them are quite minimal over what already exists for coherency and branch prediction support.

## 2.4 Coherency Mechanisms

Cache coherency is usually maintained via Snooping or Directory based protocols [26; 27], although more alternative protocols such as Token coherency have been proposed. Each of these broad classifications encompasses a large variety of different protocols.

#### 2.4.1 Snooping

One of the simplest means of ensuring hardware coherency [27], and one of the earliest implemented for microprocessors [28] is a technique called snooping. This relies on all processors using a shared bus to memory, where every core can see the memory requests of other cores by "snooping" the bus. Many of these snooping protocols can be implemented using an alternative broadcast scheme for coherency messages, separate from the memory interconnect.

#### 2.4.1.1 Write-through Invalidate

The simplest protocol is to use a write through cache with a write-invalidate protocol [27]. This allows any core to load any value into cache at any time, because the main memory is always up to date. If they see a store on the bus they invalidate their local copy, and must fetch an updated copy from main memory or a shared cache level the next time they require the value.

#### 2.4.1.2 Write-through Update

With these protocols, instead of invalidating cached copies upon witnessing a write, all the snooping caches take the new value off the bus to update their local copies. This requires the snooping coherency controller to have a port into the data store of the cache RAM however, while write-invalidate only requires the coherency controller to write into the tag RAM.

#### 2.4.1.3 Write-back Invalidate

Obviously write-through caches have a significant performance impact for write-heavy workloads. Also it is often undesirable to broadcast writes because this requires every memory write to gain bus arbitration, and spend energy transmitting the data. As such a variety of write-back invalidate protocols have been developed, usually named after the coherency states involved, which have been shown to be significantly more energy efficient [10].

- MSI: The simplest write-back scheme, Modified-Shared-Invalid, assumes that any clean cache line is shared, and to perform a write it must send all of the sharers an invalidate signal, transitioning the local line the Modified state, and all others to Invalid. To access a cache line which another core has in the Modified state, the modified cache line must be written back to memory and either changed to Shared or Invalid, depending on if the new core wishes to load or store from the address.

- Write-once: This protocol [29] is a hybrid write-through and write-back protocol with states Invalid, Valid, Reserved and Dirty. When a processor first writes to a clean memory location, it performs a write-through operation which both informs all other cores to invalidate their copy, and updates the backing memory store, the cache line now changes to the Reserved state. A subsequent write transitions the cache line to Dirty. Upon a read from another core, the Reserved state would simply revert to Valid, and the second core can retrieve the value from memory, however from Dirty, the first core must block the main memory from providing the data, and provide the data directly. The data should also be written to backing store, and the state transitioned to Valid. If another core wishes to make a write, a similar series of events takes place except the original core will arrive at the Invalid state. This is very similar to MSI, except the first write performs a write-through to optimise the touch-once then share access pattern.

- MESI: Modified-Exclusive-Shared-Invalid [27] is an optimisation of MSI where

a cache line currently in use by a single core is marked as Exclusive, rather

than Shared. This allows the core to promote it to Modified without sending a

message to the other cores in the system, and transitioning from Exclusive to

Shared does not require a write-back.

- MOSI: Modified-Owner-Shared-Invalid is another extension of MSI in which a cache can take ownership of the most up to date value of a cache line. This means once a cache line has been modified and another core requests it, the core with the modified line can transition to Owner of this cache line, and serve all requests for the modified cache line, until it writes back to main memory sometime in the future. The owned state can also encapsulate the Forward state of MESIF, if Owned-clean states are allowed.

- MOESI: [26] This is an obvious combination of the MOSI and MESI states, to

enable serving of modified cache lines from the owning core, while also incorporating the Exclusive state optimisation.

- MESIF: Proposed by Intel [30], this protocol substitutes the Owned state for a Forwarding state. Unlike the Owned state, the Forwarding state must always be clean. Introduced to optimise the case where a cache miss is fulfilled by another on-chip cache, this state allows exactly one cache to respond, rather than all Shared state caches [31].

#### 2.4.1.4 Write-back Update

The final set of protocols allow the update of remote caches, while avoiding write-back to main memory for every store operation.

• Firefly: [32] This protocol contains three states, corresponding to the M, E, and S states of MESI. Some argue that because there is no invalidation in Firefly that it does not have an Invalid state, but when cache line has no contents because it is cold then it could be considered Invalid. If a cache line is held clean by a single core, it is Exclusive, this can transition to Modified without signalling other cores, or transition to Shared if another core makes a request for the cache line. If the cache line is Modified and another core requests it the cache line must be written back to main memory and transitioned to Shared. Once in the Shared state the cache line remains in this state until it falls out of all caches due to capacity or conflict misses over time. A write to the cache line while in the Shared state acts as a write-through update operation, where both the main memory and all snooping caches are updated at the same time. For this reason sometimes Firefly is classified as a write-through update protocol, even though the single sharer case is a write-back behaviour.

• Dragon: [33; 32] A very similar protocol to Firefly, Dragon differs by differentiating the Shared state into Shared-clean and Shared-dirty, equivalent of the Shared and Owned state of MOESI. A write to a shared cache line in Dragon requires updating all snooping sharers, but does not write back to main memory, making it more efficient than Firefly. The most recent writer to a cache line takes the Shared-dirty state, while all others are Shared-clean. It is the responsibility of the Shared-dirty cache to fulfil cache line requests and write-back to main memory on eviction (which will be due to self invalidation from capacity or conflict misses).

#### 2.4.1.5 Snoop Filtering

To reduce the accesses to all caches when broadcasting invalidation or fetch requests, and traffic for more complex interconnects, it is possible to add special filtering controllers to various points on the bus. These reduce accesses to caches which don't contain the data by storing an approximate but conservative overview of the sharing state, which can be used to remove cores from the broadcast operation when it is known that it definitely has not cached this data. One mechanism is to create a form of directorylike cache which sits on the bus and is responsible for actually sending out broadcasts. When it has information about the cache line it uses this to reduce the broadcast to a multicast, but if the cache has over-flowed it will send a full broadcast. This can save on energy when a cache line is being rapidly passed between a subset of the cores in the system. Another snoop-filtering mechanism is to put Bloom-filter structures in front of each core, or clusters of cores, to track addresses that have been recently cached. The Bloom-filter with either guarantee that a cache line is not present, so the request will not propagate to the cache, or return that the cache line may be present, so the request must be forwarded. So long as the energy to maintain the Bloom-filter is less than the energy to access all of the cache it guards there is the potential to save energy. If the cache tag RAM has a limited number of ports it may also improve performance, since the core will have to arbitrate with bus snooping requests less often.

#### 2.4.2 Directory

Directory protocols are a more scalable solution which do not require the cores to constantly snoop and broadcast to each other, instead a dedicated structure is used to track the state of cache lines in the system, and is used to coordinate the cache line coherency state transitions. On older multi-processor systems, which use discrete processor chips, it would be more likely that a full directory is implemented in main memory, to store the sharing state for every cache line in the memory space. This has a very large memory overhead, but allows the simultaneous caching of any and all cache blocks in the system. For multiple processor chips the first common level in the memory hierarchy is the main memory, so this is an obvious level at which to perform the directory service. On-chip directories can either act as a directory-cache for an off-chip full directory, or maintain directory information just for memory blocks currently residing in cache. Both on- and off-chip directories need not be centralised, and can instead be distributed across last level cache blocks, or processor nodes in a large scale multiprocessor system. Distributing the directory enables higher throughput, at the expense of complicating the directory coherence protocol.

For inclusive cache hierarchies the sharer information can simply be kept in the last level cache (LLC) tags, maintaining the directory information without dedicating a whole new directory structure. However for large scale systems, a fully inclusive shared cache can become undesirable, and the directory structure must either become extremely large and associative to allow all on-chip caches to be fully utilised, or accept that it cannot contain the maximum number of unique cached memory blocks' sharing state.

#### 2.4.2.1 Sharer-reconstruction

Instead of requiring the directory to hold all on-chip cache state, the directory can instead be used to cache a subset of the cache state, providing efficient coherency transitions when possible. When there is a miss in the directory, a broadcast probe must be sent out to reconstruct the sharer information from the processors in the system. This can provide good performance when the application benefits most from full utilisation of the on-chip caches, but suffers the high energy and performance cost of having to snoop the whole chip whenever there is a cold cache miss or the working set is significantly larger than the on-chip caches [34].

#### 2.4.2.2 Forced Invalidations

An alternative to snooping to reconstruct sharer state is to instead invalidate cache entries when the directory becomes full and needs to replace an entry. This saves the expensive snoop on a directory miss, but can reduce performance by limiting the utility

of on-chip caches if the directory is not large or associative enough. Previous work has shown that this is more scalable than the snoop filtering approach [34].

#### 2.4.2.3 Off-chip Backing Store

Instead of discarding directory overflows, it is possible to overflow the on-chip directory to a dedicated region of main memory. This can be handled either by hardware, or trap to a software handler. There are two aspects of the directory which can overflow, the number of cache line entries, or the sharer list for a given entry, examples of each are discussed in Section 3.1.

#### 2.4.2.4 Highly Associative Directory Caches

Various work has been done in increasing the apparent associativity of the directory cache to cope with the high associativity of the on chip caches (an N core CMP with M way set associative caches requires an  $M \times N$  way associative directory structure for full coverage). These have predominantly focused around using different hashing functions to index into different ways, to reduce aliasing between different cores' caches, allowing them to use larger sets, but fewer of them, to reduce parallel lookup energy and time. The main work is encompassed by the Z-Cache [35], Cuckoo Directory [36], and Scalable Coherence Directory [37] (SCD) papers discussed in Section 3.1.

#### 2.4.3 Other Sharer-Tracking Mechanisms

#### 2.4.3.1 Token Coherence

Rather than have a directory structure to track all sharers, Token Coherence [38] works using broadcasts in the same way as a Write-back Invalidate snooping protocol, but enabling correctness on unordered interconnects by using tokens. With Token Coherence each cache block has an associated number of tokens, T, the exact number is not important to the correctness of the protocol but limits the number of sharers which can simultaneously hold a read-only copy of the data. The tokens reside in caches, main memory, and in-flight transactions, but exactly T tokens must exist at all times for every cache line. This requires additional memory space to store the token count for cache blocks which are not live in the processor caches, and extra bits in each processor cache line. For a read operation the processor requires at least one token, while for write operations all tokens must be held. This token protocol ensures that all tokens

for a cache line contain the most recent cache-line data, which is only modified when all tokens are together at a single core. The token policy ensures correctness, but the mechanism by which tokens are acquired depends on the specific performance policy implemented, with TokenB (Token Broadcast) for example making a full chip broadcast for both read and write misses. If a read request is received at a core or cache, then a single token is sent back with a copy of the cache line data and the local count reduced by one, if a write request is made then all tokens must be returned. When a cache line is self-invalidated then the token count must be written back to the next level of cache or memory hierarchy. When races occur, such as two concurrent writemisses to the same cache line, a time-out on the transaction is used to ensure that cores which fail the transaction make a subsequent attempt after a fixed delay. To prevent starvation, after four consecutive failed requests a special Persistent request is made. Each processor has a small table to record any pending persistent requests, and the processor will always forward tokens for this cache line to the requesting processor to ensure that it is satisfied. It has been shown that for a 16 core processor, across a range of benchmarks, requests are only re-issued for 2-3% of transactions, and persistent requests only required for 0.1-0.3%.

Token coherence can require a lot of cross chip traffic, but its point-to-point style of communication is well suited to a highly connected architecture such as a mesh or torus, however the broadcast requirements can be challenge to the on-chip bandwidth without hardware broadcast or multicast support [39]. While other performance policies such as TokenD (Token Directory) and TokenM (Token using Multicast) reduce the bandwidth requirement, the number of bits required to track the token counter, along with the cross-chip traffic cost, both scale poorly when considering architectures with hundreds of cores and workloads which require whole-chip data sharing.

#### 2.4.3.2 Sharer-Chaining

Alternatively an in-hardware linked list of sharers can be used in a similar fashion to Scalable Coherence Interface (SCI) [40]. This method allocates every cache block a home node (like a distributed directory), where only a pointer to the first sharer is stored. Each core that holds a cached copy then joins the linked list by holding a pointer to the next core in the list. To read the cache line, a core must send a request to the home node. Then it will be inserted into the start of the linked list, with the home node pointing to it, and it pointing to the core which was previously at the start of the list. When a core wants to write to the address, it must walk the linked list

sending invalidations, until it has received all responses, the home node entry is locked to prevent read requests progressing until the write is complete. A similar process must occur if the home node runs out of capacity and must evict the entry for this cache line.

#### 2.4.4 Software Managed Coherency

Not all platforms provide transparent hardware coherence, but it is possible to use the operating system and traditional MMU memory protection features to provide a running application with the illusion of cache coherency, and even provide a distributed system with the appearance of a single shared memory space. These work by marking shared pages as read-only, then on a write fault communicate with other processors in the system to arbitrate write access and disable the other read-only pages (depending on the memory consistency model), before allowing the processor to promote its page to writeable. If another processor has a read-fault on this page, it will request a "diff" or full copy from the core which modified the page. There has been work on optimising this process [41] and relaxing the memory model to allow multiple writers to the same page. There are also hardware assisted techniques to automatically handle remote memory accesses, where pages which are often modified are pinned to a single core, somewhat like the Owned state in the MOSI protocol, except that writes may be stored directly to the remote cache, without a local duplicate being created [41].

It is also possible to use techniques like this to simply reduce the demands on the hardware coherency system, to isolate pages that do not require coherency (such as code pages and thread local memory) and only run hardware coherency on pages for which it is necessary.

On deeply embedded systems without any form of page protection, it is up to the programmer to manage cache behaviour and ensure there is no write-masking. Special cache-bypassing instructions can be used to synchronise cores and coordinate the flushing of caches as necessary. Systems like this can be easier to program using an abstracted message passing library, leaving the complicated cache management to the expert library writer.

Software based coherency can also benefit greatly from compiler support [17], although the results of many studies comparing software and hardware coherence has been inconclusive, due to the different circumstances under which each is preferable [42]. Like many things, a compromise where some hardware support is provided, but software only uses it when necessary, is probably the optimal solution.

# 2.5 Architecture Scalability

When designing a CMP or MPSoC architecture there are a lot of areas that are a scalability concern, the most dominant being the performance of the cache coherency mechanism, and the properties of the interconnect joining the cores, caches, and other onchip components. This section will focus on the scalability of the interconnect options.

## 2.5.1 Buses and Crossbars

The shared bus, and the crossbar are two of the most poorly scaling interconnect options. The shared bus is a single communication link that is shared and arbitrated for all components, connecting all cores to the memory system. This allows the simple implementation of snooping coherency, but scales poorly as more devices are attached to the bus. Ignoring physical constraints at first, the bus bandwidth must be shared between all devices, this means that the per core bandwidth scales as  $^1/_N$ , where N is the number of cores in the system. When the electrical characteristics of the bus are considered, adding more devices requires the bus to grow approximately linearly with the number of devices. Unfortunately, the longer the bus, the greater its electrical capacitance, so the bus must operate at lower frequencies or be driven at a higher voltage. The wire lengths along with the number of devices will also affect the complexity of arbitration, and how quickly it can be resolved. This all means that the frequency and bandwidth of the bus itself may have to be reduced, making the per core bandwidth scaling worse than  $^1/_N$ .

Unlike a shared bus, a crossbar allows all connected devices to send a message to another device simultaneously, so long as there is not a conflict at the destination. This interconnect is good for core-to-core communication, or NUMA systems. One of the largest crossbar architectures actually produced is probably the 80-core Cyclops-64 [43] (discussed in Section 3.2.5), produced by Cray to be used as nodes in a supercomputer. Unfortunately crossbars cannot be used with passive snooping, so a snooping based coherence protocol would require dedicated request and acknowledge messages. They also scale extremely poorly in terms of area when adding more nodes, and when increasing the width of the connection.

25

### 2.5.2 Mesh and Tiled Architectures

One of the most popular manycore interconnects is the 2D mesh, used to build a tiled architecture. The 2D mesh has many traits which make it an obvious choice when designing a scalable architecture:

- bandwidth scales linearly with the number of nodes

- area overhead per node is constant, each new node requires the same router and connecting wire overhead

- switch radix is constant, all routers are the same, and adding more nodes does not increase the number of ports required on each

- supports core-to-core communication

- redundant routing for fault tolerance

- short wires, so the links can be run at high frequencies.

Unfortunately the downsides to mesh topologies are:

- average node to node latency is  $^2/_3\sqrt{N}$

- every router is at least  $5 \times 5$ , which is quite large, and can take multiple cycles to route

- hard to verify that complicated routing rules and virtual channels are free of deadlock

- no simple multicast or broadcast scheme

- no single point of serialisation for coherency protocols, which requires more complex protocols with a greater number of messages.

#### 2.5.3 Tree and other NoC architectures

There are other interconnects that trade off bandwidth in return for latency, and use much simpler switches. One of the simplest conceptually is a binary tree (or H-tree, named for the shape it takes when routed on a chip), where a central last level cache or coherency controller might reside at the root. The tree may also be used without a root node, in a point to point communication fashion, where messages get reflected back

up the tree when they have reached the first common node. This would resemble each half of the chip being an H-tree fanout, with the root of each tree linked to connect the two halves of the chip together. Picturing it like this makes the downside of the tree obvious, the bisection bandwidth is that of the single link between the two roots.

The benefits of tree based topologies are:

- switch area overhead per node is approximately constant, N nodes require N-1 switches

- node to root latency is log 2N

- switch radix is constant, all routers are the same, and adding more nodes does not increase the number of ports required on each

- every router is  $2 \times 1$  (or  $2 \times 2$  if core-to-core routing is enabled at all levels), which is small and fast to route

- supports core-to-core communication

- centralised point for coherency transactions if a coherency controller such as a directory is placed at the root node.

Unfortunately the downsides are:

- bisection bandwidth is limited to a single link, like the shared bus

- no redundant routing for fault tolerance

- long wires at the root of the tree, so operating frequency may be limited.

The bandwidth concerns can be mitigated slightly by using Fat Trees [44], which use higher bandwidth links between the lower nodes and the root, but this does not help for small packets. Long wires can also be split with registers, but this introduces extra latency and can complicate arbitration policies.

Between the extremes of the mesh and tree architectures, are other multi-state logarithmic networks, such as the delta networks: Omega, Butterfly, Baseline, and Benes [45]. These all work by implementing a perfect shuffle network between the source and destination, taking  $\log 2(N)$  layers to do so.

2.6. Simulation 27

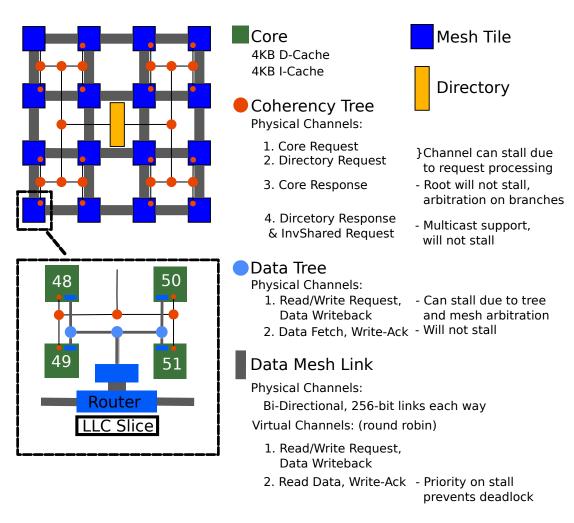

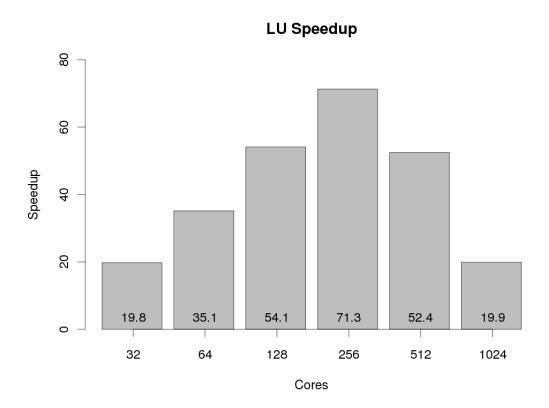

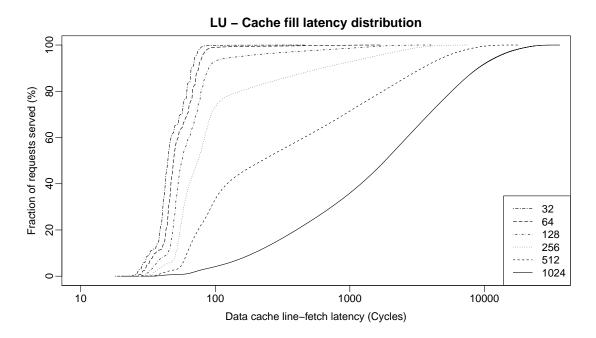

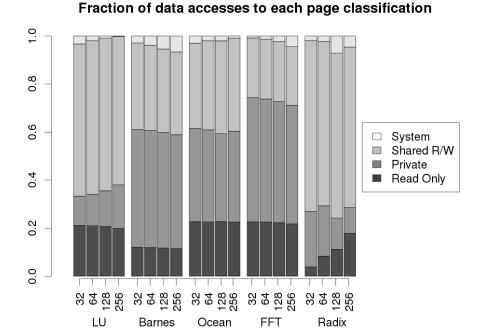

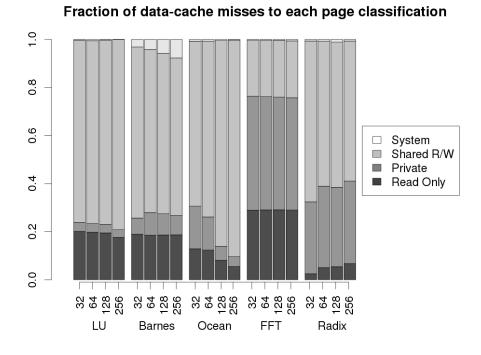

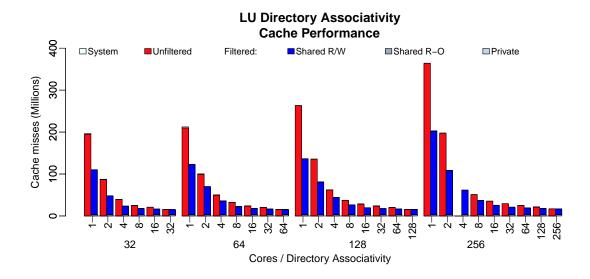

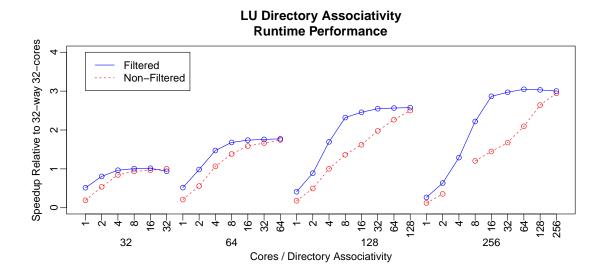

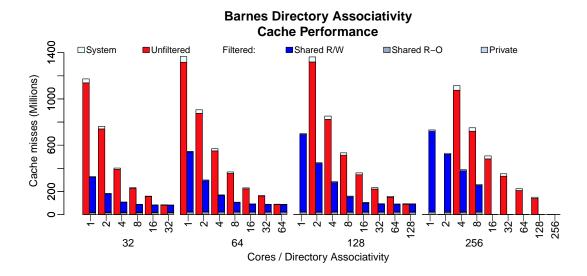

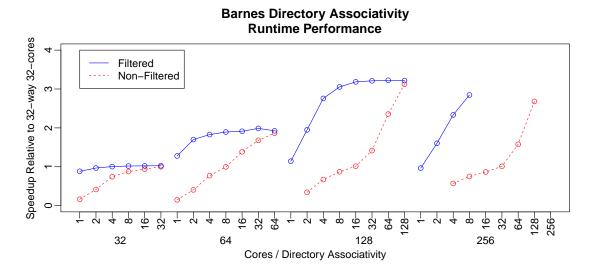

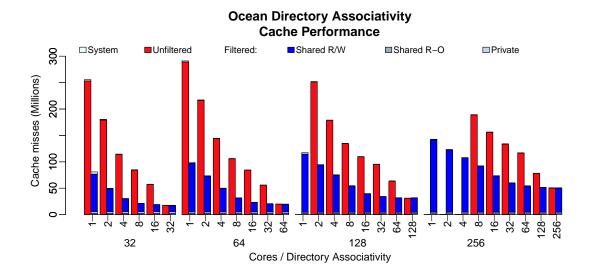

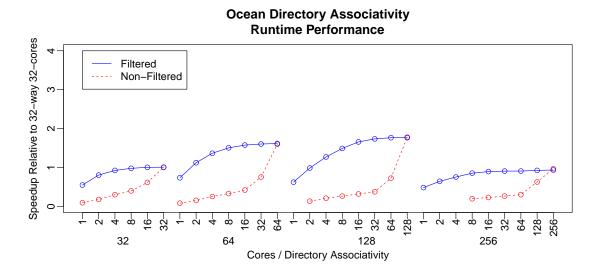

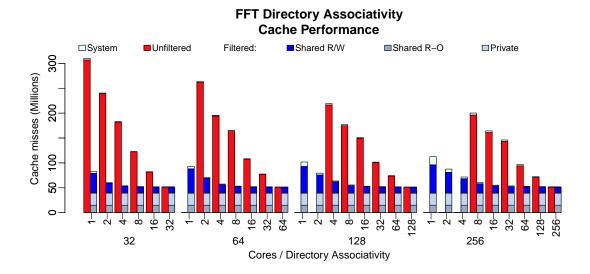

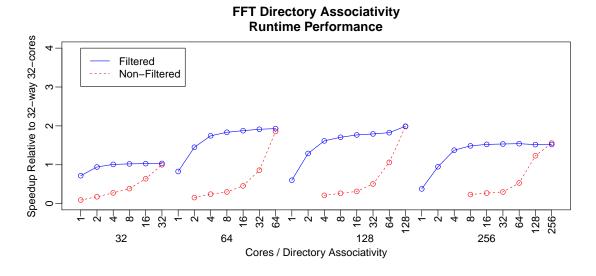

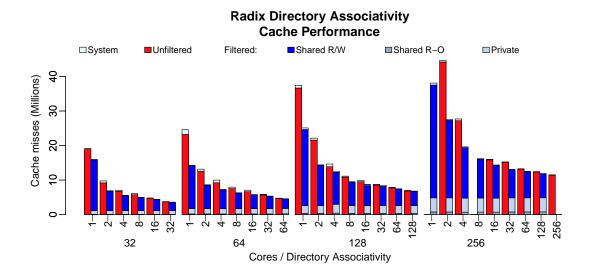

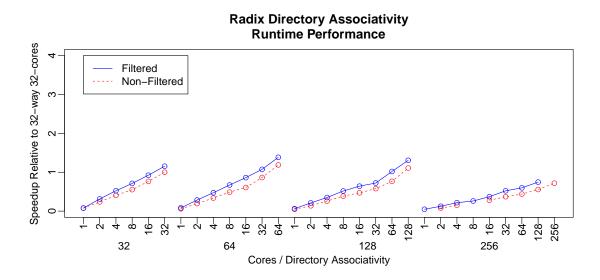

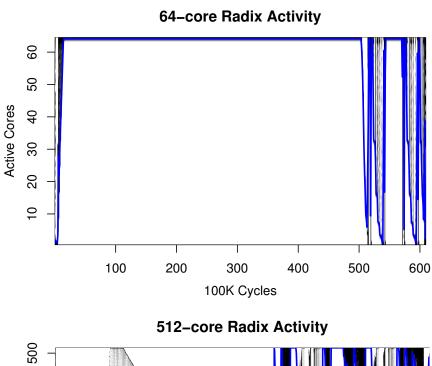

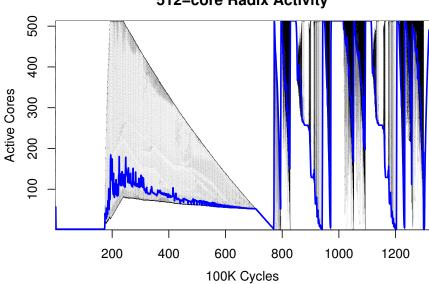

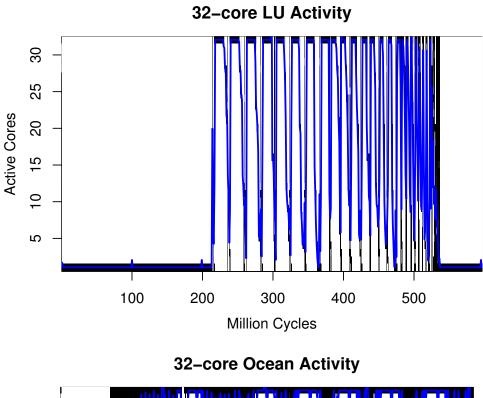

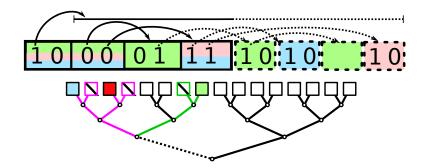

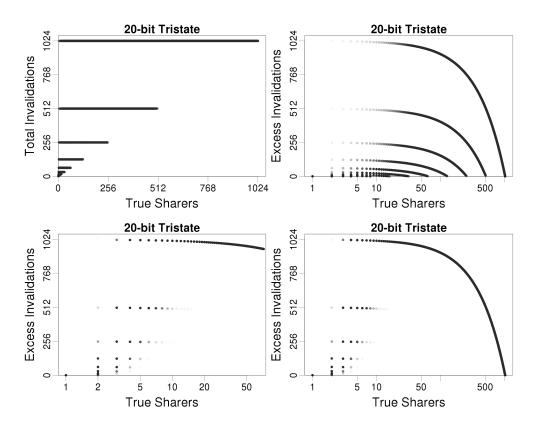

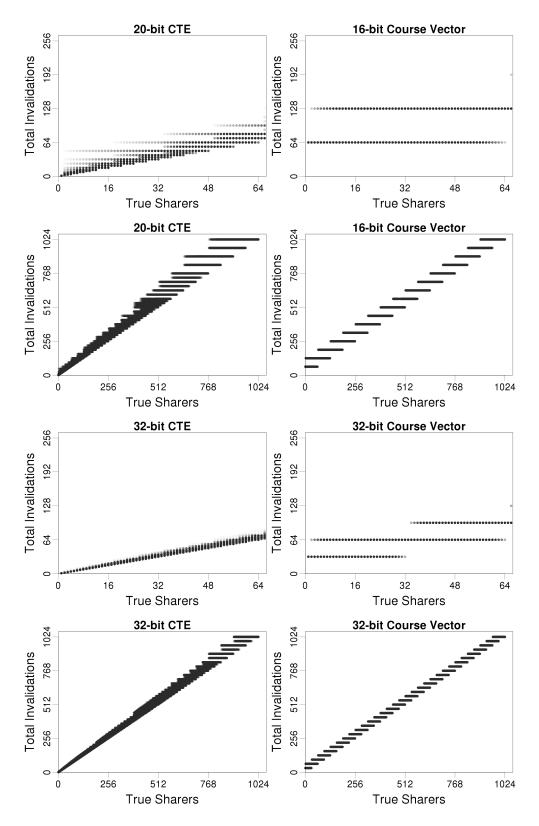

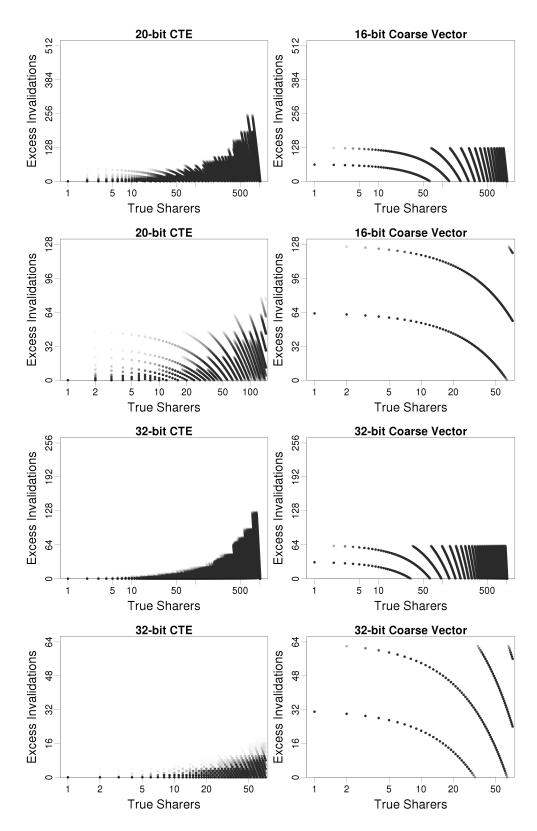

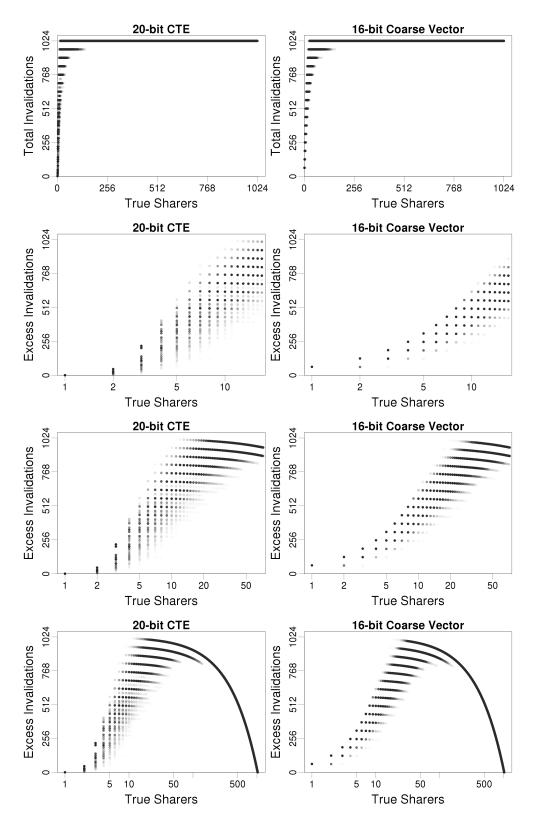

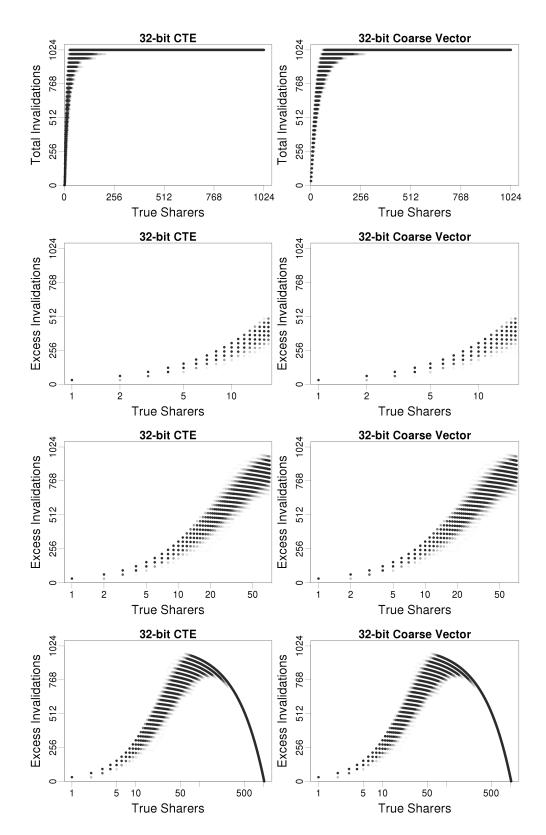

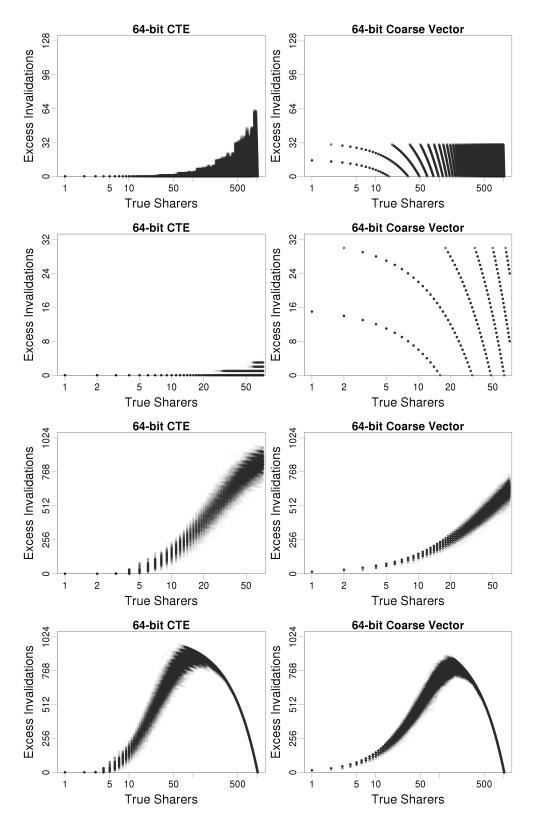

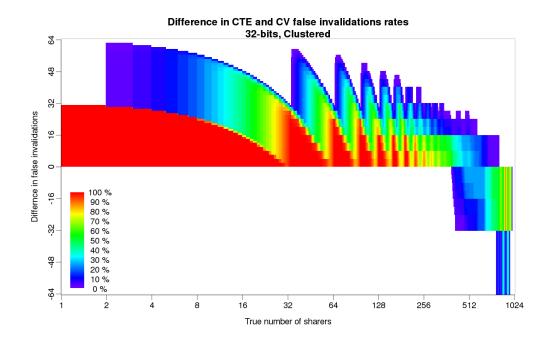

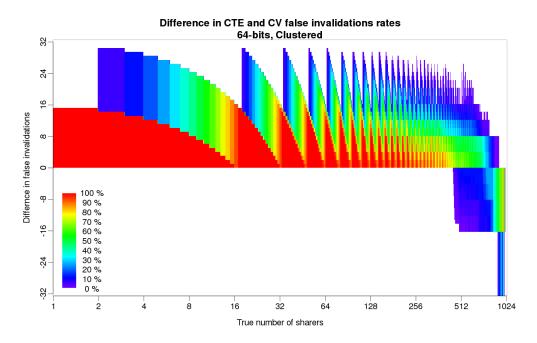

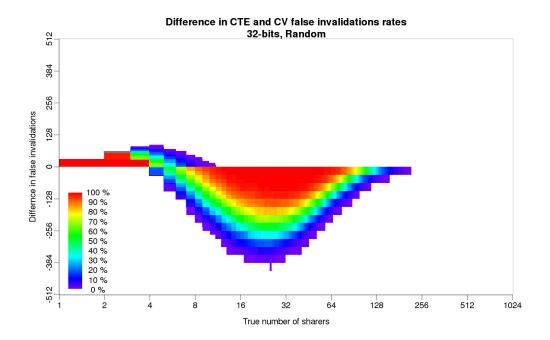

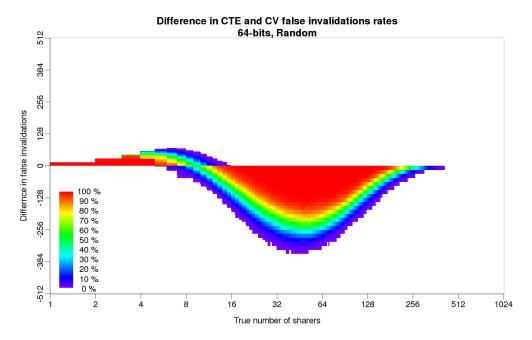

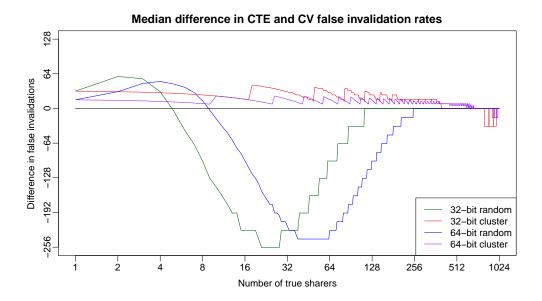

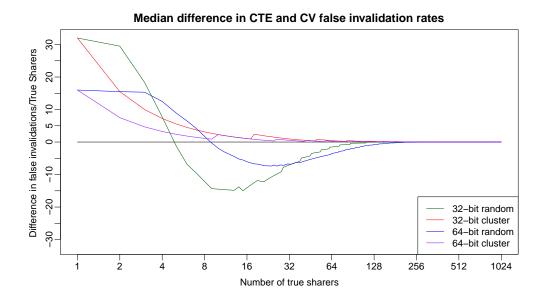

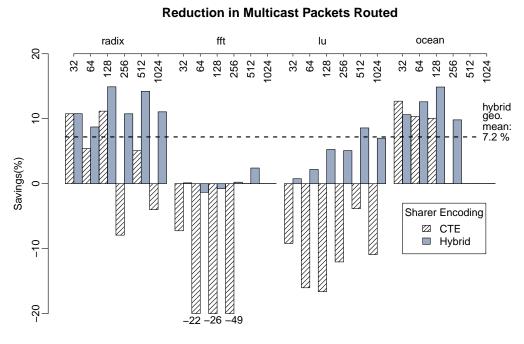

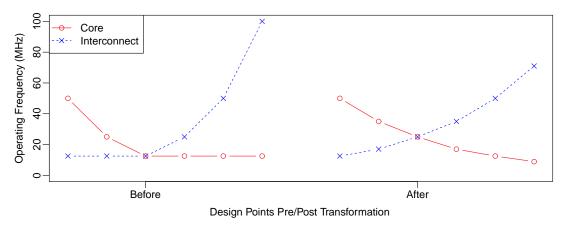

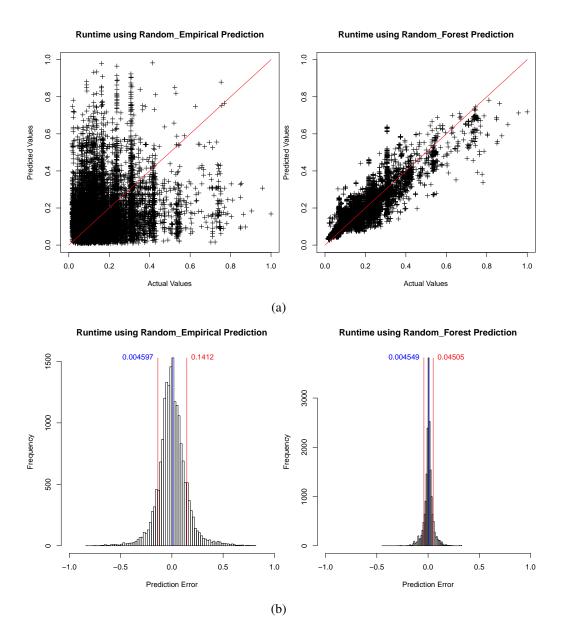

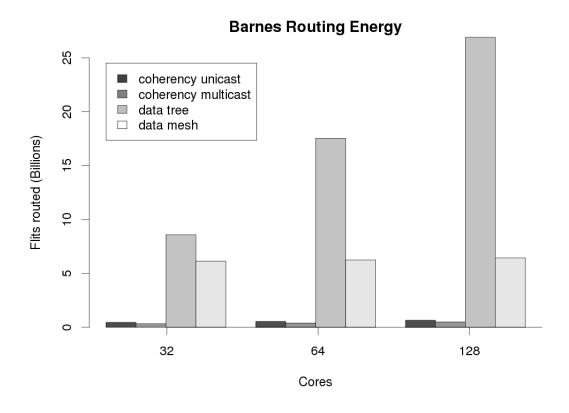

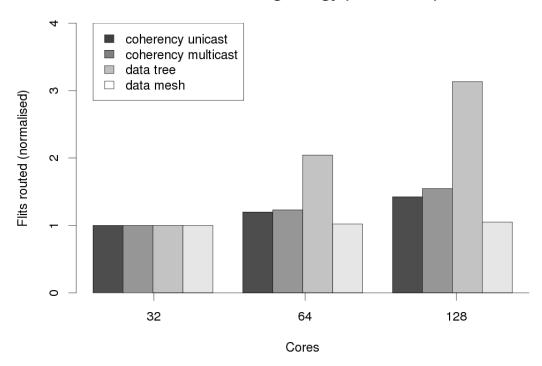

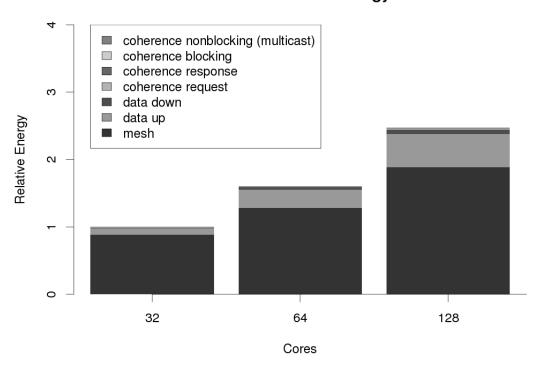

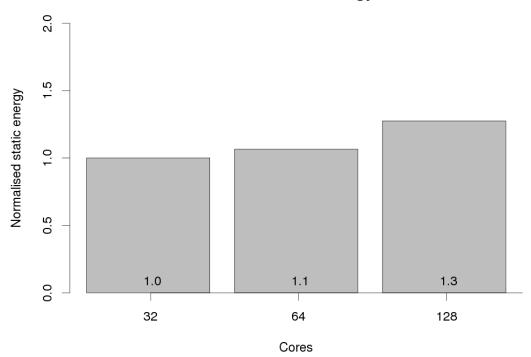

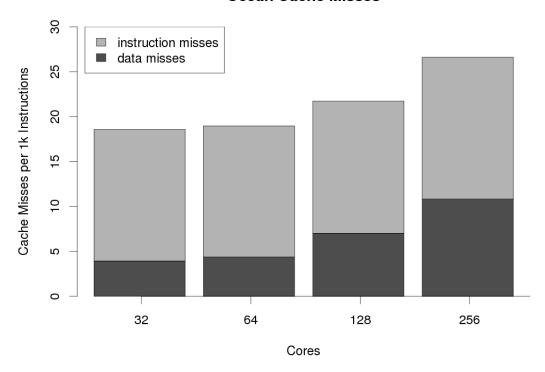

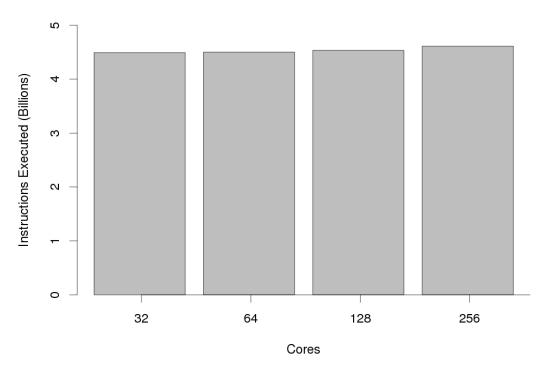

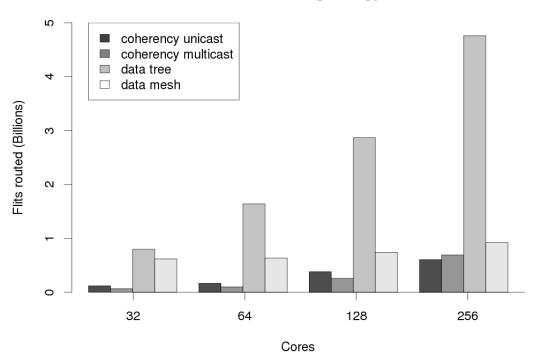

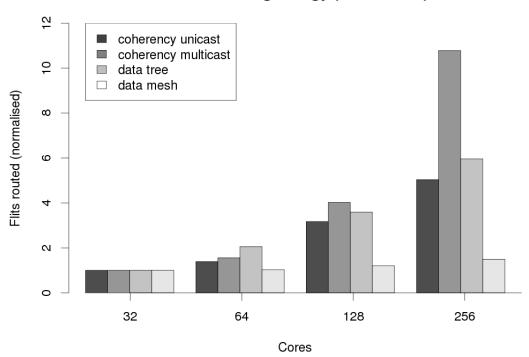

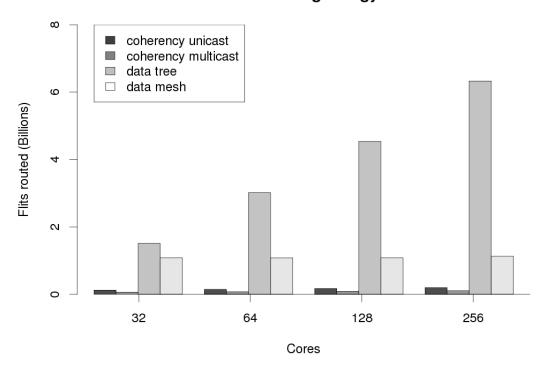

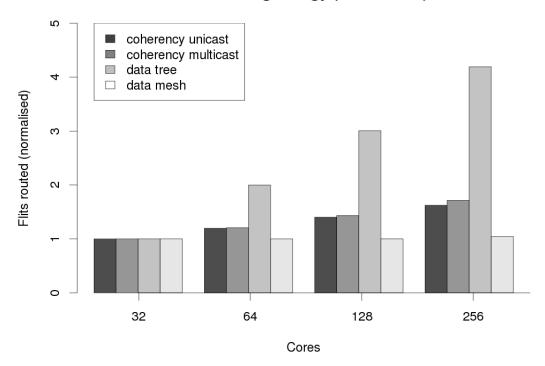

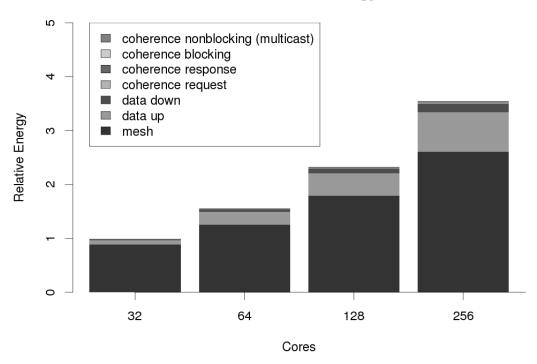

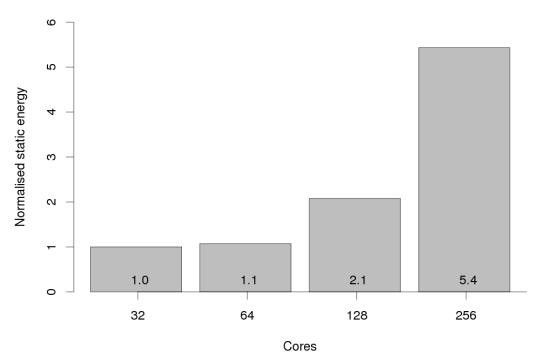

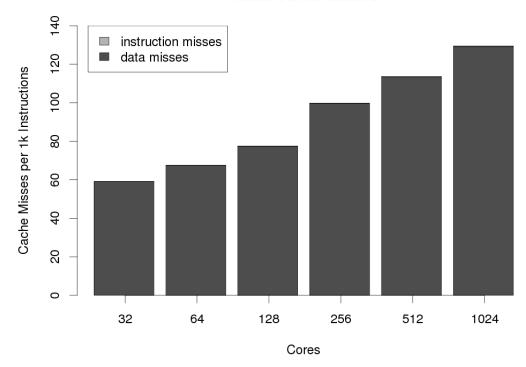

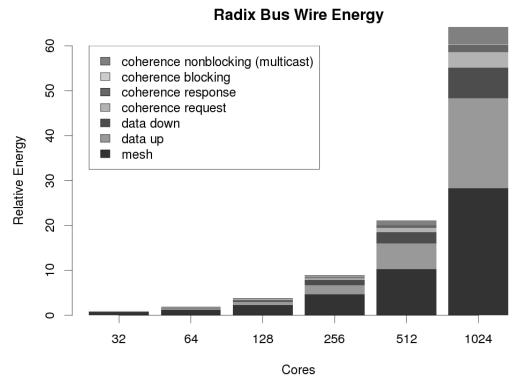

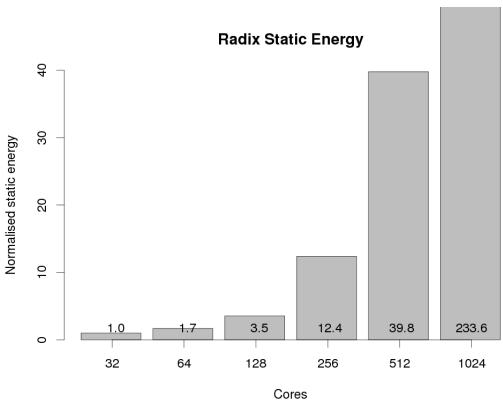

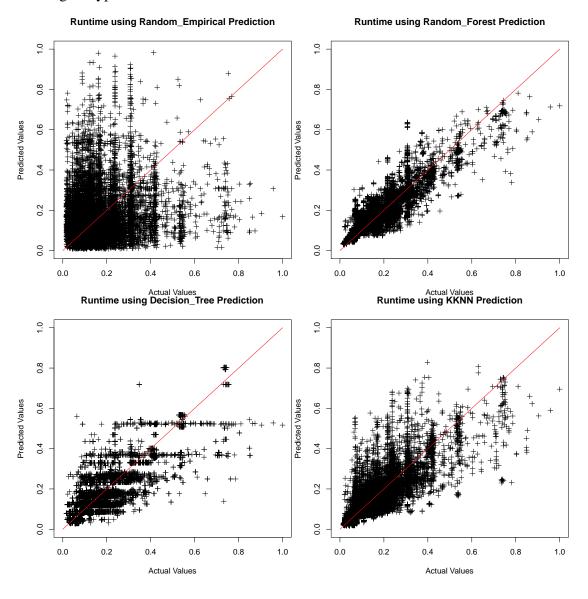

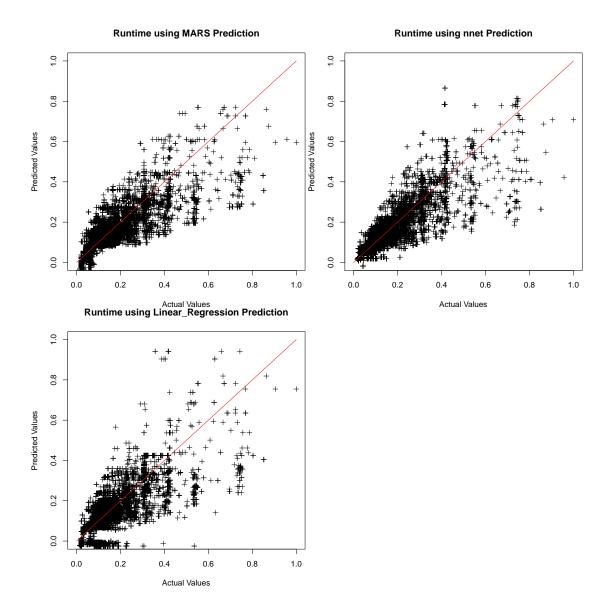

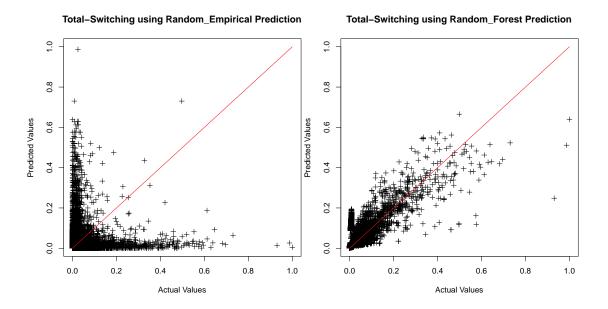

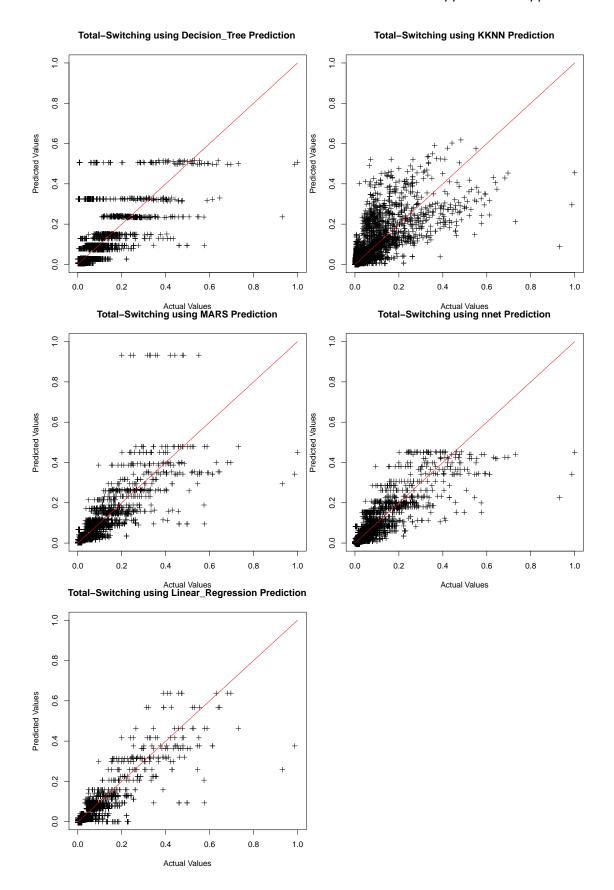

# 2.5.4 Design Space Exploration