# ENHANCEMENT OF PROCESS CONTROL USING REAL-TIME SIMULATION

EWAN A. CAMERON

PhD University of Edinburgh 1989

#### **ACKNOWLEDGEMENTS**

work was sponsored by the Science Engineering Research Council (SERC) and Plessey Research (Caswell) Ltd. under the SERC Co-operative Awards Science and Engineering (CASE) scheme. I am grateful to both bodies for financial assistance. I would like to acknowledge the continued encouragement and support of my academic supervisors Professor J. M. Robertson and Dr. R. Holwill of the Edinburgh Microfabrication Facility (EMF) and my industrial supervisor Mr. H. Richards of Plessey The assistance of the staff and research students at the EMF throughout the project appreciated. I would also like to acknowledge the cooperation of the people with whom I had contact at Plessey Research. Vielen Dank to Siemens AG for use of text processing facilities and to Dorothy Dickson for her hard work in preparing the text.

#### **ABSTRACT**

As semiconductor devices are reduced in size, it becomes increasingly more important to control process parameters that determine device performance. A novel technique is proposed that enhances control by automatically taking into account all major variables encountered during processing. simulation, supplied with measured process variables, is the basis of the technique. The chosen application is thermal growth of thin silicon dioxide Gate oxide thickness is a critical parameter in MOS devices, appearing as a first order term in all principal device equations. Control using conventional means based on а fixed oxidation time becomes increasingly difficult as thickness is scaled to below 250Å for VLST devices and growth times correspondingly reduced.

A microprocessor-based system that uses simulated oxide growth to actively control oxide thickness has been Process data available through conventional furnace control system is utilised, with the that little modification to the existing process equipment is necessary. The system provides closed-loop control and process data storage at the 'local' equipment level, and as such forms the foundation for a highly-automated processing module for oxidation that can be integrated into the automated production environment.

# **CONTENTS**

| CHAPTER 1. Introduction                             | • 1        |

|-----------------------------------------------------|------------|

|                                                     |            |

| CHAPTER 2. Review of Fabrication                    | 13         |

| 2.1 Principles of Silicon Fabrication               | 13         |

| 2.1.1 Thermally Grown SiO <sub>2</sub>              | 17         |

| 2.2 NMOS Process Outline                            | 19         |

| 2.3 Requirements for VLSI processing                | 23         |

| 2.3.1 Gate Oxides for VLSI                          | 24         |

| 2.3.2 Process Automation                            | 28         |

| 2.4 Process Simulation                              | 30         |

|                                                     |            |

|                                                     |            |

| CHAPTER 3. Theory of Silicon Oxidation              | <b>3</b> 3 |

| 3.1 Kinetics of Oxide Growth                        | 33         |

| 3.2 Examples of Oxide Growth and Relation to Theory | 39         |

| 3.2.1 Temperature Dependence of Rate Constants      | 40         |

| 3.2.2 Influence of Silicon Crystal Orientation      | 43         |

| 3.2.3 Pressure Dependence of Oxidation Rate         | 44         |

| 3.2.4 Influence of Substrate Doping                 | 49         |

| 3.2.5 Mechanism of Oxide Growth                     | 53         |

| 3.3 Kinetics of Thin Dry Oxidation                  | 57         |

| 3.4 Chlorinated Oxidation                           | 62         |

| 3.5 Simulation of Oxide Growth                      | 67         |

|                                                     |            |

| CHAPTER | 4. Practical Aspects of Oxide Growth | 75  |

|---------|--------------------------------------|-----|

| 4.1 Fur | nace Description                     | 75  |

| 4.1.1   | The Furnace Tube                     | 77  |

| 4.1.2   | The Boat Loader                      | 78  |

| 4.1.3   | The Furnace Gas System               | 81  |

| 4.1.4   | The Temperature Control System       | 83  |

| 4.1.5   | The Process Controller               | 85  |

| 4.1.6   | EMF Research Furnace                 | 8.7 |

| 4.2 Lim | nitations of Furnace Control         | 88  |

| 4.2.1   | Temperature Profiles                 | 88  |

| 4.2.2   | The Hydrogen Flame                   | 91  |

| 4.2.3   | Temperature Reduction on Loading     | 92  |

| 4.2.4   | Mass-Flow Controller Characteristics | 94  |

| 4.2.5   | Discussion                           | 98  |

| 4.3 Pre | e-oxidation Treatment                | 99  |

|         |                                      |     |

|         |                                      |     |

| CHAPTER | 5. Assessment of Silicon Dioxide     | 102 |

| 5.1 Thi | .ckness Measurement                  | 102 |

| 5.1.1   | Optical Interference Method          | 102 |

| 5.1.2   | Ellipsometry                         | 104 |

| 5.1.3   | Surface Profiling                    | 107 |

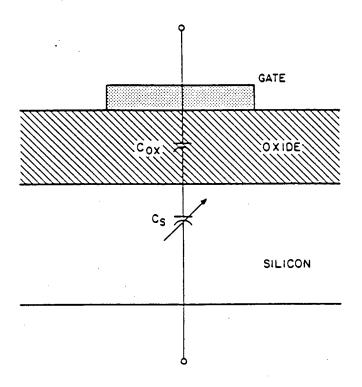

| 5.1.4   | Capacitance Method                   | 108 |

| 5.1.5   | Colour Charts                        | 114 |

| 5.1.6   | Comparison of the Nanospec and the   |     |

|         | Ellipsometer                         | 114 |

| 5.2 Oxi | de Quality                           | 121 |

| 5.2.1   | Oxide Charges                        | 122 |

| 5.2.2   | Capacitance and Conductance Analysis | 126 |

| 5.2.3   | Dielectric Breakdown                 | 132 |

| CHAPTER 6.               | Evaluation of Existing Furnace       |     |  |  |

|--------------------------|--------------------------------------|-----|--|--|

|                          | Technology                           | 136 |  |  |

| 6.1 Introduction         |                                      |     |  |  |

| 6.2 Furnace Verification |                                      |     |  |  |

| 6.2.1 Pa                 | rasitic Oxide Growth                 | 137 |  |  |

| 6.2.2 Ox                 | ide Quality                          | 139 |  |  |

| 6.3 Oxide                | Thickness Variability                | 144 |  |  |

| 6.3.1 Qu                 | antitative Study of Contributions to |     |  |  |

| Va                       | riability                            | 146 |  |  |

|                          |                                      |     |  |  |

| CHAPTER 7.               | A New Furnace Control System         | 164 |  |  |

| 7.1 Contro               | l System Description                 | 164 |  |  |

| 7.2 Implem               | entation of an Oxidation Model       | 167 |  |  |

| 7.2.1 Si                 | mulation Dependence on Time Interval | 172 |  |  |

| 7.3 Determ               | ination of Rate Constants            | 174 |  |  |

| 7.4 Interf               | ace between Model and Furnace        | 195 |  |  |

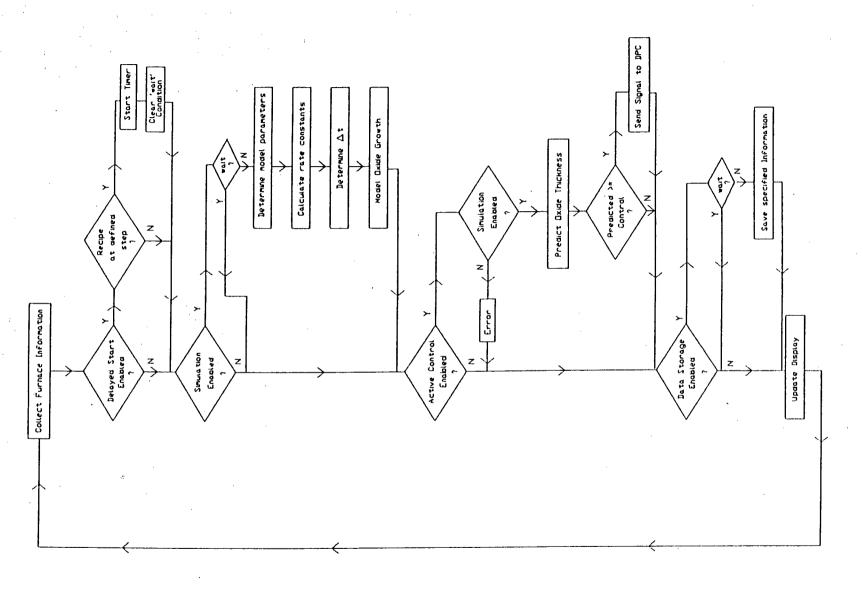

| 7.5 FACS S               | oftware Description                  | 201 |  |  |

| 7.6 Invest               | igation of System Capabilities       | 205 |  |  |

|                          |                                      | -   |  |  |

|                          |                                      |     |  |  |

| CHAPTER 8.               | Conclusions and Future Work          | 220 |  |  |

|                          |                                      |     |  |  |

| APPENDIX A               | Principal MOSFET Relationships       | 228 |  |  |

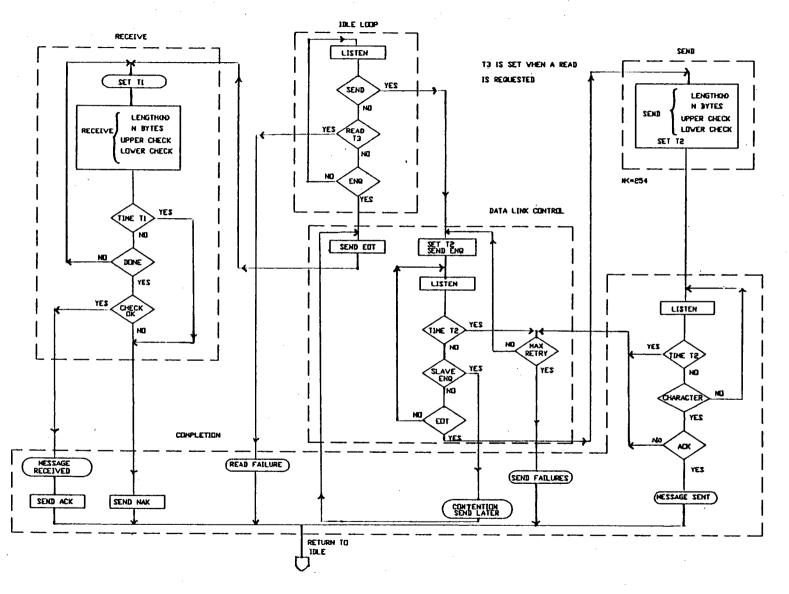

| APPENDIX B               | SEMI Equipment Communications        |     |  |  |

|                          | Standard (SECS)                      | 232 |  |  |

| APPENDIX C               | FACS Program Listing                 | 239 |  |  |

| REFERENCES               |                                      | 252 |  |  |

#### CHAPTER 1

#### INTRODUCTION

Integrated Circuit (IC) manufacturing technology has advanced rapidly since the first ICs were produced in the late 1950's. This is most apparant in device geometries, which have shrunk steadily to allow increased levels of integration and improved circuit performance. VLSI (Very Large Scale Integration) processes are currently capable of producing circuit features with minimum geometries of around lum, and minimum feature size will continue to decrease well into the sub-micron region in the future.

Associated with this trend towards smaller geometries is an overall increase in processing complexity, and advanced processes may typically involve over two hundred distinct process steps. For a stable, well-controlled process, it has therefore increasingly critical that the individual steps have a high degree of reproducibility and uniformity. technologies will require much higher levels of control than can presently be achieved, if process quality and yield are to be maintained at acceptable levels. means by which process control can be enhanced to meet future manufacturing needs is the topic addressed by this thesis.

Process control, in its broadest sense, involves the measurement and monitoring of important process parameters and analysis of the information so that the status of the process can be determined. Corrective action is taken when the status is found to be unacceptable (feedback). In IC fabrication, process control exists in many forms, and operates in various

timescales. For example, electrical testing is normally carried out at the end of processing on special test structures. This produces a valuable means of monitoring the overall process. However, it cannot be used very effectively to adjust the process because the feedback loop is too long. If there is a malfunction in the process, many batches will have been processed before it is detected and corrected.

By comparison, control at much shorter timescales operates on individual process steps or several steps Thus layer thickness is measured grouped together. after a deposition step; and sheet resistance after an implantation-anneal sequence, to verify respective processes have been carried out correctly. Through such in-process monitoring, it is possible for errors to be corrected at some later processing step or through repetition of the faulty step (rework). worst, the waste of further resources on wafers that are already defective is prevented. Analysis methods such as process-control-charts can be used to detect trends in the measured data, and provide a basis for process feedback.

It is imperative that monitoring and analysis be carried out as quickly as possible so that problems can be readily identified and appropriate action taken to rectify faults. Only by doing so will the number of mis-processed batches (and therefore fabrication costs) be minimised. However, the data handling requirements associated with process control are large, and increase with increasing process complexity. Much of the current effort towards improving process control has therefore centred control the extensive information management capabilities of Computer Aided Manufacture (CAM) systems.

CAM [1,2] concentrates primarily on factory integration and management. Specific areas that it covers include tracking of all batches being processed (work-in-progress), maintenance of batch histories and materials management. Integration of process data into the CAM database will be a necessary part of the advanced manufacturing environment, allowing for organised, efficient use of process information.

equipment provides another control. In response to the tighter tolerances demanded equipment control systems are becoming increasingly sophisticated, and many incorporate microprocessor-based digital systems. It is useful here to distinguish between two types of control parameters : 'process inputs' and 'process outputs'. Process inputs are causal in nature. Obvious examples temperatures, pressures and times. They can be thought of as characteristics of the process environment whose influence becomes apparent in one or more of the process These process outputs are the measured outcome of the process and include, for example, film thickness, resistivities and dimensions of patterned Equipment control systems generally have structures. relatively fast control loops which confer control during However, they control the process the process run. environment and operate on process input parameters, when usually it is the related process output parameters that are of main concern. (Process outputs are of primary importance since they are of direct relevance to the characteristics of completed device structures.)

Process outputs can rarely be controlled directly in a feedback loop, because they are difficult to monitor in-situ. If the measured process outputs warrant an adjustment to the process, then this is normally carried

out by adjusting the set points of the appropriate equipment-controlled process inputs. Effective control depends on a well-understood relationship between outputs The problem is that the relationship between the two is complex and sometimes ill-defined. Many separate process inputs can affect a single process output, and the effects are often interrelated. example in the silicon oxidation process, the resultant oxide thickness will be influenced by a combination of times, temperatures and qas flow Conversely, a single process input may influence several outputs; for example, a higher temperature process step will influence all dopants introduced into the substrate up to that point. Not surprisingly, true closed-loop control of the process step(s) is usually It is the experienced process engineer who provides the necessary understanding for instigating changes to equipment settings, based on information about the measured process outputs.

A means of closing the loop and enhancing control is via the factory CAM system [3]. In the advanced, highly-computerised manufacturing environment, automatic feedback (or feedforward) to appropriately interfaced equipment is possible. The CAM system automatically adjust equipment settings by loading new instructions (i.e. recipes) the microprocessor-based equipment control systems. The process database, built up by the aforementioned input of measured process data into the CAM system, forms the basis decision-making for by the CAM software. Automatic data collection, through interfacing measurement equipment to the CAM system, would further enhance the process.

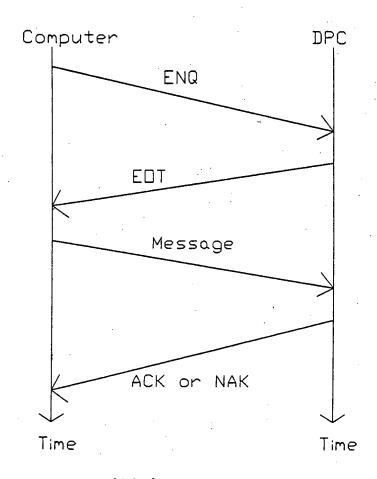

Although interface standards for equipment (SEMI Equipment such as SECS<sup>1</sup> communications Communications Standard) [4] now exist and are being increasingly implemented in the hardware and software of advanced process equipment, this approach is generally made difficult by the wide range of equipment that is available, each with different forms of internal control system and varying levels of capability for automatic Moreover, it would be a formidable task to develop an integrated system that applied to all areas of the production environment covered by the CAM system since, as already mentioned, the decision-making process necessary for feedback is seldom simple.

Even assuming that these difficulties could be overcome, the feedback loop would still be long and slow, and in all cases changes to equipment settings would arrive too late for the mis-processed or poorly processed wafers that had induced the change. The method also assumes that the process specification, in the form of recipe delivered to the equipment, accurately actual wafer environment. deviations from set point of parameters controlled by the equipment (i.e. process inputs) frequently especially in the transient periods that occur during processing, and so nullify this assumption. particularly important for processes with short process times, where transient periods may form a significant part of the overall timescale.

In this work, a radically new approach to enhancing process control, that overcomes all  $_{\lambda}^{\text{of}}$  the above problems, is presented. This is possible by implementing process outputs in a feedback control loop at the equipment

<sup>1</sup> The SECS protocol is outlined in Appendix B

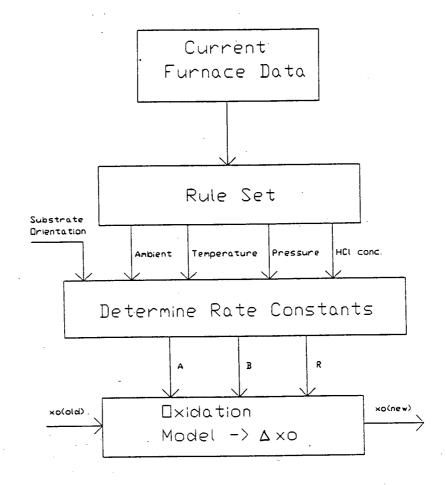

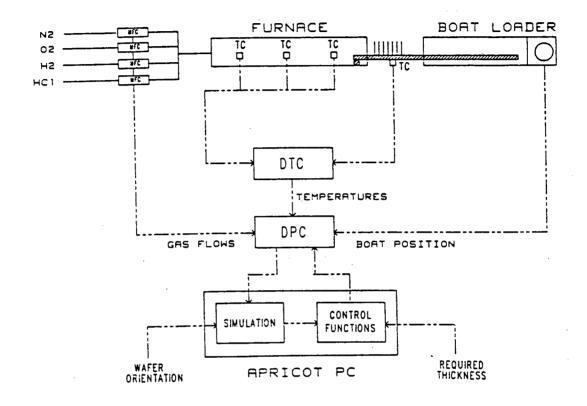

Real-time computer simulation of the process step forms the basis of the system, constituting the essential link between process inputs and process Housed in a microcomputer, the simulation is fed with real-time measurements of all important process If these are regularly updated, then a realtime estimate of process outputs can be calculated. estimates can then be used to predict endpoints for the The microcomputer provides feedback to the process equipment, which is actively controlled during every run.

The advantages of this approach are:

- In comparison to the control loop via the factory CAM system, this approach is implemented at the 'local' level of process equipment, and is more easily optimised to suit the individual process step(s) involved.

- ii) Actual process conditions, as opposed to the idealised status of the process specification, are considered in the control loop.

- iii) Any number of relevant output parameters can be considered, as long as the physical relationships to input parameters are known or an adequate empirical model exists.

- iv) Process outputs, not process inputs are the basis of control. Desired values (i.e. set points) for the process outputs are entered at the microcomputer (e.g. the desired oxide thickness would be entered at an oxidation step).

- v) Processing is optimised to give the desired process outputs for every run. Variation in any measured

input parameter during the process is automatically taken into account.

vi) The system is independent of deviation from set point of any parameter controlled by the equipment control system that is input into the real-time simulation. Thus allowance is made for transient periods, during which equipment parameters are generally poorly controlled.

The success of a real-time simulation-based control system obviously rests on the availability of an accurate process model. However, advanced models for many fabrication steps already exist, and are being constantly improved as the understanding of underlying physical processes increases. These models are most often applied in process simulation programs such as SUPREM III [5], where they have an important role as an aid to process development. The control system presented here introduces a new application of process simulation beyond this mainly passive role.

This work investigates whether the current simulation capability can be successfully utilised in an active control system. It focuses on a single aspect of silicon fabrication - thermal growth of thin silicon dioxide films. A real-time simulation-based control system for the oxidation process was developed. There were several reasons for the choice of silicon oxidation:

Oxidation is a critical process in Metal Oxide Semiconductor (MOS) device fabrication, currently the most commercially important fabrication technology. It is also of great importance in the fabrication of bipolar devices. The oxidation process directly determines the electrical properties of MOS devices; hence the ability to

reproducibly form clean high-quality gate oxide is fundamental to successful MOS IC manufacture. The thickness of the oxide film is the primary process output of the oxidation process and must be carefully controlled. There is a particular need for enhanced control as oxide thicknesses are reduced to meet VLSI demands and process times are correspondingly decreased.

- ii) Silicon oxidation has been extensively investigated in recent years. There is a relatively large amount of information available concerning the kinetics of oxide growth and the influence of processing conditions on oxide properties.

- iii) Advanced oxidation equipment generally incorporates microprocessor-based controllers and interfacing possibilities to external microcomputers.

order to provide the background for chapters, Chapter 2 of the thesis presents a review of fabrication. Emphasis is given to aspects fabrication which are of particular relevance to this Much of silicon fabrication is based on the project. iterative cycle of deposition-photolithography-etch. The principal individual operations in this cycle are discussed, including the applications and methods oxidation. 5-micron NMOS thermal Α process described, a process which is representative of fabrication technology used for LSI (Large It illustrates the complexity of device Integration). fabrication and the importance of monitoring controlling each of the individual steps if high-quality working devices are to be produced.

The advance to VLSI requires processing techniques in addition to those used for LSI fabrication and these

are discussed. Two of the most important topics for future VLSI, gate oxides for MOS devices and automation of the fabrication process, are especially relevant to this work, and are looked at in detail. simulation has important role an in VLSI The major objectives of simulation and the development. computer packages currently principal in use described.

In Chapter 3, the oxide growth process is discussed in detail. The discussion provides the background for implementation of a growth model the later simulation control Much of system. the understanding of oxidation kinetics is based on the work of Deal and Grove carried out in the 1960's [6]. model of the growth kinetics is outlined, and the relation between this theory and the main process inputs which influence oxide growth is examined. The more detailed theories that have been proposed to explain the Si-SiO, interface reaction and the observed kinetics are also described. Even when first proposed, it was clear that the Deal-Grove model did not adequately describe the kinetics of thin oxides grown in oxygen. Such oxides are of increasing significance to VLSI processing. additional models that have been developed to explain the anomalously high oxidation rate in this regime are Of equal significance to VLSI is the use of chlorine-containing compounds in the oxidising ambient. The addition of a few percent HCl gas, for example, can considerably improve oxide quality. The additives used, their influence oxidation growth rates on discussed in the penultimate section of the chapter. The final section returns to process simulation, and looks at the implementation of oxide growth models in several packages. The models used are defined, along limitations. with their This forms an

starting point for the real-time simulation of oxide growth.

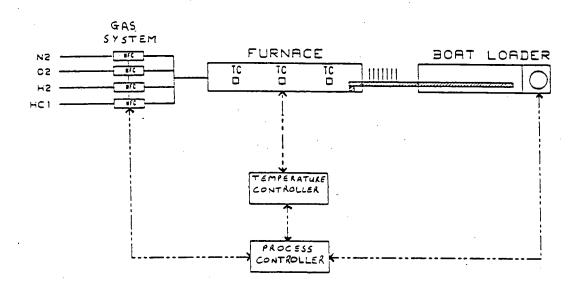

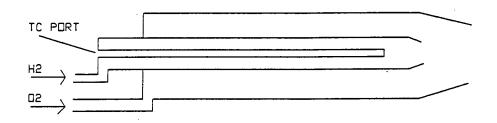

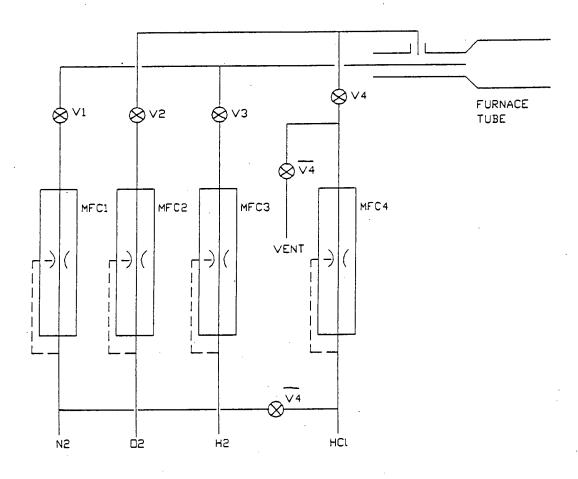

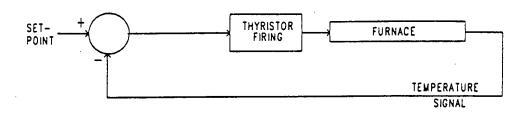

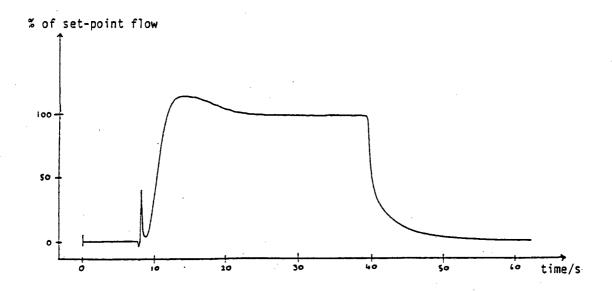

Following the theory of oxidation in Chapter 3, Chapter 4 switches to the practical aspects of carrying out oxidation in the IC production environment. generalised scheme for state-of-the-art oxidation is suggested and the component parts equipment individually reviewed. Emphasis is placed on control aspect, including the principal feedback loops used to control the oxidation process inputs. furnace used for the experimental work of later chapters is described and related to the generalised outline. shown that current furnace systems are unable confer full control the oxidation on experienced by wafers. Experimental data specifically demonstrate problems with temperature control and control of the gases supplied to the oxidation equipment. established that significant transient periods during the oxidation process.

It is argued that pre-oxidation cleaning should be an integral part of practical oxidation procedures. As well as being crucial from the point of view of contamination, pre-oxidation cleaning influences the final oxide thickness, and must be well-regulated to obtain a stable, controlled process. The cleaning sequences in common use are reviewed.

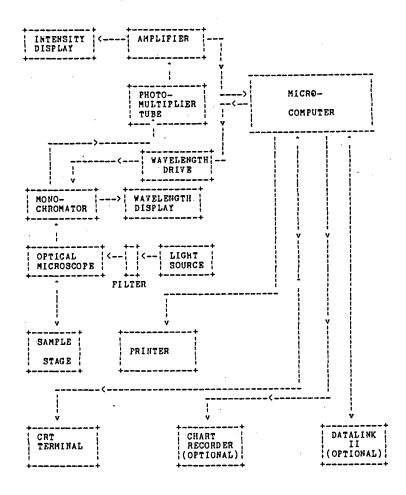

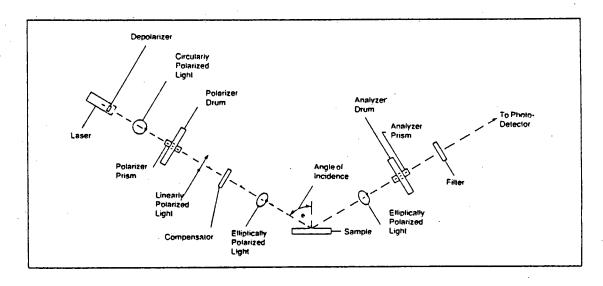

Measurement and analysis of an oxide film is a necessary part of the investigations in Chapters 6 and 7. Many methods are available, and Chapter 5 is devoted to an investigation of the principal techniques. split into two broad sections covering measurement of oxide thickness and assessment of oxide quality. thickness measurement, ellipsometry is generally considered to be one the of most accurate techniques.

However, it is shown by comparison of standard commercial equipment that optical interferometry can give comparable reproducibility. It is suggested that interferometry should be the preferred technique when large amounts of data are to be collected, since the time to complete a measurement on the available equipment is considerably shorter.

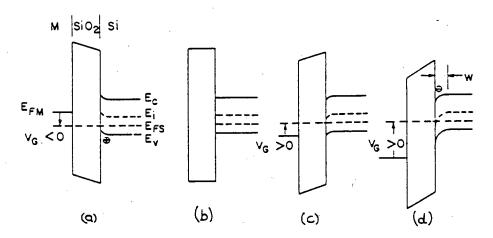

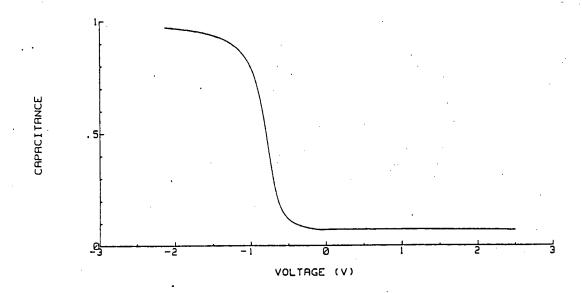

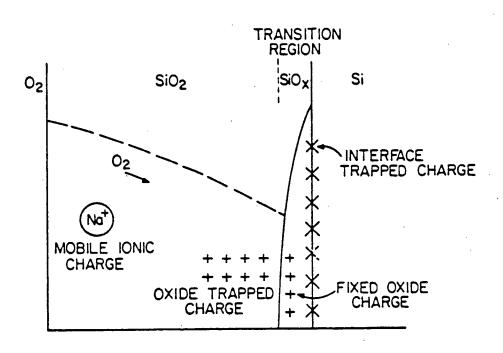

The discussion on oxide quality centres on MOS capacitor measurements. These are used to monitor both concentrations oxide dielectric oxide charge and It is important to distinguish the various integrity. types of oxide charge, and the standard terminology now use is detailed. Capacitance and conductance potentially measurements have large benefits, analysis methods are generally complex. An overview of the information that can be obtained is presented, along important practical points concerning measurement conditions. By comparison, dielectric breakdown measurements are relatively straightforward, but remain vitally important in the investigation of oxide defects and oxide reliability.

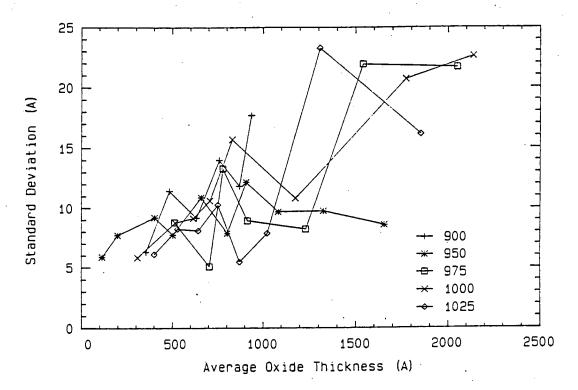

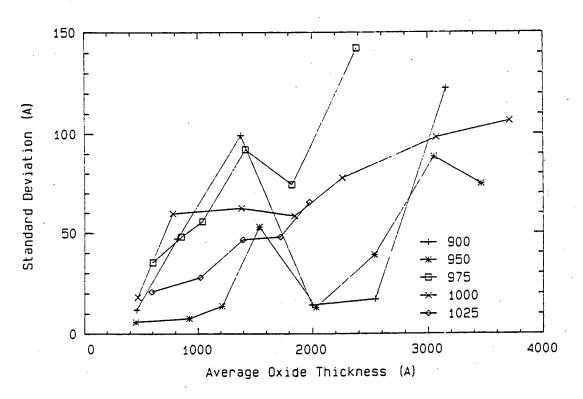

In Chapter 6 the uniformity in oxide thickness that achievable with current furnace technology Oxide thickness variability is measured investigated. several different oxidation processes, and both between-batch and within-batch components are assessed. It is argued that significant between-batch variation is related to transient effects and the inadequacy of the current control methods. Specific patterns in the collected data are related to the control problems noted in Chapter 4. The furnace used in the investigation was first subjected to a rigorous verification procedure, the results of which are also presented in this chapter.

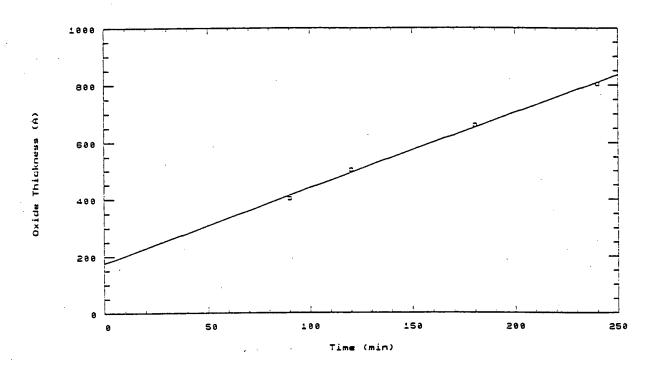

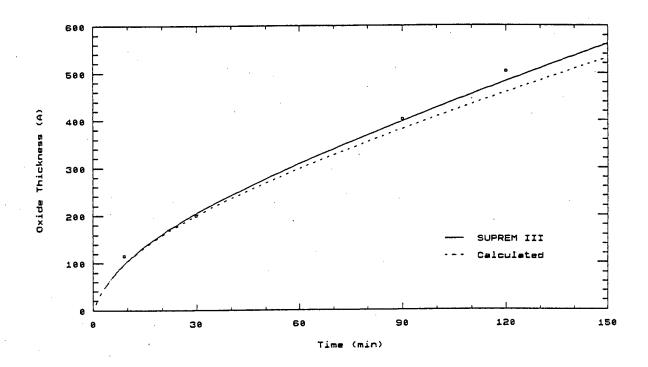

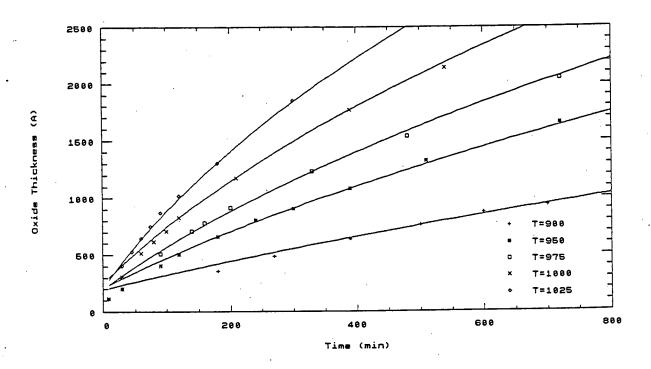

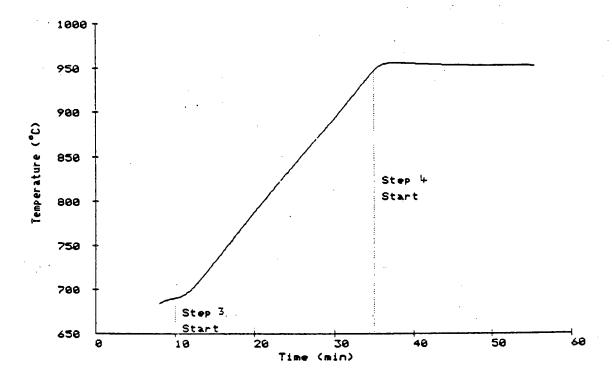

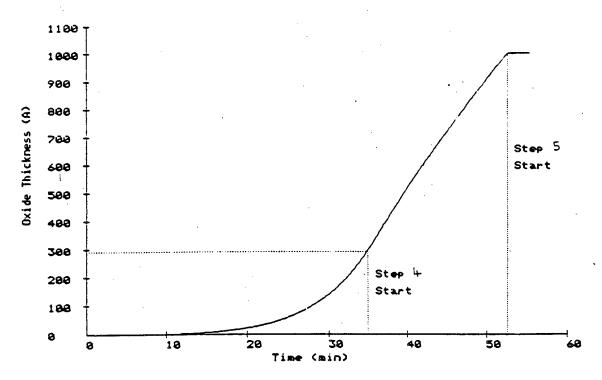

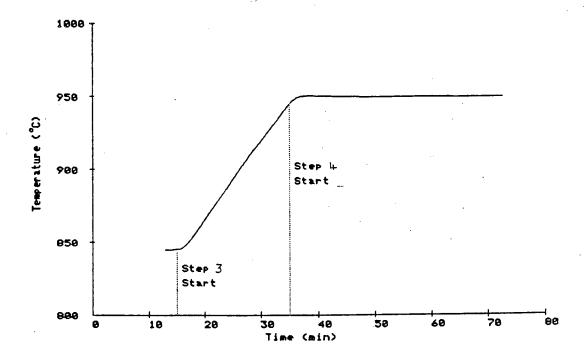

Chapter 7 describes the new control system, based on real-time simulation, that has been developed for furnace oxidation. The system implements the oxidation theory developed in Chapter 3. The accuracy of the model depends on suitably chosen rate constants. Simulation using literature values is compared with oxide growth rate data obtained from a series of oxidation runs. New values for the rate constants are extracted from the data set for additional comparison.

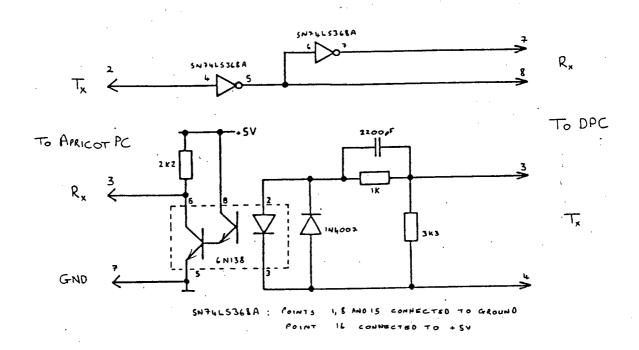

A bi-directional interface between oxidation model and furnace system was developed to realise active control of furnace operations. An extensive software system was also developed to execute all interface and modelling requirements, and provide a friendly user interface. The complete system was tested under a wide range of oxidation conditions, including processes involving substantial oxide growth under dynamic study, conditions. With this experimental feasibility of the real-time simulation control technique is examined.

#### **CHAPTER 2**

#### **REVIEW OF FABRICATION**

#### 2.1 Principles of Silicon Fabrication

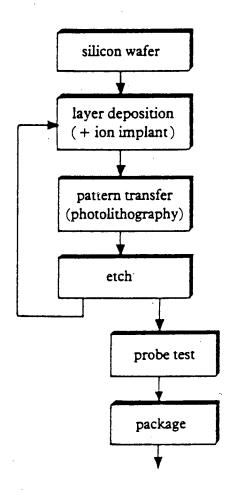

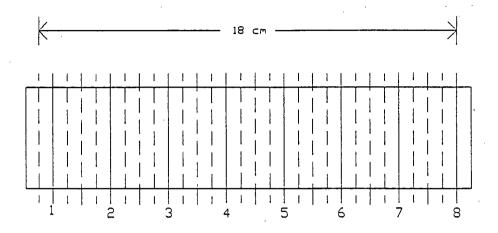

The IC fabrication process is of a highly complex nature - typically involving hundreds of individual operations - and has many variations depending on the type of product. However, there is a basic sequence of operations common to all processing technologies (Fig. Device structures are built up on a substrate repetitions of through many the deposition-photolithography-etch sequence. may be repeated over 10 times in advanced VLSI processes and may include additional steps such as ion implantation and high-temperature "drive-in" treatments.

In silicon IC production the starting substrates are single crystal silicon wafers which are typically between 3 and 6 inches in diameter. These are processed in batches of up to 200 wafers. Coupled with the large number of individual chips that can be created on a wafer, this batch production is capable of giving very large numbers of ICs and is the main reason why the fabrication process is cost-effective.

The individual operations in the processing cycle are now discussed.

Layer deposition forms a controlled amount of new material on the wafer surface. Several materials, selected for their insulating, conducting or masking properties, are used and several deposition methods are involved. The following list describes some of the most

Fig. 2.1 Basic IC Fabrication Sequence.

important techniques. Polysilicon, silicon dioxide and silicon nitride can be deposited by Low Pressure Chemical Vapour Deposition (LPCVD) [7,8]. These materials have the advantage of being able to withstand high-temperature Deposited oxide is often doped with phosphorous, using suitable additions to the reactant The presence of phosphorus allows the oxide to flow during high-temperature treatment and is used to smooth sharp edges for improved step coverage. Aluminium is usually deposited electron by evaporation or by sputtering techniques [9,10]. In the latter case argon ions bombard an aluminium target, releasing aluminium which coats wafers placed in the sputter chamber.

implantation [11,12] allows well-controlled adjustment to be made to the density of dopant atoms in the substrate material. The technique accelerating arsenic, boron or phosphoruss dopant ions at energies in the range 20-200 keV. The ion beam is deflected over the silicon wafers, which are penetrated to depths of up to 2um. The implanted depth depends primarily on the ion energy. An alternative method of into silicon introducing dopant atoms is gas-phase diffusion [13], which is carried out as a furnace process at temperatures between 900 and 1200°C. Due to its poor controllability, diffusion has been mostly superseded by implantation, apart from instances where heavy doping levels are required.

Photolithography [14,15] provides the means of transferring a desired pattern into deposited material. The entire wafer is covered with a light sensitive film of photoresist which is then exposed to UV light through an appropriate mask. Exposure equipment must be able to accurately align successive layer patterns to each other

so that device structures can be built up. High demands are also made on the optical system which must be capable of resolving the minimum feature size of the technology. Wafer-steppers using masks 5x or 10x the final size offer several advantages over the older contact and proximity techniques and are being increasingly used in advanced processes [16], despite their much reduced throughput.

Of the two types of photoresist - positive and negative - positive is now generally preferred due to its better resolution. With positive resist, exposed areas are washed away upon development. A protective resist left in unexposed areas which prevents is underlying material from being etched away subsequent etch step. Etching [17,18,19] transfers a resist pattern into deposited material and is carried out either with liquid chemicals (wet etching) or in a plasma process (dry etching). Plasma processes can be mainly anisotropic (as in reactive ion sputtering) or mainly isotropic (usually referred to as "plasma-etching") or a mixture of the two. Wet etching is isotropic. choice of the etching method must be made since it can greatly effect feature size and edge profiles. etching, remaining resist is removed by chemical plasma treatments and the next cycle of the process is started.

When all iterations are complete, an electrical probe test is normally carried out on special test structures to check that all operations have been successfully carried out. Individual chips are then finally cut from the wafers using a diamond saw and packaged.

## 2.1.1 Thermally Grown SiO<sub>2</sub>

Although not classified as a deposition process, the thermal oxidation of silicon to produce SiO, is also a means of forming new material on silicon. It is normally carried out in 0, or H2O ambients (corresponding to wet and dry oxidation respectively) at temperatures in Oxidation forms a passivating the range 900-1150°C. insulator on the silicon surface and is the main reason for the success of silicon as a semiconductor material in microelectronics. The oxide layer serves several functions in the fabrication of devices, and advanced processes may involve over 15 separate oxidation steps. The main functions are:

## i) Isolation

In both MOS and bipolar technologies, thick field oxide regions (typically 5000-15000Å) provide insulation between active devices, and between conducting layers and the silicon substrate. In double polysilicon processes, isolation of the two poly layers involves thermal oxidation of polysilicon.

#### ii) Gate dielectric

The low charge densities associated with (dry) thermal oxidation are crucial to the stable operation of MOS devices.

## iii) Implant/diffusion barrier

Patterned oxide is able to selectively mask parts of the silicon against introduction of dopant ions. Implantation through thin oxide is often used to adjust the dopant profile in the substrate.

#### iv) Stress relief SiO, is used as a mechanical buffer between Si and in the LOCOS [20] process. is necessary relieve stress caused by the to difference thermal expansion between Si in and Si<sub>3</sub>N<sub>4</sub>.

Oxidations are normally carried out in furnaces open to atmospheric pressure. Oxidation rate depends strongly on temperature which must therefore be carefully controlled1. The actual oxidation technique used depends on the particular application. Thicker oxides are grown under wet conditions since the oxidation rate is much faster than with dry oxidation. In modern furnaces water vapour is created by the pyrogenic technique, which involves direct combination of hydrogen Chlorinated dry oxidation has well-known with oxygen. beneficial effects on oxide quality<sup>2</sup> [21,22] and is frequently used to form gate oxide. Likewise, a hightemperature post-oxidation anneal in an inert ambient (such as  $N_2$ ) can improve oxide quality [23]. warpage is a problem at higher oxidation temperatures, but is commonly minimised using a low loading/unloading temperature and ramping to the desired oxidation temperature.

When thicker oxides are required, high-pressure oxidation [24,25] (HIPOX) offers advantages. At high pressures, the growth rate is accelerated and allows oxidation to take place at lower temperatures whilst maintaining reasonable oxidation times. Thus the detrimental effects of long high-temperature oxidation, such as the growth of oxidation-induced stacking faults

The features of advanced microprocessor-controlled furnaces are discussed fully in Chapter 4.

$<sup>^2</sup>$  This will be discussed in Section 3.4

and excessive dopant diffusion can be avoided. Plasma-enhanced oxidation [26] also considerably increases the oxidation rate and offers similar benefits.

#### 2.2 NMOS Process Outline

MOS-based technologies have become dominant in the IC market, mostly due to their suitability for high levels of integration. The original commercial MOS process was PMOS and was introduced in the early 1960's. However, with the advent of ion implantation in the 70's, allowing accurate adjustment of transistor threshold voltage, NMOS processing became commercially viable. In NMOS technology, the basic circuit element is the nchannel MOSFET [27]. Because of the inherent higher switching speeds of n-channel devices over p-channel devices, NMOS soon overtook PMOS in importance. combination of n-channel and p-channel in one chip - CMOS technology - offers lower static power consumption and is of increasing prominence, despite its added complexity. NMOS technology is still likely to However, significant importance in the future.

Table 2.1 shows a typical sequence of steps for NMOS fabrication. It has been based on the 5-micron [28] which is run Edinburgh process in the Microfabrication Facility (EMF) clean rooms at University of Edinburgh. The major processing steps are now discussed:

- i) The starting material is 3" diameter, <100> orientation, lightly-doped p-type silicon wafers.

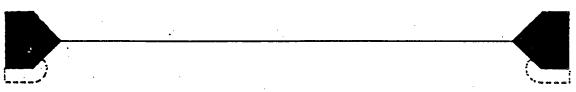

- ii) Active device areas are first isolated with thick field oxide (Fig. 2.2(a)) using the LOCOS process. An  $\mathrm{Si}_3N_4$  mask is used to inhibit oxide growth in

```

1. Substrate : P-type <100> 14-20 ohm.cm silicon

2. Pad Oxide: 500Å dry-wet-dry oxide (950°C)

3. Si<sub>3</sub>N<sub>4</sub> Deposition : 500Å, LPCVD

4. 1st Photo : Definition of field areas

5. Field Implant : Boron 2 x 10^{13} cm<sup>-2</sup> 130 keV

6. Si<sub>3</sub>N<sub>4</sub> Etch : CF<sub>4</sub>/O<sub>2</sub> plasma

7. Resist Strip : Fuming nitric acid

8. Oxide Etch : HF/NH,F solution

9. Field Oxidation: 10 000Å wet oxidation (950°C, 16 hrs)

10. Si_3N_4 Etch : CF_4/O_2 plasma

11. 2nd Photo: Depletion threshold adjustment

12. Depletion Threshold Implant: Arsenic 1.5x10<sup>12</sup> cm<sup>-2</sup> 90 keV

13. Resist Strip : Fuming nitric acid

14. Gate Oxidation: 800Å dry-wet-dry oxide (950°C)

15. Enhancement Threshold Implant: Boron 11.3x10<sup>11</sup> cm<sup>-2</sup> 40 keV

16. Anneal: 950^{\circ}C for 30 min in N<sub>2</sub>

17. 3rd Photo: Buried contact

18. Oxide Etch : HF/NH,F solution

19. Resist Strip : Fuming nitric acid

20. Polysilicon Deposition: 3500Å, LPCVD

21. 4th Photo : Polysilicon gate and interconnect

22. Polysilicon Etch : CF4/O2 plasma

23. Resist Strip : Fuming nitric acid

24. Phosphorms: Diffusion: 1000°C in N2 (solid Ph source)

25. Polysilicon Oxidation: 2000Å dry-wet-dry oxide (950°C)

26. Ph-doped Oxide Deposition: 7500Å phosphosilicate glass

27. Reflow 1 (densification): 20 min at 1050°C in O,

28. 5th Photo: Contact holes

29. Oxide Etch : HF/NH,F solution

30. Resist Strip : Fuming nitric acid

31. Reflow 2 (step coverage) : 20 min at 1050°C in O2

32. Aluminium Deposition: 15000Å evaporated aluminium

33. 6th Photo: Aluminium interconnect

34. Aluminium Etch : Aluminium etch sloution

35. Resist Strip : Fuming nitric acid

36. Sinter: Low temperature anneal (450°C)

37. Ph-doped Oxide Deposition: 7500Å phosphosilicate glass

38. 7th Photo: Pad areas

39. Oxide Etch : HF/NH,F solution

40. Resist Strip : Fuming nitric acid

```

TABLE 2.1 Outline of the processing steps in the EMF  $5\,\mathrm{um}$  NMOS process.

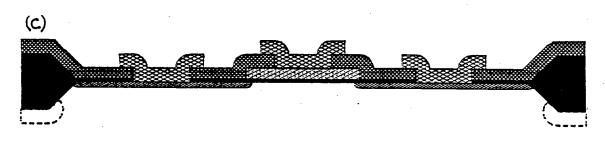

Fig. 2.2 Three stages in the production of an n-channel MOSFET (a) Isolation of active device areas (b) Fabrication of the MOSFET structure. (c) Interconnection with Aluminium.

active regions. A boron implant under the field areas provides the electrical isolation between active areas.

- iii) The MOSFET is fabricated with a thin thermallygrown gate oxide and a phosphorous-doped polysilicon gate material (Fig. 2.2(b)). A selfaligning process [29] that aligns the start of the diffused source/drain regions to the edge of the is used to reduce parasitic overlap capacitances and give faster circuit operation. Implants of arsenic and boron are used to adjust the threshold voltages of the two types transistors found in NMOS : enhancement (i.e. normally off) and depletion (i.e. normally on). An additional sequence not shown in Fig. 2.2(b) defines buried contacts, where polysilicon makes direct contact to the silicon substrate.

- iv) The individual devices are interconnected with aluminium (Fig. 2.2(c)). Before its evaporation, a thick phosphorous-doped silicon dioxide layer is deposited over the whole wafer to isolate the underlying structures. Contact holes are etched in this layer where the aluminium is to contact polysilicon or diffused regions.

- v) A final phosphorous-doped oxide layer provides mechanical protection and reduces the sensitivity of the devices to ionic contamination. Windows are cut in this passivation layer over the pad areas where external connection will be made to the chip.

#### 2.3 Requirements for VLSI Processing

A process such as that just described produces devices with a minimum feature size of 5um. The shrinking of this minimum geometry to VLSI levels (i.e. <2um) requires many additional processing techniques and technological innovations. Gate oxidation and process automation are two particularly crucial areas of VLSI fabrication and will be discussed later in detail. Other VLSI techniques include:

- i) replacement of the LOCOS process with alternative isolation techniques that reduce or eliminate the well-known bird's beak effect [30] and so enhance packing density. A variety of techniques exist including the SWAMI process [31], moat isolation [32] and trench isolation [33].

- ii) the use of implantation to form source/drain regions. This allows shallower, better controlled junctions. Arsenic is used as the dopant, in preference to phosphoruss, to reduce lateral dopant diffusion under the transistor gate.

- iii) reducing unwanted dopant diffusion by using rapid thermal processing [34,35] instead of long, high-temperature furnace treatments.

- iv) the use of refractory metal silicides in place of, or in conjunction with, polysilicon as gate and inter-connect material [36]. This reduces parasitic resistances and speeds up circuit operation.

- v) drain-engineering techniques [37,38] such as lightly doped drain (LDD) that reduce the problems associated with high-fields encountered in small geometry MOSFETS.

vi) additional channel implants below the silicon surface. These raise the doping concentration and help prevent device punchthrough without increasing the bulk dopant concentration.

#### 2.3.1 Gate Oxides for VLSI

The general downward scaling of device dimensions has necessitated a reduction in gate oxide thickness. Thicknesses of 150-250Å are now required for lum technologies, and even thinner oxides will be needed in the future. Two problems are associated with thin oxides - thickness uniformity and oxide quality (i.e. dielectric properties and charge density levels).

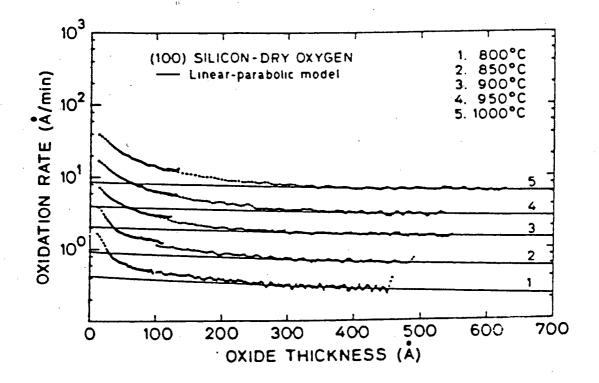

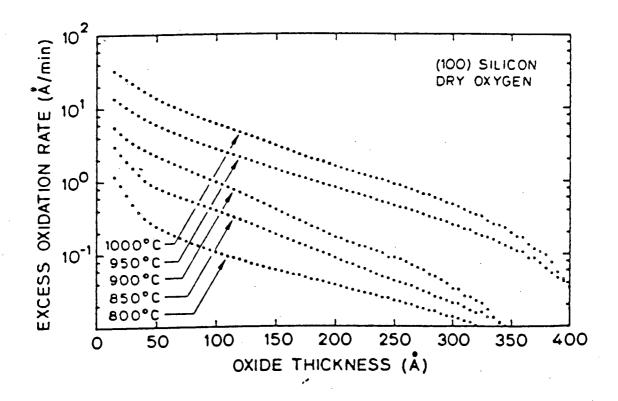

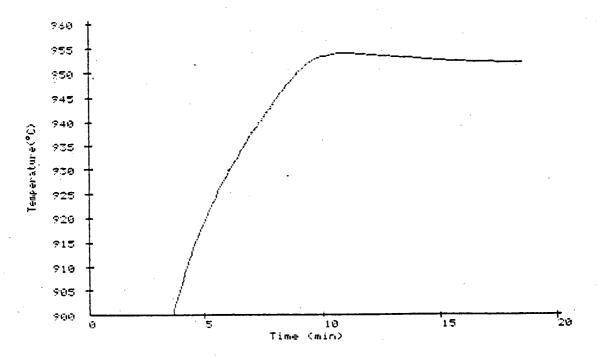

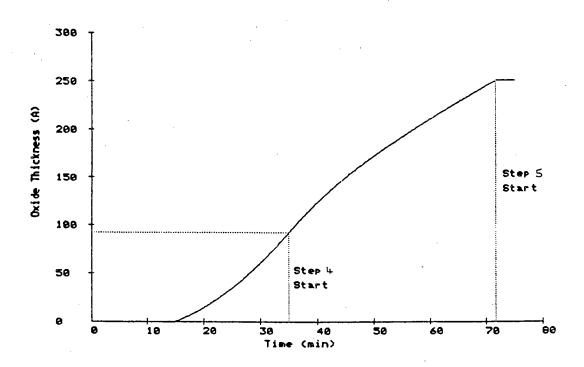

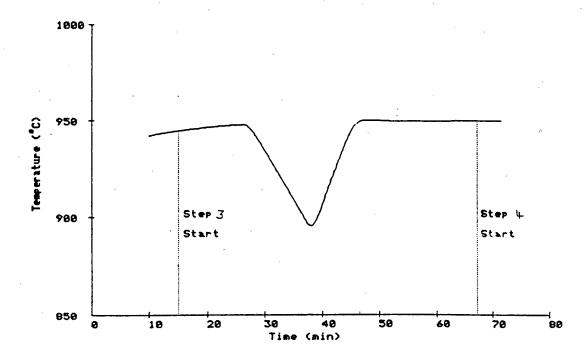

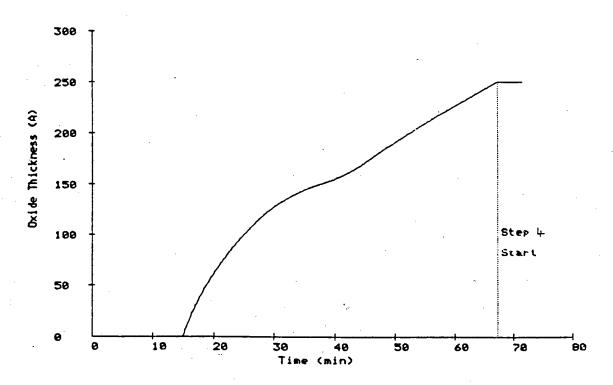

Oxide thickness is one of the most important MOS and appears as a first order expressions for threshold voltage, transconductance, gain and the body effect<sup>3</sup>. Control of oxide thickness is therefore crucial for stable device operation. As the oxide thickness is reduced, the tolerable thickness variation is also reduced (Table 2.2) increasingly difficult to achieve. The established method of growing gate oxide is furnace oxidation in a dry ambient at high temperature (950-1100°C). thinner oxides, growth times become very short (e.g. about 30 minutes for 200Å at 950°C). This augments the problem since growth during transient periods becomes increasingly significant. The control capability of current furnace technology, with respect to transient effects, is investigated in Chapter 4.

The principle MOSFET relationships are discussed in Appendix A. Comprehensive treatments on MOS device physics can be obtained in texts such as Sze [27] and Nicollian and Brews [39].

| Minimum Device<br>Feature<br>(um) | Typical<br>Gate Oxide<br>Thickness<br>(Å) | Required<br>Tolerance<br>(Å) | Approx. Dry Oxidation Time at 950°C (min) |

|-----------------------------------|-------------------------------------------|------------------------------|-------------------------------------------|

| 5.0                               | 800                                       | 40.0                         | 245                                       |

| 2.5                               | 400                                       | 20.0                         | 90                                        |

| 1.25                              | 250                                       | 12.5                         | 40                                        |

| 0.5                               | 100                                       | 5.0                          | 9                                         |

|                                   |                                           |                              |                                           |

TABLE 2.2 The effect of scaling on the tolerable variation in oxide thickness.

Lowering the oxidation temperature below 900°C will decrease the growth rate and allow longer oxidation times. Such low-temperature oxides have good breakdown characteristics, but the Si-SiO<sub>2</sub> interface properties are found to be poorer than those from high-temperature oxidations [40]. Since MOSFET characteristics are very sensitive to interface and oxide charges<sup>4</sup>, the higher temperature oxides are still preferable.

The need to optimise dielectric properties and charge density levels has given rise to novel oxidation procedures for VLSI gate oxides. The beneficial effects of adding chlorine species to a dry oxidation ambient or a post-oxidation annealing in an inert ambient have been exploited in multi-step oxidation processes. include dual-HCl [41], dual-TCE (trichloroethylene) [42] processes and oxidation with an intermediate anneal [43]. However, all involve very high-temperature (>=1050°C) and go against the general VLSI tendency towards lower temperature processing. Such complex procedures may also be expected to hinder control of oxide thickness.

Rapid Thermal Oxidation (RTO) has recently been suggested as an alternative method for the growth of high-quality thin oxides [44,45]. In this technique, single wafers are placed flat on support pins inside a small quartz tube. Heating is provided by tungstenhalogen lamps, which allow very fast temperature ramps. Without the thermal mass of a boat load of wafers to heat, as in conventional oxidation, high temperatures of up to 1200°C can be achieved in the order of a few seconds (even wafer heating prevents induced thermal stress and wafer warpage). Rapid purging of process

<sup>4</sup> Oxide charges are discussed in Chapter 5.

gases in the small reactor volume further reduces the impact of transient periods on the overall process. Oxidation rates are enhanced by this method [45,46] and very short high-temperature cycles (i.e less than 5 minutes) are possible, with the result that excessive silicon dopant redistribution is avoided.

Temperature in RTO systems is usually monitored with a pre-calibrated optical pyrometer and is computer-controlled with a closed feedback loop. The accuracy of this method seems to be adequate and wafer-to-wafer thickness uniformities of 1% to 6% have been reported for thicknesses in the range 50Å to 350Å [45]. However, problems at high temperatures with high lamp intensity interfering with the pyrometer measurements were also noted in [45]. Since very high oxidation temperatures are possible, the oxide films produced using RTO can be of high quality [47].

Despite the above advantages, RTO cannot match the throughput of conventional furnace systems and RTO films have not yet seen widespread use as a gate dielectric However, with future processes, where wafers larger 6" than diameter, RTO and applications of rapid thermal processing (see previous section) are likely to see increased use in critical This is because wafers are heated (and process steps. cooled) uniformly, in comparison to conventional furnace systems where wafer heating is from the edge inwards. Additionally, in specific applications such as ASICs (which are becoming an increasingly important branch of IC production) batch size may be small and so throughput by rapid thermal processing techniques becomes more comparable with that from conventional methods.

Nitrided SiO<sub>2</sub> and nitrided Si have also generated recent interest as alternatives to thermally grown gate

oxide [48]. The films are formed in pure ammonia gas at high temperature. Plasma enhancement is usually used since the thermal reaction is a very slow process. Although improved characteristics - including a higher dielectric constant - can be obtained, further investigation of such films is needed before they can fully replace the much better understood Si-SiO<sub>2</sub> system.

It is clear that there are significant advantages from be conventional gained furnace oxidation including throughput, equipment reliability and general compatibility with existing fabrication procedures. ability satisfy the to thickness uniformity requirements of VLSI under the conditions necessary for high oxide quality is crucial to its continued use in gate oxidation. Advances in furnace technology over the past ten years have led to total automation of furnace The significance of these developments with operations. respect to oxide thickness control is investigated in Chapter 6.

## 2.3.2 Process Automation

Automation of the wafer fabrication process is becoming increasingly important to maintain VLSI productivity. It is driven by the need for high process yield in the face of increasing process complexity and reduced feature size. Automation takes many forms but can be most easily categorised with respect to the three main mechanisms that influence overall process yield. These are:

i) defects caused by particles and contamination

Even with advanced clean room capability,

particulate contamination cannot be completely

eliminated. Humans are amongst the largest

sources and considerable effort has been directed keeping humans and wafers apart. automation has already been implemented at individual equipment level, but only recently have the problems of wafer transport between stations and the equipment loading/unloading interface been Concepts such as the SMIF box [49] addressed. coupled with robotic handling systems [50] are now seeing increased use. Clean track systems suspended from a ceiling or wall, or automated quided vehicles are the main alternatives for wafer transportation [51].

#### ii) wafer breakage and misprocessing factory management is needed concurrently steer many different successfully through the hundreds of individual of advanced technologies, process steps particularly when the factory may be running several different processes and process variations. Computer aided manufacturing (CAM) software [1,2], such as COMETS and PROMIS, can help eliminate wastage by keeping track of, and routing, work in progress.

#### iii) process control

As discussed in Chapter 1, many process steps run open-loop and process control would be enhanced by the provision of automatic feedback control. This thesis develops a specific means of implementing such control at the equipment level. In addition, automated data handling and movement, by means of equipment interfaced to a centralised CAM system, will reduce the scope for error and can also be expected to improve overall process yield.

Although CAM systems are now implemented in many fabrication lines, and much new equipment incorporates standard interfaces like the SMIF concept or SECS, full process automation is still some way off. The transition will be facilitated by the development of individual highly-automated processing modules that can complemented by automatic wafer transport. These modules can gradually be introduced as they become available, with minimum disruption to the production The active control system proposed here, environment. being based at the equipment level, is in accordance with this approach to process automation.

#### 2.4 Process Simulation

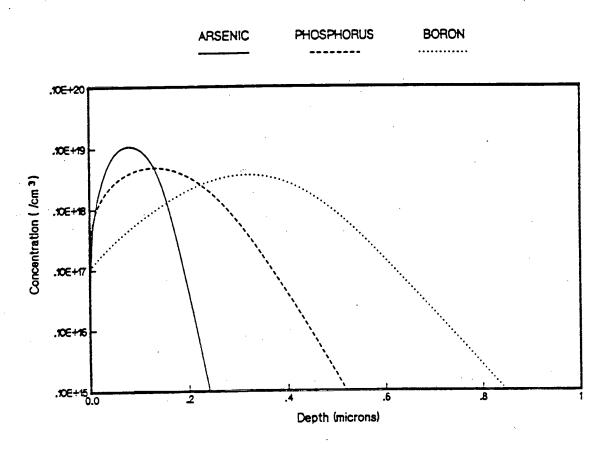

The driving force behind process simulation has been the need to predict the effect of process changes on device and circuit characteristics. Not only is experimentation thus reduced, but detailed information and added insight about the process can be obtained. A description of the process flow - including details of temperature and time - is used as input to the process simulation. The effect of each process step on dopant ions is modelled and the resultant impurity distribution forms the output (Fig. 2.3). This may then be coupled with a device simulator to estimate device parameters.

Of several process simulation packages available, SUPREM II, ICECREM, SUPREM III, SUPRA and SAMPLE are amongst the most well-known. SUPREM II [52], one of the earliest programs, incorporates one-dimensional models for oxidation, diffusion, deposition, implantation and etching. It is limited to two process layers and has been superseded by SUPREM III [5] which can model up to ten layers, including polysilicon, and includes some

Fig. 2.3 Sample output form ICECREM simulation : Concentration profiles of implanted As, P and B after a high temperature diffusion.

enhancement to the individual models. ICECREM [53] has similar capabilities to SUPREM II.

As device geometries shrink, lateral effects must also be considered, and much effort has been directed at the development of 2-D simulators [54,55]. SUPRA models oxidation and diffusion in two dimensions and SAMPLE is a topographical simulator of the lithographic process. SUPREM IV [55] is a more advanced 2-D process simulator, that has recently been developed as the 2-D equivalent to SUPREM III.

The models used in simulators are based on a mixture of physical theory and empirical fits to experimental data. Numerical methods are used to solve the complex diffusion equations. Simulation is complicated by coupling between oxidation and diffusion, impurity clustering and impurity segregation. In two dimensions, the changing shape of the device structure (e.g. bird's beak in LOCOS) must also be considered and has prompted the use of new mathematical algorithms to avoid excessively long computing time.

Model parameters may sometimes be adjusted to suit individual processes and there remain gaps understanding of some physical processes (examples include phosphorus diffusion and thin oxide growth). Nevertheless, models have generally improved over the years and are applicable under an ever wider range of operating conditions. They are sufficiently refined that new applications of simulation, beyond the role as a tool in process development, can now be considered. such application, simulation in real-time through direct coupling with process equipment, is the topic addressed by this thesis.

#### **CHAPTER 3**

#### **OXIDATION OF SILICON**

### 3.1 Kinetics of Oxide Growth

Silicon oxidises in the presence of oxygen or water vapour according to the following reactions, to give a film of SiO<sub>2</sub> on the silicon surface.

"Dry" oxidation:

$$Si + O_2 ----> SiO_2$$

(3.1)

"Wet" oxidation :

$$Si + H_2O ----> SiO_2 + H_2$$

(3.2)

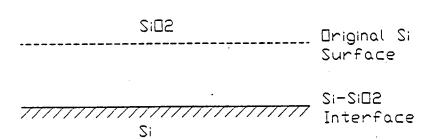

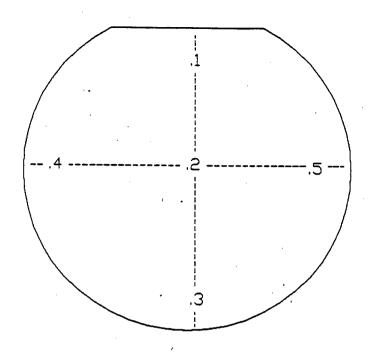

Marker experiments using  $^{18}\mathrm{O}$  have shown that the mechanism of these reactions involves diffusion of the oxidising species through any existing  $\mathrm{SiO}_2$  film, and subsequent reaction with silicon at the  $\mathrm{Si-SiO}_2$  interface [56,57]. The interface therefore moves into the silicon as more and more  $\mathrm{Si}$  is converted to  $\mathrm{SiO}_2$ . The differences in the density and molecular weight of  $\mathrm{Si}$  and  $\mathrm{SiO}_2$  indicate that a volume increase of approximately  $\mathrm{100}$ % accompanies the reaction, so that the  $\mathrm{SiO}_2$  is not coplanar with the original silicon surface (Fig. 3.1).

The following analysis of the kinetics of the oxidation reaction leads to the well-known linear-parabolic growth law and is based on the description proposed by Deal and Grove in 1965 [6].

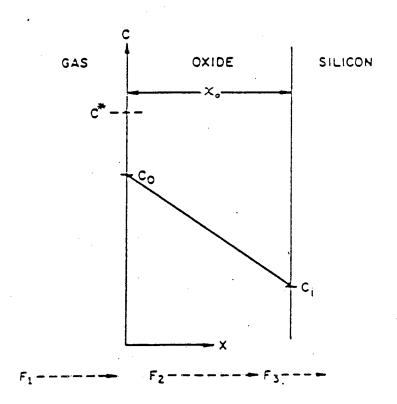

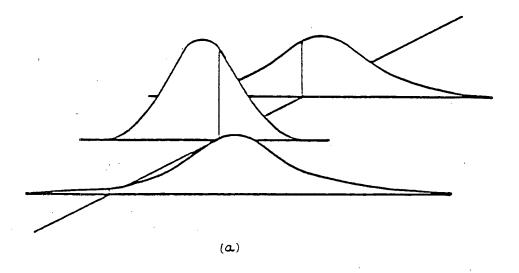

For oxide to form at the  $Si-SiO_2$  interface, the oxidising species must go through three distinct stages as shown in Fig. 3.2. It must first be adsorbed from

Fig. 3.1 The volume increase resulting from oxidation of silicon. Approximately 60% of the newly formed  $\rm SiO_2$  lies above the original Si surface.

Fig. 3.2 Model for the thermal oxidation of silicon. The fluxes  $F_1$  to  $F_3$  correspond to the three stages of oxide growth: adsorption of the oxidising species from the gas phase, diffusion through the oxide, and reaction with silicon respectively.

the gas phase onto the outer surface of the oxide already formed. It then diffuses through the oxide to reach the interface where it finally reacts with the Si to form  $SiO_2$ .

Assuming that all these processes reach a steadystate, then the flux of oxidant in each are equal. (Flux is the number of molecules crossing a unit area in unit time.)

Flux  $F_1$ , as illustrated in Fig. 3.2, is assumed to be

$$F_1 = h (C^* - C_0)$$

(3.3)

where  $C_0$  is the concentration of the oxidant in the outer surface of the oxide and  $C^{\star}$  is the equilibrium concentration for the oxidant in the oxide. h is a gasphase mass transport coefficient. Henry's Law states that the equilibrium solid concentration is proportional to the bulk gas partial pressure, so that

$$C^* = K P \tag{3.4}$$

The use of Henry's Law assumes that there is no dissociation (or association) of the oxidant at the outer surface.

Flux  $F_2$ , the diffusion of oxidant across the oxide layer, is assumed to be given by Fick's Law, which states that flux is proportional to the concentration gradient.

$$F_2 = -D_{eff} - \frac{dC}{dx} = D_{eff} - \frac{(C_o - C_i)}{x_o}$$

(3.5)

where  $D_{\rm eff}$  is the effective diffusion coefficient,  $C_{\rm i}$  is the oxidant concentration near the oxide-silicon interface and  $x_{\rm o}$  is the oxide thickness.

Flux  $F_3$ , describing the oxidation reaction at the interface, is given by

$$F_3 = k_s C_i \tag{3.6}$$

where  $\mathbf{k}_{\mathrm{S}}$  is the interface reaction rate constant for the oxidation.

If steady-state conditions exist, then  ${\bf F_1}={\bf F_2}$  and  ${\bf F_2}={\bf F_3}$ , and it can be shown that

$$C_{i}^{*} = \frac{C^{*}}{1 + k_{s}/h + k_{s}x_{o}/D_{eff}}$$

(3.7)

and

$$C_{o} = \frac{C^{*} \{ 1 + k_{s}x_{o}/D_{eff} \}}{1 + k_{s}/h + k_{s}x_{o}/D_{eff}}$$

(3.8)

The flux of oxidant  $F = F_1 = F_2 = F_3$  is given by

$$F = k_s C_i = \frac{k_s C^*}{1 + k_s / h + k_s x_o / D_{eff}}$$

(3.9)

and the oxide growth rate by

$$\frac{dx_{o}}{dt} = \frac{F}{N_{1}} = \frac{k_{s}C^{*}/N_{1}}{1 + k_{s}/h + k_{s}x_{o}/D_{eff}}$$

(3.10)

where  $N_1$  is the number of oxidant molecules incorporated into a unit volume of the oxide.

This differential equation is solved by integration, assuming an initial condition  $x_0 = x_1$  at time t=0.

This yields the following generalised relationship:

or

$$x_0^2 + Ax_0 = B (t + \tau)$$

(3.12)

where

$$A = 2 D_{eff} (1/k_s + 1/h)$$

(3.13)

$$B = 2 D_{eff} (C^*/N_1)$$

(3.14)

$$T = (x_i^2 + Ax_i)/B \qquad (3.15)$$

$\tau$  corresponds to a shift in time which corrects for the presence of an initial oxide of thickness  $x_i$ .

The growth rate is given by

$$\frac{dx_{o}}{-dt} = \frac{B}{-x_{o} + A}$$

(3.16)

The solution to equation 3.12 gives two distinct limiting cases:

i) When

$$(t + \tau) >> A^2/4B$$

then  $x_0^2 = B(t + \tau)$  (3.17)

Parabolic kinetics: B is referred to as the parabolic rate constant.

ii) When

$$(t + \tau) << A_0^2/4B$$

then  $x_0 = B/A(t + \tau)$  (3.18)

Linear kinetics: B/A is referred to as the linear rate constant.

$$B/A = \frac{C^*}{N_1 (1/k_s + 1/h)}$$

(3.19)

The reaction rate in those two cases is determined by different mechanisms as shown by the different expressions for B and B/A (equations 3.14 and 3.19). In the linear regime, oxygen is in excess at the interface and the oxide growth rate is controlled only by the rate at which oxygen can react with silicon. This is

indicated by the dependence of B/A on  $k_{\rm s}$ . In this respect, the gas-phase mass transport coefficient, h, is assumed to be large, so that the 1/h term in the expression for B/A can be neglected. Oxide growth is then said to be surface reaction-limited.

In the parabolic regime, oxidant reacts with silicon faster than it can be supplied to the interface and the oxide growth rate is controlled by the diffusion of oxidant across existing oxide, as indicated by the  $D_{\mbox{eff}}$  dependence of B. Here the oxidation is said to be diffusion-limited.

Whether the oxidation is reaction-limited or diffusion-limited depends upon temperature and oxide thickness. Generally, short oxidations are reaction-limited (linear kinetics) and long oxidations are diffusion-limited (parabolic kinetics).

# 3.2 Examples of Oxide Growth and Relation to Theory

Oxide growth is influenced by a number of experimental factors, notably oxidation ambient, temperature, substrate crystal orientation, pressure and substrate doping concentration. Although the Deal-Grove model provides a basis for all these observed effects, it does not give a complete understanding of the formation of  $SiO_2$ . Additional and more detailed theories have therefore been developed with the increased amount of experimental oxidation data that has become available. The above effects and their relation to Deal-Grove theory are now discussed.

## 3.2.1 Temperature Dependence of Rate Constants

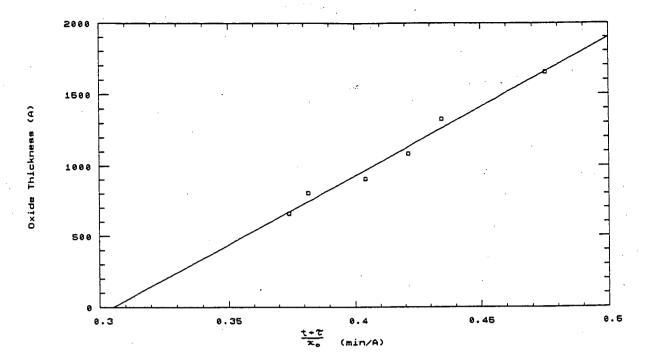

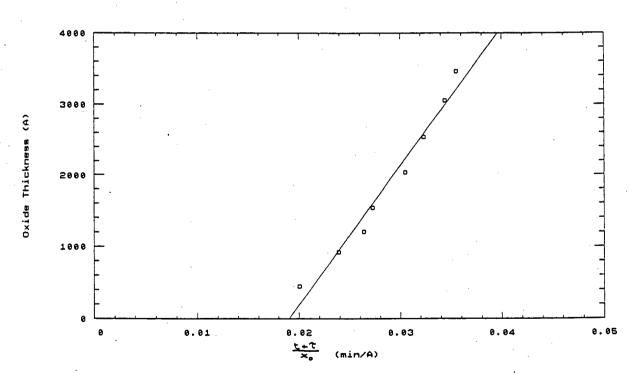

The values of B and B/A can be evaluated from experimental data by rewriting equation 3.12 as

$$x_0 = \{ (t + \tau)/x_0 \} B - A$$

(3.20)

Hence a plot of  $x_0$  versus  $(t + \tau)/x_0$  gives a straight line of slope B and an intercept on the vertical axis equal to -A. Such an analysis was carried out by Deal and Grove on oxidation data of <111> orientated silicon [6]. The results are summarised in Table 3.1. It can be seen that the parabolic rate constant B is substantially greater for wet oxidation than for dry oxidation. This is reflected in the dependence of B on the equilibrium concentration of  $C^*$  (equation 3.14), which is three orders of magnitude larger for water than for oxygen.

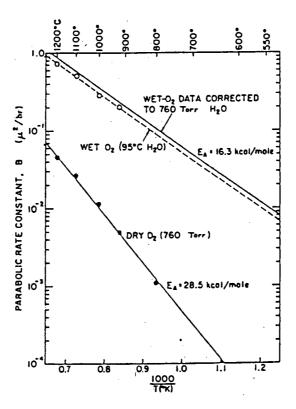

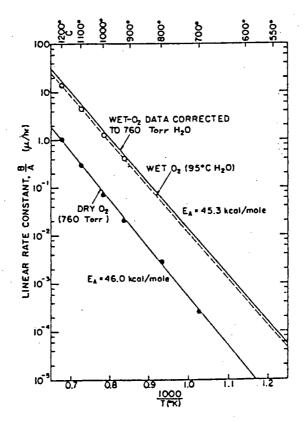

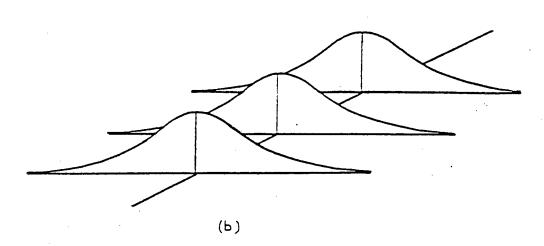

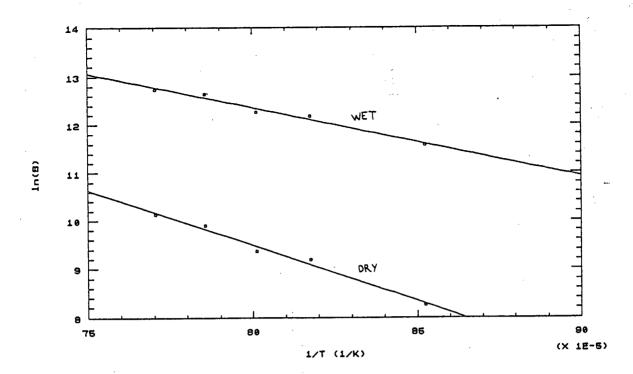

These early experimental measurements of the rate constants showed them to exhibit Arrhenius behaviour. The temperature dependence of B (Fig. 3.3) is similar to that of  $D_{\rm eff}$  as might be expected from equation 3.14, i.e. B increases exponentially with temperature. The activation energies are different for wet and dry oxidations, but the calculated values of 0.71 eV and 1.24 eV respectively (units converted from the original kcal/mole used in [6]) compare well with the diffusivity through silica of  $H_2O$  (0.80 eV) and  $O_2$  (1.17 eV).

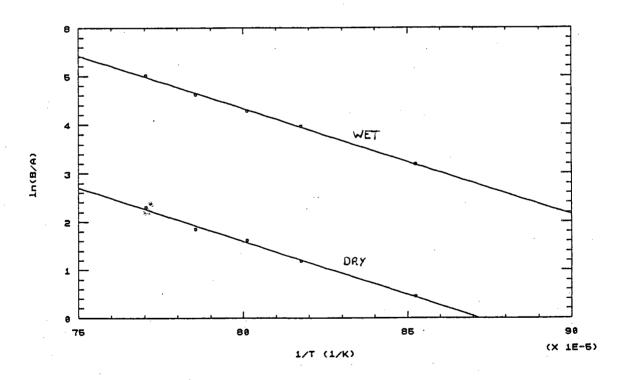

The temperature dependence of B/A (Fig. 3.4) shows almost identical activation energies for both wet and dry oxidation (1.96 eV and 2.00 eV respectively). Since the linear reaction regime is reaction-controlled, this indicates a similar reaction mechanism for the two

| Ambient | Oxidation<br>Temp<br>(°C) | A<br>(Å) | B<br>(10 <sup>3</sup> Å <sup>2</sup> /min) | B/A<br>) (Å/min) | T<br>(min) |

|---------|---------------------------|----------|--------------------------------------------|------------------|------------|

| DRY     | 800                       | 3700     | 1.8                                        | 0.5              | 540.0      |

| DRY     | 920                       | 2350     | 8.2                                        | 3.5              | 84.0       |

| DRY     | 1000                      | 1650     | 19.5                                       | 11.8             | 22.2       |

| DRY     | 1100                      | 900      | 45.0                                       | 50.0             | 4.5        |

| DRY     | 1200                      | 400      | 75.0                                       | 187              | 1.6        |

| WET     | 920                       | 5000     | 338                                        | 67.7             | 0          |

| WET     | . 1000                    | 2260     | 478                                        | 212              | 0          |

| WET     | 1100                      | 1100     | 850                                        | 773              | 0          |

| WET     | 1200                      | 500      | 1200                                       | 2400             | 0          |

TABLE 3.1 Rate constants for oxidation of <111> silicon in wet and dry oxidation. (from [6])

Fig. 3.3 Temperature dependence of the parabolic rate constant B (from [6]).

Fig. 3.4 Temperature dependence of the linear rate constant B/A (from [6]).

oxidants. The activation energies represent the temperature dependence of the interface reaction-rate constant  $k_{\rm s}$ , and approximate to the Si-Si bond energy of 2.00 eV.

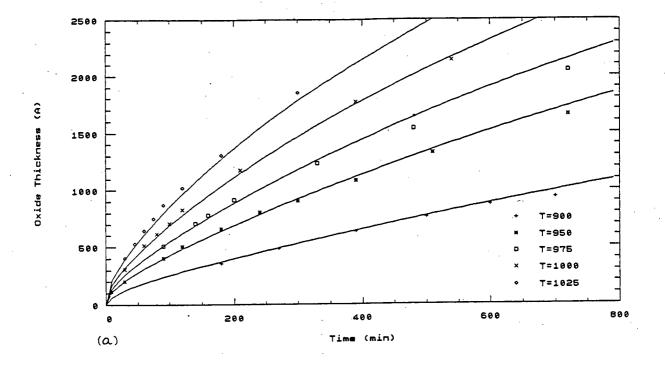

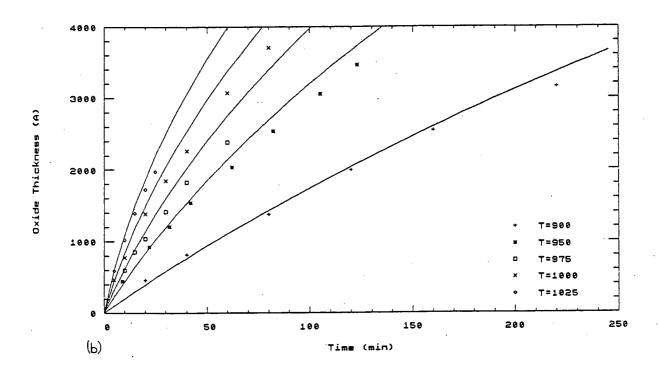

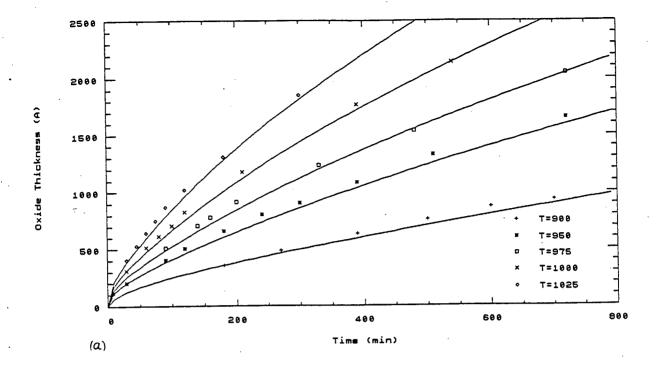

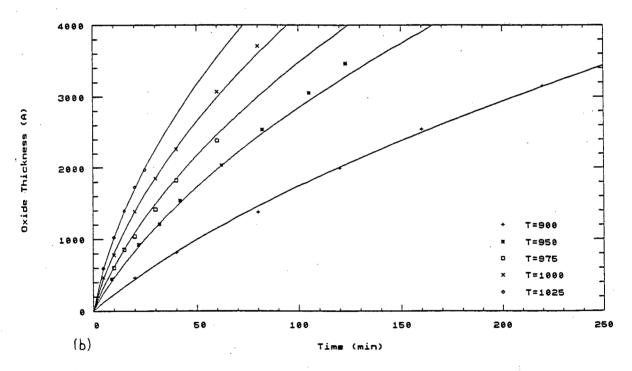

More recent investigations [58] were extended to include thinner oxides and lower oxidation temperatures than those previously studied. It was found that the Arrhenius plots had considerable curvature, indicating that the reaction mechanism may be more complex than that portrayed by the Deal-Grove model (this is discussed further in Section 3.2.5.). However, oxide growth data collected by this author (see Chapter 7), temperature range 900°C to 1025°C and thickness range 100Å to 4000Å, showed no clear curvature within the distribution of points in the Arrhenius plots, and a linear fit was used. The controversy here is due to propagation of error in the parameter extraction method and the general insensitivity of the Deal-Grove model to the parameter values used. In a recent paper [59] it was shown that a broad range of B and B/A combinations could give model fitting errors smaller than experimental error and that the existence of breakpoints in the Arrhenius plots could therefore be an artifact of the analysis method. In Chapter 7 two different parameter sets are shown to give comparable fitting errors, confirming the model insensitivity to the parameter values used.

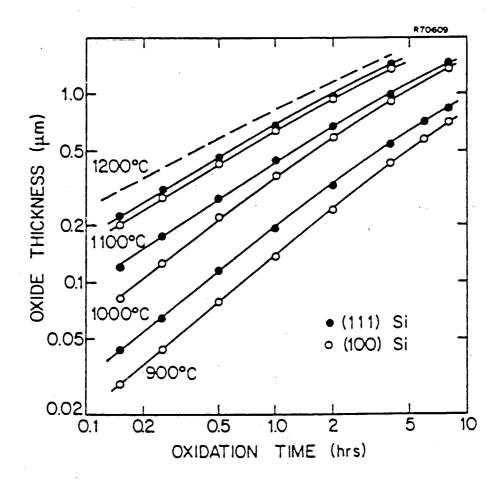

# 3.2.2 Influence of Silicon Crystal Orientation

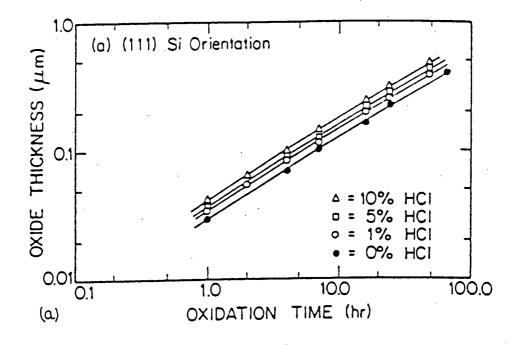

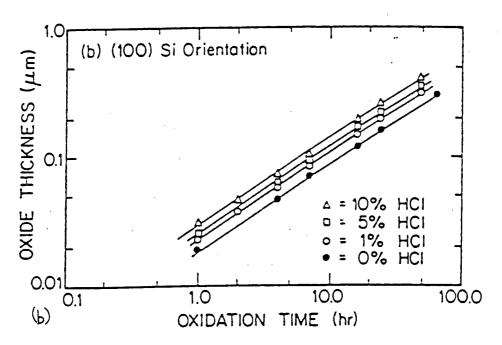

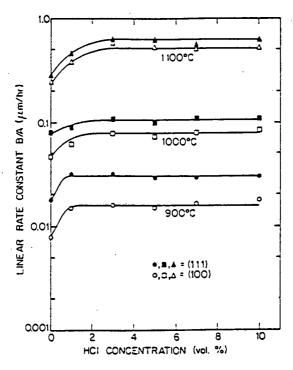

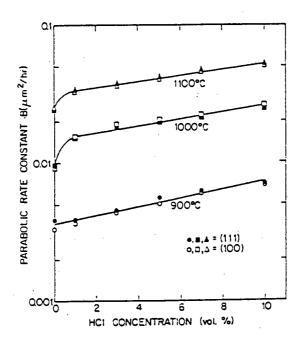

The data in Fig 3.5 show how oxidation kinetics depend upon the crystallographic orientation of the silicon surface. Orientation determines the silicon surface atom concentration. It is logical that this

will influence the interface reaction rate constant k, and hence the linear rate constant B/A. In comparison, the parabolic rate constant would be expected to be independent of silicon orientation. These properties have been confirmed [60] for the wet oxidation of <111> and <100> orientation silicon (Table 3.2). rate constants for <111> silicon are 1.68 times the for <100> silicon at all corresponding temperatures, indicating a similar enhancement mechanism.

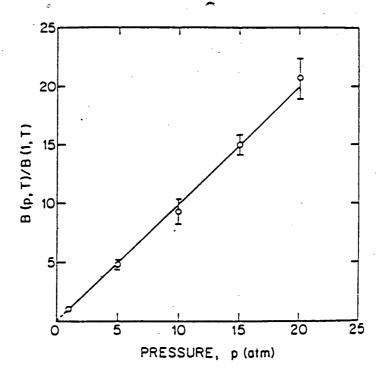

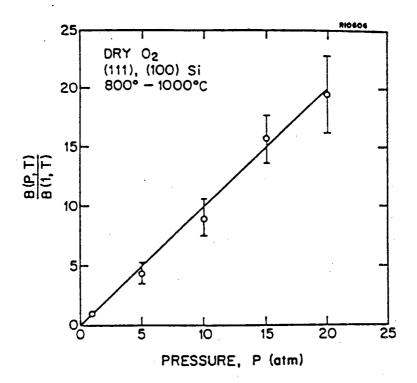

# 3.2.3 Pressure Dependence of Oxidation Rate

The expressions for both the linear and parabolic rate constants (equations 3.14 and 3.19) show a dependence on  $C^*$ , the equilibrium concentration of oxidant in the oxide. Since  $C^*$  is proportional to oxidant partial pressure (assuming Henry's Law - equation 3.4), both B and B/A are expected to have a linear partial pressure dependence.

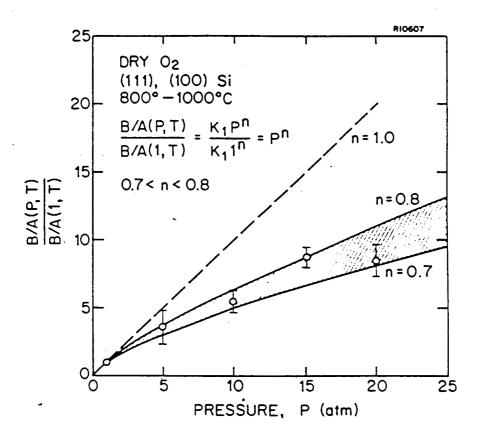

Deal and Grove [6] presented confirmation of this for the parabolic rate constant based on the experimental data of Flint [61]. The argument has been extended to high pressure oxidation [62,63], where investigations have shown a linear pressure dependence of B up to 20 atmospheres for both wet and dry oxidation (Figs. 3.6 and However, the same investigations have shown that 3.7). the (high) pressure dependence of B/A is only linear for wet oxidation: in dry oxidation a sub-linear pressure dependence of B/A observed (Fig. 3.8), is proportionality to the power of n where 0.7 < n < 0.8. Similar results for pressures less than one atmosphere have also been found [64].

Fig. 3.5 The effect of crystal orientation on the oxidation rate of silicon. Data shown is for <111> and <100> silicon under wet oxidation conditions. (from [60])

|          | 0:3:                   | В                               | B/A            | B/A ratio   |

|----------|------------------------|---------------------------------|----------------|-------------|

| Temp(°C) | Silicon<br>Orientation | $(10^5 \text{ Å}^2/\text{min})$ | (Å/min)        | <111>/<100> |

| 000      | 41005                  | 2.20                            | 25.0           |             |

| 900      | <100><br><111>         | 2.38<br>2.52                    | 25.0<br>42.0   | 1.68        |

| 950      | <100>                  | 3.85                            | 51.8           |             |

|          | <111>                  | 3.85                            | 87.3           | 1.68        |

| 1000     | <100><br><111>         | 5.23<br>5.23                    | 110.7<br>193.8 | 1.75        |

| 1050     | <100>                  | 6.88                            | 233.3          |             |

|          | <111>                  | 6.88                            | 384.5          | 1.65        |

| 1100     | <100><br><111>         | 8.68<br>8.62                    | 496.2<br>821.0 | 1.65        |

|          |                        |                                 |                |             |

|          |                        | 1                               | Average        | 1.68        |

TABLE 3.2 Rate constants for wet oxidation of <100> and <111> silicon. (from [60])

Fig. 3.6 Pressure dependence of B for wet oxidation. Data is normalised to P=1 atm. and is for the oxidation of <100> and <111> silicon in the temperature range 800-1000°C (from [62]).

Fig. 3.7 Pressure dependence of B for dry oxidation. Data is normalised to P=1 atm. and is for the oxidation of <100> and <111> silicon in the temperature range 800-1000°C (from [63]).

Fig. 3.8 Pressure dependence of B/A for dry oxidation. Data is normalised to P=1 atm. and is for the oxidation of <100> and <111> silicon in the temperature range 800-1000 °C (from [63]).

The linear pressure dependence of both B and B/A in wet oxidation indicates the species diffusing in the oxide is molecular  $H_2O$  (i.e. no dissociation occurs at the gas-oxide interface). Similarly, the pressure dependence of B in dry oxidation indicates the diffusing species is molecular 02. This is of course contradicted by the sub-linear pressure dependence of B/A Chez and Van der Meulen [65] have in dry oxidation. suggested that this discrepancy may be due oxygen dissociation of molecular at the interface, yielding atomic oxygen, and that both species (molecular and atomic oxygen) then undergo reaction at the interface. The relative contribution of these species accounts for the observed pressure dependence. similar explanation by Blanc [66] suggests interface reaction occurs by atomic oxidation only, but this results in a square-root dependence on partial pressure (n=0.5) and is therefore inaccurate. That a full physical explanation of the B/A pressure reflects still lacking, further dependence is complexity of the oxidation reaction mechanism, suggests the Deal-Grove model is over-simplified.

#### 3.2.4 Influence of Substrate Doping

During oxidation, substrate doping elements such as boron and phosphorous redistribute at the interface so that their chemical potential is equal on each side of the interface. This results in an abrupt shift in dopant concentration across the interface or, expressed differently, the dopant segregates either into the oxide or into the silicon substrate. It is defined quantitatively by the segregation coefficient, m:

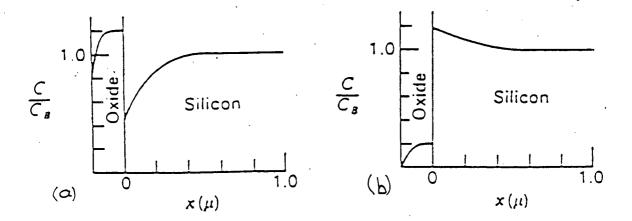

Boron is observed to segregate into oxide (m < 1) as shown in Fig. 3.9(a). The segregation coefficient increases with increasing temperature and is greater for <100> orientation than for <111> orientation silicon [67]. It has also been found to be greater for dry oxidation than for wet oxidation [68]. In contrast to boron, phosphorus segregation is into the silicon (m > 1) as shown in Fig. 3.9(b), a phenomenon known as 'pile-up'.

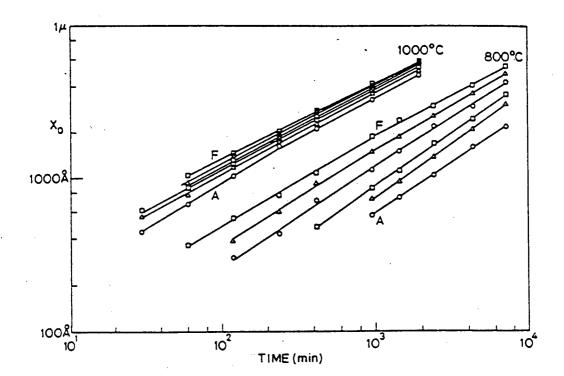

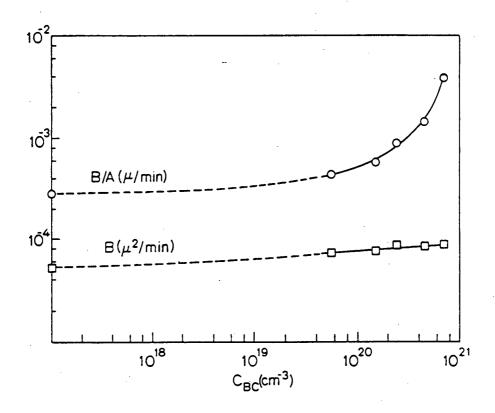

The oxidation rate of silicon is found to be enhanced by high concentrations of substrate elements [70] such as might be found in the source and drain regions of MOS devices. Fig. 3.10 shows the effect of high phosphorus doping levels on the dry oxidation kinetics of <111> silicon. Phosphoruss enhances the rate most effectively at lower temperatures. In contrast, boron gives a greater rate enhancement at temperatures (>1050°C). This temperature dependence of the rate enhancement has been correlated with dopant segregation effects [58]. The enhancement for both boron and phosphoruss is principally accounted for by an increase in the linear rate constant B/A [58,71] and the parabolic rate constant B relatively unchanged (Fig. 3.11). This relates to an influence on the Si-SiO, interface reaction rate constant Further explanation than this requires greater understanding of underlying physical mechanisms of the interface reaction, which are conveniently together in the parameter  $k_{\rm s}$ , and this is discussed in the next section.

Fig. 3.9 Impurity concentration (after oxidation) against depth, for initially uniformly doped silicon:

(a) m<1 (boron) - oxidation takes up impurity (b) m>1 (phosphorus) - oxide rejects impurity. (from [69])

Fig. 3.10 Oxide thickness against time for <111> silicon under dry oxidation conditions. A to F indicate increasing phosphorus doping concentrations:  $A=1\times10^{15}$ ,  $B=5.1\times10^{19}$ ,  $C=7.2\times10^{19}$ ,  $D=1.8\times10^{20}$ ,  $E=3.2\times10^{20}$  (units in cm<sup>-3</sup>). (from [71])

Fig. 3.11 Effect of phosphorous doping concentration on the rate constants B and B/A (data for dry oxidation of <111> silicon at  $900^{\circ}$ C). (from [71])

As is seen in Fig. 3.11, B is slightly enhanced with increasing dopant concentration, but the effect is much less distinct than that for B/A. It reflects an influence on the oxidant diffusivity and thus modification of the term  $D_{\rm eff}$  in the expression for B (equation 3.14). Oxidant diffusivity is enhanced because incorporation of dopant in the oxide gives a loosened SiO<sub>2</sub> structure [58].

#### 3.2.5 Mechanism of Oxide Growth

There is still uncertainty about the fundamental mechanisms of the Si-SiO2 interface reaction. Certainly the linear-parabolic model offers no physical insight into details of the interface reaction mechanism, successful as it is in describing many of the observed kinetics. It is clear, however, that for oxidation to proceed, a quantity of 'free volume' must be supplied, as evidenced by the volume change that occurs when silicon becomes SiO2. If insufficient volume is available, intrinsic stress develops in the oxide. This stress has been observed in oxides grown at low temperatures (<950°C) [72]. The absence of such stress in high temperature oxidations has been explained by Irene et al. [73] based on a visco-elastic model. In this model, high temperatures lower the oxide viscosity and allow oxide to flow in a direction normal to the wafer surface. This provides free volume and so relieves intrinsic At low temperatures, the viscosity is too high to relieve all the stress, which can then accumulate. Note that intrinsic stress should not be confused with thermal expansion stress which is zero at oxidation temperature and only develops as the sample cools down due to mismatch in the thermal expansion coefficients between silicon and SiO2.

The role of stress on oxide growth is further evidenced by densification of oxides grown at temperatures [74]. Densification occurs as a mechanism alleviate the build-up of stress and has correlated with the increase in the refractive index of oxides grown at low temperatures [75,76]. The intrinsic stress would be expected to influence both the diffusion of oxidant through the oxide and the interface reaction mechanism, and therefore affect the parabolic and linear Recent experiments [77,78] have rate constants. confirmed this, and it may explain, at least in part, the non-Arrhenius behaviour of the rate constants (Section 3.2.1). Oxide stress can lead to structural damage in the silicon and adversely affect the performance of devices.

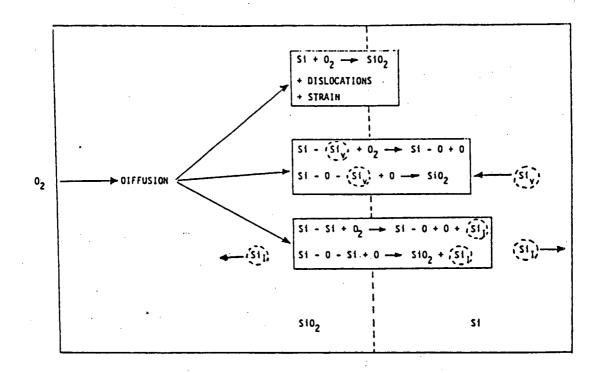

Fig. 3.12 shows a detailed model of the Si-SiO<sub>2</sub> interface reaction developed by a group at Stanford University. As oxidation proceeds and the interface progresses into the silicon, it leaves an excess of silicon atoms in each lattice plane [79,80]. This causes lattice mismatch at the interface which is stored as dislocation lines (dangling bonds) and strain in the SiO<sub>2</sub> film. It is represented by the top reaction in Fig. 3.12. Away from the interface, the strain is relieved by viscous flow that provides the required free volume, as discussed above.

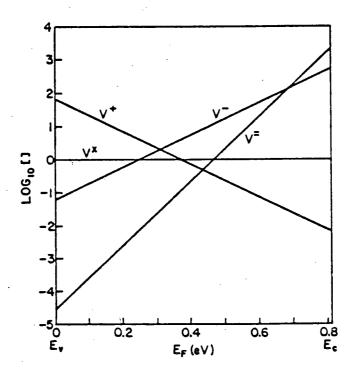

Alternative methods of providing free volume at the interface region itself are shown by the bottom two reactions in Fig. 3.12. These are based on point defects, representing the presence of a silicon vacancy ( $\mathrm{Si}_{\mathrm{V}}$ ) in the substrate and the removal of silicon atoms from lattice sites to create interstitials ( $\mathrm{Si}_{\mathrm{I}}$ ) respectively. Point defects exist in several charge states [81] which have energy levels in the band gap, so

that their concentration depends upon the position of the Fermi level (Fig. 3.13). A shift in the position of the Fermi level will therefore change the number of point defects and so influence the oxidation. This can explain the observed rate enhancement with high phosphorous doping levels. The increased doping level shifts the Fermi level nearer the conduction band, resulting in an increased silicon vacancy concentration which affects the rate through the middle reaction of A quantitative model based on this mechanism Fig. 3.12. has been developed by Ho and Plummer [81,82] and has given a good fit to their data.

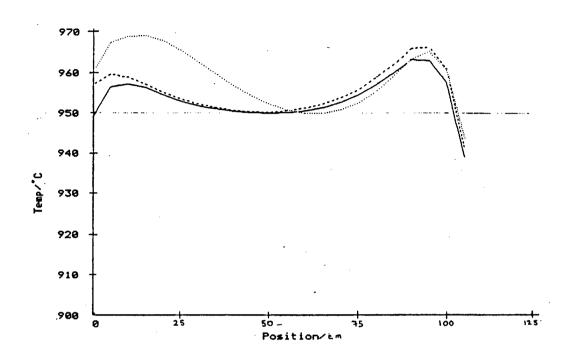

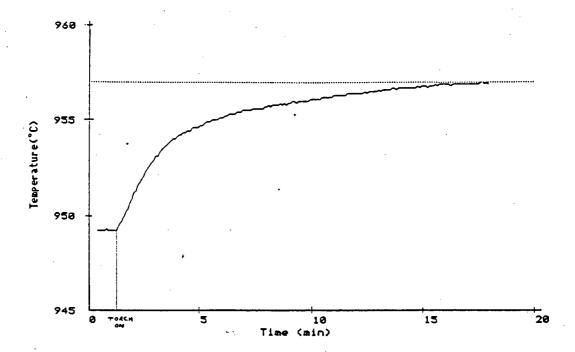

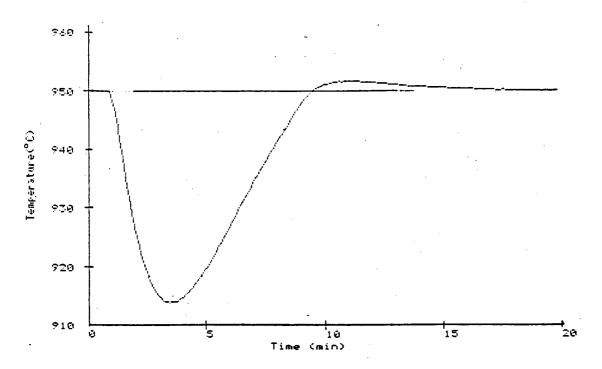

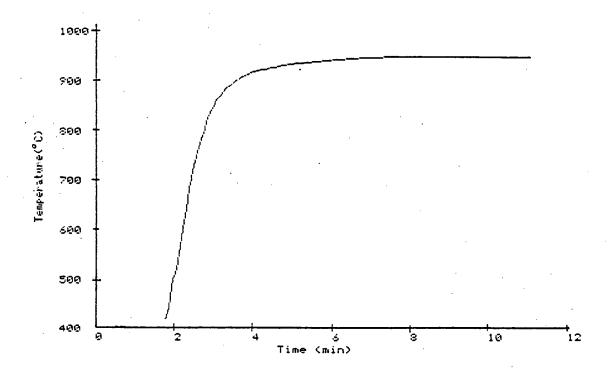

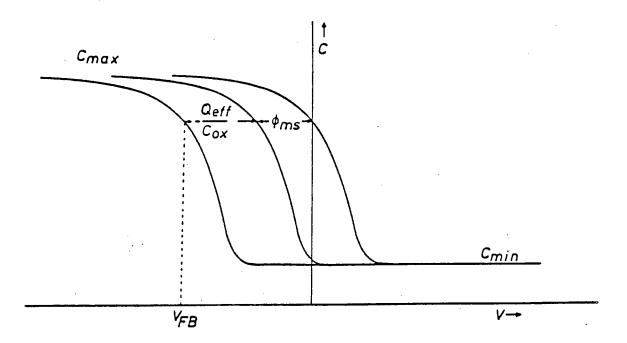

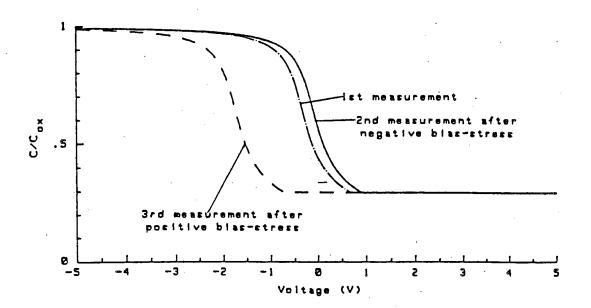

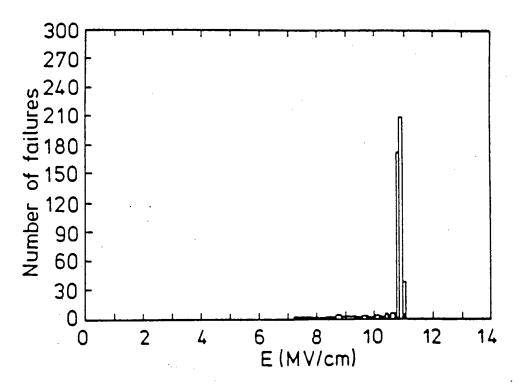

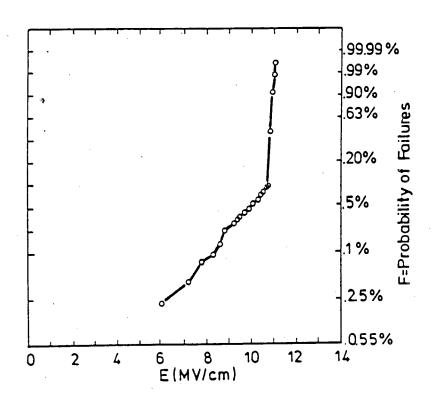

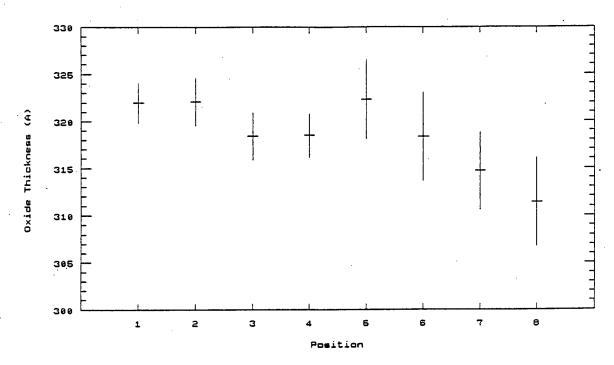

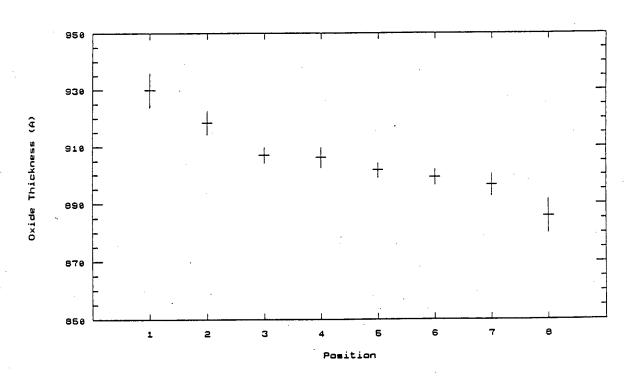

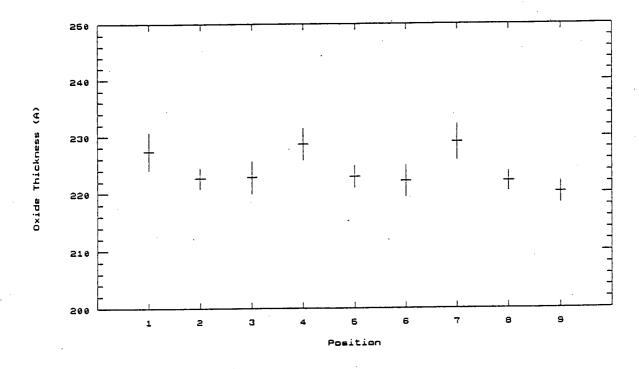

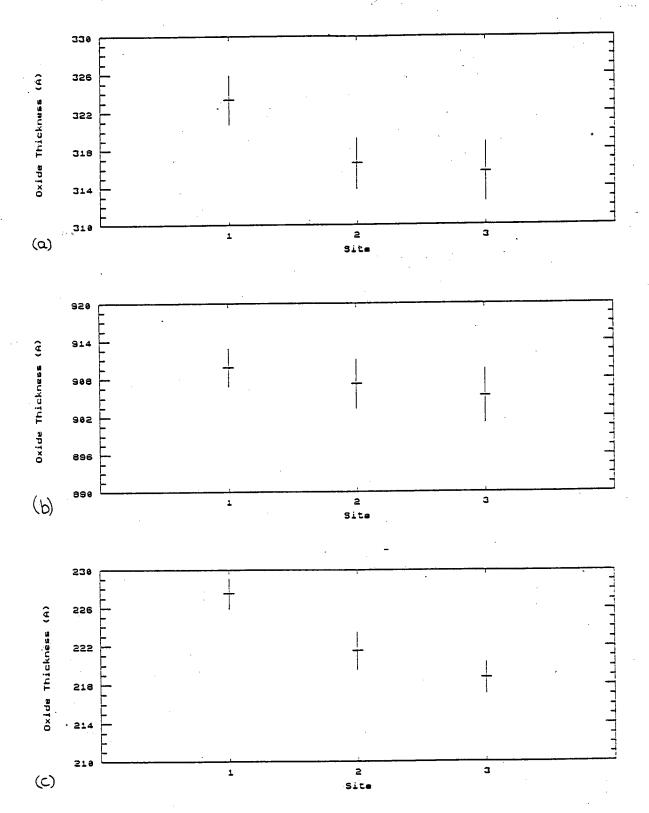

Although the model of Fig. 3.12 is not necessarily comprehensive in its treatment of interface mechanisms, has explained several other oxidation-related phenomena. In particular, the creation of silicon interstitials has been linked to the growth of oxidationinduced stacking faults (OISF) [83] and the mechanism of oxidation-enhanced dopant diffusion [84]. All three mechanisms in Fig. 3.12 have experimental evidence to support them, as discussed above. It is reasonable to assume that all take part concurrently in the oxidation process, although any one may be dominant under specific conditions.