# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## An Asynchronous Spike Event Coding Scheme for Programmable Analogue Arrays and its Computational Applications

Luiz Carlos Paiva Gouveia

A thesis submitted for the degree of Doctor of Philosophy. **The University of Edinburgh**.

September 2011

#### **Abstract**

This work is the result of the definition, design and evaluation of a novel method to interconnect the computational elements - commonly known as Configurable Analogue Blocks (CABs) - of a programmable analogue array. This method is proposed for total or partial replacement of the conventional methods due to serious limitations of the latter in terms of scalability.

With this method, named Asynchronous Spike Event Coding (ASEC) scheme, analogue signals from CABs outputs are encoded as time instants (spike events) dependent upon those signals activity and are transmitted asynchronously by employing the Address Event Representation (AER) protocol. Power dissipation is dependent upon input signal activity and no spike events are generated when the input signal is constant.

On-line, programmable computation is intrinsic to ASEC scheme and is performed without additional hardware. The ability of the communication scheme to perform computation enhances the computation power of the programmable analogue array. The design methodology and a CMOS implementation of the scheme are presented together with test results from prototype integrated circuits (ICs).

## Declaration of originality

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, that this work was developed in the School of Engineering at The University of Edinburgh and that this work has not been submitted for any other degree or professional qualification except as specified.

Luiz Carlos Paiva Gouveia

### Acknowledgements

During this thesis project, many people helped to create an enjoyable and collaborative environment within the Institute for Micro and Nano Systems (IMNS). Although all of them have been important for different reasons, I would like to thank particularly to the following friends.

Dr. Alister Hamilton, who was a great supervisor, offering me total freedom and conditions to the development of the thesis. I am also thankful to his patience. Dr. Thomas Jacob Koickal, who acted as an informal second supervisor. He helped me with bits of everything, from English revision to presentation skills, from project incomes prediction to equipment acquisition and much more. Dr. Martin Reekie, who offered me his time and his deep knowledge on analogue circuits. Dr. Keith Muir, who kindly offered me his PCB layout from his project, which I used as a starting point for my ons PCB designs. He instructed me on the joys of PCB design and FPGA programming tools. He also advised about test equipment. Dr. Katherine Cameron, who helped me on conducting me throughout the School procedures and locations and her coordination of the Paper Club, where lots of ideas were shared. Dr. Simeon Bamford, with whom I shared lots of experiences and had many productive discussions about the thesis, from the incomes to several technical details. He also redesigned the AER circuitry used on this thesis. Dr. Giacomo Indiveri, Dr. Shih-Chii Liu and Dr. Tobi Delbrück from ETH Neuroscience Center in Zurich. They made available the AER circuitry used by Dr. Simeon Bamford in this thesis. They were also very kind and helpful whenever I meet them in conferences and workshops. Dr. Kwabena Boahen of Stanford University for clarifications about the AER protocol. Everyone that has worked with me in room 2.2 of Alrick Building for a light, friendly and productive environment.

I would also like to thank to the Engineering and Physical Sciences Research Council (EPSRC) which funded this project under the grant to University of Edinburgh (EP/C015789/1) and the U.S. National Science Foundation and other sponsors for financial support to the 2007 Telluride Neuromorphic Engineering Workshop.

Although not have contributed directly to the thesis itself, my special thanks to my wife Andreia Nobre for her love, motivation, dedication and patience. Also to my son Fabio, who took away many hours of my sleep, but always paid back with a smile.

## Contents

|   |                                                                  | Declaration of originality                                      |  | iii  |  |  |  |  |

|---|------------------------------------------------------------------|-----------------------------------------------------------------|--|------|--|--|--|--|

|   |                                                                  | Acknowledgements                                                |  |      |  |  |  |  |

|   |                                                                  | Contents                                                        |  |      |  |  |  |  |

|   |                                                                  | List of figures                                                 |  | viii |  |  |  |  |

|   |                                                                  | List of tables                                                  |  |      |  |  |  |  |

|   |                                                                  | Acronyms and abbreviations                                      |  |      |  |  |  |  |

| 1 | Intr                                                             | oduction                                                        |  | 1    |  |  |  |  |

| 1 | 1.1                                                              | Motivation                                                      |  |      |  |  |  |  |

|   | 1.2                                                              | Statement of hypothesis                                         |  |      |  |  |  |  |

|   | 1.3                                                              | Thesis overview                                                 |  |      |  |  |  |  |

| _ |                                                                  |                                                                 |  |      |  |  |  |  |

| 2 |                                                                  | munication in programmable analogue arrays                      |  | 5    |  |  |  |  |

|   | 2.1                                                              | Introduction                                                    |  |      |  |  |  |  |

|   | 2.2                                                              | Programmable analogue architectures                             |  |      |  |  |  |  |

|   |                                                                  | 2.2.1 Neuromorphic systems as FPAAs                             |  |      |  |  |  |  |

|   | 2.3                                                              | Analogue information routing                                    |  |      |  |  |  |  |

|   |                                                                  | 2.3.1 Timing communication                                      |  |      |  |  |  |  |

|   | 2.4                                                              | Summary                                                         |  | 24   |  |  |  |  |

| 3 | Asynchronous spike event coding scheme: the communication method |                                                                 |  |      |  |  |  |  |

|   | 3.1                                                              | Introduction                                                    |  | 25   |  |  |  |  |

|   | 3.2                                                              | Asynchronous spike event coding scheme                          |  | 26   |  |  |  |  |

|   | 3.3                                                              | The channel component: Address event representation             |  | 27   |  |  |  |  |

|   | 3.4                                                              | The coding component: Ternary spike delta modulation            |  | 30   |  |  |  |  |

|   | 3.5                                                              | Alternative modulations                                         |  | 34   |  |  |  |  |

|   |                                                                  | 3.5.1 Binary spike delta modulation                             |  | 34   |  |  |  |  |

|   |                                                                  | 3.5.2 Asynchronous delta modulation                             |  | 36   |  |  |  |  |

|   |                                                                  | 3.5.3 Spike sigma-delta modulations                             |  | 38   |  |  |  |  |

|   | 3.6                                                              | Evaluation of the communication methods: Why TSD?               |  |      |  |  |  |  |

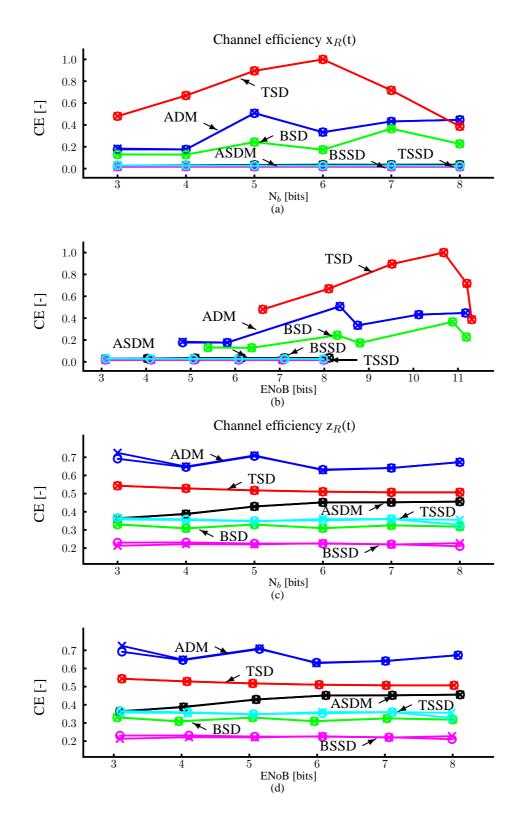

|   |                                                                  | 3.6.1 Channel efficiency                                        |  | 41   |  |  |  |  |

|   |                                                                  | 3.6.2 Comparison results and discussion                         |  | 44   |  |  |  |  |

|   | 3.7                                                              | Summary                                                         |  |      |  |  |  |  |

| 4 | Con                                                              | putation in communication with asynchronous event coding scheme |  | 51   |  |  |  |  |

| • | 4.1                                                              | Introduction                                                    |  |      |  |  |  |  |

|   | 4.2                                                              | Computational framework                                         |  |      |  |  |  |  |

|   | 4.3                                                              | Arithmetic operations                                           |  |      |  |  |  |  |

|   |                                                                  | 4.3.1 Gain operation                                            |  |      |  |  |  |  |

|   |                                                                  | 4.3.2 Negation operation                                        |  |      |  |  |  |  |

|   |                                                                  | 4.3.3 Modulus                                                   |  |      |  |  |  |  |

|   |                                                                  | 4.3.4 Summation and subtraction                                 |  |      |  |  |  |  |

|   |                                                                  | 4 3 5 Multiplication and division                               |  | 61   |  |  |  |  |

|   |      | 4.3.6 Average operation                                               | 62  |

|---|------|-----------------------------------------------------------------------|-----|

|   | 4.4  | Signal conversion                                                     | 62  |

|   | 4.5  | Other operations                                                      | 64  |

|   |      | 4.5.1 Shift keying modulations                                        | 64  |

|   |      | 4.5.2 Weighted summation                                              | 66  |

|   | 4.6  | Summary                                                               | 66  |

| 5 | Asyı | nchronous spike event coding scheme: VLSI design and characterisation | 69  |

|   | 5.1  | Introduction                                                          |     |

|   | 5.2  | ASEC implementation                                                   |     |

|   |      | 5.2.1 Design parameters of the ASEC                                   |     |

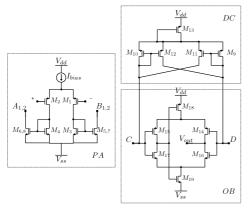

|   | 5.3  | Circuits design                                                       |     |

|   |      | 5.3.1 Comparator                                                      |     |

|   |      | 5.3.2 Spike and pulse generators                                      |     |

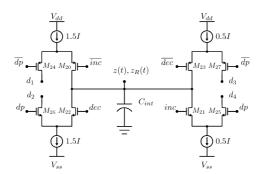

|   |      | 5.3.3 Integrator                                                      |     |

|   |      | 5.3.4 Filter                                                          |     |

|   |      | 5.3.5 AER communication                                               |     |

|   | 5.4  | IC results                                                            |     |

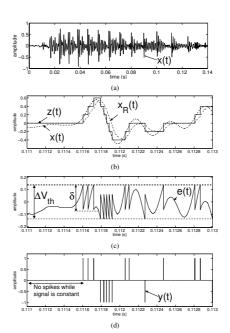

|   |      | 5.4.1 Demonstration: speech input                                     |     |

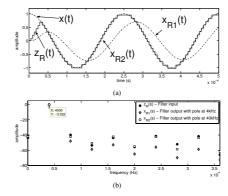

|   |      | 5.4.2 Resolution: single tone input                                   |     |

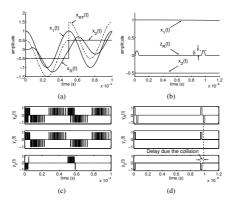

|   |      | 5.4.3 Computation: gain, negation, summation and bpsk                 |     |

|   |      | 5.4.4 Area and power consumption                                      |     |

|   | 5.5  | Summary                                                               | 89  |

| 6 |      | amary and conclusions                                                 | 93  |

|   | 6.1  | Review of the thesis                                                  |     |

|   | 6.2  | Further work                                                          |     |

|   | 6.3  | Final considerations and conclusion                                   | 96  |

| A |      | lysis of spike frequency and channel efficiency                       | 97  |

|   |      | Delta based modulations                                               |     |

|   | A.2  | Sigma-delta based modulations                                         | 100 |

| В | Spik | te modulations numerical models                                       | 105 |

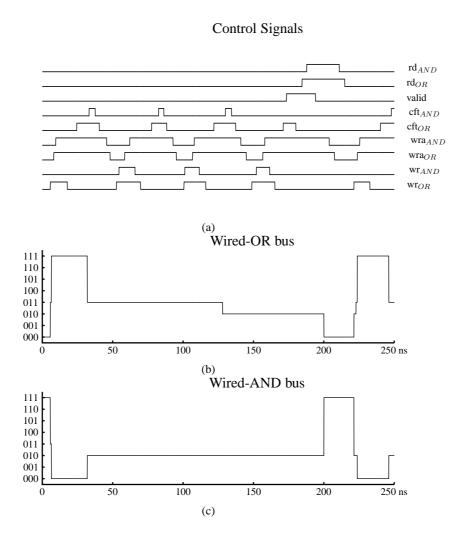

| C | A di | stributed arbitration for AER protocol                                | 117 |

|   | C.1  | Distributed arbitration description                                   |     |

|   | C.2  | Comparison with other AER arbitration techniques                      | 120 |

| D |      | itional summation methods using timing modulations                    | 125 |

|   |      | PFM, PDM and PPM                                                      |     |

|   |      | Examples of circuits for PPM                                          |     |

|   | D.3  | Summation expressions for the methods studied                         | 130 |

| E | Sche | ematics of the ASEC circuits                                          | 133 |

| F | Swit | ched-capacitor integrator design                                      | 141 |

|                | Contents |

|----------------|----------|

|                |          |

| G Publications | 145      |

| References     | 168      |

## List of Figures

| 2.1<br>2.2<br>2.3<br>2.4 | Academic FPAA architectures                                | 10<br>14<br>16<br>17 |

|--------------------------|------------------------------------------------------------|----------------------|

| 2.4                      |                                                            | 18                   |

| 2.6                      |                                                            | 20                   |

| 2.7                      |                                                            | 20<br>22             |

| 2.7                      | 1                                                          | 23                   |

| 2.0                      | FDM distortion                                             | 23                   |

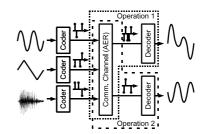

| 3.1                      | Proposed communication architecture                        | 26                   |

| 3.2                      | ASEC-CAB interface diagram                                 | 27                   |

| 3.3                      | Address Event Representation - AER                         | 28                   |

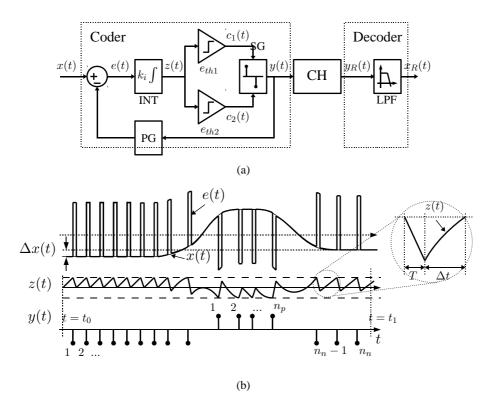

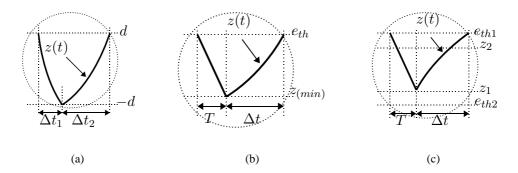

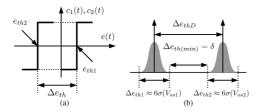

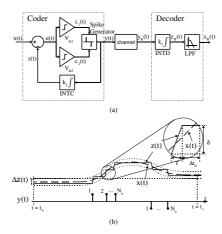

| 3.4                      | Ternary Spike Delta modulation - TSD                       | 32                   |

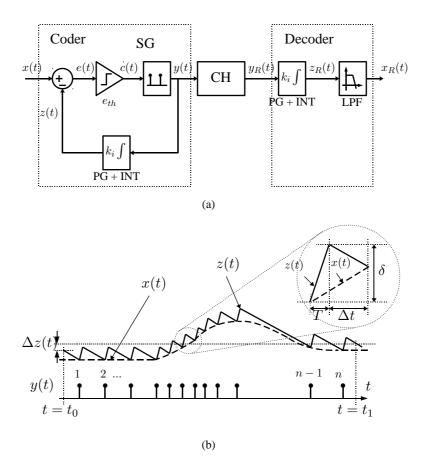

| 3.5                      | Binary Spike Delta modulation - BSD                        | 35                   |

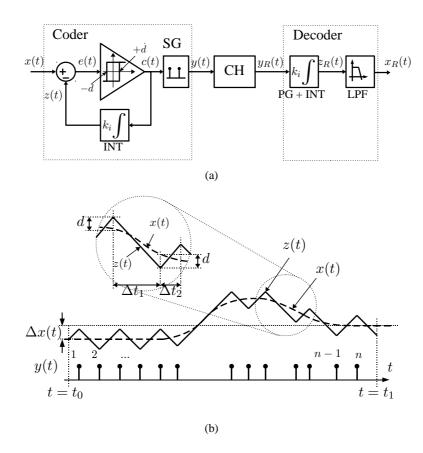

| 3.6                      | Asynchronous Delta Modulation - ADM                        | 37                   |

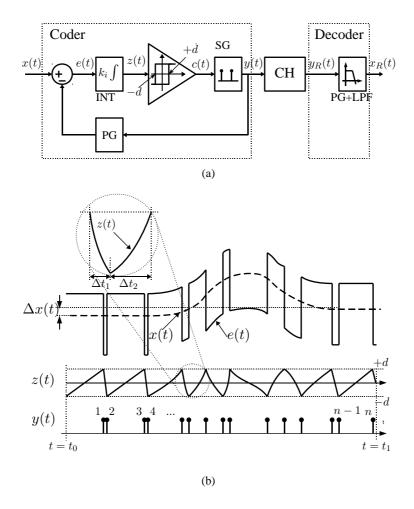

| 3.7                      | Asynchronous Sigma Delta modulation - ASDM                 | 38                   |

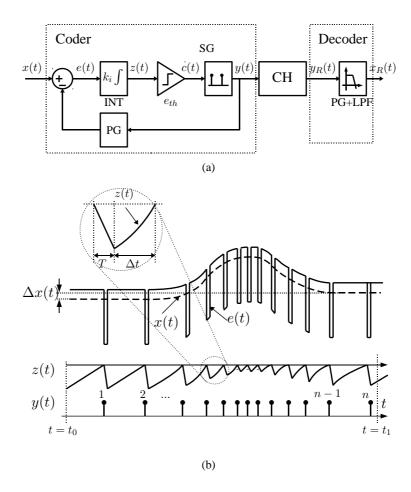

| 3.8                      | Binary Spike Sigma Delta modulation - BSSD                 | 39                   |

| 3.9                      | Ternary Spike Sigma Delta modulation - TSSD                | 40                   |

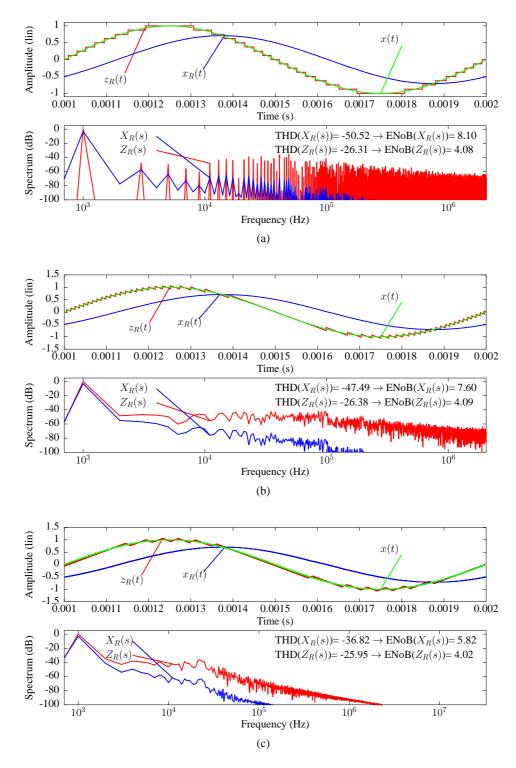

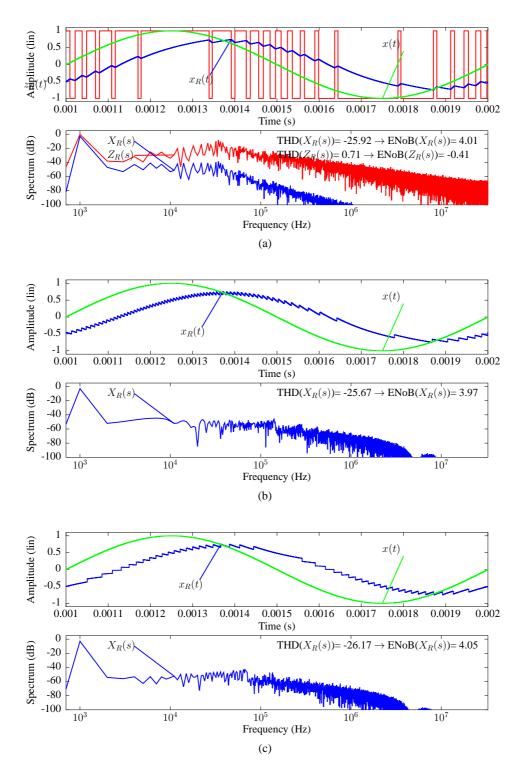

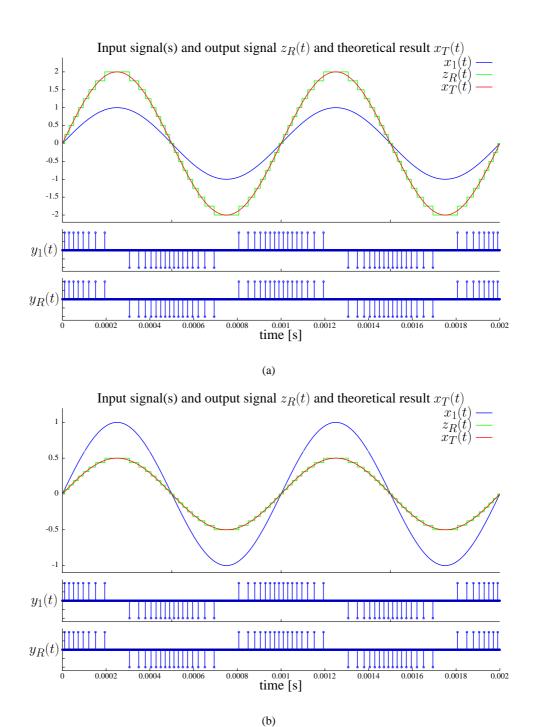

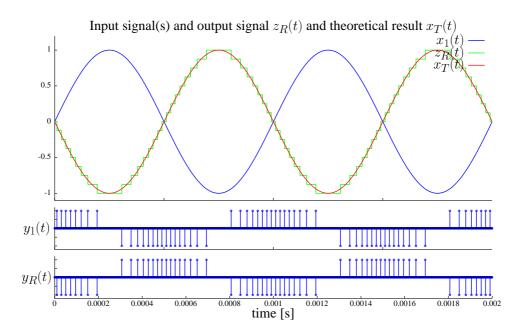

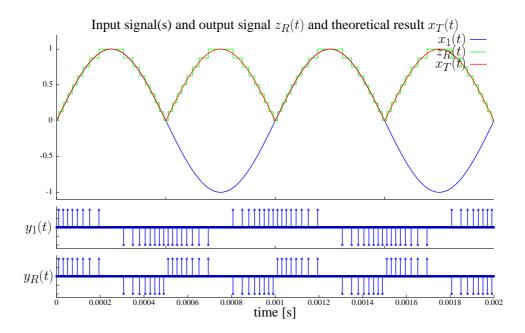

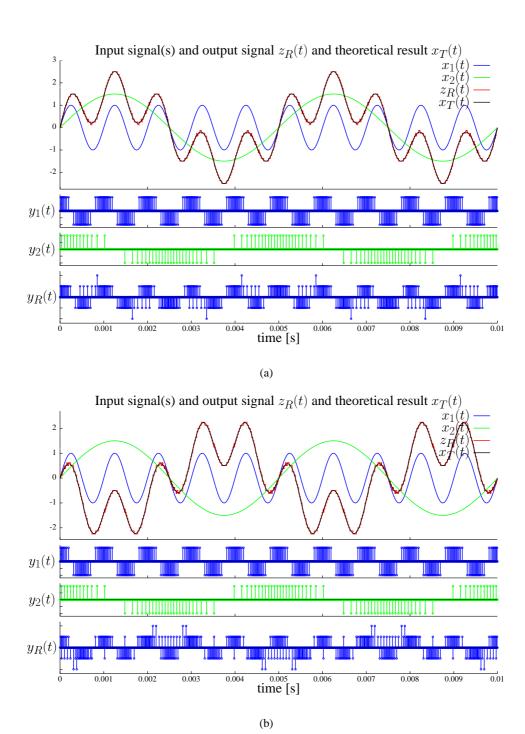

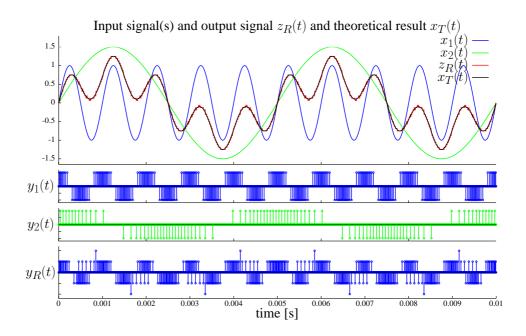

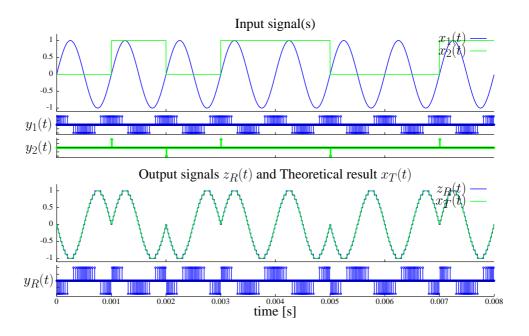

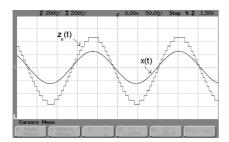

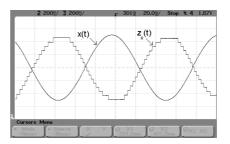

| 3.10                     | Numerical simulation of the delta modulations models       | 45                   |

| 3.11                     | Numerical simulation of the sigma delta modulations models | 46                   |

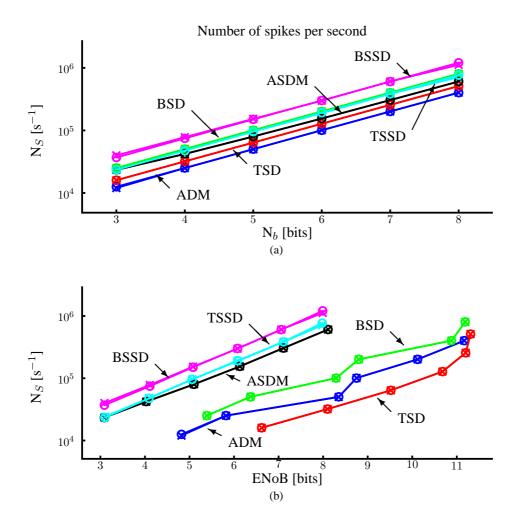

|                          | <u> </u>                                                   | 48                   |

|                          | • •                                                        | 49                   |

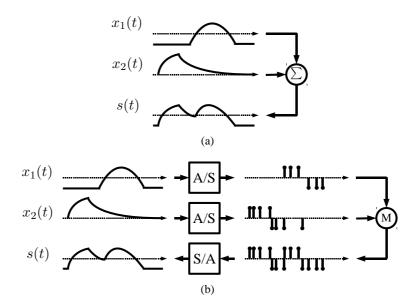

| 4.1                      | Computation in the communication scheme                    | 53                   |

| 4.1                      |                                                            | 55                   |

|                          | 1                                                          |                      |

| 4.3                      | $\mathcal{E}$ 1                                            | 57                   |

| 4.4                      | 1                                                          | 58<br>50             |

| 4.5                      |                                                            | 59<br>50             |

| 4.6                      | 1                                                          | 60<br>62             |

| 4.7                      | $\varepsilon$ 1                                            | 62                   |

| 4.8                      | $\mathcal{E}^{-1}$                                         | 63                   |

| 4.9                      | Binary phase shift keying                                  | 65                   |

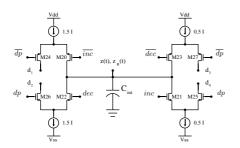

| 5.1                      | Block diagram of the ASEC implementation                   | 70                   |

| 5.2                      | •                                                          | 73                   |

| 5.3                      | T                                                          | 73                   |

| 5.4                      | *                                                          | 74                   |

| 5.5                      |                                                            | 75                   |

| 5.6                      |                                                            | 76                   |

| 5.7                      | -                                                          | 77                   |

| 5.8                      | •                                                          | 78                   |

| 5.9                      |                                                            | 79                   |

| 5.10        | Schematic of the integrator based on a SCI technique 80                 |

|-------------|-------------------------------------------------------------------------|

| 5.11        | SCI divergence                                                          |

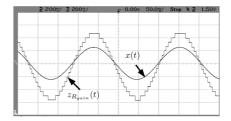

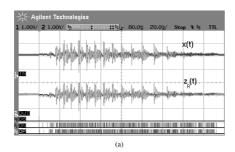

|             | Demonstration with an audio signal for the first implementation 84      |

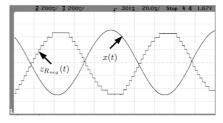

|             | Demonstration with an audio signal for the second implementation 85     |

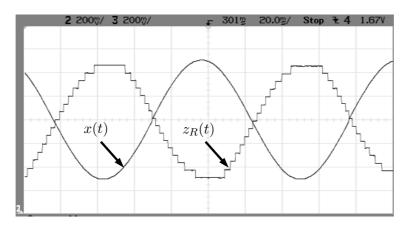

| 5.14        | Resolution of the coding                                                |

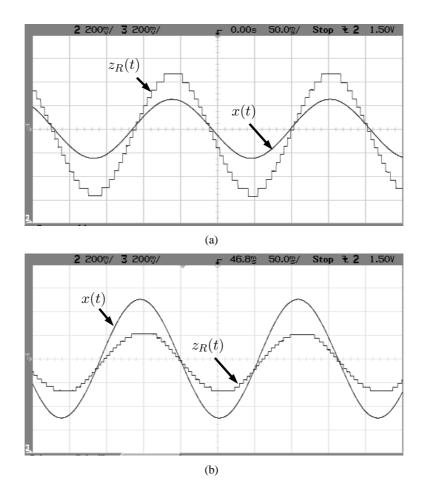

|             | IC results for the gain operation operation                             |

|             | IC results for negation operation                                       |

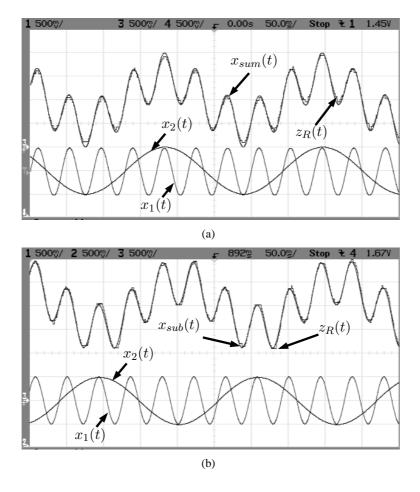

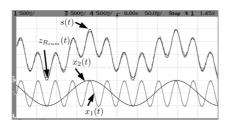

|             | Summation and subtraction operations results from chip                  |

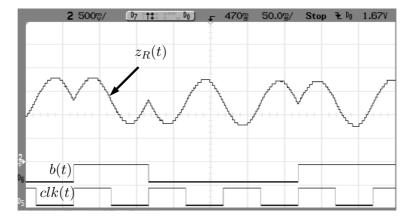

|             | Results of the binary phase shift keying operation from IC 89           |

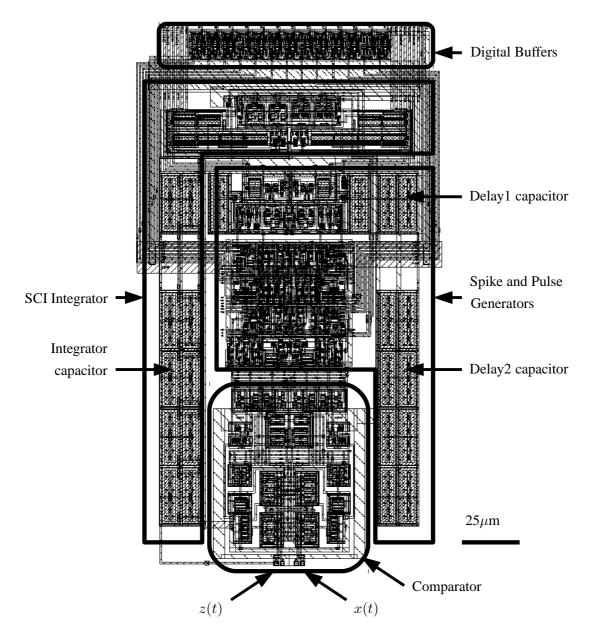

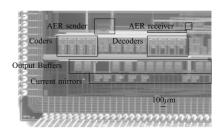

|             | ASEC coder layout                                                       |

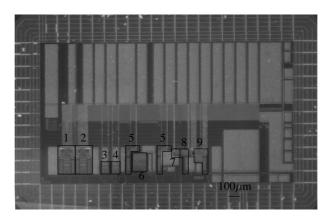

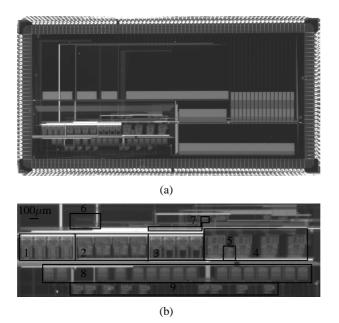

| 5.20        | First test chip photograph                                              |

| 5.21        | Second test chip photograph                                             |

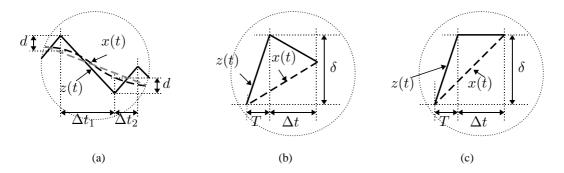

| <b>A</b> .1 | Waveform details of TSD, BSD and ADM                                    |

| A.2         | Waveform details of ASDM, BSSD and TSSD                                 |

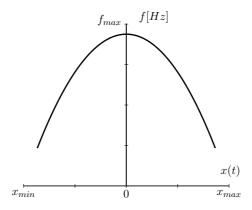

| A.3         | Spike frequency as a function of input signal for ASDM modulation 101   |

| 11.5        | spike frequency as a function of input signal for Assert modulation for |

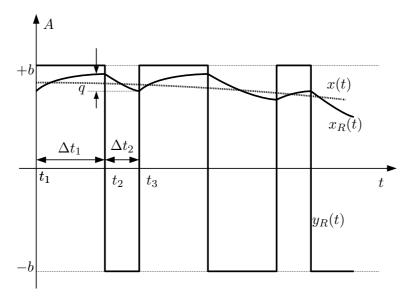

| B.1         | Asynchronous sigma-delta modulation output                              |

| C.1         | Distributed arbiter example waveform                                    |

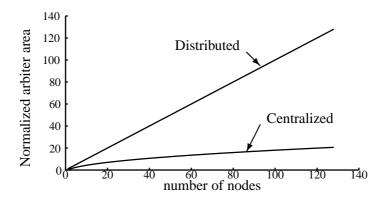

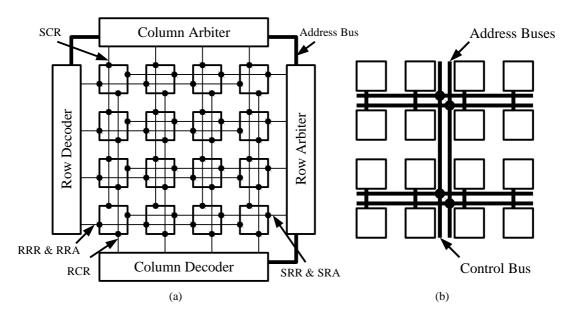

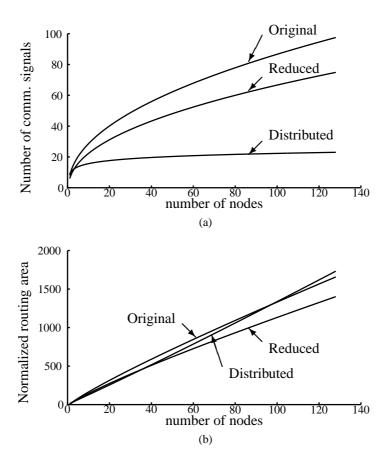

| C.2         | AER arbiter area                                                        |

| C.3         | Example of routing placements                                           |

| C.4         | AER number of signals and routing area                                  |

|             |                                                                         |

| D.1         | PPM summation circuit and waveform: version 1                           |

| D.2         | PPM summation circuit and waveform: version 2                           |

| D.3         | PPM 4 quadrant summation circuit and waveform: version 2                |

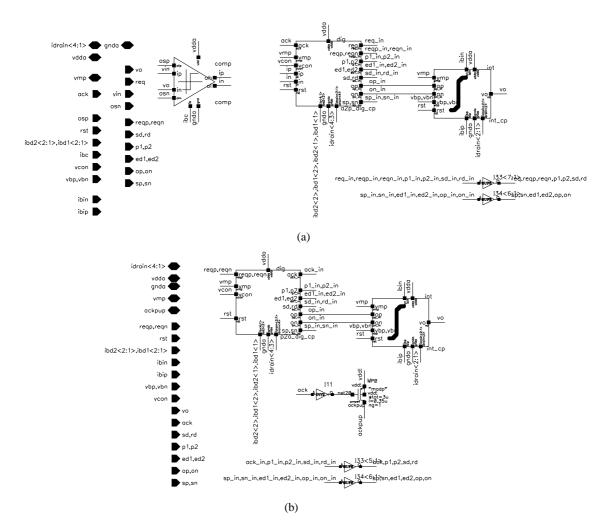

| E.1         | Schematics of the ASEC coder and decoder                                |

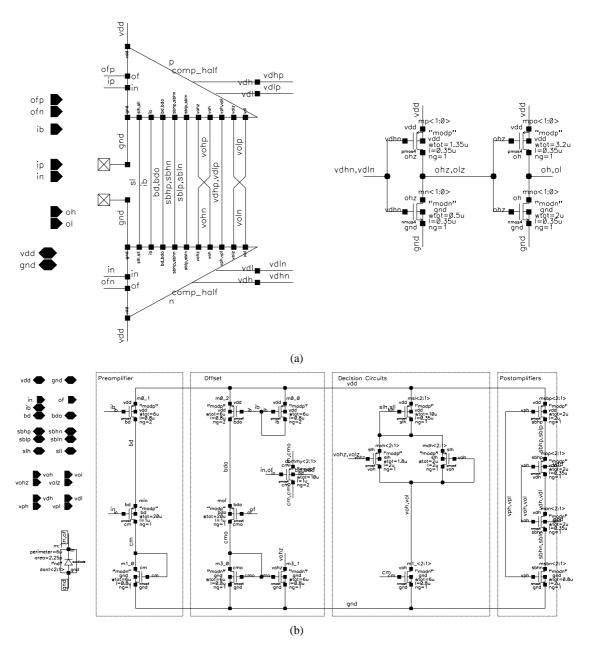

| E.2         | Schematic of the compound comparator                                    |

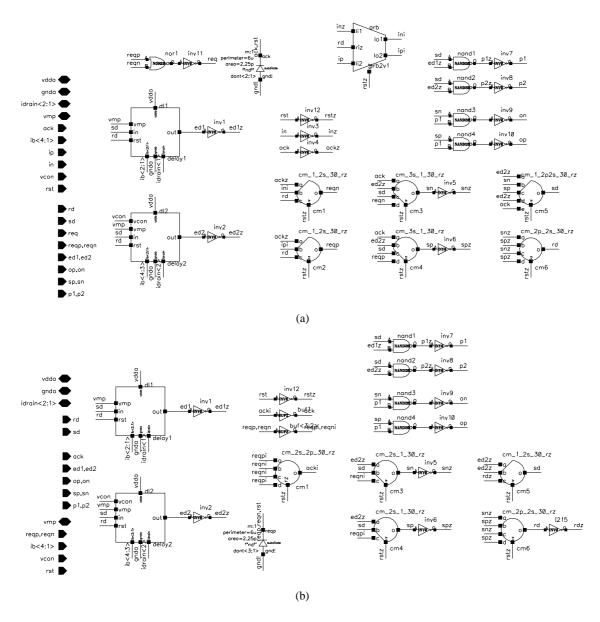

| E.3         | Schematics of the digital control circuits                              |

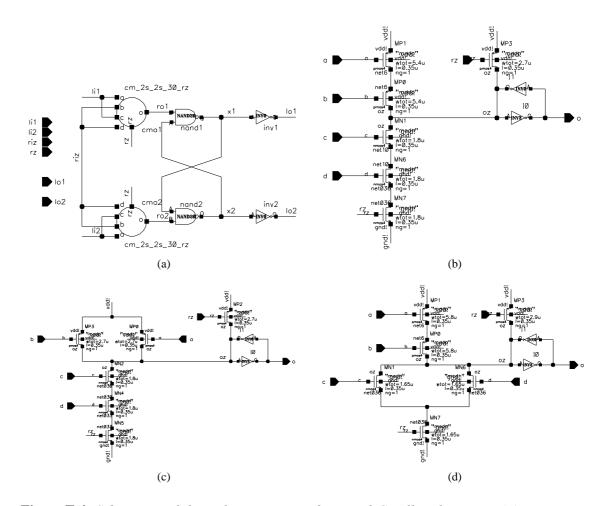

| E.4         | Schematics of the spike generator arbiter and C-miller elements         |

| E.5         | Schematics of the C-miller elements (cont.)                             |

| E.6         | Schematics of the digital control delays circuits                       |

| E.7         | Schematic of the SCI integrator                                         |

| г1          |                                                                         |

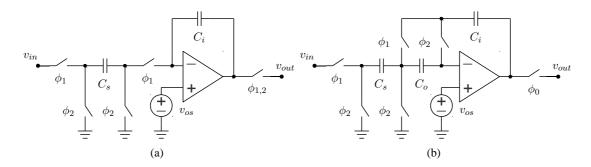

| F.1         | Switched-capacitor integrator topologies                                |

| F.2         | Switched-capacitor integrator                                           |

| F.3         | Switched-capacitor integrator divergence                                |

## List of Tables

| 2.1 | Architectures characterization                              |

|-----|-------------------------------------------------------------|

| 3.1 | Spike frequency and channel efficiency comparison           |

| 5.2 | Transistor sizes of the compound comparator                 |

| B.1 | Code global variables                                       |

| F.1 | Components sizes of the switched-capacitor based integrator |

## Acronyms and abbreviations

ADM Asynchronous Delta Modulation

AER Address Event Representation

ANN Artificial Neural Networks

ASDM Asynchronous Sigma Delta modulation

ASEC Asynchronous Spike Event Coding

ASIC Application Specific Integrated Circuit

BSD Binary Spike Delta modulation

BSSD Binary Spike Sigma-Delta modulation

CAB Configurable Analogue Block

CMOS Complimentary Metal-Oxide-Substrate

ENoB Effective Number of Bits

CE Channel Efficiency

FPAA Field Programmable Analogue Array

FPGA Field Programmable Gate Array

IC Integrated Circuit

I&F Integrate-and-fire neuron

LUT Look-up Table

MOS Metal-Oxide-Substrate

OP-AMP Operational Amplifier

OTA Operational Transconductance Amplifier

PCB Printed Circuit Board

TSD Ternary Spike Delta modulation

TSSD Ternary Spike Sigma-Delta modulation

VLSI Very Large Scale Integration

## Chapter 1 **Introduction**

#### 1.1 Motivation

Electronic engineering attempt to realize mathematical models using electrical devices configured and connected appropriately. In general such models can be implemented using digital, analogue or combined approaches. Each approach has their own paradigms, techniques, advantages and limitations.

Analogue systems use continuous variables to represent information whilst digital ones uses discrete - usually binary - numbers. The continuous characteristic of the information implies analogue systems are more vulnerable to a wide number of physical effects than digital ones. Therefore the digital approach tends to make complex system designs easier and faster than the analogue approach. This characteristic helps to explain the ever-increasing popularity of digital designs.

The robustness of digital designs allows for automation and flexibility and both of them are difficult to achieve with analogue designs. These characteristics allow for complex systems like digital Central Processing Units (CPUs), micro-controllers, Digital Signal Processors (DSPs) and Field-Programmable Gate Arrays (FPGAs). In particular, FPGAs are digital systems used specially for rapid prototyping. They contain a large number of basic digital circuits which can be configured and connected to implement specific functions. Doing this is much faster than designing a different system whenever you need to implement a different function.

With these crucial advantages of digital circuits, analogue designs survive due to specific applications. In particular, analogue circuits are used to interface with real world because most of its information — measurements and controls — are continuous variables as well. Moreover analogue designs usually present a more fitted solution than digital circuits because they are usually smaller, spend less power and presents a higher processing speed for the same applications.

Therefore, if the main reason that drives the popularity of the digital circuits is design automation and operation flexibility, it is a reasonable ambition to incorporate these characteristics to

an analogue design. This would shorten analogue design cycles, provides reconfiguration levels similar to the digital case and, furthermore, will benefit from the analogue properties listed in the previous paragraph.

Some efforts have been made on the automation field, as in Analogue-to-Digital Converters (ADC) designs [1]. Regarding the flexibility, studies have been made on analogue CPUs [2, 3] and on programmable analogue arrays.

Several researchers in institutions and companies have been trying to achieve a level of programmability in analogue systems similar to digital arrays. Some had coined terms as "Field-Programmable Analogue Arrays" (FPAA) [4] and "Field-Programmable Mixed-signal Arrays" (FPMA) [5] to define the class of circuits that are the analogue and mixed-signal counterparts of the digital FPGA, respectively.

In general these architectures are built from a number of basic programmable processing blocks, known as Configurable Analogue Blocks (CABs). The configurable blocks are then interconnected using specific configurable signal routing. This signal routing is usually implemented in a similar fashion as it is in a digital array, i.e., using switched-matrices: a collection of wires and switches connected in a special pattern, defined by design requirements. However this routing method imposes serious limitations to the number of CABs allowed in the array.

The limitation on the scalability of programmable analogue circuits was the main motivation for this thesis whose objectives are described in next section. To achieve this objectives, other research fields with similar properties were investigated, mainly the systems developed to implement neuromorphic circuits which are reviewed in the next chapter.

#### 1.2 Statement of hypothesis

The main objectives of this thesis are:

- 1. to propose an alternative method for analogue communication between functional blocks in a low-to-medium resolution, large-scale programmable analogue arrays context and

- 2. to demonstrate that this method is able to perform a set of computations on analogue signals independently of or when combined with the configurable analogue blocks.

#### 1.3 Thesis overview

The chapters of this thesis are as follows:

The next chapter presents a brief history of FPAAs and the current state of those systems, focusing on the communication methods used on them. The limitations of the current communication strategies are highlighted. Paradigms of neuromorphic systems leading to an alternative communication methods are therefore reviewed.

A novel method to interconnect the CABs of a programmable analogue array is then introduced in the third chapter. The heart of this new architecture lies on the appropriate choice of the coding scheme. A set of asynchronous pulse-based differential methods are also considered. A figure of merit is used to choose the most suitable option for the specifications.

The fourth chapter introduces computational operations that can be performed by the proposed communication method and are demonstrated with chip results.

The fifth chapter presents the design flow and parameters of the chosen coding scheme. It also describes CMOS circuits designed for the implementation of the method with chip results being shown.

Conclusions and possible future work are them discussed in the sixth and last chapter.

# Chapter 2 Communication in programmable analogue arrays

#### 2.1 Introduction

The first step taken in this work to achieve the goals stated in the introduction was a comprehensive bibliographic review of work done in the programmable analogue arrays field up to date. This review is synthesized in this chapter.

The general concept and reasons for using programmable analogue arrays are presented. Both commercial and academic programmable analogue arrays developed so far are revisited, categorised and analysed. A list of implementations is given with their main characteristics and differences.

The issue of the transmission of information both between the elements inside the array and with the external world is studied. Despite being the most conventional method to perform this communication, voltage or current signal representation using switch matrices for signal routing present some limitations. An alternative method based on timing rather than voltage or current is presented.

Using this alternative method, a novel programmable analogue array communication architecture is described.

#### 2.2 Programmable analogue architectures

Analogue circuits are much less robust than digital ones, because of their greater sensitivity to noise, cross-coupling, process and temperature drifts among others. This characteristic makes more difficult to change parameters and functionality of analogue circuits without degrading the system performance. Therefore most of analogue circuits are the result of full-custom, application-specific designs — presenting no reconfiguration capabilities — to provide high-performance operations.

The greater flexibility offered by digital systems has made them very popular. Digital computers have replaced their analogue counterparts a long time ago and most of the signal processing is done in digital domain.

However analogue circuits have intrinsic advantageous characteristics comparing to digital circuits, in general being faster, smaller and less energy demanding [6, 7]. Naturally, these advantages lead engineers and researchers to a quest to develop analogue architectures that also provide the high degree of flexibility experienced by FPGAs, DSPs or digital microprocessors [2].

Similarly to FPGAs, there are a wide range of potential applications for programmable analogue systems, including low-power computing [8], remote sensing [9], rapid prototyping [10].

Although it was written in 1998, a good review of patents and academic and commercial circuits point is presented in [5]. In this work, the authors first described the general idea of the Field Programmable Analogue Array (FPAA), proposed some classifications and gave examples of implementations. Usually, the characteristics of programmable analogue architectures can be defined using different classifications. Some of these classifications are:

**Programming capability** - A system can be defined according to how many times it can be programmed. Different systems vary from being only programmable once, like fused or anti-fused architectures [11] and metal-mask programmable analogue arrays, to allowing several — possible infinite — reconfigurations, like switched-capacitor circuits [12] and neural networks [13].

**Programming method** - This classification defines how to change the system behaviour. These changing can be obtained by either direct programming, where the designer or designer tool has the detailed knowledge of the signal flow [4], or learning and adapting techniques, where the system is seen as a "black box". Usually, the latter is achieved using genetic algorithms [14, 15] or neural networks [16, 17].

**Structure flexibility** - A system can also be characterized according to its versatility. Some architectures allow only their parameters to be programmable, like programmable automatic gain control (AGC) amplifiers and adaptive filters [18] whilst other systems allow the signal path be changed [19], by changing the interconnection of different circuits.

Granularity - The basic idea behind FPAAs is the use of basic units — usually known as

Configurable Analogue Blocks (CABs) — to implement a range of functions. In general, the complexity of these basic blocks is a trade-off between performance and flexibility. The block complexity can range from fine granularity, where the basic blocks are basic components, like transistors, resistors and capacitors [9], to coarse granularity, with more complex circuits like capacitively coupled current conveyors (C4) and vector-matrix multipliers [20].

**Signal representation** - Signals need some sort of physical representation to be processed by electronic circuits. Analogue circuits are defined as operating in one or more domains, usually voltage, current or charge domain. Voltage domain is the classical choice for analogue engineers, but current and charge techniques have their common applications, like power control and CCD image sensors, respectively. Recently, timing has been used as another possible representation. This representation and its benefits and drawbacks will be presented in detail in the next section.

Other FPAA characteristics can be used to define other classifications. For instance, signal timing characteristics employed, by using discrete or continuous time circuitry [21, 22]; design techniques implemented, for instance sub-threshold transistor operation [4] or fully-differential versus single-ended circuit structures; and signal routing approaches, e.g. global, hierarchical or local routing [13].

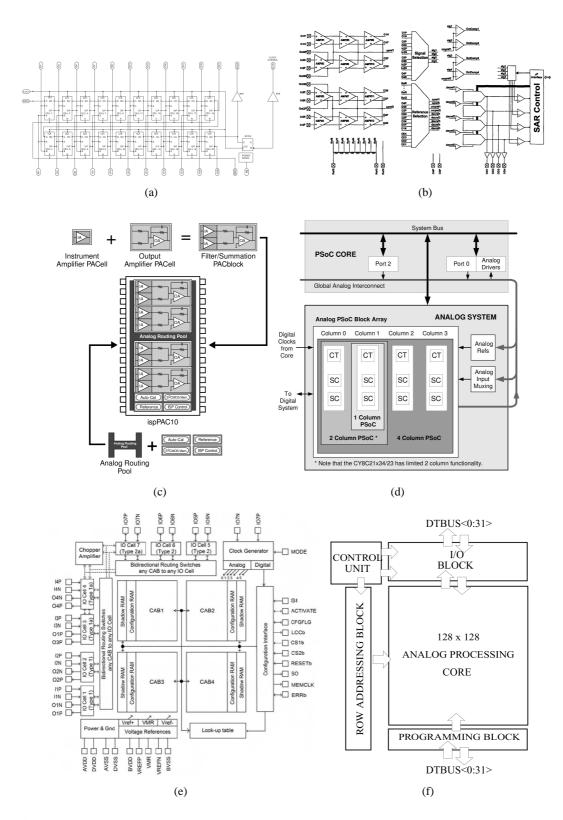

Since the 1990s lot of work has been done to develop analogue architectures with a functional philosophy similar to the digital FPGAs. This work resulted in various techniques and some commercial products. It is worth describing in brief some commercial products that appeared in the last two decades. Some of them were discontinued, like the first three examples, but some still are available:

• Totally Reconfigurable Analogue Circuit (TRAC®) IC family from Zetex Semiconductors Inc. - Fast Analogue Solutions branch of Zetex group introduced this technology about twenty years ago. This architecture operates in continuous mode and is essentially a collection of operational amplifiers configured as one of a set of predefined functions to process analogue signals [23]. For instance, TRAC020LH [24] is a chip with twenty CABs where each one can be configured to perform summation (of two signals), negation, logarithm compression, anti-log expansion, rectification, amplification, differentiation and integration (the last three operations performed using external components, like

resistors and capacitors). Further operations are possible combining them, like RMS conversion, filtering and others. Every CAB input and output are available outside and internal routing is done connecting theses CABs terminals.

- Field Programmable System on a Chip (FIPSOC) from Sidsa: This system is a mixed mode programmable circuit originally aimed to general front end and data acquisition [25]. The chip contains twelve differential amplifiers combined in four input channels, four comparators, one analogue multiplexer, ADC/DAC blocks and a digital micro-controller and memory [26]. The system is configured by the micro-controller or the internal logic using the ADC and DAC blocks. Signal routing is performed by the analogue multiplexer.

- In-system programmable analogue circuit (ispPAC®) family from Lattice Semiconductor Corp. TM- These circuits are hierarchically built from basic cells (PACellTM) grouped in functional modules (PACblockTM) and using an Analogue Rooting Pool (ARP) to connect PACell and PACblocks inputs and outputs, DACs and the device pins [27]. Each product in the family was designed to one specific function and each one has its own PACells [28]. PACells of ispPAC® 10 targeted to signal conditioning functions, like amplification and filtering consist of four PCAblocks containing instrumentation and summing amplifiers and arrays of capacitors. Elements like comparators and polarity switches are added to the ispPAC10's PACells to include non-linear processing in ispPAC® 20 architecture. IspPAC® 30's PACells include multiplying DACs, which make it a FPMA.

- Mixed-Signal Programmable System-on-Chip (PsoC®) from Cypress Semiconductor<sup>TM</sup>-It is a family of architectures comprising both digital and analogue programmable blocks, with supporting circuits, as SRAMs, clock generators and micro-controllers (M8, 8051 or ARM). Each block of PSoC®1 sub-family consists of one operational amplifier. Additional circuitry determines whether they will operate either in continuous-time or discrete-time fashion. Rather than providing universal connectivity and switch programming, each block presents multiplexers sourcing the amplifier inputs, resistor strings, capacitor terminals from its neighbour blocks outputs [29]. Block designs were optimized to support a few key functions such as a delta sigma modulator, a gain amplifier, digital-to-analogue converter (DAC), or differencing amplifier [30].

- Dynamically programmed Analogue Signal Processors (dpASP) and Field Programmable

Analogue Arrays (FPAA) from Anadigm® - The former Motorola's reconfigurable analogue group [31] designed new system consisting of a matrix of fully Configurable Analogue Blocks (CABs), surrounded by programmable interconnect resources and analogue inputs and output cells with active elements and supporting circuits. The first generation of these systems presented up to twenty CABs [32], but current products work with just four CABs [33] in order to present greater signal-to-noise ratio and bandwidth. Anadigm's products are based on switched-capacitor circuit techniques. Therefore, the core of their CABs is one operational amplifier and a programmable bank of capacitors and they are surrounded by a fabric of programmable interconnect resources, such as bandgap circuits, clock generators and lookup tables. These CABs are routed inside and to external pins using local and global switch-matrices.

• Cellular Visual Microprocessor (CVM) from AnaLogic Computers Ltd. (Eutecus Inc. in USA) - This system is a visual sensor and processor based on Cellular Neural Networks (CNN) technique which is explained further in this section. For instance, ACE16k¹ is an 128x128 Focal-Plane Analogue Programmable Array Processor to work with high-speed and moderate accuracy (around 8bits) requirements [34]. Each ACE16k's CAB is built with several different circuits like analogue multipliers, non-linear dynamic blocks, analogue memory, optical detection circuits and others. Each CAB is analogue connected with other eight adjacent CABs and digitally connected with column ADC and DAC.

The previous list of commercial FPAAs are not exclusive, as there are other systems that incorporate some analogue array processing. Figure 2.1 shows diagrams of cited architectures whilst table 2.1 shows a comparison between the commercial products using the classifications presented before.

<sup>&</sup>lt;sup>1</sup>ACE16k is the analogue core of the CVM system and was designed by Instituto de Microelectrónica de Sevilla (CNM-CSIC), Spain.

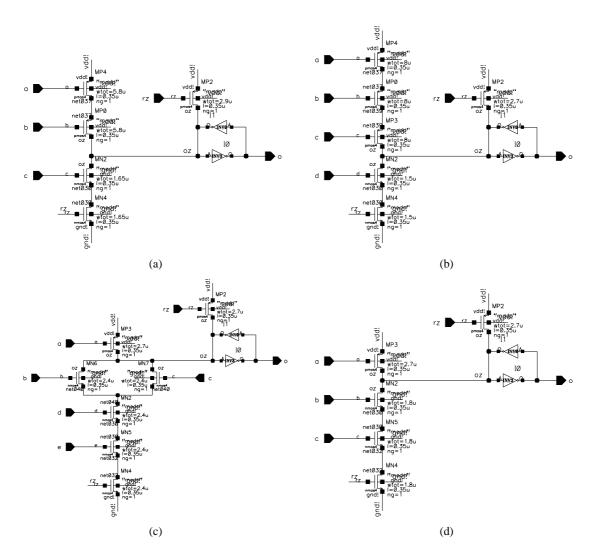

Figure 2.1: Architecture diagrams of the commercial FPAAs cited in this work. (a) TRAC020LH [24] from Zetex, (b) FipSoc [26] from Sidsa, (c) ispPAC10 [27] from Lattice, (d) PSoC CY8C27x43 [29] from Cypress, (e) AN231E04 [33] from Anadigm and (f) ACE16k [34] from CNM-CSIC.

| Architecture     | Type       | Method                | Flexibility                                   | Granularity                                                  | Routing                                                                       | Applications                                                                                                                                                                   |  |

|------------------|------------|-----------------------|-----------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Zetex's TRAC     | ANA        | Direct                | PAR (using external components), FUN and ROUT | Medium<br>(op-amp)                                           | External                                                                      | General signal processing. Able to implement functions like filtering, amplification, envelope and peak detection.                                                             |  |

| Sidsa's FIPSOC   | MS         | Direct                | PAR and ROUT                                  | Coarse<br>(op-amp,<br>DAC and<br>ADC)                        | Internal<br>multiplexer                                                       | General purpose front-end for signal conditioning and data acquisition.                                                                                                        |  |

| Lattice's ispPAC | ANA/<br>MS | Direct                | PAR, FUN and ROUT                             | Medium<br>(op-amp)                                           | Crossbar/<br>switch matrices                                                  | General signal processing with different architectures for specific applications, e.g. signal conditioning, control loop and monitoring and analogue front-ends.               |  |

| Cypress's PsoC   | MS         | Direct                | PAR, FUN and ROUT                             | Medium<br>(op-amp,<br>comparators)                           | Local<br>multiplexers<br>(PSoC1),<br>multiplexers<br>and crossbars<br>(PSoC3) | General signal processing with different architectures for specific applications, e.g. touch screen sensors, LED Back-light, Motor Control, Power Management and Gyro Sensing. |  |

| Anadigm's dpASP  | ANA/<br>MS | Direct                | PAR, FUN and ROUT                             | Coarse<br>(op-amp,<br>comparator,<br>SAR)                    | Switch matrices                                                               | General signal processing like signal conditioning, filtering and process control.                                                                                             |  |

| AnaLogic's CVM   | ANA        | Direct/<br>Adaptation | PAR and FUN                                   | Coarse<br>(multipliers,<br>memories,<br>photo-<br>detectors) | Crossbar/ direct connection                                                   | Complex image processing implemented locally like terrain feature classification, multi-target tracking and optical flow calculation.                                          |  |

**Table 2.1:** Characterization of commercial programmable analogue architectures. These systems are classified according to its signal processing type - either Analogue (ANA) or Mixed-Signal (MS); programming method; flexibility for configure CABs parameters (PAR), functions (FUN) and routing (ROUT); the granularity level; signals routing techniques and target applications. All architectures present infinite programmable capability and signals are represented in voltage-domain.

In academia, research groups in these areas were identified with projects related to FPAA field:

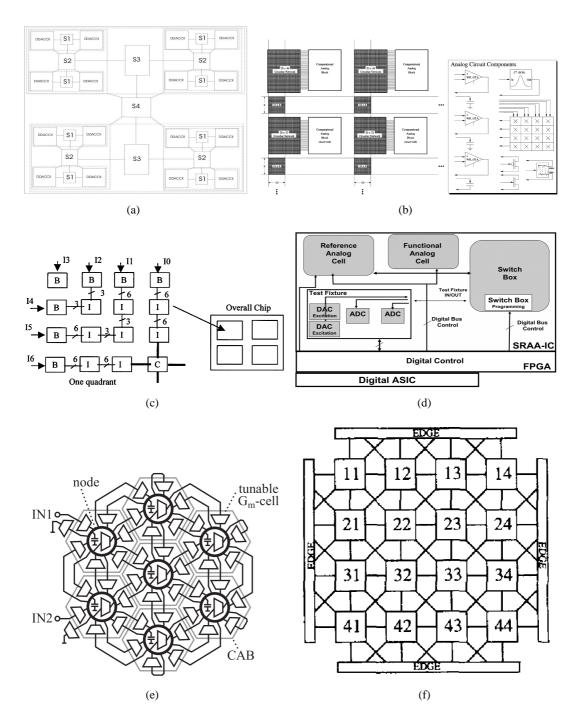

- Electronic Systems Design Group at University of Southampton, where continuous time FPAA architectures were developed. This group was active until 2008. In [35], the group presented the continuous-time Hierarchical Field Programmable Analogue Array (HFPAA). This system presents a Differential Difference Amplifier (DDA) as the CAB. This is an example of mixed signal representation due its dual voltage/current output mode. The architecture uses hierarchical interconnection switches to achieve maximum routing capability between CABs and minimum number of routing resources.

- Cooperative Analogue and Digital Signal Processing (CADSP) at Georgia Technology Institute, where Dr. Paul Hasler's group continues the development of floating gate technique in FPAA [36, 37, 38] architectures and in the neuromorphic systems. By using floating gates as a switch for signal routing or even to reconfigure the function parameters, the group aims at very high-density field-programmable analogue arrays. Several CABs architectures can be implemented using this technique. For instance, in [20], two CABs were implemented, containing a mixture of fine-grained (MOSFETs and capacitors), medium-grained (OTAs), and coarse-grained (capacitively coupled current conveyors) computational blocks. Signals are routed using crossbars and switch-matrices using floating gate devices.

- NASA's JPL Evolvable Hardware Laboratory, where Dr. Adrian Stoica's group works on adaptive techniques for the use in analogue processing [9]. Their work objective is to develop a class of self-configurable and evolvable hardware, which adapts to its working environment to obtain optimal signal processing and provides fault tolerant functionality. In special the group has been working with Field Programmable Transistor Array (FPTA), where the CABs are fine-grained components like MOSFETs. In the Evolutionary Oriented Reconfigurable Architecture [39], CABs are made of 8 transistors, being 4 PMOS and 4 NMOS, and 24 switches. CABs are divided in clusters, where each cluster presents CABs with different transistor sizes. The routing are performed by switches and multiplexers. FPTA has also been the subject of other groups in University of Heldelberg [40], whose architecture is based on all-PMOS and all-NMOS CABs configurable in up to 75 different sizes in a checker-board pattern and routed using also switch-matrices and multiplexers. Recently, JPL group has designed another architecture Self-Reconfigurable Analogue Array (SRAA) [41] which presents a medium coarse granularity (OTA).

- Dr.-Ing. Joachim Becker from Department for Microelectronics at the University of Ulm. His Ph.D. studies at Institute of Microsystem Technology (IMTEK) with supervision of Prof. Yiannos Manoli resulted in an architecture based on digitally configurable transconductors. These continuous-time CABs presents a number (normally seven), binary weighted sizes  $G_m$ -cells that can be turned on or off. These cells are configured in a parallel fashion to obtain different transconductance. The CABs are also used to routing the signals inside the system and, therefore, avoiding the use of switches in the signal path [42]. A more recent implementation of this architecture use floating-gates to add current programmability and a 3-bit capacitor array [43].

- Prof. Leon O. Chua on Control, Robotics & Biosystems group at University of California Berkeley works on Cellular Neural (or Non-linear) Networks (CNN). The Universal Machine version of this architecture (CNN-UM) is based on the concept of specific connectivity model and analogue circuit dynamic with continuous valued state variables [44]. Signals are routed through direct, local interactions within a finite radius, however further cells can be "virtually" connected due to dynamic propagation. The research of CNN techniques and applications involved other groups and researchers like Dr. Támas Roska at Neural Computing Lab at Hungarian Academy of Sciences. This architecture is chiefly used to model physical phenomena, neuromorphic control and different applications like visual processing [45].

The diagrams for these architectures are shown in figure 2.2. All approaches mentioned so far face the problem of sensibility of analogue signal to interferences in different ways, either by careful layout routing [27], using specific circuit techniques [20] or trying to limit the scope of routing [13, 42]. This research differs from these approaches as we aim to use timing representation for convey analogue variables instead of traditional voltages and currents. The inspiration for this idea came from in a specific class of systems described next.

#### 2.2.1 Neuromorphic systems as FPAAs

While general purpose FPAAs architectures have been continuously undermined by successive failures and struggle on producing viable and popular market solutions, at least one application field has provided a better prospectus: artificial neural networks with neuromorphic systems in particular.

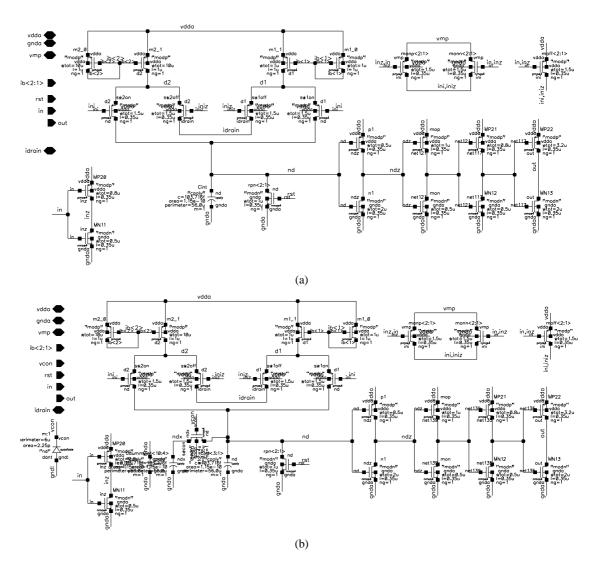

**Figure 2.2:** Architecture diagrams of some academic FPAAs. (a) Hierarchical Field Programmable Analogue Array [46], (b) Large scale FPAA as in [20], (c) Field Programmable Transistor Array (FPTA) presented in [9], (d) Self-Reconfigurable Analog Array (SRAA) [41], (e) the  $G_m$ -C based Field Programmable Analogue Array with floating gate transistors [43] and (f) analogue programmable Cellular Neural Network (CNN) chip [45].

Artificial Neural Networks (ANNs) are computational architectures where each element perform a similar computational role of biological neurons and synapses. The computation is highly associated with the interconnection between the elements in the network rather than with the elements functionality. Usually its configuration is adaptive and it is defined though the use of learning algorithms.

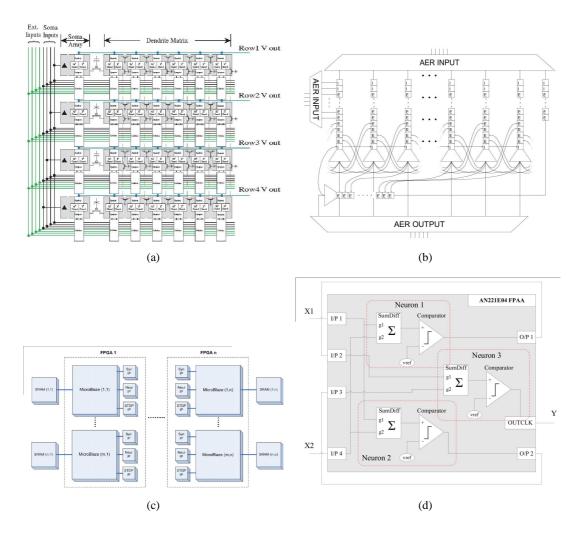

Although ANN can be implemented in software, its hardware implementations (HNN) lead to greater computational performance [47]. These hardware architectures can be implemented either using specific designed IC (ASIC) or a more generic platform. Examples of ASIC ICs include digital-based designs [48, 49], analogue [50, 51], mixed-mode [52] or even optical [53] designs. More recently, artificial neural networks designed on programmable platforms have appeared, both in digital [54], analogue [55, 16] and mixed-mode domains [17].

ANN computations are biologically inspired but they intend to replicate the computational functions of biological neurons rather than reproduce in detail their working principles. In other words, ANN aims to mimic the biological neurons computational principles but not their structures. For this goal the concept of neuromorphic systems was created. Neuromorphic systems are VLSI systems designed to mimic at least some functional and computational properties of the biological nervous systems [6].

Most of the neuromorphic systems are classified as Spike Neural Network (SNN), based on the concept that the information is transferred between neurons using temporal information conveyed on the onset of spikes [59]. Accurate representations of the neuron functionality may include complex and non-linear mathematical models like the Hodgkin and Huxley or Izhikevich [60] models of ions channels on the neuron membrane. As an example of VLSI implementation of such ion channels is the Field Programmable Neural Array (FPNA) [56]. It is an array of neurons (one per line) with sub-threshold circuits emulating dendrite sections (columns) and the soma. Regarding the connectivity, in this circuit external inputs and soma outputs are routed back to dendrite sections throughout cross-bars.

However most of the neuromorphic architectures are based on the simpler integrate-and-fire (I&F) representation of the neuron [61]. From this principle, very simple basic blocks were designed to represent neurons and synapses [62, 63, 64]. Although some recent approaches use digital architectures, traditionally these circuits were designed using analogue circuitry mainly [65, 57] due their smaller sizes.

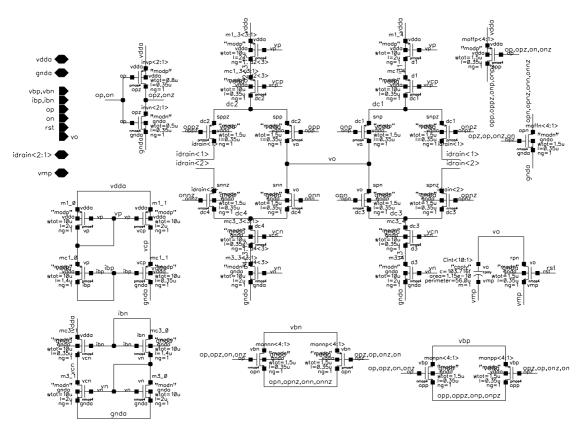

**Figure 2.3:** Examples of neuromorphic architectures. (a) Field programmable neural array (FPNA) presented in [56] is an array of sub-threshold circuits to mimic ion channels presented in neuron membrane; (b) an event-based VLSI network of integrate-and-fire (I&F) neurons from [57] with neurons (trapezoids) and excitatory (E) and inhibitory (I) synapses; (c) a FPGA-based neuromorphic architecture as in [58] and (d) a neuromorphic system implemented into the AN221E04 FPAA from Anadigm Inc. presented in [55].

Most neuromorphic systems are very specialised programmable arrays, where neurons, synapses and other functional blocks act as CABs. In [57] the system is built from 32 neurons with 22 synapses each. However these systems can also be implemented using generic programmable arrays, both digital — DSPs [66] and FPGAs [58, 67] — and analogue [68, 69]. The last two systems implement an I&F SNN and a pulsed coupled oscillator, respectively, into Anadigm's FPAAs. Due to limited hardware resources on these FPAAs, the I&F SNN system were implemented using multiple devices. Figure 2.3 shows some ANN and neuromorphic systems.

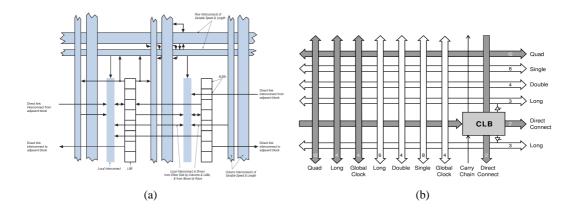

**Figure 2.4:** Altera and Xilinx FPGA routing styles. (a) Altera's Stratix II architecture presented in [70] and (b) the Xilinx XC4000 family as presented in [71].

Despite all these interesting and innovative "analogue programmable architectures", the main contribution to this thesis from neuromorphic systems is the most common method (Address Event Representation — AER, described on next chapter) used to rout information among its elements, which differs from the conventional analogue routing methods used so far.

#### 2.3 Analogue information routing

As said before, one of the main issues faced by programmable analogue systems is the communication of information between their computational blocks. The main characteristics of analogue routings are their degree of connectivity, signal integrity and power and area used by them. The ideal routing architecture would present a maximum degree of connectivity, connecting every signal of any CAB to any other CAB in the system. It would also convey the signals with no degradation, either from the routing itself or from other signals, and present the minimum area and power consumption overhead.

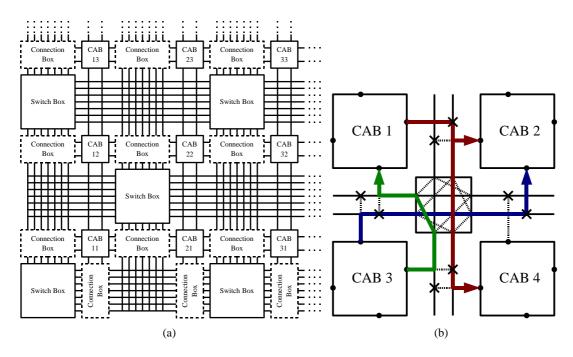

In FPGAs the signals are usually routed using switch-based routers and buffers with each vendor presenting different routing implementations. Xilinx implements island-style architectures with each logic block surrounded by connection blocks which connect them to different wires segments that end at switching blocks. The different wire segments allows for short, direct interconnection for speed optimization to long wires to large fan-out and clock signals. Local and global connections are used by Altera FPGAs as depicted in figure 2.4(a) whilst a Xilinx routing example is illustrated in figure 2.4(b).

**Figure 2.5:** FPAA routing example. (a) An example of a programmable analogue array as presented in [73] and (b) an example of CABs connection pattern.

Similar approaches are used by most of the programmable analogue systems [72], with the figure 2.5 showing an example architecture and connection examples. Examples of commercial systems include architectures from Lattice, Cypress and Anadigm as shown in table 2.1. Academic examples that use switch-based routers are HFPAA [35] and floating-gate based FPAAs [20], among others.

Using switch matrices and crossbars leads to some design issues like connectivity and signal integrity. The degree of connectivity is related to the power and area usage<sup>2</sup>. The degree of connectivity (fanout) presented by these techniques are given by Rent's rule, after E.F. Rent's empirical work on sockets for digital computers to IBM [74] and can be applied even for brain connectivity [75]. In one interpretation of this rule [76], if a group of elements is arbitrary bounded, then it defines the number of links crossing this boundary:

$$P = P_0 N^b (2.1)$$

with P being the number of links (wires),  $P_0$  being the number of pins of each N elements

<sup>&</sup>lt;sup>2</sup>In digital systems, timing is also affected by the degree of connectivity

inside the boundary and b is an empirical constant dependent of specificity and optimization of the system. For programmable gate arrays b is close to 1 [75] where different algorithms are employed to optimise number of switches and wire lengths.

Considering a chip with N elements, Sivilotti [76] defined  $\beta$  as the fanout of each element:

$$\beta = \frac{N_s}{P_0^2 N} \tag{2.2}$$

where  $N_s$  is the number of switches to connect these elements. In a non-hierarchical connection pattern with  $P_0N$  inputs and P outputs then applying equation 2.1:

$$N_s = P_0^2 N^{b+1} (2.3)$$

which gives  $\beta = N^b$ . For full connectivity, each element needs to connect to any other element, giving b = 1. Therefore, the number of switches needed for a full connectivity using crossbars increases proportionally to the square of the number of elements. Hierarchical approaches can reduce this number [76].

The switch-based analogue routing is used by many analogue programmable arrays implementations. As crossbars are efficient only for small size architectures [75], current systems tend to present a small number of CABs [77].

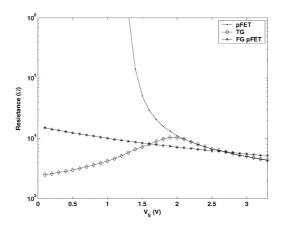

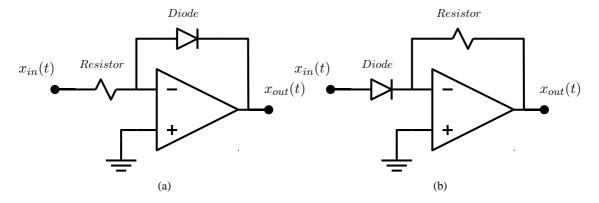

Other issues appear with the use of switches for routing analogue signals and one is related to the linearity of switches. When implemented with MOS transistors, the switch resistance is heavily dependent of the signal amplitude, which leads to signal distortion. CMOS transmission gates and, more recently, floating-gate transistors can reduce but not eliminate this limitation [20], as shown in figure 2.6. However, floating-gate transistors require highly complex programming methods due the high voltage required for the generation of tunnelling effect.

In a programmable array a signal is normally connected to several other CABs, i.e. the signal has a high fanout. These CABs are located at different distances from the signal origin and, therefore, the connections present different dynamic responses. These responses are due to different capacitances and resistances (wire lengths and number of switches) of each connection. These differences results in destination-dependent signal distortion due to the different delays (phase shift) applied to the signal.

**Figure 2.6:** Non-linear switch resistance. Typical MOS switch (pFET), transmission gate (TG) and floating-gate switch (FG pFET) resistance as a function of input signal amplitude (Vs), from [20]. This input amplitude dependence contribute to signal distortion on switch-based routing.

In a switch-based routing, signals are transmitted using wires laid orthogonally. Capacitive coupling between these wires leads to another source of distortion known as inter-channel interference. Longer the routing path, higher is the probability of a signal suffer interference from other signals.

When a high fanout is required, CABs are designed with buffers for their output signals. As these buffers are designed to meet the worst case condition (highest fanout) their inclusion leads to high power consumption.

If crossbars are in one extreme point presenting full connectivity, in the other extreme are systems where each cell is allowed to connect only to its neighbours, like in CNN topologies [44] and in hexagonal FPAAs [42]. Whilst these approaches avoid most of the area overhead of routing-dedicated circuitry, they tend to use the CABs themselves as routing channels. Unless these systems target very specific applications, they tend to require a high level of CABs used exclusively for routing.

#### 2.3.1 Timing communication

Analogue signals conveys information which using a limited range of continuous values changing in continuous or discrete times. The continuous characteristics of its amplitude, although allows for more compact information representation, make its storage and transmission less accurate due to presence of noise and distortion among others.

Modulation methods are used to increase the efficiency of such signals because they use a more robust carrier for transmission. Information is then coded by changing one or more characteristics of the carrier. Because this carrier is more easily detected and measured, its use can reduce information loss common to analogue signals.

Modulations are usually classified into digital, analogue and pulse modulations. In analogue modulations the carrier is also an analogue signal with well defined characteristics such a sine wave. The information is then coded into the carrier's amplitude (AM), frequency (FM) or phase (PM). Although it presents greater immunity then the original representation, these modulations are also susceptible to the same effects due its analogue characteristics. Digital modulations also use analogue carriers but coded with a digital representation according to the information to be transmitted. It requires analogue-to-digital conversions of the information before signal transmission, therefore losing the advantages of the analogue representation.

In contrast, the carrier in the pulse modulations is usually a signal with a limited number of states. The information is coded into the switching time or switching frequency of these states. Binary state representation presents a higher amplitude separation and, therefore, an easier distinction between them. This distance has the potential to offer good noise immunity [78] and, therefore, an easier routing in a programmable analogue array architecture when compared to the use of an analogue signal. Inaccuracies appears on the switch timing (jitter) rather than in the carrier amplitude.

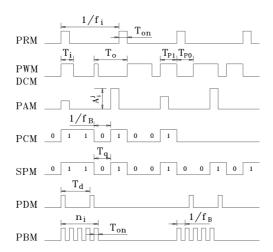

Examples of pulse modulations are Pulse Frequency and Rate Modulation (PFM/PRM), Pulse Delay or Position Modulation (PDM), Pulse Width Modulation (PWM), Pulse Code Modulation (PCM) and Stochastic Pulse Modulation (SPM) and are shown in figure 2.7. A detailed review of these modulations is found in [79], where the author did an extensive analysis of the mentioned modulations regarding on accuracy, multiplexing and power dissipation, and in [80], where the modulations are considered in neuromorphic realm.

The idea of using timing as the key parameter in analogue processing is not new, and it is more clear if we consider PWM modulations. The PWM is used in D-class audio amplifiers, which are more energy-efficient than other power amplifiers classes, electric motor drive control and communications, for instance.

As an analogue signal representation, timing representation coding has been used by neuromorphic systems groups in their quest to mimic the biological neuron [81]. The coding is associated

Figure 2.7: Some pulse stream modulations. From the top: Pulse Rate Modulation (PRM), Pulse Width Modulation (PWM), Pulse Amplitude Modulation (PAM), Pulse Code Modulation (PCM), Stochastic Pulse Modulation (SPM), Pulse Delay Modulation (PDM) and Pulse Burst Modulation (PBM). Adapted from [79].

with spike trains in this specific case. A great number of circuits modelling specific properties of the neurons have been published [82, 83], whilst others focus on its computational potentials [59]. Currently, these researches find applications on field of neuro-inspired circuits, like auditory [84], olfactory [85] and visual [86] systems.

Other two groups — the Hybrid Group at University of Florida (Dr. John G. Harris) and the Bionet Group at University of Columbia (Dr. Aurel A. Lazar) — have developed similar works also using spike coding. Their researches focus on mathematical foundations and implementations of time encoding machines using irregular sampling techniques [87, 88]. Both uses the integral characteristic of integrate-and-fire neurons models to perfectly reconstruct an analogue signal from a spike train. This reconstruction is based on finding the weights of a coefficient matrix.

By using timing representation, the signal dynamic range is increased. Voltage and current dynamic ranges tend to be reduced with the evolution of the CMOS fabrication technologies and system requirements, as low voltage supplies and low power consumption are required. On the other hand, timing dynamic range tends to increase as the IC fabrication technology delivers faster and smaller transistors.

One limitation of timing to express analogue variables is regarding to its continuity. Because of the analogue (voltage or current) to time conversion, there is always a period of time allowed

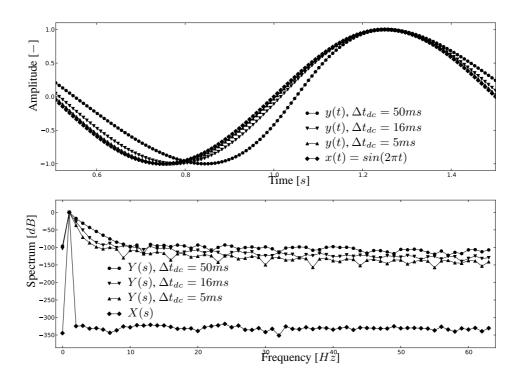

**Figure 2.8:** PDM distortion. Example of distortion due to asynchronous pulse distance modulation (PDM). Each y(t) is the modulated output for the sine wave x(t) with different timing characteristics.  $\Delta t_{dc}$  represents the mean time distance of events for each case. A constant ratio between the timing dynamic range to mean time distance of 1.8 was used. In other words, for y(t) modulated with  $\Delta t_{dc} = 50ms$ , the highest x(t) value presents a distance of 50ms - 1.8\*50ms/2 = 5.0ms whilst for the lowest value of x(t) the distance is 50ms + 1.8\*50ms/2 = 95.0ms. As the output y(t) is updated at different times, this output is a distorted version of the input x(t).

to represent the measured value. Therefore information cannot be measured continuously and therefore every timing modulation is time-sampled. This sampling time can be fixed — as in clocked systems — or variable, allowing another measurement after a previous one has finished.

Clocked versions — specially PWM-based ones — have been used for transmission of analogue information in arrays [21, 89]. However, the requirement of a global clock signal to synchronize the transmission leads to greater power consumption and issues such as clock skew, noise [90], metastability and high levels of electromagnetic interference (EMI) compared to variable-timed sampled (asynchronous) systems [91].

However continuously-update variable-timed sampled systems leads to signal distortion due to phase shift generated by different timing windows, as shown in figure 2.8 for PDM modulation.

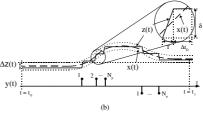

A special class of timing modulations are known as differential modulations. The information transmitted with these methods is related to the previous measurements rather than the information itself. Because of this property these modulations need some type of memory to store previous information.

Delta-based modulations [92] are differential modulations where the conveyed information is restricted to represent an increase or decrease by a fixed small amount. In the simplest case, a simple bit is enough to represent these binary states. In their asynchronous versions of these modulations, each timing event does not convey signal amplitude information, but rather the instant when the signal amplitude has changed by a fixed value and the direction of this change. Some of these modulations are studied in more details in the next chapter.

# 2.4 Summary

In this chapter, a brief history of the analogue programmable arrays was presented. This type of circuits have been struggling to obtain the same level of maturity and popularity as the digital arrays. One of the reasons is the relatively small array size in the available analogue arrays and it is due mainly to the intercommunication between the array elements.

The problem of intercommunication between each block inside an array is an important issue in digital arrays but rather more problematic in its analogue counterpart. In digital domain the used area, power overhead, the degree of flexibility in the communication pattern and the delays inserted in the signal path are the main aspects to be considered in the communication design. In analogue arrays, these aspects are added to intrinsic analogue challenges of the signal distortion, white noise and interference.

The use of communication methods similar to the digital arrays present a great limitation on the practical size of the analogue array and power consumption. In the next chapter a time based alternative to overcome this essential limitation is proposed.

# Chapter 3

# Asynchronous spike event coding scheme: the communication method

#### 3.1 Introduction

In the previous chapter a detailed review of the field of programmable analogue arrays were presented. The limitations of the current communication mechanisms were explained and a different approach using time as the information representation was suggested.

In this chapter a novel programmable analogue communication architecture is proposed. This architecture uses timing-encoded signals to convey information between the CABs within the array and outside the system.

Firstly, the communication method used for the proposed programmable architecture is presented and its functionality is explained. In this chapter the communication aspects of the method is studied whilst its computational properties are presented in chapter 4. Address Event Representation (AER) constitutes an important part of the method and therefore is presented in this chapter as well.

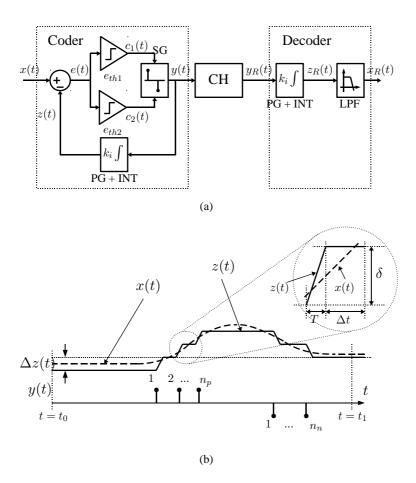

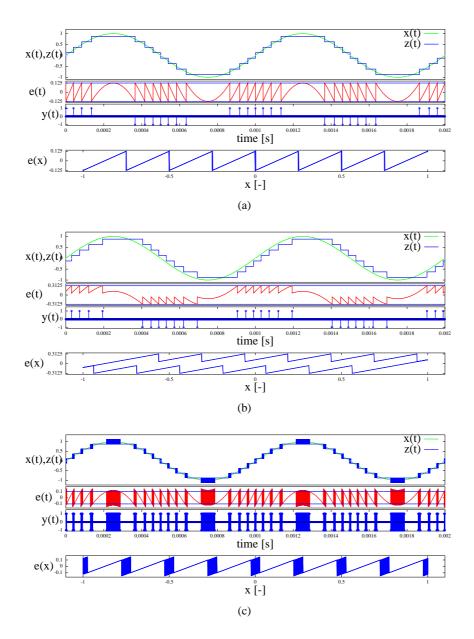

The core of such method, the timing coding, is presented. A specific timing coding scheme, the Ternary Spike Delta (TSD) modulation is used in this work. However other timing schemes are also able to be integrated into the architecture. A set of these alternative methods are presented in the following sections.

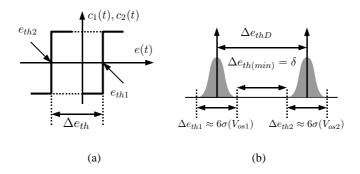

Finally, with different timing coding candidates being available, a method to evaluate the performance of each coding schemes is needed. The evaluation is performed by measuring its *Channel Efficiency* (CE) together with other constraints, mainly their computational properties. The outcome of such evaluation reveals that the TSD coding is theoretically the most suitable to be implemented.

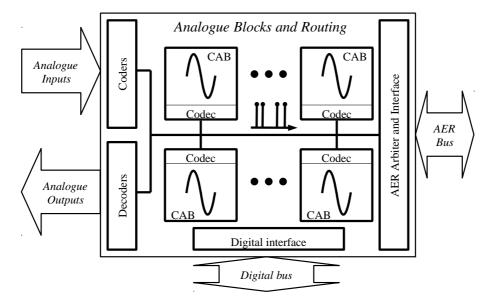

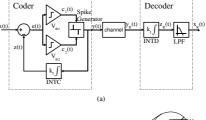

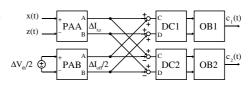

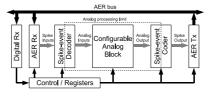

**Figure 3.1:** Proposed communication architecture. The array of Configurable Analogue Blocks (CABs) is connected using an asynchronous digital channel. Asynchronous Spike Event Coding (ASEC) coders and decoders (codec) are also used to interface the array with external circuitry.

# 3.2 Asynchronous spike event coding scheme

From the review of the previous and existing FPAA architectures, the inter CABs communication was identified as an important issue and one of the main limitations of FPAA performance. In this work a novel architecture is proposed based on the timing communication.

The architecture is designed to be flexible regarding the CAB's internal functionality or implementation as long their inputs and outputs signals respect the limitations of the communication scheme. The system is flexible enough to even allow a hybrid implementation of communication methods. For instance, a system can use conventional communication method of analogue switch matrices to transmit information inside a small-size cluster of CABs and the timing method used to communicate between clusters.

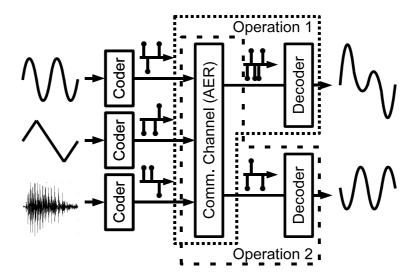

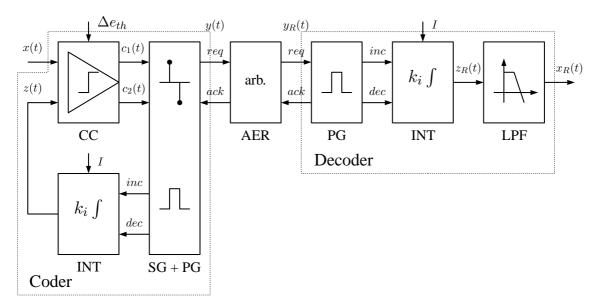

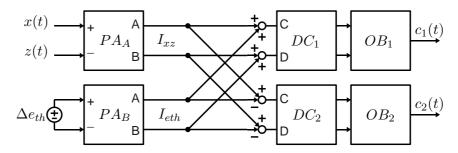

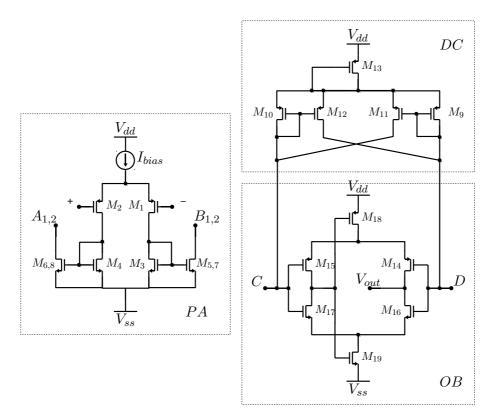

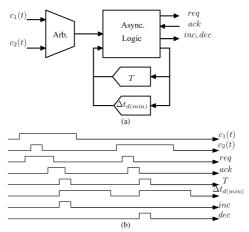

In the architecture shown in figure 3.1, CABs in an array are virtually interconnected using a common asynchronous digital channel. The communication between those CABs is the role of the Asynchronous Spike Event Coding (ASEC) communication scheme [93]. This scheme is the result of the *association* of the AER communication method with the TSD modulation which perform the conversion of analogue signals into timing information and vice-versa. The TSD modulation output is used to trigger AER communication signalling in the digital channel.

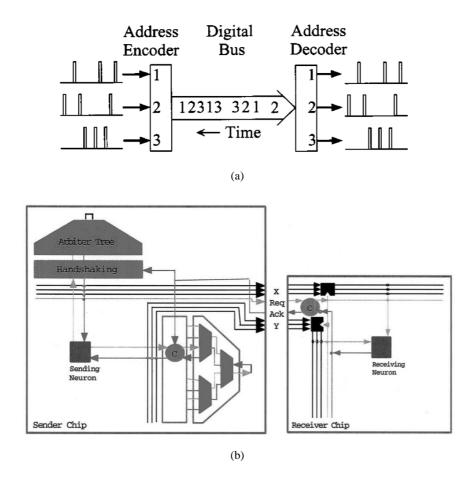

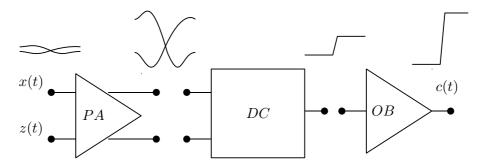

**Figure 3.2:** ASEC-CAB interface diagram. Block diagram of the Asynchronous Spike Event Coding (ASEC) scheme interfacing with a CAB. With this architecture, analogue signals are limited to the CAB realm, reducing the levels of interference.

ASEC conversion consists of one *Spike Event*<sup>1</sup> coder and decoder pair for each CAB as shown in figure 3.2. These coders and decoders work on the onset of specific events: whenever the CAB output analogue signal is found in certain conditions for the coders and on the common channel state for the decoders.

The transmission of these spike events is implemented using the common digital channel rather than dedicated interconnections. Because these events are asynchronous, the AER protocol — widely used in neuromorphic designs [94] — is an appropriate choice<sup>2</sup> for the management of information flux inside the array. This protocol has been used to convey analogue information in the past, as in [96].

# 3.3 The channel component: Address event representation

As said in the previous chapter, neuromorphic systems try to mimic structures and functionalities of biological neuronal systems into VLSI technology. Similar to biological neurons, most of such systems use spike representation for transmit information between their elements. However real neurons can be connected to hundreds or thousands of other neurons in a 3-D

<sup>&</sup>lt;sup>1</sup>The "Spike" part of the name is derived from the neuromorphic systems, where the communication method was inspired. In these systems, as well as in actual neurons, an abrupt change of the a variable state (the membrane potential) encodes information in the instant it has happen rather than the change itself.

<sup>&</sup>lt;sup>2</sup>In [95], Boahen performed a statistical evaluation of the AER protocol against other asynchronous protocols like ALOHA and CSMA. He concluded that arbitrated channels provide a communication throughput five fold than an non-arbitrated (ALOHA) channel.

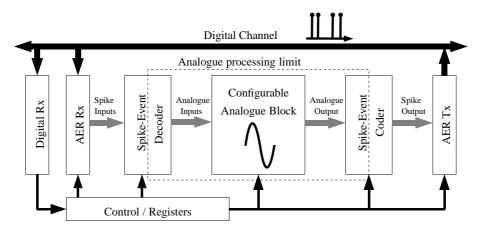

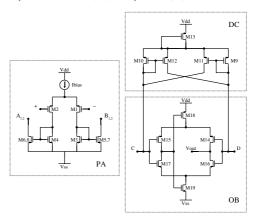

**Figure 3.3:** Address Event Representation. (a) Address Event Representation (AER) working principle and (b) conventional AER architecture from [95]. All events generated by the neurons (or CABs in our case) are coded according to the neuron address (an unique identification), multiplexed in time and then decoded at the receiving side. The conventional architecture comprises of horizontal and vertical arbiter trees and handshaking signalling circuitry.

configuration whilst individual elements in analogue VLSI systems are connected in a 2-D silicon IC. A solution to overcome this limitation is to create "virtual connections" between those elements. An asynchronous communication system which implement these connections is the *Address Event Representation* (AER).

Original AER is a point-to-point asynchronous handshaking protocol for transmission of digital words using a Multiple Access Channel (MAC) common to every element in the array. The information coded in these transmitted digital words represents the identification (address) of either the transmitting or receiving CAB, depending on the implementation. The former case will be used in the following description.

The communication initiates whenever an element (a CAB in a FPAA) in the array generates an event. This element requests a permission to access the digital bus. If granted by the arbiter, its address is written on the digital bus, broadcasting the event to other elements in the array. An AER router is responsible for distributing these events to the appropriate receiver using internal or external LUTs, for instance. In this work, we use an external FPGA to route the spikes between coders and decoders. After the target element had acknowledged the reception of the event, the bus is freed to further utilization.

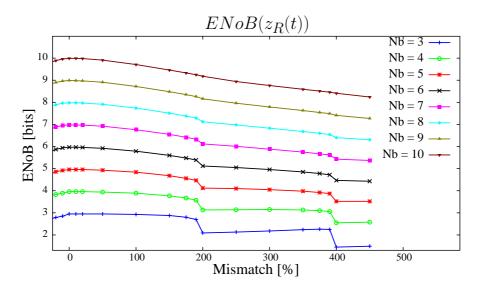

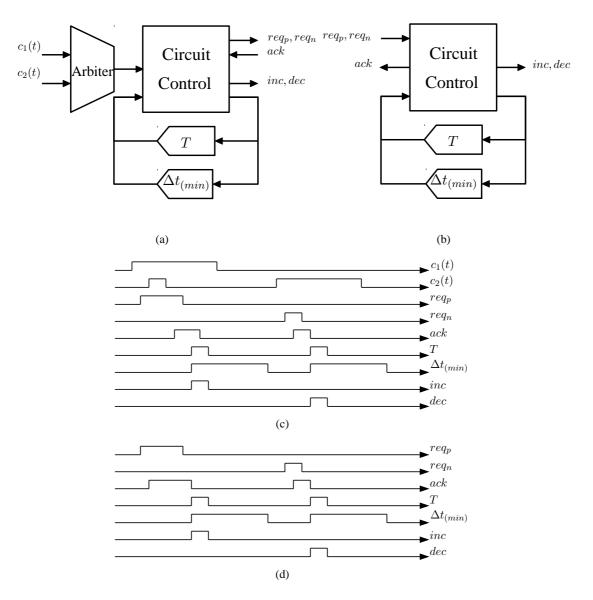

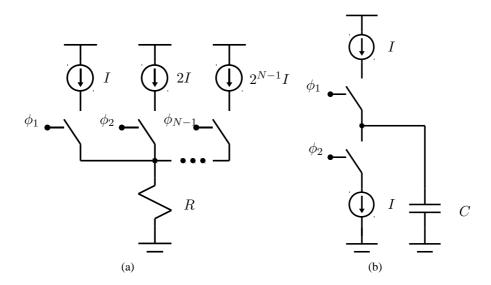

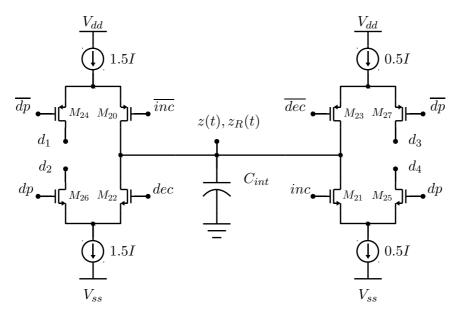

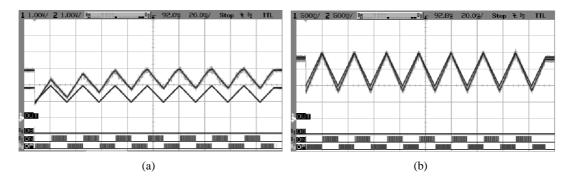

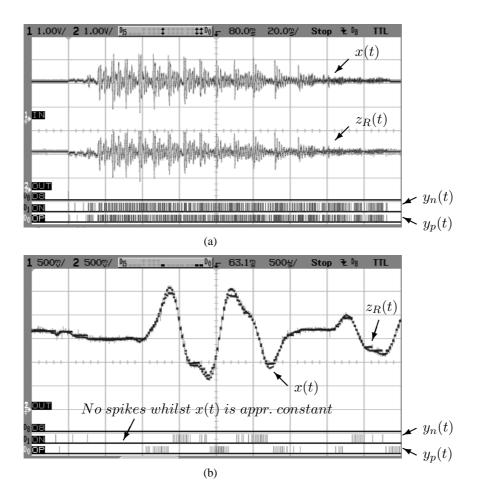

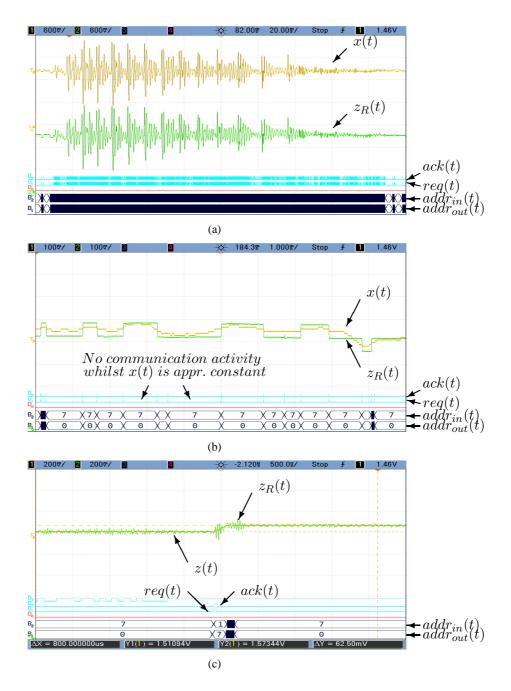

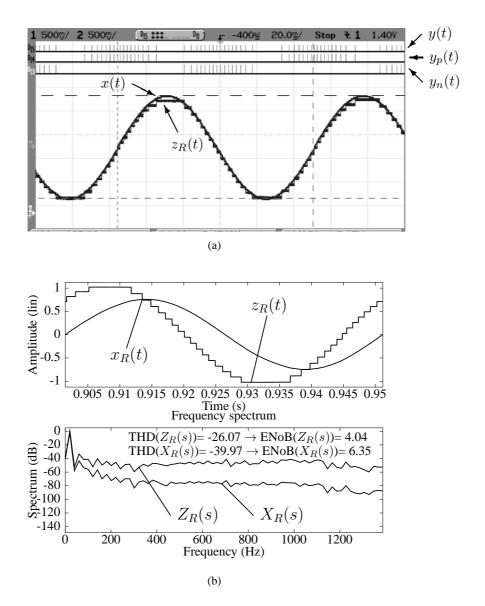

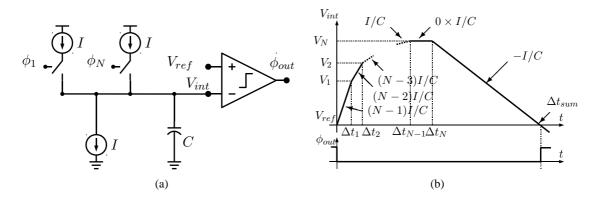

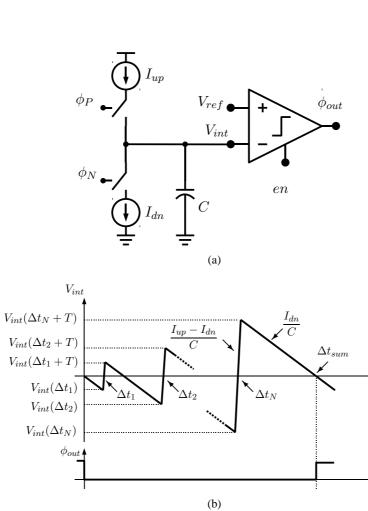

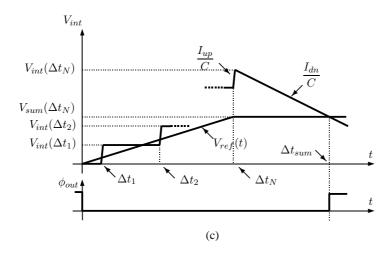

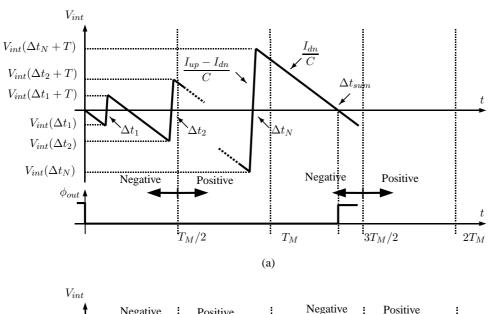

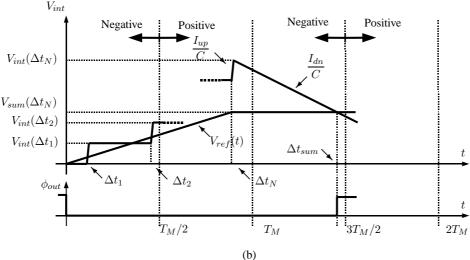

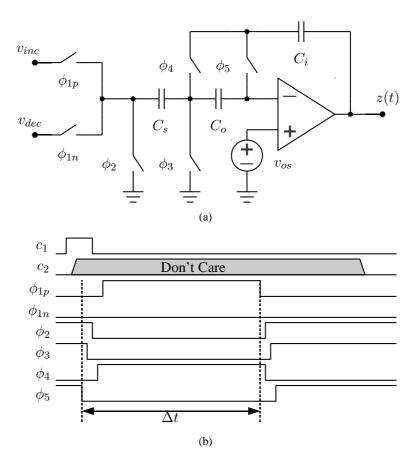

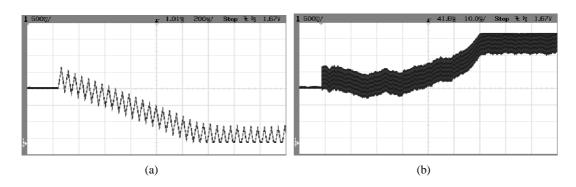

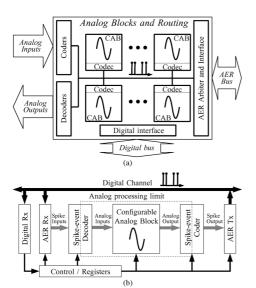

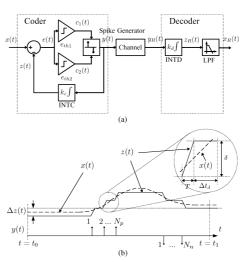

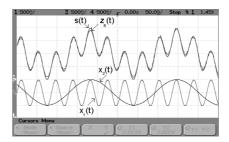

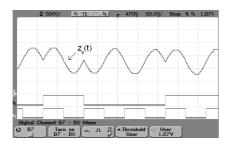

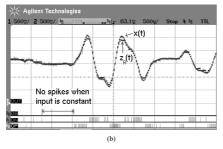

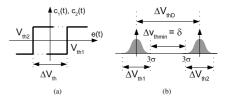

The asynchronous nature of the AER protocol greatly preserves the information conveyed in the time difference between events. The main source of inaccuracy between the generated and the received time difference is found in the presence of event collisions. Because the access to the channel is asynchronous and random, different elements may try to access the channel simultaneously. The AER protocol offers mechanisms to handle these spike collisions. Usually, a unique and central arbiter is used to manage collisions. In this case, collisions are resolved by an arbiter by queueing and transmitting successively all the spike events involved in a collision. Although this process can be made relatively faster than the signal, it is the main source of distortion due to the communication channel.