# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## Parallel Quantum Computing From Theory to Practice

Einar Pius

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy to the University of Edinburgh

August 2014

## Abstract

The term quantum parallelism is commonly used to refer to a property of quantum computations where an algorithm can act simultaneously on a superposition of states. However, this is not the only aspect of parallelism in quantum computing. Analogously to the classical computing model, every algorithm consists of elementary quantum operations and the application of them could be parallelised itself. This kind of parallelism is explored in this thesis in the *one way quantum computing* (1WQC) and the *quantum circuit* model.

In the quantum circuit model we explore arithmetic circuits and circuit complexity theory. Two new arithmetic circuits for quantum computers are introduced in this work: an adder and a multiply-adder. The latter is especially interesting because its depth (*i.e.* the number of parallel steps required to finish the computation) is smaller than for any known classical circuit when applied sequentially. From the complexity theoretical perspective we concentrate on the classes  $QAC^0$  and  $QAC^0[2]$ , the quantum counterparts of  $AC^0$  and  $AC^0[2]$ . The class  $AC^0$  comprises of constant depth circuits with unbounded fan-in AND and OR gates and  $AC^0[2]$  is obtained when unbounded fan-in parity gates are added to  $AC^0$  circuits. We prove that  $QAC^0$  circuits with two layers of multi-qubit gates cannot compute parity exactly. This is a step towards proving  $QAC^0 \neq QAC^0[2]$ , a relation known to hold for  $AC^0$  and  $AC^0[2]$ .

In 1WQC, computation is done through measurements on an entangled state called the resource state. Two well known parallelisation methods exist in this model: *signal shifting* and *finding the maximally delayed general flow*. The first one uses the measurement calculus formalism to rewrite the dependencies of an existing computation, whereas the second technique exploits the geometry of the resource state to find the optimal ordering of measurements. We prove that the aforementioned methods result in same depth computations when the input and output sizes are equal. Through showing this equivalence we reveal new properties of 1WQC computations and design a new algorithm for the above mentioned parallelisations.

# Declaration

Except where otherwise stated, the research undertaken in this thesis was the unaided work of the author. Where the work was done in collaboration with others, a significant contribution was made by the author.

Parts of this work have been published in the Journal of Quantum Information Processing [1] and other parts submitted to the Journal of Quantum Information and Computation. An earlier archived version of the latter can be found at [2].

> E. Pius August 2014

## Acknowledgements

First and foremost, I would like to express my gratitude to my supervisors Elham Kashefi, Chris Johnson, and Chris Maynard. I thank Elham for getting me interested in quantum computing in the first place, and for asking the right questions during the PhD. She guided me through my PhD while being both critical and encouraging at the same time and I am grateful for that. I also thank Chris Maynard, who is responsible for me pursuing a topic that eventually led me to the quantum arithmetic circuits. And many thanks to Chris Johnson who took up my supervision from Chris Maynard midway through my PhD and has taken care of me since then.

I would like to thank Alain Tapp who kindly accepted me as a visiting student at the University of Montreal in autumn 2012. The discussions I had with Alain ultimately led to the two results in the final part of the thesis. I would like to thank my colleagues Vedran Dunjko, Raphael Dias da Silva, and Theodoros Kapourniotis for the good times we had together and for the discussions we had.

This PhD was made possible through the funding from the Archimedes Foundation in Estonia and for that I am very grateful.

Finally, but by no means least, I am grateful to my lovely girlfriend Riinu, who not only supported me while I was spending long hours in the evenings working on the thesis, but also helped me proofread my work. I could not have done it without her.

# Contents

| $\mathbf{A}$  | bstra          | $\mathbf{ct}$                                          | i             |

|---------------|----------------|--------------------------------------------------------|---------------|

| D             | eclara         | ation                                                  | ii            |

| A             | cknov          | vledgements                                            | iii           |

| C             | onten          | $\mathbf{ts}$                                          | $\mathbf{iv}$ |

| $\mathbf{Li}$ | st of          | figures                                                | vii           |

| $\mathbf{Li}$ | st of          | tables                                                 | ix            |

| In            | trodu          | action                                                 | 1             |

| Ι             | Qua            | antum Arithmetic Circuits                              | <b>5</b>      |

| 1             | $\mathbf{Pre}$ | liminaries                                             | 8             |

|               | 1.1            | Classical Circuits                                     | 8             |

|               |                | 1.1.1 Numerical Representation                         | 10            |

|               | 1.2            | Quantum Circuits                                       | 13            |

|               |                | 1.2.1 Unbounded Quantum Gates                          | 20            |

|               |                | 1.2.2 Translating Boolean circuits to quantum circuits | 22            |

|               |                | 1.2.3 The Quantum Fourier Transform                    | 24            |

|               | 1.3            | Arithmetic Circuits                                    | 26            |

|               |                | 1.3.1 Adders                                           | 27            |

|               |                | 1.3.2 Multipliers                                      | 40            |

|               |                | 1.3.3 Multiply-Adders                                  | 42            |

| <b>2</b>      | The            | QFT Multiply-Adder                                     | <b>45</b>     |

|               | 2.1            | The QMAC Circuit                                       | 45            |

|               | 2.2            | Analysis of the Circuit                                | 49            |

|               |                | 2.2.1 Pipelining: a classical alternative              | 54            |

| 3             | The            | QFT Adder                                              | 55            |

|               | 3.1            | The QFT Adder Circuit                                  | 56            |

|    | 3.2                              | Analysis of the Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58                                              |

|----|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 4  | Imp<br>4.1<br>4.2<br>4.3<br>4.4  | Dementing the QFT Arithmetic Circuits         Initialisation                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64<br>65<br>67<br>67<br>68<br>71                |

| 5  | Disc                             | cussion and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74                                              |

| II | $\mathbf{M}$                     | easurement Based Quantum Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 78                                              |

| 6  | <b>Pre</b><br>6.1<br>6.2         | liminaries         The measurement calculus         6.1.1       An example measurement pattern         6.1.2       Rewriting patterns         0.1.2       Rewriting patterns         0.1.1       Flow         0.1.2       Rewriting patterns         0.1.3       Rewriting patterns         0.1.4       Flow         0.1.5       Rewriting patterns         0.1.6       Flow         0.1.7       Flow         0.2.1       Flow         6.2.2       General flow         6.2.3       Focused flow | 80<br>81<br>83<br>84<br>84<br>85<br>86<br>88    |

| 7  | Sign<br>7.1<br>7.2<br>7.3<br>7.4 | hal shifted flowSignal shifting                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>89</b><br>89<br>90<br>93<br>97<br>100<br>103 |

| 8  | Con<br>8.1<br>8.2<br>8.3<br>8.4  | The last two layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\frac{114}{121}$                               |

| 9  | Disc                             | cussion and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 126                                             |

| II | I Q                              | uantum Circuit Complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 128                                             |

| 10 | 10.1                             | liminaries<br>Classical Low-Depth Complexity Classes                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| 11 Properties of QAC circuits | 140 |

|-------------------------------|-----|

| 12 Lower Bounds on Parity     | 144 |

| 13 Discussion and Results     | 155 |

| References                    | 157 |

| Publications                  | 163 |

# List of Figures

| 1.1  | Computing the depth of a Boolean circuit                                                                                                         | 9  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Adding a negative number in the two's complement representation using                                                                            |    |

|      | columnar addition. The values in the carry row correspond to the carry                                                                           |    |

|      | from the added bits in the previous column, <i>i.e.</i> the carry bit is 0 if the                                                                |    |

|      | sum of the previous column above the line is 01 or 00, and 1 if the sum                                                                          |    |

|      | is 10 or 11                                                                                                                                      | 12 |

| 1.3  | Multiplying two integers in the two's complement representation                                                                                  | 13 |

| 1.4  | An example quantum circuit.                                                                                                                      | 16 |

| 1.5  | Calculating the depth of a quantum circuit.                                                                                                      | 17 |

| 1.6  | Common Quantum Gates.                                                                                                                            | 18 |

| 1.7  | A legend of the notation used in this thesis                                                                                                     | 19 |

| 1.8  | The principle of deferred measurement                                                                                                            | 20 |

| 1.9  | Transforming a Toffoli to a $\wedge Z$ gate                                                                                                      | 21 |

| 1.10 | Transforming a parity to a fan-out gate                                                                                                          | 22 |

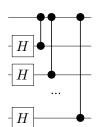

| 1.11 | The four unbounded gates used in this thesis                                                                                                     | 23 |

| 1.12 | Using the Toffoli gate to replace classical Boolean gates                                                                                        | 24 |

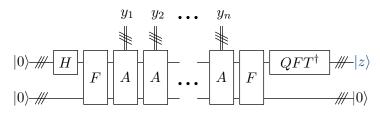

| 1.13 | The Quantum Fourier Transform                                                                                                                    | 25 |

| 1.14 | The half adder                                                                                                                                   | 28 |

| 1.15 | The full adder                                                                                                                                   | 29 |

| 1.16 | The quantum full adder                                                                                                                           | 30 |

| 1.17 | The decomposition of the Toffoli gate into two-qubit gates [42]                                                                                  | 30 |

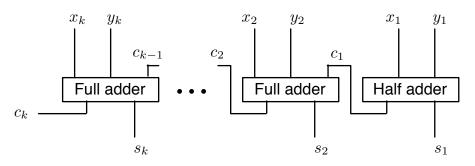

|      | The ripple-carry adder                                                                                                                           | 31 |

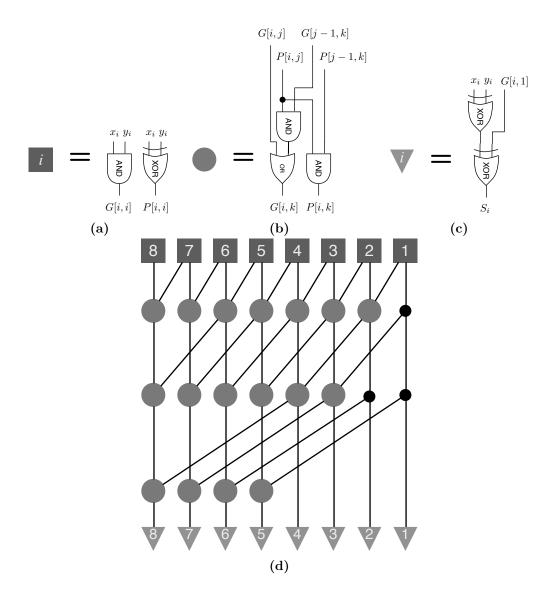

|      | The 8-bit Kogge-Stone Adder                                                                                                                      | 34 |

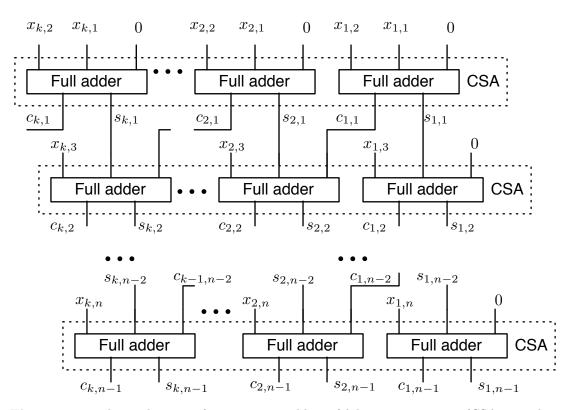

| 1.20 | The carry-save adder                                                                                                                             | 36 |

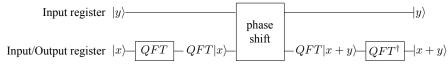

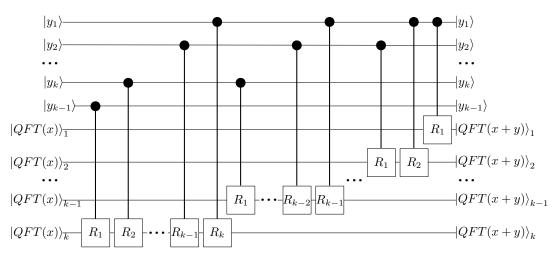

| 1.21 | The Draper adder.                                                                                                                                | 37 |

|      | The phase shift block of a $k$ -qubit Draper adder                                                                                               | 38 |

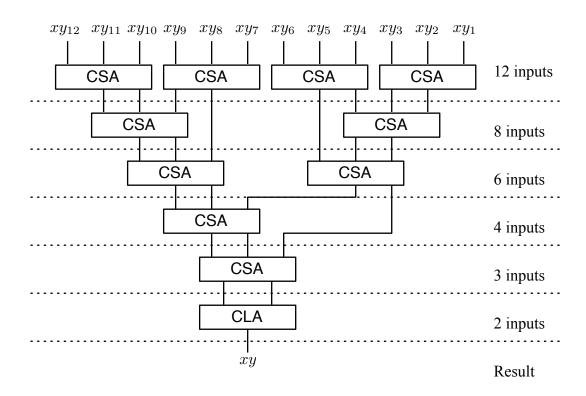

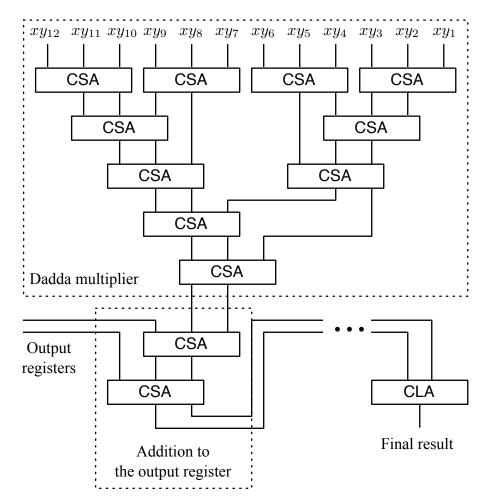

| 1.23 | The structure of the Wallace and Dadda multipliers                                                                                               | 41 |

| 1.24 | A multiply-accumulator circuit.                                                                                                                  | 44 |

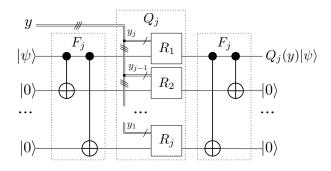

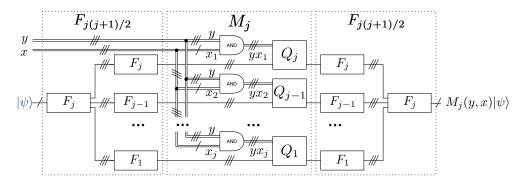

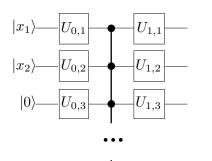

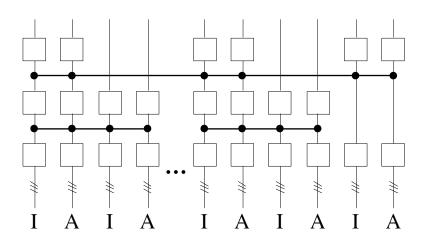

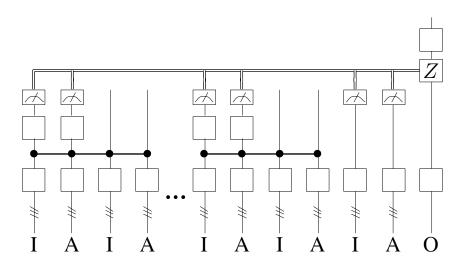

| 2.1  | The parallel $Q_j(y)$ operator $\ldots \ldots \ldots$ | 48 |

| 2.2  | The parallel hybrid circuit of the $M_j(y, x)$ operator                                                                                          | 49 |

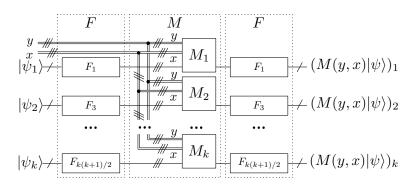

| 2.3  | The parallel hybrid circuit of the $M(y, x)$ operator                                                                                            | 49 |

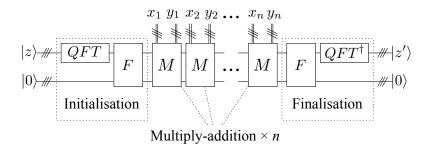

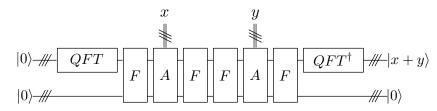

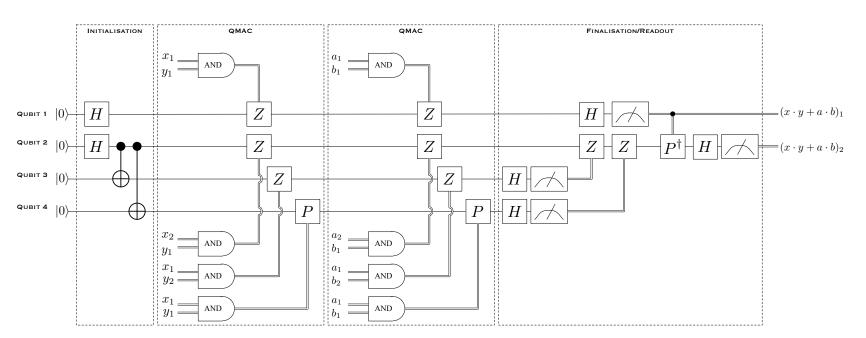

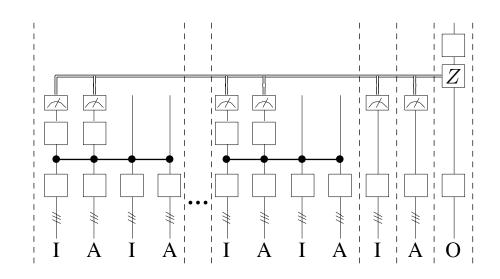

| 2.4  | Applying the QMAC $n$ times in a sequence $\ldots \ldots \ldots \ldots \ldots \ldots$                                                            | 50 |

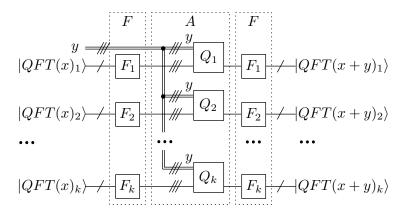

| 3.1  | The parallelised Draper phase shift block                                                                                                        | 56 |

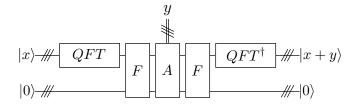

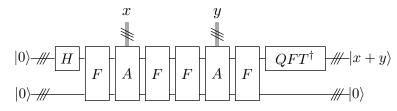

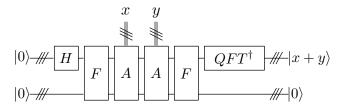

| $3.2 \\ 3.3 \\ 3.4 \\ 3.5 \\ 3.6$          | Constructing the QFT Adder: parallelising the phase shift block $\ldots$ .<br>Constructing the QFT Adder: from in-place to out-of-place adder $\ldots$ .<br>Constructing the QFT Adder: removing the initial QFT $\ldots$ .<br>Constructing the QFT Adder: removing the cancelling fan-out gates $\ldots$ .<br>Applying the QFT adder $n$ times in a sequence $\ldots$ . | $56 \\ 57 \\ 57 \\ 57 \\ 61$              |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

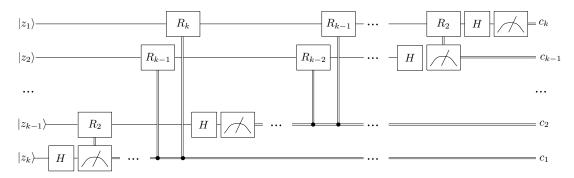

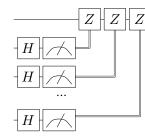

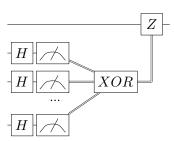

| $4.1 \\ 4.2 \\ 4.3$                        | The semiclassical QFT                                                                                                                                                                                                                                                                                                                                                    | 67<br>69<br>70                            |

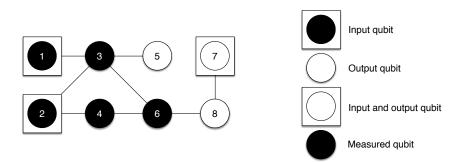

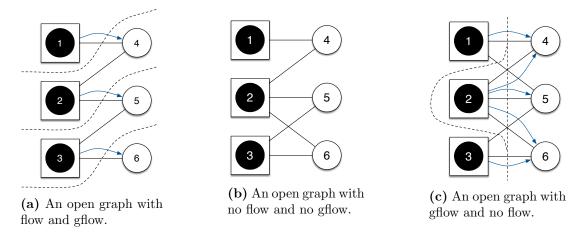

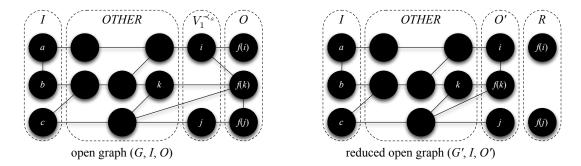

| $6.1 \\ 6.2 \\ 6.3$                        | An example of an open graph $\ldots \ldots \ldots$                                                                                                                                                                                                       | 82<br>83<br>86                            |

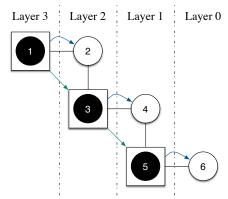

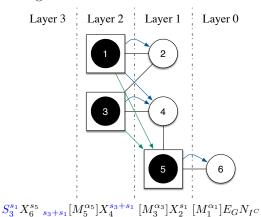

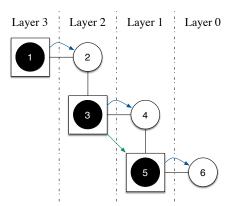

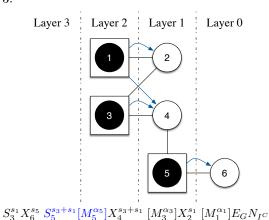

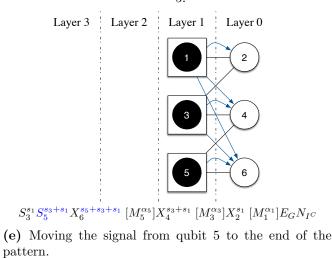

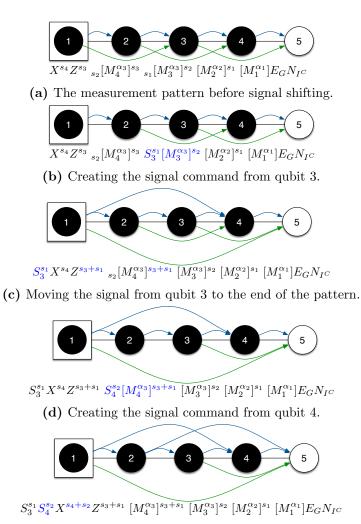

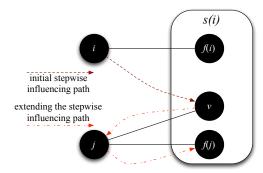

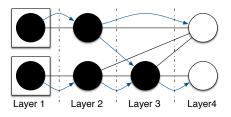

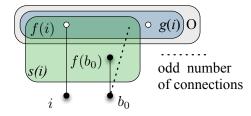

| $7.1 \\ 7.2 \\ 7.3$                        | Signal shifting a measurement pattern                                                                                                                                                                                                                                                                                                                                    | 91<br>92<br>105                           |

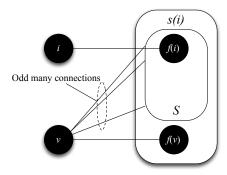

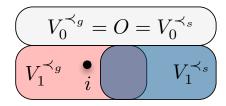

| $8.1 \\ 8.2 \\ 8.3 \\ 8.4 \\ 8.5 \\ 8.6$   | A gflow g with $ I  =  O $ and $ V_1^{\prec g}  <  V_0^{\prec g} $                                                                                                                                                                                                                                                                                                       | 107<br>108<br>109<br>109<br>115<br>116    |

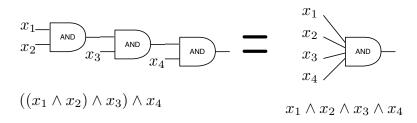

|                                            | Merging subsequent AND gates                                                                                                                                                                                                                                                                                                                                             | $\begin{array}{c} 131 \\ 139 \end{array}$ |

|                                            | The $\wedge Z$ gate applied to $ 0\rangle$                                                                                                                                                                                                                                                                                                                               | $\begin{array}{c} 143 \\ 143 \end{array}$ |

| $\begin{array}{c} 12.2\\ 12.3 \end{array}$ | Simplifying a multi-gate depth one $QAC_a$ circuit                                                                                                                                                                                                                                                                                                                       | 145<br>148<br>148<br>150                  |

| 13.1                                       | A multi-gate depth two circuit computing parity of four qubits $\ldots$ .                                                                                                                                                                                                                                                                                                | 156                                       |

# List of Tables

| 1.1          | Comparison of classical and quantum ripple-carry adders                                                     | 32       |

|--------------|-------------------------------------------------------------------------------------------------------------|----------|

| 1.2          | The value of carry output in a carry-lookahead adder                                                        | 33       |

| 1.3          | Comparison of classical and quantum carry-lookahead adders                                                  | 35       |

| 1.4          | Comparison of classical and quantum carry-save adders                                                       | 37       |

| 1.5          | Draper Adder Resources                                                                                      | 39       |

| 1.6          | Dadda Multiplier Resources                                                                                  | 42       |

| 1.7          | The depth and gate count of the MAC                                                                         | 42       |

| $2.1 \\ 2.2$ | A summary of the properties of the MAC and QMAC circuits A detailed comparison of the MAC and QMAC circuits | 53<br>53 |

| 3.1          | Comparison of the QFT adder with carry-save and Draper adders                                               | 62       |

| 3.2          | A breakdown of the properties of the QFT, carry-save, and Draper adders                                     | 63       |

| 5.1          | Summary of possible optimisations to the QFT Arithmetic circuits                                            | 77       |

## Introduction

The quantum computing model has two concepts of parallelism. First, quantum computations can act on a superposition of states, modifying all of them simultaneously. This effect has for example been used in the famous Shor's [2] and Grover's [3] algorithms and does not exist in classical computers. Second, the parallelism achieved through the application of multiple quantum gates simultaneously. This corresponds to the classical approach of parallelisation and has been studied in both the circuit [4, 5, 6, 7, 8] and one way quantum computing (1WQC) model [9, 10, 11]. The latter kind of parallelism, which is the focus of this work, is important in at least two aspects. First, parallel computations could be executed faster (that is the main motivation for parallelising), thus reducing the time that quantum states need to be coherent for. Second, the quantum model could allow the implementation of some algorithms in a more parallel manner than is possible classically, thus computations could possibly run faster on parallel quantum computers. This has motivated the search for new parallel quantum algorithms [12] and parallelisation methods [9, 10, 11]. The problem addressed in this work is twofold: do there exist any arithmetic operations benefitting from quantum parallelism, and how much can we expect to parallelise computations in the quantum model?

The first part of this thesis presents a new quantum arithmetic circuit, which is more parallel than any of its known classical counterparts. The later chapters try to establish limits on parallelism in quantum computing by first clarifying that two common methods in 1WQC model produce equivalent results (Part II) and proving a lower bound on the parallel circuits computing parity (Part III).

This work introduces two new quantum Fourier transform (QFT) based arithmetic circuits. The first of these circuits, the QFT multiply-accumulator (QMAC), is introduced in Chapter 2 and has been published in the Journal of Quantum Information processing [1]. A multiply-accumulator (MAC) is a circuit performing the operation z = z+xy on numbers and is an important operation in modern digital signal processors;

thus accelerating this operation has significant practical uses. Our QMAC is the first published quantum MAC circuit and the first basic quantum arithmetic circuit that exhibits a lower depth than any of its classical counterparts. The defining feature of the QMAC is its depth on sequential application, which is asymptotically smaller than in any previously known classical or quantum MAC. This property makes the QMAC not only a suitable candidate for a MAC unit in future quantum processors, but it could be beneficial to implement it as an accelerator or co-processor in classical computers. The second arithmetic circuit, the QFT adder presented in Chapter 3, has not yet been published. It was initially left out of the QMAC paper [1] since it does not exhibit an asymptotically lower depth than its classical counterparts, as the QMAC does. However, later analysis showed that in sequential application its implementation could have as much as 24 times smaller depth than any other quantum adder. Therefore, possible future developments of quantum processors should consider the use of the QFT adder.

In August 2013, the QMAC was presented to the physicists at the Centre for Quantum Photonics in the University of Bristol. There was interest in the QMAC and questions about simplifying the circuit for implementation with the technology available to their group. Their interest and questions motivated the inclusion of Chapter 4, which contains modifications that could simplify the experimental realisation of a QMAC. One request from the Bristol group was the simplified circuit schema of a QMAC with an explicit proof that it would perform the multiply-accumulation of a two-bit integer. This circuit is included towards the end of Chapter 4 and could be used as a starting point for experimentalists wishing to implement the QMAC.

The second part of the thesis focuses on parallelisation methods in the one way quantum computing (1WQC) model. Computations in the 1WQC model are performed by doing measurements on entangled qubits. These measurement outcomes are in general probabilistic, but can be used to correct subsequent measurements to obtain computations performing unitary operations [13]. The main result of Part II states that two well known parallelisation techniques in 1WQC result in equal depth when applied to computations translated from quantum circuits. These two methods work on distinct representations of measurement based computation: one on the *measurement patterns* [14] and the other on the *flows* [15] and *general flows* [16] of the underlying graph. The description of flows and of the 1WQC is included in Chapter 6, signal shifting is covered separately in Chapter 7. First of those methods, signal shifting [14], comprises of a set of rewriting rules for measurement patterns. The second technique, finding the maximally delayed general flow [9], uses only the structure of the graph representation of 1WQC to provide a low depth dependency

structure for the measurements. Through the construction of the proof, many new properties of 1WQC which could be used in future research of flows and signal shifting have been discovered. One of the main techniques from the proof has already been successfully applied to construct a translation method from 1WQC to quantum circuits which does not increase the number of qubits in the computation [17]. In the course of constructing the main proof, a new algorithm for signal shifting and finding maximally delayed general flows is created. This new algorithm works on computations derived from quantum circuits and requires  $O(n^2)$  operations to complete. This is smaller than the operations required for the best previously known algorithms for signal shifting and finding the maximally delayed general flow,  $O(n^6)$  [14] and  $O(n^2)$  [9] correspondingly. The work in Part II is available on arXiv.org [18] and has been submitted to the Journal of Quantum Information and Computation.

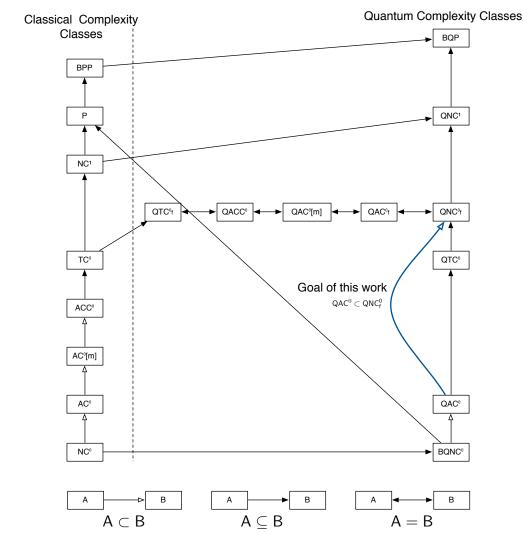

The final part of this thesis focuses on quantum circuit complexity. Proving lower bounds in complexity theory for general circuits is very hard, hence numerous circuit families with various restrictions have been created. One of those restrictions limits the depth of the circuits. Depth restricted circuits can also be seen as parallel circuits, since the number of gates and bits/qubits allowed is polynomial in input, *i.e.* a larger number of resources can be used to simultaneously perform a computation in fewer sequential steps. The only lower bound known in quantum parallel complexity is between the classes  $QNC^0$  and  $QAC^0$ . The class  $QNC^0$  consists of constant depth quantum circuits containing only quantum gates that act on a constant number of qubits. The class  $QAC^0$  is the quantum equivalent to the classical  $AC^0$  class: constant depth Boolean circuits with unbounded fan-in AND, OR and NOT gates. Unbounded fan-in means that the gates can have an arbitrary number of inputs. The inequality  $QNC^0 \neq QAC^0$ holds because circuits in the  $QNC^0$  class cannot compute functions that depend on all the input qubits [6].

Although not many lower bounds have been found, research in quantum circuit complexity has revealed surprising differences in the relations between quantum circuit classes and their classical counterparts. First, the quantum circuit classes  $QAC^{0}[n]$ and  $QAC^{0}[m]$  have been proven to be equal for every m and n [5], whereas in classical circuit complexity  $AC^{0}[p] \neq AC^{0}[q]$  for distinct primes p and q [19, 20].  $QAC^{0}[m]$  is the quantum counterpart to the  $AC^{0}[m]$  class, which is the class  $AC^{0}$  with the addition of Mod m gates acting on any number of inputs. Second, the relation  $AC^{0}[p] \subset TC^{0}$  [21] (where p is a prime) between the classical classes does not hold for their quantum counterparts, where  $QTC^{0} \subseteq QAC^{0}[m]$  (for every m) [7, 22]. Here  $TC^{0}$  notes constant depth threshold circuits, *i.e.* circuits with unbounded threshold gates and  $QTC^{0}$  is its quantum counterpart where quantum threshold gates are used. Since in [7] it was also established that  $\mathsf{TC}^0 \subseteq \mathsf{QAC}[m]^0$ , these results show that the quantum parallel complexity classes  $\mathsf{QAC}^0[m]$  are strictly more powerful than their classical counterparts.

We present two new results in low depth quantum circuit complexity theory. These two results are a step towards proving the inequality of two quantum circuit classes:  $QAC^{0}$  and  $QAC^{0}[2]$ . Admittedly, the initial goal was to prove this inequality in this thesis, but this was not possible under the time constraints imposed by this PhD. The relation  $AC^{0} \neq AC^{0}[2]$  is known to hold for classical circuits [23]. The approach in proving that  $QAC^{0} \neq QAC^{0}[2]$  is to show that computing the parity of input qubits, possible in  $QAC^{0}[2]$ , cannot be done in  $QAC^{0}$ . It has already been shown that this is impossible exactly and cleanly if the number of auxiliary qubits in the circuit is less than the input size [8]. However, before this work nothing was known for the case when the number of auxiliary qubits is polynomial in the input size. First, we prove that QAC circuits with one multi-qubit gate layer cannot compute parity even probabilistically. Second, we show that when the number of multi-qubit gate layers is two, parity cannot be computed exactly and cleanly. During these two proofs, a number of properties for QAC circuits are discovered. These could be useful in proving the inequality of the QAC<sup>0</sup> and QAC<sup>0</sup>[2] classes.

There exist computational problems that exhibit more parallelism in the quantum than classical computing mode. This thesis expands the number of problems benefiting from quantum computers by introducing a new parallel quantum arithmetic circuit (Part I), while establishing boundaries through proving the equivalence of two parallelisation methods (Part II) and giving a new lower bound of the parity function (Part III). Part I

# Quantum Arithmetic Circuits

Quantum computing has the potential to dramatically change the nature of computing, but has mostly been a theoretical subject partly due to the difficulties in building physical quantum circuits. However, recent progress has enabled the first, albeit small, quantum devices to be constructed, for example utilising photonics [24]. These devices are not complete quantum computers, but consist of simple quantum circuits capable of processing information to solve specific problems. These devices can be made in silicon [24] which could lead to their integration with conventional microelectronics. How would such a hybrid of conventional and quantum microprocessor be used? Coprocessor architectures have been developed in the past but perhaps the most promising context would be to consider the quantum device as an accelerator.

There are several examples of modern heterogeneous computer architectures. For example, Graphical Processing Units (GPUs) have been used extensively in the field of scientific numerical computing to accelerate specific aspects of these calculations, where some suitably defined kernel, *i.e.* the core of the computation, is offloaded from the CPU and executed faster on the GPU. Another analogy can be drawn with field programmable gate arrays (FPGAs) where particular computational patterns in software can be instantiated in hardware using the reprogrammable logic of these devices, see for example [25, 26]. Rather than accelerating an entire kernel as would be required for a GPU, a quantum device could be employed to accelerate a specific computational pattern. Moreover, as this device would function as an accelerator, a complete quantum computer would not be required. Furthermore, the effects of quantum decoherence which destroys quantum information can be mitigated because such quantum circuits need only to be in an entangled state for a brief period compared to a full quantum computer.

The main result of this chapter is a quantum multiply-adder (QMAC) circuit, which could potentially be implemented as a quantum accelerator for classical computers. It is the first quantum multiply-adder design and, more importantly, the first quantum arithmetic circuit that has a smaller depth than its classical counterparts. This is achieved through the use of the Quantum Fourier Transform (QFT) and entangled quantum states combined with the ability to easily copy classical bits. This new quantum-classical hybrid circuit is presented in Chapter 2. A MAC is an important hardware module, *i.e.* electronic sub-circuit, in digital signal processors (DSPs), which are used, for example, in audio and video processing, encryption, pattern recognition, *etc* [27]. Since DSPs have a very wide area of application, improving the performance of MACs would be immensely useful. There exist two types of DSPs: fixed point and floating point DSPs. The integer QMAC introduced in this work can be adapted for fixed point arithmetics and could thus be used instead of classical MAC circuits in fixed point DSPs.

This part starts with a brief introduction to classical and quantum arithmetic circuits in Chapter 1 and contains some basic concepts and definitions referred to throughout this thesis (not just from Part I). After the introduction of the QMAC circuit in Chapter 2, the same techniques are applied in Chapter 3 to create a parallel quantum adder, corresponding to a highly parallel Draper adder [28]. Chapter 4 contains implementation optimisations applicable to both the QMAC and the new adder, followed by the discussion about the results and impact of the new arithmetic circuits in Chapter 5.

## Chapter 1

## Preliminaries

## **1.1 Classical Circuits**

The classical arithmetic circuits in this work are represented as Boolean circuits.

**Definition 1.1** (Boolean circuit [29]). A Boolean circuit is a directed graph with a set of source nodes called the inputs, and one or more sink nodes called the outputs. Each internal node, or "gate," is labelled AND, OR, NOT, and produces the corresponding function of its inputs. This graph is acyclic, meaning that there are no loops information flows in one direction from the inputs to the outputs.

In our work we also allow the use of the XOR gate in the Boolean circuits, since the gate set consisting of consisting of NOT, AND, OR, and XOR is the usual gate set used in the literature on arithmetic circuits. We use  $a \cdot b$  for representing the AND of two bits, a + b for the OR,  $a \oplus b$  for the XOR, and  $\neg$  for the NOT. The XOR an be replaced with two AND, one OR, and one NOT gate (Equation 1.1), thus the number of gates in our circuits is at most four times smaller than when using a gate set without the XOR.

$$a \oplus b = (a+b) \cdot \neg (a \cdot b) \tag{1.1}$$

Some estimates on the number of gates used in circuits require rounding of values. We use  $\lceil n \rceil$  to denote the value of n rounded up to the nearest integer and  $\lfloor n \rfloor$  the value of n rounded down to the nearest integer. The *fan-in* of a gate is its number of inputs [30]. Logic gates usually have a constant fan-in, *i.e.* they act on a fixed (usually small) number of bits. This number is often, as in this thesis, chosen to be 2. The *fan-out* of a circuit is the number of outputs a gate has [30]. This value is usually considered to

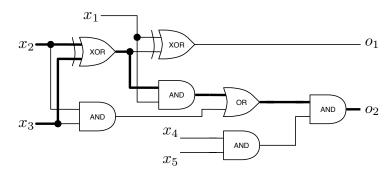

**Figure 1.1:** An example illustrating the concept of depth in Boolean circuits. The longest directed paths from inputs to outputs is highlighted in bold. In this example, there exist two longest paths (from  $x_2$  to  $o_2$  and from  $x_3$  to  $o_2$ ). The length of the path is the number of gates it passes through. In this circuit the longest path, and thus the depth, of this circuit is 4.

be unbounded, *i.e.* there can be any number of outputs. The main parameter we use in comparing parallelism in classical and quantum circuits is the *depth* of the circuit.

**Definition 1.2** (The depth of a Boolean circuit [31]). The depth of a Boolean circuit is the longest directed path from an input to the output.

An example illustrating the depth of a Boolean circuit is in Figure 1.1. Each circuit can only process inputs of a specific size, but often it is useful to estimate how the circuits' parameters like number of gates or depth depend on the input size. This can be done by using *circuit families*.

**Definition 1.3** (Circuit families [31]). Let  $T : \mathbb{N} \to \mathbb{N}$  be a function. A T(n)-size (depth) circuit family is a sequence  $\{C_n\}_{n\in\mathbb{N}}$  of Boolean circuits, where  $C_n$  has n inputs and a single output, and its (depth) size is  $|C_n| \leq T(n)$  for every n.

Throughout this thesis, if it is mentioned that there exists a O(n) depth (or size, etc.) circuit solving a problem, it is implicitly meant that there exists a family of O(n) depth (or size, etc.) circuits.

Obviously the time it takes to execute any circuit depends very much on the implementation but it is proportional to the depth of the circuit. In addition to the number of gates on the longest path, there are many other parameters that contribute to the execution time of a digital circuit: wiring, fan-out, *etc.* The depth is thus not the most accurate measure of performance, but it is an implementation independent way to compare the performance of various circuits. This is especially desirable when comparing classical circuits with quantum circuits, since there has not yet emerged a quantum architecture from where the execution times of different components could be taken. The classical arithmetic circuits presented here are often represented as digital circuits, where the term *delay* [30] is used instead of depth to represent the performance

of a circuit. There, each type of gate is assigned a fixed gate delay and the overall delay of the circuit is the longest delay from inputs to outputs. This work uses the simpler notion of depth, because it is the concept used in circuit complexity theory, which is the focus of Part III.

### 1.1.1 Numerical Representation

Although the arithmetic circuits presented in this thesis are shown to work for unsigned integers, they can be generalised to signed fixed point numbers. Unsigned integers are used since this simplifies the notation. The adaption to use signed fixed point numbers does not require any changes to the circuits as will be explained in the following sections. The concepts following can be found in most of the textbooks on digital signal processing or on computer arithmetic circuits [27, 30, 32, 33].

### **Fixed Point Representation**

There are two main representations for real numbers in digital circits: the *floating* point and the *fixed point* representations [27, 30, 32, 33]. This thesis uses the fixed point representation since it is not clear if and how the new arithmetic circuits designed in the later chapters can be adapted to floating point representation. Although the floating point representation has superior precision and ease of use when programming, the fixed point system is still widely used. The main advantages of fixed point arithmetic circuits are its simple and cost efficient implementation and performance compared to the floating point systems. When large value ranges are not needed, fixed point representation is often suitable and provides a speed-up over floating points [30]. Thus, many Digital Signal Processors (DSPs) still use fixed point systems (for example the Texas Instruments TMS320C64xx [34] and the Analog Devices Blackfin [35] DSP families).

In this work the binary representation of integers is used. In a conventional number system every k-digit number x can be written as [30, 32]

$$\sum_{i=1}^{k} w_i x_i,\tag{1.2}$$

where  $x_i$  is the *i*-th digit of x and  $w_i$  is the weight associated with the digit. In the binary system  $w_i$  is always a power of two and  $x_i \in \{0, 1\}$ . Generally, a number can have both an integer and a fractional part. In the fixed point system this can be

achieved by interpreting the *m* rightmost digits as the integer part and k - m leftmost digits as the fractional part. These two parts are separated by the radix point (.). For example in the number  $z_9z_8z_7z_6z_5.z_4z_3z_2z_1$  the 4 rightmost digits comprise the fractional part and the digits  $z_5$  to  $z_9$  make up the integer part. In general the fixed point representation of a *k* digit number *z* with an *m*-digit fractional part is written as  $z_k \cdots z_{m-2}z_{m-1}.z_m \cdots z_2z_1$ . The weights of the bits in the integer part are always non-negative powers of two and the weights of the fractional parts are negative powers of two. The value of a *k*-bit fixed point number with *m* bit fractional part is therefore

$$\sum_{i=1}^{k} 2^{i-1-m} x_i. \tag{1.3}$$

As an example, the binary number  $z_9 z_8 z_7 z_6 z_5 . z_4 z_3 z_2 z_1$  can be written as

$$z_92^4 + z_82^3 + z_72^2 + z_62^1 + z_52^0 + z_42^{-1} + z_32^{-2} + z_22^{-3} + z_12^{-4}.$$

(1.4)

The fixed point numbers are stored as integers, with the position of the radix point stored separately. To add or subtract two fixed point integers with the radix point at the same position, it is enough to add or subtract the underlying integers and keep the radix point at the same location. To multiply two fixed point integers with the radix point at the same position, the underlying integers can be multiplied together and the radix point will be positioned to twice as many digits from the right as it was before. This way it is also easy to obtain the new fixed point value with the radix point at the same position as the multiplicands: namely the last digits can be just discarded or not even computed. This allows us to use the arithmetic circuits presented in this thesis on integers without having to consider whether the integers represent fixed point numbers or not. The downside of using the fixed point representation is the loss of precision. Namely, when multiplying two fixed-point numbers, the result can have as many bits as the sum of the number of bits in the multiplicands. To fit the result in a fixed size register of the size of the inputs, some of the bits might have to be be discarded. In the worst case, half of the bits need to be discarded resulting in a significant loss of precision.

### **Two's Complement Representation**

It is possible to perform arithmetic operations on signed integers (and thus also on signed fixed point values as explained in the previous section) as if they were all positive and just interpret the numbers as having a sign. This greatly simplifies the implementation of digital arithmetic circuits by eliminating the need for considering signs independently. One way of achieving this is to use the two's complement representation, which is also the most common representation for signed integers in modern computers. In two's complement representation, the negative number is represented by [30]:

- 1. taking the binary representation of its positive counterpart,

- 2. flipping the bits of the positive counterpart,

- 3. adding one to the result.

For example the two's complement representation of a six bit number -13:

- 1. the binary representation of 13 is 001101,

- 2. flipping these bits results in 110010,

- 3. and finally, adding 1 to it gives the two's complement representation of -13: 110011.

The sign of integers in the two's complement representation is determined by the leftmost bit: 0 for unsigned and 1 for signed. Adding negative numbers in this representation does not require any overhead and subtraction can be performed by adding the two's complement of the positive number. An example showing how adding a negative number results in a correct answer is shown in Figure 1.2. Multiplication

| 1 | 1 | 0 | 1 | 1 | 0 |   | (carry) |

|---|---|---|---|---|---|---|---------|

|   | 0 | 1 | 0 | 1 | 1 | 0 | (22)    |

| + | 1 | 1 | 0 | 0 | 1 | 1 | (-13)   |

|   | 0 | 0 | 1 | 0 | 0 | 1 | (9)     |

Figure 1.2: Adding a negative number in the two's complement representation using columnar addition. The values in the carry row correspond to the carry from the added bits in the previous column, *i.e.* the carry bit is 0 if the sum of the previous column above the line is 01 or 00, and 1 if the sum is 10 or 11.

works similarly, with the additional constraint that the result must fit in the number of bits available, but this needs to be considered even when regular binary representation is used. The intermediate results need only to hold as many bits as is in the result, the rest can be discarded. An example of how multiplication in two's complement notation works is presented in Figure 1.3 as noted by d in the example below:

Thus addition and multiplication of signed two's complement numbers can be done using exactly the same method as for unsigned integers. Therefore, although unsigned

|   | 0 | 0 | 0 | 0 | 1 | 1 | (3)   |

|---|---|---|---|---|---|---|-------|

| × | 1 | 1 | 1 | 0 | 1 | 1 | (-5)  |

|   | 0 | 0 | 0 | 0 | 1 | 1 |       |

|   | 0 | 0 | 0 | 1 | 1 | 0 |       |

|   | 0 | 0 | 0 | 0 | 0 | 0 |       |

|   | 0 | 1 | 1 | 0 | 0 | 0 |       |

|   | 1 | 1 | 0 | 0 | 0 | 0 |       |

| d | 1 | 0 | 0 | 0 | 0 | 0 |       |

| d | 1 | 1 | 0 | 0 | 0 | 1 | (-15) |

**Figure 1.3:** Multiplying two integers in the two's complement representation. The multiplication is done in two stages. First, the partial products are found by multiplying each bit in the multiplier (-5) with the multiplicand (3). In the second stage, the partial products are summed together. Here the result should be a 6-bit number, hence the 7th (leftmost) bit is discarded.

integers are used in this thesis, the circuits would work for signed numbers in two's complement representation.

## **1.2 Quantum Circuits**

We assume that the reader of this thesis is familiar with the basics of quantum computing. A good overview can be found in the textbooks of Nielsen and Chuang [36], and Kaye, Laflamme and Mosca [37]. Nevertheless, we provide a very brief introduction to quantum circuits and highlight some of the definitions, concepts, terms and techniques most often used in this thesis. We also give the four postulates of quantum mechanics which define the underlying the mathematical framework required for this thesis.

The analogue of the classical bit in quantum computing is the *qubit*. A qubit corresponds to a two-dimensional quantum mechanical system.

**Postulate 1.1** (State Space Postulate [37]). The state of a quantum system is described by a unit vector in a Hilbert space  $\mathcal{H}$ .

We can choose an orthonormal basis in the two-dimensional Hilbert space and label the basis vectors as  $|0\rangle$  and  $|1\rangle$ . Then the general state of a qubit is:

$$\alpha|0\rangle + \beta|1\rangle,\tag{1.5}$$

where  $\alpha$  and  $\beta$  are complex coefficients and  $|\alpha|^2 + |\beta|^2 = 1$ . The  $\{|0\rangle, |1\rangle\}$  basis for the state of a qubit is called the *computational basis*. Physical systems can be combined

to form a larger *composite system*, the following postulate explains how these systems can be described.

**Postulate 1.2** (Composition of Systems Postulate [36]). The state space of a composite physical system is the tensor product of the component physical systems. Moreover, if we have systems numbered from i through n and the system number i is prepared in the stat  $|\psi_i\rangle$ , then the joint state of the total system is  $|\psi_1\rangle \otimes |\psi_2\rangle \otimes \cdots \otimes |\psi_n\rangle$ .

As a shorthand the tensor product  $|\psi_1\rangle \otimes |\psi_2\rangle \otimes \cdots \otimes |\psi_n\rangle$  is commonly written as  $|\psi_1\psi_2\rangle \cdots |\psi_n\rangle$ , where  $\psi_i \in \{0, 1\}$ . An *n*-qubit state is thus a unit vector in the *n*-fold tensor product space  $\mathcal{H}_1 \otimes \mathcal{H}_2 \otimes \cdots \otimes \mathcal{H}_n$ . The  $2^n$  basis states of this space are the *n*-fold tensor products of the states  $|0\rangle$  and  $|1\rangle$ . With these basis states, a *n*-qubit state  $|\phi\rangle$  is a  $2^n$  dimensional complex unit vector

$$|\phi\rangle = \sum_{i \in \{0,1\}^n} \alpha_i |i\rangle.$$

(1.6)

Not all multi-qubit states can be written as tensor products of their components, the ones that cannot be represented as products are *entangled states*.

**Definition 1.4** (Entangled states [36]). A multi-qubit state is entangled if it cannot be written as a product of its component states.

A quantum system whose state is known exactly is said to be in a *pure state*, otherwise the system is said to be in a *mixed state*. A mixed state is described by a *density operator*:

$$\rho = \sum_{i} p_{i} |\psi_{i}\rangle \langle\psi_{i}|, \qquad (1.7)$$

where  $p_i$  is the probability that the system is in the pure state  $|\psi_i\rangle$ . The density operator of a pure state  $|\psi\rangle$  is defined as

$$\rho = |\psi\rangle\langle\psi|. \tag{1.8}$$

To be able to perform computations with qubits, we need to be able to change their state. The following postulate describes, how the state of qubits changes over time.

**Postulate 1.3** (Evolution Postulate [37]). The time-evolution of a closed quantum system is described by a unitary operator. That is, for any evolution of the closed system there exists a unitary operator U such that if the initial state of the system is

$|\psi\rangle$ , then after the evolution the state of the system will be

$$|\psi'\rangle = U|\psi\rangle. \tag{1.9}$$

Thus one way to change the state of a quantum state is to apply a unitary operator to it. Another operation that can change the state of qubits is the measurement, which also gives us the way to observe quantum systems.

**Postulate 1.4** (Measurement Postulate [36]). Quantum measurements are described by a collection  $\{M_m\}$  of measurement operators. These are operators acting on the state space of the system being measured. The index m refers to the measurement outcomes that may result in the experiment. If the state space of the system is  $|\psi\rangle$  immediately before the measurement, then the probability that result m occurs is given by

$$p(m) = \langle \psi | M_m^{\dagger} M_m | \psi \rangle, \qquad (1.10)$$

and the state of the system after the measurement is

$$\frac{M_m |\psi\rangle}{\sqrt{\langle \psi | M_m^{\dagger} M_m |\psi\rangle}}.$$

(1.11)

The measurement operators satisfy the completeness equation,

$$\sum_{m} M_m^{\dagger} M_m = I. \tag{1.12}$$

An important measurement, used in this thesis, is the computational basis measurement, defined by measurement operators  $M_0 = |0\rangle\langle 0|$ ,  $M_1 = |1\rangle\langle 1|$ . It is easy to see, that performing a computational basis measurement on a general quantum state  $\alpha|0\rangle + \beta|1\rangle$  results in 0 with probability  $|\alpha|^2$  and in 1 with probability  $|\beta|^2$ . All measurements in this work are computational basis measurements unless they are explicitly defined.

In the quantum circuit model the qubits are represented as horizontal *wires* and the unitary operators are represented as *gates* acting on a number of wires [37]. A generic quantum circuit can be seen in Figure 1.4. Unless explicitly stated, the circuits used in this thesis are only allowed to contain one and two qubit gates. Computations represented by quantum circuits are executed by applying quantum gates from left to right until all the gates have been applied. Due to the following principle, all the quantum wires at the end of the computation will be assumed to be measured in this

thesis.

**Principle 1.1** (Principle of implicit measurement [36]). Without loss of generality, any unterminated quantum wires (qubits which are not measured) at the end of a quantum circuit may be assumed to be measured.

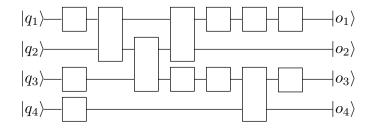

**Figure 1.4:** A generic quantum circuit. Each horizontal line represents a "wire". Each wire represents a qubit in the computation performed by the quantum circuit.  $|q_1\rangle$ ,  $|q_2\rangle$ ,  $|q_3\rangle$ , and  $|q_4\rangle$  are the initial states of the qubits represented by the wires.  $|o_1\rangle$ ,  $|o_2\rangle$ ,  $|o_3\rangle$ ,  $|o_4\rangle$  are the output states of those qubits. The rectangles on the wires represent quantum gates. Gates can be applied to any number of wires.

Assume that applying a gate to the qubits in the circuit takes one discrete time step, and that gates acting on distinct qubits can be applied in parallel. Then we can divide quantum circuits to a number of layers, so that executing each layer takes exactly one time step. This allows us to define the central concept thesis: the *depth* of a quantum circuit. The definition used throughout this work is adapted from [4] by removing the restriction on using only one and two qubit gates, thereby allowing to compute the depth of circuits containing unbounded gates in Part III.

**Definition 1.5** (Quantum circuit depth, adapted from [4]). A one layer circuit is a unitary operator consisting of a tensor product of gates where each gate couples a disjoint set of gates. A quantum circuit of depth d is a unitary operator written as a product of d one layer circuits.

An example of how the depth of a circuit can be found is shown in Figure 1.5. Parallel circuit complexity teory uses asymptotic complexity of the circuit depth, instead of execution time to compare algorithms. Rather than comparing exact execution times, the number of parallel steps required to finish the computation is used. This simplification allows to compare algorithms without the need to consider the underlying architecture (by architecture we mean the technology used to implement the quantum gates, *i.e.* photonics, ion traps, *etc.*). As long as the execution time of a quantum gate does not depend on the input size, the exact execution time will differ by at most a constant factor from the depth of the circuit. Note that although the asymptotic circuit depth does not depend on the architecture, it depends on the computational model, *i.e.* whether the computation is represented in the adiabatic, circuit, 1WQC, or any other

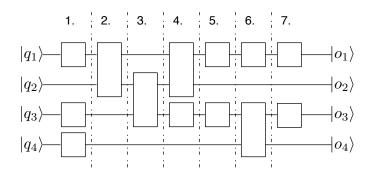

Figure 1.5: An example of how the depth of a quantum circuit can be calculated by dividing the circuit into layers. The depth of this particular circuit is 7.

model. This dependency on the model is due to translating an algorithm to a different models, which can change the depth of the computation. For example, it is known how to translate computations from circuit model to 1WQC without increasing the depth [10], but it is not know how to perform the opposite depth preserving translation in the general case (see Part II for more detailed description of depth in 1WQC).

Often, instead of computing the depth of a single circuit, a uniform family of quantum circuits is used to estimate a it function of the number of input qubits. The definition is very similar to the definition of Boolean circuit families in Definition 1.3.

**Definition 1.6** (Quantum circuit families [6]). A quantum circuit family is a sequence  $\{C_n\}_{n\in\mathbb{N}}$  of quantum circuits, where each  $C_n$  has n inputs. We say that  $\{C_n\}$  is uniform if there is a classical polynomial-time algorithm that outputs  $C_n$  on input  $0^n$ .

For example, if we say that a quantum circuit has logarithmic depth, then we mean that the number of discrete time steps it takes to evaluate the circuit increases logarithmically corresponding to the problem size, and the depth of the circuit is  $O(\log n)$ .

Implementing a specific quantum circuit exactly is not always possible with a finite set of gates. It not necessary in practice to compute a circuit exactly, it is enough to *approximate* it to some specific accuracy.

**Definition 1.7** (Approximate unitary operators). A unitary operator V approximates another unitary operator U with with error E(U, V), if

$$E(U, V) = \max ||(U - V)|\psi\rangle||.$$

(1.13)

An operator U can be approximated to arbitrary precision if for every  $\epsilon > 0$  there exists another unitary V such that  $E(U, V) < \epsilon$ .

| The gate name                     | The gate symbol and its unitary matrix                                                                                      | Symbol used in<br>quantum circuits |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| The identity gate                 | $I = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$                                                                          |                                    |

| The Pauli X gate                  | $X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$                                                                          | X                                  |

| The Pauli Y gate                  | $Y = \begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix}$                                                                         | Y                                  |

| The Pauli Z gate                  | $Z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$                                                                         | Z                                  |

| The arbitrary phase rotation gate | $Z(lpha) = egin{pmatrix} 1 & 0 \ 0 & e^{ilpha} \end{pmatrix}$                                                               | $Z(\alpha)$                        |

| The phase rotation gate           | $P = \begin{pmatrix} 1 & 0 \\ 0 & i \end{pmatrix}$                                                                          | P                                  |

| The Hadamard gate                 | $H = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 1\\ 1 & -1 \end{pmatrix}$                                                       | <i>H</i>                           |

| The J gate                        | $J(\alpha) = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & e^{i\alpha} \\ 1 & -e^{i\alpha} \end{pmatrix}$                          | $J(\alpha)$                        |

| The square root of NOT gate       | $V = \frac{1+i}{2} \begin{pmatrix} 1 & -i \\ -i & 1 \end{pmatrix}$                                                          | V                                  |

| The CNOT gate                     | $CNOT = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix}$                     |                                    |

| The control-Z gate                | $\wedge Z = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & -1 \end{pmatrix}$                |                                    |

| The control-phase gate            | $R_n = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & e^{\frac{2\pi i}{2^n}} \end{pmatrix}$ |                                    |

Figure 1.6: Some of the most common one and two-qubit quantum gates.

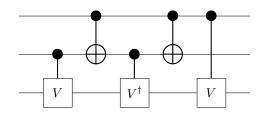

Every computation realisable by quantum circuits can be implemented approximately by using only a small set of different gates. We call such set a *universal* set of gates. **Definition 1.8** (Universal set of gates [37]). A set of gates is said to be universal, if for any integer  $n \ge 1$ , any n-qubit unitary operator can be approximated to arbitrary accuracy by a quantum circuit using gates from that set.

Some of the most common one and two-qubit quantum gates are presented in Figure 1.6. Most of the gates used in this work are present in this figure. The remaining gates are either introduced immediately before they are used or are defined in Section 1.2.1. The gates in Figure 1.6 can be used to create multiple distinct universal sets of gates, for example  $\{Z(\frac{\pi}{8}), H, CNOT\}$  [36] and  $\{J(\frac{\pi}{8}), H, \wedge Z\}$  [38].

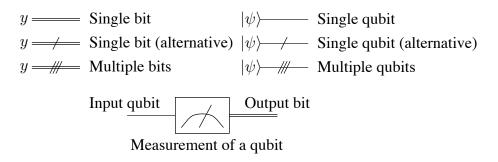

Many of the circuits presented in this work are *hybrid circuits*, *i.e.* circuits which contain both classical and quantum bits and gates. Sometimes we also need to represent multiple qubits or bits compactly in the figure. The notation used to display all this information is shown in Figure 1.7.

Figure 1.7: The notation used to distinguish between qubits and bits and multiple instances of them. Double lines for bits are only used when there is the possibility ambiguity in the figures, otherwise single lines are used for both bits and qubits. Likewise, the alternative single qubit lines with a single dash are used to avoid confusion over whether multiple qubits or a single qubit is meant.

Given a 1-qubit quantum gate U, the corresponding 2-qubit *controlled-U* gate, denoted as  $\wedge U$ , performs the following operation [36, 37]:

$$\wedge U|0\rangle|\psi\rangle = |0\rangle|\psi\rangle, \tag{1.14}$$

$$\wedge U|1\rangle|\psi\rangle = |1\rangle U|\psi\rangle. \tag{1.15}$$

The qubit that controls the application of U is called the *control qubit* and the qubit on which U acts is called the *target qubit*. It is possible to replace a controlled quantum gate at the end of a quantum circuit with a measurement of the control qubit in the computational basis followed by the application of U to the target qubit if and only if the measurement outcome is  $|1\rangle$  [36, 37]. This is due to the principle of deferred measurement. **Principle 1.2** (Principle of deferred measurement [36]). Measurements can always be moved from an intermediate stage of a quantum circuit to the end of the circuit. If the measurement results are used at any stage of the circuit then the classically controlled operations can be replaced by conditional quantum operations.

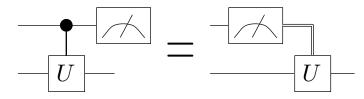

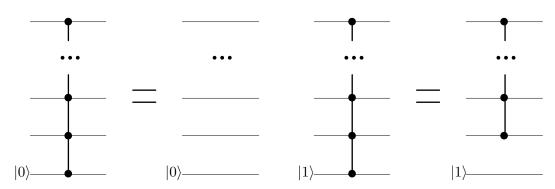

The principle of deferred measurement is illustrated in Figure 1.8. This useful property of controlled gates is used in Chapter 4 to reduce the number of two-qubit gates in our quantum multiply adder circuit and in Chapter 12 to analyse the probabilities of the target qubit being modified.

Figure 1.8: A controlled U gate at the end of a circuit can be replaced with a measurement and a single-qubit gate.

The following trivial lemma is included since it is often used in both Part I and III of this thesis.

**Lemma 1.1.** Quantum gates commuting with the measurement of the output qubit can be removed from the circuit without affecting the measurement outcome of output qubit.

*Proof.* Let U be any quantum gate commuting with the measurement of the output qubit o. Since U commutes with the measurement of o we can measure o and then apply U. Obviously the application of U cannot influence the already measured value, hence we can remove it from the circuit without affecting the measurement outcome on o.

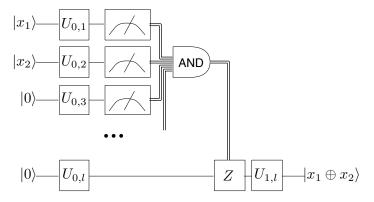

### 1.2.1 Unbounded Quantum Gates

In some instances gates that act on an unlimited number of qubits are used, these quantum gates are called *unbounded quantum gates*.

**Definition 1.9** (Unbounded quantum gates). A quantum gate U is unbounded if it can act on unlimited number of qubits.

Unbounded quantum gates are used in quantum circuit complexity (See Part III) where adding an unbounded gate to the set of gates allowed in a circuit can increase the number of solvable problems in a complexity class. The unbounded quantum gates are also used in regular quantum circuits as a shorthand to denote their decomposition to two-qubit and single-qubit gates, *i.e.* instead of writing out the full decomposition the symbol of an unbounded gate is used. In what follows, the definitions of the unbounded quantum gates used throughout this thesis are given.

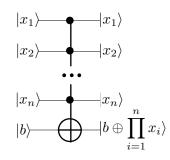

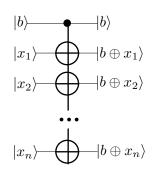

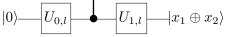

**Definition 1.10** (The unbounded Toffoli gate [8]). The unbounded Toffoli gate T is the unitary operator implementing the following map

$$T|x_1, x_2, \dots, x_n, b\rangle = |x_1, x_2, \dots, x_n, b \oplus \prod_{i=1}^n x_i\rangle.$$

(1.16)

The symbol representing the unbounded Toffoli gates in quantum circuits is shown in Figure 1.11(a).

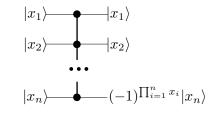

**Definition 1.11** (The unbounded  $\wedge Z$  gate [8]). The unbounded  $\wedge Z$  (controlled-Z) gate is the unitary operator implementing the following map

$$\wedge Z|x_1, x_2, \dots, x_n\rangle = (-1)^{\prod_{i=1}^n x_i} |x_1, x_2, \dots, x_n\rangle.$$

(1.17)

The symbol representing the unbounded  $\wedge Z$  gates in quantum circuits is shown in Figure 1.11(b).

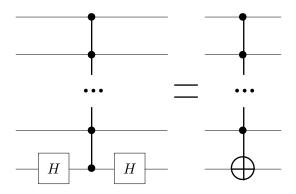

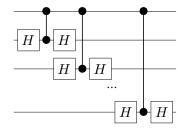

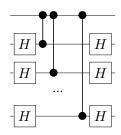

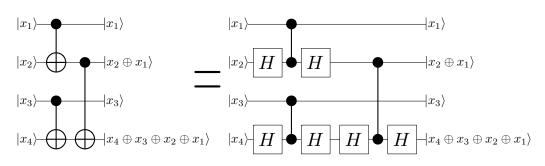

The unbounded Toffoli gates can be turned into  $\wedge Z$  gates by applying Hadamard gates to to the target bit of the Toffoli gate [8] as is shown in Figure 1.9.

Figure 1.9: The  $\wedge Z$  gate can be turned to a Toffoli gate with two Hadamard gates and vice versa [8].

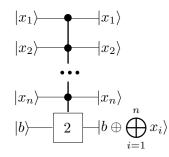

**Definition 1.12** (The unbounded fan-out gate [8]). The unbounded fan-out gate F is the unitary operator implementing the following map

$$F|b, x_1, x_2, \dots, x_n\rangle = |b \oplus x_1, b \oplus x_2, \dots, b \oplus x_n\rangle.$$

(1.18)

The symbol representing the unbounded fan-out gates in quantum circuits is shown in

Figure 1.11(c).

**Definition 1.13** (The unbounded parity gate [8]). The unbounded parity gate P is the unitary operator implementing the following map

$$P|x_1, x_2, \dots, x_n\rangle = |x_1, x_2, \dots, x_n, b \oplus \bigoplus_{i=1}^n x_i\rangle.$$

$$(1.19)$$

The symbol representing the unbounded parity gates in quantum circuits is shown in Figure 1.11(d).

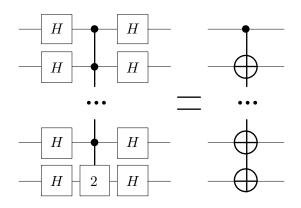

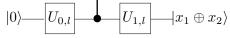

The unbounded parity gate can be turned into an unbounded fan-out gate via layers of Hadamard gates before and after the gate [5] as is shown in Figure 1.10.

Figure 1.10: The parity gate can be turned to a fan-out gate with two Hadamard layers and vice versa [5].

The quantum  $MOD_q$  gate is a generalisation of the unbounded quantum parity gate.

**Definition 1.14** (The unbounded  $MOD_q$  gate [5]). The unbounded  $MOD_q$  gate is the unitary operator implementing the following map

$$MOD_q|x_1, x_2, \dots, x_n\rangle = |x_1, x_2, \dots, x_n, b \oplus Mod_q(x_1, x_2, \dots, x_n)\rangle,$$

(1.20)

where  $Mod_q(x_1, x_2, \ldots, x_n) = 1$  if and only if  $\sum_{i=1}^n x_i \not\equiv 0 \mod q$ .

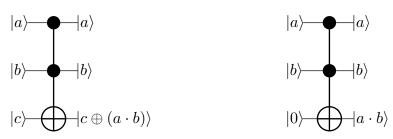

### 1.2.2 Translating Boolean circuits to quantum circuits

Boolean circuits can be translated to quantum circuits on a gate-by-gate basis. This can be done by replacing the Boolean gates with quantum gates, which on computational basis input will output a single qubit computational basis state corresponding to the

(a) The unbounded Toffoli gate

(c) The unbounded fan-out gate

(b) The unbounded  $\wedge Z$  gate. The phase change resulting by the application of the  $\wedge Z$  gate can be written before any of the *n* qubits, since it is not associated with any particular qubit but with the state  $|11\cdots 1\rangle$ .

(d) The unbounded Parity gate

Figure 1.11: The four unbounded gates used in this thesis.

output of the Boolean gate. First, the NOT gate is translated to a Pauli X gate since:

$$X|0\rangle = |1\rangle \tag{1.21}$$

$$X|1\rangle = |0\rangle \tag{1.22}$$

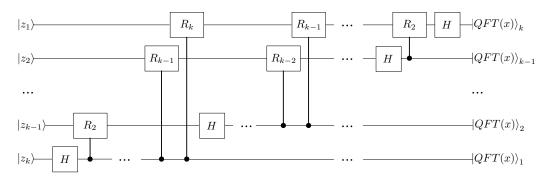

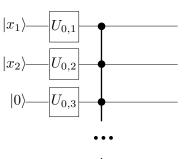

Second, the AND gate is replaced with a Toffoli gate and the input to the target bit is fixed to  $|0\rangle$  as shown in Figure 1.12(b). Third, the OR gate is replaced with one Toffoli and four Pauli X gates as shown in Figure 1.12(c). Finally, we must consider the fanout in classical circuits. Since copying of qubits is not possible in general [36], this is not a trivial operation as in Boolean circuits. Note that the intermediate states of a gate by gate translation of a Boolean circuit will be computational basis states if the input is a computational basis state, *i.e.* the input to the quantum circuit correspond to classical bit-strings. It is possible to copy the value of qubits if they are in a computational basis state, which is the case of a translation from Boolean circuits. Namely, the unbounded fan-out-gate (Definition 1.12 and Figure 1.11(c)) copies the state of the control qubit (b in Figure 1.11(c)) to target qubits ( $x_1$  to  $x_n$  in Figure 1.11(c)) if they are initialised to  $|0\rangle$  [5]. Thus, every Boolean circuit has a corresponding quantum circuit. The unbounded fan-out gates can be removed from the quantum translation of a Boolean

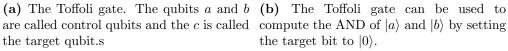

the target qubit.s

$\mathbf{S}$

(c) Using Pauli X gates and the De Morgan's laws the Toffoli gate can be used to compute the OR gate.

Figure 1.12: Using the Toffoli gate to replace classical Boolean gates.

circuit by replacing them with  $O(\log n)$  depth sub-circuits (where n is the number of qubits the unbounded gate acts on) consisting of two-qubit CONT gates [4].

#### 1.2.3The Quantum Fourier Transform

The quantum Fourier transform (QFT) is the quantum analogue of the discrete Fourier transform (DFT) algorithm. For a given dimension n, the DFT is a linear function mapping the vector  $(a_0, a_1, \ldots, a_{N-1})$  in  $\mathbb{C}^N$  to the vector  $(b_0, b_1, \ldots, b_{N-1})$ , where

$$b_x = \frac{1}{\sqrt{N}} \sum_{y=0}^{N-1} e^{\frac{2\pi i x y}{N}} a_y.$$

(1.23)

Let  $\{|0\rangle, |1\rangle, \ldots, |N-1\rangle\}$  be an orthonormal basis of  $\mathcal{H}^{\otimes 2^n}$ . QFT is the unitary operator that maps the *n* qubit quantum state  $\sum_{x=0}^{2^n-1} a_x |x\rangle$  to the state  $\sum_{x=0}^{2^n-1} b_x |x\rangle$ , where the amplitudes  $b_x$  are the DFT values from equation 1.23. The QFT of a k-qubit computational basis state  $|z\rangle$  has the following useful representation [36]:

$$QFT|z\rangle = \frac{1}{\sqrt{2}}(|0\rangle + e^{2\pi i 0.z_1}|1\rangle)$$

$$\otimes \frac{1}{\sqrt{2}}(|0\rangle + e^{2\pi i 0.z_2 z_1}|1\rangle)$$

$$\otimes \cdots$$

$$\otimes \frac{1}{\sqrt{2}}(|0\rangle + e^{2\pi i 0.z_k \cdots z_2 z_1}|1\rangle).$$

(1.24)

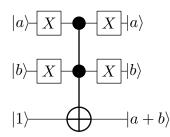

The circuit computing the QFT is given in Figure 1.13. Throughout this thesis we use the following notation for the individual qubits in the quantum state resulting from the application of QFT on a computational basis state:

$$|QFT(z)\rangle_b = \frac{1}{\sqrt{2}} \left( |0\rangle + e^{2\pi i 0.z_b \cdots z_2 z_1} |1\rangle \right).$$

(1.25)

The QFT in Figure 1.13 will be used as a sub-circuit in the quantum arithmetic circuits,

Figure 1.13: The quantum circuit computing the QFT of up to a permutation of the output qubits, *i.e.* the output qubits need to be rearranged by reversing their order. This circuit is the QFT circuit presented in textbooks [36, 37] and has O(k) depth [12], which is conjectured to be the best possible depth for the exact QFT [4]

thus the parameters of the circuit are given in the following lemma:

**Lemma 1.2.** The QFT of k qubits in Figure 1.13 requires k qubits, k single-qubit gates, and  $(k^2 - k)/2$  two qubit gates.

*Proof.* The circuit acts only on the input qubits, without requiring any auxiliary qubits; hence the number of qubits needed is k. The only single-qubit gates are the Hadamard gates, of which there is exactly one applied to each qubit; thus the number of one qubit gates is k. It can be seen from Figure 1.13 that every qubit  $z_i$  is the control qubit for exactly i - 1 two qubit controlled  $R_j$  gates. Thus the total number of two qubit gates

$$\sum_{i=1}^{k} i - 1 = k(k-1)/2 = (k^2 - k)/2.$$

(1.26)

As a summary, the parameters of the circuit in Figure 1.13 are following:

- **Depth**: 2k 1 [12] (Conjectured to be the best depth for the exact QFT [4]),

- Qubits required: k (Lemma 1.2),

- Single-qubit gates: k (Lemma 1.2),

- Two qubit gates:  $(k^2 k)/2$  (Lemma 1.2),

- Total gates:  $k + (k^2 k)/2 = (k^2 + k)/2$ .