# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

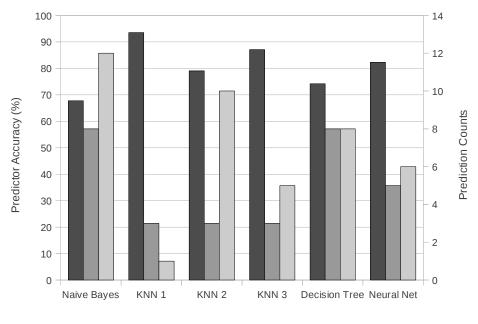

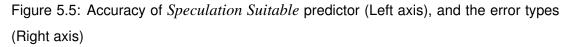

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Lightweight Speculative Support for Aggressive Auto-Parallelisation Tools

Daniel C. Powell

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh

2015

## Abstract

With the recent move to multi-core architectures it has become important to create the means to exploit the performance made available to us by these architectures. Unfortunately parallel programming is often a difficult and time-intensive process, even to expert programmers. Auto-parallelisation tools have aimed to fill the performance gap this has created, but static analysis commonly employed by such tools are unable to provide the performance improvements required due to lack of information at compile-time. More recent aggressive parallelisation tools use profiled-execution to discover new parallel opportunities, but these tools are inherently unsafe. They require either manual confirmation that their changes are safe, completely ruling out autoparallelisation, or they rely upon speculative execution such as software thread-level speculation (Sw-TLS) to confirm safe execution at runtime.

Sw-TLS schemes are currently very heavyweight and often fail to provide speedups for a program. Performance gains are dependent upon suitable parallel opportunities, correct selection and configuration, and appropriate execution platforms. Little research has been completed into the automated implemention of Sw-TLS programs.

This thesis presents an automated, machine-learning based technique to select and configure suitable speculation schemes when appropriate. This is performed by extracting metrics from potential parallel opportunities and using them to determine if a loop is suitable for speculative execution and if so, which speculation policy should be used. An extensive evaluation of this technique is presented, verifying that Sw-TLS configuration can indeed be automated and provide reliable performance gains. This work has shown that on an 8-core machine, up to  $7.75 \times$  and a geometric mean of  $1.64 \times$ speedups can be obtained through automatic configuration, providing on average 74% of the speedup obtainable through manual configuration.

Beyond automated configuration, this thesis explores the idea that many SW-TLS schemes focus too heavily on recovery from detecting a dependence violation. Doing so often results in worse than sequential performance for many real-world applications, therefore this work hypothesises that for many highly-likely parallel candidates, discovered through aggressive parallelisation techniques, would benefit from a simple dependence check without the ability to roll back. Dependence violations become extremely expensive in this scenario, however this would be incredibly rare. With a thorough evaluation of the technique this thesis confirms the hypothesis whilst achieving speedups of up to  $22.53 \times$ , and a geometric mean of  $2.16 \times$  on a 32-core machine. In a competitive scheduling scenario performance loss can be restricted to at least sequential speeds, even when a dependence has been detected.

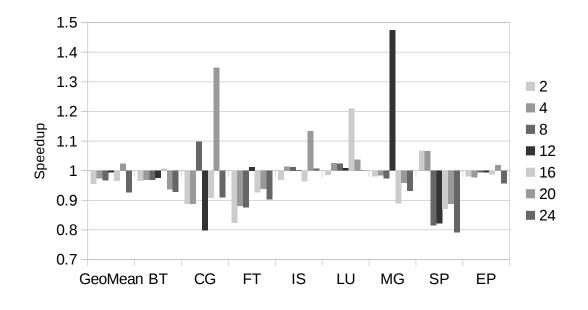

As a means to lower costs further this thesis explores other platforms to aid in the execution of speculative error checking. Introduced is the use of a GPU to offload some of the costs to during execution that confirms that using an auxiliary device is a legitimate means to obtain further speedup. Evaluation demonstrates that doing so can achieve up to  $14.74 \times$  and a geometric mean of  $1.99 \times$  speedup on a 12-core hyperthreaded machine. Compared to standard CPU-only techniques this performs slightly slower with a geometric mean of  $0.96 \times$  speedup, however this is likely to improve with upcoming GPU designs.

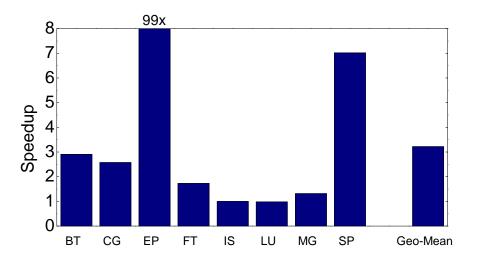

With the knowledge that GPU's can be used to reduce speculation costs, this thesis also investigates their use to speculatively improve execution times also. Presented is a novel SW-TLS scheme that targets GPU-based execution for use with aggressive auto-parallelisers. This scheme is executed using a competitive scheduling model, ensuring performance is no lower than sequential execution, whilst being able to provide speedups of up to  $99 \times$  and on average  $3.2 \times$  over sequential. On average this technique outperformed static analysis alone by a factor of  $7 \times$  and achieved approximately 99% of the speedup obtained from manual parallel implementations and outperformed the state-of-the-art in GPU SW-TLS by a factor of 1.45.

## Lay Summary

Recent trends in computer design have more towards using multiple processors inside a single computer. These processors have the ability to perform several tasks at once, in parallel, allowing for an overall increase in the number of tasks they are able to complete in a set amount of time. Taking advantage of this is, however, a complex and time intensive process, even for experienced programmers. The problem is that when you perform multiple tasks at once, each task may interfere with each other, potentially causing errors to occur.

Instead of having programmers create tasks that don't conflict, there has been a lot of research into automatically converting tasks such that they can be performed in parallel, however these methods are not very good at doing so. Some automated methods are more aggressive and instead predict when tasks can run in parallel without conflicting, performing much better than the non-aggressive methods, however their predictions are not always correct. When they are not correct errors can occur. A new way of running tasks in parallel is to take the tasks suggested by the aggressive means and run them in parallel anyway, instead keeping track of what every task is doing. This is called running them speculatively. If two tasks interfere with each other, they are stopped, the changes they have made a undone and the tasks are allowed to continue one by one, ensuring that they don't interact with each other. These methods work relatively well, but when tasks interact they often end up taking longer overall to be performed than if they were simply run one after the other in the first place. Also, sometimes the checking to ensure that they do not interact also takes longer.

This thesis investigates ways to automatically determine whether it will be faster to run multiple tasks speculatively, or to just run them one after another. If it will be faster to run them speculatively then this thesis also presents a method to automatically determine which way to ensure two tasks haven't interacted will be the fastest.

Further to that this thesis hypothesises that some aggressive methods are very good at detecting which tasks can be ran safely in parallel, and instead of using a speculation technique that focuses on very quick recovery if they do interact, instead focuses on running each task as fast as possible, possibly with the aid of extra processing devices. This becomes extremely costly when two tasks do interact, effectively

meaning they have to be restarted entirely, but that is extremely rare.

Finally there are different types of processors in existence, standard style processors found in every computer, and customised ones that used to be used solely for displaying items on a computer screen. These customised processors have been found to be very quick at performing hundreds of tasks at once, but only in very specific circumstances. They also suffer from the same problems as standard processors in that tasks could interact. This thesis investigates ways to use both the aggressive techniques to find tasks that can run in parallel, and the speculative techniques to ensure that errors don't occur when tasks do interact. This is a technique that has had wide investigation on standard processors, but very little investigation on these customized processors.

# Acknowledgements

Many thanks to my supervisor and my girlfriend, for the constant support they have provided; my tireless proofreading elves; and of course, my kettle for not breaking down when I needed it the most.

# **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Daniel C. Powell)

# **Publications**

The following refereed conference papers (in reverse chronological order) have been published during the course of this PhD. These form the basis for parts of this thesis as indicated.

- Daniel C. Powell, Björn Franke. "Safety Net: Lightweight Software-TLS Support for Probably Parallel Applications." Currently under peer review.

— Chapter 6 is partially based on this paper.

- Zheng Wang, Daniel C. Powell, Björn Franke, Michael O'Boyle. "Exploitation of GPUs for the Parallelisation of Probably Parallel Legacy Code." In: *Proceedings of 23rd International Conference on Compiler Construction (CC'14), Held as Part of the European Joint Conferences on Theory and Practice of Software (ETAPS'14)*, Grenoble, France, April 2014. Chapter 7 is based on this paper.

- Daniel C. Powell, Björn Franke. "An Integrated Approach to Software Thread-Level Speculation: Machine-Learning Based Policy and Parameter Selection." In: *Proceedings of HIPEAC Compiler, Architecture and Tools Conference (CATC'12)*, Haifa, Israel, November 2012.

- Chapters 4 and 5 are based on this paper.

# **Table of Contents**

| 1 | Introduction |                                      |                                |      |  |  |  |  |  |

|---|--------------|--------------------------------------|--------------------------------|------|--|--|--|--|--|

|   | 1.1          | Moder                                | rn Parallel Architectures      | . 2  |  |  |  |  |  |

|   | 1.2          | nated Parallelisation                | . 3                            |      |  |  |  |  |  |

|   | 1.3          | Specul                               | lative Parallelisation         | . 4  |  |  |  |  |  |

|   |              | 1.3.1                                | Hardware or Software           | . 5  |  |  |  |  |  |

|   | 1.4          | Motiva                               | ation                          | . 6  |  |  |  |  |  |

|   | 1.5          | Goals                                |                                | . 6  |  |  |  |  |  |

|   | 1.6          | Hypotl                               | heses                          | . 7  |  |  |  |  |  |

|   | 1.7          | Structu                              | ure                            | . 7  |  |  |  |  |  |

| 2 | Bac          | Background: Thread Level Speculation |                                |      |  |  |  |  |  |

|   | 2.1          | Paralle                              | elism and Dependences          | . 10 |  |  |  |  |  |

|   |              | 2.1.1                                | DOALL loops                    | . 10 |  |  |  |  |  |

|   |              | 2.1.2                                | DOWHILE loops                  | . 11 |  |  |  |  |  |

|   |              | 2.1.3                                | Thread Blocks                  | . 12 |  |  |  |  |  |

|   |              | 2.1.4                                | Transactional Memory           | . 13 |  |  |  |  |  |

|   |              | 2.1.5                                | Dependence Types               | . 14 |  |  |  |  |  |

|   |              |                                      | 2.1.5.1 Safe Data Dependences  | . 14 |  |  |  |  |  |

|   |              |                                      | 2.1.5.2 False Data Dependences | . 15 |  |  |  |  |  |

|   |              | 2.1.6                                | Other Hazards                  | . 15 |  |  |  |  |  |

|   | 2.2          | Autom                                | nated Parallelism Discovery    | . 16 |  |  |  |  |  |

|   |              | 2.2.1                                | Static Analysis                | . 16 |  |  |  |  |  |

|   |              | 2.2.2                                | Execution Profiling            | . 17 |  |  |  |  |  |

|   |              | 2.2.3                                | Performance Considerations     | . 18 |  |  |  |  |  |

|   | 2.3          | lative Execution                     | . 18                           |      |  |  |  |  |  |

|   |              | 2.3.1                                | Speculation Workflow           | . 19 |  |  |  |  |  |

|   |              | 2.3.2  | When to    | Check                            | 22       |  |

|---|--------------|--------|------------|----------------------------------|----------|--|

|   |              |        | 2.3.2.1    | Lazy Checking                    | 22       |  |

|   |              |        | 2.3.2.2    | Eager Checking                   | 24       |  |

|   |              |        | 2.3.2.3    | Combined Checking                | 24       |  |

|   |              | 2.3.3  | Trace To   | pologies                         | 25       |  |

|   |              |        | 2.3.3.1    | Distributed Traces               | 25       |  |

|   |              |        | 2.3.3.2    | Centralised Traces               | 26       |  |

|   |              |        | 2.3.3.3    | Hybrid Topologies                | 27       |  |

|   |              | 2.3.4  | Synchron   | nisation                         | 27       |  |

|   |              |        | 2.3.4.1    | Barriers                         | 28       |  |

|   |              |        | 2.3.4.2    | Master Thread                    | 28       |  |

|   |              |        | 2.3.4.3    | Overlaps                         | 29       |  |

|   |              | 2.3.5  | Trace Str  | ructures and Collision Detection | 29       |  |

|   |              |        | 2.3.5.1    | Bitsets                          | 30       |  |

|   |              |        | 2.3.5.2    | Counters                         | 31       |  |

|   |              |        | 2.3.5.3    | Address Lists                    | 32       |  |

|   |              | 2.3.6  | Accuracy   | y and False Dependences          | 32       |  |

|   |              |        | 2.3.6.1    | Addressing Size                  | 33       |  |

|   |              |        | 2.3.6.2    | Hashing Techniques               | 33       |  |

|   |              |        | 2.3.6.3    | Single or Multiple Traces        | 34       |  |

|   |              | 2.3.7  | Version 1  | Management                       | 35       |  |

|   |              |        | 2.3.7.1    | Management Scheme                | 35       |  |

|   |              |        | 2.3.7.2    | Versioning Schedule              | 36       |  |

|   |              |        | 2.3.7.3    | Data Structures and Topology     | 37       |  |

|   |              |        | 2.3.7.4    | Value Forwarding                 | 38       |  |

|   |              |        | 2.3.7.5    | Granularity                      | 38       |  |

|   | 2.4          | Conclu | usions     |                                  | 39       |  |

| 3 | Related Work |        |            |                                  |          |  |

| 5 | 3.1          |        |            |                                  |          |  |

|   | 3.2          |        |            |                                  | 41<br>43 |  |

|   | 5.2          | 3.2.1  |            |                                  | 43       |  |

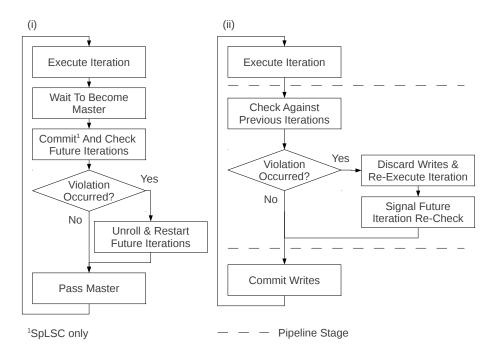

|   |              | 3.2.1  |            | 3TLS                             | 44       |  |

|   |              | 5.2.2  | 3.2.2.1    | SPLSC                            | 44       |  |

|   |              |        | 3.2.2.1    | SPLIP                            | 45       |  |

|   |              |        | J. L. L. L | <u> </u>                         | 15       |  |

|   |                         | 3.2.3                       | STMLITE                                       | 47 |  |  |

|---|-------------------------|-----------------------------|-----------------------------------------------|----|--|--|

|   |                         | 3.2.4                       | DSWP & SMTX                                   | 47 |  |  |

|   | 3.3                     | GPGPU Speculation           |                                               |    |  |  |

|   |                         | 3.3.1                       | PARAGON                                       | 49 |  |  |

|   | 3.4                     | Hardw                       | vare Based Speculation                        | 51 |  |  |

|   |                         | 3.4.1                       | Transactional Synchronisation Extensions      | 51 |  |  |

|   | 3.5                     | Conclu                      | usion                                         | 52 |  |  |

| 4 | t Pipelined Speculation | 55                          |                                               |    |  |  |

|   | 4.1                     | Specul                      | lative Storage Structure                      | 56 |  |  |

|   | 4.2                     | Pipelir                     | ne Stages and Execution Workflow              | 57 |  |  |

|   | 4.3                     | Suppo                       | rted Dependences                              | 58 |  |  |

|   | 4.4                     | Confli                      | ct Detection                                  | 58 |  |  |

|   | 4.5                     | Empir                       | ical Evaluation                               | 60 |  |  |

|   |                         | 4.5.1                       | Experimental Methodology                      | 60 |  |  |

|   |                         | 4.5.2                       | Summary of Key Results                        | 61 |  |  |

|   | 4.6                     | Conclu                      | usion                                         | 63 |  |  |

| 5 | Sma                     | art Spec                    | culation Policy Selection                     | 65 |  |  |

|   | 5.1                     | Motivating Example          |                                               |    |  |  |

|   | 5.2                     |                             |                                               |    |  |  |

|   |                         | 5.2.1                       | Factors Affecting Performance                 | 68 |  |  |

|   |                         | 5.2.2                       | Common Speculation Parameters                 | 68 |  |  |

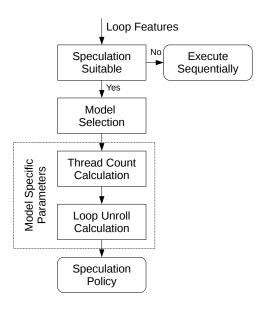

|   | 5.3                     | B Policy Selection Workflow |                                               | 69 |  |  |

|   |                         | 5.3.1                       | Prediction Model Training                     | 69 |  |  |

|   |                         | 5.3.2                       | Policy Calculation                            | 70 |  |  |

|   | 5.4                     | Empir                       | ical Evaluation                               | 71 |  |  |

|   |                         | 5.4.1                       | Evaluation Methodology                        | 71 |  |  |

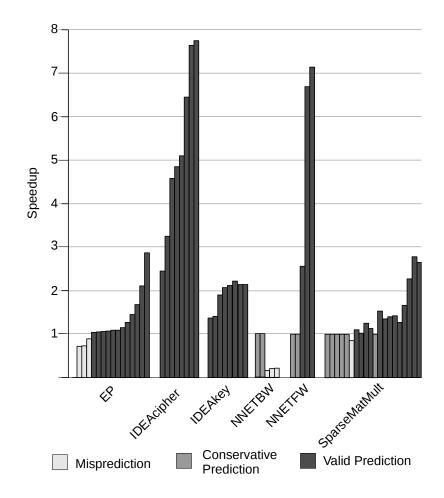

|   |                         | 5.4.2                       | Policy Selection Testing                      | 71 |  |  |

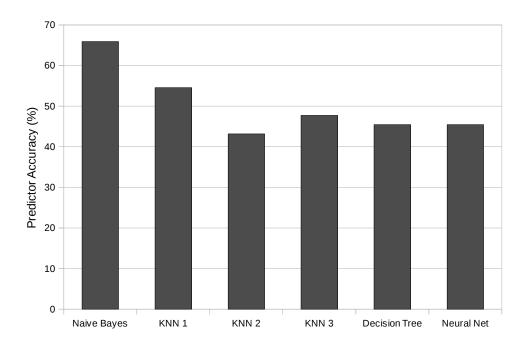

|   |                         |                             | 5.4.2.1 Machine Learning Techniques           | 72 |  |  |

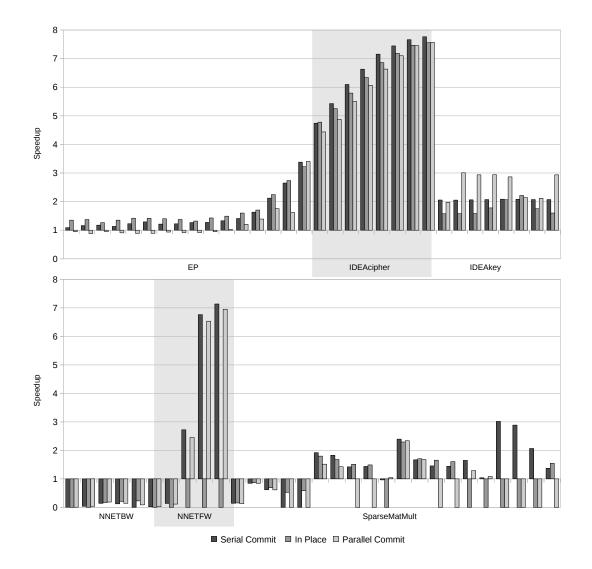

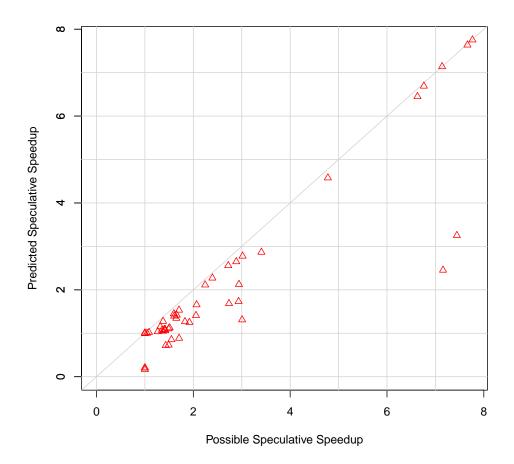

|   | 5.5                     | Summ                        | ary of Key Results                            | 73 |  |  |

|   | 5.6                     | Conclu                      | usions                                        | 78 |  |  |

| 6 | Auto                    | omated                      | Error Checking for Aggressive Parallelisation | 81 |  |  |

|   | 6.1                     |                             | elisation Target                              | 82 |  |  |

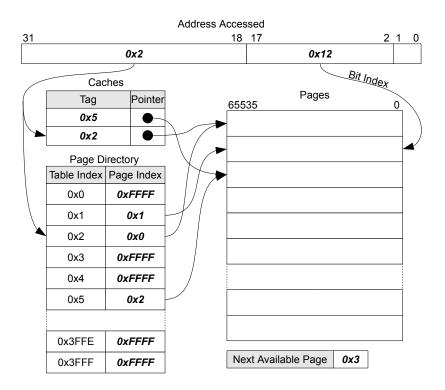

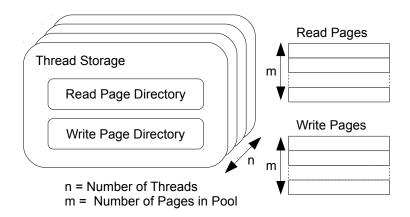

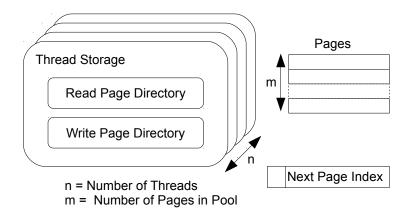

|   | 6.2                     |                             | bry Trace Data Structure                      | 83 |  |  |

|   |                         |                             |                                               |    |  |  |

|   |                                   | 6.2.1                  | Page Cac                       | ching                                   | 85  |  |  |  |

|---|-----------------------------------|------------------------|--------------------------------|-----------------------------------------|-----|--|--|--|

|   |                                   | 6.2.2                  | Structure                      | Usage                                   | 86  |  |  |  |

|   |                                   |                        | 6.2.2.1                        | Allocation/Initialisation               | 86  |  |  |  |

|   |                                   |                        | 6.2.2.2                        | Trace                                   | 87  |  |  |  |

|   | 6.3                               | Simple                 | Distribute                     | ed Error Detection                      | 88  |  |  |  |

|   |                                   | 6.3.1                  | Scalabilit                     | ty                                      | 90  |  |  |  |

|   | 6.4                               | Reduct                 | tion-Tree E                    | Error Detection                         | 90  |  |  |  |

|   |                                   | 6.4.1                  | Scalabilit                     | ty                                      | 95  |  |  |  |

|   | 6.5                               | GPU C                  | Conflict De                    | etection                                | 95  |  |  |  |

|   | 6.6                               | Autom                  | ated Progr                     | am Transformations                      | 101 |  |  |  |

|   | 6.7                               | Empiri                 | cal Evalua                     | ution                                   | 104 |  |  |  |

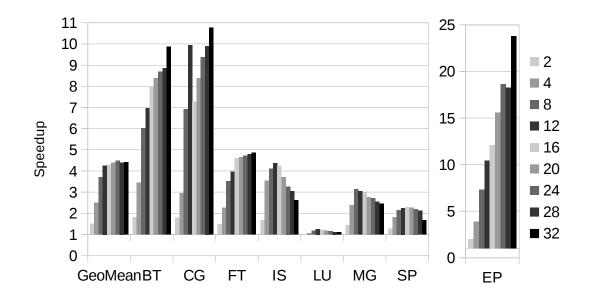

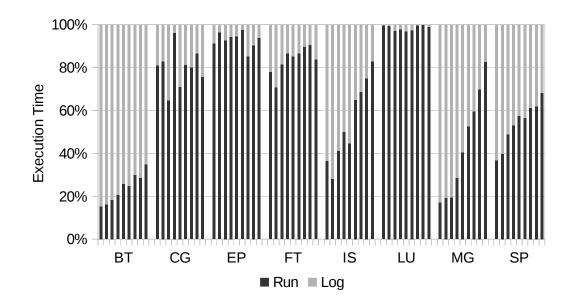

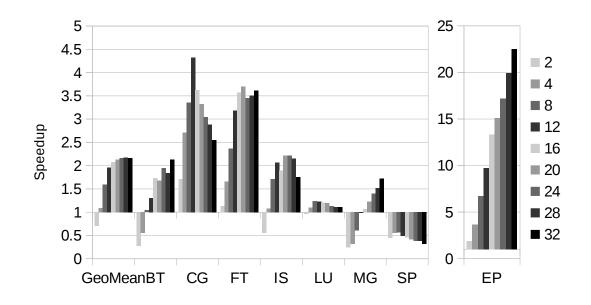

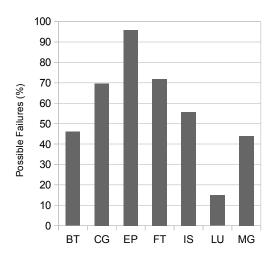

|   |                                   | 6.7.1                  | Auto-Par                       | allelisation Analysis                   | 106 |  |  |  |

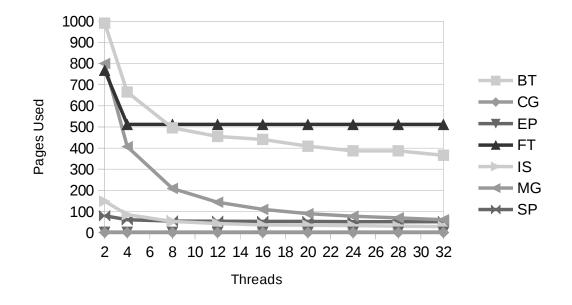

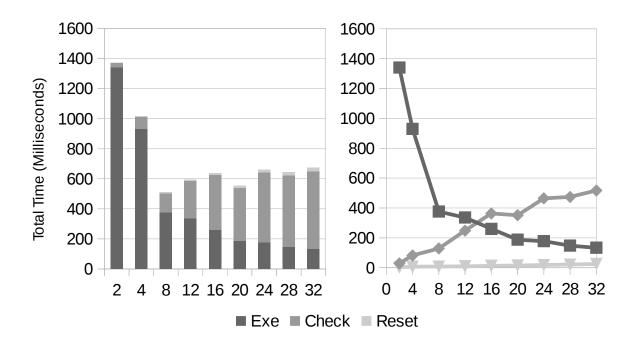

|   |                                   | 6.7.2                  | Page Tab                       | le Statistics                           | 108 |  |  |  |

|   |                                   | 6.7.3                  | Simple D                       | Distributed Detection Scheme            | 112 |  |  |  |

|   |                                   | 6.7.4                  | Reductio                       | n-Tree Detection Scheme                 | 114 |  |  |  |

|   |                                   |                        | 6.7.4.1                        | Comparison to Simple Distributed Scheme | 114 |  |  |  |

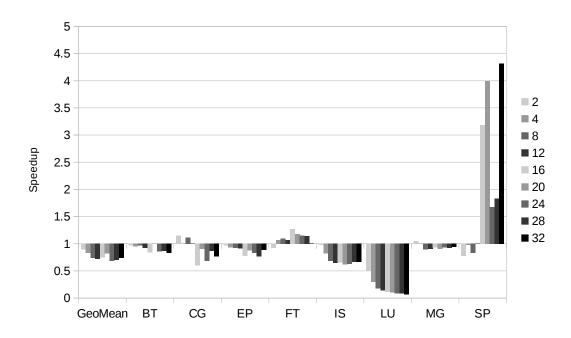

|   |                                   | 6.7.5                  | Hybrid C                       | CPU-GPU Detection Scheme                | 116 |  |  |  |

|   |                                   | 6.7.6                  | Depende                        | nce Violations                          | 118 |  |  |  |

|   | 6.8                               | Conclu                 | ision                          |                                         | 119 |  |  |  |

| 7 | Gpu                               | -Based Speculation 121 |                                |                                         |     |  |  |  |

|   | 7.1                               | Motiva                 | vation                         |                                         |     |  |  |  |

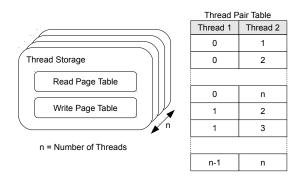

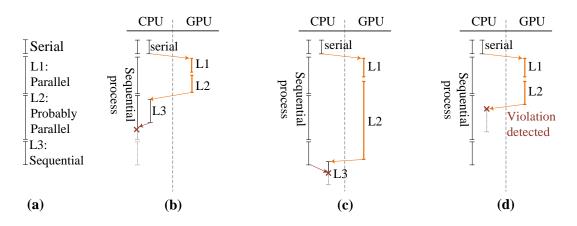

|   | 7.2                               |                        |                                |                                         | 124 |  |  |  |

|   | 7.3                               |                        |                                |                                         | 125 |  |  |  |

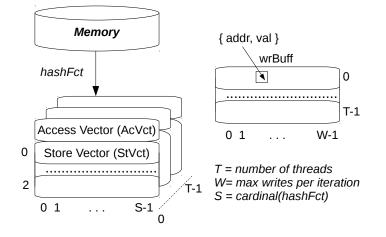

|   | 7.3.1 Speculative Data Structures |                        | ve Data Structures             | 125                                     |     |  |  |  |

|   |                                   | 7.3.2                  | Violation                      | Detection                               | 126 |  |  |  |

|   |                                   |                        | 7.3.2.1                        | Speculative Load                        | 127 |  |  |  |

|   |                                   |                        | 7.3.2.2                        | Speculative Store                       | 127 |  |  |  |

|   |                                   |                        | 7.3.2.3                        | Flow Dependence                         | 128 |  |  |  |

|   |                                   |                        | 7.3.2.4                        | Anti Dependence                         | 128 |  |  |  |

|   |                                   |                        | 7.3.2.5                        | Output Dependence                       | 128 |  |  |  |

|   |                                   | 7.3.3                  | Comparison to Other Approaches |                                         |     |  |  |  |

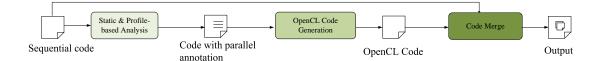

|   | 7.4                               | Compi                  | lation and                     | Code Transformations                    | 129 |  |  |  |

|   |                                   | 7.4.1                  | Parallelis                     | m Detection                             | 129 |  |  |  |

|   |                                   |                        | 7.4.1.1                        | Speculative Variables                   | 130 |  |  |  |

|                        |       | 7.4.2               | OpenCL Code Generation                       | 130 |

|------------------------|-------|---------------------|----------------------------------------------|-----|

|                        |       | 7.4.3               | Code Merging                                 | 131 |

| 7.5 Experimental Setup |       |                     |                                              | 131 |

|                        |       | 7.5.1               | Platform                                     | 131 |

|                        |       | 7.5.2               | Benchmarks                                   | 131 |

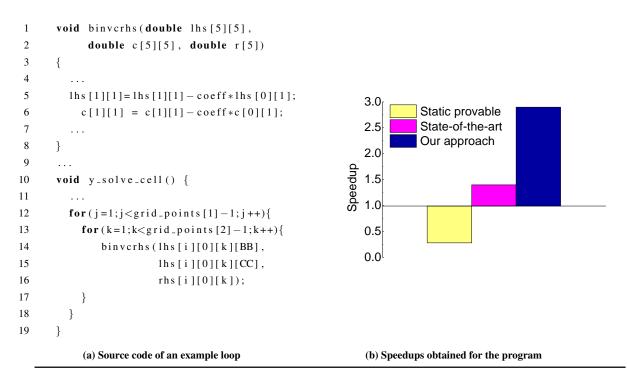

|                        |       | 7.5.3               | Compiler and Evaluation Runs                 | 133 |

|                        |       | 7.5.4               | Comparison                                   | 133 |

|                        | 7.6   | Empir               | ical Evaluation                              | 134 |

|                        |       | 7.6.1               | Overall Results                              | 134 |

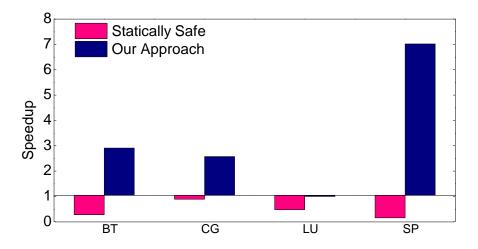

|                        |       | 7.6.2               | Comparison with the Statically Safe Approach | 135 |

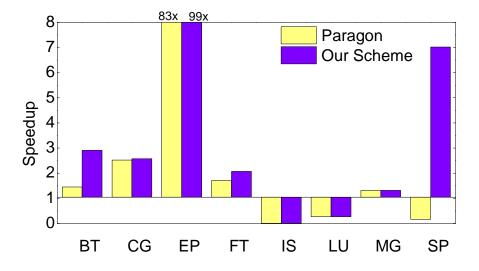

|                        |       | 7.6.3               | Comparison with Paragon                      | 136 |

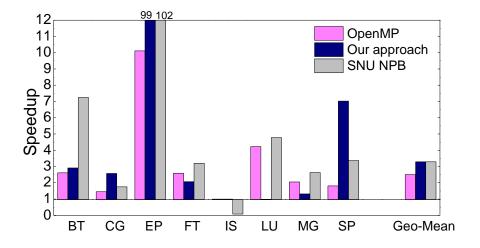

|                        |       | 7.6.4               | Comparison to Manually Parallelized Code     | 137 |

|                        |       | 7.6.5               | Analysis                                     | 138 |

|                        |       |                     | 7.6.5.1 Limitation of Static Analysis        | 138 |

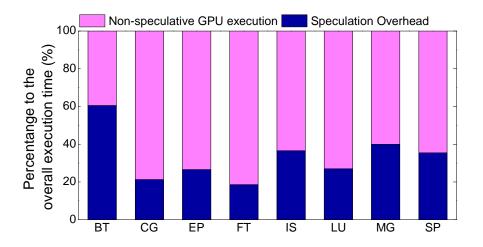

|                        |       |                     | 7.6.5.2 Speculation Costs                    | 139 |

|                        |       |                     | 7.6.5.2.1 Dependence Violation               | 140 |

|                        | 7.7   | Conclu              | usion                                        | 140 |

|                        | Con   | clusion             |                                              | 143 |

|                        | 8.1   | Contri              | butions                                      | 144 |

|                        |       | 8.1.1               | Automated Policy Selection                   | 144 |

|                        |       | 8.1.2               | Lightweight Error Checking                   | 144 |

|                        |       | 8.1.3               | GPU-Based Speculative Execution              | 145 |

|                        |       | 8.1.4               | Pipelined Speculation Scheme                 | 146 |

|                        |       | sis and Future Work | 146                                          |     |

|                        |       | 8.2.1               | Limitations of Policy Selection              | 146 |

|                        |       | 8.2.2               | Scalable Centralised Error Detection         | 147 |

|                        |       | 8.2.3               | Block Tracing                                | 147 |

|                        |       | 8.2.4               | Combination CPU-GPU Speculation              | 148 |

| il                     | bliog | raphy               |                                              | 149 |

|                        | ~ 8   | · · · · · ·         |                                              |     |

# **Chapter 1**

# Introduction

Since the dawn of the computing era the demands on computing power have been ever increasing. As time has progressed faster processors have been developed to meet those demands, combined with newer tools, languages and techniques to support that power. In an effort to better utilise the resources that are available many different execution paradigms have been developed in many forms most of which are loosely based around some form of parallel processing. This ranges from the very high level such as shared mainframes in the 50s, allowing many distinct users to work in parallel by sharing processing resources split into timeslices, to a lower level such as allowing multiple processes to execute on a machine at once through scheduling, to the very low level such as pipelining instructions so that different parts of each instruction are executing at the same time.

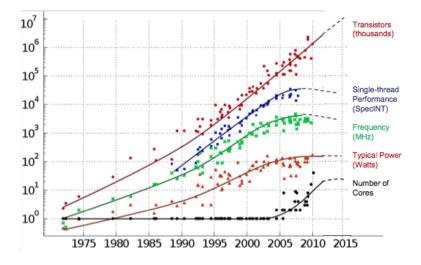

Each of these styles of execution have a very clear limitation, the single threadedexecution model [42]. For many years however that limitation has been overcome by relying upon the development of faster, more complex processing architectures to increase the performance of applications. This is such a well known and relied upon trend that it was developed into a law deciding the abilities of future architectures, Moore's Law [39]. Moore's Law surmised that over time the density of components that could fit on a single die would increase and the cost per component would continue to fall. In 1975 the rule became more formalised in that the circuit density would double roughly every 24-months [46]. The effects of this law is demonstrated in Figure 1.1. This density of components translated into a direct performance increase for processors with adaptations of the law stating that the performance of such processors

Figure 1.1: Processor trends for 1970-2012. The graph shows consistent exponential growth of the number of elements on a die (Moore's Law) and the introduction of multi-core designs due to flattening of performance, frequency and power growth trends. Source: C.Moore [27]

would double approximately every 18 months, a trend that was able to be maintained into the mid-2000s. Beyond that however it became apparent that processor designers had started to reach the physical limits of a single-threaded processor causing exorbitant power consumption and thermal output requirements [5]. Ultimately this required a complete shift in architectural design, a move towards parallel processing and multicore designs.

## **1.1 Modern Parallel Architectures**

Despite the long history of development that parallel processing and architectures have had [4] their widespread use has only taken off within the last decade. Before that single-threaded microprocessors were good enough and continued to provide performance increases year over year, demonstrated by Figure 1.1. Since that decline multicore architectures have found their way into virtually all modern computing devices ranging from mobile phones, games consoles, personal computers, laptops all the way to today's large-scale data centres and supercomputers. Producing parallel programs targetting these processors is one of today's grand challenges in computer systems research [38]. Despite the progress in parallel programming languages and systems [8], programming of multicore platforms still remains a skilled activity in the hands of a few expert programmers [17].

Further complexity exists due to the range of different architectural designs available ranging from the more common chip multiprocessors, to more heterogeneous designs with differently designed processing units for specific tasks. The designs of heterogeneous processors are wide in variety, for example the Cell [18] multiprocessor that has additional units designed for specific powerful computations, to devices with power consumption considerations, such as ARM's big.LITTLE processor, one core for slower low-power processing and another for faster, power intensive processing [20]. Rapidly becoming a viable programming platform is the use of general purpose GPUs [11] whose memory architecture and processing unit designs require extremely different programming considerations to obtain useful performance [6]. This adds further difficulty to well performing parallel programming and makes auto-parallelisation techniques a very desirable solution.

## **1.2 Automated Parallelisation**

As with parallel architectures, automated parallelisation has undergone decades of research [22]. Initially these were based around the automated vectorisation of programs to speed up single-threaded programs that were then translated into parallelising techniques. More explicit parallel languages have been developed to aid in the autoparallelisation process [8], however these languages require a large investment to learn a new programming paradigm. This approach also does not aid in the parallelisation of the vast quantities of legacy code that exist [23].

The applicability of much research into auto-parallelisers is often restricted to niche settings such as array-based numerical computations [41]. Outside these specialist domains the performance of even state-of-the-art auto-parallelisers on real-world codes is highly disappointing [44]. One of the key reasons for this dramatic failure is that compilers are notoriously weak at raising the abstraction level [31]. This includes inference of dependence patterns from sequential applications, where such information is not explicitly expressed by the programmer, yet it is essential for successful parallelisation. In fact, solutions to the general data dependence problem are not computable [7].

A large number of static dependence analyses, which compute approximations of the actual dependence information, have been developed [33]. These analyses are necessarily conservative, i.e. they may report the presence of a so-called *may* dependence

even if this dependence does not materialise for any of the legal program inputs, but no actual dependence will remain undetected. Unfortunately, most static analyses report *may* dependences overly frequently and this, in turn, prevents parallelisation. Such *may* dependences can also be triggered through the use of many common programming techniques, such as pointer aliasing and indirect addressing.

A recent approach to capturing dependence information more precisely is based on profiled execution [44]. For this technique a program is instrumented and then executed. The resulting profile is analysed and checked for dependences. Such profileguided parallelisation schemes are effective at uncovering non-statically analysable parallel loops, however it lacks a correctness guarantees for all inputs different to the ones used during profiling allowing for undetected dependences to exist in the program, ultimately making it unsafe to execute without further manual analysis or runtime checking.

## **1.3 Speculative Parallelisation**

Thread-level speculation (TLS) has attracted the attention of a number of researchers, e.g. [32, 9, 43], as a means of adding safety to potentially unsafely parallelised programs. This is performed by speculatively executing possibly independent work items such as loop iterations or function calls on multiple processor cores. Through the use of TLS a program is executed with additional memory-access tracking code. For each potentially unsafe region of code the memory accesses performed are recorded and then at relevant intervals they are analysed to detect any data dependences that may have occurred. Prior to executing any potentially unsafe regions of code a checkpoint is made which, if a dependence is detected the program rolls back to and re-executes safely.

Most TLS frameworks are geared towards the case when the majority of work items are independent and can be executed in parallel, but every so often dependence violations require work items in flight to be squashed. In fact, almost all work has focused on TLS for when there is a realistic chance of serialising dependences, i.e. discarding of non-committed memory writes and rollback to safe state is needed. This, for example, may happen in loops that are sometimes parallel and sometimes not, depending on the actual data inputs provided to the program.

#### **1.3.1 Hardware or Software**

To support TLS various hardware [19, 10] and software schemes [29, 28, 24, 25, 36, 30] have been developed for the provision and management of buffers and dependence detection mechanisms.

Hardware supported TLS (HW-TLS) includes the use of specifically tasked hardwarebased buffers for memory tracing and recovery. These schemes are generally very reliable and provide significant speedups to a given program whilst being very accurate at detecting dependences that occur. The implementation of speculative execution of a program can also happen completely automatically in the hardware making it a very desirable feature. However, HW-TLS requires customised hardware to support its execution. Designing and implementing such hardware can be very costly and requires large regions of a CPU die to perform correctly. This makes the process very expensive for hardware designers when there exist easier targets for optimisation, that provide more demonstratable speedup and consume less of the available resources on chip. Hardware-based speculation also suffers from fixed limits on the size of memory buffers restricting the ability to speculate over large sections of code. As such, there are currently no full commercially available implementations of Hw-TLS. Instead there is one architecture that supports a subset of TLS features, Intel's Haswell [15]. Haswell uses Transactional Synchronisation Extensions (TSX) to provide hardware transactional support that, with additional software support, could be extended to implement a full TLs system. Haswell's architecture is discussed further in Section 3.4.

In contrast, software-based TLS (SW-TLS) is much more flexible. The size of buffers used can be customised to the needs of a given program and the methods of storing traces, detecting dependences and even performing rollbacks/commits of speculative state can be changed to suit the needs of both the program and the platform it is executed on. SW-TLS is also very cheap to implement, requiring no customised hardware. SW-TLS can be executed on any multi-core machine. The specific designs of SW-TLS can also be explored cheaply requiring no simulators or additional hardware. However, SW-TLS is very unreliable at providing a respectable speedup and generally slower than its hardware equivalent. The flexibility that it provides results in performance varying based on the program that is being speculated on, the hardware used to execute the program and the specific type of speculation being performed. In many cases the use of SW-TLS can result in a slowdown of the original sequential program,

but, given the correct circumstances and configuration SW-TLS can provide significant speedups. As such it is essential that an appropriate SW-TLS configuration be selected for a given program.

### 1.4 Motivation

To further the state of auto-parallelising technologies it is desirable to add safety to some of the more aggressive auto-parallelisers that currently exist. TLS appears to be suitable for this but due to the costly nature and unavailability of Hw-TLS it is impractical to consider it as an option and SW-TLS is currently too unreliable at providing speedup to truly be considered. No research has as yet been performed into the automated use of SW-TLS.

Through profiled execution it is clear that there are many missed opportunities when it comes to parallel execution. Profiling can also provide a high-confidence prediction that a loop is probably parallel and, as such, does not require some of the more heavyweight techniques such as those geared towards recovering from a dependence violation that many Sw-TLS focus on. There are also additional platforms, such as GPUs that have not yet been widely targetted by Sw-TLS methods.

### 1.5 Goals

The goal of this thesis is to extend the existing knowledge and technologies surrounding software-based thread-level speculation. It intends to do this by:

- Describing research into automating the speculative process by:

- Creating a means to select which loops will profit from speculative execution,

- Automating the process of inserting speculative parallel markup into existing sequential programs,

- Developing a means for automatically selecting an appropriate speculation scheme, and tune it so that significant, reliable speedup can be obtained.

- Investigating the hypothesis that standard heavyweight Sw-TLS methods are unnecessary by:

- Creating a very lightweight speculation scheme that prioritises fast execution over rollback.

- Attempting to offload part of the speculative process to an auxiliary processing device such as a GPU.

- Attempting to create a useful lightweight speculation scheme for use on a general purpose GPU.

## 1.6 Hypotheses

It is the hope that this thesis can prove that additional performance can be obtained completely automatically and safely through the use of code profiling and speculative execution. As such it is desirable to prove that Sw-TLS can be configured completely automatically to provide a near-optimal solution that provides consistent performance increases over sequential code.

This thesis also argues that in many circumstances it can be predicted with enough confidence that a given, potentially unsafely parallelised region of code does not contain any data dependences, and as such can execute with very little support for safety and rollbacks. Instead it is theorised that any version control normally used by Sw-TLS schemes can be discarded in favour of an extremely lightweight dependence detection scheme that merely confirms that no dependence has occurred.

Finally, it is hypothesised that the GPU is both an appropriate target for SW-TLS and that it can be a useful tool to provide further speedup of standard CPU based SW-TLS schemes.

## 1.7 Structure

The rest of this thesis is structured as follows:

• Chapter 2 provides a thorough investigation into the principles of parallel execution and speculative execution, with a detailed analysis of the benefits and disadvantages of each method.

- Chapter 3 provides a look at already existing auto-parallelisation schemes and Sw-TLS schemes with an evaluation of how well they perform and their limitations.

- Chapter 4 provides an alternative speculation scheme that attempts to address some niche scenarios that existing schemes perform poorly at.

- Chapter 5 introduces an automated loop selection process that identifies loops that will benefit from speculative execution and selects a suitable speculation policy that will provide improved performance.

- Chapter 6 investigates the hypothesis that heavy-weight speculative schemes are often not necessary and instead programs can execute only with simple confirmation that dependence violations have not occurred. This chapter also investigates the use of a GPU as an auxiliary unit to offload some of the speculative processing to.

- Chapter 7 introduces a new, automated scheme to take sequential programs and execute them speculatively on a GPU.

- Chapter 8 summarises the final discoveries and conclusions of this work, along with a look at possible future work beyond this thesis..

# Chapter 2

# Background: Thread Level Speculation

As a way to progress beyond the end of Moore's law and continue increasing performance beyond the physical limitations of single-threaded execution, commercial processor architects have adopted the multi-core processor design as the de-facto standard in modern, general purpose computing systems. There is also a rapidly growing trend of using lower-power multi-core architectures in mobile platforms such as mobile phones and tablets, improving user interaction and increasing performance on these platforms. As such it is essential that the applications executed on these platforms are designed to exploit these parallel architectures and utilise their resources effectively. Manual parallelisation is a difficult, time-intensive task [23], and automatic parallelisation techniques using static analysis, while achieving some performance increases, have left much to be desired in more complex real-world applications [44]. Software thread-level speculation is intended to address these limitations.

Prior to addressing the designs of modern Sw-TLS techniques, this chapter provides a brief background on frequently encountered types of parallel execution and the hazards that they can introduce in Section 2.1. This chapter then discusses static analysis and the automated parallelism discovery and mapping methods that this work targets in Section 2.2. An in-depth description of common speculation techniques is provided in Section 2.3 with final conclusions provided in Section 2.4.

```

1 for (int i = 0; i < n; i++) {

2     a[i] = b[i] + c[i];

3 }</pre>

```

Figure 2.1: A simple DOALL based loop that would benefit from parallelisation.

### 2.1 Parallelism and Dependences

Application-level parallelism is a diverse and complex subject with many different styles of implementation. Application-level parallelism also creates the possibility of various hazards that can occur causing the incorrect execution of a program. This section first lists several different parallel programming paradigms that commonly employ TLS, then goes on to list several hazards that TLS must account for.

### 2.1.1 DOALL loops

One of the simplest ways to implement parallelism is to split the processing of individual iterations of a standard DOALL loop between multiple threads [22]. Such loops include DOALL loops in Fortran, and for and foreach loops as implemented in C/C++/Java and many other imperative languages. An example loop that would benefit from parallelisation can be found in Figure 2.1. This style of parallelism can also be extended to more functional programming constructs such as list comprehensions.

To parallelise a DOALL loop it is essential to be able to calculate the number of iterations and the values of their loop condition variables, be it a simple counter such as in for loop, or a collection of objects as in foreach loops and list comprehensions. These values must be determinable prior to the start of execution so that each iteration can be distributed evenly among the available worker threads. Additionally these loops must not contain break statements as these can prevent some iterations from executing. If they do then additional support is required to prevent future iterations from executing. These conditions provide a guarantee that all iterations of the loop will execute allowing them to be distributed evenly between all worker threads. They also provide a guarantee that the loop execution condition does not contain any data dependences, however the iteration body of the loop may contain data dependences that must be handled appropriately.

```

while (has_next(item)) {

item = get_next(item);

...

}

```

Figure 2.2: A simple DOWHILE based loop that could benefit from parallelisation.

In TLS these loops are the simplest to implement allowing for a flexible tracking and dependence detection scheme. The guarantee that all iterations will execute allows for dependence checks to be deferred until a point after the loop has executed, and the explicit order in which each iteration is executed allows for simple rollback methods ensuring a deterministic output.

### 2.1.2 DOWHILE loops

A more complex construct to parallelise is the DOWHILE loop. Traditional DO-WHILE loops continue to execute each iteration whilst a certain condition remains true. This condition is normally updated within the iteration body itself. An example of a loop doing so can be seen in Figure 2.2. This makes it more difficult to determine how many iterations the loop will execute and hence makes it harder to parallelise by distributing iterations between each thread. Additional static or runtime analysis is required to determine how many iterations and the runtime state of each iteration before parallel execution can begin.

Many other loops can fit into this category such as DOALL loops that contain break statements, or DOALL loops whose run condition relies upon functions or on variables other than those in the initialisation stage.

In TLS these loops are complex to implement as they are likely to require speculation across their execution condition. For more eager parallelisation schemes one or more iterations may execute beyond the final run condition making it important to allow for the side effects of these iterations to be rolled back individually. This also restricts when dependence checks can be performed as they may have to occur at the end of every iteration instead of allowing them to be delayed until after the loop has finished. However, as with simple DOALL loops the order in which each iteration is executed is very strict ensuring a deterministic output.

```

1 for(int i = 0; i < n; i++) {

2     a += b[i];

3 }

4 for(int j = 0; j < n; j++) {

5     c += d[i];

6 }</pre>

```

Figure 2.3: A simple two-stage process that could be split into two thread blocks.

### 2.1.3 Thread Blocks

Beyond loops is the concept of threading, where each thread executes code based upon the specific task assigned to it. Whilst each thread is often contributing towards the same goal, each executes different instructions to achieve their assigned task, often working in tandem with the other threads through the use of barriers and synchronisation and communication between threads using shared memory or message passing. Figure 2.3 provides a simple example of a region of code that can be easily split into two threads. Many parallel programming paradigms have been devised to make use of this concept such as producer-consumer models [21], where one thread generates an object (the producer), which is then passed on to another thread which processes it and generates the required output (the consumer). A more complex version of this is pipelined processing, where each thread is assigned a particular stage of the processing with the result of each passed to the next thread to complete their stage. Costs associated with this form of processing are based on the setup and destroy times taken to fill each stage of the pipeline. However, once full the pipeline can process in parallel a number of items equal to its depth.

Alternately, threads can be working on completely separate tasks using shared resources, producing their own individual output. Examples of this are databases and web servers where each client request is performed in a separate thread. These threads are less likely to require direct communication, but may require locks and other synchronisation based on access to shared resources.

In TLS pipelined processing and parallel tasks are complex to handle. Pipelined processing ensures the order in which tasks are tasks completed but does not necessarily guarantee the consistent ordering of access to shared resources. Dependence checks

```

void addAmount(index, amount) {

entry = database.get(index);

entry += amount;

database.put(index, entry);

}

```

Figure 2.4: A simple database process that could use transactional support.

must be performed at any synchronisation points, but the type of synchronisation restricts how these checks can be performed, often with a thread having to compare its progress to every other executing thread before being allowed to continue. This makes checking more costly as each thread is unable to share the checking costs between the other threads as with loops. Similarly with parallel tasks there is no concept of ordering for each thread to access or update shared resources, forcing checks and rollbacks to be performed on a first-come-first-served basis.

### 2.1.4 Transactional Memory

A concept similar to TLS in thread blocks is often employed, for example, in database systems [45]. This is transactional memory where, on each access to the database, a thread will start a transaction. Figure 2.4 provides a simple database process that may benefit from the use of transactional memory. The thread will request the information it requires to continue, process them and generate the results to be committed back to the database. Once this has been done the transaction will attempt to commit itself, first checking if other threads have accessed the same resources. If they have, the process will have to be repeated until the thread is able to perform the required actions without interference from other threads or clients. This process can lead to hazards such as live-lock where the thread is constantly prevented from performing its required tasks as other threads block it from doing so. Additionally, as with thread blocks, there is no easily defined ordering for each transaction, again resulting in a first-come-first-served processing basis.

### 2.1.5 Dependence Types

During access to shared resources by parallel threads there are several similar but distinct data dependences that can occur, resulting in incorrect output. In each of these cases if the access was performed sequentially by a single thread an error would not occur and the resulting output would be deterministic and correct; however, as parallel threads can access data in any order each dependence can also be performed in any order, resulting in a non-deterministic program and potentially an error in the final output of a program.

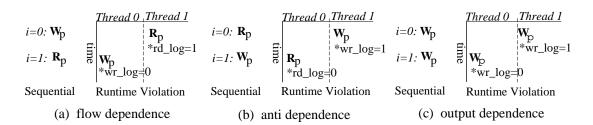

- **Read-After-Write Dependences** When one thread reads an element of shared data followed by another thread writing to that same element there is a *flow* or *read-after-write* (RAW) dependence on that element.

- Write-After-Read Dependences When one thread writes an element of shared data followed by another thread reading that same element there is an *anti* or *write-after-read* (WAR) dependence on that element.

- **Write-After-Write Dependences** When one thread writes an element of shared data followed by another thread also writing that same element there is an *output* or *write-after-write* (WAW) dependence on that element.

#### 2.1.5.1 Safe Data Dependences

A *safe* data dependence is one that occurs during execution between iterations but the specific order in which it was executed does not cause an error in the final output. Specifically if the ordering in which the dependence is executed is the same as that of a sequential version of the program this would result in a *safe* data dependence. For instance, if a write by a programmatically earlier iteration by a parallel thread occurs before the read or write of a later iteration then there is a data dependence between the two iterations, but the order in which the dependence executed is the same as it would be if it were executed sequentially, hence it is a *safe* dependence. By not being able to distinguish between standard dependences and *safe* dependences, deferred detection would trigger an unnecessary rollback.

#### 2.1.5.2 False Data Dependences

A *false* data dependence is one that is detected by speculative tracking schemes that did not actually occur in a program. This is frequently triggered by schemes that employ memory reduction methods such as memory address hashing or larger than byte size addressing. These methods are described in more detail in Section 2.3.6. *False* data dependences often trigger unnecessary rollbacks or other version control techniques resulting in additional processing and longer execution times, potentially much longer than the original sequential version of a program.

### 2.1.6 Other Hazards

By allowing code that potentially contains data dependences to execute can also trigger several other hazards. In particular these include:

### **Inifinite Loops**

If the execution condition of a loop is the subject of a data dependence, or derived from any variable that may contain a data dependence could result in an inconsistently executed loop. This can include the execution of additional iteration, missing iterations and possibly even an inifinite loop. The simplest solution to this is to ensure the loop condition is not derived from an unsafe variable, however this a potentially difficult task to ensure automatically. Worse still, many speculation schemes may never detect this error as dependence checks occur after the loop has finished executing.

#### Segfaults

In cases of indirect memory addressing and pointer arithmetic it is possible for a memory access to be performed outside of its expected address range. For instance an access of an array may cross the boundaries of the array itself into the memory of other variables. This can be handled as the value causing the erroneous access would be detected as a dependence violation. A special case of this is to access memory outside of the program itself, triggering a segfault. This is easily recoverable by speculative execution by overriding the segfault handler and treating the fault as a failed speculation. An extreme example would be to override a loop varible resulting in an infinite loop, or an access to nonspeculative memory that cannot be restored. These are difficult issues that have not been widely investigated by speculative research.

### Irreversible I/O

Many programs perform I/O during their standard operation. Should any occur during speculative execution it may be impossible to reverse the consequences should a dependence be detected. This can be handled through buffering of both input and output during speculative regions.

### 2.2 Automated Parallelism Discovery

This section reviews several methods and their limitations for performing automated parallelism detection. The simplest form of parallel execution to detect and implement automatically is that of DOALL loops, as described in the previous section. Hence, most auto-parallelising compilers and tools focus heavily on these loops [14]. As this dissertation is intended to be an extension on top of existing auto-parallelising tools it will focus mainly on these same loops.

### 2.2.1 Static Analysis

The primary method for detecting parallelism in sequentially executing code is static analysis [14]. During this stage compilers/parallelising tools generate a model of a program and analyse the data dependences that may exist. The ordering of every read and write performed on an array/variable is analysed to extract whether or not a flow, anti or output dependence exists on that variable. The program is then split into basic blocks that can or cannot be parallelised and rewritten into separate threads based on various performance metrics embedded into the tool. A common case is the parallelisation of loops where static analysis is used to detect cross-iteration data dependences that would prevent the parallel execution of individual iterations.

In many circumstances sequential code may re-use a variable to calculate new data that is independent of prior uses of that variable, for instance a piece of data calculated during each iteration of a loop. In the sequential program this re-use would not cause an error, but during parallel execution this variable must be *privatised* such that each thread has its own copy, which may be used without interfering with other threads. Many existing parallelising tools will automatically detect these variables and privatise them correctly.

Similarly, in many circumstances a *reduction* on a variable will occur, for instance the summing of a value across iterations of a loop. Due to the inherent data dependence that exists on such a reduction variable, many compilers will determine this case as unparallelisable. However, such cases are simple to parallelise by creating a thread-private copy of the reduction variable and, at the end of parallel execution, adding additional code to perform the reduce operation across the privatised copies to the final output variable.

Dependence detection, privatisation and reduction are relatively simple exercises on individual variables, but each of these phases become significantly more difficult when programs involve the use of arrays or pointer manipulation, a very common circumstance. When a program uses arrays a tool must pre-calculate every index into the array, or identify a common access pattern to the array to determine whether no data dependences exist for each access of the array. Similarly a compiler must be able to determine which piece of data a pointer is accessing to be able to provide a guarantee that no data dependences exist. These are significant tasks for a parallelisation tool to perform, relying upon advanced knowledge of the program being executed that simply cannot be represented by many intermediate representations used during static analysis. The problem becomes even worse in circumstances of pointer aliasing or the use of indirect array indexing that prevent the compiler from determining any array access patterns. In these circumstances many parallelising tools and compilers are necessarily conservative and determine these sections of code to be unparallelisable to prevent possible errors in the program from occurring. However, in doing so they miss many possible opportunities for obtaining faster programs through parallel execution.

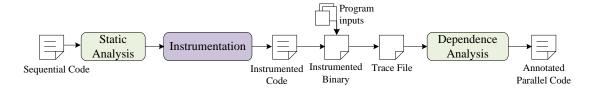

### 2.2.2 Execution Profiling

To extract further parallel opportunities from sequential code, static analysis can be augmented with profiled execution analysis [44, 48]. To perform profiled execution a sequential program is instrumented with additional code to allow it to generate traces of all memory operations that a program will execute. Such traces include pointers into the original high-level code that indicate which section is being executed: for instance the start and finish of each iteration of a loop. These logs containing additional program structure can then be analysed to determine if a data dependence occurred during execution.

This technique is meant to be used as an addition to static analysis. In many cases static analysis can prove with absolute certainty that no data dependence exists, and also in many cases that a dependence definitely exists. This technique is for use in circumstances where static analysis cannot prove either.

The analysis of memory trace logs can provide absolute certainty for cases where a dependence exists but where static analysis has failed. In cases where no dependence is detected profiling can provide no guarantee that a dependence does not exist due to alternative execution scenarios, such as different input data sets to the program. Many tools leave the final decision of whether a loop can be parallelised to the programmer using the tool, delegating the consequences of incorrectly identified parallelism to the programmer. In fully automated parallelisation tools this situation is untenable, partly because programmers themselves are fallible.

## 2.2.3 Performance Considerations

Modifying a program to execute in parallel can provide significant speedups, but the process also introduces additional overheads related to thread creation and management, thread communication and synchronisation. These overheads can easily outweigh any benefits that parallel execution may present. During parallelisation many tools include various metric analyses to determine if a speedup will be obtained. These metrics are not precise but are a useful indicator of the possible performance benefits of parallelisation. Similar tools exist for profiled execution, with the added benefit that performance can be measured during profiling. The possible speed estimated by these metrics can also vary depending on the configuration of the program, input data sets and the platform performing the execution. As yet, no such metrics exist for speculative execution.

# 2.3 Speculative Execution

This section provides an in-depth description of many common speculation techniques, with analysis of their suitability in various scenarios and their effects on the performance and resource utilisation of a program.

This section begins with a description of the standard workflow of S-TLS systems in

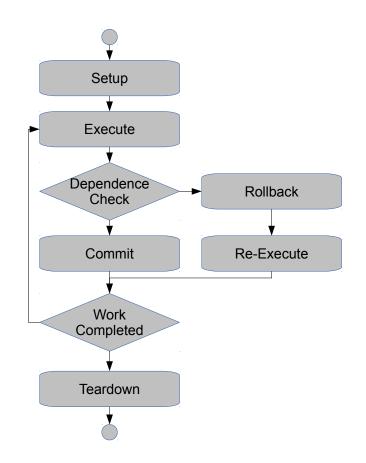

Figure 2.5: Generalised Workflow of Common Speculative Execution Schemes

Section 2.3.1, before analysing the effects on the ordering of that workflow in Section 2.3.2. A description of storage layouts used for speculative data is provided in Section 2.3.3 and then the various methods of synchronisation commonly used by S-TLS in Section 2.3.4. Next a description of the data structures used to store memory traces is given in Section 2.3.5 with an analysis of the techniques used to reduce the size of those structures and the hazards that can occur by doing so in Section 2.3.6. Finally a description of the version management methods used to provide the underlying safety of S-TLS is provided in Section 2.3.7.

## 2.3.1 Speculation Workflow

Thanks to the nature of speculative execution most schemes follow a similar pattern of execution. This general workflow can be seen in Figure 2.5. Execution of a program is split up into sequential, parallel and speculative sections based on the analysis performed on the program. When a speculative region of code is encountered the following stages are performed:

- (i) Set-up. At the start of speculative execution, or at some point prior, the structures necessary to store the speculative state are created and reset. These structures include, for example, memory trace logs and rollback/restore logs.

- (ii) Execution. Once ready, threads are created/assigned individual blocks of code and execution commences. During execution of the parallel section, each thread maintains a trace of the accesses to memory it performs. The number of accesses recorded can vary greatly dependent on the amount of analysis that can be performed statically, ranging from every access to only those of specific variables or even lines of code. Reads and writes are normally tracked separately so that they can be used to detect each different type of data dependence. Each thread often also maintains its own rollback or commit logs to be used in case a data dependence is detected, storing their own private copy of a memory location, or the original copy that they are modifying for use during the commit or rollback stages.

- (iii) Dependence Check. After execution, or at suitable intervals during execution, the memory traces for each thread are analysed to detect data dependences.

- (iv) Commit. After the dependence check has been performed and no data dependences have been discovered each thread's state has to be commited. Depending on how version control has been implemented this can involve writing back a thread's private copy of each memory location it modified, or it can simply involve discarding any rollback logs. After commit, each thread can be assigned more blocks to be executed speculatively, or if there is no more work to be executed then standard sequential or parallel execution continues.

- (v) **Rollback.** Should a dependence be detected during the check then a rollback will be triggered allowing the program to return to a previous state of execution before the dependence occurred. Being able to rollback to a prior state is the primary means of ensuring that every speculative section executes correctly and produces correct results. Rollback methods also depend upon how rollback or commit logs are created, and can involve simply discarding a thread's private copy of a memory location, or something more complex such as replaying all memory accesses between threads in reverse to restore them to their original values.

- (vi) Re-execution. After a rollback has been performed part or all of the speculative section is re-executed. Depending on the scheme this can be a safe, sequential execution, or an attempt at executing in parallel speculatively again. For instance, an iteration of a loop where a dependence was triggered by an earlier iteration that has now been committed may re-execute the current iteration again sequentially, or simply retry speculatively now that the earlier dependence triggering iteration has been committed.

- (vii) Teardown. Finally once the speculative section has finished executing correctly with no data dependences speculative structures are often reset ready for the next speculative execution. Occasionally these structures can be destroyed however this tends to be inefficient in cases where more than one speculative section may exist.

As mentioned, most speculation schemes follow this same pattern; however, they can involve more complex operations allowing stages to be merged. For example, execution and dependence detection can be merged allowing for dependences to be detected *on-the-fly*. This can be beneficial if dependences are likely as it restricts the amount of wasted execution, however it also makes each thread's execution more complex and slower. Similarly dependence detection, commit and rollback stages can be merged however this requires specifically designed trace and version control structures to allow this.

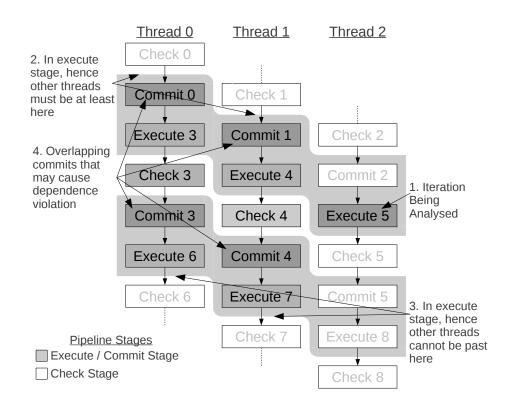

The inter-thread ordering of each stage can also vary for each speculative model with the use of synchronisation to enforce ordering for each. There are two main types that exist, block-based execution, and pipelining. In block-based execution every thread executes the same stage or set of stages at the same time. If a thread reaches the end of its block before the other threads it must wait until they have before progressing. Alternatively, each thread could be pipelined with synchronisation preventing later threads to get ahead of earlier threads. For example, several threads could be executing, whilst another thread is performing its dependence check and another thread is commiting back to memory.

## 2.3.2 When to Check

The most important design aspect of a speculative scheme is the timing of the dependence check. This aspect influences every other aspect of the scheme, including the type and layout of the memory traces, the synchronisation methods used, version control types chosen and even how accurate the tracing needs to be.

This aspect is largely influenced by the type and requirements of the code being parallelised and the machine that the program is being executed on. For instance a loop that has a very low chance of containing a data dependence would likely benefit from a delayed and optimised or *lazy* dependence check, however using a delayed check requires that memory traces need to be stored for longer and are likely to consume more memory. In contrast, a loop with a higher chance of containing a dependence may benefit from *on-the-fly* or *eager* checking so that the dependence is discovered more quickly, however this requires more computation on each access restricting possible performance gains.

This section describes each method and analyses how they are likely to influence the other design aspects and performance of a speculative scheme.

### 2.3.2.1 Lazy Checking

For many loops and programs *lazy checking* is a suitable choice for when to perform a dependence check. In lazy checking each speculative memory access is logged and stored into memory until it is ready to be used to scan for data dependences. Then, at some later point during execution the traces generated are analysed to detect if a data dependence has occurred and, if so, handle the situation appropriately.

Isolating the memory-trace and dependence-detection stages tends to create a scheme that is simpler to implement. Each speculative access is often cheaper as it is less likely to interact with or share data with other threads thereby reducing the amount of expensive synchronisation required. With lower synchronisation costs the scheme will scale to higher thread counts more easily. Lazy schemes are also more versatile as the delay between tracing and detection can be fine-tuned to suit a given program and architecture. Additionally, the delayed dependence check can be optimised to perform as a batch scan of all logged accesses.

However, overall lazy detection is more taxing on memory. The size of the delay influences the size of memory access trace logs. Not only does a larger delay result in more accesses being recorded, but the structures used must also be more accurate in recording the address of each access to prevent *false* dependences from being detected. Longer time before a check also generates longer commit or rollback logs further increasing memory usage.

Besides higher memory usage, lazy detection also increases the cost of version control. For instance a longer rollback log increases the amount of memory that has to be restored if a dependence were to be found. Or it will increase the amount of time spent committing an execution back to non-speculative memory. Lazy detection is often unable to account for *safe* data dependences as the order in which accesses have occurred has not been recorded.

The added versatility and flexibility of lazy checking also adds complexity to the configuration of a scheme. Most notably is the selection of a suitable checking interval. Common intervals can include:

- (i) Iteration Based. The dependence check is performed at the end of every iteration. This interval is used when a dependence is more likely to exist in a loop. It uses the least amount of memory for traces and version control and minimizes the amount of wasted computation in both execution and rollback should a dependence occur. It is, however, the most expensive interval in terms of synchronisation required between threads. It is also unsuitable to use during pipelined schemes as a way to hide critical sections in a scheme.

- (ii) Chunk Execution. This interval, sometimes called a *sliding window*, performs the dependence check after a set quantity or *chunk* of iterations. This interval increases the amount of memory required, however is a good compromise between memory, synchronisation and version control costs. It is also suitable for pipelined schemes that use critical sections as the cost of a critial section can be hidden amongst the execution of each chunk.

- (iii) Extreme Laziness. The dependence check can be left until the end of speculative execution, or until synchronisation points that are already inherently present in the parallel code. This method requires the least amount of additional synchronisation allowing for the fastest execution times. However, by leaving the dependence check until the last possible moment this method requires the largest mem-

ory traces, the longest dependence checks and the most expensive re-execution times. As an additional benefit, the complete isolation of the dependence check from speculative execution can allow for it to be performed independently of the rest of the program or even to be passed off to an auxiliary processing unit.

#### 2.3.2.2 Eager Checking

For some loops or schemes it may be necessary to perform the dependence check on every memory access. This may be due to a higher risk of a dependence existing, or memory limitations such as being too small or slow to access. This is called *eager checking*.

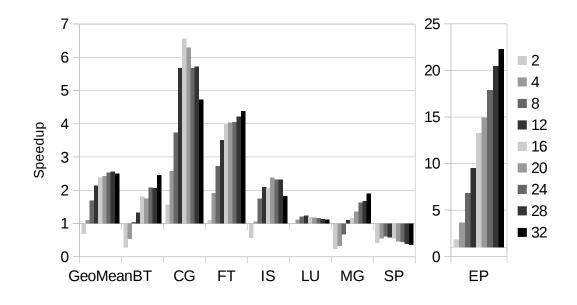

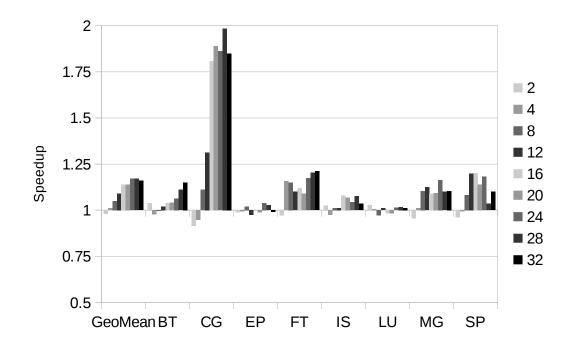

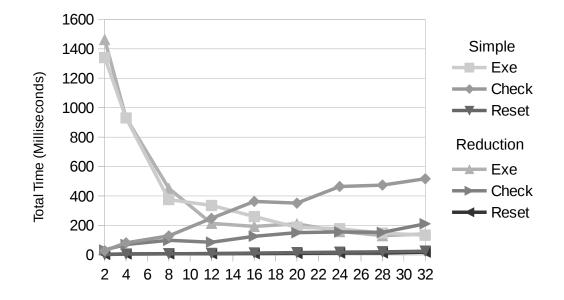

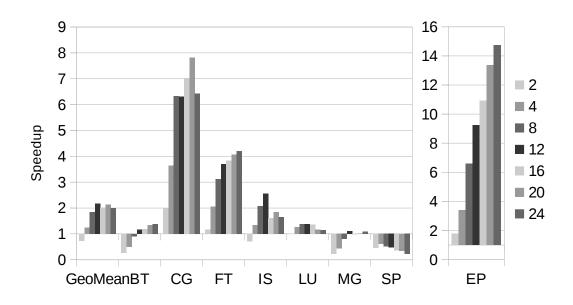

On most architectures the use of eager checking is more expensive as it places the dependence check directly on the critical path of execution, increasing the amount of computation required for each memory access. Additional pressure is also added to memory by increasing the amount of information that is shared between each thread, limiting scalability. Additional synchronisation is required in the form of atomic operations or memory fences to ensure correct operation, further limiting scalability.