# Design of an Asynchronous Processor

Christos Panagiotis Sotiriou

Doctor of Philosophy University of Edinburgh 2001

# Abstract

Designing performance-scalable computer architectures is becoming an increasingly complex problem in small dimension integrated circuits, as the effects of physical laws increasingly constrain circuit design and computer architecture.

This thesis investigates the implementation of asynchronous circuits and asynchronous computer architectures. In the area of asynchronous circuits, it proposes the direct-mapped approach to control circuit design, originally devised by Hollaar, mapped to CMOS technology. In the area of asynchronous computer architecture, it investigates scalable, concurrent computer architectures, with the aim of solving the problems of scaling performance and utilising the increasing device count. The design and implementation of two hardware structures, Shared Register Files and  $\mu$ net (micronet) architectures is detailed, together with their incorporation into the design of an asynchronous prototype processor, the A1 chip.

The Shared Register File approach provides a scalable and segmented datapath by partitioning the conventional monolithic register file into multiple register files which physically share registers. Communication and synchronisation between the shared register files takes place via the shared registers. This approach can be used to implement a clustered uniprocessor or a single-chip multiprocessor system. The shared register file approach allows for the exploitation of program level concurrency, where different parts of the same program or different programs can run on the different shared register file datapaths. The design and implementation of shared register files is presented.

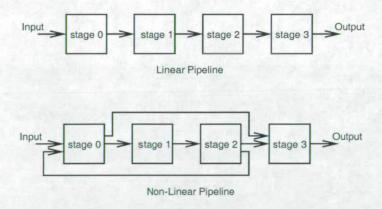

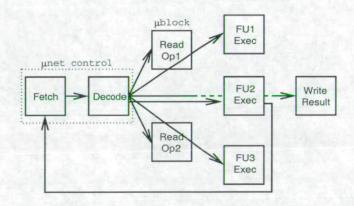

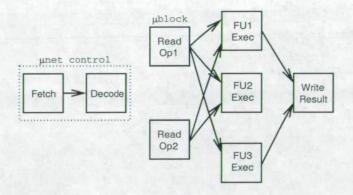

The  $\mu$ net approach is a methodology for asynchronous processor design, which allows fine-grain instruction level parallelism to be exploited. It implements a processor architecture as a non-linear pipeline with inputs at every pipeline stage. In this way, a  $\mu$ net architecture exploits more fine-grain parallelism than a conventional pipelined architecture. The design and implementation of generic, scalable  $\mu$ net architectures is described and evaluated.

# Acknowledgements

First and foremost I would like to thank my supervisor Prof. Roland N. Ibbett for his invaluable help, support and guidance. Without him this work would not have been possible.

I also want to thank my fellow PhD students, with which we became close friends, and everyone that made my stay in Edinburgh a very special and memorable time.

Finally, I would like to thank my family for all their help and support.

# Declaration

I declare that this thesis has been composed by myself and all the work contained in this thesis is my own, except where otherwise stated in the text.

Christos Panagiotis Sotiriou

# Table of Contents

| List of | Figure  | es                                              | 5  |

|---------|---------|-------------------------------------------------|----|

| List of | Tables  |                                                 | 10 |

| Chapte  | er 1 In | ntroduction                                     | 11 |

| 1.1     | Scalab  | le Architectures                                | 11 |

|         | 1.1.1   | Scalability in Architectures                    | 11 |

|         | 1.1.2   | Scaling Performance                             | 12 |

|         | 1.1.3   | Architectures of today and tomorrow             | 15 |

|         | 1.1.4   | The Rôle of the Register File                   | 17 |

|         | 1.1.5   | Alternatives to the MRF                         | 18 |

| 1.2     | The SI  | RF Approach                                     | 20 |

|         | 1.2.1   | Register Windows                                | 20 |

|         | 1.2.2   | Overlapping or Shared Register Files            | 21 |

|         | 1.2.3   | SRFs in Architectures                           | 22 |

| 1.3     | Timing  | g in Circuits and Architectures                 | 23 |

|         | 1.3.1   | Synchronous Systems                             | 23 |

|         | 1.3.2   | Asynchronous Systems                            | 24 |

| 1.4     | Asynch  | pronous Processors                              | 25 |

| 1.5     | Aims o  | of the thesis                                   | 27 |

| 1.6     | Thesis  | Structure                                       | 28 |

| Chapte  | er 2 A  | synchronous Direct-Mapped Finite-State Machines | 29 |

| 2.1     |         | Circuit Design                                  | 29 |

| 2.2     |         | Specification Methods                           | 30 |

| 2.3     |         | nentation of Digital Control Circuits           | 31 |

|         | 2.3.1   | Transistors and Logic Gates                     | 31 |

|         | 2.3.2   | Combinational Logic                             | 32 |

|         | 2.3.3   | Sequential Logic                                | 32 |

| 2.4     |         | Implementation Problems                         | 33 |

|     | 2.4.1 Hazards                                         | 34 |

|-----|-------------------------------------------------------|----|

|     | 2.4.2 Races                                           | 36 |

|     | 2.4.3 Example                                         | 36 |

| 2.5 | Delay Models                                          | 39 |

| 2.6 | Modes of Operation of Sequential Circuits             | 39 |

|     | 2.6.1 Synchronous Circuits                            | 40 |

|     | 2.6.2 Asynchronous Circuits                           | 41 |

| 2.7 | Asynchronous Finite State Machines                    | 41 |

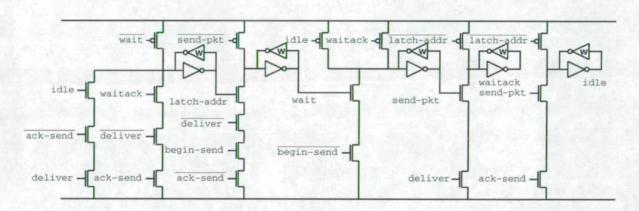

| 2.8 | Asynchronous CMOS Direct-Mapped FSMs                  | 46 |

|     | 2.8.1 Domino CMOS Structure                           | 47 |

|     | 2.8.2 CMOS Direct-Mapped AFSMs                        | 48 |

|     | 2.8.3 The CMOS Direct-Mapped Approach                 | 50 |

|     | 2.8.4 Comparison with other implementation techniques | 60 |

|     | 2.8.5 Automating the CMOS Direct-Mapped Approach      | 67 |

| 2.9 | Conclusions                                           | 68 |

| C)  |                                                       |    |

|     | er 3 Asynchronous Processor Design                    | 70 |

| 3.1 | Fundamentals of Asynchronous Systems                  | 70 |

|     | 3.1.1 Communication and Synchronisation               | 70 |

|     | 3.1.2 Completion Detection                            | 71 |

| 0.0 | 3.1.3 Arbitration                                     | 73 |

| 3.2 | Asynchronous Processor Design                         | 74 |

|     | 3.2.1 Pipelining                                      | 74 |

|     | 3.2.2 Synchronous Pipelining                          | 75 |

|     | 3.2.3 Asynchronous Pipelining                         | 75 |

|     | 3.2.4 Instruction Pipelines                           | 76 |

| 0.0 | 3.2.5 Instruction Pipeline Hazards                    | 77 |

| 3.3 | The $\mu$ net (micronet) architectural approach       | 77 |

| 3.4 | μnet Structure                                        | 78 |

| 3.5 | $\mu$ operations                                      | 79 |

| 3.6 | $\mu$ operation Dependencies                          | 79 |

| 3.7 | Generic $\mu$ net Implementation                      | 80 |

|     | 3.7.1 $\mu$ net Control Implementation                | 81 |

|     | 3.7.2 $\mu$ net Data Registers                        | 82 |

| 3.8 | Scaling a $\mu$ net Datapath                          | 83 |

|     | 3.8.1 Implementing a Scalable $\mu$ net Datapath      | 83 |

|     | 3.8.2 Multiple $\mu$ net Datapaths                    | 87 |

| 3.9 | Shared Register Files                                 | 88 |

|    |       | 3.9.1   | Concept of register sharing               | 9 |

|----|-------|---------|-------------------------------------------|---|

|    |       | 3.9.2   | Possible Sharing Schemes                  | 9 |

|    |       | 3.9.3   | SRF design                                | 1 |

|    |       | 3.9.4   | SRF and MRF issues                        | 1 |

|    |       | 3.9.5   | Asynchronous vs. Synchronous SRFs 95      | 2 |

|    | 3.10  | Conclu  | isions                                    | 3 |

| Cl | napte | er 4 In | mplementation of Shared Register Files 94 | 1 |

|    | 4.1   | Asyncl  | hronous SRF Circuit Design                | 4 |

|    |       | 4.1.1   | Completion Detection                      | 7 |

|    |       | 4.1.2   | Control Circuitry                         | 8 |

|    |       | 4.1.3   | The 2-way sharing organisation            | 9 |

|    |       | 4.1.4   | The 1-way sharing organisation            | 5 |

|    |       | 4.1.5   | The 4-way sharing organisation 10'        | 7 |

|    |       | 4.1.6   | SRF Access Times                          | 8 |

|    | 4.2   | Effecti | veness of SRFs in a system                | 0 |

|    |       | 4.2.1   | SRF Performance Metrics                   | 0 |

|    |       | 4.2.2   | SRF Performance                           | 0 |

|    | 4.3   |         | r SRF 2-way System                        | 5 |

|    | 4.4   | Bus-B   | ased Systems                              | 1 |

|    |       | 4.4.1   | Implementation                            | 4 |

|    | 4.5   | Conclu  | asions                                    | 2 |

| Cl | napte | er 5 I  | The A1 Processor Design 133               | 3 |

|    | 5.1   | The A   | 1 Prototype Chip                          | 3 |

|    | 5.2   | The A   | 1 Architecture                            | 5 |

|    | 5.3   |         | ction Flow and Execution                  | 0 |

|    |       | 5.3.1   | $\mu$ operation Issue                     | 0 |

|    |       | 5.3.2   | Operand Fetch                             | 1 |

|    |       | 5.3.3   | Operand Data Arrival                      | 2 |

|    |       | 5.3.4   | Functional Unit Execution                 | 2 |

|    |       | 5.3.5   | Result Data Arrival                       | 3 |

|    |       | 5.3.6   | Result Write-back                         | 1 |

|    |       | 5.3.7   | Register Locking Mechanism                | 1 |

|    | 5.4   | Proces  | ssor Components                           | 5 |

|    |       | 5.4.1   | Data Registers                            | 5 |

|    |       | 5.4.2   | $\mu$ controllers                         | 3 |

|    |       | 5.4.3   | Processor Control Unit                    | 3 |

|         | 5.4.4  | Processor Control Unit Simulation                     |

|---------|--------|-------------------------------------------------------|

|         | 5.4.5  | Memory Interface                                      |

|         | 5.4.6  | Write-Back Unit                                       |

|         | 5.4.7  | 32-bit and 8-bit Adders with Completion Detection 166 |

|         | 5.4.8  | 32-bit Comparator with Completion Detection 173       |

|         | 5.4.9  | Shared Register Files                                 |

| 5.5     | A1 Tes | sting and Simulations                                 |

|         | 5.5.1  | Simple Program Test                                   |

|         | 5.5.2  | SRF Addition Test                                     |

| 5.6     | Conclu | sions                                                 |

| Chapte  | er 6 C | Conclusions and Future Work 188                       |

| 6.1     | A1 Ev  | aluation                                              |

|         | 6.1.1  | Parallelism                                           |

|         | 6.1.2  | Performance                                           |

|         | 6.1.3  | Design Problems                                       |

|         | 6.1.4  | Silicon Areas                                         |

|         | 6.1.5  | Testing                                               |

| 6.2     | Future | Work                                                  |

|         | 6.2.1  | Shared Register File Architectures                    |

|         | 6.2.2  | $\mu$ net Architectures                               |

| 6.3     | Conclu | sions                                                 |

| Bibliog | graphy | 196                                                   |

# List of Figures

|      | - 1.1.kg : 1.1 kg : 1 |    |

|------|-----------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Example Limited Connectivity VLIW Architecture                                                                  | 19 |

| 1.2  | Clustered Queue Register File Architecture                                                                      | 19 |

| 1.3  | Part of a dual-node Multicluster Architecture                                                                   | 19 |

| 1.4  | Example Multiscalar Architecture                                                                                | 20 |

| 1.5  | Partitioned Register File Architecture                                                                          | 20 |

| 1.6  | Register Windows                                                                                                | 21 |

| 1.7  | Shared Register Files                                                                                           | 22 |

| 2.1  | Truth Table for an AND gate                                                                                     | 30 |

| 2.2  | Flow Table for a 2-bit grey-code Counter                                                                        | 31 |

| 2.3  | State Diagram for 2-bit Counter                                                                                 | 31 |

| 2.4  | Different Realisations of a.b+c                                                                                 | 32 |

| 2.5  | Complex CMOS Gate Structure                                                                                     | 33 |

| 2.6  | General Form of a Sequential Circuit or FSM                                                                     | 33 |

| 2.7  | Combinational Hazards                                                                                           | 34 |

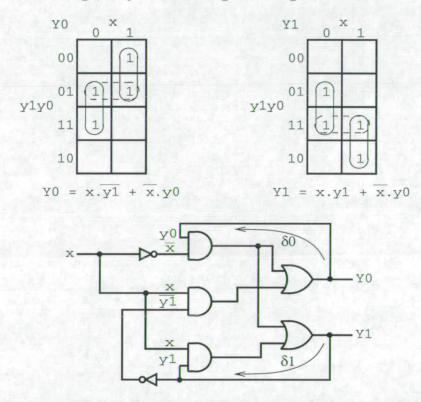

| 2.8  | Flow Table for a 2-bit grey-code Counter                                                                        | 37 |

| 2.9  | Realisation of the 2-bit grey-code Counter                                                                      | 37 |

| 2.10 | Hazard-Free Realisation of the 2-bit grey-code Counter                                                          | 38 |

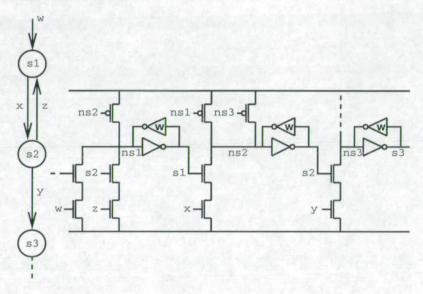

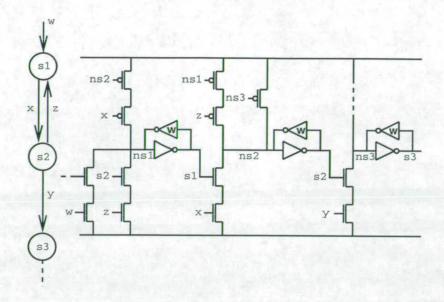

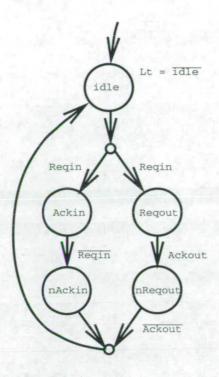

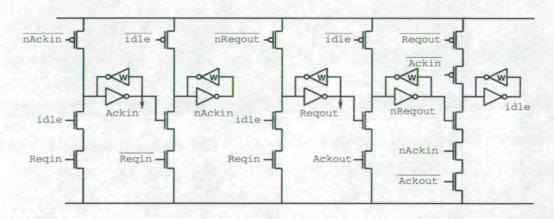

| 2.11 | Hollaar's One-hot AFSM Example                                                                                  | 45 |

| 2.12 | Scale-of-two loop implementation                                                                                | 46 |

| 2.13 | Properly functioning scale-of-two loop                                                                          | 47 |

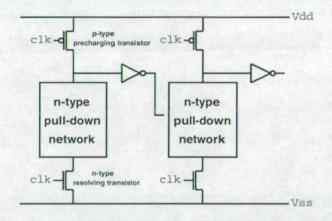

| 2.14 | Synchronous Domino CMOS Structure                                                                               | 47 |

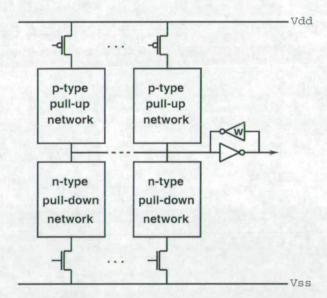

| 2.15 | Asynchronous Direct-Mapped State Gate                                                                           | 48 |

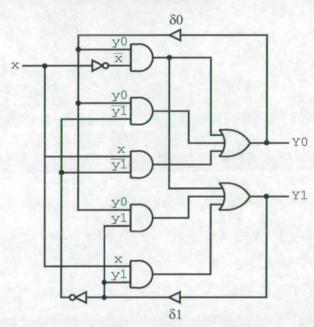

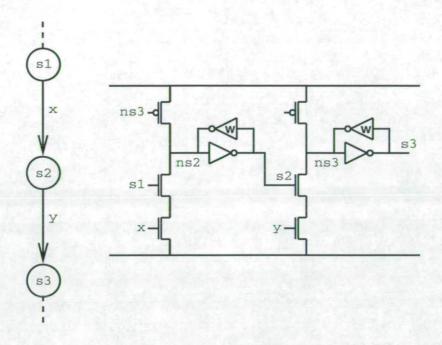

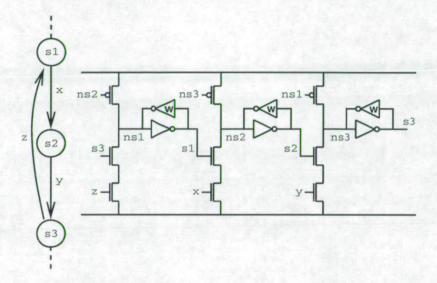

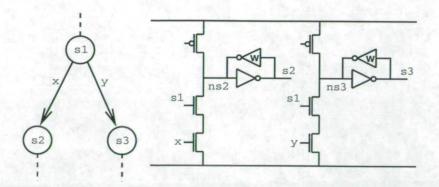

| 2.16 | Asynchronous Direct-Mapped Example                                                                              | 51 |

| 2.17 | Closed Loop Example                                                                                             | 52 |

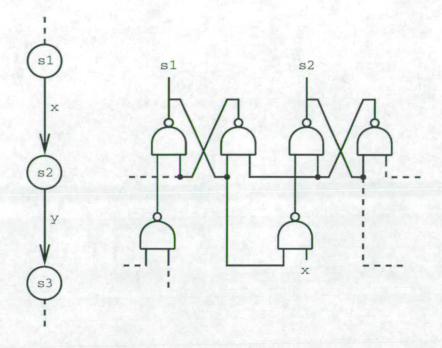

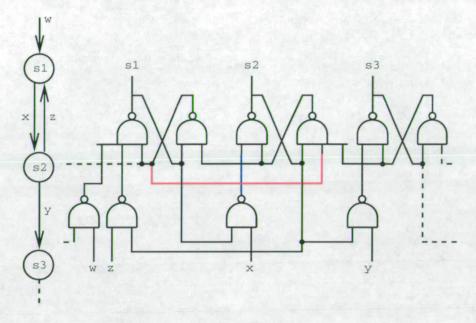

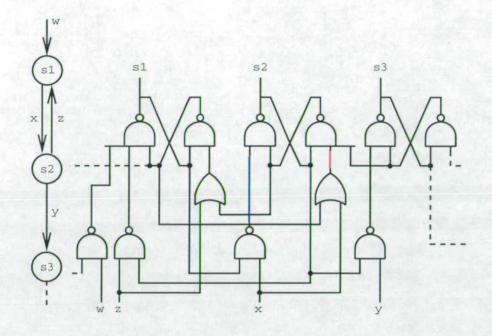

| 2.18 | Parallel Path Expansion Example, states s2 and s3                                                               | 53 |

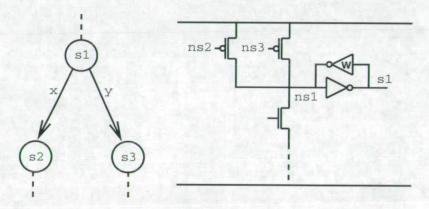

| 2.19 | Parallel Path Expansion Example, state s1                                                                       | 53 |

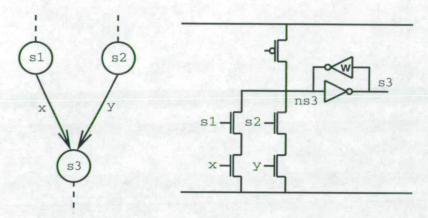

| 2.20 | Parallel Path Merging Example, state s3                                                                         | 54 |

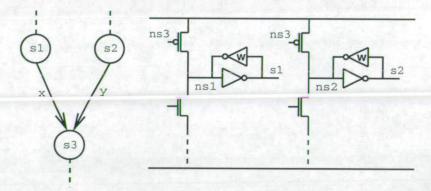

| 2.21 | Parallel Path Merging Example, states s1 and s2                                                                 | 54 |

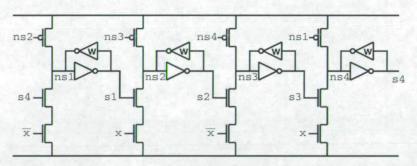

| 2.22 | Scale-of-two loop CMOS implementation                                                                           | 55 |

| 2.23 | Properly Functioning Scale-of-two loop                          | 56 |

|------|-----------------------------------------------------------------|----|

|      | Flow Table for a 2-bit grey-code Counter                        | 59 |

| 2.25 | Four State Counter                                              | 59 |

| 2.26 | Semi-decoupled latch controller using asymmetric C-gates        | 61 |

| 2.27 | Structure of an asymmetric C-gate                               | 61 |

| 2.28 | State graph for semi-decoupled latch controller                 | 62 |

| 2.29 | Semi-decoupled latch controller using DM-AFSMs                  | 62 |

| 2.30 | Fully-decoupled latch controller using asymmetric C-gates       | 63 |

| 2.31 | State graph for fully-decoupled latch controller                | 64 |

| 2.32 | Fully-decoupled latch controller using DM-AFSMs                 | 64 |

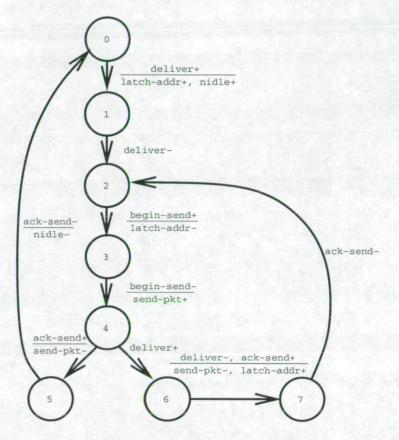

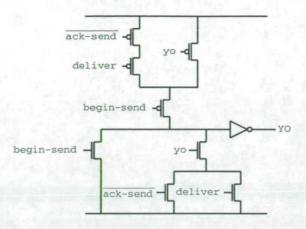

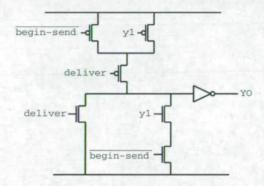

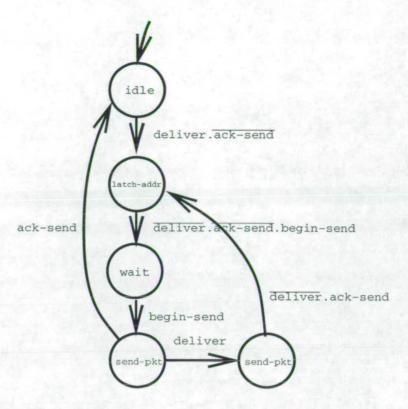

| 2.33 | Sbuf-send-ctl Burst-mode AFSM (Davis et. al)                    | 65 |

| 2.34 | Sum-of-Products realisation for output Y0 of Sbuf-send-ctl AFSM | 66 |

| 2.35 | Sum-of-Products realisation for output Y1 of Sbuf-send-ctl AFSM | 66 |

| 2.36 | Sbuf-send-ctl minimised AFSM state graph                        | 67 |

| 2.37 | Sbuf-send-ctl minimised AFSM state graph                        | 67 |

| 2.38 | CMOS Direct-Mapped AFSM Synthesis Tool CDL/Spice Output         | 69 |

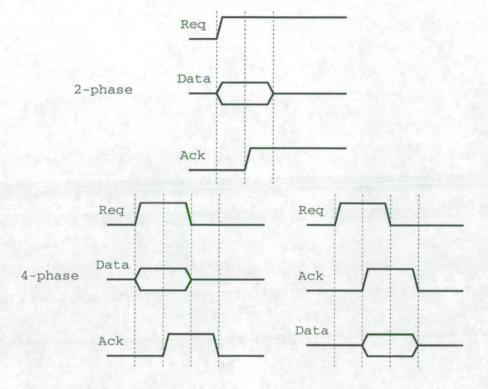

| 3.1  | 2 and 4-phase Handshaking Protocols                             | 71 |

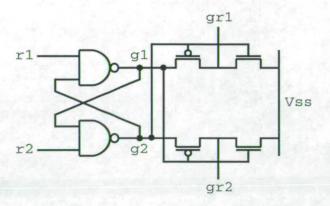

| 3.2  | Mutual Exclusion Element                                        | 74 |

| 3.3  | Linear and Non-Linear Pipelines                                 | 74 |

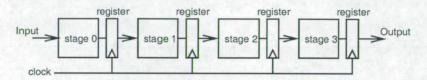

| 3.4  | Synchronous Pipeline Implementation                             | 75 |

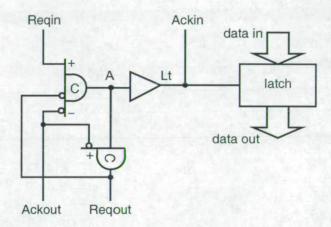

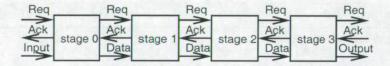

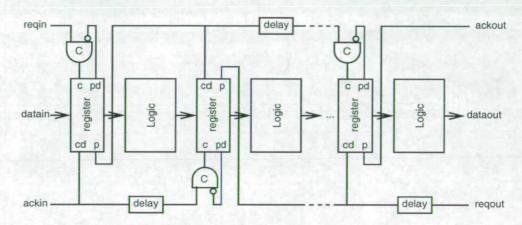

| 3.5  | Asynchronous Pipeline Implementation                            | 75 |

| 3.6  | Two-Phase Micropipeline Implementation                          | 76 |

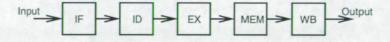

| 3.7  | A typical Instruction Pipeline                                  | 76 |

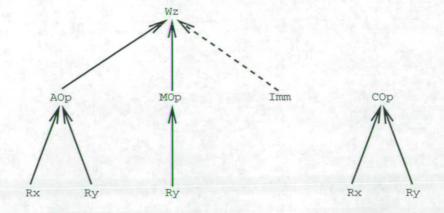

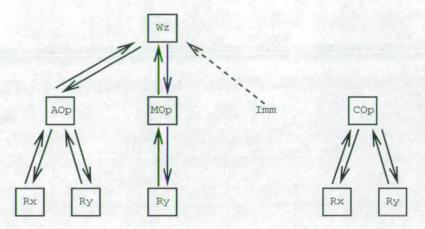

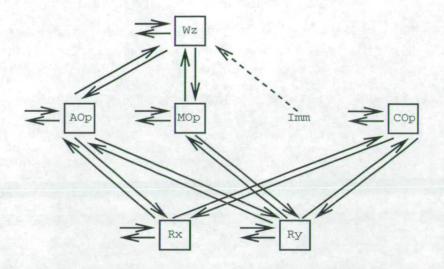

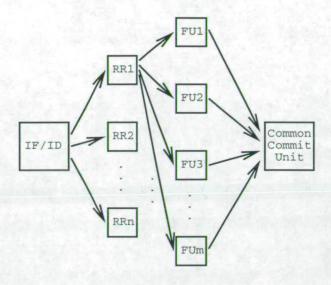

| 3.8  | Example of a $\mu$ net Architecture - $\mu$ operation Issue     | 78 |

| 3.9  | Example of a $\mu$ net Architecture - Datapath Handshakes       | 78 |

|      | $\mu$ operation Dependencies in the A1 Processor                | 80 |

|      | Operation Dependencies in a pipeline                            | 80 |

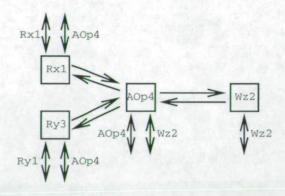

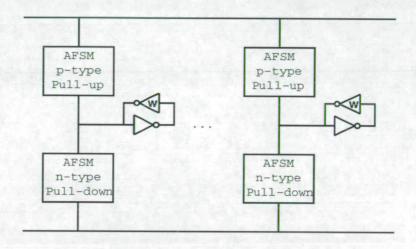

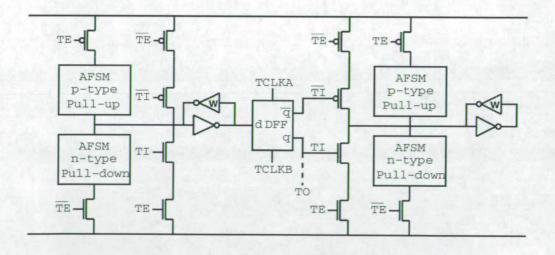

|      | $\mu$ operation Control Implementation                          | 82 |

|      | $\mu$ operation Detailed Control Implementation                 | 83 |

|      | Example FSM of a unit selection circuit                         | 84 |

|      | Example of a scaled $\mu$ net implementation                    | 86 |

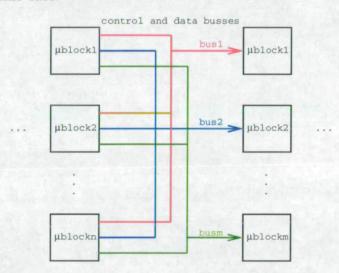

|      | Part of a scalable $\mu$ net implementation                     | 87 |

|      | Bus Interconnections in a scaled $\mu$ net implementation       | 87 |

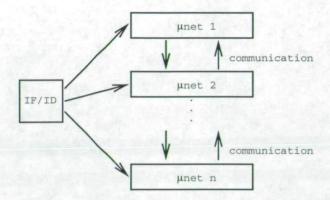

|      | Multiple $\mu$ net Architecture                                 | 88 |

|      | Register Sharing: Unidirectional                                | 89 |

|      | Register Sharing: Bidirectional                                 | 90 |

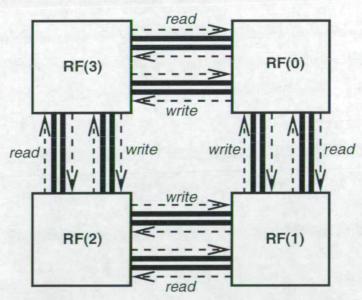

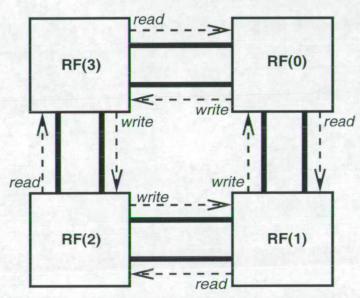

|      | Register Sharing: 4-way                                         | 91 |

|      |                                                                 | 01 |

| 4.1  | Register Sharing: Bidirectional                                       | 95  |

|------|-----------------------------------------------------------------------|-----|

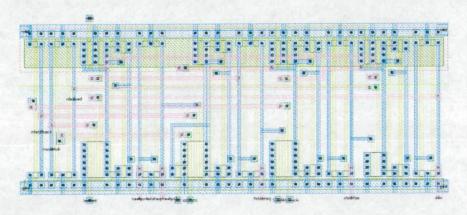

| 4.2  | 1-bit register cell layout                                            | 96  |

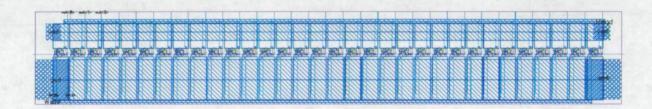

| 4.3  | 32-bit register cell                                                  | 96  |

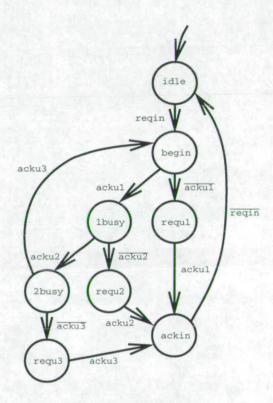

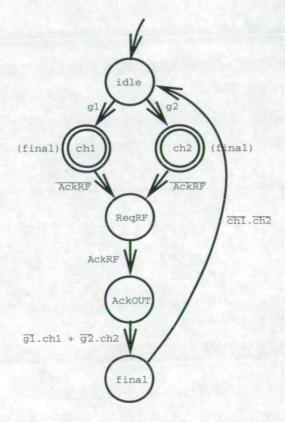

| 4.4  | FSM of read/write port logic                                          | 98  |

| 4.5  | Layout of the read/write port logic                                   | 99  |

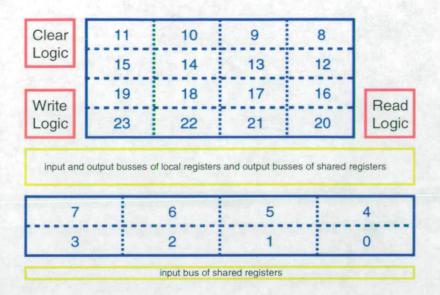

| 4.6  | Bidirectional Connectivity Diagram                                    | 100 |

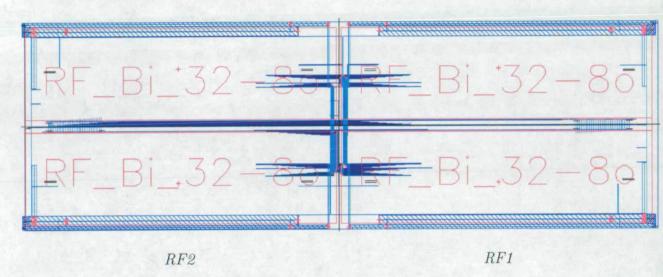

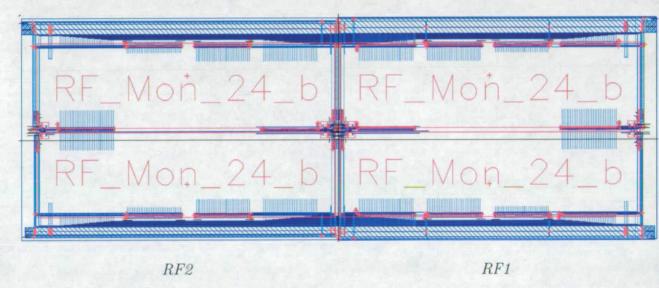

| 4.7  | Bidirectional Register File Floorplan - 16 local, 8 shared registers. | 101 |

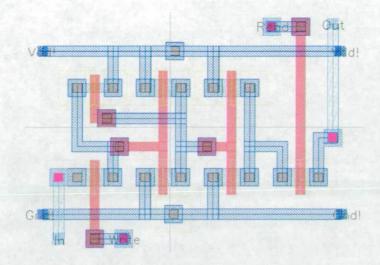

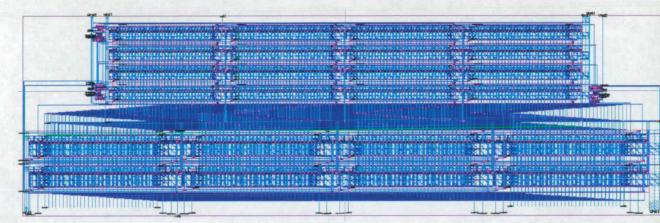

| 4.8  | Bidirectional Register File Layout - 16 local, 8 shared registers     | 101 |

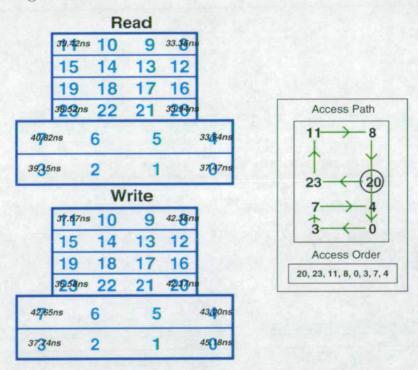

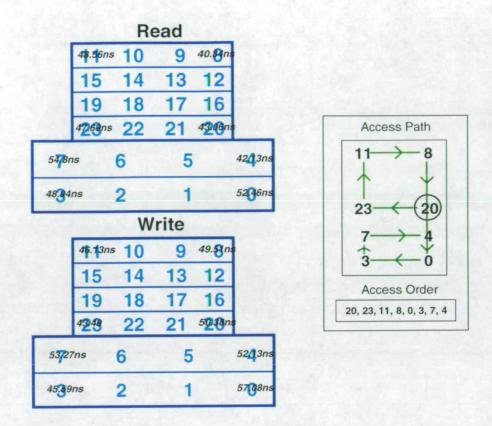

| 4.9  | Access Time Map for the 16/8, 2-way Shared RF                         | 103 |

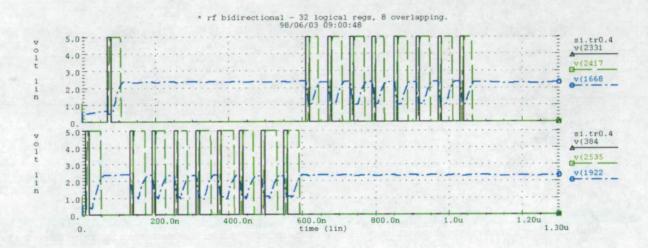

| 4.10 | Access Time Measurement Waveforms                                     | 104 |

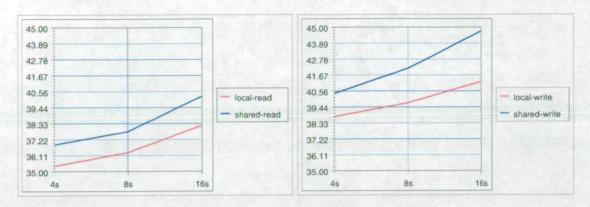

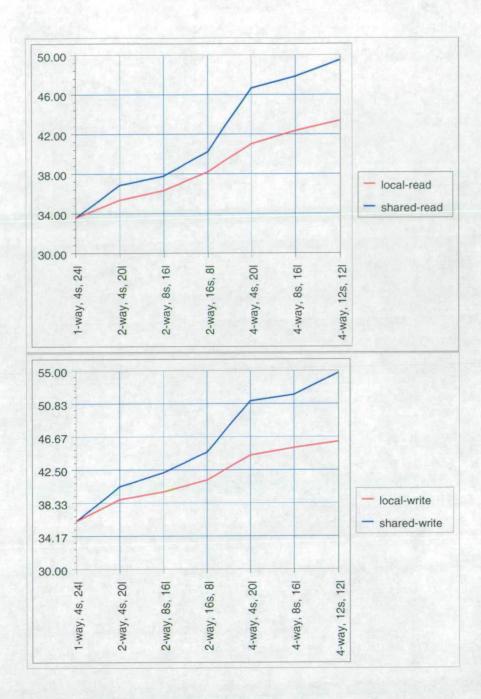

| 4.11 | Access times(ns) for 2-way SRF with 4, 8 and 16 shared registers      | 105 |

| 4.12 | Unidirectional Register File Layout - 28 local, 4 shared registers    | 106 |

| 4.13 | 4-way Connectivity Diagram                                            | 107 |

| 4.14 | 4-way Register File Layout - 16 local, 8 shared registers             | 108 |

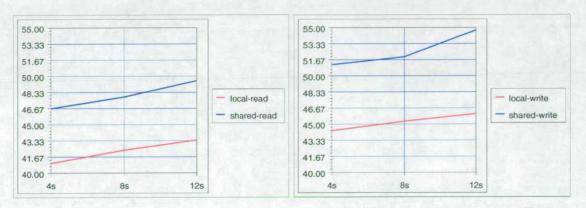

| 4.15 | Access times(ns) for 4-way SRF with 4, 8 and 12 shared registers      | 108 |

| 4.16 | Average Access Times in ns for Local and Shared Registers             | 109 |

| 4.17 | Execution of a program that adds 8 numbers                            | 112 |

| 4.18 | Program execution on 2 nodes of a 4 node, 2-way organisation          | 113 |

| 4.19 | Program execution on 4 nodes of a 4 node, 2-way organisation          | 113 |

| 4.20 | Program execution on 4 nodes of a 4-way organisation                  | 114 |

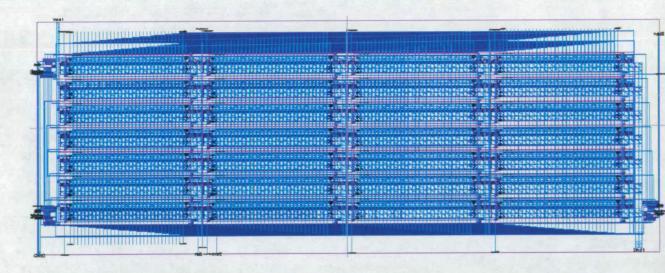

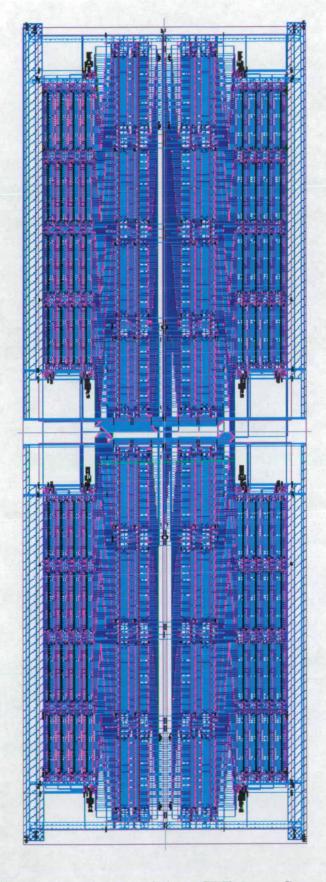

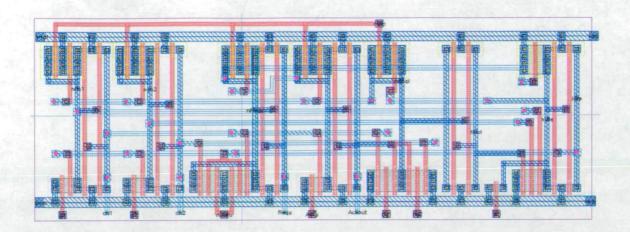

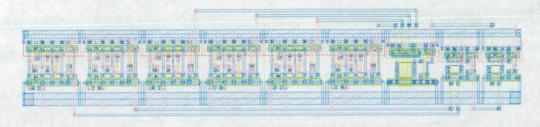

| 4.21 | Layout of the 4 SRF 2-way System                                      | 116 |

| 4.22 | Top level Connectivity of the 4 SRF 2-way system                      | 117 |

| 4.23 | Four MRF 2-way Bus System                                             | 122 |

| 4.24 | Four MRF Unidirectional Bus System                                    | 123 |

| 4.25 | Arbitration control circuit FSM for Bus System Ports                  | 125 |

| 4.26 | Arbitration control circuit layout for Bus System Ports               | 126 |

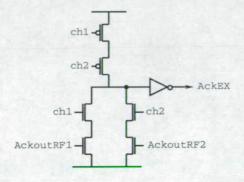

| 4.27 | RF acknowledgement gate                                               | 126 |

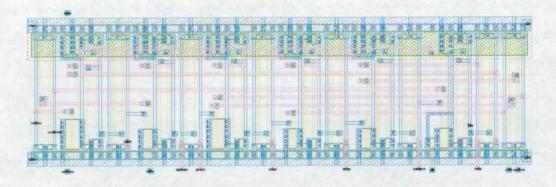

| 4.28 | Layout of the 4 MRF Arbitrated Bus System                             | 127 |

| 4.29 | Top level Connectivity of the 4 MRF Arbitrated Bus system $\dots$     | 128 |

| 4.30 | Program execution on 4 nodes of a 4 node, MRF bus organisation        | 131 |

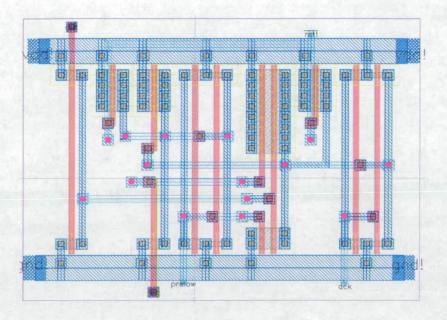

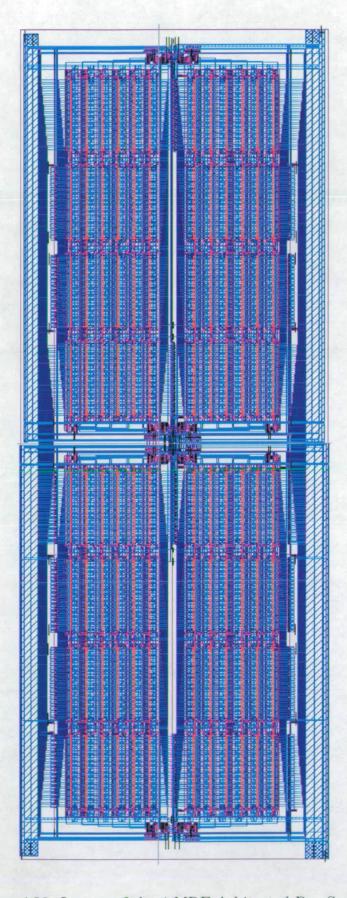

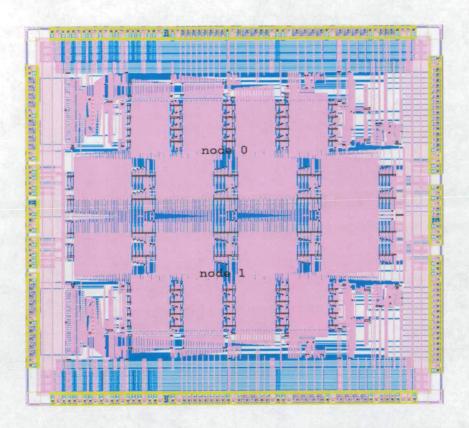

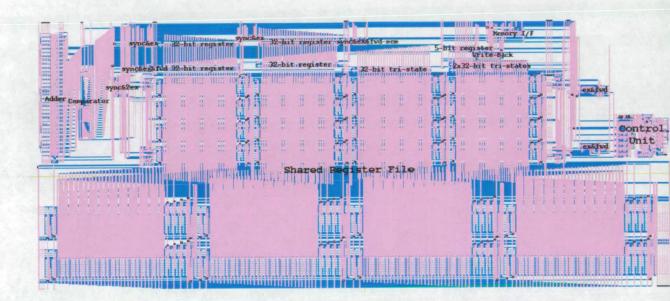

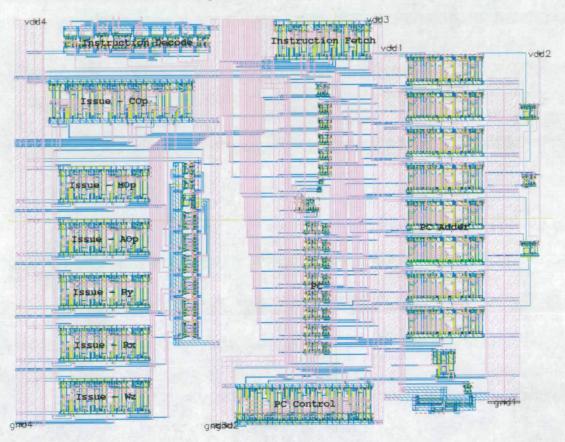

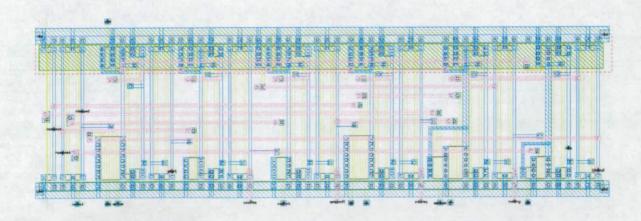

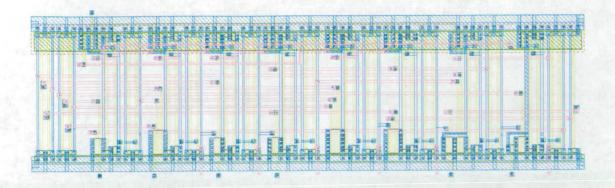

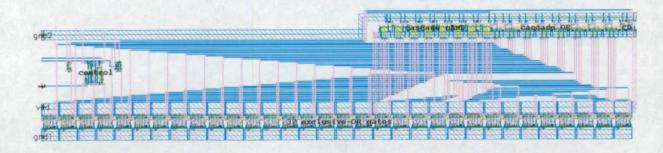

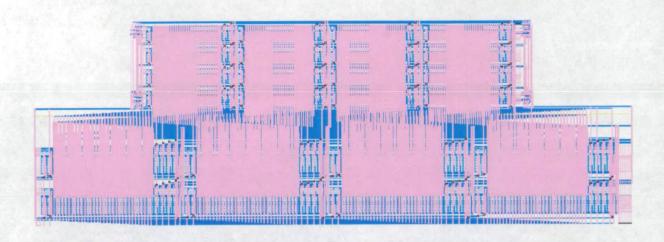

| 5.1  | The A1 Prototype top-level Chip Layout                                | 134 |

| 5.2  | The A1 Prototype top-level Hierarchy                                  | 134 |

| 5.3  | Processor node layout                                                 | 135 |

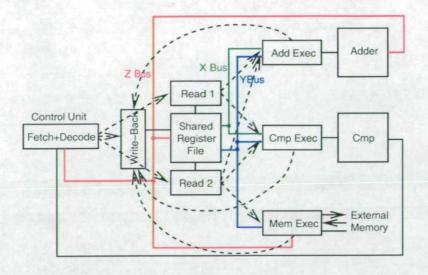

| 5.4  | High-level Diagram of an A1 node                                      | 136 |

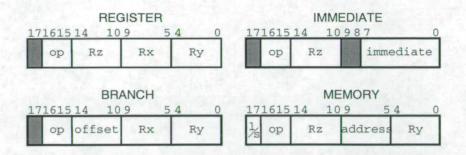

| 5.5  | A1 Instruction Formats                                                | 137 |

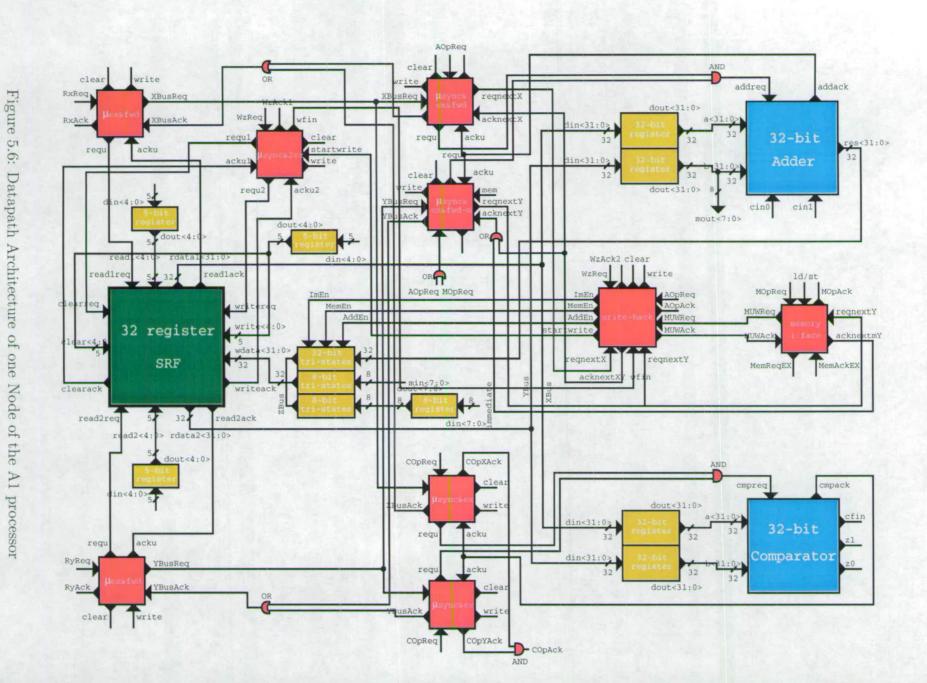

| 5.6  | Datapath Architecture of one Node of the A1 processor                 | 138 |

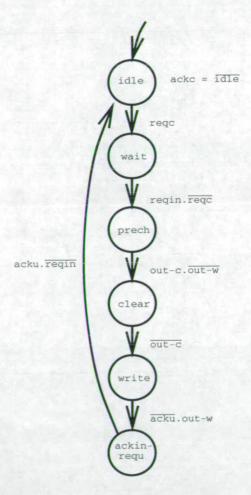

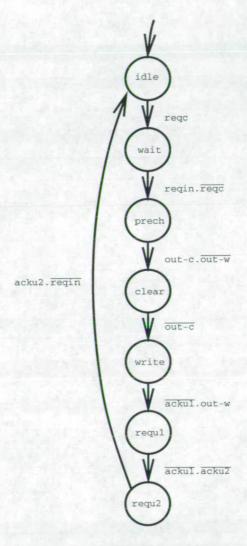

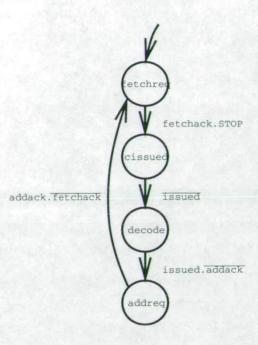

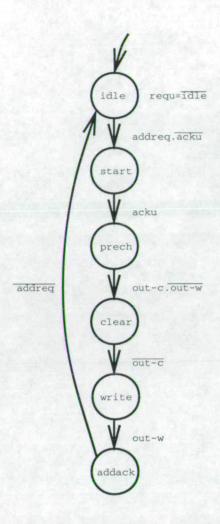

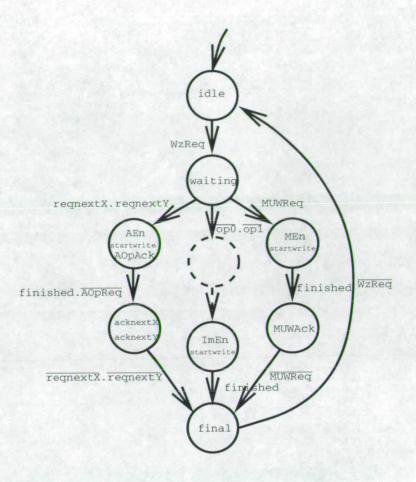

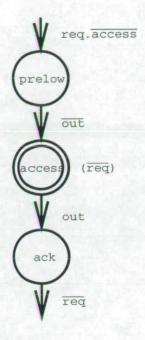

| 5.7  | FSM of $\mu$ sync&ex control circuit                                  | 146 |

|      |                                                                       |     |

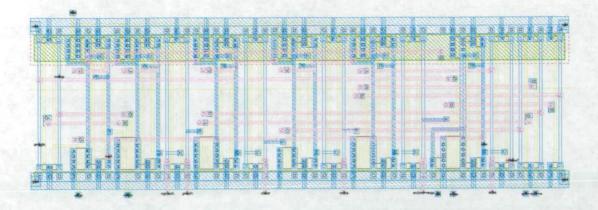

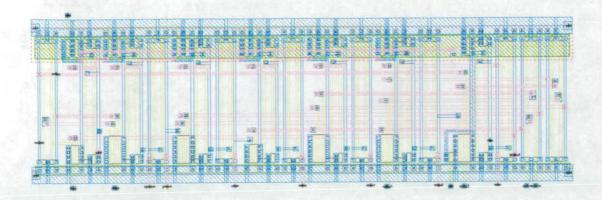

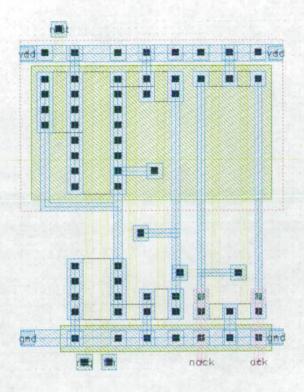

| 5.8  | Layout of $\mu$ sync&ex control circuit                       | 147 |

|------|---------------------------------------------------------------|-----|

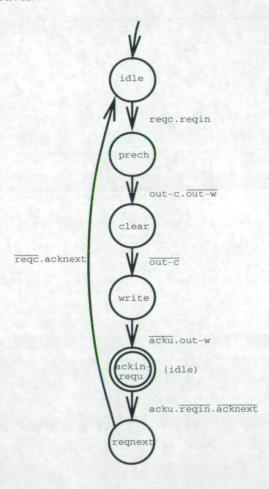

| 5.9  | FSM of $\mu$ sync&ex&fwd control circuit                      | 148 |

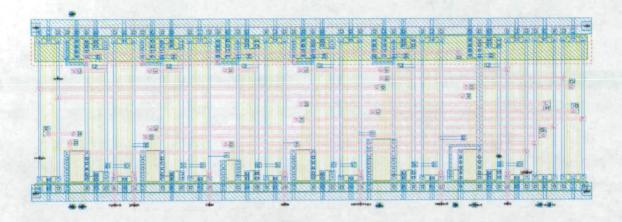

| 5.10 | Layout of $\mu$ sync&ex&fwd control circuit                   | 149 |

| 5.11 | FSM of $\mu$ sync&2ex control circuit                         | 150 |

| 5.12 | Layout of $\mu$ sync&2ex control circuit                      | 151 |

| 5.13 | FSM of $\mu$ sync&ex&fwd-m control circuit                    | 151 |

| 5.14 | Layout of $\mu$ sync&ex&fwd-m control circuit                 | 152 |

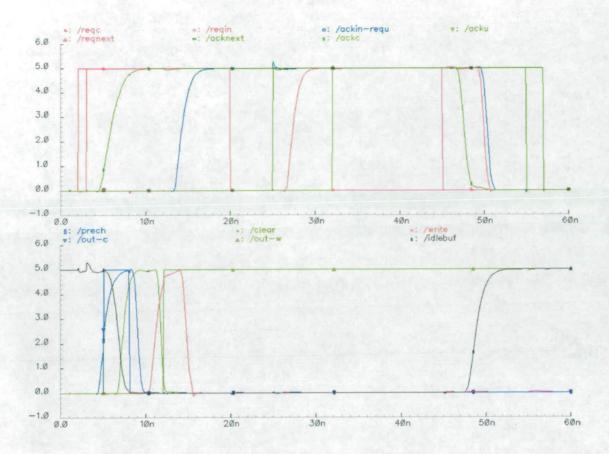

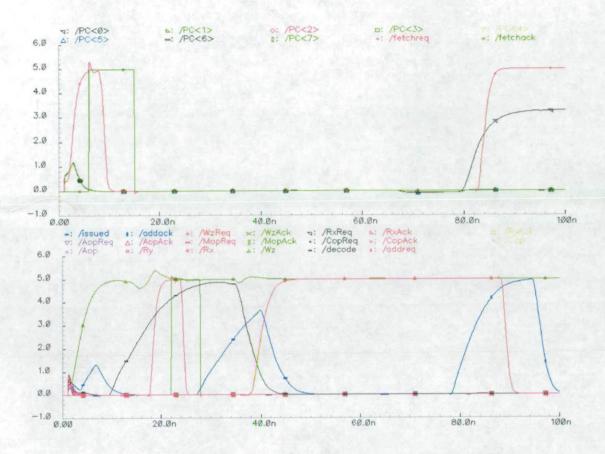

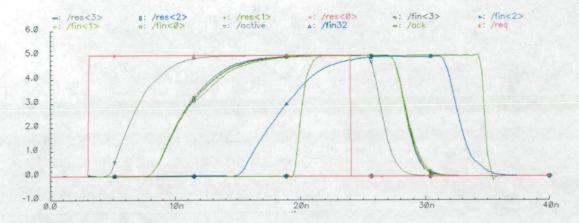

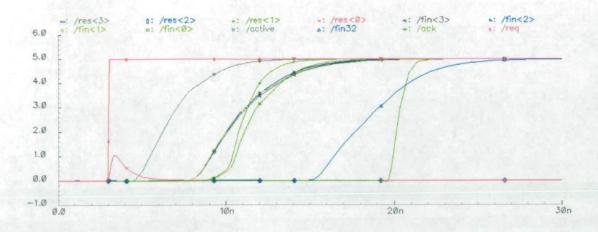

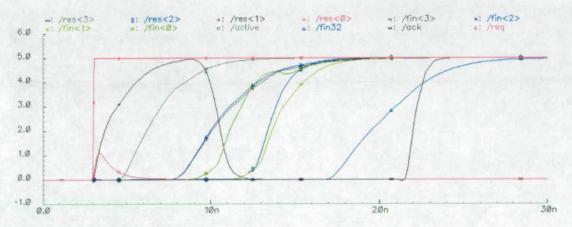

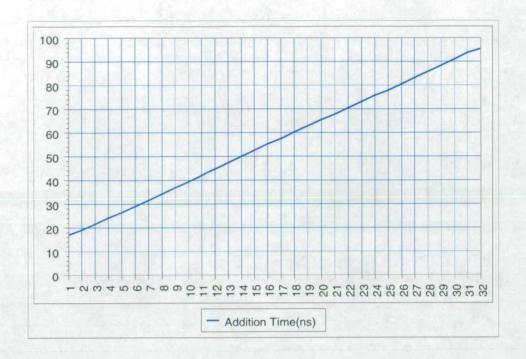

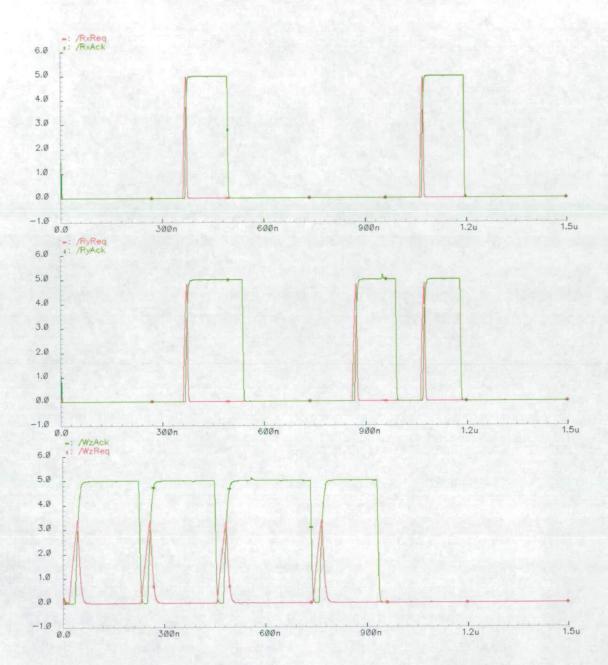

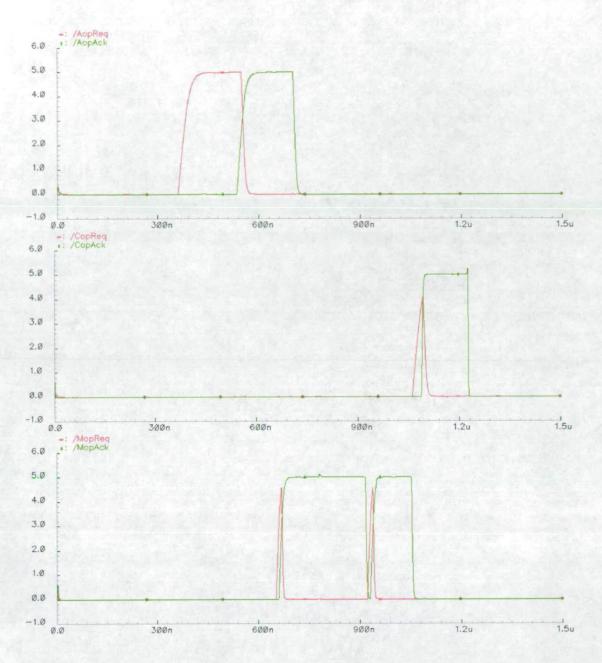

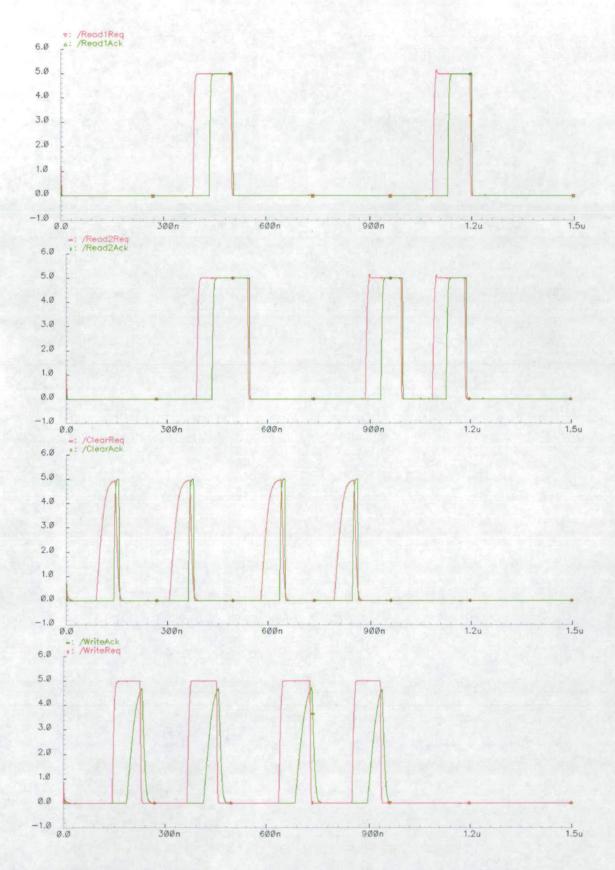

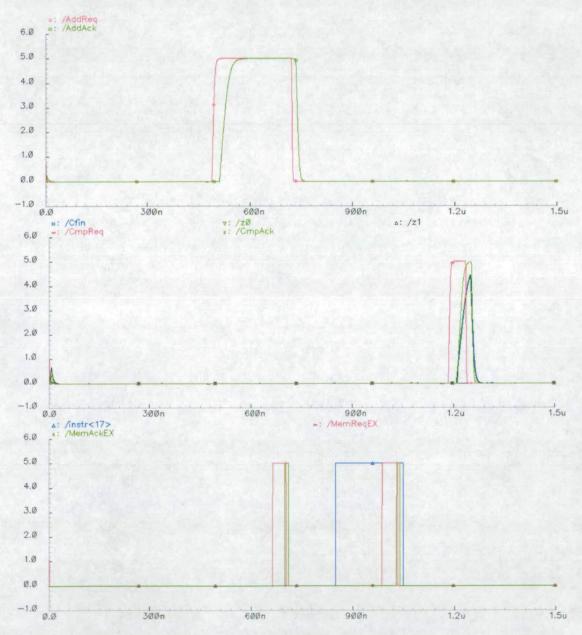

| 5.15 | Simulation of the $\mu$ sync&ex&fwd control circuit           | 153 |

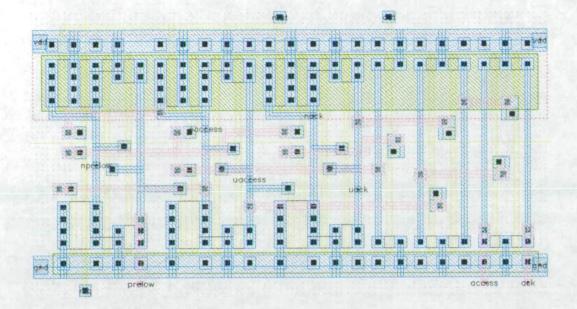

| 5.16 | Control Unit Layout                                           | 154 |

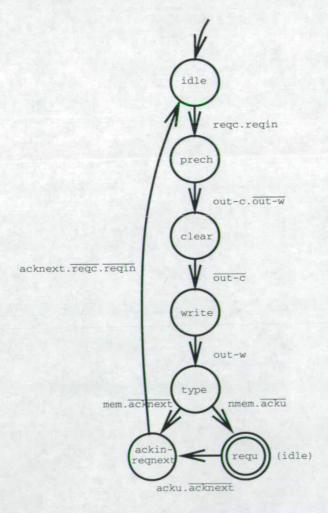

| 5.17 | FSM of the instruction fetch and issue control circuit        | 155 |

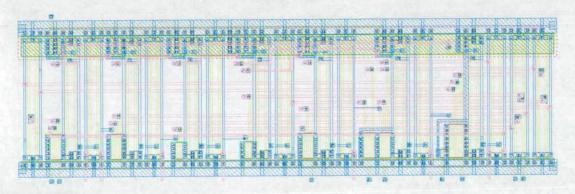

| 5.18 | Layout of the instruction fetch and issue control circuit     | 155 |

| 5.19 | Instruction decode combinational logic equations              | 156 |

| 5.20 | Layout of the instruction decode circuit                      | 156 |

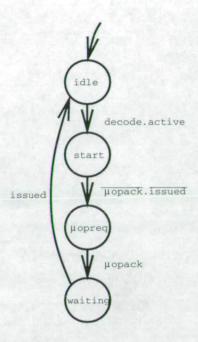

| 5.21 | FSM of the $\mu$ operation issue circuit                      | 157 |

| 5.22 | Layout of the $\mu$ operation issue circuit                   | 157 |

| 5.23 | FSM of the COp $\mu$ operation issue circuit                  | 158 |

| 5.24 | Layout of the COp $\mu$ operation issue circuit               | 158 |

| 5.25 | Layout of the $\mu$ operation issue circuit                   | 159 |

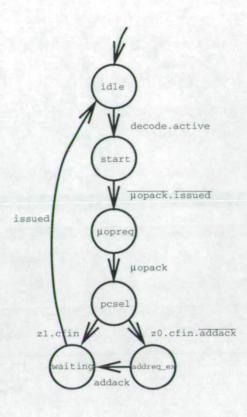

| 5.26 | FSM of the program counter control circuit                    | 160 |

| 5.27 | Layout of the program counter control circuit                 | 160 |

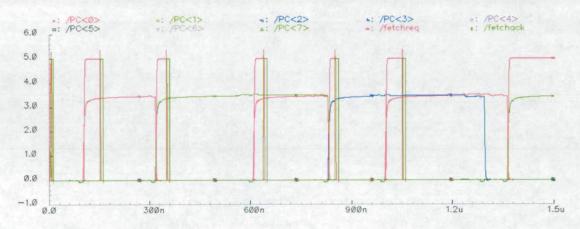

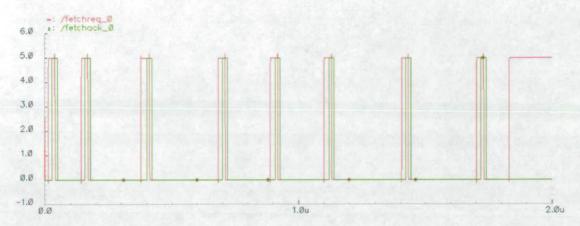

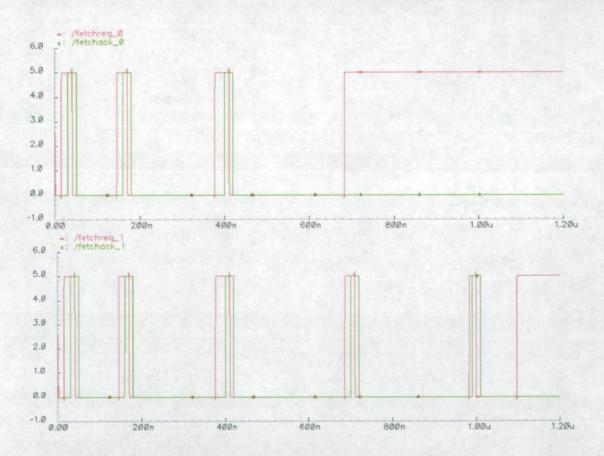

| 5.28 | Simulation of the fetch and issue of an immediate instruction | 161 |

| 5.29 | Simulation of the fetch and issue of a branch instruction     | 162 |

| 5.30 | FSM of Memory Unit                                            | 163 |

| 5.31 | Layout of the Memory Unit                                     | 164 |

| 5.32 | FSM of Write-Back Unit                                        | 165 |

| 5.33 | Layout of the Write-Back Unit                                 | 165 |

| 5.34 | Combinational logic equations for addition                    | 166 |

| 5.35 | Dual-rail encoded carry equations                             | 166 |

| 5.36 | Full-Adder, result generation                                 | 167 |

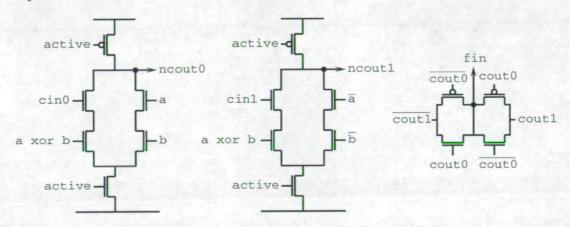

| 5.37 | Full-Adder, carry output generation and completion detection  | 167 |

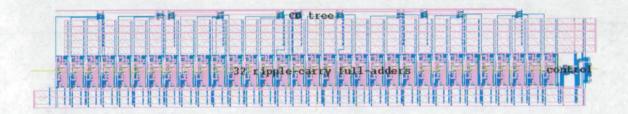

| 5.38 | Layout of the asynchronous full-adder                         | 168 |

| 5.39 | Layout of the asynchronous 32-bit ripple-carry Adder          | 168 |

| 5.40 | FSM of the adder control logic                                | 168 |

| 5.41 | Layout of the adder control logic                             | 169 |

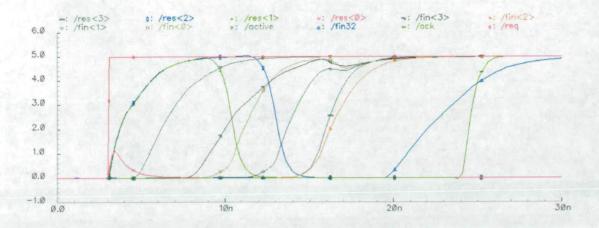

| 5.42 | Simulation of an addition with no carries                     | 170 |

| 5.43 | Simulation of the 01+01 addition                              | 171 |

| 5.44 | Simulation of an addition with one sequential carry, 01+11    | 171 |

| 5.45 | Simulation of an addition with two sequential carries, 001+111 172             |

|------|--------------------------------------------------------------------------------|

| 5.46 | Simulation of an addition with three sequential carries, 0001+1111 172         |

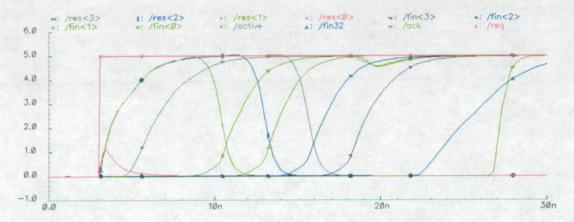

| 5.47 | Addition Time in ns as a function of the number of sequential carries 173      |

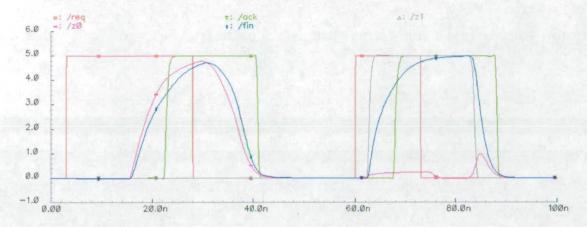

| 5.48 | Layout of the asynchronous 32-bit comparator                                   |

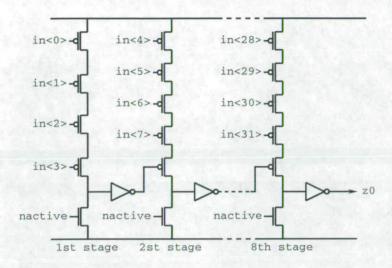

| 5.49 | cascade 32-input dynamic NAND gate                                             |

| 5.50 | cascade 32-input dynamic OR gate                                               |

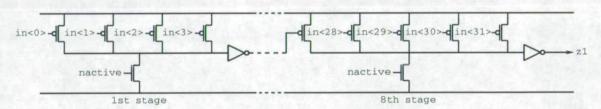

| 5.51 | Simulation of a true and a false comparison                                    |

| 5.52 | Layout of the Shared Register File with 8 shared and 16 local registers 176    |

| 5.53 | Access time map for one unconnected A1 SRF 177                                 |

| 5.54 | FSM of the SRF read/write port logic                                           |

| 5.55 | Layout of the SRF read/write port logic                                        |

| 5.56 | Simple test program for testing all the $A1$ processor instructions . $180$    |

| 5.57 | Simulation of the simple program - Instruction Fetch 180                       |

| 5.58 | Simulation of the simple program - Register $\mu \rm operation~Handshakes 181$ |

| 5.59 | Simulation of the simple program - FU $\mu$ operation Handshakes 182           |

| 5.60 | Simulation of the simple program - Register File Ports 183                     |

| 5.61 | Simulation of the simple program - FU Handshakes                               |

| 5.62 | SRF Program - one node addition                                                |

| 5.63 | SRF Program - two node addition                                                |

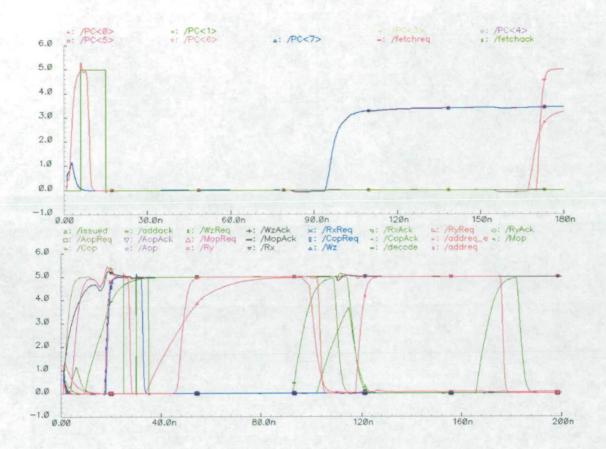

| 5.64 | One-node SRF addition program simulation - Instruction Fetch $$ . 186          |

| 5.65 | Two-node SRF addition program simulation - Instruction Fetch $$ . 186          |

| 6.1  | Conventional CMOS direct-mapped AFSM structure 192                             |

| 6.2  | CMOS direct-mapped AFSM with BIST additions 192                                |

| 6.3  | 2-phase synchronous DFF circuit                                                |

# List of Tables

| 4.1  | Access times(ns) for 2-way SRF with 4, 8 and 16 shared registers | 105 |

|------|------------------------------------------------------------------|-----|

| 4.2  | Access times(ns) for 4-way SRF with 4, 8 and 16 shared registers | 108 |

| 4.3  | SRF Performance Metrics                                          | 111 |

| 4.4  | Execution times for different organisations                      | 114 |

| 4.5  | Access Times(ns) for 4 SRF 2-way System                          | 118 |

| 4.6  | Performance Metrics for 4 SRF 2-way System                       | 119 |

| 4.7  | SRF Metrics for an unconnected SRF of this system                | 119 |

| 4.8  | Average Interconnect Distances for control and data signals (in  |     |

|      | $\mu$ m) between SRFs                                            | 120 |

| 4.9  | Updated Execution times for SRF system                           | 121 |

| 4.10 | Access Times(ns) for 4 MRF Bus System                            | 129 |

| 4.11 | Performance Metrics for a 4 MRF Bus System                       | 130 |

| 4.12 | Updated Execution times for SRF system                           | 132 |

| 5.1  | A1 μinstruction Decoding                                         | 137 |

| 5.2  | Summary of the comparison speeds                                 | 175 |

| 5.3  | Access times(ns) for 2-way SRF with 4, 8 and 16 shared registers | 176 |

| 5.4  | Access time Ratios between A1 ALCATEL SRF and 2-way ES2          |     |

|      | 1-read port SRF                                                  | 177 |

| 6.1  | Areas of various A1 components                                   | 191 |

# Chapter 1

# Introduction

### 1.1 Scalable Architectures

### 1.1.1 Scalability in Architectures

Scalability requires a compositional architecture, where components can be added or removed. These components should be designed with emphasis on both physical scalability and potentially scalable performance. Since the 1970s, fine-grain, scalable architectures have been identified as the best possible way to utilise the increased device count that the breakthrough in VLSI technology has provided [DL99]. The key aspects of these architectures relevant to performance scalability have been identified as regularity in structure, programmability in terms of the hardware-software interface and, most importantly, concurrency.

With the transition from Very Large Scale Integration (VLSI) to Giga Scale Integration (GSI), another increase in the device count is expected of the order of 1000. The number of available transistors on a single chip is rising exponentially and is expected to be in the order of 1 billion before 2010.

Additionally, as feature sizes scale, the metal wire bandwidth is becoming a potential limiting factor to circuit speed and inter-circuit communication. The propagation of signals in metal wires is now becoming comparable to the switching speed of transistors and the capacitance, resistance or even inductance of metal wires has to be considered in circuit design [CAD]. One way of tackling this problem is to change the metallisation material, currently Aluminium, to reduce RC delay and IR drop. The only three metals with better conductivity than Aluminium are silver, copper and gold. Unfortunately, even using silver, the improvement in resistance cannot exceed a factor of 2. Copper interconnect is now being used by some manufacturers [IBM97][MOT97a], despite its processing difficulties; it requires an extra barrier layer as it diffuses through  $SiO_2$  and an extra passivation layer to prevent corrosion. The net effect is a 20 to 30%

reduction of the effective resistance [CS96].

So, these technology issues must be considered when new architectures are being designed. The important challenges faced by computer architects are to manage locality, to reduce the communication overhead and to provide efficient synchronisation mechanisms.

### 1.1.2 Scaling Performance

Increases in the performance of a computer system can be achieved in two different ways; the time it takes to perform a certain task can be reduced and/or more tasks can be performed in a unit of time. The former is usually bounded by physical and implementation constraints imposed by the circuit technology. The speed of transistors, the RC delays of metal tracks, the parasitic capacitances between layers and the power supply voltage are some of the factors which influence circuit speed. Such factors depend on the technology type (e.g. CMOS or BiCMOS) and the feature size (e.g.  $0.7\mu m$ ,  $0.35\mu m$ ). Therefore, as the technology sets an upper bound to speed, concurrency is necessary for scaling performance. All of today's high-performance architectures exploit concurrency in some way to achieve performance.

Compositionality and concurrency are very much related issues. Any system which is able to perform operations in parallel must be compositional in some way. An element in such an architecture which is not compositional may act as a constraint on performance. As the performance requirements increase, so does the size of compositional architectures. Non-compositional, centralised components are potential bottlenecks, especially those whose performance scales badly with the size of the architecture. Concurrency can exist both in time and in space and both between program instructions and data.

### 1.1.2.1 Instruction Level Concurrency

Since the third generation of computers (1965-74), techniques such as pipelining, multiple functional units and scoreboarding have been used to exploit instruction level concurrency (or instruction level parallelism, ILP) and to scale performance [HP90]. The first general-purpose machines to introduce pipelining were the IBM 7030 [Blo59], known as Stretch, and Atlas [KELS62]. The IBM 7030, for example, overlapped fetch, decode and execute using a 4-stage pipeline. Then, in 1963, the CDC 6600 introduced extensive use of multiple functional units (FUs) along with scoreboarding [Tho64].

The scoreboard is essentially a hardware data structure which analyses instruction dependencies and allows instructions to execute out of order when sufficient resources and no data dependencies exist. Three years later, the IBM 360/91 went a step further by using another data dependency analysis scheme, the Tomasulo Algorithm [Tom67]. This distributed the data dependency analysis logic among the architecture's hardware units and registers and eliminated false dependencies. True dependencies exist between two instructions when the result of one instruction is required by another, also known as Read-After-Write (RAW) hazards because of the order that they impose. True dependencies cannot be removed and have to be respected for correct program execution. Two types of false dependency exist. The first type of false dependency occurs when two instructions share the same destination register and is known as a Write-After-Write (WAW) hazard. The second type of false dependence occurs when the result of one instruction is the operand of another earlier in the instruction stream but the former has not yet read its operands, and is known as a Write-After-Read (WAR) hazard. False dependences can be removed by increasing the register usage and using different registers as destinations or operands for the instructions that cause them.

The next evolutionary step was to make the pipeline structure known to the compiler. That happened in the early 80's with Reduced Instruction Set Computer (RISC) machines, such as the Berkeley RISC [PS82]. The instruction set became simpler and better suited to conform to a pipelined structure. Hardware-software interaction was enhanced by allowing the compiler to select instructions for the pipeline structure. From then on, to exploit even more instruction level concurrency, machines which fetch and issue multiple instructions in a single step were proposed.

Two types of systems were devised, Very Long Instruction Word (VLIW) [Fis83] and superscalar [Joh91][SS95]. In VLIW architectures, multiple instructions are packed into a single fixed-format instruction word by the compiler and then each instruction in that word feeds into an appropriate functional unit of a multiple FU architecture. Superscalar architectures, in which, multiple independent instructions are fetched and issued, operate at the hardware level, placing fewer demands to the compiler. Superscalar architectures check dynamically for FU availability and can support out of order issue and execution.

#### 1.1.2.2 Data Level Concurrency

Array processors followed a different approach to increasing concurrency [Hwa93]. Instead of increasing the complexity of the single processor, array processors replaced it with a number of simpler ones. The argument for array processors is that although each processor in an array processor system is not as powerful as the most powerful single processor, their combination is both much more powerful and cost-effective.

One of the first computers to adopt the idea of array processing was the Illiac IV [Hor82]. It was delivered in 1972 to NASA but difficulties with the project meant that only a quarter of the original design was implemented and this somewhat hindered the investigation of this style of architecture. After that, a number of such architectures emerged, the Burroughs BSP [KS82], the ICL DAP [Red73], the CM-2 [Thi90] and the MasPar MP1 [Mas91].

A typical array processor architecture comprises an array of processing elements and a central control unit. The control unit distributes array instructions and data among the processing elements. The processing elements can be elementary 1-bit processors as in the Illiac IV or the ICL DAP architectures or more complex as in the MasPar MP1. Typically, all processing elements execute the same instruction and masking logic is provided to enable or disable a processing element during the execution of an instruction. Communication between the processing elements is necessary and is implemented by a data-routing network, which is controlled by the executing program.

Vector architectures provide machine instructions that operate on data sets rather than scalar values, hence exploiting spatial parallelism. They use vector FUs which are pipelined and can operate on multiple data elements simultaneously, resulting in high data throughput and performance. The first vector machines were the CDC STAR-100 [HT72] and the TI ASC [Wat72] which were both announced in 1972. These were both memory-memory machines meaning that a vector operation had a high start-up overhead due to the amount of memory fetches. Also, the vector size ranged from several hundred to several thousand elements. The CRAY-1 [Rus78], introduced in 1976, was a vector-register architecture which reduced the start-up overhead of vector operations. The CRAY-1 was the first commercially successful vector machine due to its high vector and scalar performance. The evolution of vector machines continued and as the need for higher performance continued, so did the exploitation of concurrency. Deeper pipelining, exploitation of instruction level concurrency and the use of multiple processors followed. The CRAY X-MP was the first vector architecture to intro-

duce multiprocessor configurations.

#### 1.1.2.3 Program Level Concurrency

Architectures that exploit a different type of concurrency, *i.e.* explicit concurrency between program data and instructions were also devised. This class is referred to as parallel architectures. Such architectures include multiprocessors and multicomputers.

Multiprocessors and multicomputers are architectures with multiple processing elements, which are able to execute multiple program threads simultaneously. The nature of the processing elements can vary from a simple scalar processor to a complex deeply-pipelined vector processor. The difference between multiprocessors and multicomputers is the memory system and the communication medium between processing elements. In a multiprocessor system, processors communicate via shared variables in a common memory. In a multicomputer system, each computer node has a private, local memory and communication takes place between nodes through messages on communication links.

Multiprocessors can be classified according to their memory access model: the uniform memory access (UMA) model, the nonuniform memory access (NUMA) model, and the cache only memory architecture (COMA) model. The difference between these models is the structure of the memory hierarchy.

In the UMA model, all processors have equal access times to a uniformly shared memory. In the NUMA model, the memory is physically distributed across the processors and each processor has a local memory. The memory access time varies with the physical location of a memory word; the local memory is the fastest to access, remote memory access is longer because of the delay of the interconnect. The COMA model is a special case of the NUMA model, where the distributed memories are replaced by cache memories, which form a global address space.

Multicomputers are composed of multiple processors with local memories and a message-passing interconnection network which provides static connections between the nodes. The local memories in multicomputer systems can only be accessed by the processor they are attached to, this is why they are sometimes referred to as no-remote-memory-access (NORMA) machines.

## 1.1.3 Architectures of today and tomorrow

Contemporary processors like the Intel Pentium family [Sha98] and clones, the Alpha 21264 architecture [Com99] and the PowerPC architecture [Mot97b] are

all ILP architectures. Their common characteristics is that they are all pipelined, have multiple FUs, operate on multiple instructions simultaneously and support out-of-order and speculative execution. ILP architectures use a mixture of static (compiler driven) and dynamic (hardware) techniques.

They typically fetch multiple instructions in a single operation, in the original program order. They then remove false instruction dependencies by renaming the logical registers assigned by the compiler to physical ones. After this stage, execution of instructions can occur out-of-order, *i.e.* depending on the availability of operands. Results of instructions can be forwarded to other instructions. The instruction's results are stored in the original program order in a queue called the reorder buffer. Their results are committed to the registers and memory in-order to ensure correct program behaviour. Branch instructions are handled in the fetch stage. Their outcome is typically predicted by some scheme and instruction execution continues speculatively. Depending on whether the prediction was correct or not, the results of speculatively executed instructions are committed.

The differences between these processors are their architectural parameters and their fabrication processes. Examples of such parameters are the size of the data and instruction caches, the number of registers and their size, the maximum number of instructions that can be issued, the size of the branch prediction tables, the number of FUs, etc.

The trend in ILP processor design is to keep increasing the processor resources and investigate new techniques for exploiting parallelism. The number of registers, the number of FUs and the number of instructions that a processor can handle in a given cycle are parameters which keep increasing.

There are limitations to this approach however [PJS97][ONH+96]. The register requirements of ILP architectures are high [FJC95][MSAD92] both in terms of the number of registers and the number of ports because of the high number of instructions that are in flight in the architecture and the existence of multiple FUs. The performance scalability of the centralised, monolithic register file is a problem for such architectures. Forwarding results between instructions directly is a common approach used to bypass the register file and improve performance. However, a typical implementation to allow full connectivity between the inputs and outputs of all FUs also scales badly. This is because it is dominated by RC delays due the use of multiple result busses and tri-state circuits.

The continuous shrinking of transistor sizes, the interconnect problem and the ability to integrate more devices onto the same chip have triggerred a rethink about the architectures of tomorrow. The ability to integrate a few small-scale, embryonic processors on the same chip has given new potential to array processors and multiprocessor systems, giving rise to clustered and single-chip multiprocessor architectures. Both of these architectures are compositional and therefore scalable, whereas ILP processors are not. In general, they aim at a higher degree of parallelism than the ILP processor, but ILP processors have reached the limits of parallelism that they can exploit anyway.

Clustered and single-chip multiprocessor architectures are composed of a number of processing elements which are fed by a single or multiple instruction streams respectively. Each processing element is typically composed of a number of FUs and some form of local storage. The ability of the processing elements to communicate is paramount for the exploitation of parallelism and performance.

In this work, the problem of communication and synchronisation between processing elements in a clustered or single-chip multiprocessor system is considered.

### 1.1.4 The Rôle of the Register File

Historically, the first machines were accumulator based. Machine instructions always involved the accumulator, a special register for storing one of the operands of an operation, for reasons of hardware simplicity. This approach implied a high memory traffic as no means of temporary storage existed. The CDC 6600 introduced hardware registers because the multiple FUs of the machine could not be fed fast enough with operands at the speed of the main memory.

The register file (RF), a bank of general purpose registers has since become almost ubiquitous as a component in computer architectures. In contemporary architectures, the most common instruction types are load/store, *i.e.* instructions which transfer data between the RF and the lower levels of the memory hierarchy, and register-register, *i.e.* instructions which operate on data stored in registers and store their result back into the RF. The RF is the part of the memory hierarchy closest to the processor; it can be randomly accessed and results stored once can be read multiple times by multiple instructions. Although it is so commonly used, it is one of the most difficult components to scale in an otherwise scalable architecture, both in terms of performance and compositionality.

Assuming fixed length registers (say 32-bits), the speed of an RF depends primarily on two factors, the number of registers it contains and the number of access ports. The dependence is not linear but quadratic [Kum96]. This is because an increase in either of these parameters has an effect on the electrical parameters of the RF datapath, increasing both its capacitance and resistance, whose product yields the time constant which determines circuit speed.

The numbers of ports and registers are determined by the architecture. For maximum performance, if the number of FUs is increased, then the bandwidth between the FUs and the registers must be increased, implying an increase in the input and output ports of the RF. An architecture with n FUs requires 2n read and n write ports. Concurrent, look-ahead architectures, such as superscalar or VLIW, increase register usage even more, both through the use of register renaming to remove false dependencies and by operating on many instructions simultaneously [FJC95][MSAD92]. It is important therefore to find an alternative solution to the centralised or monolithic register file (MRF) approach.

#### 1.1.5 Alternatives to the MRF

A number of scalable architectures have considered the MRF problem. Two approaches have been followed: multiple RFs and partitioned RFs.

The use of multiple RFs is the most common approach, where the MRF is segmented into a number of smaller RFs, *i.e.* with fewer registers and fewer ports. Each of these RFs is then allocated a number of functional units (FUs), yielding an architecture which is composed of a number of nodes or clusters of FUs. The most important characteristic which distinguishes this type of architecture is the communication method established between the nodes.

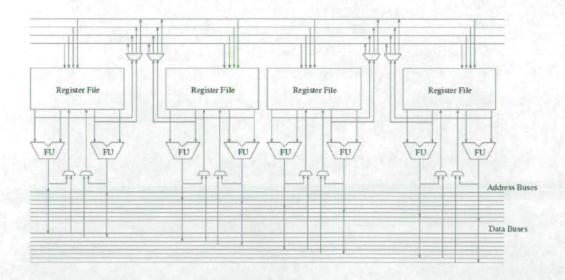

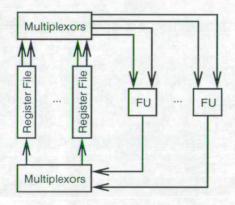

Capitanio's limited-connectivity VLIW machine [CDN92] (Figure 1.1) is a clustered VLIW architecture which has multiple RFs and uses extra busses and extra RF ports for inter-RF communication (busses at the top of Figure 1.1). Multiplexers are used to provide a fully connected network (a crossbar) between the multiple RFs allowing them to write to all RFs busses.

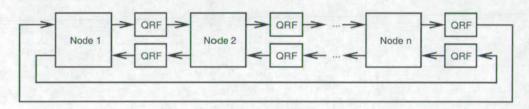

Fernandes' queue RF approach [Fer98] (Figure 1.2) is again a clustered VLIW architecture where all communication between RFs takes place via a number of queues. These queues establish a bi-directional communication ring between the clusters.

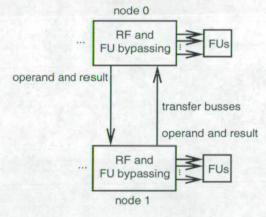

The multicluster architecture, Farkas et al, [FCJV97] (Figure 1.3) is a dynamically scheduled superscalar architecture that uses multiple nodes, each with its own RF, and that allows inter-node communication to take place at the register level by using multiple register transfer busses between the nodes.

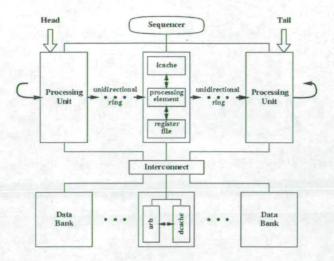

The Wisconsin-Madison multiscalar processor [SBV95] (Figure 1.4) is a coarsegrain machine, again with multiple nodes each with its own RF, but each node runs a statically selected task and communication between the nodes takes place with a uni-directional ring mechanism which follows the order of execution.

The other approach is partitioned RFs [JC95]. This approach, instead of

Figure 1.1: Example Limited Connectivity VLIW Architecture

Figure 1.2: Clustered Queue Register File Architecture

Figure 1.3: Part of a dual-node Multicluster Architecture

distributing the multiple RFs across the architecture, groups them together into a single partitioned RF and views each RF as a partition of the complete one (Figure 1.5). This is achieved by another level of register decoding in order to select the partition.

Figure 1.4: Example Multiscalar Architecture

Figure 1.5: Partitioned Register File Architecture

# 1.2 The SRF Approach

# 1.2.1 Register Windows

The concept of register windows was introduced in the Berkeley RISC and SPARC architectures. It was conceived as a means to address the problem of efficient communication of register values between procedures in a program. Conventionally, procedure calls have to use the stack, *i.e.* the main memory hierarchy, to communicate register values and the time required for writing to the stack is quite considerable, firstly because all the registers of the machine have to be saved and secondly because main memory accesses are slow.

In an architecture with register windows, procedures can only use a subset of the RF at a time, the current register window, and this is composed of a set of input registers, for receiving data from the calling procedure, a set of local registers, for storing local variables, and a set of output registers for sending data to a called procedure.

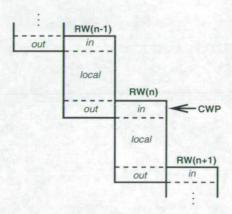

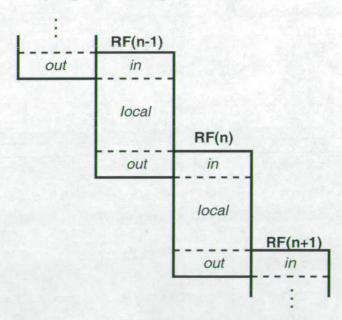

Along with register windows came the idea of overlapping registers. The input and output registers of communicating procedures overlap. When a procedure calls another it writes to its output registers and after the call the output registers of the caller become the input registers of the callee. This is achieved through the use of the current window pointer (CWP), a register which points to the start of the current register window in the RF. A register windows RF is composed of a number of windows as shown in Figure 1.6. In addition, the last window overlaps with the first one.

Figure 1.6: Register Windows

It is possible for overflow to occur, if the function call depth exceeds the number of windows. In that case, the main memory has to be used, so capacity is still a problem.

### 1.2.2 Overlapping or Shared Register Files

Register windows establish a communication pattern for communicating procedures of a single thread of code. Communication can be thought of as occurring in the time dimension, as when one procedure calls another, it stops, then the latter takes over until it is finished and then control is returned to the former.

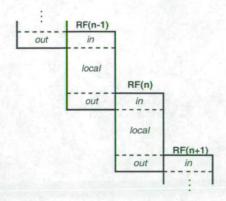

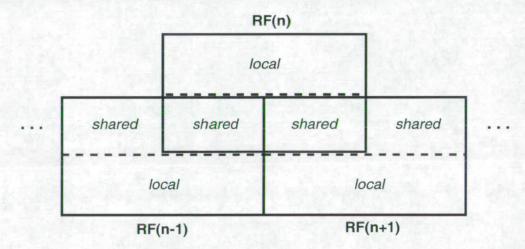

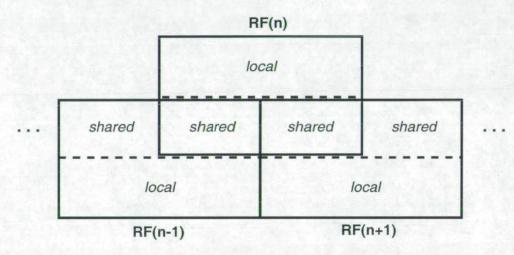

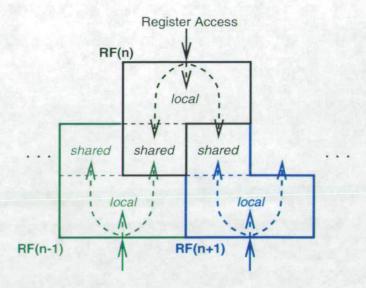

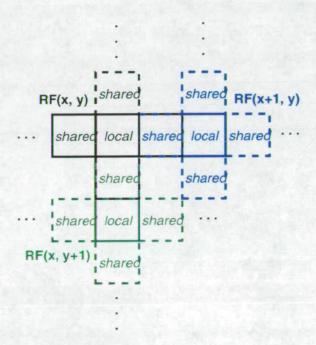

In multiprocessor systems, the problem of communication through main memory between processors is similar to that of communication through main memory between procedures in a uniprocessor. The overlapping registers idea of the register windows scheme inspired the idea of overlapping register files or shared register files, where portions of RFs overlap and multiple RFs share a portion of their registers. A scheme of shared register files (SRFs) is shown in Figure 1.7.

Figure 1.7: Shared Register Files

Shared register files establish a communication mechanism for multiple threads of code running on separate nodes. Each of these threads is executing using different RFs. Communication takes place in space, rather than time, as data between these threads is shared through shared registers.

In this scheme, multiple neighbouring RFs share registers for communication. If RF(n) wants to communicate with RF(n+1), it writes to its output section and then the data can be read from the latter's input section. The shared portions are physically shared. The scheme shown establishes a unidirectional connection between the SRFs. It is possible to expand this scheme for multi-way communication as will be shown later in this thesis.

#### 1.2.3 SRFs in Architectures

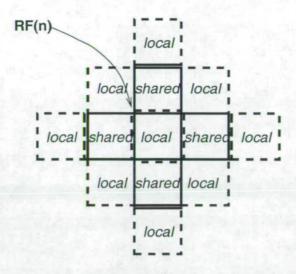

SRFs provide a fine-grain communication mechanism for scalable architectures by providing a simple, efficient and scalable method for segmenting the centralised RF. The details of such an architecture will affect the SRF sharing scheme but the SRFs themselves do not impose a particular architecture. Different configurations of SRFs are discussed in Chapter 4.

SRFs manage locality by providing local sections for local processing and shared sections for inter-RF communication. The design and implementation process of SRFs will show that they have a natural mapping to implementation and not only provide conceptual but also physical locality for the local sections and a scalable connection method for communication.

SRFs reduce the communication overhead by providing flexibility in the degree of communication and by their ability to communicate multiple values at the same time. The degree of communication is reflected by the number of shared registers, the number of shared sections in an SRF and the register sharing scheme.

Although only one value can be written at any one time in any one SRF, (unless multiple write ports are used), shared sections can be accessed directly by all neighbours without the need for arbitration. This provides the potential for multi-way communication with low complexity.

SRFs provide implicit synchronisation at the register level through the use of a register locking mechanism, which is much more desirable for exploiting concurrency than coarse grain process level synchronisation.

# 1.3 Timing in Circuits and Architectures

The most common approach to designing digital control circuits is the synchronous one, *i.e.* the utilisation of a timing reference signal, called a clock, for separating system states. In high-level terms, the clock signal has two phases, an active phase and a wait phase. During the active phase, an operation is performed, whereas during the wait phase communication of results takes place. The clock period, *i.e.* the time between the clock signal changes is determined by the speed of an operation.

Because of the dominance of the synchronous approach in circuit design, most contemporary systems including processor architectures are synchronous. Historically, the synchronous approach has dominated due to its simplicity, however with today's complex systems it is no longer clear whether the synchronous approach is still the simplest one.

## 1.3.1 Synchronous Systems

Synchronous systems are time-driven. The most important parameter of a synchronous system is the clock period (or the clock frequency, its inverse), which is either specified before a system design, or estimated after a system has been designed. All clocked blocks in a synchronous system must have delays which are less than the clock period for correct circuit operation.

The most common way of increasing the performance of a synchronous system is to make the clock period smaller. This involves identifying the longest paths in the control circuit logic, the critical paths, as they are called, and attempting to make them faster. The global nature of the clock signal implies that all of the control circuits must have delays of the same order. Therefore, operations longer than a specified clock period must be broken down into suboperations which take less than or equal to the clock period. This implies than if the speed of an operation is not an exact fraction of the clock period, a performance penalty is incurred.

This is one of the difficulties of synchronous design, *i.e.* that inhomogenuities between circuit speeds cannot be efficiently accommodated.

The implementation of synchronous circuits is becoming more and more difficult as the density of integration increases and higher clock frequencies are required in order to achieve high-performance. Clock buffering and clock skew are becoming important problems in GSI. As the number of devices that can be implemented on a single chip is increased, so must the drive strength of the clock to drive them. Therefore, the silicon area which is occupied by the clock routing and buffers is increasing. In addition, minimising clock skew, *i.e.* the differences in the arrival time of the clock at different circuit parts, is a hard problem, because both the clock buffers and the wire delays must match among different circuit parts. In addition, as the wire delays are becoming increasingly significant, the amount of die area which is reachable in a single clock cycle is dropping [Mat97].

The power consumption of synchronous circuits is another problem. Not only the clock buffers and clock routing, but also circuits which are inactive consume a lot of power without performing any useful function. The increasing power dissipation of the clock, with increasing clock frequencies and integration densities, has presented the need for power management techniques. In a synchronous circuit, current is drawn globally when the clock switches. This maximises radio interference at frequencies which are harmonics of the clock frequency.

### 1.3.2 Asynchronous Systems

Asynchronous (also called self-timed) systems do not rely on an external timing reference. They are composed of asynchronous circuit blocks. Communication between these blocks is no longer based on timing, but on an asynchronous communication protocol. Each of these blocks is responsible for communication with other blocks and for detecting the completion of its operation.

In this way, each block operates autonomously, taking only as much time as is necessary to perform its function, rather than waiting for the next clock transition to occur. It is often the case that the time required for the completion of an operation is variable and depends on the operands, rather than being fixed. In such cases, an asynchronous implementation is more advantageous, as it can accommodate these variations and does not incur a performance penalty. In a synchronous implementation, the clock period must allow for the worst case, the critical path, yielding worst-case performance for the particular circuit being implemented, whereas an asynchronous implementation that is data-dependent will yield average-case performance.

The most important advantages of asynchronous systems, which are direct consequences of the autonomy of their constituent components, are compositionality and therefore scalability, expandability and ease of improvement.

Compositionality and scalability are key aspects for scalable performance, as they allow for the exploitation of parallelism. Expandability and ease of improvement relate to compositionality. Once a system has been specified and possibly implemented, it is generally possible to expand one of its parts, without having to make global changes. In addition, it is possible to replace an asynchronous component with an improved one, without having to make any changes to the system.

The asynchronous system model is well suited to the GSI era, as the communication mechanism does not rely on explicit timing assumptions. Its properties make it particularly attractive for implementing systems-on-a-chip, the latest trend in semiconductor manufacturing, where single-chip systems can be constructed from standard circuit blocks. The asynchronous model solves the important problem of interfacing between these independent blocks and allows for scalable and expandable systems to be implemented. The absence of a clock signal is also advantageous for mixed analogue and digital circuits, as the clock poses interference problems for analogue circuit parts, which are usually separated, for this reason, from the digital parts as much as possible.

# 1.4 Asynchronous Processors

Historically, asynchronous architectures first appeared in the 1950s. One of the earliest machines to exploit asynchronous operation was the Atlas machine [KELS62], designed at the University of Manchester in the late 1950's. Asynchronous operation was used because Atlas had a single accumulator for floating-point instructions and the floating-point unit had a much longer latency for multiply and divide operations than it did for add or subtract. The MU5 Computer System [IC78], the successor to Atlas at Manchester, inherited this asynchrony and exploited it more extensively. It employed asynchronous communication among processor units (although some of the units were internally synchronous) and between processor units and memory, firstly to allow different instructions to follow different paths through the various sections of the pipeline and secondly to address the problem of variable functional unit delays.

The complexity of asynchronous circuit design and the preconception that asynchronous circuits are wasteful in logic and area impeded asynchronous pro-

cessor design. But the problems of the synchronous approach gave new potential to research into asynchronous architectures. In 1989, the first fully-asynchronous microprocessor [MBL+89] was designed and implemented at the University of California, based on Martin's Communicating Processes method [Mar90a]. In the same year, Sutherland's asynchronous micropipelines [Sut89] gave new potential to asynchronous research.

Today, a number of asynchronous architectures exist, some of which have been fabricated and found to operate correctly. The AMULET family of processors first appeared in 1994 with AMULET1 [FDG+94]. AMULET2 [FGR+97] and AMULET3 [GFC99] followed. The AMULET processors implement the ARM instruction set and follow the micropipeline approach. The first processor, AMULET1, employed a 2-phase, bundled data design style and a register locking mechanism for respecting dependencies between instructions. The AMULET2 used a 4-phase design style and was a more complex architecture including data forwarding and branch prediction. The AMULET3 processor implements the latest version of the ARM architecture which includes "thumb" instructions, a set of compressed instructions to improve code density. In the AMULET3 the register locking mechanism has been replaced by an reorder buffer.

The MiniMIPS Processor [MLM<sup>+</sup>97] developed at the University of California is an asynchronous MIPS R3000 architecture. It implements precise exceptions and allows for bypassing of the register file. The MiniMIPS allows for out-of-order execution of instructions and employs an instruction queue for writing back the results of instructions in the original program order.

The Counterflow Pipeline Processor [RFS94] developed at Sun is a novel type of architecture which mixes instruction and data flow. In a counterflow architecture instructions and data flow in opposite directions. Instructions look for their operands and then for a pipeline stage where they can be executed. The problem with counterflow architectures is the circuit complexity of the logic required at the pipeline stages.

The TITAC [NUK+94] and TITAC2 [TKI+97] processors were developed at the Tokyo Institute of technology. TITAC implements a simple accumulator-based instruction set. TITAC2 is an asynchronous pipelined processor with a five stage pipeline. Due to the fact that both processors use a dual-rail encoded datapath, they have a high gate count compared to a synchronous equivalent datapath.

The SCALP processor [End96] is an asynchronous architecture aiming at power efficiency. The SCALP processor allows for explicit forwarding of in-

struction operands by encoding functional unit identifiers into the processor's instruction set. It still uses a register file, as values cannot be forwarded beyond branches and often the results of one instruction are used by several others.

As industry is beginning to realise the benefits of asynchronous circuit design, commercial asynchronous chips are beginning to appear. Commercial asynchronous chips include the Cogency DSP [PDF<sup>+</sup>98], the Philips 80C51 microcontroller [vGvBP<sup>+</sup>98] and the Sharp DDMPs [TMI99]. Cogency's asynchronous DSP and Philips' 80C51 are both compatible with synchronous versions.

The Cogency DSP architecture employs the 4-phase, bundled data protocol and implements a three stage pipeline. One of the interesting features of this architecture is the implementation of communication between the datapath units. A central control unit sends control signals to the datapath units instructing them to stall or proceed, hence resolving data dependencies in the datapath. This feature saves on the chip area compared to the synchronous design. The asynchronous version shows a reduction in power consumption of up to 47% and a great difference in electromagnetic interference. The Philips 80C51 microcontroller demonstrated a power reduction of about 25%.

## 1.5 Aims of the thesis

This thesis investigates asynchronous circuit and asynchronous processor design. In the area of asynchronous circuit design, it presents the CMOS direct-mapped asynchronous finite state machine approach. The simplicity of this approach, and its robustness are demonstrated.

In the area of asynchronous processor systems, it investigates the circuit implementation of hardware structures for supporting concurrency and scalability. Two approaches are presented; Shared Register Files (SRFs) and  $\mu$ net architectures.

The SRF approach can be used to implement clustered uniprocessors or singlechip multiprocessor systems and aims at exploiting program level concurrency. The implementation of SRFs and the effect that register sharing has on the access times of register files are studied. An SRF system is contrasted, at the layout level, with the more conventional bus-based alternative.

The  $\mu$ net approach [Reb96] is an architectural approach for exploiting finegrain parallelism in an asynchronous datapath. It is capable of exploiting a higher amount of instruction level parallelism than a conventional pipelined architecture. An implementation methodology is presented for both scalar and superscalar  $\mu$ net-based architectures.

All of these ideas have been implemented in a prototype chip design, the A1 processor architecture, which has been laid out and simulated at the transistor level. The A1 is a dual-node multiprocessor, which employs the SRF approach for communication between the nodes. Each node is implemented with the  $\mu$ net approach and is capable of executing a simple instruction set.

#### 1.6 Thesis Structure

The structure of the remaining chapters of this thesis is as follows. Chapter 2 reviews some of the problems associated with implementing asynchronous control circuits and describes the CMOS direct-mapped approach for designing asynchronous finite state machines. Chapter 3 presents the basic principles of asynchronous processor systems, along with two methods for exploiting temporal and spatial parallelism, *i.e.* the  $\mu$ net (micronet) approach and shared register files. Chapter 4 describes the implementation of different configurations of asynchronous shared register files, discusses issues of their implementation and contrasts the performance of a four shared register file system to that of a more conventional bus-based system. Chapter 5 describes the design and implementation of the A1 processor. Chapter 6 presents the conclusions and proposes possible future work.

# Chapter 2

# Asynchronous Direct-Mapped Finite-State Machines

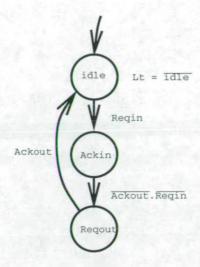

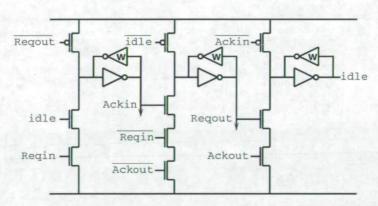

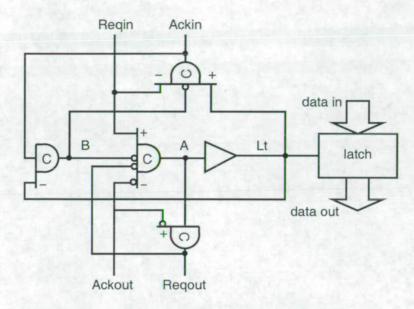

In this chapter, the problems associated with implementing asynchronous control circuits are described along with the existing approaches for designing asynchronous finite-state machines. The CMOS direct-mapped approach for designing asynchronous finite-state machines approach in CMOS technology is presented. Based on the one-hot encoding method, it is a simple, elegant and intuitive approach that produces regular, fast asynchronous control circuits.

# 2.1 Digital Circuit Design

Digital circuits can be divided into control circuits and datapaths. A datapath is a set of interconnected elements through which data flows for an operation to be performed. The operation of the datapath elements is controlled by control circuits.

A digital control circuit can be combinational or sequential. In a combinational circuit the output signals are functions only of the input signals, whereas a sequential circuit has internal state, and its output signals, as well as its future internal state, depend both on its inputs and its current internal state. Sequential circuits are also referred to as finite state machines (FSMs).

Although certain circuits can be implemented combinationally, it is frequently the case that a circuit cannot be implemented as an input-output mapping. This occurs when it is necessary for a circuit to perform a sequence of operations, "remembering" the step in the sequence that it is currently in. In such a case the storage of an internal circuit state is necessary and the circuit must be implemented sequentially.

# 2.2 Circuit Specification Methods

In order to implement a circuit its behaviour must first be specified. There are various ways of specifying a circuit's behaviour [Hau93], some of which are closer than others to the details of the implementation. After the specification has been produced, it may need to be converted into an implementable form. It is possible, for example, to specify a circuit at a high level of abstraction, for example as a program or as a graph of transitions, and at that level even the nature of the circuit, *i.e.* whether it is combinational or sequential is not obvious. Such a specification will need to be analysed and refined into a lower level specification. The lowest level of a circuit specification can be directly mapped to a circuit implementation.

For combinational circuits, a directly implementable specification is a simple function that defines an input-output mapping. For sequential circuits, it is a sequential function, *i.e.* a function that maps inputs to outputs assuming a particular internal state. The input-output mapping for combinational circuits is specified by a truth table. A truth table is a one dimensional array, where rows represent the input signals and the table entries the output signals. The truth table for an AND gate is shown in Figure 2.1. Signals a and b are the inputs and o is the output.

| a | b | 0 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Figure 2.1: Truth Table for an AND gate

Sequential circuits can be specified in a tabular form as a flow table [Ung69] or in a graph form as a state diagram. A flow table is a two dimensional array, where columns correspond to input values, rows to the internal states and the table entries are ordered pairs representing the next internal state and the current output respectively. Figure 2.2 shows the flow table specification of a 2-bit counter with an input x and two outputs. The numbers in the left-hand column represent the circuit states and the table entries represent the next state and the outputs. When the next state is the same as the current state, the circuit is stable and the next state table entry is shown in brackets.

A state diagram represents the relationship between inputs, states and outputs graphically. States are represented by vertices and transitions between states by

|   | X       |         |  |

|---|---------|---------|--|

| 3 | 0       | 1       |  |

| 1 | (1), 00 | 2, 01   |  |

| 2 | 3, 11   | (2), 01 |  |

| 3 | (3), 11 | 4, 10   |  |

| 4 | 1, 00   | (4), 10 |  |

Figure 2.2: Flow Table for a 2-bit grey-code Counter

labelled edges that connect the states. The circuit outputs are specified for each vertex in the graph, *i.e.* for each circuit state. The state diagram for the 2-bit counter is shown in Figure 2.3. The labels inside the states indicate the state and the circuit outputs. Note that the stable transitions are not shown.

Figure 2.3: State Diagram for 2-bit Counter

## 2.3 Implementation of Digital Control Circuits

## 2.3.1 Transistors and Logic Gates

The fundamental element used for the implementation of modern electronic circuits is the transistor. A transistor (**transfer-resistor**) is an analogue electronic device with three ports, such that the voltage or current across or through one pair of these ports, controls the current through the other pair.

CMOS (Complementary Metal Oxide Semiconductor) technology [WE93] provides two transistor types, an n-type transistor and a p-type transistor, fabricated

by using negatively doped and positively doped silicon respectively. The MOS structure provides a gate, a source and a drain port. The gate port controls, by a field-effect mechanism, the flow of current between the source and the drain ports. CMOS transistors can be used to implement digital logic gates, *i.e.* digital circuits that perform the fundamental logical operations, such as NOT, AND, OR, NAND, NOR, XOR, etc.

#### 2.3.2 Combinational Logic

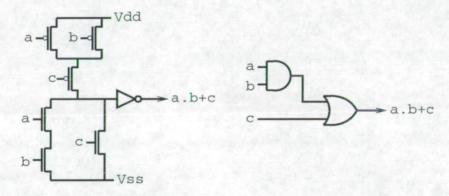

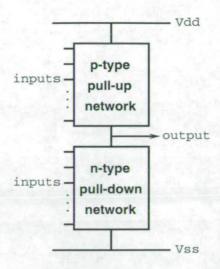

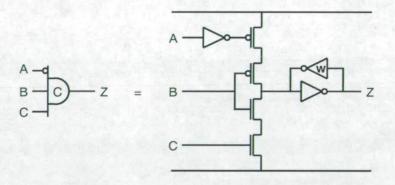

Combinational circuits can be implemented by connecting together transistors or logic gates to produce the output signals, c.f. Figure 2.4. In CMOS, so called complex gates can be used to produce an output signal depending on a number of inputs [WE93][Bla92]. These typically contain a pull-down network of n-types and a pull-up network of p-types, Figure 2.5. The function of the pull-down network is to short the output of the gate to logic 0 and of the pull-up network to short the output to logic 1. For correct digital operation these must be mutually exclusive.

Figure 2.4: Different Realisations of a.b+c

## 2.3.3 Sequential Logic

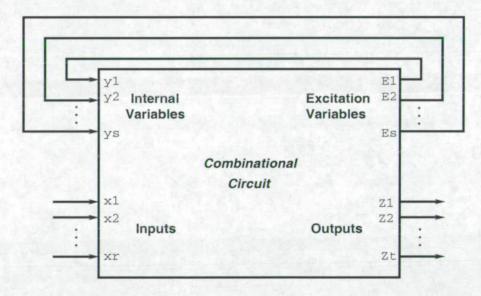

Implementing sequential circuits is a more complex task - sequential circuits require feedback. Firstly, the internal state of the circuit must be stored in memory elements. Secondly, the future internal state must be produced and this must not interfere with the current state. The circuits that produce the future state and the outputs are combinational. The general form of a sequential circuit or finite-state-machine (FSM) is shown in Figure 2.6.

The internal state is represented by the internal state variables, which must be used as inputs to the circuit to produce the future internal state, or the excita-

Figure 2.5: Complex CMOS Gate Structure

tion state variables. When the future internal state is different from the current internal state, the circuit is unstable and changes state. The number of state variables depends on the number of states of the circuit, for n states, a minimum of  $log_2n$  state variables are needed.

Figure 2.6: General Form of a Sequential Circuit or FSM

# 2.4 Circuit Implementation Problems

Although digital circuits use discrete values and can be modelled in a discrete manner, they are implemented using inherently analogue devices and interconnections which have a continuous rather than a discrete response and finite, varying delays depending on physical parameters such as device sizing and path length.

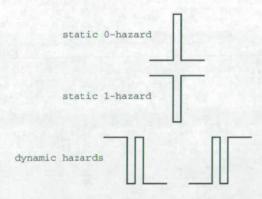

This mismatch between the logical and physical implementation, and in particular the finite, varying delays between circuit components, can lead to circuit failures called hazards. Depending on the nature of the circuit, combinational or sequential, different types of hazards are possible. Sequential circuits also present another problem, races. These circuit failures are described below.

### 2.4.1 Hazards