## Single-Stage Power Factor Correction Converter Topologies for Low Power Off-Line Applications

**Edward Michael Lord**

Thesis submitted for the degree of Doctor of Philosophy The University of Edinburgh

March 2004

### Abstract

Since January 2001 it has been necessary for equipment connected to the low voltage public distribution network in Europe and Japan to comply with IEC 61000-3-2. The regulation IEC 61000-3-2 specifies the level of current that can be drawn for particular harmonics. Much equipment today is fitted with a Switch Mode Power Supply (SMPS) at its input to interface between the line voltage and internal low voltage electronics. This SMPS must not only convert the line voltage, but also ensure that the input current to the device meets the IEC regulations.

To meet these regulations two methods are normally used, passive filtering using a large filter inductor or a boost converter cascaded with the main DC/DC SMPS converter with isolation. To try and reduce component count, cost and increase efficiency many new single-stage Power Factor Correction (PFC) topologies have been proposed. In a single-stage topology the output voltage regulation and meeting IEC 61000-3-2 are combined into a single power stage. Unfortunately very little is known about the behaviour or performance of these single-stage topologies.

In this thesis two of the more promising single-stage topologies: the bi-forward and CS  $S^2PFC$  converters are investigated further. A new topology using a low frequency switch (LFSPFC) is introduced. The topologies are analysed investigating input current shape and harmonic content, voltage variation on bulk capacitance and component stresses. Simulation in PSpice is used to confirm circuit operation.

Four 150W output power experimental circuits were built, bi-forward converter, CS S<sup>2</sup>PFC converter, passive filtering cascaded with a forward converter and a boost pre-regulator cascaded with a forward converter. The converters operate from universal input voltage and have outputs at 5V and 12V. A 100W test circuit was built for the LFSPFC operating from 230V input voltage and with an output of 5V.

Experimental results are presented showing circuit behaviour and performance of the biforward, CS S<sup>2</sup>PFC and LFSPFC converters. The bi-forward and CS S<sup>2</sup>PFC converters are compared to the passive filter and boost converter cascaded with a forward converter. It is demonstrated that neither of these single-stage topologies are at present a viable replacement for either present method, but the LFSPFC could be a lighter weight and less bulky alternative to passive filtering.

## **Declaration**

I declare this is thesis has been completed by myself and that except where indicated to contrary, the research documented is entirely my own work.

Edward Michael Lord

## Dedication

In memory of Katie Lord

### Acknowledgements

First and foremost I would like to thank my supervisor Dr. Ewen Macpherson for his guidance, encouragement and continued support during this project. His knowledge and expertise have been invaluable.

I must also thank my funding bodies, the Engineering and Physical Sciences Research Council (EPSRC) and Minebea Electronics (UK) Limited.

I would also like to thank Minebea Electronics (UK) Limited and their staff for letting me use there laboratory to carry the majority of my circuit testing, in particular Dr. Joe Leisten for all his suggestions and advice on how to get an experimental circuit working properly.

My time at Edinburgh has been enjoyable and rewarding due to the staff and students in the School of Engineering and Electronics, especially my colleagues in the former ESG. A special thanks go to Richard Loh and Kostas Papastergiou for their discussions, encouragement and friendship. Also Gareth Harrison and Xiaodan (Selina) Feng for their support during a difficult time.

I would like to thank my parents, Evelyn and Philip Lord, without whose love, encouragement and support this project would never of happened. Finally I would like to thank Gabriel and Katie not only for their love, encouragement and support, but also for many of evenings of discussion and dining.

## Abbrevations

|                              | Alternating Current                                                                       |

|------------------------------|-------------------------------------------------------------------------------------------|

| AC<br>AC/DC                  | Alternating Current<br>Alternating Current to Direct Current                              |

| BIBRED                       | Boost Integrated with a Buck Rectifier/Energy storage/Dc-dc converter                     |

| BIFRED                       | Boost Integrated with a Flyback Rectifier/Energy storage/DC-dc converter                  |

| BIFKED                       | Bipolar Junction Transistor                                                               |

| BS                           | British Standard                                                                          |

| DS<br>CCM                    | Continuous Conduction Mode                                                                |

| CCM<br>CS S <sup>2</sup> PFC | Current Source Single-Stage Power Factor Corrector                                        |

| DB                           | Diode Bridge                                                                              |

| DB<br>DCM                    | Discontinuous Conduction Mode                                                             |

| DCM                          | Discontinuous Conduction Mode                                                             |

|                              | Direct Current to Direct Current                                                          |

| DC/DC                        |                                                                                           |

| EMI                          | Electro Magnetic Interferance                                                             |

| EN                           | European Standard                                                                         |

| ESR                          | Equivalent Series Resistance                                                              |

| IC                           | Integrated Circuit                                                                        |

| ICS                          | Input Current Shaping<br>International Electrotechnical Commission                        |

| IEC                          |                                                                                           |

| IGBT<br>LC                   | Insulated Gate Bipolar Transistor                                                         |

|                              | Inductor Capacitor                                                                        |

| LFR                          | Loss Free Resistor                                                                        |

| LFSPFC                       | Low Frequency Switch Power Factor Corrector<br>Metal Oxide Silcon Field Effect Transistor |

| MOSFET                       |                                                                                           |

| PC<br>PF                     | Personal Computer<br>Power Factor                                                         |

|                              |                                                                                           |

| PFC                          | Power Factor Correction                                                                   |

| PWM                          | Pulse Width Modulation                                                                    |

| RCD                          | Resistor Capacitor Diode                                                                  |

| RMS                          | Root Mean Squared                                                                         |

| SMPS                         | Switched Mode Power Supply                                                                |

| SSIPP                        | Single-Stage Isolated Power-Factor-Corrected Power Supply                                 |

|                              | Television                                                                                |

| VMC                          | Voltage Mode Control                                                                      |

| UK                           | United Kingdom                                                                            |

ł

## **Symbols**

| ٨                  | Conduction of Input Current (I ESDEC)                                                                  |

|--------------------|--------------------------------------------------------------------------------------------------------|

| $A_c$              | Conduction of Input Current (LFSPFC)                                                                   |

| D                  | Duty Ratio for Switch $S_1$<br>Duty Ratio for Switch $S_1$ when Operating from Bulk Capacitor (LFSPFC) |

| $D_1$              |                                                                                                        |

| $D_2$              | Duty Ratio for Switch $S_1$ during Period 2 (Bi-Forward)                                               |

| Ð                  | Duty Ratio for Switch $S_1$ when Supplied Direct from Input (LFSPFC)                                   |

| $D_3$              | Duty Ratio for Switch $S_1$ during Period 3 (Bi-Forward)                                               |

| $D_4$              | Duty Ratio for Switch $S_1$ during Period 4 (Bi-Forward)                                               |

| $D_{4A}$           | Duty Ratio for Switch $S_1$ during Period 4A (Bi-Forward)                                              |

| $D_{eff}$          | Effective Duty Ratio for $L_2$ (LFSPFC)                                                                |

| $D_f$              | Duty Ratio for Fall of DCM Current in Inductor $L_1$ (CS S <sup>2</sup> PFC)                           |

| _                  | Duty Ratio for Fall of Current in Inductor $L_1$ (LFSPFC)                                              |

| $D_{f2}$           | Duty Ratio for Fall of DCM Current in Inductor $L_1$ during                                            |

|                    | Period 2 (Bi-Forward)                                                                                  |

| $D_{f3}$           | Duty Ratio for Fall of Current in Inductor $L_1$ during Period 3 (Bi-Forward)                          |

| $D_{max}$          | maximum Duty Ratio (LFSPFC)                                                                            |

| $E_{oldsymbol{c}}$ | Energy lost by Bulk Capacitor                                                                          |

| F                  | Line Frequency                                                                                         |

| $F_{Dist}$         | Displacement Factor                                                                                    |

| $F_{Dist}$         | Distortion Factor                                                                                      |

| $f_s$              | Switching Frequency                                                                                    |

| $I_1$              | RMS Fundamental Current                                                                                |

| $I_{2adif}$        | Difference between Current Rise and Fall in Inductor $L_1$                                             |

|                    | during Period 2A (Bi-Forward)                                                                          |

| $I_{2amin}$        | Minimum Current in Inductor $L_1$ during Period 2A (Bi-Forward)                                        |

| $I_{4min}$         | Minimum Current in Inductor $L_1$ during Period 4 (Bi-Forward)                                         |

| $I_{av}$           | Average Current in Inductor $L_1$ (LFSPFC) .                                                           |

| $I_{avc}$          | Average Current in Inductor $L_1$ during CCM (CS S <sup>2</sup> PFC)                                   |

| $I_{avd}$          | Average Current in Inductor $L_1$ during DCM (CS S <sup>2</sup> PFC)                                   |

| $I_{av2}$          | Average Current in Inductor $L_1$ during Period 2 (Bi-Forward)                                         |

| $I_{av2a}$         | Average Current in Inductor $L_1$ during Period 2A (Bi-Forward)                                        |

| $I_{av3}$          | Average Current in Inductor $L_1$ during period 3 (Bi-Forward)                                         |

| $I_{av4}$          | Average Current in Inductor $L_1$ during Period 4 (Bi-Forward)                                         |

| $I_{av4a}$         | Average Current in Inductor $L_1$ during Period 4A (Bi-Forward)                                        |

| $I_c$              | Current at which Diode $D_5$ Stops Conducting during CCM Operation of                                  |

|                    | Inductor $L_1$ (CS S <sup>2</sup> PFC)                                                                 |

| $I_o$              | Output Current                                                                                         |

| $I_{p1}$           | Current in Inductor $L_1$ and Reflected Current in Inductor $L_2$ (LFSPFC)                             |

| •                  | · · · ·                                                                                                |

| $I_{p2}$         | Current in Inductor $L_1$ and Reflected Current in Inductor $L_2$                     |

|------------------|---------------------------------------------------------------------------------------|

| -                | Raises too (LFSPFC)                                                                   |

| $I_{pkd}$        | Peak current in Inductor $L_1$ when Operating in DCM (CS S <sup>2</sup> PFC)          |

| $I_{pk2}$        | Peak Current in Inductor $L_1$ when Operating in DCM during                           |

| <i>pn</i> 2      | Period 2 (Bi-Forward)                                                                 |

| $I_{pk2a}$       | Peak Current in Inductor $L_1$ during Period 2A (Bi-Forward)                          |

| $I_n$            | RMS Current of Harmonic n                                                             |

| $\frac{-n}{i_c}$ | Bulk Capacitor Recharging Current                                                     |

| $i_{dir}$        | Current Flowing Directly to the Output from the Input (Bi-Forward)                    |

| $i_{f}$          | Current Flowing Directly to the Output from the Input (LFSPFC)                        |

|                  | AC Line Current Drawn by Converter                                                    |

| i <sub>s</sub>   | Turns Ratio between Primary Windings                                                  |

| n<br>D           |                                                                                       |

| $P_{in}$         | Input Power                                                                           |

| P <sub>o</sub>   | Output Power                                                                          |

| T                | Time for a Half Line Period                                                           |

| $T_s$            | Time for One Switching Cycle                                                          |

| t                | Overall clock $T_{\rm eff} = 0$ (CS S <sup>2</sup> <b>P</b> EC)                       |

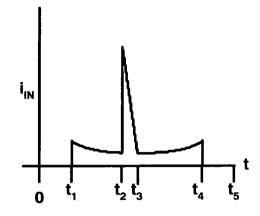

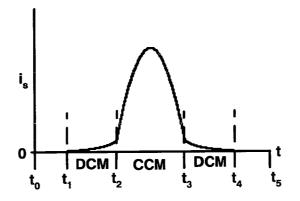

| $t_1$            | Time after Zero Crossing that Inductor $L_1$ Enters DCM (CS S <sup>2</sup> PFC)       |

| $t_2$            | Time after Zero Crossing that Inductor $L_1$ Enters CCM (CS S <sup>2</sup> PFC)       |

| $t_3$            | Time after Zero Crossing that Inductor $L_1$ Enters DCM Again (CS S <sup>2</sup> PFC) |

| $t_4$            | Time after Zero Crossing that Inductor $L_1$ Stops Conducting (CS S <sup>2</sup> PFC) |

| $t_5$            | Time after Zero Crossing that Complete Cycle Ends (CS S <sup>2</sup> PFC)             |

| $t_{2a}$         | Time after Zero Crossing that Inductor $L_1$ Enters Period 2A (Bi-Forward)            |

| $t_{3a}$         | Time after Zero Crossing that Inductor $L_1$ Enters Period 4A (Bi-Forward)            |

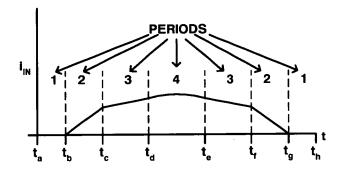

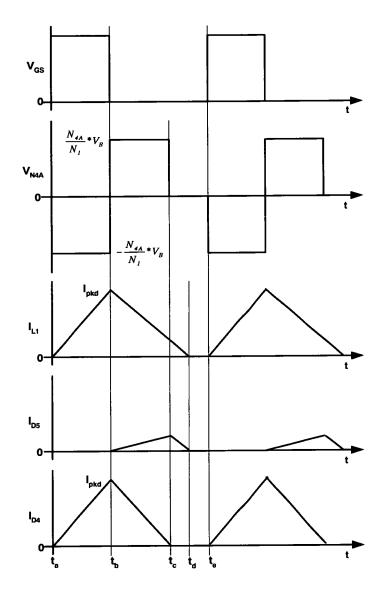

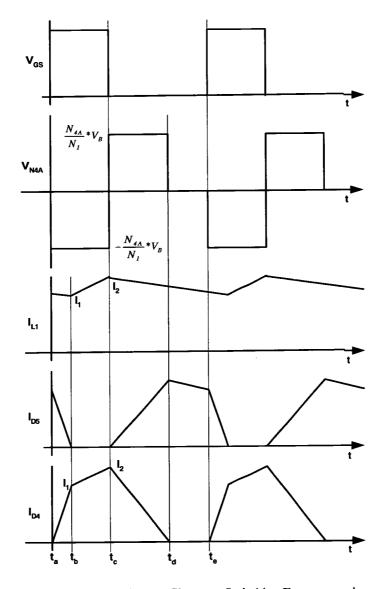

| $t_a$            | Zero Crossing Time (Bi-Forward, LFSPFC)                                               |

| $t_b$            | Time after Zero Crossing that Inductor $L_1$ Enters Period 2 (Bi-Forward)             |

|                  | Time after Zero Crossing that Inductor $L_1$ Starts Conducting (LFSPFC)               |

| $t_c$            | Time after Zero Crossing that Inductor $L_1$ Enters Period 3 (Bi-Forward)             |

|                  | Time after Zero Crossing that Inductor $L_1$ Stops Conducting (LFSPFC)                |

| $t_d$            | Time after Zero Crossing that Inductor $L_1$ Enters Period 4 (Bi-Forward)             |

|                  | Half Line Period Zero Crossing Time (LFSPFC)                                          |

| $t_e$            | Time after Zero Crossing that Inductor $L_1$ Enters Period 3 Again (Bi-Forward)       |

| $t_f$            | Time after Zero Crossing that Inductor $L_1$ Enters Period 2 Again (Bi-Forward)       |

| $t_g$            | Time after Zero Crossing that Inductor $L_1$ Enters Period 1 Again (Bi-Forward)       |

| $t_h$            | Half Line Period Zero Crossing Time (Bi-Forward)                                      |

| $t_{off}$        | Time after Zero Crossing that $S_2$ is Turned Off (LFSPFC)                            |

| $t_{on}$         | Time before Zero Crossing that $S_2$ is Turned On (LFSPFC)                            |

| $t_r$            | Time after Zero Crossing Bulk Capacitor Starts Recharging                             |

| $V_1$            | RMS Fundamental Voltage                                                               |

| $V_B$            | Average Bulk Capacitor Voltage                                                        |

| $V_{co}$         | Switch Over Voltage                                                                   |

| $V_{D2}$         | Voltage Across Diode $D_2$                                                            |

| $V_{D3}$         | Voltage Across Diode $D_3$                                                            |

| $V_{D5:5V}$      | Voltage Across Diode $D_5$ on the 5V Output                                           |

| $V_{GS}$         | MOSFET gate to source voltage                                                         |

| $V_{IN}$         | Input Voltage to Converter                                                            |

| $V_{inmin}$      | Minimum Voltage that $S_2$ can turn on and off at (LFSPFC)                            |

| $V_{min}$        | Minimum bulk Capacitor Voltage                                                        |

| $V_{pk}$         | Peak of Line Voltage                                                                  |

•

- Vo Output Voltage of Converter

- $V_{S1}$  Voltage Across Switch  $S_1$

- V<sub>SS</sub> Voltage Source Voltage

- $v_s$  AC Line Input Voltage

- $\Delta D \qquad \text{Duty Ratio for Rise of Current in Inductor } L_D \text{ (CS S}^2\text{PFC)} \\ \text{Duty Ratio for Rise of Current in Inductor } L_1 \text{ (LFSPFC)} \\ \end{array}$

- $\Delta D_3$  Duty Ratio for Rise of Current in Inductor  $L_1$  during Period 3 (Bi-Forward)

- $\Delta D_4$  Duty Ratio for Rise of Current in Inductor  $L_1$  during Period 4 (Bi-Forward)

- $\Delta D_{4A}$  Duty Ratio for Rise of Current in Inductor  $L_1$  during Period 4A (Bi-Forward)

- $\Delta I_{2af}$  Current Fall in Inductor  $L_1$  during Period 2A (Bi-Forward)

- $\Delta I_{2ar}$  Current Rise in Inductor  $L_1$  during Period 2A (Bi-Forward)

- $\Delta I_4$  Current Rise in Inductor  $L_1$  during Period 4 (Bi-Forward)

- $\Delta I_{4F}$  Current Fall in Inductor  $L_1$  during Period 4 (Bi-Forward)

- $\Delta I_c$  Current Rise in Inductors  $L_1$  and  $L_D$  during CCM (CS S<sup>2</sup>PFC)

- $\Delta I_o$  Current Ripple through  $L_2$  (LFSPFC)

- $\omega$  Angular Line Frequency

,

## **Contents Summary**

| Ał | ostract                                                                                      | i          |

|----|----------------------------------------------------------------------------------------------|------------|

| De | claration                                                                                    | ii         |

| De | dication                                                                                     | iii        |

| Ac | knowledgements                                                                               | iv         |

| Ał | brevations                                                                                   | v          |

| Sy | mbols                                                                                        | vi         |

| Co | ontents Summary                                                                              | ix         |

| Li | st of Figures                                                                                | xv         |

| Li | st of Tables                                                                                 | xxiii      |

| 1  | Introduction                                                                                 | 1          |

| 2  | PC Power Supplies: The Present                                                               | 10         |

| 3  | Review of Single-Stage PFC Topologies                                                        | 23         |

| 4  | Bi-Forward Converter                                                                         | 42         |

| 5  | Bi-Forward Converter with Input Inductor                                                     | 64         |

| 6  | High Frequency Current Source Single-Stage PFC Converter (CS S <sup>2</sup> PFC)             | 106        |

| 7  | Forward Converter with Low Frequency Switch - LFSPFC                                         | 142        |

| 8  | Comparison                                                                                   | 177        |

| 9  | Conclusions and Further Work                                                                 | 198        |

| A  | Predicted Harmonic Content at 100V for the Bi-Forward Converter                              | 202        |

| B  | Effect of Bulk Capacitance Value on the Bi-Forward                                           | 204        |

| С  | Predicted Results for $N_{1A}$ as 32 and $N_{1B}$ as 12 for the Bi-Forward with Inp Inductor | out<br>207 |

| D          | Predicted Performance of Final CS S <sup>2</sup> PFC Designs | 211 |

|------------|--------------------------------------------------------------|-----|

| E          | Predicted Harmonic Content at 230V for the LFSPFC Converter  | 214 |

| F          | <b>RMS Harmonic Currents Measured in PSpice</b>              | 217 |

| G          | Components Used in Test Circuits                             | 225 |

| Н          | Measured Efficiency and Bulk Capacitor Voltage               | 229 |

| I          | Publications                                                 | 236 |

| References |                                                              | 253 |

..

## Contents

| Ał             | ostrac                                   | t                                                                                                                                                                                                                                                                                                                                              | i                                         |

|----------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| De             | eclara                                   | tion                                                                                                                                                                                                                                                                                                                                           | ii                                        |

| De             | edicati                                  | ion i                                                                                                                                                                                                                                                                                                                                          | ii                                        |

| Ac             | know                                     | ledgements                                                                                                                                                                                                                                                                                                                                     | iv                                        |

| Ał             | obreva                                   | itions                                                                                                                                                                                                                                                                                                                                         | v                                         |

| Sy             | mbol                                     | ,                                                                                                                                                                                                                                                                                                                                              | vi                                        |

| Co             | ontent                                   | s Summary                                                                                                                                                                                                                                                                                                                                      | ix                                        |

| Li             | st of I                                  | igures x                                                                                                                                                                                                                                                                                                                                       | v                                         |

| Li             | st of ]                                  | Tables xxi                                                                                                                                                                                                                                                                                                                                     | ji                                        |

| 1              | <b>Intro</b><br>1.1<br>1.2<br>1.3<br>1.4 | DeductionThe Need for Power Factor Regulations1.1.1Power Factor1.1.2The Effects of Low Power FactorAC Power Quality Regulatory Standards: IEC 61000-3-2 [1, 2]1.2.1IEC 61000-3-2Methods to Comply with IEC 61000-3-21.3.1Thesis and Contribution to KnowledgeObjectives of the Research1.4.1Typical Application                                | 1<br>2<br>3<br>4<br>5<br>7<br>7<br>8<br>9 |

| 2 <sup>.</sup> | <b>PC</b> 1<br>2.1<br>2.2                | Basic Switched Mode Power Supplies       1         2.1.1 Continuous and Discontinuous Conduction Modes       1         2.1.2 Output Voltage Control       1         Topologies Currently used as the Main Converter in PCs       1         2.2.1 Single Switch Forward Converter       1         2.2.2 Double Switch Forward Converter       1 | 10<br>10<br>11<br>12<br>13<br>13          |

|                | 2.3                                      | 2.2.4       Flyback Converter       1         Current PFC Techniques       1         2.3.1       Passive Power Factor Correction                                                                                                                                                                                                               | 15<br>16<br>16<br>17<br>18                |

|   | 2.4  | Advantages and Disadvantages of Current PFC Methods                      | 19       |

|---|------|--------------------------------------------------------------------------|----------|

|   |      | 2.4.1 Passive PFC                                                        | 20       |

|   |      | 2.4.2 Two stage PFC with boost Pre-Regulator                             | 20       |

|   | 2.5  | The Regulations and the PC Power Supply                                  | 21       |

| 3 | Revi | ew of Single-Stage PFC Topologies                                        | 23       |

| - | 3.1  |                                                                          | 23       |

|   | 012  |                                                                          | 23       |

|   |      |                                                                          | 24       |

|   |      |                                                                          | 26       |

|   |      |                                                                          | 29       |

|   | 3.2  |                                                                          | 32       |

|   | 0.2  | 3.2.1 Parallel Single-Stage PFC using Pre-Regulator with Two Output      |          |

|   |      |                                                                          | 35       |

|   |      | 1 2                                                                      | 37       |

|   | 3.3  |                                                                          | 39       |

|   | 3.4  |                                                                          | 40       |

|   |      |                                                                          | 40       |

| 4 |      |                                                                          | 42       |

|   | 4.1  |                                                                          | 42       |

|   | 4.2  | Operation                                                                | 43       |

|   | 4.3  |                                                                          | 44       |

|   |      | 4.5.1 Optemention 111111111111111111111111111111111111                   | 45       |

|   |      | 1.5.2 Absumptions 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                 | 45       |

|   |      |                                                                          | 46<br>53 |

|   | 4.4  | Simulation of the D1 of that content of the transferred                  | 55<br>56 |

|   |      |                                                                          | 50<br>59 |

|   |      |                                                                          | 59<br>60 |

|   | 4.5  | Experimental Results 111111111111111111111111111111111111                | 60       |

|   |      | 1.5.1 Changes to the Hotospe to the total the                            | 61       |

|   |      |                                                                          | 61       |

|   |      |                                                                          | 63       |

|   | 10   |                                                                          | 63       |

|   | 4.6  | Conclusion                                                               | 05       |

| 5 |      | orward Converter with Input Inductor                                     | 64       |

|   | 5.1  | Introduction                                                             | 64       |

|   | 5.2  | Operation                                                                | 64       |

|   | 5.3  | Analysis                                                                 | 68       |

|   |      | 5.3.1 Assumptions                                                        | 68       |

|   |      | 5.3.2 Analysis at Switching Frequency                                    | 69       |

|   |      | 5.3.3 Analysis over a Half Line Period                                   | 75       |

|   | 5.4  | Converter Design                                                         | 77       |

|   |      | 5.4.1 Effect of Inductance Value of $L_1$ on Input Current RMS Harmonics | 78       |

|   |      | 5.4.2 Effect of Inductance Value of $L_1$ on the Bulk Capacitor Voltage  | 82       |

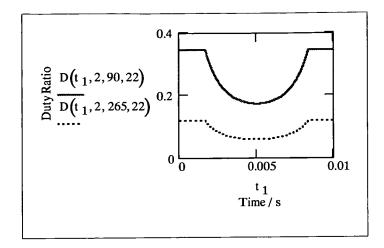

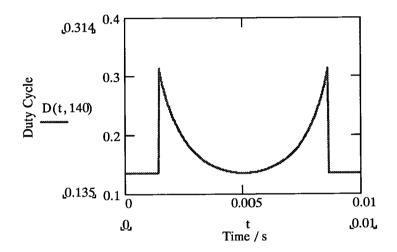

|   |      | 5.4.3 Duty Cycle Variation                                               | 85       |

|   |      | 5.4.4 Selection of $L_1$                                                 | 86       |

|   | _    | 5.4.5 Sizing of Semiconductors                                           | 87       |

|   | 5.5  | Simulation                                                               | 88       |

|   |      | 5.5.1 Simulation Results                                                 | 88       |

• ·

|   |             | 5.5.2                          | Simulation Waveforms                                                       | 89         |

|---|-------------|--------------------------------|----------------------------------------------------------------------------|------------|

|   | 5.6         | Experin                        | mental Results                                                             | 92         |

|   |             | 5.6.1                          | Changes Made to the Prototype Circuit                                      | 92         |

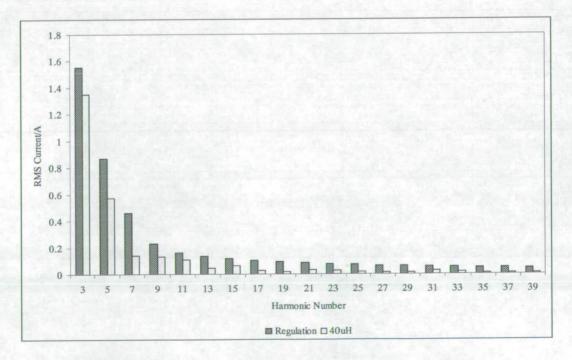

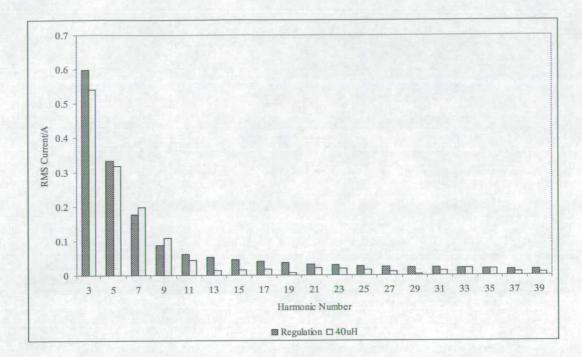

|   |             | 5.6.2                          | Harmonic Tests                                                             | 93         |

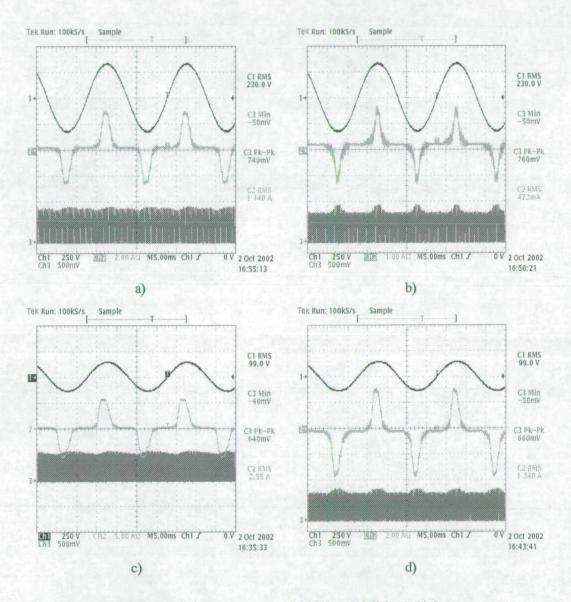

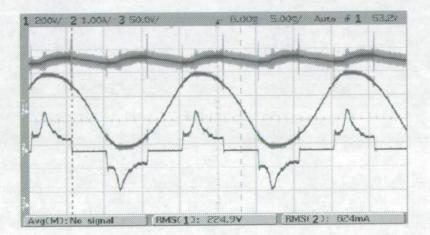

|   |             | 5.6.3                          | Input Current Waveform                                                     | 95         |

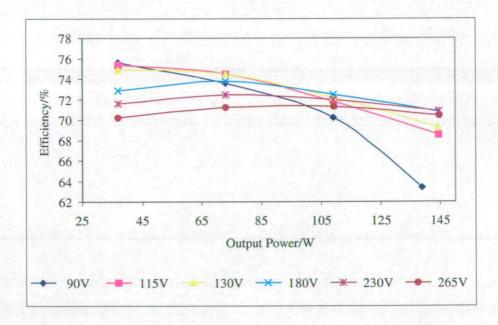

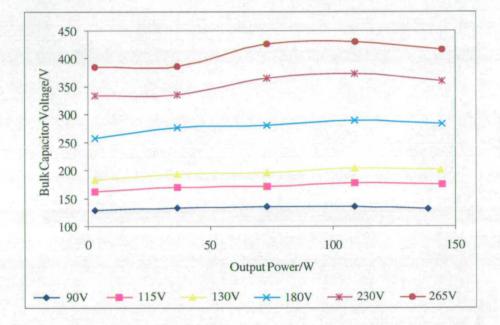

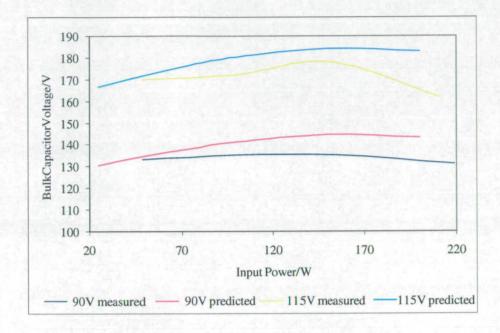

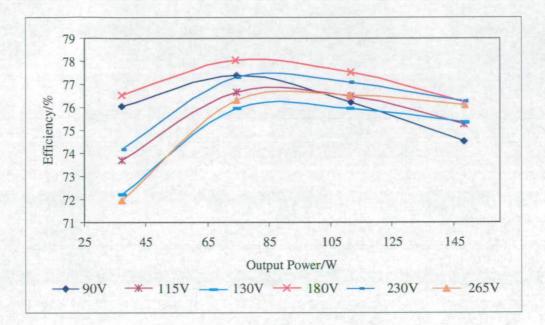

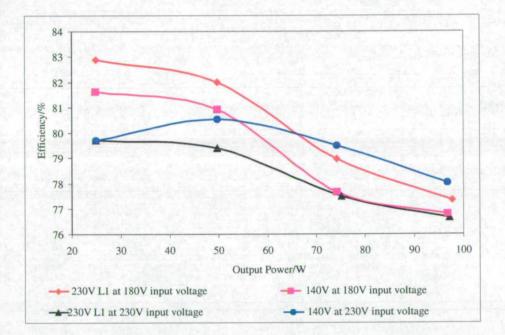

|   |             | 5.6.4                          | Voltage on the Bulk Capacitor $C_B$ and Efficiency                         | 96         |

|   |             | 5.6.5                          | Hold Up Time and Output Voltage Ripple                                     | 101        |

|   |             | 5.6.6                          | Voltage seen on key devices                                                | 102        |

|   | 5.7         | Conclu                         | sions                                                                      | 104        |

| 6 | High        | Freque                         | ency Current Source Single-Stage PFC Converter (CS S <sup>2</sup> PFC)     | 106        |

| _ | 6.1         |                                | pment of the High Frequency Current Source Single-Stage Converter          | 106        |

|   |             | 6.1.1                          | The Series Connection of a Loss Free Resistor and a Voltage Source         |            |

|   |             |                                | Concept                                                                    | 106        |

|   |             | 6.1.2                          | The Practical Implementation of the Series Connection Loss Free            |            |

|   |             |                                | Resistor and a Voltage Source                                              | 107        |

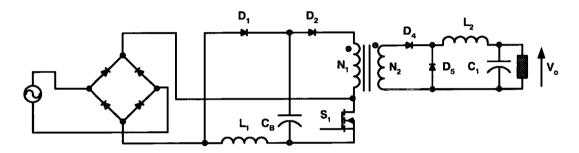

|   |             | 6.1.3                          | Application of a Voltage Doubler Scheme                                    | 108        |

|   | 6.2         |                                | ion of the High Frequency Current Source Single-Stage Converter            |            |

|   | 0.2         | 6.2.1                          | Operation at Line Frequency                                                | 109        |

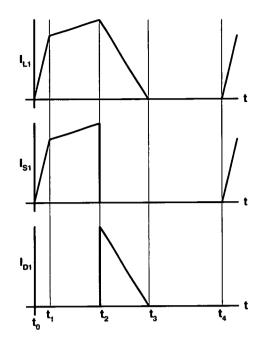

|   |             | 6.2.2                          | Operation at Switching Frequency                                           | 110        |

|   | 6.3         |                                | is                                                                         |            |

|   | 0.5         | <b>6</b> .3.1                  | Analysis when Operating in DCM for One Switching Cycle                     |            |

|   |             | 6.3.2                          | Analysis when Operating in CCM For one Switching Cycle                     | 116        |

|   |             | 6.3.3                          | Analysis at Line Frequency                                                 |            |

|   | 6.4         |                                | Procedure                                                                  |            |

|   | 0.1         | 6.4.1                          | Converter Design                                                           |            |

|   |             | 6.4.2                          | Sizing of Semiconductor Components                                         |            |

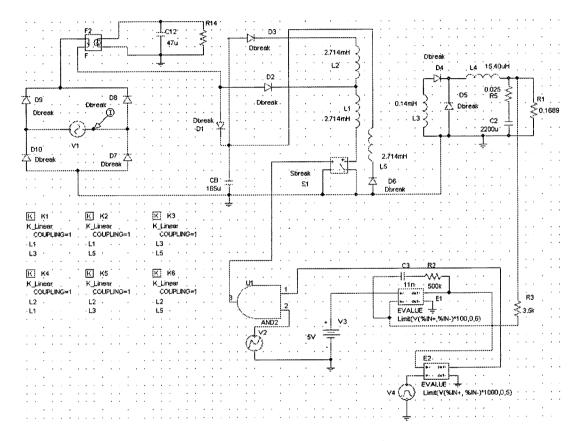

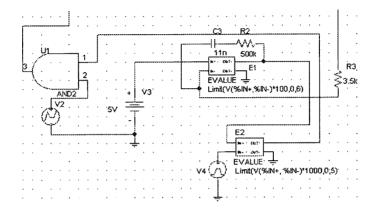

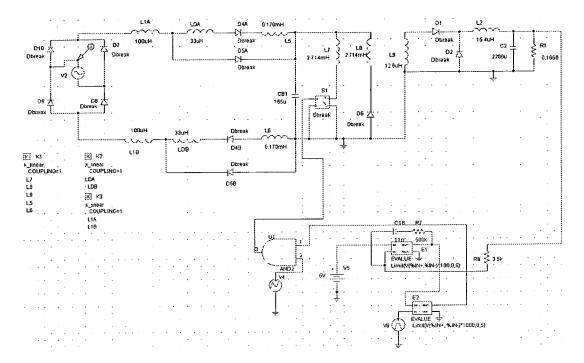

|   | 6.5         |                                | tion                                                                       |            |

|   | 0.5         | <b>6</b> .5.1                  | Simulation Results                                                         |            |

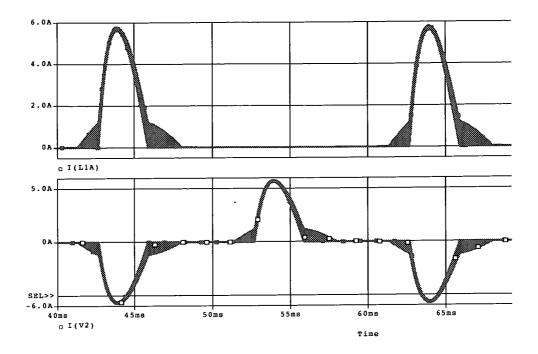

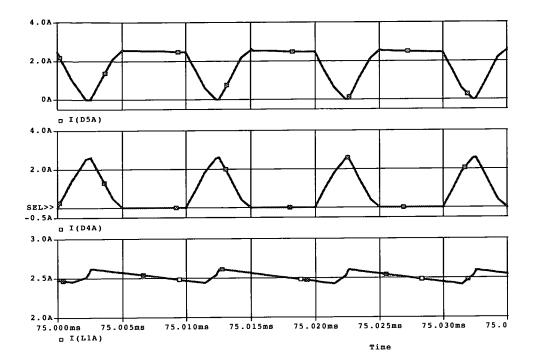

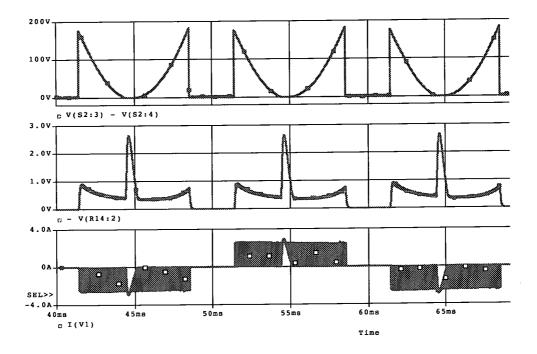

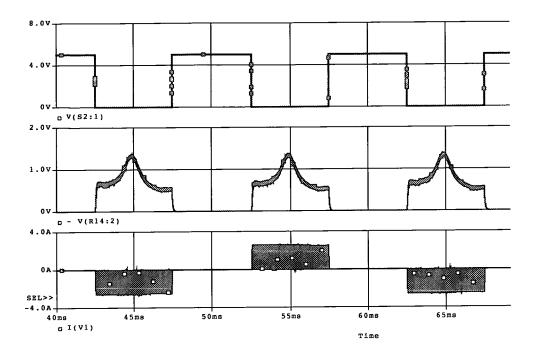

|   |             | 6.5.2                          | Simulation Waveforms                                                       |            |

|   | 6.6         |                                | mental Results                                                             |            |

|   | 0.0         | <b>6</b> .6.1                  | Changes Made to Prototype Circuit                                          |            |

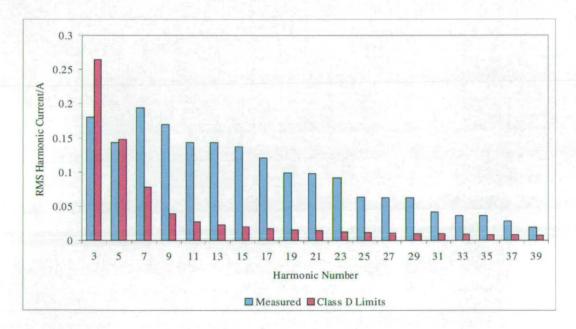

|   |             | <b>6</b> .6.2                  | Harmonic Tests                                                             |            |

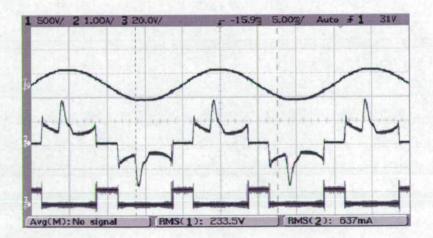

|   |             | 6.6.3                          | Input Current Waveform                                                     | 134        |

|   |             | <b>6</b> .6.4                  | Efficiency and Voltage Across the Bulk Capacitors, $C_{B1}$ and $C_{B2}$ . | 136        |

|   |             | <b>6</b> .6.5                  | Hold Up Time and Output Voltage Ripple                                     | 138        |

|   |             | <b>6.</b> 6.6                  | Voltage seen on Key Devices                                                |            |

|   | 6.7         | Conclu                         |                                                                            | 141        |

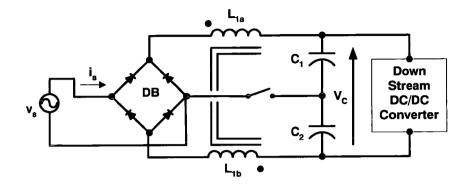

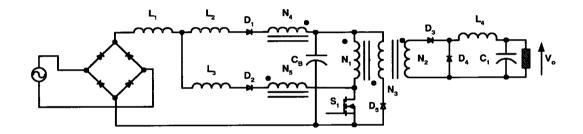

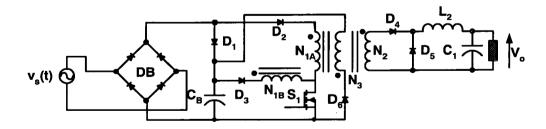

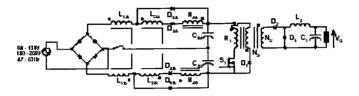

| 7 | Form        |                                | onverter with Low Frequency Switch - LFSPFC                                | 142        |

| 7 | <b>7</b> .1 |                                |                                                                            | 142        |

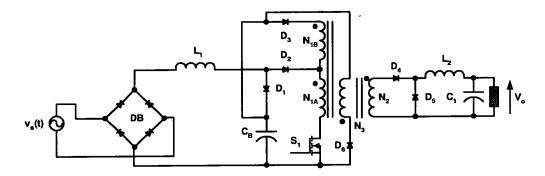

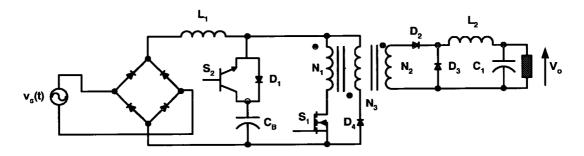

|   | 7.1<br>7.2  |                                | FSPFC Converter                                                            | 143        |

|   | 1.2         |                                | Operation                                                                  | 143        |

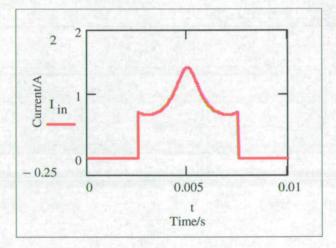

|   |             | <b>7.</b> 2.1<br><b>7.</b> 2.2 | Input Current Waveform                                                     | 144        |

|   |             |                                | Advantages and Disadvantages of the LFSPFC                                 | 144        |

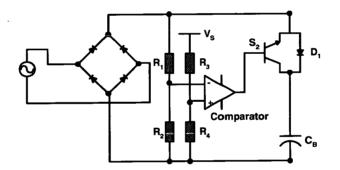

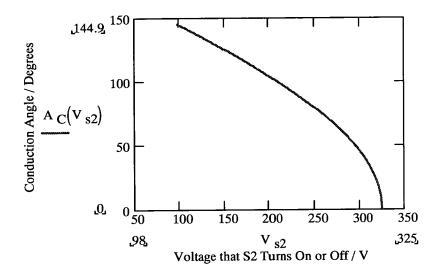

|   |             | 7.2.3                          | Operation of the Auxiliary Switch $S_2$                                    | 144        |

|   | 7 2         | <b>7.</b> 2.4                  | 1 .                                                                        | 145<br>146 |

|   | 7.3         |                                | SPFC Converter with Input Inductor                                         | 140        |

|   | <b>-</b> •  | 7.3.1                          | Operation                                                                  | 140        |

|   | 7.4         |                                | opment of a Prototype Converter                                            |            |

|   | 7.5         | Analys                         | Bis                                                                        | 140        |

|   |            | 7.5.1          | Assumptions                                                                 | 148 |

|---|------------|----------------|-----------------------------------------------------------------------------|-----|

|   |            | 7.5.2          | Basic LFSPFC                                                                | 149 |

|   |            | 7.5.3          | LFSPFC with Input Inductor $L_1$                                            | 154 |

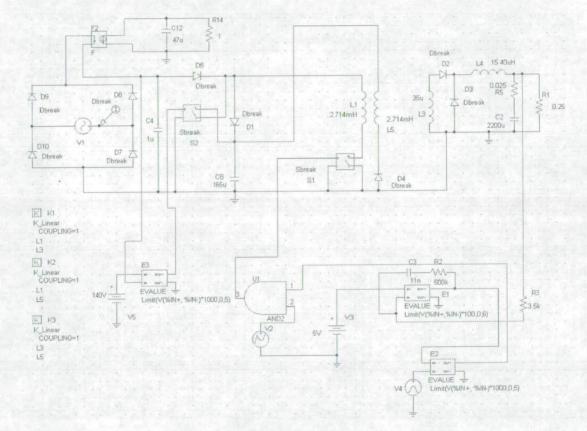

|   | 7.6        | Simula         | tion                                                                        | 162 |

|   |            | 7.6.1          | Simulation Results                                                          | 162 |

|   |            | 7.6.2          | Simulation Waveforms                                                        | 166 |

|   | 7.7        | Experie        | mental Results                                                              | 167 |

|   |            | 7.7.1          | RMS Input Current Harmonic Levels Compared to Classes A and D               | 169 |

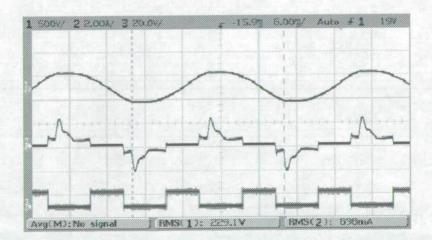

|   |            | 7.7.2          | Waveforms                                                                   | 170 |

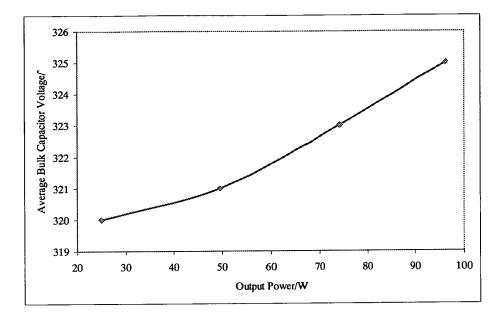

|   |            | 7.7.3          | Efficiency and Bulk Capacitor Voltage                                       | 173 |

|   |            | 7.7.4          | Semiconductor Voltage Stress                                                |     |

|   |            | 7.7.5          | Output Voltage Ripple                                                       |     |

|   | 7.8        | Conclu         | -                                                                           |     |

| 8 | Com        | parison        |                                                                             | 177 |

| 0 | 8.1        |                | ction                                                                       | 177 |

|   | 8.1<br>8.2 |                | Filter Inductor Cascaded with a Forward Converter                           |     |

|   | 8.2<br>8.3 |                | age Active PFC using a Boost Pre-Regulator Cascaded with a For-             | 1,0 |

|   | 0.3        |                |                                                                             | 179 |

|   | 0 1        |                | rison                                                                       |     |

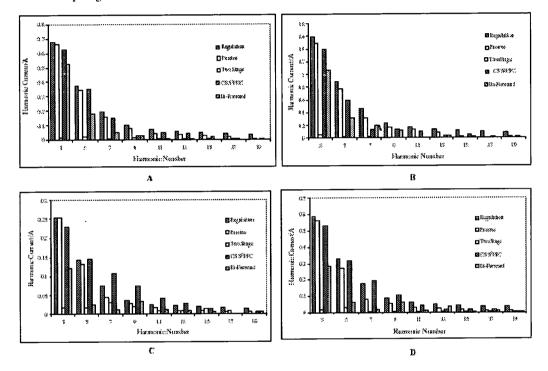

|   | 8.4        | 8.4.1          | PFC Method                                                                  |     |

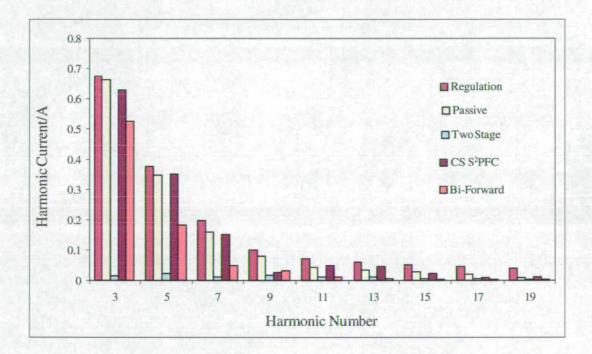

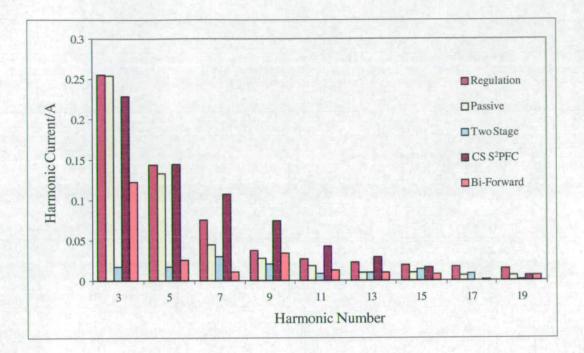

|   |            | 8.4.1<br>8.4.2 | Measured Harmonic Content to Class D                                        |     |

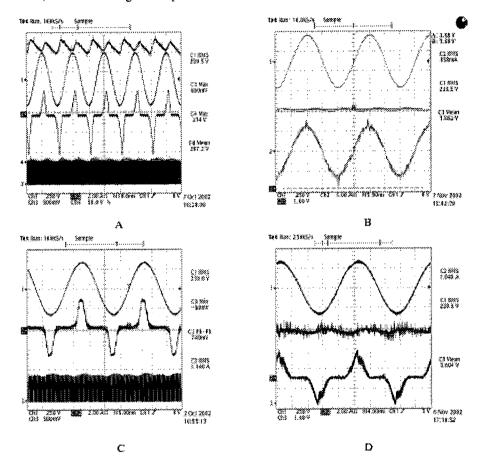

|   |            | 8.4.2<br>8.4.3 | Input Current Waveform                                                      |     |

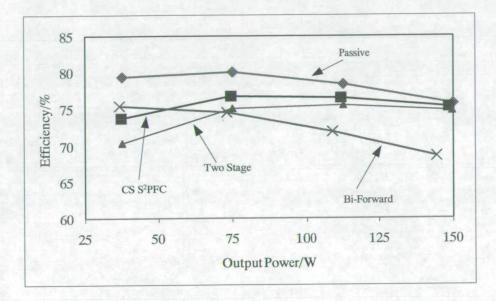

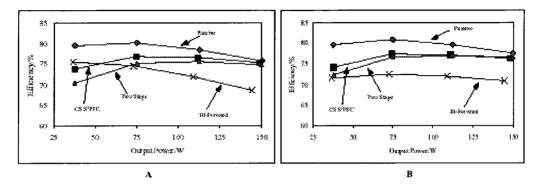

|   |            | 8.4.5<br>8.4.4 | Efficiency                                                                  | 184 |

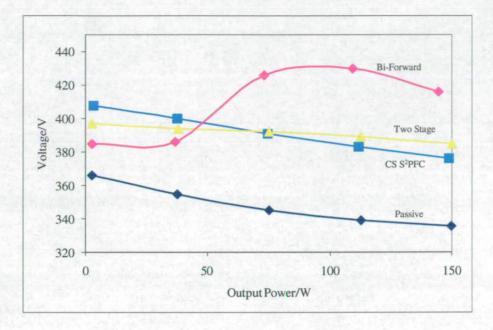

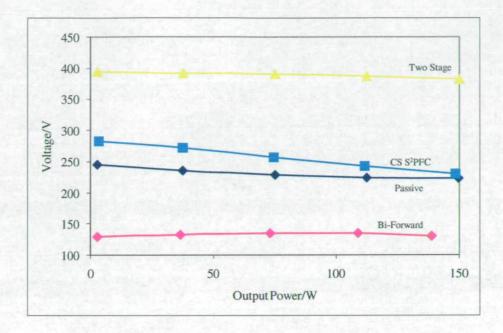

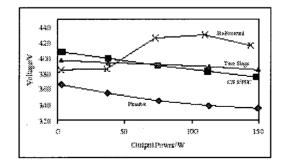

|   |            | 8.4.4<br>8.4.5 | Voltage Across the Bulk Capacitor                                           |     |

|   |            | 8.4.5<br>8.4.6 | Voltage Measured Across Components                                          |     |

|   |            | 8.4.0<br>8.4.7 | Cost                                                                        |     |

|   |            | 8.4.7<br>8.4.8 | Hold Up Time                                                                |     |

|   |            | 0.4.0<br>8.4.9 | Output Voltage Ripple                                                       | 192 |

|   | 05         |                | sion                                                                        |     |

|   | 8.5<br>8.6 |                | sion                                                                        |     |

|   | 0.0        | Conciu         |                                                                             |     |

| 9 | Con        | clusions       | and Further Work                                                            | 198 |

|   | 9.1        |                | Conclusions                                                                 | 198 |

|   | 9.2        | Further        | r Work                                                                      | 200 |

| A | Pred       | licted H       | armonic Content at 100V for the Bi-Forward Converter                        | 202 |

| В | Effe       | ct of Bu       | lk Capacitance Value on the Bi-Forward                                      | 204 |

| G |            |                | -                                                                           | .4  |

| C | Indu       |                | cesults for $N_{1A}$ as 32 and $N_{1B}$ as 12 for the Bi-Forward with Input | 207 |

| D | Pred       | licted P       | erformance of Final CS S <sup>2</sup> PFC Designs                           | 211 |

| E | Pred       | licted H       | armonic Content at 230V for the LFSPFC Converter                            | 214 |

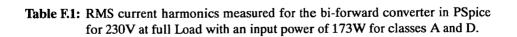

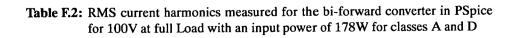

| F | RM         | S Harm         | onic Currents Measured in PSpice                                            | 217 |

| - | F.1        |                | ward Converter                                                              | 217 |

|   | F.2        |                | ward Converter with Input Inductor                                          |     |

|   |            |                | PFC Converter                                                               |     |

|    | F.4   | LFSPFC Converter                                                                                                                                                       | 223 |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| G  | Con   | ponents Used in Test Circuits                                                                                                                                          | 225 |

|    | G.1   | Bi-Forward and Bi-Forward with Input Inductor Converters                                                                                                               | 225 |

|    | G.2   | $CS S2PFC Converter \dots \dots$                                 | 225 |

|    | G.3   | LFSPFC Converter                                                                                                                                                       | 225 |

| Н  | Mea   | sured Efficiency and Bulk Capacitor Voltage                                                                                                                            | 229 |

|    | H.1   | Bi-Forward Converter with Input Inductor                                                                                                                               | 229 |

|    | H.2   | CS S <sup>2</sup> PFC Converter $\ldots \ldots \ldots$ | 229 |

|    | H.3   | LFSPFC Converter                                                                                                                                                       | 229 |

|    | H.4   | Pasive Filter and Forward Converter                                                                                                                                    | 233 |

|    | H.5   | Two Stage Active PFC                                                                                                                                                   | 233 |

| I  | Pub   | lications                                                                                                                                                              | 236 |

| Re | feren | ces                                                                                                                                                                    | 253 |

## **List of Figures**

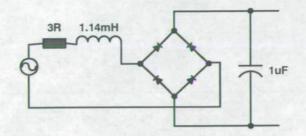

| 1.1  | Diode bridge and capacitive rectification                                    | 2  |

|------|------------------------------------------------------------------------------|----|

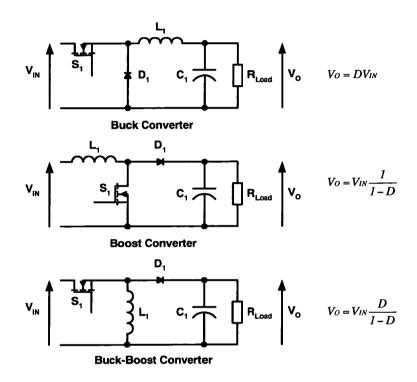

| 2.1  | Basic switched mode power supply topologies                                  | 11 |

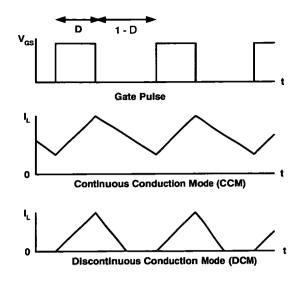

| 2.2  | Different modes of inductor current                                          | 12 |

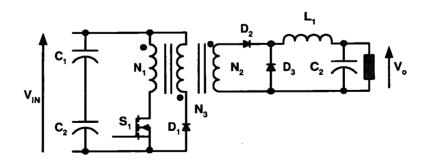

| 2.3  | Single switch forward converter with tertiary reset winding                  | 13 |

| 2.4  | Double switch forward converter                                              | 15 |

| 2.5  | Buck based half bridge converter                                             | 15 |

| 2.6  | Flyback converter                                                            | 16 |

| 2.7  | Passive filtering PFC                                                        | 17 |

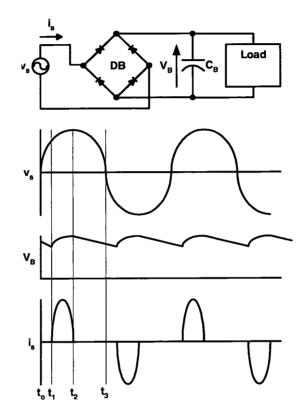

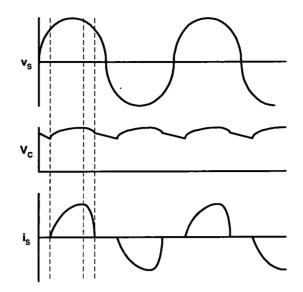

| 2.8  | Passive filtering PFC waveforms                                              | 18 |

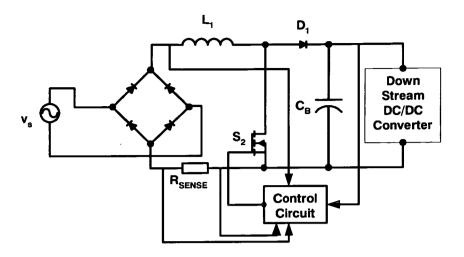

| 2.9  | PFC boost pre-regulator operating in CCM                                     | 19 |

| 2.10 | PFC boost pre-regulator operating in CCM current waveform                    | 19 |

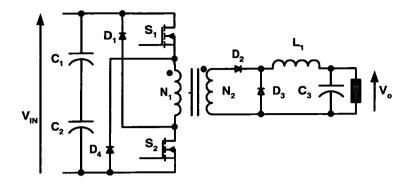

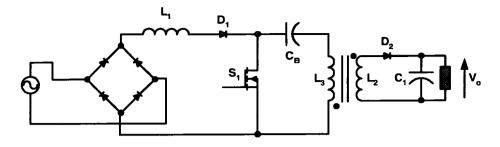

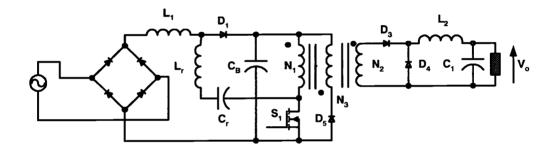

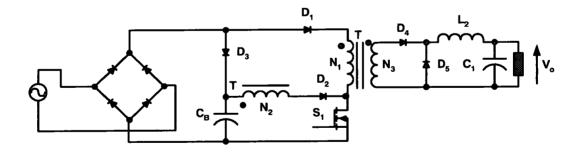

| 3.1  | The differ single stage PFC topology                                         | 24 |

| 3.2  | BIFRED converter                                                             | 25 |

| 3.3  | BIBRED converter                                                             | 25 |

| 3.4  | Single-stage isolated power-factor-corrected power supply(SSIPP)             | 26 |

| 3.5  | The SSIPP converter with possible topological variations                     | 27 |

| 3.6  | SSIPP converter with resonance based variations                              | 29 |

| 3.7  | Magnetic-switch power supply                                                 | 30 |

| 3.8  | Loss free resistor and voltage source PFC converter                          | 30 |

| 3.9  | DCM interleaved SSIPP converter                                              | 32 |

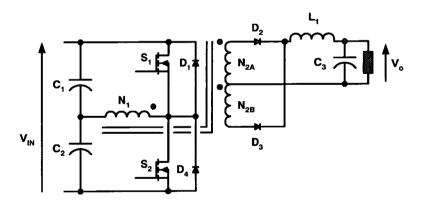

| 3.10 | Double primary Winding SSIPP converter                                       | 32 |

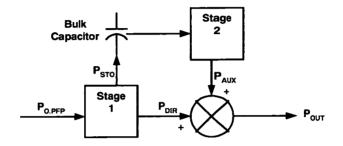

| 3.11 | Parallel PFC power flow                                                      | 33 |

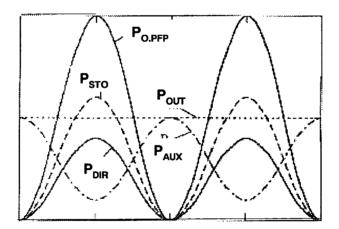

| 3.12 | Powerflow in a line period [3]                                               | 33 |

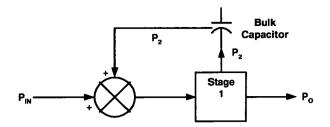

|      | Parallel PFC with altered power flow                                         | 34 |

| 3.14 | Parallel single-stage PFC using pre-regulator with two output capacitors and |    |

|      | auxilary DC/DC converter                                                     | 35 |

| 3.15 | Parallel single-stage PFC using pre-regulator with two output capacitors,    |    |

|      | with different connection, and auxilary DC/DC converter                      | 36 |

|      | Bi-Flyback converter                                                         | 37 |

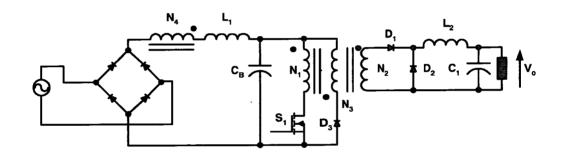

| 3.17 | Bi-Forward converter with single transformer                                 | 37 |

| 3.18 | Bi-Forward converter with centre tapped primary winding and boost type       | 38 |

| 2 10 | input inductor                                                               | 39 |

| 3.19 | The other bi-flyback converter                                               | 59 |

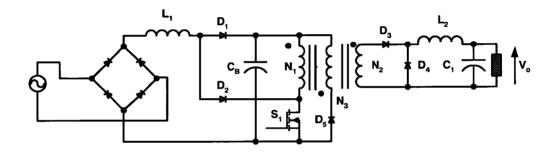

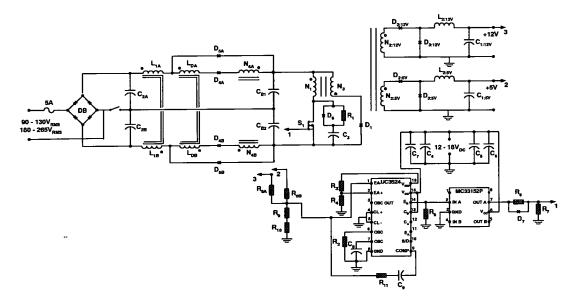

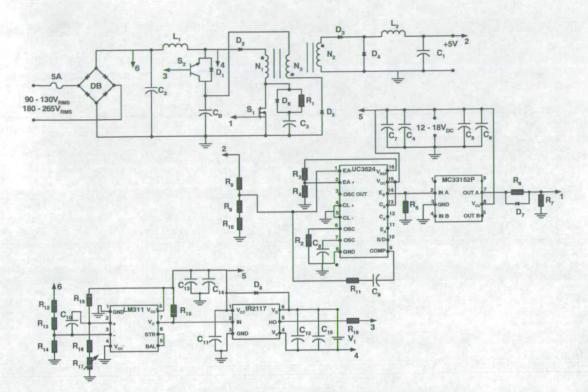

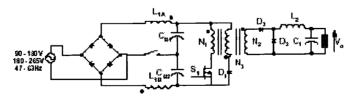

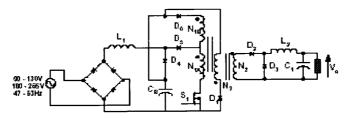

| 4.1  | Bi-Forward converter with two primary windings                               | 42 |

| 4.2  | Bi-Forward converter with centre-tapped primary winding                      | 43 |

| 4.3  | Typical input current waveform for a half line period showing the conduc-    |    |

|      | tion periods                                                                 | 44 |

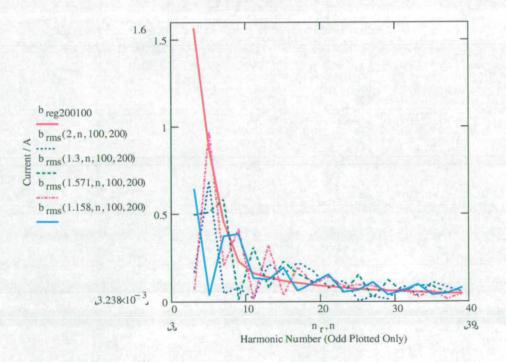

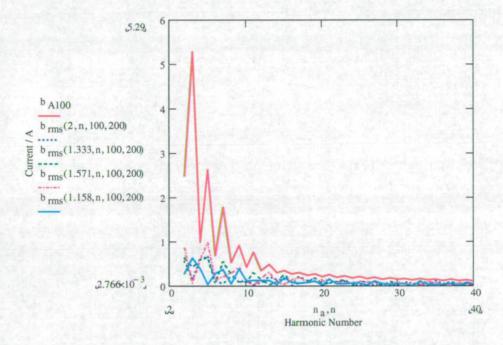

| 4.4          | RMS input current harmonics compared to class D ( $b_{reg200}$ curve) for 230V input with an input power of 200W with n as 2, 1.3, 1.57 and 1.16. Traces are listed by side of graph.                                                                      | 48       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.5          | RMS input current compared to class A (curve $b_A$ ) for 230V input with an input power of 200W with n as 2, 1.3, 1.57 and 1.16. Traces are listed by side of graph: 1st value is n, 2nd value is the input voltage and 3rd value is                       | 49       |

| 4.6          | the power                                                                                                                                                                                                                                                  |          |

|              | voltage and 3rd value is the number of turns on $N_{1A}$                                                                                                                                                                                                   | 51       |

| 4.7          | PSpice circuit schematic                                                                                                                                                                                                                                   | 54       |

| 4.8          | PSpice voltage mode controller                                                                                                                                                                                                                             | 55       |

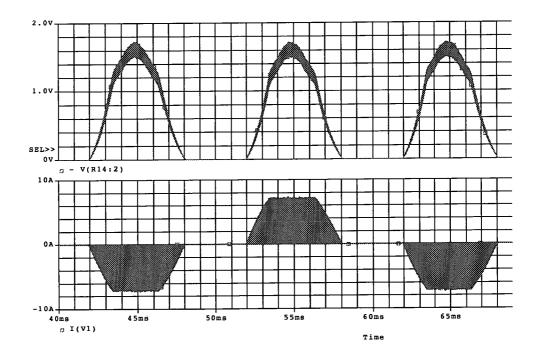

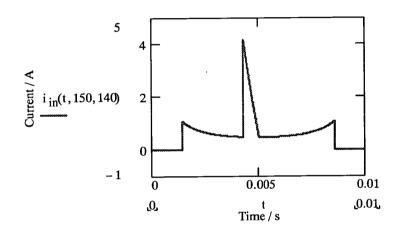

| 4.9          | Line frequency waveforms produced by PSpice at 230V input voltage and 150W output power. Top trace) averaged input current seen as a voltage                                                                                                               | 58       |

| 4.10         | across $R_{14}$ and, bottom trace) unaveraged input current                                                                                                                                                                                                |          |

|              | output at line frequency                                                                                                                                                                                                                                   | 59<br>60 |

| 4.11<br>4.12 | Final and complete circuit schematic for the bi-forward converter Measured RMS input current harmonics at 100V and full load compared to class D and A                                                                                                     | 61       |

| 4.13         | Measured RMS input current harmonics at 100V and 75W input power compared to class D                                                                                                                                                                       | 62       |

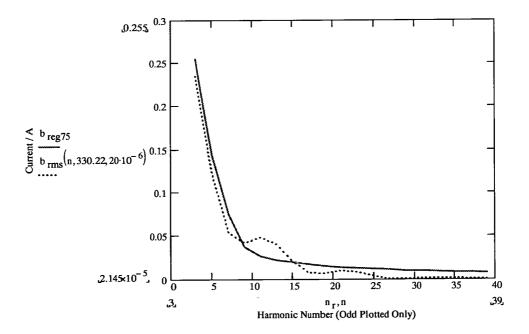

| 4.14         | Measured RMS input current harmonics at 230V and 75W input power (77W) compared to class D                                                                                                                                                                 | 62       |

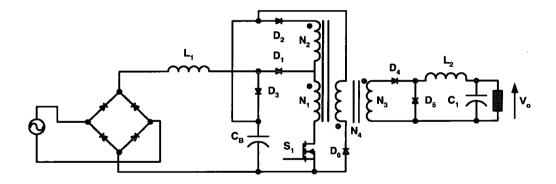

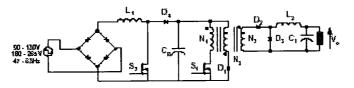

| 5.1          | Bi-Forward converter with input inductor $L_1$                                                                                                                                                                                                             | 65       |

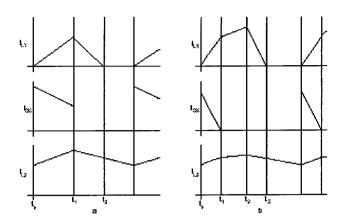

| 5.2          | Typical input current waveform for a half line period showing the different conduction periods of $L_1$                                                                                                                                                    | 65       |

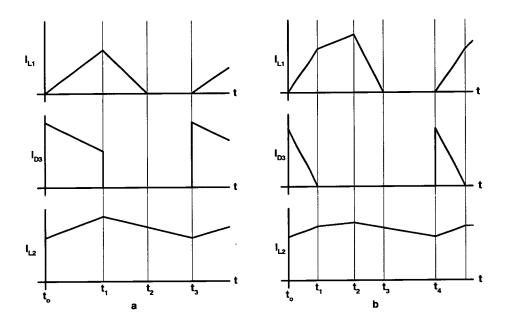

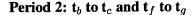

| 5.3          | a: Current waveforms for $L_1$ , $D_3$ and $L_2$ when input voltage is low between $t_b$ to $t_c$ and $t_f$ to $t_g$ ,                                                                                                                                     | 66       |

| 5.4          | a: Current waveforms for $L_1$ , $D_3$ and $L_2$ when input voltage is high between $t_4$ to $t_2$ .                                                                                                                                                       | 67       |

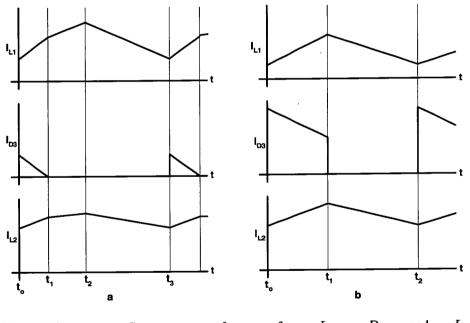

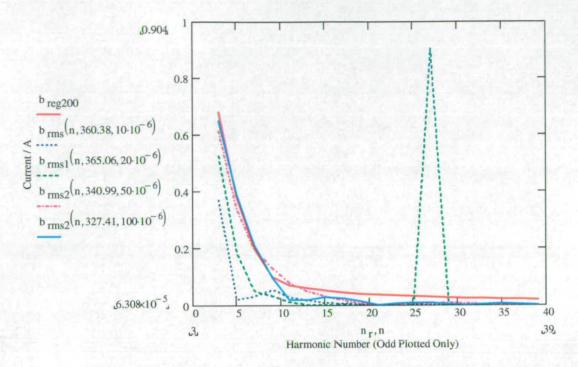

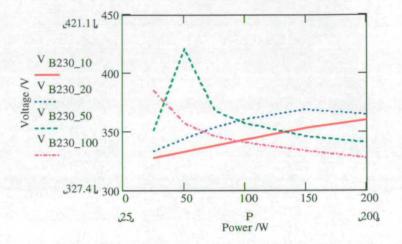

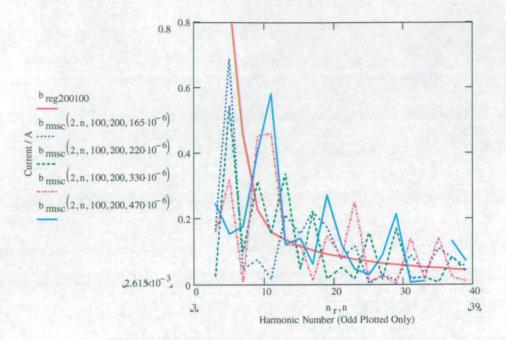

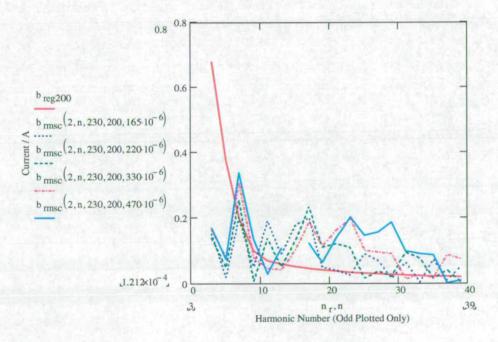

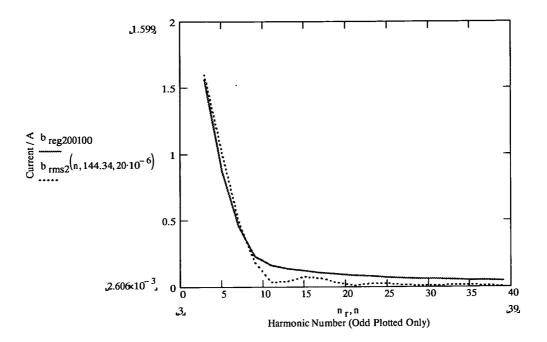

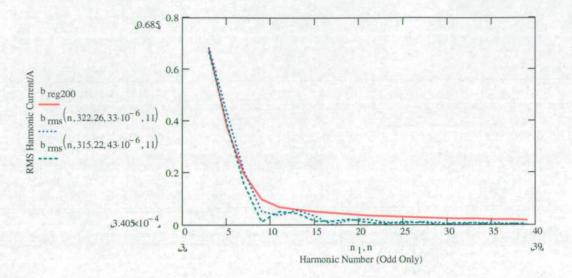

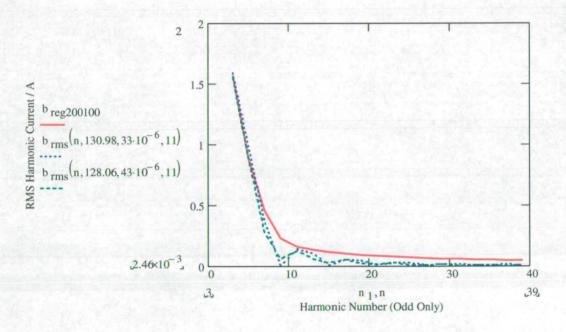

| 5.5          | Input current class D (trace $b_{reg200}$ ) harmonics for 230V input with an input power of 200W with $L_1$ as 10, 20, 50 and 100 $\mu$ H. Traces are listed by side of graph, 1st value is the voltage on $C_B$ and the 2nd value is the value of $L_1$ . | 79       |

| 5.6          | Input current class D (trace $b_{reg200100}$ ) harmonics for 100V input with an input power of 200W with $L_1$ as 10, 20 and 50 $\mu$ H. Traces are listed by side                                                                                         | ,,       |

|              | of graph, 1st value is the voltage on $C_B$ and the 2nd value is the value of $L_1$ .                                                                                                                                                                      | 80       |

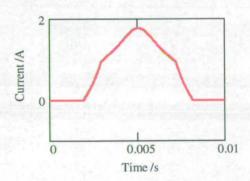

| 5.7          | Predicted input current waveform at 200W input power at 230V with $L_1$ as 10 $\mu$ H. The current is flowing in periods 1, 2 and 3. $V_B$ is 360V                                                                                                         | 80       |

| 5.8          | Predicted input current waveform at 200W input power at 230V with $L_1$ as 20 $\mu$ H. The current is flowing in periods 1 and 2. $V_B$ is 365V                                                                                                            | 81       |

| 5.9          | Predicted input current waveform at 200W input power at 230V with $L_1$ as $50\mu$ H. The current is flowing in period 1, 2 and 2a. $V_B$ is 341V                                                                                                          | 81       |

|              | Predicted input current waveform at 25W input power at 90V with $L_1$ as 10 $\mu$ H. The current is flowing in period 1, 2, 3 and 4. $V_B$ is 128V                                                                                                         | 81       |

| 5.11         | Predicted input current waveform at 25W input power at 100V with $L_1$ as 20 $\mu$ H. The current is flowing in period 1, 2, 2a and 4a. $V_B$ is 159V                                                                                                      | 82       |

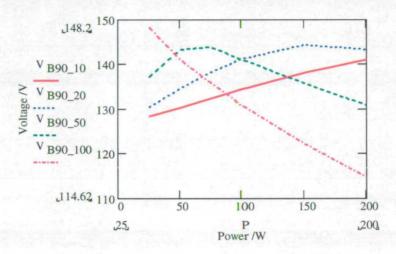

| 5.12 | Predicted voltage on bulk capacitor $C_B$ at 90V input for $L_1 = 10, 20, 50$<br>and $100\mu$ H. Traces are listed by side of graph. 1st value is the input voltage | 83 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| - 10 | and the 2nd value the value of $L_1$                                                                                                                                | 65 |

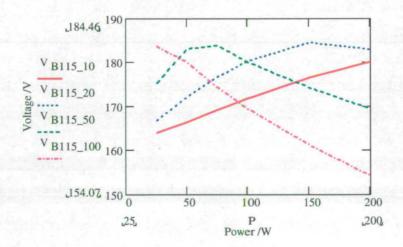

| 5.13 | Predicted voltage on bulk capacitor $C_B$ at 115V input for $L_1 = 10, 20, 50$                                                                                      |    |

|      | and $100\mu$ H. Traces are listed by side of graph. 1st value is the input voltage                                                                                  | 00 |

|      | and the 2nd value the value of $L_1$                                                                                                                                | 83 |

| 5.14 | Predicted voltage on bulk capacitor $C_B$ at 230V input for $L_1 = 10, 20, 50$                                                                                      |    |

|      | and $100\mu$ H. Traces are listed by side of graph. 1st value is the input voltage                                                                                  |    |

|      | and the 2nd value the value of $L_1$                                                                                                                                | 84 |

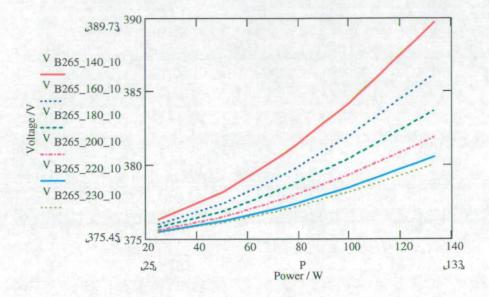

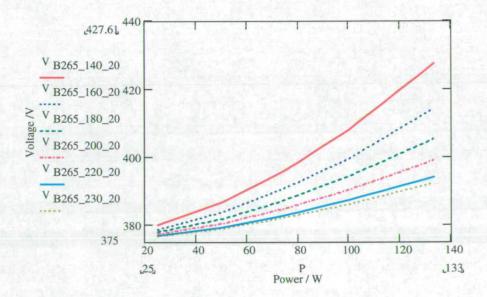

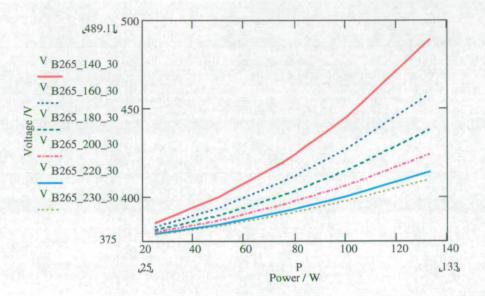

| 5.15 | Predicted voltage on bulk capacitor $C_B$ at 265V input for $L_1 = 10, 20, 50$                                                                                      |    |

|      | and $100\mu$ H. Traces are listed by side of graph. 1st value is the input voltage                                                                                  |    |

|      | and the 2nd value the value of $L_1$                                                                                                                                | 84 |

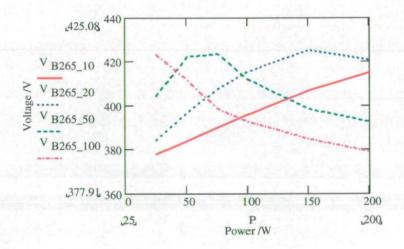

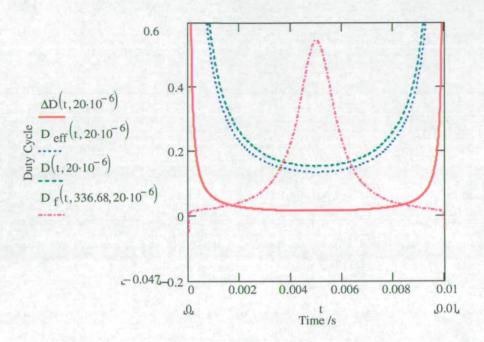

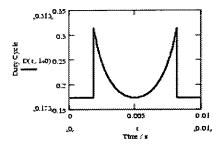

| 5.16 | Predicted duty cycle variation for 100V 200W input over a half line cycle.                                                                                          |    |

|      | Red trace is $D_2$ the duty cycle when supplied from $C_B$ , blue dot trace is                                                                                      |    |

|      | $D_3$ the on duty cycle for $S_1$ , green dash trace is $\Delta D_3$ the duty of the period                                                                         |    |

|      | where $L_1$ is charged up to the load current, lilac dash-dot trace is $D_{f3}$ the                                                                                 |    |

|      | duty for the fall of current in $L_1$ to zero and light blue trace is $D_1 + D_{f2}$                                                                                |    |

|      | the overall condution duty for $L_1$ with $V_B$ at 361V and $L_1$ equal to 10 $\mu$ H.                                                                              | 85 |

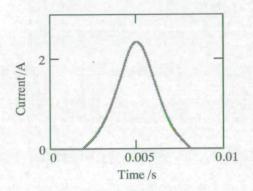

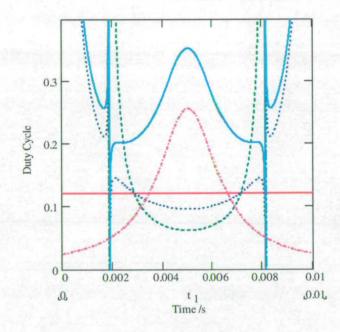

| 5.17 | Simulated averaged and non average input current waveforms for 230V and                                                                                             |    |

|      | $L_1 = 10\mu$ H. The converter is operating in periods 1 to 3. The top trace is                                                                                     |    |

|      | the averaged current shown as a voltage across $R_{14}$ and the bottom trace is                                                                                     |    |

|      | the non averaged current shown as a current.                                                                                                                        | 90 |

| 5.18 | Simulated averaged and non averaged input current waveforms for 230V                                                                                                |    |

|      | and $L_1 = 20\mu$ H. The converter is operating in periods 1 and 2. The top                                                                                         |    |

|      | trace is the averaged current shown as a voltage across $R_{14}$ and the bottom                                                                                     |    |

|      | trace is the non averaged current shown as a current.                                                                                                               | 90 |

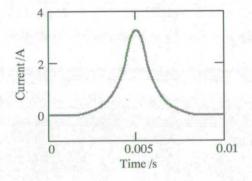

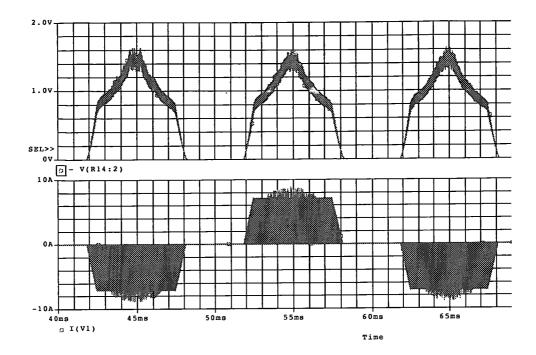

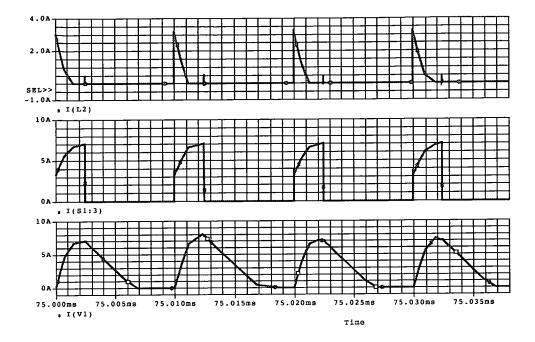

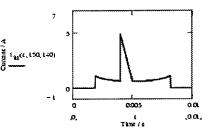

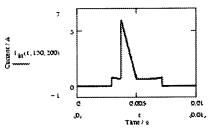

| 5.19 | Switching frequency simulation results showing period 3 conduction for                                                                                              |    |

|      | 100V and $L_1 = 10\mu$ H. Top trace is the current in $N_{1B}$ (or $L_2$ in the simula-                                                                             |    |

|      | tion), the centre trace is the current in $S_1$ and the bottom trace is the current                                                                                 |    |

|      | in $L_1$ .                                                                                                                                                          | 91 |

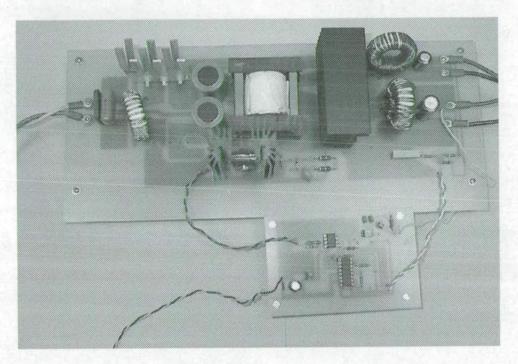

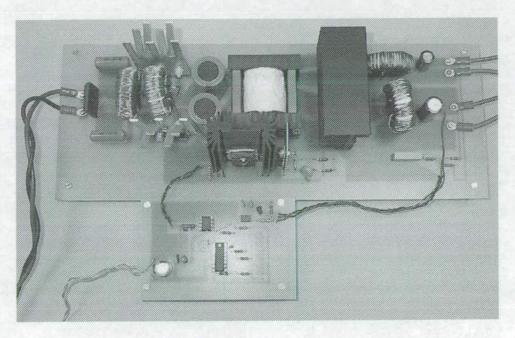

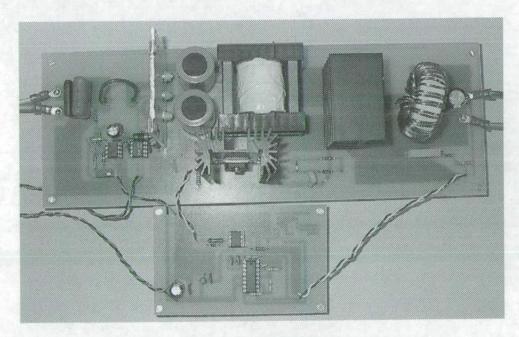

| 5.20 | Photograph of the bi-forward converter with $L_1$                                                                                                                   | 92 |

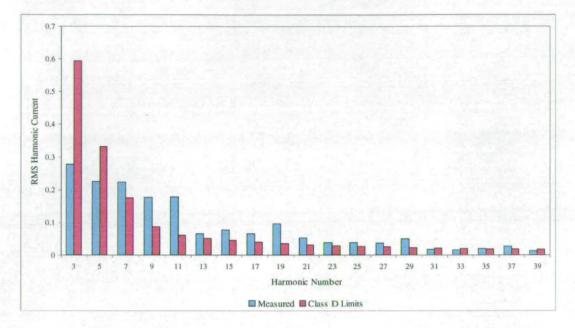

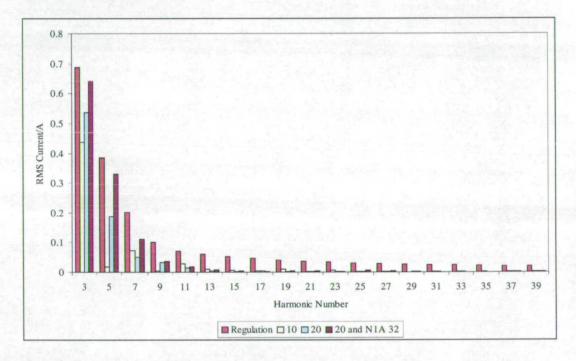

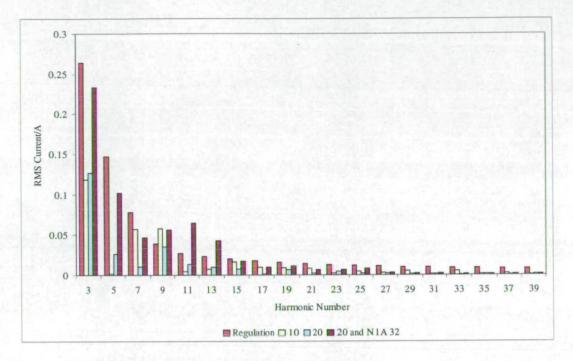

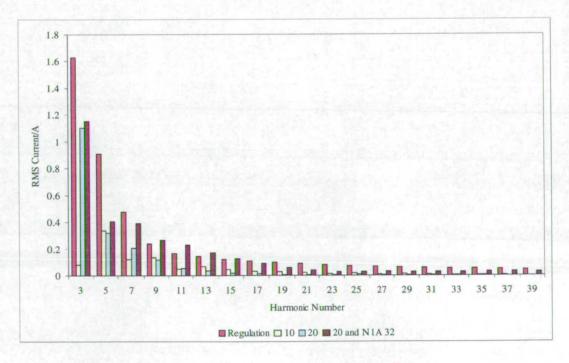

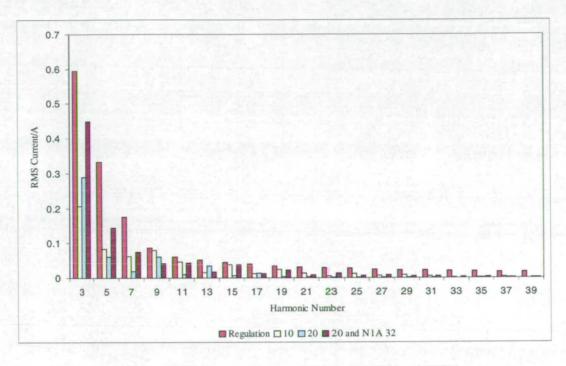

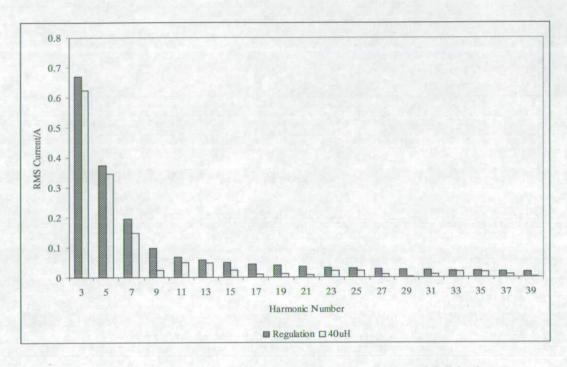

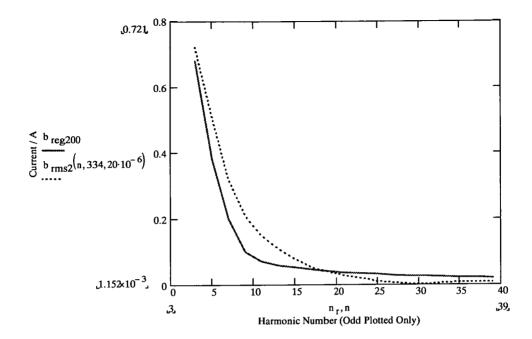

|      | Measured RMS current harmonic levels for 230V and full load output com-                                                                                             |    |

|      | pared to class D                                                                                                                                                    | 93 |

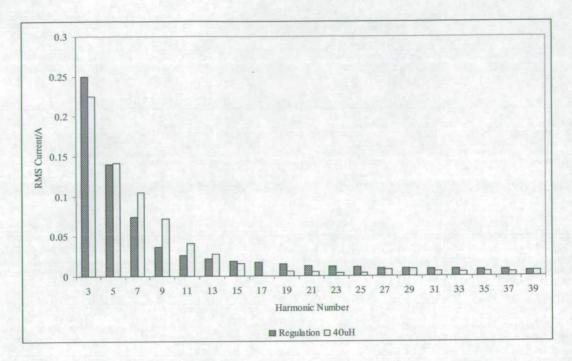

| 5.22 | Measured RMS current harmonic levels for 230V and 75W input power                                                                                                   |    |

|      | compared to class D                                                                                                                                                 | 94 |

| 5.23 | Measured RMS current harmonic levels for 100V and full load output com-                                                                                             |    |

|      | pared to class D                                                                                                                                                    | 94 |

| 5.24 | Measured RMS current harmonic levels for 100V and 75W input power                                                                                                   |    |

|      | compared to class D                                                                                                                                                 | 95 |

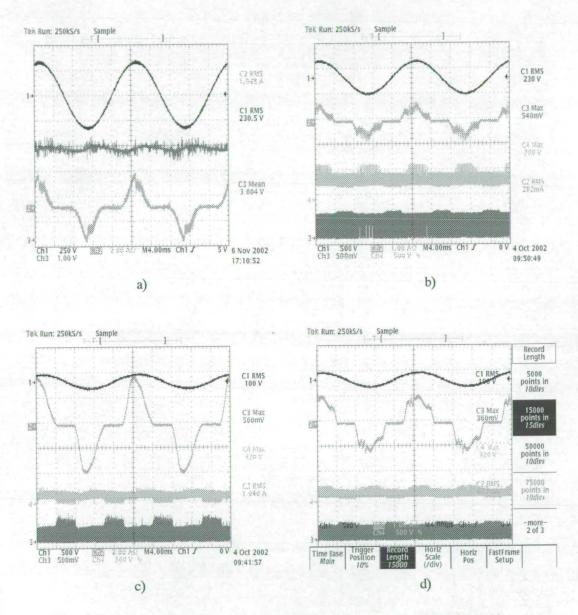

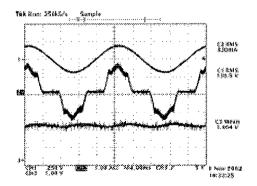

| 5.25 | Measured a) filtered input current at full load and 230V, b) filtered input                                                                                         |    |

|      | current at 75W and 230V, c) filtered input current at full load and 100V and                                                                                        |    |

|      | d) filtered input current at 75W and 100V for $L_1$ as 20 $\mu$ H. Top trace input                                                                                  |    |

|      | voltage, 2nd trace down input current (except a) where it is the voltage on                                                                                         |    |

|      | $C_B$ ), 3rd trace down voltage across $D_6$ (except a) where it is input current)                                                                                  |    |

|      | and bottom trace voltage across $S_1$                                                                                                                               | 97 |

| 5.26 | Measured a) Current in $L_1$ at full load and 230V, b) Current in $L_1$ at 75W                                                                                      | ·  |

| 2.20 | and 115V taken over the peak of input voltage. Top trace: $V_{ds}$ of $S_1$ , 2nd                                                                                   |    |

|      | trace down: $I_{L1}$ , 3rd trace down: $V_{D1}$ and the bottom: $V_{D2}$                                                                                            | 98 |

| 5.27 | Efficiency of the bi-forward converter with input inductor $L_1$                                                                                                    | 98 |

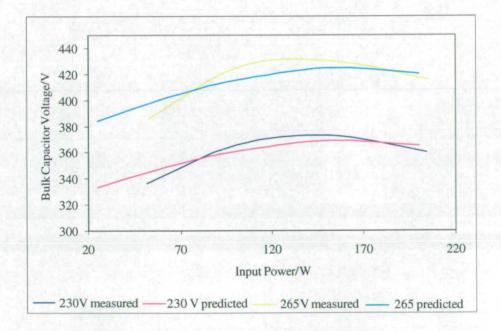

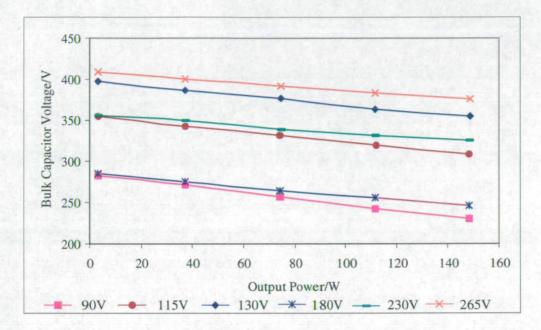

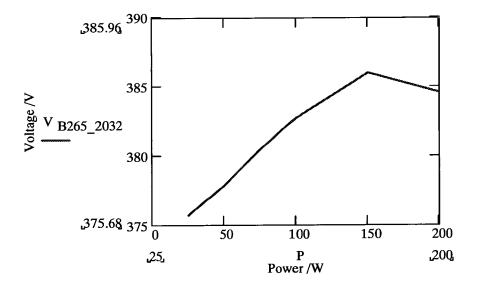

|      | Variation of bulk capacitor voltage with output power at various voltages                                                                                           | 99 |

| 5.20 | and of our expression to ange that output porter at tartous to anges the                                                                                            |    |

|      |                                                                                                                                                                     |    |

|                   | Variation of bulk capacitor voltage with input power on the low voltage range compared to predicted bulk capacitor voltage                                                             | 100         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 5.30              | Variation of bulk capacitor voltage with input power on the high voltage range compared to predicted bulk capacitor voltage                                                            | 100         |

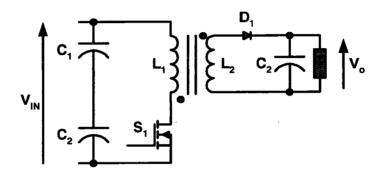

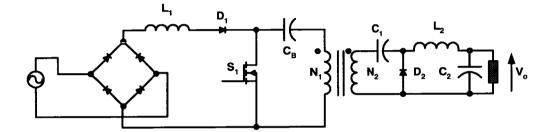

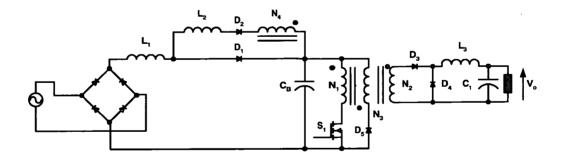

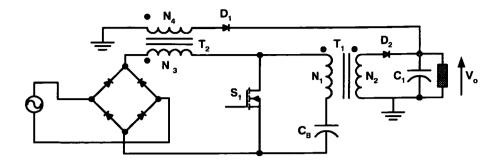

| 6.1               | Loss free resistor and voltage source PFC converter                                                                                                                                    | 1 <b>07</b> |

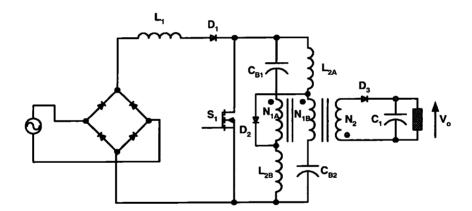

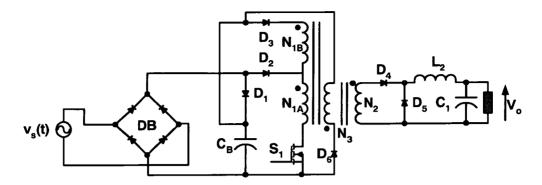

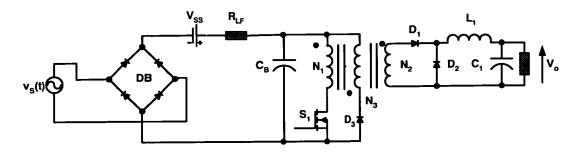

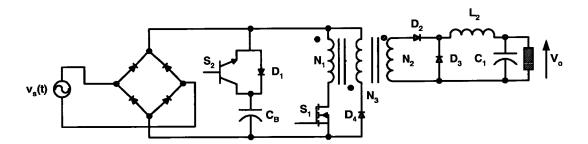

| 6.2               | gle Stage PFC Converter (CS S <sup>2</sup> PFC) $\ldots \ldots \ldots$ | 107         |

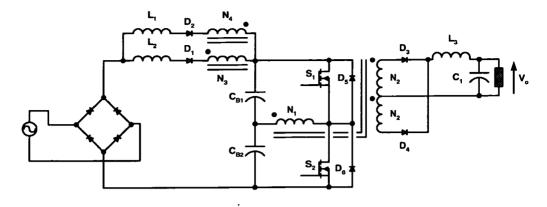

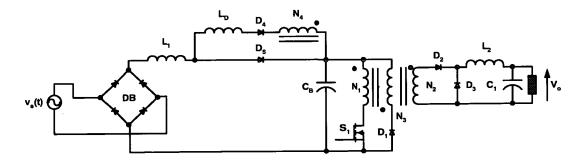

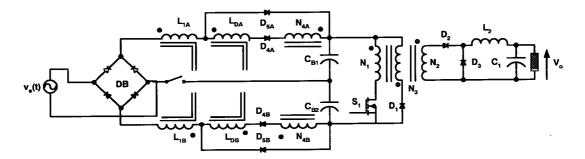

| 6.3               | CS S <sup>2</sup> PFC converter with voltage doubler $\ldots$                                                                                                                          | 108         |

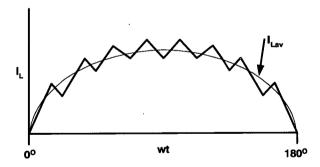

| 6.4               | Conceptual average input current                                                                                                                                                       | 100         |

| 6.5               | Waveforms in the current shaper at switching frequency when operating in                                                                                                               | 107         |

| 0.5               | DCM                                                                                                                                                                                    | 110         |

| 6.6               | Waveforms in the Current Shaper at Switching Frequency when operating                                                                                                                  | 110         |

| 0.0               | in CCM                                                                                                                                                                                 | 112         |

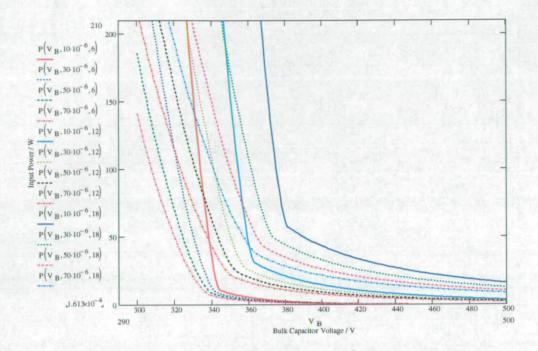

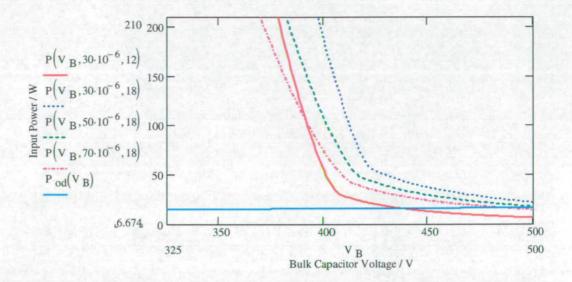

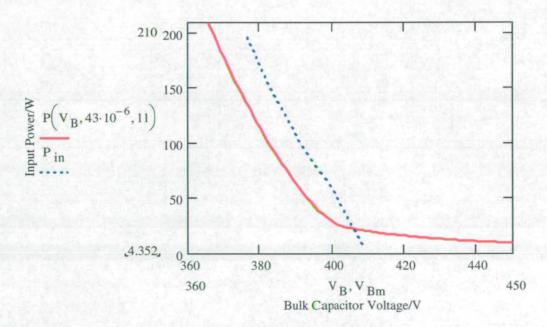

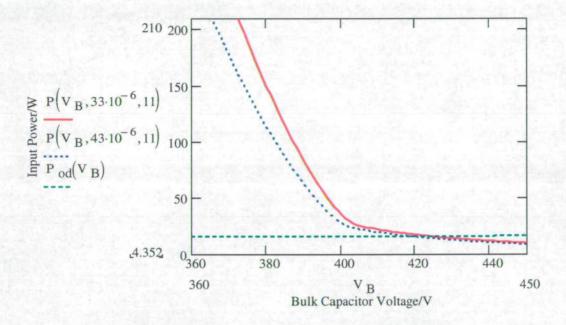

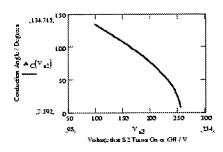

| 6.7               | Graphs showing power against bulk capacitor voltage for $230V_{RMS}$ input                                                                                                             | 114         |

| 0.7               | for $L_{DA}/L_{DB} = 10, 30, 50, 70 \mu$ H with $N_{4A}$ and $N_{4B}$ as either 6, 12, or 18                                                                                           |             |

|                   | Turns. Traces are listed by side of graph, 1st value is the value of $L_{DA}$ and                                                                                                      |             |

|                   | $L_{DB}$ and 2nd value is the number of turns on $N_{4A}$ and $N_{4B}$ .                                                                                                               | 121         |

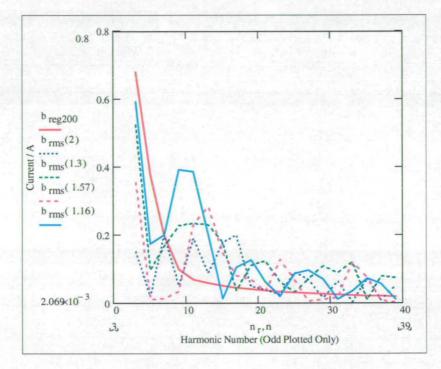

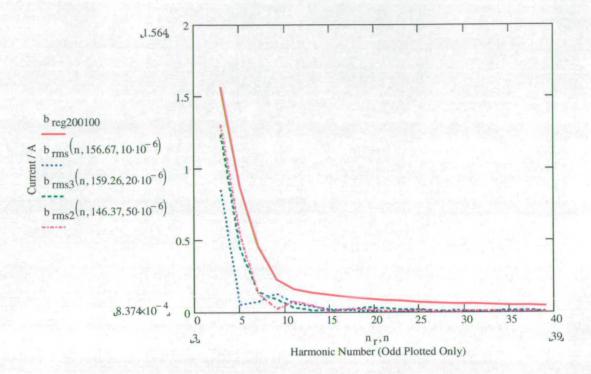

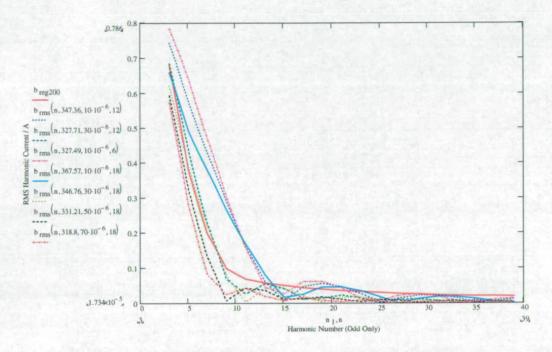

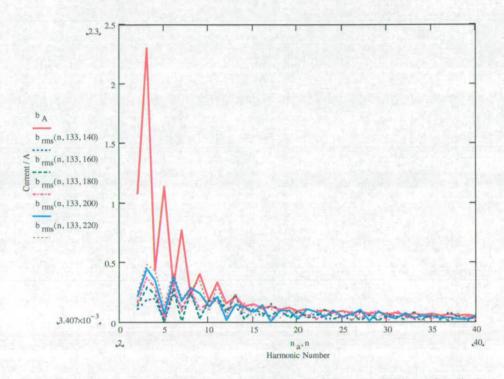

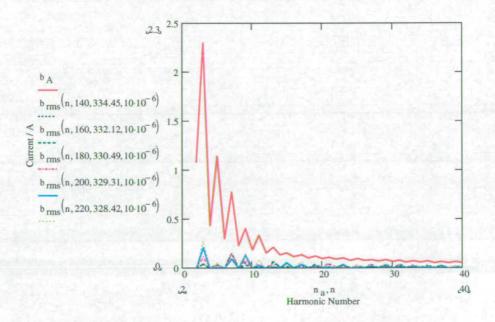

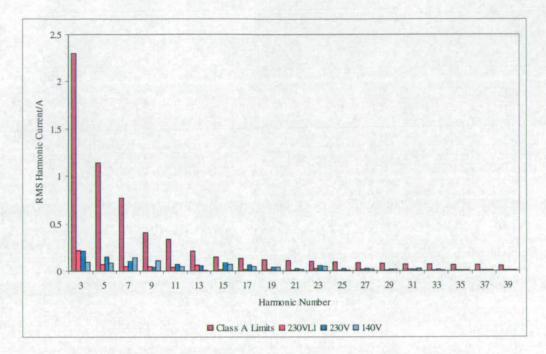

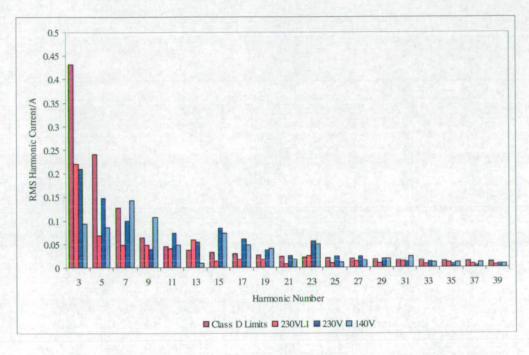

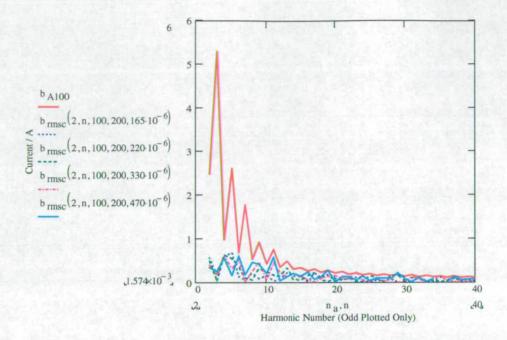

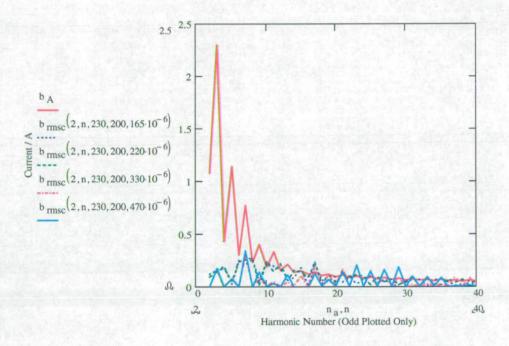

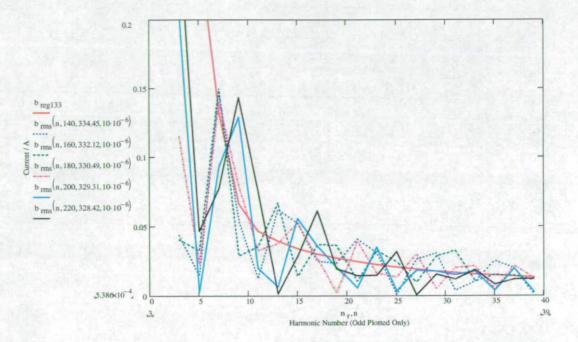

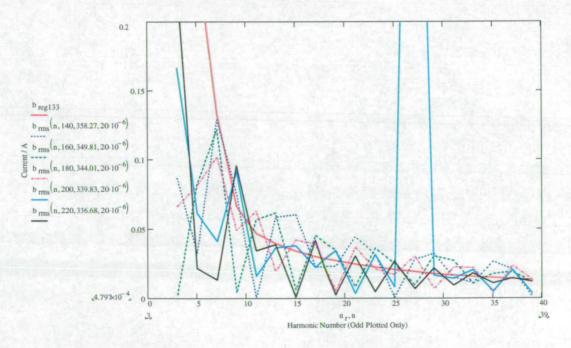

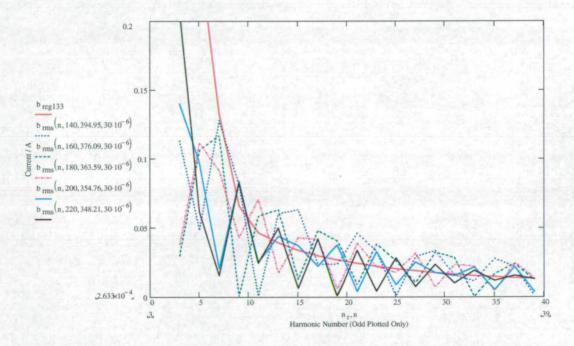

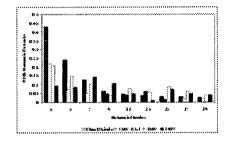

| 6.8               | Odd harmonic spectrum for input power and voltage of 200W 230V <sub>RMS</sub>                                                                                                          | 121         |

| 0.0               | for the remaining curves (only odd harmonics are plotted). The red trace                                                                                                               |             |

|                   | $(b_{reg200})$ is the class D limits for 200W. Traces are listed by side of graph:                                                                                                     |             |

|                   | $(b_{reg200})$ is the class D limits for 200 w. Haces are listed by side of graph.<br>1st value is the voltage on $C_B$ , 2nd value is the value of $L_{DA}$ and $L_{DB}$ and          |             |

|                   | 3rd value is the number of turns on $N_{4A}$ and $N_{4B}$                                                                                                                              | 122         |

| 6.9               | Graphs showing power against bulk capacitor voltage for $265V_{RMS}$ input                                                                                                             | 100         |

| 0.9               | for $L_{DA}$ and $L_{DB} = 30 \mu \text{H}$ with $N_{4A}/N_{4B}$ as 12 and $L_{DA}$ and $L_{DB} = 30$ ,                                                                                |             |

|                   | 50 and $70\mu$ H with $N_{4A}/N_{4B}$ . Traces are listed by side of graph: 1st value                                                                                                  |             |

|                   | is the value of $L_{DA}$ and $L_{DB}$ and 2nd value is the number of turns on $N_{4A}$                                                                                                 |             |

|                   | and $N_{4B}$                                                                                                                                                                           | 123         |

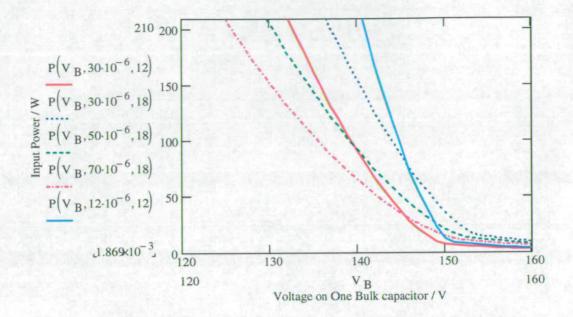

| 6 10              | Graphs showing power against bulk capacitor voltage for $100V_{RMS}$ input                                                                                                             |             |

| 0.10              | for $L_{DA}$ and $L_{DB} = 30 \mu$ H with $N_{4A}$ and $N_{4B}$ as 12 and $L_{DA}$ and $L_{DB} =$                                                                                      |             |

|                   | 30, 50 and $70\mu$ H with $N_{4A}$ and $N_{4B}$ . Traces are listed by side of graph: 1st                                                                                              |             |

|                   | value is the value of $L_{DA}$ and $L_{DB}$ and 2nd value is the number of turns on                                                                                                    |             |

|                   | $N_{4A}$ and $N_{4B}$                                                                                                                                                                  | 124         |

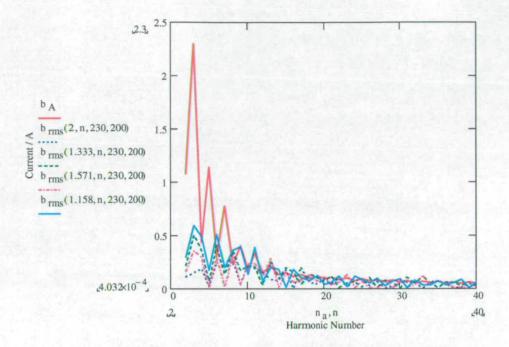

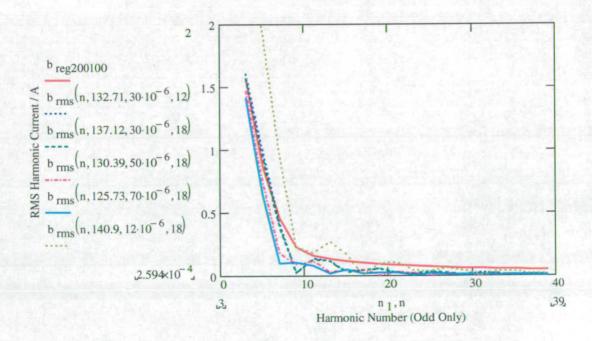

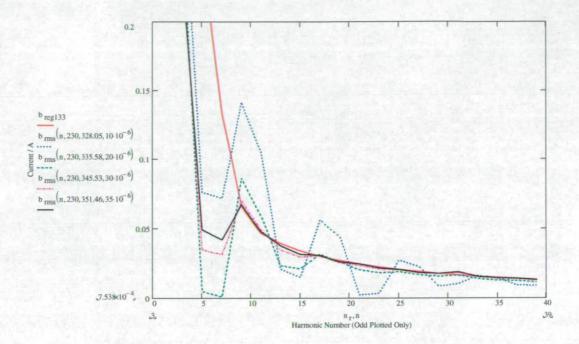

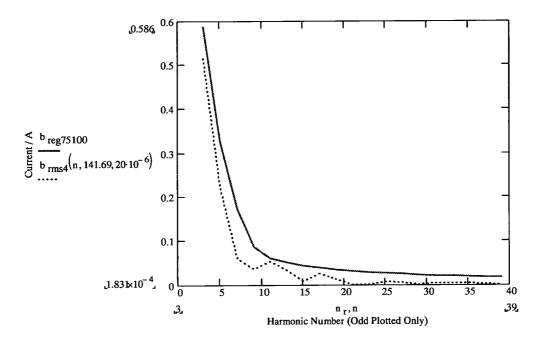

| 6.11              | Odd harmonic spectrum for input power and voltage of 200W $100V_{RMS}$                                                                                                                 |             |

|                   | for the remaining curves (only odd harmonics are plotted). The red trace                                                                                                               |             |

|                   | $(b_{reg200100})$ is the class D limits for 200W. Traces are listed by side of graph:                                                                                                  |             |

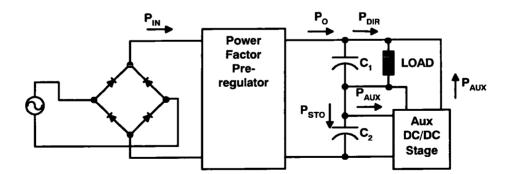

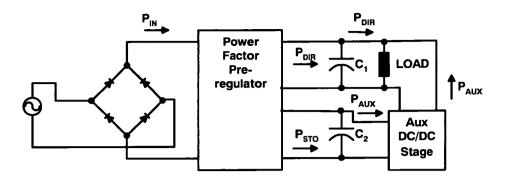

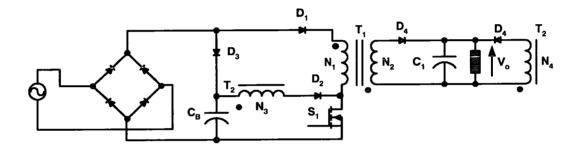

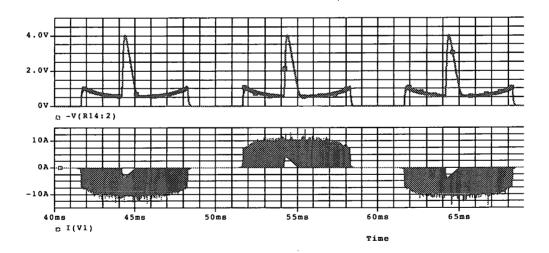

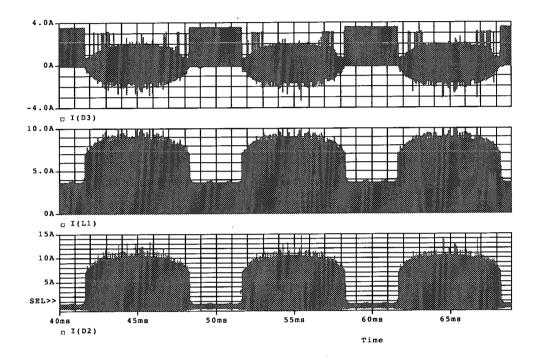

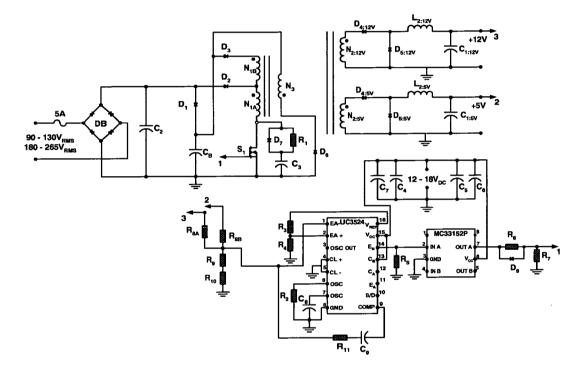

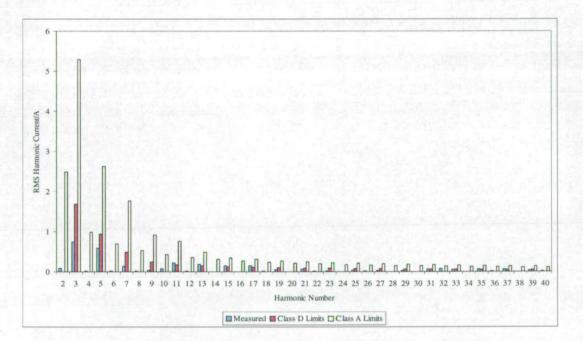

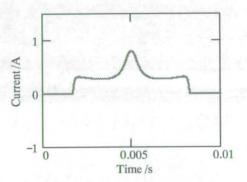

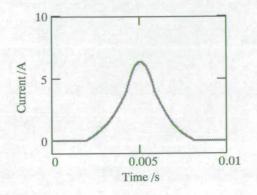

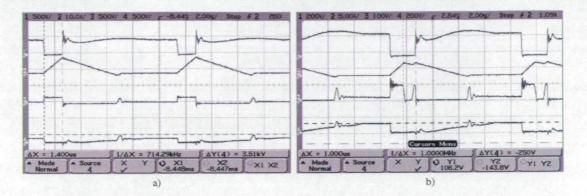

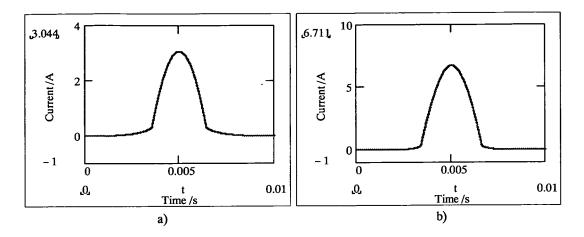

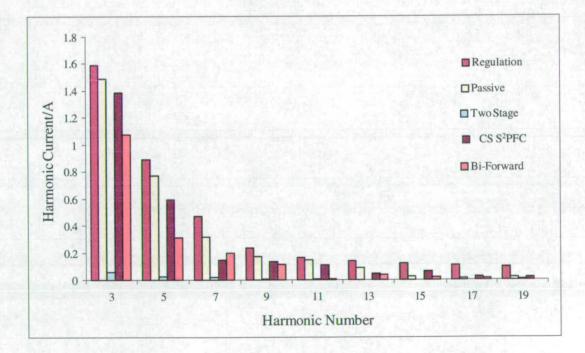

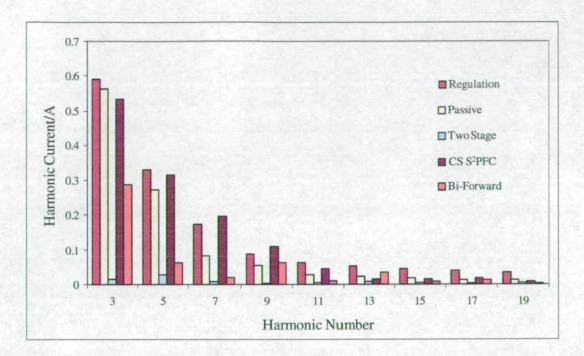

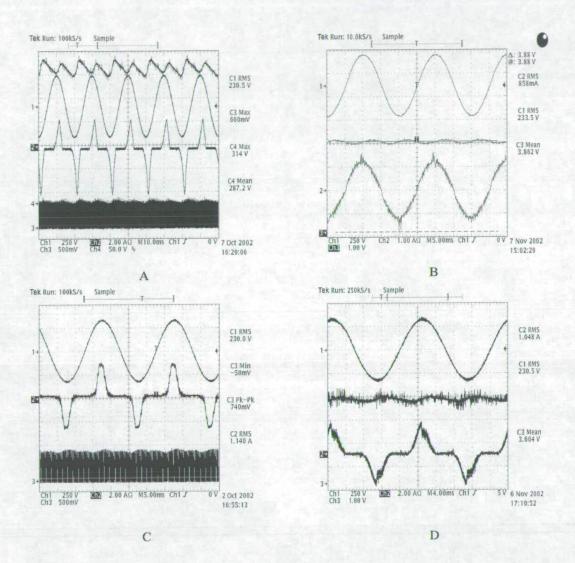

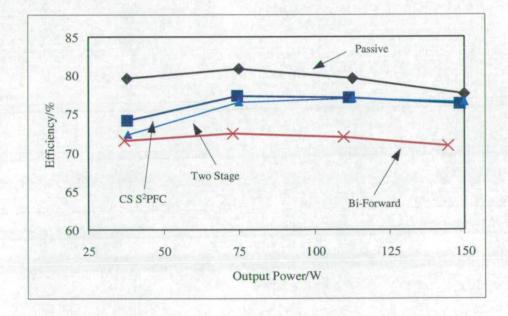

|                   | 1st value is the voltage on a single $C_B$ , 2nd value is the value of $L_{DA}$ and                                                                                                    |             |