# Hierarchical Architectural Design and Simulation Environment

Alexander Ronnfeldt Robertson

Ph.D.

University of Edinburgh

1995

June 4, 1995

#### Abstract

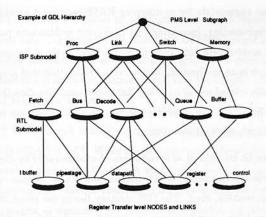

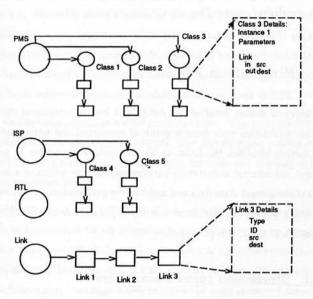

The Hierarchical Architectural design and Simulation Environment (HASE) is intended as a flexible tool for computer architects who wish to experiment with alternative architectural configurations and design parameters. HASE is both a design environment and a simulator. Architecture components are described by a hierarchical library of objects defined in terms of an object oriented simulation language. HASE instantiates these objects to simulate and animate the execution of a computer architecture. An event trace generated by the simulator therefore describes the interaction between architecture components, for example, fetch stages, address and data buses, sequencers, instruction buffers and register files. The objects can model physical components at different abstraction levels, eg. PMS (processor memory switch), ISP (instruction set processor) and RTL (register transfer level). HASE applies the concepts of inheritance, encapsulation and polymorphism associated with object orientation, to simplify the design and implementation of an architecture simulation that models component operations at different abstraction levels. For example, HASE can probe the performance of a processor's floating point unit, executing a multiplication operation, at a lower level of abstraction, i.e. the RTL, whilst simulating remaining architecture components at a PMS level of abstraction. By adopting this approach, HASE returns a more meaningful and relevant event trace from an architecture simulation. Furthermore, an animator visualises the simulation's event trace to clarify the collaborations and interactions between architecture components. The prototype version of HASE is based on GSS (Graphical Support System), and DEMOS (Discrete Event Modelling On Simula).

# Table of Contents

| 1. | Arc | chitect | ural Issues and the Design Problem | 1 |

|----|-----|---------|------------------------------------|---|

|    | 1.1 | Intro   | duction                            | 1 |

|    | 1.2 | Defini  | ing Computer Architecture          | 3 |

|    |     | 1.2.1   | The PMS Level                      | 4 |

|    |     | 1.2.2   | ISP Level                          | 4 |

|    |     | 1.2.3   | RT Level                           | 5 |

|    | 1.3 | Archi   | tecture Experiments                | 6 |

|    |     | 1.3.1   | Memory Latency Issues              | 6 |

|    |     | 1.3.2   | Pipeline Issues                    | 1 |

|    |     | 1.3.3   | Internal Parallelism               | 6 |

|    |     | 1.3.4   | Code density Experiments           | 0 |

|    |     | 1.3.5   | Overlapping Register Windows       | 1 |

|    |     | 1.3.6   | Impact of Compiler Optimisation    | 2 |

|    | 1.4 | The A   | rchitecture Design Problem         | 3 |

|    |     | 1.4.1   | Analytical Approach                | 3 |

|    |     | 1.4.2   | Simulation Approach                | 4 |

|    |     | 1.4.3   | Motivation for HASE                | 2 |

|    | 1 411 | damen  | car concepts of Simulation   |   |   |     |  |   |   |   |      |   |      |     |   |   | 00 |

|----|-------|--------|------------------------------|---|---|-----|--|---|---|---|------|---|------|-----|---|---|----|

|    | 2.1   | Conce  | pt of a System               |   |   |     |  | • | ٠ |   | • 5  | • |      | •   | * |   | 35 |

|    |       | 2.1.1  | Definitions                  |   |   |     |  |   |   |   |      |   | ×    |     |   | ٠ | 36 |

|    |       | 2.1.2  | Classifying Systems          |   |   |     |  |   |   |   | ٠    |   |      |     |   | ٠ | 36 |

|    | 2.2   | Discre | te System Simulation         | • |   |     |  |   |   |   |      | • | •    | *13 |   | * | 39 |

|    | 2.3   | Simula | ation Languages              |   |   |     |  |   |   |   |      |   |      |     |   |   | 41 |

|    |       | 2.3.1  | Programming Representation   |   |   |     |  |   |   |   |      |   |      |     |   |   | 41 |

|    |       | 2.3.2  | Object Oriented Programming  |   |   |     |  |   |   |   |      |   |      |     |   |   | 42 |

|    |       | 2.3.3  | SIMULA                       |   | • |     |  |   |   |   |      |   |      |     |   |   | 45 |

|    |       | 2.3.4  | Sim++ and Virtual Time       |   |   |     |  |   |   |   |      |   |      |     |   |   | 46 |

|    | 2.4   | Diagra | ammatic Representation       |   |   |     |  |   |   |   |      |   |      |     |   |   | 47 |

|    |       | 2.4.1  | Attraction of Diagrams       |   |   |     |  |   |   |   |      |   |      |     |   |   | 47 |

|    |       | 2.4.2  | Software Graphics            |   |   |     |  |   |   |   |      |   |      |     |   |   | 47 |

|    |       | 2.4.3  | Comments                     |   |   |     |  |   |   |   |      |   |      |     |   |   | 49 |

| 3. | The   | HASI   | E Design Environment         |   |   |     |  |   |   |   |      |   |      |     |   |   | 50 |

|    | 3.1   | Overv  | iew                          |   |   |     |  |   |   |   |      |   | 7.50 |     |   |   | 50 |

|    | 3.2   | Progra | amming Environment           |   |   |     |  |   |   |   |      |   |      |     |   |   | 52 |

|    |       | 3.2.1  | Prototyping in DEMOS         |   |   |     |  |   |   |   |      |   |      |     |   | • | 52 |

|    |       | 3.2.2  | Hardware Resources           |   |   |     |  |   |   |   |      |   |      |     |   |   | 53 |

|    | 3.3   | Design | Environment                  |   |   |     |  |   |   | ٠ | •    |   |      |     |   |   | 53 |

|    |       | 3.3.1  | Component and Abstraction Hi |   |   | 70. |  |   |   |   |      |   |      |     |   |   | 54 |

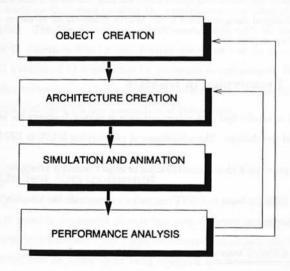

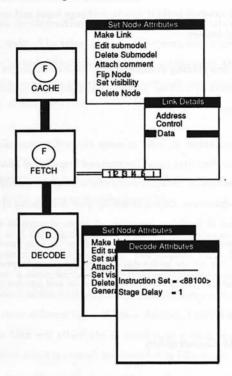

|    |       | 3.3.2  | Object Creation              |   |   |     |  |   |   |   | 7237 | 1 |      |     |   |   | 55 |

| mI  |      | ~    |      |

|-----|------|------|------|

| Tab | e or | Cont | ents |

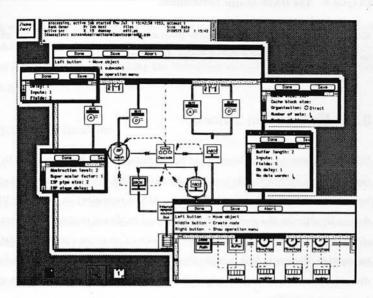

|    |     | 3.3.3   | Architecture Creation                        | 59 |

|----|-----|---------|----------------------------------------------|----|

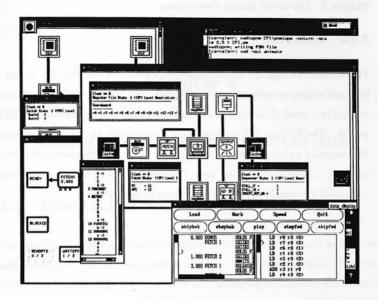

|    |     | 3.3.4   | Code Generation                              | 61 |

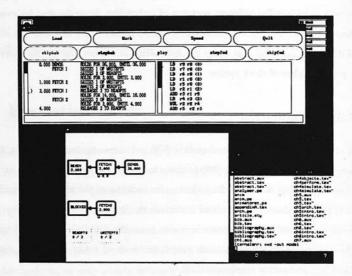

|    | 3.4 | Simul   | ation Phase                                  | 62 |

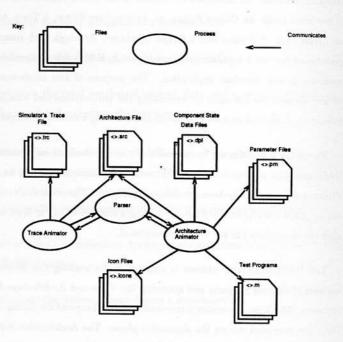

|    |     | 3.4.1   | Input/Output                                 | 62 |

|    |     | 3.4.2   | Operation                                    | 63 |

|    | 3.5 | Evalu   | ation Phase                                  | 64 |

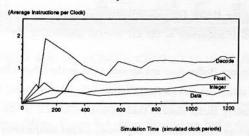

|    |     | 3.5.1   | Statistics and Graphic Visualisation         | 64 |

|    |     | 3.5.2   | Animation                                    | 65 |

|    |     | 3.5.3   | Comment                                      | 68 |

| 4. | Des | sign an | nd Implementation                            | 69 |

|    | 4.1 | Hiera   | rchical Approach                             | 69 |

|    |     | 4.1.1   | Classifying Abstraction Levels               | 69 |

|    |     | 4.1.2   | Implementing the Abstraction Level Hierarchy | 70 |

|    |     | 4.1.3   | Implementing Resources                       | 72 |

|    | 4.2 | Imple   | ementing the Design Environment              | 73 |

|    |     | 4.2.1   | Object Editor                                | 75 |

|    |     | 4.2.2   | Architecture Editor                          | 83 |

|    | 4.3 | Simul   | ation Phase                                  | 88 |

|    |     | 4.3.1   | Simulation Input Parameters                  | 88 |

|    |     | 4.3.2   | Simulation Execution                         | 91 |

|    | 4.4 | Evalua  | ation Phase                                  | 94 |

|    |     | 4.4.1   | Overview                                     | 95 |

|    |     |         |                                              |    |

| m 11 40           |  |  |

|-------------------|--|--|

| Table of Contents |  |  |

|                   |  |  |

iv

|    |     | 4.4.2   | Trace Animator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |     | 4.4.3   | Architecture Animation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |     | 4.4.4   | Graph Displayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | _   |         | Seems by the common of the contract of the con |

| 5. | Res | ults ar | nd Discussion 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

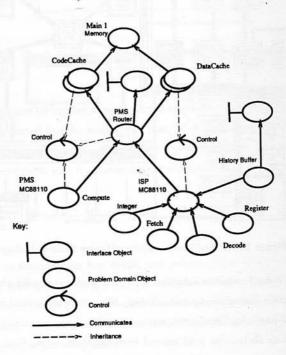

|    | 5.1 | Invest  | igating Internal Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |     | 5.1.1   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |     | 5.1.2   | Flow of Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |     | 5.1.3   | Add a History Buffer to an Existing Architecture 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 5.2 | Invest  | igating External Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    |     | 5.2.1   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |     | 5.2.2   | Flow of Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |     | 5.2.3   | Adding a New Addressing Mode to an Operation 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    | 5.3 | Optin   | nising Hardware / Software Interactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |     | 5.3.1   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |     | 5.3.2   | Flow of Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |     | 5.3.3   | Delayed Branching Code Optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    |     | 5.3.4   | Register Colouring Code Optimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | 5.4 | Invest  | igating Network Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |     | 5.4.1   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    |     | 5.4.2   | Flow of Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    |     | 512     | Simulating Natural Influence on a Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6. | Con  | clusion |                                                   |       | 132   |

|----|------|---------|---------------------------------------------------|-------|-------|

|    | 6.1  | Archite | ecture Requirements                               |       | . 133 |

|    | 6.2  | Object  | Oriented Design                                   |       | . 134 |

|    | 6.3  | Archite | ecture Experiments                                |       | . 135 |

|    | 6.4  | HASE    | Prototype Performance Evaluation                  |       | . 135 |

|    |      | 6.4.1   | Advantages of the HASE Prototype                  |       | . 135 |

|    |      | 6.4.2   | Disadvantages of the HASE Prototype               |       | . 136 |

|    | 6.5  | Future  | Work                                              |       | . 137 |

|    |      | 6.5.1   | Create Architecture Components                    |       | . 138 |

|    |      | 6.5.2   | Develop a Component Object Repository             | • • • | . 139 |

|    |      | 6.5.3   | Develop a Frontend                                |       | . 139 |

|    |      | 6.5.4   | Develop a Distributed Simulation Environment      |       | . 139 |

| A  | Inst | ruction | n Set                                             |       | 141   |

| В. | Ass  | embly   | Test Programs                                     |       | 147   |

|    | B.1  | Convol  | ution Program: Optimised using Delayed Branching  |       | . 147 |

|    | B.2  | Convol  | ution Program: Optimised using Register Colouring |       | . 149 |

|    | Bib  | liograp | hy                                                |       | 151   |

|    |      |         |                                                   |       |       |

# List of Figures

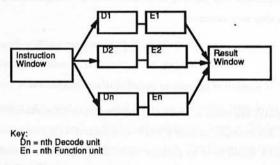

| 1-1 | A Superscalar Architecture               |   |    | ٠  | ٠  |   | ٠ |   | ٠ | * |   | ٠ |   | • | • |   | 18 |

|-----|------------------------------------------|---|----|----|----|---|---|---|---|---|---|---|---|---|---|---|----|

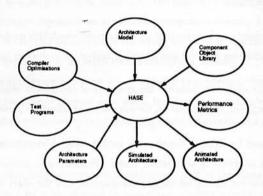

| 1-2 | The Context of HASE                      | ÷ |    |    |    |   |   |   | • |   | • |   |   |   | * |   | 34 |

| 2-1 | Deterministic versus Stochastic System . |   |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 38 |

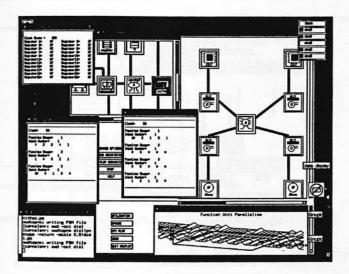

| 3-1 | HASE Environment                         |   |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 51 |

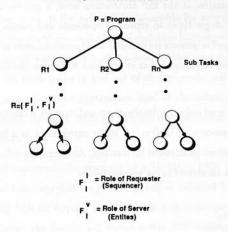

|     | Object Hierarchy                         |   |    |    |    |   |   |   |   |   |   |   |   |   |   |   |    |

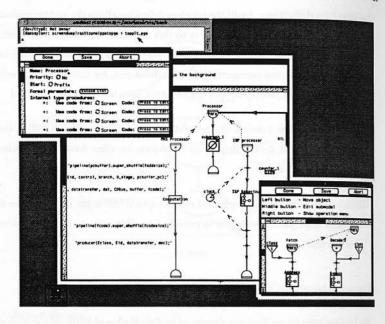

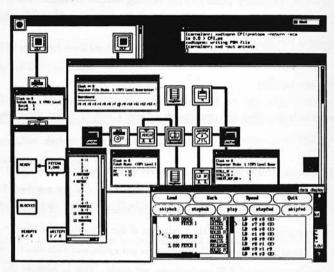

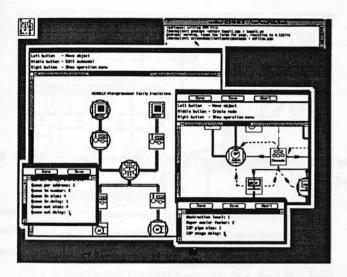

| 3-3 | Process Interaction Tool for Component C | r | ea | ti | or | 1 |   |   |   |   |   |   |   |   |   | • | 58 |

| 3-4 | Link Creation                            |   |    |    |    |   |   | • |   |   |   |   |   |   |   |   | 62 |

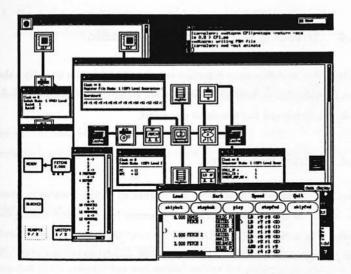

| 3-5 | An Architecture Edit                     |   |    |    |    | • |   |   |   |   | • |   |   |   |   |   | 63 |

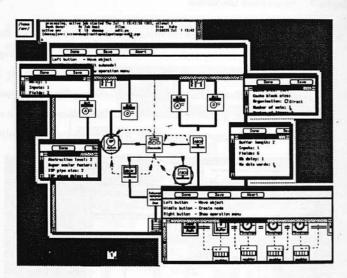

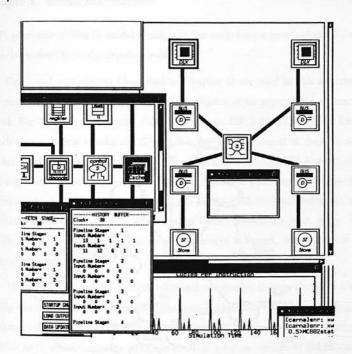

| 3-6 | An Example of the Trace Animator         |   |    |    |    |   |   | • |   |   |   |   |   |   |   |   | 66 |

| 3–7 | Example of an Animated Architecture .    |   |    | •  |    |   |   | • | • |   | • | • |   |   | • |   | 67 |

| 4-1 | Abstraction Level Taxonomy               |   | •  | •  | ÷  |   |   |   | • | • | • | • | • |   |   | • | 71 |

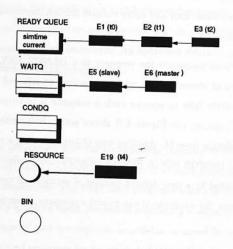

| 4-2 | Discrete Event Modelling on Simula       |   | •  |    | •  | • |   |   | * |   |   | • | • |   |   | • | 74 |

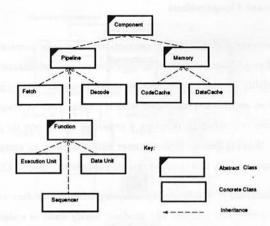

| 4-3 | Use of Object Inheritance                |   | •  |    | ×  | • |   |   |   |   |   |   |   |   | • | • | 77 |

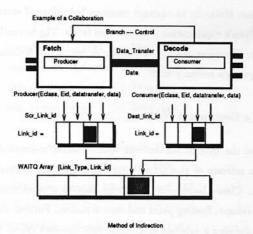

| 4-4 | Inherited Object Communication           |   | •  |    |    | • |   |   |   |   |   |   |   |   |   |   | 79 |

| 4-5 | GDL Submodels Implementing Resources     |   |    |    |    |   |   |   |   |   |   |   |   |   | • |   | 83 |

| 4-6 | Recording Node and Link Connections .    |   |    |    |    |   |   |   |   |   |   |   |   |   |   |   | 87 |

| 4-7  | Animator Structure                                                       |

|------|--------------------------------------------------------------------------|

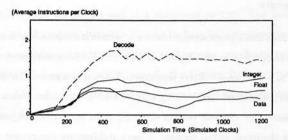

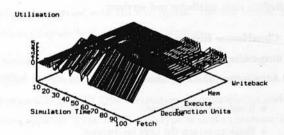

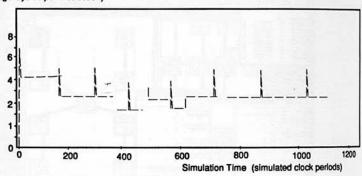

| 5-1  | Graph Displayer: Poor Throughput of Execution Unit 105                   |

| 5-2  | Architecture Animator: Identifying Control Transfer Latency $106$        |

| 5–3  | Object Editor: Creating a History Buffer                                 |

| 5-4  | Architecture Editor: Linking a History Buffer                            |

| 5-5  | Graph Displayer: Improved Function Unit Throughput 109                   |

| 5-6  | Graph Displayer: Flushing History Buffer                                 |

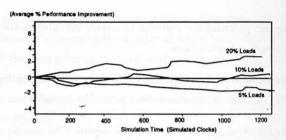

| 5–7  | Graph Displayer: Performance Increase Against Percentage of Load         |

|      | Operations                                                               |

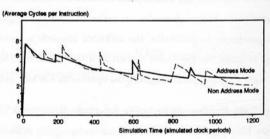

| 5-8  | Graph Displayer: CPI Trace for Non-Addressing and Addressing             |

|      | ADD operation                                                            |

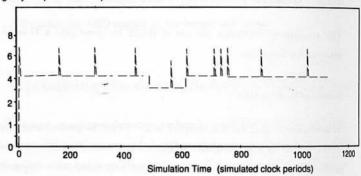

| 5-9  | Graph Displayer: Repeated Utilisation Glitches                           |

| 5-10 | Architecture Animator: Control Transfer Instruction 121                  |

| 5-11 | Graph Displayer: Executing Delayed Branch Instructions 122               |

| 5-12 | Architecture Animator: Viewing Contents of the Register File $$ 123      |

| 5-13 | Architecture Editor: Setting a Component's Abstraction Level $\dots$ 127 |

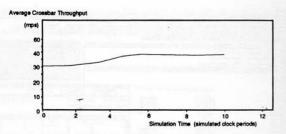

| 5-14 | Graph Displayer: Crossbar Switch Throughput againsy History              |

|      | Buffer Length                                                            |

| 5-15 | Architecture Editor: Display State of History Buffer                     |

| 5-16 | Multi Abstraction Level Simulation: Software Structure 130               |

# List of Tables

| 4-1 | External Parameters: Setting Opcode A  | ь | st | ra | ct | io | n l | Je | ve | l | • | • | • |   | 90  |

|-----|----------------------------------------|---|----|----|----|----|-----|----|----|---|---|---|---|---|-----|

| A-1 | Logical Instructions                   |   |    |    |    |    | •   |    |    |   |   |   |   |   | 142 |

| A-2 | Integer Arithmetic Instructions        |   |    |    |    |    |     |    |    |   |   |   |   |   |     |

| A-3 | Load/Store Instructions                |   |    |    |    |    |     |    |    |   |   |   |   |   | 144 |

| A-4 | Control Transfer Instructions          |   |    |    |    |    | •   |    |    |   |   | • |   | ٠ | 145 |

| A-5 | Floating-Point Arithmetic Instructions |   |    |    |    |    |     |    |    |   |   |   |   |   | 146 |

# Chapter 1

# Architectural Issues and the Design Problem

## 1.1 Introduction

Beizer [69] describes an architect's job as "the design of a hardware/software complex, subject to realistic technical, economic, operational and social constraints such that it 1) works, 2) is optimum and 3) survives." Amdahl [2] on the other hand uses the term "Architecture" "to describe the attributes of a system as seen by the programmer, i.e., the conceptual structure and functional behaviour, as distinct from the organisation of the data flow and controls, the logical design, and the physical implementation."

The earliest architectures were limited in their instruction sets by hardware technology. As soon as hardware technology permitted, architects began looking for ways to support emerging high-level languages. In the 1960s, stack architectures became popular. They were a good match for high-level languages, given the compiler technology available. To support the 1970's trend towards high level languages and structured programming, architects aimed at hiding hardware implementation details from programmers and compiler writers. The results were both the High-Level-Language Computer Architecture (HLLCA) [32] and powerful architectures like the VAX which had a large number of addressing modes, multiple data types, and a highly orthogonal instruction set.

The last decade has seen a renewed emphasis on machine performance and a return to simpler architectures. Sophisticated compiler technology is bridging Gargliardi's "semantic gap" [27], previously narrowed by HLLCAs which ultimately lead to a semantic clash. Rapid progress in hardware technology has given architects an opportunity to design more sophisticated microprocessor architectures. Silicon real estate, for example, can currently support up to 3 million transistors on a single chip. The microprocessor industry is dominated by fast Reduced Instruction Set Computers (RISC), such as Motorola's new family of 88000s and Intel's i860 and i960 [32], that support superscalar architectures and large onchip instruction and data caches. RISC methodology increases the semantic gap, because less frequently used instructions are compiled into a sequence of simple instructions, instead of being executed directly by hardware. Performance gains associated with a fast architecture are lost if the high-level language compilation is not optimised efficiently. Performance of the MC88000, for example, improved from 4 Million Instructions Per Second (MIPS) to 20 MIPS after optimisation of code written in assembler [61]. As microprocessor tradeoffs become more complex, a knowledge of hardware and software interaction is essential to understanding how a compiler can extract performance from an architecture. There are cases in which compiler strategies cease to be optimisations and actually slow down code execution e.g., when a temporary variable used in a global common subexpression elimination cannot be allocated to a register and requires a memory reference.

Research is required to explore how to avoid situations in which performance is degraded by optimisation techniques. To study optimisation methods requires an instrument to probe aspects of an architecture that may be exploited by a compiler. The proposal presented here involves the design and development of an interactive general purpose architecture simulator which supports an experimental platform to investigate hardware and software interaction critical to compiler optimisation techniques. This chapter identifies a number of issues where a visualising simulator could offer significant support to designers.

# 1.2 Defining Computer Architecture

Stone [69] defines the study of Computer Architecture as "the study of the organisation and interconnection of components of computer systems. Computer architects construct computers from basic building blocks such as memories, arithmetic units, and buses". The complexity of computer systems is better understood when the architecture is organised into different levels of abstraction. Analysis of each individual level can provide an orderly understanding of the system's functions. Progression from the most primitive level of the hierarchy to higher levels is accomplished by creating a series of abstractions [6]. By suppressing unnecessary details, each abstraction contains only the information relevant at the higher level. At the lowest level an architecture is described by a set of electronic circuit diagrams, the Circuit Level. These circuits represent an implemention in hardware of the logic circuits at the next level up in the hierarchy, the Logic Level. Above the Logic Level is the RTL (Register Transfer Level at which a floating-point arithmetic unit, for example, is represented as an interconnected set of registers and primitive ALUs. Above this is the ISP Level (Instruction Set Processor Level) at which a processor is described as an interconnected set of functional units (floatingpoint units, caches, etc). At the highest, PMS Level (Processor, Memory, Switch Level), multiprocessor systems can be represented as ensembles of interconnected processors and memories. The current version of HASE is concerned only with the three upper levels of this hierarchy; extension to the lower levels is inherent to the HASE concept but is not currently implemented.

#### 1.2.1 The PMS Level

The PMS Processor Memory Switch level defines components that interact to exchange information. They are distinguished by the kinds of operations they perform:

- Memory M: a component that holds or stores information over time. Its operations are reading and writing instructions and data out of and into memory. The memory may be considered as a number of submemories.

- Link L: transfers information from one component to another. The operation is that of transmitting an instruction or data from the component at one port to the component at the other.

- Control K: a component that evokes the operation of other components in the system. With the exception of the processor P, all other components are essentially passive and require an active agent to set them into episodes of activity.

- Switch S: each switch has associated with it a set of possible links, and its operation consists of setting some of these links and breaking others.

- Processor P: a component capable of interpreting a program in order to execute a sequence of operations. It consists of a set of operations of the classes listed above (M, L, K, S) to obtain instructions from memory and interpret them as operations to be carried out.

## 1.2.2 ISP Level

At the *Instruction Set Processing Level* each instruction specifies its operation (or operations) and the data structures that it is to act upon. Superimposed on this is a control structure that specifies which instruction is to be executed next.

Normally this is done in the order in which the instructions are given, with a *jump* out of sequence specified by a branch instruction.

At the logic level the computer system is composed of parallel devices, with all components active simultaneously. At the ISP level, computers are represented essentially as serial devices, executing one instruction after another (or 2 or 4 depending on whether the machine is superscalar). The ISP is essentially linguistic in nature, the logic level is not. At the ISP level objects can be labelled, decisions made and instructions interpreted. The ISP level does not implement decision or interpretation mechanisms, only their functional characteristics are of importance to ISP simulation.

#### 1.2.3 RT Level

The components of an RT (Register Transfer) level system are registers and functional units which operate on data as it is transferred between registers. The system undergoes discrete operations, whereby the values in various registers are combined according to the appropriate function and are then stored into some other register. The laws of combination may be anything from the simple unmodified transfer (A=B) through logic combinations (A = B OR C) to arithmetic functions (A = B+C). Thus a specification of the behaviour, equivalent to the boolean equations of sequential circuits or the differential equations of electronic circuits, is a set of expressions which give the conditions under which such transfers will be made. Register transfer level systems are usually visualized as having two components: Control and Data. The data part is composed of registers, operators and data paths. The control part provides the sequence of timing signals that evoke activities in the data path. This may be implemented as a hardwired state machine or a microprogrammed sequencer.

# 1.3 Architecture Experiments

This section identifies some architectural issues that are critical to a microprocessor's performance and that are addressed in chapter 6 to demonstrate the design, simulation and performance evaluation phases of HASE. The architectural issues discussed here include memory and cache design, pipeline interlocking tradeoffs and onchip parallelism including the design of multiprocessors. A study of these particular architectural issues can suggest improved methods for extracting performance through more effective hardware/software interaction. One of the main aims of HASE is to focus on visualising these issues in order to gain further insight into achieving performance. The nature of HASE allows rapid modifications to the design of hardware to experiment with a variety of, for example, pipeline configurations, instruction and data fetch buffer sizes, or likewise examine how rescheduling a sequence of instructions can increase the utilisation of parallel function units. HASE can return the exact number of clock cycles it takes to process a given sequence of instructions.

# 1.3.1 Memory Latency Issues

A computer's external cache memory is critical to its throughput, but the cache's performance varies with the operating system and with the applications being run. The use of multi-tasking, and LANs to allow multiple users access to a common data bus, affects the *temporal* and *spatial* locality of data in a cache. A small cache is therefore less likely to hold the instruction set window, and cache misses, for example, are more likely to occur. One of the questions facing architects is what cache size is enough to achieve a reasonable (85 % to 95 %) cache hit rate.

### Cache Associativity

There are three types of cache organisation that must be considered when carrying out realistic computer architecture simulations: direct mapped, n-way associative and fully associative [35]. Although cache design techniques have not reached the point where it is possible to predict cache performance as a function of cache organisation and external machine architecture, simulation experiments of cache environments can provide the foundation for proposed designs of on- and off-chip caches. Each memory location of a direct mapped cache is mapped to one cache location. The disadvantage of this design becomes apparent when a cache miss occurs and the missing address must be loaded into the cache. Because of a one to one correspondence between cache and memory locations, the desired location will automatically replace the cache location to which it is mapped, instead of, for example, the least recently used cache entry [66]. If the next instruction immediately accesses the replaced data, the memory and cache must swap locations for a second time; this 'thrashing' process is defined to be the worst case behaviour of a direct mapped cache. However, the advantage of this placement policy is the fast hit-time associated with the simple address tag relationship between the processor and memory. Hill's simulation experiments [34] suggest that if the cache is large then the fast hit-time advantage outweighs the small probability of worst case behaviour.

The fully associative cache is the extreme opposite to the direct mapped cache. The least recently used replacement policy can be applied because each location can contain any memory address. When a cache miss occurs, the missed instruction or data can be written anywhere in the cache, preferably replacing the instruction or data item that has the lowest probability of being fetched by the processor during the next instruction cycle. Its major disadvantage is that it is complex to design, especially for large cache sizes, because a sophisticated tagging mechanism is required, involving as many comparators as there are cache

locations. On a restricted piece of silicon real estate, the percentage increase in hit-rate does not justify the extra space and design cost. Furthermore, because of its complex circuitry, a fully associative cache has a poor access time compared to direct mapped caches.

An n-way set associative cache is a tradeoff between the direct mapped and fully associative cache. Instead of each memory location being mapped to only one cache location, it is mapped to one of 2<sup>n</sup> locations. Hence the designer may decide to use a 2-way set associative cache, or a 4-way or 8-way, depending on the behaviour of the targeted computer system and its application. Although it does not have the freedom of a fully associative cache, an n-way associative cache can execute a restricted version of a least recently used replacement policy, which compares n cache locations and replaces the location which has the lowest thrashing probability. The set associative cache is organised into sets and blocks; an n-way set associative cache will have n blocks in each set. Simulation experiments [67] have been used to determine the most efficient block size for a given processor type (i.e. RISC or CISC) and application. During the last decade, computers have supported many different types of caches and cache hierarchies. Until now a direct-mapped cache could support virtually all the microprocessors used in PCs. However, the next generation of microprocessors, such as Intel's new Pentium, will contain multiple processor units that can operate independently of each other. With one or more processors making memory calls at clock rates approaching 100MHz, a direct-mapped cache of any practical size simply cannot sustain an acceptable hit rate. As a result, set-associative cache will be used increasingly in future PC designs.

Design analysts use simulation studies to search for a cache placement compromise because the problem cannot be described mathematically. Hardware and software simulators are both used, the software simulator provides the bulk of the simulation results, while the hardware simulator verifies the software simulator's results. Researchers at Digital [33] have derived a few equations for estimating the effectiveness of hierarchical memories by studying how parameter changes affect the overall system's performance [1] [76]. These general relationships do not appear to depend on operating system, compiler, architecture or workload. Digital emphasises however, that these equations, derived empirically from VAX hit-rate data, cannot replace thorough simulation. These rules of thumb are particularly useful to designers who have no time for extensive simulation studies. The equations include relationships such as: miss rate as a function of size, miss rate as a function of associativity, optimal block lengths, and refill bandwidths.

Cache design goals are generally to reduce processor bus activity, in the case of the 68000, for example, to between 70% and 90%, and to increase the CPU's throughput by reducing the average memory access time.

### Cache Consistency Methods

HASE can provide a framework in which to consider cache consistency mechanisms. The hardware/software interaction associated with cache consistency is difficult to visualise, and contemporary high level functional behavioural tools are inadequate at capturing and visualising its mechanisms and providing a means to obtain performance evaluation of a variety of different schemes.

If a multiprocessing system is required, for example, adding another FIFO to the main memory controller FIFOs allows reflective reads without providing separate reflective read circuitry in each cache controller. Reflective reads help to reduce bus traffic in a multiprocessing system whenever a snooping cache supplies data to another processor that has experienced a cache miss. The cache controller for another processor in the system, which has been snooping the bus, observes that it has a valid copy of the requested data and inhibits the first processor's read to the main memory and supplies the requested line. In a reflective read the cache for the second processor updates main memory at the same time that it is supplying the data to the first processor and its cache. The challenge in

reflective reads is that data must be buffered to accommodate the speed of the main memory.

#### Caching on Decoupled Architectures

One of the experiments reported in Chapter 6 attempts to examine the effect of decoupling the address and data bus from the cache and processor. The aim of the experiment is to reduce memory latency and increase processor tolerance to memory latency by decoupling its memory address and data busses. Various current trends in computer architecture involve one or the other technique, and in some cases it has been suggested that both be used [24].

The primary time where the latency of main memory will contribute to execution times on a decoupled architecture is when the Address Processor (AP) and Data Processor (DP) must synchronise; so-called "loss of decoupling" events. Trace simulation has shown that caching can reduce memory latency caused by AP and DP synchronisation. In a multiprocessing environment, cache coherency must be considered, and this introduces further overheads. Detailed simulation studies can identify the successfulness of hardware and software based coherency schemes. The future version of HASE will provide a useful framework in which to carry out similar kinds of experiments.

The PIPE architecture [20] improved memory tolerance by incorporating short queues, of the order of 64 bytes long, between the instruction cache and the instruction unit and between the data cache and the load and store units. SPICE simulation runs indicated that the PIPE approach was 2 to 3 times faster than the MIPS and RISC-II architecture, achieving an estimated 18 MIPS. However, to achieve this performance, the PIPE's data queues must remain filled and this is only possible when data accesses can operate in advance of arithmetic operations.

### 1.3.2 Pipeline Issues