# High resolution electron beam lithography for exploratory silicon device fabrication

**David William Travis**

Thesis submitted for the degree of Doctor of Philosophy

The University of Edinburgh

July 1999

#### **Abstract**

This thesis reports on a study into the fabrication of metal oxide silicon field effect transistors using electron beam lithography to pattern features with dimensions down to 100nm and below. The study is in an area of extensive research, with devices at these dimensions of interest for future generations of integrated circuit manufacture.

The design and construction of a high resolution electron beam system is reported. The system is based on a very high resolution scanning electron microscope equipped with a thermal field emission gun. Chemically amplified resist processes, for electron beam lithography, have been characterised for silicon device fabrication and sub 100nm patterns have been demonstrated.

The development of a fabrication process for silicon devices, with dimensions down to 100nm, is described. The process uses electron beam lithography for all levels of patterning and electrical measurements are reported for a range of the fabricated devices

Devices fabricated in this study are used to explore a novel width modification technique using focused ion beam milling to reduce the current drive of individual transistors. The transistors are characterised before and after modification and electrical measurements are presented which provide the basis for a new chip modification strategy.

# **Declaration**

I declare that this thesis has been completed by myself and that, except where indicated to the contrary, the research documented is entirely my own.

## Acknowledgements

I would like to thank everyone in the EMF who has helped to make this piece of work possible. Particularly my supervisor, Dr. Clive Reeves, for his excellent guidance and assistance, especially for finding time when there were more pressing matters to be dealt with. Thanks also to Alan Gundlach, Tom Stevenson and Alec Ruthven for maintaining the processing equipment and always helping with the constant requests for wafer processing.

Thanks to my parents for all the support and encouragement through the many years of education, none of my achievements would have been possible without it. Also, to my brother, whom I now expect to sit down and read this 'Ph-amphlet' from cover to cover.

To all the people down in the terrapin, past and present, I thank you for putting up with me and helping out with all the problems and questions. Thanks also to Dot for the cheerful and prompt stores service, nothing would have been built without it. I'm also grateful to everyone who has spent their time reading this thesis and providing valuable feedback, especially Professor Anthony Walton.

Finally, a special mention goes to all the members of Edinburgh University Boat Club, especially Wally, Olly, Miles and Alex, for many good times and the odd pint or two!

# Contents

| GLOSSARY                                               |      |

|--------------------------------------------------------|------|

| LIST OF SYMBOLS                                        | vii  |

| LIST OF FIGURES                                        | ix   |

| LIST OF TABLES                                         | xiii |

| 1. INTRODUCTION                                        | 1    |

| 1.1 HIGH RESOLUTION LITHOGRAPHY                        |      |

| 1.1.1 Electron beam lithography                        | 2    |

| 1.2 MOSFET DEVICES                                     | 3    |

| 1.3 PROJECT AIMS                                       | 4    |

| 1.4 THESIS PLAN                                        | 5    |

| 2. MOSFET DEVICE OPERATION                             | 7    |

| 2.1 THE LONG CHANNEL MOSFET                            | 7    |

| 2.1.1 Basic MOSFET operation                           | 8    |

| 2.1.2 I-V characteristics of the MOSFET                | 9    |

| 2.1.3 Threshold Voltage                                |      |

| 2.2 THE SHORT CHANNEL MOSFET                           | 17   |

| 2.2.1 Short-channel device operation                   |      |

| 2.2.2 Device Reliability                               | 25   |

| 2.3 MOSFET DEVICE SCALING                              | 28   |

| 2.3.1 Scaling strategies                               | 28   |

| 2.3.2 High performance and low power scaling scenarios | 30   |

| 2.3.3 Scaling projections                              | 31   |

| 2.4 PRESENT SILICON DEVICE RESEARCH                    | 32   |

| 2.5 SUMMARY                                            |      |

| 3. ELECTRON BEAM LITHOGRAPHY                           | 34   |

| 3.1 ELECTRON BEAM LITHOGRAPHY SYSTEMS                  | 34   |

| 3.1.1.A general system                                 | 34   |

| Contents                                               | iii |

|--------------------------------------------------------|-----|

| 5.4.1 Layer growth/deposition                          |     |

| 5.4.2 Dry Etching                                      |     |

| 5.4.3 End point detection                              |     |

| 5.4.4 Ion implantation                                 |     |

| 5.5 SUMMARY                                            |     |

| 6. FABRICATION PROCEDURE                               | 92  |

| 6.1 Characterisation                                   | 92  |

| 6.1.1 Negative photoresist                             | 93  |

| 6.1.2 Positive Photoresist                             | 102 |

| 6.1.3 Polysilicon processing                           | 104 |

| 6.2 Processing sequence                                | 110 |

| 6.2.1 Active areas                                     | 111 |

| 6.2.2 Channel implant and gate oxide                   |     |

| 6.2.3 Gate formation                                   | 112 |

| 6.2.4 Junction implants and sidewall spacer            | 112 |

| 6.2.5 Contact formation                                | 113 |

| 6.2.6 Metalization                                     |     |

| 6.3 SUMMARY                                            | 114 |

| 7. DEVICE RESULTS                                      | 115 |

| 7.1 Device Structure                                   | 115 |

| 7.2 ELECTRICAL CHARACTERISATION                        | 116 |

| 7.2.1 I-V output curves                                | 117 |

| 7.2.2 Subthreshold curves                              | 119 |

| 7.2.3 Turn-on curves                                   | 121 |

| 7.2.4 Characterisation summary                         | 123 |

| 7.3 FOCUSED ION BEAM WIDTH MODIFICATION OF TRANSISTORS | 123 |

| 7.3.1 Transistor modification strategy                 |     |

| 7.3.2 FIB removal of material (0.5 µm devices)         |     |

| 7.3.3 Electrical results (0.5 µm devices)              | 127 |

| 7.3.4 FIB removal of material (0.25 \mu m device)      | 130 |

| 7.3.5 Electrical results (0.25 µm device)              |     |

| 7.4 SUMMARY                                            |     |

| 8. CONCLUSIONS                                         | 135 |

| 8.1 NANOFABRICATION FACILITY                           | 136 |

| Contents                                         | iv  |

|--------------------------------------------------|-----|

| 8.3 FOCUSED ION BEAM MODIFICATION OF MOS DEVICES |     |

| 8.4 Future work                                  | 139 |

| 8.5 CONCLUSIONS                                  | 140 |

| A. DEVICE FABRICATION RUN SHEET                  | 142 |

| B. PUBLICATIONS                                  | 145 |

| REFERENCES                                       | 150 |

# Glossary

A/D Analogue to Digital

CAR Chemically Amplified Resist

CE Constant Electric field

CVD Chemical Vapour Deposition

CMOS Complementary Metal Oxide Silicon

DAC Digital to Analogue Conversion

DIBL Drain Induced Barrier Lowering

DRAM Dynamic Random Access Memory

E-beam Electron beam

EBES Electron Beam Exposure System

ECR Electron-Cyclotron Resonance

EEBLS Edinburgh Electron Beam Exposure System

EMF Edinburgh Microfabrication Facility

FIB Focused Ion Beam

GIDL Gate Induced Drain Leakage

HMDS Hexamethyldisilizane

I/O Input to Output

LDD Lightly Doped Drain

LOCOS Local Oxidation of Silicon

LPCVD Low Pressure Chemical Vapour Deposition

LSI Large Scale Integration

MOS Metal Oxide Silicon

MOSFET Metal Oxide Silicon Field Effect Transistor

nMOSFET n-channel Metal Oxide Silicon Field Effect Transistor

PECVD Plasma Enhanced Chemical Vapour Deposition

PMMA Poly Methyl Methacrylate

Glossary

Resist Photoresist

RIE Reactive Ion Etching

SCALPEL SCattering with Angular Limitation in Projection Electron-beam

Lithography

SEM Scanning Electron Microscope

SIA Semiconductor Industry Association

UV Ultraviolet

ULSI Ultra Large Scale Integration

VLSI Very Large Scale Integration

## **List Of Symbols**

Cox Gate oxide capacitance

D<sub>n</sub> Electron diffusion constant

D<sub>I</sub> Dose of implanted ions

$\varepsilon_0$  Permittivity in vacuum

$\varepsilon_{Si}$  Semiconductor permittivity

$\varepsilon_{ox}$  Oxide permittivity

f frequency

g<sub>m</sub> Transconductance

g<sub>d</sub> Drain conductance

$\gamma_n$  Contrast of negative resist

$\gamma_p$  Contrast of positive resist

I<sub>D</sub> Drain current

I<sub>PT</sub> Punchthrough current

k Boltzmann constant

1 Characteristic length of the channel

L Channel length

ΔL Pinch off region length

μ<sub>n</sub> Carrier velocity

n<sub>i</sub> intrinsic carrier concentration

N<sub>A</sub> Number of acceptor atoms

N<sub>sub</sub> Substrate doping concentration

q electron charge

Q<sub>tot</sub> Total electronic charge

φ<sub>b</sub> Energy required for electrons to surmount the Si/SiO<sub>2</sub> barrier

φ<sub>B</sub> Semiconductor doping parameter

φ<sub>ms</sub> Metal-semiconductor workfunction difference

φ<sub>surf</sub> Surface potential

$\kappa_{si}$  Semiconductor interface constant

St Subthreshold slope

t<sub>ox</sub> Gate oxide thickness

T Temperature

V<sub>bi</sub> Built in potential between source-substrate and drain-substrate

junctions

V<sub>D</sub> Drain voltage

V<sub>Dsat</sub> Drain voltage in saturation

V<sub>G</sub> Gate voltage

V<sub>PT</sub> Punchthrough voltage

V<sub>S</sub> Source voltage

V<sub>T</sub> Threshold voltage

$\Delta V_T$  Threshold voltage shift

W Active area width

x<sub>i</sub> Implantation depth of impurities

# List of Figures

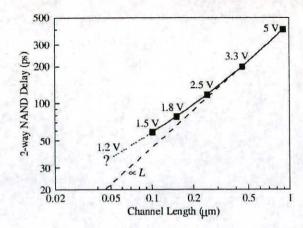

| FIGURE 1.1 GRAPH SHOWING THE PERFORMANCE INCREASE, AS A FUNCTION OF TIME DELAY, IN A                                      |          |

|---------------------------------------------------------------------------------------------------------------------------|----------|

| CMOS CIRCUIT WITH A REDUCTION IN THE MINIMUM FEATURE SIZE[TAUR 1997]                                                      | 4        |

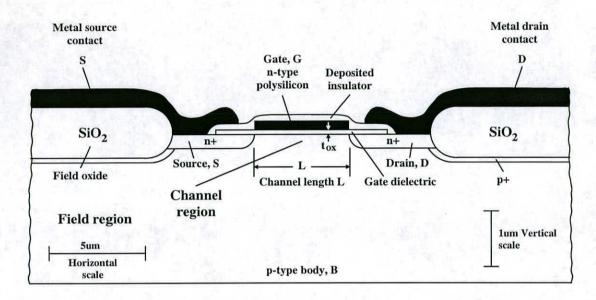

| FIGURE 2.1 LAYOUT OF A LONG CHANNEL MOSFET A) CROSS SECTIONAL VIEW B) GENERAL                                             |          |

| STRUCTURE C) SCHEMATIC DIAGRAM[HODGES 1983]                                                                               | 8        |

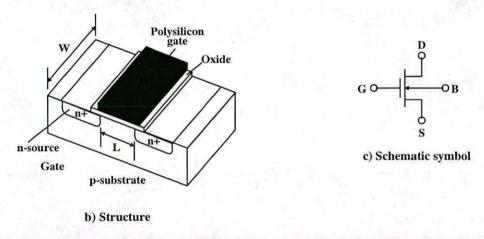

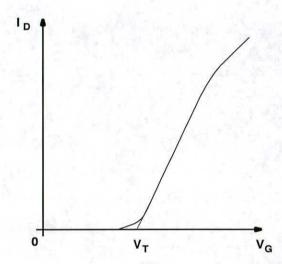

| FIGURE 2.2 TURN ON CHARACTERISTICS OF A N-MOSFET                                                                          | 9        |

| Figure 2.3 The variation of $I_D$ with increasing $V_D$ for a fixed $V_G > V_T$                                           | 0        |

| Figure 2.4 Visualisation of the regions of operation for the MOSFET: a) $V_D \approx 0V$ , b)                             |          |

| Inversion layer narrowing under moderate $\mathrm{V}_{\mathrm{D}}$ biasing, c) pinch-off and d) post pinch                | I-       |

| OFF, $V_D > V_{DSAT}$                                                                                                     | 1        |

| FIGURE 2.5 SUBTHRESHOLD CHARACTERISTICS FOR A LONG CHANNEL DEVICE [TROUTMAN 1974] 1                                       | 4        |

| FIGURE 2.6 GATE INDUCED DRAIN LEAKAGE CURRENT IN A MOSFET                                                                 | 5        |

| Figure 2.7 Calculated threshold voltages of a nMOSFET as a function $N_{\text{sub}}$ and $\tau_{\text{ox}}[\text{Sze M}]$ | ,        |

| 1988]                                                                                                                     | 6        |

| FIGURE 2.8 DIAGRAMS OF INCREASING SHORT CHANNEL BEHAVIOUR IN MOSFETS. A) LONG CHANNEL                                     | ,        |

| BEHAVIOUR, B) WITH CHANNEL MODULATION, AND C) WITH VELOCITY SATURATION[DUVVURY                                            |          |

| 1986]                                                                                                                     | .8       |

| Figure 2.9 Diagram showing the pinched-off region, $\Delta L$ , in the channel of a short channel                         | <i>y</i> |

| LENGTH MOS TRANSISTOR OPERATING IN SATURATION                                                                             | 9        |

| FIGURE 2.10 PUNCHTHROUGH CURRENT PATHS (DOTTED) IN A SURFACE-CHANNEL NMOSFET WITH                                         |          |

| $V_D$ =0.5 and 3.5V. Solid line shows the depletion region edge[Zhu 1988]2                                                | 21       |

| Figure 2.11 Subthreshold curves for, $\log I_D$ versus $V_G$ , for a) Long channel nMOSFET and                            | D        |

| B) SHORT CHANNEL NMOSFET[WOLF 1995]2                                                                                      | 22       |

| FIGURE 2.12 HALO P <sup>+</sup> IMPLANTS AROUND THE JUNCTIONS OF A NMOSFET[CODELLA 1985]                                  |          |

| FIGURE 2.13 THRESHOLD VOLTAGE AS A FUNCTION OF EFFECTIVE CHANNEL LENGTH[LIU 1993]                                         | 24       |

| FIGURE 2.14 REVERSE SHORT CHANNEL EFFECT ON THRESHOLD VOLTAGE[ORLOWSKI 1987]2                                             | 25       |

| FIGURE 2.15 ILLUSTRATION OF HOT-CARRIER EFFECTS INCLUDING HOT-CARRIER GENERATION,                                         |          |

| INJECTION AND TRAPPING[CHEN 1988].                                                                                        | 26       |

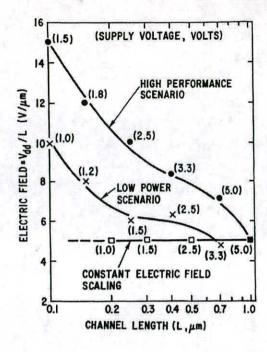

| Figure 2.16 A measure of the electric field, $V_{\text{DD}}\!/L$ , as a function of channel length for                    |          |

| VARIOUS SCALING SCENARIOS[DAVARI 1995]                                                                                    | 31       |

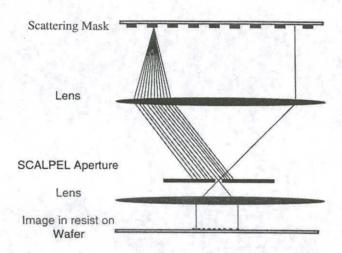

| FIGURE 3.1 SCHEMATIC DIAGRAM OF THE SCALPEL IMAGING STRATEGY[HARRIOTT 1997]                                               | 37       |

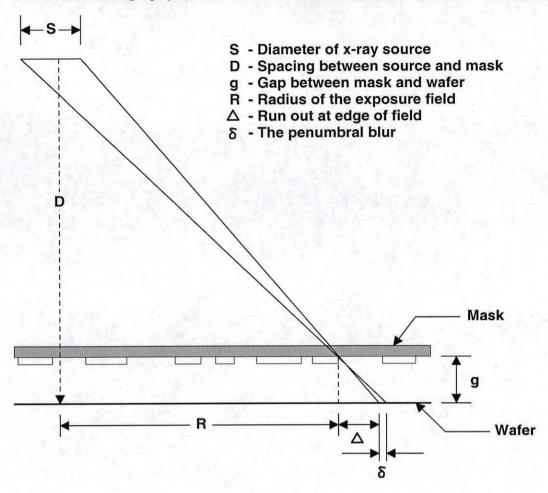

| FIGURE 3.2 Y-DAY DROYIMITY DRINTING[] EPSELTER 1983]                                                                      | 11       |

| List of Figures                                                                                   |      |

|---------------------------------------------------------------------------------------------------|------|

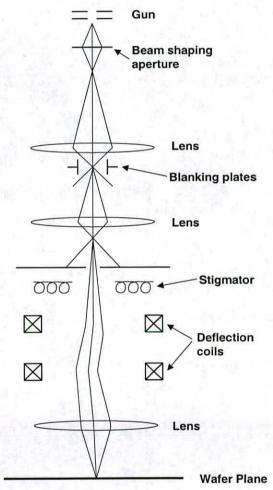

| FIGURE 3.3 PROJECTION OPTICS OF AN ELECTRON COLUMN                                                | 43   |

| FIGURE 3.4 RESPONSE CURVES FOR A) POSITIVE RESIST AND B) NEGATIVE RESIST IN TERMS OF THE          |      |

| DEVELOPED THICKNESS NORMALISED TO THE INITIAL RESIST THICKNESS AS A FUNCTION OF LO                | )G   |

| (DOSE) [MOSS 1987]                                                                                |      |

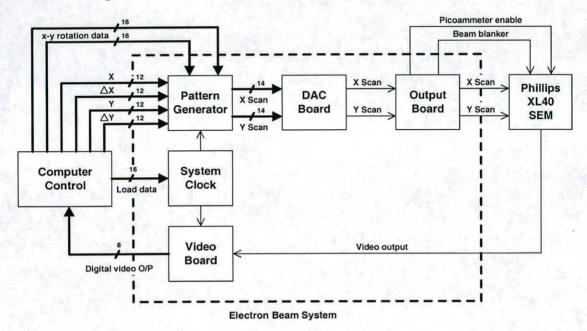

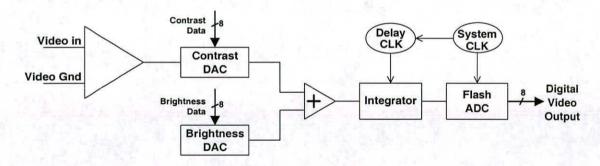

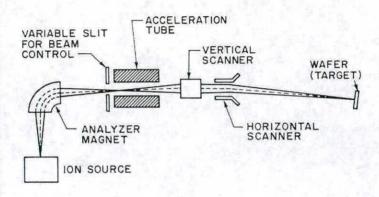

| FIGURE 4.1 GENERAL LAYOUT OF THE EEBLS                                                            |      |

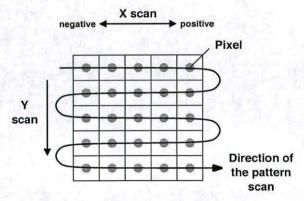

| FIGURE 4.2 VECTOR SCANNING OF A 5x5 PATTERN                                                       | 53   |

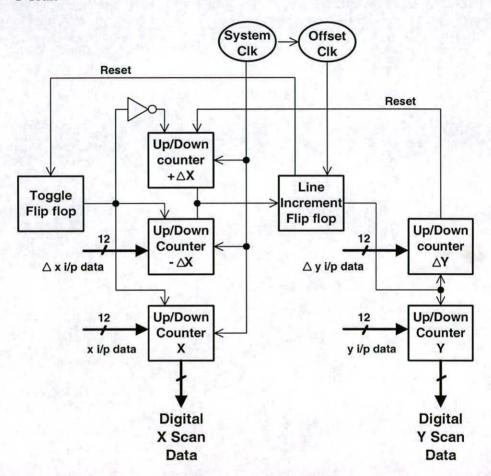

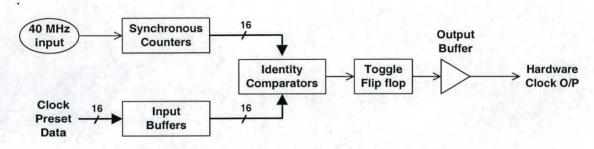

| FIGURE 4.3 SCHEMATIC DIAGRAM OF THE PATTERN GENERATOR CIRCUITRY                                   | 54   |

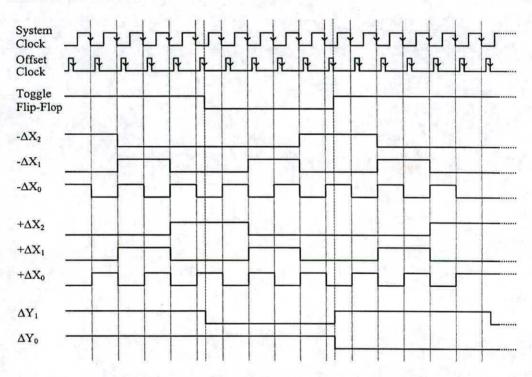

| FIGURE 4.4 TIMING DIAGRAM FOR A 5x3 (X×Y) PATTERN FROM THE PATTERN GENERATOR CIRCUIT              | г 55 |

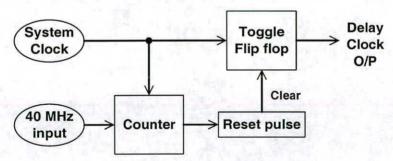

| FIGURE 4.5 SCHEMATIC DIAGRAM OF THE SYSTEM CLOCK                                                  | 57   |

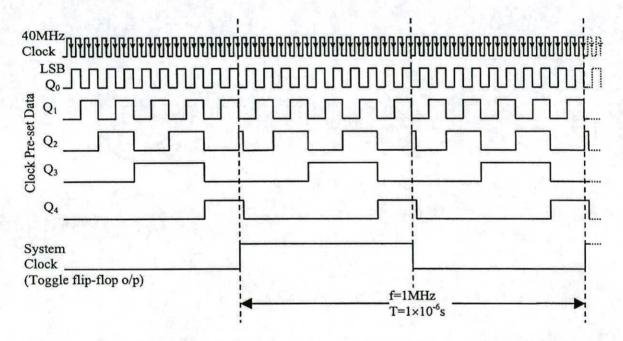

| FIGURE 4.6 TIMING DIAGRAM FOR 1MHZ OPERATION OF THE SYSTEM CLOCK                                  | 57   |

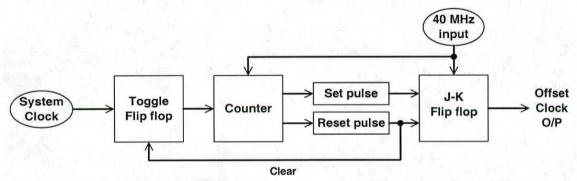

| FIGURE 4.7 SCHEMATIC DIAGRAM OF THE OFFSET CLOCK                                                  | 58   |

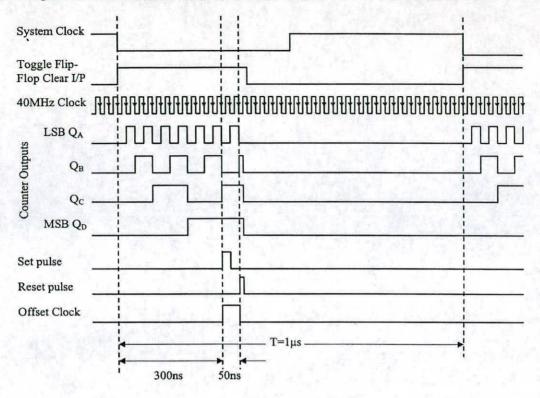

| FIGURE 4.8 TIMING DIAGRAM OF THE OFFSET CLOCK WITH A 1MHZ SYSTEM CLOCK FREQUENCY                  | 59   |

| FIGURE 4.9 BLOCK DIAGRAM OF THE DELAY CLOCK CIRCUITRY                                             | 59   |

| FIGURE 4.10 TIMING DIAGRAM OF THE DELAY CLOCK                                                     | 60   |

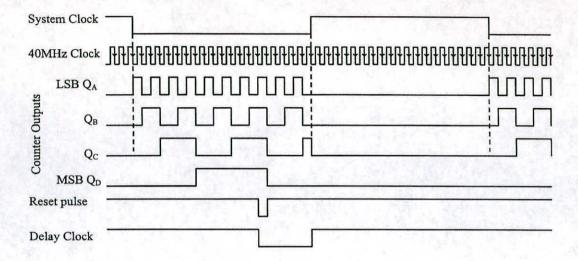

| FIGURE 4.11 LAYOUT OF THE DAC BOARD CIRCUITRY                                                     | 62   |

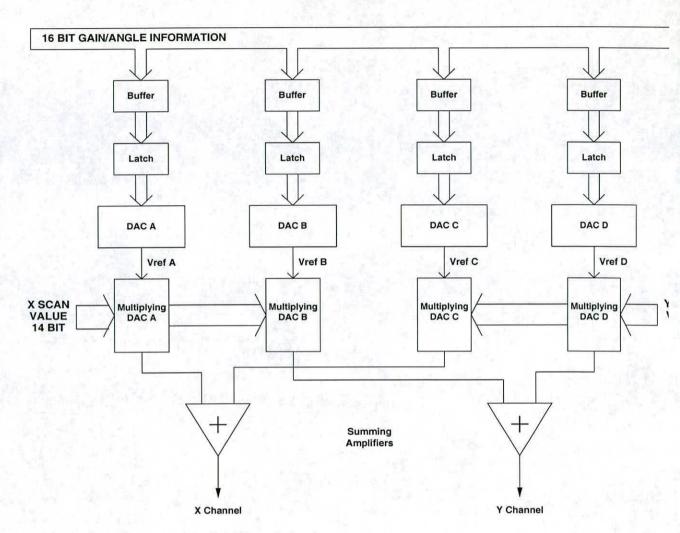

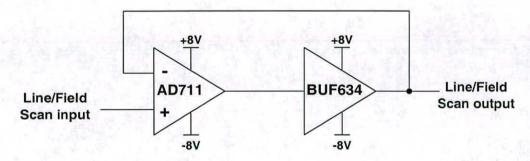

| FIGURE 4.12 VIDEO BOARD SCHEMATIC DIAGRAM                                                         | 63   |

| FIGURE 4.13 OUTPUT BUFFER CIRCUIT                                                                 | 64   |

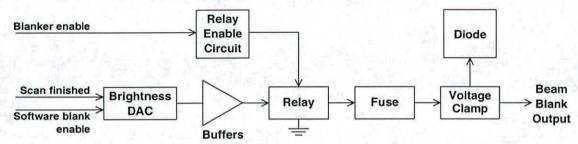

| FIGURE 4.14 SCHEMATIC DIAGRAM OF THE BEAM BLANKER CIRCUITRY                                       | 65   |

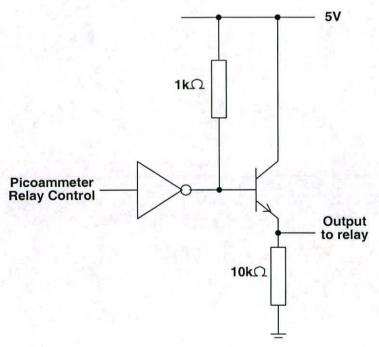

| FIGURE 4.15 PICOAMMETER RELAY CONTROL CIRCUIT                                                     | 66   |

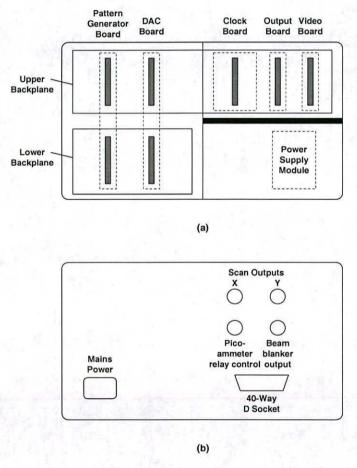

| FIGURE 4.16 ELECTRON BEAM LITHOGRAPHY SYSTEM LAYOUT, (A) BOARD LAYOUT VIEWED FROM                 | THE  |

| FRONT OF THE SYSTEM AND (B) INPUT/OUTPUT CONNECTIONS VIEWED FROM THE BACK OF THE                  | IE   |

| SYSTEM.                                                                                           | 67   |

| FIGURE 4.17 LAYOUT OF THE CONNECTIONS TO THE UPPER AND LOWER DATA BUSES                           | 68   |

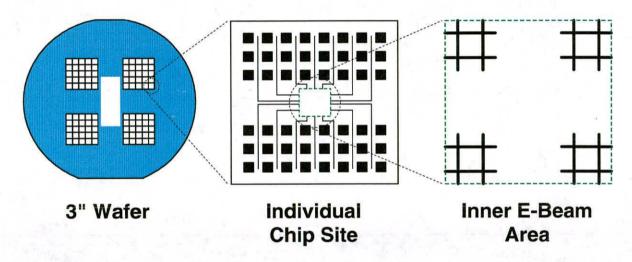

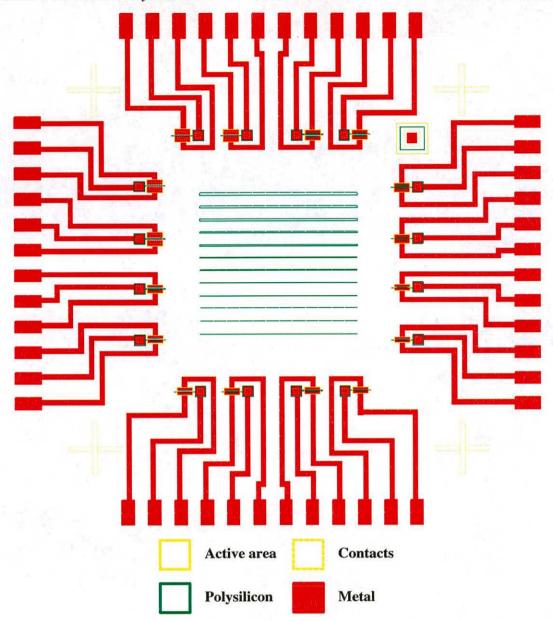

| FIGURE 5.1 LEVELS OF LITHOGRAPHY PATTERNING FOR THE DEVICE EXPERIMENT                             |      |

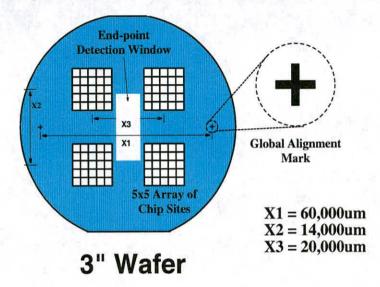

| FIGURE 5.2 PATTERN LAYOUT ON THE 3" WAFER                                                         | 72   |

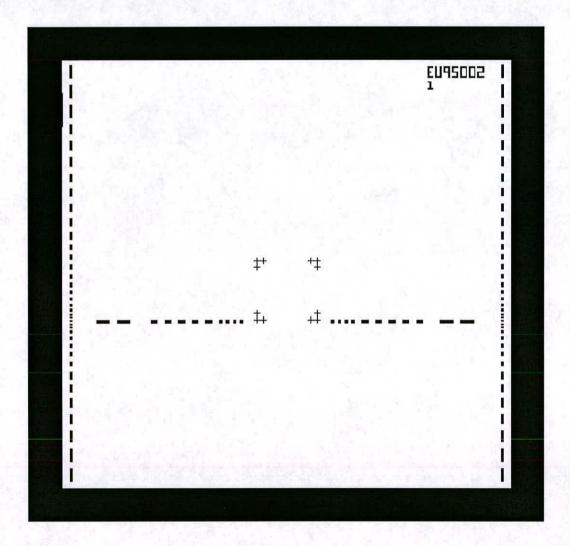

| FIGURE 5.3 OPTICAL MASK FOR THE FRAME LEVEL OF LITHOGRAPHY                                        | 73   |

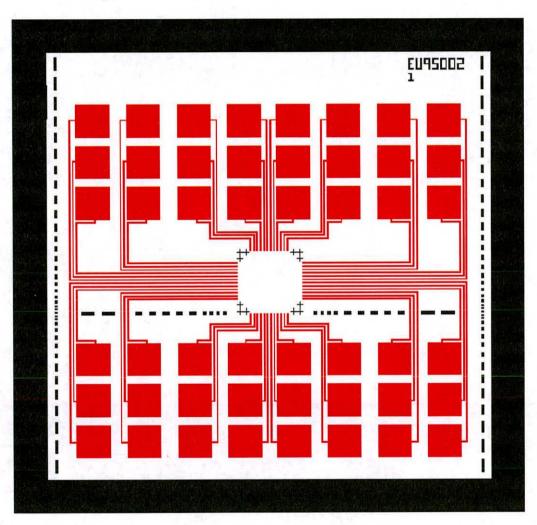

| FIGURE 5.4 OPTICAL MASK FOR THE METAL LEVEL OF LITHOGRAPHY                                        | 74   |

| FIGURE 5.5 ELECTRON BEAM LITHOGRAPHY PATTERNS FOR THE INNER E-BEAM AREA                           | 76   |

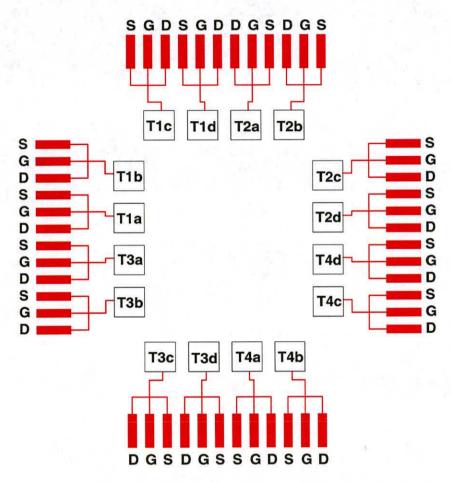

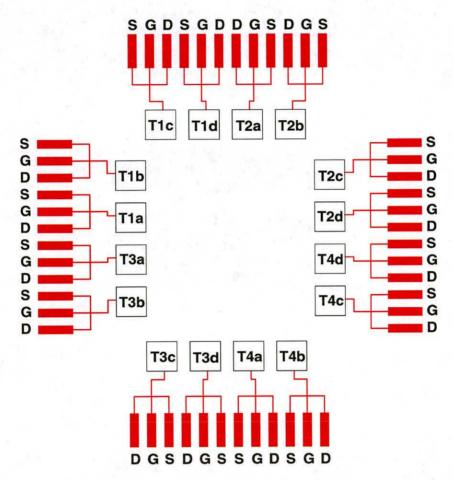

| FIGURE 5.6 LAYOUT OF THE TRANSISTORS IN THE PATTERN DESIGNO                                       | 77   |

| FIGURE 5.7 LAYOUT OF THE TRANSISTORS IN THE PATTERN DESIGN1                                       | 78   |

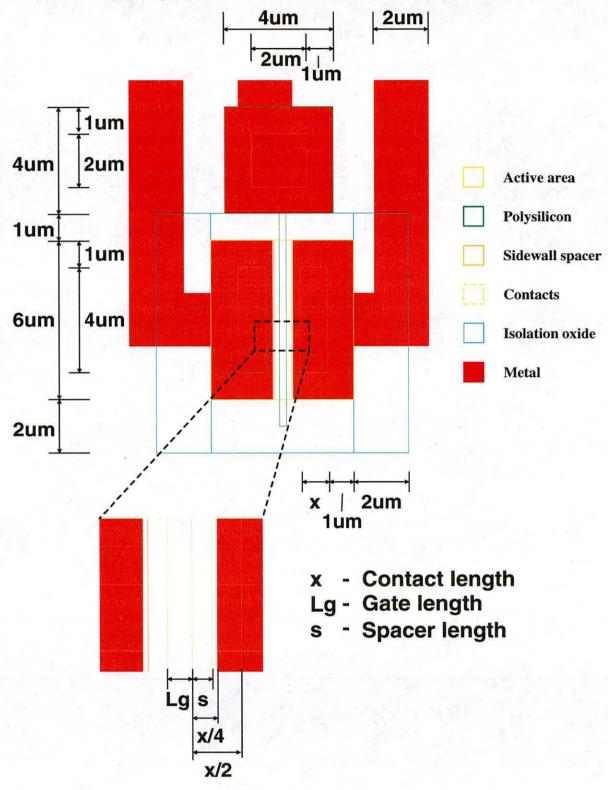

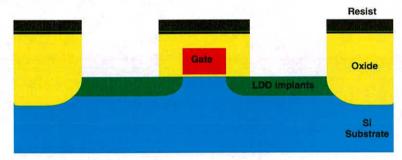

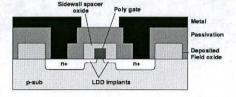

| FIGURE 5.8 MOS DEVICE STRUCTURE                                                                   | 80   |

| FIGURE 5.9 DIAGRAM OF THE SIDEWALL SPACER PROFILE AND ISOLATION OXIDE                             | 81   |

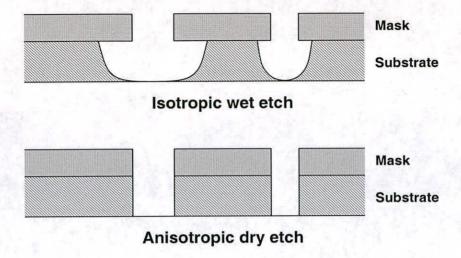

| FIGURE 5.10 DIAGRAM SHOWING THE FEATURES PRODUCED WITH A ISOTROPIC WET ETCH AND                   |      |

| ANISOTROPIC DRY ETCH                                                                              | 86   |

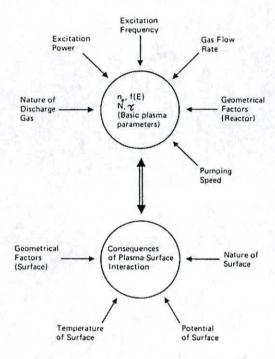

| Figure 5.11 Representation of the parameter problem in plasma etching systems ( $N_{\text{E}}$ is | THE  |

| ELECTRON DENSITY, F(E) IS THE ELECTRON ENERGY DISTRIBUTION FUNCTION, N IS THE GAS                 |      |

| DENSITY AND τ IS THE RESIDENCE TIME[WOLF 1986]                                                    | 87   |

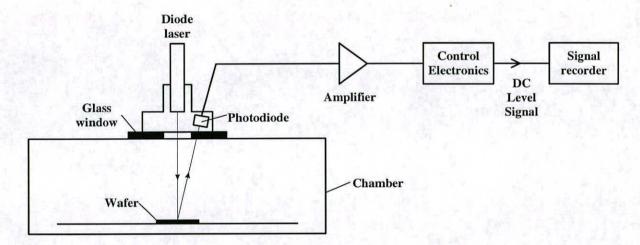

| FIGURE 5.12 SCHEMATIC DIAGRAM OF A LASER INTERFEROMETRY/REFLECTANCE END POINT DETECTOR 89                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 5.13 SCHEMATIC OF AN ION IMPLANTATION SYSTEM[BRODIE 1982]                                                                             |

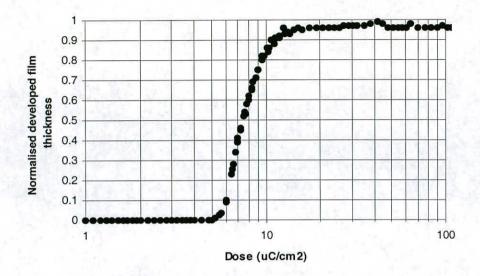

| FIGURE 6.1 SENSITIVITY CURVE FOR AZ PN 114 EXPOSED BY E-BEAM LITHOGRAPHY AND DEVELOPED                                                       |

| IN SHIPLEY MF 319                                                                                                                            |

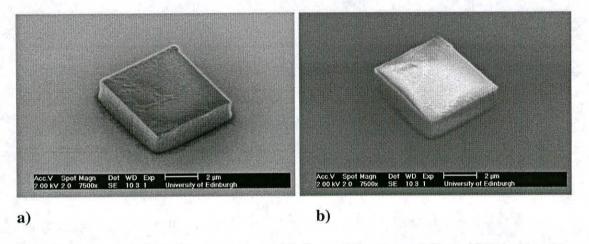

| FIGURE 6.2 4X6µM ACTIVE AREA PATTERN A) BEFORE RESIDUE REMOVAL. B) POST O2 PLASMA ASH95                                                      |

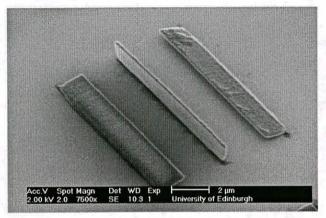

| FIGURE 6.3 COLLAPSED 100NM LINE PATTERNED IN 1µM THICK PHOTORESIST96                                                                         |

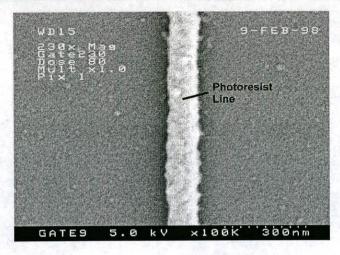

| FIGURE 6.4 PHOTORESIST LINE PATTERNED IN RESIST DILUTED IN THE RATIO 1:5 (RESIST:THINNER) 97                                                 |

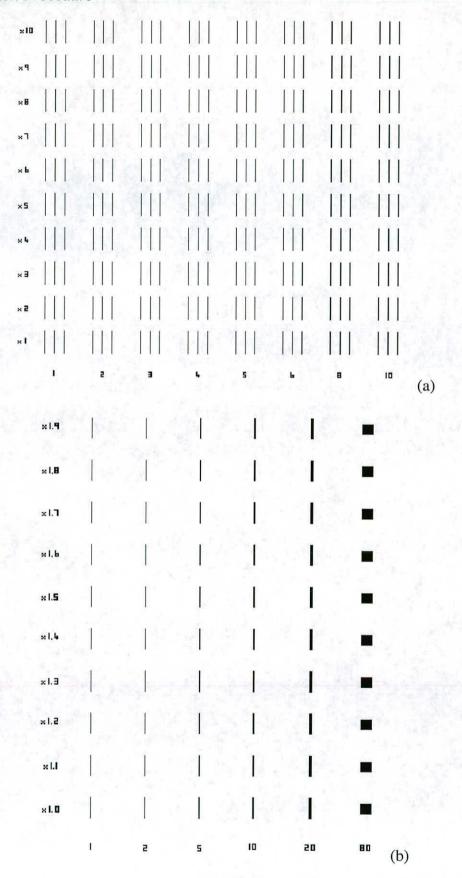

| FIGURE 6.5 TEST PATTERN OF LINES WITH INCREASING WIDTH EXPOSED WITH INCREASING DOSE                                                          |

| BETWEEN 5 AND 50μC/cm-2                                                                                                                      |

| FIGURE 6.6 A) TEST PATTERN 'AZRESA' B)TEST PATTERN 'GATE230'                                                                                 |

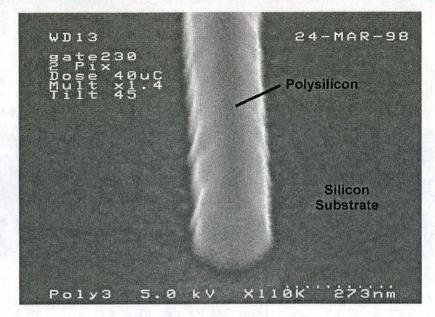

| FIGURE 6.7 CROSS-SECTION OF A NEGATIVE PHOTORESIST LINE OF 1 PIXEL DEFINED WIDTH                                                             |

| FIGURE 6.8 TEST PATTERN CONTACTB, USED FOR THE CALIBRATION OF THE POSITIVE RESIST AZ PF 51410                                                |

| FIGURE 6.9 IMAGE OF A 2 PIXEL WIDE TRENCH, EXPOSED IN POSITIVE AZ PF 514 PHOTORESIST 104                                                     |

| FIGURE 6.10 PATTERNED POLYSILICON LINE AFTER STEP2 ETCH PROCESS USING AZ PN 114 RESIST AS A                                                  |

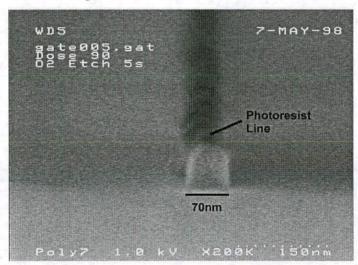

| MASK                                                                                                                                         |

| FIGURE 6.11 PATTERNED POLYSILICON LINE AFTER STEP2 FOLLOWED BY STEP3 ETCH PROCESS 107                                                        |

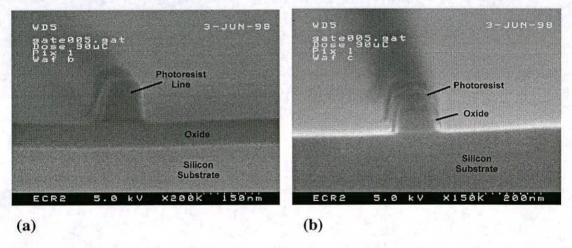

| FIGURE 6.12 IMAGE OF A SINGLE PIXEL LINE A) PRE-OXIDE ETCH AND B) POST-OXIDE ETCH108                                                         |

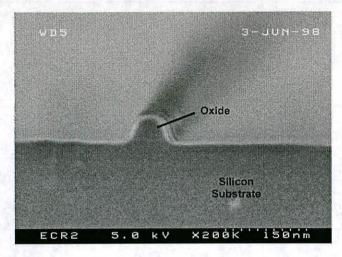

| Figure 6.13 Image of an oxide line after a pattern transfer step from the resist and a $2$                                                   |

| MINUTE O2 PLASMA ASH                                                                                                                         |

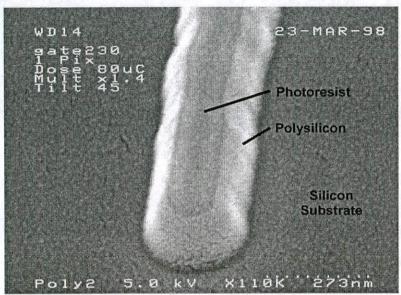

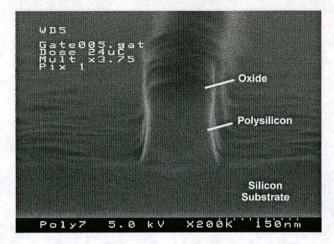

| FIGURE 6.14 CROSS-SECTION OF A POLYSILICON LINE AFTER PATTERN TRANSFER ETCH WITH AN OXIDE                                                    |

| MASK                                                                                                                                         |

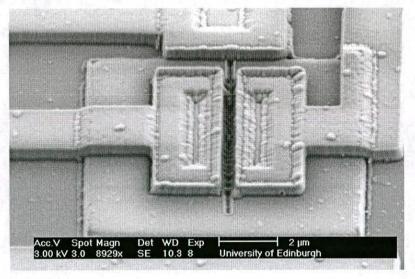

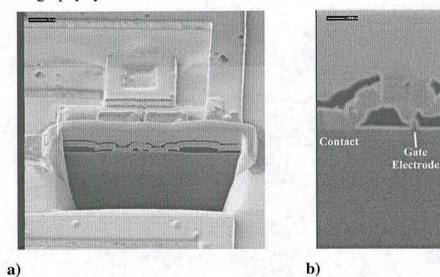

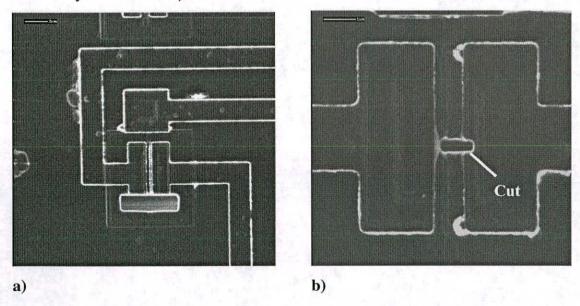

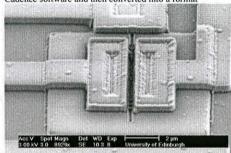

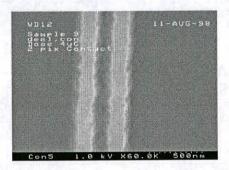

| FIGURE 7.1 SEM IMAGE OF A FABRICATED N-MOSFET                                                                                                |

| FIGURE 7.2 FIB CROSS-SECTIONS OF A NMOSFET DEVICE: A) OVERVIEW OF DEVICE, B) MAGNIFIED                                                       |

| VIEW                                                                                                                                         |

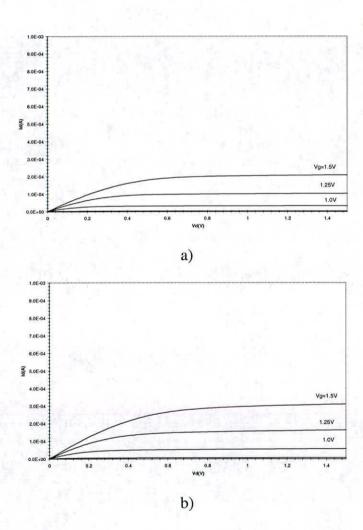

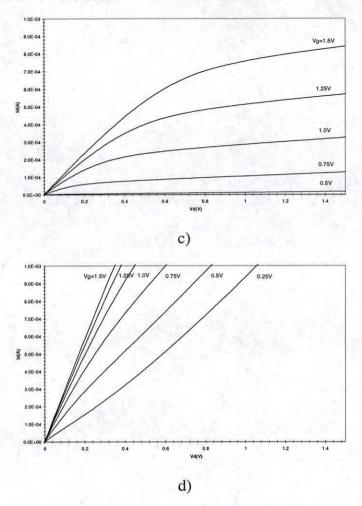

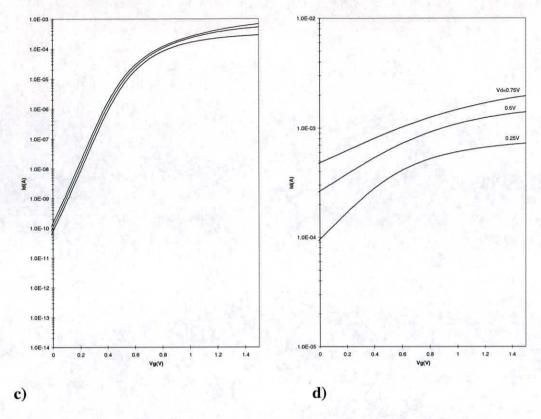

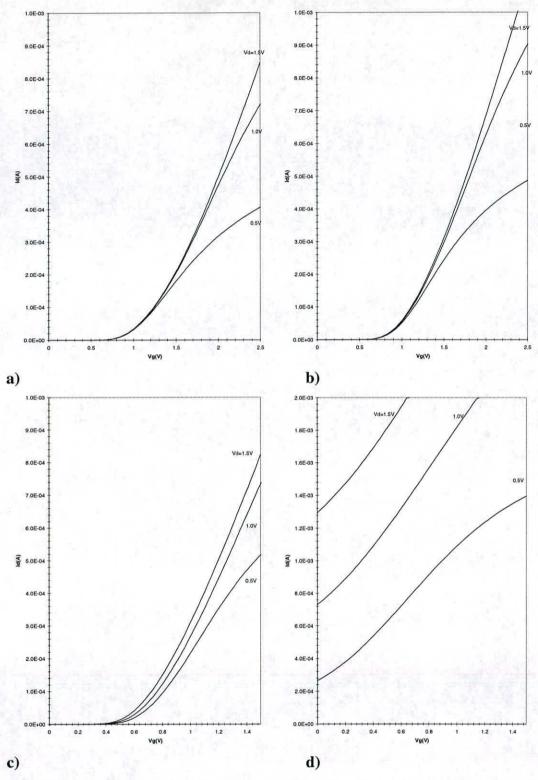

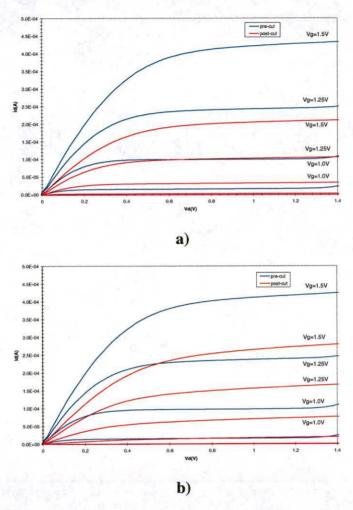

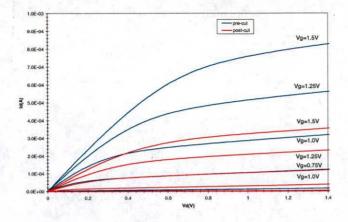

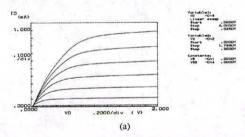

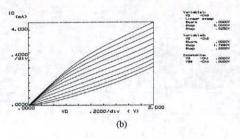

| Figure 7.3 I-V curves for devices with gate lengths: a) $1\mu\text{m}$ , b) $0.5\mu\text{m}$ , c) $0.25\mu\text{m}$ , d) $0.1\mu\text{m}119$ |

| Figure 7.4 Subthreshold curves for devices with gate lengths: a) $1\mu\text{m}$ , b) $0.5\mu\text{m}$ , c) $0.25\mu\text{m}$ ,               |

| D) 0.1µM                                                                                                                                     |

| Figure 7.5 Turn on curves for devices with gate lengths: a) 1μm, b) 0.5μm, c) 0.25μm, d)                                                     |

| 0.1μм                                                                                                                                        |

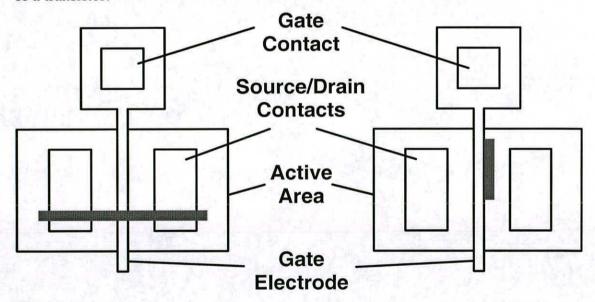

| FIGURE 7.6 MODIFICATION STRATEGY OF TRANSISTORS, A) LENGTHWAYS CUT ACROSS THE GATE, B)                                                       |

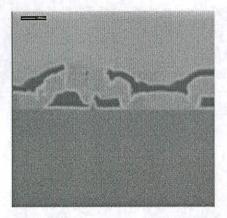

| VERTICAL CUTS UP THE WIDTH OF THE DEVICE                                                                                                     |

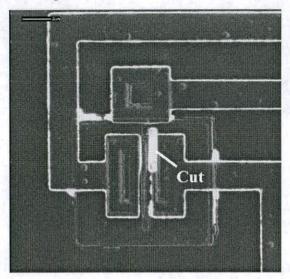

| FIGURE 7.7 LATERAL FIB CUTS ACROSS TRANSISTORS: A) T1 B)T2                                                                                   |

| FIGURE 7.8 ORTHOGONAL FIB CUT IN TRANSISTOR T3                                                                                               |

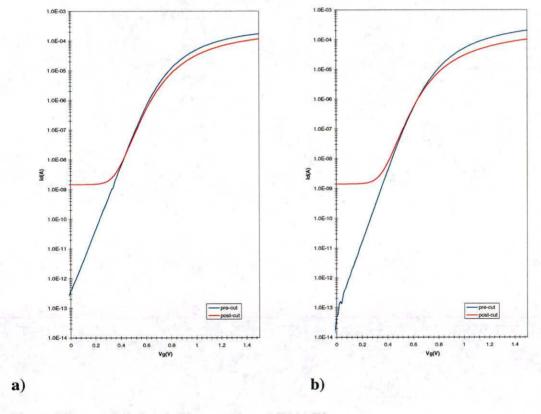

| FIGURE 7.9 SUBTHRESHOLD CURVES FOR: A) T1 B) T2                                                                                              |

| FIGURE 7.10 CURRENT-VOLTAGE CHARACTERISTICS FOR: A) T1 B) T2                                                                                 |

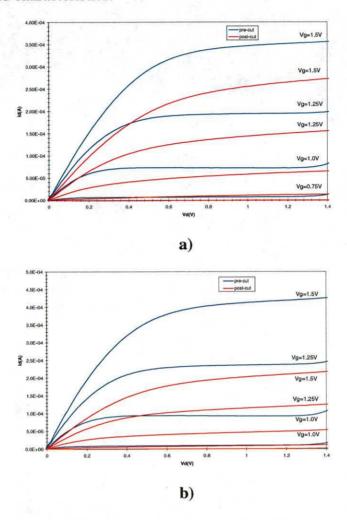

| FIGURE 7.11 SUBTHRESHOLD CHARACTERISTICS FOR DEVICE T3: A) FORWARD CONNECTION, B)                                                            |

| PEVERSE CONNECTION 129                                                                                                                       |

| List of Figures                                                               | X11     |

|-------------------------------------------------------------------------------|---------|

| FIGURE 7.12 CURRENT-VOLTAGE CHARACTERISTICS FOR DEVICE T3: A) FORWARD CONNECT | ION, B) |

| REVERSE CONNECTION                                                            | 130     |

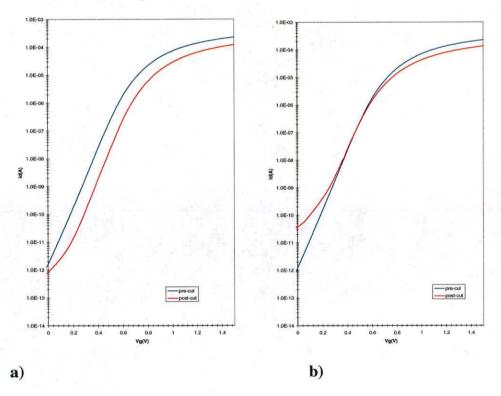

| FIGURE 7.13 LATERAL FIB CUT ACROSS TRANSISTOR T4.                             | 131     |

| FIGURE 7.14 SUBTHRESHOLD CURVES FOR TRANSISTOR T4                             | 132     |

| FIGURE 7.15 CURRENT-VOLTAGE CHARACTERISTICS FOR TRANSISTOR T4                 | 133     |

# **List of Tables**

| TABLE 2.1 RELATIONSHIPS BETWEEN CONSTANT-ELECTRIC FIELD AND GENERALISED SCALING[I | DAVARI |

|-----------------------------------------------------------------------------------|--------|

| 1995]                                                                             | 29     |

| TABLE 2.2 MOSFET TECHNOLOGY PROJECTIONS[SIA, 1997]                                | 32     |

| TABLE 4.1 EDINBURGH ELECTRON BEAM LITHOGRAPHY SYSTEM SPECIFICATION                | 52     |

| TABLE 5-1 KEY OF TRANSISTOR GATE AND CONTACT DIMENSIONS FOR PATTERN DESIGNO       | 77     |

| TABLE 5-2 KEY OF TRANSISTOR GATE AND CONTACT DIMENSIONS FOR PATTERN DESIGN1       | 78     |

| Table 6.1 Exposure conditions for AZ PN 114                                       |        |

| Table 6.2 Exposure conditions for AZ PF 514                                       | 103    |

| TABLE 6.3 PROCESS CONDITIONS FOR THE POLYSILICON ETCH PROCESS                     | 105    |

| TABLE 6.4 ETCH RATES OF THE POLYSILICON ETCH PROCESS                              | 105    |

| TABLE 7.1 DIMENSIONS OF THE CHARACTERISED NMOS TRANSISTORS                        | 117    |

| TABLE 7.2 DIMENSIONS OF TRANSISTORS MODIFIED USING FIB SYSTEM                     | 125    |

1.

### Introduction

The continued expansion of the microelectronics industry, with widespread use of semiconductor technology, has led to the demand for increased performance of silicon devices. Historically metal oxide silicon field effect transistor (MOSFET) device performance has been improved by reducing the device's physical dimensions, which increases the operating speed and packing density[Wong 1999]. This thesis demonstrates the challenges involved in the fabrication of high performance MOSFETs and reducing the dimensions of the devices.

#### 1.1 High Resolution Lithography

Lithography is an important stage in the fabrication of MOSFET devices. It involves defining patterns in a photoresist material, which is used to reproduce structures in material layers after development of the resist. Improvements in the resolution of the lithographic process have been the driving force behind performance increases in metal oxide silicon (MOS) devices, as reducing the device feature sizes increases device performance. High resolution lithography is a label given to the lithography of advanced features, beyond those achievable with current manufacturing lithography systems. Due to this definition, high resolution lithography is an imprecise term that changes as technology improvements enhance the resolution of lithography systems. Other terms that are used to describe the resolution of lithography processes are:

- Sub-micron lithography below 1μm

- Deep sub-micron lithography below 0.35μm

- nano-lithography lithography below 0.1μm

High resolution lithography is presently best defined by nano-lithography.

There are various forms of exposure techniques available for the lithography of MOS devices. The three most widely used methods of exposure are:

- Optical

- X-ray

- Electron beam

Optical lithography uses ultra-violet radiation as the exposing medium and is currently used in the high volume production of integrated circuits. The technology, however, is being pushed to its limits to expose features in the deep sub-micron region of pattern definition. X-ray lithography uses a smaller wavelength of exposure radiation and can hence define features of reduced dimensions from optical lithography. The use of x-rays has inherent problems, described in section 3.2.2, and because of these is not currently favoured for the production of integrated circuits. Electron beam lithography, as described in this work, is primarily used as a high resolution research tool for the lithography of advance devices.

#### 1.1.1 Electron beam lithography

For research applications, electron beam lithography is an important tool for the fabrication of advanced semiconductor devices. High resolution electron beams have enabled patterns to be produced with dimensions smaller than those achieved with the available optical lithography procedures. This is an established trend which continues to the present generation of MOSFET devices. The trend is well demonstrated by the fact that present industrial optical lithography steppers are used to manufacture devices with 0.18µm dimensions yet, electron lithography is used in the research environment at sub-0.1µm [Ochiai 1996, Kawaura 1998]

Electron beam lithography has many advantages as a patterning technique in a research environment. The systems are of relatively low cost, starting at around \$1-5M for a unit, compared to \$5-10M for an optical stepper system. The operating costs are also low with the patterns defined sequentially, in a vector scan system, by a series of co-ordinates, instead of a physical masking method as used with optical and

x-ray techniques. This method of pattern definition also allows for multiple sets of patterns to be defined over the area of the silicon wafer, which is also useful in a research environment as many test structures can be utilised on a single processing wafer, which reduces fabrication costs. As the patterns are defined with an electron beam, the maximum area that can be patterned without moving the stage is smaller than exposed with optical techniques, this can cause complications when imaging larger patterns. Stitching techniques with careful stage positioning can overcome these problems, but can lead to a low throughput of wafers. It is this low throughput of wafers that inhibits electron beam lithography for use in the manufacturing environment.

#### 1.2 MOSFET devices

The MOS transistor is the predominant silicon device currently in use by the microelectronics industry. Since the MOSFET's first reported use in 1960 by D. Kahng and M. M. Atalla [Kahng 1976], the basic structure of the device has remained relatively unchanged. The present generation of devices still use a gate electrode that is situated between two junctions, where a voltage is applied to the gate to produce an inversion layer in the channel below that enables a flow of electrons between the junctions.

Although the MOSFET has retained its basic structure, the devices size has reduced considerably, with minimum feature sizes, in state of the art production devices down to 0.18µm. The performance of the devices has also significantly increased with reduction in feature size, this is shown in the graph of figure 1.1 which highlights the performance increase in a CMOS circuit as the feature size of the device is reduced.

Figure 1.1 Graph showing the performance increase, as a function of time delay, in a CMOS circuit with a reduction in the minimum feature size[Taur 1997]

#### 1.3 Project aims

The motivation behind the work described in this thesis was to address the challenges of developing advanced silicon devices. As described in the previous sections, the challenges in this field are wide ranging with many different techniques available for the fabrication of silicon devices. For this reason the field of study has to be reduced to specific areas. The aims of the study can be stated as:

- Investigate high resolution electron beam lithography for application to the fabrication of silicon MOSFET devices

- Fabrication of advanced MOSFET devices using electron beam lithography

- · Analysis of the operating characteristics of deep sub-micron MOSFETs

To realise these project aims it was necessary to develop the following systems and techniques.

The design and construction of a high resolution electron beam lithography system based around a thermal field emission scanning electron microscope.

• Characterisation of this system for high resolution lithography with chemically amplified photoresists.

The development of techniques to enable the fabrication of MOS transistors at deep submicron and nanoscale dimensions.

The development of these systems enabled the project to focus on the stated aims and investigate the challenges of advanced silicon device fabrication.

#### 1.4 Thesis plan

The operation of MOS transistors is discussed in chapter 2. Initially the characteristics of a long channel device are described and used in later sections of the discussion for more advanced short channel devices. The challenges of fabricating short channel MOSFETs are also described in this section.

Chapter 3 introduces the area of electron beam lithography. The chapter discusses the technology used with this lithography technique and includes the past and present status of electron beam systems within microelectronic processing. Alternative lithography techniques are also discussed to provide a comparison of lithographic fabrication procedures. The electron beam lithography system that was designed and constructed as part of this project is discussed in detail in chapter 4. This section provides an in depth study of the operating systems within the e-beam system and is intended to provide both an insight into such systems and provide a reference manual for any future analysis of the system.

The design and layout of the experiment to fabricate MOS transistors is described in chapter 5. The patterns that were designed for lithographic patterning with the e-beam system are discussed and the dimensions of the designed transistors are displayed. Discussion of processing techniques that were used in the fabrication procedure are included, providing reference for the later discussion on process characterisation.

The characterisation of fabrication techniques are discussed in chapter 6, including characterisation of negative and positive photoresists and polysilicon processing. The fabrication procedure of the MOSFET devices is also described.

Chapter 7 discusses the analysis of the fabricated transistors with advanced focused ion beam techniques. The electrical characteristics of the devices are described and the effect of focused ion beam sectioning of the devices is discussed. Finally, the thesis is concluded in chapter 8.

2.

## **MOSFET Device Operation**

The basic operation of the MOS transistor is discussed in this chapter. The information presented provides an overview of MOSFET operation and relates to the devices that are demonstrated in subsequent chapters of this thesis. The long channel characteristics of device operation are initially presented, highlighting the parameters that affect the output characteristics of the transistors. Short channel devices are then discussed, highlighting the variations in device performance as the channel length of the MOSFET is reduced. The analysis of short channel devices is important as current and future trends of MOS device fabrication involve the reduction of geometries to increase chip packing density and performance. Finally, a discussion on the scaling strategies of MOS transistors is included, with a discussion of the current trends in MOS device research.

#### 2.1 The Long Channel MOSFET

The basic layout of a long channel n-MOSFET is shown in fig 2.1. The substrate is lightly doped, p-type silicon.. The device is controlled by four terminal connections, the gate, drain, source and body. The active region of the device contains the gate, source and drain. The gate is a conducting electrode, usually polysilicon, that is insulated from the channel region of the device by a thin oxide. Either side of the gate lie the source and drain regions, these are n-type impurities implanted into the substrate. The field region bounds the active area with a field oxide and a reasonably heavily doped p-type implant, that is used to isolate the device. The basic structure of a p-MOS transistor is the same as that described for the n-MOS device, except the substrate is n-type with p-type impurities implanted in the source and drain regions. Electrons are the carriers in the n-MOSFET and the device is biased with positive

voltages. A p-MOS device has holes as the carriers and the transistor is biased with negative voltages. The analysis of the MOSFET from herein after will describe the n-MOSFET.

a) Cross section

Figure 2.1 Layout of a long channel MOSFET a) Cross sectional view b) General structure c) Schematic diagram[Hodges 1983]

#### 2.1.1 Basic MOSFET operation

For initial analysis of the MOS-transistors operation, the effect of the gate voltage on the channel will be considered. With no gate voltage applied there is a deficit of n-type carriers (electrons) in the channel region due to the doped p-type substrate, which has an excess of holes. Negligible current can flow in this condition. As  $V_G$  is

increased, the positive bias on the gate produces a transverse electric field across the channel region, this attracts electrons that form an inversion layer. The inversion layer is an induced n-type region which increases the conductance of the channel, causing a current to flow between the positively biased drain and the grounded source regions. The point at which the transistor begins to conduct is referred to as the threshold voltage,  $V_T$ . The magnitude of  $V_G$  determines the conductance of the channel and hence the output current flow,  $I_D$ . A larger gate bias accumulates more electrons and causes an increase in  $I_D$ . The graph displayed in figure 2.2 shows this relationship between the gate voltage and the output current. The relationship between  $I_D$  and  $V_G$  is not linear and the reasons behind this are discussed in the next section.

Figure 2.2 Turn on characteristics of a n-MOSFET

#### 2.1.2 I-V characteristics of the MOSFET

There are three main regions of operation for the MOSFET:

- Subthreshold

- Linear

- Saturation

Subthreshold operation occurs when the gate voltage,  $V_G$ , is less than the threshold voltage ( $V_G < V_T$ ). Under these conditions the transistor is switched off, this is discussed in more detail later in this section. The linear and saturation regions of

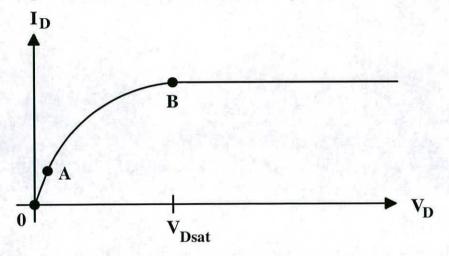

operation occur under strong inversion ( $V_G > V_T$ ) and the current that flows through the channel,  $I_D$ , under these conditions is shown in figure 2.3.

Figure 2.3 The variation of  $I_D$  with increasing  $V_D$  for a fixed  $V_G > V_T$

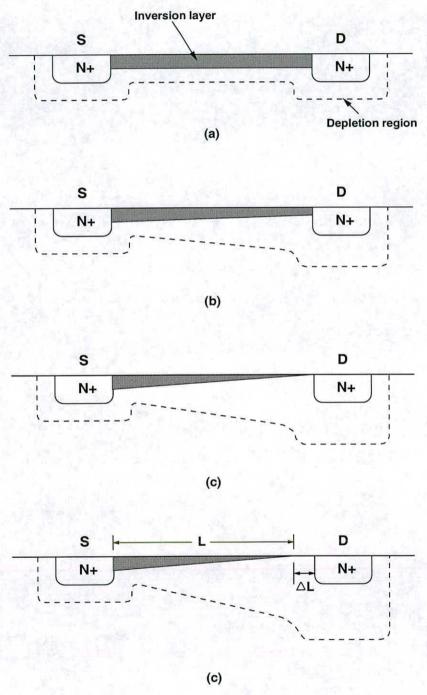

With V<sub>D</sub> at a small positive voltage the inversion region in the channel remains uniform over its length, shown in figure 2.4a. The current, ID, increases linearly with the increase in V<sub>D</sub> as the conductance of the channel remains constant under these conditions. This region of operation is indicated in figure 2.3 between points 0 and A and is referred to as the linear region. As V<sub>D</sub> increases beyond a few tenths of a volt the current flowing in the channel causes a voltage gradient across the length of the channel, which in turn produces a widening of the depletion region under the gate at the drain end of the channel (see figure 2.4b). The mobile charge concentration in the inversion layer of this region decreases with the widening of the depletion region and causes a lowering of the channel conductance. The gradual increase in V<sub>D</sub> therefore results in a smaller increase in ID, which is displayed in the ID-VD characteristics of figure 2.3 between points A and B. If V<sub>D</sub> is sufficiently increased so that V<sub>D</sub>=(V<sub>G</sub>-V<sub>T</sub>) the inversion layer decreases to zero at the edge of the drain. This is shown in figure 2.4c and is referred to as pinch-off. The pinch-off point is represented in figure 2.3 at the point B, and occurs at the saturation voltage, V<sub>Dsat</sub>. Any further increase in V<sub>D</sub> after V<sub>Dsat</sub> causes a further widening of the pinch-off region, ΔL, as shown in figure 2.4d. This widening occurs because the gate voltage is no longer sufficient to establish inversion in the pinch-off region. Most of the voltage increase above V<sub>Dsat</sub> is dropped across the pinched-off region  $\Delta L$  and because of this  $I_D$  does not significantly increase with a rise in  $V_D$  above  $V_{Dsat}$ . This remains valid as long as L>> $\Delta$ L. However, as  $\Delta$ L approaches the value of L, usually only occurring in short channel MOSFETs, the effect on  $I_D$  is increased and is explained in more detail in section 2.2.1.

Figure 2.4 Visualisation of the regions of operation for the MOSFET: a)  $V_D \approx 0V$ , b) Inversion layer narrowing under moderate  $V_D$  biasing, c) pinch-off and d) post pinch-off,  $V_D > V_{Dsat}$

#### Linear and Saturation regions of operation

The linear and saturation characteristics of the MOSFET can be quantified with equations to describe the devices operation. The equations are derived from models such as the Pao-Sah[Poa 1966], charge sheet[Baccarani 1978], bulk-charge[Brews 1978] and square law[Pierret 1983] models all varying in complexity and hence computational time. The simplest model, the square law model demonstrates the parameters that affect the operation of the MOSFET under strong inversion.

The square law model assumes that the electric field is constant across the length of the channel region and is perpendicular to the current flow. In the linear region the equation that models the current flow is given in equation 2.1.

$$I_{D} = \mu_{n} C_{ox} \frac{W}{L} \left[ (V_{G} - V_{T}) V_{D} - \frac{{V_{D}}^{2}}{2} \right]$$

2.1

where:

ID - Drain current

μ<sub>n</sub> - Carrier mobility

Cox - Gate oxide capacitance

W - Width of device active area

L - Channel length

V<sub>G</sub> - Gate voltage

V<sub>T</sub> - Threshold voltage

V<sub>D</sub> - Drain voltage

In the post pinch-off regime, when the device is operating in saturation, an increase in the drain voltage is assumed to cause no increase in the drain current. The current equation is then modelled by equation 2.2.

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ \left( V_G - V_T \right)^2 \right]$$

2.2

The relationships between the output current and the gate and drain voltages, shown in equations 2.3 and 2.4, are expressed as the drain conductance  $g_d$  and the transconductance,  $g_m$ .

$$g_d = \frac{\partial I_D}{\partial V_D}$$

2.3

$$g_m = \frac{\partial I_D}{\partial V_G}$$

2.4

Differentiating equations 2.1 and 2.2 give expressions for g<sub>d</sub> and g<sub>m</sub>.

$$g_d = \mu_n C_{ox} \frac{W}{L} [V_G - V_T - V_D]$$

2.5

$$g_M = \mu_n C_{ox} \frac{W}{L} [V_G - V_T]$$

2.6

#### Subthreshold region of operation

When the MOSFET is biased in weak inversion ( $V_G < V_T$ ) the current which flows in the channel is referred to as the subthreshold current,  $I_{Dst}$ . This current occurs because of the small number of carriers present in the channel. The equations from the square law model that were previously used to describe the behaviour of the MOSFET assume  $I_D$ =0 when  $V_G>V_T$  and are, therefore, not useful in calculating  $I_{Dst}$ . The equation used to approximate the subthreshold current[Wolf 1995], shown in equation 2.7, is derived from the charge sheet model of current flow, which can account for the diffusion current in the MOSFET that is predominant when operated under weak inversion.

$$I_{Dst} = qD_n \frac{W}{L} \frac{kT}{q} \frac{\sqrt{\kappa_{si} \varepsilon_0}}{\sqrt{2qN_A \varphi_{surf}(source)}} \frac{n_i^2}{N_A} \exp\left(\frac{q \varphi_{surf}(source)}{kT}\right)$$

2.7

where:

q - electron charge

$D_{\boldsymbol{n}}$  - electron diffusion constant

k - Boltzmann constant

T - temperature

N<sub>A</sub> - number of acceptor atoms

φ<sub>surf</sub> - surface potential

$\kappa_{si}$  - semiconductor dielectric constant

$\varepsilon_0$  - permeability of free space

n<sub>i</sub> - intrinsic carrier concentration

The component  $\phi_{surf}^{(source)}$  is roughly proportional to  $V_G$  in the subthreshold region, which implies that  $I_{Dst}$  is exponentially dependant on  $V_{Gs}$ . This relationship is shown in figure 2.5 which is a logarithmic plot of the current against gate voltage for a long channel MOSFET.

Figure 2.5 Subthreshold characteristics for a long channel device [Troutman 1974]

The slope of the subthreshold curve is an important factor in the MOSFETs operation. The inverse of this slope is known as the subthreshold swing,  $S_t$ , and indicates how effectively the transistor can be switched off, i.e., the steeper the slope the more effective the switch off.  $S_t$  is calculated using equation 2.8

$$S_t = \ln 10 \left( \frac{d \ln I_D}{dV_G} \right)^{-1}$$

2.8

The value of  $S_t$  is expressed in mV/decade and a typical value for a long channel MOSFET is around 70mV/decade.

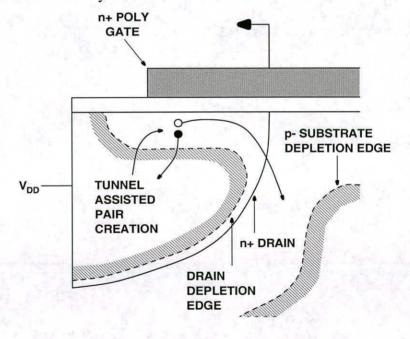

Another form of leakage current that occurs in the MOSFET when it is in the subthreshold region of operation is the gate-induced drain leakage (GIDL). This leakage current flows when the gate is grounded and the drain is at the supply voltage. A depletion region forms around the drain under the gate because of the electric field that occurs across the oxide, shown in figure 2.6. If the electric field becomes large enough an inversion layer attempts to form at the silicon surface of the drain. As the minority carriers move to form the inversion layer they are influenced by the substrate, which is at a lower potential, and drawn sideways to the substrate. This movement of minority carriers constitute the GIDL current.

Figure 2.6 Gate induced drain leakage current in a MOSFET

#### 2.1.3 Threshold Voltage

The threshold voltage has been previously defined as the applied voltage at which the channel of the MOSFET starts to conduct. The equation which defines  $V_T$  in a uniformly doped channel, with  $V_B = 0$ , is given by [Wolf 1995]:

$$V_T = \varphi_{ms} - \frac{Q_{tot}}{C_{ox}} + \frac{2\sqrt{\kappa_{si}\varepsilon_0 q N_{sub}\varphi_B}}{C_{ox}} + 2\varphi_B$$

2.9

where:

$\phi_{ms}$  - metal-semiconductor workfunction difference

Qtot - total electronic charge

$N_{\text{sub}}$  - substrate doping concentration

φ<sub>B</sub> - semiconductor doping parameter

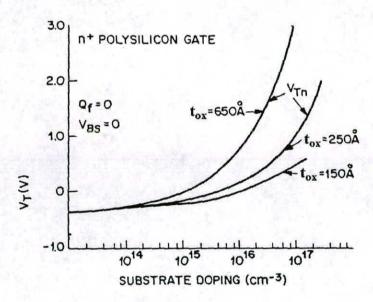

The curves in figure 2.7 show the calculated values of  $V_T$  as a function of gate oxide thickness,  $t_{ox}$ . The graph highlights two variables of gate oxide thickness and substrate doping, which affect the value of  $V_T$ . For MOSFETs the gate oxide thickness is designed to maximise the output current,  $I_D$ , with the substrate doping of the channel region used to adjust the value of the threshold voltage.

Figure 2.7 Calculated threshold voltages of a nMOSFET as a function  $N_{sub}$  and  $t_{ox}[Sze\ M,$  1988]

The substrate doping is normally performed by implanting a thin layer of impurity atoms in the channel region. This causes the substrate to become non-uniformly doped. The equation for the threshold voltage has to take this non-uniformity into account and the modifications are shown in equation 2.10.

$$V_T = \varphi_{ms} - \frac{Q_{tot}}{C_{ox}} + 2\varphi_B + \frac{qD_I}{C_{ox}} + \frac{\sqrt{2\kappa_{si}\varepsilon_0 qN_A \varphi_B}}{C_{ox}} \left(\frac{2\varphi_B + qD_I x_i}{2\kappa_{si}\varepsilon_0}\right)^{\frac{1}{2}}$$

2.10

where:

D<sub>I</sub> - dose of implanted ions

x<sub>i</sub> - implantation depth of impurities

#### 2.2 The Short Channel MOSFET

The trend of MOSFET design is the reduction in size of the patterned features. Each progressive device generation reduces the minimum feature size to increase the density of transistors on the silicon and increase the drive current, I<sub>Dsat</sub>, and hence the operating speed. The main feature that is scaled to improve device performance is the gate length, which increases the current drive of the transistor. The gate oxide thickness is also reduced and the source/drain regions are decreased in depth. All of these parameters impact the operating characteristics of the devices and the models described in the previous section, for long channel transistors, do not accurately define the characteristics of the MOSFET. This phenomena is referred to as "short-channel effects". The short channel effects describe three main areas of the MOSFETs characteristics that are affected by the feature size reduction:

- I<sub>D</sub> is not as predicted by the long-channel models

- · Subthreshold currents are increased

- Device reliability is reduced

The subsequent sections will discuss these effects and describe the steps that can be used to minimise their influence on the operation of short-channel MOSFETs.

#### 2.2.1 Short-channel device operation

#### **Current-Voltage Characteristics**

As the gate lengths of MOS transistors are reduced the prominence of short channel effects on the current-voltage characteristics increases. These occur as the electric fields from the junction regions and gate electrode have a greater effect on the relatively smaller channel region. The characteristics of the I-V curves of MOS transistors change with the onset of short-channel effects and begin to deviate from the long channel curves, that are shown in figure 2.8a.

Figure 2.8 Diagrams of increasing short channel behaviour in MOSFETs. a) Long channel behaviour, b) with channel modulation, and c) with velocity saturation[Duvvury 1986]

When operated in saturation  $(V_G>V_T)$  the short channel transistor exhibits a constant rise in drain current with an increasing value of  $V_D$ , shown in figure 2.8b. This is due to the effect of the channel length modulation factor,  $\lambda$ . This occurs when the MOSFET is operating in saturation because the pinch-off length,  $\Delta L$ , in short channel

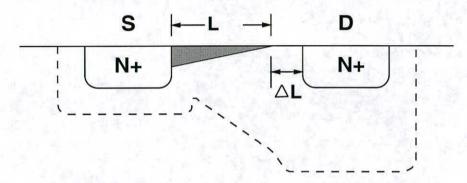

devices (see figure 2.9) approaches the same size as the remaining effective channel length,  $L_{eff}$ . With most of the excess voltage above  $V_{Dsat}$  dropped across  $\Delta L$ , the voltage across  $L_{eff}$  remains constant. However, with increasing  $V_D$ , and hence a lengthening value of  $\Delta L$ , the size of the channel progressively gets shorter. This increases the current drive of the transistor and hence causes a rise in the output current. In longer channel length transistors this effect is not as apparent because the size of  $\Delta L$  is only a small fraction of the size of  $L_{eff}$ , thus having negligible impact on the gain of the transistor.

Figure 2.9 Diagram showing the pinched-off region,  $\Delta L$ , in the channel of a short channel length MOS transistor operating in saturation.

Velocity saturation effects also influence the I-V characteristics of short channel MOSFETs. The carriers in the channel reach a saturation velocity when the lateral electric field reaches a critical value,  $\varepsilon_{sat}$ , and this occurs with the formation of the pinched-off region in the channel. The depletion region, from the drain, extends into the channel and in short-channel devices  $\varepsilon_{sat}$  occurs closer to the source. This has the effect of the current saturation point,  $V_{Dsat}$ , occurring at approximately the same value of  $V_D$ , independent of the effect of the gate voltage. This effect is shown in figure 2.8c.

The I-V characteristics are also affected by the reduction in the mobility of the carriers in the inversion layer of short-channel devices. The mobility degradation factor,  $\theta$ , is the parameter that describes the mobility reduction of the carriers and is an empirically defined value. The mobility is reduced because of scattering of the surface charge carriers at the Si/SiO<sub>2</sub> interface that are acted upon with a transverse

electric field from the gate electrode. While this effect is present in long channel transistors it is more pronounced in short-channel devices, as the electric fields are higher because of the reduced dimensions of the channel region. The effect causes a reduction of the gain of the device, hence reduced current drive, in both the linear and saturation regions of operation.

#### Subthreshold characteristics

When the MOSFET is switched off, with the gate voltage below threshold, there are three components that contribute to the leakage current; punchthrough,  $I_{PT}$ , which is a sub-surface current flowing from the drain to the source, a surface diffusion current and the gate-induced drain leakage (GIDL) current,  $I_{GIDL}$ , which was discussed in section 2.1.2.

Punchthrough is an effect that occurs when the source and drain depletion regions merge together, causing a larger drain current than is predicted with the long-channel MOSFET equations. This is because the gate, that controlled  $I_D$  with the applied electric field, can no longer influences the current flow and  $I_D$  increases exponentially with applied  $V_D$ . Punchthrough can place a limit on the maximum drain voltage that can be applied to the MOSFET and hence limit the output current,  $I_D$ . The voltage at which punchthrough occurs is related to the doping profile of the channel and the effect of the gate, but a simple one-dimensional approximation of the punchthrough voltage,  $V_{PT}$ , is shown in equation 2.11[El-Kareh et al, 1986]. From this it can be determined that  $V_{PT}$  is proportional to the level of substrate doping and the square of the channel length.

$$V_{PT} = L^2 N_a \frac{q}{2\varepsilon_0 \varepsilon_{Si}}$$

2.11

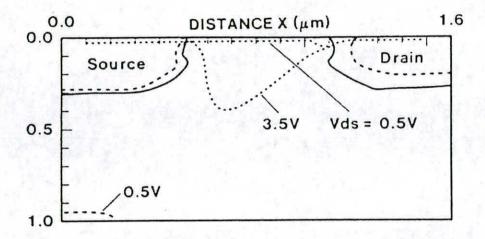

The doping in the channel region, from the  $V_T$  adjustment implant, affects the magnitude of the junction depletion regions. The increased doping near the surface of the channel reduces the depletion widths at the surface, compared to lower down in the bulk, where the regions converge to produce a sub-surface current flow[Zhu 1988]. Figure 2.10 shows the predominant path of  $I_{DST}$  change from a surface current

at low  $V_D$ , to a subsurface current at high  $V_D$ . From equation 2.11 it is evident that  $V_{PT}$  can be raised by increasing the doping level.

Figure 2.10 Punchthrough current paths (dotted) in a surface-channel nMOSFET with  $V_D$ =0.5 and 3.5V. Solid line shows the depletion region edge[Zhu 1988].

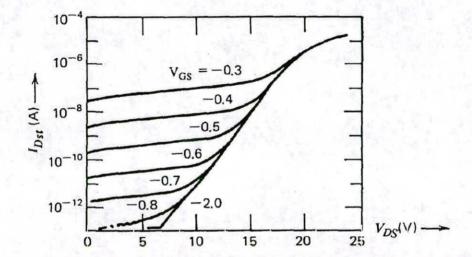

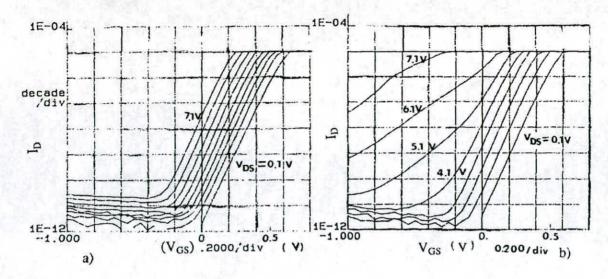

The onset of punchthrough also affects the value of the subthreshold swing.  $S_t$  increases in value with the onset of punchthrough. This is shown in figure 2.11. The curves of the long channel MOSFET in figure 2.11a do not exhibit punchthrough, as they show no change in  $S_t$  as  $V_D$  is increased. The curves of the short channel MOSFET in figure 2.11b, however, gradually begin to flatten out with increasing values of drain current, thus increasing the value of  $S_t$ . The increase in  $S_t$  occurs because there is an increase in the drain current at low gate voltages, due to the influence of the junction depletion regions merging across the shorter channel length with the increasing drain voltage.

Figure 2.11 Subthreshold curves for,  $\log I_D$  versus  $V_G$ , for a) Long channel nMOSFET and b) Short channel nMOSFET[Wolf 1995]

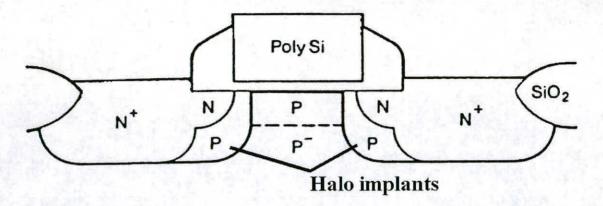

Punchthrough can be reduced by increasing the doping in the substrate region where the subsurface current flows. The increased doping decreases the size of the junction depletion regions, in the same way as the channel doping implant. The doping can be increased with an implantation of atoms, p-type for the nMOSFET, at an energy which locates the ion impurities in the substrate below those for the  $V_T$  adjustment implant. This implant is known as a punchthrough stopper implant. A development of this technique is to locally implant the impurities in the regions around the junctions, shown in figure 2.12, by tilting the sample as the implant is performed. This technique is referred to as halo implantation[Jung 1996]. The heavily doped inside sidewalls of the junctions suppress the extension of the depletion regions with increasing  $V_D$ , thus reducing the punchthrough effect.

Figure 2.12 Halo p<sup>+</sup> implants around the junctions of a nMOSFET[Codella 1985]

At low drain biases in short channel transistors a surface current can initiate the punchthrough effect[Fu 1997]. The effect dominates the subthreshold current until the drain voltage increases enough to produce bulk punchthrough, as described in the previous paragraph. The current path of surface current is shown in figure 2.10 for the low drain voltage of 0.5V.

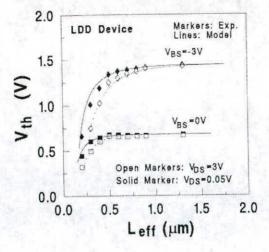

## Threshold voltage

The reduction in the channel length of MOSFETs affects the value of the threshold voltage, V<sub>T</sub>. In very short channel devices the threshold voltage reduces dramatically as the device's effective gate length is reduced, as shown in figure 2.13. This occurs because of the effects of the lateral electric fields from the source/drain junction regions. As the channel length, L, approaches the dimensions of the source/drain junction depletion widths, a larger part of the channel-depletion region begins to consist of the space charge in the junction depletion regions. Under these conditions less gate charge is required to invert the channel of the MOS transistor, causing the appearance of a lowering of V<sub>T</sub>. This effect can be suppressed with an increase in the doping of the channel region, that reduces the lateral electric fields in the channel by curbing the junction depletion regions.

Figure 2.13 Threshold voltage as a function of effective channel length[Liu 1993]

Modelling the threshold voltage in short-channel devices therefore requires the lateral electric fields and their effect on the channel region to be considered, unlike the longer channel equation given with equation 2.10. The method of analysis to characterise the change in  $V_T$  is to calculate the shift in the threshold voltage,  $\Delta V_{Tsc}$ , from the one-dimensional value calculated using the model given in equation 2.10. Liu et-al determined a quasi-two-dimensional model to determine  $\Delta V_{Tsc}$ , which is given by [Liu 1993]

$$\Delta V_{Tsc} = 3(V_{bi} - 2\varphi_B) + V_D e^{-L/l} + 2\sqrt{(V_{bi} - 2\varphi_B)(V_{bi} - 2\varphi_B + V_D)} e^{-L/2l}$$

2.12

where:

$$l = \sqrt{\frac{\varepsilon_{si} t_{ox} d_{\text{max}}}{\varepsilon_{ox} \eta}}$$

2.13

V<sub>bi</sub> - built in potential between source-substrate and drain-substrate junctions

1 - characteristic length

$\varepsilon_{ox}$  Oxide permittivity

η Fitting parameter

The overall effect of a reduction in the channel length of MOS transistors shows a decrease in the value of the threshold voltage, as described by the two-dimensional analysis of equation 2.12. Observation of fabricated short-channel devices, however,

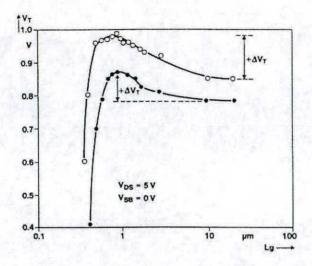

shows an anomalous initial increase in  $V_T$  with a reduction in channel length, shown in figure 2.14 as a shift  $\Delta V_T$ . This increase in  $V_T$  is described as a reverse short channel effect (RSCE).

Figure 2.14 Reverse short channel effect on threshold voltage[Orlowski 1987]

The cause of the threshold rollup due to the reverse short channel effect has been attributed to the localised pileup of channel dopants along the edge of the gate at the silicon-silicon dioxide interface. The magnitude of the effect can be reduced by adjusting the processing stages of the device fabrication[Lutze 1995]. The main processing step to affect the threshold rollup is thought to be the source/drain junction implantation that causes interstitials in the lattice that leads to transient enhanced diffusion of the channel dopant[Chaudrhry 1997]. The profile of the channel doping has also been shown to affect the magnitude of the RSCE[Lutze 1995], though adjusting the profile of the channel implant also changes many of the transistors' characteristics, such as short channel effects, which can lead to a compromise of the devices performance.

## 2.2.2 Device Reliability

Reliability is a primary concern to the integrated circuit designer, where millions of transistors can be incorporated onto a single chip design. Failure within a chip can come from two key areas[Chenming 1993]; firstly from the gate oxide and secondly the metal level for the interconnects. At the device level the gate oxide reliability is of primary concern and this type of failure is discussed in the following sections.

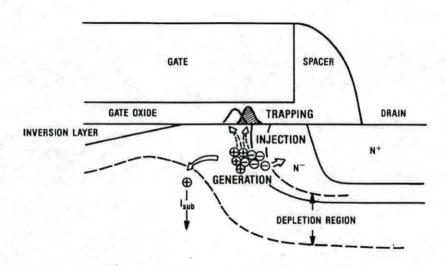

## Hot carrier degradation

Hot carrier degradation occurs in the gate oxide of a MOSFET when the carriers in the channel and pinch-off region, gain sufficient energy, from the lateral electric field, to surmount the energy barriers and tunnel into the oxide from the silicon. The problem is exaggerated in n-channel devices as the Si/SiO₂ energy gap for the carriers is smaller at ≈3.1eV for the electrons than ≈4.9eV for holes. Typical effects caused by hot-carriers include a shift in the threshold voltage, a change in the subthreshold swing and a reduction in the transconductance and hence current drive[Chen 1988].

Figure 2.15 Illustration of hot-carrier effects including hot-carrier generation, injection and trapping[Chen 1988].

The main hot carrier effects of hot-carrier generation, injection and trapping are shown in figure 2.15. A high drain field generates hot carriers, which channels hot electrons and electron-hole pairs generated by impact ionisation. The generation tends to occur in the high field area of the channel called the velocity saturation region, which is produced when the device is operated in saturation, between the drain and the pinched-off inversion layer, shown in figure 2.15. The magnitude of the electric field also affects the injection of the hot-carriers into the oxide. A lower field strength corresponds to a lower electron temperature, or energy, and therefore less

probability of gaining sufficient energy to break through the Si/SiO<sub>2</sub> interface. The probability of a carrier being injected into the oxide can be expressed as[Chen 1988]:

$$p = \exp\left(\frac{\phi_b}{kT_e}\right) \exp\left(-\frac{x}{\lambda}\right)$$

2.14

where: φ<sub>b</sub> - energy required for electrons to surmount the Si/SiO<sub>2</sub> barrier

T<sub>e</sub>(x) - electron temperature

x - distance from the interface

λ - energy dependant mean free path

The mechanisms of hot carrier trapping include bulk oxide trapping and interface trap generation. The predominant form of degradation is thought to occur by interface trap generation with the simultaneous injection of holes and electrons[Groeseneken 1995]. The injection of holes however are most effective by about four orders of magnitude over that of electrons. With LDD n-MOS devices the trapping of electrons in the sidewall spacer can enhance current degradation through an increase in the series resistance.

There are three main strategies for improving the hot-carrier effects in MOSFETs: Drain engineering, oxide quality and power supply reduction. Strategies for drain engineering have included the introduction of the lightly doped drain (LDD), where the doping concentration of the device's junction is reduced with a shallow implant either side of the gate, shown as the N-well extension in figure 2.12. The lower doping concentration reduces the peak of the lateral electric field near the drain and hence reduces the generation of the hot-carriers. It has also been reported[Song 1996] that an optimised halo/LDD structure at the junctions can reduce the effects of the hot-carriers by limiting their generation. Oxide quality is an important factor in increasing the life-span of MOSFETs. The reliability of the standard SiO<sub>2</sub> process has been shown to be improved upon with the introduction of nitrided oxides[Sodini 1992]. This process reduces the interface trap generation because of the presence of

nitrogen at the Si/SiO<sub>2</sub> boundary, but without optimisation of the process the influence of charge trapping increases. There is, however, a trade off with this process because of a slight degradation of the electrical characteristics over SiO<sub>2</sub>. Reduction of the drain voltage produces a corresponding reduction of the lateral electric field in the channel region, though this circuit parameter is generally outwith the control of the design engineer and is instead set for the technology generation of the devices. The supply voltage for the 0.25μm generation is 2.5-1.8V, which is projected to drop to 1.2-0.9V for the 0.1μm generation[SIA, 1997].

# 2.3 MOSFET Device Scaling

The scaling of MOSFET devices involves the downsizing of the major features of the device, including the physical dimensions and the electrical constraints, such as power supply. This section discusses the basic theory of scaling strategies and the future implementation of different scaling scenarios. A prediction of the future scaling trends is also highlighted.

## 2.3.1 Scaling strategies

## Constant electric field scaling

The basis of scaling strategies is to reduce the dimensions of a MOS device while still maintaining the same long channel characteristics. The basic strategy is constant electric-field (CE) scaling, where the electric field potentials within a device are kept constant, while the dimensions and properties are changed using a scaling factor  $\alpha$  ( $\alpha$ >1)[Dennard 1974]. The physical dimensions of the device are reduced by the factor  $1/\alpha$  and the electric fields within the device are kept constant by reducing the operating potentials by  $1/\alpha$  and increasing the doping concentration by  $\alpha$ . This technique increases the packing density of devices by  $\alpha^2$  and the speed by  $\alpha$ , while the power dissipation is reduced by  $\alpha^2$ .[Davari 1995].

## **Actual scaling strategy**

The scaling of MOSFETs has taken a slightly different path than the proposed method of CE scaling. While the dimensions of the devices were decreased in accordance with the scaling theory, the power supply was maintained at the same 5V level as previous generations. This level was maintained until the 0.5µm generation of transistor, where the power supply was reduced to 3.3V. The power supply levels of the different generations of transistors was kept constant, because it allowed design compatibility between the levels, even though the electric field in the MOSFET was increasing with the progressive decrease in the gate length feature sizes. The increase of electric fields within the devices was accounted for with a more generalised scaling strategy[(I)Baccarani 1984], where the electric field patterns within a scaled device are still preserved, but the intensity of the field can be changed everywhere in the device by a multiplication factor  $\varepsilon$ . The relationship between the generalised theory and constant-electric field scaling is shown in table 2.1. The supply voltage is scaled less rapidly by a factor  $\varepsilon/\alpha$ , while the electric field patterns are maintained by increasing the doping concentrations by the factor ε. Limits to the generalised scaling include the gradual increase in electric field which leads to long term reliability problems from gate insulator failure or hot-carrier effects.

| Physical parameters      | Constant-electric field | Generalised scaling factor |  |  |

|--------------------------|-------------------------|----------------------------|--|--|

|                          | scaling factor          |                            |  |  |

| Linear dimensions        | 1/α                     | 1/α                        |  |  |

| Electric-field intensity | 1                       | ε                          |  |  |

| Voltage (Potential)      | 1/α                     | ε/α                        |  |  |

| Impurity concentration   | α                       | α                          |  |  |

Table 2.1 Relationships between constant-electric field and generalised scaling[Davari 1995]

## Scaling MOSFETs to 0.1 µm and below

As the dimensions of MOSFETs are reduced further down to 0.1µm the scaling of devices becomes constrained by the physical limits of the scaling parameters[Iwai

1998]. Parameters such as gate insulator thickness and channel length will approach a limit where scaling can no longer occur. As these limits are approached the scaling strategy has to consider a trade off between increased device performance and reliability. Channel hot-carrier effects limit the selection of optimum power supply voltage for devices below 0.25µm, and these effects have been discussed in section2.2.2. Drain engineering with increased doping affects the performance of the device by increasing the source/drain resistance, although these effects can be counteracted with the use of silicides at the source, drain and gate connections to lower the sheet resistance of the silicon or polysilicon material[Murarka 1983]

## 2.3.2 High performance and low power scaling scenarios

With the scaling of MOSFETs being a trade off between device performance, reliability and subthreshold current, two different scenarios for scaling have been proposed[Davari 1995]. The high performance and low power scenarios, shown graphically in figure 2.16, provide an outlook for device scaling with the focus for each strategy focused on a different goal. The high performance scenario uses a higher supply voltage, for a given channel length, over the low power version. The electric fields within the device will be higher and so adequate long term device reliability has to be maintained. The gate oxide thickness and doping profiles are optimised with this scenario to provide low off and high drive current without the electric field producing gate oxide tunnelling and GIDL current. The low power scenario uses a reduced supply voltage, compared to the high performance case, with the aim to reduce the power dissipation per device and therefore maintain a lower power density.

Figure 2.16 A measure of the electric field,  $V_{DD}/L$ , as a function of channel length for various scaling scenarios[Davari 1995].

## 2.3.3 Scaling projections

The introduction of MOS technology generations to the marketplace followed a 3-year cycle. The projections for the introduction of future technologies are documented by the Semiconductor Industry Association (SIA), and the lead time between generations with the latest predictions are a two year gap between the introduction of a new technology[SIA, 1997]. The projections for the scaling of future technologies by the SIA are shown in table 2.2.

| most El Bortee operation                  |         |         |         |         |         |         |

|-------------------------------------------|---------|---------|---------|---------|---------|---------|

| Minimum Feature Size for Dense lines (nm) | 180     | 150     | 130     | 100     | 70      | 50      |

| Dense lines (lilii)                       |         |         |         |         |         |         |

| Minimum Feature Size for                  | 140     | 120     | 100     | 70      | 50      | 35      |

| Gate Lithography (nm)                     |         |         |         |         |         |         |

| Year of Introduction                      | 1999    | 2001    | 2003    | 2006    | 2009    | 2012    |

| DRAM (bits)                               | 1G      | 17      | 4G      | 16G     | 64G     | 256G    |

| Supply Voltage (V)                        | 1.5-1.8 | 1.2-1.5 | 1.2-1.5 | 0.9-1.2 | 0.6-0.9 | 0.5-0.6 |

|                                           |         |         |         |         |         |         |

Table 2.2 MOSFET technology projections[SIA, 1997]

## 2.4 Present Silicon Device Research

Research into future device technologies is presently focused on devices with minimum feature sizes of 100nm and below. Devices of 100nm dimensions, and operated at low temperature, were first reported by Sai-Halasz in 1987[Sai-Halasz 1987]. Since that time a number of papers have demonstrated MOSFETs, operating at room temperature, with dimensions of 100nm[Taur 1993][Yan 1992]. More recently research has investigated devices with fabricated gates of dimensions below 100nm. Ochiai et al have reported 40nm MOSFETs using electron beam lithography to fabricate the gate electrodes[Ochiai 1996]. The current-voltage curves of the devices displayed transistor operation although punchthrough was evident from the characteristic curves. A reduction in the short channel effects of the sub-100nm transistor has been reported by Kawaura et al with the fabrication of a dual gate in a 30nm gate length MOSFET[Kawaura 1998]. The dual gate involves the fabrication of a second longer gate over the existing gate in the device. This upper gate produces an inversion layer in the channel that acts like an ultra-shallow source/drain implant, reducing the short channel effects caused by the electrostatic field in the channel region.

## 2.5 Summary

This chapter has provided an introduction to MOSFET device operation. The parameters that affect the operation of both long and short channel devices have been highlighted, and the equations used to model the respective devices performance have been introduced. Some of the short channel effects associated with the miniaturisation of MOSFETs have been presented, with reference to the current-voltage, subthreshold and threshold voltage characteristics. Reliability considerations of hot carrier effects have been discussed with methods of failure prevention highlighted. Finally a discussion of device scaling strategies was displayed with a discussion of the current state of the art research into silicon device technology.

3.

# **Electron Beam Lithography**

The progressive reduction of feature sizes in the fabrication of MOS devices puts an increasing demand upon the lithography techniques used to define the nano scale features. Industrial production of devices currently uses an optical lithography process and can define feature sizes down to 180nm. Research into future device technologies, however, requires much smaller feature sizes to be defined, predicted to be down to 70nm by the year 2006[SIA, 1997]. Electron beam lithography is an ideal approach for such narrow structure patterning as the system uses a finely focused electron beam of a few nanometers diameter to define the structures.

This chapter provides an overview of electron beam lithography. The technology of electron beam systems is explained in order to provide an insight into the design strategy of the Edinburgh built system that is illustrated in chapter 4 of this thesis. Alternative techniques, of optical and x-ray lithography are also described to provide a comparison of technologies available for pattern definition.

# 3.1 Electron beam lithography systems

Electron beam pattern writing systems can be used in two roles for LSI production[Saitou 1996]. Firstly, as a direct write lithography tool for fabricating advanced devices and structures, and secondly as a mask making device for other lithography techniques such as optical and x-ray masks.

## 3.1.1 A general system

Electron beam lithography uses a high energy beam of electrons to define patterns on the substrate of a silicon wafer. The imaging beam is produced by an electron gun and is focused on a photoresist coated substrate. The beam is then scanned across defined areas of the substrate by deflecting it in a controlled way. The single beam writes one pattern at a time, so multiple patterns are imaged sequentially. After exposure, the patterns are wet developed and rinsed to produce a patterned image with the remaining resist.

## 3.1.2 History of e-beam systems

The development of electron beam lithography has progressed steadily since the mid 1960s[Watts 1989]. Initially the main impact of this technology was the fabrication of masks for lithography tools, such as optical steppers, and more recently for x-ray lithography. Another use of the systems has been for low-volume manufacture of advanced, small scale, high performance devices.