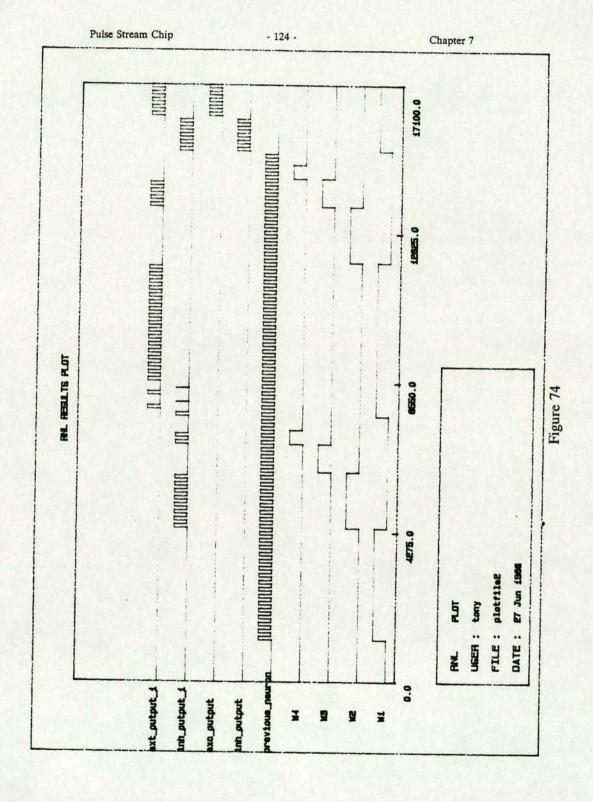

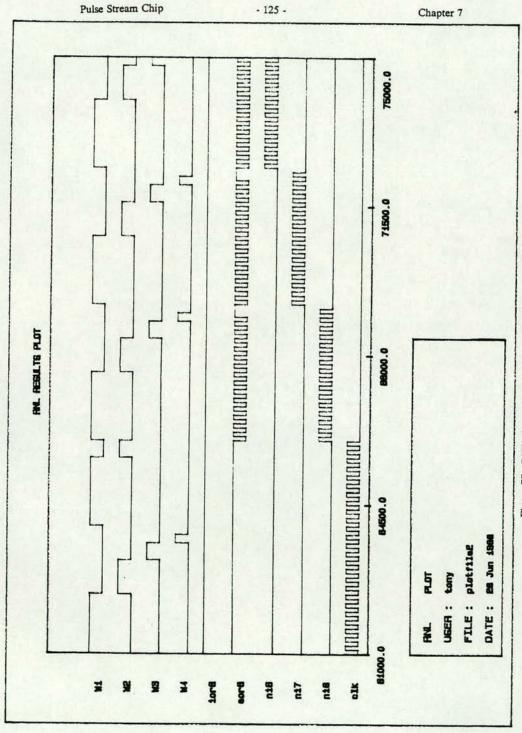

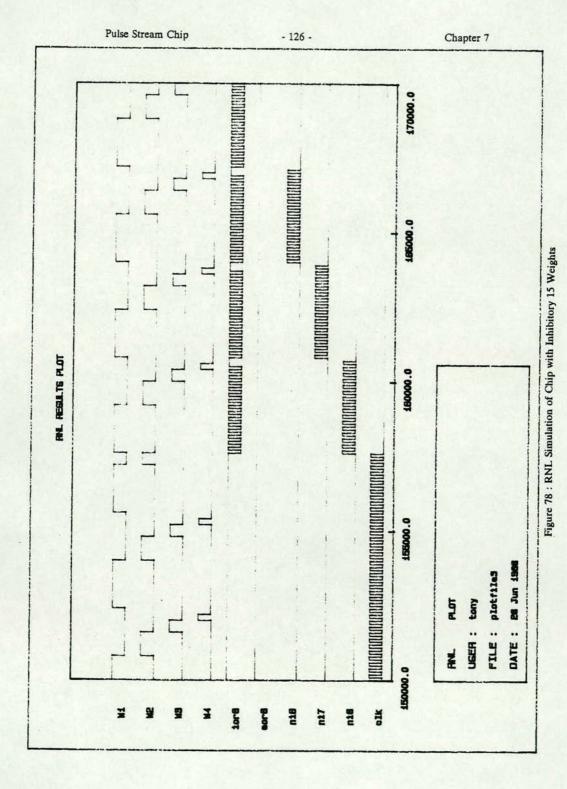

## The Implementation of Neural Networks as CMOS Integrated Circuits

Anthony V. W. Smith

Thesis submitted for the degree of

Doctor of Philosophy

University of Edinburgh

November 1988

### Dedication

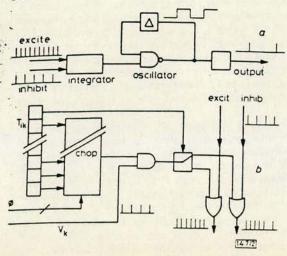

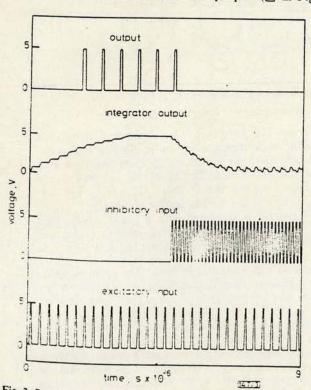

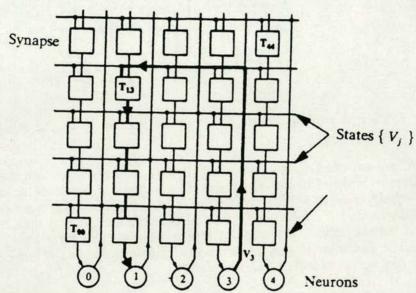

I would like to dedicate this thesis firstly to my parents who have supported and encouraged me throughout these three years.

Also to Sharon, Shital, Yoginee and Martin whose support when I was an undergraduate enabled me gain the qualifications necessary for me to do this PhD.

The research described in this thesis was the unaided work of the author, unless otherwise indicated. Where the research was done in collaboration with others, there was a significant contribution by the author.

#### Acknowledgements

The preparation of this work would have been less of a pleasure, more of a chore, and probably impossible were it not for the help and encouragement of several people. I would like to express my deepest thanks:

to my supervisor **Dr. A.F. Murray**, for his guidance and patience throughout the three years which has ensured the completion of the research and the submission of this thesis;

to the Computer Support Staff for their help with the production of this thesis; to my father, for proof-reading this work;

to my mother, who encouraged me to complete it within the time available; to the Science Research Council for their financial support.

Finally I would like to thank Professor J. Mavor and Professor P. Denyer for their interest and guidance, and for the use of the excellent research facilities of the Department of Electrical Engineering in Edinburgh University.

## **Table of Contents**

| Introduction                                             | 1   |  |

|----------------------------------------------------------|-----|--|

| 1 Introduction to Neurons                                | 4   |  |

| 1.1 The Neuron                                           | 4   |  |

| 1.2 Myelination of Axon                                  | 6   |  |

| 1.3 Resting Potential of the Neuron                      | 6   |  |

| 1.4 Generation of Action Potential in Neurons            | 7   |  |

| 1.5 Synapses                                             | 10  |  |

| 1.6 Types of Chemical Synapse and their Properties       | 12  |  |

| 1.7 Special Properties of Synapses                       | 14  |  |

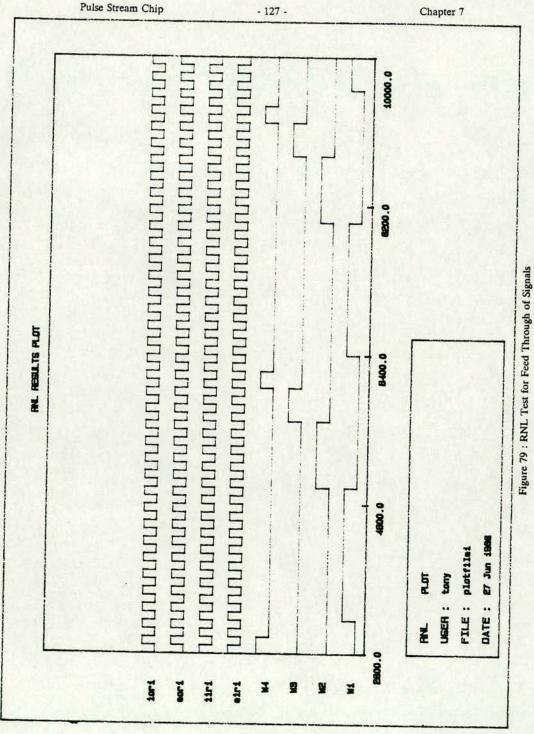

| 2 A History of Research into Biological Neural Networks  | 17  |  |

| 3 A History of Research into Synthetic Neural Networks   | 21  |  |

| 4 Neural Models and Learning Recipies                    |     |  |

|                                                          | 32  |  |

| 4.1 The Perceptron Model                                 | .32 |  |

| 4.2 Widrow and Hoff Model                                | 35  |  |

| 4.3 Hopfield Model                                       | 36  |  |

| 4.4 Wallace-Hopfield Model                               | 40  |  |

| 4.5 Barto Model                                          | 42  |  |

| 4.6 Grossberg Model                                      | 45  |  |

| 4.7 Von der Malsburg's Model                             | 45  |  |

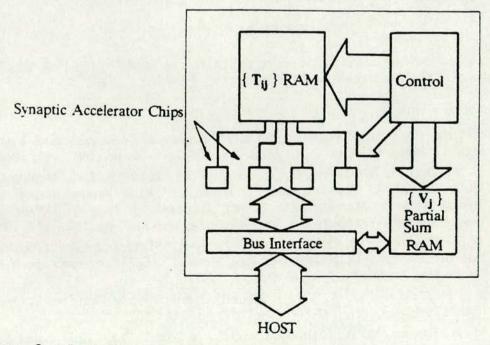

| Present Trends in VLSI Implementation of Neural Networks | 47  |  |

| Digital Neural Networks                                  |     |  |

| 6.1 Simulations of Digital Neural Network                | 54  |  |

| or official of Digital Neural NetWork                    | 54  |  |

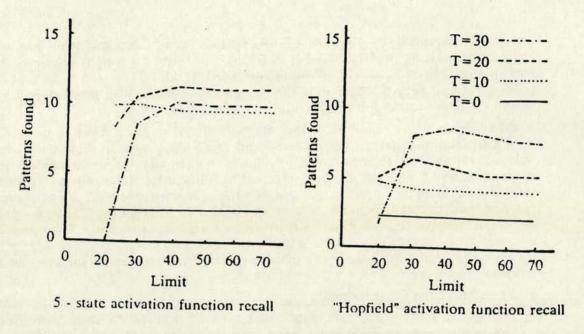

| Reduced Precision Arithmetic                                  | 54 |

|---------------------------------------------------------------|----|

| 5-State Activation Function                                   | 54 |

| Using 5 State as an approximation to a Sigmoid                | 56 |

| The Problem                                                   | 58 |

| Method of learning with fixed weights                         | 60 |

| Renormalisation                                               | 60 |

| Forgetting                                                    | 62 |

| Clipping                                                      | 62 |

| Results                                                       | 62 |

| Comparison of Learning with Binary, 5-State and Sigmoid Func- |    |

| tions                                                         | 64 |

| Recall of Learnt Patterns with 12.5% noise                    | 66 |

| Conclusions                                                   | 70 |

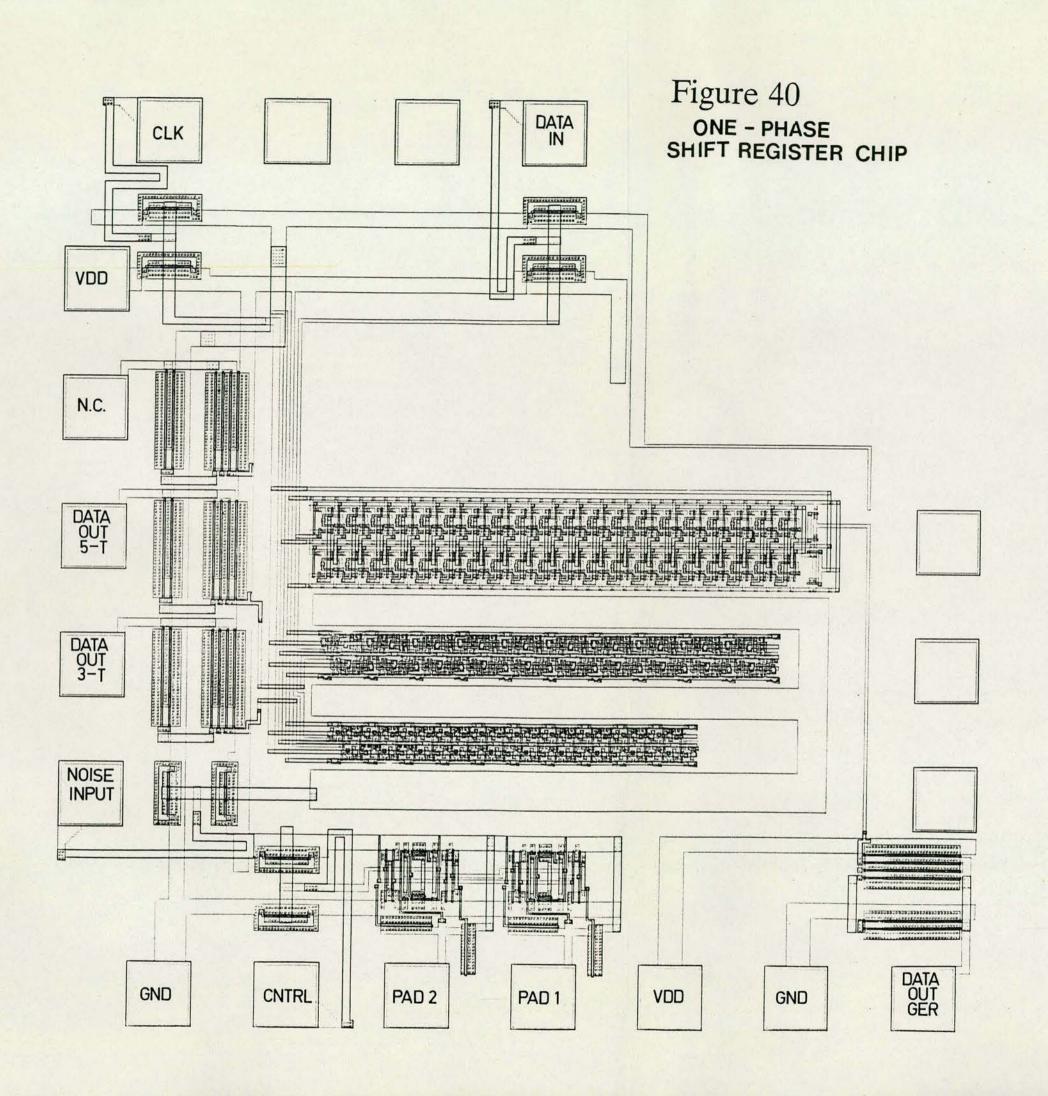

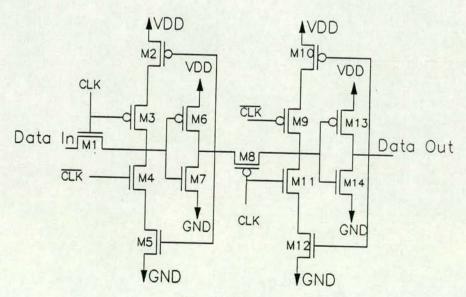

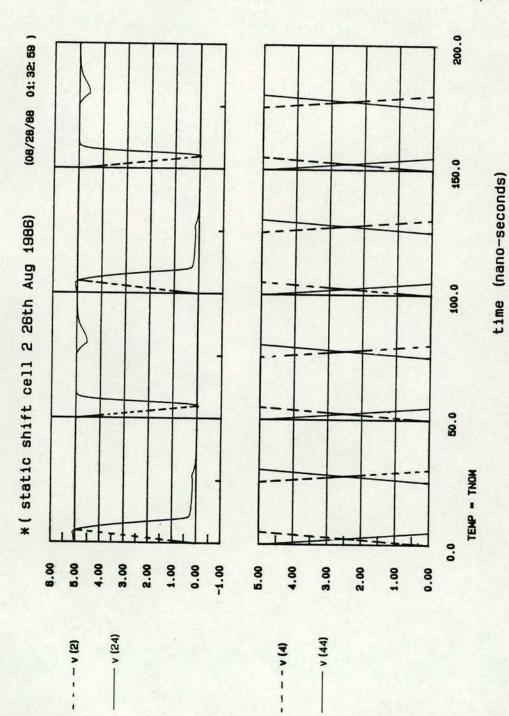

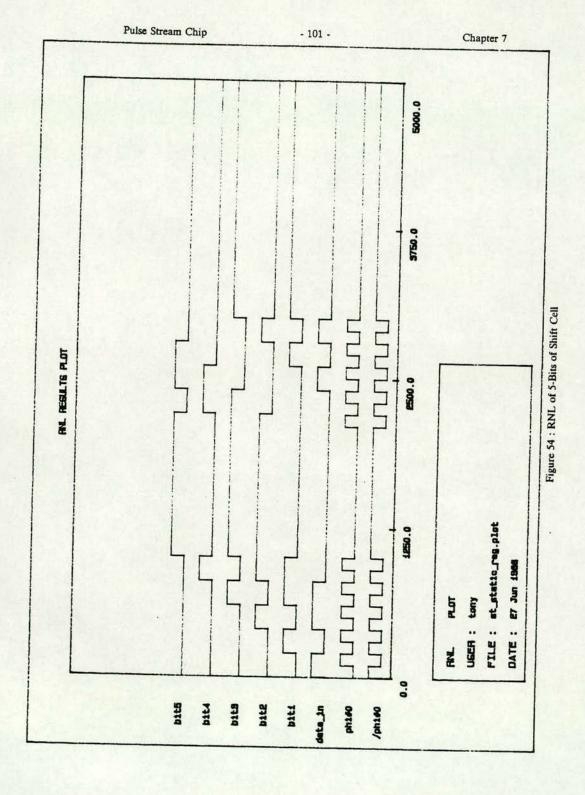

| 6.2 One Phase Shift Register Chip                             | 71 |

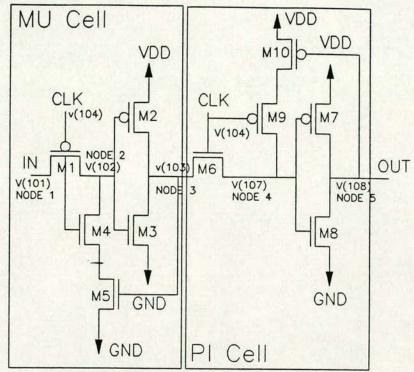

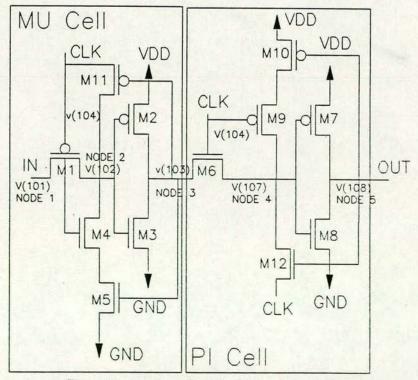

| Design of Shift Cells                                         | 71 |

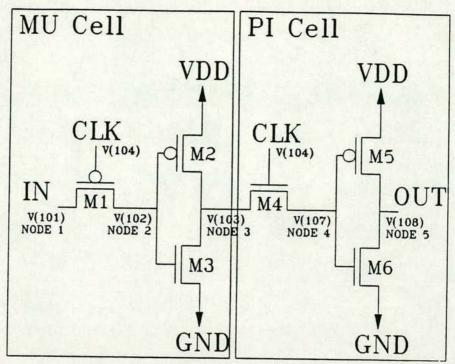

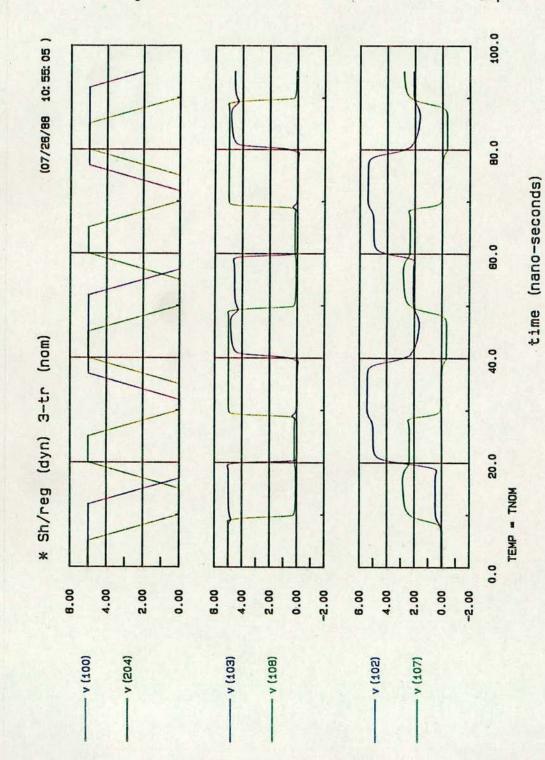

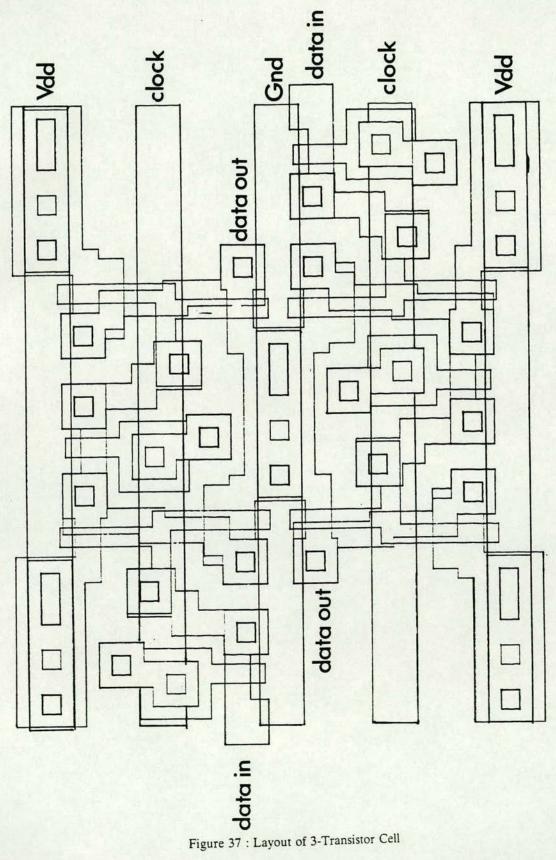

| 3-Transistor Cell                                             | 71 |

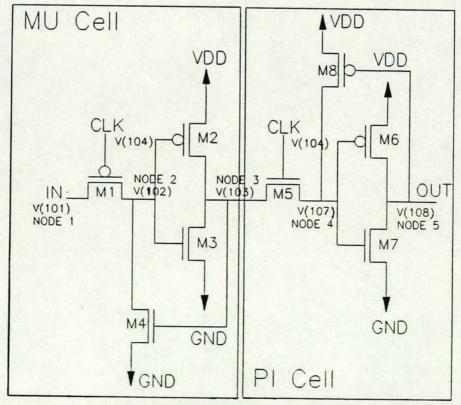

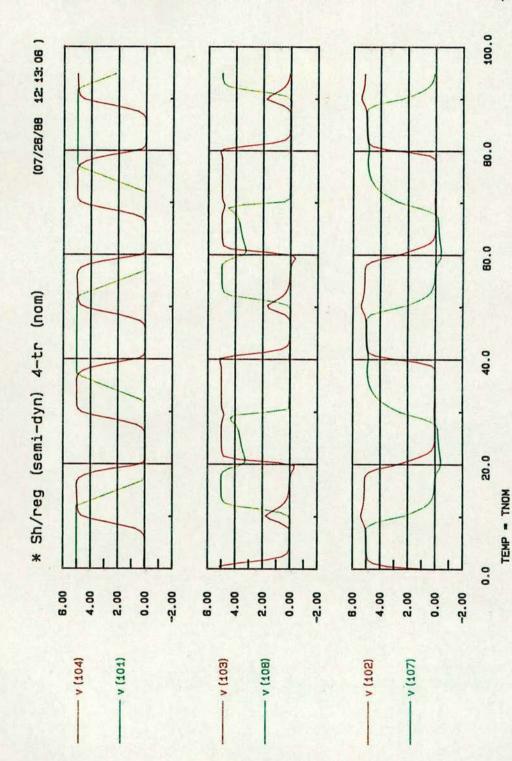

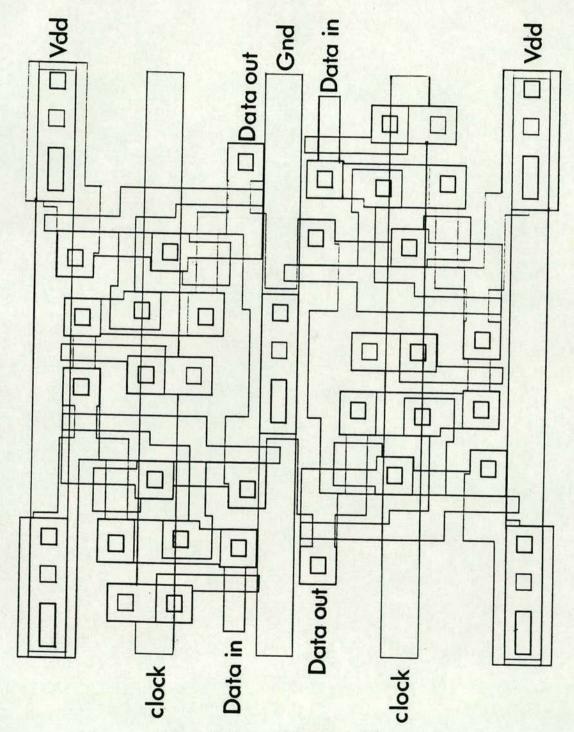

| 4-Transistor Cell                                             | 74 |

| 5-Transistor Cell                                             | 76 |

| 6-Transistor Cell                                             | 79 |

| Layout of Cells                                               | 79 |

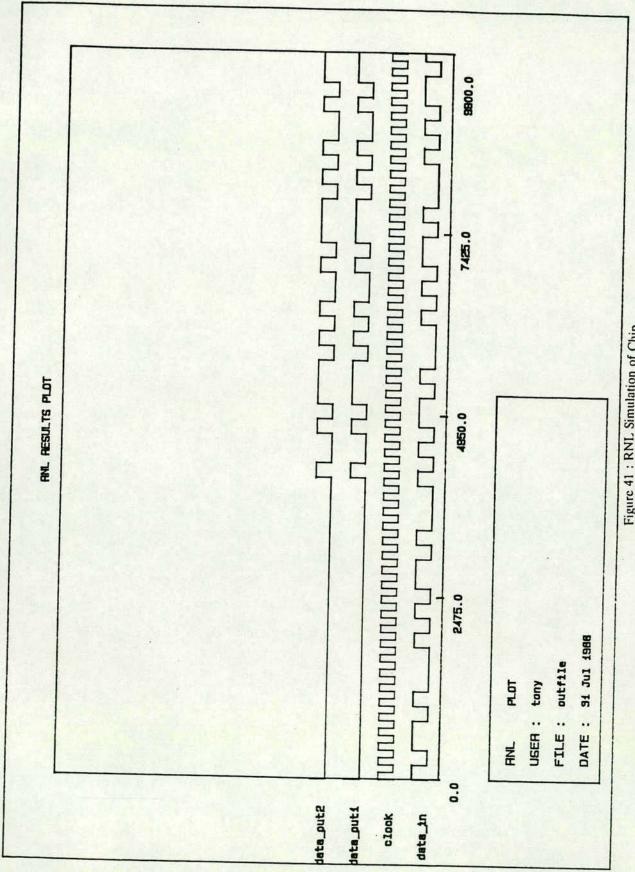

| The Shift Register Chip                                       | 84 |

| Results                                                       | 85 |

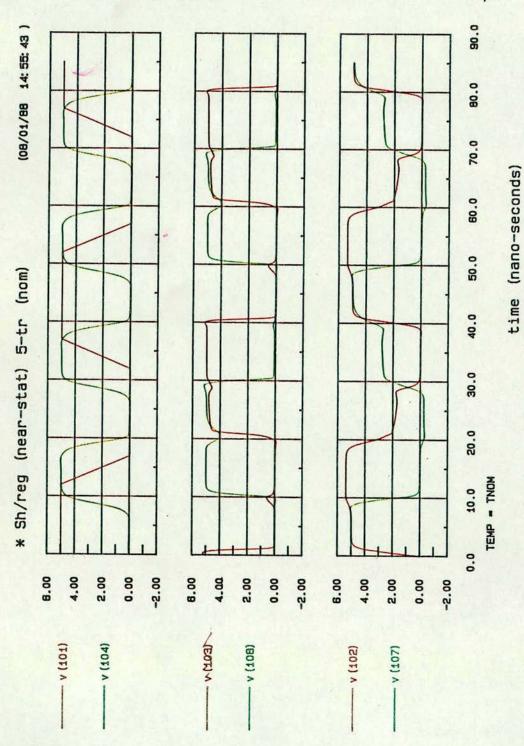

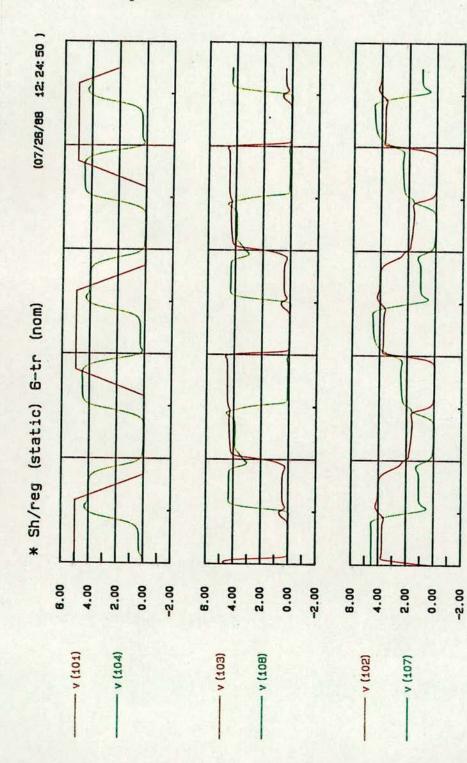

| 3-Transistor Shift Register                                   | 85 |

| 5-Transistor Shift Register                                   | 85 |

| Conclusions                                                   | 85 |

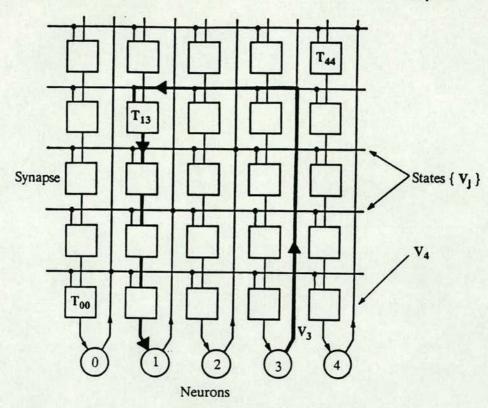

| 7 Pulse Stream Approach to Neural Networks                    | 89 |

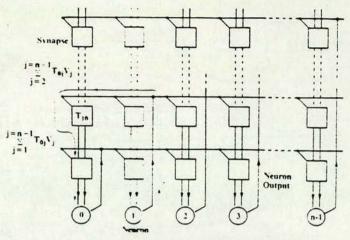

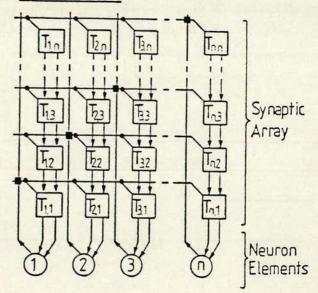

| 7.1 Overall Architecture                                      | 89 |

|                                                               |    |

Contents

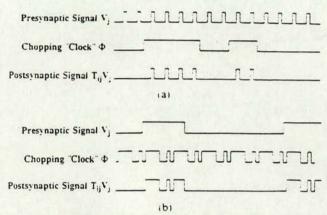

|   | 7.2 Signalling Mechanism                   | 89  |

|---|--------------------------------------------|-----|

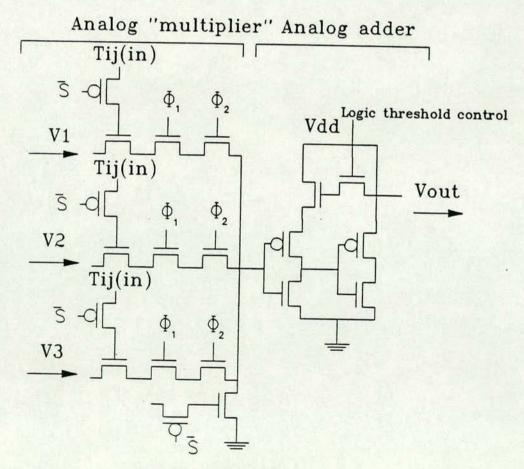

|   | 7.3 Arithmetic Operations on Pulse Stream  | 90  |

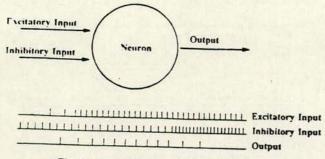

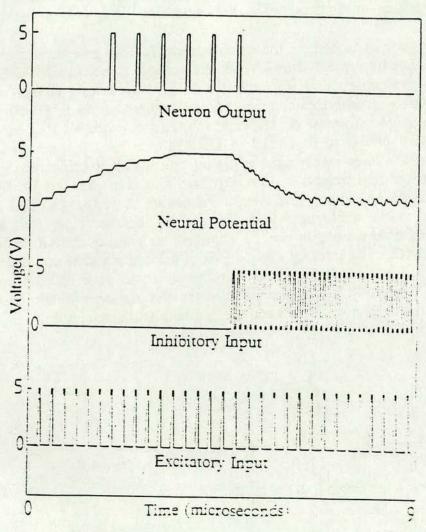

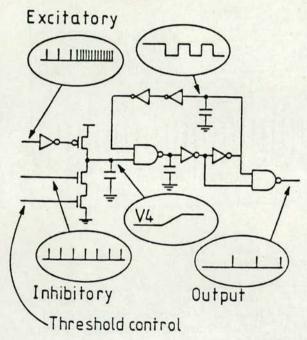

|   | 7.4 Neuron Function                        | 90  |

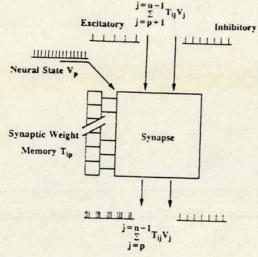

|   | 7.5 Synaptic Function                      | 92  |

|   | 7.6 Neuron Circuit                         | 92  |

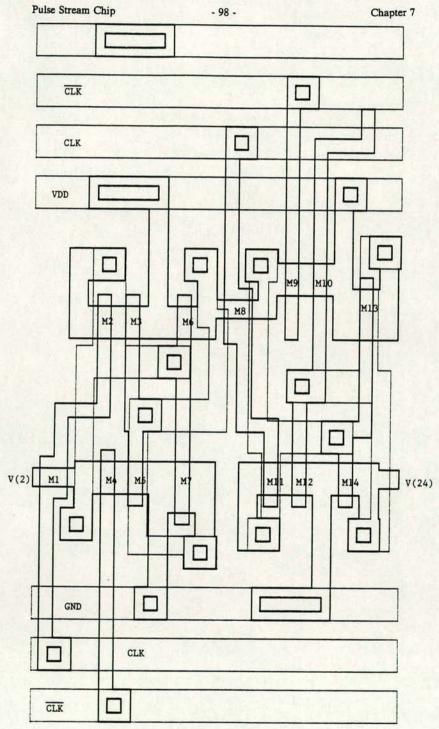

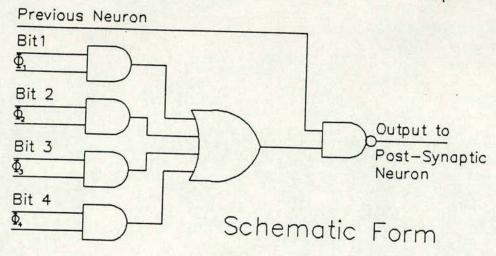

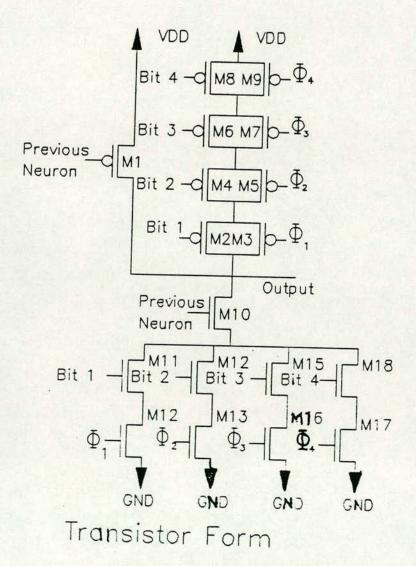

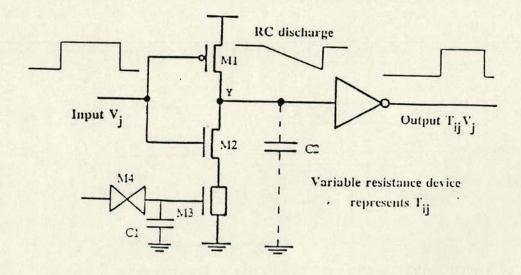

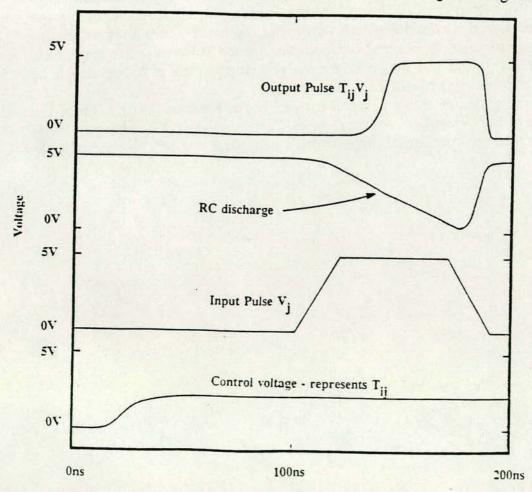

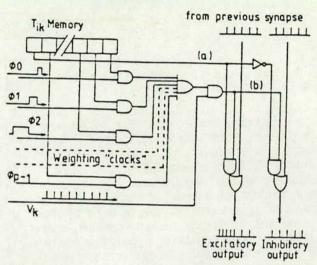

|   | 7.7 Synaptic Circuit                       | 94  |

|   | 7.8 The Synapse                            | 94  |

|   | Weight Storage Circuitry                   | 94  |

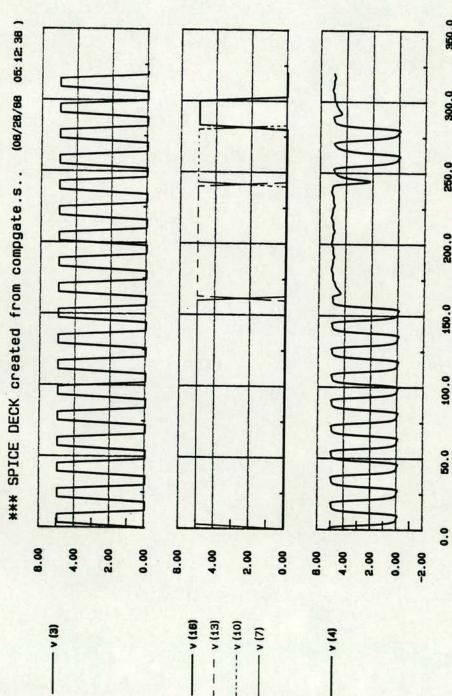

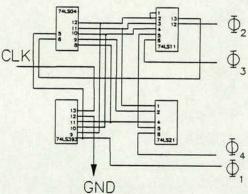

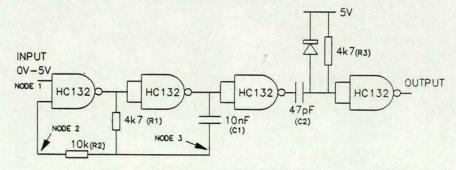

|   | Chopping Clock Circuit                     | 100 |

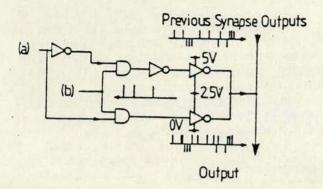

|   | The Output Unit                            | 100 |

|   | Tertiary Output Stage                      | 105 |

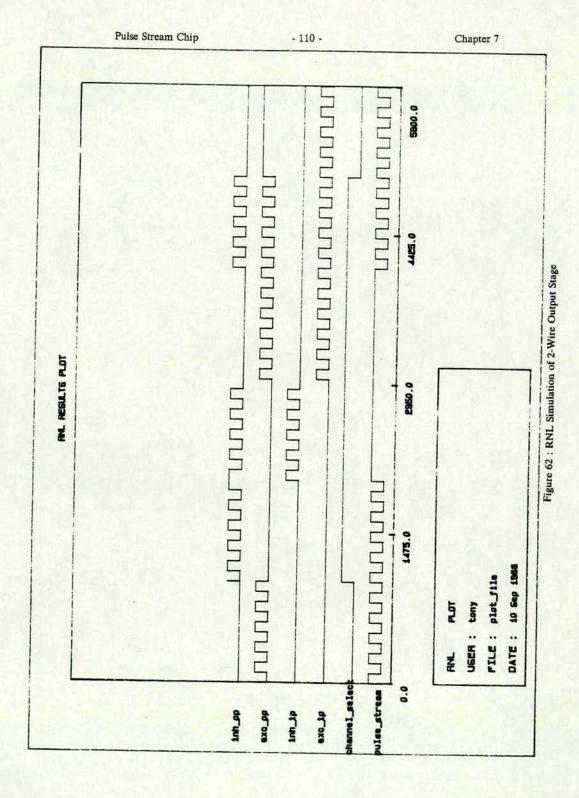

|   | 2-Wire Output Stage                        | 105 |

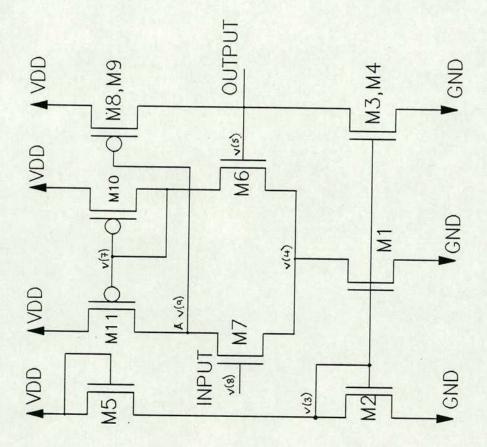

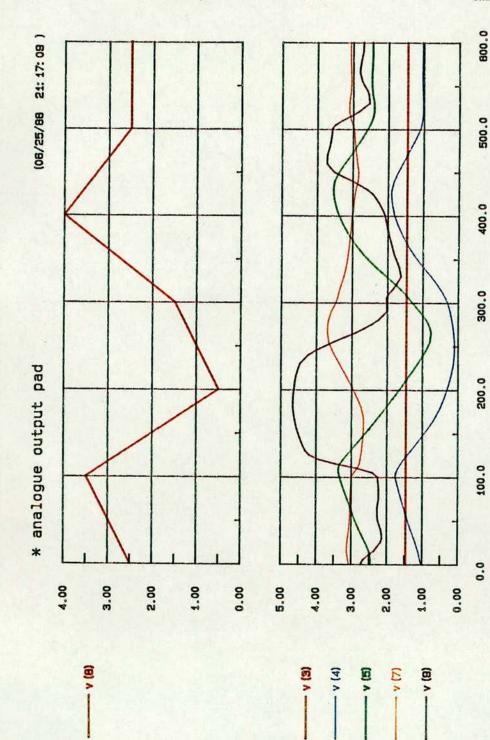

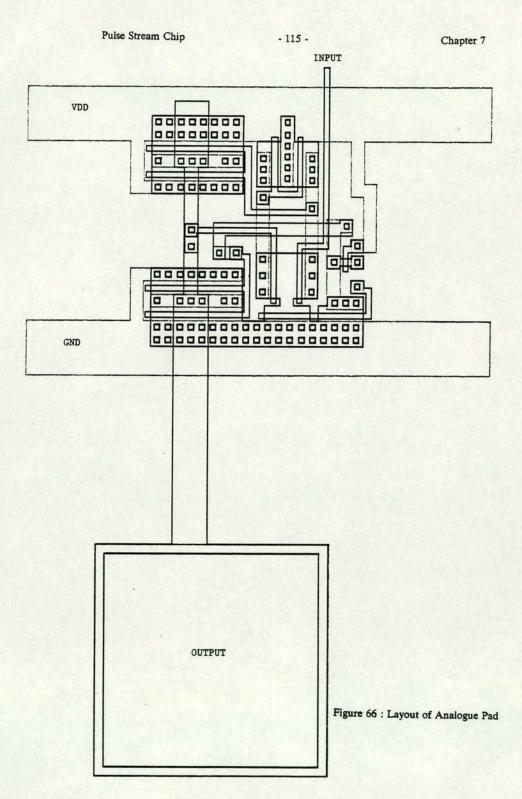

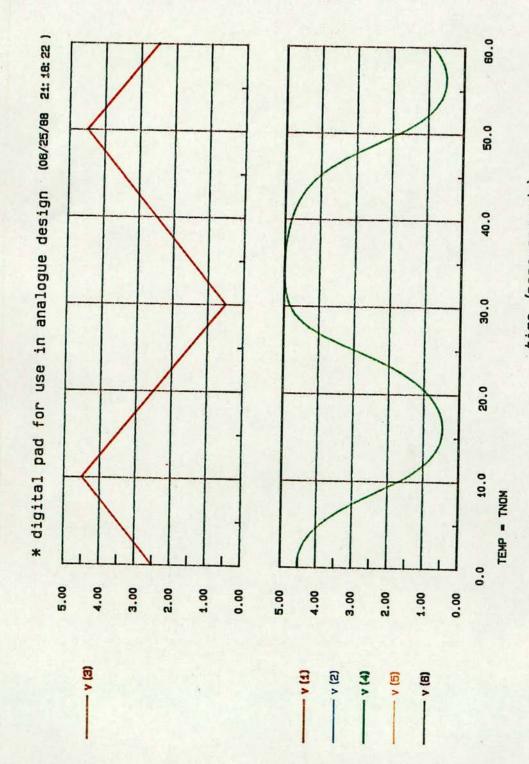

|   | 7.9 Analogue Pad                           | 105 |

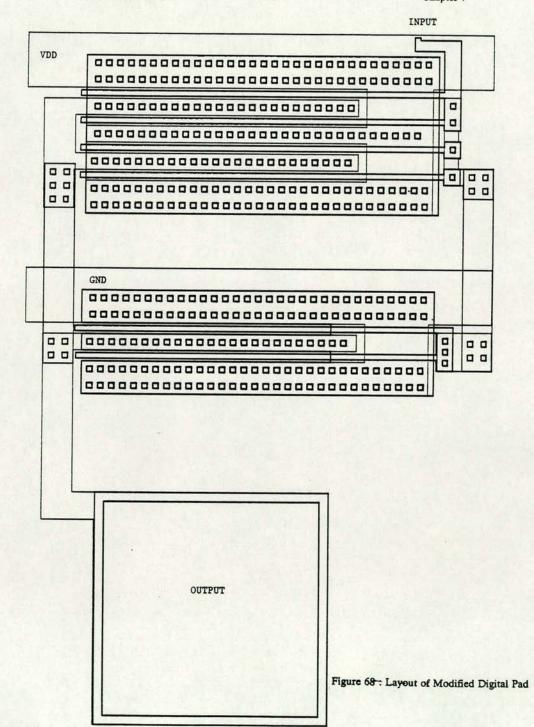

|   | 7.10 Digital Pad used for Analogue Signals | 113 |

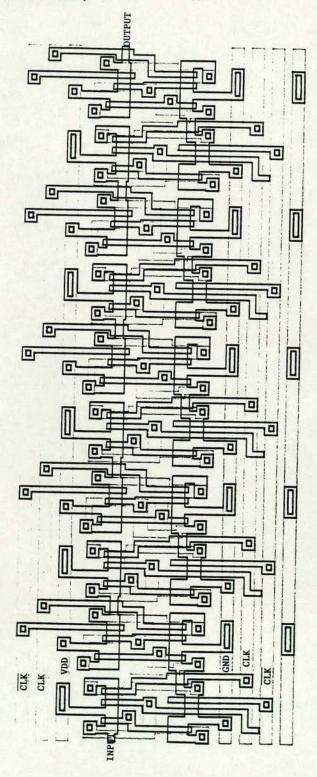

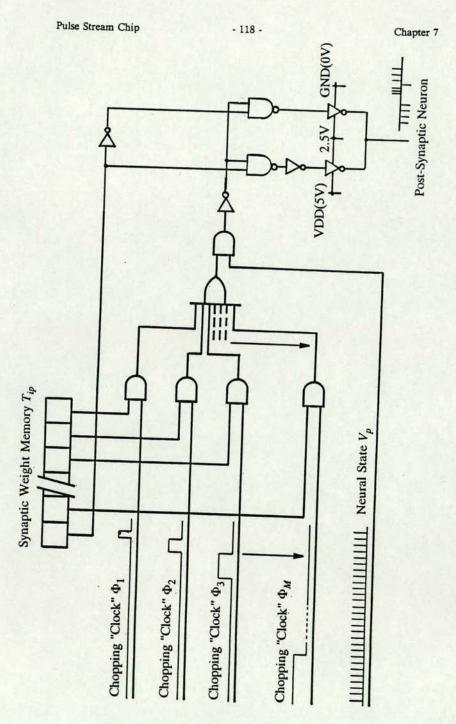

|   | 7.11 Synapse Circuits                      | 113 |

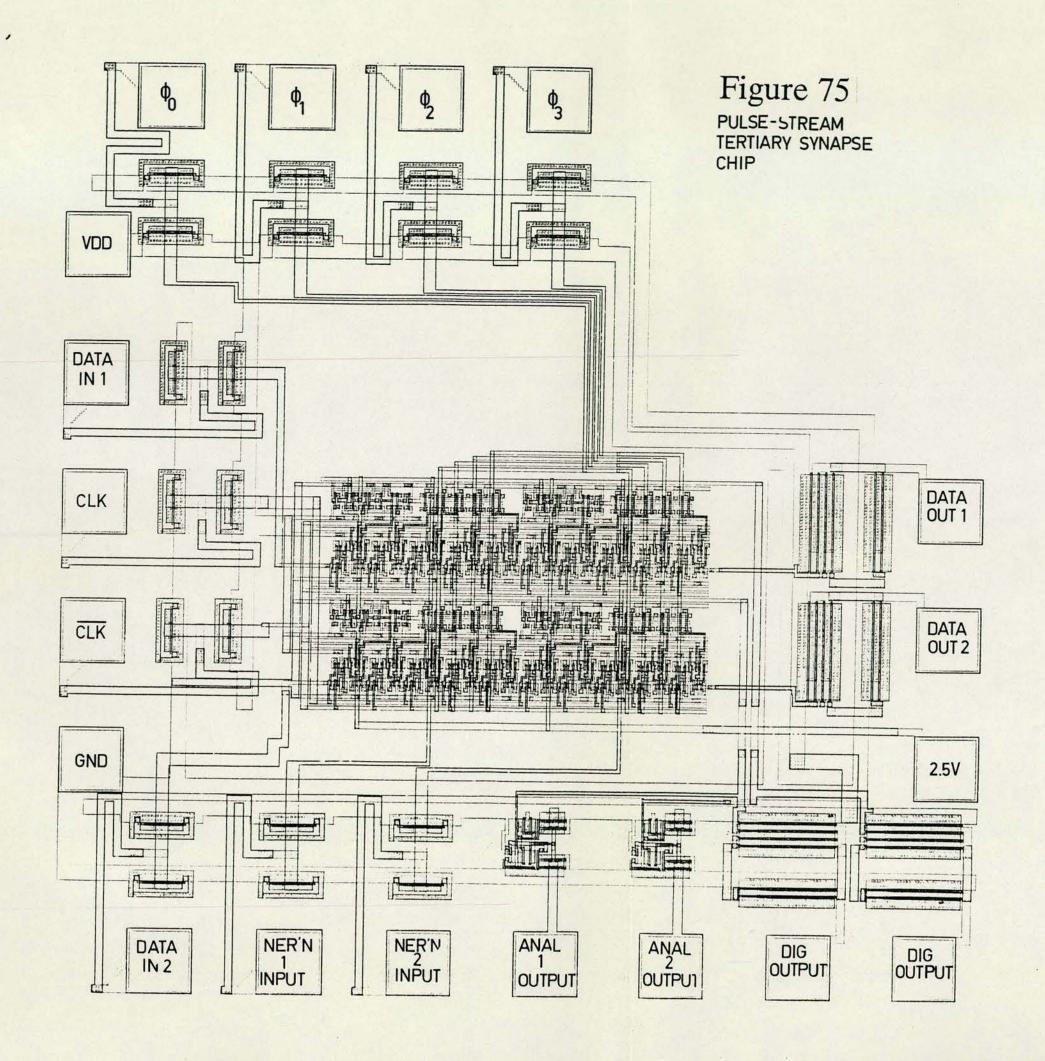

|   | Tertiary System                            | 113 |

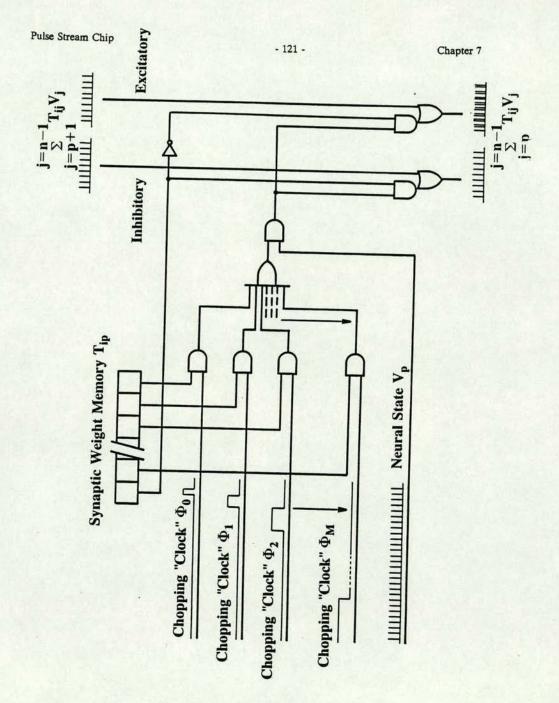

|   | 2-Wire System                              | 120 |

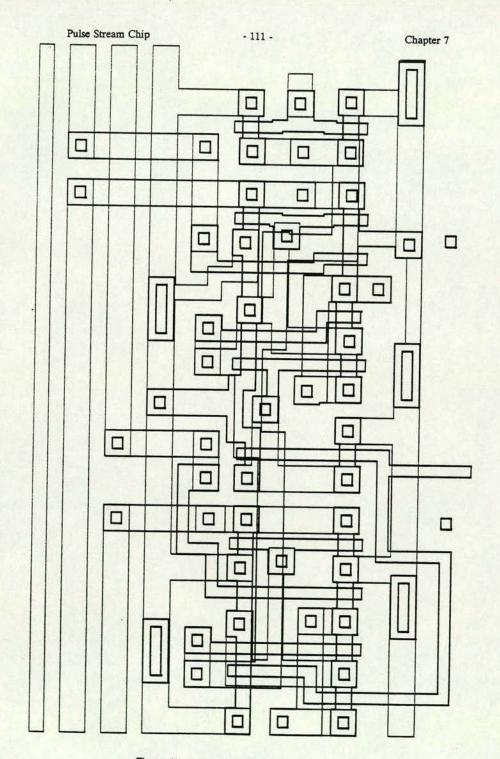

|   | 7.12 Final Chip Layout and Testing         | 120 |

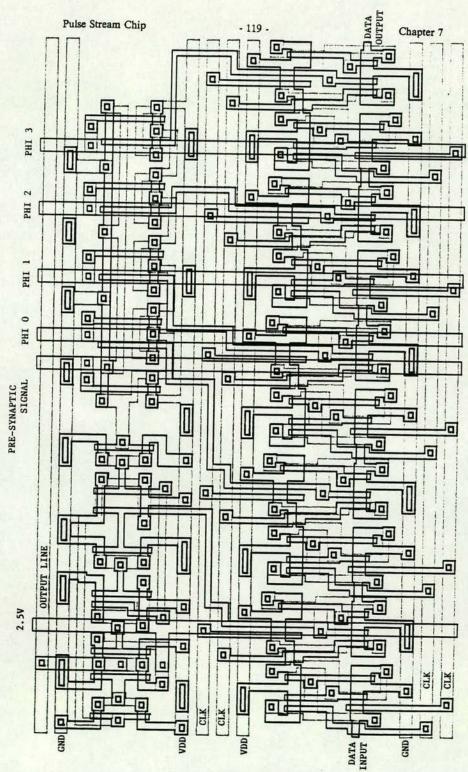

|   | Tertiary System                            | 120 |

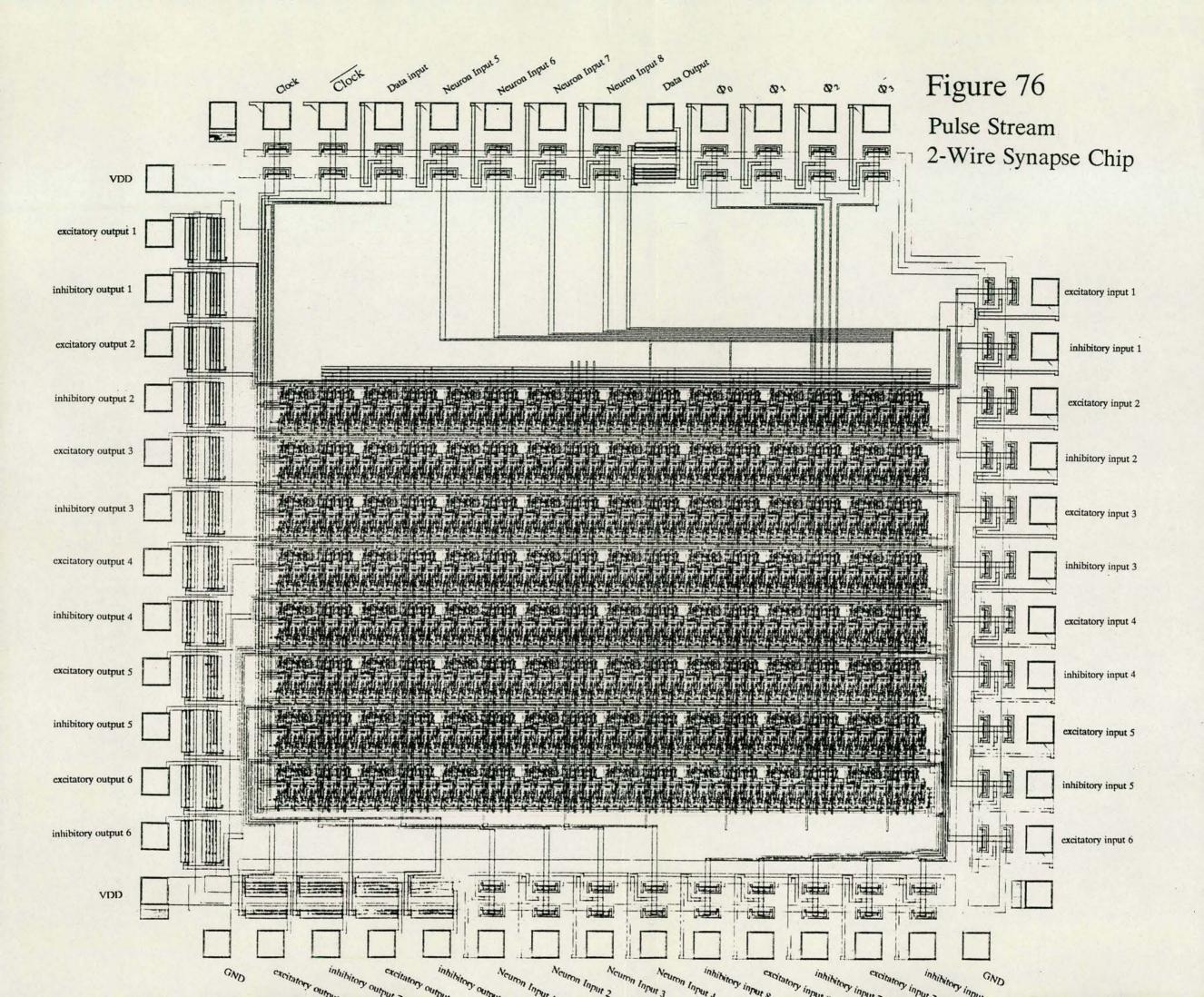

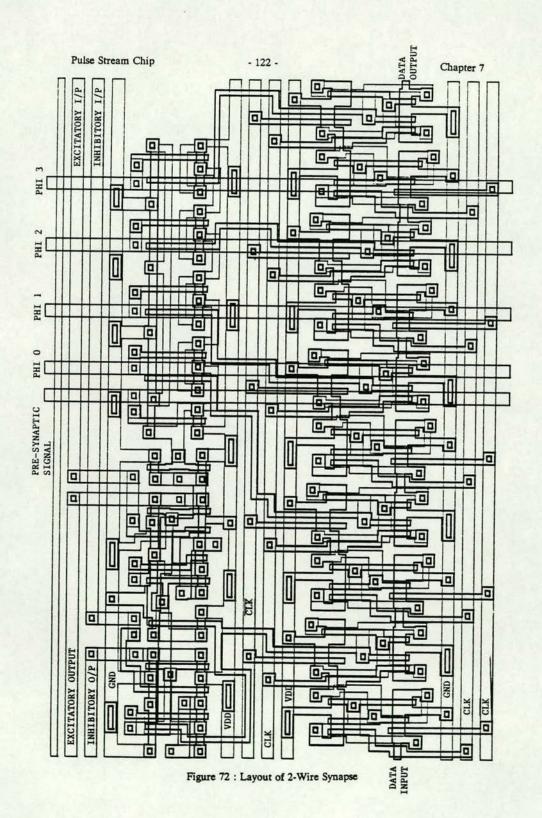

|   | 2-Wire System                              | 128 |

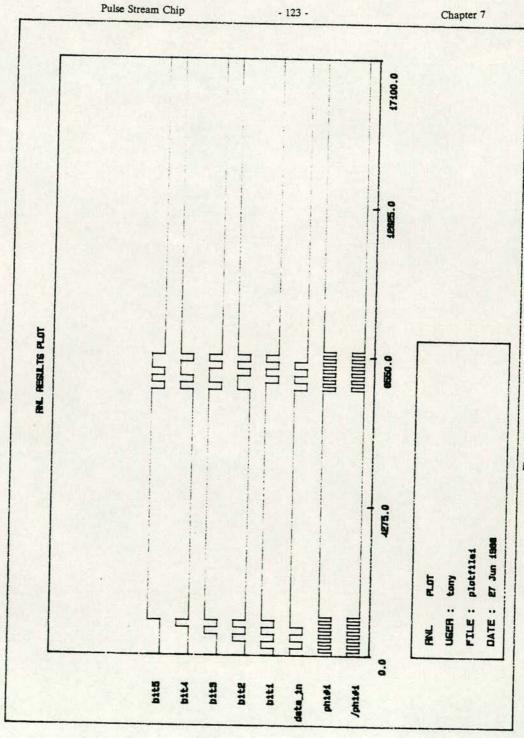

|   | 7.13 Results from Fabrication              | 128 |

|   | 7.14 Chip Photographs                      | 130 |

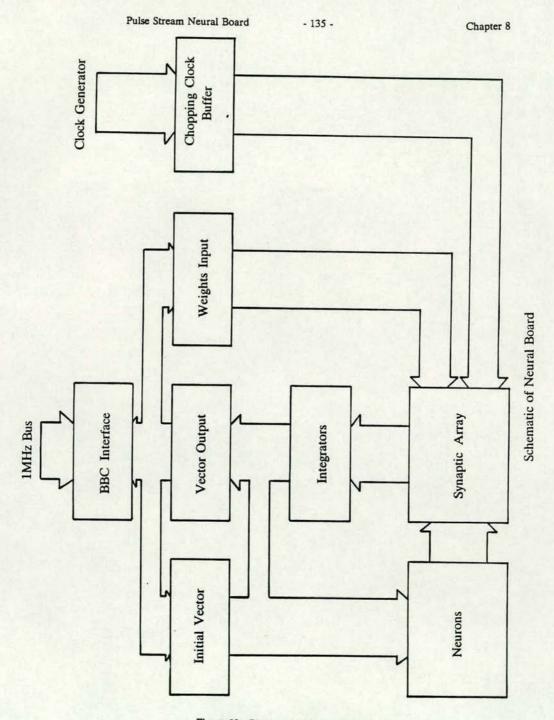

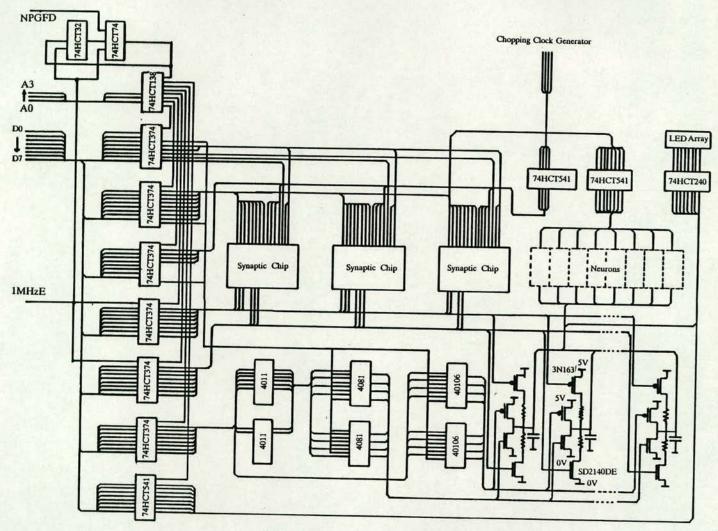

| 1 | Neural Board                               | 134 |

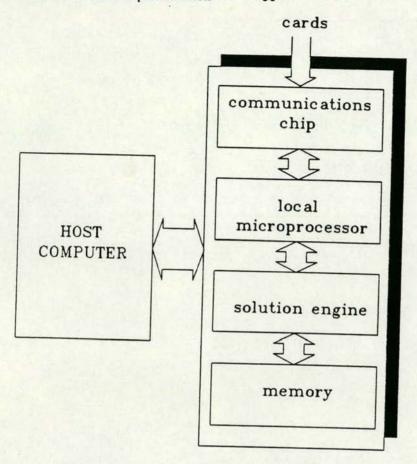

|   | 8.1 Introduction                           | 134 |

|   | 8.2 Major Components                       | 134 |

|   | The BBC Interface                          | 134 |

|   | The Weights Loading Circuitry              | 136 |

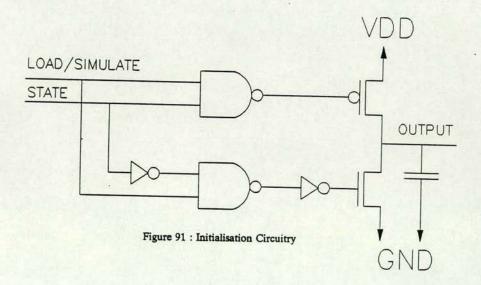

| The Initial Vector Setup Circuitry                            | 139 |

|---------------------------------------------------------------|-----|

| The Stable Vector Output Circuitry                            | 140 |

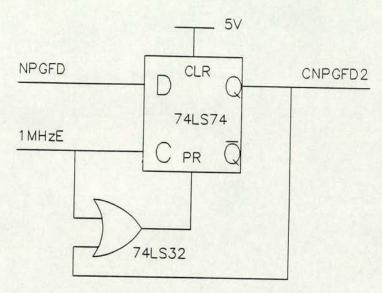

| The Chopping Clock Circuitry                                  | 140 |

| The Vector Display Circuitry                                  | 142 |

| 8.3 Debugging Hardware                                        | 143 |

| 8.4 Results                                                   | 143 |

| Results with First Neural Circuit                             | 143 |

| Debugging of the Neural Board                                 | 143 |

| Fully Functioning Neural Board                                | 145 |

| Learning and Recall of Patterns                               | 145 |

| Results Using Second Neuron Circuit                           | 147 |

| Neuron Circuit                                                | 148 |

| Results With New Neuron Circuit                               | 148 |

| Learning and Recall                                           | 148 |

| 8.5 Conclusions                                               | 150 |

| 9 Conclusions and Recommendations                             | 151 |

| Appendix 1 : List of Publications                             | 153 |

| Appendix 2 : Calculation of components for alternative neuron | 154 |

### Introduction

There has been increasing interest in neural networks during the last few years, and it is now one of the fastest growing fields in electronics. Interest in neural networks has waxed several times in the past century and subsequently waned. The present revival is partly owed to the failure of Artificial Intelligence (AI) to accomplish goals set over a decade ago. With no significant progress in rule-based inference systems, research has begun in other areas.

Neural systems are networks of simple computational units (neurons), operating in parallel, that capture some of the computational strengths and functionality of the human nervous system. The functions a synthetic neural network may aspire to mimic, are the ability to consider many solutions simultaneously, an ability to work with corrupted data and a natural fault tolerance. This arises from the parallelism and distributed knowledge representation that gives rise to gentle degradation as faults appear. These functions are attractive for implementation in VLSI and WSI. For example, the natural fault-tolerance could be useful in silicon wafers with imperfect yield, where the network degradation is approximately proportional to the non-functioning silicon area.

The credit for the present surge in implementation should go to Hopfield <sup>1</sup> whose valuable contribution was to communicate neural principles to engineers. Technology has developed to a point where supercomputers can simulate large neural networks quickly and the integrated circuit technology has become small enough to allow many synaptic structures to be integrated on a single chip.

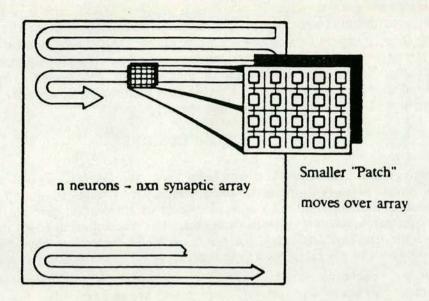

Although the neural function is simple enough, in a totally interconnected nneuron network there are  $n^2$  synapses requiring  $n^2$  multiplications and summations

and a large number of interconnects. The challenge in VLSI is therefore to design a

simple, compact synapse that can be repeated to build a VLSI neural network with

manageable interconnects. In a network with fixed functionality, this is straightforward. If the network is to be able to learn, however, the synaptic weights must be

programmable, and therefore more complicated.

Planar silicon technology is almost certainly not the ultimate medium in which neural networks will find their power fully realised. Three-dimensional biological materials are intrinsically better suited to the essentially three-dimensional form of a neural net, but their usefulness as understandable and predictable "circuit-building" media is a long way off. To delay research into implementation of neural networks until analysis and simulation demonstrate their full power and a better technology emerges would be short-sighted. There is much to learn form LSI/VLSI implementation, and hardware networks developed will be able to make rapid use of developments in network design and learning procedures to solve real problems.

This thesis is based on the research undertaken between February 1986 and September 1988 into the implementation of neural networks that have programmable synaptic units in silicon using CMOS integrated circuits.

The thesis is presented in 4 parts.

- (a) This section provides a background to the research and will be useful to new researchers into neural networks. Chapter 1 is a brief introduction to the biological neuron to introduce the reader to neural terminology. Chapters 2 and 3 give a history of neural networks and show how the models were developed and it identifies all the major workers. Chapter 4 discusses the various neural models, giving worked examples. Finally Chapter 5 gives an introduction to other VLSI implementations of neural networks.

- (b) Chapter 6 presents research into a digital neural machine that uses a reduced precision arithmetic to simplify circuitry. Simulation shows how this system performs compared with simple and more complex neural models. This section also discusses some of the practical implementation problems, such as a limited weights set, and tries to offer solutions.

- (c) Chapters 7 and 8 show how pulse streams offer a novel solution to reducing the complexity of circuits whilst still allowing complex functions. An integrated circuit is presented that performs the communications and processing and shows how this can be incorporated into a system to solve neural network problems.

- (d) Where relevant, conclusions are presented at the end of a chapter and the thesis concludes with Chapter 9 which is a discussion of the work undertaken and presents

Introduction - 3 - Introduction

ideas for further developments in this field of research.

## Chapter 1

#### 1. Introduction to Neurons

Some neural network terminology is derived from biological science. To introduce this terminology to engineers the first chapter discusses the biological neuron. It describes the structure and functions of the neuron and the importance of the myelin sheath. It explains the origin of the electrical potential across the outer membrane and the generation of an action potential which constitutes the nerve impulse that is propagated along the length of the axon in a nerve fibre. The structure and functions of synapses are also described together with some of their special properties which play an important role in the processing of nerve impulses as they pass through the Central Nervous System.

#### 1.1. The Neuron

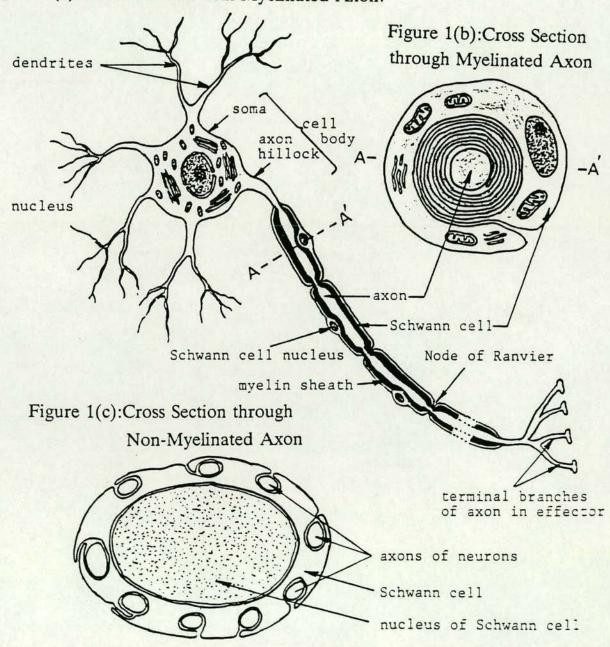

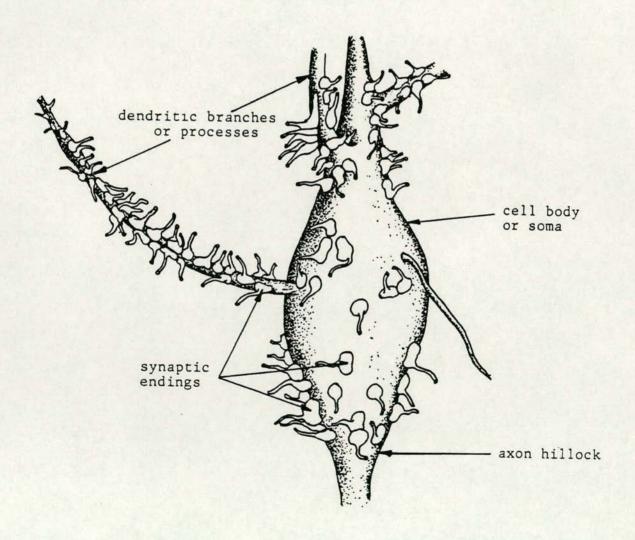

The neuron or nerve cell is the basic functional unit of the human communication system which is composed of about  $3\times10^{10}$  neurons, the majority located in the human brain. Neurons have distinctive shapes, see Figure 1(a), and are unique in the ability of their outer membranes to generate electrical impulses. They posses 3 regions; the dendrites, the cell body and the axon.

**Dendrites** are repeatedly branching extensions of the cell body forming the surface which receives most of the incoming signals.

The Cell body which is spherical or pyramidal, containing the nucleus and organelles involved in the biochemical activities of the cell, including energy production and enzyme synthesis.

The Axon, which extends from the axon hillock, forms a pathway along which output signals pass from the cell body. Axons are longer, thinner and less branched than dendrites and terminate in Synaptic Buttons (or Knobs) or Neuro-Muscular Junctions.

Figure 1(a):Motor Neuron with Myelinated Axon.

#### 1.2. Myelination of Axon

All axons are sheathed by several Schwann Cells, the outer membranes of which may be spirally wrapped around the axon many times forming an insulating Myelin Sheath. Gaps between the Schwann cells where the axon membrane is exposed, are called Nodes of Ranvier and they occur every 1mm or so. Such axons are said to be Myelinated, see Figure 1(b). Sometimes a Schwann cell may be wrapped around the axons of several neurons forming much thinner sheaths, and these axons are said to be Non-Myelinated, see Figure 1(c). Myelinated neurons are only found in vertebrate nervous systems and they transmit impulses much faster than non-myelinated neurons. Myelination conserves the neuron's metabolic energy and increases the speed at which they transmit an impulse.

### 1.3. Resting Potential of the Neuron

Most important to the functioning of a neuron is the electrical potential difference that it maintains across its outer membrane. In all living cells this forms part of the *Electro-Chemical Potential* (ECP) gradients which promote the absorption of negative anions and oppose the absorption of positive cations. The presence of *Ion Pumps* in the outer membrane, which selectively absorb or expell ions, helps to maintain the potential difference. The ECP gradient ensures the absorption of ions needed to meet the nutritional and functional requirements of each cell.

The resting potentials of nerve axons vary between 30mV and 110mV and are much higher than those of other cells. They are produced by the differential distribution of ions between the Axoplasm and the external medium. The axoplasm (inside) has a high concentration of potassium (K<sup>+</sup>) ions and a low concentration of sodium (Na<sup>+</sup>) ions, while the concentrations of these ions are reversed in the external medium. These gradients are maintained by the Active Transport of these ions against their electro-chemical potential gradients by special regions of the axon membrane known as Sodium or Cation Pumps. These pumps remove Na<sup>+</sup> ions from the axon and at the same time absorb K<sup>+</sup> ions, the energy for this process coming from ATP (Adenosine Triphosphate). This movement of ions is opposed by the Passive Diffusion of the same ions down the electro-chemical potential gradients at rates

mainly determined by the permeability of the axon membrane to the ions. Since the  $K^+$  ions have an ionic mobility and membrane permeability 20 times greater than  $Na^+$  ions,  $K^+$  ions are lost from the axon at a greater rate than  $K^+$  ions are gained resulting in a negative charge within the vertebrate axon of about -70mV.

### 1.4. Generation of an Action Potential in Neurons.

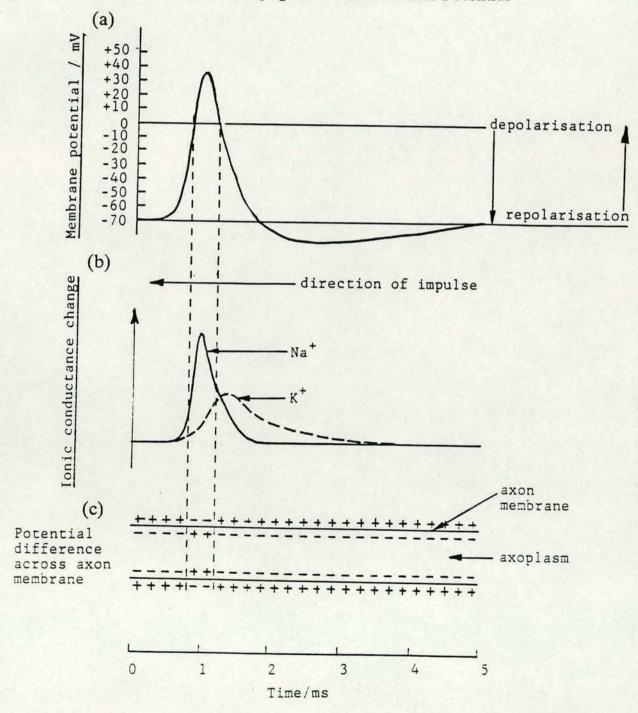

Stimulation of an axon by an electrical impulse changes the electrical potential across the axon membrane from a negative internal value of about -70mV to a positive internal value of about 40mV. This polarity change is called an *Action Potential* (AP) or *Spike* which can be viewed with an oscilloscope, see Figure 2(a). The AP is generated by the sudden and momentary increase in the permeability of the axon membrane to Na<sup>+</sup> ions which enter the axon. The resulting increase in Na<sup>+</sup> ions in the axon changes the internal axon potential to about +40mV and this change in potential is called *Depolarisation* with a maximum value of about 110mV.

After the peak of the AP, about 0.5ms after the initial depolarisation, the permeability of the membrane to Na<sup>+</sup> declines and the permeability to K<sup>+</sup> increases so K<sup>+</sup> diffuse out of the axon, see Figure 2(b). This results in re-polarization of the axon, the internal positive charge being replaced by negative charge, see Figure 2(c).

The initiation of depolarisation when the neuron or a receptor receives a stimulus ≥ the threshold value. The amplitude of the resulting AP, for a given neuron, is constant.

Information is transmitted through the NS as a series of APs or nerve impulses. They pass along the axon as a wave of depolarisation followed by a wave of negativity. The APs are self-generated or propagated along the axon by the effects of the Na<sup>+</sup> entering the axon. This creates an area of positive charge and a flow of current is set up forming a local current between this area and the negatively charged area immediately ahead. The current reduces the membrane potential in the resting region ahead and the depolarization causes an increased permeability to Na<sup>+</sup> ions and the development of an action potential ahead. The process is

Figure 2:Changes in the Potential(mV) and Ionic Conductance during the propagation of an Action Potential

repeated so the APs are propagated along the axon. The AP suffers no loss of potential as each is generated by a local change in the concentration of ions. The nerve impulses thus pass along the axon in one direction, from active to resting regions.

The active region undergoes a *Recovery Phase* during which it cannot respond to a further depolarisation by a change in permeability. This *Absolute Refractory Period* lasts about 1ms and it is followed by a *Relative Refractory Period* lasting 5-10ms during which a much higher intensity stimulus is needed to produce depolarisation.

Neurons are thus specialised cells adapted to respond to stimuli from the internal and external environments by producing a pattern of electrical impulses. To ensure a meaningful response to this information from the receptors, the impulses are carried by Sensory neurons to the Central Nervous System (CNS), a neuron network, where they are processed. The output impulses of the neuron network are relayed by Motor neurons to Effector organs, muscles or glands, producing an appropriate response.

In non-myelinated axons the speed of conduction of an AP depends on the longitudinal resistance of the axoplasm which is in turn related to the diameter of the fibre. The smaller the axon diameter, the greater is the resistance of the axoplasm and therefore the slower is the speed of conduction. A fine axon of about 0.1mm diameter conducts at about 0.5m s<sup>-1</sup>, while a giant axon of about 1mm diameter will conduct at a velocity of about 100m s<sup>-1</sup>.

The presence of a thick myelin sheath around vertebrate axons, produces a low resistance to current flow at the Nodes of Ranvier and a high insulation between. The depolarisation of the axon membrane therefore only occurs at the Nodes of Ranvier and the APs "jump" from node to node increasing the conduction velocity to about 120m s<sup>-1</sup> for quite small diameter neurons. This type of conduction is described as *Saltatory*.

The velocity of conduction is related to temperature and increases with increasing temperature up to 40°C. The impulses have a fixed amplitude so the

information cannot be carried as an amplitude code. Information is carried as a frequency code in which the frequency of the impulses is directly related to the intensity of the stimulus or response required.

#### 1.5. Synapses

Crucial to the integrative functioning of the nervous system is the way in which the neurons inter-connect and the way in which APs are transferred between neurons. Central to this are the *Synapses* which are areas of functional contact, but not physical contact, between the fine terminal branches of the axon of one neuron and the dendrites or cell body of another neuron, for the transfer of information. Brain neurons may receive up to 10 000 synapses which can occupy up to 80% of the neurons surface, the greatest concentration being on the dendrites, see Figure 3.

There are 2 types of synapse, *Electrical* and *Chemical* with similar functions but different structures. The *Neuro-Muscular Junctions* or *End-Plates* of the motor axons terminating on muscle fibres have a similar structure and function to the synapse.

The electrical synapses represent the more primitive condition, being more widespread in *Invertebrates*. The transmission across the electrical synapse occurs as an electric current which on reaching a threshold value will induce an action potential in the axon of the next neuron.

Chemical synapses are more widespread in vertebrates and their more open structure allows current to leak away so not producing an electrical change in the post-synaptic cleft, it is probable however that a small amount of electrical conduction takes place in both directions across these synapses.

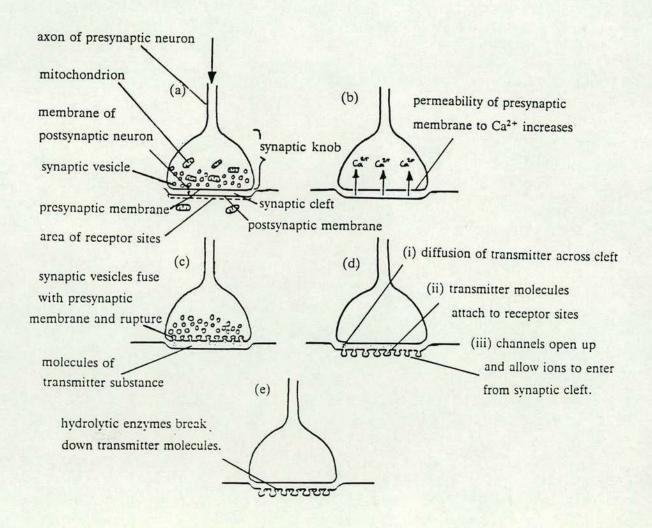

Chemical synapses are more efficient in depolarising the post-synaptic membranes and therefore generating APs in the receiving neurons so speeding up the rate at which information is processed. The chemical synapse is a bulbous expansion of the nerve terminal called a *Synaptic Knob* or *Bouton Terminale* which lies in close proximity to the membrane of the dendrite or cell body of the next neuron. Both the *Pre-Synaptic Membrane* of the synaptic knob and the *Post-Synaptic Membrane* of

Figure 3:Reconstruction of brain neuron showing positions of synapses with other neurons.

the next neuron are thickened and separated by a synaptic cleft 20nm wide. The transmitter substance (TS) is formed in the cell body or the synaptic knob where it is packaged in synaptic vesicles approximately 50nm in diameter, each containing about 300 molecules of TS, and stored pending release. The main TS in vertebrates are Acetylcholine released by Cholinergic neurons and Noradrenaline released by Adrenergic neurons.

The functioning of the synapse is illustrated in Figure 4.

The arrival of an action potential at the synaptic knob depolarises the presynaptic membrane increasing its permeability to Calcium (Ca<sup>2+</sup>) ions which enter the synaptic knob causing the synaptic vesicles to fuse with the presynaptic membrane and release their transmitter substance into the synaptic cleft by exocytosis. The empty vesicles return to the cytoplasm to be refilled. The transmitter substance diffuses across the cleft, imposing a delay of 0.5ms and attaches to a specific receptor site on the post-synaptic membrane allowing the entry of ions which either depolarise or hyperpolarise the post-synaptic membrane depending on the type of synapse. The TS is then quickly removed from the synaptic cleft by reabsorption through the pre-synaptic membrane, diffusion out of the cleft or by hydrolysis. In cholinergic synapses, the enzyme *Cholinesterase* attached to the post-synaptic membrane, hydrolyses acetylcholine to choline which is reabsorbed and recycled in the synaptic knob.

### 1.6. Types of Chemical Synapse and Their Properties.

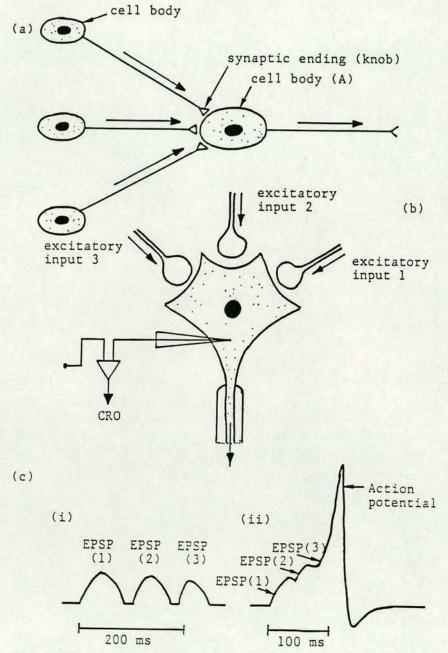

Synapses may be Excitatory or Inhibitory. Activation of an excitatory synapse increases the permeability of the post-synaptic membrane to Na<sup>+</sup> and K<sup>+</sup> ions and results in depolarisation creating an Excitatory Post-Synaptic Potential (EPSP), smaller in amplitude but longer lasting than an action potential AP. A single EPSP resulting possibly from the release of 1 vesicle containing TS is normally unable to produce sufficient depolarisation to initiate an AP in the post-synaptic neuron. The depolarising effect of the EPSP is additive so together several EPSPs may initiate an AP in the neuron, this process being termed Summation. It is termed Spatial summation if the EPSPs are produced simultaneously by different synapses attached to

<sup>(</sup>i) Exocytosis: An active process involving the bulk transport of materials through membranes. In this case vesicles fuse with the membrane releasing the transmitter substance into the synaptic cleft.

Figure 4:Diagrams illustrating the mechanisms involved in chemical transmission at a neuronal synapse, (a) to (e) time sequence.

the same neuron or *Temporal* summation when an intense stimulus causes the release of many synaptic vesicles and the individual EPSPs are close together and summate giving rise to an AP, see Figure 5.

APs can result from repeated stimulation by one of its pre-synaptic neurons or weaker stimulation by several of its pre-synaptic neurons.

Inhibitory synapses release transmitter substances which increase the permeability of post-synaptic membrane to K<sup>+</sup> and Cl<sup>-</sup> ions and the resulting movement of ions increases the polarisation of the membrane causing hyperpolarisation known as *Inhibitory Post-Synaptic Potential* (IPSP) which acts counter to the EPSP making it more difficult to produce an AP, hence it has an inhibitory effect.

At the Neuro-Muscular Junction the synapses are replaced by motor end-plates similar to the synaptic knob and they function in a similar way producing local depolarisation known as End-Plate Potential (EPP) which produces an AP in the muscle fibre which initiates muscle contraction.

### 1.7. Other Properties of Synapses

In addition to the transmission of information from the receptors to the effectors, they possess several other important functional features.

- (a) Unidirectionality: The release of transmitter substances from the presynaptic membrane and the presence of receptor sites on the post-synaptic membrane ensures that nerve impulses only pass in one direction.

- (b) Adaptation: The amount of transmitter substance falls off if the synaptic knob is subjected to constant stimulation because the supply of transmitter substance becomes exhausted. The synapse is thus *Fatigued* and no further impulses can follow the pathway preventing damage by over stimulation.

- (c) Integration: The post-synaptic neuron may receive impulses from excitatory or inhibitory pre-synaptic neurons. As a result of this *Synaptic Convergence* all the pre-synaptic stimuli are summated enabling the integration of stimuli coming from several different sources producing a single response.

- (d) Facilitation: This may occur at some synapses. The stimulus passing

Figure 5:Diagrams illustrating convergent neural pathways and summation of excitatory stimuli

- (i) Delay between EPSPs does not allow threshold to be reached

- (ii) Rapid excitatory stimuli summate to reach threshold and trigger an action potential

through a synapse leaves the synapse more responsive to the next stimulus. This is not electrical summation, but a chemical change in the post-synaptic membrane.

- (e) **Discrimination**: Temporal summation permits the filtering out of weak and unimportant stimuli but changes in the intensity of stimuli, increase the frequency of stimuli which pass across the synapse and these are summated to produce response in the post-synaptic neuron.

- (f) Inhibition: When synaptic knobs from excitatory and inhibitory neurons are in close proximity, the inhibitory synapses reduce the number of synaptic vesicles released inhibiting the response of the synaptic knob. This inhibition may be post or pre-synaptic.

The cell bodies of many neurons, especially in the brain, may be covered with many hundreds of synaptic knobs. Most of the synaptic knobs are in contact with the dendrites. The dendrites however have low excitability and high thresholds while the axon hillocks are highly excitable and have lower thresholds. The cell bodies have intermediate excitability and thresholds.

A large number of inputs both inhibitory and excitatory are collected by the dendrites but due to the low excitability and high threshold (25mV) it requires several similar excitatory inputs to summate to reach the threshold. The axon hillock is the spike or AP initiator because it has the lowest threshold (10.6mV) and highest excitability, so control of this region leads to control of action potentials.

This section of the thesis was written from the Part 1 of Book 10 of the Basic Biology Course entitled Nerves and Muscle and from chapter 16 of Book 2 of Biological Science entitled Systems, Maintenance and Change. Both books are published by Cambridge University Press.

## Chapter 2

### 2. A History of Research into Biological Neural Networks

Neural networks research is interdisciplinary, covering the biological, chemical and mathematical sciences as well as the sociological, physiological and psychological sciences. Research into neural networks, though not in the form we see today, has been going on for some considerable time. In giving a history of the development it is necessary to integrate these disciplinary histories to give a broader understanding of neural networks.

The fundamental difference between a modern computer and a neural network is that a computer stores a piece of information in one location, whereas a neural network distributes the same information in several locations. The former is known as *local representation* and latter as distributed representation.

The functioning of the brain, which is itself a neural network, and in particular the functioning of memory, has intrigued mankind for several millennia. One of the first suggestions to explain memory was by Plato <sup>2</sup>. He suggested an analogy between memory and a block of wax. A ring imprint on the surface of the wax represented a memory. By making more imprints more memories were stored or learnt. This idea can be thought of as being local since the imprints were discrete, each at a separate location in the wax block.

The local theory was enhanced by James Mill in 1773-1836 when he suggested that the human mind concerned itself with the linking together of pieces of sensory experience. Each experience had a unique location and learning was the linking together of these locations.

Until this time no neural structures had been proposed to implement the storage of local memories until Alexander Bain in 1818-1903 stated "for every act of memory, every exercise of bodily attitudes, every habit, recollection, train of ideas, there is a specific grouping or coordination of sensations and movements by virtue of specific growth in the cell junctions" and also "there is no improbability in supposing an independant nervous track for each separate acquisition". This suggestion again

proposed that memories were local in nature, although the idea that growth in cell junctions created new memories began to emerge.

As the brain is likened to modern computers today, in the early part of the twentieth century the brain was likened to a telephone switch board. Thorndike <sup>3</sup>proposed that learning involved the setting up of new connections from input to output lines. He stated "All psychological processes consist of the functioning of native and acquired connections between situations and responses".

Perhaps the most well known of the local theorists was Pavlov <sup>4</sup>. He is best known for his work with dogs, which he conditioned to salivate in response to the stimulus of a ringing bell. He further suggested that memory traces were similar in principle to reflex arcs.

However local theories failed to explain why memories were not lost in local damage to the brain. It was Lashley <sup>5</sup> who found that rats, which after learning mazes and subsequently undergoing brain surgery, suffered brain defects dependant on the amount and not the location of the brain tissue removed. He inferred that all parts of the cerebral cortex play an equal role in the memory process. "The alternative to the theory of the preservation of memories by some local synaptic change is the postulate that the neurons are somehow sensitized to react to patterns or combinations of excitation. It is only by such permutations that the limited number of neurons can produce the variety of functions that they carry out... But speculation about this mechanism without direct evidence is likely to be futile as speculation concerning changes in resistance in the synapse has been ...

The conclusion is justified, I believe, ... that all of the cells of the brain are constantly active and are participating, by a sort of algebraic summation, in every activity. There are no special cells reserved for special memories".

This major piece of experimental evidence divided the scientific community. On one side were the localists, and on the other the doubters and negativists.

Lashley contrived the theory that each learned event was represented by a particular pattern of vibrations in the brain. This attempted to explain the observed data but did not however explain how human memories survive grand mal epileptic attacks, or how brain activity can be severely reduced by cooling or by anaesthesia without serious impairment of memory.

This type of distributed theory and theories similar to it where grouped under the name Gestalt Theories. This explained the former in terms of patterns of excitation. David Willshaw explained the Gestalt theories in his PhD thesis <sup>6</sup> as "Consider how they would explain the perception of a circle. The sensory input is transformed into a pattern of excitation in the brain, modifying its ongoing activity. That the circle has been seen is noted by the pattern of excitation leaving a record of some description in the brain. When the circle comes into the organism's field of view again, the brain recognises that the current pattern of excitation caused by the circle is similar to the pattern which laid down the original trace and the organism remembers that it has seen the circle before".

Roy <sup>7 8</sup> attempted to explain Lashleys findings. He suggested a distributed nerve net with one input and one output channel, made up of a number of identical nerve cell-like units functioning as delay lines. By the mechanism of threshold lowering within the units, the net was able to recall a particular part of a stored signal by using the preceding part as an address.

It was Hebb in 1949 <sup>9</sup> who attempted to reconcile "switchboard" and "field" theories (e.g. Gestalt), by putting forward the idea of modifiable excitatory synapses - that is the excitatory synapse between an axon and a dendrite is facilitated if activity in the axon coincides with depolarisation of the dendrite. As learning proceeds, cells are modified by this means and they form themselves into interacting groups, called assemblies, each capable of supporting patterns of excitation. One nerve cell can belong to more than one assembly and can change allegiance from one assembly to another. Thus one cell can contribute to the storage of more than one message.

Milner <sup>10</sup> extended Hebb's treatment to include inhibitory synapses and both theories were tested by computer simulation by Rochester et al in 1956. Rochester also found that cell assemblies could only be produced in a set of interacting neuron-like elements if both inhibitory and excitatory synapses were present.

Although the preceding history has been about the physiological investigation of memory, the ideas behind Parallel Distributed Processing (PDP) can be seen from other branches of science. Pillsbury 11, in the late nineteenth century was the first to begin the investigations into neural structures. By observing the visual perception of words he investigated the way in which partly obscured letters could be recovered by observing the words containing them. Some of the earliest roots of the PDP approach can also be found in the work of the neurologists, Jackson 12, and Luria 13. Jackson was a forceful and persuasive critic of the simplistic localisationist doctrines of late nineteenth century neurology, and he argued convincingly for distributed, multilevel conceptions of processing systems. Luria, the Russian psychologist and neurologist, put forward the notion of the dynamic functional system. On this view, every behavioural or cognitive process resulted from the coordination of a large number of different components, each roughly localized in different regions of the brain, but all working together in dynamic interaction. At the beginning of the twentieth century a frenchman, Henri Poincare 14, introduced the idea of a "bottom-up" approach to neural networks from primitives, instead of trying to evolve ideas of neural structure from psychological observations.

Although evidence today suggests that in higher mammals memories are of a distributed form there is evidence to suggest that in lower animals memories might be localized. Young <sup>15</sup> <sup>16</sup> suggested that memory of an octopus consists of a number of simple components, each of which records the consequences of stimulation by a particular type of visual or tactile input. There is some evidence today to suggest that both local and distributed processing are integrated together.

<sup>†</sup> Henri Poincare is also known for his work on the planetary three body problem and his insights into special relativity before its formulation by Einstein.

Perhaps the most interesting research has been in the development of a distributed model of human learning and memory. Theorists have shown that sometimes human memory represents information in a general form and at other times in a specific form. Although conventional rule-based systems can implement one of these properties they find it difficult to implement both at the same time. McClelland and Rumelhart have proposed and demonstrated a neural network model of human memory which can capture both properties. Their system used the Delta Rule (see Chapter 4) to store patterns on a highly interconnected network. These patterns were used in the learning phase to alter the interconnection strengths between neurons to encode the patterns onto the network. It was possible to recall patterns by inputing part of the original pattern back into the network. The model was limited due to the fact that it could only learn to respond appropriately to sets of patterns which obeyed the linear predictability constraint. This constraint is when, over an entire set of patterns, the external input to each unit must be predictable from a linear combination of the activations of every other unit. At present they are researching into overcoming this problem by including hidden units within their network.

Rumelhart and McClelland<sup>60</sup> have shown how synthetic modelling can be used as a route to the understanding of human memory. However, the research into biological mechanisms can be used as a guide, or as inspiration for neural modellers. Using biological research Carver Mead has designed and built electronic neural networks with local interconnectivity to perform neural processing. He has used biological research on the neural structure of the retina and cochlea to built an electronic neural network able to perform audio and visual processing. As more information is uncovered about the structure of the human brain this will be included in the design of more complex neural systems.

Other techniques such as Back-Propagation have taken an entirely different route and ignored biological research. These techniques are described in the next section under the general heading mathematical modelling. This research route has some justification for example the use of excitatory and inhibitory synapses on the same neuron, no biological neuron has been found that has both excitatory and inhibitory synapses. Another restriction is that biological networks must grow and therefore the neural structures which can be formed is limited. Neither of these restrictions apply to electronic neural networks. Although electronic neural networks will have many similarities with their biological counterparts it is unlikely that they will be exactly alike.

The third technique used by Grossberg and the author is to compromise between the biological models and the pure mathematical models and use the advantages of both. This work is described later in the thesis.

## Chapter 3

### 3. A History of the Research into Synthetic Neural Networks

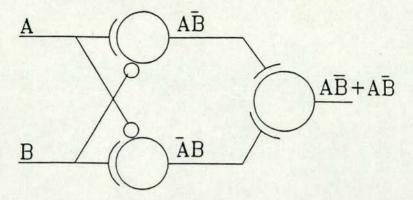

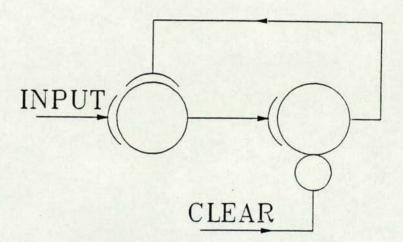

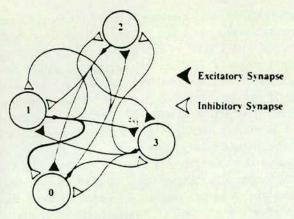

The first major worker to attempt a mathematical description of biological processes was Rashevsky <sup>17</sup>, who in 1938 discussed not only nerve net action but also a wide variety of physiological phenomena from basic cell chemistry to the behaviour of populations of organisms. Although Rashevsky appeared unaware of Boolean algebra in his first edition, in effect he pointed out how certain logical operations might be carried out by simple nerve arrangements. Figure 6 shows that the exclusive-or function is mechanized by an arrangement of excitatory and inhibitory connections. Rashevsky also suggested an explanation of short-term memory by means of recirculating neuron loops, in which an impulse, once initiated, would continue to cycle indefinitely or until terminated by a specific inhibitory impulse. The simplest form of such a loop is illustrated in Figure 7.

In 1943, McCulloch and Pitts <sup>18</sup> published a continuation to Rashevsky's work by applying Boolean algebra to nerve net behaviour. This enabled techniques, normally associated with the design of digital computers, be used with neural networks.

In 1949, Hebb <sup>9</sup> advanced two hypotheses which have become the basis of many nerve net models. Hebb postulated, that the synaptic junction was the site of permanent memory, and that memory of any event was a distributed phenomenon residing in small changes in synapse strength. These changes result from an event impinging upon a large number of synapses. Hebb suggested the following qualitative rule for change of strength of a junction as the result of activity: "When an axon of cell A is near enough to excite a cell B and repeatedly or persistently takes part in firing it, some growth process or metabolic change takes place in one or both such that A's efficiency, as one of the cells firing B, is increased." Hebb's postulates are in agreement with many observable psychological phenomena, especially Pavlov's observations on conditioned reflexes. Although there are several learning rules in use today, the Hebb law is most widely accepted. Hebb also introduced the concept of cell assemblies and discussed the idea of reverberation of activation within neural networks. Hebb's ideas however related to neural functioning rather than

Figure 6: Rashevsky Exclusive OR

Figure 7: Rashevsky Local Memory Loop

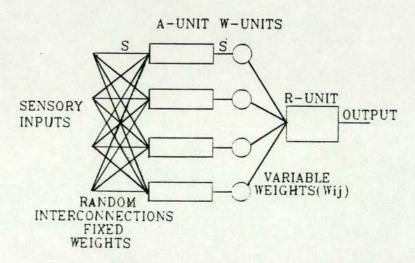

Figure 8: Perceptron Model

distributed processing, and it was Lashley <sup>19</sup> who insisted upon the idea of distributed processing. This was encapsulated in the statement, "there are no special cells reserved for special memories".

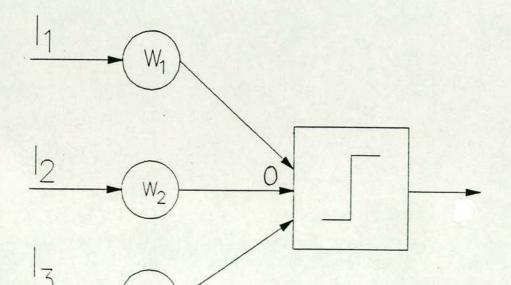

Hebb's ideas remained untested speculations until the early fifties when Dean Edmonds and Marvin Minsky built the first electro/mechanical learning machine 20. In 1958, Rosenblatt reported on the Perceptron model 21. This model attempted to place a complete learning sequence of an artifical nerve-net on a rigorous mathematical basis. Rosenblatt proved that learning of an input-output relationship would occur in a linear summation network under conditions of repeated presentation of input and comparison with desired outputs. The Perceptron model is illustrated in Figure 8. Rosenblatt proposed that synaptic strengths follow certain rules of growth, and that a solution existed for the set of values of the weighting elements required to realize the given output function. Rosenblatt assumed in his model that sensory inputs were mapped, by means of random connections with fixed synaptic strengths, to a set of neurons termed A-units. Since no learning occurs at this stage of the network, input pattern S is transformed to pattern S' which forms the input into the A-units. The transformed inputs are then mapped through variable connections to a set of response-units (R-units) which determine the outputs (only one shown). Binary neuron operation and linear input summation may be formalized as follows:-

$$R_j = 1 \text{ if } \sum_i x_i W_{ij} - \theta_j \ge 0 \tag{1}$$

$$R_j = 0 \text{ if } \sum_i x_i W_{ij} - \theta_j < 0$$

(2)

where  $x_i$  = transformed binary input signal corresponding to activity of unit  $A_i$  (e.g., 0 and 1, or -1 and +1),  $W_{ij}$  = weight of unit connecting  $A_i$  to  $R_j$ , and  $\theta_j$  = threshold of  $R_j$ .

During the learning process<sup>†</sup>, the values stored in the W-units are changed whenever the state  $R_j$  does not correspond to some arbitrary desired response  $D_j$  for

<sup>†</sup> Which is of a Hebbian nature

a given input pattern. This process is termed error-correcting "forced" learning, in that a correction is forced upon the network only if an erroneous response is made. Whenever it is necessary to correct a response, the strengths of all synaptic junctions (W-units) connected to that erroneous output (R-unit), change simultaneously according to a simple rule. Rosenblatt pioneered two techniques of fundamental importance to learning in neural-like networks, namely digital computer simulation and formal mathematical analysis. In 1959, Rosenblatt claimed that because of their statistical properties perceptrons offered things which computers could not do. Unfortunately this irritated Minsky et al. who claimed that he was exaggerating the importance of the perceptron. However Rosenblatt's results stimulated research into the perceptron, until Minsky and Papert <sup>22</sup>, published a book entitled "Perceptrons". The central theme of this work was that parallel recognizing elements, such as perceptrons, are beset by the same problems of scale as serial pattern recognizers. The book had a very dampening effect on the study of neuron-like networks as computational devices for the following decade.

By the late 1960's and early 1970's, three main personalities began to emerge. The best known, and perhaps the most controversial of these researchers is Stephen Grossberg. He bases most of his work on observations of psychological events. His mathematical analysis of the properties of neural networks have led him to many insights. He deserves credit for seeing the relevance of neurally inspired mechanisms in many areas of perception and memory <sup>23</sup>. Grossberg <sup>24</sup>, was also one of the first to analyse mechanisms of competitive learning.

The second of the personalities was Anderson. His work differed from Grossberg's by insisting upon distributed representation, and in showing the relevance of neurally inspired models for theories of concept learning<sup>25</sup>, 26. Anderson's work also played a crucial role in the formulation of the Cascade model <sup>27</sup>, a move from serial processing towards Parallel Distributed Processing (PDP).

The last was a group led by Longuet-Higgins from Edinburgh University. Their main research was into distributed memory models. In particular, David Willshaw, provided some very elegant mathematical analysis of the properties of various distributed representation schemes <sup>28</sup>.

Other researchers working on related topics at this time were, Fukushima<sup>29</sup>, researching into multi-layered neural networks, Kohonen on using neural networks as associative memories <sup>30</sup>, Amari produced a mathematical approach to neural systems <sup>31</sup>, von der Malsberg <sup>32</sup>, and Munro <sup>33</sup>, produced theories of the self-organization of neurons and the development of neural activity.

By the mid 1970's parallel processing enjoyed a renaissance in computational circles and many different models of neural systems began to emerge. Marr and Poggio introduced a model to explain depth perception <sup>34</sup>, and a model of speech called *HEARSAY*. *HEARSAY*, although demanding in computational time, inspired an interactive model of reading <sup>35</sup>, and the interactive activation model for word recognition <sup>36</sup>.

Many new concepts were introduced in the 1980's and saw the first electronic implementations of neural networks. A new term *connectionism* was used by Feldman and Ballard <sup>37</sup> when they established the computational principles of their PDP approach. In connectionism the computations performed by a processing system are controlled by the connections among a large number of simple processing units. The processing units update the strength of the output signal on the basis of signals they receive from other processing units. The capabilities of the system are determined by the interconnections amongst the units. They also stressed the biological implausibility of most of the prevailing computational models in Artifical Intelligence (AI). Hofstander <sup>38</sup> <sup>39</sup> pointed out the importance of delving into the microstructure of neural systems to gain insight into their function. Sutton and Barto <sup>40</sup> analysed the "Delta Rule" and illustrated the power of the rule to account for some properties of classical conditioning.

The recent explosion of research into neural networks can be attributed partly to John Hopfield <sup>1</sup>. His contribution was to visualise a neural network as an energy landscape model which seeks to find a minimum energy state and to make the analogy with spin glasses. This idea played a prominent role in the development of the Boltzmann machine. The Boltzmann machine is composed of primitive computing elements called units that are connected to each other by bidirectional links. A unit is always in one of two states, on or off, and it adopts these states as a probabilistic

function of the states of its neighbouring units and the weights on its links to them. The weights can take on real values of either sign. A unit being on or off is taken to mean that the system currently accepts or rejects some experimental hypotheses about the domain. The weight on a link represents a weak pairwise constraint between two hypotheses. A positive weight indicates that the two hypotheses about the domain tend to support one another; if one is currently accepted, accepting the other should be more likely. Conversely, a negative weight suggests, other things being equal, that the two hypotheses should not both be accepted. Link weights are symmetric, having the same strength in both directions. The resulting structure is related to the system described by Hopfield 1, and as in his system, each global state of the network can be assigned a single number called the "energy" of that state. With the correct assumptions, the individual units can be made to act so as to minimize the global energy. If some of the units are externally forced or "clamped" into particular states to represent a particular input, the system will then find the minimum energy configuration that is compatible with that input. The energy of a configuration can be interpreted as the extent to which that combination of hypotheses violates the constraints implicit in the problem domain, so in minimizing energy, the system evolves towards "interpretations" of that input that increasingly satisfy the constraints of the problem domain. This work has promoted the implementation of neural networks into silicon.

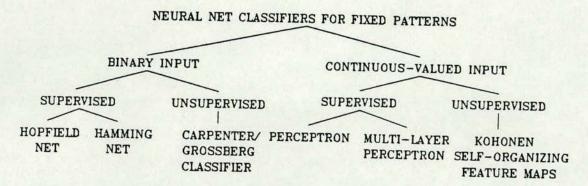

This brings neural research up to the present time. Present research is concentrated in six major models. The models may use binary inputs or continuous valued inputs and they may have supervised or unsupervised learning. This is illustrated in Figure 9.

The Hopfield network, based on gradient descent, can be used as a content addressable memory. An initial set of weights is computed from the patterns to be learnt. A pattern is recalled by firstly initiallising the network to an input pattern and allowing the network to iterate until it achieves a stable state. This stable state should be one of the original patterns used, but it will be the pattern closest to the input pattern in the computation of the weights set. The algorithm used to produce the weight set unfortunately also forms intermediate stable patterns which are cross-

Figure 9: Present Neural Research

# OUTPUT (Valid After MAXNET Converges)

INPUT (Applied At Time Zero)

Figure 10: Hamming Network

products of the original patterns. Hence recall accuracy declines as the number of patterns learnt is increased.

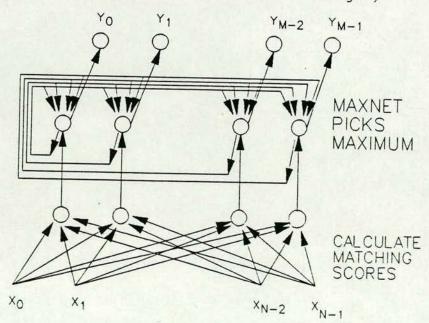

The Hamming network differs from the Hopfield network in trying to find the node with the smallest Hamming distance from the input pattern, whereas the Hopfield network is using an energy gradient descent method to obtain the closest pattern. Figure 10 shows a diagram of a Hamming network. The first layer of neural elements calculates an activation value for each node. This is projected into the layer above which selects the highest activation by using a lateral inhibition network ie. the node with the highest activation value over-rides all the other nodes which are switched off so the end result is that only one output node is active.

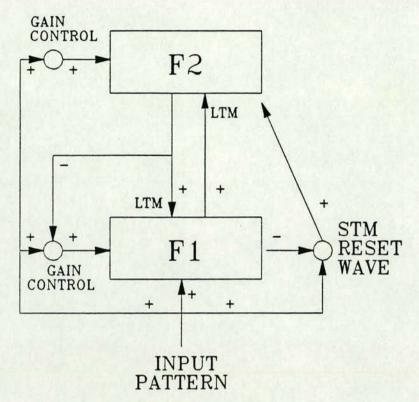

The Carpenter/Grossberg Classifier has similar principles to the Hamming network. The classifier uses a matching score technique to select categories. When the Grossberg net is presented with a new pattern which cannot be classified, it is able to encode this new pattern onto a new node, hence creating a new category. Figure 11 shows a Carpenter/Grossberg classifier network. This Classifier has unsupervised learning and consists of two networks, F1 and F2. Inputs into the Classifier enter the F1 network. The F1 network projects this input pattern onto F2, Like a Hamming net F2 computes a best score and using lateral inhibition selects the strongest activity. The Grossberg net differs from the Hamming net in having connections running from the F2 (scoring/classifier) network back into the F1 (input) network. A separate node not in networks F1 and F2 detects a node in F2 having "won", and sends an inhibitory signal to all the nodes in F1, implying that a category has been selected. There are three stimuli upon nodes in F1, firstly the inputs into the Classifier, secondly the pattern being projected down from "winning" node in F2 and finally the inhibitory category select signal. All the F1 nodes with active inputs from the input pattern and the F2 network remain "on". A separate vigilance node takes output pattern from the F1 network and the input pattern and computes how close the input pattern is to the pattern being projected down from F2. If the Hamming distance is not within an accepted limit then the vigilance node sends a global reset wave to the F2 network. This has the effect of inhibiting the "winning" node in F2 for a period of time, without affecting any other nodes. Another node representing

Figure 11: Grossberg Model

Figure 12: Multi-Layer Perceptron

a different category can then be selected while the first category node is being held "off". A short time later the first category node is released and the system continues. Modification of the pattern of weights or "learning" is continuous and unsupervised but it is slow compared to the overall functioning of the system.

The fourth network is the Perceptron network which has been discussed previously.

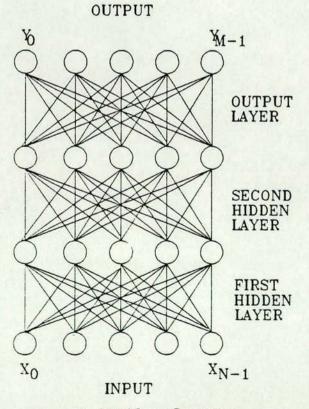

A development of the Perceptron network is the multi-layer Perceptron network, which is shown in Figure 12. A recent development for this type of network is the back-propagation training algorithm <sup>41</sup>. The input pattern is presented to the first layer of the network. The second and output layers go into the appropriate states based on these inputs. It is important to note that these nodes are not binary, they are continuously valued. Output and error values are produced by each output node. The weights from the second to the output layer are adapted to take account from the error values. The weights from the first layer to the second layer are also modified, as are the weights from the input to the first layer. This process is repeated until all the input and desired output patterns are learnt. These networks have been shown to be able to generalise information <sup>41</sup>, and are used to a large extent in encoding problems.

Kohonen's Self-Organizing Feature Maps differ from Grossberg networks in that they are feed-forward networks. The output network uses parallel inhibition to classify input patterns onto groups of output nodes. Kohonen noticed that neural structures in the interior of the brain often reflected physical characteristics of the external stimulus being sensed. This is exemplified in the vision system, where retinal cells have a corresponding one to one mapping to neurons in the interior of the brain. The auditory pathway also shows similar anatomical relationships.

I wish to acknowledge the use of diagrams from two sources which have been included in chapters 2 and 3. Figures 8 to 10 and figure 12 were taken from "An introduction to computing with neural nets" by Lippman<sup>42</sup>. Figure 11 was taken from "A massively parallel architecture for a self-organising neural pattern recognition machine" by Grossberg<sup>43</sup>.

The two preceding chapters have described the general development of neural research. The following chapters will describe attempts to implement neural models in silicon. In particular, it presents work undertaken at Edinburgh University, by the author, who has developed several novel techniques.

## Chapter 4

### 4. Neural Models and Learning Recipes

This chapter introduces several models which have been used to implement neural networks. Each model is illustrated by an example.

Most, if not all, neural network learning rules are based around the concept advanced by Hebb in 1949<sup>9</sup>. In this he stated that "When an axon of cell A is near enough to excite a cell B and repeatedly or persistently takes part in firing it, some growth process or metabolic change takes place in one or both, such that A's efficiency, as one of the cells firing B, is increased".

#### 4.1. The Perceptron Model

When in 1958, Rosenblatt reported his work on the Perceptron<sup>44</sup>, a binary neuron, he introduced the first neural network learning law. Table 1 shows one of the simplest rules. The rule takes the general form,

$$\Delta W_{ij} = \eta (D_j - R_j) x_i \tag{3}$$

In this  $D_j$  is the desired output,  $R_j$  is the output of neuron j after being transformed,  $x_i$  is the transformed binary input signal corresponding to activity of neuron i, and  $\Delta W_{ij}$  is the amount by which the weight is changed. If we assume that  $x_i$  is cell A and  $D_j - R_j$  corresponds to cell B then when the product is positive the weight is increased, and when negative decreased. Since the Perceptron is a binary neuron,  $D_j - R_j$  is either 1 or 0. When the output of the neuron differs from that of the target neuron, the weights are changed, but if they are correct they are not changed. By repeating the process of stepping the network through time, the network can be made to converge on the correct pattern. This work was formalized qualitatively by means of digital computer simulation by Farley and Clark.

| Sy    | maptic  | Weigh | t Logic         |

|-------|---------|-------|-----------------|

| $x_i$ | $D_{i}$ | $R_i$ | $\Delta W_{ii}$ |

| -1    | 0       | 0     | 0               |

| 4)    | 1       | 1     | 0               |

| 1     | 0       | 0     | 0               |

| 1     | 1       | 1     | 0               |

| -1    | 0       | 1     | $a_1$           |

| 4     | 1       | 0     | a <sub>2</sub>  |

| 1     | 0       | 1     | a <sub>3</sub>  |

| 1     | 1       | 0     | a <sub>4</sub>  |

Table 1.

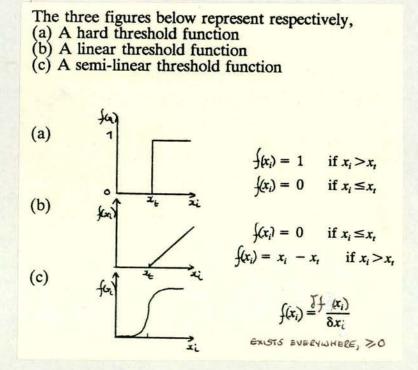

An example of a Perceptron learning system is now given. The activation function of a Perceptron is given in equation 4.

$$O_{j} = \sum_{i=1}^{N} x_{i} W_{ij} \quad \begin{cases} 1 & \text{if } O_{j} > \theta \\ 0 & \text{if } O_{j} \leq \theta \end{cases}$$

(4)

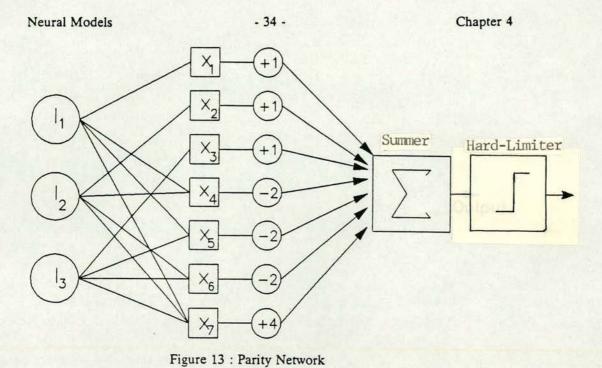

In these equations  $O_j$  is the unnormalised output of the Perceptron, and theta is a threshold function. Figure 13 shows an example of such a system.  $x_i$  is a function of the inputs  $I_i$ , in this particular case it is an AND function. It is important to note that it is an AND function of the inputs to a particular  $x_i$ , for example,  $x_7$  is an AND function of  $I_1, I_2$  and  $I_3$ , whereas  $x_6$  is an AND function of  $I_2$  and  $I_3$ . With  $\theta = 0$  the results for the system are given in the Table 2 below.

|       | Results |       |       |       |       |    |    |    |    |     |        |

|-------|---------|-------|-------|-------|-------|----|----|----|----|-----|--------|

| $I_1$ | $I_2$   | $I_3$ | $x_1$ | $x_2$ | $x_3$ | x4 | X5 | x6 | x7 | Sum | Output |

| 0     | 0       | 0     | 0     | 0     | 0     | 0  | 0  | 0  | 0  | 0   | 0      |

| 0     | 0       | 1     | 0     | 0     | 1     | 0  | 0  | 0  | 0  | 1   | 1      |

| 0     | 1       | 0     | 0     | 1     | 0     | 0  | 0  | 0  | 0  | 1   | 1      |

| 0     | 1       | 1     | 0     | 1     | 1     | 0  | 0  | 1  | 0  | 0   | 0      |

| 1     | 0       | 0     | 1     | 0     | 0     | 0  | 0  | 0  | 0  | 1   | 1      |

| 1     | 0       | 1     | 1     | 0     | 1     | 0  | 1  | 0  | 0  | 0   | 0      |

| 1     | 1       | 0     | 1     | 1     | 0     | 1  | 0  | 0  | 0  | 0   | 0      |

| 1     | 1       | 1     | 1     | 1     | 1     | 1  | 1  | 1  | 1  | 1   | 1      |

Table 2.

The results show that the system is a parity generator.

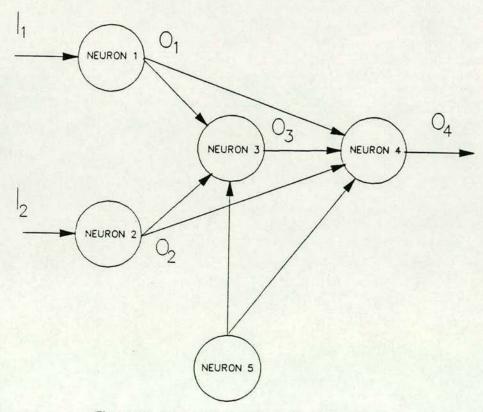

Figure 14: Network using Standard Delta Rule

#### 4.2. Widrow and Hoff Model Standard Delta Rule.

The Perceptron model was succeeded by the Standard Delta Rule developed by Widrow and Hoff in  $1960^{45}$

. Widrow and Hoff considered the learning process from the point of view of minimizing the mean-square-error between the analog sum and the desired output over a set of patterns. The rule for changing the weights following the presentation of input/output pair q is given by

$$\Delta_q W_{ji} = \eta (t_{qj} - o_{qj}) i_{qi}$$

(5)

which is almost identical to that used by Rosenblatt. The activation rule takes the form,

$$o_j = \sum_{i=1}^N i_i W_{ij} - \theta \tag{6}$$

$o_j$  being the output,  $i_i$  the inputs,  $W_{ij}$  the weight between neuron i and neuron j and  $\theta$  is a threshold.

The Standard Delta Rule is formulated for linear neurons, and is only applicable to feed-forward networks without hidden units. A linear function is one in which the output is directly proportional to the sum of the weighted input signals. This rule is similar to Rosenblatt's rule. An error signal is produced at the output neuron, and this is used with the input neuron signal to produce, in accordance with Hebb's law, an update to the weights.

Figure 14-shows an example of this system. The system is a single neuron with three external inputs,  $I_1$ ,  $I_2$  and  $I_3$ . Examination of the diagram shows a close similarity with the Perceptron, the difference being that  $x_i$  in the Perceptron model is limited to a function of a single variable, in this case  $I_i$ .

|       |       |       |      |   |       | Result       | S            |              |       |       |       |

|-------|-------|-------|------|---|-------|--------------|--------------|--------------|-------|-------|-------|

| $I_1$ | $I_2$ | $I_3$ | 0    | t | t-o   | $\Delta W_1$ | $\Delta W_2$ | $\Delta W_3$ | $W_1$ | $W_2$ | $W_3$ |

| 1     | 1     | 1     | 0.00 | 1 | 1.00  | 0.10         | 0.10         | 0.10         | 0.10  | 0.10  | 0.10  |

| 1     | 1     | 1     | 0.30 | 1 | 0.70  | 0.07         | 0.07         | 0.07         | 0.17  | 0.17  | 0.17  |

| 1     | 1     | 1     | 0.51 | 1 | 0.49  | 0.05         | 0.05         | 0.05         | 0.22  | 0.22  | 0.22  |

| 1     | 1     | 1     | 0.66 | 1 | 0.34  | 0.03         | 0.03         | 0.03         | 0.25  | 0.25  | 0.25  |

| 1     | 1     | 1     | 0.76 | 1 | 0.24  | 0.02         | 0.02         | 0.02         | 0.27  | 0.27  | 0.27  |

| 1     | 1     | 1     | 0.83 | 1 | 0.17  | 0.02         | 0.02         | 0.02         | 0.29  | 0.29  | 0.29  |

| 1     | 1     | 1     | 0.88 | 1 | 0.12  | 0.01         | 0.01         | 0.01         | 0.30  | 0.30  | 0.30  |

| 1     | 1     | 1     | 0.91 | 1 | 0.08  | 0.01         | 0.01         | 0.01         | 0.31  | 0.31  | 0.31  |

| 1     | 1     | 1     | 0.94 | 1 | 0.06  | 0.01         | 0.01         | 0.01         | 0.32  | 0.32  | 0.32  |

| 1     | 1     | 1     | 0.96 | - |       |              |              |              |       |       |       |

| 1     | 1     | 0     | 0.64 | 0 | -0.64 | -0.06        | -0.06        | 0.00         | 0.26  | 0.26  | 0.32  |

| 1     | 1     | 0     | 0.51 | 0 | -0.51 | -0.05        | -0.05        | 0.00         | 0.21  | 0.21  | 0.32  |

| 1     | 1     | 0     | 0.41 | 0 | -0.41 | -0.04        | -0.04        | 0.00         | 0.16  | 0.16  | 0.32  |

| 1     | 1     | 0     | 0.33 | 0 | -0.33 | -0.03        | -0.03        | 0.00         | 0.13  | 0.13  | 0.32  |

| 1     | 1     | 0     | 0.26 | 0 | -0.26 | -0.02        | -0.02        | 0.00         | 0.10  | 0.10  | 0.32  |

| 1     | 1     | 0     | 0.21 | 0 | -0.21 | -0.02        | -0.02        | 0.00         | 0.08  | 0.08  | 0.32  |

| 1     | 1     | 0     | 0.17 | 0 | -0.17 | -0.02        | -0.02        | 0.00         | 0.07  | 0.07  | 0.32  |

| 1     | 1     | 0     | 0.13 | 0 | -0.13 | -0.01        | -0.01        | 0.00         | 0.05  | 0.05  | 0.32  |

| 1     | 1     | 0     | 0.11 | 0 | -0.11 | -0.01        | -0.01        | 0.00         | 0.04  | 0.04  | 0.32  |

| 1     | 1     | 0     | 0.08 | 0 | -0.08 | -0.01        | -0.01        | 0.00         | 0.03  | 0.03  | 0.32  |

| 1     | 1     | 0     | 0.06 | 0 | -0.06 | -0.01        | -0.01        | 0.00         | 0.02  | 0.02  | 0.32  |

| 1     | 1     | 0     | 0.04 | - |       |              |              |              |       |       |       |

Table 3

To clarify the operation of the Widrow-Hoff model, an example is now given to illustrate it. Initially  $\eta = 0.1, \theta = 0$  and all weights are set to zero. On presentation of the inputs  $(I_i)$  the output o is evaluated (see equation 6). This is compared to a target value t and  $\Delta W_i$  is calculated (see equation 5) for each weight. A new output is calculated with the adjusted weights and this is compared again with the target value. This process is repeated until the desired output is reached. Although the target value may be 1, it can be seen from the results in Table 3 that it can take the system many iterations to reach this value. Hence, a result slightly below the target value is taken as the correct result (say 0.95). By increasing the value of  $\eta$  the system can be made to converge faster.

#### 4.3. Hopfield Model

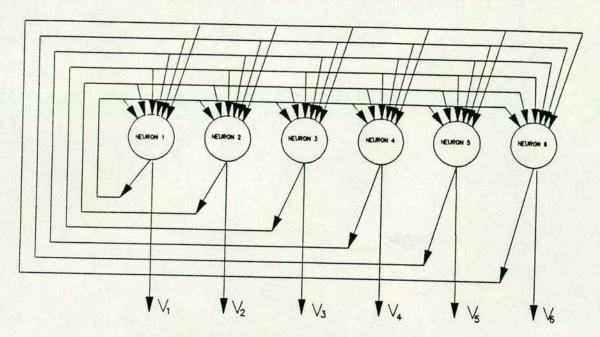

Another widely used learning rule was developed by Hopfield in the late seventies<sup>1</sup>. The Hopfield model cannot use hidden units and it is mainly applied to content addressable memories and optimisation problems. Hopfield networks are

single layer and symmetrical with high interconnectivity between neurons. The neuron activation function is similar to that of a Perceptron. The activation function of this system takes the form,

$$V_{j} = \sum_{i=1}^{N} V_{i} W_{ij} \begin{cases} 1 & \text{if } V_{j} > U_{j} \\ 0 & \text{if } V_{j} \leq U_{j} \end{cases} \quad \text{where } \bigcup_{j} = \sum_{i=1}^{N} \bigvee_{i} \bigcup_{i \in I} (7)$$

Unlike the previous rules no training is required. Using equation 8,

$$W_{ij} = \sum_{r=1}^{p} (2V_i^{(r)} - 1)(2V_j^{(r)} - 1); \quad \text{if } i = j \quad W_{ij} = 0$$

(8)

it is possible to calculate a set of initial weights across a set of r patterns. In the Hopfield model,  $V_i$  and  $V_j$  are output states, however since the neurons in each layer are totally interconnected,  $V_i$  is the input to  $V_j$  and vice-versa. The weight is computed by comparing every neuron output within the network with every other neuron output. If the neuron outputs are the same (ie both "on" or both "off"), the weights between then are increased so that they reinforce each other, otherwise they are decreased.† This process is repeated for every pattern, and the results for a particular weight are added together to get a final weight. By initialising the network to an arbitrary pattern and iterating, the network can be used to find the closest minima.

The following example illustrates the model. The network functions as a content addressable memory (CAM). Figure 15 shows 6 totally interconnected neurons. The three vectors to be stored are 110000, 001100 and 000011. Taking the calculation of  $W_{12}$  as an example

$$W_{12} = (2V_1^{(1)} - 1)(2V_2^{(1)} - 1) + (2V_1^{(2)} - 1)(2V_2^{(2)} - 1) + (2V_1^{(3)} - 1)(2V_2^{(3)} - 1)$$

$$W_{12} = (2.1 - 1)(2.1 - 1) + (2.0 - 1)(2.0 - 1) + (2.0 - 1)(2.0 - 1)$$

$$W_{12} = (1)(1) + (-1)(-1) + (-1)(-1)$$

$$W_{12} = 3$$

<sup>†</sup> The process is not strictly Hebbian, since a true Hebbian function would only increase the weight if the input and output neuron were both active. ie both "on".

Figure 15: 6 Neuron Hopfield Network

Figure 16: Network using Generalised Delta Rule

Neural Models - 39 - Chapter 4

By repeating the calculation for all weights, the weights array is formed.

$$\begin{bmatrix} 0 & 3 & -1 & -1 & -1 & -1 \\ 3 & 0 & -1 & -1 & -1 & -1 \\ -1 & -1 & 0 & 3 & -1 & -1 \\ -1 & -1 & 3 & 0 & -1 & -1 \\ -1 & -1 & -1 & -1 & 0 & 3 \\ -1 & -1 & -1 & -1 & 3 & 0 \end{bmatrix}$$

Using the first learnt vector as the initial states of the neurons.

$$V_1 = 1 \;,\, V_2 = 1 \;,\, V_3 = 0 \;,\, V_4 = 0 \;,\, V_5 = 0 \;,\, V_6 = 0$$

Using equation 7 the output vector after a single iteration is calculated as follows,

$$V_1 = V_1 W_{11} + V_2 W_{21} + V_2 W_{31} + V_3 W_{31} + V_4 W_{41} + V_5 W_{51} + V_6 W_{61}$$

$$V_1 = 1.0 + 1.3 + 0. -1 + 0. -1 + 0. -1$$

$$V_1 = 3$$

Assuming that  $V_i = 0$  for all i then after normalisation  $V_1 = 1$ . After calculation of all outputs,  $V_2 = 1$ ,  $V_3 = 0$ ,  $V_4 = 0$ ,  $V_5 = 0$  and  $V_6 = 0$ . If the vector has been correctly learnt the neuron values before and after will be the same. The results of several input vectors are shown below.

|     | Input  |   | Output |                |

|-----|--------|---|--------|----------------|

| (a) | 110000 | + | 110000 | learnt vector  |

| (b) | 001100 | - | 001100 | learnt vector  |

| (c) | 000011 | - | 000011 | learnt vector  |

| (d) | 110010 | - | 110001 | random pattern |

| (e) | 110100 | - | 111000 | random pattern |

| (f) | 110110 | - | 110000 | random pattern |

These results show that the learnt vectors have been stored correctly (see a-e). The results also indicate that if a start vector is chosen at random, it sometimes will fail to iterate to one of the stored vectors (see d-f). The learning recipe produces "cross-products" of the learnt states, which are commonly referred to as *local minima*. The number of local minima increase with the number of vectors learned. This property makes the learning algorithm unsuitable for a CAM, because all

possible input patterns should result in one of the learnt vectors. The number of vectors which can be stored correctly on a given number of neurons, before the learning recipe starts to fail, is limited.

#### 4.4. Wallace - Hopfield Model

As the number of patterns increases, the Hopfield model has increasing difficulty in storing the patterns perfectly. To improve the information storage of Hopfield networks, Wallace <sup>46</sup> improved the model by including a training prescription. The formula used is

$$\Delta W_{ij} = \sum_{r=1}^{N} (2V_i^{(r)} - 1)(2V_j^{(r)} - 1)(e_i^{(r)} + e_j^{(r)})$$

(9)

As mentioned before the input vector is the target. The network is set to the initial vector, and then released to iterate once. The resultant vector is then compared with the initial vector to ascertain which neurons have changed. If a neuron changes an appropriate error bit/is set to 1, if it remains the same, the error bit is set to 0. Taking two nodes as an example, if they are initially the same and after one iteration one node changes, then the weight between them is increased. This increases the effect of one node on the other. If both are incorrect then the weight is increased by a greater amount. Conversely, if both nodes are initially different then the weight between the nodes is decreased.

Attempting the same problem as used previously in the Hopfield example, there are two starting points. Either initially setting the weights to zero, or using the Hopfield learning recipe to calculate an initial set of weights. Assume that the weights are all initially zero. By setting the initial states of the neurons to the vectors to be learnt and iterating once, a new set of vectors can be calculated.

| -            |    | 0.9 |     |

|--------------|----|-----|-----|

| v            | OC |     | lts |

| $\mathbf{r}$ |    | ш   | 118 |

|    | Input  |   | Output |               |

|----|--------|---|--------|---------------|

| a) | 110000 | - | 000000 | learnt vector |

| b) | 001100 | - | 000000 | learnt vector |

| c) | 000011 | - | 000000 | learnt vector |

From a only bits 1 and 2 change, therefore the error bit array for vector  $e^{(1)}$  is 110000. Repeating for all patterns produces,

$$\begin{bmatrix} 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 \end{bmatrix}$$

Using equation 9 a new weights array is calculated. Taking  $W_{12}$  as an example,

$$\begin{split} W_{12} &= (2V_1^{(1)} - 1)(2V_2^{(1)} - 1)(e_1^{(1)} + e_2^{(1)}) \\ &+ (2V_1^{(2)} - 1)(2V_2^{(2)} - 1)(e_1^{(2)} + e_2^{(2)}) \\ &+ (2V_1^{(3)} - 1)(2V_2^{(3)} - 1)(e_1^{(3)} + e_2^{(3)}) \\ W_{12} &= (2.1 - 1)(2.1 - 1)(1 + 1) + (2.0 - 1)(2.0 - 1)(0 + 0) + (2.0 - 1)(2.0 - 1)(0 + 0) \\ W_{12} &= (2 - 1)(2 - 1)(2) = 2 \end{split}$$

Repeating for all weights gives an updated weight array,

$$\begin{bmatrix} 0 & 2 & -2 & -2 & -2 & -2 \\ 2 & 0 & -2 & -2 & -2 & -2 \\ -2 & -2 & 0 & 2 & -2 & -2 \\ -2 & -2 & 2 & 0 & -2 & -2 \\ -2 & -2 & -2 & -2 & 0 & 2 \\ -2 & -2 & -2 & -2 & 2 & 0 \end{bmatrix}$$

Using the updated weights array the process is repeated giving the results

## Results

|     | Input  |   | Output |               |

|-----|--------|---|--------|---------------|

| (a) | 110000 | - | 110000 | learnt vector |

| (b) | 001100 | - | 001100 | learnt vector |

| (c) | 000011 | - | 000011 | learnt vector |

Thus all vectors have been stored correctly. If errors remain after the first iteration the process is repeated until there are no errors.

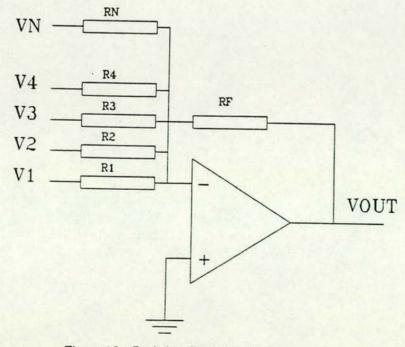

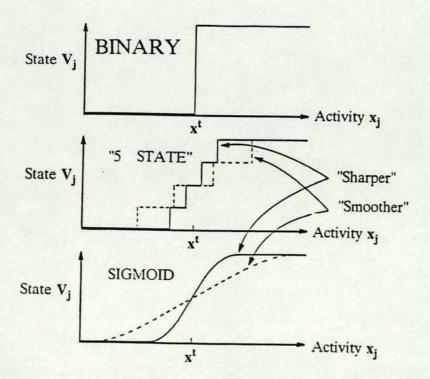

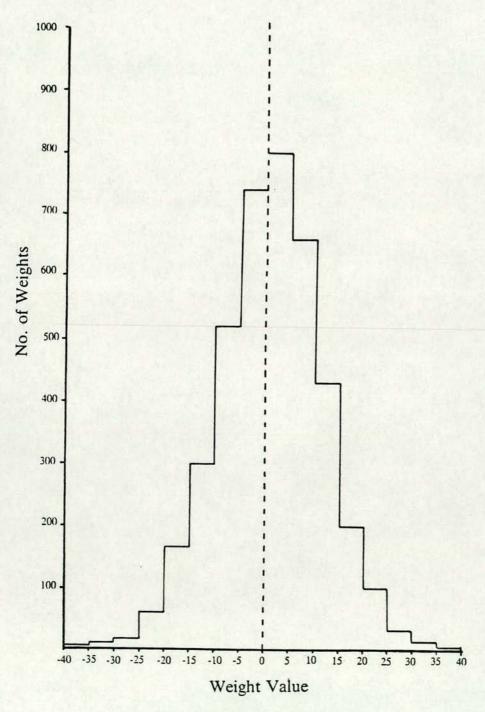

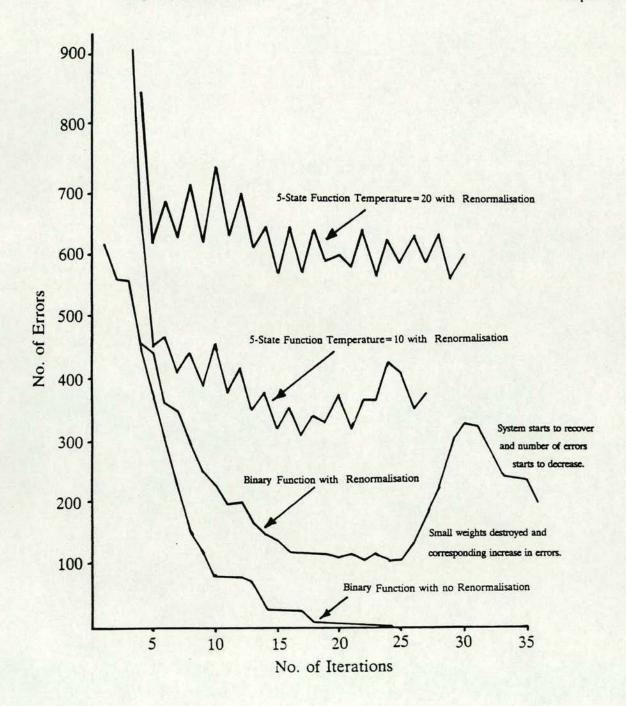

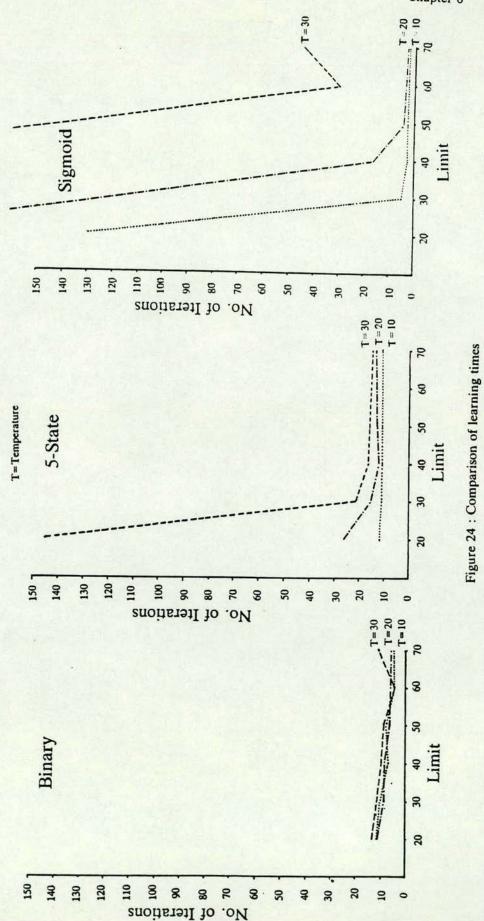

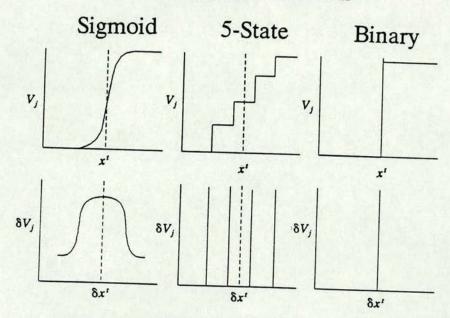

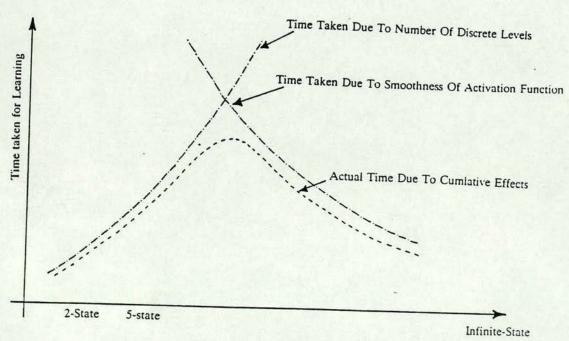

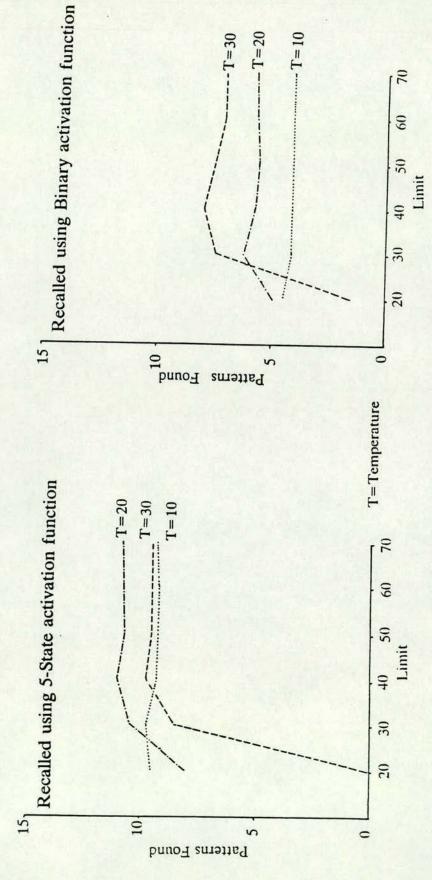

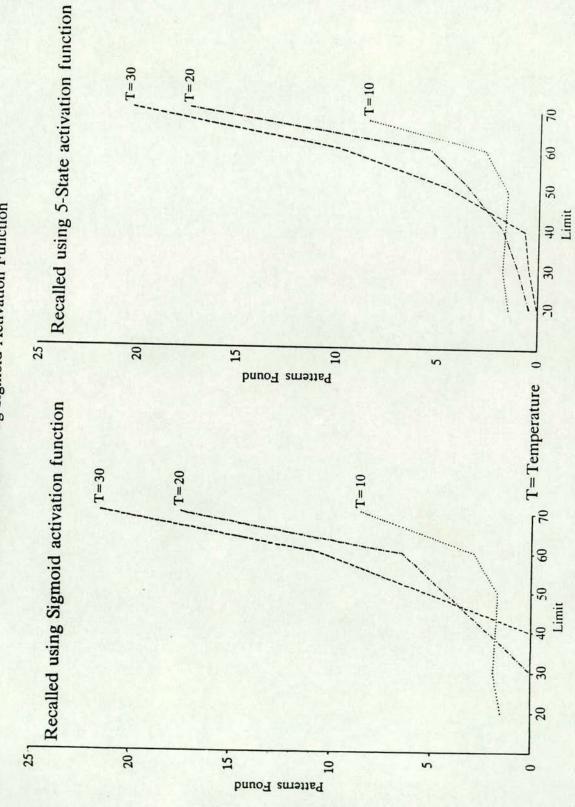

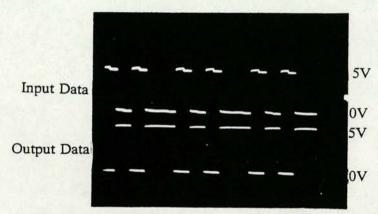

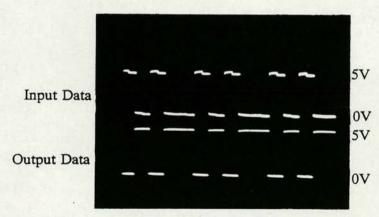

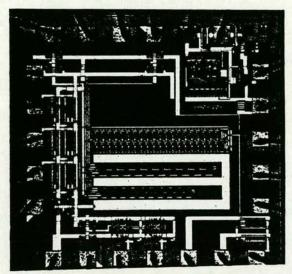

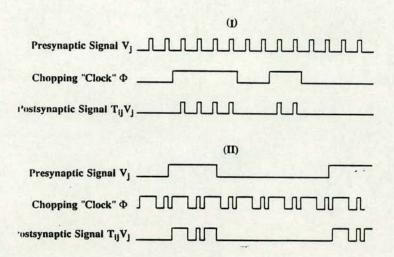

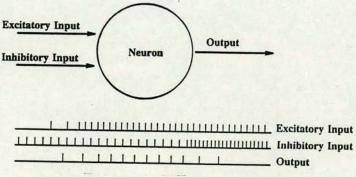

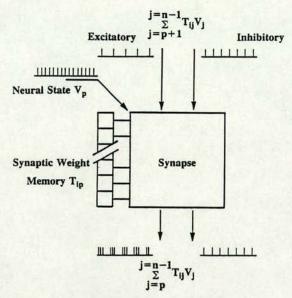

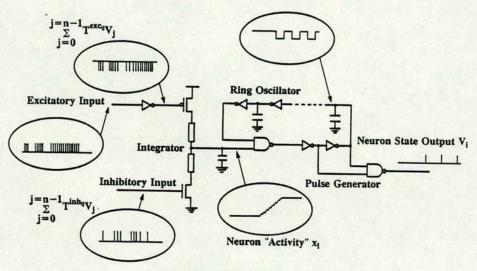

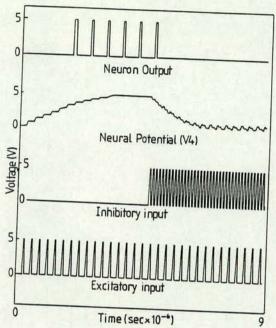

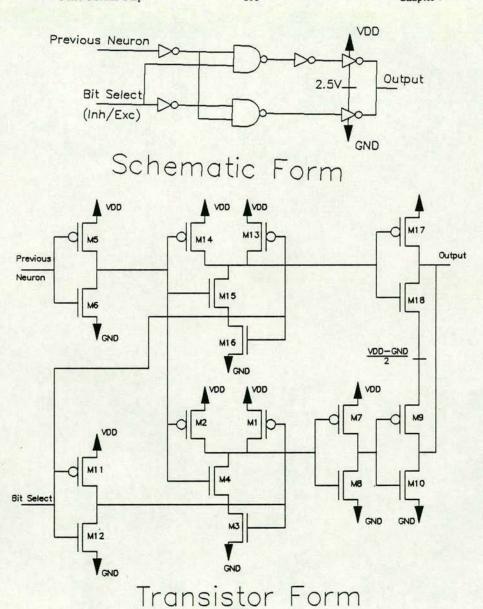

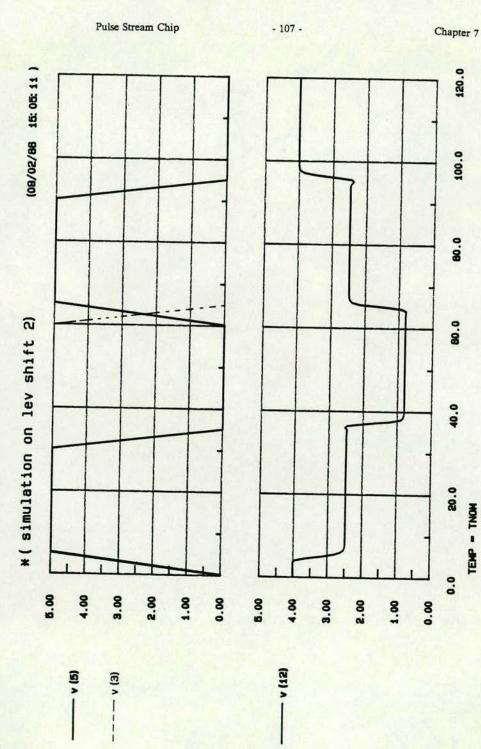

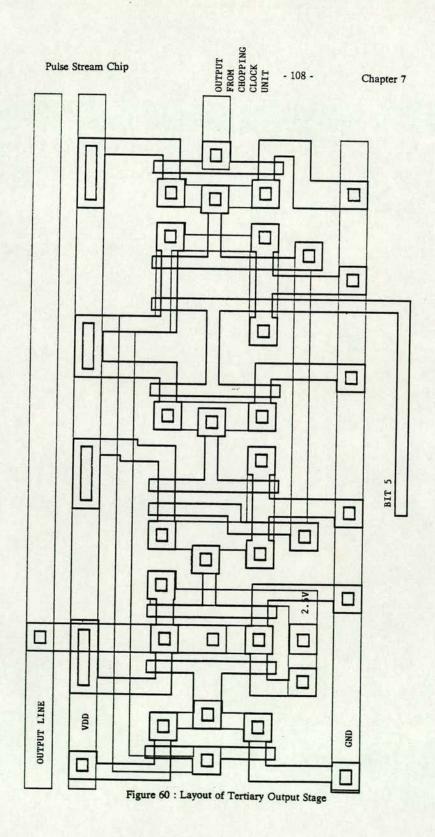

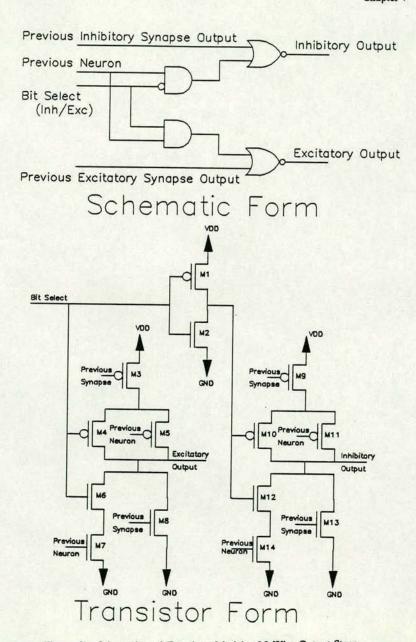

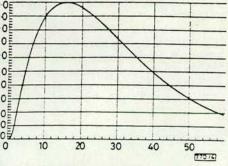

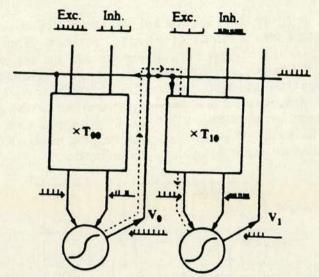

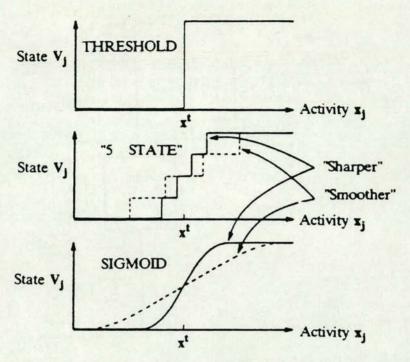

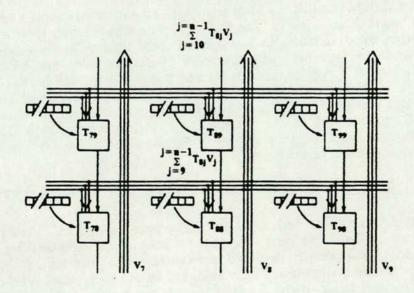

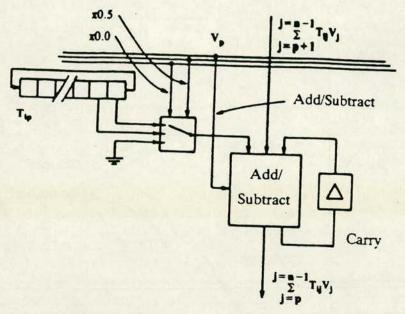

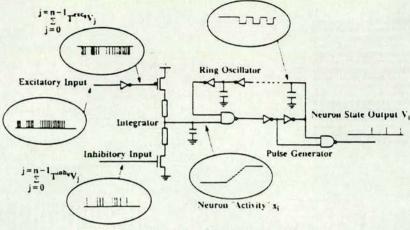

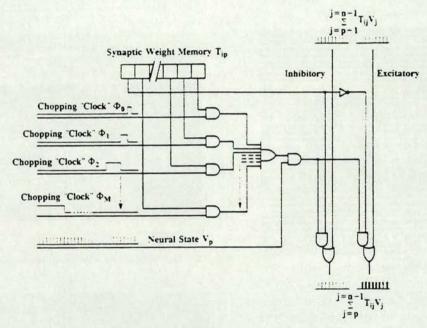

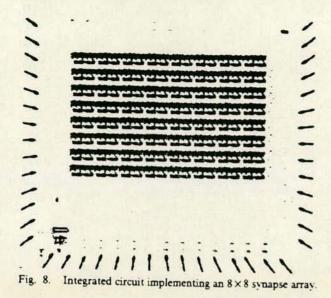

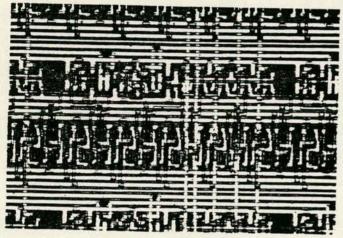

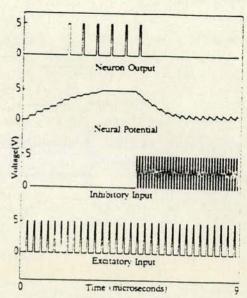

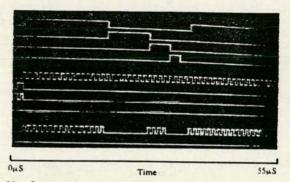

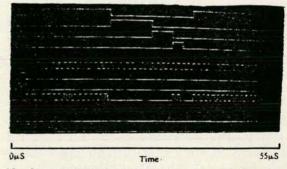

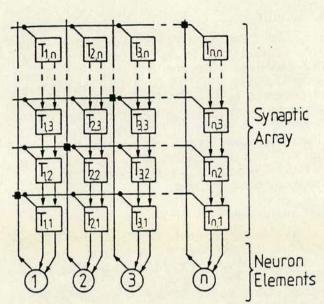

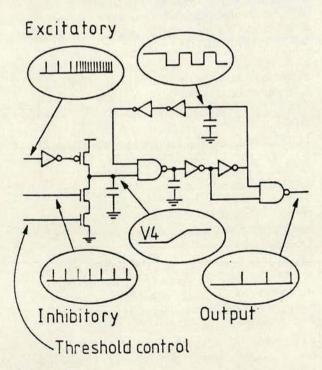

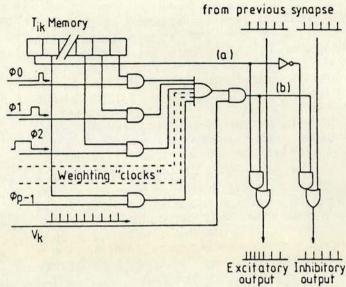

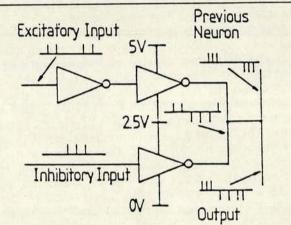

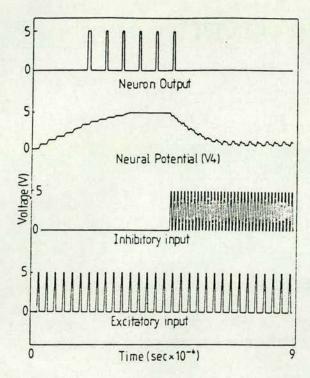

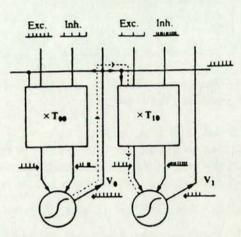

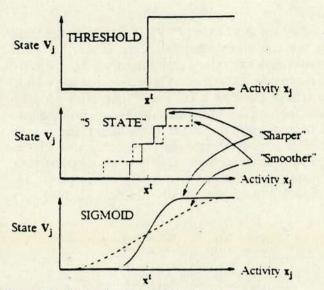

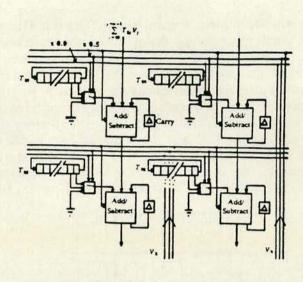

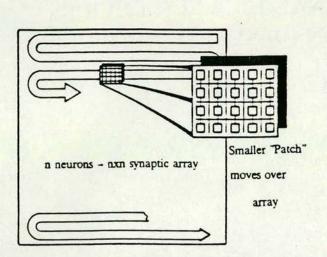

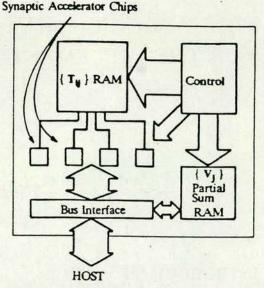

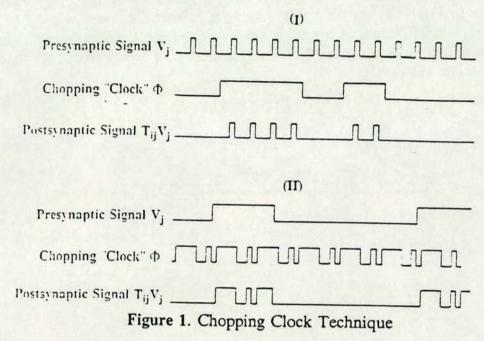

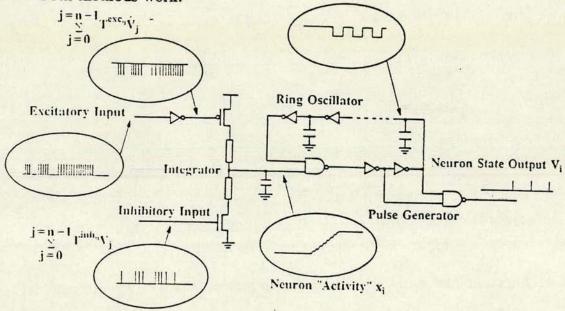

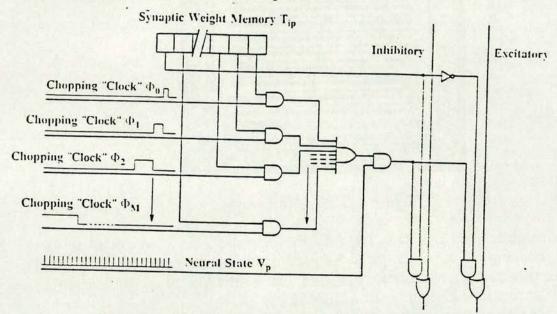

## 4.5. Barto Model Generalized Delta Rule