# A Globally Asynchronous Locally Synchronous Configurable Array Architecture for Algorithm Embeddings

Bo Gao

A thesis submitted for the degree of Doctor of Philosophy

Department of Computer Science

University of Edinburgh

August, 1996

# A thesis for the degree of Doctor of Philosophy Department of Computer Science University of Edinburgh

I declare that this thesis has been composed by myself and that the work described within this thesis is entirely my own except where clearly indicated otherwise in the text.

#### Abstract

Advanced VLSI/ULSI technologies have made it possible to realise parallelism and pipelining processing principles at affordable cost. One of the consequences is that more and more algorithms are now directly implemented in hardware. The configurable hardware algorithm approach has the potential to combine the performance of hardware algorithms and the flexibility of software algorithms at the user level. On the other hand, system timing design problems become one of the determining factors on design complexity, correct system function and high performance. This timing problem plays an even more important role in configurable systems. There are two typical system timing control design approaches, the synchronous timing design and the asynchronous timing design. This thesis investigates and demonstrates the idea and feasibility of applying asynchronous timing control at the system level and synchronous timing control to system composition modules, namely a Globally Asynchronous Locally Synchronous (GALS) design approach, for very large scale configurable hardware algorithms.

A systematic approach has been adopted in this thesis to develop a configurable GALS array architecture. With the analysis of general algorithmic properties, a novel multiple threads computation model consisting of an architecture with a pool of programmable hardware operators having configurable interconnections and a GALS system timing control structure is first established. The multiple threads computation model bridges algorithms and the architecture for efficient algorithm embeddings. The GALS timing control makes this threads model practical. A novel and fast event-driven GALS data transfer interface is developed upon which a bit-serial configurable GALS array system for algorithm embeddings is designed. Some good average performance results are obtained with a polynomial evaluation algorithm embedded as a frame buffer. The work on the GALS system timing design principle can be easily extended to the design of general GALS systems.

#### Acknowledgements

The work described in this thesis was inspired by Dr Thomas Kean's work on cellular Configurable Array Logic (CAL). Many useful suggestions were also obtained from direct discussions with Dr Thomas Kean. Dr David Rees has very patiently supervised me and given me a lot of encouragement all the way through my research work. He also carefully proof read the draft of this thesis and has made many useful comments. Special thanks also go to Professor David Kinniment from University of Newcastle upon Tyne who has helped me to clarify the synchronisation issue discussed in this thesis.

I would like to thank the department of Computer Science of Edinburgh University where an excellent research environment and computing facilities are provided, and from where I have obtained substantial knowledge on computer architectures and skills on programming.

I would also like to acknowledge the support of Sino-British Friendship Scholarship Scheme which made my research in Britain a reality.

## Table of Contents

| 1. | Intr | oduction                              | 1  |

|----|------|---------------------------------------|----|

|    | 1.1  | Computing Systems                     | 2  |

|    | 1.2  | Algorithms                            | 2  |

|    |      | 1.2.1 Software Solutions              | 3  |

|    |      | 1.2.2 Hardware Solutions              | 3  |

|    |      | 1.2.3 Parallelism and Pipelining      | 6  |

|    | 1.3  | Regular and Modular Architectures     | 8  |

|    |      | 1.3.1 Granularity of Array Element    | 9  |

|    |      | 1.3.2 Array Configurability           | 9  |

|    |      | 1.3.3 Array System Timing and Control | 10 |

|    | 1.4  | Overview of the Thesis                | 12 |

| 2. | Mas  | sively Parallel Computing Systems     | 14 |

|    | 2.1  | Cellular Logic Image Processor        | 15 |

|    | 2.2  | Distributed Array Processor           | 17 |

|    | 2.3  | Massively Parallel Processor          | 19 |

|    | 2.4  | Connection Machine                    | 22 |

| Tabl        | le of | Contents                                      |  |

|-------------|-------|-----------------------------------------------|--|

| 2           | .5    | Adaptive Array Processor                      |  |

| 2           | .6    | A Data-Driven VLSI Array                      |  |

| 2           | 2.7   | Reconfigurable Arithmetic Processor           |  |

| 2           | 8.8   | Reconfigurable Parallel Array Processor       |  |

| 2           | 2.9   | Field Programmable Gate Arrays                |  |

| 2           | 2.10  | Cellular Array Logic                          |  |

| 2           | 2.11  | Comparisons and Remarks                       |  |

| 2           | 2.12  | Impacts on Configurable Hardware Algorithms   |  |

|             |       | 2.12.1 Circuit Switching vs. Packet Switching |  |

|             |       | 2.12.2 PE local memory                        |  |

|             |       | 2.12.3 PE Degree                              |  |

|             |       | 2.12.4 PE Functionality                       |  |

|             |       | 2.12.5 System Timing Control Strategies       |  |

| 2           | 2.13  | Summary                                       |  |

| 3. <i>A</i> | Algo  | rithmically Configurable Architectures        |  |

| 3           | 3.1   | Towards Algorithmically Structured Systems    |  |

| 3           | 3.2   | Hardware Algorithms                           |  |

| 3           | 3.3   | Computation Architectures                     |  |

|             |       | 3.3.1 Dimensionality and Connectivity         |  |

|             |       | 3.3.2 Configuration Methods                   |  |

| . 3         | 3.4   | Computation models for Hardware Algorithms    |  |

|             |       | 3.4.1 Combinational Hardware Algorithms       |  |

1

.

| 7 | Table o | f Conte       | nts                                              | iii |

|---|---------|---------------|--------------------------------------------------|-----|

|   |         | 3.4.2         | Systolic Algorithms                              | 58  |

|   |         | 3.4.3         | Computational Wavefronts                         | 60  |

|   |         | 3.4.4         | Non Control-Driven Computations                  | 62  |

|   |         | 3.4.5         | Multiple Threads Computations                    | 64  |

|   | 3.5     | Timin         | g Control Structures                             | 70  |

|   |         | 3.5.1         | Clocks and Clock Skews                           | 71  |

|   |         | 3.5.2         | Computing without Clocks                         | 73  |

|   |         | 3.5.3         | Separately Timed Communications and Computations | 74  |

|   |         | 3.5.4         | Communicating Synchronous Logic Modules          | 78  |

|   | 3.6     | Algori        | thm Embeddings                                   | 80  |

|   | 3.7     | Summ          | aary                                             | 81  |

| 4 | l. A C  | Configu       | rable GALS Array                                 | 82  |

|   | 4.1     | Basic         | Architecture Constraints                         | 82  |

|   |         | 4.1.1         | Architecture Regularity                          | 83  |

|   |         | 4.1.2         | Architecture Scalability                         | 84  |

|   |         | 4.1.3         | Communication Overheads                          | 84  |

|   | 4.2     | Syster        | n Level Physical Topology                        | 85  |

|   |         | 4.2.1         | Interstitial of a Switch Lattice and PE Array    | 86  |

|   |         | 4.2.2         | Linearisation                                    | 87  |

|   |         | <b>4</b> .2.3 | Overlapped Communications and Computations       | 88  |

|   |         | 4.2.4         | Aggregated Switched Communication Network        | 89  |

|   |         | 4.2.5         | A Pseudo Nearest neighbour Configurable Array    | 91  |

| Table of | Contents | iv |

|----------|----------|----|

|          |          |    |

| 4.3                               | The GALS Scheme in PNCA                                                                                                                                                                                                                                | 95                                     |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                                   | 4.3.1 Synchronous Regions in PNCA                                                                                                                                                                                                                      | 95                                     |

|                                   | 4.3.2 Communicating Synchronous $PH_{op}$ s                                                                                                                                                                                                            | 96                                     |

|                                   | 4.3.3 A Configurable GALS Array                                                                                                                                                                                                                        | 99                                     |

| 4.4                               | RC and $PH_{op}$                                                                                                                                                                                                                                       | 101                                    |

|                                   | 4.4.1 DFG Computation Properties                                                                                                                                                                                                                       | 101                                    |

|                                   | 4.4.2 The Routing Cell                                                                                                                                                                                                                                 | 104                                    |

|                                   | 4.4.3 The Programmable $H_{op}$                                                                                                                                                                                                                        | 107                                    |

| 4.5                               | PH <sub>op</sub> Local Memory                                                                                                                                                                                                                          | 109                                    |

| 4.6                               | Summary                                                                                                                                                                                                                                                | 111                                    |

| 5. An                             | Implementation of a GALSA                                                                                                                                                                                                                              | 112                                    |

| 5.1                               | Design Tools and Implementation Technology                                                                                                                                                                                                             | 112                                    |

|                                   |                                                                                                                                                                                                                                                        |                                        |

| 5.2                               | The Configuration Technique                                                                                                                                                                                                                            | 114                                    |

| <ul><li>5.2</li><li>5.3</li></ul> | The Configuration Technique                                                                                                                                                                                                                            |                                        |

|                                   |                                                                                                                                                                                                                                                        | 117                                    |

|                                   | Asynchronous Data Transfer Interface                                                                                                                                                                                                                   | 117<br>117                             |

|                                   | Asynchronous Data Transfer Interface                                                                                                                                                                                                                   | 117<br>117<br>119                      |

|                                   | Asynchronous Data Transfer Interface                                                                                                                                                                                                                   | 117<br>117<br>119                      |

|                                   | Asynchronous Data Transfer Interface                                                                                                                                                                                                                   | 117<br>117<br>119<br>124<br>126        |

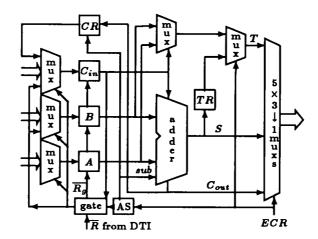

| 5.3                               | Asynchronous Data Transfer Interface  5.3.1 Hand-Shaking Cycle  5.3.2 Data Status Signal  5.3.3 Event-Driven Hand-shaking  5.3.4 An Event-Driven Register Transfer Interface  The Implementation of a $PH_{op}$                                        | 117<br>117<br>119<br>124<br>126        |

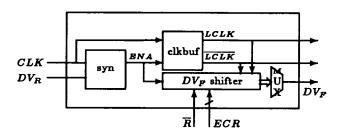

| 5.3                               | Asynchronous Data Transfer Interface  5.3.1 Hand-Shaking Cycle  5.3.2 Data Status Signal  5.3.3 Event-Driven Hand-shaking  5.3.4 An Event-Driven Register Transfer Interface  The Implementation of a PH <sub>op</sub> 5.4.1 The Clock Management Unit | 117<br>117<br>119<br>124<br>126<br>129 |

Table of Contents

|    |     | 5.4.4  | The Execution Code Register                  | 41 |

|----|-----|--------|----------------------------------------------|----|

|    |     | 5.4.5  | Multiplexers                                 | 45 |

|    | 5.5 | The R  | Couting Network                              | 46 |

|    |     | 5.5.1  | Switches                                     | 46 |

|    |     | 5.5.2  | The Configuration Control Memory             | 48 |

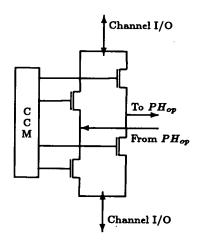

|    |     | 5.5.3  | The Routing Cell                             | 49 |

|    |     | 5.5.4  | Routing Channel Buffers                      | 50 |

|    | 5.6 | A GA   | LSA System                                   | 50 |

|    |     | 5.6.1  | The Pre-loading Circuits                     | 51 |

|    |     | 5.6.2  | GALS Array I/O Interface                     | 53 |

|    | 5.7 | Testal | pility                                       | 53 |

|    | 5.8 | Summ   | nary                                         | 55 |

| 6. | Exa | mple . | Algorithms and Simulation Results            | 56 |

|    | 6.1 | Туріс  | al Timing Characteristics                    | 56 |

|    |     | 6.1.1  | Simulation and Measurement Conditions        | 57 |

|    |     | 6.1.2  | The tri-state register and the GALS DTI 1    | 57 |

|    |     | 6.1.3  | The Transmission Gate Adder and Multiplexers | 59 |

|    |     | 6.1.4  | The Routing Cell and Channel Buffer          | 60 |

|    |     | 6.1.5  | Array Element Test                           | 60 |

|    |     | 6.1.6  | Configuration Test                           | 61 |

|    |     |        |                                              |    |

|    | 6.2 | A 4 ×  | 4 Multiplier in a GALSA                      | 63 |

|    |     | 6.2.2  | Embedding the $4 \times 4$ Array Multiplier into a GALSA | 164 |

|----|-----|--------|----------------------------------------------------------|-----|

|    | 6.3 | A Seve | en Segment Display Decoder                               | 167 |

|    | 6.4 | Evalua | ation of Polynomial Expressions                          | 170 |

|    |     | 6.4.1  | Display of Pixels for Different Objects                  | 170 |

|    |     | 6.4.2  | Polynomials in Single Variable                           | 171 |

|    |     | 6.4.3  | Polynomials in Two Variables                             | 174 |

|    |     | 6.4.4  | A Bit-Serial Frame Buffer                                | 175 |

|    |     | 6.4.5  | Embedding the Frame Buffer into a GALSA                  | 175 |

|    | 6.5 | Comp   | arisons                                                  | 177 |

|    | 6.6 | Summ   | ary                                                      | 179 |

| 7. | Con | clusio | ns and Future Prospects                                  | 180 |

|    | 7.1 | Overv  | iew of the Thesis                                        | 180 |

|    | 7.2 | Achie  | vements and the Author's Contributions                   | 182 |

|    | 7.3 | Other  | Work to Be Done                                          | 183 |

|    | 7.4 | Auton  | natic Configuration Vector Generation                    | 183 |

| -  |     | 7.4.1  | Automatic Data Flow Mapping                              | 183 |

|    |     | 7.4.2  | Automatic Algorithm Mapping                              | 184 |

|    | 7.5 | Fault- | Tolerance                                                | 185 |

|    | 7.6 | Future | e Developments and Prospects                             | 186 |

|    |     | 7.6.1  | Taking Advantages of New Technologies                    | 186 |

|    |     | 7.6.2  | Multi-layer Metal and Three dimensional Structures       | 187 |

|    |     | 7.6.3  | Wafer Scale Integrations                                 | 187 |

|    | 7.7 | Concl  | usions                                                   | 189 |

| Table of Contents            | vii |

|------------------------------|-----|

| Bibliography                 | 190 |

| A. Hspice Transient Analysis | 206 |

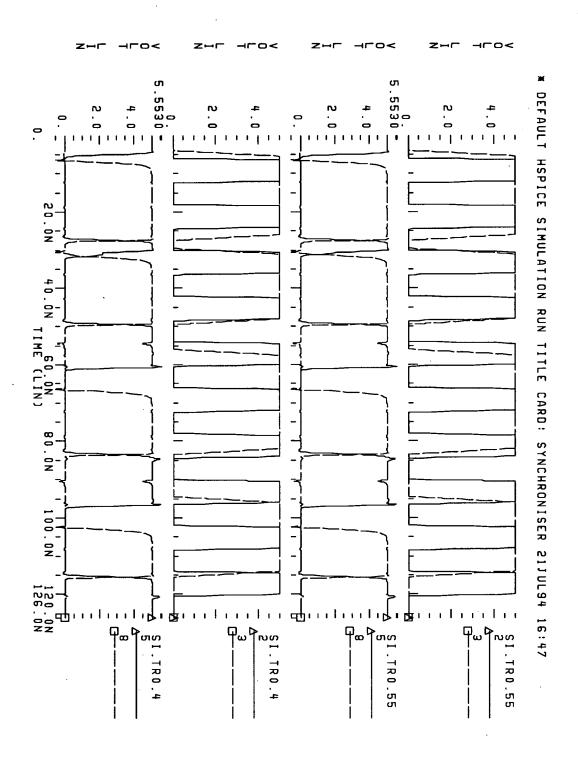

| A.1 The Synchroniser         | 206 |

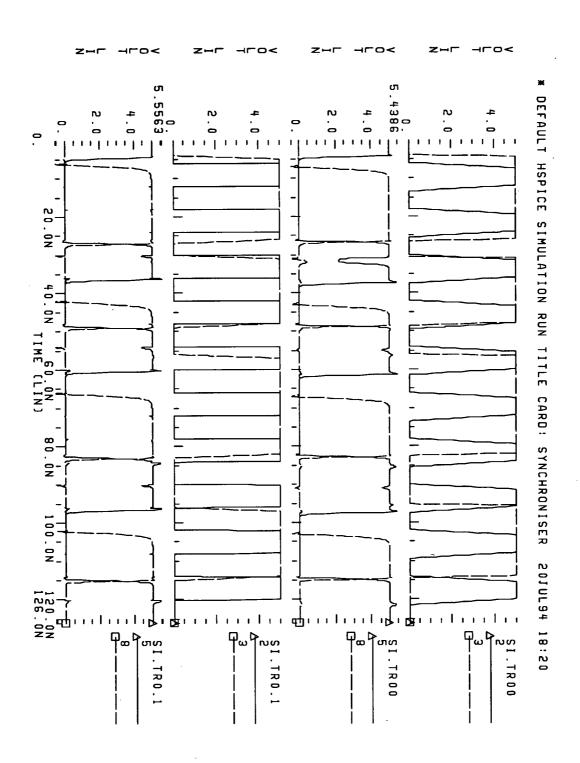

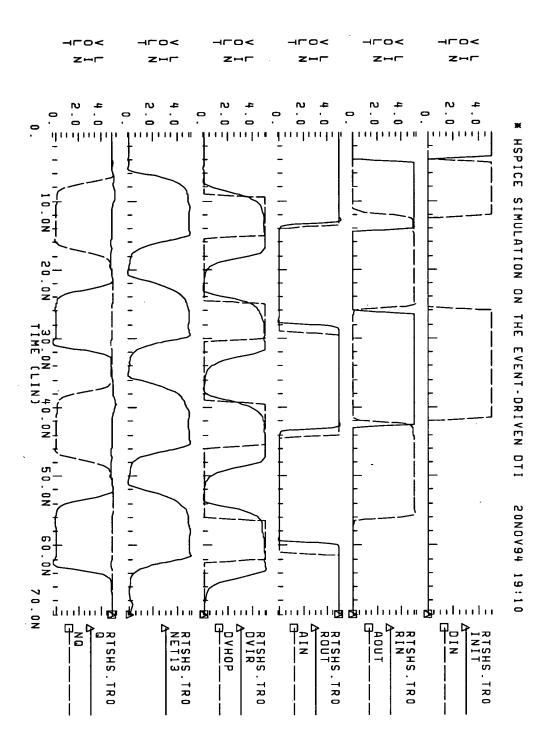

| A.2 The Event-Driven DTI     | 207 |

## List of Figures

| 1–1  | The spectrum of arrays                                    | 9          |

|------|-----------------------------------------------------------|------------|

| 2–1  | CLIP5: (a) Bit-planes, (b) PE, (c) Array interconnections | 16         |

| 2–2  | AMT DAP: (a) PE, (b) Array organisation                   | 18         |

| 2–3  | MPP: (a) PE, (b) Array edge topologies                    | 20         |

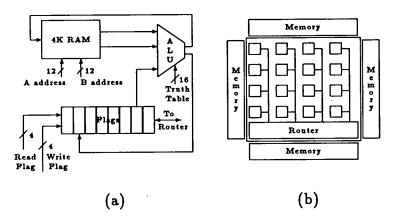

| 2–4  | Connection Machine (a) PE, (b) A subarray of 16 PEs       | 23         |

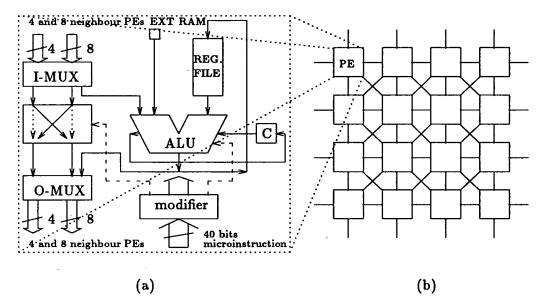

| 2–5  | AAP: (a) PE, (b) Array interconnection paths              | 26         |

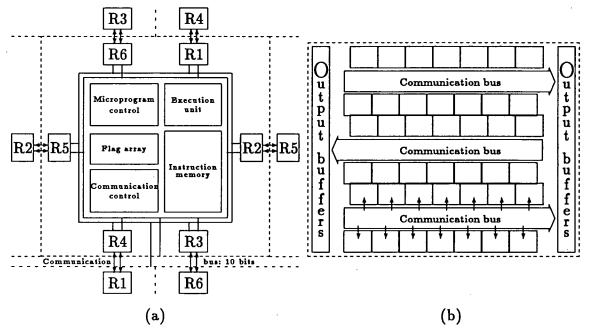

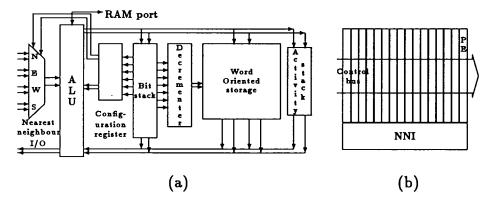

| 2–6  | DDVA: (a) PE, (b) array architecture                      | 27         |

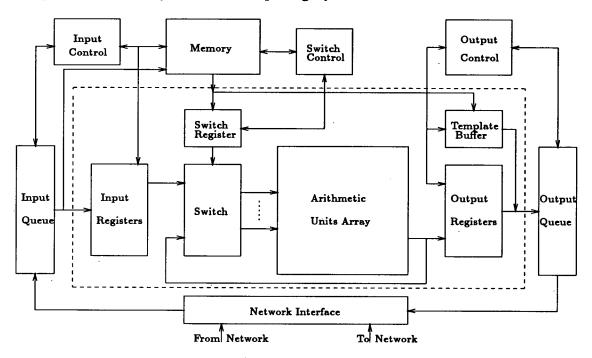

| 2–7  | RAP system architecture                                   | 28         |

| 2–8  | RPA: (a) PE, (b) The array floor plan                     | <b>3</b> 0 |

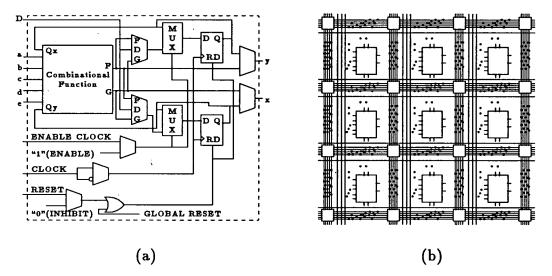

| 2–9  | Xilinx LCA: (a) Function cell, (b) Interconnect resources | 32         |

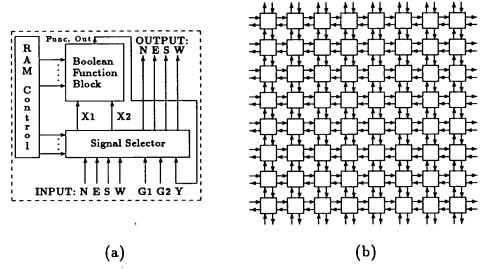

| 2–10 | CAL: (a) Cell, (b) Cellular array                         | 34         |

| 3–1  | A linear systolic computation model                       | 59         |

| 3–2  | Computational wavefronts and their propagation            | 61         |

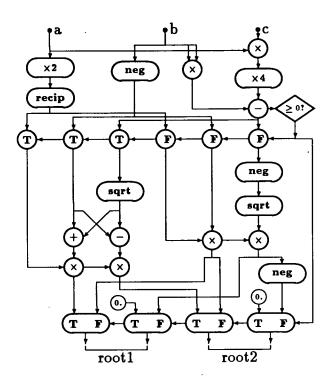

| 3–3  | The data flow graph of equation 3.5                       | 66         |

| 3–4  | The computation thread graph for figure 3-3               | 69         |

| 3–5  | Absolute and relative clock skews                         | 72         |

| List of Fi   | igures                                                                    | ix          |

|--------------|---------------------------------------------------------------------------|-------------|

| 4-1          | Typical switched interconnection schemes                                  | 86          |

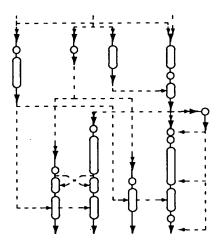

| 4-2 A        | A Pseudo Nearest neighbour Configurable Array                             | 92          |

| <b>4–3</b> A | Asynchronous guarded communications                                       | 97          |

| 4-4          | The channel width and RC ports                                            | 105         |

| 4–5 (        | (a) A switch unit in an RC, and (b) Switching states of (a)               | 106         |

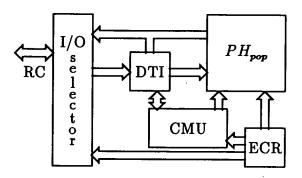

| 4–6          | $PH_{op}$ block diagram                                                   | 107         |

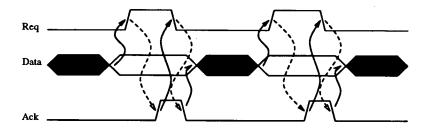

| 5–1 I        | Level signalling                                                          | 118         |

| 5-2          | Transition signalling                                                     | 118         |

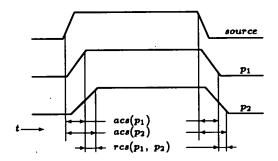

| 5-3          | Data status signal from a pre-determined block latency                    | <b>12</b> 0 |

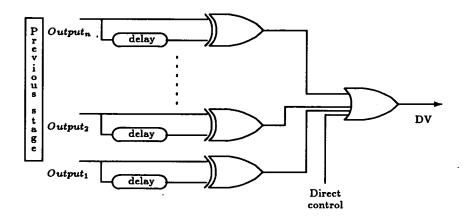

| 5-4          | A data transition detector                                                | 121         |

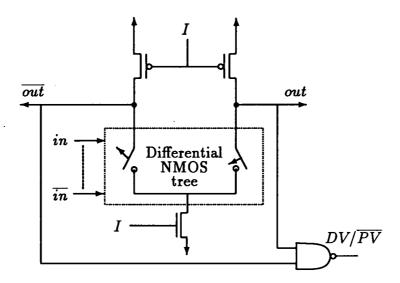

| 5-5 ]        | Hand-shaking signals generated from differential logic                    | 122         |

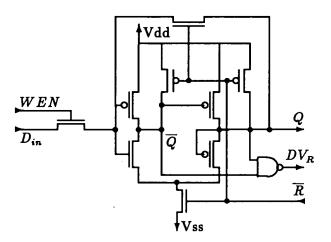

| 5-6          | A tri-state register design with $WEN, \overline{R}, DV_R$                | 124         |

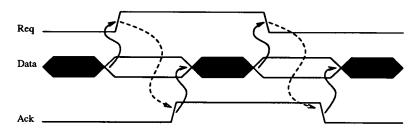

| 5–7 ]        | Event sequence in event-driven hand-shaking                               | 125         |

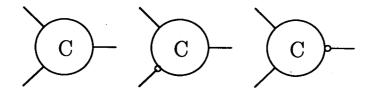

| 5-8          | Muller C-element and its variations                                       | 125         |

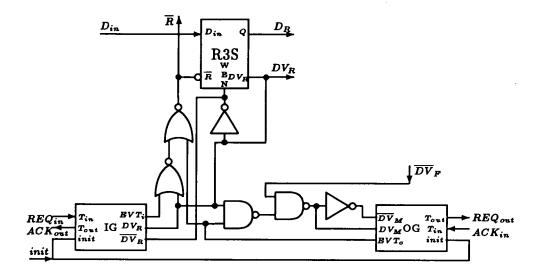

| 5-9          | An event-driven DTI                                                       | 127         |

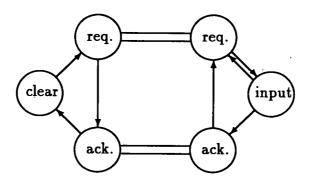

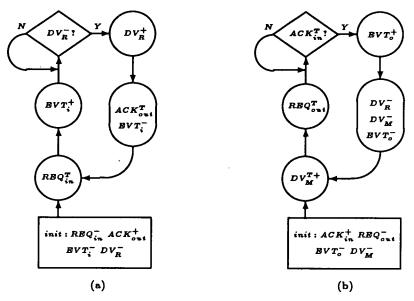

| 5-10 \$      | State transition graphs: (a) input guard, (b) output guard                | 128         |

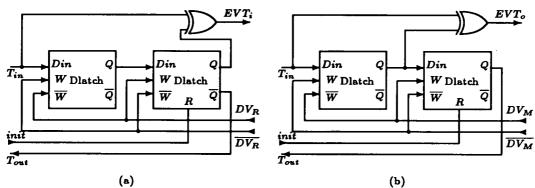

| 5–11         | Event-driven (a) input guard, (b) output guard                            | 129         |

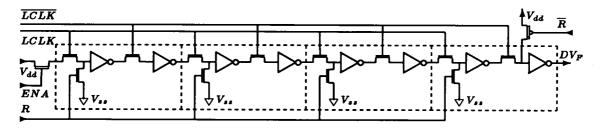

| 5–12         | A Clock Management Unit                                                   | <b>13</b> 0 |

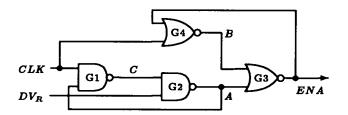

| 5–13         | A synchroniser for $DV_R$ and $CLK$                                       | 133         |

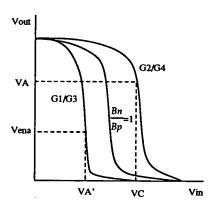

| 5–14         | Voltage transfer curves for different $\frac{\beta_{neff}}{\beta_{peff}}$ | 134         |

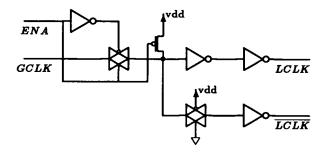

| 5–15         | A local clock buffer                                                      | 135         |

| 5–16         | A dynamic shifter for $DV_{\mathbf{r}}^+$ control                         | 136         |

List of Figures x

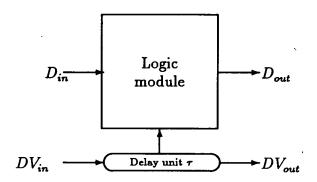

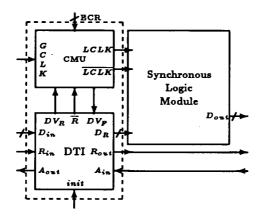

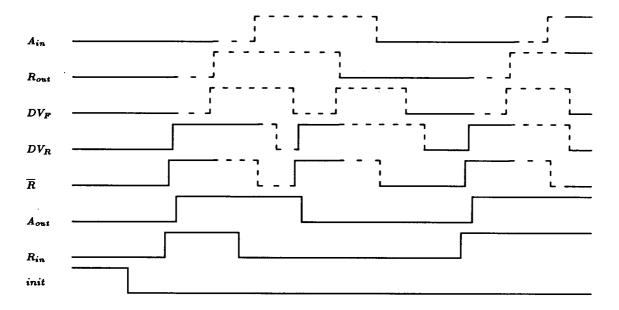

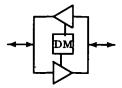

| 5-17 A general GALS logic module                                     |

|----------------------------------------------------------------------|

| 5-18 Waveforms for the event-driven GALS data transfer interface 137 |

| 5-19 A $PH_{pop}$ and its I/O multiplexers                           |

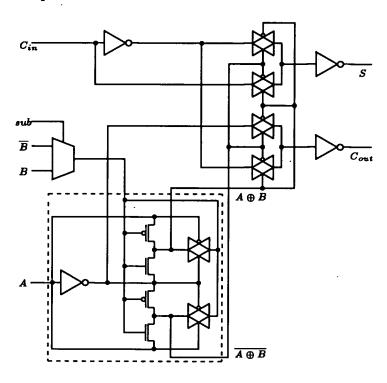

| 5-20 A transmission gate full adder                                  |

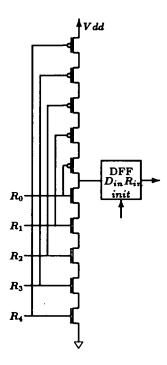

| 5-21 A 5-input Muller C-element                                      |

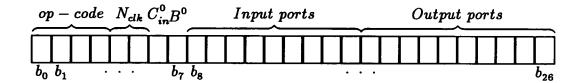

| 5-22 The Execution Code Register                                     |

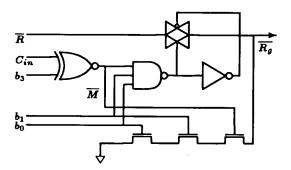

| 5-23 Gate logic block                                                |

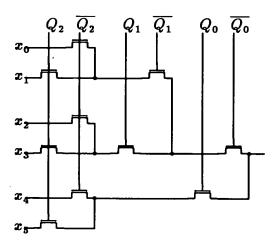

| 5-24 A 6-to-1 NMOS pass transistor tree multiplexer                  |

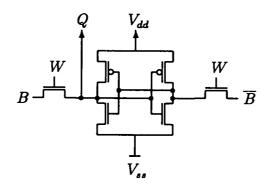

| 5-25 A six transistor static CCM                                     |

| 5-26 A switch unit with 4 bits CCM and 4 NMOS pass transistors 149   |

| 5-27 A bi-directional channel buffer                                 |

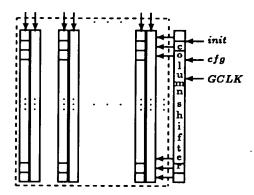

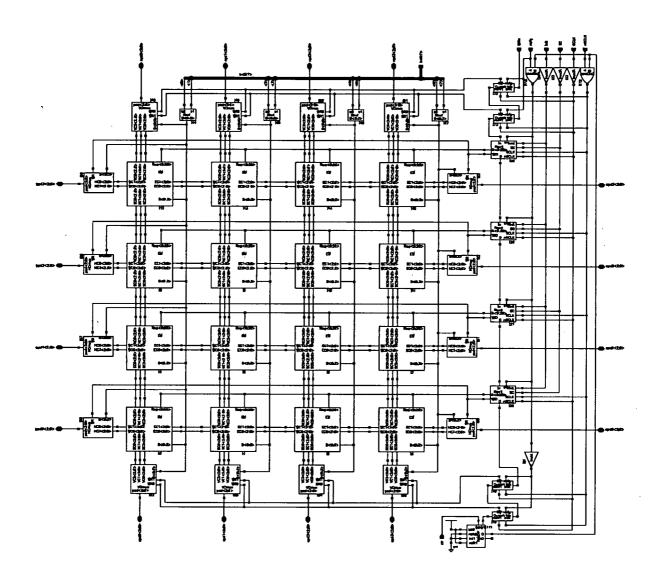

| 5-28 A configuration preloading structure                            |

| 5-29 The schematic of a $4 \times 4$ GALS array                      |

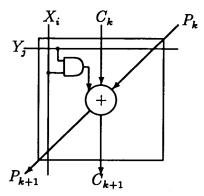

| 6-1 A multiplier cell for an array multiplier                        |

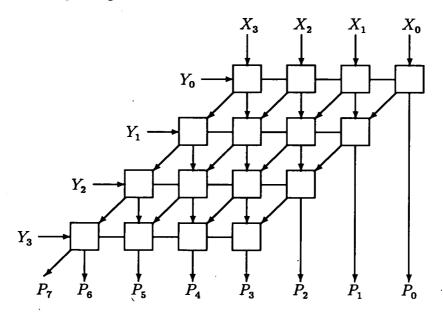

| 6-2 An array multiplier for a 4 × 4 multiplication                   |

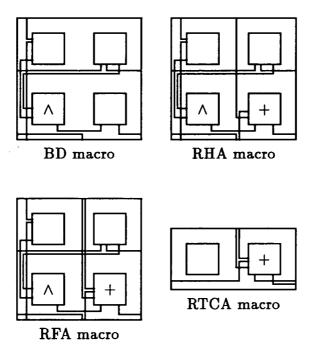

| 6-3 Macro-cells for an array multiplier                              |

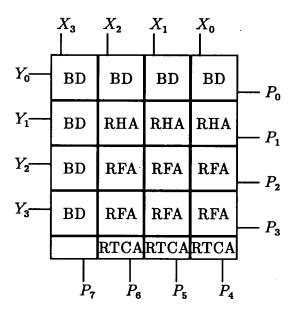

| 6-4 A 4 × 4 array multiplier in a GALSA array                        |

| 6-5 A seven segment display                                          |

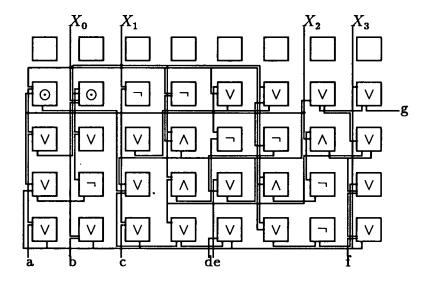

| 6-6 A seven segment display decoder in a GALSA array 169             |

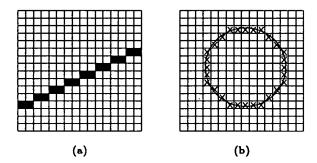

| 6-7 Pixel display: (a) a line; (b) a circle                          |

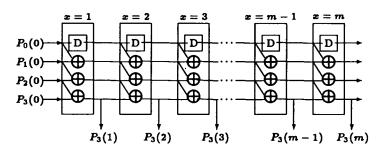

| 6-8 A linear array for evaluating cubic polynomials                  |

| 6-9 A y-array element at y:                                          |

| List of Figures                                 | хi  |

|-------------------------------------------------|-----|

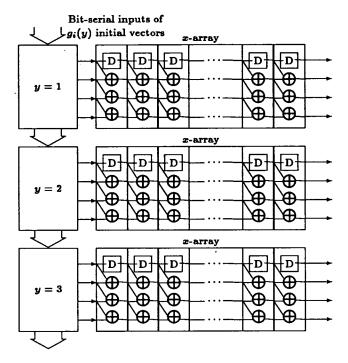

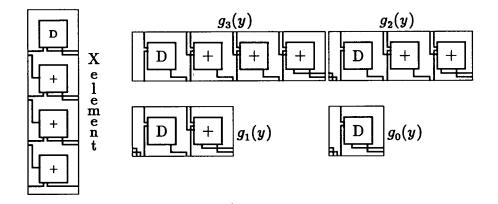

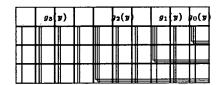

| 6-10 A bit-serial frame buffer processing array | 176 |

| 6–11 Macro cells for an X-element and $g_i(y)$  | 176 |

| 6-12 A Y-element for the y-thread               | 176 |

| A-1 A $DV_R^{T+}$ before a risk zone            | 208 |

| A-2 A $DV_R^{T+}$ after a risk zone             | 209 |

| A-3 The event-driven DTI                        | 210 |

### List of Tables

| 3–1 | PE states, I = INPUT, C = COMPUTE, O = OUTPUT              | 62  |

|-----|------------------------------------------------------------|-----|

| 4–1 | Selected primitive functions for $PH_{pop}$                | 109 |

| 5–1 | Possible functions from a full adder                       | 140 |

| 5–2 | Functions defined by op-code                               | 142 |

| 5–3 | Bit settings for I/O port selection in an ECR              | 144 |

| 5–4 | ECR execution codes and text expressions                   | 145 |

| 5–5 | Delays in switch chains                                    | 148 |

| 6–1 | The tri-state register timing                              | 157 |

| 6–2 | The Input Guard and Output Guard                           | 158 |

| 6–3 | Delays in the 5 input Muller C-element                     | 159 |

| 6–4 | Delays in the transmission gate adder and multiplexers     | 159 |

| 6–5 | Delays in a Routing Cell and bi-directional channel buffer | 160 |

| 6–6 | A $4 \times 4$ integer multiplication                      | 164 |

| 6–7 | Seven segment decoder truth table                          | 168 |

| 6–8 | Multiplier and decoder comparison                          | 178 |

| 6–9 | Polynomial evaluation performance comparison               | 178 |

#### Chapter 1

#### Introduction

In this thesis we investigate the issue of implementing algorithms directly in configurable hardware architectures (configurable hardware algorithms). We aim to establish a proper computation, architecture model and system timing control strategy for configurable hardware algorithms, and to construct a system based on the models established. A configurable system can be used as an attached subsystem to a computer where it can be configured to run a computation intensive task. Therefore it can be regarded as an algorithm memory and data are processed on-the-fly when they flow through such an algorithm memory so as to achieve high computation throughput on the task and improve the system performance of the host computer. It can also be used as a testbed to test high level algorithm designs at hardware level. This is of particular interest to software-hardware co-designs where a complex algorithm is partly solved by software and partly by hardware to meet some special criteria such as real-time response and the cost.

There are several driving factors which inspired this research when we took a brief look at the evolution history of computing systems and how complex computation problems are solved.

#### 1.1 Computing Systems

From the hardware point of view, a traditional computing system (a von Neumann computer) in general consists of a computation part (a central processing unit or CPU), a data storage part (memory), a control part, and a communication structure which connects these parts together. Each of these hardware parts implements some essential functions, such as basic arithmetic and logic operations in an Arithmetic and Logic Unit (ALU), addressed data read/write in a memory, or instruction decoding in a control part. A complicated computation task is decomposed into a sequence of essential functions directly supported by these parts. Functions which require one hardware part, for example the ALU, have to be evaluated one after another by sharing the same hardware in the time domain (sequential model).

The evolution of computing systems is two fold. Firstly, the performance and reliability of hardware components have been greatly improved over the years. Secondly, hardware costs are decreasing rapidly. Hence, it is possible to design and implement more complicated and faster computing systems by exploring novel system architectures different from the traditional sequential model to solve many difficult computation problems quickly which were almost impossible or very slow to do before.

#### 1.2 Algorithms

An algorithm defines a computational method which solves a target problem in finite steps for all of the possible inputs of the problem. Different algorithms may be designed to solve a given problem. Performance (speed and hardware resource requirements) of these algorithms, however, will probably be very diverse. The design of efficient and high performance algorithms is highly system dependent.

#### 1.2.1 Software Solutions

If a complex algorithm is to be solved on a computing system with limited hard-ware resources, for example one ALU which supports only one arithmetic or logic operation at a time point, a software solution is required to decompose complex functions, procedures, and data access operations defined in the algorithm into a proper sequence of basic operations supported by the existing hardware. A control sequence has to be generated while the algorithm is decomposed. The sequence of the decomposed operations will be executed in the system in accordance with the control sequence to obtain the required results.

Software solutions are the basis for the efficient handling of problems on a von Neumann type computing system. A von Neumann computer is a general purpose architecture developed with restrictions on hardware costs. No data dependencies of any algorithms can be reflected in the von Neumann architecture. The control sequence generated from an algorithm holds all the required data dependencies for solving a problem on a von Neumann computer. The performance of von Neumann computers replies heavily on the improvement of the single CPU operation speed. But as a matter of fact, the pace of improvements on the operation speed of hardware devices is usually behind requirements. The performance of von Neumann computers is inherently limited by the sequential computing bottle-neck because many properties of algorithms are simply ignored. New computing architectures and models are the ultimate choice which can take full advantage of many algorithmic properties and can result in a real leap in the system performance with existing micro-electronic technologies.

#### 1.2.2 Hardware Solutions

It is possible to implement high level algorithm specifications and schedule their control tasks directly in hardware (hardware algorithms) by eliminating the sin-

gle CPU bottle-neck with a properly established computation model, a system architecture, and a control scheme to achieve a high system performance.

It becomes evident, if we take the design evolution history of microprocessors as an example, that more and more computing functions are directly implemented in hardware. The only arithmetic operation implemented in the first microprocessor design was addition; any operations more complicated than addition had to be done by software methods. For example, the instruction set of a Zilog Z80 did not have multiplication which had to be realised as an algorithm when invoked. Then there have been lots of efforts made in implementing various multiplication algorithms as hardware multipliers [44,13,140,86,122,133,16,19,18]. In the subsequent generations of microprocessor designs, multiplication is eventually included in the instruction set. Hardware accelerators for multiplication had been integrated into the designs of many microprocessors, for instance, Intel 80486, Motorola MC68040, and INMOS T800. Coprocessor approaches which can further extend the CPU instruction set to trigonometric, logarithmic, exponential and other floating-point arithmetic instructions were developed, examples are Intel 80387 and Motorola MC68881 math coprocessor. More complicated algorithms, such as sorting and Fast Fourier Transform (FFT), were also implemented directly in hardware. The implication of this development is that it is now very practical to implement many algorithms directly in hardware which previously had to be done with software solutions and this is the route that we follow to develop high performance systems.

The coprocessor approach is one of the ways to implement many functions in hardware. However, this approach is still limited in that there is only small amount of hardware resource to be sequentially programmed in a user transparent way. Another common approach is by parallel processing where data dependencies of algorithms can be reflected to some degree in the actual hardware. Systolic arrays are one of the intensively studied hardware solutions to a class of regularly structured algorithms. Systolic algorithms are designed in such a way that adequate hardware resources are provided and data movements are properly scheduled at

the design stage to meet the entire optimized computation requirements instead of sequencing data through limited hardware blocks many times. Many Application Specific Integrated Circuits (ASIC) can also be classified as hardware solutions to specific application problems.

A hardware system can be classified as a hardware algorithm if it has a large proportion or all of the data dependence structures of a class of algorithms and can directly output required results after a finite latency upon the presence of valid inputs. Unlike software solutions, control sequencing and scheduling are all hard-wired in hardware algorithms.

There are two ways to design hardware algorithms. The ASIC design is a popular approach to implement a hardware algorithm exactly as the algorithm specification. Another way is to design a blank hardware system which can be configured by end users. By blank system we mean a system that does not perform any specific functions before it is configured. A user has the freedom to design an application algorithm for the system. The specification of the user's algorithm will be mapped into such a blank hardware system assisted by an algorithm mapping tool. The algorithm is said to be embedded into the system after it is configured according to the map generated from the mapping tool.

The ASIC approach provides some advantages in design and performance. It is relatively easy to automate ASIC design procedures by taking advantage of both special silicon architectures, such as gate-array, and particular data dependencies of the target applications. Algorithms implemented in ASICs are faster than their configurable counter parts. However, ASICs also suffer from some drawbacks.

1. Turn-around time: The design time for an ASIC based on the gate-array structure is faster compared with custom Very Large Scale Integrated Circuit (VLSI) designs since many Computer Aided Design (CAD) systems are available. However, they still have to go through a design phase, fabrication phase, test phase and shipping phase which often take at least 3 to 4 months

to complete. It may take more than one such a cycle to get a final correct design.

- 2. High cost: The cost of designing an ASIC may be high because of the above mentioned multi-phase design and manufacturing process and sometimes the relatively small number of chips produced.

- 3. Low user controllability: The algorithmic aspects of an ASIC design are usually determined at the design phase and cannot be changed easily once chips are fabricated. This low user controllability means that ASICs cannot accept any minor revisions without substantial efforts and costs. This low flexibility renders ASICs not suitable for applications at early stages of development which will often undergo modifications.

On the other hand, a configurable system provides a fast design turn-around time and flexibility for easy design modifications. As far as costs are concerned, it may appear that a single configurable chip may cost more because of the extra configuration logic. The average cost can be brought down when large numbers of chips are produced since they can be used for a wide range of applications. For example, Field Programmable Gate Array (FPGA) products with configurable architectures are growing rapidly in recent years because of these attractions. Therefore a configurable architecture for algorithm embeddings has advantages of high performance by running algorithms directly in hardware and the flexibility of configurable logic.

#### 1.2.3 Parallelism and Pipelining

A proper computation model is required to transform a user defined algorithm into a form which can be embedded efficiently into a configurable hardware system to achieve the best performance on the algorithm.

Parallel and pipeline processing are effective ways to increase the system performance. Parallel processing is to process non-dependent computing tasks in a set of processing elements (PE) simultaneously so that the single CPU bottle-neck in von Neumann computers is eliminated. The concept of pipelining came from industrial assembly lines through which end products are consecutively assembled step by step. Each step will always be kept busy with partly assembled parts continuously fed from the previous step and will feed newly assembled parts to the next step. It is obvious that each product only goes through an assembly line once. After the first product is output from the assembly line, there will be the same number of products being assembled as the number of steps of the line, while each product is at a different stage of its final completion. Pipelining techniques in computing systems are exactly the same as assembly lines, simply replacing parts and products with intermediate and final data values, and steps with processing blocks as pipeline stages. The outstanding properties of pipeline processing techniques are highly efficient utilization of hardware resources and application level parallelism.

These concepts are not new to scientific researchers at all. People, including von Neumann, had already realised the potential of parallel and pipeline processing as early as in 1950's [131]. Many parallel and pipeline processing systems were developed 25 years ago. However, it may involve some substantial software programming work for users on some of these parallel computers because it is often the user's responsibility to determine the parallel properties of an algorithm, decompose and schedule (similar to the control sequence on von Neumann computers) process controls on these parallel systems. It is often difficult for a user to figure out some implicit or run-time parallel properties of a problem. Users are often required to be aware of the parallel architecture of a system in order to use it efficiently. The application of these techniques is relatively new in configurable architectures. A parallel and pipeline processing computation model for a configurable hardware algorithm system is established in this thesis. This will

enable the system to make use of the parallel properties, especially the run-time properties, of an embedded algorithm automatically.

#### 1.3 Regular and Modular Architectures

Hardware algorithms are mostly based on regular VLSI architectures. Examples are array multipliers and matrix multipliers. Advanced VLSI technologies have made it possible to investigate and develop various novel architectures for a wide range of applications. One of the most popular regular architectures is the array architecture because it is very good for VLSI implementation and algorithm embedding. Array architectures can be classified according to the granularity of elements, programmability, array processing timing control strategy and array operation control strategy.

There are some common characteristics among VLSI arrays.

- Regularity: An array system is formed by the duplication of one or several

very limited types of cells in a very regular way normally in a two dimensional plane. Some three dimensional arrays also exist. The interconnections

between array elements are also distributed in a regular pattern.

- Simplicity: Although an entire VLSI array may consist of a large number of duplicated elements, the design complexity of a large array system is often proportional to the complexity of the building elements of the array.

- Scalability: Due to the duplication nature in arrays, it is very easy to shrink or expand the size of an array so as to fit it to certain particular application requirements.

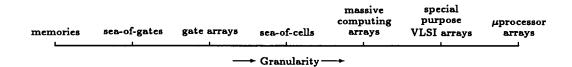

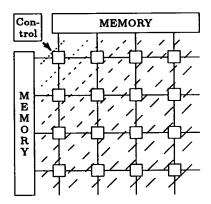

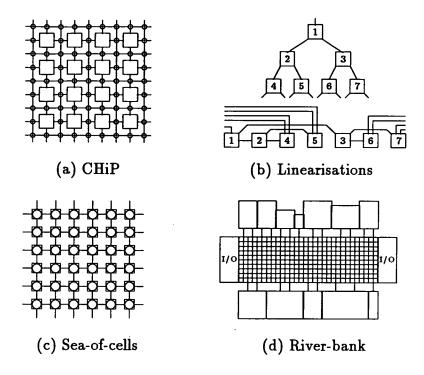

Figure 1-1: The spectrum of arrays

#### 1.3.1 Granularity of Array Element

VLSI array architectures can be found spreading over a wide spectrum as shown in figure 1–1. VLSI arrays with the most fine-grained elements are memory arrays. The granularity of array elements is increased following sea-of-gates arrays, gate arrays, sea-of-cells arrays, massively parallel processing arrays, special purpose VLSI arrays, and very expensive microprocessor arrays where each processing element can be used as a CPU in a von Neumann computer. We choose the massively parallel processing array as the foundation for our configurable hardware algorithm architecture. This is a good compromise of system functionality, flexibility, size and rational cost.

#### 1.3.2 Array Configurability

Array configurability reflects the flexibility with which an array system can be applied to embed just one or a class of algorithms, that is, the generality of a system. There are many different technologies to choose for the implementation of a configurable system. Some of these technologies have advantages in area and performance, but they require special processing techniques, such as laser structuring or fuse-blowing, which permanently change the physical structure of a hardware system and the cost can be high. Configurable systems using conventional low cost circuit switch devices can offer much higher user flexibility and reusability with slight degradation in performance and increase in silicon area.

The choice of a configuration method is determined by the design purpose and the target implementation technology for the design. Our system design will be based on a normal CMOS process technology and it requires higher user configurability and reusability, so MOSFETs will be used as the basic switch devices in our configurable array architecture for algorithm embeddings.

#### 1.3.3 Array System Timing and Control

There is a classification of arrays based on the type of instruction and data flow. An array whose elements operate on one instruction at a time to process one data stream is called a Single Instruction Single Data flow (SISD) array. Similarly, an SIMD array has Single Instruction and Multiple Data flow. If elements in an array operate on different instructions to process multiple data streams, the array is called a Multiple Instruction and Multiple Data flow (MIMD) array. An MISD array has Multiple Instruction and Single Data flow. A configurable array architecture for hardware algorithms can be regarded as a two phase MIMD array. A configuration phase is a Multiple Instruction flow (MI) phase. Once the array is configured, it runs in Multiple Data flow (MD) phase.

Because an array system can usually be divided into two types of essential parts: computation modules and a communication network, different timing control methods may be applied separately to computation modules and the communication network. A best match between these two timing control methods on computation modules and the communication network will make it possible to achieve an optimal performance and efficient system resource utilization.

It is a common practice to select either a synchronous or an asynchronous timing control method as the basis for an entire system timing control. In synchronous systems where all system operations are lock-stepped with a central global control clock, it is impossible to consider individual timing control for computation modules and the communication network. The speed of the central control clock in a synchronous system is determined by the worst possible case so as to secure the correct data movement in computation modules and the communication network.

The worst possible case is jointly determined by the worst clock distribution skew, the delay of the longest communication path and the slowest sequential logic in the computation modules.

There are no global system control clocks in asynchronous systems. The control of data movement and operation in an asynchronous system is completely localised. The performance of an asynchronous system is data dependent and measured by an average instead of the worst case for a maximum clock frequency as in a synchronous system.

We argue in this thesis that an asynchronous timing control can make the best out of a communication network, particularly a configurable communication network. It is also an excellent choice in general for timing control at the system level. We also argue that the synchronous timing control with clocks is still a very good choice for computation modules of sufficient complexity. Based on this argument, we look at the possibility of combining these two timing control methods together. A system timing design approach for a Globally Asynchronous communication network and Locally Synchronous computation modules (GALS) is established in the thesis. A configurable array architecture for algorithm embeddings is designed by applying our parallel multiple threads computation model and the GALS system timing control approach in the rest of the thesis. This architecture can easily accommodate any new technology, system design and user design changes. It also offers a solution to timing problems of the immediate future in the design of Ultra Large Scale and Wafer Scale Integrated (ULSI/WSI) systems.

#### 1.4 Overview of the Thesis

- Chapter 1: The essential concepts and ideas of hardware algorithms, configurable architectures and system timing control methodologies are introduced. The aim of this project is elaborated: the establishment of a proper computation model, configurable architecture and system timing control approach for high performance algorithm embeddings

- Chapter 2: Some typical massively parallel computing systems are analysed and compared in this chapter. The purpose of these comparisons is to look at the common characteristics and the problems in these existing systems so that we can establish a proper computation model, interconnection network structure, and an overall system architecture for configurable hardware algorithms.

- Chapter 3: In this chapter, a multiple threads computation model for irregular algorithms is established for algorithm embeddings. A configurable architecture template with a connected pool of hardware operators and a globally asynchronous locally synchronous (GALS) system timing control approach is proposed for algorithmically configurable architectures. A configurable GALS array system will be designed based on the ideas elaborated in this chapter.

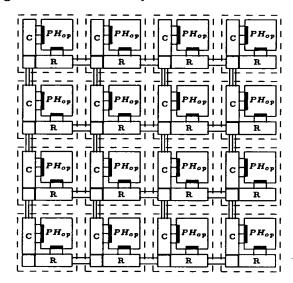

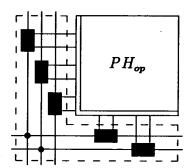

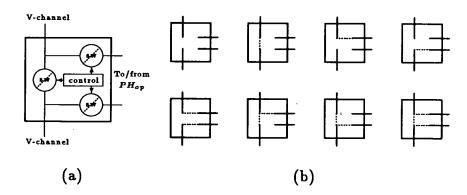

- Chapter 4: A Pseudo Nearest neighbour Configurable Array (PNCA) architecture with some constraints is proposed in this chapter. By combining the PNCA and GALS approach, a top level configurable GALS array topology and the logical structure of the interconnection network and a programmable hardware operator  $PH_{op}$  are illustrated. A guarded asynchronous handshaking communication protocol is also described.

- Chapter 5: Various issues concerning the implementation of the GALS array system are discussed in this chapter. The design of a bit-serial configurable GALS array (GALSA) is presented. Some key components, such as an event-driven GALS data transfer interface, a novel tri-state register, the synchronisation issue, the design of a  $PH_{op}$  and a routing network, are described in detail. An example  $4 \times 4$  GALS array is given. The event-driven GALS data transfer interface can also be used to construct general GALS systems.

- Chapter 6: In this chapter, simulation results of the designs described in chapter 5 are presented. Three algorithm to the GALSA system mapping examples are given. The performance of the GALSA system is analysed and compared with some other similar systems. Although there are some extra delays caused by configuration switches in the routing network, the performance of the GALSA system is still very good because the system can process tasks based on the multiple threads computation model.

- Chapter 7: This chapter summarises all the work presented in this thesis and the author's contributions. Further development of the current work is outlined.

The prospects for configurable hardware algorithms in the future are also discussed.

#### Chapter 2

# Massively Parallel Computing Systems

The work described in this thesis is closely related to a class of architectures called massively parallel computing arrays. A massively parallel processing array normally consists of one or a few types of processing elements (PE) which are duplicated as many times in a two dimensional plane and connected by a network as an application task requires. Some existing systems already have an array of 16K or 64K PEs. We shall analyse and compare some typical existing systems and other related work in this chapter. While some common points in these system designs are found, distinctions are also drawn between the research work carried out in this project and the existing systems.

Since 1970, the dramatic reduction in costs of integrated circuits and increasing requirements for high performance computing systems have stimulated the research and development of many parallel array architectures. Many of them have been implemented on Large Scale Integrated (LSI) circuit technologies. Newer generations of these systems and many other new systems are now mostly implemented in VLSI technologies. This makes it possible to accommodate more PEs in a silicon chip.

#### 2.1 Cellular Logic Image Processor

The Cellular Logic Image Processor (CLIP) [24] was the first bit-serial array processor chip designed and fabricated. The development of the CLIP architecture can be traced back to 1973. It started at the time with many technology constraints which no longer apply. Although the early CLIP chip implementation is in current terms inefficient, the CLIP architecture is very heuristic. People are also trying to update the CLIP design with the latest state-of-art technology. The history of CLIP evolved from the the first prototype to CLIP4 (with 8 PEs on one chip in 1978) [24,35], CLIP5 (with 16 PEs on one chip in 1981) [34] and CLIP6 (1983) [33]. The CLIP5 PE uses essentially the same logic as the CLIP4 PE, while the chip configuration has been improved in several aspects, such as the use of a larger package which enables more pins to be assigned to control functions and more PEs to be integrated on one chip; local data storage has been removed to off-chip RAM and the data path design has been improved. There were substantial changes in the CLIP6 design principles. The major differences in CLIP6 are that all data paths and functional blocks are bit-parallel in operation on 8-bit of data. A single multi-bit ALU instead of a dual Boolean/adder PE is used, a multi-bit multiplexer for input selection replaces input gating circuitry, and a local condition code register supports a degree of PE autonomy control.

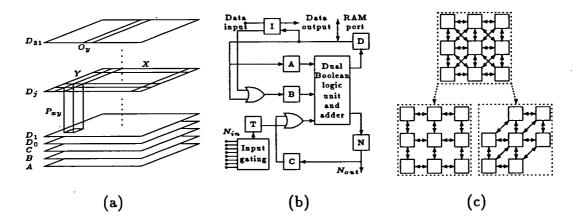

The data structure in an  $n \times n$  CLIP array can be visualised as a stack of bit-planes as shown in figure 2-1(a). Each bit-plane is composed of an array of  $n \times n$  data. One data bit in such a structure is represented as  $D_j = \{d_{j,x,y} : x, y = 1, 2, \dots, n\}$ , where  $d_{j,x,y}$  is a bit located at (x,y) in the jth plane. A data word can be stored in either binary stack format (vertical format) or binary column format (horizontal format). In binary stack format, a datum is uniquely addressed by (x,y) and passing through g bit-planes:  $P_{x,y} = \{d_{j,x,y} : j = k, k + 1, \dots, k+g-1\}$ . The binary stack format is very suitable for storage and processing

Figure 2-1: CLIP5: (a) Bit-planes, (b) PE, (c) Array interconnections

of pixels in an image. When numerical calculations are to be performed, it is sometimes convenient to represent data in binary column format:  $O_y = \{d_{j,x,y}: y=1,2,\cdots,n\}$  in which there will be no one-to-one correspondence between data and  $n^2$  PE addresses. The data structure in most of the two dimensional regular massively processing arrays can be modelled by this stacked bit-plane structure.

An old CLIP PE consists of a dual Boolean and a full adder processing unit, input gating circuitry, three registers (A, B, C) corresponding to a bit location in A, B, C bit-planes, a memory D for  $D_{j,x,y}$  locating at (x,y) in  $D_j$   $(j=1,2,\cdots,n)$  bit-plane, and some glue logic. The PE can perform all the 16 Boolean functions with two variables and bit-serial addition which are all controlled by signals fed from an external control unit. The input gating however can be individually set to meet special application communication requirements. The CLIP PE schematic is shown in figure 2-1(b). Each CLIP PE is physically connected to its eight neighbours, but the actual CLIP logical connectivity among PEs can be configured as hexagonal, 4 nearest neighbour, or 8 neighbour connection to reflect the requirements of a specific application data structure (c.f. figure 2-1(c)). The input gating and full neighbourhood connectivity also make it possible to complete many operations in only one cycle for which other later designs may require as many as twelve cycles.

The CLIP system was specially designed for high speed image processing applications. A system with total of 9216 (96 × 96) PEs has been built with CLIP array chips. Data captured and A/D converted from a video camera are processed through the CLIP array and results are again D/A converted and output to a monitor. Some typical applications of such a system are simple edge detection, labeling, two-dimensional filtering operations on images, image enhancement, and skeletalisation.

#### 2.2 Distributed Array Processor

The prototype Distributed Array Processor (DAP) [51] was designed and constructed in 1976 by Reddaway and others at International Computers Limited (ICL) as an enhanced memory module for ICL2900 series mainframes, and eventually evolved to an independent parallel processing system. The development of the DAP system was later separated from ICL to an independent company called Active Memory Technology Ltd (AMT). The first of the second generation DAP systems, built on LSI technology, was delivered in 1985. A prototype mini-DAP was built from a gate array chip which integrated 16 PEs together on one chip, and the whole system consists of an array of 32 × 32 PEs. A 64-PE custom VLSI chip is used in a version of the re-engineered 64 × 64 AMT DAP [55]. A DAP PE, as depicted in figure 2-2(a), is designed with a bit-serial full adder supported by a set of registers (A, C, Q, S, D), signal multiplexers, and an external local memory port which can address up to a maximum of 1M bits of RAM in the present architecture. The A register is used for PE "activity control" which can inhibit memory write operations in certain instructions in a PE. The activity control is also important in cases such as inhibiting PE operations at the predefined boundaries of a problem, or in conditional data-dependent operations. Q can be regarded as an accumulator and C as a carry register. The third input to the adder is selected by a multiplexer from PE memory, Q, A, data broadcast by the

Figure 2-2: AMT DAP: (a) PE, (b) Array organisation

MCU (Master Control Unit), or the carry output of a neighbouring PE. S and D register are transparent to users, but play a very important role in assisting data movement. D is used as a buffer for data input/output through a fast interface unit, and S is a buffer for such instructions that need to read from and write to a memory. When A, C, Q, D and memory are viewed as an abstract data structure, they can also be represented as bit-planes as illustrated by figure 2-1(a) but with at least 32K array memory planes. Hence data in a DAP machine can be stored in either vertical or horizontal format.

Interconnections among PEs are essentially nearest neighbour connection but enhanced with X- and Y- buses for fast data broadcasting to the PE array or fast data retrieving from the array. Data in a register of a PE can move in any of the four directions (North, South, East, West) to a corresponding register in a neighbouring PE. It is also possible to extract data from a specified row or column of PEs, or to AND together data from all of the rows or all of the columns. PEs at the edge of a DAP array are simply connected to their counterparts at the opposite edges, thus allowing shifts to "wrap-around" if required.

The DAP system has been efficiently applied to areas where large volumes of regularly structured data have to be processed, for instance, matrix manipulations, image processing, and sorting.

#### 2.3 Massively Parallel Processor

The Massively Parallel Processor (MPP) project was initiated in 1971 and the construction of a real MPP system started from 1979 under a contract awarded to Goodyear Aerospace by NASA [7]. The first delivered MPP system consists of a physical array of 16896 PEs which can be logically configured as an array of 16384 (128 × 128) PEs with 512 (128 × 4) redundant PEs for the fault-tolerant purpose.

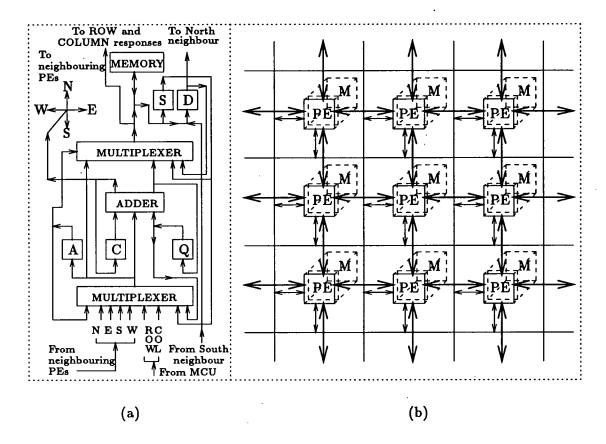

The interconnection topology in an MPP PE array is a simple conventional 4 nearest neighbour connection. The choice of this simple interconnection pattern is determined by the target application area of the MPP — two-dimensional image data processing, and by the huge number of PEs required. However, the edge topology of the MPP array is made very flexible as shown in figure 2-3(b). Programmable switch circuits are located on the four array edges. The connectivity between the right and left edge can be set as one of the following four states: open (no connection); cylindrical,  $PE_{i,1}$  is connected to  $PE_{i,127}$ ,  $i = 0, 1, 2, \dots, 127$ ; open spiral  $(PE_{i,1})$  is connected to  $PE_{i-1,n}$  for  $1 \le i \le 127$ ); and closed spiral (similar to open spiral but  $PE_{0,1}$  is connected to  $PE_{127,127}$ ). The top and bottom edges of the array can be either connected or left open. When both left and right, top and bottom edges are connected, a ring configuration is formed. Since an

Figure 2-3: MPP: (a) PE, (b) Array edge topologies

MPP array is composed of a large number of PEs, fault-tolerance and reliability become important issues in the MPP system. Two measures are adopted. One is the simple group redundancy scheme by which a group of 128 × 4 redundant PEs is added. The entire array is divided into 33 groups of 4 × 128 PEs together with group bypassing gates in the routing network. The array can survive PE faults in one group by disabling (bypassing) the entire faulty group and activating the redundant group. The other technique is the parity error detection to find memory faults. One parity bit is combined with eight data bits of every 2 × 4 PE subarray. Whenever a fault is discovered, the group redundancy control will be used to disable the group containing the error.

Because the target workload of an MPP array is image processing in which the resolution of input pixels may vary from 6 to 12 bits, and intermediate results can be of length from 6 to more than 30 bits, the MPP PE had to be custom designed based on the bit-serial processing principle. This is very efficient to process operands of varying length. The actual PE structure as shown in figure 2—

3(a) was optimized for bit-serial arithmetic operations by combining a single bit full adder, a variable length shift register, and six single bit registers (A, B, C, P, G, S). Different from many other bit-serial PE design, a local data bus (D) is also used to provide a convenient way for data movement among PE registers and local RAM. All types of arithmetic operations are supported in the MPP PE array, such as integer/floating-point addition/subtraction, multiplication/division. The MPP PE logic circuit can also perform all 16 Boolean functions with two input variables from P and D register. A special routing operation which can shift the state in P to one of its four neighbours is included. The G register holds a mask bit so that masked operations are only performed in those PEs whose G is set to 1. The S register is used for shifting input and output data to/from the MPP PE array. A local RAM of 1K bits, from where operands are fetched and results are stored in a one-bit operation, is attached to each PE.

The implementation of the MPP PE array used a rather outdated technology. A subarray of 8  $(2 \times 4)$  PEs is integrated on one chip [110] designed with CMOS/SOS technology and packed in a 52-pin flatpack.

In 1986, a new project called BLITZEN motivated at miniaturising the physical size of the MPP system was started at the Microelectronics Center of North Carolina [10,47,21]. Years later, a custom VLSI CMOS chip containing 128 (8×16) PEs on an 11.0mm × 11.7mm die was fabricated and mounted on a 176 pin PGA. The BLITZEN PE design is basically the same as the MPP PE but enhanced with more control functions such as local control of masking, local condition testing which may lead to alternative local processing actions and local modification of global addresses. But the interconnection pattern among PEs is very different from the MPP in that an "X" interconnection and rows of I/O buses are used. The "X" configuration enables each PE to communicate directly with its eight nearest neighbours and allows data to be routed along diagonals in an array which is faster than Manhattan routes.

#### 2.4 Connection Machine

The Connection Machine (CM) is the largest massively parallel array processing system built so far. The architecture was originally conceived by Hillis in his thesis [49] at MIT, and was constructed by Thinking Machines Corporation. The major part of the CM has an array of 64K (2<sup>16</sup>) data processors (PE) and a complex data communication network among these PEs. The communication network in the CM is completely different from other systems, using a packet-switched network instead of circuit-switched network. One of the goals of the CM design is to construct a very flexible architecture so that many different application types can be processed by the system. Operations based on data-parallelism make it possible for the CM to exhibit very high performance on processing massive amounts of data concurrently in each PE. The CM is well developed at the user interface level with a virtual-machine model which presents users with an abstract machine architecture to ease programming tasks for users on the machine. A virtual-processor model makes it possible to solve problems of sizes larger than the physical size of a CM.

The unique flexible communication network of the CM is supported by routers and a NEWS (North, East, West, South) grid. Every subset of 16 PEs shares one router while a total of 4,096 ( $2^{12}$ ) routers is hard-wired in the pattern of a Boolean n-cube (n=12). Therefore any router can be reached from any other router by travelling over no more than 12 wires. Each router handles messages for its subordinate 16 PEs and also serves as the interface with other routers. The operations of the router can be divided into five types: injection, delivery, forwarding, buffering, and referral. Injection is the process of sending new messages into the network from a subset of 16 PEs. The process by which a router removes a message from the network and sends it to a destination PE is called delivery. If an injected message is going to somewhere outside the cluster of 16 PEs, it must be forwarded. When several messages are delivered at once or several messages

Figure 2-4: Connection Machine (a) PE, (b) A subarray of 16 PEs

are to be forwarded over the same wire, they will be buffered by the router. If a router's buffer is full, the router may refer a message to another router. Each router is uniquely assigned with a 12-bit binary address for the convenience of routing algorithms. The NEWS grid provides a two-dimensional Cartesian direct connection for nearest-neighbour communication which is faster than router communication for simple and regular data structures. Other communication modes such as broadcast communication and global OR of ALU carry output from all PEs are also supported in the CM.

A CM PE, which is shown in figure 2-4(a), consists of a bit-serial ALU unit, a local bit-addressable RAM, eight one-bit flag registers, a router interface, and a NEWS grid interface. The ALU is a logic element which can compute any two Boolean functions with three inputs and two outputs. The actual function of the ALU is determined by 8 bits stored in a function table. The A and B address specify the external memory locations from where the first and second operands to the ALU are read. The A-address is also the memory location to where the memory output of the ALU is written. The read flag selects one of the 16 (8 general purpose, 8 special purpose) flags from which the F input of the ALU is taken. The write flag selects one of the 16 flags to which the flag output of the

ALU is written. Flags in each PE are used to set communication modes and for memory error detection/correction.

The implementation of the CM architecture has evolved from CM-1 to CM-2 [130]. Both CM-1 and CM-2 use off-the-shelf RAM chips and a custom designed CMOS VLSI chip which contains a subarray of 16 PEs with one router and a control unit (c.f figure 2-4(b)). CM-2 has been improved in many aspects while keeping the same essential architecture as CM-1. The major differences in CM-2 are: 64K bits instead of 4K bits memory for each PE, four flag registers instead of eight, an optional floating point accelerator for every group of 32 PEs, increased error detection circuitry, redesigned router with improved reliability, diagnostic capability and performance, replacement of the two-dimensional NEWS grid with a more general n-dimensional grid on top of Hypercube, and a high speed I/O system.

The CM is a very flexible architecture which can be applied both in numeric and symbolic processing to a very broad range of applications. For instance, grid-based communication finds primary application in regularly structured problems such as particle simulations and matrix manipulations, while the general packet routing supports varying topologies in circuit simulation and computer vision.

## 2.5 Adaptive Array Processor

The Adaptive Array Processor (AAP) [64] was developed at NTT in Japan. The AAP architecture was designed to be used as a high performance system with a certain degree of flexibility for various two-dimensional data processing applications and small overhead for inter-PE communications over long distances. The adaptability of the AAP to applications is supported by three special features:

Duplicated communication paths. Each PE is connected with its eight neighbours, and a duplication of connection between upper and lower PEs makes it possible to implement hierarchical bypass for flexible and fast data transfer.

- A complex data transfer unit in each PE. Since the physical interconnections

among AAP PEs are fixed, a complex data transfer unit is used in each PE to

support flexible data routing and hierarchical data bypass. The data transfer

unit is implemented with various multiplexers and some control registers.

Combined with duplicated interconnection paths, data can be routed rather

freely among PEs in the AAP.

- Local modification of global controls. The local adaptability of each PE

is determined by the contents of local control registers which can modify

common control signals fed from a single global control unit outside the PE

array.

The AAP PE comprises a 16-function bit-serial ALU for two inputs and a set of supporting registers. One unusual feature is the use of one of the data registers to hold a control signal which determines the storage destination for a result. A 64bit register file is used to hold temporary data and makes it possible to implement various operation modes on an AAP. Data can also be structured in either vertical or horizontal format in an AAP as shown in the stacked bit-plane of figure 2-1(a). However, the AAP extends the stacked bit-plane structure with more operation modes. Bit-serial operations can be carried out in each PE on entire words stored in vertical format. The PE array can also be structured to either word-unit or block-unit operation modes. When part or the entirety of a row or column of PEs are combined to process data in horizontal format, the AAP is in word-unit mode. If a block of PEs (a subarray) is grouped together, horizontal words can also be processed in block-unit mode. The AAP PE schematic is shown in figure 2-5. The first prototype AAP chip integrates 64 (8  $\times$  8) PEs together with 6K bits  $(64 \times (64 + 32))$  of memory on a die of nearly  $1cm^2$ . The second generation of the AAP - AAP2 [65] is designed with an external RAM port of up to 1M bits logical address space in each PE. The AAP2 has one 40-bit microinstruction modifier which can support wideband modifiable PE operations in the array (called pseudo MIMD by AAP designers). The interconnection paths are also enhanced

Figure 2-5: AAP: (a) PE, (b) Array interconnection paths

by a duplicated 4 neighbour connection network (c.f. figure 2-5(b)) instead of the upper-lower path in the AAP prototype. One external 64K bytes (8 × 64K bits, static) RAM module and one AAP2 64 PE array chip can be mounted on one special package.

The AAP system can be applied to many two-dimensional data processing applications. Examples are grey tone level histogram calculation, distorted image correction, feature extraction of character images, and logic simulation of electronic circuits.

## 2.6 A Data-Driven VLSI Array

I. Koren and B. Mendelson [66] developed a Data Driven VLSI Array (DDVA) for embedding arbitrary algorithms. The DDVA is different from most of the massively parallel processing array architectures in that it operates on a data-driven principle. With the elimination of global control on data-flow, correct operation of the system will be guaranteed by the availability and presence of matching input data to each PE in a DDVA. The DDVA is designed with a hexagonal interconnect architecture where each PE is connected to six nearest neighbours. There are

Figure 2-6: DDVA: (a) PE, (b) array architecture

rows of communication I/O buses of 10-bit wide (figure 2-6(b)). Communications among PEs are all through some of the six registers in each PE as shown in figure 2-6(a). A data flow graph for an algorithm can be mapped into a DDVA where nodes (vertices) of the graph are embedded into the PEs of the DDVA and edges (arcs) of the graph are mapped either as a connection between two communicating registers or a series of PEs which are only set as communication path if connection resources are not enough. Each DDVA PE processes 8-bit operands and is datadriven, i.e. a PE instruction is initiated only when all of its required operands are available and its destination registers are empty. Each PE can be loaded with at most six instructions, the execution order of instructions is completely data-driven instead of depending on a program counter. The complexity of the prototype PE is about 9,000 transistors in a NMOS technology. The microprogram control unit is the largest block in the PE which requires about 4,500 transistors. This unit translates instructions stored in the PE instruction memory into sequences of control signals that control the operation of the execution unit. This microprogram control unit is the fundamental feature of a DDVA that makes it possible for the DDVA to embed arbitrary algorithms and operate on the data-driven principle.

Figure 2-7: RAP system architecture

The DDVA architecture has very low hardware efficiency for arbitrary algorithms because it uses PEs as routing cells with very limited routing resources. It is too expensive to use such a complicated PE for just a simple routing function.

## 2.7 Reconfigurable Arithmetic Processor

The Reconfigurable Arithmetic Processor (RAP) [32] is actually developed as an arithmetic processing node for an MIMD concurrent computer. The aim of the RAP design is to reduce the amount of off-chip and memory data transfer traffic by evaluating an entire arithmetic formula directly in an RAP upon the configuration of the RAP to the structure of the formula to be evaluated. Only final evaluation results are sent back to a host computer after a set of inputs is presented to the configured RAP. All of the intermediate data are calculated, referred to and eliminated locally; no global memory references which will otherwise require expensive high speed I/O channels that are often a performance bottle-neck. All of the external communication requirements of an RAP are the input of configuration control data (which will be done prior to calculations), input of coefficients and values of

variables, and the output of final results. The schematic of the RAP architecture is illustrated in figure 2-7. The major building blocks in an RAP are a set of arithmetic processing units which include adders/subtractors and multipliers, a switching network, and a switch configuration control unit. Partial bit-parallel arithmetic units are designed to process 4-bit of operands in one operation or a serial-of 4-bit if longer operands are presented. The switching network in the RAP can be configured with the switch configuration control unit to interconnect arithmetic units in a way which represents the data-dependencies of the formula.

One of the most important features of the RAP architecture is the highly reduced memory communication flow requirements. Once all of the required data is retrieved from the memory, the entire evaluation of an arithmetic formula will be carried out without interaction with the host system until final results are obtained.

## 2.8 Reconfigurable Parallel Array Processor

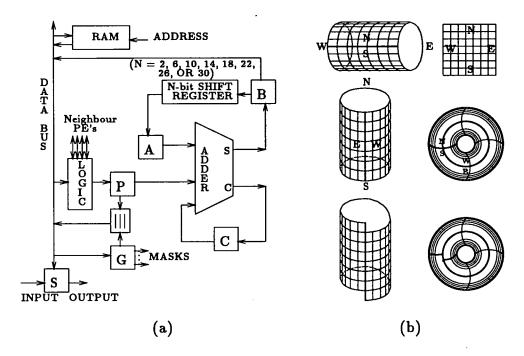

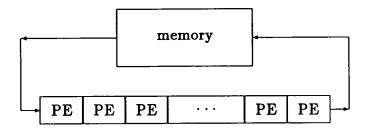

The Reconfigurable Parallel Array Processor (RPAP) was developed by Rushton and Jesshope [117] [52, Section 3.5.4] at Southampton University with the aim of implementing a more general-purpose flexible architecture assuming Wafer Scale Integration techniques. The RPAP architecture is very flexible in that it can be logically configured to perform from bit-serial, through partial bit-parallel, to word operations. To minimise the communication problem between a host and an RPAP array, a shared memory between the two is used so that the address of the array memory can be directly mapped into the address space on the host. The RPAP is not a real SIMD system because some fields of the instruction words distributed across an RPAP array can be locally modified in a PE.

An RPAP is physically a two dimensional four nearest neighbour interconnected (NNI) array of simple bit-serial PEs with wrap-around at both opposite edges. The whole system is synchronously operated. The RPAP chip VLSI floor-

Figure 2-8: RPA: (a) PE, (b) The array floor plan