# The Design and Implementation of Gallium Arsenide Digital Integrated Circuits

A thesis submitted to

the Faculty of Science of

the University of Edinburgh,

for the degree of

Doctor of Philosophy

by

A.D. Welbourn, MA, CEng, CPhys

Department of Electrical Engineering

March 1988

#### Acknowledgements

In undertaking a research project of this nature, one has cause to be grateful to innumerable people, and I must begin by apologising to those who are omitted from this formal acknowledgement, and by offering them my thanks for their help and support.

There are those who are deserving of especial mention, and I am most grateful for the guidance and encouragement given by Alec Livingstone, Bob Merrett and Peter Mellor, from the Gallium Arsenide Integrated Circuit section at British Telecom's research laboratories. Some of the measurements, specifically identified in the body of the text, were performed by my colleagues Graham Blau, Ian Sturgess and Bob Merrett, and I add my thanks to them by name here.

To Professor Mavor and Professor Jack, my supervisors at Edinburgh, I also owe a great deal of thanks, not the least for their patience in awaiting this manuscript, and for their most helpful and constructive comments.

I also acknowledge the Directorate of British Telecom Research and Technology, firstly for permission to undertake this study, and then for permission to publish this thesis.

Greatest thanks of all must be reserved for my wife Elizabeth, without whose love, patience, suffering and encouragement, this thesis would never have been completed.

## List of Contents

| Contents:                                                         | Page:         |

|-------------------------------------------------------------------|---------------|

|                                                                   |               |

| Title page.                                                       | i             |

| Abstract.                                                         | ii            |

| Declaration of Originality.                                       | iii           |

| Acknowledgements.                                                 | iv            |

| List of contents.                                                 | v             |

| List of figures.                                                  | vii           |

| List of tables.                                                   | xiii          |

| List of symbols.                                                  | xiv           |

| Chapter 1. Introduction.                                          | 1             |

| Chapter 2. An introduction to Gallium Arsenide.                   | 5             |

| 2.1 Fundamentals of GaAs.                                         | 6             |

| 2.1.1 GaAs material properties.                                   | 6             |

| 2.1.2 Historical exploitation of GaAs. 2.1.3 Back-gating.         | 13            |

|                                                                   | 19            |

| 2.2 GaAs IC fabrication.                                          | 23            |

| 2.2.1 The preparation of GaAs wafers. 2.2.2 Doping in GaAs.       | 24            |

| 2.2.2 Doping in GaAs. 2.2.3 Isolation between devices.            | 26            |

| 2.2.4 Junction formation.                                         | 31            |

| 2.2.5 Interconnection.                                            | 32<br>35      |

| 2.3 MESFET Logic.                                                 |               |

| 2.3.1 Introduction to GaAs MESFETs.                               | 37            |

| 2.3.2 Critical History of Normally-on MESFETs in GaAs             | 37<br>ICs. 40 |

| 2.3.3 Development of Normally-off Logic.                          | 52            |

| Chapter 3. Simple GaAs IC design using CCL.                       | 63            |

| 3.1 Starting position.                                            | 63            |

| 3.1.1 Device models.                                              | 63            |

| 3.1.2 The fabrication process.                                    | 70            |

| 3.1.3 A simple test chip.                                         | 72            |

| 3.2 Capacitor coupled logic.                                      | 76            |

| 3.2.1 The inverter.                                               | 76            |

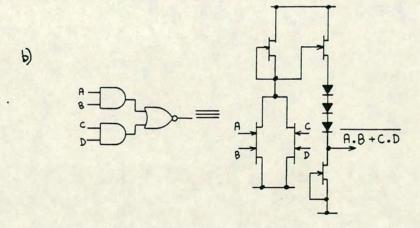

| 3.2.2 Other simple logic gates.                                   | 86            |

| 3.2.3 Pre-charging simple gates.                                  | 95            |

| 3.2.4 Practical application of theory.                            | 100           |

| 3.3 Functional blocks.                                            | 111           |

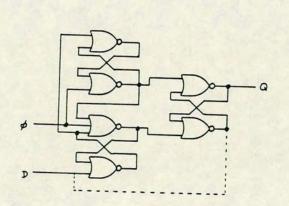

| 3.3.1 Latch design.                                               | 111           |

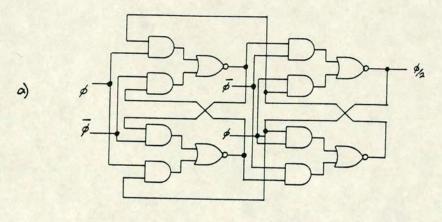

| 3.3.2 Complementary clock generator.                              | 125           |

| 3.3.3 Input and output buffers.                                   | 133           |

| Chapter 4. Modelling.                                             | 139           |

| 4.1 Schottky Diode modelling. 4.1.1 Physics of Schottky junctions | 139           |

| 4.1.1 Physics of Schottky junctions. 4.1.2 Diode current.         | 139           |

| 4.1.3 Diode capacitance.                                          | 143           |

|                                                                   | 149           |

| Contents:                                                                                                                                                                                | Page:                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.2 MESFET modelling. 4.2.1 Physics of MESFET behaviour. 4.2.2 DC models. 4.2.3 AC models. 4.3 Interconnections. 4.3.1 Introduction.                                                     | 162<br>163<br>165<br>173               |

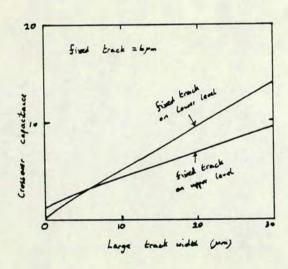

| 4.3.2 Track capacitances. 4.3.3 Cross-over capacitances.                                                                                                                                 | 176<br>177<br>185                      |

| 4.4 Discussion.  Chapter 5. The design of an MSI Circuit in CCL.  5.1 Specification.                                                                                                     | 188                                    |

| 5.1 Specification. 5.2 Design. 5.2.1 Options. 5.2.2 Layout philosophy.                                                                                                                   | 190<br>192<br>192<br>214               |

| 5.3 Circuit simulation. 5.3.1 Ground rules for the simulations. 5.3.2 Clock generator and driver stages. 5.3.3 Pre-scalar simulations. 5.3.4 Input amplifier. 5.3.5 Remaining circuitry. | 223<br>223<br>226<br>231<br>238<br>240 |

| 5.4 Multiplexer operation. 5.4.1 Test techniques. 5.4.2 Results.                                                                                                                         | 241<br>241<br>246                      |

| Chapter 6. Discussion and Recommendations.                                                                                                                                               | 256                                    |

| 6.1 Improved performance from CCL. 6.1.1 Circuit design reworks. 6.1.2 Technology improvements.                                                                                          | 256<br>257<br>260                      |

| 6.2 Improved circuit technology. 6.2.1 Capacitor diode FET logic. 6.2.2 Capacitor enhanced FET logic.                                                                                    | 265<br>266<br>274                      |

| 6.3 Concluding remarks.                                                                                                                                                                  | 278                                    |

| Appendix 1 Current in a distributed diode.                                                                                                                                               | 280                                    |

| References.                                                                                                                                                                              | 284                                    |

| Publications.                                                                                                                                                                            | 200                                    |

## List of figures

|             | Figure:                                    | Page: |

|-------------|--------------------------------------------|-------|

|             |                                            |       |

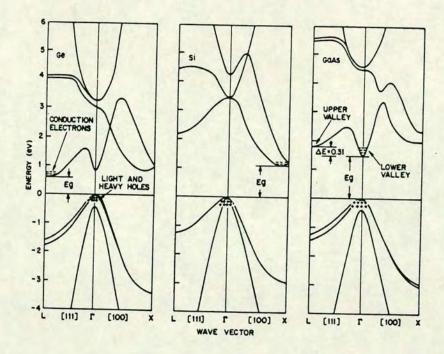

| Figure 2.1  | Band structures of Ge, Si and GaAs.        | 7     |

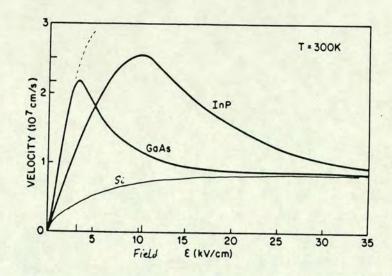

| Figure 2.2  | Velocity-field characteristics of          | 9     |

|             | electrons in various semiconductors.       |       |

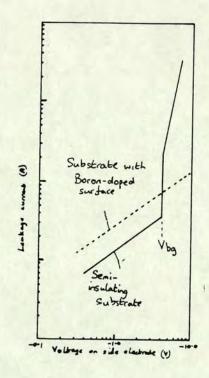

| Figure 2.3  | Leakage currents in GaAs.                  | 21    |

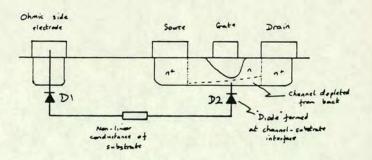

| Figure 2.4  | Model to explain the effect of back-gating | 21    |

|             | on MESFETs.                                |       |

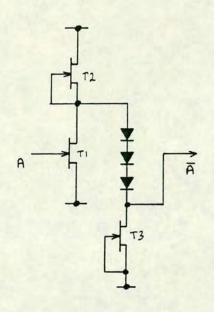

| Figure 2.5  | Buffered FET Logic (BFL) Inverter.         | 40    |

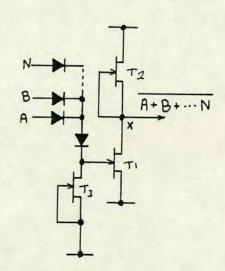

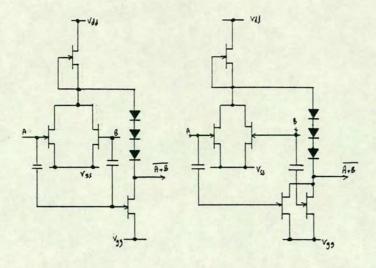

| Figure 2.6  | Schottky Diode FET Logic (SDFL) Inverter.  | 45    |

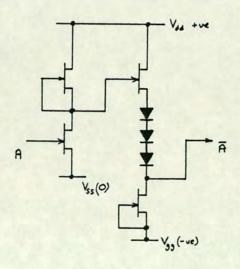

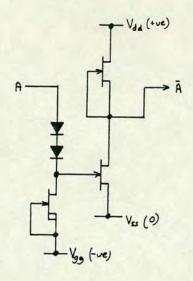

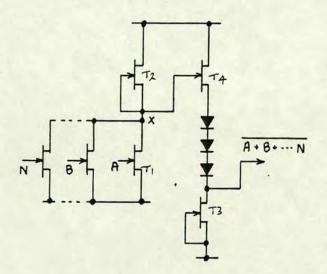

| Figure 2.7  | BFL NOR gate.                              | 46    |

| Figure 2.8  | SDFL NOR gate.                             | 46    |

| Figure 2.9  | Efficient AND-NOR divider in BFL.          | 47    |

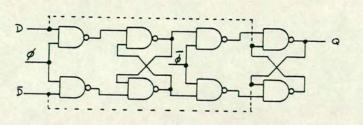

| Figure 2.10 | Edge triggered D-latch.                    | 47    |

| Figure 2.11 | Traditional master-slave latch.            | 47    |

| Figure 2.12 | Modified BFL Inverter.                     | 49    |

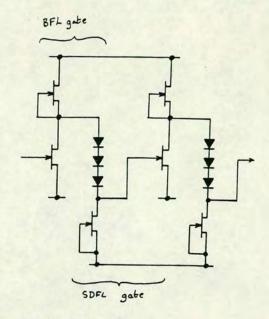

| Figure 2.13 | Common origins of BFL and SDFL gates.      | 49    |

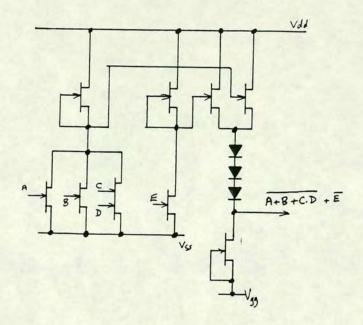

| Figure 2.14 | BFL circuit with combinatorial logic in    | 50    |

|             | buffer as well as switch.                  |       |

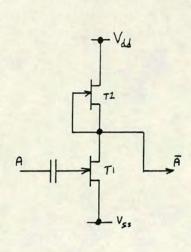

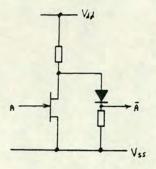

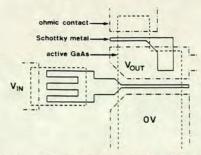

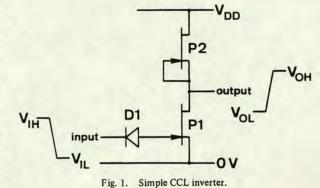

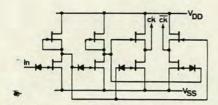

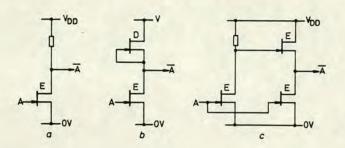

| Figure 2.15 | Capacitor coupled logic (CCL) inverter.    | 51    |

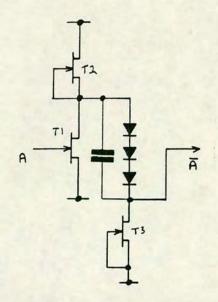

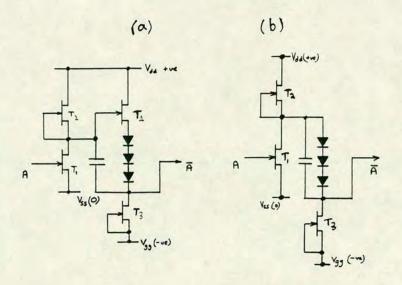

| Figure 2.16 | Capacitor diode FET logic (CDFL) inverter. | 51    |

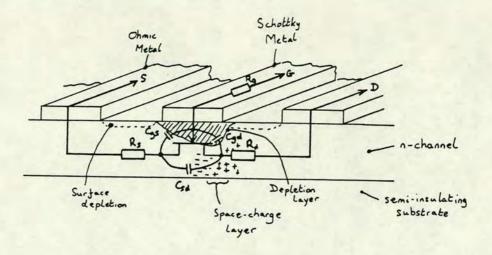

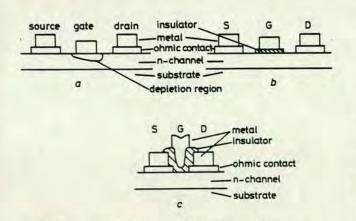

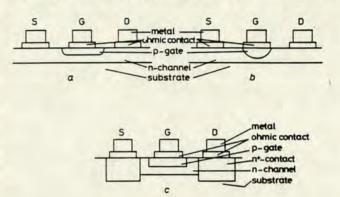

| Figure 2.17 | MESFET cross-section and electrical model. | 56    |

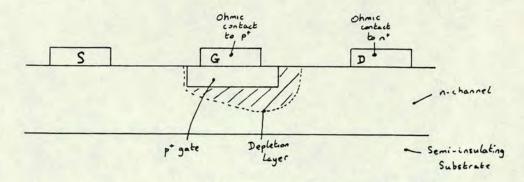

| Figure 2.18 | Cross-section through a JFET.              | 59    |

| Figure 2.19 | Low-pinchoff FET logic (LPFL) inverter.    | 61    |

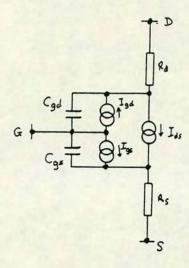

| Figure 3.1  | FET electrical model.                      | 64    |

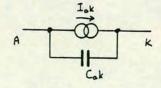

| Figure 3.2  | Diode model.                               | 65    |

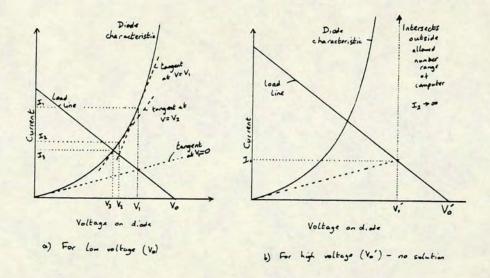

| Figure 3.3  | Schematic solution of the current flowing  | 66    |

|             | in a series combination of diode and       | 00    |

|             | resistor.                                  |       |

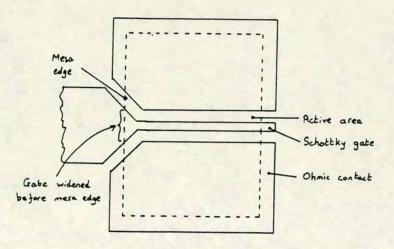

| Figure 3.4  | Design of tapered gate transistor.         | 71    |

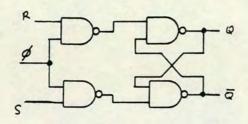

| Figure 3.5  | Basic bistable circuit.                    | 73    |

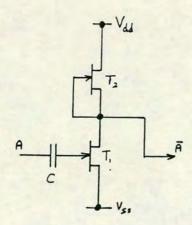

| Figure 3.6  | CCL Inverter.                              | 75    |

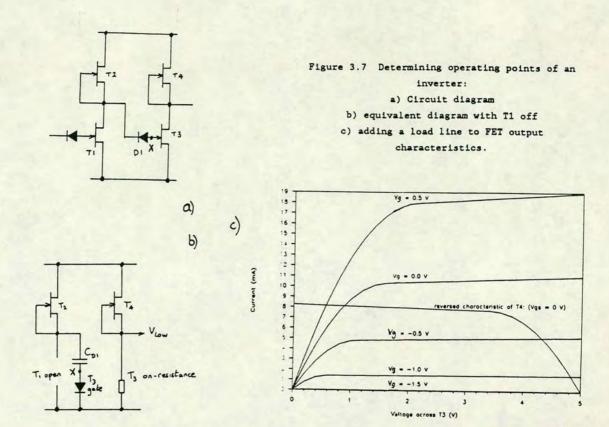

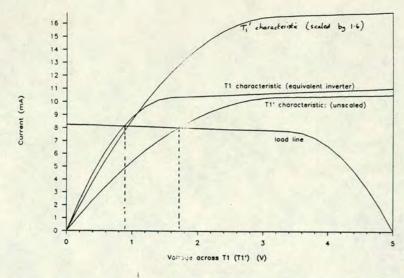

| Figure 3.7  | Determining operating points of an         | 77    |

|             | inverter.                                  |       |

| Figure 3.8  | Shift in logic-0 as capacitor charges up.  | 79    |

| Figure 3.9  | Model to indicate loss of coupling         | 80    |

|             | efficiency.                                | 00    |

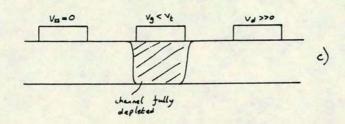

| Figure 3.10 | Depletion in a MESFET.                     | 82    |

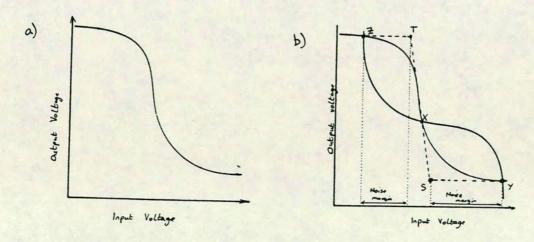

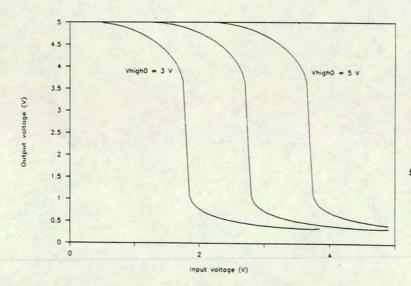

| Figure 3.11 | Transfer characteristics of an inverter.   | 82    |

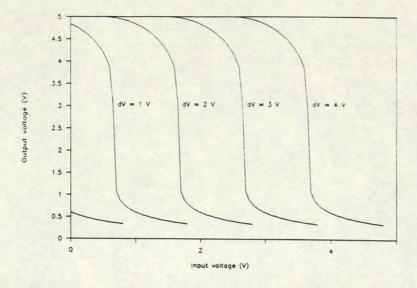

| Figure 3.12 | Transfer characteristics of a CCL inverter | 84    |

|             | with a fixed voltage level shift.          | 04    |

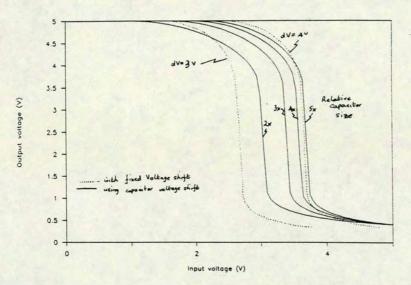

| Figure 3.13 | Transfer characteristics of a CCL inverter | 84    |

|             | for a logic-1 to logic-0 input transition  | 04    |

|             | for different sizes of capacitor.          |       |

| Figure 3.14 | Transfer characteristics of a CCL inverter | 84    |

|             | for a logic-0 to logic-1 input transition  | 04    |

|             | - input voltage prior to logic-1 to        |       |

|             | logic-O transition as parameter.           |       |

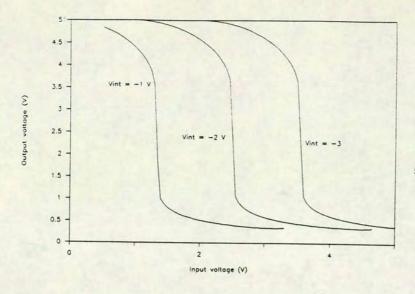

| Figure 3.15 | Transfer characteristics of a CCL inverter | 86    |

|             | for a logic-0 to logic-1 input transition  | 00    |

|             | - intermediate node voltage V as           |       |

|             | parameter.                                 |       |

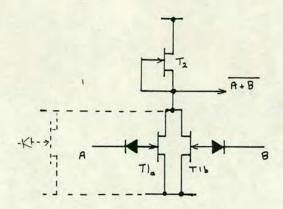

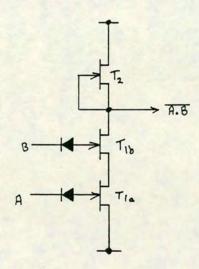

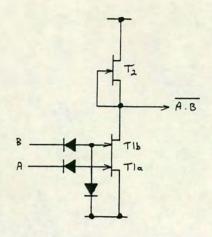

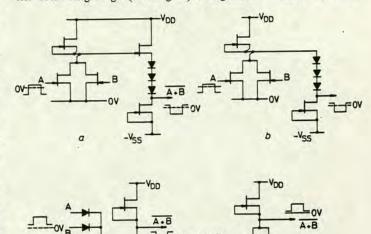

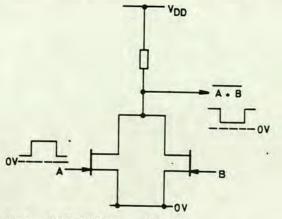

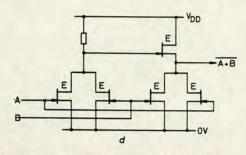

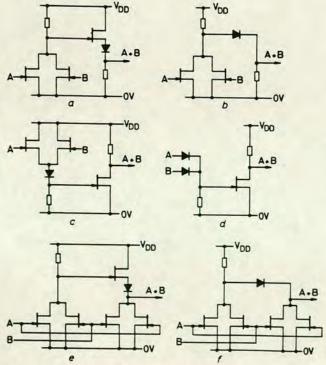

| Figure 3.16 | Two input CCL NOR gate.                    | 0.7   |

|             |                                            | 87    |

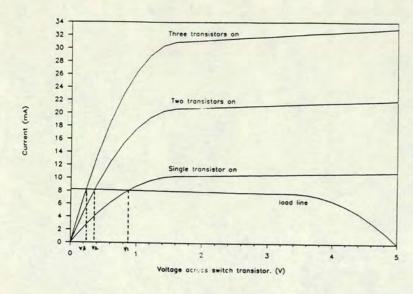

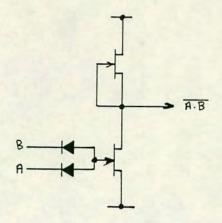

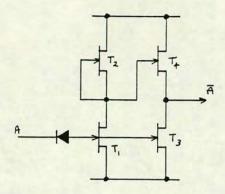

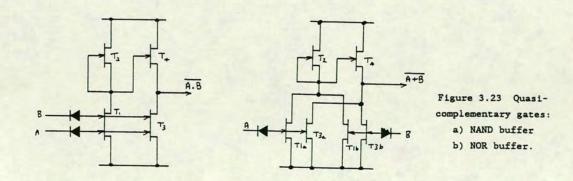

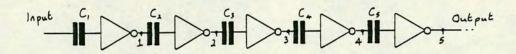

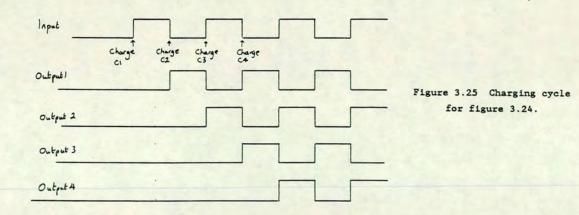

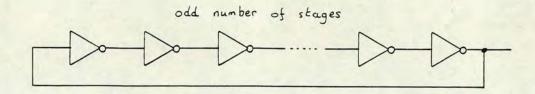

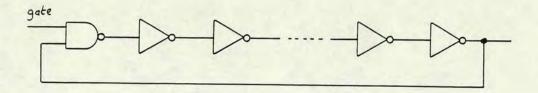

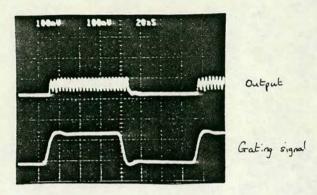

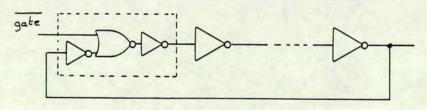

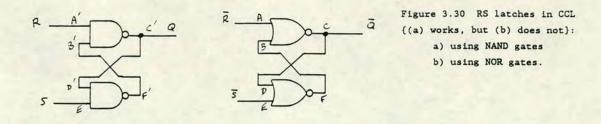

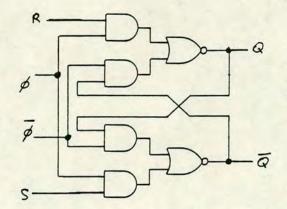

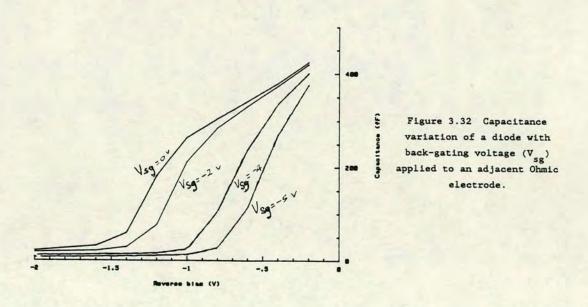

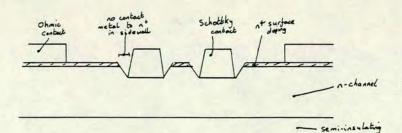

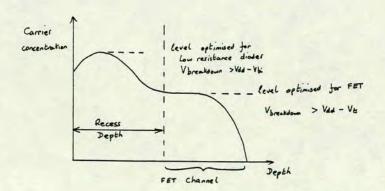

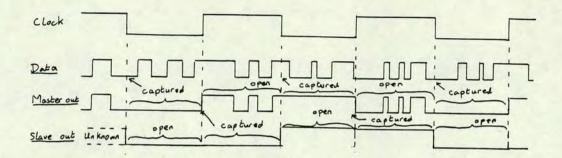

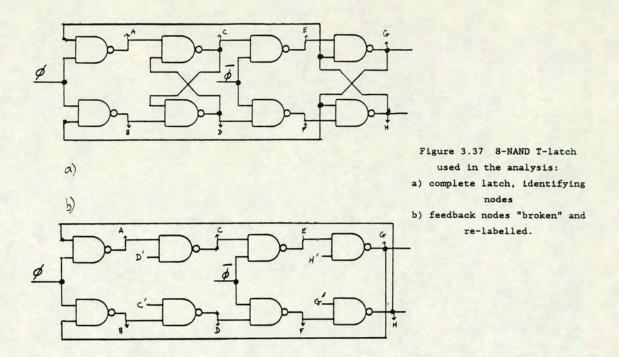

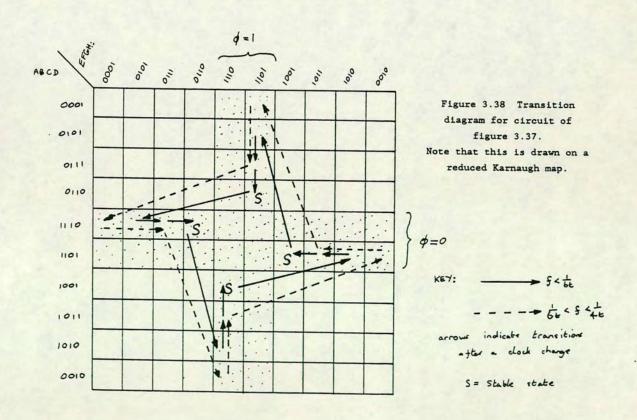

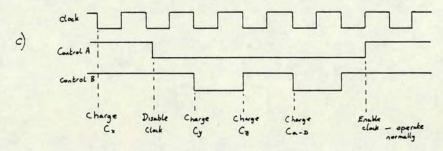

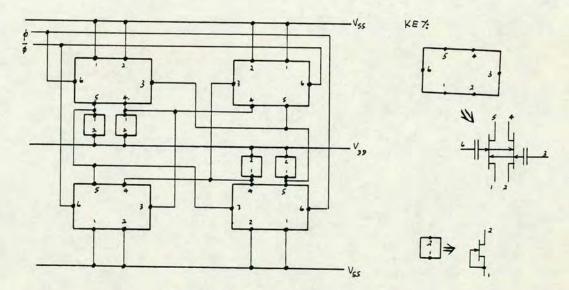

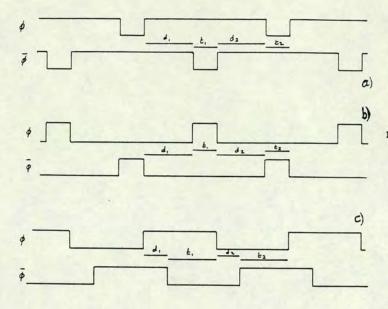

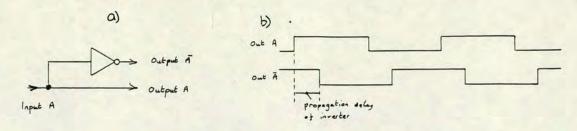

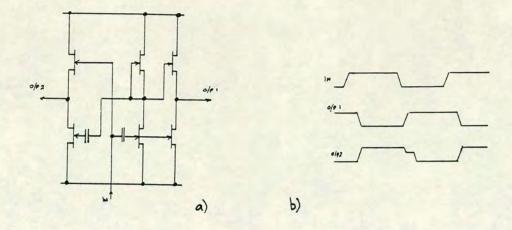

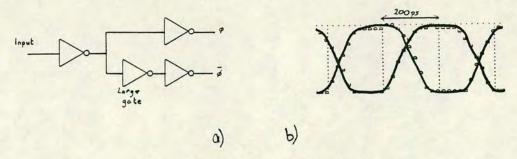

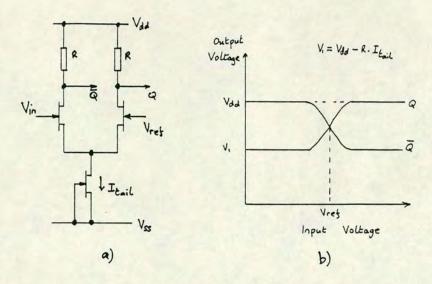

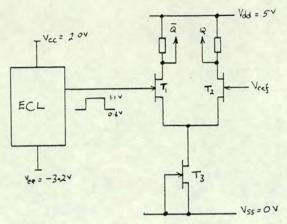

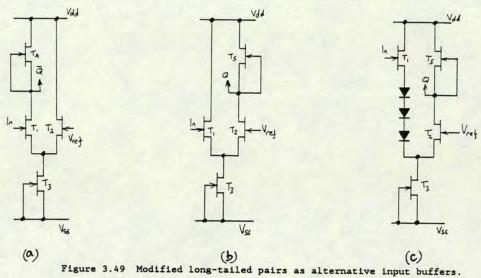

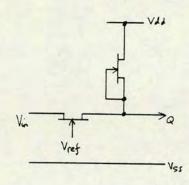

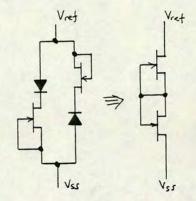

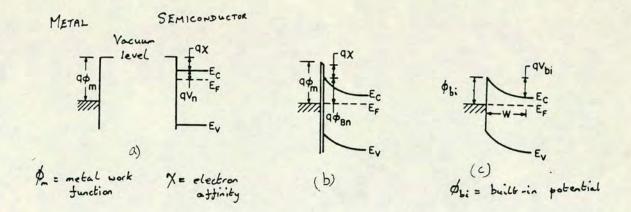

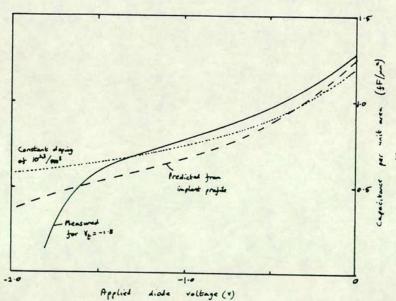

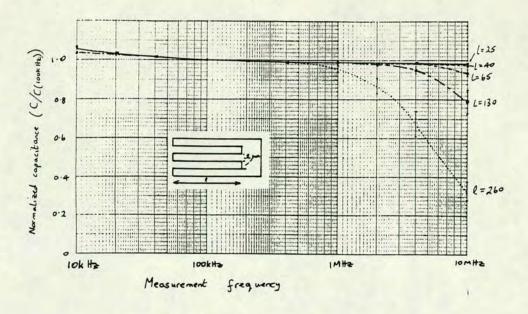

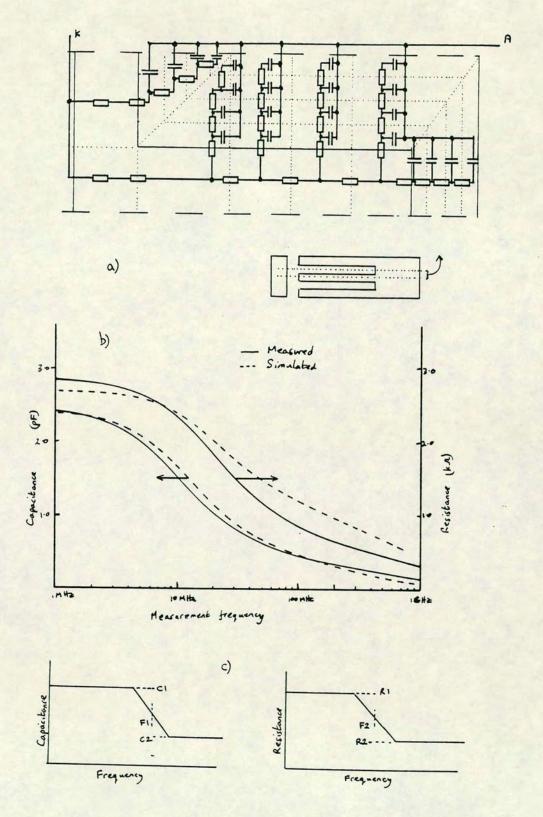

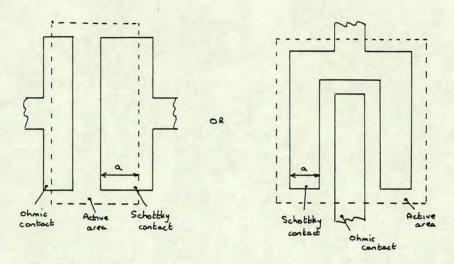

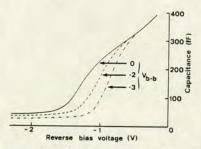

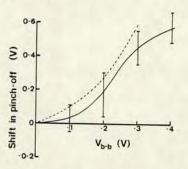

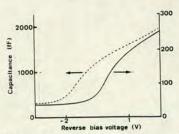

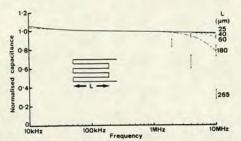

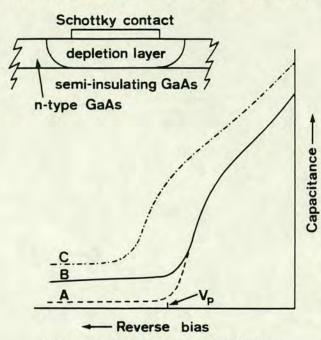

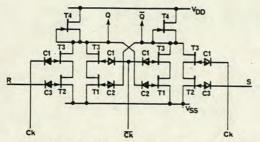

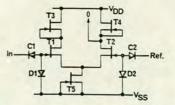

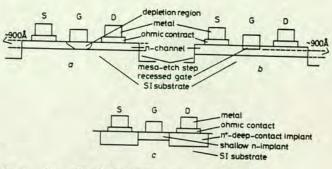

Figure: Page: Figure 3.17 Dependence of V on input states for NOR 88 gates. Figure 3.18 CCL NAND gate. 89 Figure 3.19 Shift in NAND gate Vol for scaled and 91 unscaled transistors. Figure 3.20 CCL NAND gate with guaranteed charging 92 paths. Figure 3.21 Multiple capacitor NAND gate. 92 Figure 3.22 Quasi-complementary buffer. 94 Figure 3.23 Quasi-complementary gates. 94 Figure 3.24 Charging a long inverter chain. 96 Figure 3.25 Charging cycle for figure 3.24. 96 Figure 3.26 Conventional ring oscillator. 97 Figure 3.27 Gated ring oscillator. 97 Figure 3.28 Output waveforms of a gated ring 98 oscillator. Figure 3.29 NOR gated ring oscillator, grouped to show 98 Boolean equivalence to figure 3.27. Figure 3.30 R.S. latches in CCL. 99 Figure 3.31 Alternative latch using AND-NOR gate, 100 which can be made to work in CCL. Figure 3.32 Capacitance variation of a diode with 101 back-gating voltage ( $V_{sg}$ ) applied to an adjacent Ohmic electrode. Figure 3.33 Cross-section of a "self-aligned", recess-105 etched dual-gate MESFET. Figure 3.34 Doping profile for recessed-gate process. 108 Figure 3.35 Detailed cross section through GaAs IC 110 process used in this work. Figure 3.36 Schematic timing diagram for a master-113 slave latch. Figure 3.37 8-NAND T-latch used in the analysis. 116 Figure 3.38 Transition diagram for circuit of figure 117 3.37. Figure 3.39 AND-NOR divider. 118 Figure 3.40 8-NAND T-latch showing capacitor 120 placements. Figure 3.41 Operation of AND-NOR latch in CCL. 123 Figure 3.42 Physical layout of AND NOR latch. 124 Figure 3.43 Non-ideal phasing of the complementary 126 clock signals. Figure 3.44 Simplest complementary signal generator. 129 Figure 3.45 Improved complementary signal generator. 130 Figure 3.46 Final complementary clock generator. 131 Figure 3.47 Long-tailed pair. 132 Figure 3.48 Long tailed pair input amplifier 136 interfacing with ECL. Figure 3.49 Modified long-tailed pairs as alternative 137 input buffers. Figure 3.50 Common gate input amplifier. 138 Figure 3.51 Input protection circuit. 138

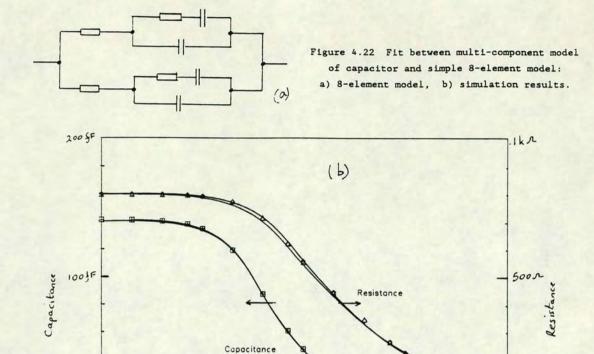

|             | Figure:                                                                 | Page: |

|-------------|-------------------------------------------------------------------------|-------|

| T: / 1      |                                                                         |       |

| Figure 4.1  | Band structure and definitions for a metal and semiconductor interface. | 140   |

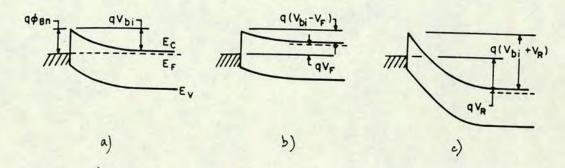

| Figure 4.2  |                                                                         | 141   |

| Figure 4.3  |                                                                         | 145   |

| Figure 4.4  |                                                                         | 147   |

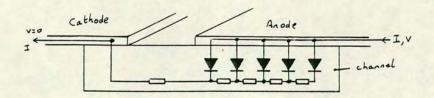

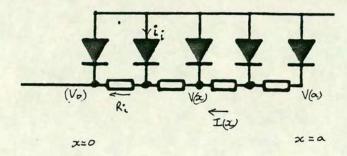

| E           | diode model.                                                            |       |

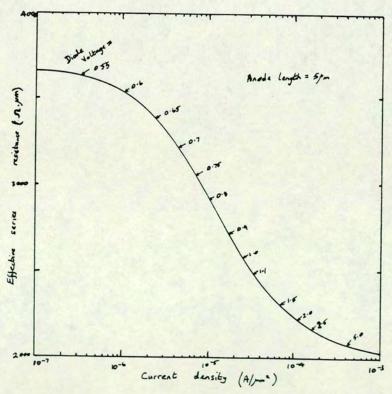

| Figure 4.5  | Effective series resistance of a                                        | 147   |

|             | distributed diode.                                                      | -     |

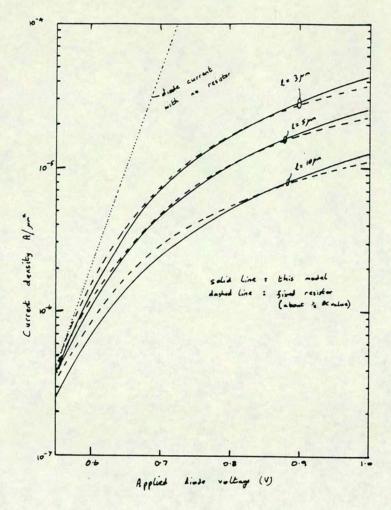

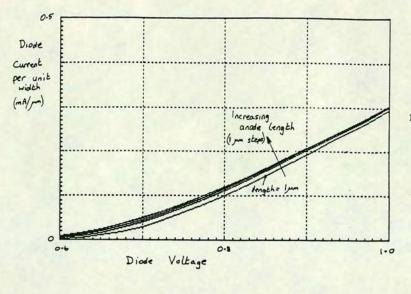

| Figure 4.6  | I-V relationship of a distributed diode                                 | 148   |

|             | operated at high current density.                                       |       |

| Figure 4.7  |                                                                         | 148   |

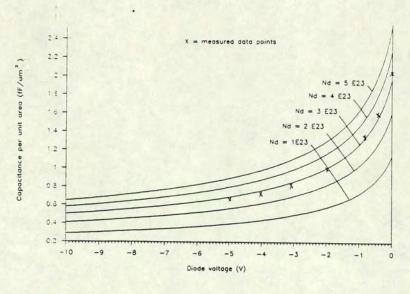

| Figure 4.8  |                                                                         | 150   |

|             | constant doping.                                                        |       |

| Figure 4.9  |                                                                         | 150   |

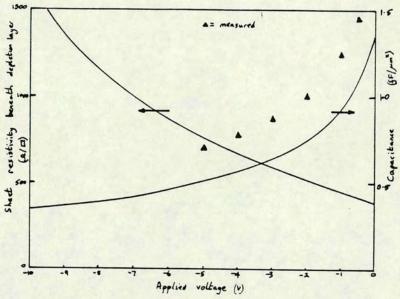

|             | resistivity for a deep implant into semi-                               |       |

|             | insulating GaAs.                                                        |       |

| Figure 4.1  |                                                                         | 150   |

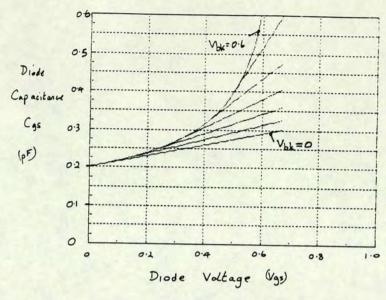

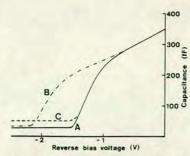

| Figure 4.1  | 1 Capacitance of a Schottky junction under                              | 153   |

|             | forward bias.                                                           |       |

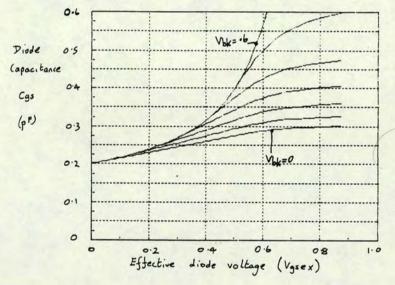

| Figure 4.1  |                                                                         | 153   |

|             | diode voltage, allowing for the current                                 |       |

|             | flowing in the extrinsic resistor.                                      |       |

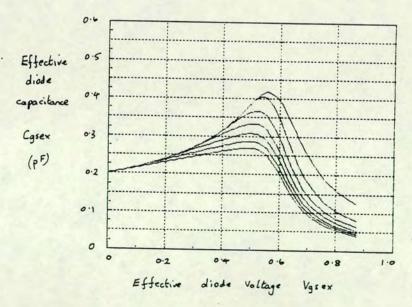

| Figure 4.1  |                                                                         | 153   |

|             | effective capacitance, derived from dQ/dV.                              |       |

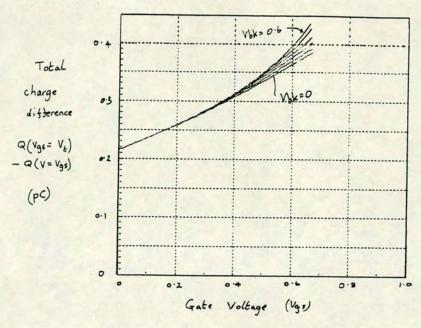

| Figure 4.1  | 4 Effect of breakpoint used in model of                                 | 155   |

|             | capacitor on total charge switched from on                              |       |

|             | to off.                                                                 |       |

| Figure 4.1  | Todatica co                                                             | 155   |

|             | switch a transistor off according to this                               |       |

| T           | model of capacitance.                                                   |       |

| Figure 4.1  | J abbamba Lot                                                           | 155   |

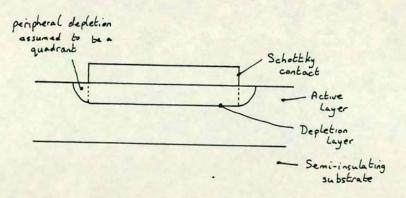

| F: / 1      | depletion layer periphery.                                              |       |

| Figure 4.1  | i deptecton                                                             | 157   |

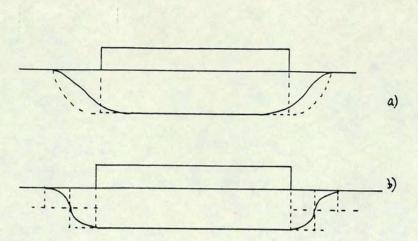

| Figure / 1  | periphery.                                                              |       |

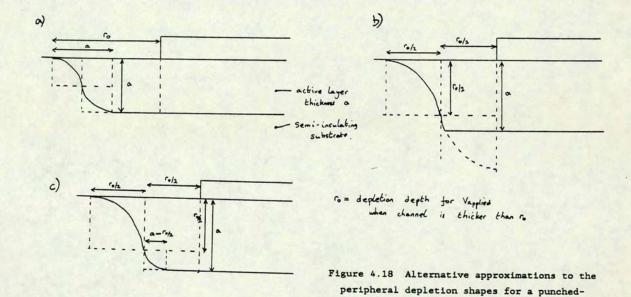

| Figure 4.1  | Transfer to the                                                         | 157   |

|             | peripheral depletion shapes for a punched-                              |       |

| Figure 4.1  | through layer (V <v<sub>t).</v<sub>                                     |       |

| rigure 4.1  | t approximation                                                         | 157   |

| Figure 4.2  | beyond threshold.                                                       |       |

| Figure 4.2  | The state of difficult diodes.                                          | 158   |

| rigure 4.2. | b b criects in                                                          | 159   |

| Figure 4.2  | digitated diodes.                                                       | 4 144 |

| 116ulc 4.2. | manufacture model of                                                    | 161   |

| Figure 4.2  | capacitor and simple 8-element model.                                   |       |

| 116ulo 4.2. | Total Total Total Total                                                 | 162   |

| Figure 4.2  | frequency usage.                                                        | 1000  |

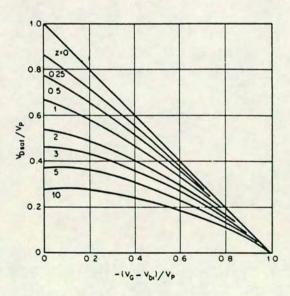

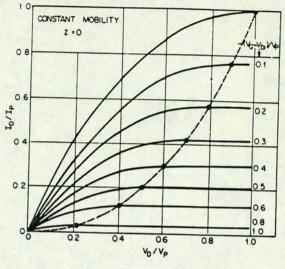

| Figure 4.2  | Characteristics.                                                        | 164   |

| -5          | characteristic.                                                         | 166   |

| Figure 4.2  |                                                                         |       |

|             | Saturation voltage using velocity-field characteristic of figure 4.25.  | 166   |

|             | THE TOTAL OF TIRE 4. Z.                                                 |       |

| I             | Figure:                                                                  | Page: |

|---------------|--------------------------------------------------------------------------|-------|

| Figure 4.27   | Lincoriaina of antonomic contract                                        | 1.00  |

| rigule 4.27   | Linearising of saturation current using velocity-field characteristic of | 167   |

|               | figure 4.25.                                                             |       |

| Figure 4.28   | Transconductance obtained from using                                     | 167   |

|               | velocity-field characteristic of figure 4.25.                            |       |

| Figure 4.29   | Output characteristic of a MESFET                                        | 160   |

| Figure 4.30   | Fit between measured and simulated output                                | 169   |

| 116416 4.30   | characteristics for widely different                                     | 171   |

| Earnest a val | transistors, using new model.                                            |       |

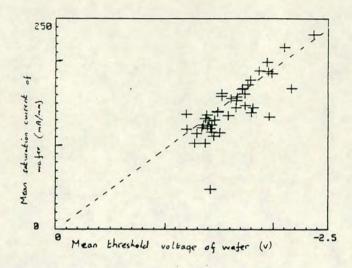

| Figure 4.31   | Correlation between threshold voltage and                                | 172   |

|               | saturation current of FETs.                                              |       |

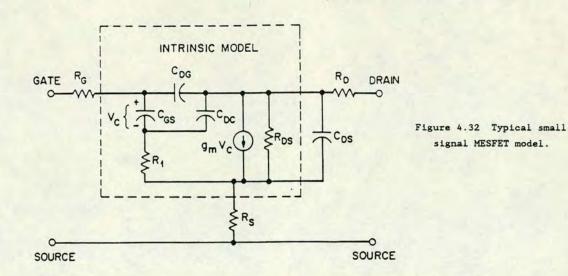

| Figure 4.32   | Typical small signal MESFET model.                                       | 173   |

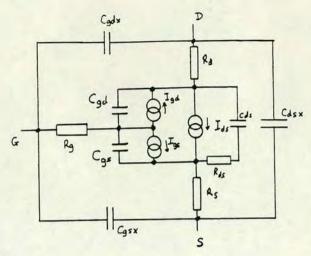

| Figure 4.33   | Large signal model of a MESFET.                                          | 175   |

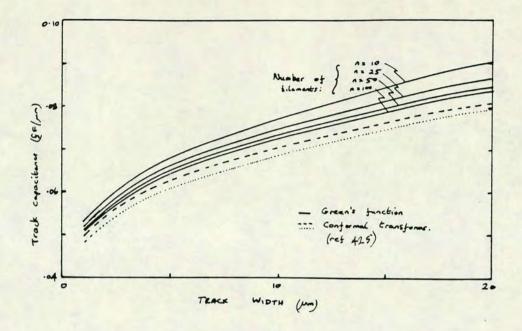

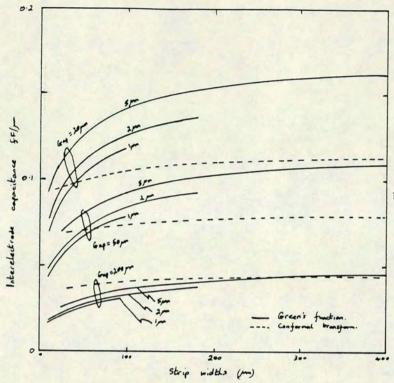

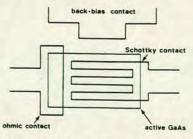

| Figure 4.34   | Capacitance of a single track an GaAs.                                   | 179   |

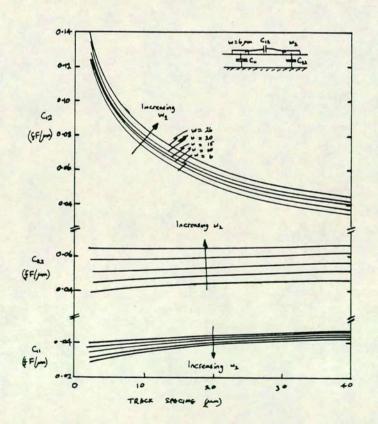

| Figure 4.35   | Capacitance between a pair of equal sized                                | 180   |

| Figure 4 26   | tracks on GaAs.                                                          | 200   |

| Figure 4.36   | Capacitance matrix for unequal tracks on GaAs.                           | 180   |

| Figure 4.37   | Models for electrode capacitance of an                                   | 183   |

| Figure 4.38   | FET.                                                                     |       |

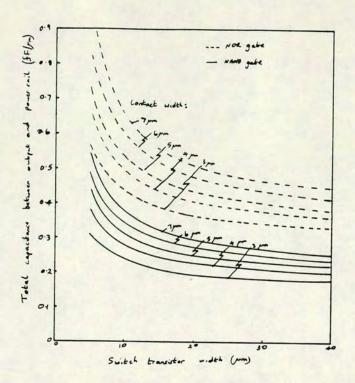

| rigure 4.56   | Output capacitance vs switch width for NOR and NAND gates.               | 184   |

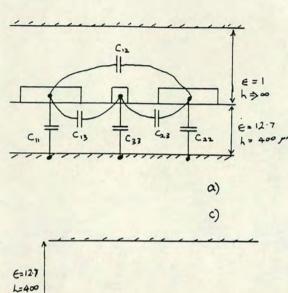

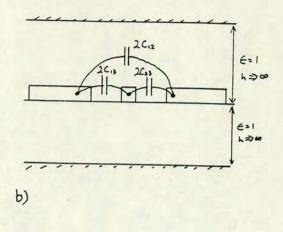

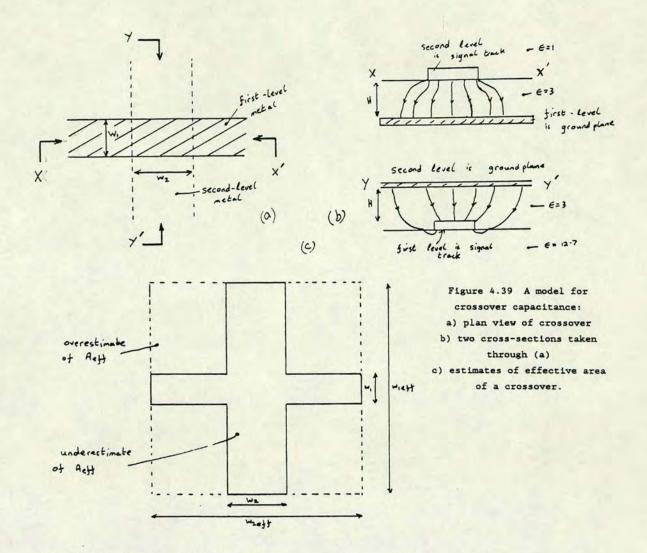

| Figure 4.39   | A model for crossover capacitance.                                       | 185   |

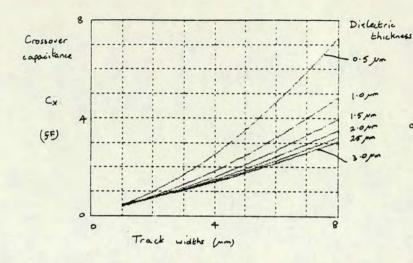

| Figure 4.40   | Crossover capacitances for equal sized                                   | 187   |

|               | tracks.                                                                  | 107   |

| Figure 4.41   | Effect of metal thickness (in 0.1 um                                     | 187   |

|               | steps) on crossover capacitance of 6 um                                  | 10,   |

| Fi / / 0      | tracks.                                                                  |       |

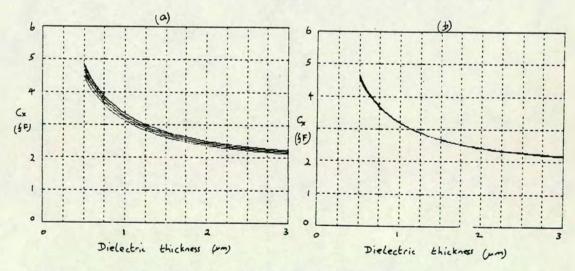

| Figure 4.42   | Crossover capacitance for dissimilar                                     | 188   |

| Pierres E 1   | tracks.                                                                  |       |

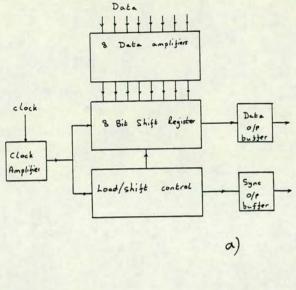

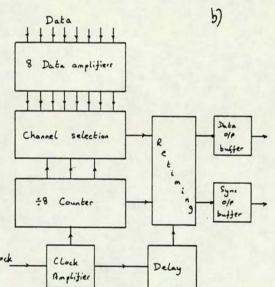

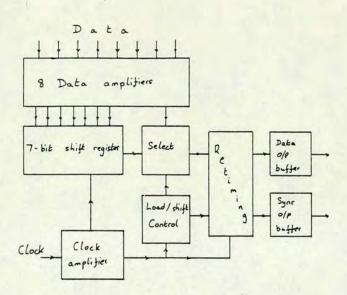

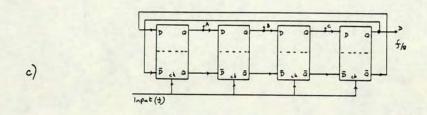

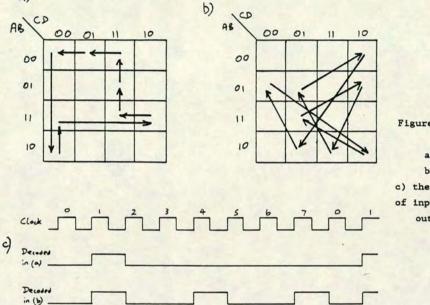

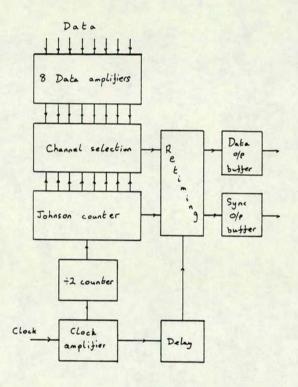

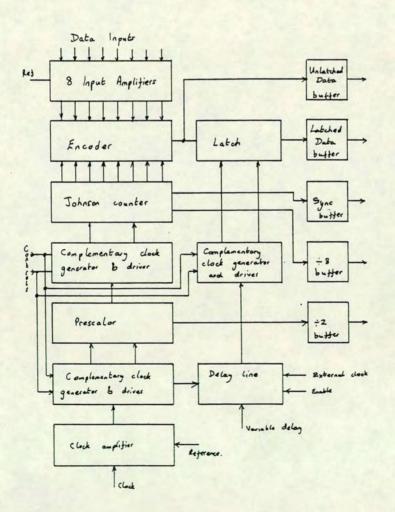

| Figure 5.1    | Block diagrams of alternative 8-channel multiplexers.                    | 193   |

| Figure 5.2    |                                                                          |       |

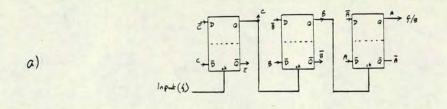

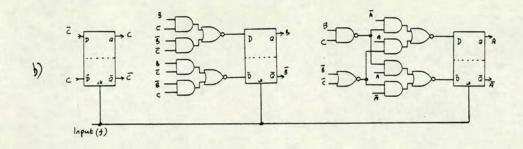

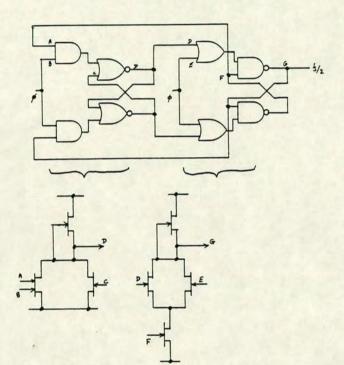

| Figure 5.3    | Regrouped shift-register multiplexer.                                    | 194   |

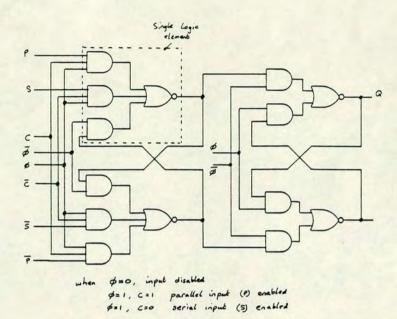

| Figure 5.4    | Multi-input gate used in a shift register.                               | 195   |

|               | The use of two half-speed multiplexers to reduce the speed requirements. | 197   |

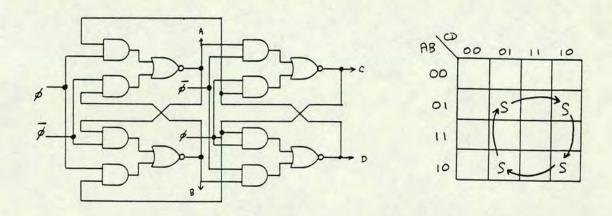

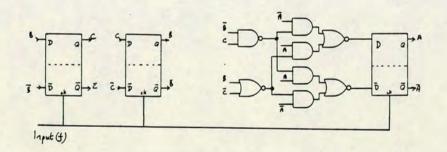

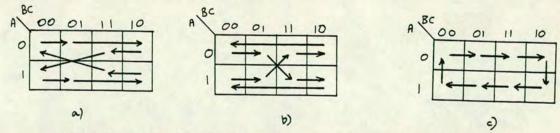

| Figure 5.5    | Various modulo-8 counters.                                               | 100   |

| Figure 5.6    | Synchronous modulo-8 counter (non-binary).                               | 198   |

| Figure 5.7    | Karnaugh transition map of modulo-8                                      | 199   |

|               | counters.                                                                | 199   |

| Figure 5.8    | Logic diagram of Gray code modulo-8                                      | 200   |

|               | counter.                                                                 |       |

| Figure 5.9    | Count sequence of 4-stage Johnson counter.                               | 201   |

| Figure 5.10   | Johnson counter sequences.                                               | 201   |

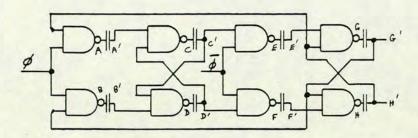

| Figure 5.11   | Improved decoding from a 4-stage Johnson                                 | 202   |

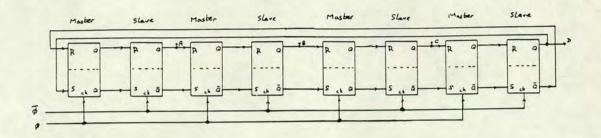

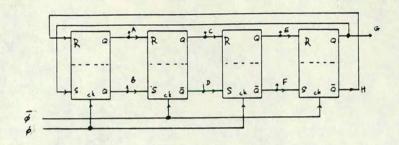

| Figure 5.12   | counter.                                                                 | 200   |

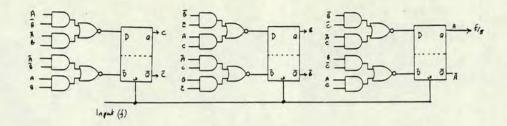

|               | 4-stage Johnson counter with master-slave gates expanded.                | 203   |

| Figure 5.13   | Final choice of counter.                                                 | 001   |

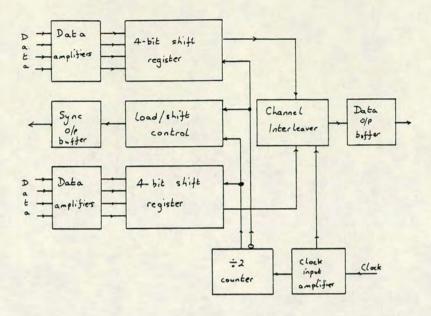

| Figure 5.14   | Revised multiplexer block diagram.                                       | 204   |

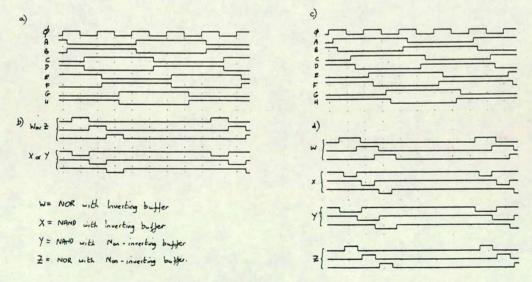

| Figure 5.15   | Schematic waveforms from Johnson counter.                                | 204   |

|               | Tom Johnson Counter.                                                     | 204   |

|        | F    | Figure:                                                       | Page: |

|--------|------|---------------------------------------------------------------|-------|

|        |      |                                                               |       |

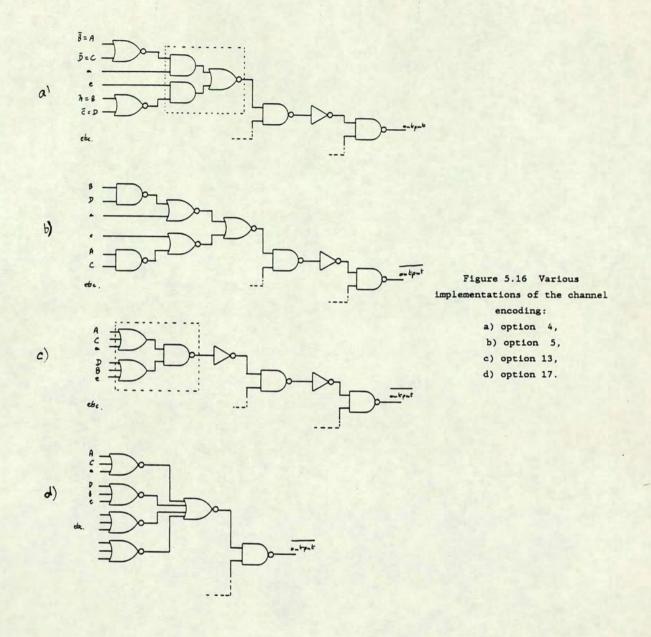

| Figure | 5.16 | Various implementations of the channel encoding.              | 209   |

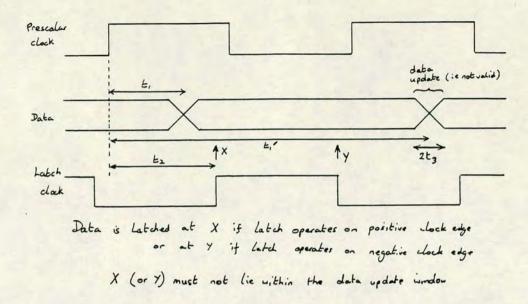

| Figure | 5.17 | Critical timing path for correct latching of data.            | 210   |

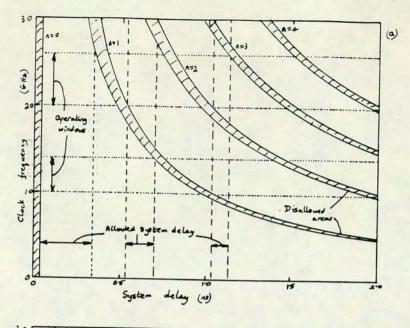

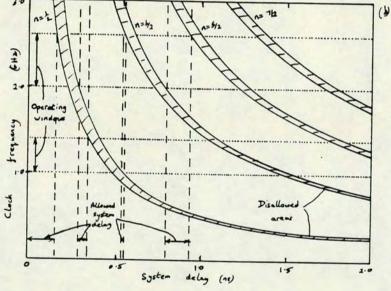

| Figure | 5.18 | Timing analysis for multiplexer operation.                    | 212   |

| Figure |      | Circuit to allow switching of operation of                    | 212   |

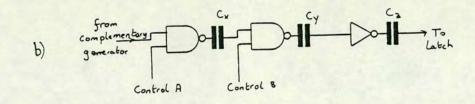

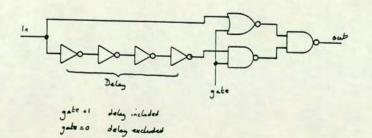

| Figure | 5 20 | latch by 180°.<br>Circuit to allow variation of the delay     | 010   |

|        |      | time.                                                         | 212   |

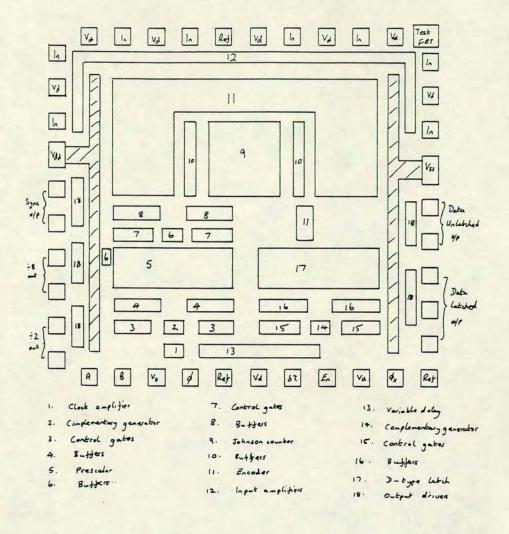

| Figure | 5.21 | Preliminary floor plan and pad layout of the multiplexer.     | 216   |

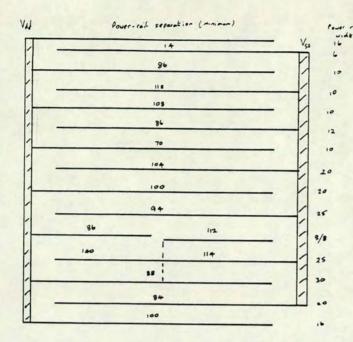

| Figure | 5.22 | Schematic layout of power distribution                        | 219   |

|        |      | showing preliminary allocation of space and track widths.     | -     |

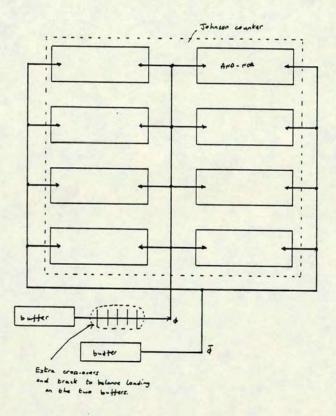

| Figure | 5.23 | Balancing of loading on the clock                             | 221   |

|        |      | distribution to the Johnson counter.                          | 221   |

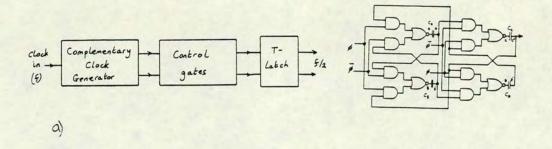

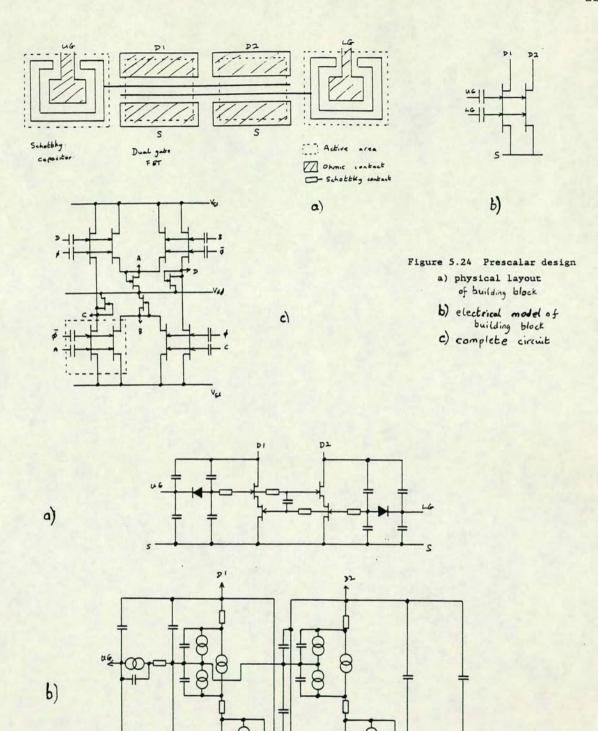

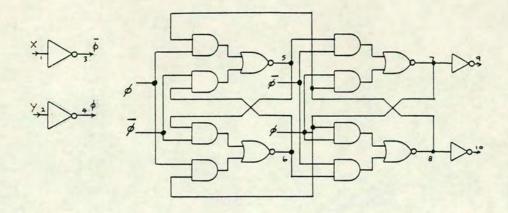

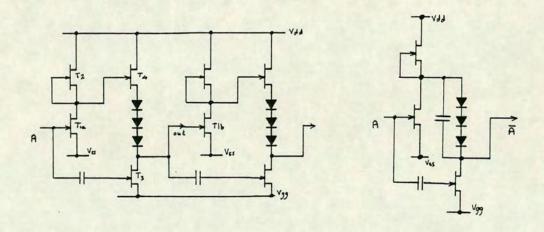

| Figure | 5.24 | Prescalar design.                                             | 224   |

| Figure | 5.25 | Models for the elements of figure 5.24b.                      | 224   |

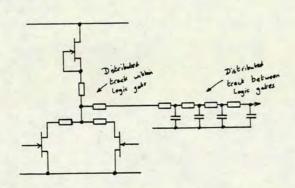

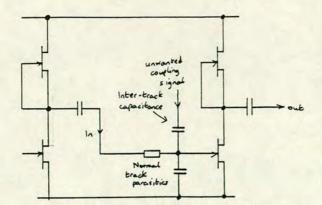

| Figure | 5.26 | Parasitic elements within and between                         | 225   |

|        |      | logic gates.                                                  | 220   |

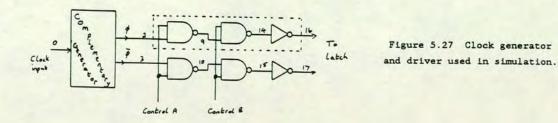

| Figure | 5.27 | Clock generator and driver used in simulation.                | 226   |

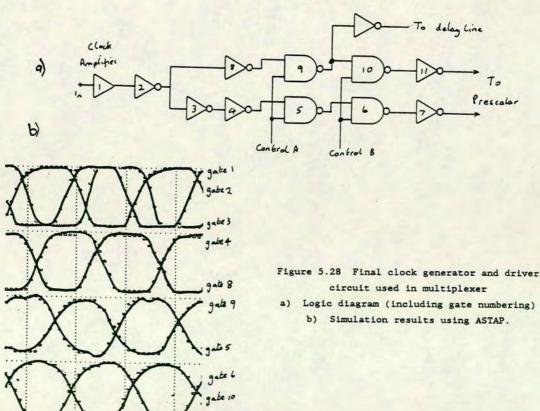

| Figure | 5.28 | Final clock generator and driver circuit                      | 230   |

|        |      | used in multiplexer.                                          | 250   |

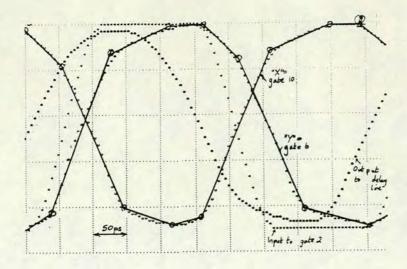

| Figure | 5.29 | Simulated output from gates 6 and 10,                         | 231   |

|        |      | showing piecewise approximation to the waveforms.             |       |

| Figure | 5.30 | Circuit used for prescalar simulations.                       | 232   |

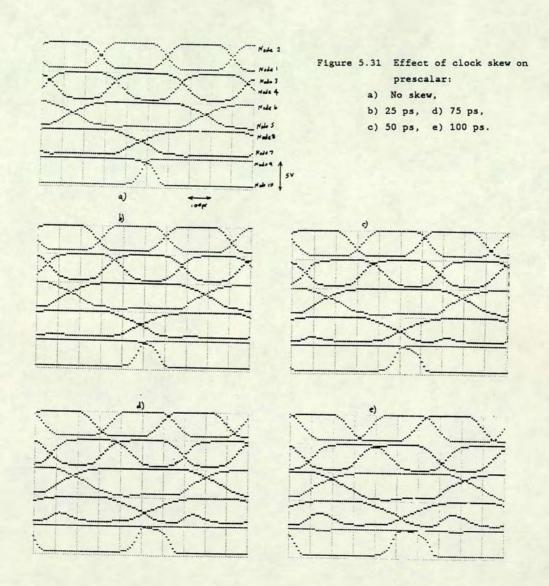

| Figure | 5.31 | Effect of clock skew on prescalar.                            | 233   |

| Figure |      | Final block diagram of multiplexer.                           | 234   |

| Figure | 5.33 | Simulated waveforms for T-latch driven at                     | 235   |

|        |      | high speed.                                                   | 233   |

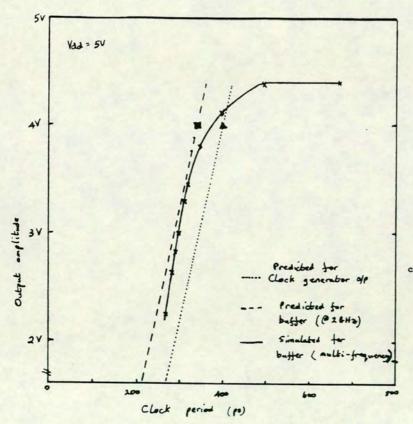

| Figure | 5.34 | Roll-off in voltage levels for high                           | 236   |

|        |      | frequency operation: comparison of                            | 250   |

|        |      | prediction and simulation.                                    |       |

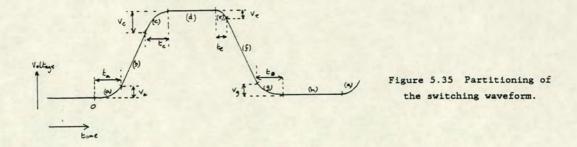

| Figure |      | Partitioning of the switching waveform.                       | 237   |

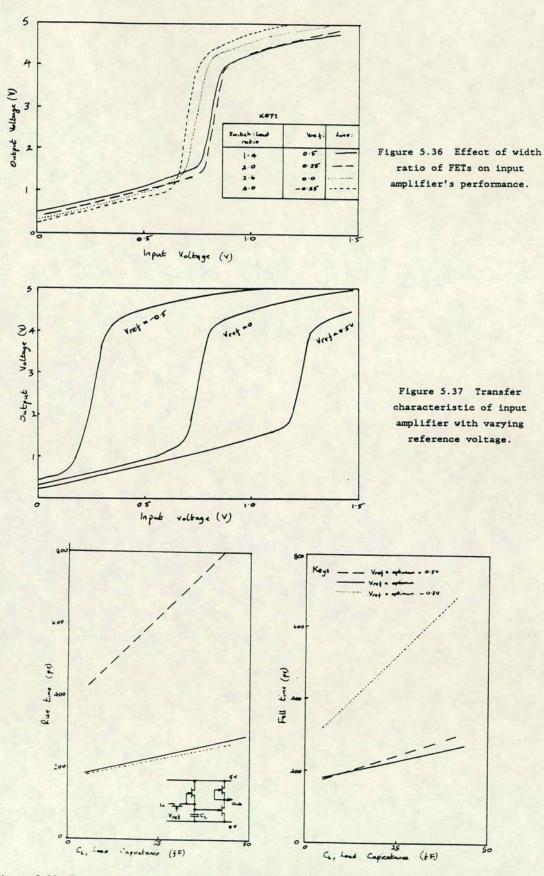

| Figure | 5.36 | Effect of width ratio of FETs on input                        | 239   |

|        |      | amplifier's performance.                                      | 200   |

| Figure | 5.37 | Transfer characteristic of input amplifier                    | 239   |

|        |      | with varying reference voltage.                               |       |

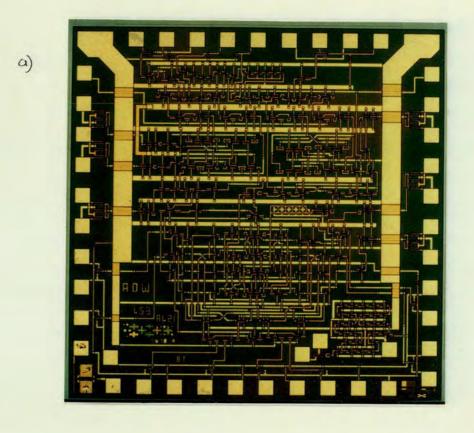

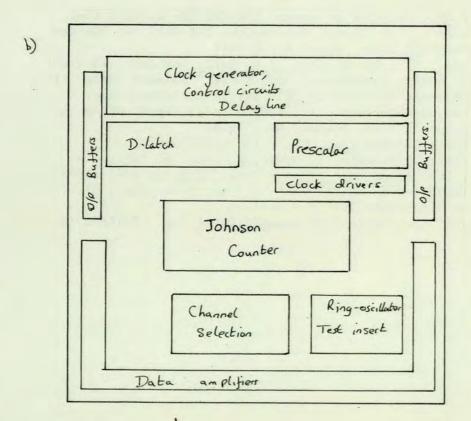

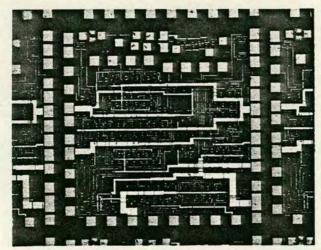

| Figure |      | Finished chip layout.                                         | 239   |

| Figure | 5.39 | Variation in input amplifier transition                       | 242   |

|        |      | times with load capacitance and reference voltage             |       |

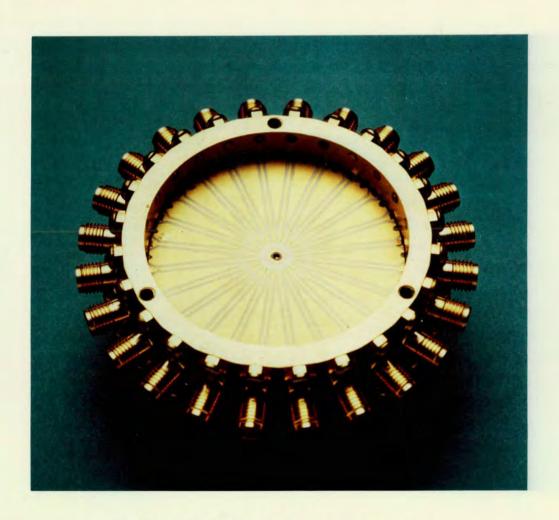

| Figure |      | Photograph of high frequency test jig.                        | 243   |

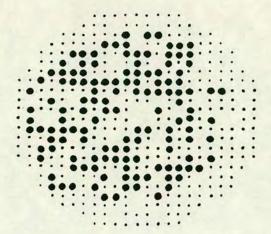

| Figure | 5.41 | Wafer map of multiplexer yield at low-                        | 245   |

| Figure | 5 /2 | frequency functional test.                                    |       |

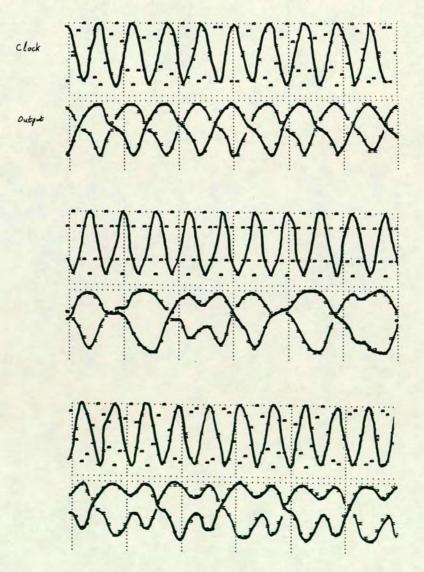

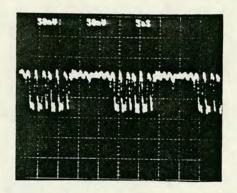

| Figure | 3.42 | Multiplexer operating at 2.8 GHz with arbitrary data pattern. | 246   |

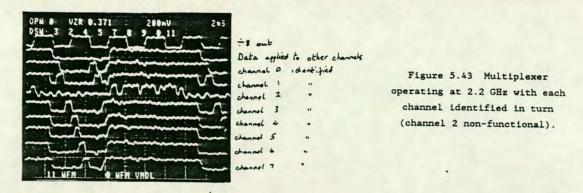

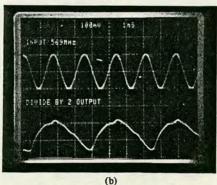

| Figure | 5.43 | Multiplexer operating at 2.2 GHz with each                    | 246   |

|        |      | channel identified in turn.                                   | 240   |

|             | Figure:                                                                                                     | Page: |

|-------------|-------------------------------------------------------------------------------------------------------------|-------|

|             |                                                                                                             |       |

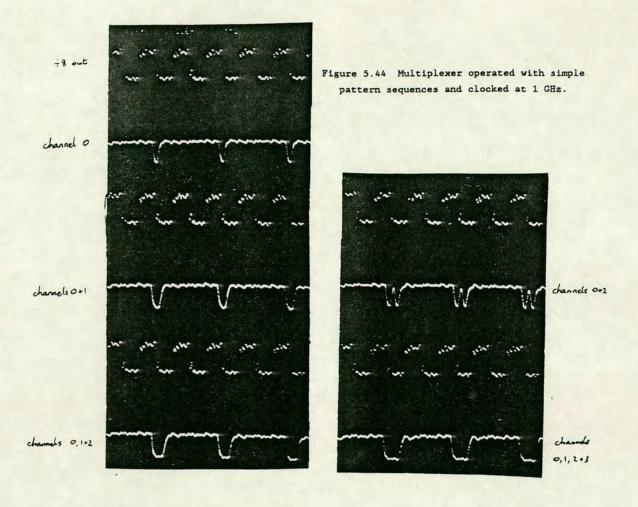

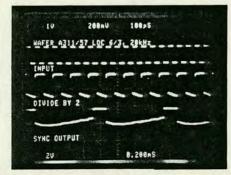

| Figure 5.44 | Multiplexer operated with simple pattern sequences and clocked at 1 GHz.                                    | 247   |

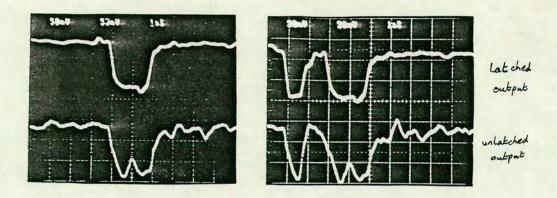

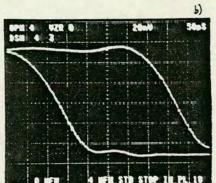

| Figure 5.45 | Operation of the output latch to clean-up the data pulses.                                                  | 248   |

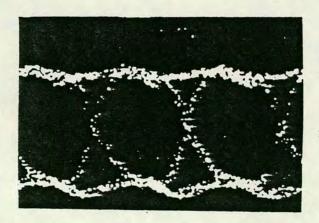

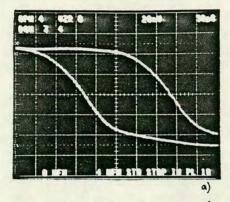

| Figure 5.46 | Eye diagram of a D-type latch operating at 2 GHz.                                                           | 248   |

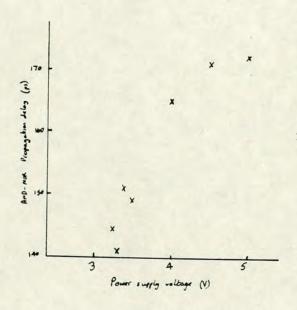

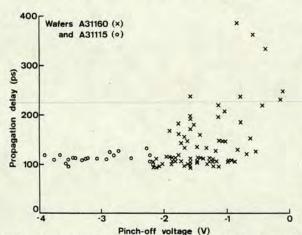

| Figure 5.47 | Variation of AND-NOR propagation delay with circuit operating voltage - obtained directly from multiplexer. | 249   |

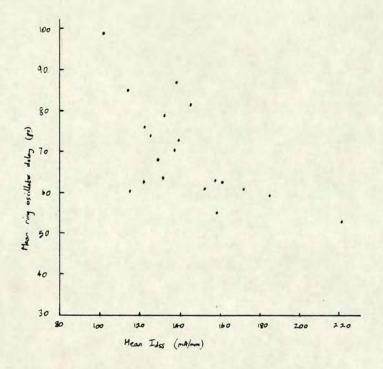

| Figure 5.48 | Variation of ring oscillator delay with saturation current.                                                 | 250   |

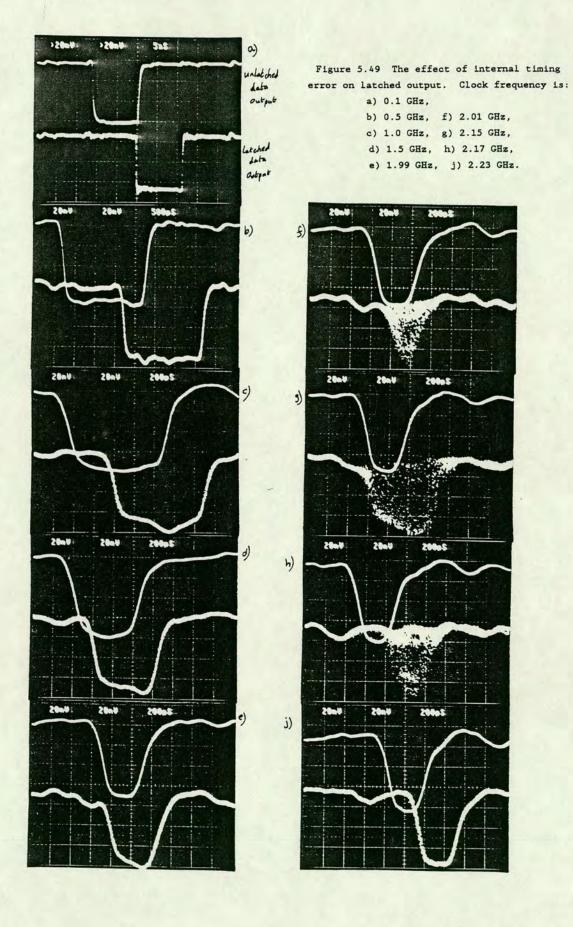

| Figure 5.49 | The effect of internal timing error on latched output.                                                      | 251   |

| Figure 5.50 | Measurement of the shift in one edge of latched output data, due to switching the programmable delay.       | 253   |

| Figure 5.51 | input frequency of 2.3 GHz - no DC bias added to sine wave.                                                 | 254   |

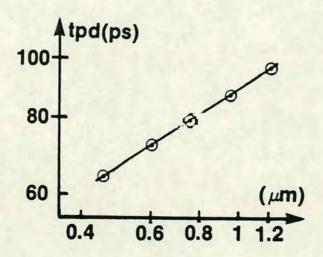

| Figure 6.1  | Increase in performance as gate-length is shrunk.                                                           | 261   |

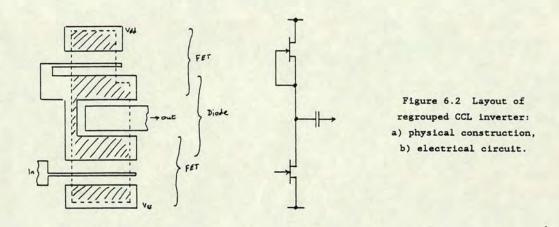

| Figure 6.2  | Layout of regrouped CCL inverter.                                                                           | 263   |

| Figure 6.3  | Model for crosstalk in modified CCL.                                                                        | 264   |

| Figure 6.4  | Capacitor diode FET logic inverter (CDFL)                                                                   | 267   |

| Figure 6.5  | AND-NOR: OR-NAND divider and constituent gates.                                                             | 274   |

| Figure 6.6  | BFL Inverter converted to CEFL.                                                                             | 275   |

| Figure 6.7  | CEFL extension to CDFL inverter.                                                                            | 275   |

| Figure 6.8  | Extending CEFL to NOR gates.                                                                                | 277   |

## List of tables.

| Marie I | No. 14 | Table:                                                     | Page: |

|---------|--------|------------------------------------------------------------|-------|

|         |        |                                                            |       |

| Table   | 3.1    | Truth table for a J-K latch.                               | 114   |

| Table   | 3.2    | Analysis of the circuit in figure 3.37.                    | 117   |

| Table   | 3.3    | Charging of the capacitors in an 8-NAND CCL T-latch.       | 121   |

| Table   | 4.1    | Crossover capacitance modelled as a circular disc.         | 186   |

| Table   | 5.1    | Shift register versus direct addressing.                   | 196   |

| Table   | 5.2    | Comparison of encoding techniques.                         | 208   |

| Table   | 5.3    | Pad count for the 8:1 MUX.                                 | 214   |

| Table   | 5.4    | Track loading on Johnson counter outputs.                  | 222   |

| Table   | 5.5    | Switching transients for circuit of figure 5.27.           | 227   |

| Table   | 5.6    | Switching transients for fig 5.27 with $V_{-}=-1.5$ V.     | 227   |

| Table   | 5.7    | Switching transients for fig 5.27 vs V.                    | 228   |

| Table   | 5.8    | Switching transients vs gate width.                        | 229   |

| Table   | 5.9    | Switching transients for fig 5.27 (new sizes).             | 230   |

| Table   | 5.10   | Predicted propagation delay of AND-NOR gate vs load width. | 232   |

| Table   | 5.11   | Noise spike amplitude vs clock skew.                       | 233   |

| Table   | 5.12   | Timing analysis of the multiplexer.                        | 253   |

| Table   | 6.1    | AND: NOR T-Latch sequence.                                 | 277   |

## List of symbols used in equations.

| Symbol:                                                               | Definition:                                              |

|-----------------------------------------------------------------------|----------------------------------------------------------|

|                                                                       |                                                          |

| a                                                                     | channel thickness                                        |

| A                                                                     | voltage amplitude                                        |

| A <sub>eff</sub>                                                      | effective cross-over area                                |

| C                                                                     | capacitance or capacitance per unit area                 |

| Cds                                                                   | drain-source capacitance                                 |

| C <sub>dsx</sub>                                                      | drain-source metal capacitance                           |

| Ceff<br>Cad                                                           | effective capacitance of cross-over                      |

| Cod                                                                   | gate-drain capacitance                                   |

| C <sub>gd</sub>                                                       | gate-drain metal capacitance                             |

| Com                                                                   | gate-source capacitance                                  |

| Cgsx                                                                  | gate-source metal capacitance                            |

| Cgs<br>CLgsx                                                          | capacitance of a metal disc on first interconnect level  |

| C                                                                     | capacitance at zero bias (for a diode junction)          |

| C                                                                     | peripheral capacitance (per unit length)                 |

| Cn                                                                    | capacitance of a metal disc on second interconnect       |

|                                                                       | level                                                    |

| d <sub>1,2</sub>                                                      | system delay times                                       |

| C C C P C U C C T C T C T C T C T C T C T C T C                       | electric field                                           |

| f                                                                     | clock frequency                                          |

| f                                                                     | effective fan out                                        |

| f <sub>stop</sub>                                                     | frequency at which latched data disappears               |

| -111                                                                  | mutual transconductance                                  |

| g <sub>meff</sub>                                                     | available transconductance in a real device current      |

| I <sub>ds</sub>                                                       | drain-source current                                     |

| Idas                                                                  | FET saturation current at zero gate bias                 |

| I dss I I sat                                                         | saturation current of a diode                            |

| Isat                                                                  | FET saturation current                                   |

| K                                                                     | Boltzmann constant                                       |

| k <sub>1</sub>                                                        | arbitrary constant used in exponential roll-off equation |

| m                                                                     | power-law fitting parameter for FET saturation region    |

| n                                                                     | ideality factor of diode                                 |

| n                                                                     | integer multiplier                                       |

| N <sub>d</sub>                                                        | doping level in channel                                  |

| q                                                                     | electron charge                                          |

| Q <sub>tot</sub>                                                      | total impurity charge in a conducting channel            |

| r <sub>1</sub> , r <sub>0</sub>                                       | depletion layer thickness at a given reverse bias:       |

| D                                                                     | used in periphery conditions                             |

| R <sub>o</sub>                                                        | diode resistance                                         |

| K s                                                                   | source resistance                                        |

| K <sub>x</sub>                                                        | slew rate during period x                                |

| R° R° R° t t t <sub>1,2</sub> T                                       | propagation delay                                        |

| T1,2                                                                  | pulse widths                                             |

| v                                                                     | absolute temperature                                     |

| v<br>v<br>v                                                           | electron velocity                                        |

| V                                                                     | saturated drift velocity                                 |

| V V                                                                   | voltage                                                  |

| $V_1, V_2$                                                            | node voltage                                             |

| V <sub>1</sub> , V <sub>2</sub><br>V <sub>bg</sub><br>V <sub>bi</sub> | back-gating threshold voltage                            |

| bi                                                                    | built-in potential of Schottky barrier                   |

| Symbol:                               | Definition:                                                                       |

|---------------------------------------|-----------------------------------------------------------------------------------|

|                                       |                                                                                   |

| V <sub>cc</sub>                       | Most positive power supply voltage in bipolar circuits (common collector voltage) |

| V <sub>dd</sub>                       | Most positive power supply voltage in FET circuits (common drain voltage)         |

| Vds                                   | drain-source voltage                                                              |

| Vee                                   | Most negative power supply voltage in bipolar circuits (common emitter voltage)   |

| V <sub>gg</sub>                       | Most negative power supply voltage in FET circuits (gate pull-down bias)          |

| V                                     | gate-source voltage                                                               |

| V V V V V V V V V V V V V V V V V V V | arbitrary offset voltage in FET model                                             |

| V                                     | pinchoff voltage                                                                  |

| Vsat                                  | saturation voltage                                                                |

| V<br>sat0                             | peak saturation voltage                                                           |

| V                                     | back-gating bias applied to a side electrode                                      |

| V <sub>ss</sub>                       | Zero bias supply voltage in FET circuits (common source voltage)                  |

| V_                                    | threshold voltage                                                                 |

| V <sub>t</sub>                        | Terminating voltage in ECL circuits                                               |

| W                                     | width of FET channel or diode anode                                               |

|                                       | t11-1-1                                                                           |

length of FET gate or diode anode

absolute permittivity of free space electron velocity at low field

effective track widths of equivalent parallel plate

scaling parameter in Lehovec and Zuleeg's FET model

arbitrary parameter used to solve non-linear equation

relative permittivity / dielectric constant

$\mathbf{w_1}$ ,  $\mathbf{w_2}$   $\mathbf{w_{1eff}}$ ,  $\mathbf{w_{2eff}}$

z E

€° H + W

track widths

angular frequency

capacitor

#### 1. Introduction

This thesis is the culmination of three years part time research work, and, I confess, three harder years of writing. The prime objective of this research was to develop the necessary infrastructure to be able to design high speed digital integrated circuits in gallium arsenide (GaAs). At the same time, colleagues were developing the necessary expertise to undertake the fabrication of the circuits. This thesis therefore describes the development of new models, the investigation of new logic circuits, and the adoption of these in constructing a circuit of medium scale integration (MSI) complexity. Although one circuit, an 8:1 multiplexer, was chosen as the vehicle for this work, the aim of the project was to develop the necessary techniques to undertake a number of different designs. presenting the results, quite clearly the design of this circuit figures large (Chapter 5), but it has been treated as an exemplar design, rather than as a unique circuit development. The reader is also asked to bear in mind that details of the processing technology were also changing throughout the duration of this work, demanding a very close interaction between the circuit and process design engineers, coupled with a highly flexible approach to the development of the circuit elements.

I am aware that the passage of time during the second (writing) phase has had a major influence on the content of this work. On the negative side, a proportion of the work reported has become outdated, where others have repeated and bettered the contribution I have made. Much more significant, however, is the positive side, where I believe that time has lent maturity to my views and analyses. This is particularly so, as I have spent this period employed in research in the parallel, competing field of silicon bipolar technology. I have therefore been forced to balance the advantages of the two technologies and, from this experience, I have found that there can be no better way to a true comparison of technologies than to be employed in one, contemporaneously with extolling in print, the virtues of the other. This document then is the outcome of this balancing of ideas.

The research leading to this thesis was performed at British Telecom Research Laboratories during 1981 to 1984, and I am particularly indebted to the management of these laboratories for the opportunity to conjoin both study and employment. As a "part time" degree study in industry, some constraints not always present in University research have been in force, one of which requires elaboration.

As in all research, the entrance to many interesting avenues of exploration has been opened throughout the work. Whilst many graduate students would have had the freedom to explore these, at least to their own satisfaction, the direction of industrial research is generally single-minded, and this project proved no exception. Some of the steps along the path toward the final goal have therefore been left with remaining question marks. This is nowhere more clear than in Chapter 4, which describes the development of computer models to aid the understanding and prediction of circuit performance. models were developed to be of use in the overall scheme, not to be a complete piece of work in themselves. As shown from the results presented in Chapter 5, the detail was sufficient to achieve the desired objectives, but an expert in modelling will recognise that there is ample scope for others to pick up the threads. In searching for completeness in the work, it is in Chapter 5 that the reader should look, for here is contained the main objective of the exercise, the design and successful implementation of a chosen MSI IC.

As this work was undertaken as a part of a team of some ten professional engineers, I should take a moment to underline those areas for which I can claim sole responsibility, and on which I would expect my own contribution to be judged. I begin in Chapter 2 by claiming for my own the interpretation of the background material, and it is here especially that the work benefits from the passage of time during the writing phase. I hope in here there is some useful linking of facts, hitherto treated only in isolation. In Chapter 3 I rely on claiming only the analysis, but once again, here is a compilation of material not hitherto collated. As the thesis progresses through Chapters 4-6, I may lay claim to an increasing

proportion of the work as original, with the circuit design and chip development being the culmination of this.

At the beginning of this research project, the idea of using capacitor coupled logic (CCL) for GaAs ICs had been suggested by the head of the GaAs IC section at BTRL. A breadboard mock-up using silicon transistors had shown the principle to be sound, and the first integrated test structures had been designed. Elsewhere in the world, a few renowned laboratories had reported successes in the field, but a great number of problems were still unsolved. CCL purported to offer solutions to some of these, and it is from here that my research began. Although I cannot claim the CCL technique as my own, almost all of the more detailed understanding of its behaviour, arose out of my work. It is gratifying to know that although BTRL was alone in using the technique for many years, many of the early, commercially available GaAs IC components employ a very similar basic cell.

There is no single logical structure for a work of this size which surpasses all others, and I have endeavoured to create a structure which makes the fewest number of assumptions in the early chapters, only to prove them in the later text. In so doing, I have been forced to break the circuit description into two distinct Chapters. In Chapter 3, the reader is led to an intuitive understanding of the behaviour of the more basic functional elements, and in Chapter 5, these elements are put together into a useful circuit of much more complex behaviour. These two are separated by Chapter 4 which introduces the detailed account of device and component modelling not required for the intuitive circuit descriptions of the earlier Chapter, but essential to the completion of the IC design. selecting this sequence, the simple description of CCL flows more naturally from the historical overview of Chapter 2. Furthermore, as the thesis progresses from the overview of Chapter 2, to the climax of the complete IC design in Chapter 5 and onto a brief glimpse of the future in Chapter 6, there is a gradual focussing of attention toward the unique contribution of this research project, as already described.

This focussing is also a mirror of that within the overview of Chapter 2, which begins by introducing GaAs as an engineering material, and moves on to describe its range of applications, placing in context the use employed here, before discussing the techniques which enable it to be used. In the final Section, the history of its use in IC applications is treated, leading ultimately to its use in CCL.

Finally in Chapter 6, two further possible configurations are discussed. One of these is now in widespread use, but it developed out of the work contained here, and the other is a completely new possibility, not yet published in open literature.

#### Chapter 2. An Introduction to Gallium Arsenide

It is the intention of this Chapter to introduce the reader to the technology and circuits in gallium arsenide (GaAs). Clearly this is a large subject, and the chapter is therefore necessarily large. It is hoped that for all there will be something new, either new material, or just a new treatment of the facts.

The Chapter begins from a material scientist's point of view, introducing the fundamental properties of GaAs as a crystalline solid. Some basic understanding of the physics of such materials is assumed but, wherever possible, the underlying assumptions have been kept to a minimum and some reasoning has been presented to explain why the material has certain properties. The consequence of these properties is also explored. Following this important background lies a link between the materials physics and both the commercial and engineering aspects of GaAs. A brief history of the development and exploitation of GaAs is presented, referring to the materials properties and how both an electronics engineer and a technologist may put these properties to work. A separate section is devoted to "back-gating", not a fundamental property of GaAs, but a phenomenon often encountered in a practical circuit. As such, it is only fully understood in the context of both the materials and applications sections.

The second major division within this Chapter outlines the technology of GaAs integrated circuit (IC) manufacture, again taking a somewhat historical perspective. Where appropriate, comparisons are drawn with the more widely known and understood technology of silicon IC production. This Section is intended to be helpful to the silicon technologist interested in GaAs and to the design engineer wishing to understand the technology.

The final Section leads the reader towards the specific subject of digital integrated circuits, and presents a critical history of the way in which GaAs circuits have progressed from 1976 until the present day. Again, reference is made to the comparative development

of silicon digital integrated circuits, to set the work in its context.

#### 2.1 Fundamentals of GaAs.

#### 2.1.1 GaAs Material Properties

To many accustomed to the "schoolboy" description of the operation of semiconductors, the concept of a compound semiconductor seems quite However, gallium arsenide is just one (probably the best known) of a wide range of semiconducting compounds [1]. The crystal structure is very similar to both silicon and germanium [2], but with one of the atoms of the unit cell replaced by gallium and the other by arsenic. Instead of being entirely covalent the crystal bonding is therefore partially ionic, but this causes only marginal changes to the material properties. Perhaps the most significant change to arise from the chemistry is that the (111) cleavage planes leave a pure surface of either gallium or arsenic. As these arrangements are not energetically the most favourable, some surface re-ordering takes place, leaving the surface region with an entirely different energyband structure from that in the bulk. Similar re-ordering takes place to a lesser extent on the other exposed crystal faces. It is responsible for a high density of surface states [3] property which has significant bearing on the performance and design of GaAs semiconducting devices.

GaAs is much more brittle than silicon, and this too could be caused by the ionicity. Thus if a (100) [4] plane is disturbed laterally in a <010> direction the usual ionic attraction force across the plane will be replaced by a repulsive force separating the two planes and breaking the crystal. This property makes thin wafers of GaAs more difficult to handle than the equivalent silicon wafers. Whilst this does not present an insurmountable problem, it does cause some concern when using equipment designed to handle the more robust silicon.

The presence of two atomic species in the crystal widens the range of crystal defects which are found compared with that containing a single element [5]. The most obvious additional defect being due to the substitution of the antitype. Of the two alternatives, the

Figure 2.1 Band structures of Ge, Si and GaAs.

presence of arsenic on a gallium site is the more important. This defect gives rise to a mid-gap energy level denoted "EL2" [6], which, at least in part, contributes towards the semi-insulating property discussed later. The influence of EL2 is described in Section 2.2.

Apart from these properties arising from the chemistry, most of the material properties of particular interest in semiconductors derive from the electronic band structure of the crystal [7]. Ignoring the ionicity, GaAs crystallises in a form very similar to both germanium and silicon, and the similarity extends to the energy band diagram [8] of figure 2.1, in which the energy of the electrons is plotted against the wave vector [9]. The wave vector represents the electron momentum within the crystal. The small differences in the wave functions of the constituent atoms are reflected by similar differences in the energy-band diagrams of the crystals, and silicon, germanium and gallium arsenide all have different band structures. Nevertheless, all three materials show similarities in the lowest conduction band (the band immediately above the energy gap), with three minima corresponding to three different wave vectors in the

crystal. These lie in the X and L directions (along the <110> and <100> directions respectively), and at the centre of the Brillouin zone [10] (corresponding to a zero in the crystal momentum). The separation between the top of the valence band and the lowest of these minima is the energy gap [11].

Unlike both germanium and silicon, the lowest minimum in GaAs lies at the zone centre, at the same value of momentum as the top of the valence band. Transitions between the two bands are thus made significantly easier. Energy is conserved by absorption or emission of a photon, and no momentum change is required. This transition is termed "direct", in contrast to the "indirect" transition in both silicon and germanium, in which the interaction demands the presence of a phonon as well as the photon [12]. The direct transition allows GaAs to be used for both light emitting diodes (LEDs) [13] and lasers [14] with a useful energy conversion efficiency.

A second property follows from the direct transition. Because the electron-hole pairs recombine as a two-body, rather than a three-body interaction, the probability of recombination is much higher, and the minority carrier lifetime is much reduced. The lifetime is typically five orders of magnitude smaller in GaAs than in silicon [15]. This property alone prevents the exploitation of bipolar junction transistors in GaAs.

The other important property of GaAs is the very high electron mobility at room temperature - at 8500 cm²/Vs in undoped material [16], it is some 5 or 6 times greater than in silicon. Quite clearly, since switching speed is related to mobility [17], this large increase in mobility should be reflected in faster circuits.

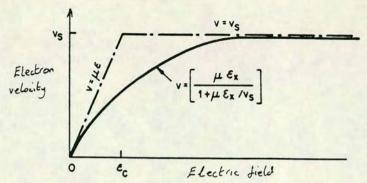

However, the electron mobility alone does not dictate the total carrier behaviour. Strictly, the parameter termed mobility, derived as the slope of the velocity versus electric field characteristic, should be referred to as the low-field mobility, because it is not independent of the applied field. In any semiconductor, the carrier velocity tends to saturate at higher fields [18]. This is most

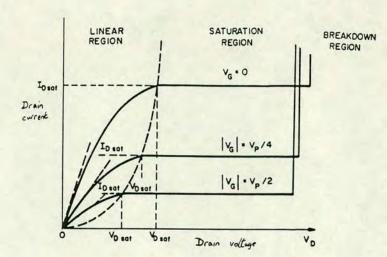

Figure 2.2 Velocity-field characteristics of electrons in various semiconductors.

readily explained as a loss of energy from the carriers to the lattice, because the effective temperature of the carriers is raised above that of the crystal. In GaAs a second, much more pronounced effect is seen [19], as shown in figure 2.2. As the electrons are given more energy from the electric field, a point is reached when the electrons cease to increase their velocity, instead slowing down significantly.

This behaviour can once again be explained directly from the band structure. The high electron mobility is a consequence of the tight radius of curvature on the bottom of the conduction band (actually, the effective mass is inversely proportional to the second derivative of the energy with respect to the wave vector [20]). A further consequence of this is that the density of states near the edge of the conduction band is small [21]. When the electron is given more energy by acceleration, it will eventually have sufficient energy to occupy one of the other minima in the conduction band. As the radii

of curvature of these other minima are large, the effective mass is high, leading to a lower velocity for a given energy. The density of states is also high in each of these minima and its effect is further increased because there are six silicon-like and eight germanium-like minima, all at a similar energy (see figure 2.1) [22]. As the

probability of occupation of a given state is proportional to the density of states, an electron will transfer preferentially to the high mass, low velocity state.

It should be noted that the transfer between valleys requires a phonon interaction [23], and scattering is therefore not instantaneous even when the energy is sufficiently high. Thus an electron may continue to accelerate for a short time, as depicted by the dotted line in figure 2.2. This behaviour is variously termed "ballistic transport" [24] or "velocity overshoot" [25].

Electron behaviour as outlined above is clearly susceptible to variations in temperature. At high temperature the electrons will obtain the required energy to change bands more readily, and the necessary phonon interaction will be more probable. These two factors combine to give a drastic reduction in mobility, and a lowering of the peak velocity as the temperature is increased [26]. At reduced temperature, the converse is true.

The effect of temperature on GaAs device performance further differs from that on silicon devices because of other differences in material properties. The much larger bandgap in GaAs [27] allows device operation up to high temperature, and the lower ionisation energies of both electrons and holes reduces the temperature at which carrier freeze-out occurs [28]. Together these two properties offer the potential for operation of GaAs devices over a very wide temperature range [29]. One practical consideration for operation at high temperature is that the vapour pressure of GaAs is relatively high, with surface decomposition and release of arsenic vapour above 600°C [30]. This limit is independent of the actual device being made, but there is commonly a much lower temperature limit because of subsequent fabrication steps; the latter is clearly dependent upon the type of device being made and the processing sequences adopted. For example, the metal used to form a Schottky junction with the GaAs may interdiffuse above a certain temperature, causing degradation of the junction [31].

In marked contrast to the superior electron mobility, the hole mobility in GaAs is similar to that obtained in silicon [32]. Again, this can be inferred directly from the band structure diagrams, there being little difference in the valence bands of the materials. The light-hole band [33] in silicon has a somewhat tighter curvature, and it thus exhibits a slightly higher hole mobility. Whilst the two or three to one ratio of electron to hole mobilities may be tolerated in complementary devices in silicon [34], the twenty to one ratio renders such considerations in GaAs impractical for most applications, although it has found use in very low power memory cells [35].

There are other properties of interest which are related directly to the choice of GaAs as the substrate material, but which do not follow directly from a simple interpretation of the band structure. These include the thermal conductivity and thermal expansion coefficient, in addition to the ability to form a semi-insulating variety.

The most notable of these is that GaAs has a semi-insulating form [36], in which the free carrier concentration is so low that the material acts as an adequate insulator. Devices formed in separate islands within a semi-insulating (SI) GaAs substrate are electrically isolated from each other inherently. The factors associated with the SI nature of GaAs are explored further in Section 2.2. Under certain circumstances this insulating property breaks down, according to the back-gating effect, which is described more fully in Section 2.1.3.

The most widely discussed of the thermal properties is the thermal conductivity. At 45 W/m.K at room temperature in GaAs [37], it is only one third of that of silicon. This is often claimed to be a serious disadvantage [38], it being argued that in a power limited chip (nearly always the case for ultra-high speed operation [39]) a lower thermal conductivity implies the imposition of a lower limit on the allowed power dissipation and, therefore, on chip complexity. Thus the potential speed-power advantage of GaAs must immediately be forfeit. In reality, only a fraction of the total chip-to-air thermal resistance is accounted for in the chip itself [40], and the basic value of the substrate conductivity is almost immaterial.

Less commonly cited as a problem is the higher thermal expansion coefficient in GaAs [41]. In practice, this may well prove more important than the poorer thermal conductivity. There are three basic problems; firstly in the registration between different stages of the processing, secondly from stresses induced during die bonding and thirdly from variations in parameters caused by stresses arising during fabrication.

Firstly, when fabricating integrated circuits, the thermal expansion coefficient of the glass chosen for the lithographic mask plates should be similar to that of the substrate material. As the minimum dimensions are shrunk and the wafer diameter is increased, differences in the expansion rates of the mask and substrate become comparatively more important [42]. Most readily available optical mask plates are designed for use with silicon and are thus non-ideal for GaAs.

Secondly, the dice are heated during the packaging operation in order to achieve a uniform die bond [43]. On cooling, the substrate might crack if the stresses are too great.

Thirdly, GaAs, being more brittle than silicon, is more susceptible to damage by stresses induced by temperature cycling during IC fabrication. Various surface dielectrics are used during the manufacturing, and these can have widely different expansion from that of the underlying semiconductor [44]. As any stress arising is close to the active device, device parameters can be widely changed as a result [45]. The larger expansion coefficient of GaAs demands that more care is taken in process design, in order to avoid these problems.

A final property of GaAs which is often quoted is the radiation hardness [46]. This is of particular interest to the military, who have invested a great deal of money in research on GaAs for this reason. There are several forms of radiation damage; a slow degradation leading to eventual failure, caused by total accumulated dose, and sudden catastrophic failure caused by different types of single event (e.g. by neutrons or by gamma rays). The advantage of

GaAs here is sometimes overstated. It is now possible to get good protection to most of these radiation events in both MOS and bipolar silicon technologies, but special techniques are required to obtain this [47]. In GaAs this proof against damage appears to be available "free". It might be argued that the hardness of GaAs might be improved with effort, in much the same way that the hardness of silicon has already been improved. Radiation hardness will not be considered further in this thesis.

## 2.1.2 Historical exploitation of GaAs

As discussed in the previous Section, a major advantage of GaAs is the direct bandgap. This leads immediately to the exploitation of GaAs for both light emitting diodes (LEDs) and lasers. A high quantum efficiency [48] is achieved because the recombination of the carriers and the attendant release of a photon may be directly stimulated by a photon; no phonon interaction is required. Even with this special property, GaAs lasers would not have developed so rapidly, but for two additional factors.

Firstly, the infra-red emission of the GaAs laser (at a wavelength of 0.85 um [49]) was suitable for use in early optical fibre transmission systems [50].

Secondly, a second semiconductor, aluminium arsenide (AlAs), shares an almost identical lattice parameter with GaAs [51]. A family of materials, Al<sub>x</sub>Ga<sub>1-x</sub>As, can be formed from a mixture of the two (here 'x' denotes the mole fraction of AlAs), and because the lattice parameters of both components are equal, layers of different composition can be grown without strain induced defects forming in the interface [52]. The bandgap of the material changes according to its composition [53]. By using layers of differing composition (and doping) a whole gamut of useful devices can be built [54] which exploit the change of bandgap at the interface. The term heterostructure or (heterojunction) is used to describe these interfaces.

The technology required for the fabrication of such heterostructure lasers emerged contemporaneously with the explosion of interest in

optical fibre transmission. The continued development of the GaAs laser became dominated by market potential, rather than by the more common, but less urgent driving force of future promise.

Consequently, both the availability and quality of GaAs material advanced rapidly.

It soon became clear that alternative materials (based on indium phosphide, InP [55]) would allow better transmission because they could operate at 1.3 and 1.55 um wavelength, where attenuation in the fibre could be significantly reduced [56]. The techniques necessary for working in these newer compound semiconductors (containing three or four of In, Ga, As, and P) followed directly from those developed for GaAs and, in turn, GaAs has since benefited from work on these materials. Despite the fact that the technological forefront in optoelectronics has moved away from GaAs, other applications have followed, no doubt stimulated both by the availability of devices and by the example set in optical transmission. Most notable of these is in the compact disc (CD) system [57], well established in domestic HiFi systems and now being developed as a mass storage medium for computing [58]. This consumer application, in which low cost is the key to success, is entirely dependent upon the GaAs laser, and probably represents the largest commercial market for GaAs at the moment.

It is probable that GaAs would still have been developed for conventional electronics applications, even in the absence of the special optical properties, but the rapid deployment of effort on GaAs for optoelectronics certainly helped to advance this. The combination of the high electron mobility and semi-insulating substrate is the key factor here. The electron behaviour alone is sufficient for interest to be expressed in GaAs for high frequency active devices [59] and the insulating property allows the fabrication of high quality, high frequency passive components, such as inductors and transmission lines [60]. Quite clearly, in those applications where GaAs might be considered simply because of its high electron mobility, silicon devices of reduced geometry might also be considered [61]; the increased difficulty of the reduced geometry being balanced against the additional experience of silicon

technology. However, most high frequency passive components on silicon are ruled out because of the lossy substrate [62], leaving GaAs unchallenged for those applications requiring both active and passive devices. Perhaps it is not surprising then that the exploitation of GaAs has followed the path of discrete microwave devices [63] into analogue microwave integrated circuits (firstly hybrid and then monolithic) [64] and finally into digital ICs [65].

The highest frequency active devices are generally two terminal structures, as the parasitic feedthrough from input to output of a three terminal structure tends to restrict the bandwidth. diodes for use both as mixers [66] and oscillators [67] extend in frequency performance well beyond transistors. When GaAs was first explored, the anomalous electron behaviour allowed a completely new type of diode to be made; the Gunn diode [68]. The action of this device follows directly from the slowing down of the electrons at the critical electric field, and the so-called "negative differential mobility". In order to accommodate the reduction in velocity, a space charge layer develops to change the field distribution. this space charge layer becomes mobile, a Gunn domain [69] is formed. The arrival of this domain at the electrode releases the charge packet. A new domain will form rapidly, because the discharging of the first domain once again allows the electric field to exceed the threshold field again. The overall effect is a periodic pulsing of the current - an oscillator. Such devices can oscillate at several tens of gigahertz, delivering quite high power [70].

In addition to this and other special devices, there is much interest in conventional diodes for high frequency operation. In the simplest analysis, the higher mobility of GaAs allows a higher current to flow in the material for a given electric field. This translates directly into a lower resistance for a given size and shape of junction, giving both a lower noise figure [71] and a lower capacitance. These are both advantages for high frequency mixers.

This same principle of low resistance and noise figure for a given current would be expected to follow in three terminal devices and there is quite clearly an interest in GaAs transistors. The range of

GaAs transistors is more limited than the range of silicon transistors. Again the material properties explain why.

The most useful transistor for high frequency use is the bipolar transistor [72]. Several factors account for this, but the two key points are the very large transconductance [73] which can be achieved and the vertical nature of the device. The latter allows the critical dimension of the bipolar transistor (the vertical base width) to be much smaller than the equivalent, lithographically defined, dimension of an FET (the horizontal channel length). However, as already stated, the minority carrier lifetime in GaAs is too short to allow conventional bipolar transistors to be made with a usable current gain.

Recently, bipolar transistors have been made using a heterojunction comprising both GaAs and AlGaAs to overcome these problems [74]. The technology for this so called HBT (heterostructure bipolar transistor) is similar to that developed for the heterostructure laser devices already discussed. There is great interest in HBTs, both as a means of coupling the mobility advantage of GaAs with the attractive device properties of the bipolar junction transistor, and also because of the numerous additional advantages which accrue from the use of the heterojunction [75]. It is very much a device of the future, being still in the early development stages.

Having eliminated the homojunction bipolar transistor as a means of exploiting GaAs, attention is turned to the family of unipolar or field-effect devices. The most obvious FET to consider is the metal oxide semiconductor transistor (the MOSFET or MOST) [76], which has proved itself to be most successful in silicon. This success is in part attributable to the advent of CMOS [77], in which both p- and n-channel devices are fabricated together, making a complementary circuit in which the DC power dissipation is virtually zero. This configuration is clearly not available in GaAs, as already stated, because of the grossly dis-similar electron and hole mobilities.

Clearly then one would like to make use of the single polarity MOS transistor, which in practice means the n-channel (or nMOS)

transistor (again the low hole mobility of GaAs offers a poorer performance prospect for the p-channel device than is already available with silicon). The MOSFET is selected in preference to the junction FET (or JFET), because of the higher transconductance [78] and the more controllable and simpler fabrication procedure. Sadly, the MOSFET too is unavailable in GaAs, because of the very large numbers of trapping centres at the interface between the semiconductor and the oxide [79]. As the band-bending at the semiconductor surface adjusts with changes in the applied gate voltage, the occupation of surface traps changes depending on the relative energy of the trap and the Fermi-level [80]. Relaxation of any trapped electrons or holes results in a change in the surface potential of the semiconductor, and a consequent change in the magnitude of any accumulation or inversion charge. In silicon, the traps are few in number and the surface charge is stable with time, but in GaAs, the trap density is significant, and the net surface charge is unstable [81]. The DC and AC behaviour of such an MOS gated transistor in GaAs are therefore very different. The MOS gate effectively acts as a leaky capacitor at the input to an ideal FET [82].

Many different surface treatments and alternative dielectrics have been tried to enable MOSFETs to be made in GaAs [83]. (Because the GaAs embodiment of the MOS structure does not necessarily use either a native oxide, or in some cases an oxide at all, the term MISFET is preferred, denoting the metal-insulator-semiconductor construction.) Some success has been claimed, but it has always proved short lived. Probably the most successful attempt to use GaAs MISFETs applied the model of a leaky capacitor to design circuits capable of accommodating the imperfect FET behaviour [84], but this approach too has its shortcomings. This approach is very similar to that employed in the bulk of the work in this thesis, the concept actually being derived from the philosophy underlying capacitor coupled logic [85].

Having eliminated the widely used transistor types, only the JFET remains [86] as a possible means of widely exploiting GaAs amplifiers or switches. The GaAs JFET is indeed a viable transistor and, as expected, the performance of this device does bear out the initial

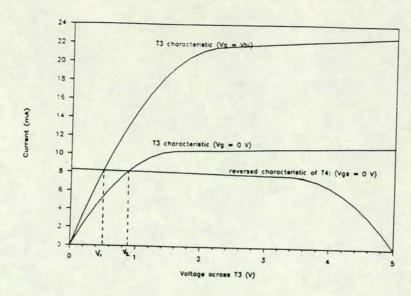

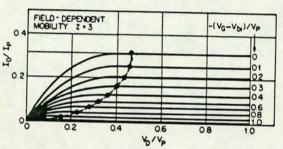

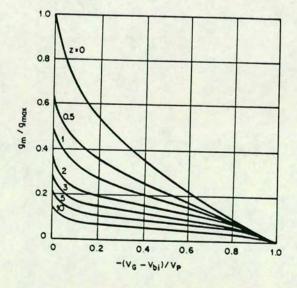

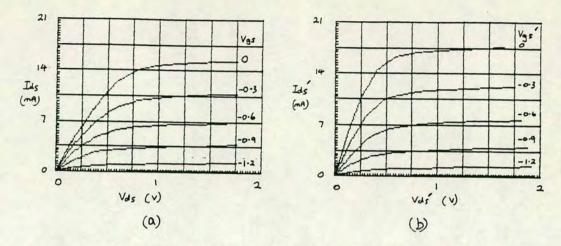

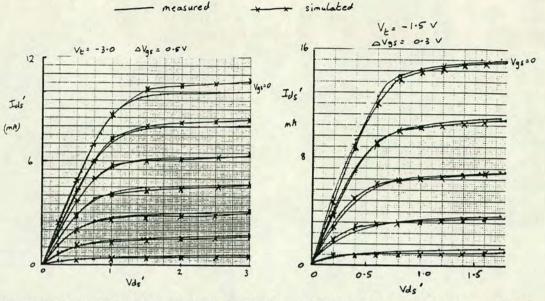

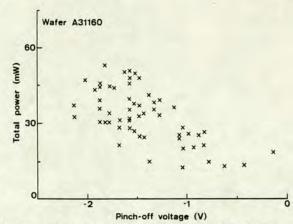

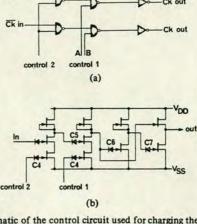

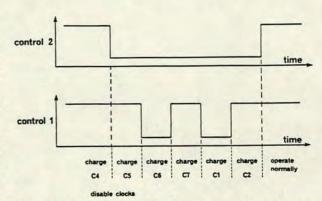

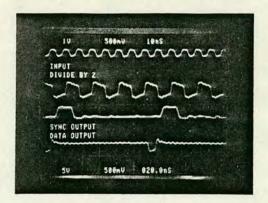

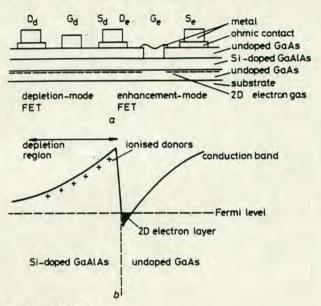

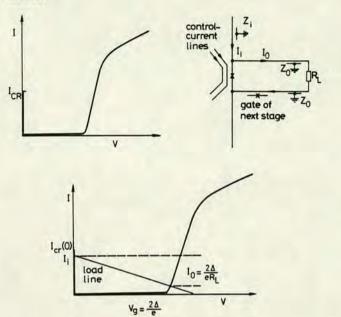

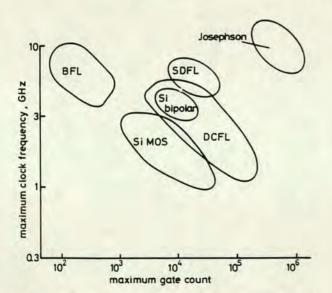

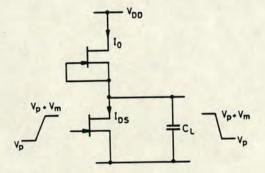

expectation that the higher electron mobility of GaAs would be reflected in a better high frequency performance, whether measured as a digital switching speed [87], or as an amplifier noise figure [88].