# Development and Characterisation of a Novel LDMOS Macro-model for Smart Power Applications

Steven Frère

A thesis submitted for the degree of Doctor of Philosophy. The University of Edinburgh June 30th, 2005

### Abstract

In the automotive industry, there is a strong trend that has increased the electronics in cars for various functions like fuel injection, electric control of doors and windows, electric chair adjustment, air-conditioning, drive-by-wire, brake-by-wire, etc. The 12V battery used in present cars will not be sufficient for the increasing number of functions and as a consequence, a change towards 42V batteries will be necessary.

For these "automotive" systems, so-called smart power ICs must be used. These are chips in which the power functionality, e.g. the control of a motor is integrated with the logic control. There is also a trend towards operation at high voltages and integrating more intelligence using a microcontroller's RAM/ROM memory and several sensors and interfaces. The final goal is the integration of a complete system on a single chip, a so-called power System-on-Chip (SoC).

State of

The interest in accurately modeling high-voltage transistors has increased in recent years due to the compatibility of these devices with standard CMOS technology. However, existing LDMOS models are not accurate enough for this task and SPICE models are especially weak when modeling AC performance. The limitation of these models lies in their lack of any capability to physically model some of the characteristic phenomena observed in LDMOS devices. The increased difficulty is related to complex 2D effects, specific to modern high voltage device architectures.

This thesis presents a new physically based macro-model. This model is based on the investigations performed on the key phenomena occurring in an LDMOS transistor. These phenomena were investigated by TCAD simulations and were confirmed by newly developed test-structures.

The model is accurate for wide geometry and temperature variations as well as for DC and AC operation. A novel corner extraction methodology based on neural networks has been developed making it possible to easily generate worst-case corners. As an extension of the neural network worst-case corner generation methodology, a static aging model card generation methodology is presented.

The model was verified on device level as well on circuit level yielding good results.

## **Declaration of originality**

I hereby declare that the research recorded in this book and the manuscript itself was composed and originated entirely by myself in the department of Electronics and Electrical Engineering at the University of Edinburgh and in the Technology Research and Development group in the facilities of AMI Semiconductor Belgium BVBA. I actively contributed in the IST project Automacs and other DMOS releated R&D projects at AMIS and personally furnished original contributions on the topology of the DMOS model, especially on the AC part. I personally developed the extraction procedure and the novel corner generation methodology. I proposed a technique to create aged model cards.

Steven Frère

### Acknowledgements

This thesis is dedicated to my parents. Without them all this would not have been possible.

A great many people have helped me over the past years I have been working towards my Ph.D. So I am sorry if I have left anyone out. The first person I would like to thank is Professor Anthony Walton, without whom none of this would have happened.

I would also like to thank everyone I have worked with at AMI Semiconductor's Technology Research and Development department and specifically the modelling group, most of whom have had some influence on this work in one way or another. Special thanks go to Renaud Gillon, Joseph Rhayem, Bart Desoete, Peter Moens and Davide Bolognesi for the interesting and fruitful discussions. I also would like to thank Marnix Tack, director of the Technology Research and Development department for giving me the opportunity to explore this topic at AMI Semiconductor.

The most important person I have to thank is Katrien for always being there with love and support over the last few years, even though it has meant many sacrifices. I would never have managed to finish this work without her patience and understanding.

Finally, I need to thank my friends for providing all the distractions required to make me take so long to finish the thesis. Thanks !

## Contents

| Al | bstract                                       | i    |  |

|----|-----------------------------------------------|------|--|

| De | Declaration                                   |      |  |

| Ac | cknowledgements                               | iii  |  |

| Co | ontents                                       | iv   |  |

| Li | st of figures                                 | viii |  |

| Li | st of tables                                  | xiii |  |

| 1. | Introduction                                  | 1    |  |

|    | 1.1. Background                               | 2    |  |

|    | 1.2. LDMOS transistor models                  | 4    |  |

|    | 1.3. Thesis plan                              | 4    |  |

| 2. | Introduction to LDMOS transistors             | 7    |  |

|    | 2.1. Introduction                             | 8    |  |

|    | 2.2. Structure of a n-type LDMOS              | 8    |  |

|    | 2.3. Important design parameters              | 9    |  |

|    | 2.4. The AMIS I2T technology family           | 12   |  |

|    | 2.5. LDMOS transistors in the I2T family      | 12   |  |

|    | 2.6. Circuit for model characterisation       | 16   |  |

|    | 2.7. Conclusion                               | 19   |  |

| 3. | Introduction to modelling                     | 20   |  |

|    | 3.1. Introduction                             | 21   |  |

|    | 3.2. Definition of terms                      | 21   |  |

|    | 3.3. Modelling example based on a diode model | 22   |  |

|    | 3.4. Model types and their implementation     | 28   |  |

|    | 3.5. Conclusion                               | 33   |  |

| 4. | LDMOS macro-model characteristics and macro-model requirements                       |     |

|----|--------------------------------------------------------------------------------------|-----|

|    | 4.1. Introduction                                                                    | 37  |

|    | 4.2. Electrical device characteristics                                               | 37  |

|    | 4.3. Model accuracy and robustness                                                   | 42  |

|    | 4.4. Accuracy targets for the macro-model                                            | 44  |

|    | 4.5. Summary of accuracy targets                                                     | 45  |

|    | 4.6. Robustness specifications                                                       | 47  |

|    | 4.7. Conclusion                                                                      | 47  |

| 5. | TCAD simulation of LDMOS transistors                                                 | 49  |

|    | 5.1. Capacitance behaviour of LDMOS transistors                                      | 50  |

|    | 5.2. Intrinsic Drain voltage $(V_K)$ behaviour in relation to gate and drain voltage | 56  |

|    | 5.3. Conclusion                                                                      | 60  |

| 6. | Description and results of the developed test-chips for DC and AC-analyses           | 62  |

|    | 6.1. Introduction                                                                    | 63  |

|    | 6.2. introduction to MESDRIFT test-structure                                         | 63  |

|    | 6.3. W-array test-structure                                                          | 74  |

|    | 6.4. Junction diode test-structure                                                   | 76  |

|    | 6.5. RF-measurement test-structure                                                   | 78  |

|    | 6.6. Introduction to capacitance extraction based on s-parameter measurements        | 79  |

|    | 6.7. Capacitance calculation for an LDMOS transistor from measured s-parameters      | 86  |

|    | 6.8. Conclusion                                                                      | 89  |

| 7. | The macro-model: definition / extraction procedure / worst-case corners              | 90  |

|    | 7.1. Introduction                                                                    | 91  |

|    | 7.2. Macro-model topology                                                            | 91  |

|    | 7.3. Detailed description of the macro-model components                              | 94  |

|    | 7.4. Model parameter extraction procedure                                            | 102 |

|    | 7.5. Worst-case corner extraction                                                    | 109 |

|    | 7.6. Conclusion                                                                      | 117 |

| 8.  | The macro-model: verification / static-aging / self-heating | 118 |

|-----|-------------------------------------------------------------|-----|

|     | 8.1. Introduction                                           | 119 |

|     | 8.2. Model verification                                     | 119 |

|     | 8.3. Methodology to include static-aging                    | 140 |

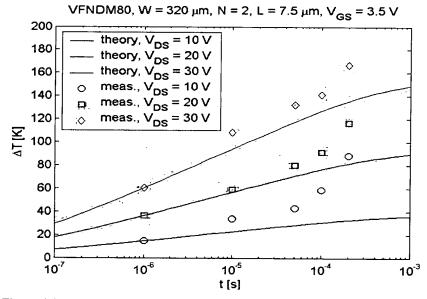

|     | 8.4. Methodology to include self-heating                    | 146 |

|     | 8.5. Conclusion                                             | 149 |

| 9.  | Conclusion and future work                                  | 150 |

|     | 9.1. Challenges and opportunities                           | 151 |

|     | 9.2. Conclusions                                            | 152 |

|     | 9.3. Future work                                            | 154 |

|     | 9.4. Final conclusion                                       | 156 |

| Apj | pendix A: Verilog-A model code                              | A-1 |

| Apj | pendix B: Published papers                                  | B-1 |

# List of figures

| 2.1 | Generic structure of an n-type LDMOS                                        | 8  |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | Current flow in an LDMOS                                                    | 9  |

| 2.3 | Formation of depletion regions in DMOS devices                              | 10 |

| 2.4 | Punch Through in an LDMOS                                                   | 11 |

| 2.5 | Identification of layout dimensions                                         | 13 |

| 2.6 | Schematic view of the BULB-circuit                                          | 16 |

| 2.7 | Schematic view of the motor driver-circuit                                  | 17 |

| 2.8 | The four valid H-bridge switching states (excluding open circuit load       |    |

|     | state): (a) Supplies +VDC; (b) Supplies -VDC; (c) & (d) Both supply         |    |

|     | zero voltage (short-circuited load)                                         | 18 |

| 3.1 | Equivalent diode circuit                                                    | 22 |

| 3.2 | Diode DC characteristic                                                     | 23 |

| 3.3 | CV measurement setup                                                        | 26 |

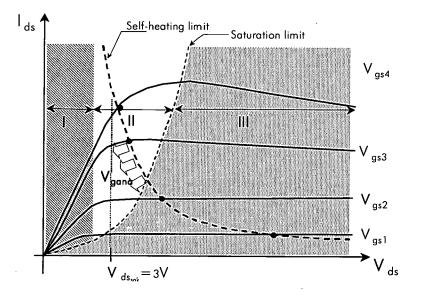

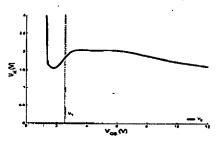

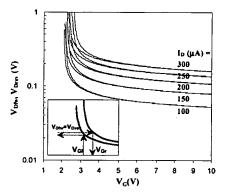

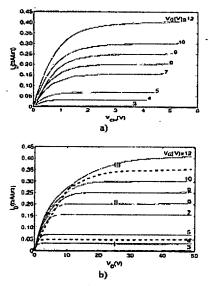

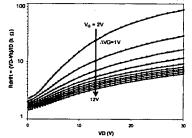

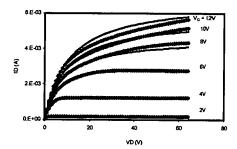

| 4.1 | Operating regions : Linear (I), Quasi-Saturation (II), Saturation (III)     | 37 |

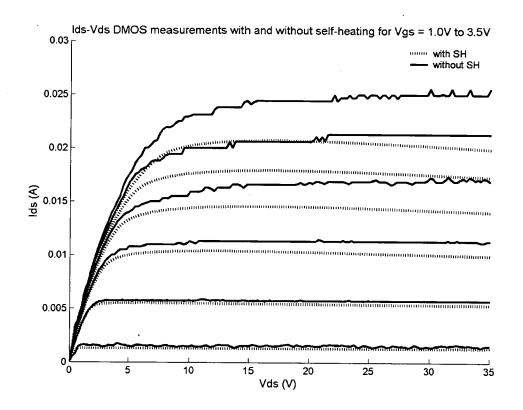

| 4.2 | Measured output characteristics of a device with W= $40\mu m$ , VGS = $1 -$ |    |

|     | 3.5V.                                                                       | 43 |

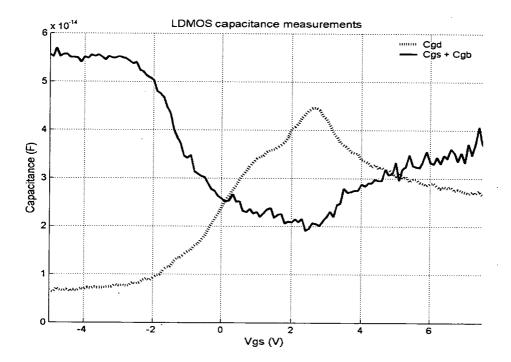

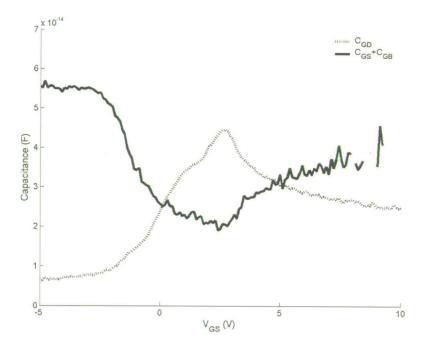

| 4.3 | Measured capacitances (Cgs, Cgd and Cgb) of an LDMOS device with            |    |

|     | width = $80\mu m$ at Vgs= -5 till 8V and Vds=0V.                            | 42 |

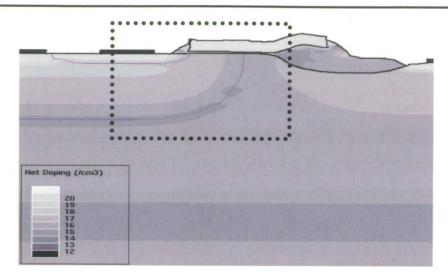

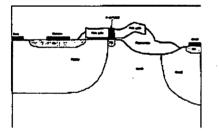

| 5.1 | Schematic and TCAD cross-section view. The black squares indicate the       |    |

|     | regions zoomed in on in the following graphs.                               | 50 |

| 5.2 | Schematic and TCAD cross-section view. The black dotted squares             |    |

|     | indicate the regions zoomed in on in the following graphs.                  | 52 |

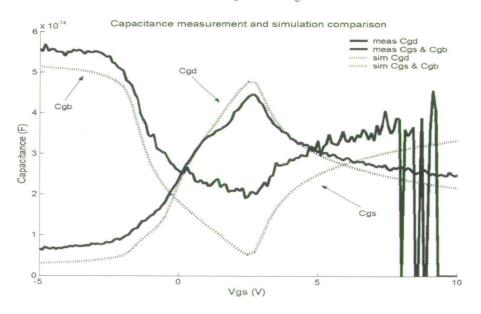

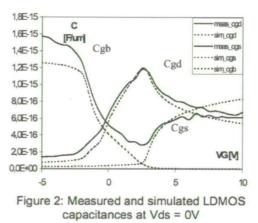

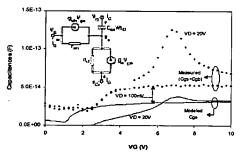

| 5.3 | Comparison between measurements and simulations at $Vds = 0V$               | 52 |

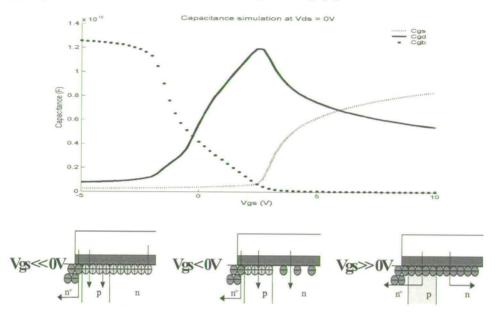

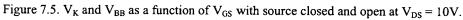

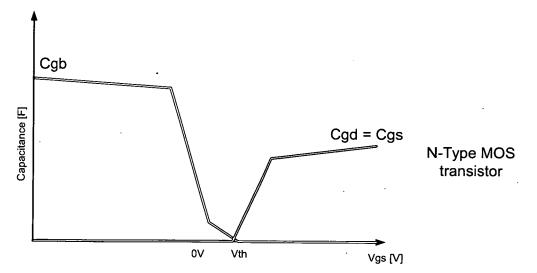

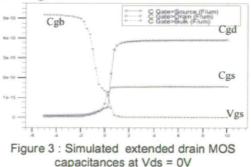

| 5.4 | Cgs, Cgb and Cgd at $Vds = 0V$                                              | 53 |

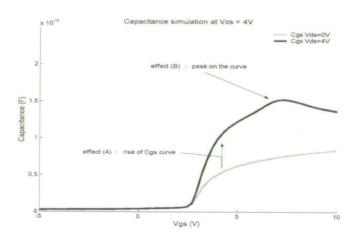

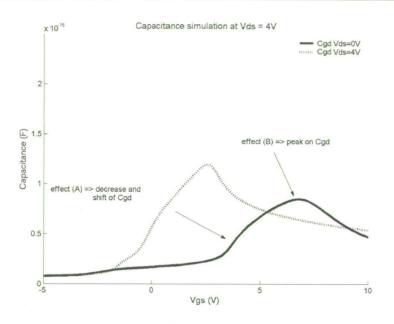

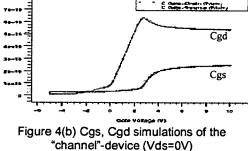

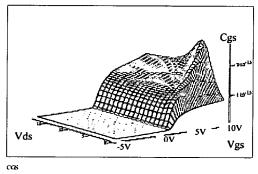

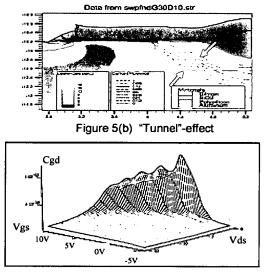

| 5.5 | Cgs and Cgd when $Vds > 0V$                                                 | 54 |

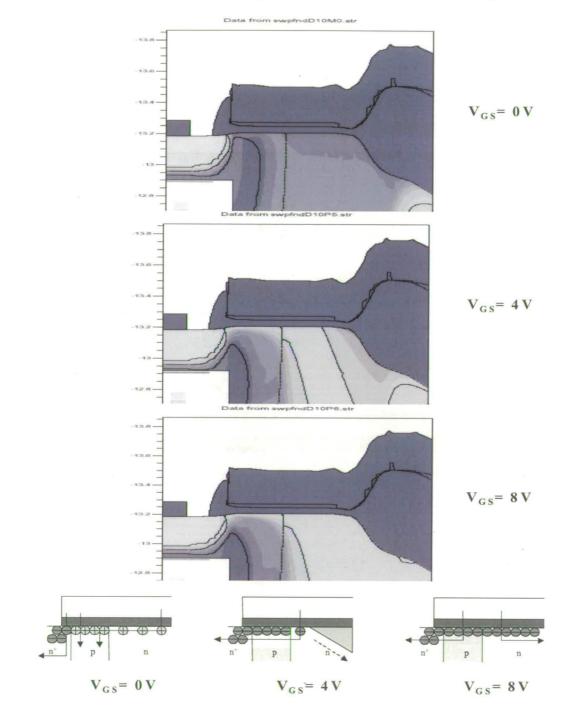

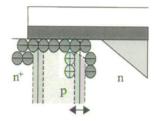

| 5.6 | Depletion region in the drift region under the gate                         | 55 |

| 5.7 | Sensitivity of p-body/n-tub junction to VGS                                 | 56 |

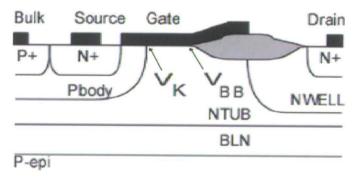

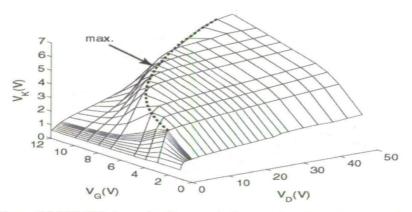

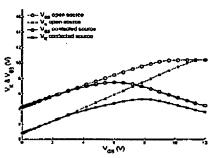

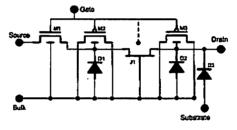

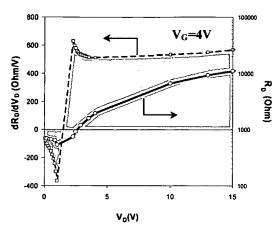

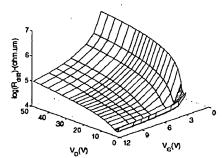

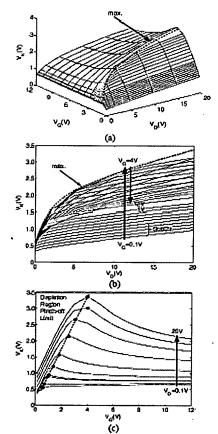

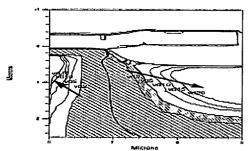

| 5.8 | LDMOS channel voltage variation as a function of VGS and VDS                | 57 |

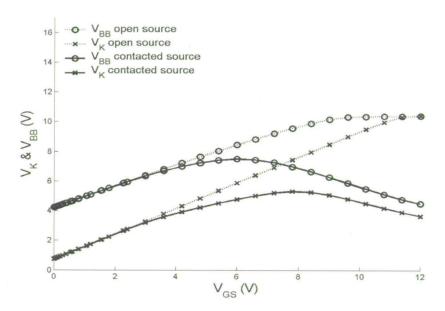

| 5.9  | VK and VBB as a function of VGS with source closed and open at VDS           |    |

|------|------------------------------------------------------------------------------|----|

| 5 10 | = 10 V.                                                                      | 58 |

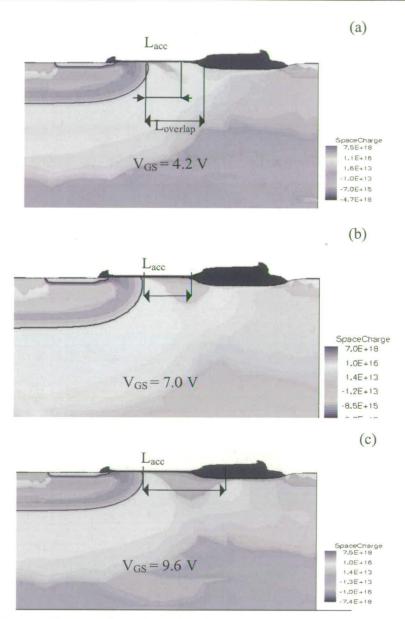

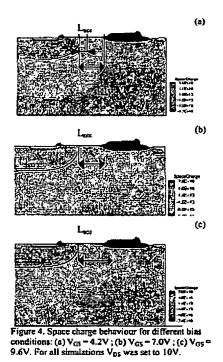

| 5.10 | Space charge behaviour for different bias conditions: (a) $VGS = 4.2V$ ; (b) |    |

| ~    | VGS = 7.0V; (c) $VGS = 9.6V$ . For all simulations VDS was set to 10V.       | 59 |

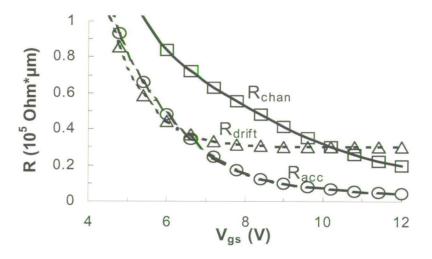

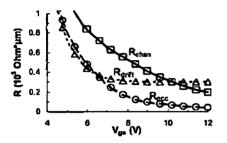

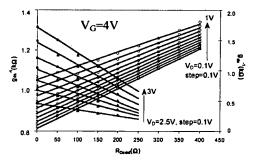

| 5.11 | Variation of the channel, accumulation and field oxide drift region          |    |

|      | resistance (Rchan, Racc and Rdrift) as a function of VGS (VDS=10V).          | 60 |

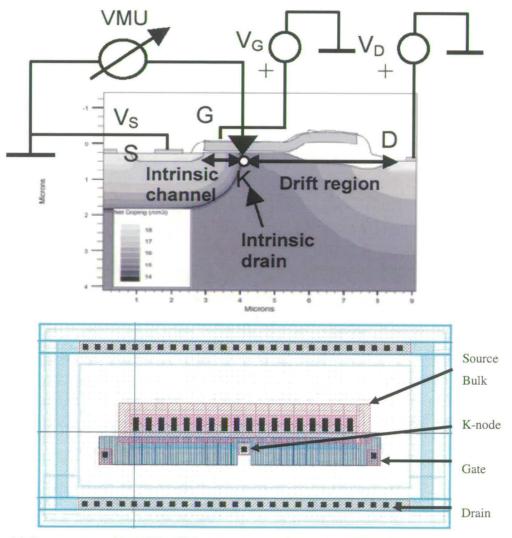

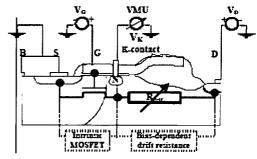

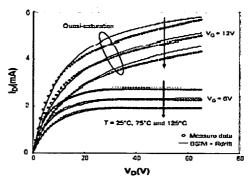

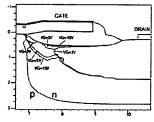

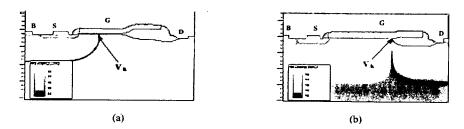

| 6.1  | Cross section of MESDRIFT test structure and associated HP4156               |    |

|      | measurement set-up. K-contact (n+ type) is designed in the drift region      |    |

|      | (close to pn junction) and its width, WK, is negligible compared to          |    |

|      | DMOS width, W.                                                               | 64 |

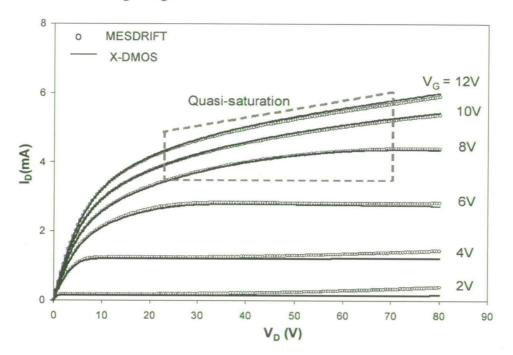

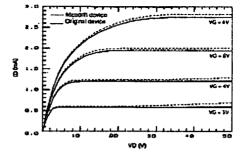

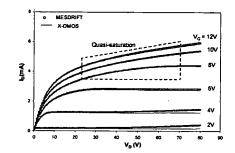

| 6.2  | Typical output characteristics, IDS vs. VDS, of X-DMOS (solid) and           |    |

|      | MESDRIFT (symbol) (both with W=40 $\mu$ m): very good agreement is           |    |

|      | observed (including quasi-saturation region) demonstrating that the K-       |    |

|      | contact does not significantly change the HV MOSFET characteristics.         | 65 |

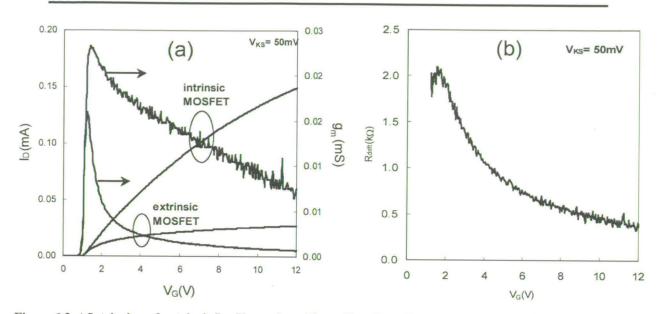

| 6.3  | a) Intrinsic and extrinsic IDS-VGS and gm-VGS at VKS=VDS=50mV,               |    |

|      | measured with MESDRIFT mirroring X-DMOS, b) Extracted Rdrift at              |    |

|      | low VDS (=50mV).                                                             | 66 |

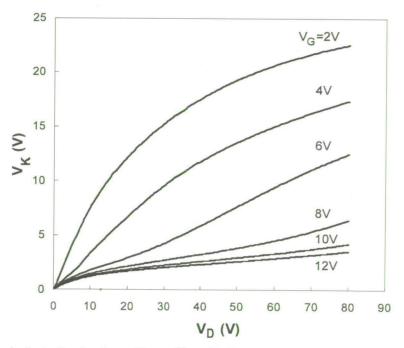

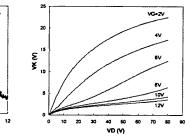

| 6.4  | Intrinsic drain (key) voltage, VK, vs. VDS with VGS as parameter,            |    |

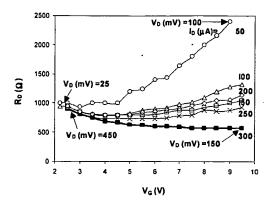

|      | experimentally revealed by MESDRIFT.                                         | 66 |

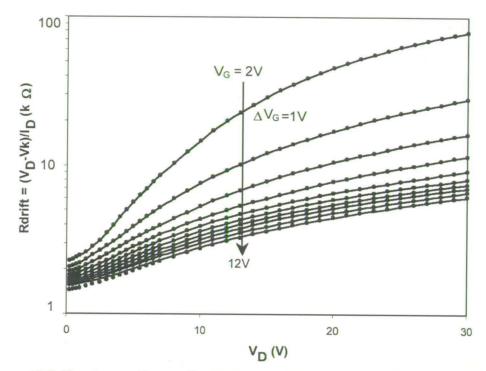

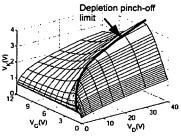

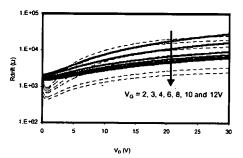

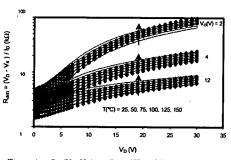

| 6.5  | Drift resistance, Rdrift vs. VDS for a range of VGS, as experimentally       |    |

|      | extracted with MESDRIFT (X-DMOS) at room temperature                         | 67 |

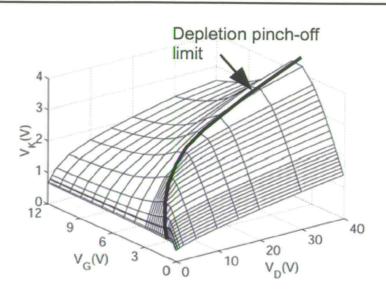

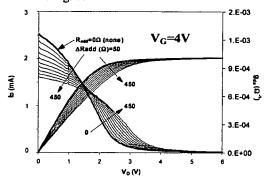

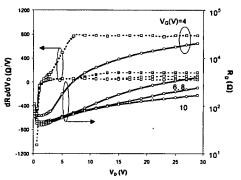

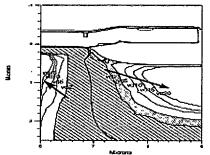

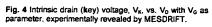

| 6.6  | Intrinsic drain voltage, VK, predicted by numerical simulation with          |    |

|      | calibrated 2D structure, calibrated on X-DMOS characteristics. Inset:        |    |

|      | drift depletion pinch-off limit highlighted.                                 | 68 |

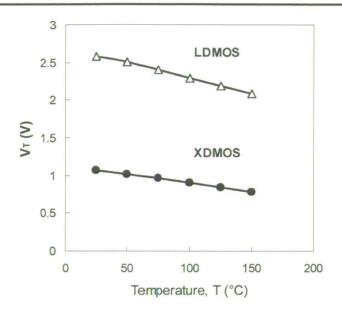

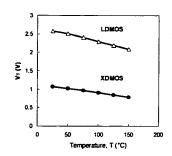

| 6.7  | Threshold voltage, VT, vs. temperature, T, for X- and L-DMOS.                | 69 |

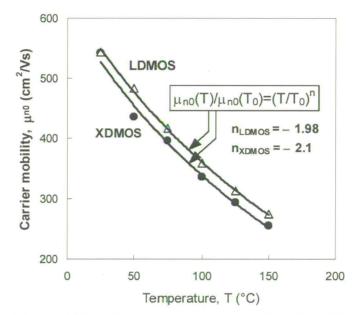

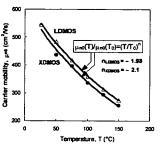

| 6.8  | Low field mobility, µn0, vs. temperature, T, for X- and L-DMOS.              | 69 |

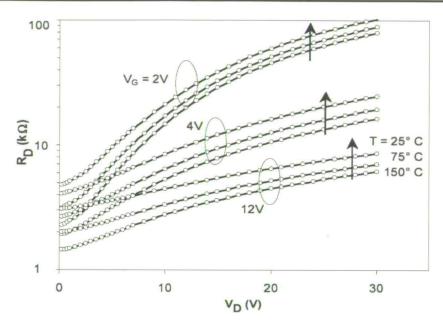

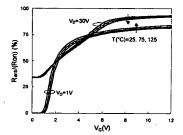

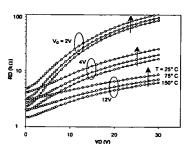

| 6.9  | Rdrift vs. VDS at constant VGS with the temperature, T, as a parameter.      | 70 |

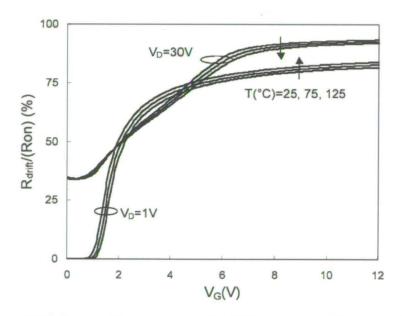

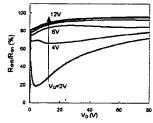

| 6.10 | Influence of temperature on Rdrift/Ron characteristics revealed by           |    |

|      | MESDRIFT.                                                                    | 70 |

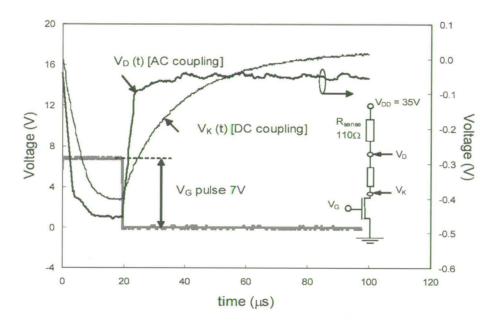

| 6.11 | Dynamic behaviour of MESDRIFT (X-DMOS) highlighted by a simple               |    |

|      | pulsed measurement set-up designed to study self-heating in HV               |    |

|      | MOSFETs: VDS and VK time constants are different.                            | 71 |

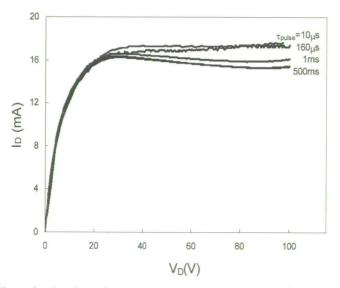

| 6.12 | Effect of pulse duration on the reconstructed output characteristics of X- |    |

|------|----------------------------------------------------------------------------|----|

|      | DMOS. The self heating appears acceptably eliminated when impulse <        |    |

|      | 10 µs.                                                                     | 71 |

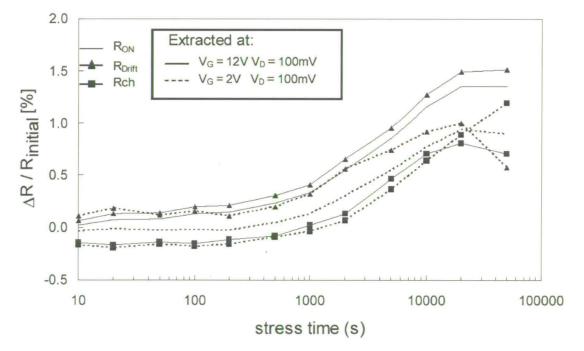

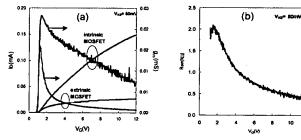

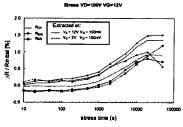

| 6.13 | degradations of Rch, Rdrift, Ron induced by hot carrier measurements       |    |

|      | conducted on MESDRIFT with VDS=100V and VGS=12V: .Rdrift>0,                |    |

|      | Rdrift and Ron are similarly degraded.                                     | 72 |

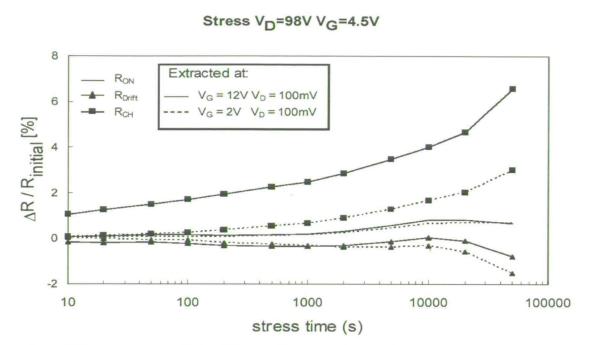

| 6.14 | degradations of Rch, Rdrift, Ron induced by hot carrier measurements       |    |

|      | conducted on MESDRIFT with VDS=98V and VGS=4.5V (at max                    |    |

|      | Ibody): .Rdrift<0, Rch is significantly more degraded than in Figure       |    |

|      | 6.13.                                                                      | 73 |

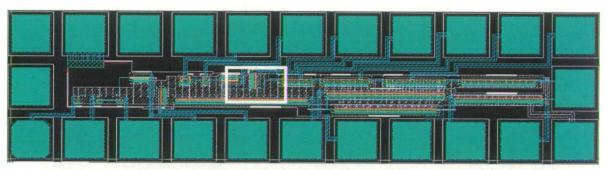

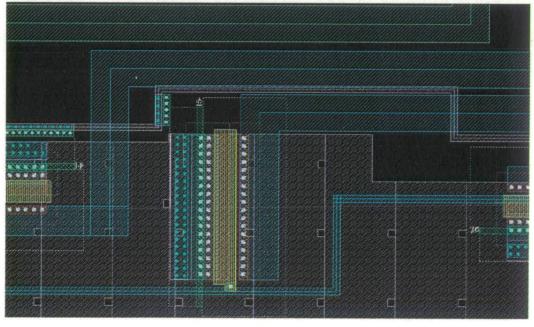

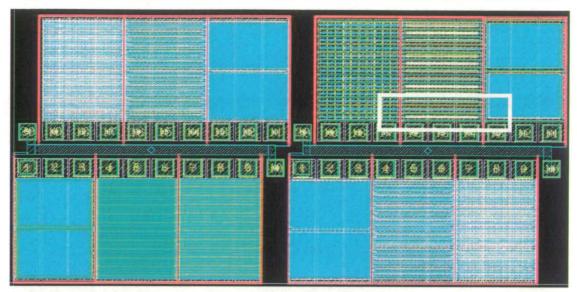

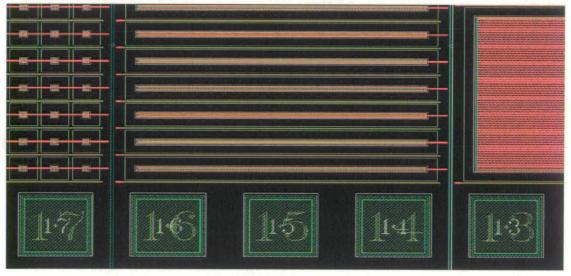

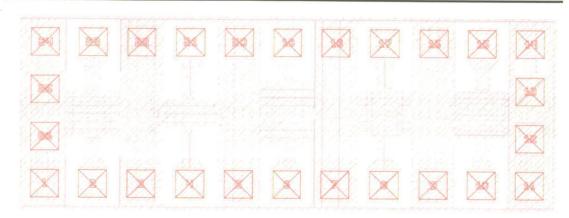

| 6.15 | W-array (a) overview of a W-array test-structure containing 17 LDMOS       |    |

|      | transistor variations. (b) Close-up                                        | 74 |

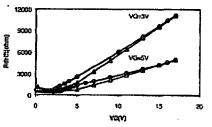

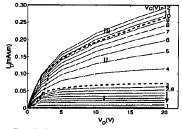

| 6.16 | DC LDMOS measurement results of a W-array test-structure                   | 76 |

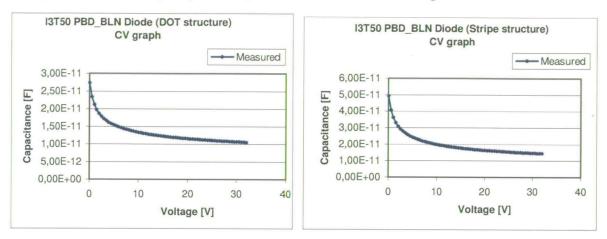

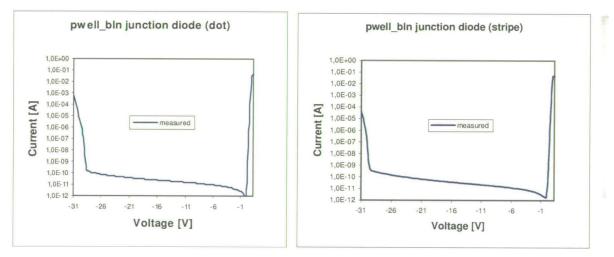

| 6.17 | junction diode test-structure                                              | 77 |

| 6.18 | Measurement results of the junction diode teststructure for the Pbody-     |    |

|      | BLN diode                                                                  | 78 |

| 6.19 | RF-test-structure frame                                                    | 78 |

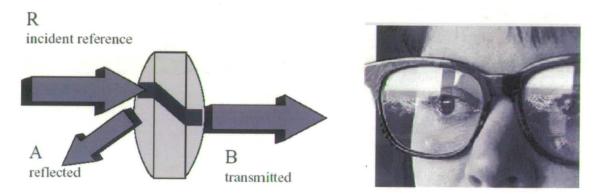

| 6.20 | S-parameter comparison to reflection and through pass of a pair of         |    |

|      | spectacles                                                                 | 79 |

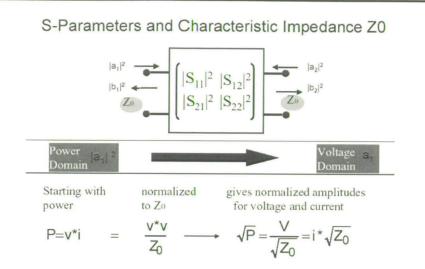

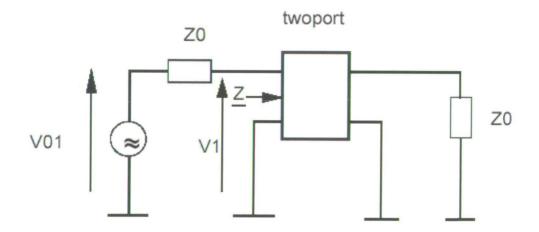

| 6.21 | S-Parameters and characteristic impedance Z0                               | 80 |

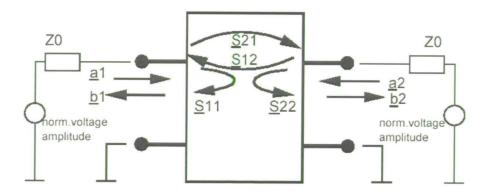

| 6.22 | signal flow                                                                | 81 |

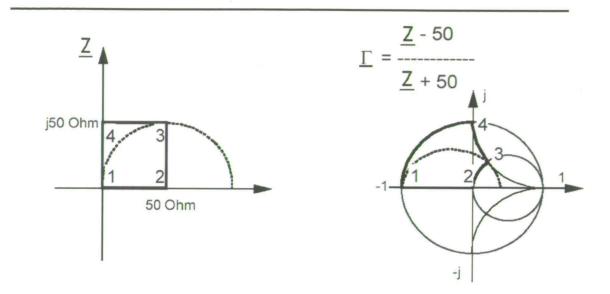

| 6.23 | the relationship between Sxx and the complex impedance of a twoport.       | 81 |

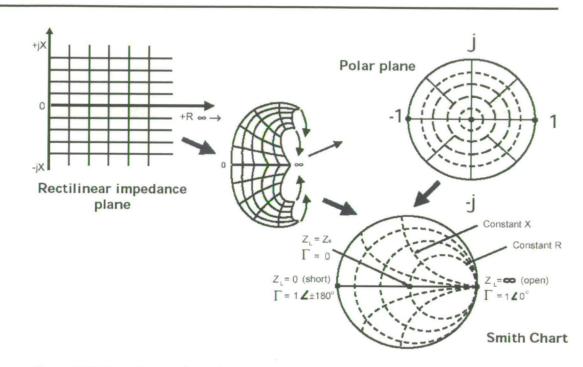

| 6.24 | about the definition of S11 (S22 is just analogous).                       | 84 |

| 6.25 | how the complex resistance plane is transformed into the Smith chart       | 85 |

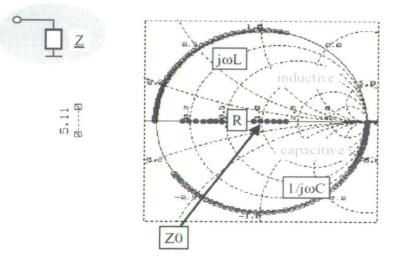

| 6.26 | Smith chart overview                                                       | 86 |

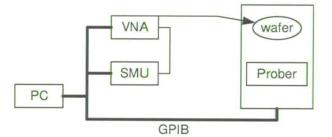

| 6.27 | Schematic overview of the measurement setup                                | 86 |

| 6.28 | Extraction results of the RF measurement test-structure                    | 88 |

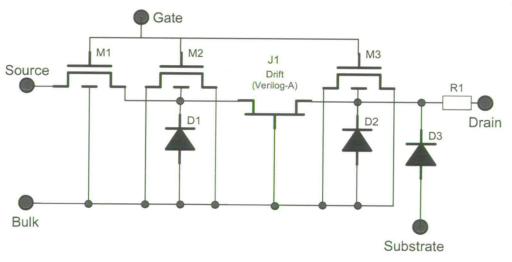

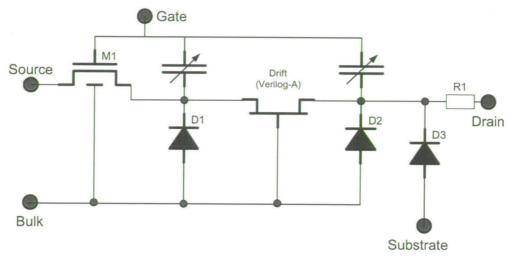

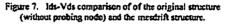

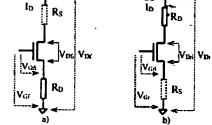

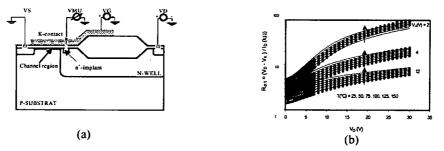

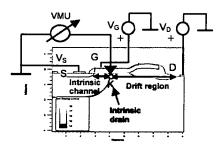

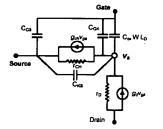

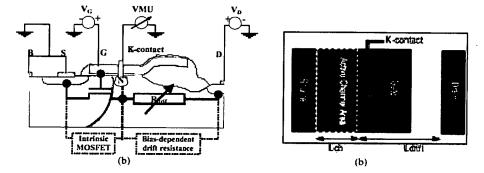

| 7.1  | Sub-circuit model of LDMOS device                                          | 91 |

| 7.2  | Sub-circuit model of LDMOS device                                          | 92 |

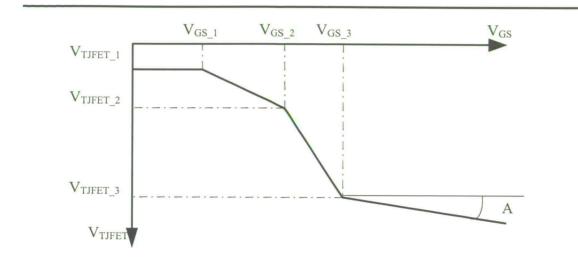

| 7.3  | JFET VT dependence as a function of VGS.                                   | 96 |

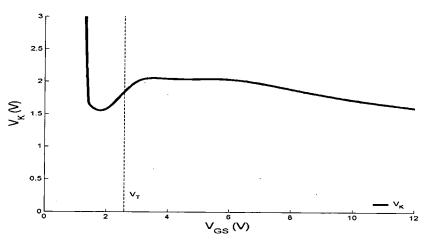

| 7.4  | VK as modelled by a JFET as a function of VGS at VDS=10V.                  | 96 |

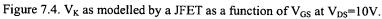

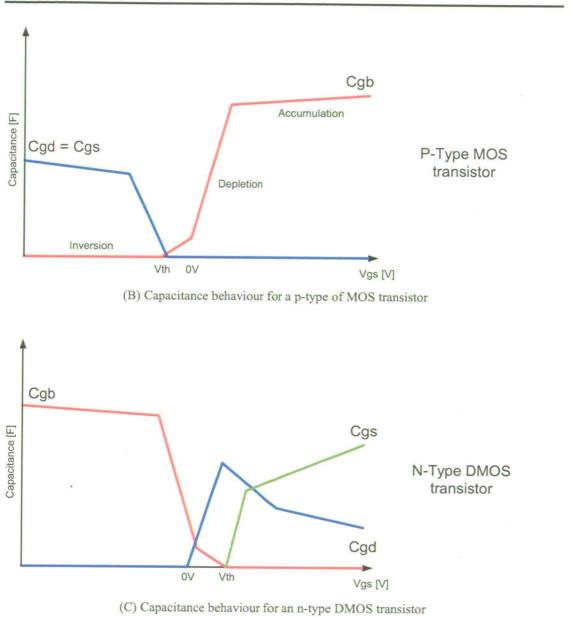

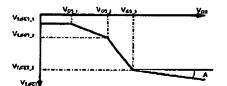

| 7.5  | VK and VBB as a function of VGS with source closed and open at VDS         |    |

|      | = 10V.                                                                     | 97 |

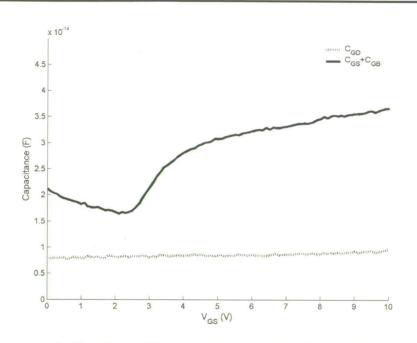

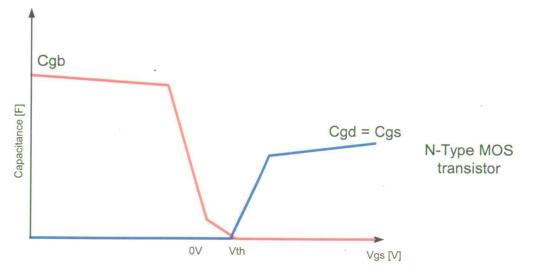

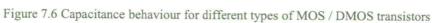

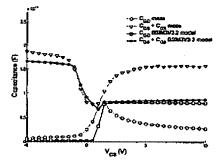

| 7.6  | Capacitance behaviour for different types of MOS / DMOS transistors        | 99 |

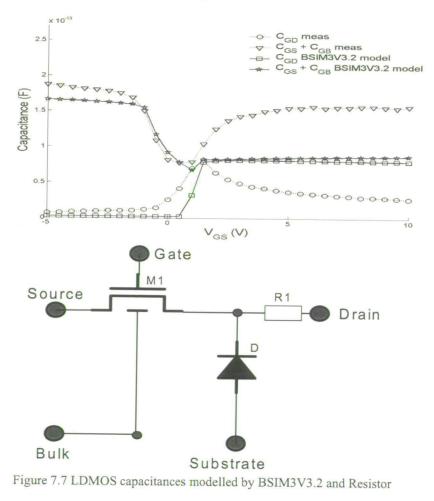

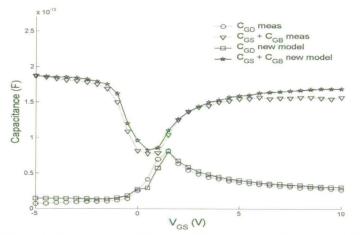

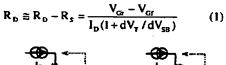

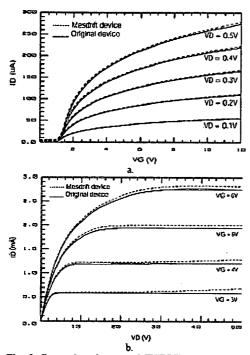

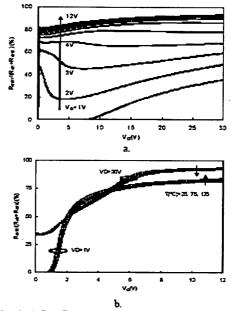

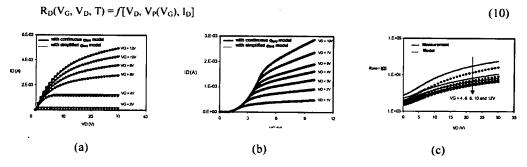

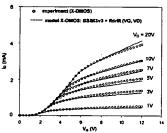

| 7.7  | LDMOS capacitances modelled by BSIM3V3.2 + Resistor                     | 100 |

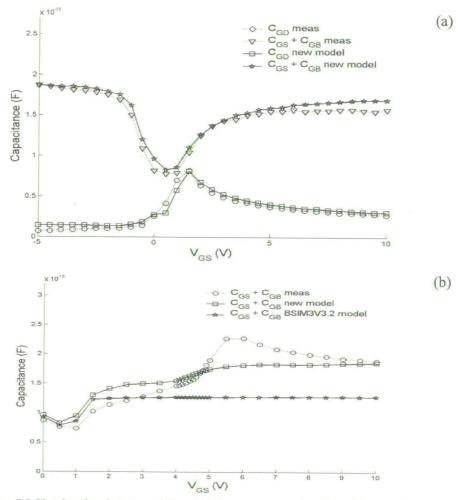

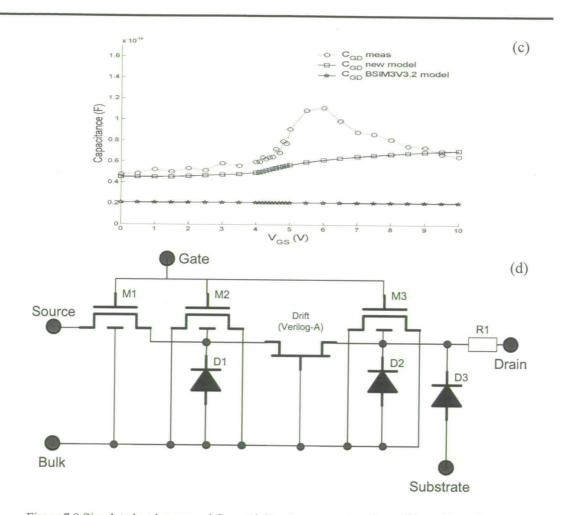

|------|-------------------------------------------------------------------------|-----|

| 7.8  | Simulated and measured CGD and CGS curves as a function of VGS at       |     |

|      | VDS = 0 and 20V for both the old and new models. (a) Comparison         |     |

|      | between measurements and simulations based on the new macro-model       |     |

|      | at $VDS = 0V$ ; (b) Comparison of CGS measurements and simulations      |     |

|      | based on the new macro-model and old model at $VDS = 20V$ ; (c)         |     |

|      | Comparison of CGD measurements and simulations based on the new         |     |

|      | macro-model and old model at $VDS = 20V$ ; (d) model topology           | 102 |

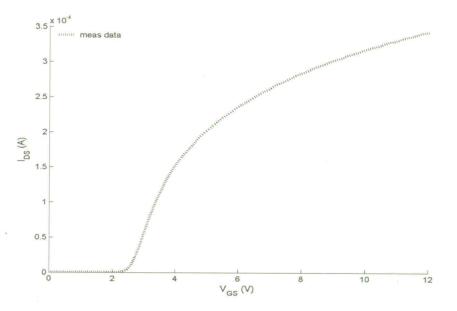

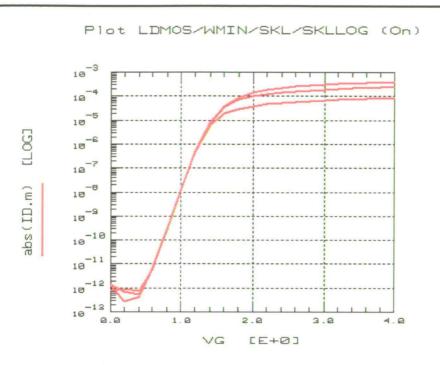

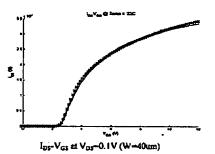

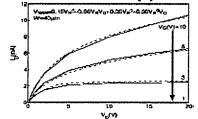

| 7.9  | LDMOS, Ids-Vgs curve, different W, logarithmic scale                    | 105 |

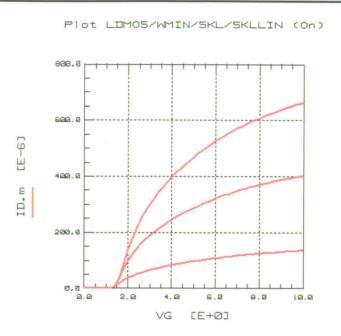

| 7.10 | LDMOS, Ids-Vgs curve, different Widths, linear scale                    | 106 |

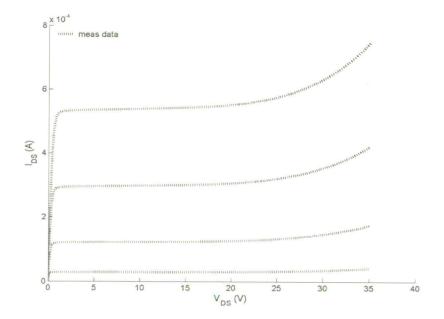

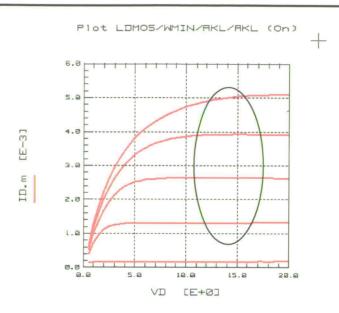

| 7.11 | LDMOS, Ids-Vds curve, different Vgs, linear scale                       | 107 |

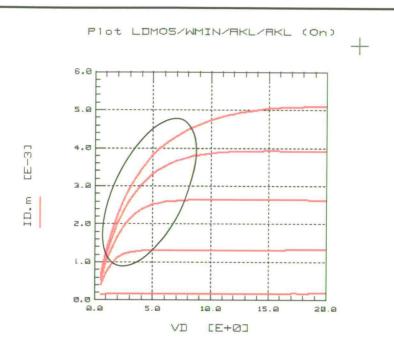

| 7.12 | LDMOS, IDS-VDS curve, different VGS, linear scale                       | 108 |

| 7.13 | JFET VT behaviour in relation to the LDMOS VGS                          | 109 |

| 7.14 | Simulated and measured CGD and CGS curves as a function of VGS at       |     |

|      | VDS = 0                                                                 | 111 |

| 7.15 | Section through an LDMOS.                                               | 112 |

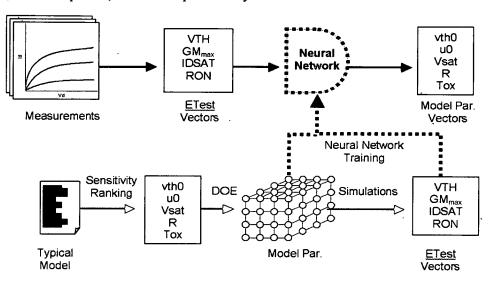

| 7.16 | Flow for translating E-Test parameter vectors into model parameter      |     |

|      | vectors.                                                                | 115 |

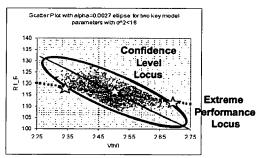

| 7.17 | Corners as the intersection of the extreme performance locus and the    |     |

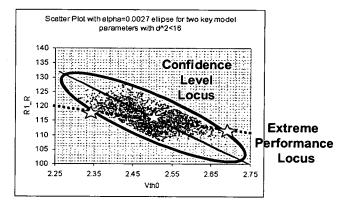

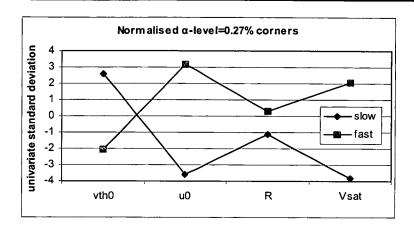

|      | 99.73% confidence locus of the population.                              | 116 |

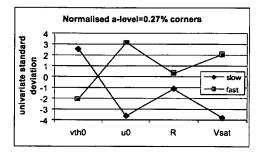

| 7.18 | Parameter excursions for worst-case models normalised to univariate     |     |

|      | standard deviations.                                                    | 117 |

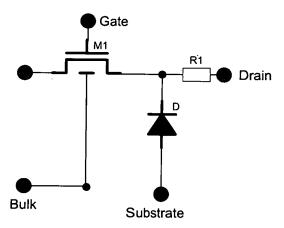

| 8.1  | old LDMOS model topology.                                               | 119 |

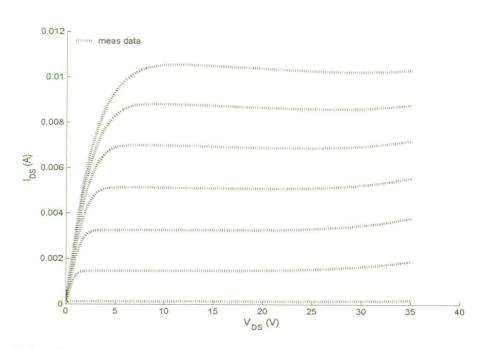

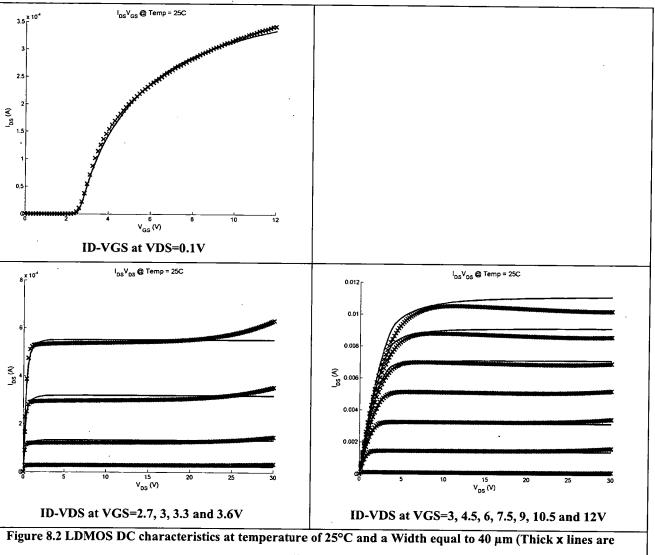

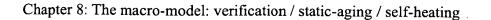

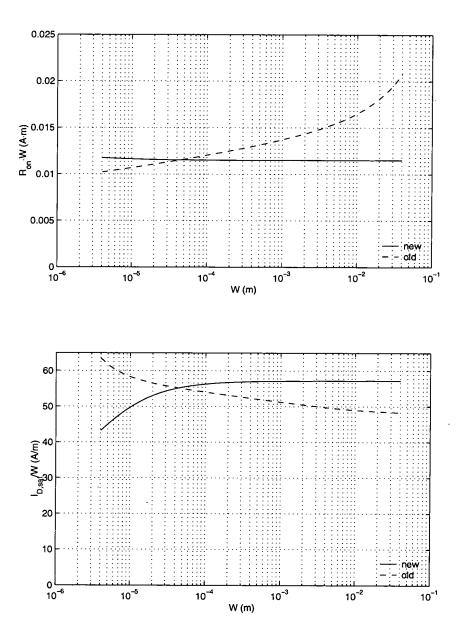

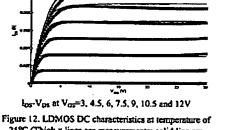

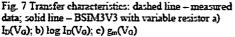

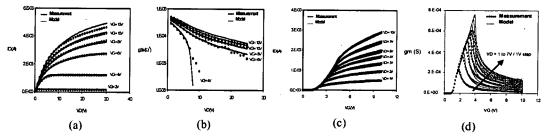

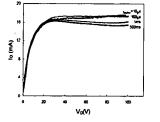

| 8.2  | LDMOS DC characteristics at temperature of 25C                          | 122 |

| 8.3  | LDMOS DC-characteristics at temperature of 125C                         | 123 |

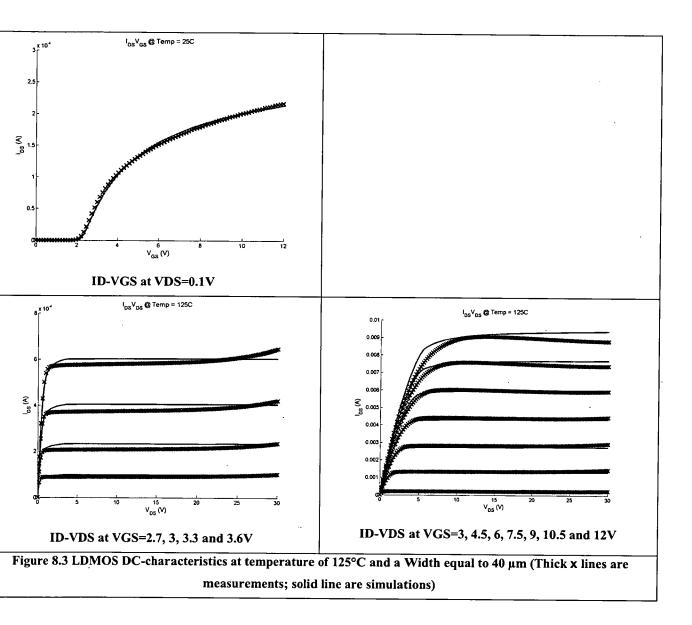

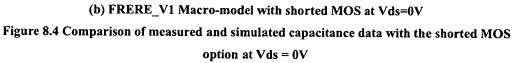

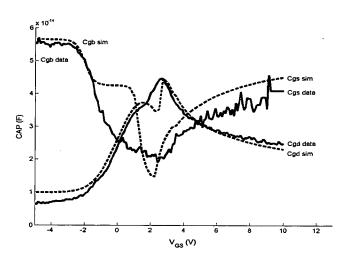

| 8.4  | Comparison of measured and simulated capacitance data with the          |     |

|      | shorted MOS option at $Vds = 0V$                                        | 124 |

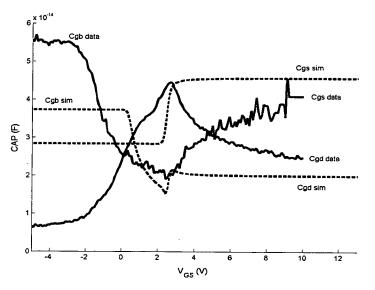

| 8.5  | Comparison of measured and simulated capacitance data with the          |     |

|      | shorted MOS option at $Vds = 20V$                                       | 126 |

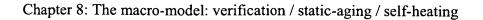

| 8.6  | evolution of (RON*W) and (IDSAT/W) versus W for the extracted model     | 127 |

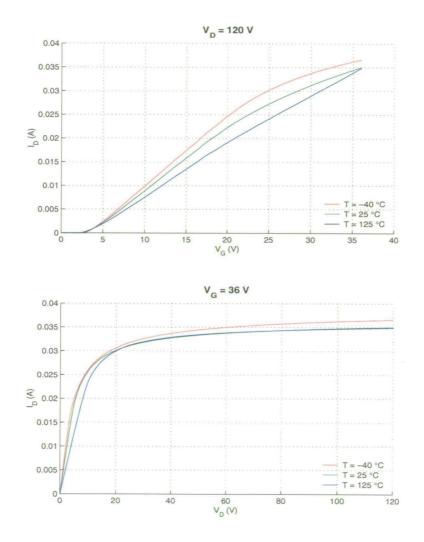

| 8.7  | Robustness test at device level of the extracted model                  | 128 |

| 8.8  | Simulated E-test parameters for three corners at three temperatures for |     |

|      | the extracted model.                                                    | 129 |

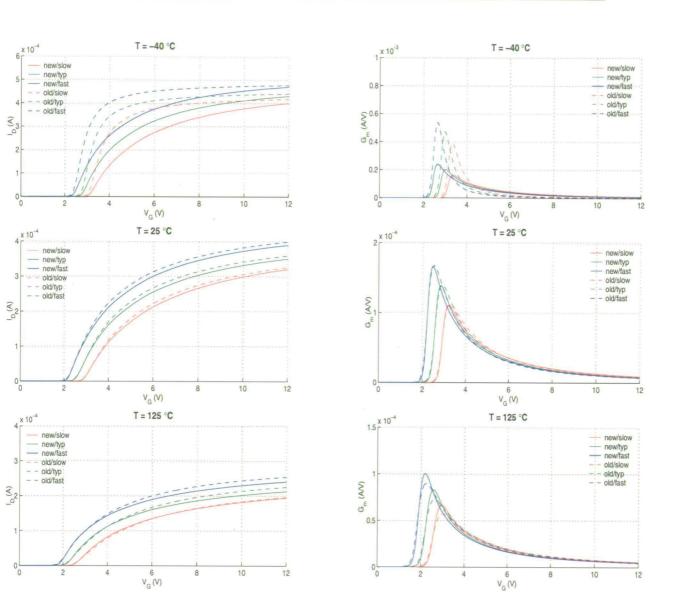

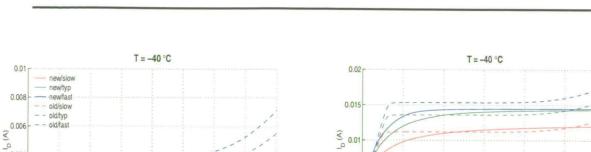

| 8.9  | Ids-Vgs and Gm-Vgs at Vds=100mV at three different temperatures: old  |     |  |

|------|-----------------------------------------------------------------------|-----|--|

|      | and new model.                                                        | 131 |  |

| 8.10 | Ids-Vds at Vgs=5V (left) and at Vgs=12V (right) at different          |     |  |

|      | temperatures, old and new model.                                      | 132 |  |

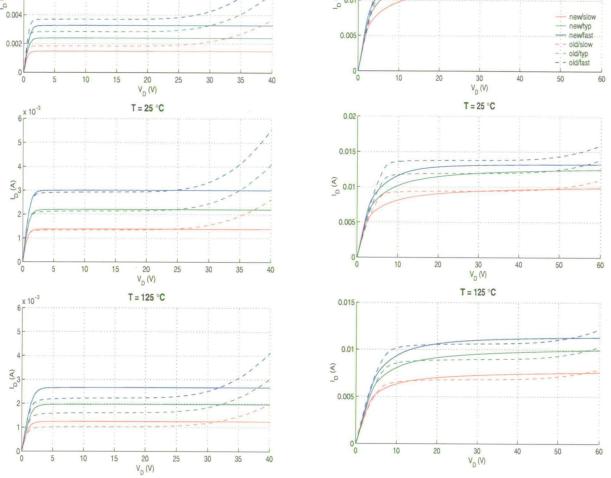

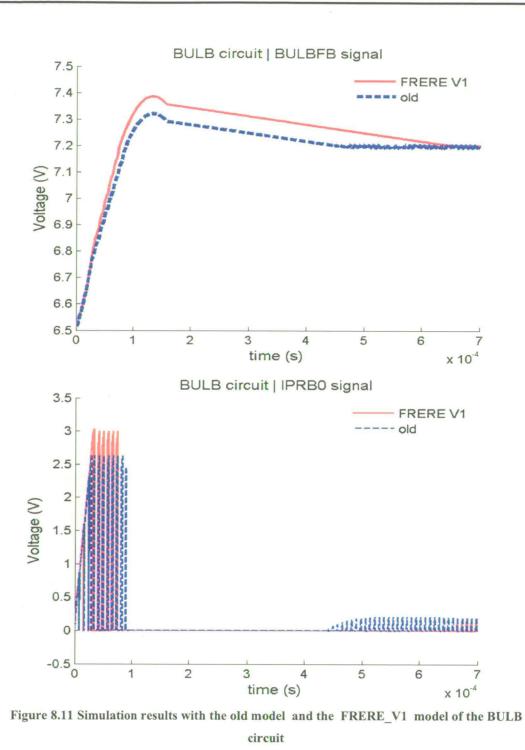

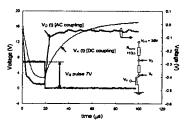

| 8.11 | Simulation results with old model / new model of the BULB circuit     | 135 |  |

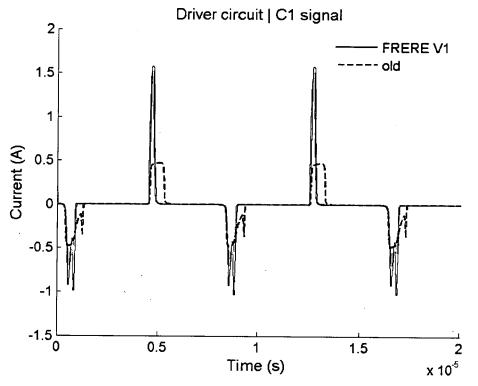

| 8.12 | Circuit simulations results of the motor driver with old / new model  | 137 |  |

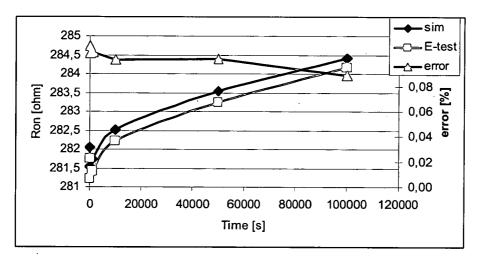

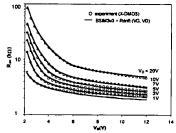

| 8.13 | Comparison of the modelled and measured RON                           | 140 |  |

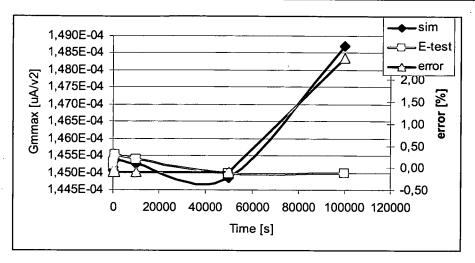

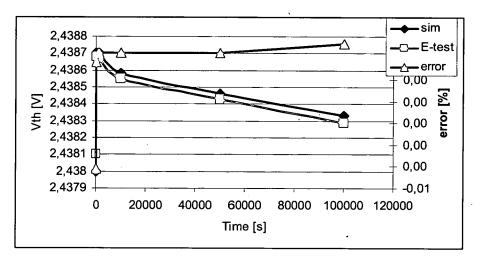

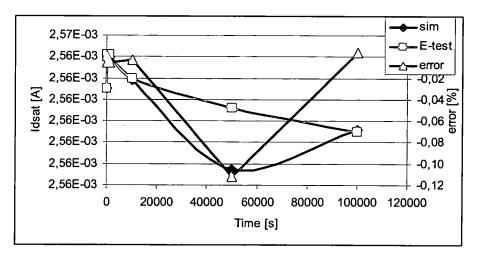

| 8.14 | Comparison of the modelled and measured GMMAX                         | 141 |  |

| 8.15 | Comparison of the modelled and measured VTH                           | 141 |  |

| 8.16 | Comparison of the modelled and measured IDSAT                         | 142 |  |

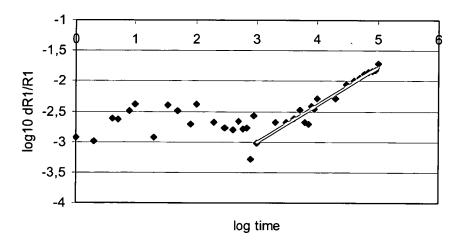

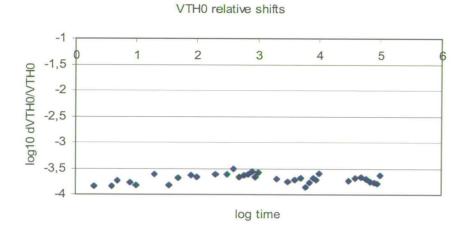

| 8.17 | Logarithmic plot of the relative shifts of R1.r with time             | 143 |  |

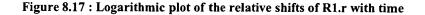

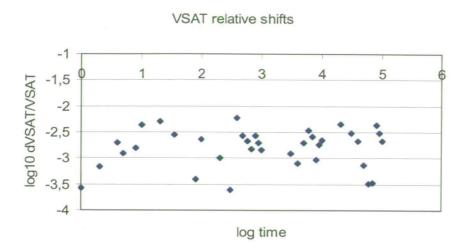

| 8.18 | Logarithmic plot of the relative shifts of U0 with time               | 143 |  |

| 8.19 | Logarithmic plot of the relative shifts of VTH0 with time             | 144 |  |

| 8.20 | Logarithmic plot of the relative shifts of VSAT with time             | 144 |  |

| 8.21 | Comparison of measurements to the simulated values based on the       |     |  |

|      | Rinaldi equation                                                      | 145 |  |

| 8.22 | Comparison of corrected measurements to the simulated values based on |     |  |

|      | the Rinaldi equation                                                  | 146 |  |

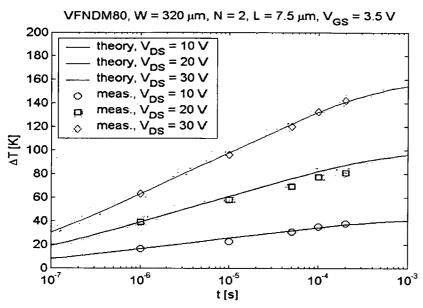

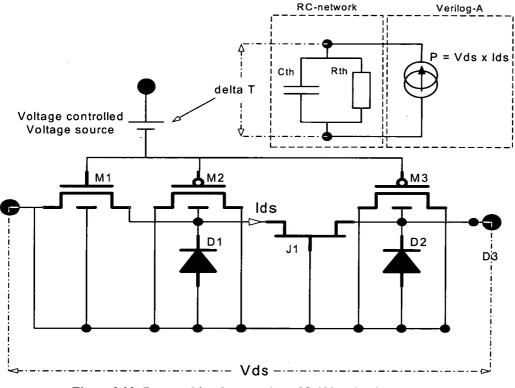

| 8.23 | Proposed implementation of Self-heating into the macro-model          | 147 |  |

## List of tables

| 2.1.  | Important implants and layers thickness parameters for DMOS devices         |     |  |  |

|-------|-----------------------------------------------------------------------------|-----|--|--|

| 2.2.  | Geometrical parameters definition                                           |     |  |  |

| 2.3.  | Overview of N-channel LDMOS device features                                 |     |  |  |

| 2.4.  | Overview of N-channel XDMOS features                                        |     |  |  |

| 2.5.  | Overview of P-channel XDMOS features                                        | 15  |  |  |

| 3.1.  | Overview/comparison of the different modelling concepts. $1 = $ excellent 5 |     |  |  |

|       | = poor                                                                      | 32  |  |  |

| 4.1.  | Characteristic bias voltages for an LDMOS device.                           | 38  |  |  |

| 4.2.  | Electrical parameters definitions for LDMOS devices                         | 39  |  |  |

| 4.3.  | DC characteristics. The voltage values and voltage ranges in the table are  |     |  |  |

|       | specified for N-channel devices. For P-channel the inequaities and signs    |     |  |  |

|       | need to be adapted.                                                         | 40  |  |  |

| 4.4.  | Generalised small-signal parameters of LDMOS devices                        | 41  |  |  |

| 4.5.  | Pulsed characteristics for LDMOS devices                                    | 41  |  |  |

| 4.6.  | Summary of the accuracy targets specified as max. allowed error.            | 45  |  |  |

| 4.7.  | Summary of the accuracy targets specified as max. allowed RMS error.        | 46  |  |  |

| 7.1.  | Description of the different geometry parameters                            | 104 |  |  |

| 7.2.  | Subthreshold parameters                                                     | 105 |  |  |

| 7.3.  | Triode parameters                                                           | 106 |  |  |

| 7.4.  | Saturation parameters                                                       | 107 |  |  |

| 7.5.  | JFET parameters modelling quasi-saturation                                  | 108 |  |  |

| 7.6.  | subthreshold temperature parameter                                          | 109 |  |  |

| 7.7.  | linear region temperature parameters                                        | 110 |  |  |

| 7.8.  | Saturation temperature parameters                                           | 110 |  |  |

| 7.9.  | AC-parameters                                                               | 111 |  |  |

| 7.10. | Impact of the key model parameters on the E-test parameters.                | 114 |  |  |

| 7.11. | Comparison between worst-case corners obtained from analysis on model       |     |  |  |

|       | parameter space versus E-test parameter space.                              | 118 |  |  |

| 8.1. | Range of DC-IV and AC-CV Characteristics.                                     | 121 |

|------|-------------------------------------------------------------------------------|-----|

| 8.2. | 8.2. Comparison of the statistically measured E-test parameters with the E-te |     |

|      | parameters extracted from the new model based on the worst-case corner        |     |

|      | extraction method previously described.                                       | 130 |

| 8.3. | Results of the BULB-circuit.                                                  | 134 |

| 8.4. | Results of the motor driver.                                                  | 136 |

|      |                                                                               |     |

٠

## Introduction

| 1.1 | Background              | 2 |

|-----|-------------------------|---|

| 1.2 | LDMOS transistor-models | 4 |

| 1.3 | Thesis plan             | 4 |

.

#### 1.1 Background

The history of microelectronics effectively began with the creation, at the Bell Telephone Laboratories, of the point contact transistor by Bardeen and Brattain in 1947. Around the same time, Shockley developed the theory behind the bipolar junction transistor, though this was not successfully fabricated until 1951 [1]. Similarly the effect of electric fields on the conductivity of semiconductors was demonstrated by Shockley and Pearson in 1948, but it took over ten years before the first Si/SiO2 MOSFET, which is now so widely used, was demonstrated by Kahng and Atalla [2]. Discrete transistors quickly found applications in hearing aids and transistor radios where their small size and low power consumption made them ideal replacements for thermionic valve technology [3]. However, they were not small enough for some applications and the impetus was there for the work, carried out at Texas Instruments by Kilby and at Fairchild Semiconductor by Noyce, which led to the production of the first integrated circuits at the end of the 1950's [4]. Kilby's circuits consisted of transistors fabricated using the mesa technique, where the collector contact is made to the backside of the wafer, and bonded gold wire is used for interconnect interconnect. Novce's ICs more closely resembled present day chips because they used a planar fabrication technique, developed by Hoerni at Fairchild, where oxide masking and diffusion were used to form the transistors [5]. His chip also included interconnects, created by photolithographic definition of evaporated aluminium, in a process very similar to that used today.

The initial circuits were oscillators and simple digital flip-flops using two or three active devices along with passive elements but by 1971 the technology had advanced to the stage where the first microprocessor, the Intel 4004, was fabricated with 2300 transistors [6]. In 1965 Moore published a paper on the state of the semiconductor industry which predicted that the number of devices in an integrated circuit would double each year [7]. This prediction became known as "Moore's Law" and was revised in 1975 to state that the number of transistors per chip would double every 18 months [8]. More recently the slope has changed again to give a doubling of circuit complexity approximately every two years, which leads to the prediction that within the next ten years microprocessors will exist which contain one billion transistors [9].

The increases in integration and chip complexity have come about as a result of the scaling of the transistors, in particular the scaling of the gate length of MOSFETs, and this has driven the advances in technology. More recently however limits have been placed on the scaling of interconnect which has encouraged advanced interconnect technologies such as low-k dielectrics and copper metallisation [10]. The International Technology Roadmap for Semiconductors (ITRS) charts the requirements for future technologies and the most recent release covers the technology nodes extending to 2007 where 65nm interconnect half-pitch lengths are expected with MOS gate lengths approaching 25nm [11, 12]. The increases in complexity have placed a premium on testing for process control and verification and the most recent roadmap focuses heavily on future metrology requirements [13,14].

In the automotive industry, there is a strong trend that has increased the electronics in cars for various functions like fuel injection, electric control of doors and windows, electric chair adjustment, air-conditioning, drive-by-wire, brake-by-wire, etc. The 12V battery used in present cars will not be sufficient for the increasing number of functions and as a consequence, a change towards 42V batteries will be necessary.

For these "automotive" systems, so-called smart power ICs must be used. These are chips in which the power functionality, e.g. the control of a motor is integrated with the logic control. There is also a trend towards operation at high voltages and integrating more intelligence using a microcontroller's RAM/ROM memory and several sensors and interfaces. The final goal is the integration of a complete system on a single chip, a so-called power System-on-Chip (SoC).

For all these reasons, a more advanced technology is required. Such technologies for smart power applications are based on a standard low-voltage CMOS technology, where power devices suited for middle to high voltages (80V spikes for the 42V car-battery) are fabricated with additional process modules, for example a thicker gate oxide module.

Examples of such integrated power transistors are vertical and lateral DMOS (Double diffused MOS) and IGBT (Insulated Gate Bipolar Transistor). In many cases, a power switch is the key application.

In such devices, the on-resistance and breakdown voltage are important performance parameters. A trade-off is necessary to obtain a device with a low on-resistance and a high energy capability. Needless to say, there is also the requirement for low production costs and high reliability.

3

#### 1.2 LDMOS transistor-models

The interest in accurately modelling high-voltage transistors has increased in recent years due to the compatibility of these devices with standard CMOS technology. LDMOS (Lateral Double diffused Metal Oxide Semiconductor) devices are now being more often employed in dynamic applications such as switches within power systems and fine slope control of electrical motor drivers. However, existing LDMOS models are not accurate enough for this task and SPICE models are especially weak when modelling AC performance. The limitation of these models lies in their lack of any capability to physically model some of the characteristic phenomena observed in LDMOS devices. The increased difficulty is related to complex 2D effects, specific to modern high voltage device architectures. Several workers have addressed the physics involved in the specific behaviour of these transistors [15], [16], [17], [18].

This thesis presents a new physically based macro-model. This model is based on the investigations performed on the key phenomena occurring in an LDMOS transistor. These phenomena were investigated by TCAD simulations and were confirmed by newly developed test-structures.

#### 1.3 Thesis plan

This section briefly outlines the contents of the chapters, which follow.

**Chapter 2: Introduction to LDMOS transistors** A basic overview of the LDMOS transistor is presented. The LDMOS transistor is situated in the family of components that are used in automotive integrated circuits. A short description will be presented of the AMIS high voltage I2T family which is used throughout this thesis, highlighting the distinction made between the different types of LDMOS / XDMOS transistors. Finally, some circuits that are of key importance in automotive designs are presented.

**Chapter 3: Introduction to modelling** Some definitions in relation to modelling are outlined. An example of modelling a diode is presented which shows many different aspects of modelling.

Chapter 4: LDMOS macro-model characteristics and macro-model requirements The electrical characteristics that matter for the modelling of DMOS devices and for circuit design are identified. These characteristics will be used for benchmarking the macro-model and in particular for the specification of accuracy targets. **Chapter 5: TCAD simulation of LDMOS transistors** Several physical effects are observed in a DMOS transistor and these can be simulated in TCAD (Technology Computer Aided Design). The key effects will be presented and discussed in the context of TCAD, illustrating how this can be applied to help develop models for circuit simulation programs.

Chapter 6: Description and results of the developed test-chips for DC and ACanalyses Test-structures are devices or a set of devices, used to analyse or verify a certain part of the process device behaviour. This chapter describes the different teststructures that were developed and used for the building-up and extraction of the macromodel. These test-structures and test-devices are designed so that they can be used to characterise either some of the behaviour observed from the TCAD simulations, or the complete device itself.

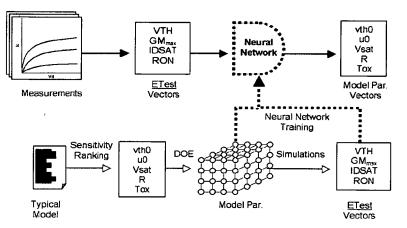

**Chapter 7: The macro-model: definition / extraction procedure / worst-case corners** Based on the findings of chapter 5 and chapter 6, a macro-model has been developed. As a first step, a topology is proposed and then the functionality of the topology is confirmed and an extraction procedure developed. As a model should be able to accurately predict the effect of process variations on the device performance, worst case models and a procedure to extract these models must be available This thesis proposes a novel method for this purpose, based on neural networks. A key element of establishing the model is to verify its performance against the targets set in chapter 4.

**Chapter 8: The macro-model: verification / static-aging / self-heating** This chapter presents the verification of the macro-model described in chapter 7. Proposals for future work are given at the end of the chapter, which covers methods to characterise self-heating effects and include static aging of LDMOS devices in the proposed macro-model.

Chapter 9: Conclusions and future work : In this chapter the conclusions from the work reported in the preceding chapters are reviewed. Suggestions for future work on the topics covered in this thesis are also made.

5

#### References

- [1] J.I. Nishizawa, "The Transistor: A Look Back and a Look Ahead," Solid State Technology, pp. 73-75, Dec 1987.

- [2] D. Kahng, "A Historical Perspective on the Development of MOS Transistors and Related Devices," IEEE Transactions on Electron Devices, vol. ED-23, pp. 655-657, Jul 1976.

- [3] C. Melliar-Smith, M. Borrus, D. Haggan, T. L. A. Vincentelli, and W. Troutman, "The Transistor: An Invention Becomes a Big Business," Proceedings of the IEEE, vol. 86, pp. 86-110, Jan 1998.

- [4] J. Kilby, "Invention of the Integrated Circuit," IEEE Transactions on Electron Devices, vol. ED-23, pp. 648-654, Jul 1976.

- [5] G. Moore, "The Role of Fairchild in Silicon Technology in the Early days of "Silicon Valley"," Proceedings of the IEEE, vol. 86, pp. 53-62, Jan 1998.

- [6] Y. Patt, "Requirements, Bottlenecks, and Good Fortune: Agents for Microprocessor Evolution," Proceedings of the IEEE, vol. 89, pp. 1553-1559, Nov 2001.

- [7] G. Moore, "Cramming More Components onto Integrated Circuits," Proceedings of the IEEE, vol. 86, pp. 82-85, Jan 1998.

- [8] P. Bondyopadhyay, "Moore's Law Governs the Silicon Revolution," Proceedings of the IEEE, vol. 86, pp. 78-81, Jan 1998.

- [9] E. Korcynski, "Moore's Law Extended: The Return of Cleverness," Solid State Technology, vol. 40, pp. 359-364, Jul 1997.

- [10] M. Bohr, "Interconnect Scaling The Real Limiter to High Performance ULSI," Solid State Technology, pp. 105-111, Sep 1996.

- [11] A. Allan, D. Edenfeld, W. Joyner, A. Kahng, M. Rodgers, and Y. Zorian, "2001 Technology Roadmap for Semiconductors," Computer, vol. 35, no. 1, pp. 42-53, 2002.

- [12] P. Gargini, "The Global Route to Future Semiconductor Technology," IEEE Circuits and Devices Magazine, pp. 13-17, Mar 2002.

- [13] Semiconductor Industry Association, International Technology Roadmap for Semiconductors: 2001 Edition. International SEMATECH, Austin, TX, USA, 2001. http://www.public.itrs.net/.

- [14] Solid State Technology Staff, "Meeting 2001 ITRS Challenges," Solid State Technology, pp. 42-64, May 2002.

- [15] Y.-S. Kim, J. Fossum, "New Physical Insights and Models for High-Voltage LDMOS IC CAD," IEEE Trans. Electron Devices, vol. 38, pp. 1641-1649.

- [16] J. Jaejune, T. Amborg, Yu. Zhiping and R.W. Dutton, "Circuit model for power LDMOS including quasi-saturation," Proceedings of SISPAD '99, pp.15-18.

- [17] C. Anghel, N. Hefyene, A.M. Ionescu, S. Frère, R. Gillon, M. Vermandel, B. Bakeroot and J. Doutreloigne, C. Maier and Y. Mourier, "Investigations and physical modelling of saturation effects in Lateral DMOS transistor architectures based on the concept of intrinsic drain voltage," Proceedings of ESSDERC 2001, pp. 399-402, Sep 2001.

- [18] S.F. Frère, J. Rhayem, H.O. Adawe, R. Gillon, M. Tack, and A.J. Walton, "LDMOS Capacitance Analysis versus Gate and Drain Biases, Based on Comparison between TCAD Simulations and Measurements," Proceedings of ESSDERC 2001, pp. 219-223, Sep. 2001.

## **Introduction to LDMOS transistors**

| 2 I | ntrod | uction to LDMOS transistors          | 8  |

|-----|-------|--------------------------------------|----|

| 2.1 | l In  | troduction                           | 8  |

| 2.2 | 2 St  | ructure of an n-type LDMOS           | 8  |

| 2.3 | 8 In  | nportant design parameters           | 9  |

|     | 2.3.1 | The Breakdown Voltage                | 9  |

|     | 2.3.2 | The on-resistance                    | 11 |

| 2.4 |       | he AMIS I2T technology family        | 11 |

| 2.5 | 5 DI  | MOS transistors in the I2T100 family | 12 |

| 4   | 2.5.1 | Implants and oxide layers            | 12 |

| 4   | 2.5.2 | Geometrical parameters definitions   | 13 |

| 4   | 2.5.3 | LDMOS device family                  | 14 |

| 2   | 2.5.4 | XDMOS devices                        |    |

| 2.6 | i Ci  | rcuit for model characterisation     | 16 |

| . 2 | 2.6.1 | Bulb – circuit                       | 16 |

| 2   | 2.6.2 | MOTOR-driver circuit (H-bridge)      |    |

| 2.7 | Co    | onclusion                            |    |

### 2 Introduction to LDMOS transistors

#### 2.1 Introduction

This chapter presents a basic overview of the LDMOS transistor. The LDMOS transistor is situated in the family of components that are used in automotive integrated circuits. A short description will be presented of the AMIS high voltage I2T family which is used throughout this thesis highlighting the distinction made between the different types of LDMOS / XDMOS transistors. Finally, some circuits that are of key importance in automotive designs are presented.

#### 2.2 Structure of an n-type LDMOS

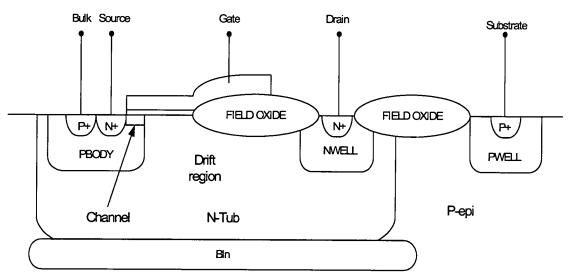

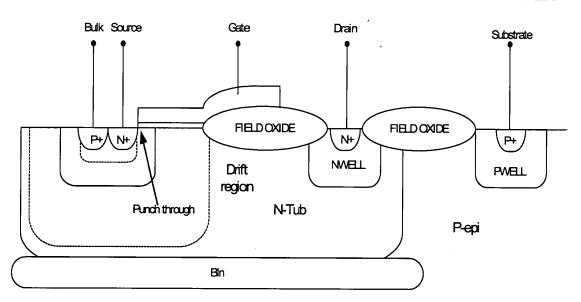

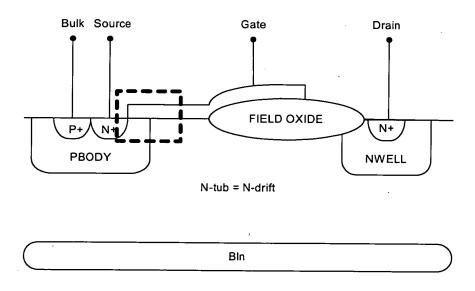

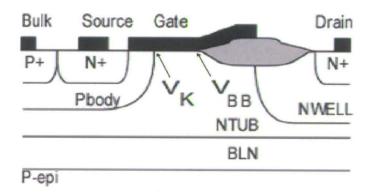

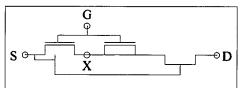

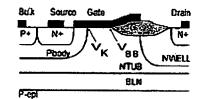

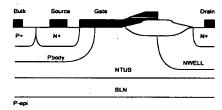

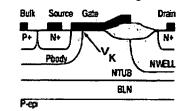

Figure 2.1 Generic structure of an n-type LDMOS

The cross-section of a generic n-type Lateral Double diffused MOS (LDMOS) is shown on Figure 2.1. The term lateral indicates the fact that the LDMOS is a horizontal device, where the current flows horizontally from the drain to the source. The second qualifier expresses the fact that the PBODY and the N+ source regions are diffused through a common window defined by the edge of the polysilicon gate.

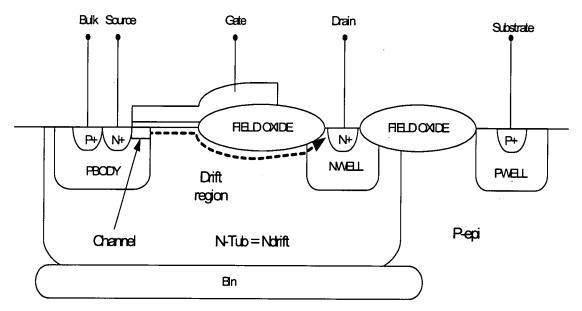

In the on-state the LDMOS works as a normal MOS device. The positive potential applied to the gate attracts electrons (in the case of an n-type LDMOS) at the surface of the PBODY under the gate creating a channel allowing current to flow (Figure 2.2). The difference between a MOS and an LDMOS device comes from the presence of the drift

region (light grey region in Figure 2.1, which is a combination of the N-Tub and N-well areas). The drift region is lightly doped and its purpose is to provide a high voltage blocking capability during off-state. This blocking capability (characterised by the breakdown voltage) is created by the reverse biased PBODY-Ndrift junction.

The LDMOS has a parasitic Bipolar Junction Transistor (BJT). It is constituted by the source  $N^+$ , PBODY and Ndrift layers, which are respectively the emitter, the base and the collector. The triggering of this parasitic BJT reduces the performance of the LDMOS and, hence, the source and the body layers are usually shorted.

The thick field oxide is necessary to avoid the destruction of the thin gate oxide resulting from a high drain to gate voltage.

Figure 2.2 Current flow in an LDMOS

#### 2.3 Important design parameters

#### 2.3.1 The Breakdown Voltage.

The breakdown voltage of the device is the voltage at which the device enters into avalanche breakdown and therefore is the fundamental determinant of the maximum operating voltage. Large values of breakdown voltage are desired to provide high blocking capabilities. The breakdown voltage is largely defined by the doping profile and the length of the PBODY-Ndrift blocking junction.

To be able to provide a high forward blocking capability, an optimum has to be determined for the doping profile of the PBODY-Ndrift junction and the PBODY depth.

9

.

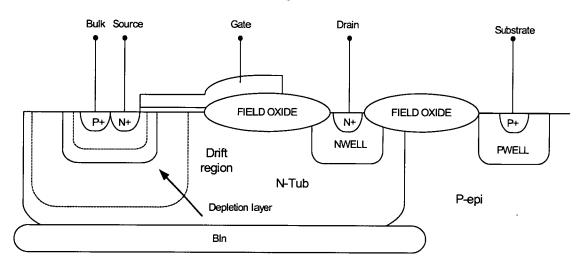

When a positive voltage is applied at the drain (assuming the source and the gate are set at zero volts), the PBODY-Ndrift junction becomes reverse biased. It supports the drain voltage by extending the depletion layer on both sides of the junction. (Figure 2.3) To enhance the drain blocking voltage, the doping of the Ndrift region has to be reduced. The forward blocking capability is created by the reverse biased PBODY-Ndrift junction. The depletion layer extends effectively only into the Ndrift layer as it is lightly doped. Therefore decreasing the Ndrift doping increases the depletion width. As a result, the potential barrier becomes higher, improving the blocking capability. However this results in higher resistivity and thus a higher on-resistance.

Figure 2.3 Formation of depletion regions in DMOS devices

This twofold effect implies that the doping level of the PBODY layer should be optimised between the LDMOS threshold voltage and the triggering of the parasitic bipolar. However, there is also another phenomenon which must be taken into account. It is called the punch-through effect and occurs when the depletion region in the PBODY extends so far that it comes into contact with the N+ source. At this moment, the potential barrier vanishes (Figure 2.4) and the device begins to conduct. To prevent punch-through, there are two alternatives. On the one hand, we can vary the PBODY thickness and doping level. Alternatively the N-Tub layer thickness can be increased because the depletion layer spreads approximately equally in every direction.

Figure 2.4 Punch Through in an LDMOS

#### 2.3.2 The on-resistance

The on-resistance of the LDMOS is defined as the total resistance between the source and the drain contacts in the on-state. It is an important parameter as it directly determines the power dissipation during current conduction which is given by:

$$P = V_{DS} I_D$$

(2.1)

= R<sub>or</sub> I<sub>D</sub><sup>2</sup> (2.2)

The on-resistance is the sum of all the resistance contributions along the path travelled by the carriers during the on-state:

$$R_{on} = 2 x R_{N+} + R_{CH} + R_A + R_{Ntub} + R_{NWELL}$$

(2.3)

where

| $R_{N^+}$          | is the contribution from the N+ source or drain diffusion.     |

|--------------------|----------------------------------------------------------------|

| R <sub>CH</sub>    | is the channel resistance.                                     |

| R <sub>A</sub>     | is the resistance of the accumulation layer formed in the Ntub |

|                    | under the polysilicon gate.                                    |

| R <sub>Ntub</sub>  | is the Ntub resistance.(under the thick oxide)                 |

| R <sub>NWELL</sub> | is the NWELL resistance.                                       |

|                    | •                                                              |

#### 2.4 The AMIS I2T technology family

The AMIS I2T100 technology family will be used for all the LDMOS devices which will be modelled in this thesis. The following gives a brief description of the major attributes. The Intelligent Interface Technology (I2T) is the high voltage extension of the AMIS CMOS  $0.7\mu m$  mixed signal technology. I2T100 has been developed to meet the increasing demand for more digital integration in mixed analogue/digital ASICs and more programmability/flexibility.

This technology is derived from a fully digital  $0.7\mu m$  CMOS process and extended with the following analogue capabilities:

- Precision highly linear thin oxide poly/diffused capacitors

- Precision high ohmic polysilicon resistors

- Low Vt PMOS transistor

- Medium-High voltage NDMOS

- Floating medium-high voltage NDMOS and PDMOS

- Floating CMOS

- Low-medium-high voltage bipolar transistors

- Zener zap diode for OTP (One Time Programmable) applications

- High-Medium voltage floating capacitors

- Deep n+ doped guard rings

- EEPROM matrix blocks in the basic CMOS 0.7μm platform as well as in I2T100

Europractice distributes the design kit from AMIS, using the Cadence environment based on the Spectre simulator (Analog Artist) [1] for mixed mode front-end simulation and Silicon Ensemble place&route for CMOS 0.7µm back-end.

### 2.5 DMOS transistors in the I2T100 family

The purpose of this section is to describe the various devices types in more detail. In particular, it identifies the location, extent and doping level of implants as well as the range of layout dimensions. This is necessary to obtain a better understanding of the features that are required by any model that is created.

#### 2.5.1 Implants and oxide layers

The most important layers in DMOS devices are listed in Table 2.1 together with the order of magnitude of their doping levels, diffusion depths and gate-oxide thicknesses.

|                  | Doping level                   | Depth      |

|------------------|--------------------------------|------------|

| PBody            | $\sim 10^{15} \text{ cm}^{-3}$ | ~1.5 µm    |

| PWell            | $\sim 10^{17} \text{ cm}^{-3}$ | ~0.5 µm    |

| PSub             | $\sim 10^{14} \text{ cm}^{-3}$ | ~500 µm    |

| P-Epi            | $\sim 10^{16} \text{ cm}^{-3}$ | ~3.5 µm    |

| NBody            | $\sim 10^{15} \text{ cm}^{-3}$ | ~1.5 µm    |

| NWell            | $\sim 10^{17} \text{ cm}^{-3}$ | ~2 µm      |

| NTub             | $\sim 10^{15} \text{ cm}^{-3}$ | ~5 µm      |

| Thick Gate Oxide | n.a                            | 35 – 50 nm |

| Thin Gate Oxide  | n.a.                           | 15 – 20 nm |

Table 2.1 Important implants and layer thickness parameters for DMOS devices

#### 2.5.2 Geometrical parameter definitions

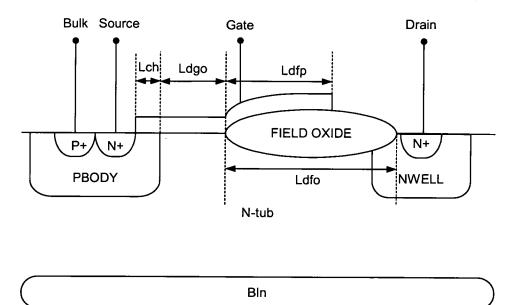

The naming conventions for geometrical parameters, used in this document, are defined in Figure 2.5 and Table 2.2.

Figure 2.5 Identification of layout dimensions

| Dimension | Description                                  |  |

|-----------|----------------------------------------------|--|

| W         | Total width of the channel                   |  |

| Lch       | Length of the channel region                 |  |

| Ldgo      | Length of the drift region under the gate-   |  |

| Lugo      | oxide                                        |  |

| Ldfp      | Overlap of the gate poly on the field-oxide  |  |

| Ldfo      | Length of drift region under the field-oxide |  |

Table 2.2 : Geometrical parameter definitions

#### 2.5.3 LDMOS device family

LDMOS devices present one of the biggest modelling challenges due to the continuously varying doping concentration along the channel and the presence of an accumulation region of substantial length underneath the gate-oxide. The modelling of the drift region also requires a great deal of attention.

A description of the different parameters of the n-channel LDMOS device is presented in Table 2.3. In the I2T100-family no p-channel LDMOS device is available.

|               | Channel : Pbody                 |                 |  |

|---------------|---------------------------------|-----------------|--|

| Layers        | Drift : Nwell                   |                 |  |

| Layers        | Bulk : Pbody                    |                 |  |

|               | Gate Oxide : Thick              |                 |  |

|               | Lch                             | 0.5 μm – 1.5 μm |  |

|               | Ldgo                            | 1 μm – 2.5 μm   |  |

| Layout param. | Ldfp                            | 1 μm – 6 μm     |  |

|               | Ldfo                            | 2 μm – 9 μm     |  |

|               | W                               | 2 µm– 10 mm     |  |

| Comments      | • Floating, Self-aligned device |                 |  |

#### 2.5.3.1 N-channel LDMOS device

#### Table 2.3 Overview of N-channel LDMOS device features

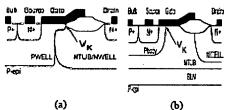

#### 2.5.4 XDMOS devices

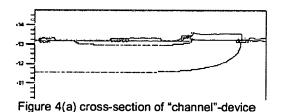

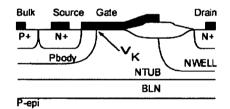

This new acronym was introduced to designate the family of 'eXtended Drain MOS' transistors, for which no real consensus exists in the literature. Contrary to LDMOS devices, the extent of the channel region is defined by specific masking steps, and the drain-end of the channel is not self-aligned to the source. The channel of these devices closely resembles that of common MOSFETs, and the major modelling challenges reside in the transition region at the end of the channel as well as in the drift region.

A description of the different parameters of the n and p-channel XDMOS devices is presented in Table 2.4 and Table 2.5 respectively. The cross-section of the device is similar to Figure 2.5.

|                           | Channel : Pwell                 |                       |  |  |

|---------------------------|---------------------------------|-----------------------|--|--|

| T                         | Drift : Nwell or ntub           |                       |  |  |

| Layers                    | Bulk : p-epi/ psub              |                       |  |  |

|                           | Gate Oxide : Thick or thin      |                       |  |  |

|                           | Lch                             | 3.5 μm – 4.5 μm       |  |  |

|                           | Ldgo                            | 1.8 μm – 2.4 μm       |  |  |

| Layout param.             | ' Ldfp                          | 2 μm – 3 μm           |  |  |

|                           | Ldfo                            | 2.5 μm – 13 μm        |  |  |

|                           | W .                             | 2 µm – 10 mm          |  |  |

| Comments                  | Non-floating, Non self-aligned, |                       |  |  |

| Comments                  | with or without BLN             |                       |  |  |

| Table                     | 2.4 : Overview of N-c           | hannel XDMOS features |  |  |

|                           | Channel : Ntub or nwell         |                       |  |  |

| Layers levels             | Drift : PField + Pbody or pwell |                       |  |  |

| Layers revers             | Bulk : Ntub                     |                       |  |  |

|                           | Gate Oxide : Thick              |                       |  |  |

|                           | Lch                             | 0.5 μm – 1.5 μm       |  |  |

|                           | Ldgo                            | 1 μm – 2.5 μm         |  |  |

| Layout param.             | Ldfp                            | 1 μm – 1.7 μm         |  |  |

|                           | Ldfo                            | 2 μm – 3.5 μm         |  |  |

|                           | W                               | 2 μm – 10 mm          |  |  |

| Comments Floating device. |                                 | Floating device.      |  |  |

Table 2.5 : Overview of P-channel XDMOS features

#### 2.6 Circuit for model characterisation

The following describes two standard circuits that have been used in commercial products where the main component is the DMOS transistor. These circuits will be used later in the thesis to evaluate the circuit-performance of the proposed macro-model.

#### 2.6.1 Bulb - circuit

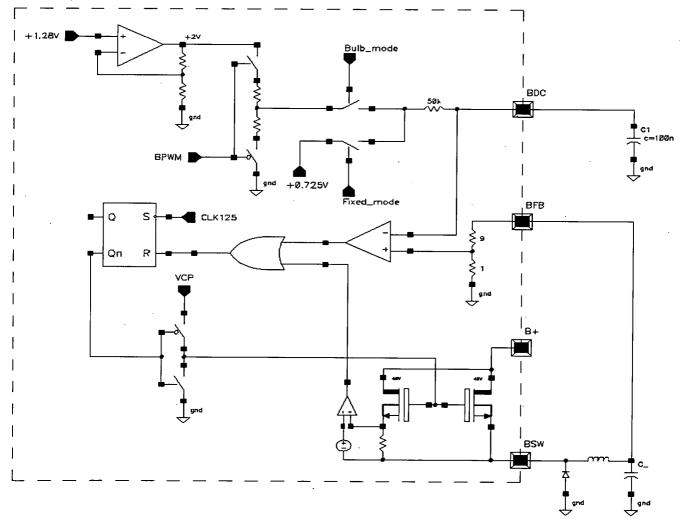

Figure 2.6 Schematic view of the BULB-circuit

The bulb driver is a variable voltage source that can be used in two different modes, either in 'bulb' or in 'fixed' mode. A circuit schematic view is shown in Figure 2.6. In 'bulb' mode, it can generate an output voltage between 1.8V and 20V. The output voltage is defined by an external signal (Pulse Width Modulated = PWM), entering on the input pin (BPWM). In this 'bulb' mode, the load is an inverter circuit (DC/AC

converter), which supplies the bulb. In the 'fixed' mode the output voltage is fixed to a typical nominal level of 7.25V and in this mode the external PWM signal has no effect on the output voltage. In the 'fixed' mode the 7.25V output voltage is used to pre-regulate the internal 5V linear regulator and to supply the external LEDs, whose currents are controlled by internally programmable current source circuitry.

The bulb regulator/driver is implemented as a constant ripple buck regulator. This regulator can operate in discontinuous or continuous mode, depending on the load current and input voltage. The clock source is an on-board 125 kHz signal, realized by dividing down the master oscillator of 4 MHz by 32. Pulse skipping is applied for the lower current range. The N-type LDMOS power-switch is part of the ASIC, but the remaining components like the recovery diode, inductors and output capacitors, are external.

#### 2.6.2 MOTOR-driver circuit (H-bridge)

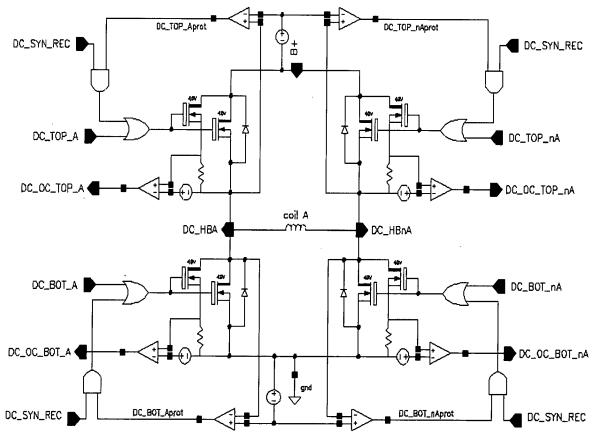

Figure 2.7 Schematic view of the motor driver-circuit

A typical circuit where DMOS transistors are used is an H-bridge driving a DC motor and a schematic view is shown in Figure 2.7. This versatile circuit is capable of applying voltages of both polarities across the load, by controlling the gating sequences of the four switches.

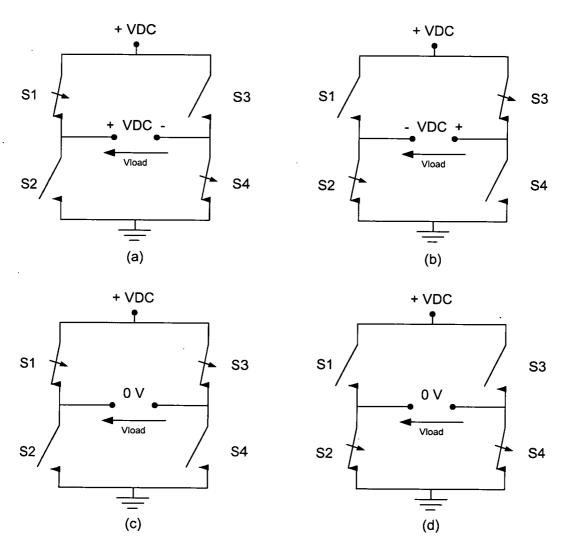

Figure 2.8 The four valid H-bridge switching states (excluding open circuit load state): (a) Supplies +VDC; (b) Supplies -VDC; (c) & (d) Both supply zero voltage (short-circuited load)

It is important to recognise that there are only four valid states for current conduction, as shown in Figure 2.8. Neglecting semiconductor voltage drops for the moment, one of these states applies +VDC across the load (Figure 2.8(a)), another applies -VDC (Figure 2.8 (b)) and the other two states (Figure 2.8(c) and (d)) effectively short circuit the load.

Current-regulated PWM control generally provides the basis for higher performance motor control than voltage regulation since torque is directly related to the motor winding current amplitude. Basic PWM voltage regulation is accomplished by means of a high-frequency duty cycle control. One straightforward PWM implementation compares the desired voltage level to a fixed-frequency ramp signal, switching the H-bridge output state when the ramp exceeds the command level. Using the H-bridge locked anti-phase control mode described above, the ramp comparison PWM strategy varies the average H-bridge output voltage over the full range from - VDC to + VDC by adjusting the relative widths of the -VDC and +VDC output pulses.

These two circuits were chosen as the key devices in these circuits are DMOS transistors. Hence the comparison of measured characteristics with simulation results will be a measure for the accuracy of the model. In addition to the issue of accurate circuit simulation results, these circuits are well suited to test the robustness of the model. This is because the device states in the circuit continuously change, introducing current spikes which the model should be able to withstand.

#### 2.7 Conclusion

Different aspects of the DMOS transistor have been presented. An introduction to the various trade-offs that can be made when developing a DMOS transistor have been discussed. It has been shown that different classes of DMOS transistors exist, depending on how the channel is defined. It is these devices that will be used throughout this thesis to characterise the macro-model to be developed. Finally, two circuits have been selected (the bulb-circuit and the H-bridge) to validate the model and check the model accuracy and robustness.

#### References

[1] Affirma Spectre Circuit Simulator Reference, Product Version 5.0.33, June 2004. website: <u>www.cadence.com</u>

# Introduction to modelling

| 3 Introduct | ion to modelling                                       |    |

|-------------|--------------------------------------------------------|----|

| 3.1 Intro   | duction                                                |    |

| 3.2 Defir   | nition of terms                                        | 21 |

| 3.3 Mod     | elling example based on a diode model                  |    |

| 3.3.1       | Introduction                                           |    |

| 3.3.2       | Equivalent circuit                                     |    |

| 3.3.3       | DC Characterisation                                    | 23 |

| 3.3.4       | CV Characterisation                                    | 25 |

| 3.4 Mod     | el types and their implementation                      |    |

| 3.4.1       | Types of models                                        |    |

| 3.4.2       | Implementation in circuit-simulators                   |    |

| 3.4.3       | Overview / comparison of different modelling concepts: |    |

| 3.4.4       | Discussion and Conclusion                              | 32 |

| 3.5 Conc    | lusion                                                 |    |

| References  |                                                        | 34 |

## 3 Introduction to modelling

#### 3.1 Introduction

The purpose of this chapter is to set some definitions in relation to modelling. An example of modelling a diode is used which shows many different aspects of modelling.

#### 3.2 Definition of terms

The definitions for the terms analysis, simulation and modelling are derived from "Analyses and Simulation of Semiconductor Devices" by S. Selberherr. [1]

#### Analysis

- Separation of a whole into its component parts, possibly with comment and judgement.

- Examination of a complex, its elements, and their relations in order to learn.

#### Simulation

- Imitative representation of the functioning of one system or process by means of the functioning of another.

- Examination of a problem not subject to experimentation.

#### Modelling

- To produce a representation or simulation of a problem or process.

- To make a description or analogy used to help visualise something that cannot be directly observed.

Therefore, as difficult as it might be to decide in an individual case, analysis is at least intended to mean "exact analysis" and simulation must mean "approximate simulation" by inference. Modelling is obviously a necessity for analysis and simulation.

With a model one can analyse some phenomena, provided that the effects one wants to observe are built into the model, possibly in a very complex manner. A model for the purpose of pure simulation (like a curve fitting model) is usually much simpler than a model for analysis. Many effects can be treated in a very heuristic manner for the purpose of simulation, by representing the underlying physics in a qualitative way.

#### 3.3 Modelling example based on a diode model

#### 3.3.1 Introduction

A simple way to fit non-linear curves to measured non-linear data is to transform them to a linear representation. But the question is: how to do it? A look at the "target function" of the model equation gives a hint. For example in the case of an exponential function:

$$i = I_S \times e^{\frac{V_D}{N \times vt}}$$

(3.1)

the transformation needed is a simple logarithmic conversion. The symbols used in equation 3.1 are defined on the following pages. Once the measured data is transformed to this linear range, a linear regression analysis can be applied and the slope and yintersect extracted. The model parameters are finally determined from these two values. This will become much more transparent in the following diode modelling example. An example of the procedure to define and extract a diode model is described in the following paragraphs.

#### 3.3.2 Equivalent circuit

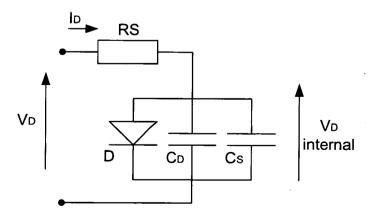

The SPICE equivalent schematic for a diode is shown in Figure 3.1. It consists of the ideal diode D representing its non-linear DC characteristic plus two voltage dependent capacitors for taking care of the space charge ( $C_S$ ) and delay effects ( $C_D$ ) as well as a series resistor RS for the high-current effects. Series inductors (bonding effects) as well as parasitic capacitors (housing effects) are neglected.

Figure 3.1 Equivalent diode circuit

#### 3.3.3 DC Characterisation

Neglecting high current effects, assuming RS=0 or  $V_D = V_{Dinternal}$ , and also neglecting recombination effects for low biasing voltage, the diode current in the forward active region is modelled as follows:

$$i_D = I_S \times \left( e^{\frac{v_D}{N \cdot v_I}} - 1 \right)$$

(3.2)

with :

$I_s$  = saturation current (leakage current, typically fA)

N =emission coefficient (Ideal diode: N=1)

$V_t$  = thermal voltage 27mV at 25°C or  $V_t$  = (k x T) / q = 8.617x10<sup>-5</sup> x (T / °C + 273.15)

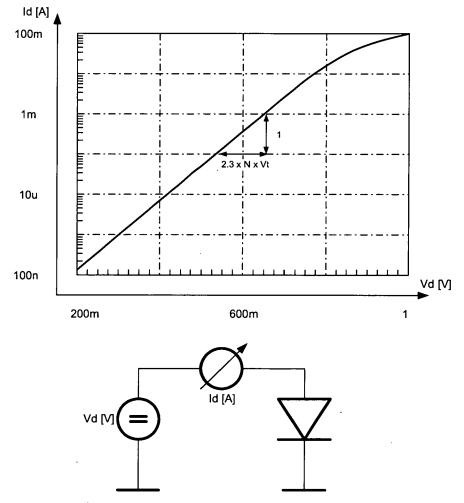

Figure 3.2 Diode DC characteristic

#### 3.3.3.1 Determination of the parameters IS and N

Provided  $V_D >> 0V$ , i.e. neglecting the term (-1) in equation 3.2, and applying a logarithmic conversion gives:

$$\log(I_D) = \log(I_S) + \frac{V_D}{N \times V_T} \times \log(e)$$

(3.3)

$$= \log(I_s) + \left(\frac{1}{2.3 \times N \times V_T}\right) \times V_D$$

(3.4)

This is an equation of the form:

$I_{s} = 10^{b}$

$$y = m \times x + b \tag{3.5}$$

In order to interpret equation 3.5 linearly, we have to substitute:

$$y = \log(I_D)$$

$$b = \log(I_S)$$

$$m = \left(\frac{1}{2.3 \times N \times V_T}\right)$$

$$x = V_D$$

(3.6)

Equation 3.6 explains how to manipulate the measured data. After the logarithmic conversion of the measured values of  $I_D$ , they are introduced with the linear values of  $V_D$  into the regression equations. Thus, the y-intersect, b, and the slope, m, of the linear regression function are obtained.

Solving for  $I_S$  and for N one is able to determine these two parameters from b and m as follows:

and

(3.7)

$$N = \frac{1}{2.3 \times m \times V_T} \tag{3.8}$$

The parameter extraction described above is valid only in that range of measured data, where the assumptions are true. This means: equations 3.7 and 3.8 are valid for  $V_D > 0$  (data above the measurement resolution (non-noisy data), typ. > 0.2V) and where  $e^{\frac{V_D}{N \times V_T}} >> 1$ . The diode current should not be dominated by recombination effects (the

weaker slope at low bias voltages) but not by high-current effects (non-ohmic effects, the knee in the half-logarithmic diode characteristic, typically above 0.7 V)

#### 3.3.3.2 Determination of parameter RS

After the parameters  $I_s$  and N are extracted, the value of RS can approximately be found from the two highest bias points of index n and index (n-1) as follows:

$$RS = \frac{V_D(n) - V_D(n-1)}{I_D(n) - I_D(n-1)}$$

(3.9)

Another more precise method to determine the ohmic part of a diode characteristic is to consider the voltage drop between the ideal diode characteristic and its shift due to the ohmic effect. This is done by first determining the maximum current from the sweep by

$$I_{RS} = Ia.m[\max\_index]$$

(3.10)

and then by calculating that voltage drop following

$V_{RS}$  = measured voltage – ideal diode voltage

or

$$V_{RS} = Va.m[\max\_index] - V_T \times N \times \ln\left(\frac{I_{RS}}{I_S}\right)$$

(3.11)

which finally gives

$$RS = \frac{V_{RS}}{I_{RS}}$$

(3.12)

Of course, the diode DC parameters  $I_s$  and N have to be determined first and are a prerequisite for good RS extraction: the ohmic effect must dominate the diode characteristics in the portion used for the extraction. Referring to Figure 3.2, the reduction in slope for high bias voltage must be clearly visible in the extraction range.

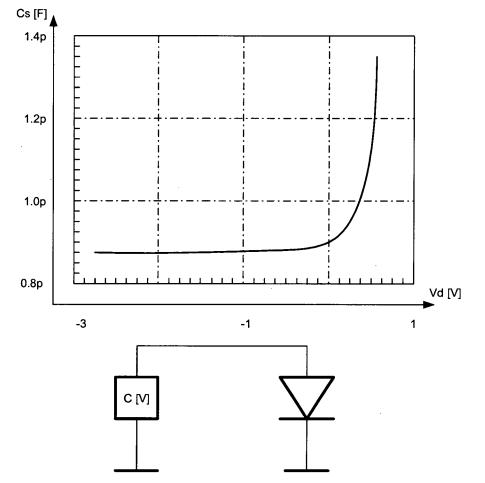

#### 3.3.4 CV Characterisation

The frequency behaviour of a diode can be modelled by a space charge capacitance (dominant at reverse bias) and a diffusion capacitance (dominant at forward bias) which models the time delay effects. The first capacitance is typically measured with a negative bias using a CV meter (capacitance versus voltage) while the latter is commonly measured using a network analyser. (Figure 3.3).

This paragraph covers the modelling of the space charge capacitor.

Extracting parameters C<sub>J0</sub>, V<sub>J</sub> and m

For  $V_D < F_C \times V_J$ :

$$C_{s} = \frac{C_{J0}}{\left(1 - \frac{V_{D}}{V_{J}}\right)^{M}}$$

(3.13)

or else :

$$C_{S} = \frac{C_{J0}}{(1 - F_{C})^{(1+M)}} \times \left[1 - F_{C} \times (1+M) + M \times \frac{V_{D}}{V_{J}}\right]$$

(3.14)

with:

$C_{J0}$ : space charge capacitance at  $V_D = 0V$

V<sub>J</sub>: built-in potential or pole voltage

M: junction exponential factor (determines the slope of the CV plot)

F<sub>C</sub>: forward capacitance switching coefficient (default 0.5)

Figure 3.3 CV measurement setup

Determination of the CV parameters:

We only use the negative bias region for parameter extraction. The logarithmic - conversion of equation 3.13 gives:

$$\log(C_s) = \log(C_{J0}) - M \times \log\left(1 - \frac{V_D}{V_J}\right)$$

(3.15)

.

This equation can be interpreted again as a linear function:

$$y = m \times x + b \tag{3.16}$$

with :

$$y = \log(C_s)$$

$$b = \log(C_{J0})$$

$$m = -M$$

$$x = \log\left(1 - \frac{V_D}{V_J}\right)$$

(3.17)

The procedure is to first logarithmically convert the measured values of  $C_S$  according to equation 3.17, along with the stimulating data of the voltage sweep  $V_D$ . Since the parameter  $V_J$  has a physical meaning, its value should be in the range of 0.2 to 1V.

Therefore 0.2V is selected as a starting value for V<sub>J</sub>. These two arrays are now introduced into the regression as yi- and. xi- values respectively. A linear model is fitted to this transformed "cloud" of stimulated and measured data and one gets the y-intersect b and the slope m for the value of V<sub>J</sub>. These two values are the best choice for the given V<sub>J</sub>. Now, this procedure is repeated with an incremented V<sub>J</sub>, to obtain another pair of  $m(V_J)$  and  $b(V_J)$  values. The regression coefficient r2 will now be different from the earlier one, depending on the value of V<sub>J</sub>, and whether the regression line fits the transformed data 'cloud' better or worse. Once the best regression coefficient is found, the iteration loop is terminated and one gets V<sub>J\_OPT</sub> as well as the corresponding  $b(V_{J_OPT})$  and  $m(V_{J_OPT})$ .

The final parameter values are then:

$$M = -m(V_{J_OPT}) \tag{3.18}$$

and

$$C_{J0} = \exp(b(V_{J_OPT}))$$

(3.19)

The parameter extraction for the space charge capacitor is valid only for stimulus voltages below  $F_C \times V_J$ , with  $F_C$ \_default = 0.5.

In practice, there is always an overlay of this capacitance with some parasitic elements, such as packaging or bond pads. If they are not known and therefore cannot be deembedded (eliminated from the measured data by using special test-structures or by calculations), the three modelling parameters may have values that have no physical meaning. This is especially true for  $V_J$  and M. Nevertheless, the fitting of the proposed method is generally very good

In order to keep the models simple and usable, and to have reasonable simulation times, models by definition suffer from some limitations:

**DC**: diodes may show recombination effects at low forward bias voltages, showing up as a lower slope on a half- logarithmic scale. In order to include this effect, the diode model is replaced by a subcircuit, consisting of a diode for the recombination effect, another one in parallel for the normal operating region and a resistance in series with both diodes.

**CV:** no parasitic capacitance is included in the diode model. A sub-circuit can easily be added to introduce a second parasitic capacitance

#### 3.4 Model types and their implementation

#### 3.4.1 Types of models

There are a number of approaches that can be taken when modelling MOS devices and the following summarises some of the options.

#### 3.4.1.1 Functional models: [1] – [5]

The approach of a functional model treats the device as a "black box" and describes the externally observed behaviour without a detailed consideration of the physical effects occurring inside the device.

#### Standard low-power device models: [1]

The standard low-power device models are adapted for power semiconductor devices by optimising their parameters. Hence, the model parameters and equations can lose their physical meaning, and a pure functional description may result. These models, however, are hardly able to simulate any high-voltage phenomena.

#### Lookup table: [5]

In lookup tables, the data resulting directly from measurements or from calculations are stored and retrieved for simulation. This method is well suited for DC characteristics, but it is much more difficult to use for dynamic effects of the device in the environment of different circuits. Therefore, the effort becomes very large to consider all the situations caused by the varying conditions in many different circuit topologies.

Empirical expressions: [2], [3], [4]

In many cases, the equations of functional models are selected from arbitrary mathematical expressions that describe the externally observed behaviour in a simplified way. When possible, the currents and voltages of the device terminals are approximated directly by straightforward functions. However, for a description of dynamic effects, it is often necessary to include additional variables into the equation set. These assumptions can be inspired by device physics, and, in some cases, they can be confirmed by theoretical derivations.

#### 3.4.1.2 Approximate solutions: [6] – [13]

The model equations of this type are based on device physics, but since exact solutions are not possible or restricted to a few special cases, appropriate mathematical representations are found to approximate the solution. These approaches are purely empirical in many cases, but it is also possible to show that some functions come close to an exact solution under certain constraints of the boundary conditions.

#### Assumed solution : [13]

The knowledge of the characteristics is obtained from theoretical considerations or numerical calculations (device simulators) and geometrical curves are then used to model the shape.

#### Substitution in an equation: [6],[12]

The substitutions transform the partial differential equation into an ordinary differential equation that can easily be solved if suitable functions are chosen.

Neglecting terms: [7], [8], [9], [10], [11]

By assuming that certain terms become unimportant under certain conditions, one can neglect them and thus simplify the equation.

#### 3.4.1.3 Transformation: [14] – [21]

Several mathematical techniques exist to solve differential equations analytically. For example, the differential equation can be transformed into an integral equation. Two methods have been used for the diffusion equation concerning power device models: Laplace transforms [14] - [20] and the application of Green's functions [21]. In

principle, these methods can lead to exact solutions. However, there are constraints for the boundary conditions and the solutions consist of infinite series. Since the series must be truncated to obtain results which are practicable, they do not require too much computational effort but the solutions are obviously an approximation.

#### 3.4.1.4 Lumped Model: [22] – [25]

In the lumped-charge approach, the charge-storing region is subdivided into several sections, and the charge of each section is assigned to a charge storage node. The charge difference between two neighbouring nodes determines the current. This leads to relatively simple equations with little computation effort. The equations are valid for all stages of operation and are not limited to special cases. However, only medium accuracy is achieved with a small number of nodes.

The lumped-charge approach looks similar to the method of finite differences (described below). It can be regarded as a simplification to the greatest possible extent with a minimal number of nodes, but in a lumped model, the average charge densities of the sections instead of the densities at the nodes are inserted into the equations

#### 3.4.1.5 Numerical Solution (TCAD approach): [26] ,[27], [32]

The most accurate solution is obtained by numerical methods, which are based on the discretisation of the considered region into a finite number of mesh points. Two methods can be distinguished.

#### Finite Differences: [27]

If the method of finite differences is used, the derivatives in the diffusion and transport equations are expressed by differences that have the form of an algebraic equation system.

#### Finite Elements: [26],[32]

Another possible numerical approach is the method of finite elements. It uses mathematical functions as approximate solutions for each of the discretised regions.

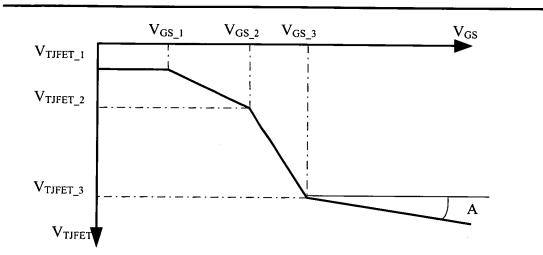

#### 3.4.2 Implementation in circuit-simulators