# Characterization and modelling of GaAs MESFETs in the design of nonlinear circuits

John C. R. Simpson

Thesis submitted for the degree of Doctor of Philosophy

Department of Electrical Engineering University of Edinburgh

September 1991

#### **Abstract**

The emergence of the MMIC as a cost effective, compact and enabling technology has increased the need for accurate CAD software. The performance of nonlinear MMICs must be evaluated during design using computer simulation, since they cannot be tuned after fabrication. Simulation relies upon accurate large-signal models for circuit components and this project involves the development of the GaAs MESFET large-signal model. In this work, the model is empirical and is derived entirely from characterizing S-parameter measurements over a range of bias levels and frequencies.

Small-signal equivalent circuits are calculated from each set of S-parameter measurements and the nonlinear model is constructed from the complete set of equivalent circuits. Frequency dispersion in the conductances of the MESFET creates differences in the device characteristics at low and high frequencies. Extra nonlinear elements have been therefore added to the nonlinear model, to account for these effects.

A series of MMIC circuits have been designed. Nonlinear measurements have been made and are compared with time domain simulations using the nonlinear model. Results indicate that this modelling approach is more accurate than one based on DC measurements, which does not account for the effects of frequency dispersion.

## Acknowledgements

I would like to thank my supervisors, Dr Brian Flynn and Dr Angus McLachlan, for their guidance and encouragement over the period that this work was carried out. They have made many helpful suggestions during our discussions and have been most generous in providing equipment for this work.

The software used in this project was supplied by Adam Jastrzebski from the University of Kent at Canterbury. He is is a leading figure in this area of research and, although very busy developing a new range of software, dealt with my frequent telephone calls and visits. I am very grateful to him for giving up so much of his time.

Funding for this work was supplied by SERC and a CASE award was made available by Thorn-EMI. I would like to thank my industrial supervisors, Mr. P. Jones and Mr. J. Nicholas, for organizing my trips to Thorn-EMI Central Research Laboratories and for allowing me to use the equipment. From Thorn-EMI, I would also like to thank D. Wenn for bonding up active devices and C. Hobbs for her help in developing TRL calibration. Accurate measured data was made available by GEC Plessey Research (Caswell) Ltd., without which the quality of work would be reduced.

I would also like to thank Physical Science Support, from Edinburgh University, for their help implementing NAG routines, and to A. Ruthven for bonding up devices and the Computing Officers (especially D. Stewart) for sorting out many software problems. Finally, I would like to thank K. Coxhill, G. Flint, P. Tatham, I. Binnie and my family, who have all contributed greatly to this work in their own way.

# **List of Symbols**

a<sub>ii</sub> Chebyshev polynomial coefficient

b<sub>ij</sub> Standard polynomial coefficient

C<sub>dc</sub> Dipole capacitance

C<sub>ds</sub> Drain-source capacitance

$C_{dg}$  Depletion region drain-gate capacitance

C<sub>gs</sub> Depletion region gate-source capacitance

C<sub>o</sub> Linear capacitance in definition of nonlinear capacitance

Copen Capacitance of open circuit standard

C<sub>i</sub> Capacitance in region i of channel

$C_x$  Parallel capacitance for  $R_x$

E Total error in optimizing function

f Frequency

g<sub>m</sub> Transconductance

g<sub>o</sub> Output conductance

$I_{ch}$  Current flowing through channel of MESFET

I<sub>ds</sub> Channel current

$I_{dss}$  Channel current at  $V_{gs}$ =0.0V

I<sub>subs</sub> Current flowing through substrate of MESFET

l Length of transmission line

L Degree of fit in V<sub>ds</sub>

L<sub>d</sub> Drain inductance

L<sub>g</sub> Gate inductance

L<sub>s</sub> Source inductance

L<sub>short</sub> Inductance of short circuit standard

K Degree of fit in  $V_{gs}$

K<sub>eff</sub> Effective permittivity

P<sub>opt</sub> Optimum power point in load-pull curve

| $Q_{dg}$   | Drain-gate charge                         |

|------------|-------------------------------------------|

| $Q_{gs}$   | Gate-source charge                        |

| $R_d$      | Drain resistance                          |

| $R_{dc}$   | Resistance at DC                          |

| $R_{ds}$   | Output Resistance                         |

| $R_{ds'}$  | Output resitance calculated from $I_{ds}$ |

| $R_{g}$    | Gate resistance                           |

| $R_i$      | Intrinsic resistance                      |

| $R_{rf}$   | Resistance at RF                          |

| $R_s$      | Source resistance                         |

| $R_x$      | Nonlinear output dispersive resistor      |

| S          | Normalized sensitivity                    |

| $S_{ij}$   | 2-port S-parameter                        |

| $T_i$      | i'th order Chebyshev polynomial           |

| τ          | Time delay                                |

| $V_{gs}$   | External gate-source voltage              |

| $V_{gs'}$  | Internal gate source voltage              |

| $V_{dg}$   | External drain-gate voltage               |

| $V_{d'g}$  | Internal drain-gate voltage               |

| $V_{ds}$   | External drain-source voltage             |

| $V_{d's'}$ | Internal drain-source voltage             |

|            |                                           |

# **Table of Contents**

| 1. Introduction                                          |            |

|----------------------------------------------------------|------------|

| 1.1 Background                                           | 1          |

| 1.2 The GaAs MESFET - Structure and Operation            | 5          |

| 1.3 Modelling MESFETs for CAD                            | 7          |

| 1.4 The MESFET Equivalent Circuit                        | 9          |

| 1.5 S-parameters to Characterize the MESFET              | 11         |

| 1.6 Outline of Project                                   | 14         |

|                                                          |            |

| 2. Large-signal Models                                   | 16         |

| 2.1 Introduction                                         | 16         |

| 2.2 Expanding the Linear Model to include Nonlinearities | 17         |

| 2.3 Different Methods of Nonlinear Simulation            | 19         |

| 2.4 Review of Large-signal Modelling Techniques          | 21         |

| 2.4.1 Categorization                                     | 21         |

| 2.4.2 The Empirical Model                                | <b>2</b> 3 |

| 2.4.3 The Semi-empirical Model                           | 31         |

| 2.4.3.1 Models for the Drain Current Ids                 | 32         |

| 2.4.3.2 Models for Cgs, Cdg, Ri and Tau                  | 40         |

| 2.4.4 The Analytical Model                               | 43         |

| 2.4.5 The Numerical Model                                | 48         |

| 2.5 Frequency Dispersion in the MESFET                   | 48         |

| 2.6 Proposed Large-signal Model                          | 50         |

| 2.7 The MESFET Model Topology                            | 53         |

| . Measurement Calibration                                     | 56 |

|---------------------------------------------------------------|----|

| 3.1 Introduction                                              | 56 |

| 3.2 Calibration Techniques                                    | 57 |

| 3.2.1 Standard Two-port SOLT Calibration                      | 58 |

| 3.2.2 On-chip SOLT Calibration                                | 60 |

| 3.2.3 TRL Calibration                                         | 61 |

| 3.2.4 Wafer-probed Measurements                               | 62 |

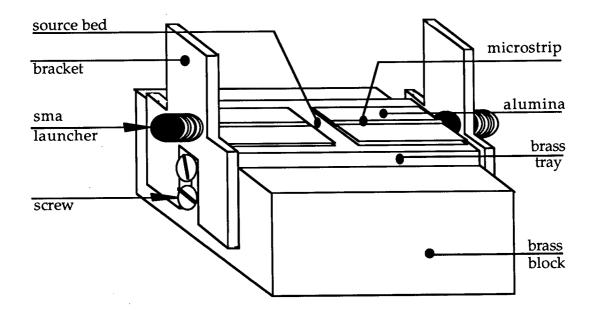

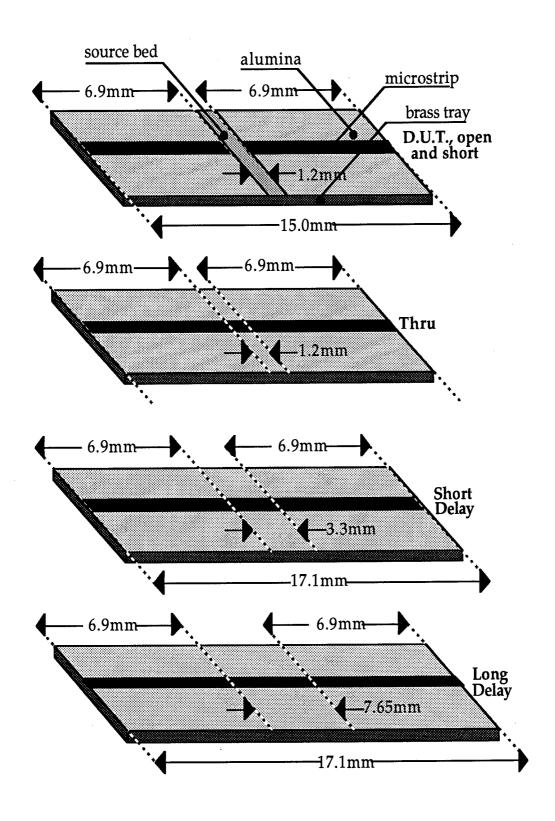

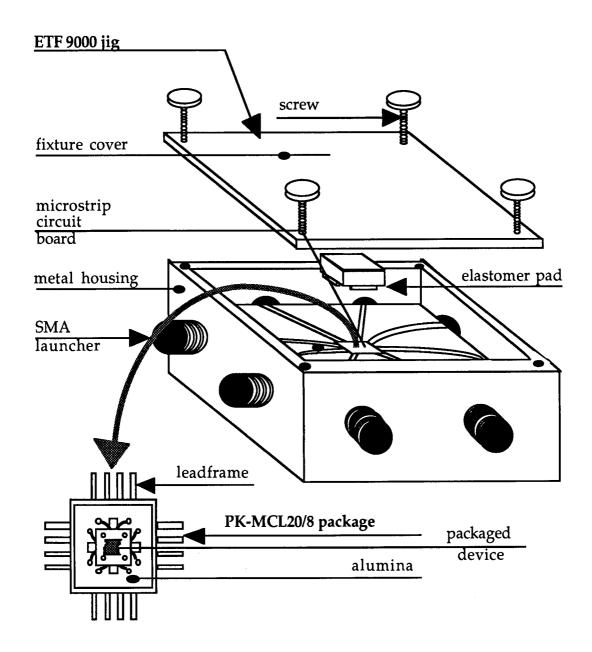

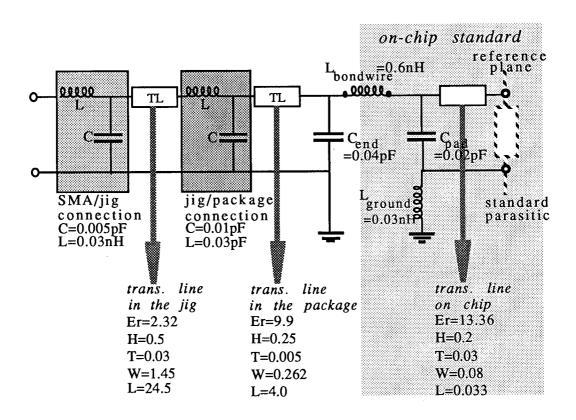

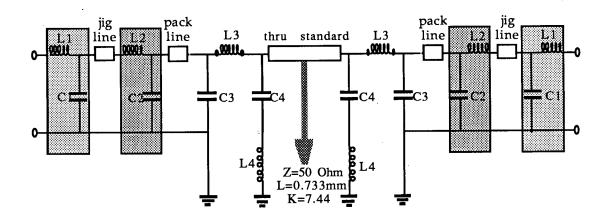

| 3.3 TRL with the Thorn-EMI Fixture                            | 63 |

| 3.3.1 Description                                             | 63 |

| 3.3.2 Calibration using 8510NA TRL Software                   | 65 |

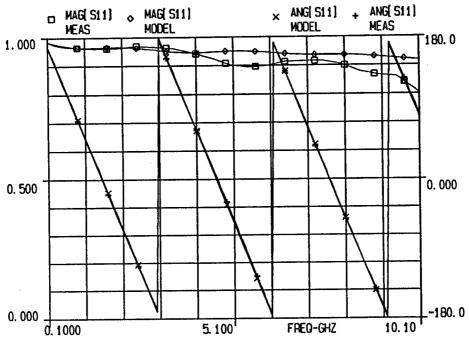

| 3.3.3 De-embedding using an Equivalent Circuit                | 66 |

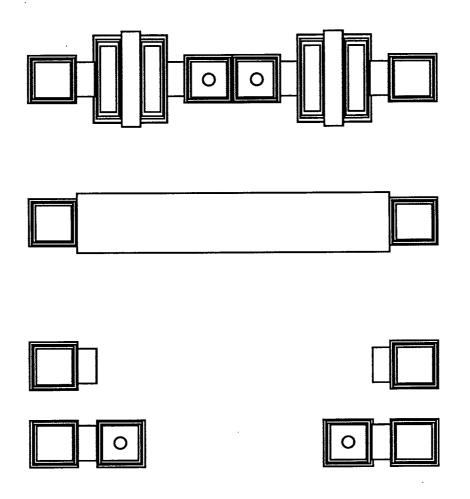

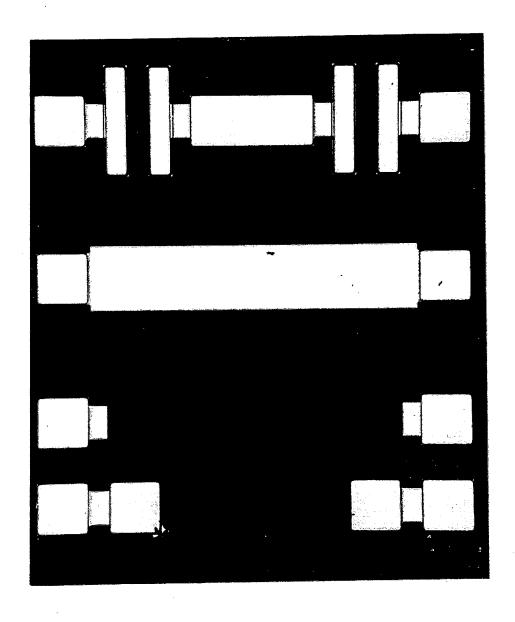

| 3.4 On-wafer SOLT Calibration with the Tektronix Jig ETF-9000 | 66 |

| 3.4.1 Introduction                                            | 66 |

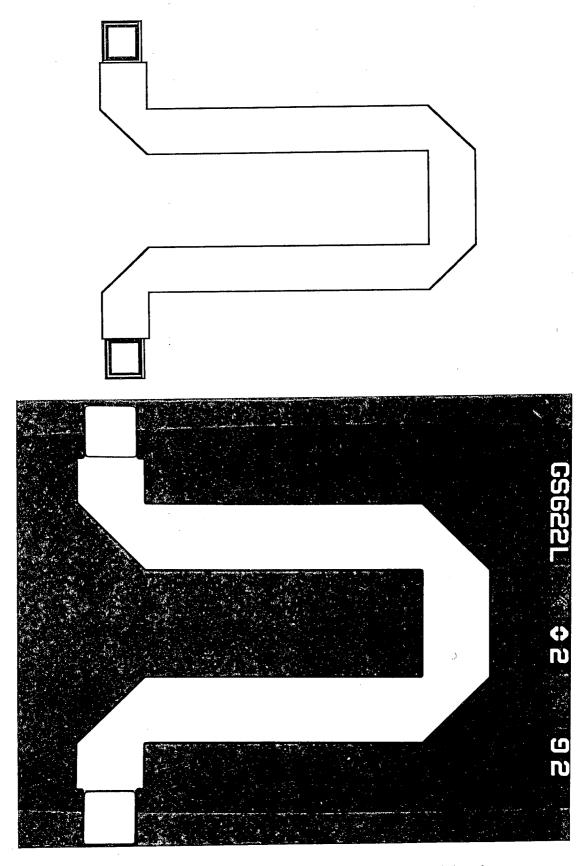

| 3.4.2 Design of On-chip MMIC Calibration Standards            | 72 |

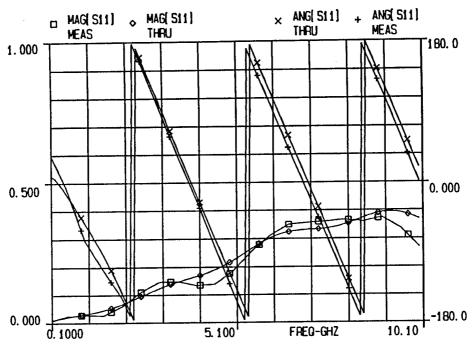

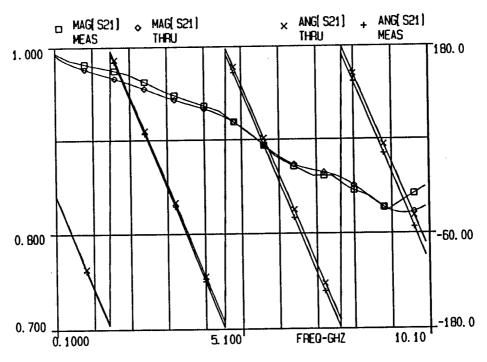

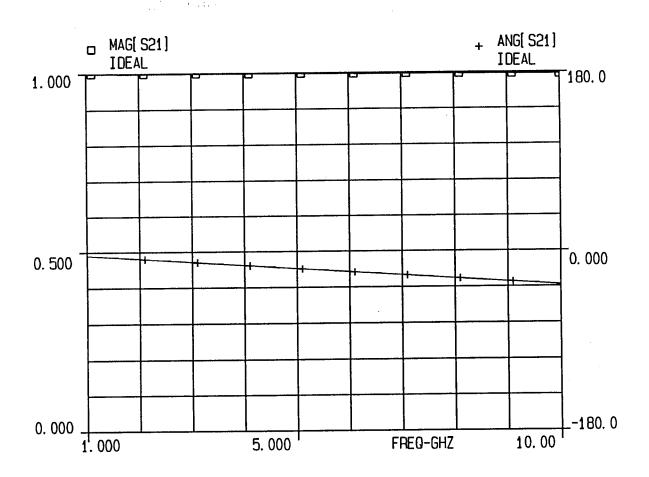

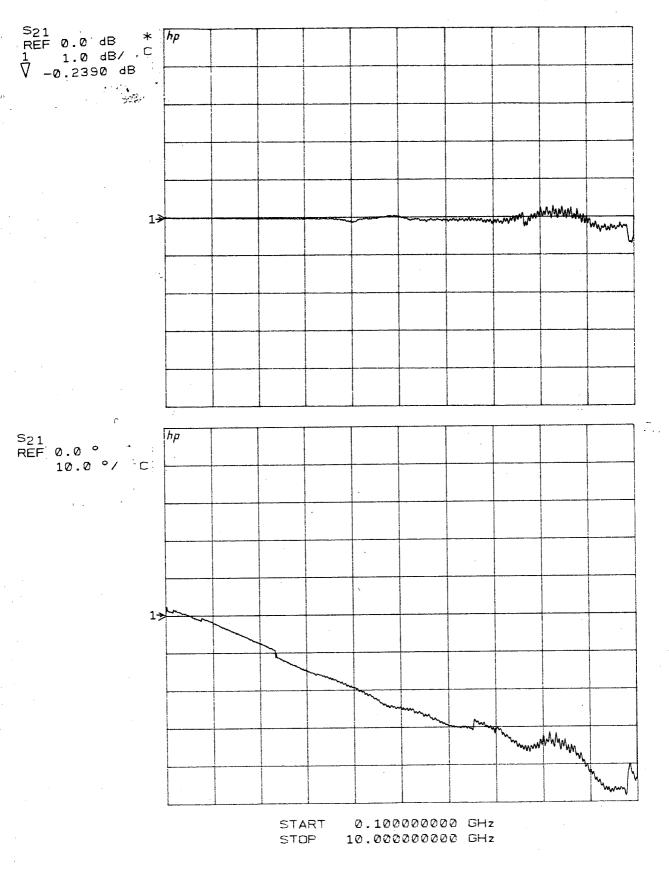

| 3.4.3 Assessment of Calibration Standards                     | 76 |

| 3.4.4 Calibration of the 8510VNA for On-chip Measurement      | 80 |

| 3.4.5 Verification and Results                                | 86 |

| . Deriving Circuit Equations                                  | 90 |

| 4.1 Introduction                                              | 90 |

| 4.2 Small-signal Measurements                                 | 91 |

| 4.3 Small-signal Simulator                                    | 93 |

| 4.3.1 Introduction                                            | 93 |

| 4.3.2 Principles of Optimization                              | 95 |

| 4.3.3 The Error Term                                          | 96 |

| 4.3.4 Using the Optimizer for Parameter Extraction            | 97 |

| 4.4 Parameter Extraction for Single Bias Measurements         | 99 |

| 4.4.1 Introduction                                     | 99  |

|--------------------------------------------------------|-----|

| 4.4.2 DC Characterization                              | 100 |

| 4.4.3 Zero Channel Bias Measurements                   | 103 |

| 4.4.4 Low Frequency S-parameter Measurements           | 105 |

| 4.5 Parameter Extraction over Multiple Bias Points     | 106 |

| 4.5.1 Introduction                                     | 106 |

| 4.5.2 Parameter Extraction                             | 108 |

| 4.5.3 Sensitivity Analysis Reveals Non-linear Elements | 110 |

| 4.5.4 Finding the Values of Nonlinear Elements         | 111 |

| 4.5.5 Local Minima                                     | 111 |

| 4.5.6 Relation of Circuit Elements to S-parameters     | 112 |

| 4.6 Bias Dependence of Nonlinear Elements              | 113 |

| 4.6.1 Defining Nonlinear Behaviour                     | 113 |

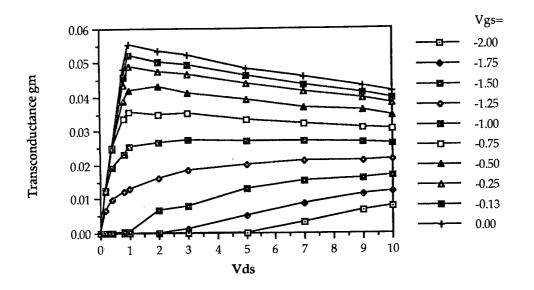

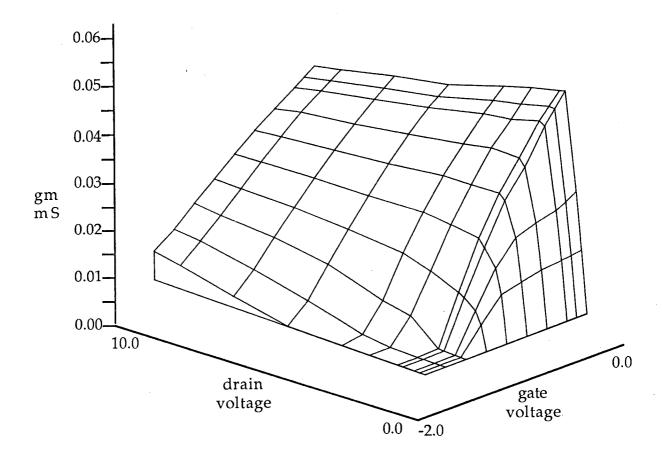

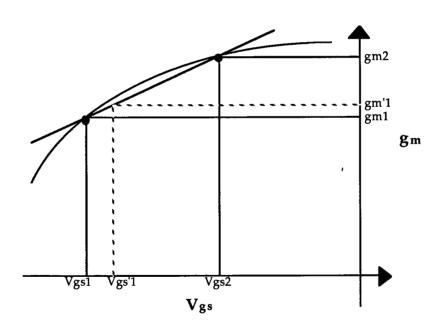

| 4.6.2 The transconductance gm                          | 114 |

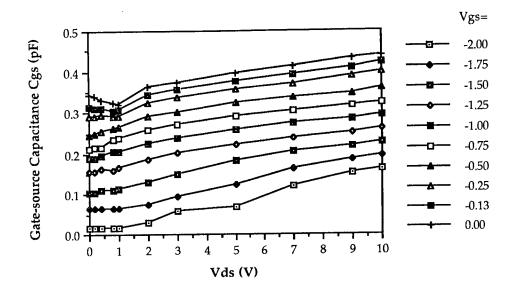

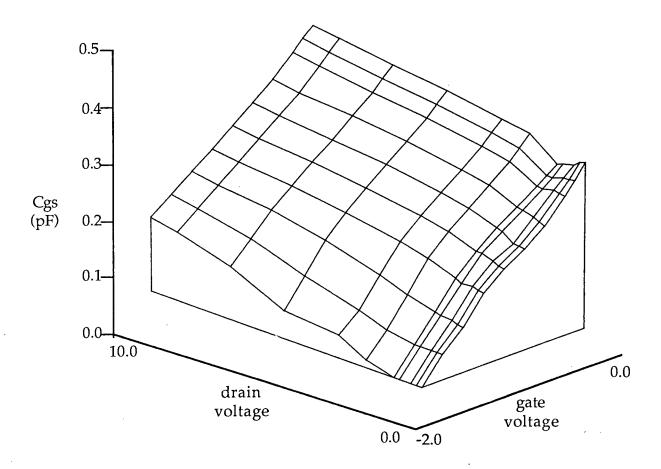

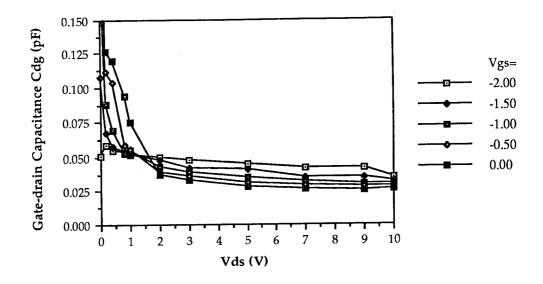

| 4.6.3 The Capacitances Cgs and Cdg                     | 118 |

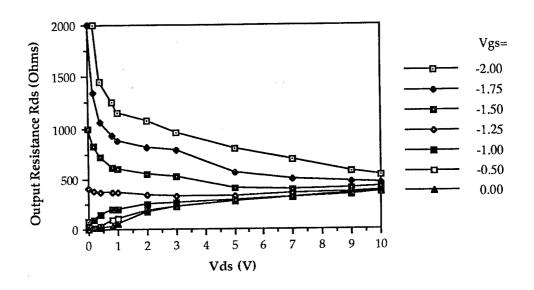

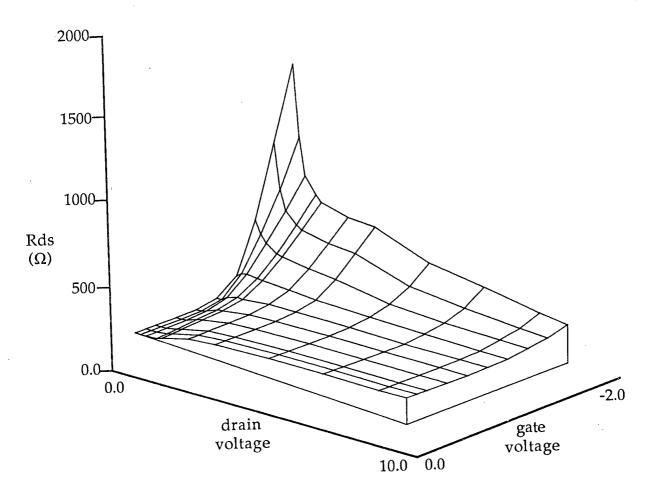

| 4.6.4 The Output Resistance Rds                        | 112 |

| 4.6.5 The Transconductance Delay $\tau$                | 124 |

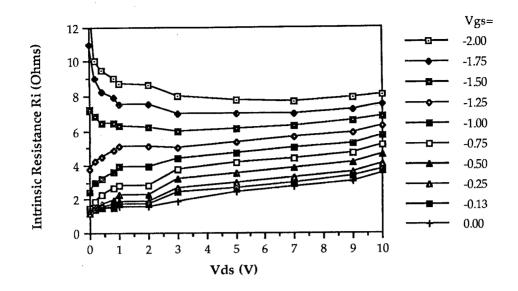

| 4.6.6 The Intrinsic Resistance                         | 126 |

| 4.7 Conclusions                                        | 126 |

|                                                        |     |

| 5. Nonlinear GaAs MESFET Model                         | 129 |

| 5.1 Introduction                                       | 129 |

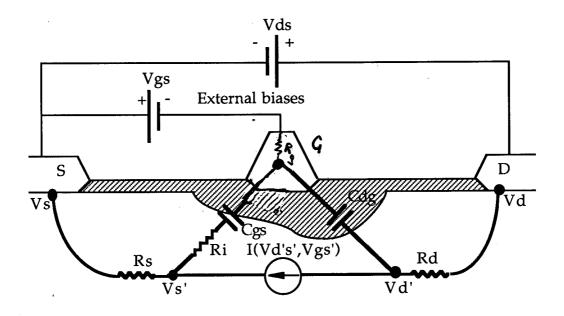

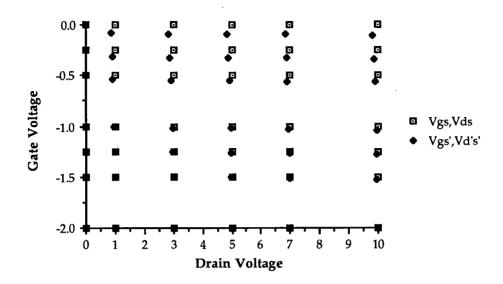

| 5.2 Converting External to Internal Voltages           | 129 |

| 5.3 The Nonlinear Current Source Ids                   | 133 |

| 5.3.1 Introduction                                     | 133 |

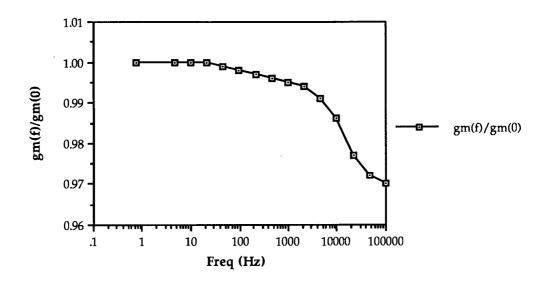

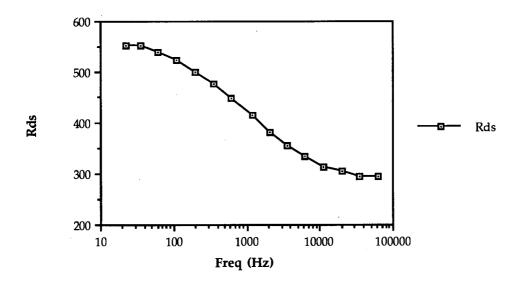

| 5.3.2 Frequency Dispersion of gm and gd                | 134 |

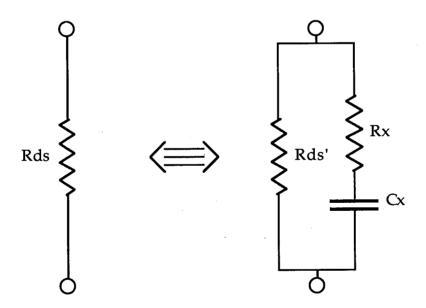

| 5.3.3 Modelling the Output Conductance Nonlinearity    | 135 |

|                        | 5.3.4 Proposed Method of Current Derivation                  | 139 |  |

|------------------------|--------------------------------------------------------------|-----|--|

|                        | 5.4 Curve Fitting                                            | 141 |  |

|                        | 5.4.1 Introduction                                           | 141 |  |

|                        | 5.4.2 Chebyshev Polynomials                                  | 148 |  |

|                        | 5.4.3 Integrating and Differentiating Chebyshev Polynomials  | 150 |  |

|                        | 5.4.4 Surface Fitting Techniques                             | 153 |  |

|                        | 5.5 Fitting Nonlinear Elements to Chebyshev Polynomials      | 155 |  |

|                        | 5.5.1 Introduction                                           | 155 |  |

|                        | 5.5.2 The Current Ids                                        | 157 |  |

|                        | 5.5.3 The Gate-source Capacitance Cgs                        | 166 |  |

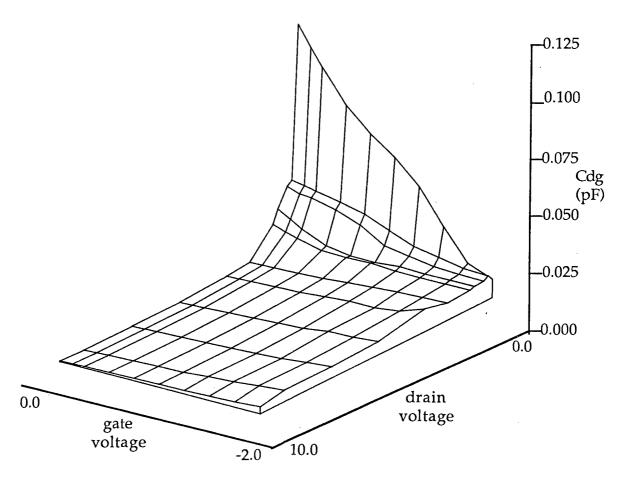

|                        | 5.5.4 The Drain Capacitance Cdg                              | 170 |  |

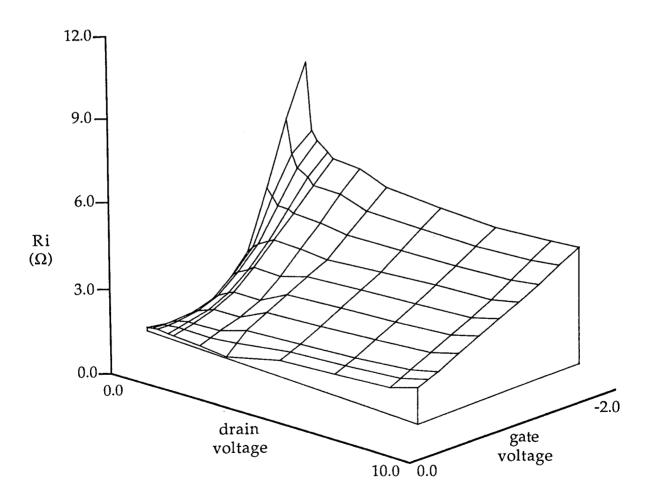

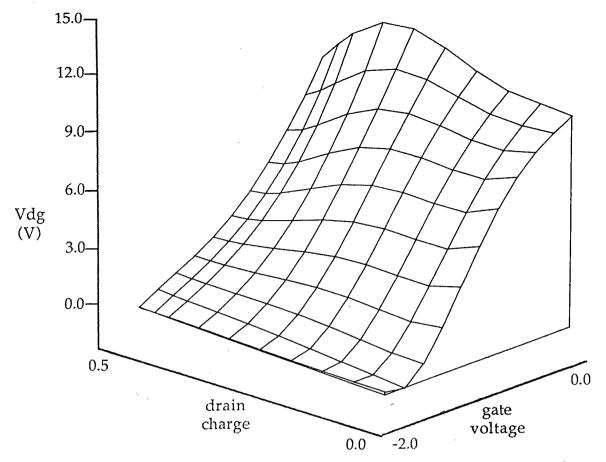

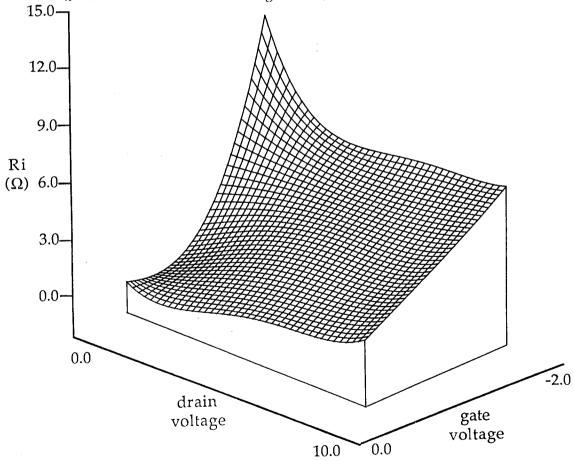

|                        | 5.5.5 The Intrinsic Resistance Ri                            | 173 |  |

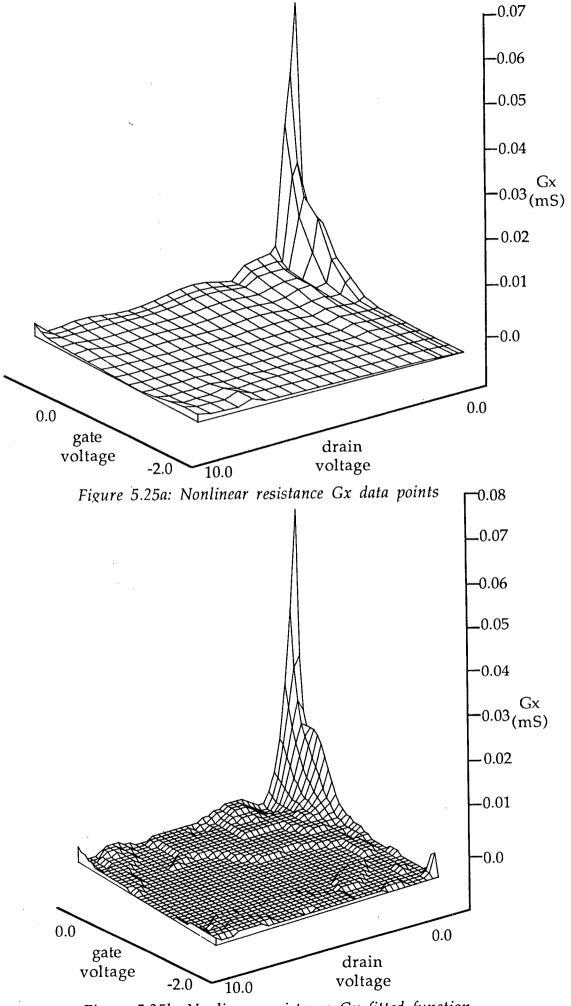

|                        | 5.5.6 The AC Output Resistor Rx                              | 176 |  |

|                        | 5.6 Conclusions                                              | 177 |  |

|                        |                                                              |     |  |

|                        |                                                              |     |  |

| 6. Device Measurements |                                                              |     |  |

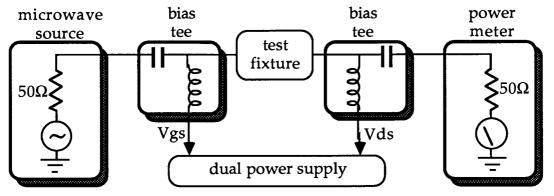

|                        | 6.1 Introduction                                             | 180 |  |

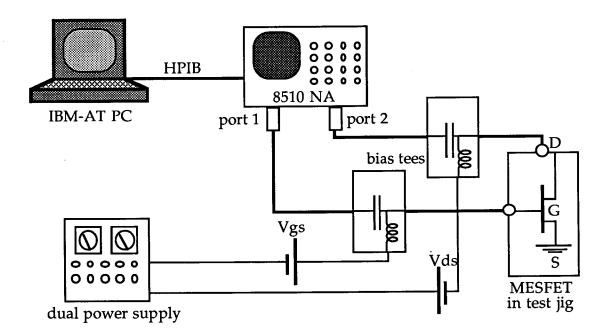

|                        | 6.2 S-Parameter Measurements on Test FETs                    | 182 |  |

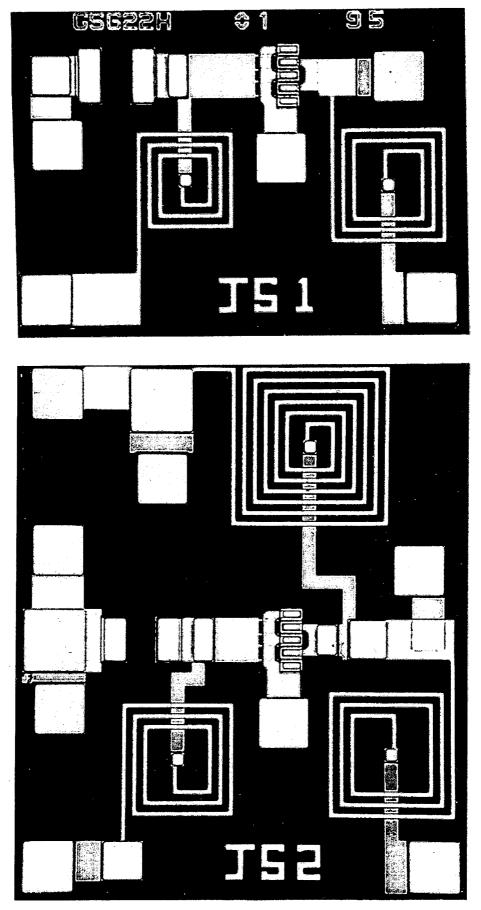

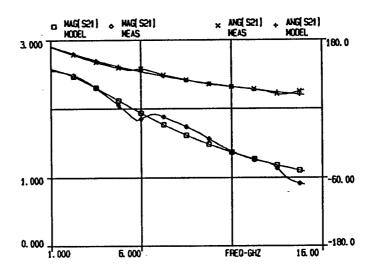

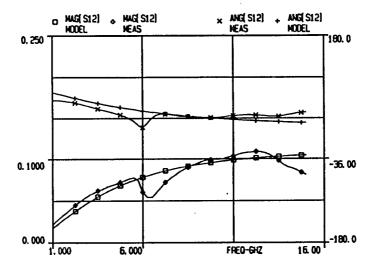

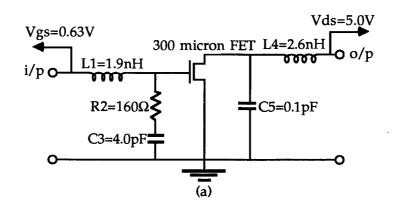

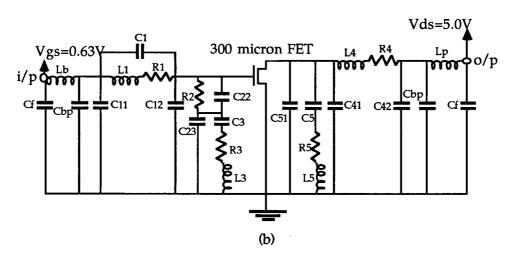

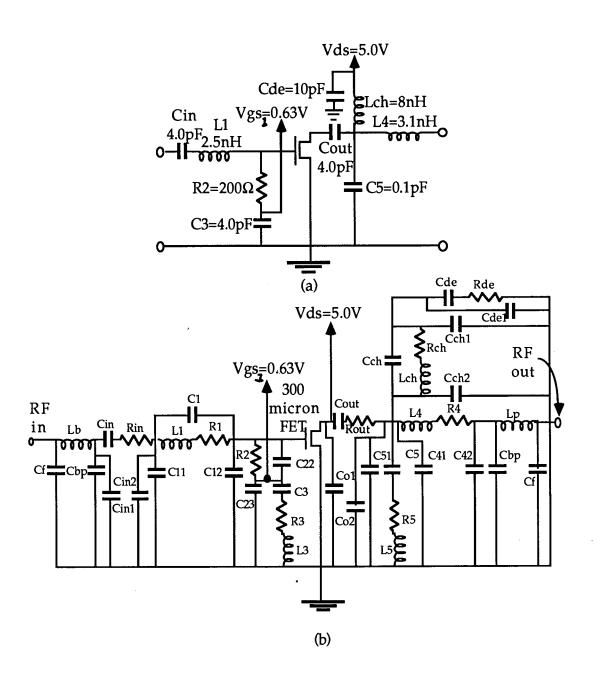

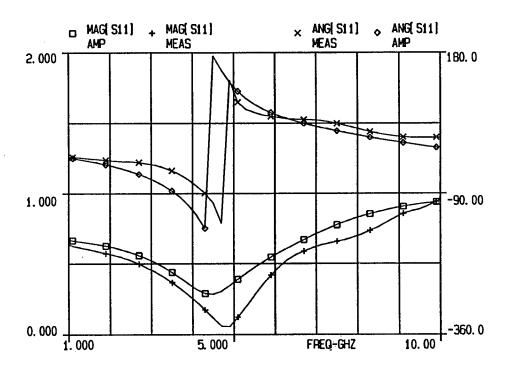

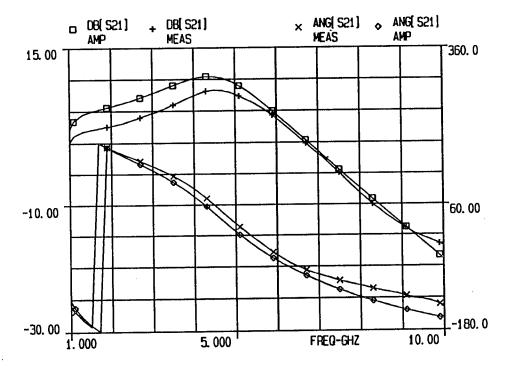

|                        | 6.3 Externally Biased Single-stage Amplifier JS1             | 191 |  |

|                        | 6.3.1 Design, Layout and Small-signal Characteristics        | 191 |  |

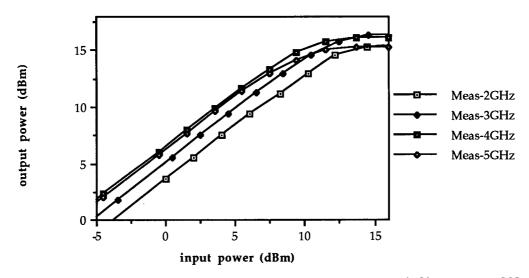

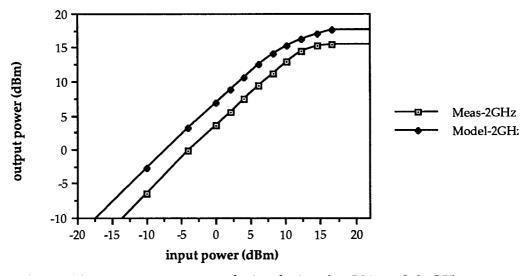

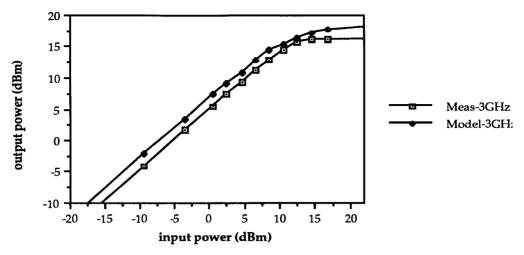

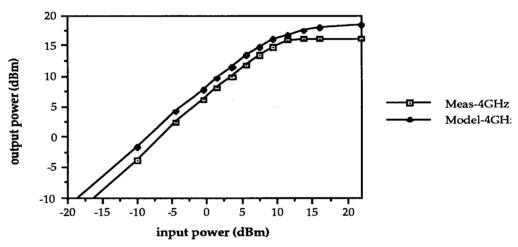

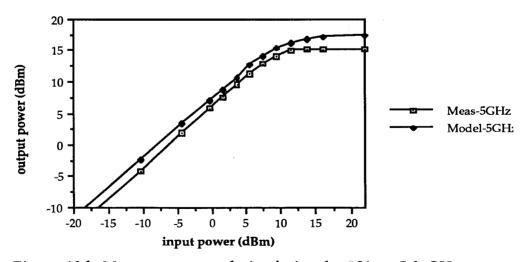

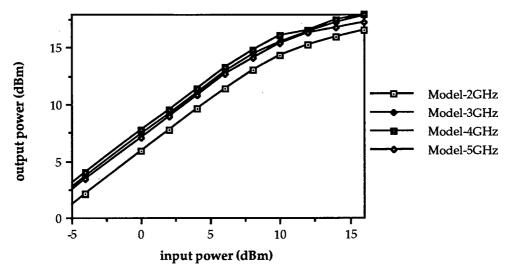

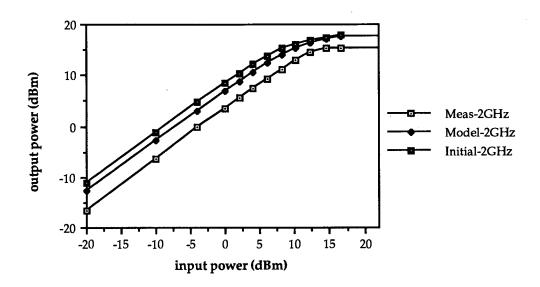

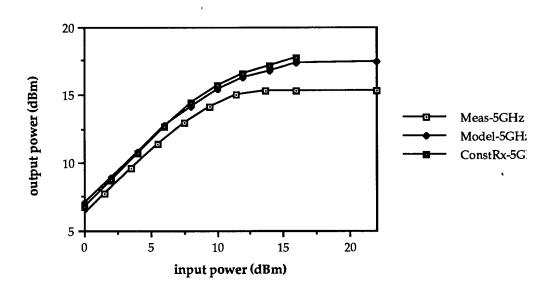

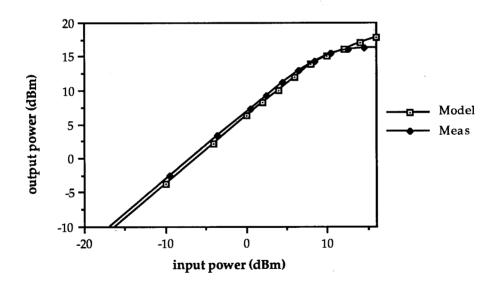

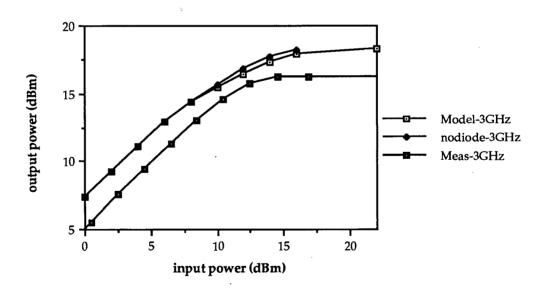

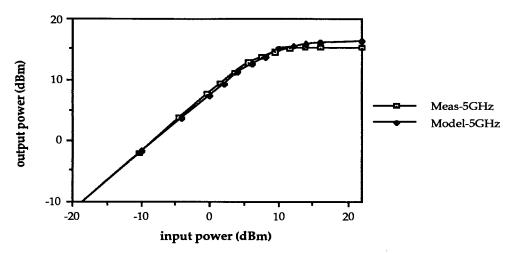

|                        | 6.3.2 Power Saturation Curves for Single-stage Amplifier JS1 | 197 |  |

|                        | 6.4 Single-stage Amplifier with 'On-chip' Bias Circuit JS2   | 208 |  |

|                        | 6.4.1 Design, Layout and Small-signal Characteristics        | 208 |  |

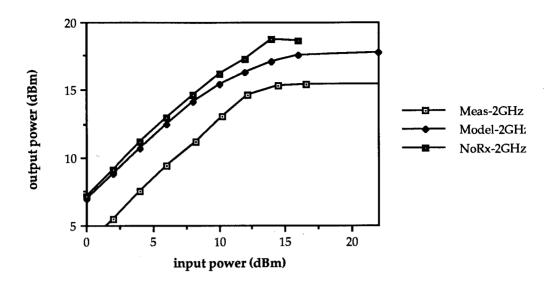

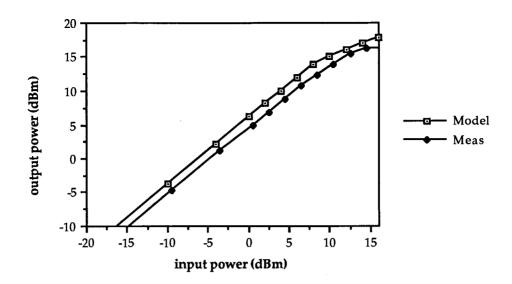

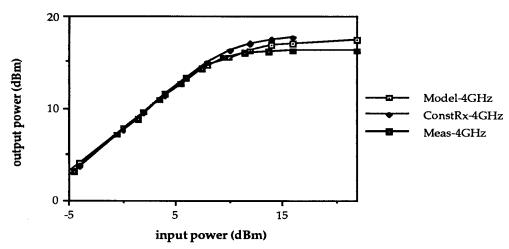

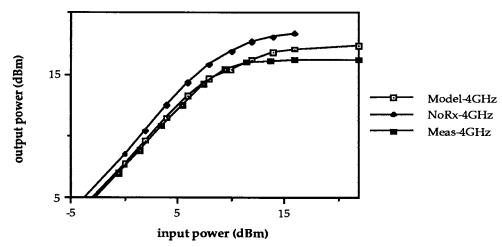

|                        | 6.4.2 Power Saturation Curves for Single-stage Amplifier JS2 | 208 |  |

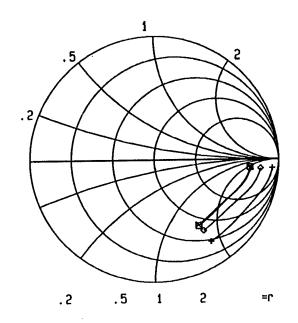

|                        | 6.5 Load-Pull Measurements                                   | 217 |  |

|                        | 6.5.1 Introduction                                           | 217 |  |

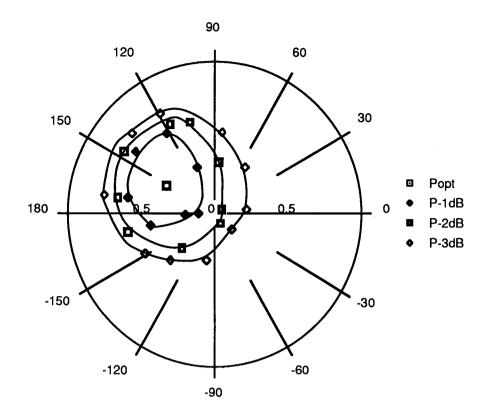

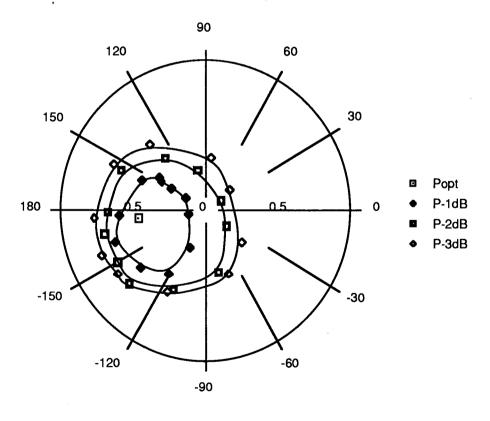

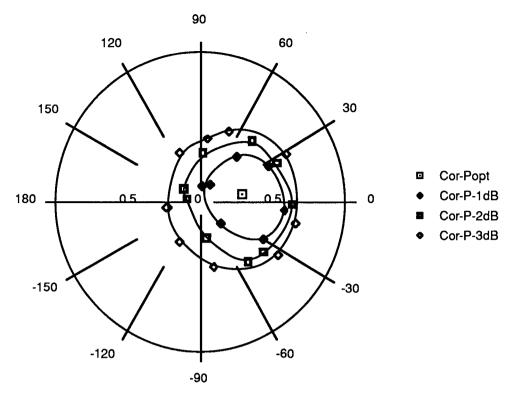

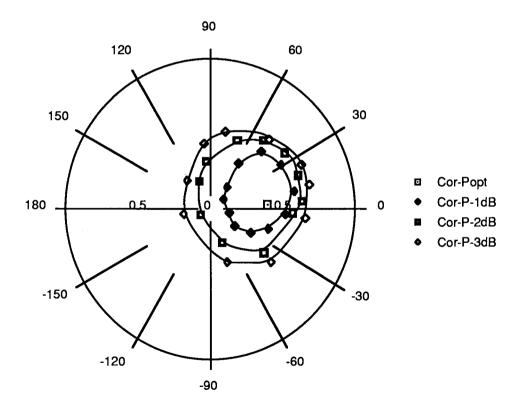

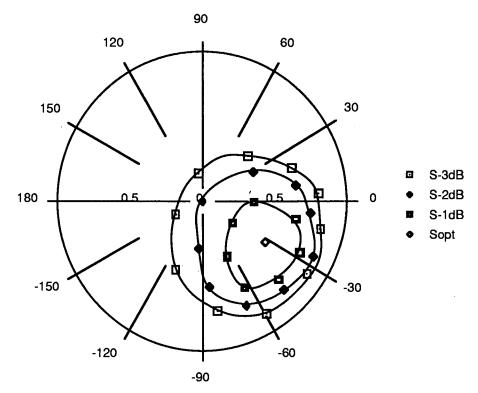

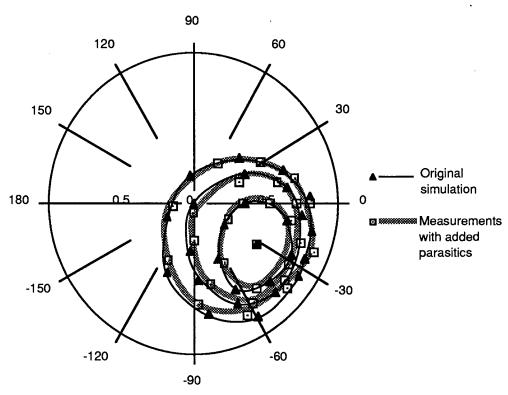

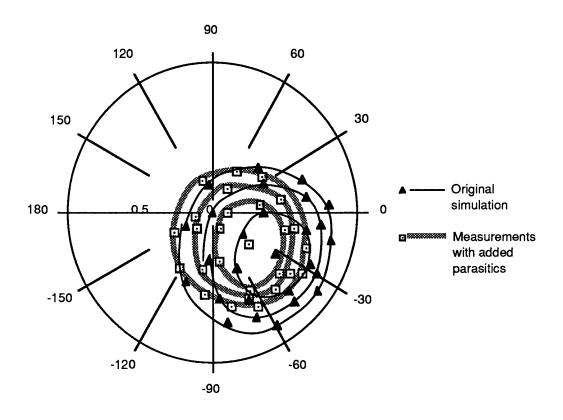

|                        | (FOT) 1 (10)                                                 | 219 |  |

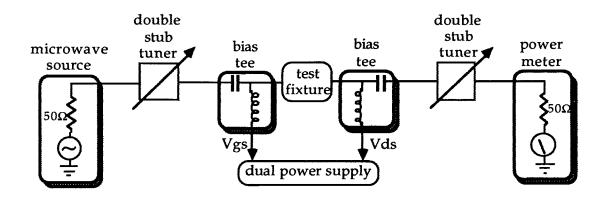

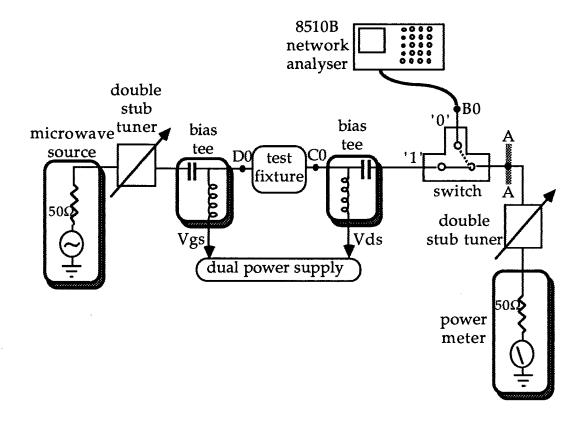

|                        | 6.5.2 Experimental Setup                                     | 219 |  |

| 6.5.3 Load-Pull Results   | 222 |

|---------------------------|-----|

| 6.4 Conclusions           | 228 |

|                           |     |

|                           |     |

| 7. Conclusions            | 230 |

| 7.1 Summary               | 230 |

| 7.2 Discussion of Results | 232 |

| 7.3 Future Work           | 234 |

| 7.4 Conclusions           | 236 |

|                           |     |

| References                | 238 |

|                           |     |

| Appendix A                | 256 |

| Appendix B                | 260 |

| Appendix C                |     |

| Appendix D                | 271 |

#### **CHAPTER ONE - Introduction**

## 1.1 Background

Microwave technology has developed continuously since its inception around 50 years ago. One of the most significant of these developments has been the emergence of solid state microwave components. Gunn and IMPATT diodes, which first appeared during the 1960's, resulted from the progress in semiconductor manufacturing and the production of new semiconductor materials.

Around the same time, low loss dielectric materials like Alumina and PTFE were developed, making possible the manufacture of compact microwave transmission media, such as microstrip and stripline. Solid state components mounted onto dielectric substrates formed hybrid microwave integrated circuits (HMICs). These were used to build lownoise amplifiers, power amplifiers, oscillators, mixers and phase shifters, all of which were considerably smaller than existing waveguide technology.

Solid state active devices which gave useful gain at microwave frequencies were slower to develop and it was not really until the gallium arsenide metal semiconductor field effect transistor (GaAs MESFET) was developed that useful gain could be obtained at more than a few GHz. The first FET was proposed in 1952 by Shockley [1] and was called the junction FET (JFET), but it was not a practical proposition until the early 1960's, due to problems associated with surface states. The silicon JFET was the first practicable field effect transistor to be produced and appeared on the market around the same time as the h.f. and u.h.f. bipolar transistor. The silicon metal oxide semiconductor FET (MOSFET) resulted from the developments in semiconductor manufacturing technology and the need for devices with lower energy consumption in highly integrated circuits.

As semiconductor technology matured in the early 1970s and progress was made with research on III-V compounds, gallium arsenide Schottky barrier FETs first appeared. These outperformed the existing silicon bipolar technology at higher frequencies with better noise figures. This new device was known as the metal semiconductor FET (MESFET). Compared with the well-established bipolar silicon technology, diodes and the travelling wave tube, the benefits of the MESFET were slow to reach the attention of the microwave market. This was partially due to material problems which prevented stable devices from being produced. Laboratories unfamiliar with GaAs technology also attempted, with mixed success, to build one-micron gate length devices which were at the limits of the existing photolithography.

Research work persisted, led by Hewlett-Packard [2], IBM and Plessey, and by 1976 the FET market had developed to a point where it could no longer be ignored. One of the first commercial MESFETs to become available was the NEC 244, launched in 1975 and offering a gain of 9.5dB at 10.0GHz. By 1987 monolithic amplifiers were being reported with gains in excess of 24.0dB across a bandwidth of 0.5-6.0 GHz [3]. GaAs MESFETs have now developed to the point that they are produced in large volumes for consumer products, such as satellite T.V. low-noise downconverters.

The first power FET was made by Fujitsu in the mid-seventies [4] and demonstrated 2.7W at 6GHz with a 6.0dB gain. By 1987 power FETs were reported with a gain of 4.3dB and an output power of 1.1W at 20.0GHz [5]. Research into the GaAs MESFET is still in progress and some laboratory results indicate its usefulness at 60GHz and beyond.

The concept of the monolithic microwave integrated circuit (MMIC) was first conceived in the mid-1960's and was seen as an obvious

development of the HMIC. The MMIC required the integration of active and passive components on the same substrate, offering reduced size and cost over HMICs. Attempts were made at building MMICs using silicon and silicon-on-sapphire bases but the problems of silicon's high resistivity, substrate losses and the silicon-sapphire interface restricted the effectiveness of these approaches.

By the early eighties, improvements in GaAs crystal growth techniques had finally made the commercialization of MMICs possible. The earliest successful MMICs [6,7] were narrowband amplifiers but applications quickly grew to cover almost all functions in microwave systems. There were a number of advantages of using the new MMIC technology in preference to the existing discrete microwave circuitry. MMICs were of greatly reduced size and weight and consumed less power. Once the design methods had been firmly established, unit costs could fall dramatically, allowing for the mass-production of many different types of circuit. Because all parts of a circuit could be integrated on the same substrate, the MMIC could give very reproducible performance as interconnect parasitics were reduced and a more broadband performance than HMICs was obtainable. By 1988, many MMIC designs had been published, including a K-band multistage power amplifier [8] with an output power of 1.33 W and a gain of 26.2 dB at 19.0 GHz.

The MMIC can be used in a wide variety of microwave circuit applications, replacing HMIC technology and acting as an enabling technology for designs which on HMICs would be too expensive, bulky and impractical to implement. An example of the enabling power of MMICs is the phased array radar. MMICs have so far been used to design small-signal, broadband, distributed and power amplifiers, although linear designs have been more successful.

MMICs have also been used to design switching and control circuitry. Tajima *et al* [9] have developed a voltage controlled attenuator with an operating frequency range of 2.0-18.0 GHz. MMIC switches have been designed for use in antenna transmit-receive modules, phase modulators and communications systems. Active and passive phase shifters have also been designed on MMIC [10]. The design of MMIC oscillators has been limited to date by the poor models for active devices in nonlinear CAD software which are available, whereas mixers have been successfully implemented [11,12].

Multifunction MMICs have also been produced, allowing for the integration of amplifiers, mixers, switches and phase shifters on the same chip. For example, a number of single chip Direct Broadcast Satellite (DBS) receivers have been realised on MMIC [13,14]. MMICs have also been designed for instrumentation, marine radars and land-mobile telephones [15].

Another trend over the past decade has been the increasing importance placed on CAD for microwave circuit design. Traditionally, HMICs were built using simple design procedures and were optimized by exercising the 'black-art' of tweaking. Post-fabrication 'tuning' was used, largely because the parasitics were not known or modelled effectively. Sometimes the circuits were designed with assistance from CAD programmes and as they could be tuned after fabrication, repeatable device models were often inaccurate and incomplete. Unlike the HMICs however, the MMIC could not be tuned after fabrication and require CAD with accurate models so that MMICs could be designed on a 'right-first-time' basis. Modelling of MMICs is made more complex because of their reduced physical size which creates field leakage and increases the coupling effects between different parts of the circuit [15].

A number of CAD programs became available during the early eighties [16,17]. Many were originally written for HMICs and were modified since the MMIC designs using older CAD systems tended to show poor yields. The modifications were made to satisfy the need for improved models of passive and especially active circuit components. Many programmes modelled passive components more successfully and contained accurate linear models for active devices. The major challenge lay in improving the nonlinear models needed for the CAD of power amplifier, mixer and oscillator designs.

# 1.2 The GaAs MESFET - Structure and Operation

Gallium arsenide is a group III-V compound offering several advantages over silicon for MESFET fabrication. High quality GaAs substrates offer better insulating properties than silicon, leading to lower parasitics and a resistivity in excess of  $10^7\Omega$ -cm. It also has a much higher electron mobility of 8900 cm²/V/s (at 300 K) compared with 1500 cm²/V/s for N-type silicon [18]. The saturation velocity for doped GaAs ( $10^7$  cm/s) is similar to silicon but occurs at a lower field threshold (3500 V/cm compared with 10000 V/cm for Si). This gives rise to steeper current saturation characteristics for the GaAs MESFET than for the silicon JFET. Current-gain bandwidths are about two to three times higher and the maximum frequency of oscillation three times higher in GaAs as opposed to silicon.

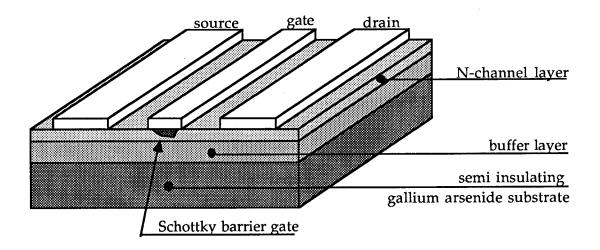

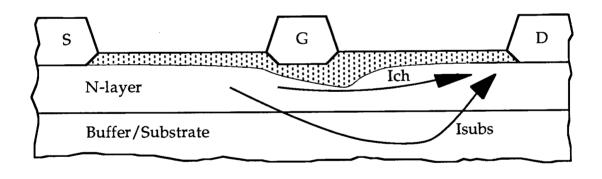

The basic structure for the gallium arsenide MESFET is given in Figure 1.1. Basically, it consists of a semiconductor resistor, where the cross section of the channel is modulated by a Schottky barrier gate. The source and drain are ohmic contacts to the N-channel layer which is doped in the range of 10<sup>17</sup>cm<sup>-3</sup> to 10<sup>19</sup>cm<sup>-3</sup> [19] and the thickness of the N-channel layer

Figure 1.1: Structure of the GaAs MESFET

is around 0.1µm. As the device is used to switch or amplify signals in the microwave frequency range, the gate length has to be short.

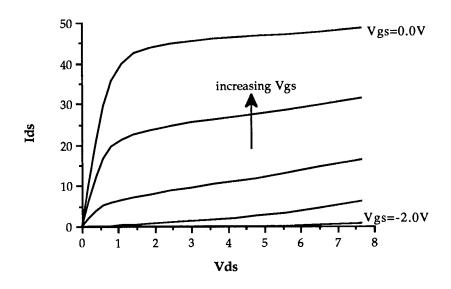

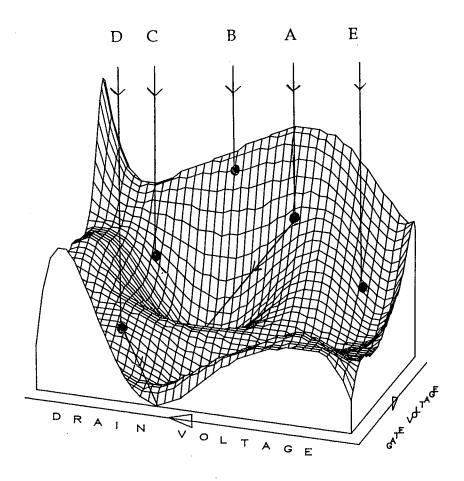

When a voltage Vds is applied between the source and drain such that the drain terminal is more positive than the source, an electric field is created, causing electrons to drift down the channel. As Vds becomes more positive, the drift velocity of the electrons increase until the saturation drift velocity is reached. At this point the channel current begins to saturate, typically at Vds=0.5V. Beyond this voltage, the current remains constant for an increase in Vds.

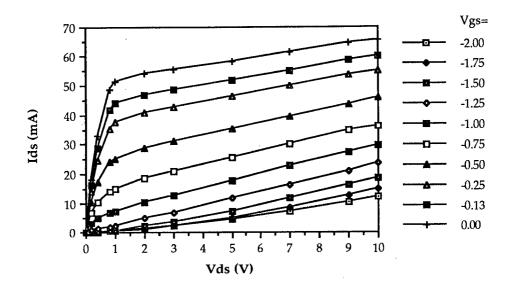

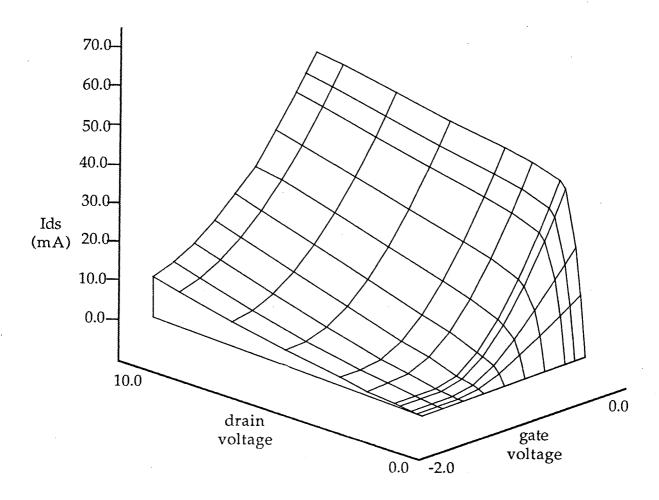

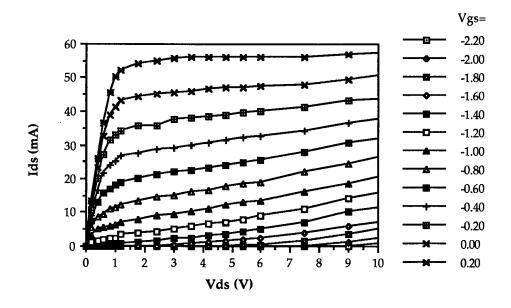

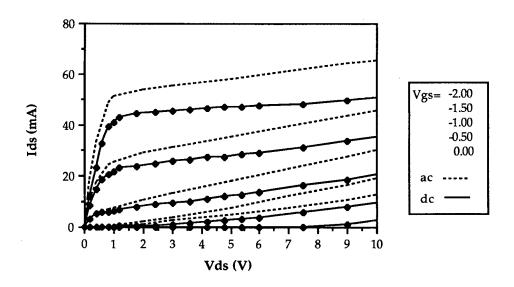

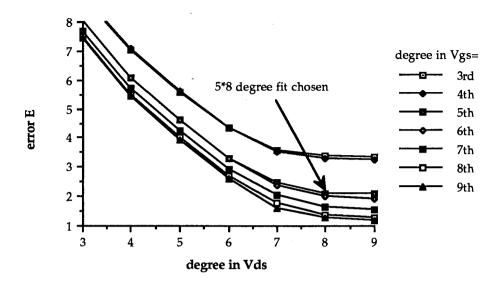

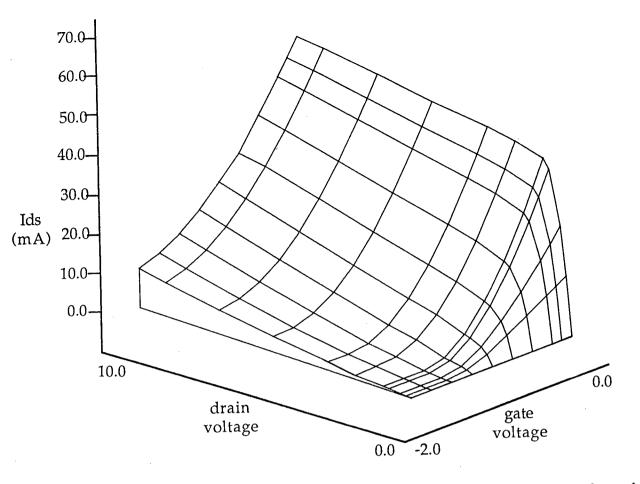

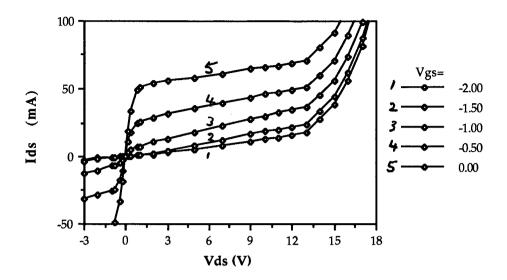

The current is also affected by the gate voltage. A negative voltage applied to the gate terminal of the MESFET removes charge carriers under the gate area and this is known as the depletion region. The size of the depletion region can be increased by increasing the negative value of Vgs. Since this removes more charge carriers, the channel current will steadily drop until the pinchoff voltage is reached. Pinchoff voltage is defined as the gate voltage at which the depletion region has effectively blocked any current from flowing through the channel. The I/V curves for a typical FET are shown in Figure 1.2.

Figure 1.2: I/V characteristics for typical FET

# 1.3 Modelling MESFETs for CAD

The need for accurate CAD for MMIC design has already been discussed. In circuit simulation packages, active and passive components, losses in transmission lines, coupling effects and parasitics are represented by mathematical models. Although all circuit elements are ultimately nonlinear, most simulators assume that devices exhibit linear characteristics. In many cases, the linear assumption is quite valid, although not entirely correct. A resistor for example, can be modelled as a linear element in most applications. The resistor only appears to behave in a nonlinear manner when the current passing through it creates thermal effects, changing the value of the resistance. Additionally, GaAs MMIC resistors are nonlinear because charge velocity saturates with field strength. A nonlinear system is defined where the outputs vary with respect to the phase and amplitude of one or more vector input signals in a way which cannot be described by a simple linear expression.

Linear simulation programmes have been used for some time.

They are especially useful in the design of circuits such as small-signal amplifiers, which are weakly nonlinear and can be assumed to be linear. Other circuits however, such as mixers, rely on the nonlinearity of circuit components for their operation. The linear simulators are of little use in these cases, and nonlinear (or large-signal) simulators must be used instead.

There are a number of different types of nonlinear simulator most of which fall into one of four different categories [20], based on the way in which the circuit nonlinearities are calculated.

- Time domain simulators (for example SPICE) evaluate the transient and steady state responses of a circuit although they can be quite slow and may suffer from instability.

- Harmonic balance simulators use the time and frequency domains to solve nonlinear circuits. They only solve for the steady state response and are most useful when the excitation is only at one frequency.

- Some simulators use nonlinear transfer functions to analyse weakly nonlinear circuits, e.g. Volterra series.

- Describing-function methods use methods which change nonlinear systems to equivalent linear systems.

A more detailed discussion of large-signal simulators is given in Chapter Two.

### 1.4 The MESFET Equivalent Circuit

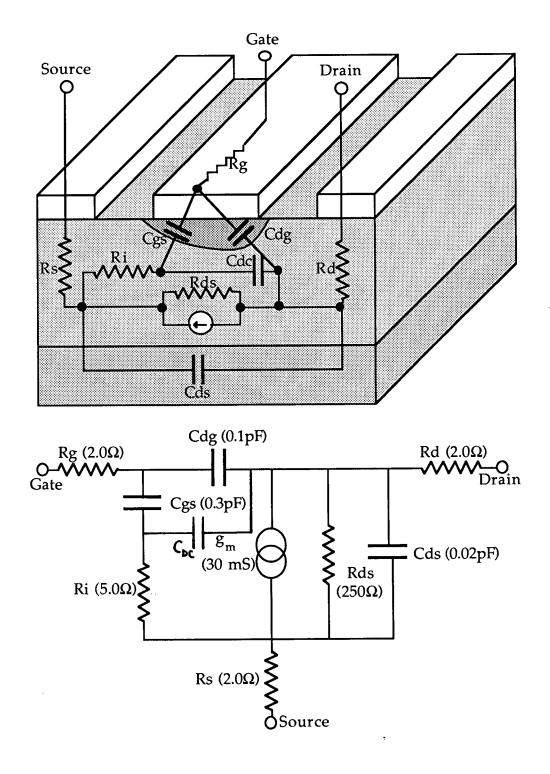

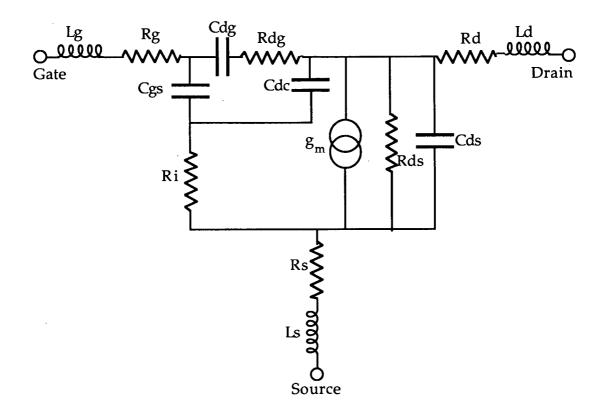

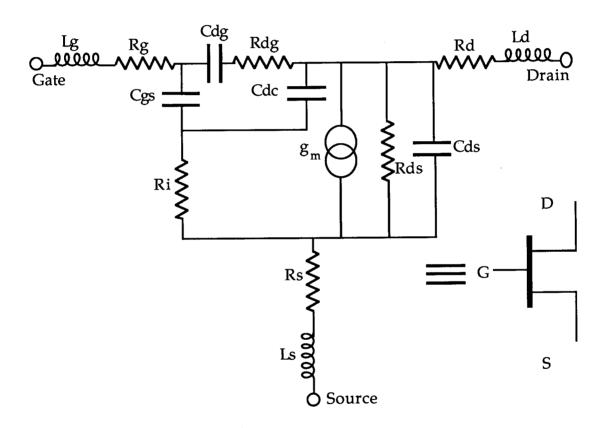

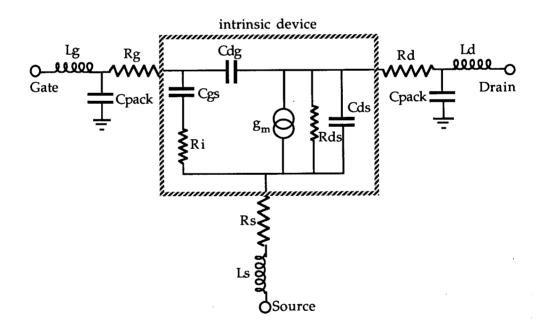

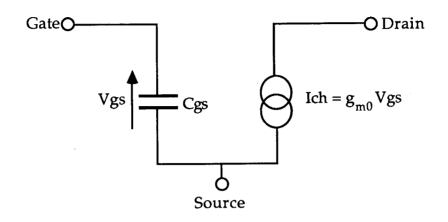

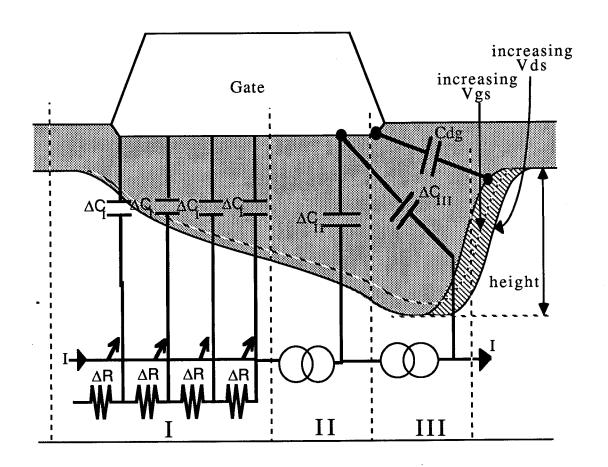

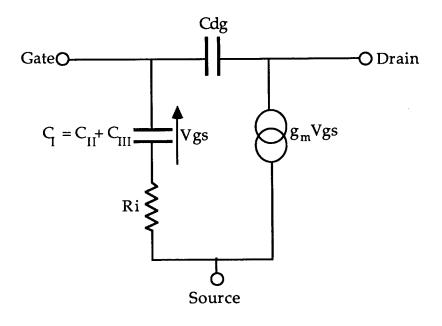

An equivalent circuit (or model) is used to describe the electrical characteristics of a MESFET. The model is found by making measurements of a device and proposing an equivalent circuit which, under simulation, produces similar results. A basic MESFET model is shown in Figure 1.3 comprising a total of ten elements; the model is also superimposed on the device structure [2] to illustrate the physical basis of the electrical model. Cgs and Cdg describe the charge stored in the depletion region between the gate and the channel. Cdc models the capacitance of the dipole layer. Ri and Rds represent the effects of the channel resistance and Rs, Rd and Rg represent the bulk resistance of the N-layer and the contact resistance at the ohmic metallization in the source, drain and gate regions respectively. The current through the channel is modelled by a voltage controlled current source with a transconductance of gm, where the control is the gate-source voltage.

The element values change with MESFET dimensions and doping concentrations, and some of these values also change with bias. Because the equivalent circuit is defined at a specified bias point, it can be considered to be a linear (or small-signal) model. The linear model is used in simulations when the signal voltages are small compared with the quiescent operating conditions.

Larger changes in the signal voltage alter the effective operating point of the device and hence the model element values. Under these conditions, the small-signal model becomes inadequate to describe the electrical behaviour of the MESFET and a nonlinear model must be used instead. As mentioned previously, there are a number of different methods of deriving nonlinear models but most are extensions of the basic

Figure 1.3: Basic FET equivalent circuit superimposed on device structure

small-signal model outlined in this section. A complete review of nonlinear models is given in Chapter Two.

In addition to predicting the electrical characteristics of MESFETs, equivalent circuits can also be used to establish the process parameters of fabrication, such as the doping profile and gate width. This is known as reverse modelling [21] and is particularly useful in diagnosing devices which have failed to meet specification. It is also used in process control monitoring and in the calculation of process yields.

# 1.5 S-parameters to Characterize the MESFET

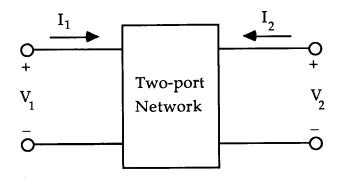

Before a small-signal model is derived for the MESFET, it must be characterized. This is done by making a series of network measurements of the device, normally configured for common source operation and therefore modelled as a two-port device.

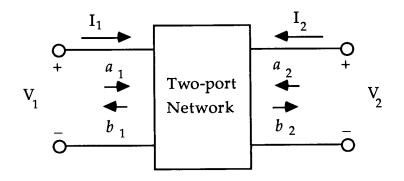

Impedance, admittance and hybrid parameters (Z,Y and h parameters) are often used by engineers to characterize devices at low frequencies. These parameters are expressed in terms of the input current and voltage I1 and V1 and the output current and voltage I2 and V2 (see Figure 1.4), where

Z-parameters;

$$V_1 = Z_{11}I_1 + Z_{12}I_2$$

$$V_2 = Z_{21}I_1 + Z_{22}I_2$$

Y-parameters;

$$I_1 = Y_{11}V_1 + Y_{12}V_2$$

$$I_2 = Y_{21} V_1 + Y_{22} V_2$$

h-parameters;

$$V_1 = h_{11}I_1 + h_{12}V_2$$

$$V_2 = h_{21} I_1 + h_{22} V_2$$

Figure 1.4: Two-port network for Z/Y/h parameters

Figure 1.5: Two port network for S-parameters

For Z parameters, when the input parameter is being measured, the output circuit is open circuited. For example,  $Z_{11} = V_1/I_1$  where  $I_2=0$ . Similarly for Y-parameters, a short circuit environment is required and for h parameters, both open and short environments are needed.

At high frequencies, the measurement of these parameters presents some problems. Broadband open circuits and short circuits are difficult to achieve at high frequencies because of the non-ideal nature of open and short connections. Active devices will often oscillate when connected to reactive loads such as open and short and direct measurement of voltage and current is very difficult at high frequencies. For these reasons, Z, Y and h parameters are not really suitable for characterizing microwave devices.

To overcome these problems, scattering parameters (S-parameters) are used to characterize high frequency networks. The voltage and current in a section of transmission line of length 1 are given as

$$V(x) = V^+ e^{-\gamma x} + V^- e^{+\gamma x}$$

$$I(x) = 1/Z_0 \{V^+e^{-\gamma x} - V^-e^{+\gamma x}\}$$

where V<sup>+</sup> and I<sup>+</sup> are the incident voltage and current, and V<sup>-</sup> and I<sup>-</sup> are the reflected voltage and current. The equations are normalized by  $\sqrt{Z_0}$  and the incident and reflected parameters a and b are defined by

$$a = V^+ e^{-\gamma l} / \sqrt{Z_0}$$

$$b = V^- e^{+\gamma l} / \sqrt{Z_0}$$

A two-port network is shown in Figure 1.5, where the S-parameters are defined by

$$b_1 = S_{11}a_1 + S_{12}a_2$$

$$b_2 = S21a_1 + S22a_2$$

where

S<sub>11</sub> =

$$b_1/a_2 \mid_{a = 0}$$

(input reflection coefficient)

S<sub>12</sub> =  $b_1/a_2 \mid_{a = 0}$  (reverse transmission coefficient)

S<sub>21</sub> =  $b_2/a_1 \mid_{a = 0}$  (forward transmission coefficient)

S<sub>22</sub> =  $b_2/a_2 \mid_{a = 0}$  (output reflection coefficient)

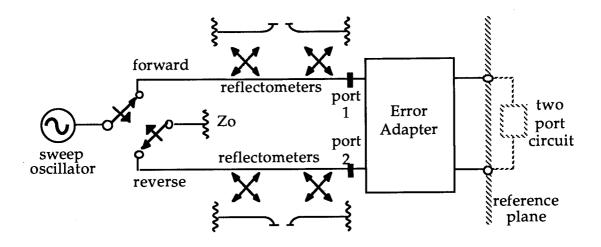

The S-parameters are found by making measurements on one port while the other port is terminated with a matched load. S-parameters can be converted to Z, Y, h or ABCD parameters using well-known equations [22]. The two-port S-parameters are conveniently measured on a network analyser and for accurate measurements the effects of connectors, lengths of transmission line, test jig and parasitics are removed using calibration techniques.

# 1.6 Outline of Project

In this chapter, the need to establish accurate nonlinear models for active devices has been noted, particularly as a result of the emerging MMIC technology. The following chapters of this thesis describe a new nonlinear model for GaAs MESFETs, which was developed so that power amplifier MMICs could be accurately modelled. A review of different nonlinear modelling techniques is presented in Chapter Two and from this review, a new nonlinear model is proposed, derived from sets of Sparameter measurements made at different bias points. The new model contains a novel aspect, in that importance is placed on the ability to model the changes in the characteristics of the MESFET with frequency. An

accurate nonlinear model can only be achieved with accurate measurements and Chapter Three describes methods used to make accurate S-parameters, including the need for good network analyser calibration. Once the S-parameter measurements have been made, a technique known as parameter extraction evaluates a small-signal equivalent circuit for each set of S-parameters and this is dealt with in Chapter Four. Chapter Five describes the way in which all of the information gathered in the previous chapter can be compressed into a nonlinear model. Finally, Chapters Six and Seven illustrate comparisons between simulations of the model and measurements of fabricated MMIC circuits. The results are discussed, further work is suggested and the final conclusions are drawn.

### CHAPTER TWO - Large-signal Models

#### 2.1 Introduction

In Chapter One, the need of accurate large-signal models of GaAs MESFETs for nonlinear circuit simulations was highlighted. The nonlinear model can be derived in a number of different ways and the purpose of this chapter is to review the merits of each different approach. It will be shown that the basic linear equivalent circuit can be expanded and adapted to model device nonlinearities.

Fundamentally, nonlinear modelling derives from one of two basic approaches. The model can be derived from theoretical considerations based on process parameters, such as device geometry and carrier concentrations. Another approach is to ignore the process information and instead derive the nonlinear model from a series of characterizing measurements. For this project, the latter of the two methods was chosen and the review therefore concentrates of this empirical type of modelling. The empirical model can be constructed without reference to process information and, for the fabrication process used in this project (at GEC Plessey Research (Caswell) Ltd.), no such information was readily available. An additional advantage of this method is that direct characterization of devices can lead to a more accurate model, since no assumptions need to be made about the physical operation of the device.

Following the review of nonlinear models, the effects of frequency dispersion are discussed. A difference between the performance of MESFETs at low and high frequencies has been widely observed [23-30] and the dispersive effects of the surface states on the FET are a major cause of this. Most commercially available nonlinear models do not specifically attempt to model these effects but the proposed model of this work is

designed to do this. The effects of frequency dispersion on the MESFET characteristics are discussed and techniques for modelling frequency dispersion are reviewed fully in Chapter Five.

The nonlinear model review illustrates that a number of different types of equivalent circuit have been used to model the MESFET. The final section in this chapter describes the topology of equivalent circuit that was chosen to represent the MESFET in this work. Also, in many of the existing models, some of the capacitive and resistive nonlinearities are omitted, or severely approximated. The proposed nonlinear model includes expressions for all of the major nonlinearities which are allowed for vary freely as functions of both the gate and drain biases.

# 2.2 Expanding the Linear Model to include Nonlinearities

The linear MESFET model can be used to accurately simulate device operation where the signal voltages are small compared with the static operating point. As the signal voltages rise, the linear assumption becomes increasingly less valid, because the signal voltages increasingly deviate from the static operating point, changing the characteristics of the device.

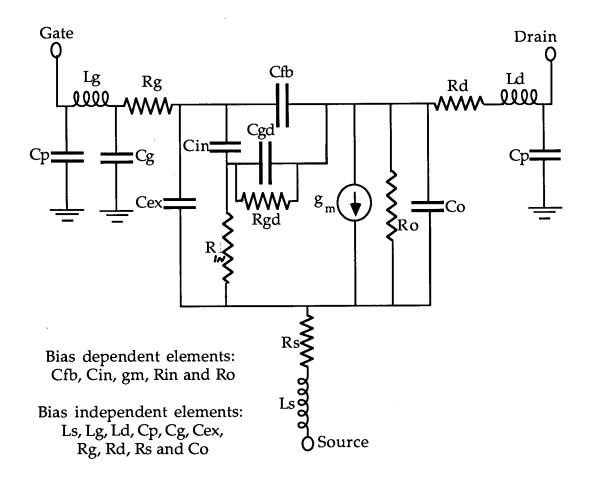

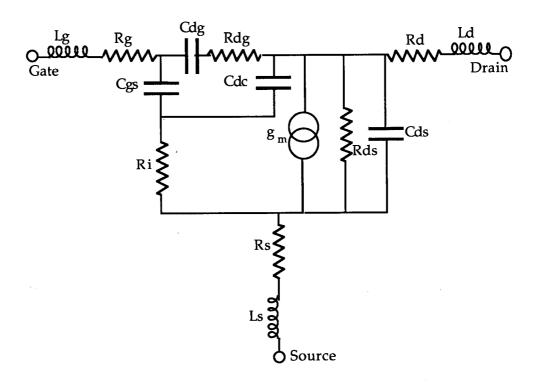

The values of some of the elements in the MESFET equivalent circuit (see Figure 1.3) do not change with bias and these are known as linear (or extrinsic) elements; the element values which change with bias are nonlinear (or intrinsic) elements. Generally, the elements  $g_m$ ,  $R_{ds}$ ,  $C_{gs}$ ,  $C_{dg}$ ,  $R_i$  and  $\tau$  (time delay) are found to be intrinsic and functions which describe their behaviour with bias will be examined later in this chapter. The small-signal model linear transconductance ( $g_m$ ) and the output conductance ( $1/R_{ds}$ ) are the derivatives of the channel current with respect to the gate and drain voltages. In the large-signal model, these linear

elements must be replaced by an expression for the current, which varies with both gate and drain voltages. The bias dependence of the gate-source capacitance  $C_{gs}$ , the gate-drain capacitance  $C_{dg}$ , the intrinsic resistance  $R_i$  and the time delay  $\tau$  are discussed in Chapter Four.

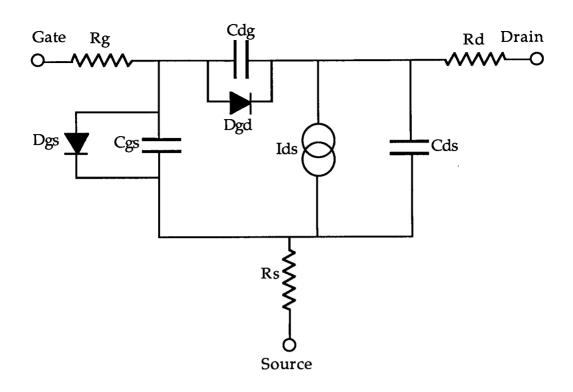

The large-signal model should include extra elements, not present in the linear model, to predict other nonlinear phenomena in the MESFET [30]. These are due to breakdown effects which occur at high voltage levels, or from forward biasing the gate-source Schottky diode. The gate-drain avalanche breakdown current occurs at high values of Vdg and the forward gate current occurs when a positive voltage is applied to the gate of the MESFET. Both of these currents substantially alter the characteristics of the device and will occur in many design applications, such as power amplifiers.

The existing model topologies have been derived by making certain assumptions. For simplicity all models have lumped elements where, in fact, distributed elements would be more appropriate. However, using distributed elements would increase the complexity of simulations and these are only needed to accurately predict model performance at very high frequencies. Many of the models also make the assumption that the characteristics of the device at a particular instant result from the voltage applied across the terminals at the same instant and this is known as the *quasi-static* assumption. However, the characteristics of the MESFET do not change immediately with voltage, which means that the quasi-static assumption degrades, to some extent, the accuracy of the large-signal model.

Ambient temperature and also thermal effects, caused by the drive levels in the device, will alter the characteristics of the device but no account is taken of temperature in either the small or large-signal models and temperature effects will not be examined in this work.

#### 2.3 Different Methods of Nonlinear Simulation

For any circuit, nonlinear behaviour can be defined where the output varies with the input and cannot be described by a linear expression. Linear circuits are generally solved in the frequency domain but this is not suitable for nonlinear characterization. In Chapter One, four different types of nonlinear analysis were listed: time domain, harmonic balance, Volterra series and describing functions. The following paragraphs describe the methods which are most often used to solve linear and nonlinear circuits.

A linear analysis of microwave circuits is most simply calculated in the frequency domain. Linear simulation techniques are well-established and have been implemented with great success on a number of simulation packages. Examples of such packages include SUPERCOMPACT [31], TOUCHSTONE [32] and MDS [33] which can all be run on personal computers, workstations and mainframes. In addition to circuit simulation, these packages have more recently offered optimization routines (which can be used to fit equivalent circuits to measurements), frequency sweeping, plotting algorithms and stability analysis. Many linear simulators can be linked to layout packages for MIC and MMIC mask design; for example, TOUCHSTONE can be used in conjunction with ACADEMY and linked to MICAD [34].

Time domain analysis is more suited to the solution of nonlinear circuits and involves solving a system of nonlinear equations with respect to time. The relationship between voltage and current in the time domain is specified for each circuit element which is solved using Kirchhoff's laws. Solutions are found over a transient period in steps of  $\partial t$ , where the size of

$\partial t$  is inversely proportional to the total solution time and the accuracy. The speed of solution is also affected by the complexity of the nonlinear circuit.

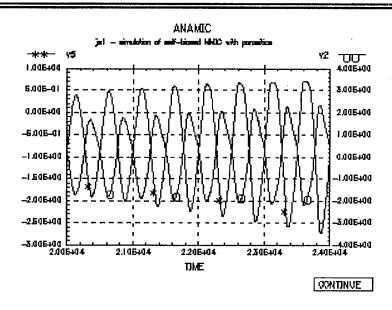

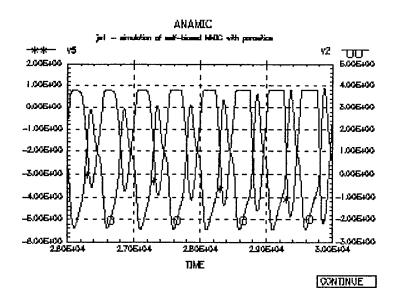

The disadvantage of time domain analysis is that all of the transients must be calculated to reach a solution, whereas in many cases only the steady-state solution is required. Often, the transient settling time (for example, of the bias circuit) can be many orders of magnitude greater than the basic RF period, leading to lengthy calculations. Another problem may occur where, for a given time step, a solution of Kirchhoff's law cannot be found and the solution fails to converge, usually caused by poorly defined nonlinear expressions. There are many time-domain simulators available including SPICE [35], ANAMIC [36], CIRCEC [37] and MICROWAVE SPICE [38].

Harmonic balance analysis is performed in both the time and frequency domains. The circuit is divided into linear and nonlinear sections: the linear section is solved most quickly in the frequency domain for each of N harmonics and the nonlinear section is solved separately in the time domain. Results are passed between the two sections by means of Fourier and inverse-Fourier transforms. Normally, simulation begins with an analysis of the linear system from the initial conditions. The solution of this analysis is used to perform an analysis of the nonlinear system and the results are passed back to the linear system once again. This iterative process continues until the error function between the two systems drops to an acceptably small level.

The speed efficiency of the harmonic balance method depends on the type of nonlinear circuit, the partitioning into linear and nonlinear blocks, the initial conditions and the number of harmonics which must be considered [39, 40]. It is usually quicker than time domain analysis but can become very complicated in applications where signals with more than one frequency are considered. Several improvements to the harmonic balance method have been proposed [41, 39, 42] which have reduced the number of time domain calculations needed and increased the number of harmonics which can be considered. Harmonic balance simulators include LIBRA, MICROWAVE HARMONICA and MDS.

Nonlinear expressions can be described using Volterra series [43]. This is useful in systems which are only weakly nonlinear and where the input signal consists of a number of different frequencies. The Volterra series expansion has an advantage over the power series expansion, that nonlinear systems with memory can be analysed. It is particularly useful in circuits where higher harmonics can be ignored, although analysis becomes rather complicated in systems where this approximation cannot be made.

Describing functions are used to analyse systems where the level of nonlinearity is low. The nonlinear system is converted a number of linear systems (usually linear filters) which can be simply analysed in the frequency domain. The accuracy of the method is largely dependent on the error that exists between the nonlinear and equivalent linear systems. The main disadvantage of this method is that it can be difficult to transpose a nonlinear circuit into a number of linear circuits, especially when the nonlinearities are more pronounced.

### 2.4 Review of Large-Signal Modelling Techniques

## 2.4.1 Categorization

There are many ways to derive large-signal models for active devices, depending on the available data, the simulation software and the chosen theoretical approach. Four different categories are listed below, although a particular method may involve a combination of two or more

methods.

- Empirical models are derived from device measurements to produce

a nonlinear model. The device is characterized using S-parameters,

DC and pulsed I-V measurements, which are then interpreted to find

the nonlinear components in the model.

- Semi-empirical models require some characterizing measurements and also some knowledge of the process parameters, like for example the MESFET gate dimensions and the channel doping concentration. These are the most commonly used commercial nonlinear models and are regarded as "industry standard".

- Analytical models are calculated from mathematical equations which describe the device physics, where certain assumptions have been made to simplify the calculations. Compared with empirical and semi-empirical models, the analytical models to date have been less accurate, mainly because the physical mechanisms controlling charge transport in the MESFET are not yet fully understood. The accuracy of the analytical model is also undermined by the assumptions and approximations which are made during derivation of the equations.

- The most complicated type of analysis is the numerical model. This type of modelling is computing intensive and requires detailed information about the material properties and device geometry. Because these equations require so much computer time to solve they are usually used by device physicists to understand device operation.

The following sections describe each of the above categories in more detail and illustrate each model with published examples. Some of the models are derived from pulsed I-V or DC measurements, zero-channel bias and low frequency S-parameter measurements. Many of the methods use parameter extraction techniques where the values of model elements are derived from S-parameter measurements. These topics are not included in this chapter but are discussed fully in Chapter Four. The techniques for the characterization and modelling of dual-gate FETs are similar to those used for single gate FETs and will not be covered in this work.

### 2.4.2 The Empirical Model

Empirical models are derived from device experimental measurements only, requiring no knowledge of any process parameters. The advantages of these models are that they are computer efficient and can be very accurate. The biggest disadvantage is that no correlation usually exists between the nonlinear model and physical parameters such as gate width, requiring new measurements to be made for each modelled device.

DC and pulsed I-V measurements can be used to characterize the channel current and breakdown effects in the MESFET. Alternatively, the current can be derived indirectly from S-parameter measurements. The remaining nonlinear parameters in the large-signal model can be established by characterizing the MESFET using S-parameter measurements, and extracting the linear and nonlinear parameters of the model from the measurements over a range of bias points [44].

One of the earliest large-signal modelling techniques was proposed

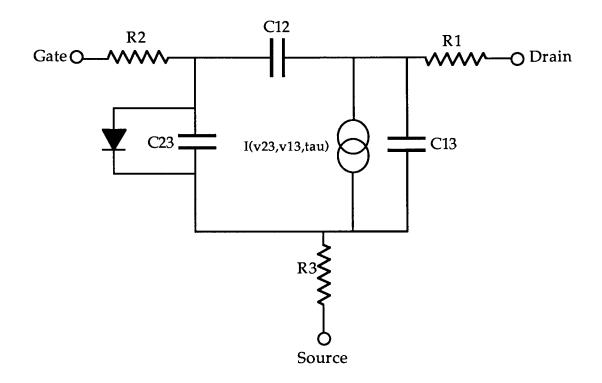

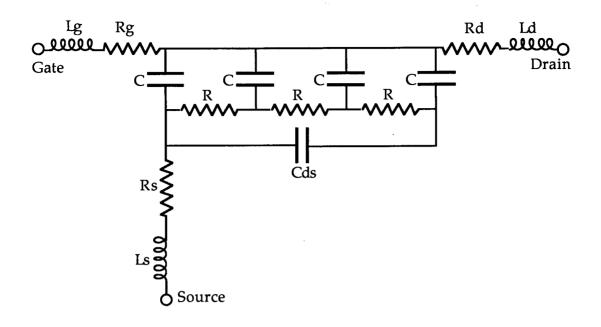

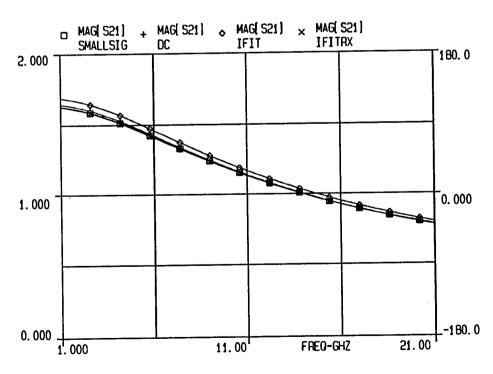

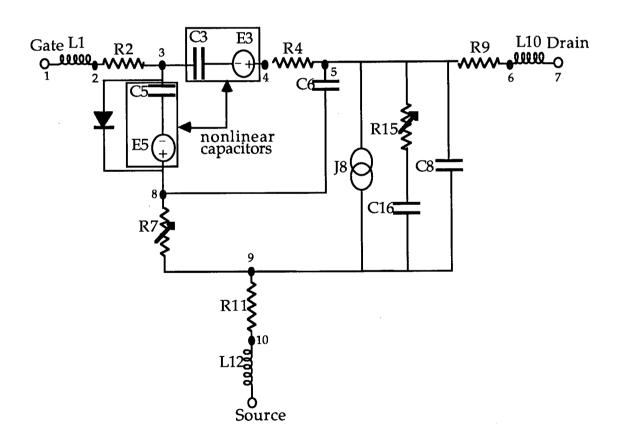

by Willing, Rauscher and de Santis [45] and is a purely empirical approach requiring no analytical or semi-analytical expressions. A device was characterized with S-parameter measurements over a range of bias points and parameter extraction (see Chapter Four) produced linear models for the MESFET at each bias point. Some of the element values in the model were found to vary with bias and were therefore nonlinear (or intrinsic). These were fitted to polynomial expressions where the nonlinearity was described as a function of the gate and drain voltages. The large-signal model shown in Figure 2.1 was verified using a time-domain analysis programme (SYSCAP) where the model was connected to purely resistive terminations. Under these conditions, the analysis was simplified and each of the nonlinear elements could be expressed as a function of only one control voltage.

In another paper [46], this technique was expanded. The instantaneous current through an element was defined as the product of the instantaneous element value and the instantaneous voltage. Nonlinear elements were expressed as either conductances (G) or capacitances (C), where the instantaneous current through them was defined as

$$i_G(t) = G[v_1(t), v_2(t)] \cdot v_G(t)$$

(2.1)

$$i_C(t) = C[v_1(t), v_2(t)] \cdot \partial v_C(t) / \partial t$$

(2.2)

Note that the time variable does not appear explicitly in the functions of G and C and any time dependence of these functions is due to the time dependence of v1 and v2. Hence the nonlinear elements are functions of instantaneous voltages and this is known as the quasi-static assumption. If the currents and voltages are broken up into static and small-signal components

Figure 2.1: Empirical nonlinear model

$$i_C(t) = I_C + i_C(t)$$

(2.3)

$$i_{C}(t) = I_{C} + \underline{i}_{C}(t)$$

(2.4)

$$v_G(t) = V_G + \underline{v}_G(t) \tag{2.5}$$

$$v_C(t) = V_C + \underline{v}_C(t) \tag{2.6}$$

IG, IC etc. represent static parameters whereas iG, iC etc. represent smallsignal dynamic quantities. It was suggested that

$$\underline{\mathbf{i}}_{G}(t) = \underline{\mathbf{G}} \left[ V_{1}(t), V_{2}(t) \right] \cdot \underline{\mathbf{v}}_{G}(t) \tag{2.7}$$

$$\underline{\mathbf{i}}_{C}(t) = \underline{\mathbf{C}} \left[ V_{1}(t), V_{2}(t) \right] \cdot \partial \underline{\mathbf{v}}_{C}(t) / \partial t \tag{2.8}$$

where G and C were the incremental values of conductance and capacitance and these parameters were found from small-signal Sparameter characterization. For all capacitances,  $C = \underline{C}$ . The transconductance and output conductance were assumed as partial derivatives of the current equation Ids and the incremental conductances were simultaneously and partially integrated to produce two definitions of the current

$$I_{ds}(V_1, V_2) = I_0 + V_1 \cdot G_M(V_1, V_2) + V_2 \cdot G_O(0, V_2)$$

(2.9)

$$I_{ds}(V_1, V_2) = I_0 + V_1.G_M(V_1, 0) + V_2.G_O(V_1, V_2)$$

(2.10)

where

$$G_{M}(V_{1}, V_{2}) = 1/V_{1} \cdot \int_{0}^{V_{1}} G_{M}(v, V_{2}) \partial v$$

$$G_{O}(V_{1}, V_{2}) = 1/V_{2} \cdot \int_{0}^{V_{2}} G_{O}(V_{1}, v) \partial v$$

(2.11)

$$G_{O}(V_{1}, V_{2}) = 1/V_{2} \cdot \int_{0}^{V_{2}} \underline{G}_{O}(V_{1}, v) \partial v$$

(2.12)

The current worked out from the two conductances was different and the final result was calculated as an average of the two.

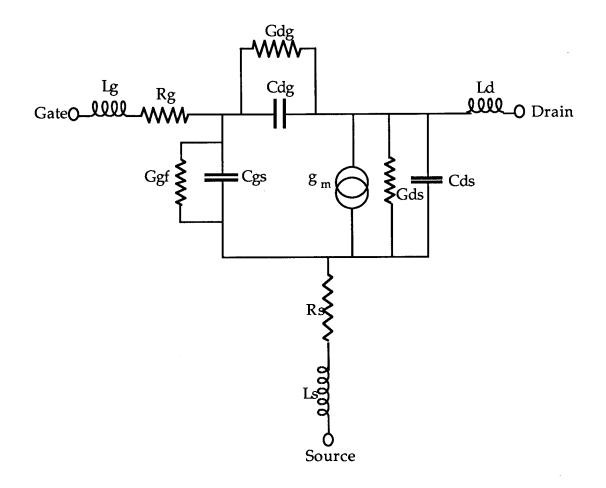

A similar technique was used by Weiss and Pavlidis [47] to empirically characterize a MESFET and produce a large-signal model. The full model contained five nonlinearities: Cgs, Rds, gm, Ggf and Gdg (see first three elements were found using parameter Figure 2.2). The

Figure 2.2: Large-signal model with five nonlinearities: Cgs, Rds, gm, Ggf and Gdg

extraction from small-signal S-parameters. The other two elements described breakdown effects in the MESFET and were characterized with DC measurements.

The voltages in the circuit were expressed as combinations of static and dynamic components (2.5+2.6). The incremental conductances (G') and capacitances (C') related to their instantaneous counterparts by the equations

$$C = \int_{0}^{2\pi} \left[ \int_{0}^{\omega} \left[ -C' \left( V_{ds}, V_{gs} \right) \sin \left( \omega t + \emptyset \right) \right] \partial(\omega t') \right] \cdot \cos \left( \omega t + \emptyset \right) \partial(\omega t) / \pi$$

(2.13)

$$G = \int_{0}^{2\pi} \left[ G' \left( V_{ds}, V_{gs} \right) \cos \left( \omega t + \emptyset \right) \right] \cdot \partial (\omega t) / \pi$$

(2.14)

An interesting aspect of the work was that the empirical model was compared with two other models, both of which are described later in this chapter. One of the models was semi-empirical and derived from Tajima's equations [48]. The other was analytical, combining Curtice's nonlinear current [49] with device physical equations. The empirical model was slightly more accurate than the semi-empirical model for predicting the power saturation curves of MESFET measurements and considerably more accurate than the analytical model.

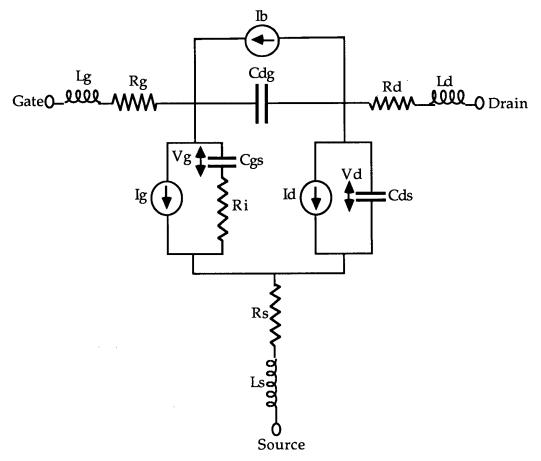

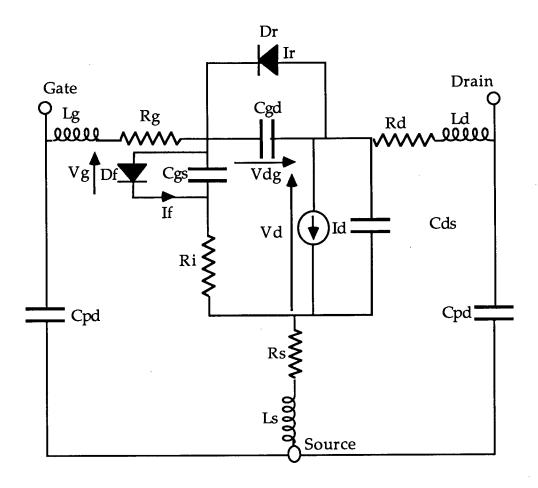

Peterson *et al* [50] used an empirical technique to establish a large-signal model, illustrated in Figure 2.3 and showing the three main nonlinear currents of ID, IG and IB. These were all assumed to be functions of the internal gate and drain voltages and were found using pulsed I-V measurements. The linear elements of RG, RD, Rs, LG, LD and Ls were found using DC characterization techniques. The capacitative elements and Ri were found from parameter extraction of small-signal S-parameters.

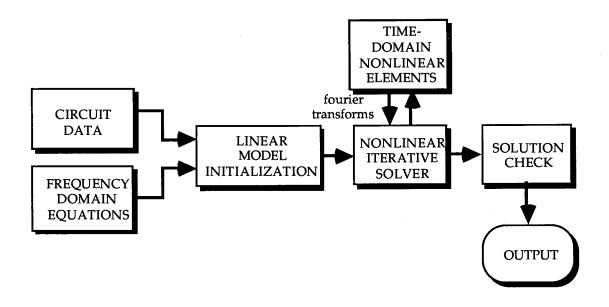

A series of complex simultaneous equations were derived using Kirchhoff's laws in the frequency domain. Expressing the nonlinearity of the currents in the frequency domain is very complex: time domain expressions for inductance and capacitance are also complex terms involving time integrals and differentials. Therefore the nonlinear currents were analysed in the time domain and the linear elements were analysed in the frequency domain using an iterative technique illustrated in Figure 2.4. This technique was also used to predict the large-signal behaviour of a MESFET modelled using the Curtice cubic current equation [51].

Figure 2.3: The Peterson nonlinear model

Figure 2.4: Iterative technique used to solve nonlinear model

Maas et al [52] described a method for measuring the channel current of the MESFET so that it could be fitted to a polynomial expression and included in a Volterra series analysis. The definition of the equation for Ids was

$$I_{ds} = a_1 v_g + a_2 v g^2 + a_3 v g^3 + \dots$$

(2.15)

The MESFET was supplied with low frequency signals and the current harmonics were observed on a spectrum analyser. The coefficient at was calculated from DC measurements and the remaining coefficients were derived from expressions for the power in each of the harmonics.

Some empirical models [53, 54] have been developed, where the elements of the equivalent circuit were optimized so that the simulated output harmonics fitted measured high frequency power measurements. This technique greatly reduced the amount of data needed to produce a large-signal model. The principal problem of this approach is that the limited amount of data used to characterize the device would not necessary achieve an adequate physical representation of its nonlinear behaviour. Whilst the model may be accurate at bias points and power levels similar to the initial measurements, it may vary considerably at different biases and power levels.

Various approaches have been used to characterize the nonlinearity of MESFETs using large-signal S-parameters. None of these approaches are entirely accurate since the measured S-parameters depend not only on signal drive levels but on port terminations as well. The parameters are similar to the linear small-signal counterparts, except that the power of the applied test signals is large enough to measure the device under nonlinear conditions. One of the first large-signal S-parameter measurement techniques [55, 56] demonstrated the effects of drive levels on nonlinear behaviour in power transistors at given frequencies and operating points.

Difficulties were reported in measuring devices under certain bias conditions and an improved technique was proposed by Mazumder *et al* [57] where S-parameters were measured at ports one and two simultaneously.

Another technique was proposed [58] whereby large signal S-parameters could be made in place of load-pull measurements, to establish the optimum load for amplifier circuits. Load-pull measurements require time consuming variations to be made in the input and output loads at a single frequency. S-parameters are more convenient as they can be made with fixed  $50\Omega$  terminations over a swept frequency range. An expression was proposed whereby the optimum load was derived from large-signal measurements for S22 and the forward gain nonlinearity could be determined from large-signal measurements for S21.

Umeda and Nakajima [59] also presented a method where the nonlinear output impedance of a device could be derived from large-signal S-parameter methods. Gain compression characteristics were also derived from the S-parameters and a good agreement with experimental data was observed.

The empirical models offer good potential for deriving an accurate nonlinear model from characterizing measurements. Some of the methods which are used to derive the nonlinear channel current are rather convoluted [46,47], whereas others rely on insufficient measurements [53,54] or are best suited to weak nonlinearities [52]. An empirical approach must be chosen to model devices for which no process information is available.

### 2.4.3 The Semi-empirical Model

Semi-empirical models result from a compromise between the

empirical and analytical approaches. These models are very popular with engineers because of their simplicity and computer efficiency. Most of the published semi-empirical models are based on fitting the DC I-V characteristics of the MESFET to equations which have been derived from analytical expressions. The equations may include process controlled parameters, such as the pinchoff voltage and the built-in voltage, but all of the equations contain arbitrary parameters ( $\alpha$ ,  $\beta$ ,  $\gamma$  etc.) which are used to fit the equation to DC measurements.

The most important nonlinear element in the large-signal model is the current equation and many semi-empirical expressions have been proposed for it. The general shapes of these equations are similar, including a linear region rising to a "knee" point and a saturation region. The following section reviews the semi-empirical models which have been proposed for the other nonlinear elements in the large-signal model.

#### 2.4.3.1 Models for the Drain Current Ids

The Curtice quadratic model [49], illustrated in Figure 2.5, is one of the most widely used and referenced nonlinear models. The definition of the nonlinear current is simple and can provide a good fit to measured DC curves. The equation was derived from an analytical expression derived by Sze [60] for the saturation current in a symmetrical JFET and was defined as

$$I_{ds} = \beta (V_{gs} + V_T)^2$$

(2.16)

where  $\beta = I_p/V_p^2$ ,  $I_p$  is the saturation current,  $V_p$  is the pinchoff voltage,  $V_p$  is the threshold voltage ( $V_p = V_p + V_{BI}$ ) and  $V_{BI}$  is the built-in voltage. A hyperbolic tangent was added to the equation to improve its response at drain voltages below saturation and the full equation became

Figure 2.5: Curtice quadratic model

$$Ids = \beta (V_{gs} + V_T)^2 (1 + \lambda V_{ds}) \tanh (\alpha V_{ds})$$

(2.17)

where  $\alpha$ ,  $\beta$  and  $\lambda$  are constants and are found by fitting the above equation to MESFET DC characteristics.

In later publications [51, 61], Curtice proposed a nonlinear cubic current equation. The cubic approximation was found to produce a better fit to the DC characteristics of the MESFET and was defined as

$$I_{ds} = (A_0 + A_1 V_{gs} + A_2 V_{gs}^2 + A_3 V_{gs}^3) \cdot \tanh(\alpha V_{ds})$$

(2.18)

where Ai were evaluated from DC channel current data in the saturation region. In simulation, the cubic model produced smaller errors than the quadratic expression, except at low drain-source voltages, where non-physical effects associated with calculation of V<sub>p</sub> with respect to V<sub>ds</sub> interfered with the optimization of the model [61].

The Curtice quadratic model was used to replace the JFET model of SPICE 2 in a number of applications and Sussman-Fort *et al* [62] published details of how this new expression could be implemented into the source code of the simulator.

Statz et al [63] proposed a modification of the Curtice quadratic model. They found that the current equation was poorly represented as a function of Vgs and suggested that, except for gate voltages near the pinchoff voltage, the current was proportional to the height of the undepleted channel. The saturated current was represented by the analytical expression

$$I_{ds} = Zv_{sat} \sqrt{(2\xi qN_d)((\sqrt{-V_T + V_{BI}}) - \sqrt{-V_{gs} + V_{BI}})}$$

(2.19)

where Z is the channel width,  $v_{sat}$  is the saturated electron velocity,  $\boldsymbol{\mathcal{E}}$  is the dielectric constant, q is the electron charge and Nd is the donor density. For  $\|V_{gs} - V_T\| \le 0.3$ , equation (2.19) was not valid since the approximation of constant channel height could not be made and equation (2.17) was used instead. An empirical expression was used to connect (2.17) and (2.19) over the whole range of gate voltages and this was

$$Ids = \beta(V_{gs} - V_T)^2 / (1 + b(V_{gs} - V_T))$$

(2.20)

The tanh function in (2.18) was found to consume too much computer time and was replaced by a polynomial P, where

$$P = 1 - (1 - \alpha V_{ds}/n)^n$$

for n=2 or 3 (2.21)

and the complete model was

$$I_{ds} = \beta (V_{gs} - V_T)^2 / (1 + b(V_{gs} - V_T)) \left\{ 1 - (1 - \alpha V_{ds} / n)^n \right\} (1 + \lambda V_{ds})$$

(2.22)

The current equation was implemented into SPICE and has also been used with success elsewhere [64, 65]. The Statz model [66] was found to give a poor fit for the current at values of Vgs close to pinchoff and the

output conductance was also poorly characterized. The poor fit for the current near pinchoff was improved by making VT a function of the drain voltage, where

$$V_{T} = V_{T0} - \gamma V_{ds} \tag{2.23}$$

The fit of the output conductance was improved by modifying the Statz model so that

$$I_{ds} = I_{ds0} / (1 + \delta V_{ds} I_{ds0})$$

(2.24)

and

$$I_{ds0} = \beta (V_{gs} - V_T)^Q \left\{ 1 - (1 - \alpha V_{ds}/n)^n \right\}$$

(2.25)

This resembles the original Statz equation with  $b=\lambda=0$  and three new parameters  $\delta$ ,  $\gamma$  and Q.

Tajima [48] proposed a nonlinear model with a similar topology to the Curtice model. The transconductance and drain conductance were found to be nonlinear and so were Ri, Cgs and Ggf (the gate forward conductance, connected in parallel with Cgs). An expression for the nonlinear channel current Ids was based purely on empirical measurements, describing the DC characteristics of the MESFET. The transconductance and output conductance were found by differentiating the current with respect to Vgs and Vds respectively. The current Ids was defined as

$$I_{ds} (V_{ds'} V_{gs}) = I_{d1} \times I_{d2}$$

(2.26)

where

$$I_{d1} = 1/k \left[ 1 + V_{gs'}/V_p - 1/m + (1/m) \times \exp \left\{ -m \left( 1 + V_{gs'}/V_p \right) \right\} \right]$$

$$I_{d2} = I_{dsp} \left[ 1 - \exp \left\{ -V_{ds}/V_{dss} - a(V_{ds}/V_{dss})^2 - b(V_{ds}/V_{dss})^3 \right\} \right]$$

$$k = 1 - 1/m \left\{ 1 - \exp(-m) \right\}$$

$$V_p = V_{p0} + pV_{ds} + V_{BI}$$

$$V_{gs'} = V_{gs} - V_{BI}$$

where  $V_{po}$  is the pinchoff voltage at  $V_{ds}=0V$ ,  $V_{ds}$  is the drain current saturation voltage,  $I_{dsp}$  is the drain current for  $V_{gs}=V_{BI}$  and a,b,m, and p are constants, found by fitting the equation to the DC characteristics of the MESFET (similar to the Curtice  $\alpha,\beta$  and  $\lambda$  terms). The model was later modified [48] to include the effects of gate-drain breakdown by adding a nonlinear resistance in parallel with the gate-drain capacitance  $C_{dg}$ . The current through the resistor was zero for  $V_{dg} < V_b$  and equalled (1/Rb) .  $(V_{dg} - V_b)$  for  $V_{dg} \ge V_b$ , where

$$V_b = V_{b0} + R_1 I_{ds} (2.27)$$

$$R_b = R_{b0} + R_2 \cdot (I_d/I_{dss})$$

(2.28)

Large-signal models were simulated [67, 68], including nonlinear sources characterized by the Tajima equation. One of the models [67] was used to simulate power spectral characteristics and was compared to measurements made on commercial packaged transistors and the other was successfully used to design a power FET multiplier [68].

A nonlinear current equation was proposed by Taki [69] to model the JFET. An analytical derivation of the JFET current equation was considered, although this was abandoned in place of a simpler empirical equation. The current Ids was defined as

$$I_{ds} = I_{dss} (1 - V_{gs}/V_p)^2 \cdot \tanh \alpha |V_{ds}/V_p - V_{gs}|$$

(2.29)

Comparisons were made [70] between the Taki and Tajima current equations and it was found that, although more complicated, the Tajima equation could be fitted to MESFET DC characteristics with greater accuracy.

Materka and Kacprzak [71] proposed a model, illustrated in Figure 2.6, which includes a current source Ids(Vgs,Vds), a nonlinear capacitance

Figure 2.6: The Materka and Kacprzak nonlinear model

Cgs, a diode representing the gate channel current and another diode to represent gate-drain breakdown. The current equation was the same as the expression proposed by Taki [69]. The model was evaluated using the harmonic balance technique; power saturation results for an amplifier containing the model were simulated and found to compare well with experimental measurements.

The Materka current equation was modified by Hwang [72] in order to model the DC characteristics of a Hughes MESFET which exhibited a negative output conductance in the saturation region. The new equation became

$$I_{ds} = I_{dss} (1 - V_{gs}/V_p)^2 . tanh [c V_{ds}/V_{gs} - V_p]$$

for  $V_{ds} < V_{sat}$ , and

$$I_{ds} = I_{dss} (1 - V_{gs}/V_p)^2 \cdot \tanh \left[ c V_{ds}/V_{gs} - V_p \right] - V_{ds} \cdot g_0 / \left[ V_s - V_{gs} \right] q$$

for  $V_{ds} \ge V_{sat}$  (2.30)

where  $V_p = V_{p0} + r.V_{ds}$  and  $I_{dss}$ , c,  $g_0$ ,  $V_{p0}$ , r,  $V_s$  and  $V_{sat}$  are optimized to fit the measured I-V curves.

Larson [73] examined the nonlinear current equation by Schichmann-Hodges for the JFET which is implemented in most SPICE simulators. The drawback of the latter expression is the assumed square-law relationship between Vgs and Ids which is not always found to be the case for MESFETs. Also, because MESFETs possess a large negative threshold voltage, current saturation occurs at lower values of Vds than can usually be predicted using the SPICE model and these observations were reported elsewhere [74]. Whilst the Curtice equation and others using the tanh function were found to provide a good fit to DC characteristics for devices with large negative threshold voltages, they were less suitable for devices with smaller thresholds.

Consequently, a new current equation was proposed, where

$$\begin{split} I_{ds} &= \beta (1 + \lambda k V_{ds}) k V_{ds} (1/q)^q \left[ (1 + q)(V_{gs} - V_T) - k V_{ds} \right]^q \\ & \qquad \qquad \text{for } V_{gs} - V_T \ge k V_{ds} \\ I_{ds} &= \beta (1 + \lambda k V_{ds}) (V_{gs} - V_T)^{1+q} \\ & \qquad \qquad \text{for } V_{gs} - V_T < k V_{ds} \end{split} \tag{2.31}$$

where the two new terms q and k were included to improve the modelling of  $I_{ds}$  with respect to  $V_{gs}$  and the onset of drain current saturation respectively.

A nonlinear current equation was also proposed by Jastrzebski [75]

and featured all of the important characteristics of the following models: Curtice, Tajima, Materka, Statz and Larson. It allowed for relationships between current and gate voltage other than square-law and for decreasing output conductance with increasing  $V_{gs}$ . The pinchoff voltage was defined as being dependent on  $V_{ds}$  and a negative slope for  $I_{ds}$  with respect to  $V_{ds}$  in the saturation region could be fitted. Also, the saturation voltage was defined as a function of  $V_{gs}$ . The models were compared with each other and with the new model and were all found to be deficient in at least one respect.

A series of comparisons were made [76] between the current models of Taki, Curtice, Materka, Statz and Tajima and a new model by Brazil. A DC curve fitting package called INTERSECT was used to fit the DC characteristics of an NE71000 chip device and a Plessey monolithic device to each of the equations and the results [76] are given below.

| Model Name | No. Parameters | RMS Error |         |

|------------|----------------|-----------|---------|

|            |                | NE71000   | Plessey |

| . Taki     | 3              | 3.66      | 4.95    |

| Curtice.Q  | 4              | 3.36      | 4.09    |

| Materka    | 4              | 2.67      | 1.48    |

| Statz      | 5              | 2.15      | 4.06    |

| Brazil     | 6              | 1.51      | 1.13    |

| Curtice.C  | 7              | 0.85      | 0.65    |

| Tajima     | 9              | 1.03      | 0.84    |

Results of the work concluded that the Curtice cubic model was best equipped to model the DC current characteristics, whilst Materka's expression was simpler and still produced acceptable results. Another set of comparisons was made [65] between the Materka, Statz and cubic Curtice models and the results showed that the best fit was obtained from Materka's expression.

Other semi-empirical models for the MESFET exist. Some of them

have been developed for use in digital applications and have been implemented on SPICE, like the large-signal models proposed by Golio *et al* [77] and Goyal [78]. Whilst adequate for digital simulation, the current equation was often found lacking with respect to modelling the output conductance which made it unsuitable for analogue circuits.

All of the semi-empirical equations for the current are implemented in the nonlinear model by fitting the equation to characterizing measurements for the DC current of the MESFET. Therefore, a critical assumption is made, that the characteristics of the MESFET are the same at high frequencies, as they are at DC, unless the DC characterization has been made using pulsed I/V measurements (see Chapter Four). This assumption will be examined in greater detail in Section 2.5.

The semi-empirical models are also susceptible to errors arising from heating effects. The channel of the MESFET heats up the longer it is held at a particular bias setting, especially for high channel currents. The temperature change will affect the characteristics of the MESFET which will in turn affect the characterizing measurements at that bias point. If the bias setting has resulted from RF excitation, the temperature of the MESFET will be less than for the DC case.

# 2.4.3.2 Models for Cgs, Cdg, Ri and $\tau$

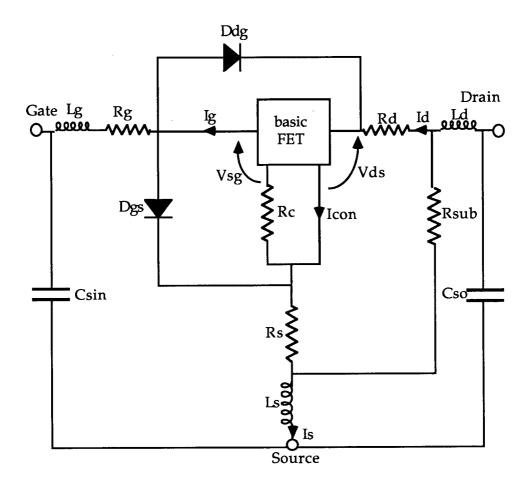

The channel current is the most important nonlinearity in the MESFET model and this is confirmed by the MESFET model sensitivity analysis given in Chapter Four. The overall accuracy of the large-signal model depends on the other nonlinear elements which, listed in descending order of sensitivity, are:  $C_{gs}$ ,  $C_{dg}$ ,  $\tau$ , and  $R_i$  (see Figure 2.3). Gatedrain breakdown and forward gate current effects should also be included

into the large-signal model by adding parallel, ideal, diode elements  $\mathsf{Ddg}$  and  $\mathsf{Dgs}$  to the existing elements  $\mathsf{Cdg}$  and  $\mathsf{Cgs}$  respectively, modelled on DC measurements

All of the published semi-empirical models include the non-linear element  $C_{gs}$ . Some of the models also include  $C_{dg}$  and/or  $D_{dg}$  and  $D_{gs}$ . Only a few of the models include nonlinear elements for  $R_i$  and  $\tau$ . A summary of these nonlinear elements is given below.

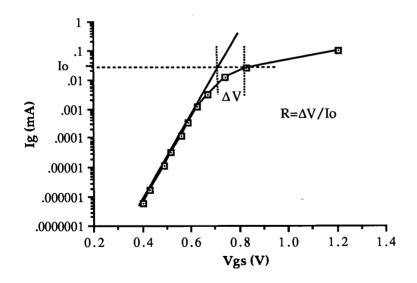

In many of the large-signal models [35, 49, 79] and in commercial simulators such as SPICE and LIBRA, the gate-source capacitance is represented by an analytical expression for a reverse biased Schottky barrier capacitance. The equation is defined as

$$C_{gs} = C_{gs0}/(1 - V_{gs}/V_{BI})^{1/2}$$

(2.32)

where VBI is the built-in voltage ( $\approx 0.8$ V) and Cgs0 is the zero bias gate capacitance. A similar equation is often used to model the gate-drain capacitance Cdg, where

$$C_{dg} = C_{dg0} / (1 - V_{dg} / V_{BI})^{1/2}$$

(2.33)

However, these expressions have a number of deficiencies. Firstly, when the source-drain voltage is zero and for a physically symmetrical MESFET, the values of Cgs and Cdg should be equal but the above equations may produce different values for both capacitances. The capacitive model also breaks down when the transistor is reverse biased and Cgs becomes Cdg and vice versa. The above equations also limit Cgs as varying with Vgs only and Cdg with Vdg only. In fact, the capacitances are functions of both voltages and this was recognised by Goyal [78] who modified (2.32) to

$$C_{gs} = C_{gs0}/(1 - V_{gs}/V_{BI})^{1/2} + C_0 V_{ds}$$

(2.34)

where the coefficient C<sub>0</sub> was added to account for the effect of V<sub>ds</sub> on the gate capacitance. Statz [63] improved the equations for the gate-source and gate-drain capacitances by modelling the capacitances as derivatives of the

gate charge  $Q_g$  and not as unconnected elements. This removed many of the problems mentioned above and allowed the MESFET to be considered as a symmetrical device.

Larson [73] suggested that the capacitance in the channel could be divided into three regions: the source end of the depletion region, the drain end of the depletion region and the central region. The charge in the central region was derived from an analytical equation [80]. Cgs was defined as the derivative of the charge with respect to Vgs plus the capacitances of the two end regions. Similarly, Cdg was the derivative of the charge with respect to Vdg plus the end capacitances.

Jastrzebski [75] proposed a semi-empirical model for both capacitances, where

$$C(V) = 0.5 C_0 / \sqrt{d(3 - h/d)} + C_{gf} \quad \text{for } V > V_{BI} - dV_{BI}$$

$$= C_0 / \sqrt{h} + C_{gf} \quad \text{for } V_{BI} - dV_{BI} > V > -V_{to}$$

$$= C_0 / (\sqrt{(1 + V_{t0} / V_{BI})}) \cdot (V + V_{to} + dV_{to}) / dV_{to} + C_{gf}$$

$$\text{for } 0 > V + V_{to} > -dV_{to}$$

$$= C_{gf} = \text{const} \quad \text{for } V < -V_{to} - dV_{to}$$

(2.35)

where  $C_0$  is the depletion capacitance at zero bias,  $C_{gf}$  is the gate fringing capacitance, h=1-V/VBI,  $V_{to}$  is the threshold voltage and d is a constant. V is either  $V_{gs}$  or  $V_{dg}$  depending on whether  $C_{gs}$  or  $C_{dg}$  is being specified.

The gate-drain capacitance has also been modelled by Hwang *et al* [72] with the equation

$$C_{dg} = C_{g0}/(1 - V_{gs}/V_{BI})^{1/2}. (1 - V_{ds}/V_{sat}) + C_{dp}$$

(2.36)

in recognition of the dependence of Cdg on both bias voltages.

Semi-empirical equations for the intrinsic resistance  $R_i$  and the time delay under the gate  $\tau$  are quite scarce. In some models [79, 81] the intrinsic resistance was assumed to vary in such a way that the charging time constant did not change. Curtice [61], on the other hand, defined the

time delay as a linear function of only the drain voltage. Jastrzebski [75] proposed a nonlinear intrinsic resistance of the form

$$R_i(V_{gs}) = R_{i0} \times (1 - V_{gs}/V_r)^{\sigma}$$

(2.37)

where  $R_{io}$  is the value of resistance at  $V_{gs}$ =0,  $V_r$  is the voltage at which  $R_i$  becomes zero and  $\sigma$  equals 1 or 2.

Less semi-empirical equations exist for the nonlinear elements  $C_{gs}$ ,  $C_{dg}$ ,  $R_i$  and  $\tau$  than for the nonlinear current. It has been shown [78] that, for the gate-source capacitance  $C_{gs}$ , the existing equations, including the equation used in SPICE, are rather limited and can decrease the accuracy of the nonlinear model. Nonlinear expressions for the gate-drain capacitance are even less common and the intrinsic resistance  $R_i$  is most often represented as a linear resistor.

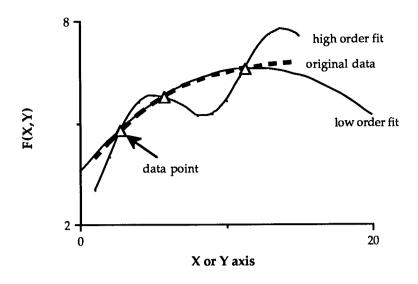

### 2.4.4 The Analytical Model