# Analysis and Parameter Prediction of Compiler Transformation for Graphics Processors

Alberto Magni

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2015

## Abstract

In the last decade graphics processors (GPUs) have been extensively used to solve computationally intensive problems. A variety of GPU architectures by different hardware manufacturers have been shipped in a few years. OpenCL has been introduced as the standard cross-vendor programming framework for GPU computing. Writing and optimising OpenCL applications is a challenging task, the programmer has to take care of several low level details. This is even harder when the goal is to improve performance on a wide range of devices: OpenCL does not guarantee performance portability.

In this thesis we focus on the analysis and the portability of compiler optimisations. We describe the implementation of a portable compiler transformation: thread-coarsening. The transformation increases the amount of work carried out by a single thread running on the GPU. The goal is to reduce the amount of redundant instructions executed by the parallel application.

The first contribution is a technique to analyse performance improvements and degradations given by the compiler transformation, we study the changes of hardware performance counters when applying coarsening. In this way we identify the root causes of execution time variations due to coarsening.

As second contribution, we study the relative performance of coarsening over multiple input sizes. We show that the speedups given by coarsening are stable for problem sizes larger than a threshold that we call saturation point. We exploit the existence of the saturation point to speedup iterative compilation.

The last contribution of the work is the development of a machine learning technique that automatically selects a coarsening configuration that improves performance. The technique is based on an iterative model built using a neural network. The network is trained once for a GPU model and used for several programs. To prove the flexibility of our techniques, all our experiments have been deployed on multiple GPU models by different vendors.

## Lay Summary

In the last decade processors originally designed to compute the color of the pixels of a computer screen (GPUs) have also been used to solve computationally intensive problems. A variety of GPU architectures by different hardware manufacturers have been shipped in a few years. The OpenCL programming language has been introduced to provide a standard programming framework for GPUs.

Writing and optimising OpenCL applications is a challenging task, the programmer has to take care of several low level details. This is even harder when the goal is to improve performance on a wide range of devices. OpenCL applications do not perform equally well on devices of different types.

In this thesis we focus on the analysis and the portability of code transformations. We describe the implementation of a portable compiler transformation: thread-coarsening. Its goal is to reduce the amount of redundant instructions executed by the parallel application.

We first develop a technique to automatically analyse performance improvements and degradations given by thread-coarsening. We also developed machine learning technique that automatically selects a coarsening configuration that improves performance on a four different GPU models.

## Acknowledgements

I would like to thank first my advisor Michael O'Boyle for his constant support, he taught me how to get things done. I am greatly indebted towards my second supervisor Christophe Dubach. He gave innumerable suggestions about life as a PhD student.

I would like to thank Dominik, Thibaut, Toomas, Erik, Michel, Yuan, Tobias, Alex, Chris, Sid, Kiran and all the members of the CARD group. A special thank to my Greek friends Vasilis, Konstantina, Christos and to Juan, who almost speaks Greek.

I would like to thank Anton Lokhmotov and ARM for hosting me for three months in Cambridge. I thank the colleagues I met there: Murat, Georgia and Alexey. I had a great time discussing with Cedric about GPU caches and thread scheduling.

I am grateful to Vinod Grover, Sean Lee and Mahesh Ravishankar at Nvidia for giving me the opportunity to work with them. I would like also to thank my colleague Nhat and my flatmate in Redmond Alexander.

I thank my office mate Andrea for sharing his brownies with me and for hosting me in Munich. My Italian friends in Edinburgh helped me free my mind from research and fill my belly with food. I would like to thank Tiziana, Manuela, Gianpaolo, Marta, Marina, Fabio, Simona and Cesare. A special thank to Marcello for all our endless discussions about computers and for not letting me down in San Francisco. I thank Ettore for convincing me to come to Edinburgh to do a PhD and for driving me around Silicon Valley. I would like to thank Antonio and Yanick for our trips to Berlin and for hosting me in California.

My parents Annalisa and Danilo always had words of encouragement and support. Finally, thank you Giada for being close to me.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

Some of the material used in this thesis has been published in the following papers:

• Alberto Magni, Christophe Dubach, Michael F.P. O'Boyle.

"A Large-Scale Cross-Architecture Evaluation of Thread-Coarsening". In Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis (SC), November 2013.

- Alberto Magni, Christophe Dubach, Michael F.P. O'Boyle. "Exploiting GPU Hardware Saturation for Fast Compiler Optimization". In Proceedings of the Workshop on General Purpose Processing Using GPUs (GPGPU), March 2014.

- Alberto Magni, Christophe Dubach, Michael F.P. O'Boyle.

*"Automatic Optimization of Thread-Coarsening for Graphics Processors"*.

In Proceedings of the International Conference on Parallel Architectures and Compilation Techniques (PACT), August 2014.

(Alberto Magni)

# **Table of Contents**

| 1 | Intro | oduction                               |

|---|-------|----------------------------------------|

|   | 1.1   | Contributions                          |

|   | 1.2   | Thesis organization                    |

| 2 | Bacl  | kground                                |

|   | 2.1   | OpenCL                                 |

|   |       | 2.1.1 Device abstraction               |

|   | 2.2   | GPU Architecture                       |

|   |       | 2.2.1 Nvidia                           |

|   |       | 2.2.2 AMD                              |

|   | 2.3   | Compiler Infrastructure                |

|   |       | 2.3.1 LLVM                             |

|   | 2.4   | Hardware Performance Counters          |

|   | 2.5   | Benchmarks                             |

|   | 2.6   | Machine Learning                       |

|   |       | 2.6.1 Regression Trees                 |

|   |       | 2.6.2 Neural Networks                  |

|   |       | 2.6.3 Principal Components Analysis    |

|   | 2.7   | Performance Evaluation                 |

|   |       | 2.7.1 Performance Metrics              |

|   |       | 2.7.2 Cross Validation                 |

|   | 2.8   | Summary                                |

| 3 | Rela  | ated Work 27                           |

|   | 3.1   | History of Graphics Processing         |

|   | 3.2   | General Purpose Computing on GPUs      |

|   | 3.3   | GPU Performance Analysis and Modelling |

|   | 3.4   | Loop optimisations                     |

|   | 3.5   | GPU Optimisations                      |

|   |      | 3.5.1 Thread-coarsening                            | 37 |

|---|------|----------------------------------------------------|----|

|   | 3.6  | Iterative Compilation                              | 39 |

|   | 3.7  | Compiler Optimisation Tuning with Machine Learning | 39 |

|   | 3.8  | Summary                                            | 41 |

| 4 | Con  | npiler Analyses and Transformations                | 42 |

|   | 4.1  | Introduction                                       | 42 |

|   | 4.2  | Divergence Analysis                                | 46 |

|   | 4.3  | Coarsening                                         | 49 |

|   |      | 4.3.1 Control Flow Management                      | 49 |

|   |      | 4.3.2 The stride option                            | 50 |

|   |      | 4.3.3 Limitations                                  | 50 |

|   |      | 4.3.4 Effects of Coarsening on Program Structure   | 50 |

|   | 4.4  | Compiler Set-up                                    | 54 |

|   |      | 4.4.1 OpenCL Backend                               | 54 |

|   |      | 4.4.2 Customization of the Compilation Process     | 55 |

|   | 4.5  | Invocation                                         | 56 |

|   | 4.6  | Memory Accesses Modelling                          | 56 |

|   |      | 4.6.1 SymEngine                                    | 57 |

|   |      | 4.6.2 Transaction Computation                      | 58 |

|   |      | 4.6.3 Evaluation                                   | 60 |

|   | 4.7  | Summary                                            | 62 |

| 5 | Perf | formance Counters Analysis                         | 63 |

|   | 5.1  | Introduction                                       | 63 |

|   | 5.2  | Motivation                                         | 64 |

|   | 5.3  | Experimental Set-up                                | 65 |

|   |      | 5.3.1 Devices                                      | 65 |

|   |      | 5.3.2 Coarsening Parameter Space                   | 66 |

|   |      | 5.3.3 Benchmarks                                   | 67 |

|   | 5.4  | Performance Results                                | 68 |

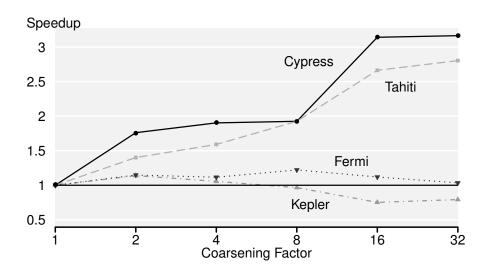

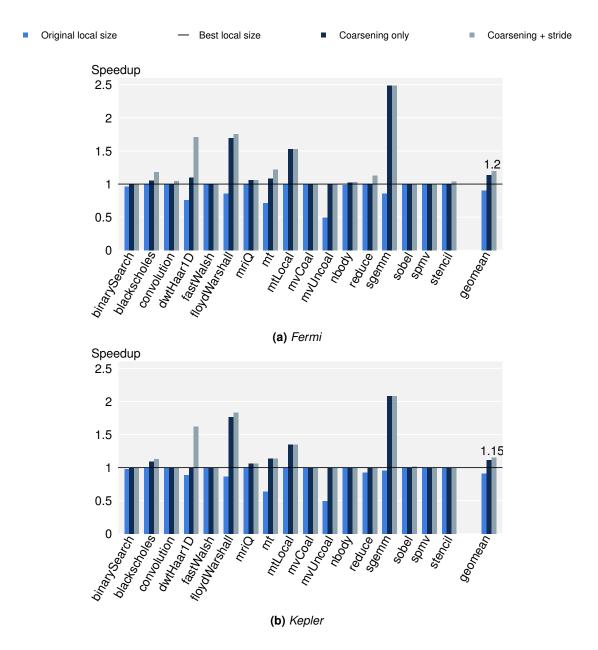

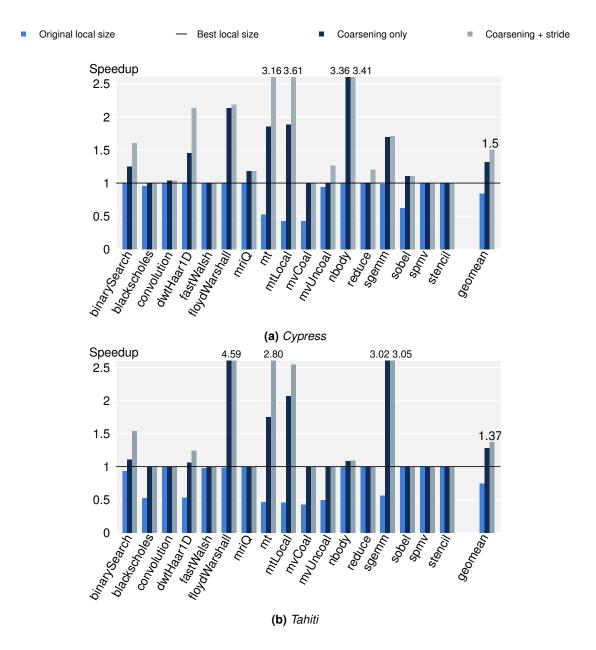

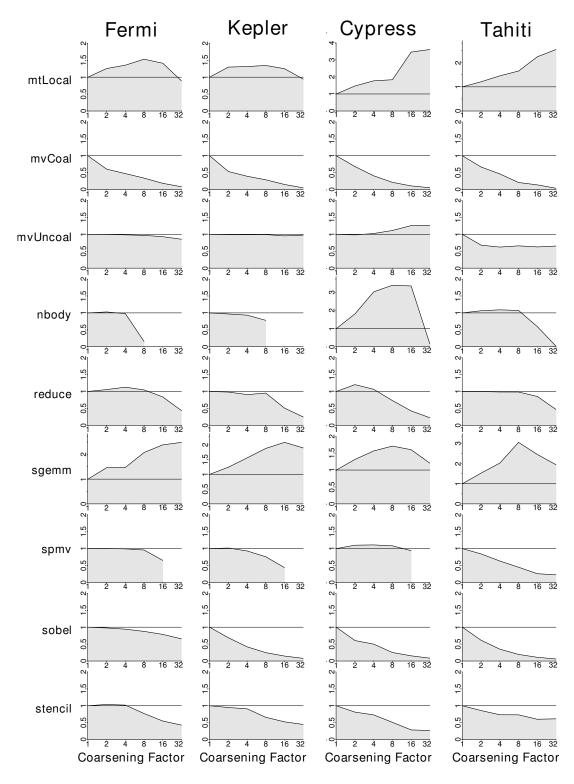

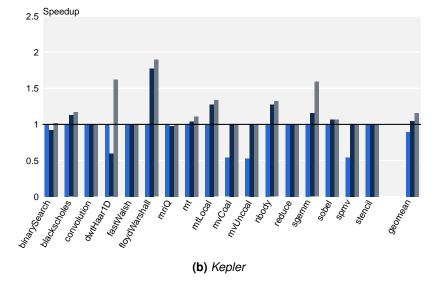

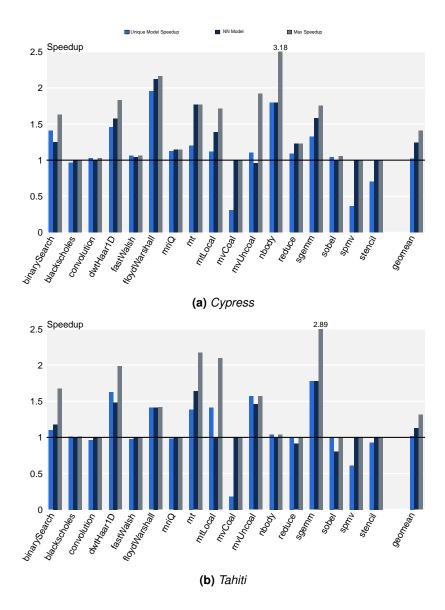

|   |      | 5.4.1 Speedups                                     | 68 |

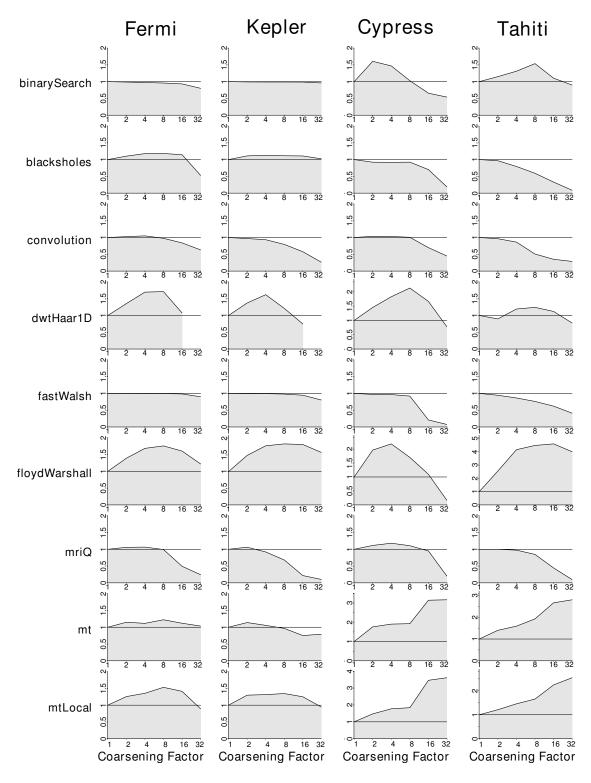

|   |      | 5.4.2 Effect of Coarsening Factor                  | 71 |

|   | 5.5  | Performance Analysis Methodology                   | 71 |

|   |      |                                                    | 71 |

|   |      | -                                                  | 75 |

|   | 5.6  |                                                    | 76 |

|   |      |                                                    | 76 |

|   |      |                                                    |    |

|   |      | 5.6.2 Nvidia <i>Kepler</i> GPU              |

|---|------|---------------------------------------------|

|   |      | 5.6.3 AMD <i>Tahiti</i> GPU                 |

|   |      | 5.6.4 AMD <i>Cypress</i> GPU 81             |

|   | 5.7  | Performance Counters                        |

|   |      | 5.7.1 Memory Loads                          |

|   |      | 5.7.2 Branches                              |

|   |      | 5.7.3 Cache Utilization                     |

|   |      | 5.7.4 Vector Instructions                   |

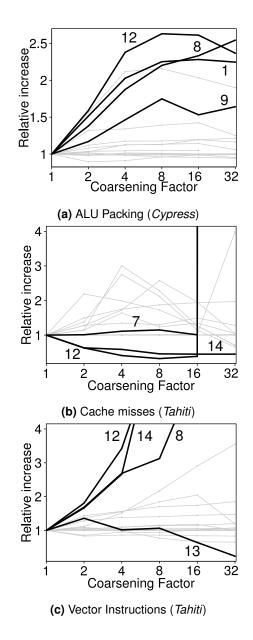

|   |      | 5.7.5 ALU Packing                           |

|   |      | 5.7.6 Instruction Cache Behaviour           |

|   | 5.8  | Summary                                     |

| 6 | Fast | Tuning of the Coarsening Transformation 84  |

|   | 6.1  | Introduction                                |

|   | 6.2  | Motivation                                  |

|   | 6.3  | Experimental Set-up                         |

|   |      | 6.3.1 Devices                               |

|   |      | 6.3.2 Coarsening Parameter Space            |

|   |      | 6.3.3 Benchmarks                            |

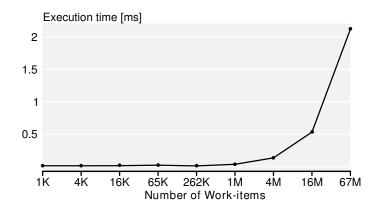

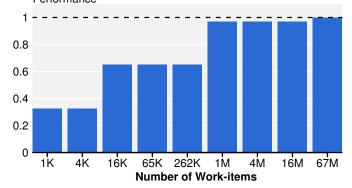

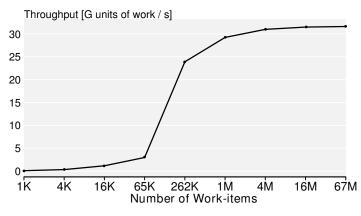

|   | 6.4  | Throughput and Hardware Saturation          |

|   |      | 6.4.1 Outliers Analysis                     |

|   | 6.5  | Throughput-Based Tuning                     |

|   |      | 6.5.1 Tuning Across Input Sizes             |

|   |      | 6.5.2 Throughput and Coarsening Factor      |

|   |      | 6.5.3 Throughput Based Input Size Selection |

|   | 6.6  | Results                                     |

|   |      | 6.6.1 Result Description                    |

|   | 6.7  | Summary                                     |

| 7 | Sele | ction of Coarsening Parameters 103          |

|   | 7.1  | Introduction                                |

|   | 7.2  | Motivation                                  |

|   | 7.3  | Experimental Set-up                         |

|   |      | 7.3.1 Parameter Space                       |

|   |      | 7.3.2 Benchmarks                            |

|   |      | 7.3.3 Devices                               |

|   | 7.4  | Optimisation Space Characterization         |

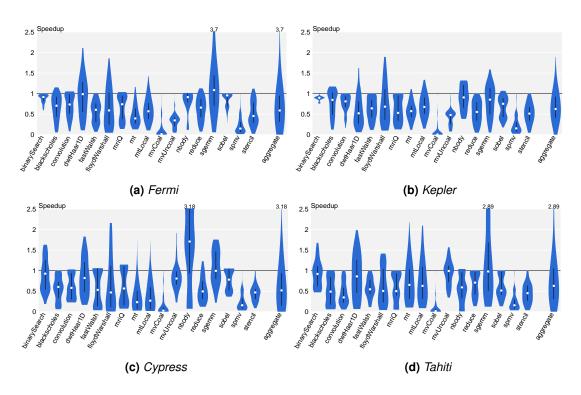

|   |      | 7.4.1 Distribution of Speedup               |

|   |      |                                             |

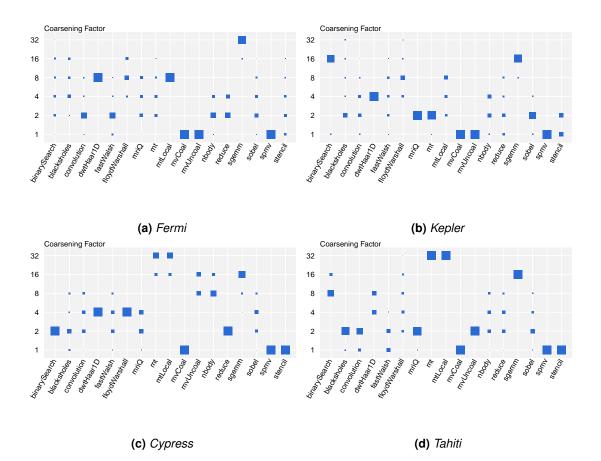

|   |     | 7.4.2   | Coarsening Factor Characterization                | . 108 |

|---|-----|---------|---------------------------------------------------|-------|

|   |     | 7.4.3   | Stride Factor Characterization                    | . 110 |

|   |     | 7.4.4   | Relationship between Coarsening Factor and Stride | . 112 |

|   |     | 7.4.5   | Cross-architecture optimisation portability       | . 113 |

|   | 7.5 | Stride  | parameter selection                               | . 115 |

|   |     | 7.5.1   | Performance Evaluation                            | . 115 |

|   | 7.6 | Neural  | Network Model Description                         | . 118 |

|   |     | 7.6.1   | Training                                          | . 118 |

|   |     | 7.6.2   | Neural Network Model                              | . 120 |

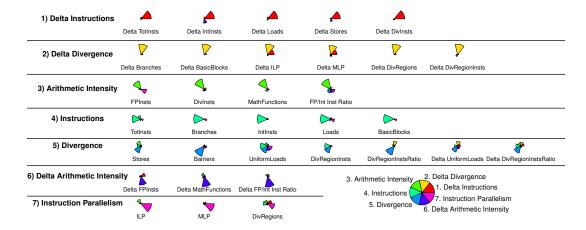

|   |     | 7.6.3   | Program Features                                  | . 120 |

|   |     | 7.6.4   | Candidate Features                                | . 121 |

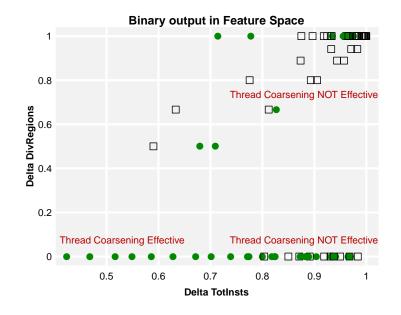

|   |     | 7.6.5   | Feature Selection                                 | . 122 |

|   | 7.7 | Model   | Evaluation                                        | . 124 |

|   |     | 7.7.1   | Unique-Factor Model Description                   | . 124 |

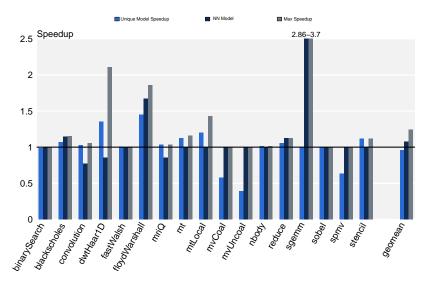

|   |     | 7.7.2   | Performance Evaluation                            | . 124 |

|   |     | 7.7.3   | Accuracy of prediction                            | . 127 |

|   |     | 7.7.4   | Neural Network Model Analysis                     | . 130 |

|   | 7.8 | Summ    | ary                                               | . 131 |

| 8 | Con | clusion |                                                   | 132   |

|   | 8.1 | Contri  | butions of the Work                               | . 132 |

|   |     | 8.1.1   | Compiler Analyses and Transformations             | . 132 |

|   |     | 8.1.2   | Performance Counters Analysis                     | . 133 |

|   |     | 8.1.3   | Fast Tuning of the Coarsening Transformation      | . 133 |

|   |     | 8.1.4   | Selection of Coarsening Parameters                | . 133 |

|   | 8.2 | Critica | ll Analysis                                       | . 134 |

|   |     | 8.2.1   | Compiler Analyses and Transformations             | . 134 |

|   |     | 8.2.2   | Performance Counters Analysis                     | . 134 |

|   |     | 8.2.3   | Fast Tuning of the Coarsening Transformation      | . 135 |

|   |     | 8.2.4   | Selection of Coarsening Parameters                | . 135 |

|   | 8.3 | Future  | Work                                              | . 135 |

|   | 8.4 | Summ    | ary                                               | . 136 |

| • |     |         |                                                   | 125   |

| Α |     |         |                                                   | 137   |

Bibliography

143

# Chapter 1

# Introduction

For decades the performance of computing processors has been improved by increasing clock speeds. The side-effect of this trend was the consequent increment of power consumption and operating temperatures. *"Power Wall"* is the term used to identify the impossibility to scale up processor frequency further due to heat constraints. The limits of frequency scaling became apparent to the broad public in 2004 when Intel stopped the development of two architectures: Tejas (the would-be successor of the Pentium 4) and Jayhawk. <sup>1</sup> These two processors were both designed for high operating frequencies. The computer architecture industry then aimed at lowering single core performance and integrating multiple cores on the same die. Heterogeneous devices have then been introduced with the goal of improving power efficiency. In this scenario, fully programmable graphics processors (GPUs) have become mainstream for solving highly parallel tasks. The application of GPUs for computational workloads has been called General Purpose computation on Graphics Processors (GPGPU). With respect to CPUs, GPUs offer much higher floating point performance per Watt, making them suitable for both embedded and high performance computing.

GPUs are radically different from CPUs. CPU cores are designed to minimise the latency of individual threads. GPUs, instead, are massively parallel machines that aim at minimising the latency of the application by instantiating thousands of parallel threads, thus maximising the throughput, *i.e.*, the number of threads terminating per unit of time. CPUs are mounted with a small number (usually less than 10) of powerful cores that aim at improving single-thread performance with branch predictors, reorder buffers and several levels of data and instruction caches. The primal way to improve performance on the CPU is by exploiting the maximum amount of instruction level parallelism (ILP) available. GPUs have instead a much larger number (thousands) of far simpler cores. Such cores are often aggregated hierarchically into clusters (called streaming multiprocessors by Nvidia). These clusters implement the logic to schedule threads onto their cores. To simplify the design of the architecture all the cores in

<sup>&</sup>lt;sup>1</sup>http://www.nytimes.com/2004/05/08/business/intel-halts-development-of-2-new-microprocessors.html

a cluster share the same instruction pointer, so that hardware threads running on a processor cluster execute in lockstep. GPU cores have a much larger register file with respect to CPUs, this is to enable the concurrent execution of a large number of threads. GPUs achieve high performance through the synchronized scheduling of multiple threads to hide memory latencies, this is called thread level parallelism (TLP). In summary, CPUs strive to keep their pipeline busy with instructions, while GPUs aim to keep their clusters of cores busy with threads.

The wide success of GPUs in delivering high performance for non-graphics applications has lead to the introduction in the market of many different hardware devices in a few years. As a result the field of GPU architecture has rapidly evolved: many vendors have come into play. Vendor diversity implied also diversity in the architecture and ISA designs.

Unfortunately, heterogeneity hinders code portability across devices. The first GPGPU programming frameworks to be introduced where Close To Metal by ATI/AMD (2006) [56] and shortly after CUDA by Nvidia (2007) [98]. Being developed by two different companies these two programming models were incompatible. A programmer that wanted to deploy code for the two architecture had to write the application twice.

In 2008 the Khronos consortium introduced a new GPGPU API and language called OpenCL [67]. This is the result of the efforts of multiple companies to define a cross-platform API for GPGPU. Being developed by a wide range of hardware vendors, the primal design goal of OpenCL is to ensure code portability, *i.e.*, a single program can successfully and transparently execute on devices of multiple manufacturers. This is a major productivity boost, allowing programmers to extensively reuse code.

The OpenCL API manages the GPU as an external accelerator and it is responsible for scheduling parallel work on the GPU. It can allocate buffers on the graphics memory and transfer data between the CPU and the GPU.

The efforts to define a portable standard fall short of achieving performance portability. This means that different devices require different optimisation techniques. Performance portability affects all the aspects of the computation: memory management, data transfers between CPU and GPU and compiler optimisations to apply to GPU code. For example, improving memory transfers between CPU and GPU must take into account the device-specific memory system. Software pipelining [58] can successfully improve performance for GPUs that do not share main memory with the CPU. The same transformation might have little or no benefit on systems that share main memory between CPU and GPU texture memory [138]. The relative performance of texture memory and texture caches with respect to main GPU memory changes across hardware vendors. Optimisation techniques that aim at adapting to the underlying hardware to extract the maximum performance are various and touch all the aspects of the computation.

In this work we focus on the performance portability of the compiler optimisation settings

for GPU code (called the *kernel* function). To achieve high performance in this context the programmer can either optimise code by hand for each device or rely on the compiler to perform aggressive optimisations. The first approach is impractical, since optimising parallel programs is extremely demanding. On the other side, the development of an optimising compiler for multiple architectures is a challenging task for the compiler engineer. The heuristics that control the transformations must be tuned for all the devices of interest. This type of tuning can by applied to high level transformations *e.g.* loop unrolling, tiling, fusion and fission. Back-end optimisations, instead, are inherently non-portable, our work does not deal with those.

To showcase our analysis and prediction techniques we use a compiler transformation specifically designed for a data parallel language: thread-coarsening. Thread-coarsening increases the amount of work performed by a single thread and, to preserve the semantics of the application, reduces the amount of threads concurrently running on the GPU. This is done by logically merging the computation of multiple threads together. By applying this transformation it is possible to reduce the overhead of redundant computation performed by the application across threads. Previous works on coarsening [138, 125] lack implementation in an optimising compiler and rigorous analysis of effects on performance. In this thesis we provide a complete implementation, analysis and a methodology to select parameters for the coarsening transformation that can improve the performance of OpenCL kernels on four GPU architectures.

## 1.1 Contributions

This thesis makes the following contributions:

- We provide implementation of the thread-coarsening compiler transformation. The transformation is implemented using the LLVM compiler infrastructure and it works on LLVM intermediate representation. The transformation makes sure to preserve high performance memory accesses by address remapping. We also present a tool that we call SymEngine that analyses GPU memory access patterns. The source code of our compiler passes is available as open-source [83, 84]. The design and the implementation of all the compiler passes are documented in chapter 4.

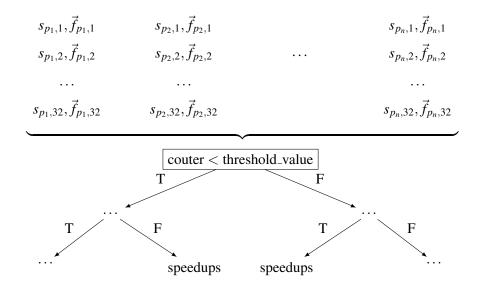

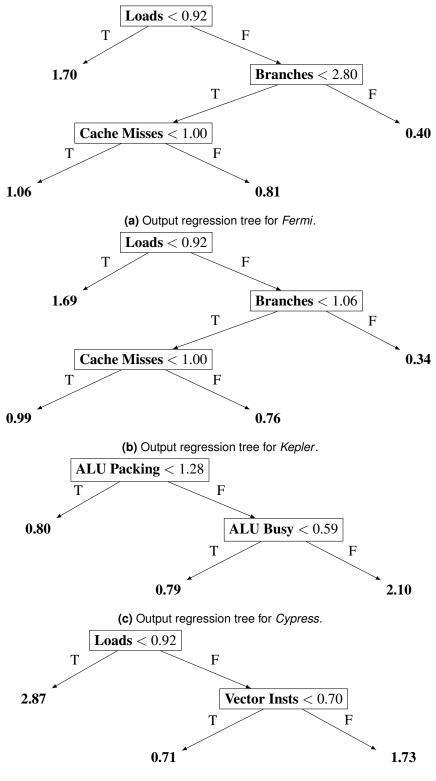

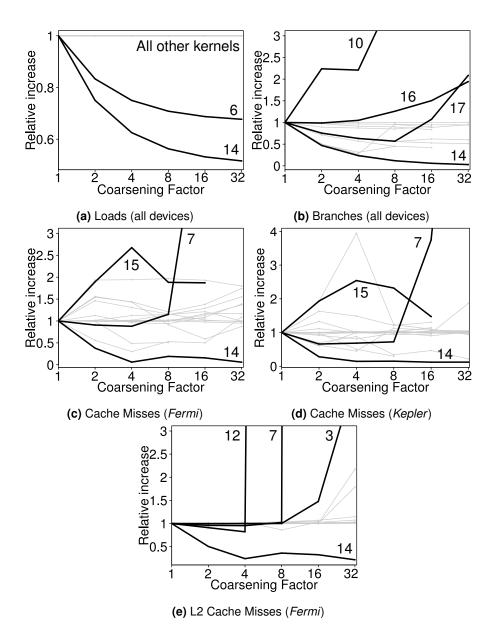

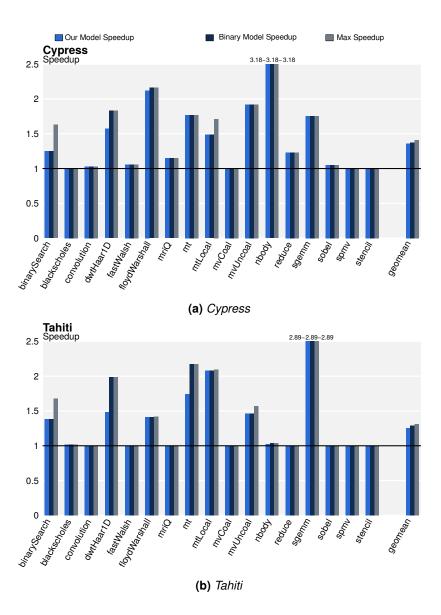

- 2. We show the performance improvements given by thread-coarsening across four architectures [85]. We show how hardware performance counters change when applying coarsening on four devices and we propose a technique based on regression trees to simplify the task of performance analysis. The trees automatically identify the counters that are affected the most by the transformation and correlate their run-time changes with execution speedup. This method is helpful in the identification of the root causes of performance differences among program versions. Chapter 5 presents this work.

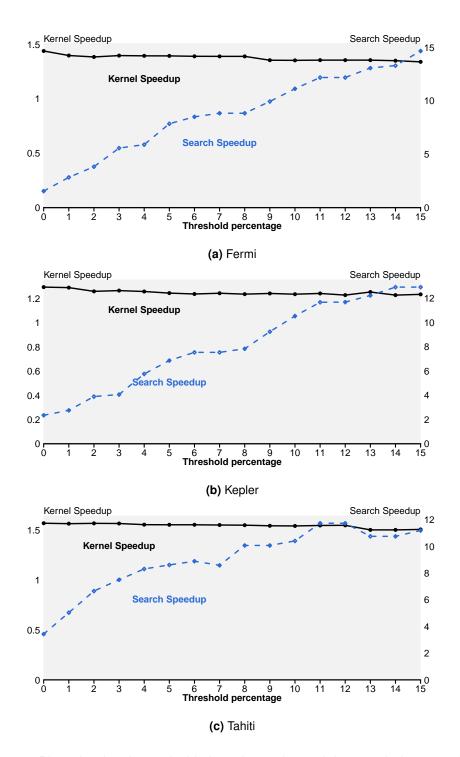

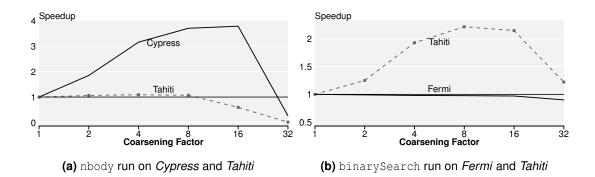

- 3. We study the impact of the problem input size on the performance given by threadcoarsening [87]. In particular we analyse how the best coarsening configuration changes across input sizes. We show that the best coarsening configuration remains the same for input sizes bigger than a threshold that is benchmark- and platform-specific. We call this threshold *saturation point*. We propose to leverage saturation to speedup iterative compilation. This study is reported in Chapter 6.

- 4. We developed a machine learning technique to attempt to predict the optimal coarsening factor for a given program and architecture [86]. We also present a heuristic to estimate the best thread-remapping policy to preserve the coalescing of memory accesses. Thus we improve over previous chapter by automatically selecting the coarsening factor and stride without the need of iterative compilation. The policy relies on the results of symbolic execution of the kernel code using our tool SymEngine. This work is described in chapter 7.

## 1.2 Thesis organization

This thesis is organized as follows:

- Chapter 2 provides the technical background needed to understand the remainder of the work. It includes: a description of GPGPU computing and OpenCL in specific, an overview of the architectural structure of Nvidia and AMD GPUs, we describe the LLVM compiler infrastructure and the relevant machine learning techniques employed in the thesis.

- **Chapter 3** presents the related work. It introduces and critically discuss prior work about relevant compiler transformations, performance modelling and optimisation for GPU, and the use of machine learning in compiler tuning.

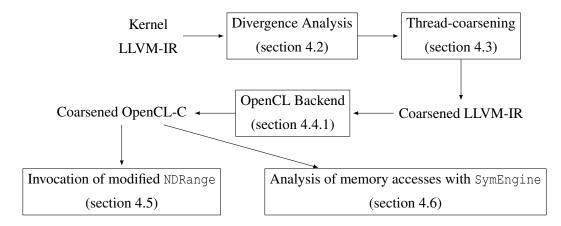

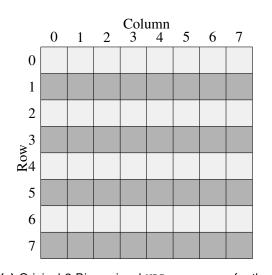

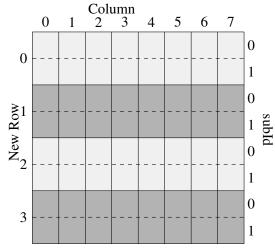

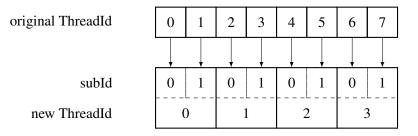

- **Chapter 4** describes the design and the implementation of thread-coarsening. It presents the design choices made in the construction of the compiler infrastructure, the implementation of divergence analysis, the coarsening transformation and the symbolic execution engine SymEngine for memory access pattern analysis.

- **Chapter 5** presents the results of performance analysis. It shows how coarsening affects performance of 17 GPGPU benchmarks on four GPU architectures. The chapter shows how regression trees are used to ease the task of cross-platform performance analysis relying on hardware performance counters.

- **Chapter 6** studies how the coarsening transformation affect run-time performance across multiple problem input sizes. It shows that the best coarsening configuration remains constant across problem sizes bigger than a lower-bound that we call minimum saturation

point. We describe how to exploit this property to speed up iterative compilation of thread-coarsening.

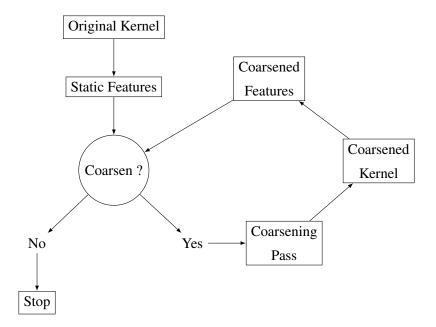

- Chapter 7 describes the prediction technique used to look for the best coarsening factor and stride factor. We employ a neural network to decide whether to apply coarsening or not. By iteratively querying the network we show that is possible to improve performance on the four architectures taken into account. We also describe our heuristic to remap threads so to preserve coalescing of memory accesses.

- **Chapter 8** concludes the thesis by summarising the contributions, the limitations and by describing possible future direction of research.

# **Chapter 2**

# Background

This chapter presents the relevant technical background needed to understand the remainder of the thesis. Section 2.1 introduces the most important concepts of the OpenCL programming language. Section 2.2 gives an overview of hardware features of Nvidia and AMD GPUs. Section 2.3 describes the LLVM compiler infrastructure. Section 2.4 explains how we collected hardware performance counter on Nvidia and AMD GPUs. Section 2.5 lists the benchmarks that we used for experiments in our work. Section 2.6 presents the machine learning techniques that we used: regression trees, neural networks and principal components analysis. Section 2.7 describes how we evaluate the performance of our machine learning methods. Section 2.8 concludes the chapter.

## 2.1 OpenCL

OpenCL [67] is the standard cross-platform data parallel programming model for multi-core hardware. The OpenCL specification is extremely flexible, giving vendors the possibility to support many different types of devices:

- Multicore CPUs, e.g. Intel i7 or ARM Cortex family.

- Graphics Processors:

- Discrete GPUs (the CPU and the GPU have different physical memories), *e.g.* Nvidia GTX, Nvidia Tesla, AMD Radeon

- Integrated GPUs (the CPU and the GPU share the same physical memory), *e.g.* ARM Mali, Intel HD series, AMD Kaveri APUs.

- Accelerators, e.g. Xeon Phi.

An OpenCL application compliant with the standard is guaranteed to correctly execute on any of these devices. This improves the productivity developers who can write an application

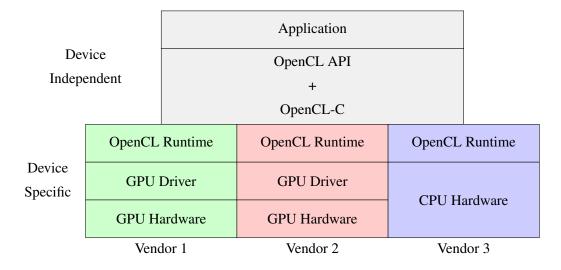

**Figure 2.1:** OpenCL abstraction layers. A single application can be deployed on multiple platforms.

once and run it to many devices. Figure 2.1 describes the OpenCL abstraction layers, clearly identifying the portable and non-portable layers of the stack. In the figure, the OpenCL runtime is a library that provides a C interface to schedule computation and to manage buffers on the computing device. In the case of GPUs these low-level tasks are performed by the device driver. Notice that the non-portable components are all provided by the hardware vendors, the application developer does not have to deal with device-specific issues to achieve the expected functionalities.

The OpenCL standard describes both an application programming interface and a programming language called OpenCL-C. OpenCL programs are made of two components: a *host* program written in C/C++ which run on the CPU and a *device* program written in OpenCL-C.

**Host code** The host code is a C program that implements the main functionalities of the application. It uses the OpenCL API functions to schedule the compute-heavy sections of the code to the parallel computing device available. The OpenCL application is initialized with the creation of a Context, a container for the following data objects:

- Devices: set of available computing devices.

- Kernels: functions running on the parallel devices.

- Program Object: instance of the kernel function containing the code compiled for the target device.

- Memory Objects: device memory buffers used to communicate with the host.

Figure 2.2: Example of an OpenCL kernel written in OpenCL-C.

All these components are created by the programmer when setting up the computation. The typical work-flow of an OpenCL application is the following:

- 1. Select the computing *platform* to use, a platform is a collection of devices from the same hardware vendor.

- 2. Create a *context* for the chosen platform.

- 3. Select a computing device from the ones available for the chosen platform.

- 4. Create the *command queue*. The queue is responsible for sending commands to the device, so to trigger data transfers and kernel invocations.

- 5. Create the *program* by compiling the kernel source code at run-time.

- 6. Allocate the buffers for data input/output on the device.

- 7. Transfer data from the host to the device.

- 8. Launch kernel execution

- 9. Transfer data from the device to the host.

- 10. Release all the OpenCL resources.

**Device code** The device code defines a *kernel* function, which is executed by the parallel device on each data point of the iteration space. The kernel is written in OpenCL-C, a subset of C99 with extensions to support multiple address spaces, vector data types and textures. Figure 2.2 shows an example of an OpenCL kernel that transposes the matrix input into output. Each parallel thread reads and writes a single element of the matrix. The kernel is compiled at run-time calling the API function clBuildProgram which invokes the vendor-specific compiler.

**Iteration space definition** Kernels are instantiated within a multi-dimensional index-space, specified at run-time, called NDRange space. A thread executing the kernel function in the NDRange space is called a *work-item*. Each work-item is uniquely identified by a tuple called the *global-id*. Work-items are associated to the cores in *work-groups* whose size is specified at the kernel launch time. Each work-group is identified by a *group-id*. Within work-groups work-items are identified by *local-ids*. The following list specifies all the names we use to identify work-items, work-groups and their sizes. We will use the same notation throughout the thesis.

- NDRange space size:  $(G_x, G_y)$

- Size of each work-group:  $(S_x, S_y)$

- Number of work-groups:  $(W_x, W_y)$

- Work-item global indexes:  $(g_x, g_y)$

- Work-group global indexes:  $(w_x, w_y)$

- Work-item local indexes, inside the work-group:  $(l_x, l_y)$

The following formulas correlate together the work-item identifiers and the sizes of the iteration space:

- $(g_x, g_y) = (w_x \cdot S_x + l_x, w_y \cdot S_y + l_y)$

- $(W_x, W_y) = (G_x/S_x, G_y/S_y)$

- $(w_x, w_y) = ((g_x s_x)/S_x, (g_y s_y)/S_y)$

For the reminder of the thesis we consider only one- and two- dimensional kernel. We map direction 0 to the *x* coordinate, while direction 1 to *y*.

#### 2.1.1 Device abstraction

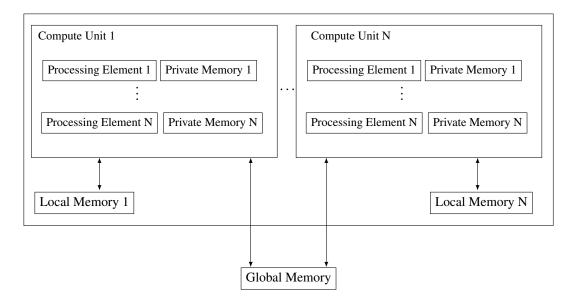

In order to support a wide range of devices the OpenCL standard provides a high level abstraction of the hardware. Figure 2.3 visualizes the abstract representation of an OpenCL device. A parallel device is made of multiple *compute units* each containing several *processing elements* (PE). Threads are scheduled in work-groups: all the work-items in work-group are associated to a single compute unit. The individual work-items are then executed by the processing elements. Each PE has a segment of private memory, not visible to the other processing elements. All the PEs in a compute unit share a piece of low-latency memory called *local memory*. Without atomic instructions the only way for work-items to safely communicate among each other is

**Figure 2.3:** Abstract representation of a parallel computing device according to the OpenCL standard.

through local memory. Writes to local memory are guaranteed to be visible by the other workitems in a work-group only after the invocation of a synchronization function called barrier. Since work-items can communicate through local memory and local memory is private for a compute unit, work-groups can not be migrated across compute units. Finally all the compute units have access to *global memory*. This is where input/output buffers for host/device communication are allocated. The OpenCL memory model is relaxed: the memory state visible by one work-item is not guaranteed to be the same across work-items. This implies that, for instance, writes to global memory are guaranteed to be visible to all the work-items only at the termination of the kernel.

In summary, for the remainder of the thesis and in particular for the coarsening transformation it is important to remember the following properties of the standard:

- Thread synchronization is possible only within the work-items of a work-group with the barrier function.

- Communication between the host and the device is possibly only through buffers in device memory. Pointers to these buffers must be passed to the kernel function as parameters.

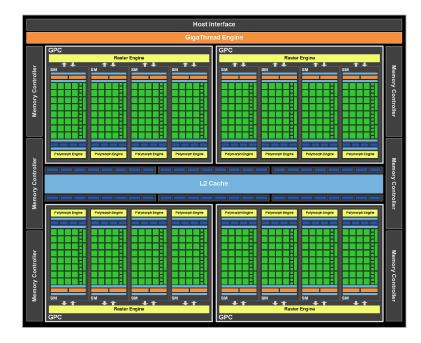

Figure 2.4: Schematic representation of the Fermi GF100 architecture. Taken from [100]

## 2.2 GPU Architecture

This section presents the hardware characteristics of modern Nvidia and AMD GPU architectures.

### 2.2.1 Nvidia

In this section we present the structure of the Nvidia Fermi Architecture [100]. In particular we focus on the version named GF100.

The Nvidia Fermi architecture is the successor of the Tesla architectures, which was the first architecture by Nvidia to support unified shader-cores (see section 3.1 for an overview of GPU hardware). Fermi features scalable and reusable graphics cores. A variable amount of cores can be employed at design time to match the performance needs of the device. Figure 2.4 presents an overview of the architecture. The GPU is organized in Graphics Processing Clusters which contain multiple Streaming Multiprocessors (SMs). Work scheduling happens in a hierarchical way, the *Giga Thread Engine* is responsible for the scheduling of work-groups to the SMs, while the per-SM *Warp Scheduler* schedules batches of threads (see section 2.2.1). To ensure high bandwidth GF100 has six memory controllers, an L2 cache shared among all the cores and private configurable L1 caches.

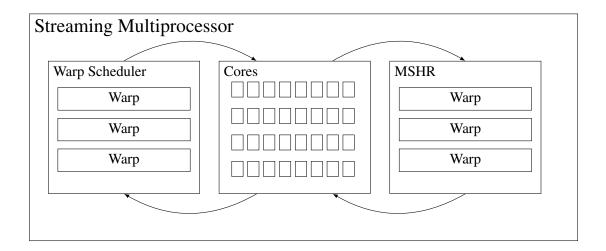

**Streaming Multiprocessor** Streaming Multiprocessors group together 32 CUDA cores, see figure 2.5. Threads are grouped into batches of 32 (called warps) which run concurrently on the cores of the SM. Threads in a warp execute in lock-step, *i.e.*, they share the same program counter, meaning that they all execute always the same instruction. This execution model is called SIMT (Single Instruction Multiple Threads): many threads execute a given instruction at the same time. This methodology is effective in reducing the overheads associated with instruction issue and decode. Each SM can support up to 48 warps concurrently. Mapping the Nvidia notation to the OpenCL standard definitions, a CUDA core corresponds to a *processing element*, while a SM corresponds to a *compute unit*.

**Warp Scheduler** Each SM has two warp schedulers. This allows two instructions coming from different warps to be issued and executed concurrently. A schematic representation of the scheduling of warps is given in figure 2.6. Warps in a work-group associated to a SM are placed in a ready queue and sent to execution to the computing cores in round-robin fashion. When threads stall due to a L1 cache miss rate they are placed in a waiting queue, the *Miss Holding Status Register*. When the data comes from memory the warp in the MSHR waiting for that data is reissued for the write-back stage.

**Local Memory and Caches** Each core is equipped with local memory. Local memory is used as L1D cache and as a programmable scratch pad. See section 2.1.1 for description and uses of local memory. L1 cache and local memory serve opposite roles. Local memory is designed to improve memory accesses for applications with regular and predictable access pattern. L1 cache, instead, improves accesses for irregular algorithms where data addresses are resolved only at run-time. GF100 streaming multiprocessors have 64KB of on-chip memory, 48KB for L1 cache and 16KB for local memory. GF100 also has a 768 KB L2 cache shared among all the cores of the GPU.

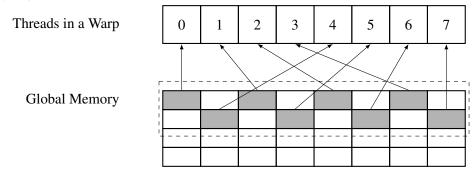

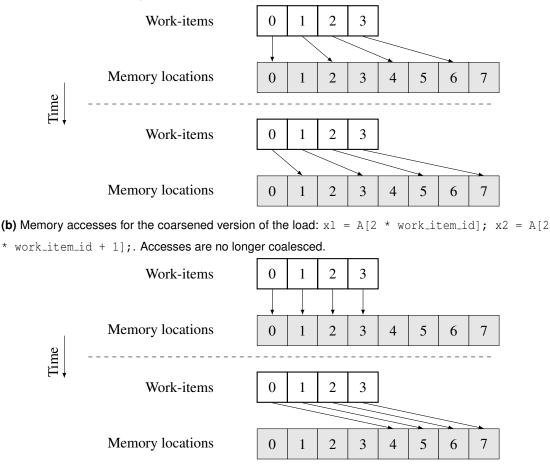

**Coalescing of Memory Accesses** An important concept for the optimisation of GPU applications is the coalescing of memory accesses. On GPUs the best memory pattern is achieved when consecutive work-items in a warp access consecutive memory locations. This is called a *coalesced access*. When a warp makes a memory request, say a float (4 Bytes) per thread, data has to be fetched from main memory to the private L1 cache of the core. The size of a transaction from main memory to the cache is equal to a cache line, 128 Bytes. So, if all the addresses requested by the warp fall in the same cache line the request can be serviced in a single transaction. In this case, all the data brought in the cache is used with no waste of bandwidth. This case is depicted in figure 2.7a. If instead, the addresses requested by the threads are scattered in memory (*i.e.*, they are not consecutive for consecutive threads) multiple transactions are needed to service the request. Thus, multiple lines have to be fetched into the

| SM     |          |            |          |                  |           |                                             |

|--------|----------|------------|----------|------------------|-----------|---------------------------------------------|

|        | Ir       | nstructio  | on Cach  | е                |           |                                             |

| War    | p Sched  | uler       | War      | p Schedu         | ıler      |                                             |

| Di     | spatch U | nit        | Dis      | spatch Ur        | nit       |                                             |

|        | +        |            |          | +                |           |                                             |

|        | Registe  | er File (3 | 82,768 x | 32-bit)          |           |                                             |

| +      |          | +          | +        | LD/ST            | +         |                                             |

| Core   | Core     | Core       | Core     | LD/ST            | SFU       |                                             |

| Core   | Core     | Core       | Core     | LD/ST            |           |                                             |

|        |          |            |          | LD/ST            | $\square$ |                                             |

| Core   | Core     | Core       | Core     | LD/ST<br>LD/ST   | SFU       |                                             |

| Core   | Core     | Core       | Core     | LD/ST            | 550       | CUDA Core                                   |

| Core   | Core     | Core       | Core     | LD/ST            |           | Dispatch Port                               |

| Core   | Core     | Core       | Core     | LD/ST            |           | Operand Collector                           |

|        |          |            |          | LD/ST            | SFU       |                                             |

| Core   | Core     | Core       | Core     | LD/ST            |           | FP Unit INT Unit                            |

|        |          |            |          | LD/ST            |           |                                             |

| Core   | Core     | Core       | Core     | LD/ST            |           | Result Queue                                |

|        |          |            |          | LD/ST<br>LD/ST   | SFU       |                                             |

| Core   | Core     | Core       | Core     | LD/ST            |           | (b) Schematic representation of a CUDA Core |

| 00000  | Inf      | erconne    | ct Netwo | rk               |           |                                             |

| ****** | 64 KB SI |            |          |                  |           |                                             |

|        |          | Uniform    |          |                  |           |                                             |

| Tex    |          | Tex        | Tex      |                  | Гех       |                                             |

|        |          | Texture    | Cache    |                  |           |                                             |

|        | F        |            | h Engine | )                |           |                                             |

| Verte  | x Fetch  | Tesse      |          | Viewp<br>Transfe | ort       |                                             |

|        | Attribu  | te Setup   | Stream   |                  |           |                                             |

|        |          | •          |          |                  |           |                                             |

(a) Schematic representation of a Streaming Multiprocessor.

**Figure 2.5:** Schemas of an Nvidia Streaming Multiprocessor and a CUDA Core. Both figures are taken from [100].

**Figure 2.6:** Schematic representation of the stages of warp scheduling for an Nvidia streaming multiprocessor. The arrows represent the flow of warps in the functional units.

cache. Only part of the data brought in the cache is going to be actually used by the threads. This type of accesses are called *uncoalesced* and must be avoided as much as possible. This case is depicted in figure 2.7b. Similar concepts apply for AMD graphics hardware.

**Compiler Toolchain** Along with GPU hardware Nvidia ships to developers a library to compile and execute OpenCL and CUDA programs. This library contains a proprietary compiler that translates OpenCL programs to an intermediate representation called PTX (Parallel Thread Execution) [4]. PTX is then further translated by a backend compiler into SASS: Nvidia assembly format.

### 2.2.2 AMD

In this thesis we worked with two AMD architectures, the first one is called *TeraScale* and the second one *Graphics Core Next*. These two are radically different.

### 2.2.2.1 TeraScale

The Terascale architecture [94] is the second one from AMD to ship a unified graphics core, the first one was C1/Xenos<sup>1</sup>. TeraScale manages the massive parallelism grouping threads in batches of 64, called *wavefronts*. The most distinctive characteristic of TeraScale are its 5-wide VLIW cores. They offer high performance for graphics computation and for matrix operations. This architecture has two main limitations. The first one is that instructions have to be statically scheduled by the compiler to fill the VLIW slots. This is a hinders the performance of general purpose workloads, where branches and unpredictable outcomes are more likely to happen

<sup>&</sup>lt;sup>1</sup>http://www.beyond3d.com/content/articles/4/2 (June 2005)

| Threads in a Warp | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-------------------|---|---|---|---|---|---|---|---|

|                   |   |   |   |   |   |   |   |   |

| Global Memory     |   |   |   |   |   |   |   |   |

|                   |   |   |   |   |   |   |   |   |

(a) Coalesced access to memory. Notice that the touched locations are aligned and contiguous. This memory request can be serviced in one transaction.

(b) Uncoalesced access to memory. The touched locations are scattered. This memory request is serviced in two distinct transactions.

**Figure 2.7:** Examples of coalesced and uncoalesced memory accesses. Each row of the memory cells corresponds to a cache line. The grey squares represent memory locations that are touched by a thread in the warp. The dashed rectangle represents all the data fetched from main memory to the private caches. Notice that in the uncoalesced case the amount of data touched by the warp is the same of the coalesced one, but the total amount of data transferred is the double.

than in graphics workloads. The second limitation lies in the limited parallelism available in the register file. It is not possible to schedule two consecutive ALU instructions, wavefronts have to be interleaved to mitigate this problem. These issues were addressed in the design of the next architecture: Graphics Core Next.

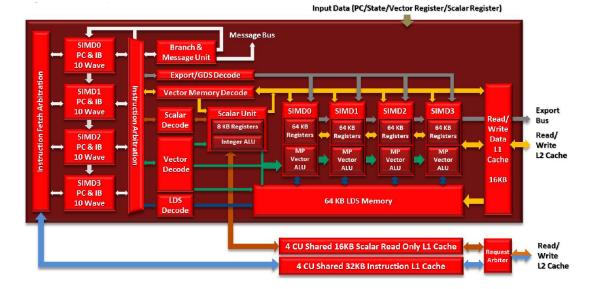

#### 2.2.2.2 Graphics Core Next

The most recent AMD architecture is called Graphics Core Next [7, 31, 9] and it is a complete redesign over TeraScale. It implements an entirely different ISA, which is more amenable for computational workloads.

**Compute Unit** Compute Units (CU) are the main processing components of the GCN architecture. A GPU is mounted with a certain amount of CUs depending on its design require-

**Figure 2.8:** Schematic Representation of the GCN architecture. Notice the four SIMD vector units and the scalar unit. Figure taken from [8]

ments and its performance budget, the typical number is 32. Each CU contains 4 SIMD units, called processing elements in the OpenCL parlance. These SIMD units execute the bulk of the computational work. Each SIMD Unit executes simultaneously one instruction from 16 work-items. The GPU scheduler can assign up to 10 wavefronts to each SIMD Unit, therefore they will execute instructions from different wavefront, possibly coming from different applications. The possibility to dynamically schedule work is a significant improvement in flexibility over the TeraScale architecture. The CU schedules work for one SIMD Unit at the time (over the four available) in round-robin fashion. Each CU is equipped with a scalar unit, used to manage conditional branches and to generate the target addresses of jumps. Figure 2.8 shows the architecture of a compute unit.

**Memory System** Each CU has a private scratch-pad memory called Local Data Share. The data cache hierarchy is organized as follows: L1 is 16KB, 4-way set associative with lines of 64 Bytes using the Least-Recently-Used replacement policy. Note that to achieve memory coalescing the memory accesses for a quarter of a wavefront (16 threads) must be all consecutive. GCN cores introduce another improvement over TeraScale: cache coherency. L1 is coherent for all the threads in a work-group and global coherency is achieved relying on L2. When a wavefront finishes execution or when a barrier statement is executed the private content of L1 cache is written L2 and becomes globally coherent. The last important characteristic of GCN cores is virtual memory support. This has been introduced to make GCN available for integrated GPUs as well, where CPU and GPU share the same physical memory.

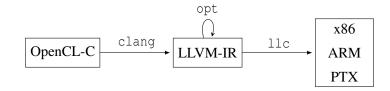

## 2.3 Compiler Infrastructure

This section presents the LLVM compiler we used to implement the coarsening pass.

### 2.3.1 LLVM

LLVM is an open-source compiler infrastructure initially developed by University of Illinois at Urbana Champaign [73]. The original design goal of LLVM is to provide a framework for aggressive code optimisation so to achieve high code quality keeping compilation times short. LLVM is a robust modern compiler designed in a modular way that provides a wide range of analysis and optimisations. In our experimental framework the OpenCL host code is compiled with GCC (the compiler of choice of the benchmarks) while only the device code *i.e.*, the kernel function, is compiler with LLVM.

**LLVM-IR** The most significant innovation introduced by LLVM is its intermediate representation, called LLVM-IR. LLVM has the following design choices:

- IR uses operations simple enough to be easily mapped onto real hardware.

- IR is portable, allowing generation of assembly code for a wide range of devices.

- IR is independent of both the operating system and the input language. The type system is generic enough to allow multiple languages to be easily mapped.

- IR supports metadata to enable optimisation transformations and generation of good machine code.

LLVM-IR is in static single assignment form [110, 29], this means that variables are assigned to in only one location. This simplifies the implementation of analysis and transformations such as constant propagation, dead code elimination and register allocation. LLVM programs are organized in *Modules*, which correspond to a translation unit of the original program. Modules contain a set of *Functions*. Functions are made of *Basic Blocks* which then contain IR *Instructions*. This organization reflects well the structure of C and C++ programs.

**Pass Manager** One of the most important components of the LLVM compiler is the *Pass Manager*. It schedules analysis and transformation passes. LLVM supports passes working on different IR structures: modules, functions and basic blocks. A function pass, for example, works on a function at the time and the pass manager makes sure to run it on all the functions in a module.

**Scalar Evolution** This thesis makes use of an important LLVM analysis called Scalar Evolution (SCEV). A SCEV of an LLVM value is a mathematical expression that describes its value during the execution of the program. It provides an abstraction over the actual LLVM instructions used to compute the value. The Scalar Evolution analysis is based on the work of [11, 145, 126, 127, 18]. SCEV expressions are constructed recursively using a set of basic types:

- Integer constant.

- Unknown value. For example an input parameter of the current function.

- Cast expression.

- Binary mathematical operation.

- N-ary operation.

- Add recurrence. This is used to represent the evolution of loop variables. This expression is made of a starting value, an operator and a increment value. At each iteration of the associated loop the current value of the expression is update using the operator and the increment.

The following expression is an example of a SCEV expression for the computation of the load address for transposeMatrix kernel (figure 2.2): ((4 \* ((%width \* %call) + %call1))+%input). The values %width, %call and %call1 are local function variables, while %input is the base pointer of the input buffer. SCEV expression can be rewritten and simplified [126] thus to easily compare the values of different variables. Scalar Evolution works effectively for integer computations, this makes it a good candidate for the analysis and the transformation of loop iteration variables memory addresses. The Scalar Evolution pass fails in analysing computation which depend on conditions evaluated at run-time, for example the trip-cont of a loop iterating a NULL-terminated linked list. More details on Scalar Evolution can be found in [48].

**LLVM and OpenCL** Thanks to the flexibility of the compiler it is relatively easy to map OpenCL constructs to LLVM-IR. Kernel functions in a module are listed in the metadata section, which can be read by all the passes. Vector data types are natively supported by LLVM-IR. Finally, memory address spaces (*e.g.* the ones identified by the keywords \_\_local and \_\_global) can be simply represented using the addrspace keyword.

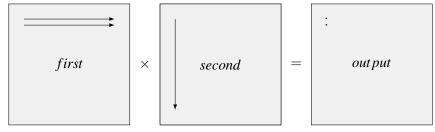

**LLVM Tools** LLVM has been designed in a modular way. The front-end, called clang, transforms the input language, in our case OpenCL-C, into LLVM-IR. The opt tool invokes the pass manager to schedule optimisation passes on the IR. Finally llc lower LLVM-IR to the target. The whole process is summarized by figure 2.9.

**Figure 2.9:** LLVM compilation stages. clang (the front-end) generates LLVM-IR, which is optimised by opt. llc lowers the IR to the target assembly language.

### 2.4 Hardware Performance Counters

Our work makes extensive use of profiler counters. In particular, chapter 5 presents a methodology to quickly relate changes in the value of performance counters with changes in the performance of the application. Here we present how we collected counters on Nvidia and AMD devices. The available counters reflect the architectural configuration of the device and differ across vendors and generations.

**Nvidia** The Nvidia profiler ships with the OpenCL SDK library, it is enabled by setting the environmental library COMPUTE\_PROFILE to 1 before the invocation of the executable. Tables A.1, A.2, A.3 and A.4 in Appendix A list the available counters for an Nvidia GTX 480 and for an Nvidia Tesla K20c. In these tables we only report the counters we collect. We ignore texture memory counters, since the benchmarks we use do not use this type of memory. These two devices are used in the experiments of chapter 5. Nvidia counters are highly accurate giving information about all the aspects of the computation. Nvidia hardware limits the execution time of profile runs by collecting counters only on one of the cores of the GPU. Therefore, to obtain a total estimate of the profiler values the output values have to be post-processed, according to this formula:

$$Thread\_ratio = \frac{G_x \cdot G_y}{thread\_launched}$$

(2.1)

$$Counter\_value = profiler\_counter \cdot thread\_ratio$$

(2.2)

Where *thread\_launched* is a counter recording the number of hardware threads that are actually profiled by the Nvidia profiler.  $G_x$  and  $G_y$  identify the x and y dimensions of the NDRange thread space.

**AMD** The AMD profiler is an executable called sprofile. It takes in input the name of the OpenCL executable and outputs instruction counts for each kernel in the application. Tables A.5 and A.6 in Appendix A list the available counters for an AMD HD5900 and for an

| Source     | Program name  |

|------------|---------------|

| AMD SDK    | binarySearch  |

| Nvidia SDK | blackscholes  |

| AMD SDK    | convolution   |

| AMD SDK    | dwtHaar1D     |

| AMD SDK    | fastWalsh     |

| AMD SDK    | floydWarshall |

| Parboil    | mriQ          |

| AMD SDK    | mt            |

| AMD SDK    | mtLocal       |

| Nvidia SDK | mvCoal        |

| Nvidia SDK | mvUncoal      |

| AMD SDK    | nbody         |

| AMD SDK    | reduce        |

| Parboil    | sgemm         |

| AMD SDK    | sobel         |

| Parboil    | spmv          |

| Parboil    | stencil       |

Table 2.1: OpenCL applications used as benchmarks in this work.

AMD Tahiti 7970. Notice that the counters exposed by the AMD profiler are fewer an much less precise than the one given by Nvidia.

## 2.5 Benchmarks

This section presents the benchmark programs that we used in this work.

Table 2.1 lists the OpenCL programs that we used in out experiments. We selected these kernels from the AMD SDK, Nvidia SDK and Parboil benchmarks suites. For the *Parboil* benchmarks we used the *opencl\_base* version. In the benchmarks selection process we avoided programs with features that our coarsening pass does not support, such as atomic instructions or texture memory. We also selected benchmarks that are easy to parametrize. In particular, we changed the C/C++ host code so to be able to change freely the work-group size. In our experiments we used various problem input sizes for the benchmarks, these are specified in each technical chapter.

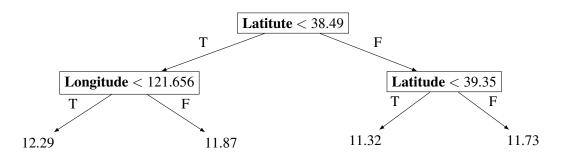

**Figure 2.10:** Example of a regression tree. The tree maps geographical locations (**Latitude** and **Longitude**) to house prices (the values in the leaf nodes). Example taken from: http://www.stat.cmu.edu/ cshalizi/350/lectures/22/lecture-22.pdf

## 2.6 Machine Learning

This section presents the relevant statistical techniques used in this thesis. Machine Learning is the field of computer science that develops algorithms that can improve with experience over time. This technique is usually applied to model data and to make predictions about it. In this thesis we apply supervised learning techniques. Supervised learning has the task of determining an unknown function from labelled data. Data used for training the statistical model comes in pairs  $\langle \mathbf{x}, y \rangle$ , one element of the pair is the set of features describing the data point (**x**), while the other element is the value of the unknown function:  $\mathbf{x} \rightarrow y$  and be able to predict the value of y for a new data point. In the remainder of the section we describe the characteristics of two techniques we used in the thesis: Regression Trees and Neural Networks.

#### 2.6.1 Regression Trees

Regression problems deal with output responses *y* having real values. Regression trees [109] attempt to solve these problems by splitting the input domain **x** in smaller regions and fitting a simple model for each region. The recursive split of the input space is represented by a decision tree. The tree contains two types of nodes: internal nodes and leaves. Internal nodes represent a split in the input space according to one dimension with a comparison against a predefined value, *e.g.*  $x_i < threshold$ . Leaf nodes, instead, represent the prediction for the output variable in the given subregion of the space. This is usually performed averaging the response variable (*y*) in the given subregion. Figure 2.10 gives an example of a regression tree mapping geographical coordinates to house prices. Finding the optimal regression tree for a given space is NP-complete [97], therefore many different heuristics have been proposed in the literature. A typical approach is the following. The construction of the tree starts top-down, with the root containing all the training points. Various split points are evaluated for each

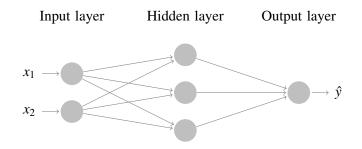

**Figure 2.11:** Example of a multi layer neural network. This network is fully connected with three layers: input, hidden and output

input dimension (feature). A pair input dimension / threshold point is selected if it maximizes a heuristic value computed on the two resulting sets. One of the heuristics used is often the difference between the variances of the two nodes with respect to the prediction.

Regression trees have advantages over other machine learning techniques: making predictions from a tree is fast and they are easy for a human to read (in particular the features most relevant for prediction appear close to the root of the tree). The most relevant drawbacks are: trees are not well suited for predicting highly irregular spaces and trees tend to overfit. This means that the resulting tree performs well on the training data but poorly on testing (unseen) data. Techniques such as early pruning are employed to mitigate this issue.

#### 2.6.2 Neural Networks

Artificial Neural Networks (NN) [19] are often used when the regression function to be learned is non-linear and highly irregular. NN are composed of multiple neurons organized in layers. Each neuron has a fixed number of input and output links to other neurons.

Figure 2.11 gives a schematic representation of a feed-forward neural network. Each edge in the topology graph is associated with a weight w, while the output of each neuron is computed according to this function:  $output(\mathbf{x}) = f(\sum_{i=1}^{n} w_i \cdot x_i)$ .  $x_i$  are the input values of the neuron. f is called the activation function an it usually has domain over the real numbers and range in [-1,1] or [0,1]. Examples of possible activation functions are: the hyperbolic tangent (f(x) = tanh(x)) and the logistic function  $(f(x) = \frac{1}{1+e^{-x}})$ .

The output function is learned by updating the weights for all the neurons so that the error between the output of the network and output value of the training data is minimised. The current state of the art learning algorithm is called *backpropagation*. The algorithm works iteratively. The weights are first initialized with random values. For each iteration the method computes the output of the network and compares it against the actual output value of the training data point. Then for each weight associated with the edges from the hidden layer to the output layer the algorithm computes  $\Delta w$  according to the formula  $\Delta w = \eta \cdot (y - \hat{y}) \cdot x_i^j$  ( $\eta$

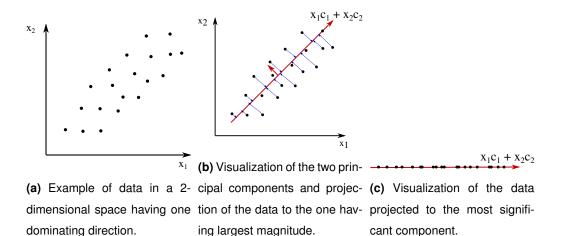

Figure 2.12: Three stages of PCA

is the learning rate and  $x_i^h$  is the value from the *j*-th hidden neuron to the *i*-th output neuron). It then computes the same delta for the weight between the input and hidden layers. Finally, update all the weights in the network using the deltas just computed. The algorithm stops when the error converges below a pre-defined threshold or a maximum number of iterations have been reached.

#### 2.6.3 Principal Components Analysis

Principal Components Analysis (PCA) [20] is a statistical technique widely used for dimensionality reduction. PCA is usually applied to feature spaces that are highly dimensional and contain redundant information. Redundancy comes from dimensions that are highly correlated with others, this means that they can be expressed as a linear combination of other dimensions. PCA removes redundancy in a highly dimensional space by projecting the available data onto the most representative directions. This can effectively improve the accuracy of predictive models.

Consider the data in figure 2.12a. It lays out in a two-dimensional space data having a strong distribution along a specific direction. PCA computes first the covariance matrix. This is determined computing the correlation factor between all dimension pairs of the data. The method then computes the eigenvalues and eigenvector for the covariance matrix. Figure 2.12b shows the eigenvectors scaled by the eigenvalue after they have been made orthogonal. The principal components are then the eigenvectors corresponding to the eigenvalues of greatest magnitude. In the example the principal component is given by the symbolic formula  $c_1x_1 + c_2x_2$ , where  $c_1$  and  $c_2$  are called *loadings*. PCA involves the determination of a threshold used to define what components to discard. The last step of the PCA algorithm Figure 2.12c is to project all the data onto the space of the selected principal components. This way the output data is defined in a different space, with smaller dimensionality and less redundancy than the

(b) After Varimax rotation one input dimension strongly contributes only to one output dimension.

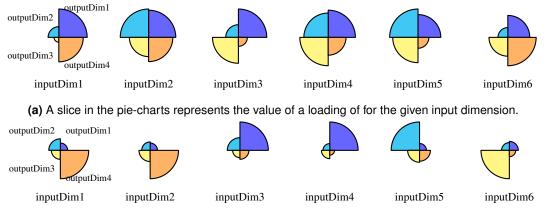

**Figure 2.13:** Visual representation of the value of loadings for a hypothetical space before and after Varimax rotation.

original space, and it still coveys similar amount of information.

**Varimax Rotation** One of the drawbacks of PCA is that the features of the transformed space are a complex linear combination of the original ones. It is often hard to identify the meaning of the new components and how they correlate to the original ones. In this context the Varimax Rotation can be of help [88].

Varimax Rotation rotates the output space in such a way that the resulting principal components have formulas having a large number of loadings set to 0 and a few (ideally only one) loadings set to large magnitude value. This enables the possibility to identify what directions of the input space strongly affect directions in the output space.

Figure 2.13 gives an example of the effects of Varimax rotation on a hypothetical space. Subfigures represents a pie-chart for each dimension of a hypothetical six-dimensional space D[1-6]. The application of PCA, in our example, shrinks the original space to a fourdimensional one. Each slice of a pie represent the relative contribution of the given input dimension to the four output dimensions in figure 2.13a. We can see that normally each feature strongly contributes to multiple output dimensions (for example the top right slice is large in area for dimensions 1,2,3,4). After the application of Varimax an input dimension strongly contributes to only one output dimension, see figure 2.13b. This property is particularly useful since it is now possible to label output dimensions (a new feature) with the name of the original direction (feature) that contributes to its value.

# 2.7 Performance Evaluation

#### 2.7.1 Performance Metrics

In the context of machine learning the metrics used to quantify the performance of a technique are usually the mean squared error for regression problems and accuracy and precision for classification problems. In the context of compiler optimisations, instead, the most important performance metric is execution time difference between the newly tested technique and a reference baseline for a run of the tested program. For this thesis we always use the execution time speedup to measure this difference. The speedup is defined as

$$speedup = \frac{t_{baseline}}{t_{new}}$$

(2.3)

Where  $t_{baseline}$  is the execution time of the program run with the configuration considered as baseline,  $t_{new}$  is the execution time of the same program run with the compiler configuration under exam. When aggregating speedups of multiple programs we use the geometric mean. In this work we always measure the effectiveness of our compiler techniques against the best attainable in our search space, the so called oracle. We thus compute the percentage of performance that we achieve. Since in our experiments the maximum speedup is always greater than one we compute performance percentage in the following way. If *speedup* is greater than 1:

$$performance\_percentage = 100 \cdot \frac{speedup - 1}{max\_speedup - 1}$$

(2.4)

If *speedup* is smaller than 1:

$$performance_percentage = 100 * (speedup - 1);$$

(2.5)

This is a stricter metric over the simple ratio  $100 \cdot \frac{speedup}{max\_speedup}$  since we only account for the speedup that we achieve *over the baseline*.

**2.7.1.0.1 Correlation** In this thesis we make use of the correlation coefficient to measure the similarity of two sets of data, these are usually predicted values and actual experimental data. Correlation measures the interdependence between two set of variables, in particular their linear relationship. Given two set of values *A* and *B*, the correlation coefficient is computed as:

$$corr(A,B) = \frac{cov(A,B)}{var(A) \cdot var(B)}$$

(2.6)

Where *cov* is the covariance between the two input sets and *var* is the variance of the input set. A positive correlation value means that when values in the *A* set increase values in the *B* increase as well, and vice-versa. Negative value of correlation instead means that when values in the *A* set increase values in the *B* set decrease. Values of 1 or -1 mean that data in set *A* can be transformed into data in set *B* with a linear transformation and vice-versa. A value of 0 means that there is no linear relationship between the two sets.

#### 2.7.2 Cross Validation

Machine learning techniques are evaluated by dividing the available labelled data into training and testing set. The model is then fitted on the training data and then evaluated on the testing set. This process is called *cross validation*. Rigorous performance evaluation prescribes not to draw conclusions about the performance of the model when evaluated on the training data. In this work we employ a specific version of Cross Validation called Leave one out. For the neural network model in chapter 7 we train the network on 16 of the 17 benchmark we use and we evaluate its performance of the 17th. We repeat this process 17 times, one for each test case.

# 2.8 Summary

This chapter presented the technical background necessary to understand the remainder of the work. We introduced the OpenCL language for programming graphics processors and we gave an overview of the main characteristics of Nvidia and AMD processors. We then described the LLVM compiler infrastructure, focusing on the components that we use in the implementation of the work. Finally we gave an overview of regression trees, neural networks and PCA, these are the machine learning techniques that we use to analyse the results of thread-coarsening.

Next chapter will give an overview of the academic publications related to this thesis.

# **Chapter 3**

# **Related Work**

This chapter reviews publications relevant for this thesis. Section 3.1 presents an overview of the evolution of graphics hardware, from fixed hardware functionalities to fully programmable processors. Section 3.2 describes the context of general purpose processing for GPUs, presenting its most important applications. Section 3.3 discusses the topic of performance analysis and modelling for GPUs. Section 3.4 presents prior works on loop optimisations for single-and multi-processors. These techniques have found new applications in the context of GPU programming. Section 3.5 introduces techniques for the optimisation of GPU programs. In Section 3.7 we give an overview the use of machine learning for compiler optimization. Section 3.8 concludes the chapter.

# 3.1 History of Graphics Processing

This chapter overviews the history of the design of graphics processors.

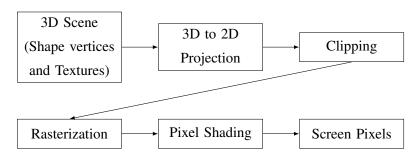

Graphics processors have been designed with the goal of quickly computing the colour of screen pixels when displaying a computer-generated image. Figure 3.1 gives a high level overview of the stages to display images on the computer screen starting from a representation of a 3D scene. This process is called *rendering*. The 3D scene is made of objects described in memory by a set of points and 2D images called textures. These points represent the vertices

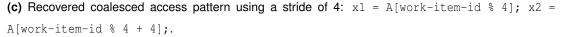

Figure 3.1: Overview of the graphics pipeline.

of triangles (called primitives) positioned on the surface of objects. Textures are images that represent the colour of the surface of objects. The first step of the pipeline is the projection of the 3D scene onto the 2D surface of the screen, transforming the world coordinates into screen coordinates. This projection is described by a 4x4 matrix. The second step is the removal of all the vertices that are invisible given the current orientation of the point of view in the 3D world. Rasterization is the process of determining which triangle in the scene covers a pixel of the screen. Finally pixels are coloured according to the colour of the triangle coving it and the position of the lights, this process is called shading.

**Fixed-Function Custom Hardware** Dedicated hardware for rendering has been proposed as early as the 1980s [27, 120]. These solutions we not parallel and had refresh times of the order of seconds or minutes. Massively parallel architectures were then introduced to take advantage of data parallelism inherent in the problem (the colour of each pixel can be determined independently of all the others) [44]. These where limited in scalability or in programmability, for example by fixing the number of cores to be able to manage a predefined number of pixels.

**The Triangle Processor** The work by Deering *et al.* [30] represents a major step forward in the design of graphics processors, introducing a system architecture used as a reference for years to come. The novel idea of this work is to split the rendering pipeline in two stages. The first stage, called *Triangle Processors*, works on one triangle at a time to determine the pixels that cover it. The second stage, called *Normal Vector Shader*, implements the shading according to the Phong model [107]. This organization of the work-flow has been implemented by all modern graphics processors. More in detail, the *Vertex Processor* (VP) works on the vertices of a primitive transforming its coordinates from world-space to screen-space, and also sets up colours and textures to be used by the fragment processor. The *Fragment Processor* (FP) interpolates the data associated with the vertices of the primitive to set each pixel of the appropriate colour. The two types of processors have different types of workloads, the VP works with high precision on mathematical operations, while the FP works on texture filtering (needed to map textures to primitives).

**Programmable Vertex Processor** The next big step in the definition of modern GPU architecture is the introduction of a programmable Vertex Processor [80]. The first GPU to ship this type of processor was the Nvidia GeForce 256 in 1999. This device addressed the need for a wider range of lighting effects. Graphics core are now programmable using the OpenGL [68] (from the Khronos Group) and Direct3D [93] (from Microsoft) frameworks. It is important to notice that usually graphic workloads are not evenly distributed among VPs and FPs. Scenes with a large number of small triangles are put pressure on VPs, while scenes with a small number of large triangles make the VPs almost idle while keeping the FPs under high utilization.

Any fixed choice of the number of FPs and VPs leads to workload imbalance and possible under-utilization of the device.

**Unified architecture** The solution to this problem came with the introduction of an unified architecture for the VPs and the FPs, so that vertex and fragment programs can be executed on the same processor. The main drawbacks of the unification comes from the increase in complexity in the processor logic and in power consumption. The first examples of this innovation came from the Nvidia Tesla Architecture [81] and ATI Xenos. The introduction of a single processor core on GPUs means having a fully-programmable highly parallel processors available for computation. Exploiting this architecture for non-graphics workload is the goal of GPGPU.

# 3.2 General Purpose Computing on GPUs

This section gives an overview of General Purpose computing on graphics processors.

Even though GPUs are designed for graphics workloads the massive parallelism they expose and their power efficiency make them an attractive candidate for general purpose computation. The first programming framework that exploited the capabilities of modern GPUs for General Purpose Computing is Brook [24]. The work introduces a programming model that abstracts the graphics hardware using streams, kernels and reductions. Data stored in memory is organized in *streams*, *i.e.*, a set of data that can be modified in parallel. Streams have a base type and a dimensionality. A *kernel* is a data parallel function which is executed for each element of the data stream. *Reductions* provide a data-parallel method to compute a single output value from a stream. From the implementations point of view Brook is composed of a compiler and a runtime library. The compiler translates Brook programs into Cg shaders [89] (a shading language by Nvidia) which are then translated to assembly by the vendor compiler. The runtime implementation lowers the programming model down to OpenGL and DirectX constructs.

In 2007 Nvidia introduced its solution for general purpose computing for GPUs: CUDA [98]. CUDA, like Brook, is made of a compiler and a runtime system. The compiler translates \_\_\_global functions into PTX assembly code and the runtime dispatches threads onto the GPUs. The runtime system is also responsible for the management of memory buffers on the GPU and the data transfers between the host CPU and the GPU.

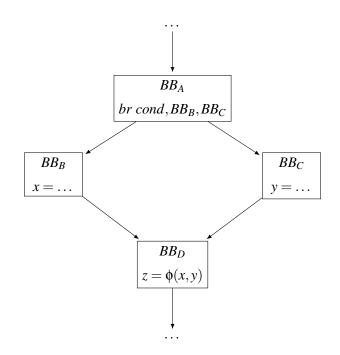

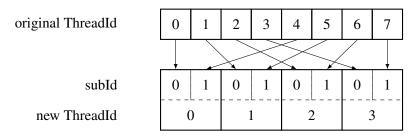

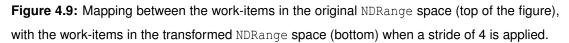

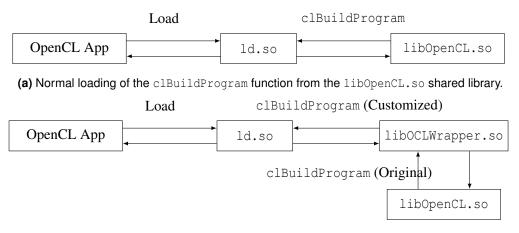

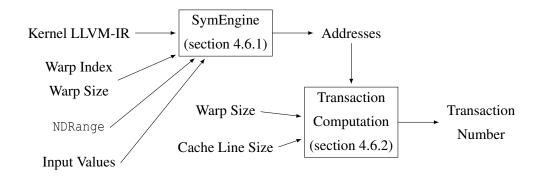

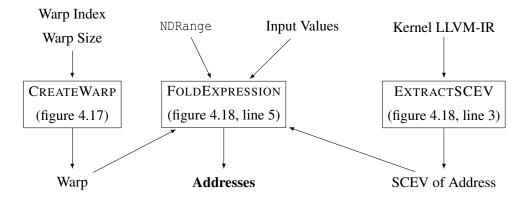

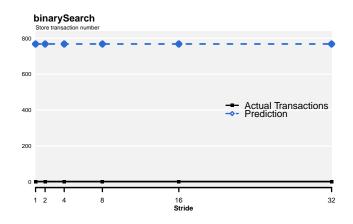

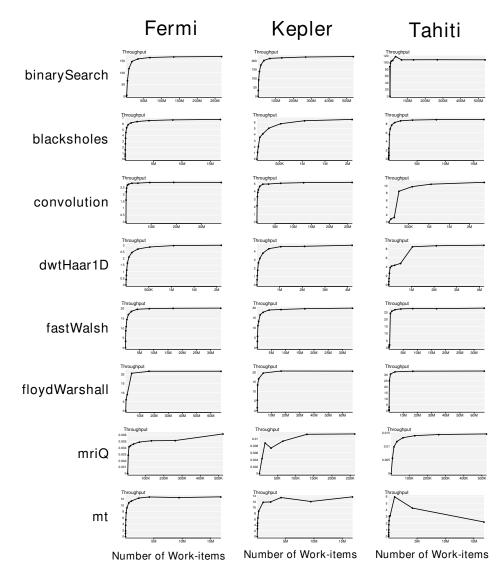

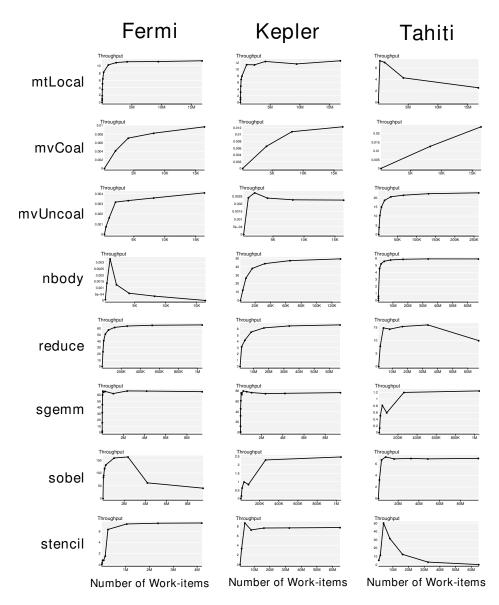

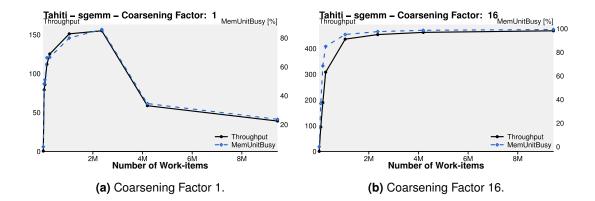

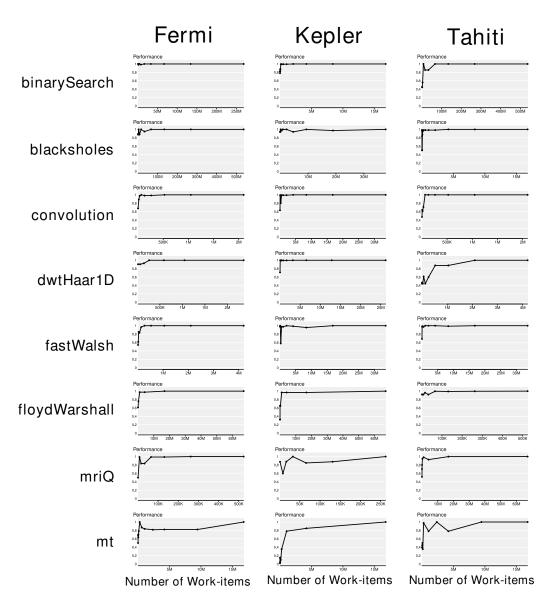

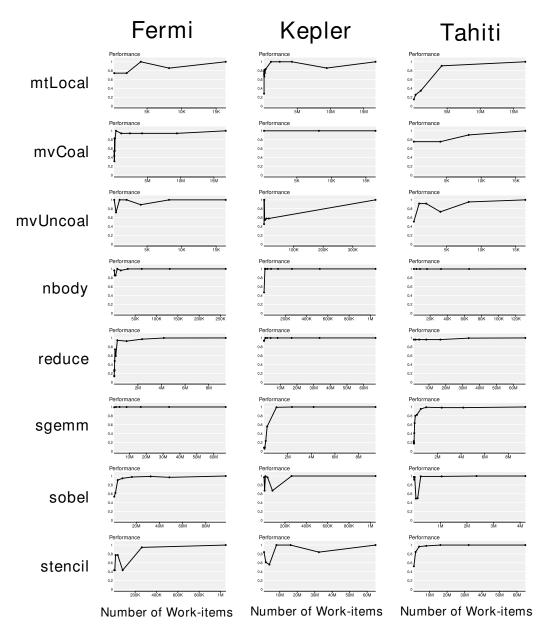

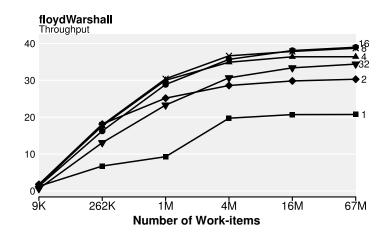

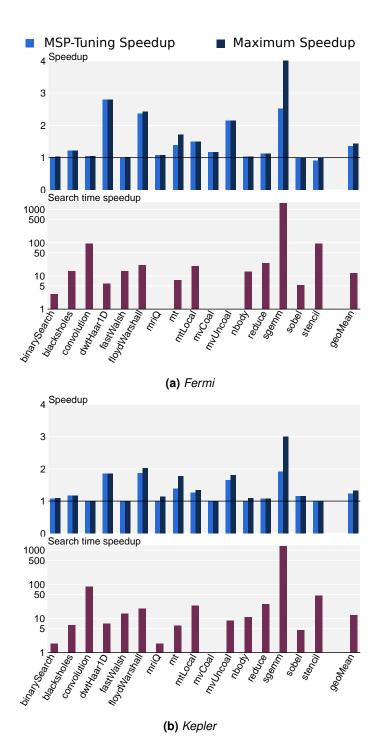

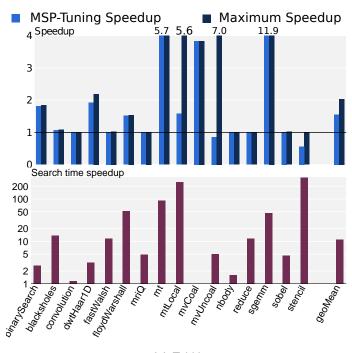

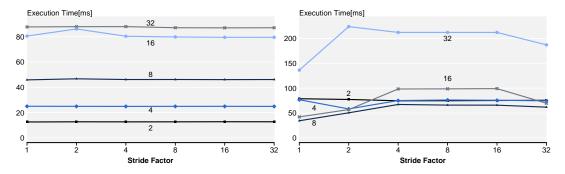

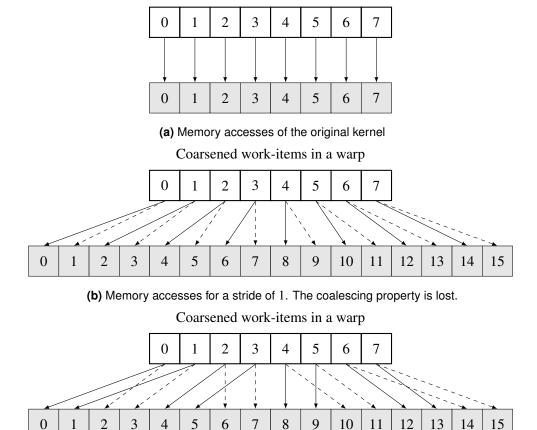

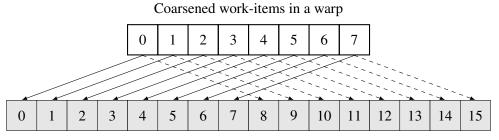

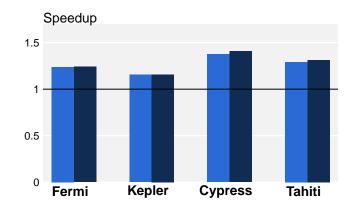

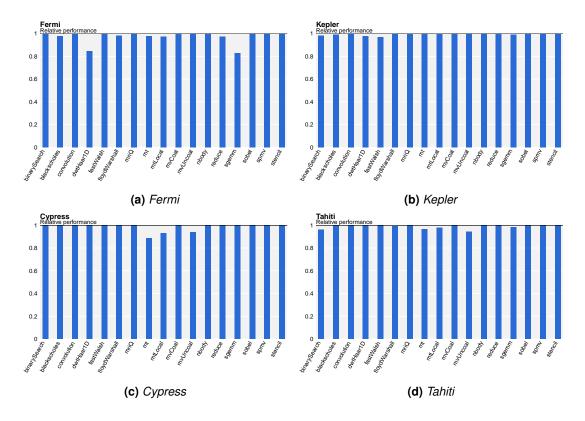

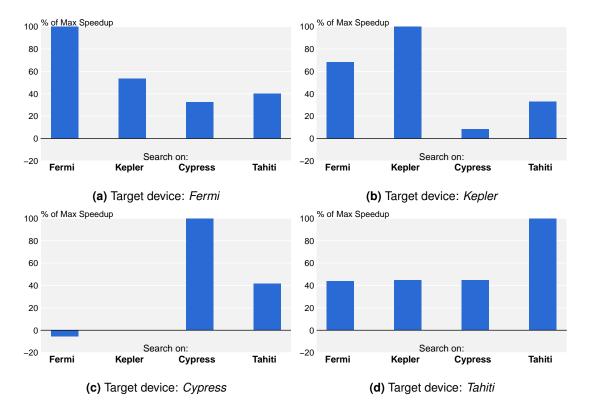

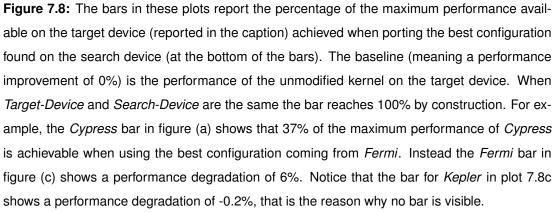

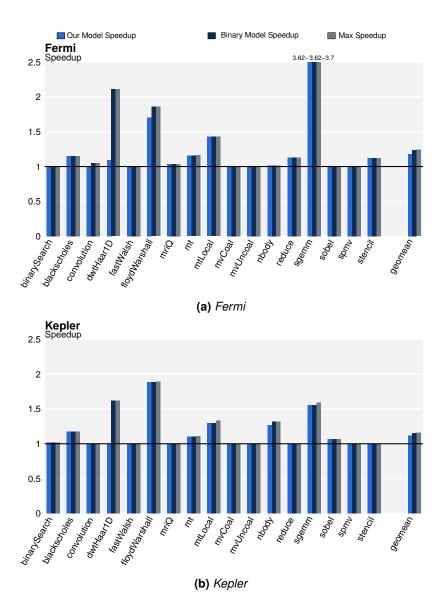

The work by Owens *et al.* [103] presents an overview of the type of applications that can benefit from GPGPU computing. Here follows a description of the most important applications of GPGPU following the guidelines given by the paper.