# Multi-core Architectures with Coarse-grained Dynamically Reconfigurable Processors for Broadband Wireless Access Technologies

Wei Han

A thesis submitted for the degree of Doctor of Philosophy.

The University of Edinburgh.

January 2010

#### **Abstract**

Broadband Wireless Access technologies have significant market potential, especially the WiMAX protocol which can deliver data rates of tens of Mbps. Strong demand for high performance WiMAX solutions is forcing designers to seek help from multi-core processors that offer competitive advantages in terms of all performance metrics, such as speed, power and area. Through the provision of a degree of flexibility similar to that of a DSP and performance and power consumption advantages approaching that of an ASIC, coarse-grained dynamically reconfigurable processors are proving to be strong candidates for processing cores used in future high performance multi-core processor systems.

This thesis investigates multi-core architectures with a newly emerging dynamically reconfigurable processor – RICA, targeting WiMAX physical layer applications. A novel master-slave multi-core architecture is proposed, using RICA processing cores. A SystemC based simulator, called MRPSIM, is devised to model this multi-core architecture. This simulator provides fast simulation speed and timing accuracy, offers flexible architectural options to configure the multi-core architecture, and enables the analysis and investigation of multi-core architectures. Meanwhile a profiling-driven mapping methodology is developed to partition the WiMAX application into multiple tasks as well as schedule and map these tasks onto the multi-core architecture, aiming to reduce the overall system execution time. Both the MRPSIM simulator and the mapping methodology are seamlessly integrated with the existing RICA tool flow.

Based on the proposed master-slave multi-core architecture, a series of diverse homogeneous and heterogeneous multi-core solutions are designed for different fixed WiMAX physical layer profiles. Implemented in ANSI C and executed on the MRPSIM simulator, these multi-core solutions contain different numbers of cores, combine various

memory architectures and task partitioning schemes, and deliver high throughputs at relatively low area costs. Meanwhile a design space exploration methodology is developed to search the design space for multi-core systems to find suitable solutions under certain system constraints. Finally, laying a foundation for future multithreading exploration on the proposed multi-core architecture, this thesis investigates the porting of a real-time operating system – Micro C/OS-II to a single RICA processor. A multitasking version of WiMAX is implemented on a single RICA processor with the operating system support.

# Declaration of originality

I hereby declare that the research recorded in this thesis and the thesis itself was composed by myself in the School of Engineering at The University of Edinburgh, except where explicitly stated otherwise in the text.

Wei Han

### Acknowledgements

This thesis would not have been what you are seeing now, without the help of my supervisors and colleagues. Foremost, I would like to thank my PhD supervisors Prof. Tughrul Arslan and Dr. Ahmet T. Erdogan for their support and guidance during my study. I would also like to thank my colleagues, Dr. Ying Yi who made great contributions to our multi-core project and did a lot of work which I was too lazy to do, Mr. Mark I.R. Muir for his valuable guidance and parser libraries, Dr. Ioannis Nousias for his help on MRPSIM simulator design, Mr. Xin Zhao and Dr. Cheng Zhan for their contributions on WiMAX implementations. Meanwhile, I would like to thank all RICA team members: Dr. Sami Khawam, Dr. Mark Milward, Dr. Ioannis Nousias, Dr. Ying Yi and Mr. Mark I.R. Muir for their brilliant invention – the RICA architecture and its tool flow. In addition, many thanks to all members in SLI group for their help throughout my PhD study.

A very special thank to my wife Xinyu Chen who encourages me with her love, stays with me getting through all tough times and cooks delicious food for me. Finally, I would like to express my deepest appreciation to my parents for their love, guide and support to me throughout my life.

## Acronyms and abbreviations

3G Third Generation

ADSL Asymmetric Digital Subscriber Line

AES Advanced Encryption Standard

ALM Adaptive Logic Module

ALU Arithmetic Logic Unit

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction Set Processor

ASSP Application Specific Standard Product

BPSK Binary Phase-Shift Keying

BS Base Station

BWA Broadband Wireless Access

CDMA Code Division Multiple Access

CLB Configurable Logic Block

CMP Chip-Level Multiprocessing

CP Cyclic Prefix

CPS Cycles Per Second

DC Direct Current

DL Downlink

DSL Digital Subscriber Line

DSP Digital Signal Processor

DR Dynamically Reconfigurable

EV-DO Evolution-Data Optimized

FEC Forward Error Correction

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Program Gate Array

GF Galois Field

GFLOPS Giga Floating-Point Operations Per Second

GPP General Purpose Processor

GSM Global System for Mobile communications

GPU Graphics Processing Unit

HDL Hardware Description Language

HPT Highest Priority Task

HSPA High Speed Packet Access

HSDPA High Speed Downlink Packet Access

HSUPA High Speed Uplink Packet Access

IFFT Inverse Fast Fourier Transform

ILP Instruction Level Parallelism

IP Intellectual Property

IPI Inter-Processor Interrupt

IPS Instructions Per Second

ISA Instruction Set Architecture

ISDN Integrated Services Digital Network

ISI Intersymbol Interference

LL Load-Link

LUT Look-Up Table

MAC Media Access Control

Mbps Megabits per second

MIMO Multi-Input Multi-Output

ML Maximum Likelihood

MDF Machine Description File

MRPSIM Multiple Reconfigurable Processor Simulator

OFDM Orthogonal Frequency-Division Multiplexing

OS Operating System

PHY Physical Layer

PLD Programming Logic Device

PPE Power Processing Element

PRBS Pseudo-Random Binary Sequence

PSE Processing and Storage Element

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase-Shift Keying

RA Reconfigurable Architecture

RAM Random Access Memory

RICA Reconfigurable Instruction Cell Array

RISC Reduced Instruction Set Computer

RRC Reconfigurable Rate Controller

RPU Reconfigurable Processing Unit

RS Reed-Solomon

RTL Register Transfer Level

RTOS Real-Time Operating System

SC Store-Conditional

SDL System Description Level

SIMD Single Instruction Multiple Data

SoC System on Chip

SOFDMA Scalable Orthogonal Frequency Division Multiple Access

SMP Symmetric Multiprocessing

SPE Synergistic Processing Element

SPMD Single Program Multiple Data

SPS Steps Per Second

SRAM Static Random Access Memory

SS Subscriber Station

TDD Time Division Duplex

TLM Transaction-Level modeling

TTA Transport Triggered Architecture

UL Uplink

UMTS Universal Mobile Telecommunications System

VLIW Very Long Instruction Word

WiMAX Worldwide Interoperability for Microwave Access

WLAN Wireless Local Area Network

#### **Publication from this work**

#### **Journals**

- 1. **W. Han**, Y. Yi, M. Muir, I. Nousias, T. Arslan, and A. T. Erdogan, "Multi-core Architectures with Dynamically Reconfigurable Array Processors for Wireless Broadband Technologies," *IEEE Transaction on Computer Aided Design of Integrated Circuits and Systems (TCAD)*, Vol. 28, Issue 12, pp. 1830-1843, December 2009.

- 2. **W. Han**, Y. Yi, M. Muir, I. Nousias, T. Arslan, and A. T. Erdogan, "Efficient Implementation of WiMAX Physical Layer on Multi-core Architecture with Dynamically Reconfigurable Processors," *Scalable Computing: Practice and Experience Scientific international journal for parallel and distributed computing*, Vol. 9, pp.185-196, ISSN 1097-2803, 2008.

#### **Conference and Workshops**

- 1. **W. Han**, Y. Yi, Xin Zhao, M. Muir, T. Arslan, and A. T. Erdogan, "Heterogeneous Multi-core Architectures with Dynamically Reconfigurable Processors for WiMAX transmitter", *the 22<sup>nd</sup> Annual IEEE International SOC Conference (SOCC'09)*, pp. 97 100, Belfast, UK, 9 11 September, 2009.

- 2. **W. Han**, Y. Yi, Xin Zhao, M. Muir, T. Arslan, and A. T. Erdogan, "Heterogeneous Multi-core Architectures with Dynamically Reconfigurable Processors for Wireless Communication", *the 7th IEEE Symposium on Application Specific Processors in conjunction with Design Automation Conference 2008 (SASP'09*), pp. 1 6, San Francisco, California, 27 28 July, 2009.

- 3. Y. Yi, **W. Han**, X. Zhao, A. T. Erdogan and T. Arslan, "An ILP Formulation for Task Mapping and Scheduling on Multi-core Architectures," *the Conference on Design, Automation and Test in Europe (DATE'09)*, pp. 33-38, Nice, France, 20 24 April, 2009.

- 4. **W. Han**, Y. Yi, M. Muir, I. Nousias, T. Arslan, and A. T. Erdogan, "MRPSIM: a TLM based Simulation Tool for MPSoCs targeting Dynamically Reconfigurable Processors," *the* 21<sup>st</sup> Annual IEEE International SOC Conference (SOCC'08), pp. 41-44, Newport Beach, California, 17 20 September, 2008.

- 5. Y. Yi, **W. Han**, A. Major, A. T. Erdogan, and T. Arslan, "Exploiting Loop-Level Parallelism on Multi-Core Architectures for the WiMAX Physical Layer," *the 21<sup>st</sup> Annual IEEE International SOC Conference (SOCC'08)*, pp. 31-34, Newport Beach, California, 17 20 September, 2008.

- 6. **W. Han**, Y. Yi, M. Muir, I. Nousias, T. Arslan, and A. T. Erdogan, "Multi-core Architectures with Dynamically *Reconfigurable Array Processors for the WIMAX Physical*

- Layer," the 6th IEEE Symposium on Application Specific Processors conjunction with Design Automation Conference 2008 (SASP'08), pp.115-120, Anaheim, California, 8 9 June, 2008.

- 7. **W. Han**, Y. Yi, M. Muir, I. Nousias, T. Arslan, and A. T. Erdogan, "Efficient Implementation of Wireless Applications on Multi-core Platforms based on Dynamically Reconfigurable Processors," *2008 International Workshop on Multi-Core Computing Systems*, pp. 837-842, Barcelona, Spain, March 2008.

- 8. **W. Han**, I. Nousias, M. Muir, T. Arslan, A.T. Erdogan, "The Design of Multitasking Based Applications on Reconfigurable Instruction Cell Based Architectures," *the 17th International Conference on Field Programmable Logic and Applications (FPL'07)*, pp. 447-452, Amsterdam, Netherlands, 27 29 August, 2007.

- 9. **W. Han**, M. Muir, I. Nousias, T. Arslan, A.T. Erdogan, "Mapping Real Time Operating System on Reconfigurable Instruction Cell based Architectures," 2007 IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM'07), pp.301-304, Napa, California, 23 25 April, 2007.

# Contents

| 1 | Inti | roduction                              | 1  |

|---|------|----------------------------------------|----|

|   | 1.1  | Motivation                             | 1  |

|   | 1.2  | Objective                              | 3  |

|   | 1.3  | Contribution                           | 4  |

|   | 1.4  | Thesis structure.                      | 5  |

| 2 | Bro  | padband Access Technologies and WiMAX  | 7  |

|   | 2.1  | Introduction                           | 7  |

|   | 2.2  | Wired broadband access technologies    |    |

|   |      | 2.2.1 DSL                              | 8  |

|   |      | 2.2.2 Cable                            | 9  |

|   |      | 2.2.3 Optical fibre                    | 9  |

|   |      | 2.2.4 Others                           | 9  |

|   | 2.3  | Broadband wireless access technologies | 10 |

|   |      | 2.3.1 HSPA                             | 10 |

|   |      | 2.3.2 EV-DO                            | 11 |

|   |      | 2.3.3 Satellite                        | 11 |

|   |      | 2.3.4 Wi-Fi                            | 12 |

|   |      | 2.3.5 WiMAX                            | 12 |

|   | 2.4  | WiMAX PHY processing chain             | 14 |

|   |      | 2.4.1 Randomising                      | 15 |

|   |      | 2.4.2 FEC encoding                     | 15 |

|   |      | 2.4.2.1 Reed-Solomon encoding          | 16 |

|   |      | 2.4.2.2 Convolutional encoding         | 17 |

|   |      | 2.4.2.3 Puncturing                     | 18 |

|   |      | 2.4.3 Interleaving                     | 19 |

|   |      | 2.4.4 Data modulation                  | 20 |

|   |      | 2.4.5 OFDM processing                  | 21 |

|   |      | 2.4.5.1 Pilot modulation and insertion |    |

|   |      | 2.4.5.2 DC and guard band insertion    | 23 |

|   |      | 2.4.5.3 FFT/IFFT                       | 23 |

|   |      | 2.4.5.4 Cyclic prefix extension        |    |

|   |      | 2.4.6 Synchronisation                  |    |

|   |      | 2.4.7 Data demodulation                |    |

|   |     | 2.4.8 FEC decoding                                                          | 26 |

|---|-----|-----------------------------------------------------------------------------|----|

|   |     | 2.4.8.1 Viterbi decoding                                                    | 26 |

|   |     | 2.4.8.2 Reed-Solomon decoding                                               | 27 |

|   | 2.5 | Summary                                                                     | 28 |

| 3 | Mu  | lti-core Processors and Reconfigurable Architectures                        | 29 |

|   | 3.1 | Introduction                                                                | 29 |

|   | 3.2 | Multi-core processors                                                       | 30 |

|   |     | 3.2.1 The advantages of multi-core processors                               | 31 |

|   |     | 3.2.2 Taxonomies of multi-core processors                                   | 32 |

|   |     | 3.2.2.1 Computing markets                                                   | 32 |

|   |     | 3.2.2.2 Heterogeneity and Homogeneity                                       | 33 |

|   |     | 3.2.2.3 Core types                                                          | 35 |

|   | 3.3 | Reconfigurable architectures                                                | 36 |

|   |     | 3.3.1 Execution structures                                                  | 36 |

|   |     | 3.3.2 Granularity                                                           | 37 |

|   |     | 3.3.2.1 Fine-grained reconfigurable architectures                           | 37 |

|   |     | 3.3.2.2 Coarse-grained reconfigurable architectures                         | 38 |

|   |     | 3.3.2.3 Medium-grained and very coarse-grained reconfigurable architectures | 40 |

|   |     | 3.3.2.4 Mixed-grained reconfigurable architectures                          |    |

|   |     | 3.3.3 Reconfiguration schemes                                               | 41 |

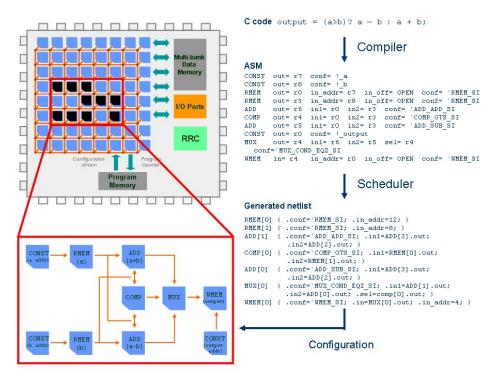

|   | 3.4 | Reconfigurable instruction cell array                                       | 41 |

|   |     | 3.4.1 Architecture                                                          | 42 |

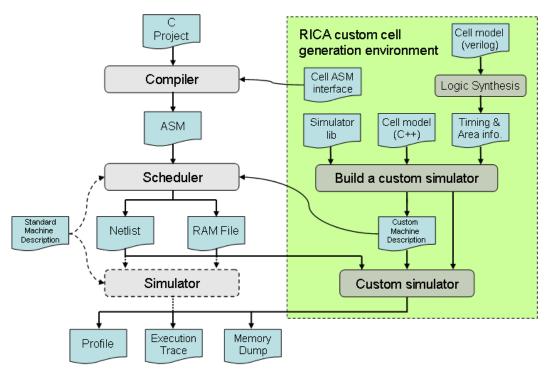

|   |     | 3.4.2 Standard tool flow                                                    | 44 |

|   | 3.5 | Traditional WiMAX silicon implementations                                   | 45 |

|   |     | 3.5.1 Custom chip implementations                                           | 45 |

|   |     | 3.5.2 GPP/DSP based SoC implementations                                     | 46 |

|   |     | 3.5.3 FPGA/PLD implementations                                              | 47 |

|   | 3.6 | Multi-core implementations of WiMAX                                         | 47 |

|   |     | 3.6.1 PicoArray                                                             | 48 |

|   |     | 3.6.2 Freescale MSC8126                                                     | 49 |

|   |     | 3.6.3 Cell Broadband Engine                                                 | 49 |

|   |     | 3.6.4 Intel IXP 2350 network processor                                      | 50 |

|   |     | 3.6.5 Sandbridge SB3010                                                     | 50 |

|   | 3.7 | RICA based multi-core architecture                                          | 51 |

|   | 3.8 | Summary                                                                     | 51 |

| 4 | A R | ICA Processor based Multi-core Architecture                                 | 53 |

|   | 4.1 | Introduction                                                                | 53 |

|   | 4.2 | The proposed multi-core architecture                                        | 54 |

|   |     | 4.2.1 Processing cores                                                      | 56 |

|   |     | 4.2.2 Memory architecture                                                   | 57 |

|   |     | 4.2.2.1 Shared memory/local memory                                          | 57 |

|   |      | 4.2.2.2 Shared register file                         | 58  |

|---|------|------------------------------------------------------|-----|

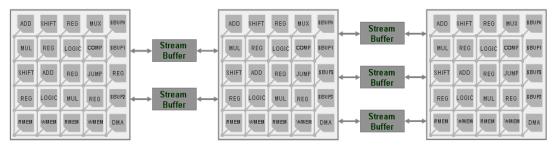

|   |      | 4.2.2.3 Stream buffer                                | 60  |

|   |      | 4.2.3 Arbiter                                        | 62  |

|   |      | 4.2.4 Crossbar switch                                | 62  |

|   |      | 4.2.5 Interrupt controller                           | 63  |

|   |      | 4.2.6 Router                                         | 63  |

|   | 4.3  | Synchronisation methods and atomic operation support | 64  |

|   | 4.4  | Custom instruction integration                       | 66  |

|   | 4.5  | Summary                                              | 67  |

| 5 | Mu   | Itiple Reconfigurable Processors Simulator           |     |

|   | 5.1  | Introduction                                         | 69  |

|   | 5.2  | Related work on multiprocessor simulators            |     |

|   | 5.3  | Trace-driven simulation.                             | 71  |

|   | 5.4  | SystemC and transaction-level modeling               | 74  |

|   | 5.5  | TLM model                                            | 76  |

|   | 5.6  | MRPSIM command line options                          | 79  |

|   | 5.7  | Mpsockit - a subsidiary tool                         | 81  |

|   | 5.8  | Results                                              | 82  |

|   | 5.9  | Summary                                              | 84  |

| 6 | Hon  | nogeneous Multi-core Solutions for WiMAX             | 87  |

|   | 6.1  | Introduction                                         | 87  |

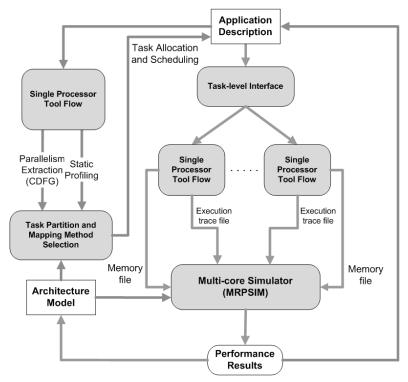

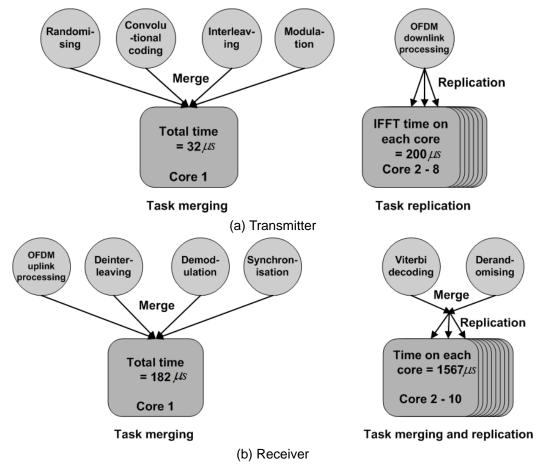

|   | 6.2  | Mapping methodology                                  | 88  |

|   | 6.3  | Task partitioning methods                            | 90  |

|   |      | 6.3.1 Task merging and task replication              | 91  |

|   |      | 6.3.2 Loop-level partitioning                        | 93  |

|   | 6.4  | Development of multi-core projects                   | 96  |

|   | 6.5  | Synchronisation between tasks                        | 97  |

|   | 6.6  | Results                                              | 98  |

|   | 6.7  | Summary                                              | 104 |

| 7 | Hete | erogeneous Multi-core Solutions for WiMAX            | 105 |

|   | 7.1  | Introduction                                         | 105 |

|   | 7.2  | Design space exploration                             | 106 |

|   | 7.3  | Timing optimisation                                  | 111 |

|   |      | 7.3.1 Code optimisation                              | 111 |

|   |      | 7.3.2 Architectural optimisation                     | 113 |

|   | 7.4  | Area optimisation                                    | 114 |

|   | 7.5  | Results                                              | 115 |

|   | 7.6  | Summary                                              | 123 |

| 8 | Mul  | titasking WiMAX on an RTOS                           | 125 |

|   |      | <b>→</b>                                             |     |

|    | 8.1   | Introduction                                              | 125 |

|----|-------|-----------------------------------------------------------|-----|

|    | 8.2   | The selection of RTOSes                                   | 127 |

|    | 8.3   | Porting Micro C/OS-II to RICA                             | 130 |

|    |       | 8.3.1 Hardware requirements                               | 130 |

|    |       | 8.3.2 Software requirements                               | 131 |

|    | 8.4   | The multitasking implementation of WiMAX on Micro C/OS-II | 132 |

|    | 8.5   | Results                                                   | 136 |

|    | 8.6   | Summary                                                   | 138 |

|    |       |                                                           |     |

| 9  | Con   | clusions                                                  | 141 |

|    | 9.1   | Introduction                                              | 141 |

|    | 9.2   | Review of thesis contents                                 | 141 |

|    | 9.3   | Specific findings                                         | 144 |

|    | 9.4   | Directions for future work                                | 146 |

|    |       |                                                           |     |

|    |       |                                                           |     |

| D۵ | foron | 90                                                        | 1/0 |

# List of Figures

| Figure 2.1 Fixed WiMAX physical layer processing chain                                       | 15 |

|----------------------------------------------------------------------------------------------|----|

| Figure 2.2 PRBS for the data randomisation                                                   | 15 |

| Figure 2.3 Reed-Solomon encoder                                                              | 17 |

| Figure 2.4 Binary convolutional encoder with a constraint length of 7 and a code rate of 1/2 | 17 |

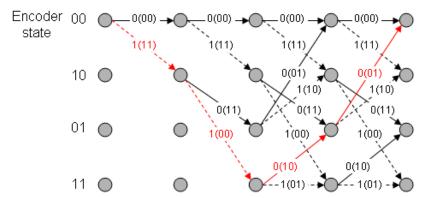

| Figure 2.5 Trellis diagram representation of a simple convolutional encoder                  | 18 |

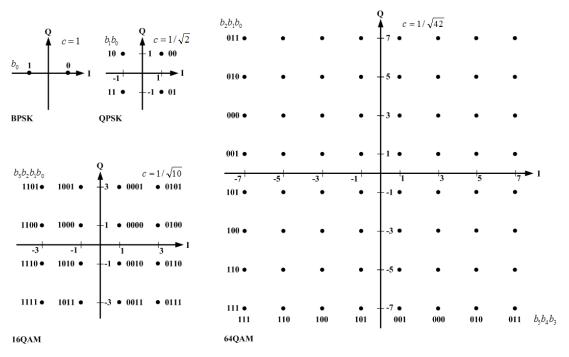

| Figure 2.6 BPSK, QPSK, 16QAM and 64QAM modulation schemes in WiMAX                           | 20 |

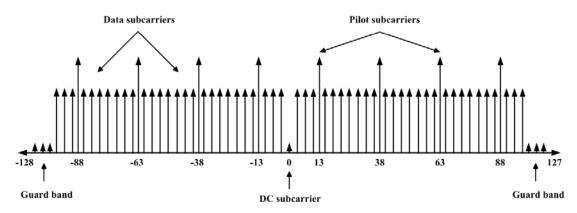

| Figure 2.7 Frequency domain representation of an OFDM symbol in fixed WiMAX                  | 22 |

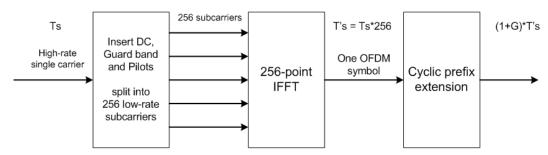

| Figure 2.8 OFDM downlink processing in the transmitter side of fixed WiMAX                   | 22 |

| Figure 2.9 PRBS for pilot modulation                                                         | 23 |

| Figure 2.10 Data flow graph of an 8-point radix-2 FFT                                        | 24 |

| Figure 2.11 Signal flow representation of a radix-2 butterfly                                | 24 |

| Figure 2.12 Timing synchronisation                                                           | 25 |

| Figure 2.13 16QAM soft decision data demodulation                                            | 26 |

| Figure 2.14 Viterbi decoding process for a convolutional code with a 1/2 code rate           | 27 |

| Figure 2.15 Reed-Solomon decoding process                                                    | 28 |

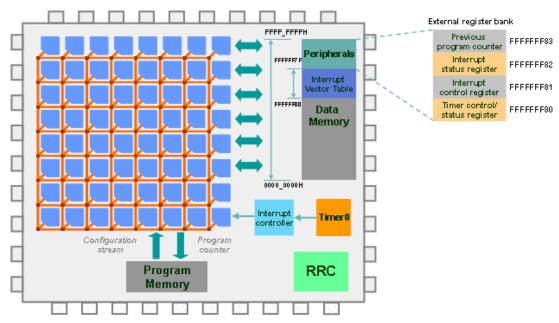

| Figure 3.1 The RICA architecture                                                             | 43 |

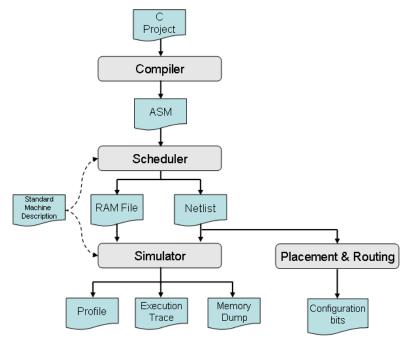

| Figure 3.2 Standard RICA tool flow                                                           | 45 |

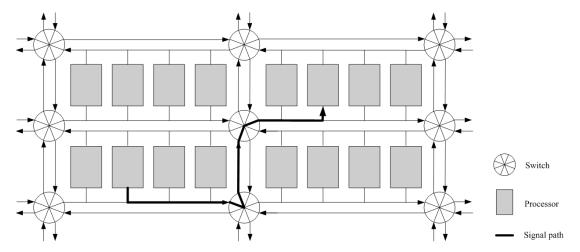

| Figure 3.3 PicoArray interconnection and the inter-processor communication                   | 48 |

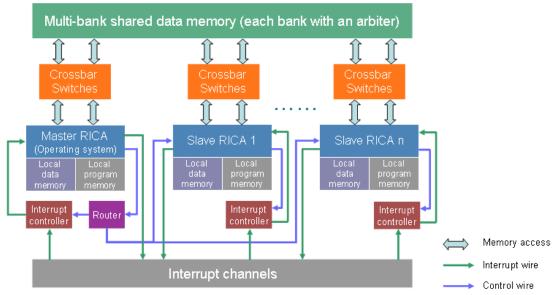

| Figure 4.1 Proposed master-slave multi-core architecture                                     | 55 |

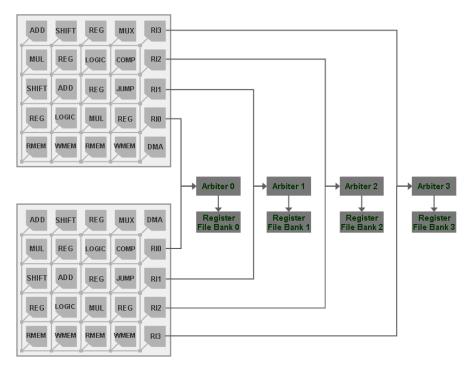

| Figure 4.2 Custom instruction cell MULTIPTBK_REG_FILE                                        | 59 |

| Figure 4.3 A 4-bank shared register file in the proposed multi-core architecture             | 60 |

| Figure 4.4 Stream buffers in the proposed multi-core architecture                            | 61 |

| Figure 4.5 RICA custom cell generation environment and custom tool flow                      | 67 |

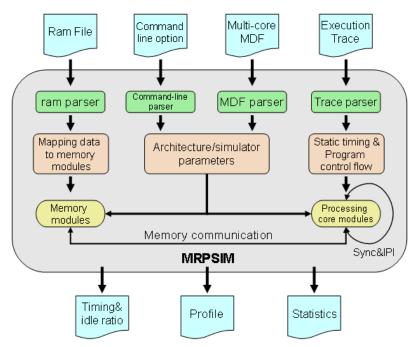

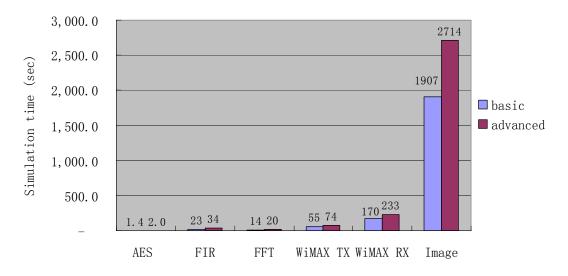

| Figure 5.1 The interface and internal structure of MRPSIM simulator                          | 72 |

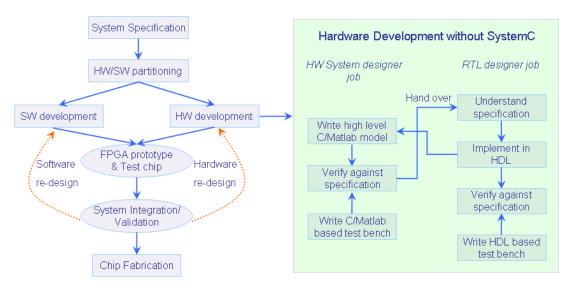

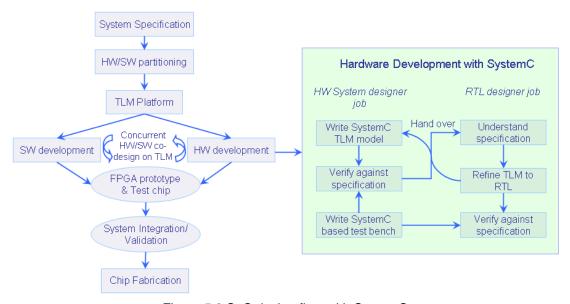

| Figure 5.2 Traditional SoC design flow without SystemC                                       | 74 |

| Figure 5.3 SoC design flow with SystemC                                                      | 75 |

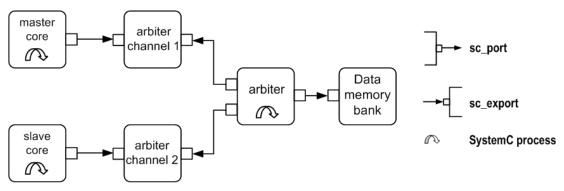

| Figure 5.4 An example demonstrating the TLM model of a multi-core architecture               | 77 |

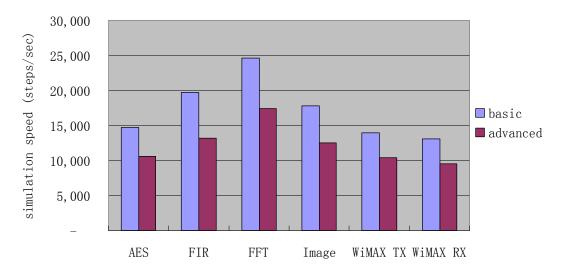

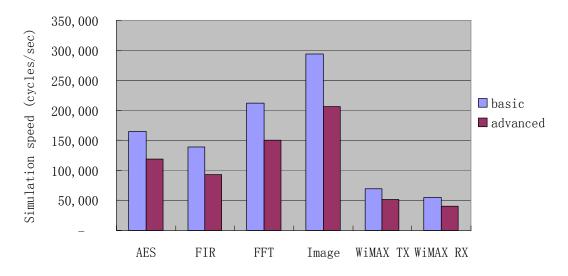

| Figure 5.5 The simulation speed (steps/sec)                                                  | 83 |

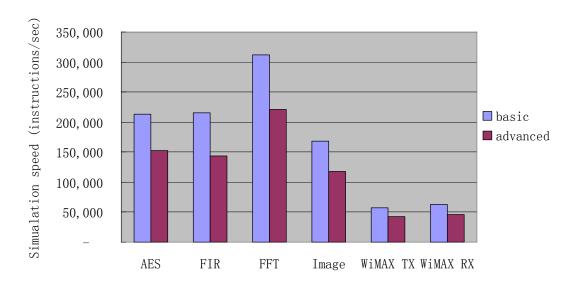

| Figure 5.6 The simulation speed (instructions/sec)                                           | 83 |

| Figure 5.7 The simulation speed (cycles/sec)                                                 | 84 |

| Figure 5.8 The simulation time (sec)                                                         | 85 |

| Figure 6.1 Mapping methodology                                                               | 89 |

| Figure 6.2 Task merging and task replication methods                                         | 92 |

| Figure 6.3 Decoding loop partitioning                                                        | 95 |

| Figure 6.4 Integration of MRPSIM in Eclipse                                      | 96     |

|----------------------------------------------------------------------------------|--------|

| Figure 6.5 Speedup and parallel efficiency of transmitter scenarios              | 101    |

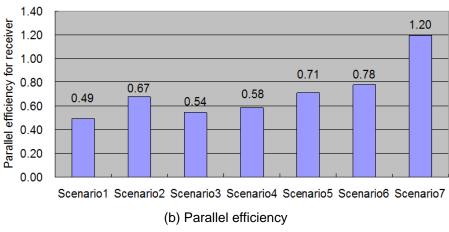

| Figure 6.6 Speedup and parallel efficiency of receiver scenarios                 | 102    |

| Figure 7.1 The main blocks in 16QAM based WiMAX transmitter and receiver         | 110    |

| Figure 7.2 Task partitioning, mapping and scheduling in receiver Design 4        | 121    |

| Figure 8.1 The Micro C/OS-II based system.                                       | 130    |

| Figure 8.2 Hardware requirements for porting Micro C/OS-II to RICA               | 131    |

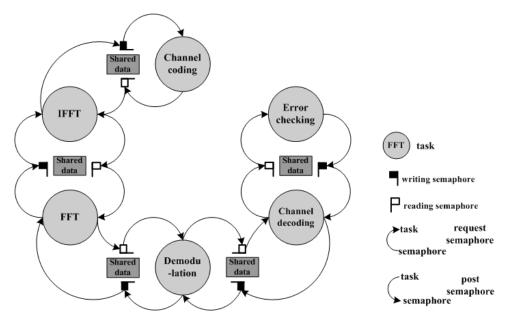

| Figure 8.3 Multitasking WiMAX function blocks                                    | 132    |

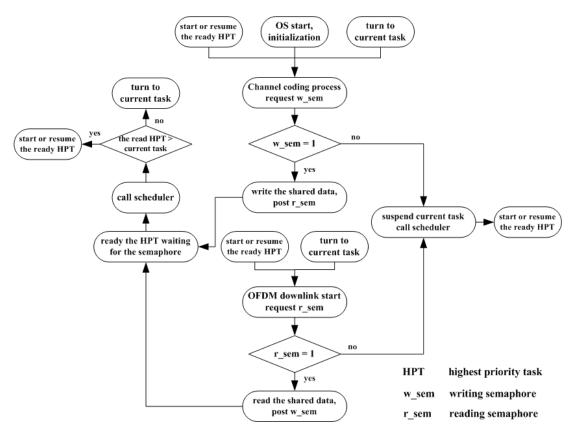

| Figure 8.4 Program flow chart of WiMAX running on Micro C/OS-II                  | 133    |

| Figure 8.5 Detailed program flow diagram for the execution of channel coding and | d OFDM |

| downlink tasks                                                                   | 134    |

# List of Tables

| Table 2.1 Pros and cons of wired and wireless broadband access technologies            | 7      |

|----------------------------------------------------------------------------------------|--------|

| Table 2.2 Comparison of 802.11 standards                                               | 12     |

| Table 2.3 Comparison of broadband Internet access technologies                         | 13     |

| Table 2.4 Comparison between Fixed and Mobile WiMAX                                    | 14     |

| Table 2.5 Puncturing patterns in WiMAX                                                 | 19     |

| Table 3.1 Comparison of multi-core processors                                          | 35     |

| Table 3.2 Comparison of coarse-grained reconfigurable architectures                    | 39     |

| Table 3.3 RICA Instruction Cells                                                       | 42     |

| Table 3.4 MSC8126 loading and task allocation                                          | 49     |

| Table 4.1 Access modes and configuration bits for RMEM and WMEM cells                  | 57     |

| Table 4.2 Pin descriptions of MULTIPTBK_REG_FILE cells                                 | 59     |

| Table 4.3 Access modes and configuration bits of MULTIPTBK_REG_FILE cells              |        |

| Table 4.4 Pin description of SBUF instruction cells                                    | 61     |

| Table 4.5 Access modes and configuration bits of SBUF cells                            | 61     |

| Table 4.6 Access modes and configuration bits for LL/SC instructions                   | 66     |

| Table 5.1 Functionality of main SystemC processes and functions in MRPSIM modules      | 78     |

| Table 5.2 Command line options of MRPSIM                                               | 80     |

| Table 5.3 Formats for original and compressed traces                                   | 81     |

| Table 5.4 Mpsockit options                                                             | 82     |

| Table 6.1 IFFT Loop Partitioning                                                       | 94     |

| Table 6.2 Synchronisation between tasks                                                | 97     |

| Table 6.3 Homogeneous multi-core scenarios for WiMAX transmitter                       | 98     |

| Table 6.4 Homogeneous multi-core scenarios for WiMAX receiver                          | 98     |

| Table 6.5 Configurations of both a standard core and a custom core                     | 99     |

| Table 6.6 Performance comparison for transmitter scenarios                             | 102    |

| Table 6.7 Performance comparison for receiver scenarios                                | 103    |

| Table 7.1 Pseudo code of the design space exploration methodology                      | 108    |

| Table 7.2 A code example of replacing jumps with multiplexers                          | 111    |

| Table 7.3 Storing constants in registers for 16QAM modulation                          | 112    |

| Table 7.4 Comparison of transmitter design configurations                              | 116    |

| Table 7.5 Comparison of receiver design configurations                                 | 116    |

| Table 7.6 Comparison between standard and custom RICA cores used in transmitter design | ns 117 |

| Table 7.7 Comparison between standard and custom RICA cores used in receiver designs.  | 118    |

| Table 7.8 Results from the exploration methodology for transmitter designs             | 119    |

| Table 7.9 Results from the exploration methodology for receiver designs | 119 |

|-------------------------------------------------------------------------|-----|

| Table 7.10 Comparison of multi-core solutions                           | 122 |

| Table 8.1 Survey of RTOSes                                              | 127 |

| Table 8.2 Comparison in term of memory size and multiprocessing support | 129 |

| Table 8.3 Comparison in term of ported devices and specific features    | 129 |

| Table 8.4 Micro C/OS-II machine dependent files for RICA                | 131 |

| Table 8.5 Results of WiMAX with/without RTOS support                    | 136 |

| Table 8.6 Comparison of multitasking WiMAX on RICA and ARM7TDMI         | 137 |

# Chapter 1 Introduction

#### 1.1 Motivation

Growing from an academic tool to owning almost one and half billion users nowadays, the Internet stands as a pivotal success. People have come to depend on the Internet more and more in their daily lives. Now users not only need traditional applications like Web surfing and emails, but also demand to experience multimedia services like interactive gaming, real-time audio and video streaming, and even high-definition TV. These applications are becoming an integral part of business as well as recreation, leading to the increased push for broadband access technologies with higher data rates, better reliability and enhanced user experience. Meanwhile currently the desire to access the Internet at any time from anywhere is dramatically rising. By combining the convenience through wireless access and the outstanding broadband performance, Broadband Wireless Access (BWA) technologies demonstrate great interests to end users and a remarkable potential success in commerce. Among various BWA solutions, Worldwide Interoperability for Microwave Access (WiMAX) defined in IEEE 802.16 standard family [1, 2] becomes more and more popular

and may help make the vision of pervasive connectivity a reality. According to the announcement from the WiMAX forum, more than 133 million WiMAX users are anticipated by 2012 [3]. Meanwhile, the WiMAX market is forecasted to reach \$3.5 billion and 4% market share of the overall broadband market by 2010 [3].

As an embedded application, WiMAX demands high throughput, strict low power, and in-field reprogrammability in order to follow evolving standards. Single-core processors fall short of meeting all these requirements. Historically, processor manufacturers answered the requirement for more processing power primarily by delivering faster processor speeds. The technology advances, such as Instruction Level Parallelism (ILP) and increased frequency due to advanced process technology, have delivered exponential performance gains for microprocessors over the last three decades. However things have changed and these traditional approaches will not provide the same gains in the future. It is mainly because high performance single-core microprocessors have reached three walls. Firstly, the memory wall results from the fact that the memory performance has a much slower growth rate than the processor performance. Therefore the gap between memory and processor speeds keeps increasing. In spite of the use of larger caches, this trend has not been curbed [4]. As a result, high frequency processors have to spend a significant amount of time waiting for the response from memory. The second wall comes from the limitation of ILP, called ILP wall. Even with various ambitious hardware and software techniques, only very low average parallelism can be found in the instruction streams and is far from enough to keep high performance processors busy [5]. The final wall is the power wall which is the main challenge incurred by high clock rates and deep submicron processes. In fact, in traditional single-core architectures, power consumption has increased at a greater rate than the clock speed. Meanwhile high processor density in sub-90 nm processes results in high power density which has already reached the level of 100W/cm<sup>2</sup> found in a nuclear reactor and probably soon will rise to the level of 1,000W/cm<sup>2</sup> found in space rocket nozzles [6].

These three walls drive people to look for alternative solutions, instead of continuing to

build complicated single-core processors. One of such scale-out solutions is to put two or more simpler and smaller processing cores on a chip. It is called Chip-Level Multiprocessing (CMP) or a multi-core processor. In multi-core solutions, multiple simple processing cores with lower operating frequency can deliver excellent overall performance while reducing the thermal output. Another drive for the adoption of multi-core processors is that parallelism exists in most real world applications such as multimedia processing and Fast Fourier Transform (FFT). As a parallel architecture, a multi-core architecture can effectively bring the parallel nature of applications into full play.

However one question arising from multi-core architectures is that what kind of processing core would be the best candidate for multi-core architectures targeting embedded applications like WiMAX? Obviously, General Purpose Processors (GPPs) are not well suited to this task, due to their generic features and proportion of the silicon for computation. On the other hand, Very Long Instruction Word (VLIW) Digital Signal Processor (DSP) architectures face the problem due to the limited amount of ILP found in programs [7]. Filling the gap between the high flexibility of DSPs and the high performance of Application-Specific Integrated Circuits (ASICs), Dynamically Reconfigurable (DR) processors offer an attractive solution for developing multi-core architectures. This thesis investigates multi-core processor architectures building upon coarse-grained dynamically reconfigurable processing cores to meet the rigorous requirements from BWA applications, such as WiMAX.

#### 1.2 Objective

The objective of this thesis is to explore a multi-core architecture by using coarse-grained dynamically reconfigurable processing cores, and develop tools and a mapping methodology which allow sequential ANSI C programs to be executed on the multi-core architecture. Afterward, based on this multi-core architecture, this thesis aims to design efficient multi-core solutions for broadband wireless access technologies, particularly WiMAX

applications.

#### 1.3 Contribution

The major contributions of the thesis are split into seven key aspects:

- 1. A novel master-slave multi-core architecture using a newly emerging coarse-grained DR processor, Reconfigurable Instruction Cell Array (RICA), has been proposed. This architecture provides a variety of memory architectural options for different application requirements and system constraints, as well as supporting inter-processor synchronisation through providing atomic operations.

- 2. A SystemC Transaction-Level modeling (TLM) based trace-driven simulator has been designed for modeling this multi-core architecture. This simulator delivers high-speed simulation and maintains timing accuracy. By providing flexible architectural options to configure the multi-core architecture, this simulator enables fast analysis and exploration of multi-core architectures as well as rapid application verification.

- 3. A profiling-driven mapping methodology has been developed to partition a target application into multiple tasks as well as schedule and map these tasks onto multi-core architectures, aiming to reduce the overall system execution time. This mapping methodology supports both homogeneous and heterogeneous multi-core solutions.

- 4. Several homogenous multi-core solutions have been developed for the Binary Phase-Shift Keying (BPSK) based fixed WiMAX physical layer application. These multi-core solutions combine different memory architectures and task partitioning schemes, and deliver high speedups compared to single-core implementations.

- 5. A design space exploration methodology has been presented to find suitable single-core and multi-core solutions under certain system constraints. Furthermore, several

timing and area optimisation techniques have been addressed for WiMAX applications, targeting the proposed multi-core architecture.

- 6. Several heterogeneous multi-core solutions have been developed for the 16-Quadrature Amplitude Modulation (QAM) based fixed WiMAX physical layer application. These solutions deliver high throughputs at relatively low area costs.

- 7. A Real-Time Operating System (RTOS) Micro C/OS-II has been ported to a single-core RICA processor. A multitasking design of a fixed WiMAX physical layer program has been implemented on RICA processor with this operating system support.

#### 1.4 Thesis structure

This thesis is structured as follows.

Chapters 2 and 3 contain descriptions of the background and existing literature. Chapter 2 provides an overview of mainstream broadband Internet access technologies and detailed descriptions for a fixed WiMAX physical layer. Chapter 3 introduces multi-core processors and reconfigurable computing technologies, and emphasises a dynamically reconfigurable processor – RICA, which is used in the proposed multi-core architecture. Meanwhile, Chapter 3 presents existing WiMAX implementations on various technologies.

Chapters 4 through 8 address my PhD research achievements. Chapter 4 proposes a basic multi-core architecture containing RICA based processing cores, and details the main components of this architecture as well as the inter-processor synchronisation methods. Chapter 5 presents a SystemC TLM trace-driven simulator which models the multi-core architecture described in Chapter 4. In addition, a trace preprocessing tool – Mpsockit is described in Chapter 4. Chapter 6 introduces homogeneous multi-core solutions for WiMAX, based on the proposed multi-core architecture. A mapping methodology and several task partitioning methods are described in this chapter as well. Chapter 7 focuses on

heterogeneous multi-core implementations for WiMAX. A design space exploration methodology is presented to find suitable single-core or multi-core solutions under specific system and performance constraints. Chapter 8 investigates the porting of a real-time operating system to RICA processor and a multitasking based WiMAX on a single-core RICA processor with an operating system supported.

Finally, the thesis is concluded with the summary in Chapter 9.

# Chapter 2 Broadband Access Technologies and WiMAX

#### 2.1 Introduction

As broadband services are frequently upgraded, the minimum bandwidth or data rate for defining broadband is gradually increased. Generally speaking, nowadays a broadband access technology should provide data rates beyond 1 Megabits per second (Mbps). Broadband access technologies can be classified into wired broadband access and broadband wireless access. Both the two categories have their own pros and cons shown in Table 2.1. In some places, they are complementary, while in other places, they compete with each other.

Table 2.1 Pros and cons of wired and wireless broadband access technologies

|                    | Pros                                                                                                                                     | Cons                                                                           |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| BWA                | Provide portable, nomadic, mobile service;<br>Serve extremely wide areas;<br>Good solution for areas lacking wireline<br>infrastructures | Lower capacity than wired broadband;<br>Less reliable and secure               |  |

| Wired<br>broadband | High capacity at high data rates High reliability and security                                                                           | Expensive to deploy new networks, especially in places lacking infrastructures |  |

As currently the desire to access the Internet at any time from anywhere dramatically increased, BWA technologies demonstrate remarkable advantages over their wire based counterparts in many emerging markets such as the burgeoning mobile Internet market where wired broadband solutions are helpless. Meanwhile BWA technologies are gradually taking more market share from traditional markets such as the last mile delivery. Here the term of last mile represents the final step in the connection from Internet service providers to end users, and does not really mean that the actual distance is one mile.

In this chapter, a brief overview is provided for both wired and wireless broadband access technologies in Sections 2.2 and 2.3, respectively. Mainstream broadband Internet access technologies are reviewed. In Section 2.4, an introduction is given for WiMAX physical layer with the details of each functional block. The aim of Section 2.4 is to present the background and context necessary for understanding the WiMAX physical layer.

#### 2.2 Wired broadband access technologies

By delivering Internet services through physical wires (e.g. twisted pair and television cable), wired broadband access technologies have inherent advantages over their wireless counterparts in reliability and security. Nowadays, there exist various wired technologies, some of which such as Digital Subscriber Line (DSL) and cable are predominant technologies in the market. The following subsections describe mainstream wired technologies available in the commercial market.

#### 2.2.1 **DSL**

DSL is the most popular technology for the last mile delivery. According to the world broadband statistics report [8], almost 65 percent of wired broadband subscribers are using DSL by Q2 2008. Actually, DSL is a family of technologies transmitting data over the high frequency band of telephone lines, while keeping voice delivered over the low frequency band. Among DSL technologies, Asymmetric Digital Subscriber Line (ADSL) is the most

common type used for home users and offers a much faster speed in the download direction than the upload direction. The latest ADSL standard provides data rates up to 24 Mbps and 3.5 Mbps for download and upload, respectively [9]. One of main drawbacks of DSL technologies is that data rates deteriorate with the distance from customers to providers' facilities increasing.

#### **2.2.2** Cable

Cable Internet is a technology to enable Internet access over the existing cable television network, especially popular in North America. According to the world broadband statistics report [8], cable Internet has up to 82 million users, more than 55 percent of them from North America. Unlike DSL which is distance sensitive, cable can maintain the same data rate over 100 kilometres. As defined in an international standard DOCSIS 2.0 [10], cable Internet can provide maximum data rates of 50 Mbps and 27 Mbps for download and upload, respectively.

#### 2.2.3 Optical fibre

Currently, many Internet service providers especially the ones in U.S. are using the optical fibre to deliver last mile communication, by directly connecting fibre to subscribers' premises. This fibre to the premises service includes the forms of fibre to the home and fibre to the building [11]. Depending on areas and communication protocols, the fibre to the premises offers data rates ranging from several Mbps to over one hundred Mbps. One disadvantage of this technology is the much more expensive connection charge and annual rental compared to other Internet access methods.

#### **2.2.4** Others

Other wired broadband technologies include Integrated Services Digital Network (ISDN), power line, T1/E1 and so on. Like DSL, ISDN is based on the telephone network. It was

popular prior to the emergence of DSL and cable. Now ISDN is gradually being superseded by DSL. Broadband over power line is a technology aiming to provide a broadband Internet at a data rate of over 100 Mbps via electric power lines. IEEE P1901 [12] is a draft standard for specifying this technology. During the thesis writing, this standard is still waiting for the approval. As for T1/E1, it can provide up to 2 Mbps bandwidth and is used for leased lines which directly connect customers such as companies to remote exchanges.

#### 2.3 Broadband wireless access technologies

Although currently wired broadband access technologies can offer better reliability and security, BWA technologies have very close performance in these fields. More importantly, BWA systems enable mobility and ubiquitous Internet access, especially in areas where their wired counterparts are not available. Since the first generation BWA systems (e.g. local multipoint distribution systems and multichannel multipoint distribution services) were deployed in the late 1990s, many BWA technologies have emerged with higher data rates, longer ranges and better reliability. They include Code Division Multiple Access (CDMA) based High Speed Packet Access (HSPA) [13] and Evolution-Data Optimized (EV-DO) [14] as well as Orthogonal Frequency-Division Multiplexing (OFDM) based Wi-Fi [15] and WiMAX. In the following subsections, mainstream BWA technologies are introduced.

#### 2.3.1 HSPA

HSPA is a family of protocols to improve the data transfer speeds in Universal Mobile Telecommunications System (UMTS). UMTS is one of Third Generation (3G) technologies, and combines wideband CDMA air interface and popular Global System for Mobile communications (GSM) infrastructures. HSPA delivers data through the UMTS network, and hence enables mobile broadband by using UMTS handheld devices. HSPA mainly consists of two standards, High Speed Downlink Packet Access (HSDPA) and High Speed Uplink Packet Access (HSUPA). Using approaches such as fast scheduling and link

adaptation, HSDPA offers a maximum data rate of 14.4 Mbps for the user downloading, while its uploading complement HSUPA provides an uploading speed up to 5.76 Mbps through the help of methods like an enhanced dedicated physical channel [16].

#### 2.3.2 **EV-DO**

EV-DO was designed to improve the data rates of another 3G technology, CDMA2000. Defined in [14], a combination of up to fifteen 1.25 MHz channels can boost the theoretical maximum rate of EV-DO to 73 Mbps. However, a typical deployment would involve just 3 channels to provide a download data rate of 14.7 Mbps. By using many of the same optimisation technologies as HSPA, EV-DO can achieve a similar spectral efficiency as HSPA. While one disadvantage of EV-DO is that EV-DO can not satisfy both voice and high-speed data communication concurrently, since it uses just one separate narrower channel for data service, compared to the efficient resource allocation for voice and data in a 5MHz channel used in HSPA. Moreover EV-DO has much less users than HSPA, as the UMTS network which HSPA is based on has more than nine times the subscribers of CDMA2000 [16].

#### 2.3.3 Satellite

Satellite broadband is a wireless broadband access method which transmits and receives data via satellites in the geostationary orbit. There are two types of this method, one is one-way communication where the uploading and the downloading are through telephone lines and satellites, respectively. The other is two-way communication which enables both uploading and downloading via satellites. Satellite broadband is suitable for locations where other Internet access methods are not available, such as the remote rural areas and vessels at sea. The main drawback of this method compared to others is the much higher latency due to the very long signal trip. In one-way communication, the signal travel path is 70,000 km, while two-way communication has a path of 140,000 km. Meanwhile, satellite broadband is more

likely affected by the weather and obstacles. Furthermore, the devices for satellite broadband are highly expensive [17].

#### 2.3.4 Wi-Fi

Recently, Wireless Local Area Network (WLAN) technologies, especially Wi-Fi, have become popular. Nowadays, almost every desktop or laptop computer is shipped with Wi-Fi functions, and varied handheld devices such as smart phones have built-in Wi-Fi chips. Moreover many cities have developed or are developing a municipal Wi-Fi project to enable a whole city or at least the city centre Internet accessible through setting up hundreds of Wi-Fi access points. Wi-Fi technologies are specified in IEEE 802.11 standards [15], four main versions of which are compared in Table 2.2. Even though the popularity of Wi-Fi, compared to other BWA technologies, Wi-Fi has some intrinsic drawbacks such as too short range, not supporting mobility and inefficient collision avoidance protocols [18].

Table 2.2 Comparison of 802.11 standards

| Standard | Release year | Operating frequency | Data rates<br>(Typical/Max) | Range<br>(Indoor/Outdoor) |

|----------|--------------|---------------------|-----------------------------|---------------------------|

| 802.11a  | 1999         | 5 GHz               | 23/54 Mbps                  | ~35/120 m                 |

| 802.11b  | 1999         | 2.4 GHz             | 4.5/11 Mbps                 | ~38/140 m                 |

| 802.11g  | 2003         | 2.4 GHz             | 19/54 Mbps                  | ~38/140 m                 |

| 802.11n  | Nov 2009     | 2.4/5 GHz           | 74/600 Mbps                 | ~70/250 m                 |

#### 2.3.5 WiMAX

Being the commercial name of IEEE 802.16 family of standards, WiMAX can provide up to tens of Mbps symmetric bandwidth over many kilometres. This gives WiMAX a significant advantage over other alternative last mile technologies like Wi-Fi and DSL. Based on OFDM, WiMAX can offer higher peak and average data rates, greater flexibility and system capacity, compared to CDMA based technologies, such as HSPA and EV-DO [18]. Table 2.3 provides a comparison between WiMAX and other broadband access technologies

Table 2.3 Comparison of broadband Internet access technologies

| Technology | Access method | Max DL/UL (Mbps) | Range     |

|------------|---------------|------------------|-----------|

| DSL        | wired         | 24/4.6           | 3 km      |

| Cable      | wired         | 50/27            | 160 km    |

| Fibre      | wired         | 50/20            | 20 km     |

| HSPA       | wireless      | 14.4/5.8         | 40 km     |

| EV-DO      | wireless      | 14.7/5.4         | 50-70 km  |

| Satellite  | wireless      | 16/2             | 35,000 km |

| Wi-Fi      | wireless      | 54/54            | 250 m     |

| WiMAX      | wireless      | 70/70            | 50 km     |

described in previous sections, in terms of Downlink/Uplink (DL/UL) data rates and the coverage. In this context, the downlink represents the transmission path from a Base Station (BS) to a Subscriber Station (SS), and the uplink represents the converse transmission path. In Table 2.3, for wired broadband access technologies, the range represents the typical distance between the subscribers' devices to a DSL access multiplexer, a cable model termination system or a fibre local central office. Among these technologies, WiMAX offers the highest symmetric data rates on downlink and uplink, as well as very good coverage.

Usually, WiMAX standards offer a wide variety of options, such as a selectable channel bandwidth and spectrum profiles, which allow the industry to set up very flexible deployments to satisfy requirements from different markets. Due to this flexibility, the WiMAX Forum was formed to certify and promote interoperable industry solutions based on the IEEE 802.16 standards. Currently there are more than 400 certified WiMAX trial or commercial networks developed around the world. One such example is WiBro developed in South Korea. The IEEE 802.16 standard family includes two major standards, 802.16-2004 (i.e. 802.16d) [2] and 802.16-2005 (i.e. 802.16e) [1] which define fixed WiMAX and mobile WiMAX, respectively. Table 2.4 provides a comparison between the two standards in some basic characteristics. It can be seen that both fixed WiMAX and mobile WiMAX have their own advantages and target applications.

This thesis focuses on the fixed WiMAX technology defined in IEEE 802.16-2004 standard.

Table 2.4 Comparison between Fixed and Mobile WiMAX

| Feature                | Fixed WiMAX (802.16-2004) | Mobile WiMAX (802.16-2005)                                         |

|------------------------|---------------------------|--------------------------------------------------------------------|

| Status                 | Completed June 2004       | Completed December 2005                                            |

| Spectrum               | 2-11 GHz                  | 2-6 GHz                                                            |

| Application            | Wireless DSL and Backhaul | Mobile Internet                                                    |

| Transmission<br>Scheme | 256-sub-carriers OFDM     | Scalable Orthogonal Frequency-division<br>Multiple Access (SOFDMA) |

| Service                | Fixed and portable        | Nomadic, portable and mobile                                       |

| Typical Cell Radius    | 4-6 miles                 | 1-3 miles                                                          |

Fixed WiMAX is much likely to succeed in three Internet service markets: residential area and small or medium enterprises, leased lines for business as well as the backhaul for Wi-Fi hotspots [18]. The first category of market demands services like high-speed file downloading, voice over Intellectual Property (IP) and multimedia applications. For this market, fixed WiMAX based broadband services can be provided by either installing an outdoor antenna or an indoor cable-like modem. Therefore, fixed WiMAX is superior to wired based cable and DSL in terms of faster and easier installation, lower deployment and operational costs. The second potential market is the leased line connecting large companies directly to remote exchanges. In this field, fixed WiMAX is good enough to compete with the dominant technology - T1/E1 by providing higher speed services for enterprise customers which are not able to access fibre. Another major opportunity for fixed WiMAX is to serve as a faster and more cost-efficient alternative to the wired backhaul technology for Wi-Fi hotspots. Meanwhile fixed WiMAX is technically and commercially viable for the area lack of good wired infrastructures, such as developing countries and rural areas in developed countries.

#### 2.4 WiMAX PHY processing chain

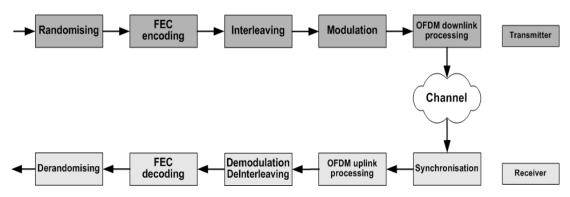

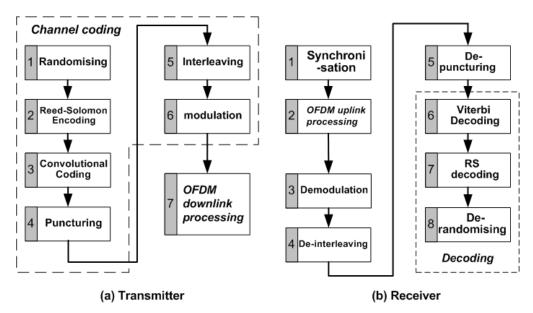

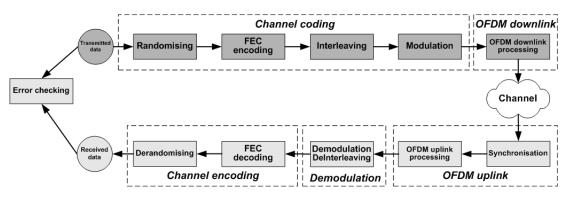

In this thesis, the target application is the fixed WiMAX Physical Layer (PHY) including both transmitter and receiver. Figure 2.1 provides an overview of the digital domain blocks in a typical fixed WiMAX PHY.

Figure 2.1 Fixed WiMAX physical layer processing chain

#### 2.4.1 Randomising

Figure 2.2 PRBS for the data randomisation

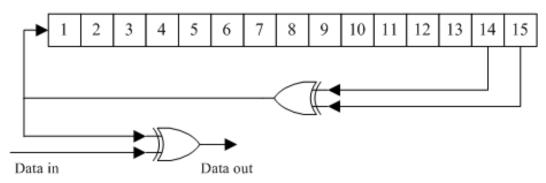

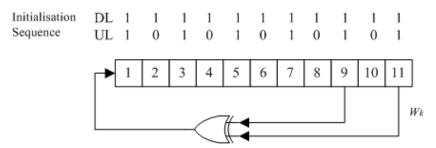

In WiMAX, randomisation is used to provide a simple encryption and prevent vicious receivers from decoding the data [2]. Each burst of information data is randomised in the transmitter side and de-randomised in the receiver side. Randomisation and de-randomisation are functionally equal by using a Pseudo-Random Binary Sequence (PRBS) with a generator polynomial of  $X^{15} + X^{14} + 1$ . The PRBS initialisation sequence is either a sequence of 100101010000000 or dependent on some parameters, such as OFDM symbol number and BS identification. The PRBS generator structure is shown in Figure 2.2.

#### 2.4.2 FEC encoding

Forward Error Correction (FEC) coding is a channel coding, broadly used in wireless communication. FEC can detect and correct errors without the need to retransmit the data through the channel which may have a large propagation delay. It is achieved by

incorporating redundant bits into the transmitted data and recovering the data in the receiver side. However, the consequence of this approach is a lower net bit rate caused by the introduced redundant bits [19]. In a WiMAX PHY, an FEC encoding is built by concatenating a Reed-Solomon (RS) block code and a punctured convolutional code [2]. The RS code is used as the outer code, and the convolutional code is used as the inner code. It means that the information data are firstly passed through the RS encoder in a block format and then encoded by a convolutional encoder followed by a data puncturing. A zero-tailing byte is appended to the end of each data package generated by RS encoding to reset the convolutional encoder state. In WiMAX, the RS encoding is applied with all modulation schemes except BPSK. Other FEC modes such as block and convolutional turbo codes are optional in the fixed WiMAX standard, and not addressed in this thesis.

#### 2.4.2.1 Reed-Solomon encoding

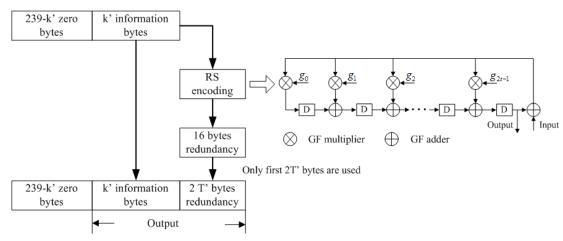

Due to its outstanding performance for error correction especially for burst errors, Reed-Solomon encoding [20] is widely used in communication and storage systems. An RS (n, k) code can correct up to t errors, where n represents the data block size after encoding, k represents the data block size before encoding and t is equal to (n-k)/2. In WiMAX specifications, an RS (255, 239) code is used to correct up to 8 errors, each sized one byte. The code generator polynomial is shown as Equation 2.1 [2]

$$g(x) = (x + \lambda^{0})(x + \lambda^{1})(x + \lambda^{2})...(x + \lambda^{2t-1}) = \sum_{i=0}^{2t} g_{i} x^{i}$$

(2.1)

where  $\lambda = 0x02$ . Both multiplication and addition operations in Equation 2.1 are performed in Galois Field (GF). Figure 2.3 shows the diagram of an RS encoder in WiMAX. Usually, the input block size k' is less than 239 bytes. Hence the first 239 - k' bytes need to be padded with zeros. As the RS (255, 239) code is systemic, the output block directly contains the input block. The information bytes are appended by 2T' bytes generated redundancy, where the value of T' depends on the modulation scheme and puncturing pattern.

Figure 2.3 Reed-Solomon encoder

#### 2.4.2.2 Convolutional encoding

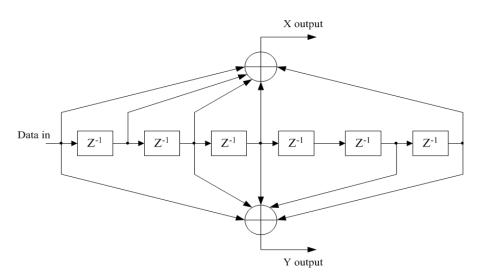

A convolutional encoder is based on a linear finite-state shift register which consists of K m-bit registers and n modulo-2 adders, where K is called constraint length [21]. A convolutional code has n generator polynomials, each of which represents the connections of all registers to one modulo-2 adder. By passing each m-bit information through the encoder, n output bits are generated through n modulo-2 adders. The code rate is defined as R = m/n. Shown in Figure 2.4, WiMAX uses a binary convolutional encoder with a constraint length of 7 and a code rate of 1/2 [2]. For m = 1, only K - 1 one-bit registers are needed, since the input bit can be directly fed into the modulo-2 adders. The

Figure 2.4 Binary convolutional encoder with a constraint length of 7 and a code rate of 1/2

two generator polynomials are G1(1,1,1,1,0,0,1) and G2(1,0,1,1,0,1,1), respectively.

In addition, theoretically the convolutional encoding operation can be graphically represented in three different ways: state diagram, tree diagram and trellis diagram. Among these diagrams, the trellis diagram is broadly used, due to its presentation of the passage of time. Here a brief introduction is given for the trellis diagram which is used in convolutional decoding as well. Figure 2.5 shows the trellis diagram for a simple convolutional encoder with a code rate of 1/2 and generator polynomials as G1(1,1,0) and G2(1,1,1). The horizontal axis represents time, while the vertical axis shows the encoder states which are the value of registers. Each new input bit causes a state transition which is represented by one connection from the current state to the next state through either a solid line for a 0 input or a dashed line for a 1 input. The corresponding output bits are shown in parentheses. The encoding operation starts from state 00. Figure 2.5 also highlights the encoding path for an input sequence of 1100 in red, where the most significant bit is fed into the encoder firstly. The generated output for this sequence is 11001001.

Figure 2.5 Trellis diagram representation of a simple convolutional encoder

#### 2.4.2.3 Puncturing

The convolutional code in WiMAX has a native code rate of 1/2 which means for every input bit, the convolutional encoder will introduce one redundant bit. If a higher code rate is demanded, a different encoder is needed. However, data puncturing can be used after a convolutional code to achieve higher code rates and also improve the flexibility of the

encoder without involving different encoders. During data puncturing, some bits in the encoder output are selectively deleted. Table 2.5 shows the puncturing patterns supported in WiMAX, which give different final convolutional code rates from 1/2 (no puncturing) up to 5/6 (minimal redundancy) [2]. In this table, "1" means corresponding bit is kept, otherwise removed.

1/2 Code rate 2/3 3/4 5/6 X 1 10 101 10101  $\boldsymbol{Y}$ 1 110 11010 11  $X_1Y_1$  $X_1Y_1Y_2$  $X_1Y_1Y_2X_3$ Output  $X_1Y_1Y_2X_3Y_4X_5$

Table 2.5 Puncturing patterns in WiMAX

# 2.4.3 Interleaving

The data transmitted in channels with multipath fading may suffer burst errors which can not be easily corrected by FEC codes. An effective method is interleaving the coded bits before the modulation, so that the burst errors can be distributed to different modulated data symbols and then corrected by FEC decoding [21]. In WiMAX, the interleaver involves two permutations given in Equations 2.2 and 2.3 [2], respectively.

$$m_k = (N_{cbps}/12) \times k_{mod12} + floor(k/12)$$

$k = 0,1,...,N_{cbps} - 1$  (2.2)

$$j_k = s \times floor(m_k / s) + (m_k + N_{cbps} - floor(12 \times m_k / N_{cbps}))_{mod(s)}$$

$k = 0, 1, ..., N_{cbps} - 1$  (2.3)

where k,  $m_k$  and  $j_k$  are the indices before and after the first and second permutations, respectively, and  $s = ceil(N_{cpc}/2)$ .  $N_{cpc}$  represents the number of coded bits per subcarrier and depends on the modulation scheme. While  $N_{cbps}$  represents the interleaver block size or coded bits per OFDM symbol, decided by both the modulation scheme and the

number of subchannels. In the receiver side, de-interleaving is performed in two permutations as well, but in an inverse direction, given in Equations 2.4 and 2.5.

$$m_j = s \times floor(j/s) + (j + floor(12 \times j/N_{cbps}))_{mod(s)}$$

$j = 0,1,...,N_{cbps} - 1$  (2.4)

$$k_{j} = 12 \times m_{j} - (N_{cbps} - 1) \times floor(12 \times m_{j} / N_{cbps})$$

$j = 0,1,...,N_{cbps} - 1$  (2.5)

where j,  $m_j$  and  $k_j$  are the indices before and after the first and second permutations, respectively.

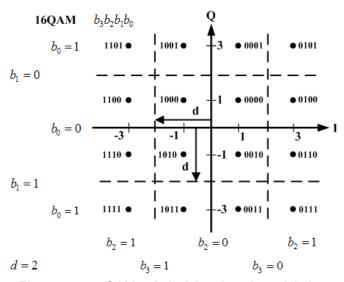

# 2.4.4 Data modulation

After interleaving, the data bits are mapped to constellation points, which are complex valued symbols, by data modulation or symbol mapping. Each symbol can represent one-bit or several bit data according to the modulation scheme. In WiMAX, various modulation schemes are supported, including BPSK, Quadrature Phase-Shift Keying (QPSK), 16QAM

Figure 2.6 BPSK, QPSK, 16QAM and 64QAM modulation schemes in WiMAX

and 64QAM [2]. Among these schemes, BPSK is most robust and 64QAM offers the highest data rate. Figure 2.6 shows the constellations for each modulation scheme. For normalisation, the absolute value of each constellation point is multiplied with a factor c shown in Figure 2.6.

# 2.4.5 OFDM processing

One of the major challenges for high-data-rate wireless broadband systems is the Intersymbol Interference (ISI) due to the multipath propagation. ISI becomes very severe when the symbol time  $T_s$  is much less than the channel delay spread  $\tau$ . It is especially true for WiMAX which has a long range and a high data rate [18]. In WiMAX, OFDM is used to overcome the ISI. OFDM is a popular multicarrier modulation technology widely used in many high-data-rate systems such as Wi-Fi and DSL. In a WiMAX physical layer, OFDM processing is one of key computation functions, composed of pilot insertion, DC and guard band insertion, inverse FFT (IFFT) and Cyclic Prefix (CP) extension in downlink processing together with CP removal, FFT, pilot removal, DC and guard band removal in uplink processing. In WiMAX, after data modulation, OFDM splits a high-rate single carrier into N low-rate subcarriers, each of which is orthogonal to each other and does not affect the encoded data on other subcarriers. Then OFDM uses IFFT to create a composite OFDM symbol stream by taking the encoded data of each subcarrier [22]. Therefore, the OFDM symbol time becomes  $T_s * N$  which can be significantly larger than  $\tau$ . Additionally through the use of CP, the channel can be made entirely ISI-free. Usually, for fixed WiMAX OFDM, there are 256 subcarriers consisting of 192 information subcarriers, 8 pilots, one Direct Current (DC) subcarrier and 55 guard subcarriers [2]. Figure 2.7 shows the frequency domain representation of an OFDM symbol for fixed WiMAX. While Figure 2.8 illustrates the OFDM downlink processing in the transmitter side for fixed WiMAX. In the receiver side, the OFDM uplink processing restores the high-rate single carrier by using FFT and removing CP, DC, guard band as well as pilots. In the following subsections, each sub-block

Figure 2.7 Frequency domain representation of an OFDM symbol in fixed WiMAX

Figure 2.8 OFDM downlink processing in the transmitter side of fixed WiMAX

of OFDM is described.

#### 2.4.5.1 Pilot modulation and insertion

In fixed WiMAX OFDM, eight subcarriers carry pilot signals which are used for synchronisation in the receiver side. The values of DL and UL pilots for OFDM symbol k are obtained from Equations 2.6 and 2.7, respectively [2], where  $w_k$  is generated by a PRBS with a generator polynomial of  $X^{11} + X^9 + 1$ , as shown in Figure 2.9. The PRBS initialisation sequences for downlink and uplink are given in Figure 2.9 as well. Each pilot is BPSK modulated and inserted into the corresponding position of an OFDM symbol as illustrated in Figure 2.7.

DL:

$$c_{-88} = c_{-38} = c_{63} = c_{88} = 1 - 2w_k$$

and  $c_{-63} = c_{-13} = c_{13} = c_{38} = 1 - 2\overline{w_k}$  (2.6)

UL:

$$c_{-88} = c_{-38} = c_{13} = c_{38} = c_{63} = c_{88} = 1 - 2w_k$$

and  $c_{-63} = c_{-13} = 1 - 2\overline{w_k}$  (2.7)

Figure 2.9 PRBS for pilot modulation

#### 2.4.5.2 DC and guard band insertion

In fixed WiMAX OFDM, there are 56 null subcarriers which are not allocated any transmit power [2]. These subcarriers include one DC subcarrier and 55 guard subcarriers whose positions in OFDM frequency domain are shown in Figure 2.7. The DC subcarrier, whose frequency is equal to the centre frequency of radio frequency, is used to prevent any saturation effect or DC offset suffered by the receiver side. Guard subcarriers are located at the edge of the spectrum to reduce the interference between a WiMAX channel and its neighbour channels. Another reason to insert the guard band is that the size of FFT is always equal to 2n, some dummy subcarriers should be padded to both edges [18].

## 2.4.5.3 FFT/IFFT

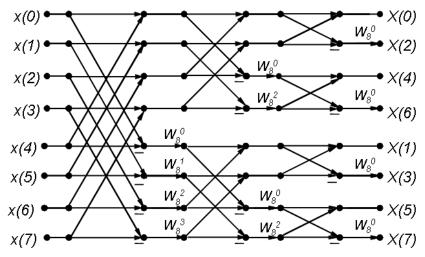

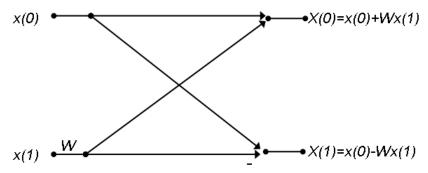

In OFDM processing, IFFT and FFT are used in the transmitter and receiver, respectively. An N-point IFFT transforms N frequency domain data into N time domain data, while FFT performs the opposite operation. IFFT and FFT have very similar structures. There are various algorithms to implement FFT/IFFT including radix-2 [23], radix-4 [24], split-radix [25] and so on. In this thesis, a simple and popular radix-2 algorithm, which is suitable for 2n point FFTs, is used. Figure 2.10 shows the data flow graph of an 8-point radix-2 FFT, where the horizontal axes signify the computation stages. There are in total 3 stages for an 8-point radix-2 FFT, and each stage has four butterfly operations. A signal flow

Figure 2.10 Data flow graph of an 8-point radix-2 FFT

Figure 2.11 Signal flow representation of a radix-2 butterfly

representation of a radix-2 butterfly is given in Figure 2.11 where W, called twiddle factor, is a trigonometric constant coefficient. After the transformation, the order of output data should be reversed into the numerical order.

# 2.4.5.4 Cyclic prefix extension

After the IFFT operation, the interference between symbols is eliminated. However each OFDM symbol still suffers Inter-Carrier Interference (ICI) or ISI within one OFDM symbol. It is because of the feature of the multicarrier modulation where many subcarriers are tightly packed into one channel, so that even small frequency shifts will cause ICI [22]. To overcome ICI, a guard time is inserted in front of each OFDM symbol. In OFDM, the guard time is implemented by duplicating a tail portion of an OFDM symbol at the beginning of this symbol. This method is termed as cyclic prefix extension. In the receiver side, the CP

will be removed before FFT performs. The ratio of CP length to useful symbol length is called guard fraction G. As shown in Figure 2.8, after the cyclic prefix extension, the symbol time becomes  $(1+G)\times T'_s$ . Obviously, a long guard time or large G will reduce the net bit rate, while a too short guard time or small G would not protect symbols from ICI. In WiMAX, G can have a value of  $\{1/4, 1/8, 1/16, 1/32\}$ . Many multi-core WiMAX solutions (e.g. Freescale WiMAX solution [26]) use 1/16 as the value of G. For the sake of comparison, a fraction of 1/16 is used in this thesis.

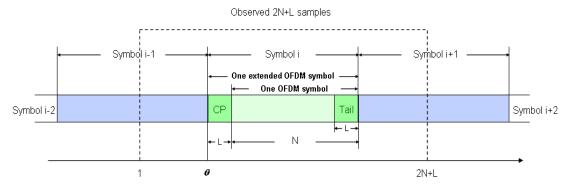

# 2.4.6 Synchronisation

The synchronisation block performs the symbol timing synchronisation to determine the symbol arrival time offset and the optimal timing instant by using the maximum likelihood (ML) estimation algorithm [27]. As shown in Figure 2.12, assume that we observe 2N+L consecutive samples represented in a 1-D vector  $\mathbf{r} [r(1)\cdots r(2N+L)]$  and these samples contain one complete CP extended OFDM symbol consisting of N+L samples, In Figure 2.12, N is the length of an OFDM symbol, L is the length of CP, and  $\theta$  is the unknown time offset. The ML estimation of  $\theta$  can be obtained by Equation 2.8 [28].

$$\hat{\theta_{ML}} = \arg \max_{\theta} \{ |\gamma(\theta)| - \rho \Phi(\theta) \}$$

(2.8)

where

$$\gamma(\theta) = \sum_{k=\theta}^{\theta+L-1} r(k) r^*(k+N)$$

,  $\Phi(\theta) = \frac{1}{2} \sum_{k=\theta}^{\theta+L-1} |r(k)|^2 + |r(k+N)|^2$  and  $\rho = \frac{SNR}{SNR+1}$ .

Figure 2.12 Timing synchronisation

# 2.4.7 Data demodulation

In the receiver side, the soft decision based data demodulation restores the original bits from the complex valued symbols by comparing the values of real and imaginary parts with some threshold values [2]. Figure 2.13 shows the soft decision demodulations for 16QAM where *d* is the threshold. 64QAM has more threshold values but maintains the similar idea of 16QAM demodulation. As for BPSK and QPSK, the original bits can be easily recovered according to the sign of the real and imaginary parts, as shown in Figure 2.6.

Figure 2.13 16QAM soft decision data demodulation

# 2.4.8 FEC decoding

In the receiver side, FEC decoding performs the inverse order of FEC encoding, and consists of de-puncturing, Viterbi decoding used to decode convolutional codes and Reed-Solomon decoding. The de-puncturing is simply performed by inserting 0 at the punctured positions. Viterbi and RS decoding are described in the following subsections.

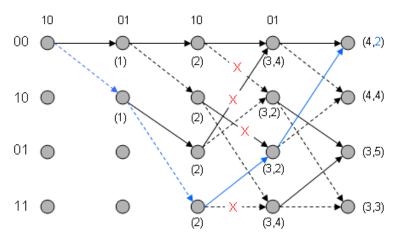

# 2.4.8.1 Viterbi decoding

The basic idea behind the decoding of convolutional codes is to compare the received sequence with all possible valid sequences, by using the trellis diagram. In WiMAX PHY,

Figure 2.14 Viterbi decoding process for a convolutional code with a 1/2 code rate

the Viterbi algorithm [29] is applied to decode convolutional codes. The Viterbi algorithm allows multiple possible paths calculated concurrently and is much faster than other decoding algorithms like Fano algorithm which deals with only one path at a time. However, the Viterbi algorithm costs more resources if implemented in hardware. The Viterbi algorithm calculates branch metrics between the incoming bits and each possible branch of a state in the trellis diagram, and then accumulates the metric values along each path to generate a path metric. When two possible paths converge on one state node, the path with the lower path metric is kept as a survivor, with the other one discarded. Eventually, only the path with the lowest path metric is the ultimate survivor. Usually the Hamming distance is used as the metric. Figure 2.14 shows the decoding process for the convolutional code in Figure 2.5 by using the Viterbi algorithm. Assuming the received sequence is 10011001, it has two bit errors compared to the output sequence 11001001 of the convolutional encoder. In Figure 2.14, the Hamming distance for each path is shown in parentheses at each state point which the path reaches. The discarded paths have a red cross on them. Finally, the path with lowest Hamming distance of 2 is the survivor, highlighted in blue. The corresponding decoded sequence is 11001001, matching the output sequence of the encoder shown Figure 2.5.

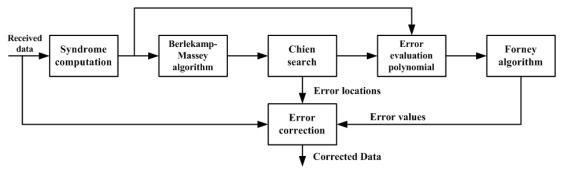

#### 2.4.8.2 Reed-Solomon decoding

In RS decoding, up to t errors (in WiMAX, t=8) can be detected and corrected following

Figure 2.15 Reed-Solomon decoding process

the process shown in Figure 2.15 [30]. Firstly the received data is fed into the syndrome computation block for detecting whether the data contains any errors. Then the generated syndromes are used for retrieving the locations and values of errors. The Berlekamp-Massey algorithm [30] is chosen to generate an error-location polynomial. If the degree of the location polynomial is greater than t which is the maximum number of correctable errors, the decoder is only able to detect the presence of errors and will stop without any further correction. Otherwise the roots of this polynomial are obtained by an exhaustive search performed in Chien search block. Once the errors have been located, the error evaluation polynomial and Forney algorithm blocks will calculate the error values. Then error values together with error locations and received data are sent to the error correction block for recovering the original data. Each of blocks shown in Figure 2.15 involves plenty of GF calculations, the detail of which can be found in [30].

# 2.5 Summary

This chapter has reviewed current mainstream broadband access solutions including both wired and wireless technologies. Some comparisons were given to exhibit the advantages of WiMAX over its counterparts. Due to its merits, WiMAX was demonstrated to be a promising solution to promote ubiquitous Internet access. As the main target of this thesis is fixed WiMAX, Section 2.4 introduced the structure of fixed WiMAX physical layer and described the function and algorithm for each main block of both transmitter and receiver.

# Chapter 3 Multi-core Processors and Reconfigurable Architectures

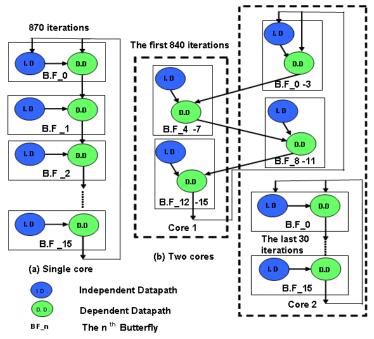

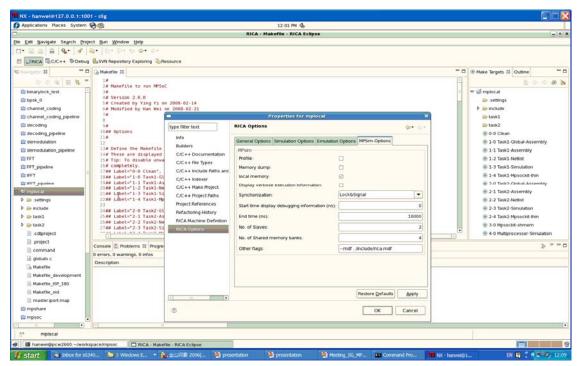

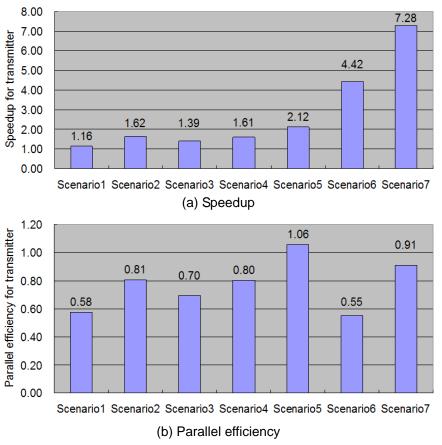

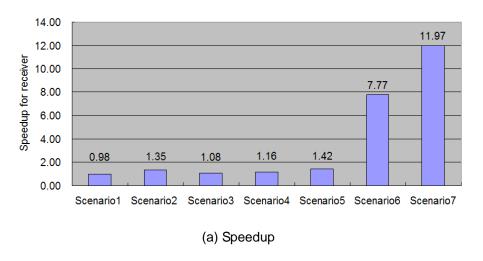

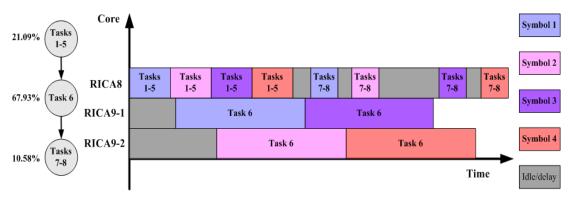

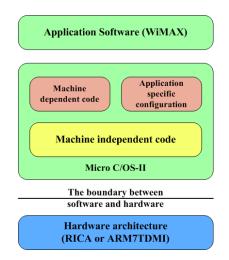

# 3.1 Introduction