# Methods and Structures for Characterising Integrated Circuit Interconnect Materials and Processes

Byron Jon Roderick Shulver

A thesis submitted for the degree of Doctor of Philosophy. **The University of Edinburgh**. November 2007

## Abstract

Advances in the semiconductor industry have introduced the demand for smaller devices with higher performance. Specific interest to this work is the manner in which new materials and processes are being adopted for the fabrication of IC interconnects. Process monitoring and material characterisation is achieved with the use of microelectronic test structures to assist in the development of new fabrication techniques. This thesis investigates a number of emerging areas in interconnect metrology with a concentration on the use of electrical test structures to extract parameters such as line width, sheet resistance, and the overlay of multiple layers.

To address the issue of calibrating optical overlay tools, a novel design for an overlay test structure is described for use as a reference material. It was developed to demonstrate the implementation of a technique devised in collaboration with researchers at NIST and allows the cross correlation between measurements of overlay taken with electrical and optical techniques. This evaluation was demonstrated successfully with close agreement of less than 10 nm between electrical and SEM extracted overlay values from the fabricated test structures.

The next portion of this thesis presents a test structure to evaluate the emerging field of copper interconnects. It is designed to allow electrical measurements from all-copper features, and therefore removes the complications introduced by barrier materials. The structure is intended to be used for reference material applications and traceability of the measurements is provided by a number of previously reported techniques which claim line width measurement accuracy to within 5 nm. The process is then used to fabricate a test chip containing line widths from 10 to 0.55  $\mu$ m for the evaluation of various methods for ECD extraction. In this work, sheet resistance is extracted from three varieties of test structure designs with an investigation to support the results obtained. Following this, Kelvin-tapped bridge resistor structures are measured electrically to allow the line width to be determined. Three different approaches to analysing this parameter are examined and compared to line width values taken from SEM imaging. The closest agreement between SEM and ECD values is achieved using a new method presented in this thesis. Furthermore, an investigation was conducted to support the choice of this algorithm and the results obtained.

The final area of this work concentrates on the developing field of MEMS thick film power devices. An implementation of traditional interconnect test structures in thick copper conductive tracks is conducted to evaluate their potential for process and material characterisation. This was realised with the combination of thick film photoresist processing and copper electroplating to fabricate the test structures. The results of this study revealed that the methods used in standard interconnect test structures are not easily transferred to the MEMS field. An algorithm is presented which permits values for line width to be extracted from Kelvin-tapped bridge resistors without the use of predetermined sheet resistance values.

## Declaration of originality

I hereby declare that the research recorded in this thesis, unaided except where otherwise acknowledged in the text, and the thesis itself was composed and originated entirely by myself in the School of Engineering and Electronics at The University of Edinburgh. This work has not been submitted for any other degree of professional qualification.

## Acknowledgements

I would like to take the time to thank those who assisted me throughout the duration of this work at the Scottish Microelectronics Centre (SMC), University of Edinburgh. First, I would like to thank my supervisors Prof. Anthony Walton and Dr. Tony Snell for providing me the opportunity to conduct this project and for guidance during my time here. I would also like to thank the staff at the SMC for their support and advice, namely; Richard Blair, Sue Bond, Andrew Brooks, Dr. Andrew Bunting, Ann Cunningham, Dr. Camelia Dunare, Hugh Frizell, Alan Gundlach, Dr. Les Haworth, Gerry McDade, Valerie McDermot, Ewan McDonald, Dr. Peter Lomax, Alan Ross, Alec Ruthven, Dr. Stewart Smith, Dr. Tom Stevenson, Dr. Jon Terry, Kevin Tierney, and anyone I may have omitted.

A large portion of this work was conducted in collaboration with researchers from the National Institute of Standards and Technology (NIST). I am greatly appreciative of the advice and support provided by Dr. Richard Allen and Dr. Michael Cresswell of NIST. Furthermore, I would like to thank National Semiconductor Corp. (NSC) for giving me the chance to work with them on the collaborative power MEMS device project. I would like to extend this thanks to Dr. Thomas McMullen, Dr. Terry Dyer, Dr. Martin Fallon, Dr. Peter Hopper, Dr. Peter Johnson, and Dr. Peter Smeys of NSC.

I would also like to acknowledge the financial support of the Engineering and Physical Sciences Research council for funding my Ph.D. studies. Without this backing I would not have been able to accept a place at the University.

Out side of the University environment I would like to thank my friends and family for their support throughout the entirety of my education. I especially thank my parents, brothers and sisters for their encouragement and backing during this period as well as my parents financial support for my undergraduate studies. I would also like to thank Michelle for her support over the last three years.

# Contents

|   |      | Declaration of originality                              |

|---|------|---------------------------------------------------------|

|   |      | Contents v                                              |

|   |      | List of figures                                         |

|   |      | List of tables                                          |

|   |      | Acronyms and abbreviations xiii                         |

|   |      | Nomenclature                                            |

| 1 | Intr | oduction 1                                              |

|   | 1.1  | Motivation                                              |

|   | 1.2  | Microelectronic test structures                         |

|   | 1.3  | Objective                                               |

|   | 1.4  | Thesis overview                                         |

| 2 | Bac  | kground to Semiconductor Metrology 9                    |

| - | 2.1  | Introduction                                            |

|   | 2.2  | Physical metrology                                      |

|   |      | 2.2.1 Optical methods                                   |

|   |      | 2.2.2 Electron microscopy                               |

|   |      | 2.2.3 Stylus profilometry                               |

|   |      | 2.2.4 Scanning probe microscopy                         |

|   | 2.3  | Electrical metrology                                    |

|   |      | 2.3.1 Four point probe                                  |

|   |      | 2.3.2 Test structures                                   |

|   | 2.4  | Reference material                                      |

|   | 2.5  | Conclusions                                             |

| 3 | Tacl | Structure for Optical-Electrical Overlay Calibration 33 |

| 5 | 3.1  | Introduction                                            |

|   | 3.2  | Background                                              |

|   | 0.4  | 3.2.1 Optical overlay measurement                       |

|   |      | 3.2.2 Electrical overlay measurement                    |

|   | 3.3  | Design                                                  |

|   | 3.4  | Fabrication   43                                        |

|   | 3.5  | Results                                                 |

|   | 3.6  | Conclusions                                             |

|   |      |                                                         |

| 4 |      | rication of All-Copper ECD Structures 52                |

|   | 4.1  | Introduction                                            |

|   | 4.2  | Background                                              |

|   |      | 4.2.1 Copper damascene process                          |

|   | 10   | 4.2.2 Barrier layers                                    |

|   | 4.3  | Requirements for a Cu FCD test structure 58             |

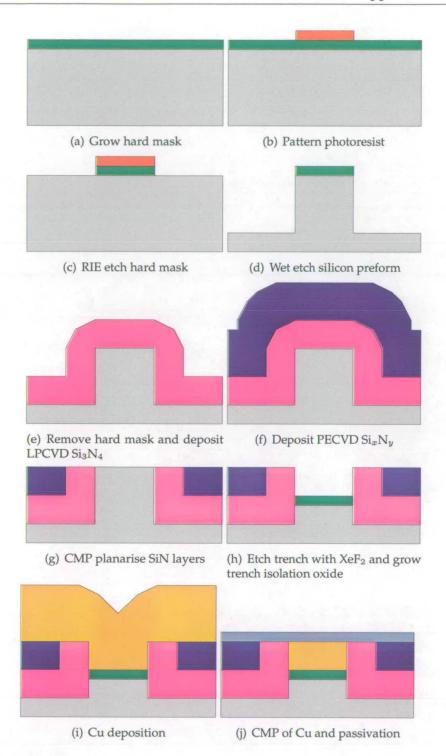

|   | 4.4   | Fabrication process                                                 |

|---|-------|---------------------------------------------------------------------|

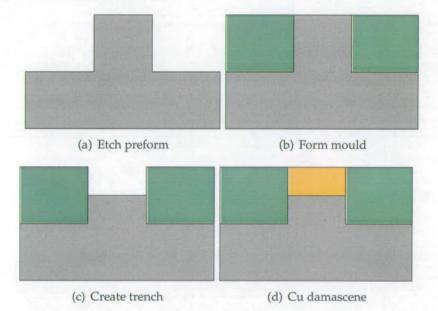

|   |       | 4.4.1 Silicon preform                                               |

|   |       | 4.4.2 Creation of the preform mould                                 |

|   |       | 4.4.3 Create trench                                                 |

|   |       | 4.4.4 Copper damascene                                              |

|   | 4.5   | Testing strategy                                                    |

|   | 4.6   | Conclusions                                                         |

|   |       |                                                                     |

| 5 | ECE   | D Extraction from All-Copper Test Structures90                      |

|   | 5.1   | Introduction                                                        |

|   | 5.2   | Background                                                          |

|   | 5.3   | Method                                                              |

|   |       | 5.3.1 Sheet resistance                                              |

|   |       | 5.3.2 Line width                                                    |

|   | 5.4   | Results                                                             |

|   |       | 5.4.1 Sheet resistance                                              |

|   |       | 5.4.2 Line width                                                    |

|   | 5.5   | Conclusions                                                         |

|   |       |                                                                     |

| 6 |       | MS Test Structure Evaluation 113                                    |

|   | 6.1   | Introduction                                                        |

|   | 6.2   | Background                                                          |

|   |       | 6.2.1 Thick film photoresist 115                                    |

|   |       | 6.2.2 Electroplating                                                |

|   | 6.3   | Fabrication process                                                 |

|   |       | 6.3.1 Substrate preparation                                         |

|   |       | 6.3.2 Mould patterning                                              |

|   |       | 6.3.3 Track formation                                               |

|   |       | 6.3.4 Post processing                                               |

|   | 6.4   | Results                                                             |

|   |       | 6.4.1 Greek cross                                                   |

|   |       | 6.4.2 Kelvin bridge                                                 |

|   | 6.5   | Conclusions                                                         |

| 7 | Con   | clusions and Future Work 136                                        |

| , | 7.1   | Introduction                                                        |

|   | 7.2   | Conclusions                                                         |

|   | / the | 7.2.1 Test structure for optical-electrical overlay calibration 136 |

|   |       | 7.2.2 Fabrication of all-copper ECD structures                      |

|   |       | 7.2.3 ECD extraction from all-copper ECD structures                 |

|   |       | 7.2.4 Evaluation of test structures for MEMS                        |

|   | 7.3   | Future work                                                         |

|   |       | 7.3.1 Test structure for optical-electrical overlay calibration 141 |

|   |       | 7.3.2 Fabrication of all-copper ECD structures                      |

|   |       | 7.3.3 ECD extraction from all-copper ECD structures                 |

|   |       | 7.3.4 Evaluation of test structures for MEMS                        |

|   | 7.4   | Final remarks                                                       |

|   |       |                                                                     |

| A  | Publications |                                                                        | 153  |

|----|--------------|------------------------------------------------------------------------|------|

|    | A.1          | International Conference on Microelectronic Test Structures, ICMTS     |      |

|    |              | (Austin, Texas, USA, 2006)                                             | 154  |

|    | A.2          | International Conference on Microelectronic Test Structures, ICMTS     | 4.64 |

|    | 1 2          | (Tokyo, Japan, 2007)                                                   | 161  |

|    | A.3          | A.3 International Conference on Microelectronic Test Structures, ICMTS |      |

|    | Δ 1          | (Tokyo, Japan, 2007)                                                   | 108  |

|    | A.4          | (Gaithersburg, Maryland, 2007) [In Press]                              | 175  |

| B  | Proc         | ess Equipment                                                          | 181  |

|    | B.1          | Fabrication                                                            | 182  |

|    | B.2          | Physical metrology                                                     | 184  |

|    | <b>B.3</b>   | Electrical test                                                        | 185  |

| C  | C Run Sheets |                                                                        | 186  |

|    | C.1          | Fabrication of optical-electrical overlay calibration test structures  | 187  |

|    | C.2          | Fabrication of all-copper ECD test structures                          | 189  |

|    | C.3          | Fabrication of power MEMS test structures                              |      |

| Re | ferer        | aces                                                                   | 195  |

# List of figures

| 1.1<br>1.2 | Fabricated ACME 99 test chip demonstrating $2 \times n$ probe pad layout Schematic illustration of drop-in and scribe line arrangement for test                                                                        | 4        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | structure location                                                                                                                                                                                                     | 6        |

| 2.1        | Optical extraction of line width from Al track patterned on SiO <sub>2</sub>                                                                                                                                           | 12       |

| 2.2<br>2.3 | SEM extraction of line width from Al track patterned on SiO <sub>2</sub> HRTEM image of single crystal silicon showing the lattice planes (inset). Reproduced with permission from the National Institute of Standards | 14       |

| 2.4        | and Technology                                                                                                                                                                                                         | 16       |

| 2.5        | effect of the stylus on the extracted profile.                                                                                                                                                                         | 17       |

| 2.6        | Schematic illustration of the principles of atomic force microscopy AFM scan of an Al track patterned on SiO <sub>2</sub>                                                                                              | 19<br>20 |

| 2.7<br>2.8 | Schematic illustration of the principles of four-point probe measurements.<br>Schematic illustration of van der Pauw measurement of a structure with                                                                   | 23       |

| 2.0        | arbitrary shape and placement of contacts.                                                                                                                                                                             | 25       |

| 2.9        | Schematic illustration of a van der Pauw cloverleaf structure for                                                                                                                                                      | 20       |

|            | reduction of contact errors                                                                                                                                                                                            | 26       |

| 2.10       | Schematic illustration of commonly adopted patterned test structures<br>used to measure sheet resistance of hatched area based on van der Pauw                                                                         |          |

| 0.11       | method.                                                                                                                                                                                                                | 26       |

|            | Schematic illustration of a Kelvin-tapped bridge resistor structure A cross-bridge test structure for extracting sheet resistance and line                                                                             | 27       |

|            | width from a single structure                                                                                                                                                                                          | 28       |

| 3.1        | Schematic illustration of the overlay components of a multilevel                                                                                                                                                       |          |

| 2.0        | interconnect system.                                                                                                                                                                                                   | 35       |

| 3.2<br>3.3 | Schematic illustration of the optical overlay structure.                                                                                                                                                               | 36       |

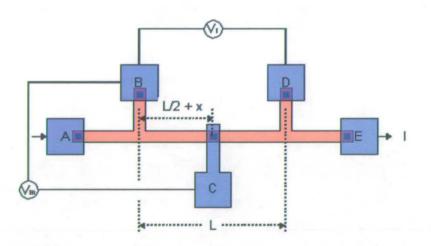

| 0.0        | Schematic illustration of the sliding wire potentiometer structure and measurement technique [59].                                                                                                                     | 37       |

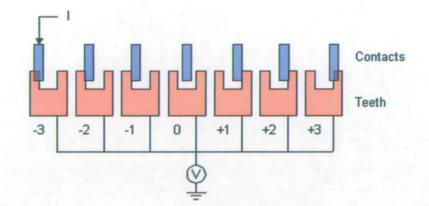

| 3.4        | Schematic illustration of the digital vernier structure with measurement                                                                                                                                               | 57       |

| 0.1        | principle [68].                                                                                                                                                                                                        | 39       |

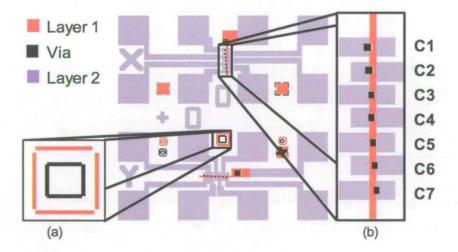

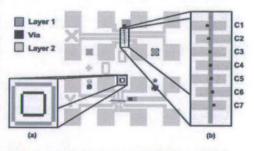

| 3.5        | Layout of single test cell of the NIST 47 design with (a) frame-in-frame                                                                                                                                               | 07       |

|            | structure and (b) diagonal arrangement of contacts.                                                                                                                                                                    | 40       |

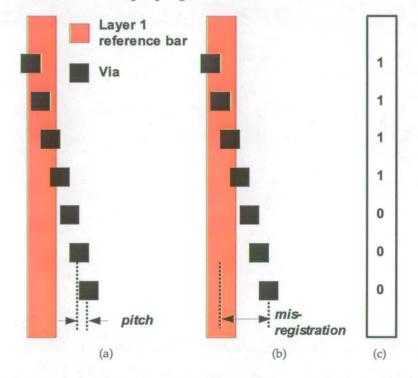

| 3.6        | Schematic illustration of reference bar with design related parameters                                                                                                                                                 |          |

|            | and corresponding binary signature                                                                                                                                                                                     | 41       |

| 3.7        | Layout of NIST 47 design; the test structure described is the 16 by 18                                                                                                                                                 |          |

| 2.0        | array of cells indicated.                                                                                                                                                                                              | 42       |

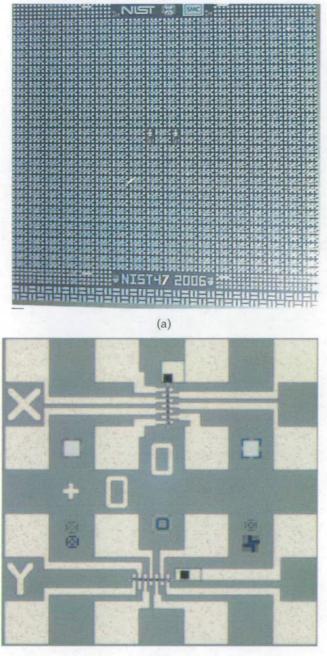

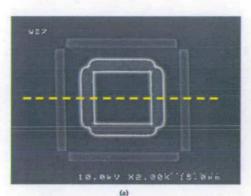

| 3.8        | Fabricated test chip with corresponding magnified image centre of test                                                                                                                                                 |          |

|            | cell                                                                                                                                                                                                                   | 45       |

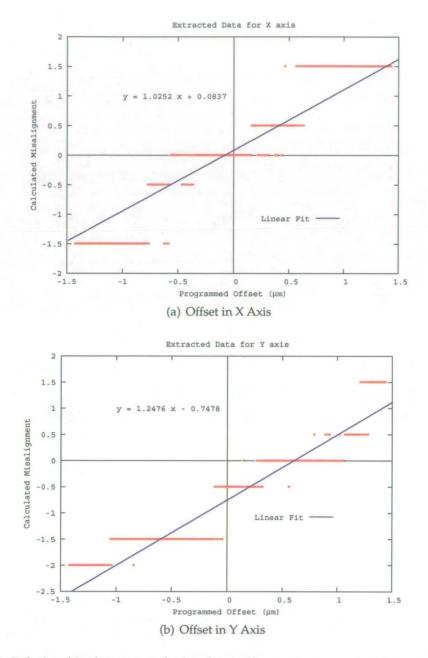

| 3.9  | Relationship between calculated misalignment measurements vs programmed structure offset for single die. | 48   |

|------|----------------------------------------------------------------------------------------------------------|------|

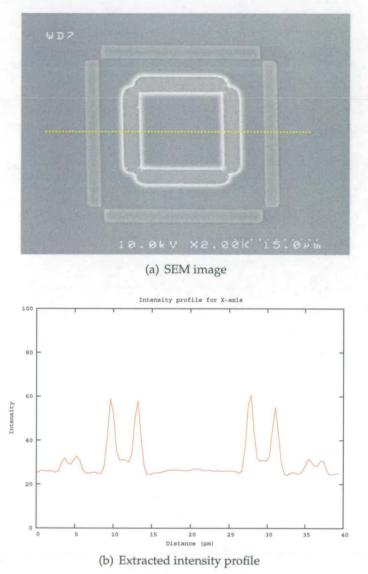

| 3.10 | SEM extraction of overlay achieved from frame-in-frame structure using intensity profile.                | 49   |

|      |                                                                                                          |      |

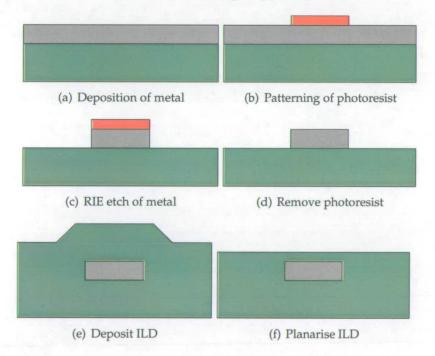

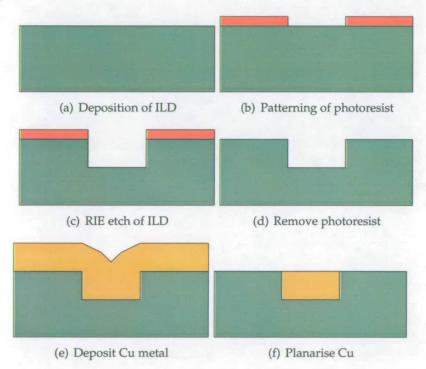

| 4.1  | Schematic illustration of the main steps in subtractive processing of                                    | = 4  |

| 10   | interconnects.                                                                                           | 54   |

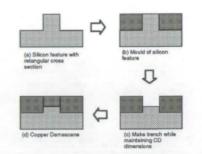

| 4.2  | Schematic illustration of the major steps in damascene processing of                                     | 55   |

| 4.3  | interconnects                                                                                            | 33   |

| 1.0  | ECD test structures                                                                                      | 59   |

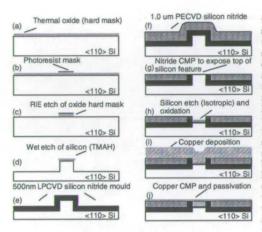

| 4.4  | Schematic illustration of the detailed process employed for all-copper                                   | 07   |

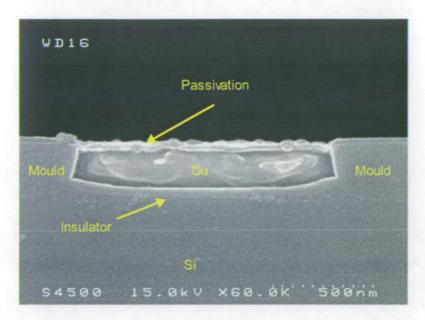

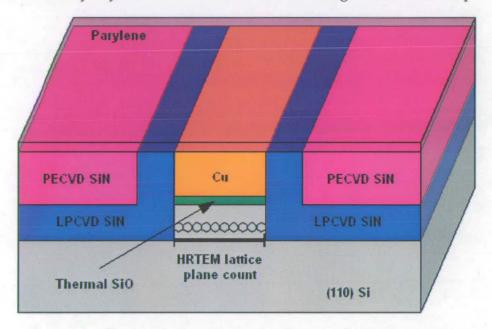

|      | ECD structure fabrication.                                                                               | 61   |

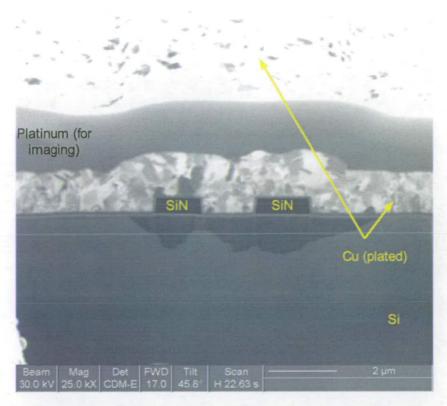

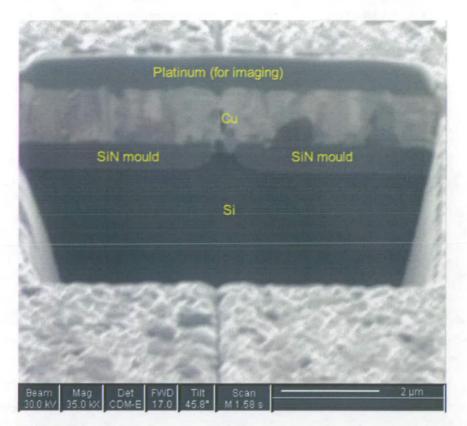

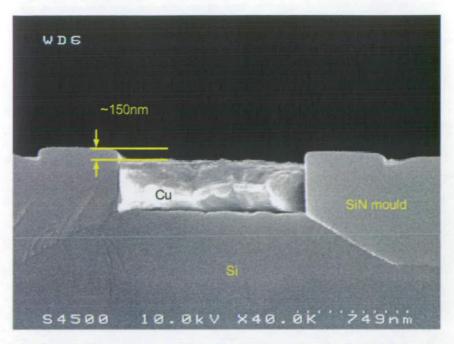

| 4.5  | Cross section of initial experimental batch to demonstrate feasibility of                                |      |

|      | Cu ECD process.                                                                                          | 62   |

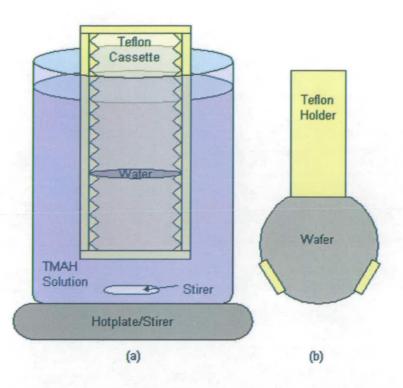

| 4.6  | Setup used for TMAH etching of Si wafers                                                                 | 65   |

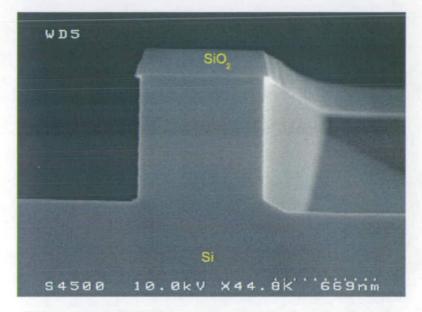

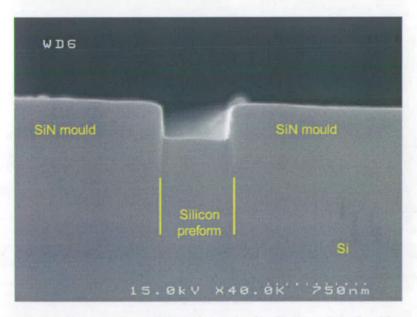

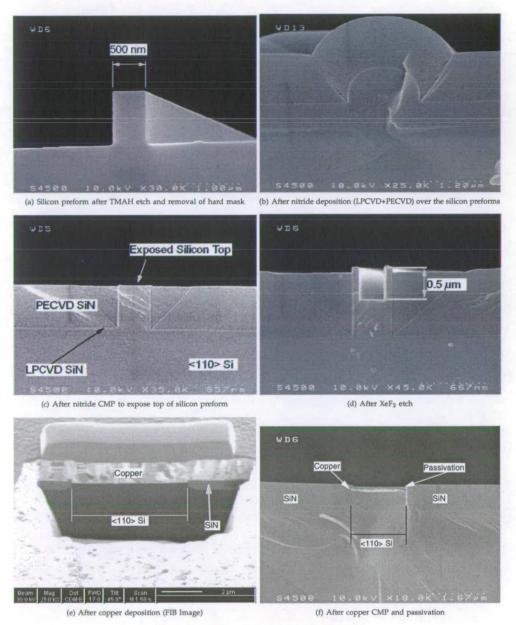

| 4.7  | Etched silicon preform with hard mask still in place                                                     | 67   |

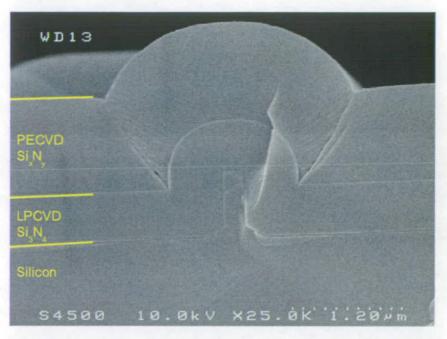

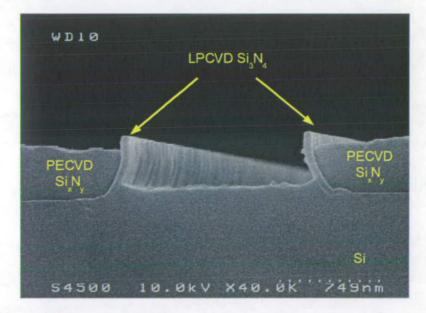

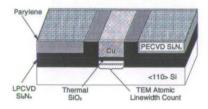

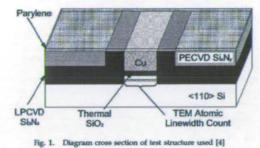

| 4.8  | Structure after deposition of both LPCVD and PECVD SiN                                                   | 69   |

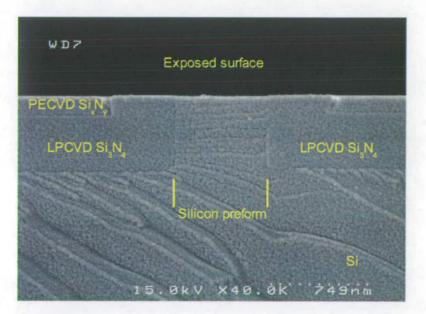

| 4.9  | Structure after CMP planarisation of the nitride layers                                                  | 70   |

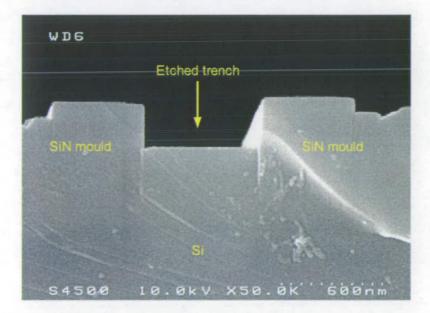

| 4.10 | Result of SF6 plasma etching of silicon preform to form trench.                                          | 71   |

| 4.11 | Result of XeF <sub>2</sub> vapour etching of silicon preform to form trench using                        | -    |

| 1.10 | HF dip prior to etch.                                                                                    | 73   |

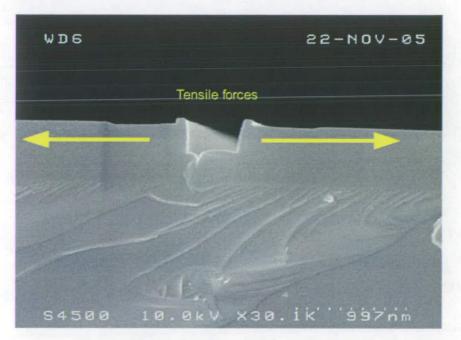

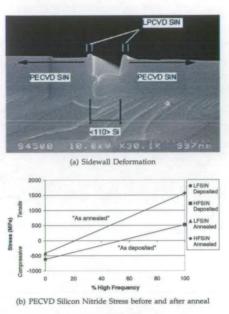

| 4.12 | Cross section demonstrating the sidewall deformation after the trench                                    | 17.4 |

| 1 12 | oxidation step                                                                                           | 74   |

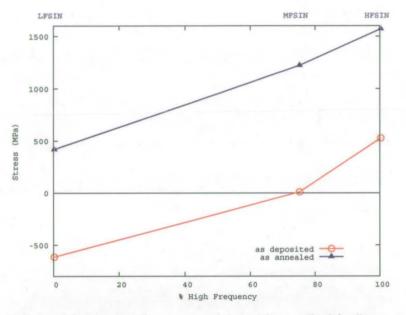

| 4.13 | annealed" and "as deposited" PECVD $Si_x N_y$ films                                                      | 76   |

| 4 14 | Cross sectional SEM of trench after XeF <sub>2</sub> etch and oxidation step                             | 76   |

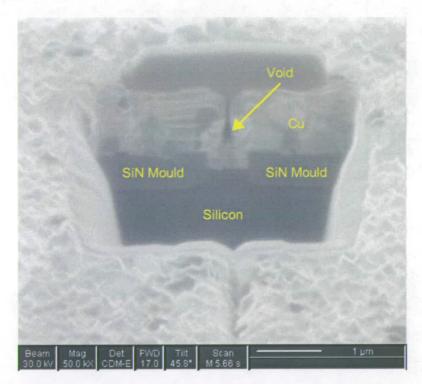

|      | FIB cross section demonstrating voids in narrow line width Cu tracks as                                  | 10   |

| 1120 | a result of DC PVD sputtering.                                                                           | 77   |

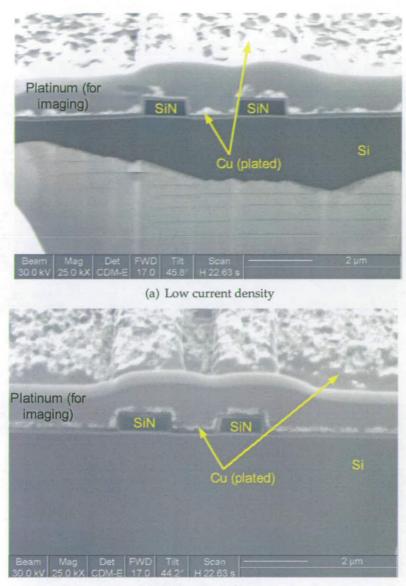

| 4.16 | FIB cross section of Cu electroplating experiments.                                                      | 79   |

|      | Simple plating setup used for deposition of Cu onto 3 inch wafers.                                       | 80   |

| 4.18 | FIB cross section of wafer with electroplated Cu film.                                                   | 81   |

| 4.19 | FIB cross section demonstrating the structure after PVD Cu deposition                                    |      |

|      | with RF bias without voids.                                                                              | 82   |

| 4.20 | Cross section demonstrating the structure after the Cu CMP stage using                                   |      |

|      | the iCue 5001 slurry.                                                                                    | 83   |

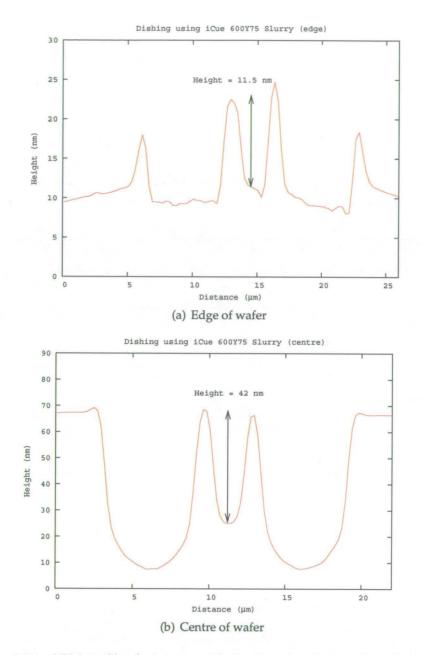

|      | AFM profile of a 2.5 $\mu$ m wide Cu line after CMP with 600Y75 slurry                                   | 85   |

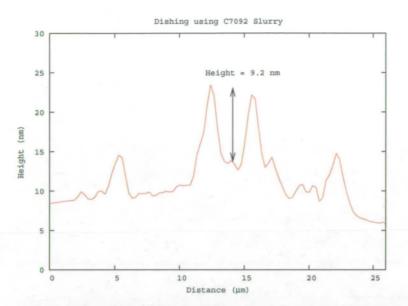

|      | AFM profile of 2.5 μm wide cu line after CMP with C7092 slurry.                                          | 86   |

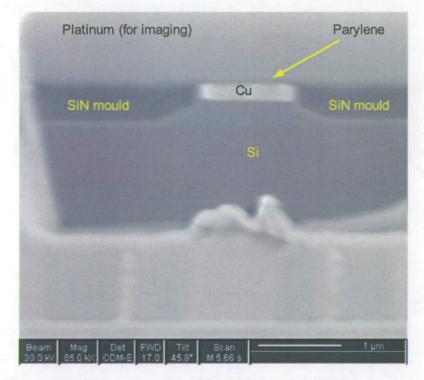

|      | FIB cross section of final fabricated Cu ECD test structure.                                             | 86   |

| 4.24 | Design of structure used for all-copper ECD reference material                                           | 87   |

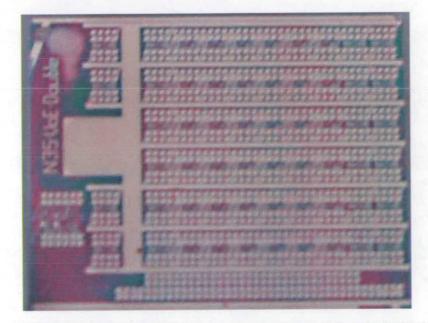

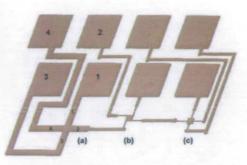

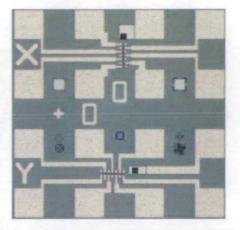

| 5.1  | Fabricated test chip used for Cu ECD analysis using the NIST 35 design.                                  | 94   |

| 5.2  | Test structures used to extract sheet resistance for Cu interconnect                                     |      |

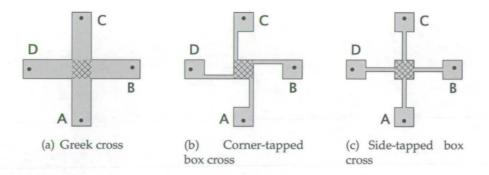

|      | features (a) Greek cross (b) corner-tapped box cross and (c) side-tapped                                 |      |

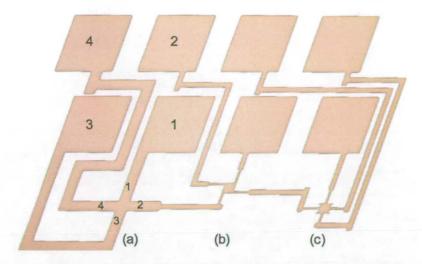

|      | box cross                                                                                                | 95   |

| 5.3  | Test structure used to extract line width for Cu interconnect features                                   | 96   |

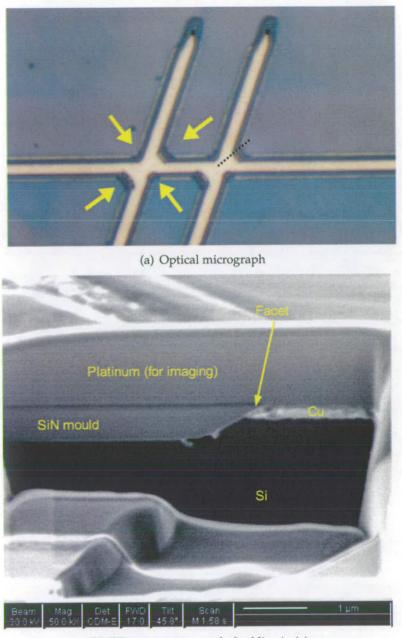

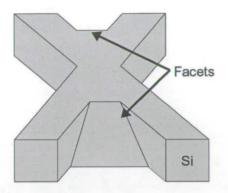

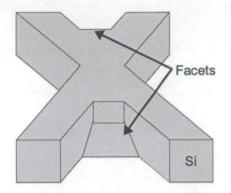

| 5.4  | Images identifying the presence of facets in intersecting angles of Cu lines.                            | 98   |

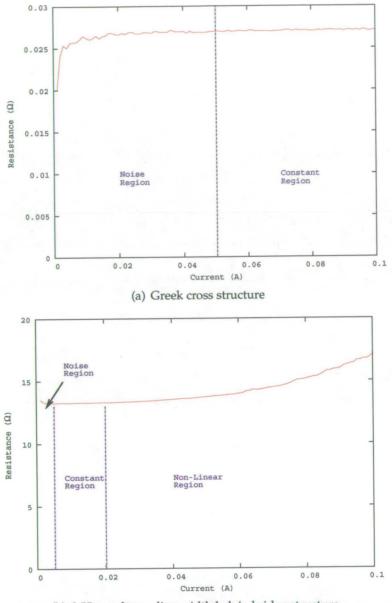

| 5.5  | Results of resistance versus current measurements on electrical test structures employed in this study. | 102  |

|------|---------------------------------------------------------------------------------------------------------|------|

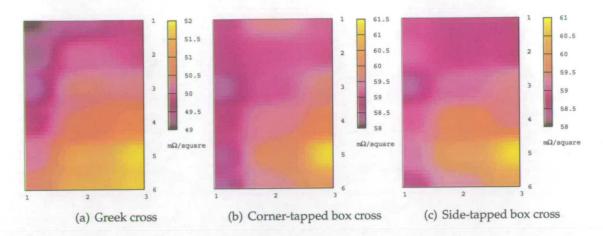

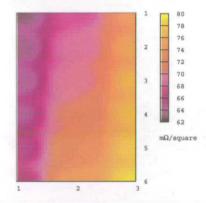

| 5.6  | Results of Rs values measured from a single die using the three van-                                    |      |

| 5.7  | der-Pauw structures shown in figure 5.2                                                                 |      |

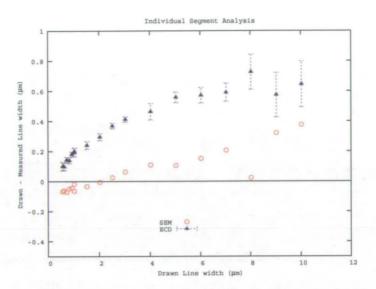

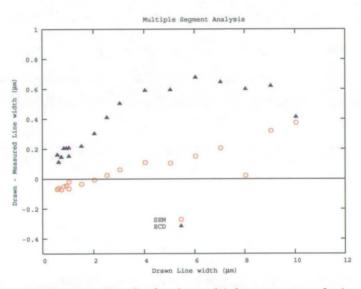

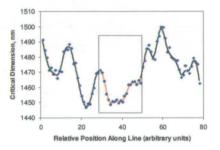

| 5.8  | Results for the individual segment analysis                                                             |      |

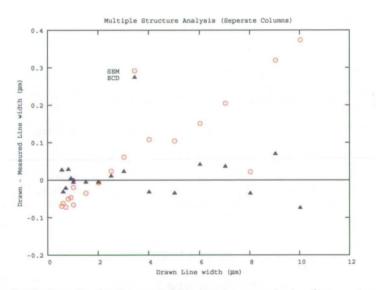

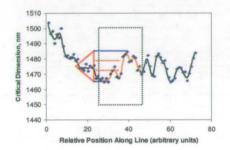

|      | Results for the multiple segment analysis                                                               | 107  |

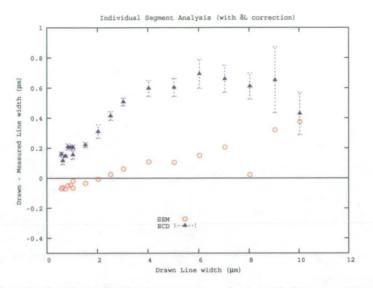

| 5.9  | Results for the individual segment analysis with $\delta L$ correction factor included                  | 108  |

| 5.10 |                                                                                                         |      |

|      | Results for the multiple structure analysis with all structures                                         |      |

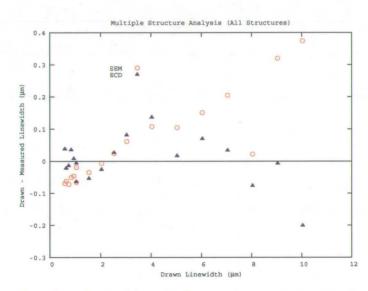

|      | Results of equivalent $Rs$ values extracted using the multiple structure                                | 207  |

|      | analysis.                                                                                               | 110  |

|      |                                                                                                         | 110  |

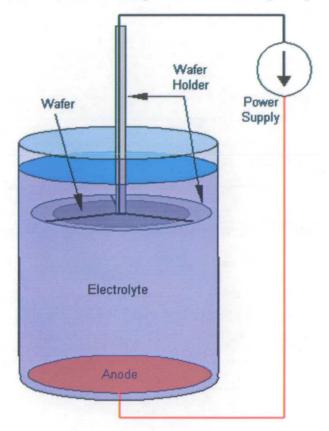

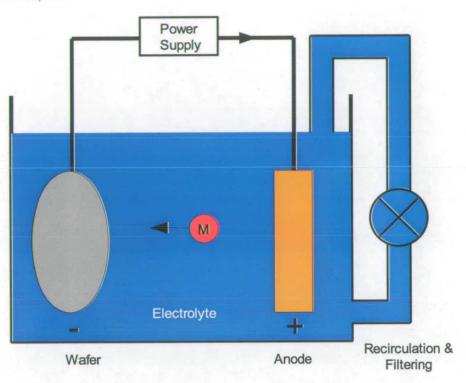

| 6.1  | Typical setup employed in the electrochemical deposition of metals on                                   |      |

| ( )  | semiconductor wafers.                                                                                   |      |

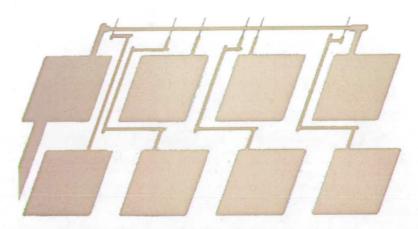

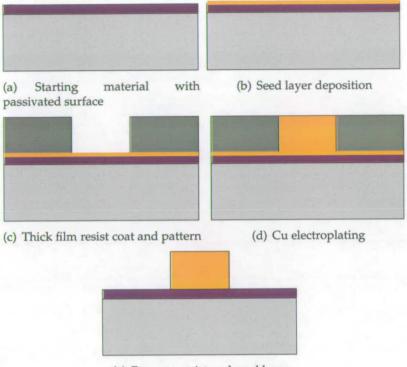

| 6.2  | Overview of MEMS mould process to form Cu conductor                                                     | 119  |

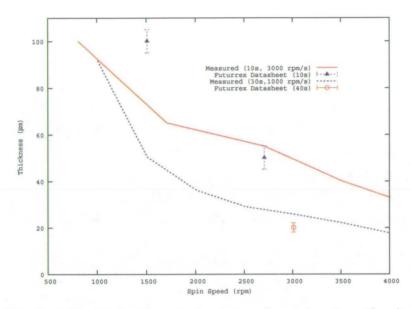

| 6.3  | Result of film thickness against spin speed experiments. Also displayed                                 |      |

|      | are the data sheet values provided by Futurrex for reference                                            | 121  |

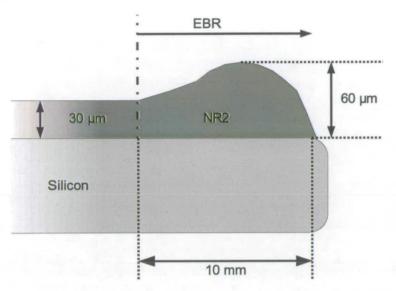

| 6.4  | Schematic illustration of the dimensions of the edge bead effect on the                                 |      |

|      | resist. Included is the point at which edge bead removal (EBR) is used                                  |      |

|      | to dissolve the thicker resist.                                                                         |      |

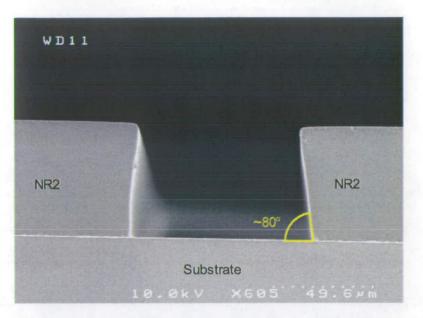

| 6.5  | Cross sectional SEM demonstrating the result of a PEB using 80 °C                                       |      |

| 6.6  | Cross sectional SEM demonstrating the result of a PEB using 100 °C                                      | 124  |

| 6.7  | Cross sectional SEM demonstrating the dome shaped top to the Cu track                                   |      |

|      | or the "bread loaf" effect                                                                              | 127  |

| 6.8  | Cross sectional SEM demonstrating the near rectangular shaped profile                                   |      |

|      |                                                                                                         | 127  |

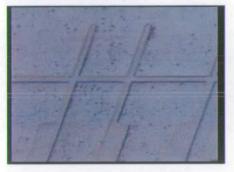

| 6.9  | Optical micrograph of the cross-bridge test structure used in this study                                |      |

|      |                                                                                                         | 132  |

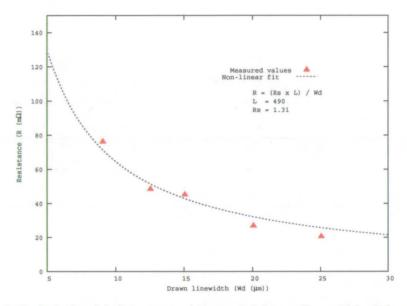

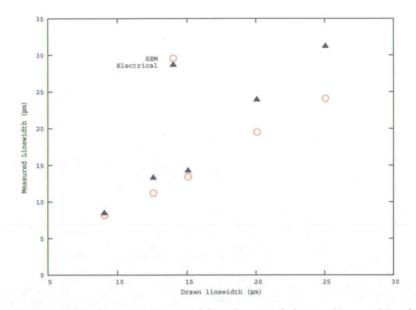

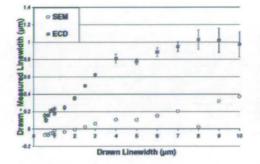

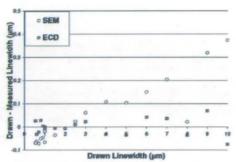

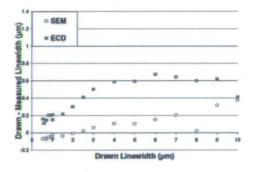

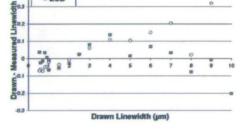

| 6.11 | Relationship between line width values and drawn line width of the                                      |      |

|      | structures for both electrical and SEM measurements.                                                    | 133  |

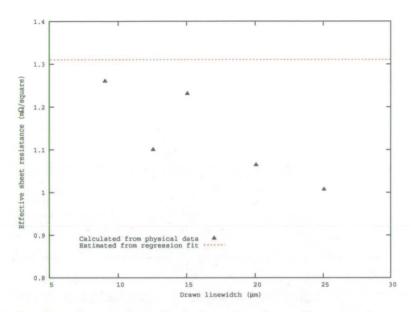

| 6.12 | Results of equivalent Rs values based on dimensional measurements                                       |      |

|      | and resistance values for each structure. Extracted Rs value from the                                   |      |

|      | Kelvin bridge measurements (dashed line) are presented for comparison.                                  | 134  |

| 7.1  | Illustration of a portion of the silicon showing a typical representation                               |      |

|      | of facets seen using single anisotropic wet etch.                                                       | 144  |

| 7.2  | Schematic illustration of the process suggested for the hybrid etch                                     | ***  |

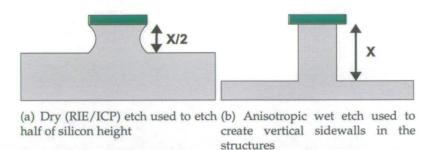

|      | approach to reduce the facet formation.                                                                 | 145  |

| 7.3  | Illustration of a portion of the silicon showing expected result of using                               | 110  |

| 1.0  | hybrid etch approach.                                                                                   | 145  |

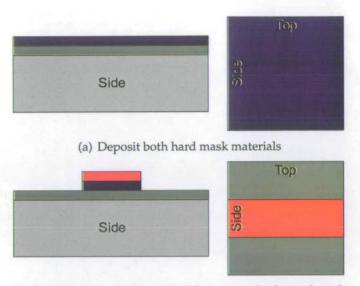

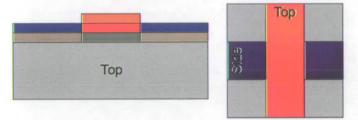

| 7.4  | Schematic illustration of the process steps involved in dual-layer                                      | 140  |

|      | patterning technique. (Note direction cross section is drawn from, top                                  |      |

|      | or side)                                                                                                | 1/7  |

| 7.5  | SEM of a sample fabricated using the dual-layer patterning technique.                                   | 1-1/ |

|      | Note that there is still a small degree of rounding at the intersecting                                 |      |

|      | angle between the two lines.                                                                            | 1/9  |

|      | angle between the two mies                                                                              | 140  |

| 7.6 | Layout of test chip for dual-l | yer patterning evaluation | 149 |

|-----|--------------------------------|---------------------------|-----|

|-----|--------------------------------|---------------------------|-----|

# List of tables

| 3.1 | Selected data from electrical overlay structure                         | 46 |

|-----|-------------------------------------------------------------------------|----|

| 4.1 | Results of uniformity experiments for TMAH wet etch on (110) Si wafers. | 66 |

| 4.2 | Plating recipe used for damascene copper plating trials                 | 78 |

| 4.3 | Recommended process conditions for Cu CMP trials.                       | 83 |

| 5.1 | Drawn dimensions of Kelvin-tapped bridge resistor structures            | 96 |

# Acronyms and abbreviations

| AFM   | Atomic Force Microscope                            |

|-------|----------------------------------------------------|

| Al    | Aluminium                                          |

| CD    | Critical Dimension                                 |

| CMOS  | Complementary Metal Oxide Semiconductor            |

| CMP   | Chemical Mechanical Polishing                      |

| Cu    | Copper                                             |

| CVD   | Chemical Vapour Deposition                         |

| DC    | Direct Current                                     |

| ECD   | Electrical Critical Dimension                      |

| FIB   | Focused Ion Beam                                   |

| HF    | Hydrofluoric Acid                                  |

| HRTEM | High Resolution Transmission Electron Microscopy   |

| IC    | Integrated Circuit                                 |

| ICP   | Inductively Coupled Plasma                         |

| LPCVD | Low Pressure Chemical Vapour Deposition            |

| MEMS  | MicroElectroMechanical Systems                     |

| NIST  | The National Institute of Standards and Technology |

| OCD   | Optical Critical Dimension                         |

| PECVD | Plasma Enhanced Chemical Vapour Deposition         |

| PVD   | Physical Vapour Deposition                         |

| RIE   | Reactive Ion Etching                               |

| SEM   | Scanning Electron Microscopy                       |

| SOI   | Silicon On Insulator                               |

| SPM   | Scanning Probe Microscopy                          |

| TEM   | Transmission Electron Microscopy                   |

| UV    | Ultra Violet                                       |

|       |                                                    |

xiii

## Nomenclature

- $\delta L$  Line length shortening variable

- I Current

- $I_X$  Current at terminal X with relation to ground

- $I_{XY}$  Current measured between terminals X and Y

- $L_i$  Length (or tap separation distance) of segment *i*.

- $\rho$  Resistivity

- *R* Resistance

- Rs Sheet resistance

- $Rs_n$  Sheet resistance of structure n

- t Thickness

- V Voltage

- $V_X$  Voltage at terminal X with relation to ground

- $V_{XY}$  Voltage difference between terminals X and Y

- W Line width

- $W_m$  Measured line width

- $W_d$  Drawn line width

# Chapter 1 Introduction

This chapter outlines the motivations and objectives behind the work conducted and reported in this thesis. It provides a brief background to semiconductor devices and the integration of interconnect wiring schemes to meet the requirements of todays modern technology. After this introduction, the role of microelectronic test structures is described to support the work conducted for the latter chapters. The primary area of interest is the use of semiconductor metrology techniques coupled with novel test structure designs to enable material and process characterisation. Finally, after a brief look at the objectives of this work, an overview for the remainder of this thesis is presented.

### 1.1 Motivation

Microelectronic devices have been around for well over a half a century now. The first implementation was demonstrated in 1947 with the creation of the point contact transistor at Bell Laboratories [1]. Since then the microelectronics community has seen huge advances in fabrication technology, allowing billions of these transistors to be placed onto a single chip. This has enabled the fabrication of items such as microprocessors, memory chips, discreet transistors and many more electronic components. The key to the future of semiconductors is the ability to decrease the size of the devices whilst at the same time improving their performance.

The many transistor devices contained on a single chip communicate with one another, as well as the outside world, with microscale wires used to electrically connect them together. These wires, or *interconnects*, occupy a large portion of the area on an Integrated Circuit (IC) chip. As the speed and performance of these devices increases then so must the capability of the interconnect wires. The parameters of an interconnect system which affect the operating conditions of the signals are its resistance and capacitance. These are collectively referred to as the R-C timing delays. The work presented in the remainder of this thesis centres around the improvement of the resistance component. This has led to improvements in fabrication methods along with the choice of new materials for the implementation of the wires and tracks. However, in this world of shrinking dimensions the tolerance and room for error during fabrication becomes increasingly small. This is such that the performance of a device can be dramatically influenced by any number of parameters involved in the interconnect system such as the physical dimensions of the tracks and the connections between different layers of tracks. In order to evaluate and understand these parameters, interconnect metrology is adopted to provide a measure of the performance and characteristics of a particular process, design or material. Test structures play a key role in allowing parameter extraction and process/design qualification. With parameter extraction, semiconductor manufacturers can decide whether a device has met design specifications and if not it is typically scrapped. This prevents applying functional testing to poorly fabricated wafers, which is a costly and time consuming process.

### **1.2 Microelectronic test structures**

Microelectronic test structures are an essential resource to the development and manufacture of successful IC devices. The structures themselves typically consist of lithographically formed patterns in the same manner that the actual IC patterns are defined. They allow engineers within the semiconductor community to characterise a device both during processing as well as after it has been fully fabricated. These test structures permit the extraction of parameters relating to (amongst others) their electrical and physical properties, depending on the design and implementation. The key challenge in test structure design is creating features which allow a reliable, efficient and accurate measure of the parameters under investigation.

Test structures are found in a wide area of semiconductor manufacturing including:

- Process control and development [2]

- Modelling and simulation parameter extraction [3]

- Reliability and defect testing [4]

- Equipment characterisation [5]

- Material property analysis [6]

- Metrology [7]

- Yield analysis [8]

There are two main methods used to extract parameters from these test structures. The first is with the use of tools that determine the physical parameters of the structures including line width, trench depth, roughness, etc. For the most part these are well defined and established techniques used regularly during semiconductor manufacture. The challenge is interpreting how the physical parameters of the interconnects affect their functionality and performance aspects. Electrical parameter extraction, on the other hand, provides a functionally relevant picture of the various properties associated with the operation of a component or circuit. On the down side, the electrical measurements and analysis can be more time consuming and, in most circumstances, require physical contact to be made to the structures resulting in possible contamination due to the generation of particles.

Electrical measurements are provided for with *probe pads* to allow wires to be connected from the device under test (DUT) to the equipment being used for parameter extraction. There are two methods for arranging the probe needles or tips to make physical contact with the probe pads. The first is achieved using micromanipulators to move the tips in X, Y, and Z directions relative to the surface of the wafer. In this method, the user arranges the probe tips to correspond to the pitch that the probe pads are patterned. On the other hand, probe cards place the tips in a fixed arrangement to correspond to the pad layout. This method is commonly used for repetitive measurements from regular test structure layouts.

The act of positioning of the wafer and contact of the arranged probe tips to the probe pads is referred to as *probing*. In manual probing the user aligns and lowers the arranged probe tips to contact the test structures across the surface of a wafer using a microscope and X-Y-Z wafer table. This presents a flexible system, independent of design, for electrical contact. However, it can prove to be time consuming to setup and conduct measurements from large arrays of structures. The alternative is to use semi-automated or automated probing. In this approach, a probe station is programed with

information pertaining to the dimensions and layout of a test chip. After the wafer has been aligned in the test system, either manually by the user or automatically using pattern recognition software, the probe station automatically positions and moves the wafer or probes to contact with the test structures. These automated systems are linked to the test equipment to coordinate the measurements and positioning of the wafer.

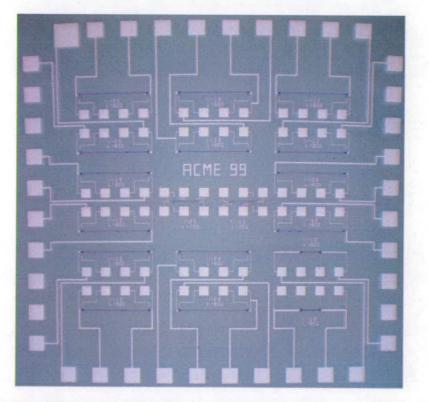

In most cases, the probe pads themselves are placed in standardised row and column format to facilitate automated probing routines with dedicated hardware. The most common arrangement is the " $2 \times n$ " pad layout which allows a single probe card to be used to probe all the structures within the whole chip [9]. An image of an ACME<sup>1</sup> test chip demonstrating a " $2 \times n$ " pad layout is found in figure 1.1. To minimise the test structure area, probe pads tend to occupy the smallest possible footprint without being so small that they are difficult to make repetitive contact with during probing. Pad sizes typically range in the order of 40 to 120 µm square.

**Figure 1.1:** Fabricated ACME 99 test chip demonstrating  $2 \times n$  probe pad layout.

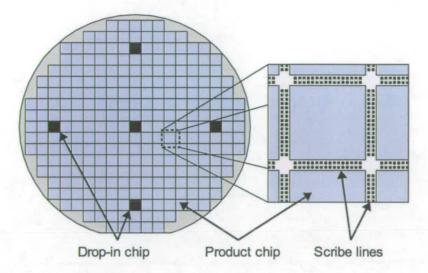

There are two main arrangements by which the test structures are incorporated into a production semiconductor wafer, both of which are illustrated in figure 1.2. The first

<sup>&</sup>lt;sup>1</sup>ACME: Aluminium to Copper Metallisation project undertaken by The University of Edinburgh.

is with "drop-in" chips, where the test structures occupy their own die site in place of a product die on the wafer being manufactured. This allows the designer to create a vast number of test structures in the large area that has been allocated. One of the drawbacks with this method is that the drop-in sites occupy what would have other wise been a product chip, and as such a balance between the number of drop-in chips required to provide a clear picture for process control while maintaining the greatest possible number of product chips must be maintained to maximise the profit of that particular wafer. As the structures occupy a whole die, a mask change is required to pattern the drop in sites and additional process time is introduced.

The alternative is to incorporate the test structures into unused portions of the wafer. While it is rare to find these unused areas within the boundaries of an IC device, the most common location is in the scribe channels of the wafer [10]. In this manner the test structures allow the extraction of parameters, while still maximising the profit of the wafer by not occupying valuable semiconducting real estate, as the scribe channels are consumed during the wafer dicing step. As the scribe channels extend across the full surface of the wafer and hence the test structures as well, a vast amount of information can be gathered from a single wafer. This extends to the ability to use wafer mapping from the large array of data obtained to characterise the process and equipment used. The one draw back to this method is that the scribe channels tend to be only as wide as the tool used for dicing requires. As a result, the available area for the test structures is limited, introducing the requirement for unique designs to fully exploit the available space.

Just as test structures are unique to a specific problem or property of interest, the analysis techniques applied to them for data extraction forms an essential element in material and process characterisation. Each test structure generally has one or more methods for deriving the desired parameters and tends to be application specific as to which algorithm selected.

### 1.3 Objective

The work presented in this thesis aims to benefit the metrology community through the development of new techniques and processes for test structure implementation

#### Introduction

**Figure 1.2:** Schematic illustration of drop-in and scribe line arrangement for test structure location

and analysis. More specifically test structures to electrically measure parameters such as overlay, line width and sheet resistance of IC interconnects. Novel processes are described in this thesis which allow these test structures to be implemented in manners specific to the application they are investigating. Furthermore, full analysis based on existing as well as some new methods are presented on these structures. The work described addresses three main areas of IC metrology. The first is the manner in which the alignment of multiple layers in a interconnect system is measured using optical tools and how it relates to the electrical functionality of the systems. The next area is the use of copper interconnects in modern day semiconductor IC systems, where a test structure is required to serve as a critical dimension reference material to allow material and device characterisation. Finally, the emerging field of thick film power MEMS devices similarly demands the use of test structures for process monitoring and as such an evaluation into the implementation and analysis of these test structures is required. The information contained in this dissertation has been partly published in five conferences [11–15]. A copy of some of these papers is presented in Appendix A.

### 1.4 Thesis overview

This thesis is the result of studies conducted for the degree of Ph.D. and is divided into three main sections. The first provides a detailed background to the work being conducted, including an in depth literature review in to the subject area. After this, the experimental procedures and results along with their analysis are presented. Finally conclusions are drawn and further work on the subject areas is suggested. An overview of the chapters is as follows:

**Chapter 2: Background to semiconductor metrology.** Semiconductor metrology provides engineers with the ability to extract a wide number of parameters from a specific process or design. A detailed review of the published work on these subjects is presented in this chapter in relation to the manner in which they are adopted for this thesis. The scope of the literature survey ranges from blanket film metrology to patterned structure testing, and from physical extraction methods to the more functionally relevant electrical methods. Finally, the concept of reference material is introduced as a means for calibrating and evaluating semiconductor metrology equipment.

**Chapter 3: Test structure for optical-electrical overlay calibration.** This chapter presents a novel design and implementation for a test structure which addresses one of the key areas of interconnect manufacturing. This structure serves as an application specific reference material for the cross correlation between electrical and optical measurements of overlay values. A brief overview of the subject is presented before looking at the technique demonstrated in the design of the structure. A standard fabrication process, traditionally found for aluminium tracks, is described for the implementation of the test structure. Then, a detailed analysis of the structure based on both electrical and SEM measurements is presented.

**Chapter 4:** Fabrication of all-copper ECD structures. Due to the demand for lower resistance interconnects, copper has been introduced as the preferred interconnect material of choice amongst many semiconductor manufacturers. A unique process is described in this chapter which combines the experience and techniques gained through silicon ECD structures with the need for an all-copper ECD structure. This novel approach results in a test structure which allows the extraction of line width and sheet resistance values from copper tracks which are not encapsulated by conducting barrier films. Traceability is provided between measurements taken using electrical extraction techniques and from methods such as AFM, CD-SEM, and HRTEM. After detailing the integration of the various steps involved, an overview of

the measurement strategy is explained.

**Chapter 5: ECD extraction from all-copper test structures.** Using the process described in Chapter 4, a thorough investigation was conducted to evaluate the process and test structure design used. Electrical measurements were taken with a DC parametric test system to extract values for both sheet resistance as well as line width of the all-copper features. Three variations of van der Pauw cross bridge resistors were employed to extract sheet resistance measurements. On the other hand, line width measurements are provided for with multiple-tapped Kelvin bridge resistor structures. SEM images have also been taken as a means for comparison to the electrical results. A number of different algorithms are reviewed and evaluated to determine values for line width and sheet resistance. Finally conclusions are drawn regarding the design and process used for the fabrication of the devices based on the results of the measurements.

**Chapter 6: MEMS test structure evaluation.** While the previous experimental chapters have focused on novel techniques and test structures to extract parameters from interconnect features with small dimensions, this chapter evaluates the area of thick film MEMS interconnects. These types of structures enable designers and manufacturing companies to integrate components, which were once placed separately on a PCB, on top of the semiconductor control circuitry. A technique for fabricating thick film copper conducting wires is evaluated for power MEMS devices. The fabrication has been demonstrated based on two enabling technologies, including thick film photoresist as well as electroplating of conductive materials. The goal of this study was to evaluate the use of traditional test structures for characterisation and process monitoring in MEMS thick film manufacturing. These structures have been measured and results presented based on an analysis of this data.

**Chapter 7: Conclusions and future work.** This final chapter reviews the information presented in this thesis and draws conclusions based on the experimental work which has been conducted. A more in depth look at the areas for further work is also presented including suggested designs and plans to allow this work to continue into the future.

# Chapter 2 Background to Semiconductor Metrology

### 2.1 Introduction

One could argue that the art of measurement dates back to the scientific programs of Galileo Galilei, where his motto was: "Count what is countable. Measure what is measurable. And what is not measurable, make measurable." Toward the end of the 19<sup>th</sup> century and at the beginning of the 20<sup>th</sup> century, the importance of measurement and the need for agreement between nations was recognised to be a requirement for the advancement of trade, technology and science. As a result, *metrology*, the science of measurement, became an important part of the infrastructure of a nation. So much so, that governmental organisations were appointed to develop and maintain a system of national measurements, often called "National Metrology Institutes" [16]. Metrology is widely used in today's rapidly changing market place, from industrial manufacturing to biological experiments. The semiconductor industry similarly relies on the use of metrology techniques to provide control and feedback during both development and manufacture of devices. One specific area of interest is the use of metrology in semiconductor interconnect fabrication.

In relation to the work conducted for this thesis, interconnect metrology has been divided into two types of extraction method: physical and electrical. The physical measurements relate the properties of a process or device to the International System of Units (SI), such as the metre. Typical parameters include film thickness, feature widths, relative placement of features, structure profiles, etc. These are also referred to as the critical dimensions (CD) and are the dimensions of the geometrical features formed during wafer processing. On the other hand, electrical methods provide a measure of the circuit behavior of a specific material or device. Typical parameters in electrical metrology include capacitance, inductance and resistance. As will be seen

later, these parameters can be used to extract information relating to the physical properties of a feature. The unique challenge posed is to determine the functional relevance of each method and furthermore to determine the relationship between the physical and electrical properties of a process or design.

## 2.2 Physical metrology

The techniques described in this section are based on those currently in practice in semiconductor manufacturing environments. The measurements themselves are either conducted on blanket films, the actual device, or test structures designed specifically for the purpose of parameter extraction.

#### 2.2.1 Optical methods

Optical microscopy is one of the most commonly used methods for metrology and inspection during wafer manufacture. It is the preferred tool due to the non-invasive and non-destructive nature of the measurements. Furthermore, the optical measurements can be integrated for real-time monitoring due to their robustness, high accuracy, low cost and small footprint. Optical microscopes are commonly found for use in inspection systems to monitor and qualify processes. However, in the context of the work conducted in the later chapters of this thesis, optical microscopes can also be used for metrology to extract line width from structures.

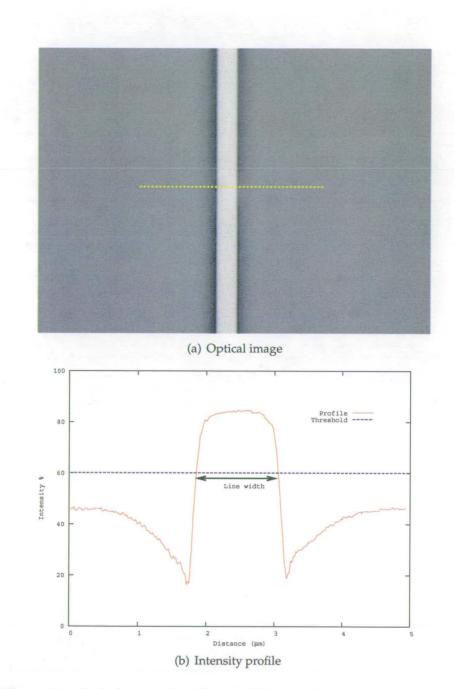

The most simple form of optical metrology is the use of a microscope with suitable hardware and software to extract the required parameters. Typically the additional hardware consists of an imaging camera that can provide suitable resolution to match the dimensions of the sample, along with image processing software to extract the desired parameters. This arrangement tends to be used to measure the lateral dimensions on a wafer, such as line width and feature placement (or overlay). Measurements are taken based on the reflected light intensity captured across a broad band wavelength range. Optical CDs (OCD) can be extracted using a single scan taken perpendicular to the feature of interest and applying data analysis techniques on the reflected light intensity profile. A typical method for analysis involves setting a threshold level on the profile and measuring the points at which the profile intersects

the threshold. Figure 2.1 displays an optical image taken from an Al track and the resulting intensity profile with threshold and equivalent line width marked.

The one draw back to this method is that as CDs decrease in size, optical measurements are not able to provide the accuracy required because the wavelengths used by these tools are comparable to the patterned dimensions. New developments using deep ultra-violet (DUV) and extreme ultra-violet (EUV) are allowing optical methods to be extended beyond the traditional methods. Other optical CD measurement techniques include scatterometry [17] and optical profilometry [18]. However, these are beyond the context of the work conducted for this thesis.

#### 2.2.2 Electron microscopy

The use of electron microscopes in semiconductor metrology has been well established and understood. The principle of this technique is that a beam of electrons are accelerated towards and focused on the surface of the sample being inspected. The image is formed based on the signal strength of the detected electrons after they have interacted with the surface of the sample. The two main types of electron microscope are the transmission electron microscope (TEM) and the scanning electron microscope (SEM). The TEM was the first type of electron microscope developed and forms an image from the electrons which have traveled through the sample and into a detector located behind it. The SEM, on the other hand, detects the secondary electrons (SE) that result from the interaction between the surface and the primary beam of electrons which are reflected off of the surface of the sample and into the detector. Both types of microscope can be found in modern day CD metrology environments.

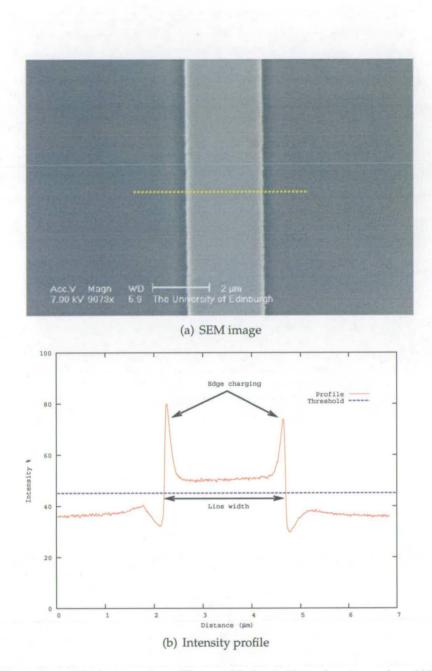

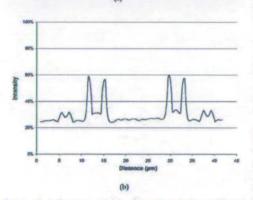

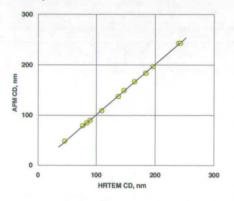

The use of an SEM to determine line width is performed in a similar manner to that used for optical line width measurements. A profile is extracted based on the intensity of the SE detected from a single line scan perpendicular to the feature being measured. For comparison with the optical line width extraction example presented in figure 2.1, an SEM image and corresponding intensity profile is displayed in figure 2.2. With this profile, a threshold or similar edge detection method can be used to determine the line width. To facilitate these type of measurements in semiconductor metrology, special SEMs for CD extraction, known as CD-SEMs, are used.

Figure 2.1: Optical extraction of line width from Al track patterned on SiO<sub>2</sub>.

There are a number of problems associated with CD metrology in SEM tools. The first is the charging effects caused by the material interactions with the electron beam. As can be seen in both the SEM image as well as the intensity plot in figure 2.2, the intensity of the Al track (as with other metal lines) is much higher at the edges than in the centre. This makes it difficult to determine the "true" edge of the track and hence determine the line width. One way of reducing this effect, as reported by Postek [19], is to use a low accelerating voltage on the SEM. Further more, this paper describes the use of backscattered electrons (BSE) detectors, as opposed to the SE detectors traditionally used in SEM imaging, to provide better edge detection for CD metrology purposes. The second problem associated with SEM metrology is the fact that the electron beam can result in the deposition of materials, mainly carbon, onto the surface of the sample during imaging. The result being that the extracted line width appears larger than the actual dimensions of the feature being measured. Finally, similar to optical techniques, as the SEM image is taken perpendicular to the surface of the sample, it does not contain sufficient information regarding the sidewall profile of the features being measured. However, a number of researchers are currently working on special techniques to extract sidewall information from a CD-SEM. Marschner and Stief [20] have demonstrated the ability to reconstruct the sidewall profile of a structure based on two images taken from a sample with varying tilt angles. Alternatively, Su et. al. [21] use a technique where the sidewall angle is determined from a single top down image. In this approach, the sidewall angle is calculated from the height of the track and the lateral difference between the edges of the top surface and those of the bottom interface of the track as detected from the extracted profile from a feature. However, this method requires the use of additional metrology tools and measurement processes to determine the step height of the track.

Another technique commonly used in semiconductor inspection and metrology is cross-sectional SEM imaging (X-SEM). A pre-requisite to this method is that samples must be prepared prior to imaging using either cleaving, dicing, or polishing tools to expose the area of interest. The imaging procedure requires that the sample be mounted and rotated using suitable fixtures and hardware to allow sample tilting and manipulation. Typically X-SEM images are taken at 90° relative to the wafers surface. When observing a sample in X-SEM analysis, information about the line width, feature height, sidewall profile, defects and many more areas can be determined.

Figure 2.2: SEM extraction of line width from Al track patterned on SiO<sub>2</sub>.

Unfortunately the preparation routines are time consuming operations, sometimes requiring specialist equipment. Additionally, as this approach is a destructive technique, it cannot be used for in-line monitoring.

The use of TEMs in semiconductor metrology is rarely seen due to the fact that samples must be thin enough to allow the transmission of electrons. As such, samples must be prepared using a number of available techniques to reduce the area of interest to a region a few hundred nanometres thick. Such techniques are similar to those used for X-SEM sample preparation, including dicing, cleaving, polishing and focused ion beam (FIB) milling [22]. However, Warren and Stein [23] demonstrate a technique to overcome this preparation routine, where the sample to be analysed is deposited directly over a thin membrane of silicon nitride supported by a silicon frame which is defined in the substrate. Using this method, line width can be extracted from the intensity profile generated by the transmitted electrons.

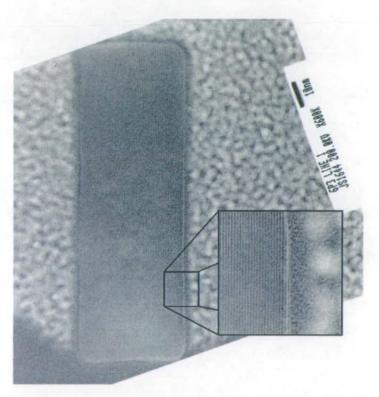

Although TEM is not viable as an in-line metrology tool, a considerable amount of work has been conducted by researchers at NIST to develop techniques for extracting CDs from single crystal Si samples when analysed under a high resolution transmission electron microscope (HRTEM) [24–27]. The authors detail the fabrication of CD line width features patterned in (110) mono-crystalline Si substrates. When the samples are observed in cross section, through an isolated patterned line in an HRTEM, the crystal lattice is made apparent, as seen in figure 2.3. By counting the number of lattice planes across the width of the patterned structure and with a knowledge of the atomic spacing of the silicon lattices, the line width can be determined. In work by Allen et. al. [26] specially designed image analysis software is described that allows the lattice planes to be counted in an automated fashion based on a fringe detection algorithm. This decreases the time required for the measurements and increases the throughput. The authors of this work claim that this method can produce values with uncertainties less than 2.5 nm for line width.

#### 2.2.3 Stylus profilometry

The next method of extracting dimensional information is based on the mechanical interactions between the sample and a measurement stylus. As a result it is not subject to the charging and edge effects seen with electron microscopy. In stylus profilometry a

Figure 2.3: HRTEM image of single crystal silicon showing the lattice planes (inset). Reproduced with permission from the National Institute of Standards and Technology

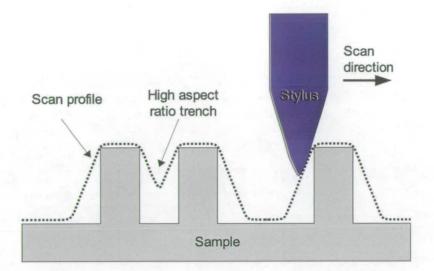

**Figure 2.4:** Schematic illustration of the principles of stylus profilometry and the effect of the stylus on the extracted profile.

stylus is driven across the surface of a sample while the vertical position is monitored, typically with a capacitance sensor, to determine height variations. This method is used to extract two dimensional (2-D) information about surfaces based on a single line scan containing height values. However, there are some tools which allow three dimensional (3-D) information to be gathered from a stylus profilometer using an X-Y raster scan technique.

As this metrology tool uses physical contact with the sample being measured, the stylus must be mechanically robust to prevent excessive wear. As a result, the stylus tends to be rather large in comparison to the feature being measured. Figure 2.4 illustrates the principles and typical issues associated with stylus profilometry. The first issue is that the extracted scan profile is only able to measure information about the sidewalls of features where the sidewall has a slope less than the angle of the stylus. Furthermore the stylus is unable to measure trenches which have an aspect ratio greater than the dimensions of the stylus used to measure it.

Line width is determined using the extracted profile based on either a threshold limit or the point in which the stylus detects the edge of the top side of the structure. However, the main use of this method is to extract topographic information such as surface roughness or step height of features.

#### 2.2.4 Scanning probe microscopy

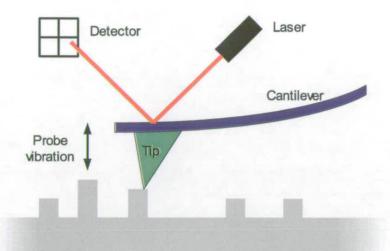

Scanning probe microscopy first began with the development of the scanning tunneling microscope (STM) which, in turn, lead to the more commonly used atomic force microscope (AFM) [28]. As in stylus profilometry, the AFM uses a tip to scan across the surface of the sample. However, instead of using physical contact with the surface, it monitors the interactions between the sample and the probe, which is positioned just above the surface of the sample. In AFM the van der Waals forces between the tip and the surface are used to determine topographic information about the sample. These forces result in varying degrees of deflection of the probe depending on the properties of the material used both for the tip and the sample. A diagram illustrating the components of an AFM operated in tapping mode (described later in this section) is seen in figure 2.5.

The probe itself is fabricated using MEMS processing techniques to produce a small tip fixed to a cantilever. As described by Wolter et. al. [29], traditionally the tips are fabricated from silicon to form a small radius point. The drawback of this process is that the silicon tips are fragile and the probes have a finite lifetime before they need to be replaced. To address this issue, Shibata et. al. [30] describe a technique used to fabricate AFM tips from diamond films. In comparison to the silicon tips, the benefits include longer life times for the probes and also the ability to be used in harsh chemical environments. The physical displacement of the probe is monitored using an optical measurement system [31] where a light source (often a laser) is aimed onto the back of the cantilever whilst a detector monitors the position of the reflected beam of light as shown in figure 2.5.

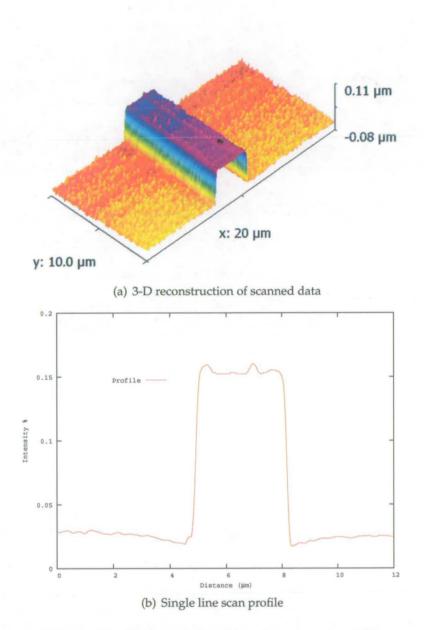

There are a number of different modes that an AFM can be operated in, with the choice depending on the properties of the sample being measured and the desired results. Of relevance to the work described in this thesis is the use of *tapping mode* AFM (TM-AFM) which is one of the most widely used instruments for atomic-resolution imaging [32]. In this mode, the probe is vibrated at, or near, its resonant frequency while the tip is scanned across the surface of the sample. The tip deflection that results from the forces that occur during the interaction between the probe and the sample is monitored. The probe is scanned in a raster like fashion across the surface to create either a 2-D or 3-D image of the sample. The image of a sample is formed from a reconstruction of the

Figure 2.5: Schematic illustration of the principles of atomic force microscopy.

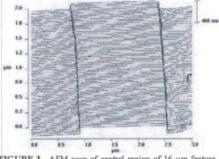

height information against the position of the tip. An example of such an image is shown in figure 2.6(a). In this image it can be seen that the AFM provides such high resolution that the surface roughness of the field area dielectric can be seen. From this 3-D image a single line scan can be extracted, as shown in figure 2.6(b) to measure the line width. This can be achieved either by setting a threshold or by determining the point at which the tip detects the edges of the sample.

The use of micro machining means that the dimensions of the tip are typically much smaller than those used for stylus profilometry. Although the measurements themselves are still subject to the effects of tip geometry on the extracted profile, as seen with stylus profilometry, they are less significant. Furthermore, special tips can be obtained that have been designed to allow measurements of high-aspect ratio trenches by using a long, narrow profile. One such probe is realised with the use of carbon nanotube technology as described by Morimoto et. al. [33]. In this paper, the authors describe the "STEP-IN" AFM approach where the thin carbon nanotube tip is of small enough radius to step into the trenches of a sample. Further more, the tips are angled at 15° to allow accurate detection of the leading edge of the sidewall at the bottom of a trench or feature. However, this does not provide the accuracy required to extract critical dimension parameters for the sub-100 nm requirements of modern day semiconductors. One key enabling technology to allow AFM to be used as a metrology tool for line width parameters is the use of unique "boot shape" tips to image the sidewalls of a feature. Guerry et. al. [34] as well as Martin and Wickramasinghe [35]

**Figure 2.6:** AFM scan of an Al track patterned on  $SiO_2$ .

report on the use of such a tip to measure sidewalls. This allows the user to gather information such as sidewall roughness and line width over the entire vertical profile. Such tips are used in conjunction with special AFM systems called CD-AFM (also 3D-AFM) [36]. It is these tools which enable accurate results for feature metrology in the semiconductor industry [37].

### 2.3 Electrical metrology

While the techniques described above allow CDs to be extracted based on the physical dimensions of the features, the true behavior of an IC component is realised using electrical testing. Electrical metrology takes two forms, measurements from blanket films and those from patterned test structures. The blanket measurements reflect properties of the materials under evaluation, including film thickness and resistivity, and tend to be used to characterise the process used to deposit them. Test structures, on the other hand, can be designed to extract parameters ranging from material properties to dimensional information including thickness and line width. The test structures also allow information to be extracted regarding design parameters used in an IC.

#### 2.3.1 Four point probe

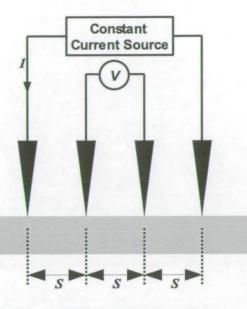

The four point probe (FPP) measurement is one of the most widely used techniques for evaluating the resistance of a blanket film or substrate as discussed by Schroder [38]. Its use was originally developed by Wenner [39] to measure the resistivity of the earth. In 1954 the FPP was adopted by Valdes [40] for use in the semiconductor industry to measure the resistivity of wafers. This method evolved from the use of a simple two electrode setup which made contact to the surface of a conducting sample where impedance is sensed between the two terminals. The problem with this method is that contact effects between the electrodes and the surface contribute to the measured impedance values, making the interpretation of the four electrode arrangement illustrated in figure 2.7, in which four probes are placed in-line and equally spaced onto the surface of the sample. Typical values for the separation of the contact electrodes (S) are in the order of 0.5 to 1.5 mm. The measurement technique is

commonly referred to as the *Kelvin technique* where a constant current source is used to force a current through the outer pair of electrodes and at the same time the potential difference between the inner pair of electrodes is sensed. Provided the four points are placed collinearly, the resistivity of a material is found using the formula in equation (2.1), where  $\rho$  is the resistivity of the material, and *I* is the current forced and *V* is the potential difference sensed during the measurement.

$$\rho = 2\pi S\left(\frac{V}{I}\right) \tag{2.1}$$

However equation (2.1) is based on the assumption that measurements are taken from a symmetrical sample of semi-infinite lateral and vertical dimensions. In semiconductor applications, the thickness (t) of the conducting material being measured is typically much less than the electrode separation distance. Additionally, when using silicon wafers, the films are limited to the lateral dimensions of the wafer. Therefore corrections are introduced to address these finite geometries, the result of which allows the resistivity ( $\rho$ ) of the thin material to be found using the modified formula in equation (2.2), provided the thickness is known.

$$\rho = \frac{\pi t}{\ln(2)} \frac{V}{I} \tag{2.2}$$

Conversely, if the resistivity of a material is known, equation (2.2) can be solved to extract the thickness of the layer. However, it is not always possible to know either the resistivity or thickness of a material and therefore *sheet resistance* is introduced as a means to characterise films without the need for dimensional information. The sheet resistance (*Rs*) is equivalent to the resistivity divided by the thickness of the film (equation (2.3)) and represents the resistance of a square area (length × width) of conducting film. Values for *Rs* are expressed in units of ohms per square ( $\Omega/\Box$ ).

$$Rs = \frac{\rho}{t} \tag{2.3}$$

One downside to the FPP method is the prerequisite for large areas of un-patterned film with which to make contact, therefore making it difficult to integrate with

Figure 2.7: Schematic illustration of the principles of four-point probe measurements.

traditional product wafers where open/un-patterned areas of the wafer can reduce the profit of each wafer. One way of overcoming this has been presented by Guillaume et. al. [41], in which a method of extracting local sheet resistance using a "small-area four-point probe" technique is described. In this paper, the authors employ a four electrode setup which occupies a 160  $\mu$ m × 160  $\mu$ m square array applied to patterned films. Measurements were conducted using the van der Pauw approach, as will be discussed later in this section. The corresponding sheet resistance of the material is calculated by referencing measured resistance values with computer simulations of the configuration.

### 2.3.2 Test structures

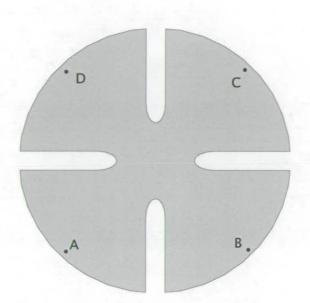

#### Van der Pauw

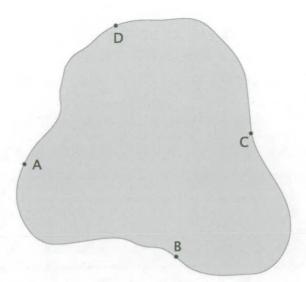

One of the most widely adopted methods to measure the sheet resistance of patterned films is the use of van der Pauw structures [42, 43]. They are similar to the FPP measurements, but allow much smaller areas to be investigated and can take advantage of semiconductor patterning techniques. The theory and practice behind this method originated from work reported by van der Pauw in 1958 [44, 45] to extract resistivity values and Hall coefficients from structures of arbitrary shape. In this study, four contacts (A,B,C,D) are placed along the periphery of a sample, as seen in the configuration depicted in figure 2.8. Van der Pauw states that when a current is applied to contact A and taken off at contact B ( $I_{AB}$ ), and the potential difference is measured between terminals D and C ( $V_D - V_C$ ) then  $R_{AB,CD}$  is defined as

$$R_{AB,CD} = \frac{V_D - V_C}{I_{AB}} \tag{2.4}$$

In a similar convention,  $R_{BC,DA}$  can be calculated by applying a current between contacts *B* and *C* whilst measuring the potential difference between *D* and *A*. The van der Pauw measurement technique is based on the theory that between  $R_{AB,CD}$  and  $R_{BC,DA}$  there exists the simple relation shown in equation (2.5), where  $\rho$  is the resistivity of the material and *t* is the thickness.

$$exp\left(-\frac{\pi t}{\rho}R_{AB,CD}\right) + exp\left(-\frac{\pi t}{\rho}R_{BC,DA}\right) = 1$$

(2.5)

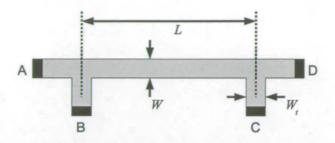

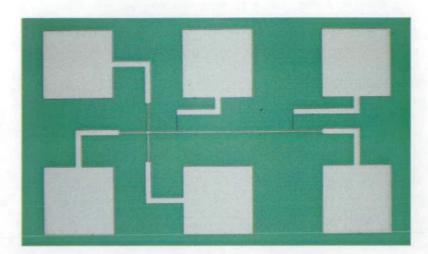

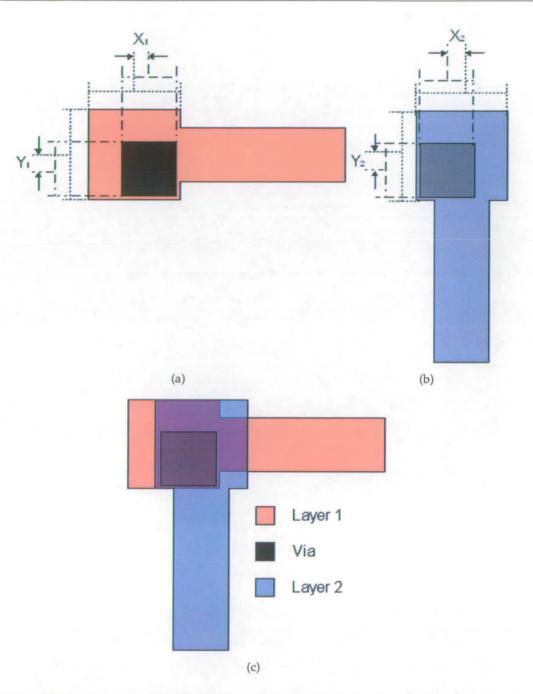

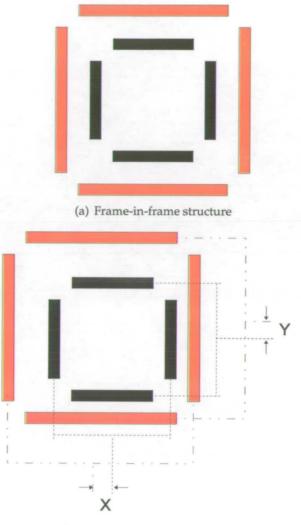

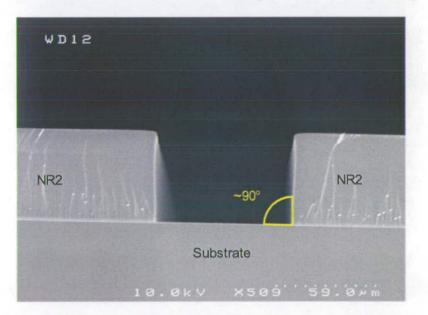

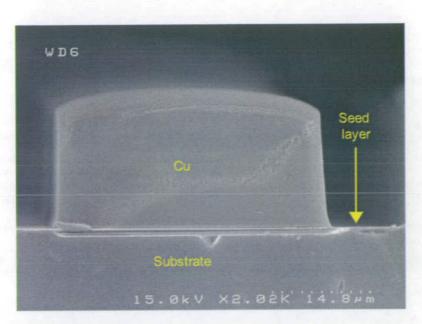

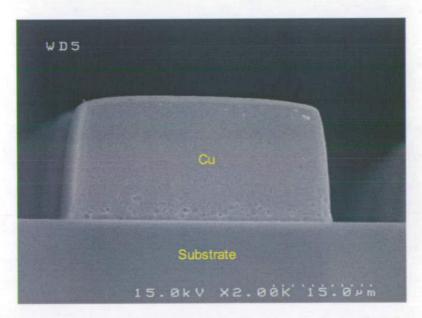

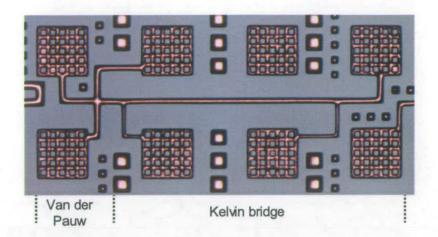

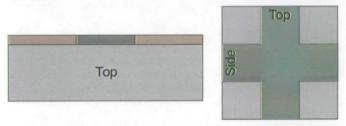

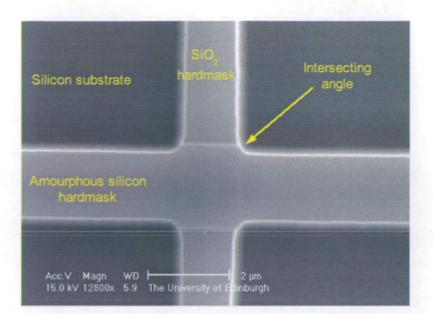

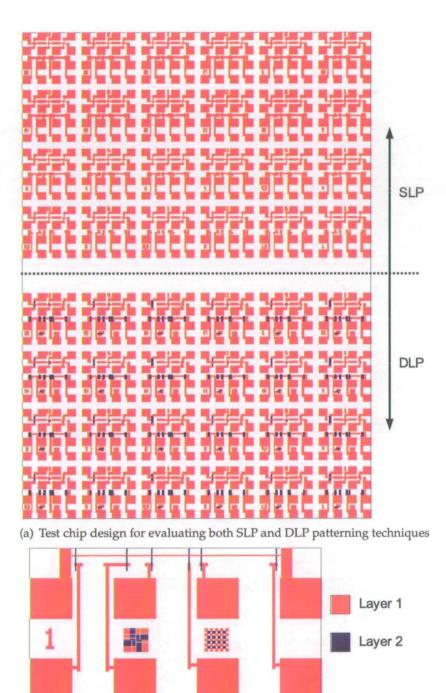

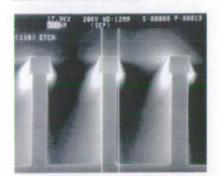

Provided values for  $R_{AB,CD}$ ,  $R_{BC,DA}$ , and t are known, then the numerical solution to equation (2.5) yields the value for  $\rho$ . The sheet resistance is similarly found by substituting the relation described in equation (2.3). This measurement approach is based upon the assumption that the material is of homogeneous thickness and resistivity, and that the contacts are finitely small and form only a single point of contact with the material.