# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# The Automatic Synthesis of Fault Tolerant and Fault Secure VLSI Systems

Ian Michael Nixon

Ph D

University of Edinburgh

1987

### Abstract

This thesis investigates the design of fault tolerant and fault secure (FTFS) systems within the framework of silicon compilation. Automatic design modification is used to introduce FTFS characteristics into a design. A taxonomy of FTFS techniques is introduced and is used to identify a number of features which an "automatic design for FTFS" system should exhibit.

A silicon compilation system, Chip Churn 2 (CC2), has been implemented and has been used to demonstrate the feasibility of automatic design of FTFS systems. The CC2 system provides a design language, simulation facilities and a back-end able to produce CMOS VLSI designs. A number of FTFS design methods have been implemented within the CC2 environment; these methods range from triple modular redundancy to concurrent parity code checking. The FTFS design methods can be applied automatically to general designs in order to realise them as FTFS systems.

A number of example designs are presented; these are used to illustrate the FTFS modification techniques which have been implemented. Area results for CMOS devices are presented; this allows the modification methods to be compared. A number of problems arising from the methods are highlighted and some solutions suggested.

# Table of Contents

| 1. | Intr | oductio  | n         |      |    |     |     |     |   |   |       |   |     |   |   |   |   |   |   |     |   |   |   | 14 |

|----|------|----------|-----------|------|----|-----|-----|-----|---|---|-------|---|-----|---|---|---|---|---|---|-----|---|---|---|----|

|    | 1.1  | Critical | Systems   |      | •  |     |     |     | • | • |       | • |     | • | • | • | • | • |   |     |   |   | • | 14 |

|    | 1.2  | Trust.   | • • • • • |      | •  |     |     |     | • | • | <br>• | • |     |   | • |   |   |   | • |     | • | • |   | 15 |

|    | 1.3  | VLSI D   | esign .   |      |    |     | •   |     |   | • |       |   |     | • | • | • | • |   | • |     |   |   | • | 16 |

|    | 1.4  | Rationa  | le        |      | •  |     |     |     | • |   |       |   |     |   | • |   |   | • | • |     |   | • |   | 18 |

|    | 1.5  | Chapter  | Outline   |      | •  |     | •   |     | • | • |       | • |     | • | • | • | • |   | • |     |   | • |   | 19 |

|    |      | 1.5.1    | Chapter1  |      | •  |     |     |     | • | • |       | • |     |   | • | • | • | • | • |     | • |   | • | 19 |

|    |      | 1.5.2    | Chapter 2 | ·    |    |     | •   |     | • |   |       | • |     |   | • |   |   |   | • |     |   | • |   | 19 |

|    |      | 1.5.3    | Chapter 3 | 3    | •  |     | •   |     | • |   |       |   |     |   | • |   |   |   | • | • • |   | • | • | 19 |

|    |      | 1.5.4    | Chapter 4 | ŀ    | •  |     | •   |     | • | • | <br>• | • |     | • | • |   | • |   | • |     |   |   |   | 19 |

|    |      | 1.5.5    | Chapter 5 | ·    |    |     | •   |     |   |   |       |   |     | • | • |   | • | • | • |     |   | • | • | 20 |

|    |      | 1.5.6    | Chapter 6 | S    | •  |     | •   |     |   | • | <br>• |   |     | • | • |   |   | • | • |     | • |   |   | 20 |

|    |      | 1.5.7    | Chapter 7 | ·    | •  |     | •   |     |   |   |       |   |     |   |   |   | • |   | • |     |   | • |   | 20 |

| 2. | Test | ing and  | Reliabi   | lity |    |     |     |     |   |   |       |   |     |   |   |   |   |   |   |     |   |   |   | 21 |

|    | 2.1  | Test and | l Testabi | lity | •  |     | •   | • • |   | • | <br>• |   |     | • |   |   |   |   | • |     | • |   |   | 21 |

|    |      | 2.1.1    | What Ca   | ıses | Fa | ult | s ? | •   | • | • |       | • | • • | • | • |   |   |   | • |     |   | • |   | 21 |

|    |      | 2.1.2    | The Prob  | lem. | •  |     |     |     |   |   |       | • |     |   |   |   |   |   | • |     |   |   |   | 22 |

| Ta | ible o | f Conte       | ents                               | 2  |

|----|--------|---------------|------------------------------------|----|

|    |        | 2.1.3         | Verification versus Confidence     | 24 |

|    |        | 2.1.4         | Design For Testability             | 24 |

|    |        | 2.1.5         | Test Patterns and Expected Results | 27 |

|    |        | 2.1.6         | Built In Self-Test (BIST)          | 28 |

|    |        | 2.1.7         | Automation                         | 29 |

|    |        | <b>2.1.</b> 8 | Programmable Logic Arrays (PLAs)   | 29 |

|    |        | 2.1.9         | Limitations of Static Test Methods | 31 |

|    | 2.2    | Reliab        | ility                              | 31 |

|    |        | 2.2.1         | What is required?                  | 32 |

|    |        | 2.2.2         | Hardware Redundancy                | 33 |

|    |        | 2.2.3         | Information Redundancy             | 34 |

|    |        | 2.2.4         | Codes and Coding                   | 34 |

|    |        | 2.2.5         | Totally Self-Checking Checkers     | 40 |

|    |        | 2.2.6         | Systemic Approaches                | 40 |

|    |        | 2.2.7         | General Approaches                 | 40 |

|    | 2.3    | Concl         | usions                             | 41 |

| 3. | For    | m vers        | us Function                        | 42 |

|    | 3.1    | Introd        | uction                             | 42 |

|    |        | 3.1.1         | Function (or What It Does)         | 44 |

|    |        | 3.1.2         | Structure (or How It Does It)      | 44 |

|    |        | 3.1.3         | Purity                             | 44 |

|    | 3.2    | Fault !       | Models                             | 45 |

|    | 3.3    | Classif       | fication                           | 46 |

| Table of | Contents                                            | 3         |

|----------|-----------------------------------------------------|-----------|

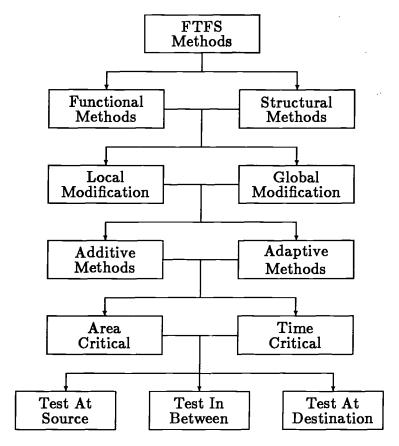

|          | 3.3.1 Structure and Function                        | 47        |

|          | 3.3.2 Local and Global Modification                 | 48        |

|          | 3.3.3 Additive and Adaptive Modifications           | 48        |

|          | 3.3.4 Time and Area Critical Methods                | 49        |

|          | 3.3.5 Where to Test                                 | 49        |

| 3.4      | Examples                                            | 51        |

|          | 3.4.1 NMR                                           | 51        |

|          | 3.4.2 State Coding                                  | <b>52</b> |

|          | 3.4.3 Mixing Functional and Structural Modification | 54        |

| 3.5      | Conclusions                                         | 56        |

| 1. The   | Chip Churn Design Tools                             | 57        |

| 4.1      | Introduction                                        | 57        |

| 4.2      | Basics                                              | 58        |

| 4.3      | Chip Churn                                          | 60        |

|          | 4.3.1 Design Representation                         | 60        |

|          | 4.3.2 Validation Tools                              | 60        |

|          | 4.3.3 Artwork Generation                            | 62        |

|          | 4.3.4 Problems                                      | 63        |

| 4.4      | Chip Churn 2                                        | 64        |

| ,        | 4.4.1 The CC2 Language                              | 64        |

|          | 4.4.2 Other Features                                | 69        |

|          | 4.4.3 Language Example                              | 72        |

|          | 4.4.4 Technology Independent Intermediate Format    | 73        |

| Ta | ble o | f Conte  | nts                        |     | 4     |

|----|-------|----------|----------------------------|-----|-------|

|    | 4.5   | Design   | Validation                 |     | , 75  |

|    |       | 4.5.1    | Timing Model               | •   | . 76  |

|    |       | 4.5.2    | Simulation Model           |     | . 77  |

|    |       | 4.5.3    | Simulator Interfaces       |     | . 80  |

|    | 4.6   | Artwo    | rk Generation              |     | . 80  |

|    |       | 4.6.1    | CC2 Optimisations          |     | . 80  |

|    |       | 4.6.2    | Function Partitioning      |     | . 83  |

|    |       | 4.6.3    | CC2 Back-Ends              | • • | . 84  |

|    |       | 4.6.4    | Elgar                      |     | . 85  |

|    |       | 4.6.5    | Bend                       | •   | . 91  |

|    |       | 4.6.6    | Bes                        | •   | . 94  |

|    |       | 4.6.7    | Example                    | •   | . 94  |

|    | 4.7   | Conclu   | usions                     | •   | . 96  |

| 5. | Mod   | dificati | ion Techniques             |     | 97    |

|    | 5.1   | Functi   | onal Modification          | •   | . 98  |

|    |       | 5.1.1    | Links                      | •   | . 98  |

|    | ,     | 5.1.2    | Functional Fault Security  | • , | . 99  |

|    |       | 5.1.3    | Functional Fault Tolerance |     | . 101 |

|    |       | 5.1.4    | State Variable Tolerance   |     | . 101 |

|    |       | 5.1.5    | Function Overhead          |     | . 102 |

|    | 5.2   | Struct   | ural Modification          |     | . 102 |

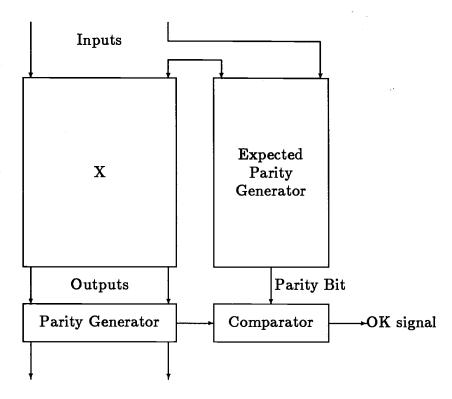

|    |       | 5.2.1    | Structural Parity          |     | 104   |

|    |       | 5.2.2    | NMR                        |     | 104   |

| Та | ble o | f Conte | ents                        | 5         |

|----|-------|---------|-----------------------------|-----------|

|    |       | 5.2.3   | Lala Scheme                 | .04       |

|    | 5.3   | Proble  | ems                         | .05       |

|    |       | 5.3.1   | What are the outputs?       | .05       |

|    |       | 5.3.2   | Drain Modification Problems | 07        |

|    |       | 5.3.3   | Function Inversion          | 10        |

|    | 5.4   | Worke   | ed Example                  | 11        |

|    |       | 5.4.1   | The Design                  | 11        |

|    |       | 5.4.2   | Functional Modification     | 12        |

|    |       | 5.4.3   | Functional Security         | 16        |

|    |       | 5.4.4   | Tolerant Modification       | 19        |

|    |       | 5.4.5   | State Variable Coding       | 20        |

|    | 5.5   | Struct  | oural Modification          | .22       |

|    |       | 5.5.1   | Structural Parity           | .22       |

|    |       | 5.5.2   | NMR and the Lala Scheme     | .23       |

|    |       | 5.5.3   | Alternative Valid Signals   | .24       |

|    | 10    | 1       |                             |           |

| 3. | Exa   | mples   | 1                           | <b>25</b> |

|    | 6.1   | Introd  | uction                      | .25       |

|    | 6.2   | 8-Bit   | Adder                       | .26       |

|    | 6.3   | Bitoni  | c                           | 26        |

|    | 6.4   | Euclid  | l's Algorithm               | .28       |

|    |       |         |                             |           |

6.5

6.6

| Ta | ble of | Contents                                            | 6          |

|----|--------|-----------------------------------------------------|------------|

|    | 6.8    | Instruction Set                                     | 31         |

|    | 6.9    | Micro Instructions                                  | 34         |

|    | 6.10   | Results                                             | 36         |

|    |        | 6.10.1 Possible Optimisations                       | 37         |

|    |        | 6.10.2 General Results                              | 38         |

|    |        | 6.10.3 Fault Coverage                               | 13         |

|    |        | 6.10.4 Time Overhead                                | 14         |

|    | 6.11   | Conclusions                                         | 17         |

| 7. | Con    | clusions 14                                         | 18         |

|    | 7.1    | Introduction                                        | 18         |

|    | 7.2    | The Chip Churns                                     | 18         |

|    |        | 7.2.1 Language and TIIF                             | 19         |

|    |        | 7.2.2 The Back-End                                  | 52         |

|    |        | 7.2.3 Elgar                                         | 53         |

|    |        | 7.2.4 Floorplanning                                 | 55         |

|    | 7.3    | System Level Design                                 | 56         |

|    | 7.4    | Designer Interaction and Reasoning about Designs 15 | 58         |

|    | 7.5    | Timing                                              | 58         |

|    | 7.6    | Testability                                         | 59         |

|    | 7.7    | Design Modification                                 | 5 <b>0</b> |

|    |        | 7.7.1 Functional Modification                       | 60         |

|    |        | 7.7.2 Structural Modification                       | 61         |

|    |        | 7.7.3 General Problems                              | 31         |

| Table of Contents                                 | 7   |

|---------------------------------------------------|-----|

| 7.7.4 Other Uses of Automatic Design Modification | 162 |

| 7.8 And Finally                                   | 163 |

| A. Mindless - A Channel Router                    | 171 |

| A.1 Introduction                                  | 171 |

| A.2 The Mindless Algorithm                        | 172 |

| A.3 Creating Geometry                             | 175 |

| B. Mynimo                                         | 176 |

| B.1 Introduction                                  | 176 |

| B.2 Mynimo                                        | 178 |

| B.2.1 Generating C                                | 178 |

| B.2.2 Selecting S                                 | 179 |

| B.2.3 Heuristics                                  | 179 |

| B.3 Results                                       | 181 |

| C. Wino Arrays                                    | 182 |

| C.1 Introduction                                  | 182 |

| C.2 Features                                      | 183 |

| C.3 Array Composition                             | 183 |

| C.4 Truth Tables                                  | 184 |

| C.5 Totally Self-Checking Logic                   | 184 |

| D. Implementation Notes                           | 186 |

| D.1 Language and Machines                         | 186 |

| D.2 CC2 compiler options                          | 186 |

| Ta       | ble of | f Conte | nts     |        |          |      |       |       |     |    |    |     |     |   |   |    |   |       | 8           |

|----------|--------|---------|---------|--------|----------|------|-------|-------|-----|----|----|-----|-----|---|---|----|---|-------|-------------|

| E.       | CC2    | 2 Syste | em Sc   | hema   | tic      |      |       |       |     |    |    |     |     |   |   |    |   |       | 189         |

| F.       | Chi    | p Chui  | rn - A  | . PLA  | A Ba     | ase  | d S   | ilic  | on  | C  | om | pi] | ler | i |   |    |   |       | 191         |

|          | F.1    | Introd  | uction  |        | • • •    |      |       |       |     |    |    |     | •   |   | • |    | • |       | <br>191     |

|          | F.2    | System  | ı Over  | view   |          |      | • • , |       | •   |    |    |     | •   |   |   |    |   |       | <br>192     |

|          | F.3    | Testab  | ility . |        | <b>.</b> |      |       | • • • |     |    |    |     | •   |   | • |    | • | <br>• | <br>193     |

|          | F.4    | Examp   | ole     |        |          |      |       |       | •   |    |    |     | -   |   |   |    | • |       | <br>194     |

|          | F.5    | Curren  | ıt Wor  | k      |          |      | • • • |       |     |    | •  |     | •   |   | • |    | • | <br>• | <br>194     |

|          | F.6    | Conclu  | sions   |        |          |      | • •   |       | •   |    | •  |     | -   |   | • | ٠. | • | <br>• | <br>197     |

| ${f G}.$ | Cif    | Plots   |         |        |          |      |       |       |     |    |    |     |     |   |   |    |   |       | 198         |

| н.       | The    | CC2     | Exam    | ple S  | our      | ce : | Des   | cri   | pti | on | g  |     |     |   |   |    |   |       | <b>2</b> 06 |

|          | H.1    | The 8-  | Bit Ad  | lder   |          |      | • • • |       | •   |    | •  |     | •   |   | • | ٠. | • | <br>• | <br>206     |

|          | H.2    | The Bi  | itonic  | Sorte  | r        |      | • • • |       | •   |    | •  |     |     |   |   |    |   | <br>• | <br>207     |

|          | H.3    | Euclid  | Chip    |        |          |      |       |       |     |    | •  |     |     |   |   |    |   | <br>• | <br>209     |

|          | H.4    | Microp  | rocess  | or .   |          |      | • •   |       | •   |    | •  |     |     |   | • |    |   | <br>• | <br>214     |

|          |        | H.4.1   | The M   | Main I | Desig    | gn ] | File  |       |     |    | •  |     |     |   |   |    |   |       | <br>214     |

|          |        | H.4.2   | The I   | PC re  | giste    | r d  | escr  | iptic | on  |    | •  |     |     |   |   |    |   | <br>• | <br>222     |

|          |        | H.4.3   | The S   | SP reg | iste     | r de | scri  | ptic  | n   |    |    |     |     |   |   |    |   |       | <br>224     |

# List of Figures

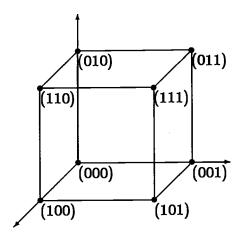

| 21   | Codes words as Cube Vertices                   | • | •   | <br>•  | • | • | • | • | • |   | 35         |

|------|------------------------------------------------|---|-----|--------|---|---|---|---|---|---|------------|

| 3–1  | A Taxonomy of FTFS Design Methods              | • |     | <br>•  |   |   |   |   | • |   | 47         |

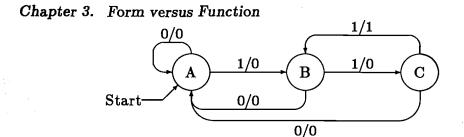

| 3–2  | A 111 detector                                 |   | •   |        | • | • |   |   |   |   | <b>52</b>  |

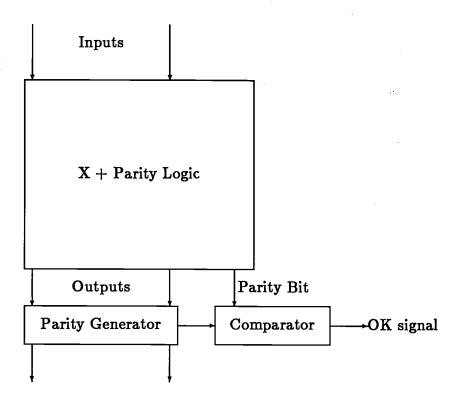

| 3–3  | A structural modification for parity checking. | • |     |        | • | • |   | • |   |   | 55         |

| 3-4  | A mixed modification for parity checking       | • | •   | <br>•  | • | • | • | • | • | • | 56         |

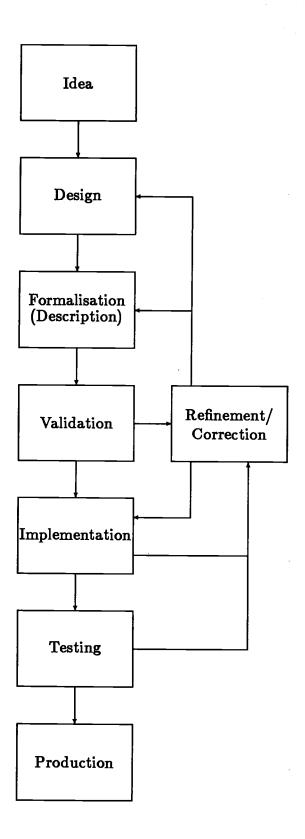

| 4–1  | Stages in the Design Process                   |   | •   | <br>•  | • | • |   |   |   | • | <b>5</b> 9 |

| 4–2  | A Chip Churn Description                       |   |     | <br>•  |   |   |   |   |   |   | 61         |

| 4-3  | A Truth Table File                             |   |     | <br>•  |   | • | • | • | • |   | 61         |

| 4–4  | A CC2 combinatorial function                   |   | •   | <br>٠. |   |   | • |   |   |   | 66         |

| 4–5  | A CC2 sequential function                      |   | •   |        |   |   | • | • | • |   | 66         |

| 4–6  | A parameterised CC2 function                   | • | •   | <br>•  |   | • |   | • | • |   | 67         |

| 4–7  | A CC2 composition block                        |   |     |        |   |   |   | • | • |   | 68         |

| 4–8  | Use of the Prosaic statement                   |   | •   |        |   | • | • | • | • | • | 72         |

| 4–9  | A CC2 example                                  |   | •   | <br>•  |   |   |   | • | • | • | 74         |

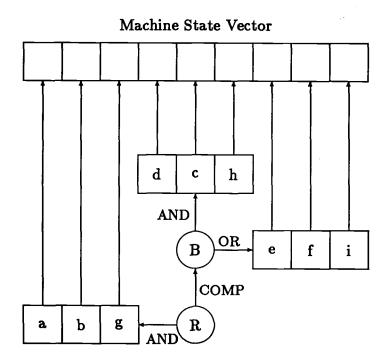

| 4–10 | State Tree Mappings to Machine State Vector    |   | •   |        |   |   | • |   | • | • | 79         |

| 4–11 | Simple Composition example                     |   | • • |        |   | • |   |   |   |   | 79         |

| 4–12 | Function Merging Example                       |   | • • |        | • |   |   |   |   | • | 82         |

| 4~13 | Building a Liszt graph                         |   |     |        |   |   |   |   |   |   | 89         |

| List of Figures                                                       | 10  |

|-----------------------------------------------------------------------|-----|

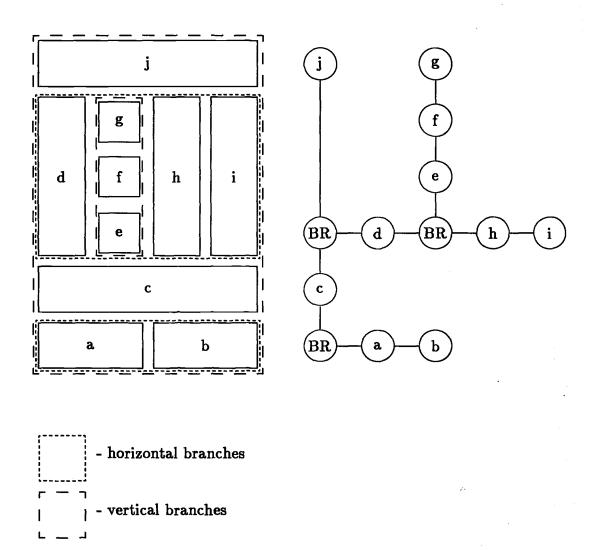

| 4-14 A Simple Liszt Composition - Layout and Graph                    | 90  |

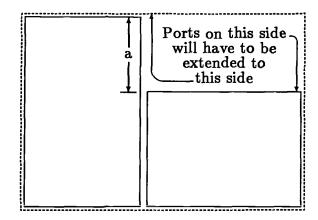

| 4-15 A composition requiring port extension                           | 91  |

| 4-16 A CIF Plot of an Eight-bit ripple carry adder                    | 95  |

| 5-1 Airlock System                                                    | 11  |

| 5-2 CC2 airlock controller                                            | 13  |

| 5-3 Airlock System                                                    | 14  |

| 5-4 The main composition block after functional parity modification 1 | 19  |

| 5-5 General form of structurally modified composition                 | 22  |

| 5-6 The Priority replacement composition for the Parity method 1      | 23  |

| 5-7 The Lala voter/checker composition                                | 24  |

| 5-8 The Lala Priority replacement composition                         | 24  |

| 6-1 A Bitonic Sorting network for 8 input values 1                    | 27  |

| 6-2 Core Machine for Euclid's Algorithm                               | .29 |

| 6-3 CMP IO signals                                                    | .30 |

| 6-4 The CMP Instruction Format                                        | .31 |

| 6-5 The CMP Architecture                                              | .32 |

| B-1 Pseudo-Code for S search routine                                  | .80 |

| C-1 Wino Array Full Adder                                             | .85 |

| E-1 The main CC2 System Components                                    | .90 |

| F-1 A Chip Churn Description                                          | 95  |

| F-2 A Truth Table File                                                | 95  |

| F-3 Plot Of Chip Churn 8 bit ripple carry adder                       | .96 |

| List of | Figures                                                  | 11  |

|---------|----------------------------------------------------------|-----|

| G-1     | The basic airlock controller device                      | 199 |

| G-2     | The TMR modified airlock controller device               | 200 |

| G-3     | The LMR modified airlock controller device               | 201 |

| G-4     | The Structural Parity modified airlock controller device | 202 |

| G–5     | The State Variable Encoded airlock controller device     | 203 |

| G-6     | The Functional Parity airlock controller device          | 204 |

| G-7     | The Functional Tolerance airlock controller device       | 205 |

# List of Tables

| 3–1        | "Cheap" code checking                                            |

|------------|------------------------------------------------------------------|

| 3-2        | A simple coding for the FSM of figure 3-2                        |

| 3–3        | Fault Tolerant coding of FSM in figure 3-2 53                    |

| 5–1        | The Non-concurrent version of the Main Control truth table 117   |

| <b>5–2</b> | Main Control Truth Table modified for link 1                     |

| 5–3        | Original Door Control Truth Table                                |

| 5–4        | Door Control Truth Table Modified for link 1                     |

| 5–5        | Tolerant Modification of Door Control Truth Table for link 1 121 |

| 56         | Parity Modified Priority Table                                   |

| 5–7        | Inverted Priority Table                                          |

| 6–1        | CMP Instruction Set                                              |

| 6–2        | Microcode Instructions                                           |

| 6–3        | "Optimised" Euclid Results                                       |

| 6–4        | Airlock Results                                                  |

| 6–5        | Adder Results                                                    |

| 6–6        | Bitonic Results                                                  |

| 6–7        | Euclid Results                                                   |

| 6–8        | Processor Results                                                |

| List of Tables |        |                       |   |   |   |   |   |   |   |            |   |   |   | 13 |   |   |   |   |   |   |   |   |   |   |   |     |

|----------------|--------|-----------------------|---|---|---|---|---|---|---|------------|---|---|---|----|---|---|---|---|---|---|---|---|---|---|---|-----|

|                | 6–9 II | N plane Logical area  | • |   | • | • |   | • | • | •          | • | • |   | •  | • | • |   | • | • |   |   | • | • |   |   | 145 |

|                | 6–10 O | UT plane Logical area | • | • |   | • | • | • | • | <b>,</b> . | • | • | • |    | • | • | • | • | • | • | • | • | • | • | • | 14  |

# Chapter 1

# Introduction

# 1.1 Critical Systems

Integrated circuits have influenced 20th century western civilisation almost as much as the harnessing of steam power affected the same civilisation one and a half centuries earlier. In the 20 years since their development, ICs have found their way into innumerable everyday items and few aspects of modern life have escaped the influence of the ubiquitous "micro-chip". It is now quite common for highly complex electronic systems to be responsible for the lives or livelihoods of large numbers of people. It is clear that such *Critical Systems*, as they will be called here, must be reliable.

There are many examples of critical systems, for instance: control computers for power stations and transport systems, such as air traffic and railways; commercial computers controlling on-line services such as share transactions; avionics systems which help to control aircraft; and medical systems such as pacemakers, patient monitoring equipment and life support machines. In some of these applications the size of the system is of secondary importance to safety, but in others there must be some trade-off between size and reliability.

Though reliability is at a premium in critical systems, there are benefits to be gained from improving the reliability of many types of device. In fact there are commercial benefits to be accrued from improving the reliability of almost all electronic systems, from washing machines to mainframe computers.

As integrated circuits become smaller and the complexity of VLSI devices increases, the trend towards "systems on silicon" accelerates. This is the process whereby complete electronic systems, which may once have occupied several printed circuit boards (PCBs), are realised as single VLSI chips or small chip sets. In applications where size and weight are constrained, critical systems will also be translated to silicon and it is therefore important to study the design of reliable VLSI devices.

# 1.2 Trust

If a device is to be seen as trustworthy, that is if you are going to ship it in a product or rely on it for your life, it must be tested in some way. Such "confidence" testing can take many forms, from one-off batch inspection to prolonged in situ evaluation. All testing is aimed at deciding whether or not a device is working. This thesis seeks to divide testing into two basic types: static and dynamic. Static tests are those tests which occur once, or infrequently, and do not occur during the normal operation of a device. Dynamic tests can be continuous or sporadic but are concurrent with the operation of a device. The main interest of this thesis is in dynamic testing.

The term "reliability" has both quantitative and qualitative connotations and it is in the latter sense that it is used in this work. It should be noted that reliability is used in a more general sense here to encompass the notion of fault security as well as fault tolerance.

Fault tolerant systems are capable of continuing to operate correctly in the presence of certain faults or types of fault. Fault secure systems behave in such a way that an external agency can observe whether certain types of fault have occurred in the system. This means that either the fault secure system can identify and flag faults, or that it behaves in some recognisably illegal way in the presence of faults. Thus fault tolerant and fault secure (FTFS) systems are reliable in the sense that the former can be relied upon to operate in the

presence of some faults, and the latter can be relied upon to indicate that they are faulty.

Though the study of FTFS systems is not restricted to the area of VLSI device design, it is to this area that this work has been directed. It will be seen later that many of the results of the work can be applied to a wider range of implementation styles.

# 1.3 VLSI Design

Designing any type of complex electronic system is a difficult task and there are features of designing in silicon which further complicate matters. In particular the "manufacture-debug" cycle is slow and expensive. This severely limits the number of design iterations which are commercially feasible. The testing of VLSI devices can be expensive in time, effort and money. This is because of the difficulty of gaining access to the individual components which make up a VLSI device.

Approaches to the problem of managing the complexity of VLSI design are as old as the problem itself. The simple expedient of employing structured design is now well known and widely used. By using high level languages for behavious description and abstraction, the VLSI design process can be moved away from the consideration of individual device elements such as gates. The use of CAD tools is now almost universal and it is generally accepted that the design of modern VLSI devices would be impossible without such tools.

The following list indicates a few of the areas in which computers and CAD tools can be of use in the design of VLSI devices.

- Managing the design task. Version and source control etc.

- Synthesis systems such as sticks and mask editors.

- Checking of design and electrical rules etc.

- Design Verification.

- Design Simulation.

- Testing e.g. test pattern generation, testability analysis etc.

- Computationally expensive tasks such as Pattern Generation for mask making.

- Automation, e.g. cell generation, routing, placement etc.

- Abstraction e.g. structured design and high level descriptions.

- Simplification. Reducing the total volume of knowledge required by a designer

As VLSI devices become yet more complex, the sophistication of the CAD tools used in their design must also increase. In some senses the "ultimate" CAD tool is the silicon compiler. The aim of silicon compilation is no less than the complete automation of the design process from specification to implementation.

Though a silicon compiler could be seen as a black box taking design specifications in at one end and producing chips at the other, this view is neither realistic nor desirable in the short term. Current silicon compilers cover a range of the design tasks but typically do not handle those levels of design below the generation of artwork. The question of where certain types of checking are carried out varies from system to system; it is not unusual for design and electrical rule checking to be carried out on mask data for completed designs outwith a silicon compiler.

Most currently available silicon compilers allow some form of manual intervention; the extent and level of this intervention varies. Designer intervention is a two edged sword; many systems could not operate realistically without it, but it is a source of potential error with which a system may not be able to cope. Manual intervention is used either because a designer can carry out a

task better than the automatic system or because a designer "knows more". A typical example of superior knowledge is the selective breaking of geometry rules in leaf cell design.

It was claimed earlier that CAD tools could simplify the design task by reducing the amount of knowledge required by a designer. If a silicon compiler requires no manual intervention and guarantees to produce correct silicon, it can remove the need for a designer to equire knowledge about some aspects of the design process. Such completely automatic systems can also provide access to VLSI devices for designers with little or no experience of VLSI design.

It is not only the naïve user who can benefit from the inherent knowledge built into a silicon compiler. Experienced designers can be exposed to new ideas, for instance in design for testability (DFT).

# 1.4 Rationale

The primary object of this study has been the investigation of fault tolerant and fault secure system design within the framework of silicon compilation. It is only within such a framework that a realistic study of automatic methods can be carried out.

If a silicon compiler is to relieve the designer of some of the burden of knowledge, it must itself possess that knowledge which the user lacks. It must also be able to apply that knowledge in the design process. The problems of obtaining knowledge and encapsulating it within a system are aspects of knowledge engineering which are not addressed in this thesis.

To be able to use knowledge not possessed by a designer, a system must either influence the designer, in some sense *educate* him, or change the characteristics of the design autonomously. For a completely automatic system, it must be the design which is changed, rather than the designer.

# 1.5 Chapter Outline

# 1.5.1 Chapter1

This introductory chapter has sought to show that the design of reliable VLSI devices is desirable for both critical systems and more mundane applications. It has also been suggested that the silicon compiler represents the most sophisticated approach to the design of VLSI devices. Therefore it has been decided to study the design of FTFS devices within the framework of silicon compilation.

# 1.5.2 Chapter 2

The next chapter will look at the general area of device testing. The object of this chapter is to identify existing ideas which would be suitable for automatic application. Particular note will be made of some schemes suggested for designing easily testable or self-testing programmable logic arrays (PLAs).

# 1.5.3 Chapter 3

The work in this chapter is intended to establish a taxonomic framework into which existing and suggested FTFS methods can be placed. Such a taxonomy provides a structure within which to carry out further investigation. It also indicates areas where new methods might most usefully be sought.

# 1.5.4 Chapter 4

Having identified possible methods of producing FTFS systems, and having decided to implement those systems automatically, it becomes necessary to provide an automatic design environment. Chapter 4 describes Chip Churn 2 (CC2) which is such an environment. The history of CC2 is described, with

particular reference to Chip Churn, its predecessor. The main elements of CC2, the language, the simulator and the back-end will be covered.

# 1.5.5 Chapter 5

A number of automatic FTFS methods have been implemented within the CC2 environment. In this chapter these methods are described and their implementation is explained. A worked example of a simple controller design is also presented.

# 1.5.6 Chapter 6

This chapter presents a number of example CC2 designs and looks at how they can be modified automatically to become FTFS. The examples range in complexity from a simple 8 bit adder to a complete microprocessor. The results of applying automatic design modifications are presented.

# 1.5.7 Chapter 7

The final chapter highlights the important elements of this work. Many of the problems which have been encountered are discussed and ideas for further work are suggested.

# Chapter 2

# Testing and Reliability

In the introduction, it was stated that testing was an essential "confidence building" exercise in the design and production of any system. This chapter looks at some of the existing methods of carrying out testing. It was established in the introduction that this work is directed towards the implementation of automatic design of FTFS systems. To this end, this chapter is intended to identify those methods which might be applicable in this area. Trends towards autonomous test and automatic design for testability are also of interest and are therefore mentioned.

# 2.1 Test and Testability

### 2.1.1 What Causes Faults?

Broadly speaking there are four types of fault which can occur in VLSI devices; some of these faults can also occur in other types of system. The first type of fault is the design fault. Design faults can arise from errors in the design specification or faulty implementation; this can make them very difficult to identify. There should be no design faults in production devices but sometimes there are. The second type of fault is the fabrication fault. Fabrication faults occur during manufacture and can result from such things as badly aligned

or damaged masks. Ideally all fabrication faults would be identified by the manufacturer but again not all of them are. The third class of fault is caused by fatigue failure; for example, PCB failure due to vibration or damage of a VLSI device by metal migration. A manufacturer cannot test for fatigue faults as they are not present when a system is "shipped". However, the manufacturer should have designed and tested the system so that fatigue faults are unlikely in the expected working environment. The final class of faults are transient faults. These are faults which cause no permanent damage to a system. Transient faults can be the most difficult to find and can be the result of faulty design, such as an unstable reset line, or short lived environmental effects such as radioactive decay or electro-magnetic pulse (EMP).

The testing of devices, which will be discussed next, is intended to identify the first three classes of fault. These permanent faults should always be identifiable in a system once they have occurred. There is no sure way of testing for transient faults other than by monitoring the actual operation of a device.

### 2.1.2 The Problem.

All testing is designed to answer the question, "Does the device under test (DUT) operate as expected?". As the complexity of the DUT increases, it becomes more difficult to give a categorical response to this question. In simple devices, exhaustive testing can be employed. In an exhaustive test every possible input pattern is supplied to the DUT and its outputs are compared with the expected outputs. In sequential logic there is the added problem of having to stimulate the DUT in every possible state. With complex devices containing sequential logic, it rapidly becomes impractical to rely on exhaustive testing.

Exhaustive testing effectively answers the question, "Does it work?". Beyond exhaustive testing, it becomes more common only to answer the question, "Can any faults be found?", the assumption being that it is simpler, or more practical, to find faults than it is to prove correctness. In order to be able to say whether any faults can be found, it is first necessary to decide which faults

are likely to occur and therefore which faults will be sought. In other words it is necessary to adopt a fault model.

Strictly speaking a fault model is not essential and random testing could be carried out without one. Random testing [2] means applying randomly selected input patterns to the DUT and comparing the outputs with the expected responses. However, without a notion of what faults to expect, it is difficult to gauge how effective random testing will be for a given DUT.

To identify faults in a system it must be possible to stimulate a DUT in such a way that its response in the presence of a fault differs from its fault free response. If such a stimulation is impossible, the fault is undetectable. In effect the fault is not a fault at all, in that the DUT performs identically with or without it. This may seem paradoxical, but an example can be found in certain types of programmable logic array (PLA) where the presence or absence of a contact has no effect on the function realised by the PLA.

Once the simple approaches to testing become inadequate, two characteristics of a device become important. Those characteristics are *controllability* and *observability*. These are, respectively, the ability to control what is going on, and the ability to observe what is going on. The idea of controllability goes beyond a simple ability to control the inputs to a functional unit; in the case of sequential logic it is necessary to be able to control the internal state of a unit.

Controllability and observability are essential in fault identification testing because of the need to stimulate identified parts of a device. Take for example a DUT in which a fault model allows for a particular gate to have its output value stuck at 0. To test whether that fault exists, it is necessary to provide an input pattern to the gate which would, under fault free operation, result in a 1 being output. In other words, it is necessary to control the inputs to the gate and observe the outputs from it. If the gate is buried in the middle of a piece of complex logic, it will be necessary to guide the required input signal through other gates and to observe the output as an effect on other gates.

Controllability and observability are inherent characteristics of a device and

so it is essential that the *testability* of a device is considered during the design process. The need to consider the testability of systems during their design has given rise to the ideas which are embodied in the principles of *design for testability* (DFT).

# 2.1.3 Verification versus Confidence

It is possible to identify two separate reasons for testing. The first is *verification* testing which is used to check that a design has been implemented correctly. The second is *confidence* testing which is used to check that a particular instance of an implementation does not contain any faults. Confidence testing can be carried out once only, for example at the time of manufacture, or sporadically, for instance whenever a test program is run.

As the need for verification testing is transient, verification test measures might, in theory, be absent from a production device. In practice it is seldom the case that verification and confidence testing are separated. This is because of the cost of design effort and fabrication. If the testability features of a design are to be discarded, so is the design effort that went into them. Also the cost of fabricating the prototypes must be written off; this is because the production devices will not be exactly the same as the development devices. The need for verification testing of individual functional units should decline as the use of verified cell generators and the like becomes more widespread.

# 2.1.4 Design For Testability

There are a number of papers, books and tutorial guides such as [56] and [4], which give a general introduction to this area. What follows is a brief outline of the main methods suggested for use in DFT.

# Scan/Set Logic

The simplest approach to improving the controllability and observability of a system is to add test points into the design. Ideally test points would be connected directly to the outside world via input/output pads. However, in most designs the large number of test points would make it impractical to connect directly to pads. In the Scan/Set logic [56] scheme, the test points are connected to a shift register on the device itself; this allows test data to be shifted in and out serially; thus reducing the number of test pads required.

# Scan Path Logic and LSSD

The problem of controlling the internal states of sequential logic has already been mentioned. The problem can be reduced to one of controlling that part of the sequential logic which constitutes its memory. If this memory cannot be directly controlled, it is necessary to develop such measures as "homing sequences". A homing sequence is a procedure whereby a piece of sequential logic can be taken from any state to a known state. Clearly there are simpler approaches to the problem, such as incorporating a reset signal which takes the machine directly to a known state. However, the best possible control which can be obtained is the ability to set the memory elements directly; this allows control of the state of the sequential logic.

Scan Path Logic [15] and Level Sensitive Scan Design (LSSD) [12] approach the problem of controllability and observability in essentially the same way. All the latches used in a design are of a special type which can be configured to work in one of two modes. In the first mode, the latch behaves ordinarily, but in the second, it can be used as an element in a shift register. The configuration of the latch can be carried out dynamically by the use of control signals.

If a design is partitioned in such a way that there are latches at the inputs and outputs of all the main functional blocks, then the shift register composed of all the latches in the device allows the inputs to a block to be controlled, and its outputs observed. In addition, if the latches are used as the memory elements of any sequential logic, the state of that logic can be controlled; this reduces the testability problem to one of testing combinatorial logic.

### Signature Analysis

One problem with testing can be the volume of input and output data. To reduce the amount of output data that has to be processed, a number of data compression techniques have been developed.

Data compression methods can be seen as mapping between a set of possible outputs and a smaller set of check patterns. Because the set of check patterns is smaller than the output set, information is lost during the mapping process. In effect, each check pattern has more than one output pattern mapped into it; this makes it possible for a faulty output to map to the same check pattern as its fault free equivalent. Faulty outputs which are mapped to their fault free equivalents will not be detected.

Perhaps the simplest form of data compression is transition counting [23]. This involves keeping a running total of the number of times that the output stream switches between logic states.

Signature Analysis [24] was developed as a data compression technique with particular application in the testing of PCB systems. The compression principle is based on the use of a linear feedback shift register (LFSR). Such shift registers can be used as pseudo-random binary sequence (PRBS) generators. With a suitable selection of feedback taps, such generators can be made to cycle through all possible internal states before repeating themselves. If an output stream is EXORed into a LFSR, the sequence of generated states is altered. So, if during a test the output stream from a DUT is fed into a LFSR, it will produce, at the end of the test, a value in the LFSR which represents a "signature" for the output stream under examination.

Some of the mathematical properties of signature analysis are discussed in [14], where it is also compared with transition counting. There are two main

points noted in this paper, the first is that signature analysis can detect all single bit errors. That is to say, no two output streams which differ in only one bit can produce the same signature. The second result quoted in the paper is that as the length of the output sequence gets larger, the chance of failing to detect a multi-bit error tends towards:

$\frac{1}{2^n}$

where n is the number of registers in the LFSR.

### Syndrome Testable Design

Another testability method which deserves note is that of syndrome testability [48]. The syndrome of a combinatorial logic function can be obtained by counting the number of 1s present in the output stream produced by an exhaustive test of the function. The advantages of this method are that the test patterns are easily generated, the output method is in itself a data compression technique, and the expected result of the test can be calculated mathematically from the function of the DUT.

# 2.1.5 Test Patterns and Expected Results

Test pattern generation (TPG) for exhaustive testing is straightforward; the test set being made up of all the possible inputs to a system. When the aim of testing is the identification of faults, TPG is more problematic. The task is to derive a set of inputs for a device which will identify a number of possible faults. We have already seen that a fault model is essential to establish which faults are expected. Once the set of possible faults has been decided upon, the TPG problem is one of deciding how to feed the appropriate input patterns to those areas of a device where faults might occur, and then to guide the results to a point where they can be observed. A number of algorithms such as the D-algorithm [45] and PODEM [19] have been used for TPG.

The expected results of a test can be derived from simulation or from existing versions of a device which are known to contain no faults. Such "known-good" devices are often called *gold units*.

# 2.1.6 Built In Self-Test (BIST)

The use of design for testability measures is intended to produce designs which are controllable and observable. Even when this aim is achieved, there are still the problems of TPG, the application of the test patterns and the analysis of the results. One drawback of scan based systems is that they work serially. This can slow down the performance of a test, a test being the application of the test patterns and the collection of the output data. It may be possible to execute a number of tests on different blocks in parallel and some work, such as [8], has attempted to speed up the test process by using such parallel test scheduling.

As we have seen, the primary steps in the testing process are test pattern generation, test pattern application and test result evaluation. The object of BIST [39],[32] is to move all three of these steps onto the DUT. Most of the current BIST techniques adopt a broadly similar approach to the problem and what follows is an outline of that approach.

It would be impractical to carry out automatic TPG (ATPG) "on-chip" if that ATPG were based upon some sophisticated algorithm. Consequently a return to the use of pseudo-random and exhaustive testing has taken place. As we saw earlier, exhaustive testing is impractical for complex devices so for BIST methods to employ this kind of testing, complex designs must be partitioned into units which can be exhaustively tested in a reasonable amount of time. Not all devices are so complex that they need to be partitioned. The work presented in [42] used special pads capable of test pattern generation and test pattern compaction, in order to carry out autonomous test of complete chips. The particular feature of the devices discussed in [42] which make them testable in this way is that they are serial.

Scan paths can be used to partition a design but they have other uses as well. LFSRs can be used for data compression (signature analysis) and as PRBS generators. So if a device is partitioned in such a way that its inputs come from a set of latches, and its outputs go into a set of latches, it is possible to configure the former to be a PRBS generator and the latter to be a signature analyser. The Built In Logic Block Observer (BILBO) is an example of this type of special register. The PRBS generators in these scan type applications differ from the original signature analysis LFSRs in that they compress multi-bit streams rather than single bit streams.

Once a test has been performed, the result needs to be compared with the expected result. This comparison can either be done off-chip, or can be hardwired into the device.

### 2.1.7 Automation

Currently, aids to DFT and BIST are more common than completely automatic approaches. TMEAS [21] and CAMELOT [4] are examples of testability measurement programs. These are intended to provide a designer with some idea as to how difficult it will be to test a device. To this end they provide metrics or scores for parts of a design; these measures reflect the controllability and observability of those parts. There are knowledge based approaches to both testability in [1] and BIST in [28] but again, neither are integrated into a complete design environment. However the work described in [16] and [3] does attempt to automate the process of DFT and BIST within a design environment.

# 2.1.8 Programmable Logic Arrays (PLAs)

The PLA is possibly the most widely used and widely studied circuit idiom currently available to the VLSI designer. Because PLAs have a very regular structure and are straightforward to generate automatically, they have become

popular for realising arbitrary logic such as datapath controllers. The regular structure of the PLA and its widespread use have led to the development of testability aids directed specifically at the PLA.

In [9] Cha presented a fault model for PLAs and a TPG method for the model<sup>1</sup>. The design of testable PLAs has been studied in [30] and elsewhere. In other work such as [17] and [18] styles of PLA design which have function independent tests have been suggested. These projects aim to produce PLAs which can be tested by universal test sets, thereby reducing the TPG problem. The main technique employed in these papers is the addition of logic which allows individual bit and product lines to be stimulated. The product lines are controlled by a shift register and simple select lines are used to control the bit lines; this allows step by step checking for cross point faults.

Self-testing of PLAs has also been studied. In [11] the AND and OR planes of a PLA are partitioned and each is tested by use of BILBO registers. The work in [20] uses the idea of function independent test sets to implement self-test. The PLAs are designed so that they can be tested with a very simple universal test set; this test set can be generated by extra logic in the PLA.

Possibly the most interesting work from the FTFS point of view is that presented in [31]. This paper presents a collection of methods which can be used to create PLAs which carry out concurrent error detection. The main limitation of the work presented is that it claims only to work on non-concurrent PLAs. Those are PLAs in which any input pattern selects only one product term. This is a severe limitation as a large percentage of minimised PLAs will be concurrent. However methods are presented in the paper which can be applied to concurrent PLAs, in particular the use of two-rail code checkers to check the input buffer lines. Two-rail codes will be mentioned later, but the point noted in the paper is that the input buffers of a PLA always produce the input signal

<sup>&</sup>lt;sup>1</sup>A version of this TPG method was implemented for the Chip Churn system

and its inverse. Therefore if the buffer lines ever had the same value, an error would have occurred.

### 2.1.9 Limitations of Static Test Methods.

So far this chapter has shown how the growing complexity of devices has led to a need for more sophisticated testing methods. Yet even the most advanced BIST techniques are static in the sense that they perform testing outwith the normal operation of a device. This means that they can only be used to check a device at some point before normal operation begins. In systems which do not need to operate continuously, BIST methods could be used during idle cycles. Though this would provide a more consistent test coverage, it would still not indicate that a device was operating correctly.

# 2.2 Reliability

In the introduction to this thesis, we saw that there was a growing need to study the design of reliable VLSI devices. However, the need for reliable electronic systems is not new and a large body of work relating to reliability already exists. Not all of the methods popular with the implementors of reliable systems are applicable to VLSI devices. For instance on-line maintenance would be difficult, if not impossible, to implement at the chip level<sup>2</sup>. What follows is an outline of some of the main aspects of reliable system design as they relate to the development of reliable VLSI devices.

<sup>&</sup>lt;sup>2</sup>On line maintenance of multi-chip systems is not impossible.

# 2.2.1 What is required?

If a device is to be considered trustworthy, it must either be fault tolerant or fault secure. If a device is to be fault tolerant it must be able to exhibit fault-free behaviour in the presence of a fault. To do this it must either have enough duplicate hardware to replace that which is at fault, or it must be able to recreate a fault-free behaviour from a faulty one. A fault secure device must contain some method of differentiating between faulty and fault-free operation, or faulty outputs from it must be easily identified.

Of the four types of fault described in section 2.1.1, FTFS systems should be able to cope with all but design faults and even some of these might be detected. Having said that, reasonable care in the fabrication testing of devices should eliminate all faults except transient ones and those fatigue failures which occur during the normal operation of a device. Confidence or fabrication testing of FTFS devices can make use of the concurrent tests being carried out by the devices. So FTFS devices can be tested by use of random or selective system excitations.

It is fair to say that it would be impossible to make a completely FTFS VLSI device. This is because there are certain types of catastrophic failure against which it would be difficult to guard; for instance power failure or static discharge which resulted in device destruction. Though they may seem extreme, these types of disastrous faults are in some ways more difficult to avoid in VLSI devices than in larger systems. The size of VLSI systems makes duplication of such things as power supplies more expensive than for larger systems.

It should also be noted that certain types of technology are susceptible to specific failures, for instance CMOS and "latch-up". If a device is to be placed in an environment which is hostile to a particular technology, it makes no sense to use that technology in the implementation of the device. A change to a less vulnerable technology is likely to be more valuable than an investment in FTFS techniques for the susceptible technology.

A common feature of most FTFS systems is that they should be able to identify if a fault has occurred and, in the case of fault tolerant systems, take some corrective action. Not all fault tolerant systems are fault secure as certain fault tolerant techniques do not rely on fault identification. In the following sections a number of FTFS methods will be outlined.

# 2.2.2 Hardware Redundancy

Hardware redundancy is a major technique used in the design of reliable systems. The idea of on-line maintenance mentioned earlier is based on an ability to remove parts of a system without affecting its operation. This allows faulty units to be replaced without having to stop the whole system. To allow this kind of flexibility, it is necessary to have at least two working copies of any module which might have to be replaced. Still, the results of such efforts can be remarkable. The Bell ESS telephone exchange cited in [35] was designed for a maximum of 2 hours "down-time" in forty years, and achieved that performance.

The classic example of hardware duplication is Triple Modular Redundancy (TMR); a specific instance of the more general N Modular Redundancy (NMR). The basic principle of NMR systems is to have n copies of each function and to "vote" on the result. An NMR system can tolerate m faults where

$$m \leq \frac{n}{2} - 1$$

This is because there must always be a majority decision on the fault free output. Typically in NMR systems n is odd thus avoiding the possibility of a tied vote. An NMR system in which n = 2 would be fault secure to single faults.

It should be noted that modular redundancy carries a reliability overhead in that there are n times as many components that might fail. So, for instance, the 2MR fault secure system would have a mean time to failure (MTF) of about half that of the equivalent simplex system. There is also a question of faults in the voting mechanism - the precautions of having duplicate hardware will come to naught if there is a single voter and it fails.

There are many flavours of hardware redundancy systems and not all of them keep duplicate hardware working in parallel. It is possible to keep redundant modules as "spares" to be switched in if the main unit fails. Systems which adopt this approach rely on error detection mechanisms to identify when a unit has failed and should be switched out. Voting is, conceptually at least, the simplest form of error detection but in the absence of operating duplicate hardware, other mechanisms have to be adopted. Some of these mechanisms will be discussed in the following section.

### 2.2.3 Information Redundancy

Probably the most widely used example of information redundancy is the error detecting/correcting code. These codes have been used extensively to cope with data transmission through a noisy communications channel. As their name suggests, these codes are designed to deal with errors rather than faults, i.e. they deal with the effect of a fault rather than the fault itself.

Error detecting/correcting codes are not new to the field of VLSI devices. Such codes have been widely used to improve the reliability of memory devices such as RAMs. The simplest error detection code is probably the single parity bit. Effectively the modulo 2 sum of the bits in a code word<sup>3</sup>, single bit parity is able to detect all odd bit errors which might occur in a code word.

## 2.2.4 Codes and Coding

Before going on to talk about specific codes, it might be worth looking at codes in general.

<sup>&</sup>lt;sup>3</sup>This is for even parity, odd parity is the inverse of this.

Figure 2-1: Codes words as Cube Vertices

#### **Background**

Any sequence of binary digits can be viewed as a code word. For a sequence of m bits there are  $2^m$  possible bit patterns and so the same number of code words. An n bit code can be seen as a set of co-ordinates for a vertex of an n-dimensional unit cube. Figure 2-1 illustrates this idea for a 3 bit code. Any error in the transmission of a code word will change the vertex to which the code refers. An m bit error will move a vertex by m edges, so if two code words map to vertices m edges apart, such an error might transform one into the other. The minimum number of edges between two vertices represents the number of bits by which the two corresponding code words differ. This value is known as the *Hamming Distance*.

The basic principle of error detection coding is to choose a set of code words which are greater than a certain distance apart. For instance if a code is to be able to detect all single bit errors, none of the code words can represent adjacent vertices. Choosing a subset of the vertices of the n-cube creates a complimentary set of vertices which represent invalid code words.

Error correction codes work on the principle of chosing vertices (code words) so that no error could move a valid vertex closer to another valid vertex than it was to the original. In other words, if n bit error correction is required, vertices

should be m edges apart where

$$m \geq 2n + 1$$

In this way any error of n bits or less will leave the resulting code word closer to its original vertex than it is to any other valid code vertex.

Other forms of error detection, such as those designed to detect specific types of error, work by selecting vertices so that any error of the given type will transform a valid vertex to an invalid one. For instance parity codes can detect all odd bit errors because they represent only even (or only odd) vertices and it is impossible to find a path with an odd number of edges between two such vertices.

#### Separable and Non-Separable Codes

In general, information which has to be coded is already itself a binary code; in this situation there are two approaches to the encoding process. The first approach adds information to the existing code, for instance a parity bit. The added information increases the Hamming distance of the original code to give it error detection/correction properties. The alternative approach is to map the existing code words into a new set of code words which may not have any bit patterns in common with the original set. The first of these approaches yields separable codes, so called because the check bits are separable from the information bits. The second method produces non-separable codes. Once a separable code has been checked, it can be translated back to the source code simply by stripping off the check bits. Non-separable codes have to be mapped back into the source code. This means that the checker/translator for a non-separable code must contain knowledge of the information being transmitted whereas that for a separable code need only know about the coding method used.

To illustrate this point consider the transmission of the information {(00),(10), (01),(11)}. If coded using an even parity bit the transmission code would

be {(000),(101),(011),(110)}. All that the checker/translator would need to know was that the last bit of the message should be the modulo 2 sum of the other bits, and that the actual message was all the bits but the last one. On the other hand, if a 1-of-4 code was used, the transmission code would be {(1000),(0100),(0010),(0001)}. In this case the checker/translator would need to know that it should only expect one 1 in any message. It would also have to know how to map the received code word back into the information bits.

Because non-separable codes require information about what is being sent, they are seldom used in transmission applications. They are usually used in systems where code translation is unnecessary, for instance for internal bus communication on VLSI devices.

#### **Parity**

In its simplest form, parity coding uses vertices a minimum of 2 edges apart. This allows the detection of all odd bit errors. The appeal of parity coding is its extreme simplicity and low overhead. Any set of code words with a Hamming distance of one can have that distance extended to two by the addition of a single extra parity bit.

The main drawback of parity coding is the low error coverage it provides. If the number of erroneous bits in a code word were random, parity would detect only about half of the corrupted transmissions. It is possible to improve the error coverage of parity codes by adopting group parity. In this scheme collections of bits in a source code are each given their own check bit. This increases the overhead of the code but also its error detection ability.

#### **Hamming Codes**

In order to be able to correct single bit errors a code must have a Hamming distance of at least three. Though it is relatively straightforward to generate non-separable codes with this property, some algorithm must be sought to generate suitable separable codes. Hamming codes [22] use just such an algorithm.

In a Hamming code the check bits occupy those bit positions which are a power of two, i.e. 1,2,4,8,16, etc. Each of these check bits is a parity bit for a collection of other bits, including check bits, in the code word. Though this may seem unnecessarily complicated, the checking procedure for the code makes error location very simple. The check procedure works by building up a second binary number by examining the check bits in the transmitted code. If a check bit is correct, a 0 is placed in this secondary number whereas an error causes a 1 to be used, these bits are arranged from right to left and eventually yield an n bit binary number where n is the number of check bits in the code. When this number is finished, it represents the binary value of the bit position which is in error. If the value is zero, there is no error.

#### Residue Codes

Residue codes are a class of separable codes in which the check bits are composed of the modulo n remainder of the number represented by the source code word. Residue codes have attracted particular attention because if n is chosen such that

$$n=2^l-1$$

where  $l\geq 2$

then a checker for the code can be implemented by a tree of -bit adders with end-around carry. Residue codes with this property are called *low-cost residue* codes and the typical value of n is 3.

#### **Berger Codes**

Berger codes are separable codes in which the check bits are the inverse of the number of 1s in the source code word. For example, the check bits for the code word (1000101) would be the inverse of (011) that is (100). Berger codes have the property that they can detect all unidirectional errors in a code word, that is errors which only change 1s to 0s or 0s to 1s but not both. The calculation of Berger codes in straightforward.

#### N-of-M Codes

N-of-M codes are a class of non-separable codes in which the code word length is m and the number of 1s in a code word is always n. N-of-M codes are a particular instance of *unordered codes*. These are codes in which no code word contains a set of ones which are a subset of the ones in another code word. This gives them the property that they can detect all unidirectional errors.

#### Serial and Parallel Codes

Many codes, particularly those inherited from the field of data communications, are easily checked by serial mechanisms. Little, if anything, is ever said about the difficulty and expense of code checking in parallel. Checking with trees of checkers such as EXOR gates for parity, or adders for low-cost residue codes, is not truly parallel and incurs a heavy cost for long code words.

#### **Omissions**

Certain types of codes have been omitted from this discussion because they do not map easily into the sorts of applications envisaged here. Most notable among these omissions is the class of *block codes*. For this type of code check bits are calculated for blocks of code words, something not often required within VLSI devices.

Another class of codes which have not been explicitly discussed are those codes which preserve their check bit integrity under simple arithmetic operations. These types of code can be used in arithmetic chips but their use was considered too limited for application to more general systems. This does not mean that no codes of this type have been considered, rather that they were not considered for this property alone.

## 2.2.5 Totally Self-Checking Checkers

The aim of totally self-checking logic is to produce outputs which can easily be identified as correct or faulty. In [35] Lala devotes an entire section to the design of TSCCs for different types of codes. Totally self-checking checkers (TSCCs) produce outputs in the form of two-rail or 1-of-2 codes; thus their only valid outputs are 10 and 01. This makes them able to detect stuck-at faults. The simplest form of TSCC checks 1-of-2 codes; thus allowing TSCCs to be used on the product of TSCCs. The following logic equations describe just such a TSCC:

$$c_0 = (x_0.y_1) + (y_0.x_1)$$

$$c_1 = (x_0.x_1) + (y_0.y_1)$$

Here  $c_0$  and  $c_1$  are the two-rail code and  $(x_0,x_1)$  and  $(y_0,y_1)$  are the two input codes. This checker is totally self-checking for all unidirectional faults.

## 2.2.6 Systemic Approaches

Hardware redundancy and localised checking can be applied at the level of individual function blocks in a design. An alternative approach to designing FTFS devices is to work at the systems level where architectural choices can be made. The design of FTFS systems for particular types of architecture, such as systolic arrays, has been studied; as has the design of fault tolerant microprocessors, as in [13]. Unfortunately these methods represent an ad hoc approach to the problem which it would be difficult to incorporate in a general automatic system. For this reason these methods are not considered here.

## 2.2.7 General Approaches

Though there is no lack of material which relates to the systemic design of FTFS systems, and particular techniques also abound, little work has been carried out on the automatic implementation of FTFS techniques. This does not mean that

methods suitable for automatic application have not been suggested as such. In [49] and [51] the application of low-cost residue codes is suggested as just such an automatic method, and in [50] a manual implementation of the ideas is presented. We have already seen that low cost residue codes are attractive because of the straightforward checking logic they require; another advantage is the predetermined nature of the check bits.

## 2.3 Conclusions

We have seen that redundant hardware can be used to duplicate function in order to provide FTFS systems and that redundant information in the form of coding can be used to detect and correct errors. How then can these techniques be applied automatically to implement FTFS systems? The next chapter presents a taxonomy for automatic techniques and suggests some examples of FTFS techniques which might be applied automatically.

## Chapter 3

## Form versus Function

## 3.1 Introduction

It has already been established that the aim of this thesis is to study the automatic design of FTFS systems. Design modification has been identified as a mechanism by which FTFS features can be introduced into a design. This chapter is intended to establish a framework in which to study FTFS system design methods; to this end a classification of design modification techniques is presented.

Three general terms will now be defined; though some people might disagree with these definitions, they are made at this point to clarify their use in the following discussion. These definitions are:

Behaviour The behaviour of a system is the way in which it responds to stimulation. In simple IO terms, it is the pattern of outputs produced by inputs to the system. For instance the behaviour of a five input AND gate is that it produces a 1 at the output if and only if all of its inputs are 1.

Function The function of a system is the method by which it achieves its behaviour. So the behaviour of a five input AND gate might be achieved by a single complex gate or as a cascade of two input AND gates.

Structure The structure of a system is the way in which the function is implemented.

The term design modification is used here to describe a process of changing a design specification so as to modify the characteristics of the design without modifying its behaviour. It should be differentiated from the more widely used term design transformation. Design transformation takes a design specification between description levels, for instance in transforming a structural specification to an artwork layout.

This chapter suggests that there are essentially two types of design modification. These are structural modifications, which change the form or structure, and functional modifications which change the function of a design. Hence a functional design modification takes a functional design description and produces another, different functional description. Similarly structural modification effects changes in the structural description or at the structural level of a design. Though a functional modification may imply a change in the structure of a design, it is not at the structural level that the change originates.

For a simple example of modification, we move away from the field of FTFS systems for a moment. Consider a design consisting of a single two input AND gate which must be modified to AND together three signals. The modification could be achieved either by designing a three input AND gate or by using two of the original AND gates cascaded together. The first of these modifications represents a functional change because the design remains one consisting of a single functional unit, whereas the second change is structural because the new design consists of two functional units rather than one.

As another example consider a two-bit ripple carry adder made up of two full adders. These full adders will communicate by means of a ripple carry signal. If the adders were modified to use a two rail code for the carry signal, the behaviour of the design would not be affected but the function and structure would.

### 3.1.1 Function (or What It Does)