# Design and characterisation of a ferroelectric liquid crystal over silicon spatial light modulator

Dwayne C. Burns

Thesis submitted for the degree of Doctor of Philosophy The University of Edinburgh

1994

#### Abstract

Many optical processing systems rely critically on the availability of high performance, electrically-addressed spatial light modulators. Ferroelectric liquid crystal over silicon is an attractive spatial light modulator technology because it combines two well matched technologies. Ferroelectric liquid crystal modulating materials exhibit fast switching times with low operating voltages, while very large scale silicon integrated circuits offer high-frequency, low power operation, and versatile functionality.

This thesis describes the design and characterisation of the SBS256 – a general purpose  $256 \times 256$  pixel ferroelectric liquid crystal over silicon spatial light modulator that incorporates a static-RAM latch and an exclusive-OR gate at each pixel. The static-RAM latch provides robust data storage under high read-beam intensities, while the exclusive-OR gate permits the liquid crystal layer to be fully and efficiently charge balanced.

The SBS256 spatial light modulator operates in a binary mode. However, many applications, including helmet-mounted displays and optoelectronic implementations of artificial neural networks, require devices with some level of grey-scale capability. The 2 kHz frame rate of the device, permits temporal multiplexing to be used as a means of generating discrete grey-scale in real-time.

A second integrated circuit design is also presented. This prototype neuraldetector backplane consists of a  $4 \times 4$  array of optical-in, electronic-out processing units. These can sample the temporally multiplexed grey-scale generated by the SBS256. The neurons implement the post-synaptic summing and thresholding function, and can respond to both positive and negative activations – a requirement of many artificial neural network models.

# Declaration

I declare that this thesis has been completed by myself and that, except where indicated to the contrary, the research documented is entirely my own.

Wayne Burns

Dwayne C. Burns

# Acknowledgements

I would like to thank the following people for their invaluable assistance during the course of my PhD project:

- My supervisors, Ian Underwood and Alan Murray, for their continuous support and guidance, and also for reading and checking this thesis.

- David Vass, leader of the Applied Optics Group, for his ideas and support throughout the project.

- The members of the Integrated Systems Group in the Electrical Engineering Department, and the Applied Optics Group in the Physics Department for their help and advice, especially Gerry Allen, James Gourlay, Drew Holmes, Will Hossack, Andy Myles, Tony O'Hara, Martin Reekie, Alec Ruthven, Mike Snook, and Robin Woodburn.

- The Department of Education Northern Ireland for providing financial support.

- Finally, thanks to Gail for all her help and encouragement throughout the project.

# **Table of Contents**

| 1. | Intr | oducti   | on                                                                                                | 1        |

|----|------|----------|---------------------------------------------------------------------------------------------------|----------|

|    | 1.1  | Backgr   | round                                                                                             | 1        |

|    | 1.2  | Object   | ives                                                                                              | <b>2</b> |

|    | 1.3  | Thesis   | outline $\ldots$ | 3        |

| 2. | Spa  | tial lig | ht modulators - an overview                                                                       | 5        |

|    | 2.1  | Introdu  | uction                                                                                            | 5        |

|    | 2.2  | Major    | SLM technologies                                                                                  | 6        |

|    |      | 2.2.1    | Digital micromirror devices                                                                       | 6        |

|    |      | 2.2.2    | Si-PLZT devices                                                                                   | 8        |

|    |      | 2.2.3    | Self electrooptic effect devices                                                                  | 10       |

|    | 2.3  | Liquid   | crystal devices                                                                                   | 12       |

|    |      | 2.3.1    | Smectic phase - the surface stabilised effect                                                     | 13       |

|    |      | 2.3.2    | Other FLC modes                                                                                   | 18       |

|    |      | 2.3.3    | Addressing schemes                                                                                | 19       |

|    | 2.4  | Ferroel  | lectric liquid crystal over silicon                                                               | 21       |

|    |      | 2.4.1    | DRAM-type devices                                                                                 | 23       |

|    |      | 2.4.2    | SRAM-type devices                                                                                 | 29       |

|    |      | 2.4.3    | Smart pixel devices                                                                               | 32       |

|    | 2.5  | Summa    | ary                                                                                               | 35       |

| 3. | FLC  | COS SL   | LM applications                                                                                   | 37       |

|    | 3.1  | Why u    | se FLCOS SLMs ?                                                                                   | 37       |

|    | 3.2  | Binary   | mode applications                                                                                 | 38       |

|    |      | 3.2.1    | Interconnect/crossbar switching                                                                   | 39       |

|    |      | 3.2.2    | Coherent optical processing                                                                       | 41       |

|    |      | 3.2.3    | Optical computing and distributed processing                                                      | 44       |

|    | 3.3  |          | cale generation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$           | 45       |

|    | 0.0  | 3.3.1    | Analogue charge metering techniques                                                               | 45       |

|    |      | 0.0.1    |                                                                                                   |          |

| Ta | ble of | Conter   | nts                                                                                                                                   | iv |

|----|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------|----|

|    |        | 3.3.2    | Multiplexing techniques                                                                                                               | 46 |

|    | 3.4    | Artifici | ial neural networks                                                                                                                   | 50 |

|    |        | 3.4.1    | The multi-layer perceptron                                                                                                            | 50 |

|    |        | 3.4.2    | Electronic implementations                                                                                                            | 52 |

|    |        | 3.4.3    | Optoelectronic implementations                                                                                                        | 52 |

|    | 3.5    | Summa    | ary                                                                                                                                   | 55 |

| 4. | The    | SBS2     | 56 - backplane design issues                                                                                                          | 56 |

|    | 4.1    | Introdu  | uction                                                                                                                                | 56 |

|    | 4.2    | Process  | s selection                                                                                                                           | 57 |

|    |        | 4.2.1    | Which CMOS process?                                                                                                                   | 57 |

|    |        | 4.2.2    | Process variation                                                                                                                     | 59 |

|    | 4.3    | Transie  | ent current spikes                                                                                                                    | 60 |

|    |        | 4.3.1    | The mechanism: switching an inverter                                                                                                  | 60 |

|    |        | 4.3.2    | Power supply noise                                                                                                                    | 62 |

|    |        | 4.3.3    | Latch-up                                                                                                                              | 62 |

|    |        | 4.3.4    | Electromigration                                                                                                                      | 62 |

|    | 4.4    | Pixel c  | circuit                                                                                                                               | 63 |

|    |        | 4.4.1    | SRAM latch                                                                                                                            | 63 |

|    |        | 4.4.2    | XOR gate                                                                                                                              | 65 |

|    |        | 4.4.3    | Pixel drive scheme                                                                                                                    | 66 |

|    |        | 4.4.4    | Pixel layout                                                                                                                          | 69 |

|    | 4.5    | Backpl   | $lane architecture \dots \dots$ | 71 |

|    |        | 4.5.1    | Data shift registers                                                                                                                  | 73 |

|    |        | 4.5.2    | Auxiliary 256-bit register-buffer                                                                                                     | 75 |

|    |        | 4.5.3    | 8-to-256 line column decoder                                                                                                          | 75 |

|    |        | 4.5.4    | Busline distribution                                                                                                                  | 76 |

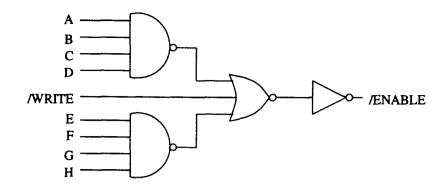

|    |        | 4.5.5    | Control signal busline test circuits                                                                                                  | 78 |

|    | 4.6    | SLM d    | lrive scheme                                                                                                                          | 78 |

|    | 4.7    | Power    | dissipation                                                                                                                           | 80 |

|    |        | 4.7.1    | Pattern independent power dissipation                                                                                                 | 81 |

|    |        | 4.7.2    | Pattern dependent power dissipation                                                                                                   | 82 |

|    |        | 4.7.3    | Total power dissipation                                                                                                               | 84 |

|    | 4.8    | Summ     | ary                                                                                                                                   | 86 |

androng **(1997)** to the solution

| Table | of | Contents |

|-------|----|----------|

|-------|----|----------|

| 5. | The | SBS2    | 56 - testing and characterisation                       | 87  |

|----|-----|---------|---------------------------------------------------------|-----|

|    | 5.1 | SLM o   | controller interfaces                                   | 87  |

|    |     | 5.1.1   | SimpleInt interface                                     | 87  |

|    |     | 5.1.2   | FastInt interface                                       | 88  |

|    | 5.2 | Backp   | lane electrical testing                                 | 90  |

|    |     | 5.2.1   | Preliminary testing                                     | 90  |

|    |     | 5.2.2   | Current spike measurements                              | 91  |

|    |     | 5.2.3   | Data shift register operating frequency                 | 92  |

|    |     | 5.2.4   | Backplane yield test structures                         | 95  |

|    |     | 5.2.5   | Backplane yield                                         | 98  |

|    | 5.3 | Post-p  | rocessing planarisation and SLM assembly                | 102 |

|    |     | 5.3.1   | Wafer planarisation                                     | 102 |

|    |     | 5.3.2   | SLM assembly                                            |     |

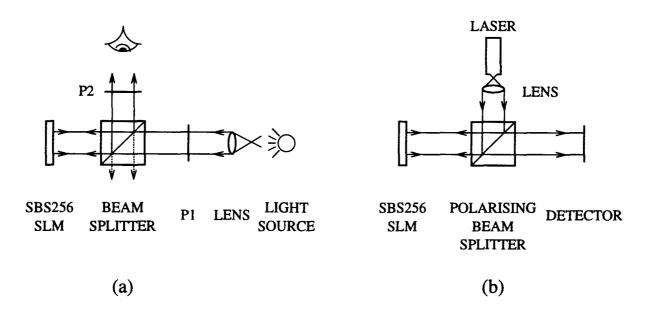

|    | 5.4 | Viewin  | ng systems                                              |     |

|    |     | 5.4.1   | Using a non-polarising beam-splitter and two polarisers | 106 |

|    |     | 5.4.2   | Using a polarising beam-splitter                        | 107 |

|    | 5.5 | Optica  | l characterisation                                      | 108 |

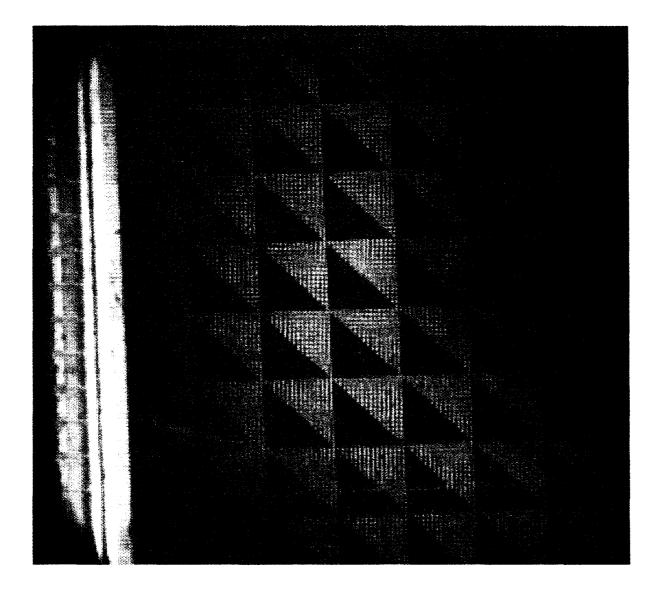

|    |     | 5.5.1   | Data storage                                            | 108 |

|    |     | 5.5.2   | Planarisation                                           | 110 |

|    |     | 5.5.3   | FLC switching time                                      | 110 |

|    |     | 5.5.4   | Contrast ratio                                          | 112 |

|    |     | 5.5.5   | Uniformity                                              | 113 |

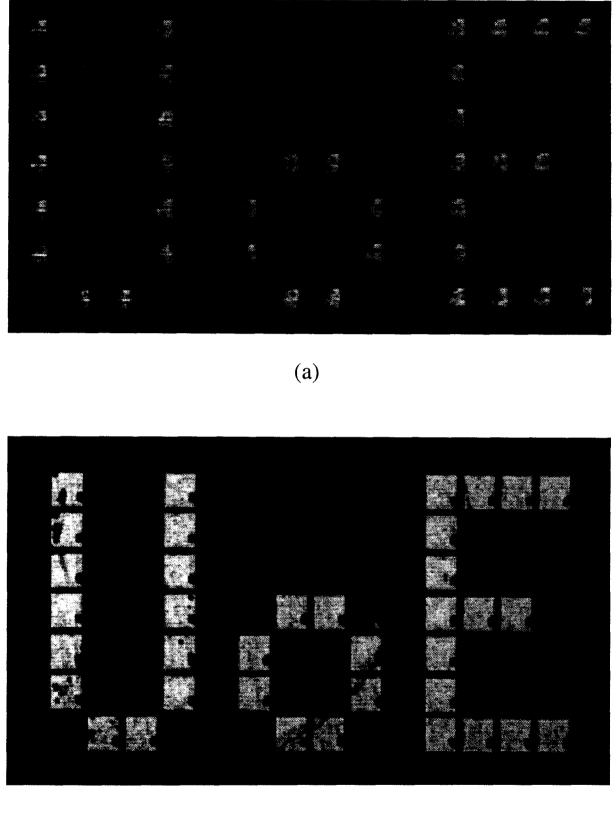

|    |     | 5.5.6   | Multiplexed grey-scale                                  | 114 |

|    | 5.6 | Summ    | ary                                                     | 115 |

| 6. | OAN | IN - a  | prototype neural-detector backplane                     | 120 |

|    | 6.1 |         | action                                                  |     |

|    | 6.2 | -       | requirements                                            |     |

|    |     | 6.2.1   | An optoelectronic hidden layer ANN                      |     |

|    |     | 6.2.2   | Using temporally multiplexed grey-scale                 |     |

|    |     | 6.2.3   | Simplified system                                       |     |

|    | 6.3 | Activit | y Storage                                               |     |

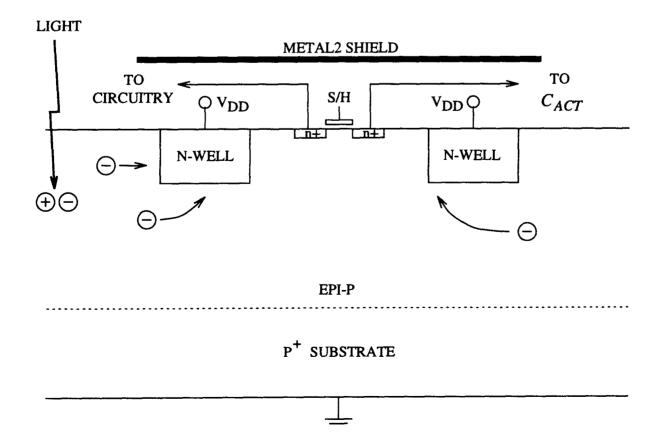

|    |     | 6.3.1   | Improving charge storage – the n-well ring              |     |

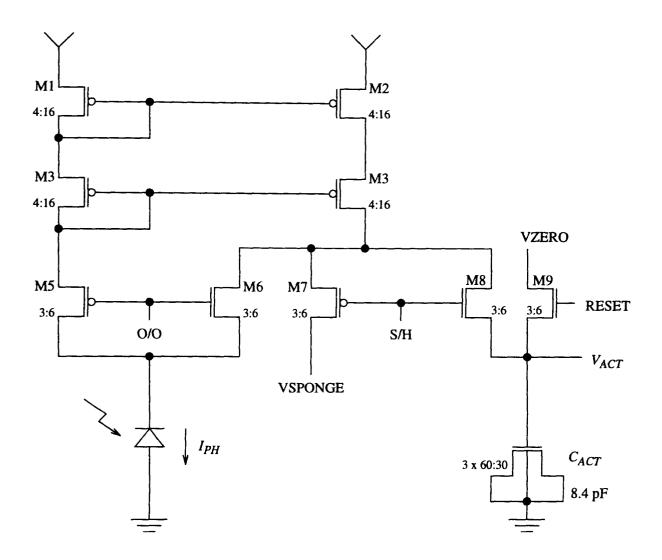

|    | 6.4 | Neuron  | 1 circuit                                               |     |

|    |     | 6.4.1   | Operation                                               |     |

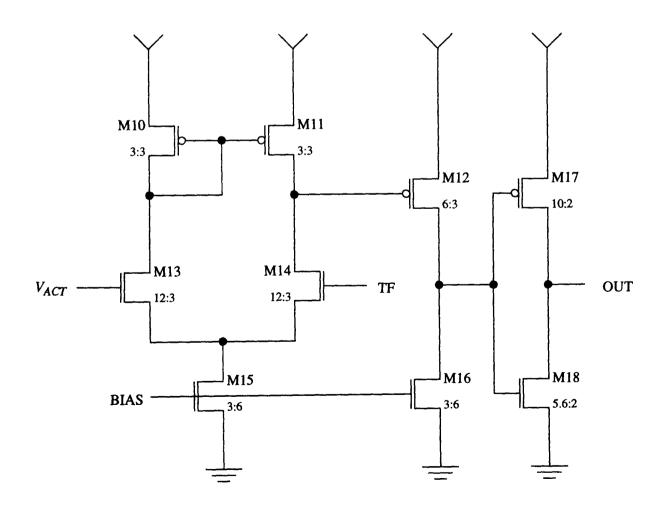

|    |     | 6.4.2   | Back-end circuit details                                | 134 |

|    |     | 6.4.3   | Front-end circuit details                               | 138 |

v

المراجع من الرابع من الرابع من . - محمد الرابع من المراجع من محمد المراجع من المراجع من المراجع المراجع من المراجع م من المراجع م

| Table of Contents | Table | of | Contents |

|-------------------|-------|----|----------|

|-------------------|-------|----|----------|

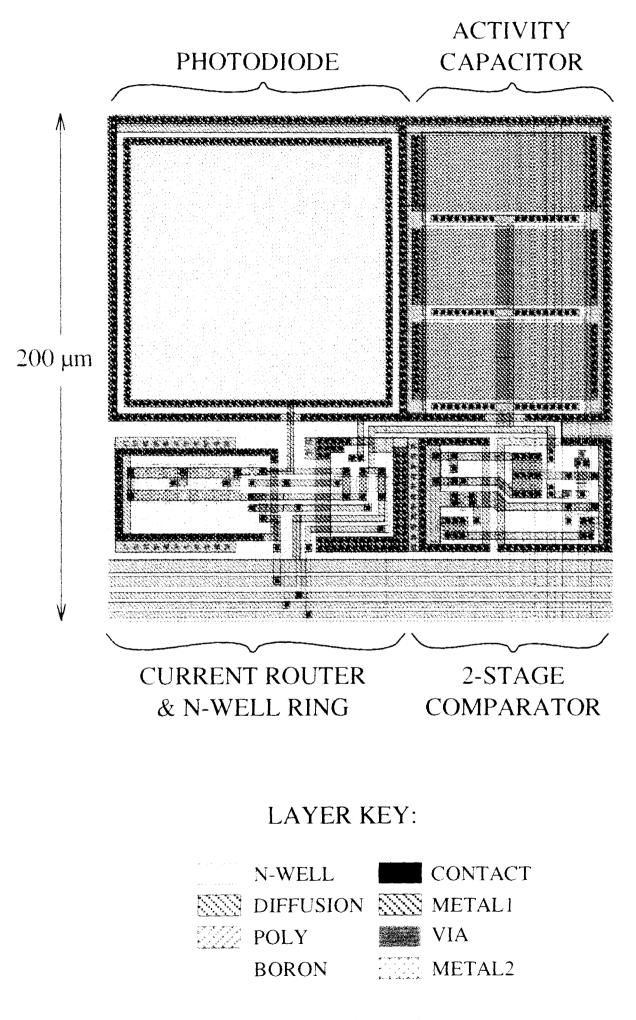

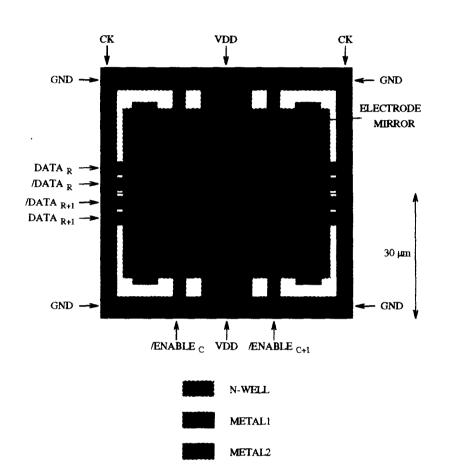

|    |         | 6.4.4   | Neuron layout                                                                                       | 139        |

|----|---------|---------|-----------------------------------------------------------------------------------------------------|------------|

|    | 6.5     | OANN    | backplane                                                                                           | 139        |

|    | 6.6     | OannI   | nt interface                                                                                        | 139        |

|    | 6.7     | Testing | g and characterisation                                                                              | 143        |

|    |         | 6.7.1   | Pulse width output versus $V_{ACT}$                                                                 | 144        |

|    |         | 6.7.2   | Sample and hold characteristics                                                                     | 144        |

|    |         | 6.7.3   | Effects of process variation                                                                        | 145        |

|    |         | 6.7.4   | Cascading the SBS256 and OANN                                                                       | 147        |

|    |         | 6.7.5   | Neuron characterisation                                                                             | 149        |

|    | 6.8     | Summ    | ary                                                                                                 | 151        |

| _  | <b></b> | •       | , , , <b>,</b>                                                                                      | 120        |

| 7. |         |         | and conclusions<br>6 SLM                                                                            | <b>152</b> |

|    | 7.1     | 7.1.1   | Backplane evaluation                                                                                |            |

|    |         | 7.1.2   | Optical evaluation                                                                                  |            |

|    |         | 7.1.3   | Improvements                                                                                        |            |

|    |         | 7.1.4   | A more compact SRAM-type design                                                                     |            |

|    |         | 7.1.5   | SRAM versus DRAM                                                                                    |            |

|    | 7.2     |         | I neural-detector backplane                                                                         |            |

|    | 1.2     | 7.2.1   | OANN evaluation                                                                                     |            |

|    |         | 7.2.2   | Improvements and future work                                                                        |            |

|    | 7.3     | Conclu  | $1$ sions $\ldots$ |            |

| Bi | bliog   | raphy   |                                                                                                     | 163        |

| А. | Pul     | se widt | th modulation test pixel                                                                            | 172        |

|    | A.1     | Circui  | t principles and operation                                                                          | 172        |

|    |         |         | ·S                                                                                                  |            |

|    | A.3     | Future  | e work                                                                                              | 175        |

| B. | SBS     | 5256 pi | ress cuttings                                                                                       | 176        |

| С. | Aut     | hor's j | publications                                                                                        | 181        |

# List of Figures

| 2 - 1  | Cross-section of a torsion-beam deformable mirror pixel             | 7  |

|--------|---------------------------------------------------------------------|----|

| 2 - 2  | Cross section of a unit cell of a Si-PLZT SLM                       | 9  |

| 2 - 3  | Cross section of a unit cell of a GaAs FET-SEED                     | 11 |

| 2 - 4  | Ferroelectric liquid crystal operation.                             | 16 |

| 2 - 5  | Cross-section of a FLCOS SLM                                        | 22 |

| 2-6    | Schematic of the one-transistor DRAM-type pixel                     | 25 |

| 2 - 7  | Equivalent circuit of the one transistor DRAM-type pixel            | 26 |

| 2-8    | Schematic of the three-transistor DRAM-type pixel                   | 28 |

| 2–9    | Schematic of the four-transistor DRAM-type pixel                    | 29 |

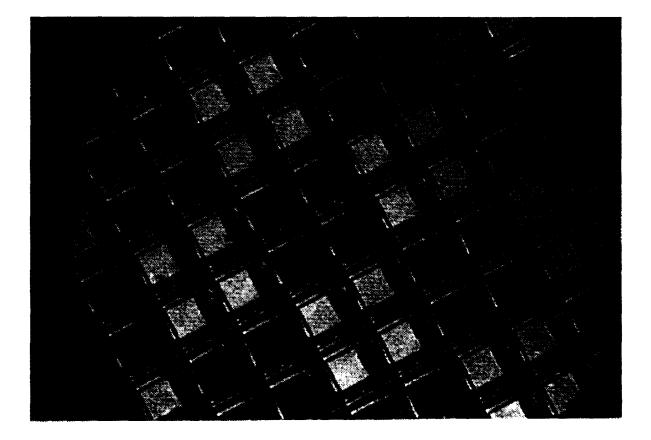

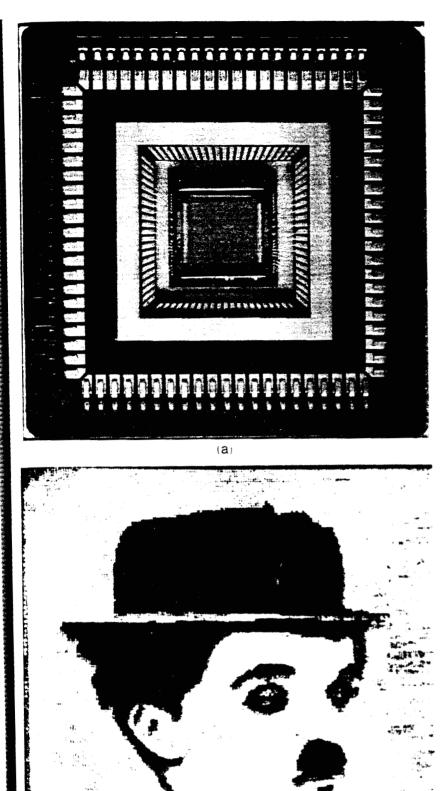

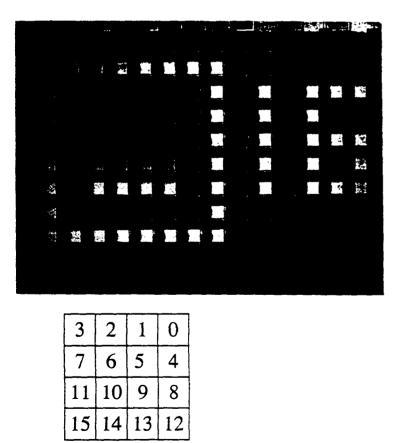

| 2 - 10 | Test pattern on the 16 $\times$ 16 SRAM-XNOR device                 | 30 |

| 2–11   | Schematic of the SRAM-XNOR pixel used in the 16 $\times$ 16 device. | 31 |

| 2 - 12 | Nearest neighbour designations for the Isophote pixel               | 33 |

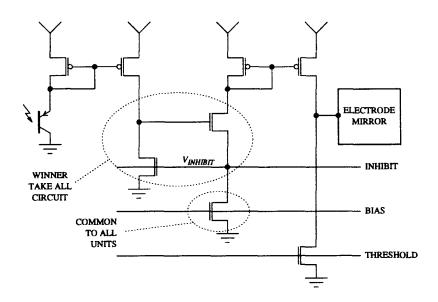

| 2–13   | Schematic of the winner-take-all pixel                              | 34 |

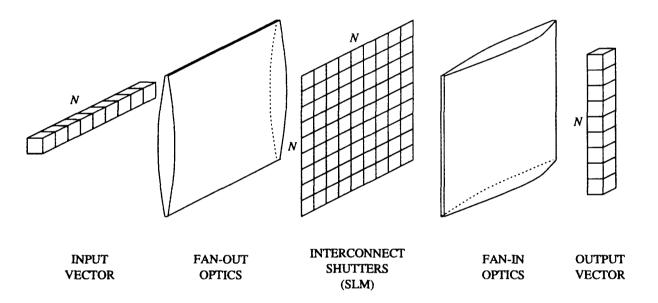

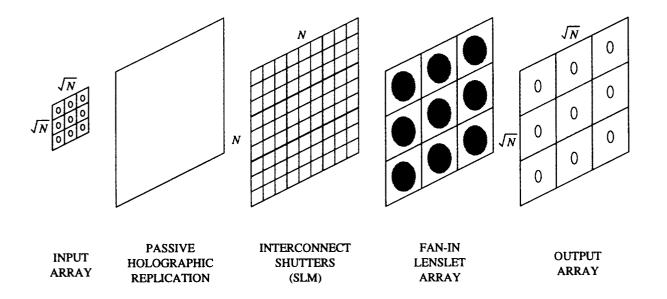

| 3 - 1  | The vector-matrix multiplier crossbar switch architecture           | 39 |

| 3 - 2  | The matrix-matrix crossbar architecture                             | 40 |

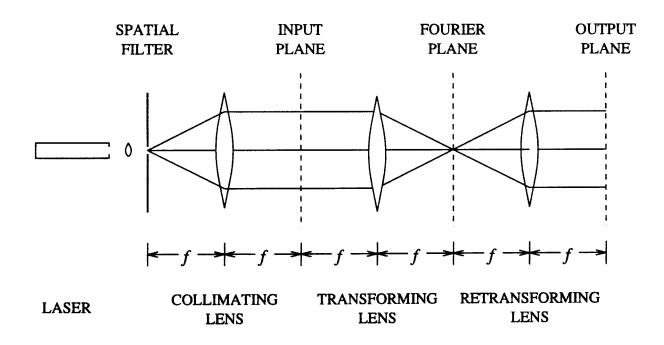

| 3–3    | The 6-f coherent optical processor.                                 | 42 |

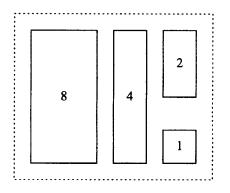

| 3–4    | Binary weighted subpixel division for spatial multiplexing          | 47 |

| 3 - 5  | Linear encoding algorithm to generate four grey levels              | 48 |

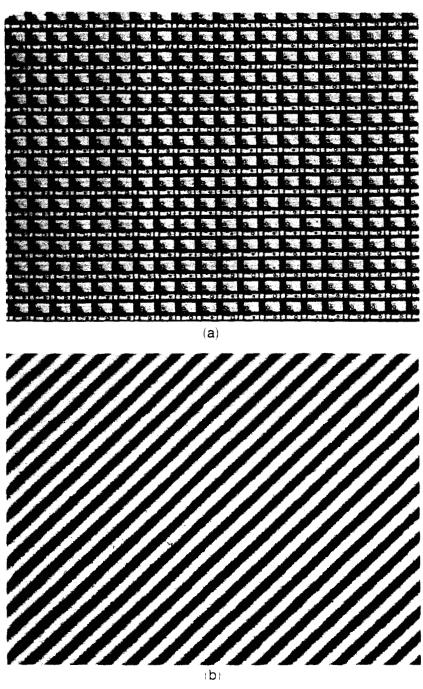

| 3–6    | Six linearly encoded grey levels on the 16 $\times$ 16 device       | 49 |

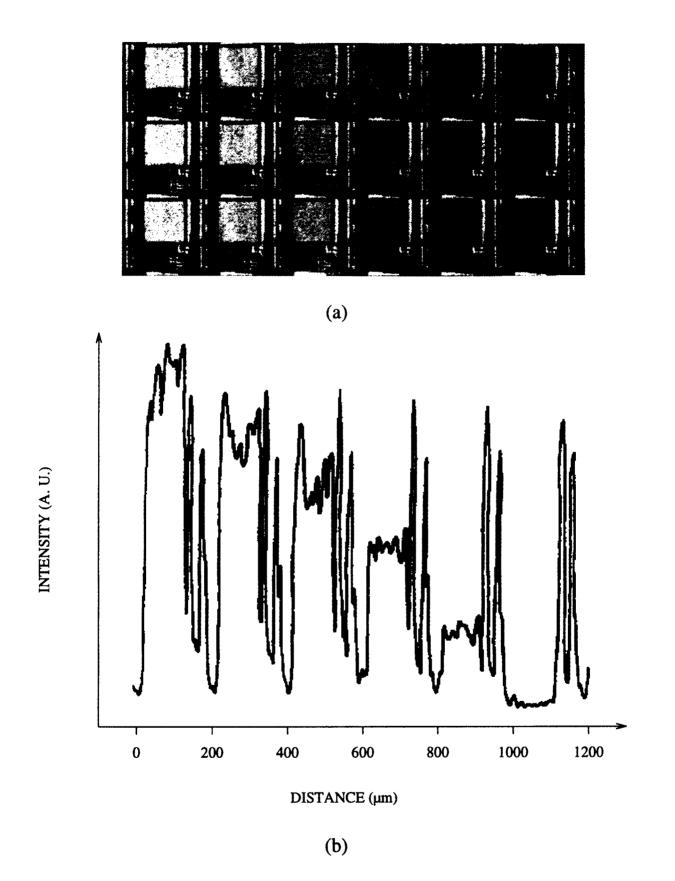

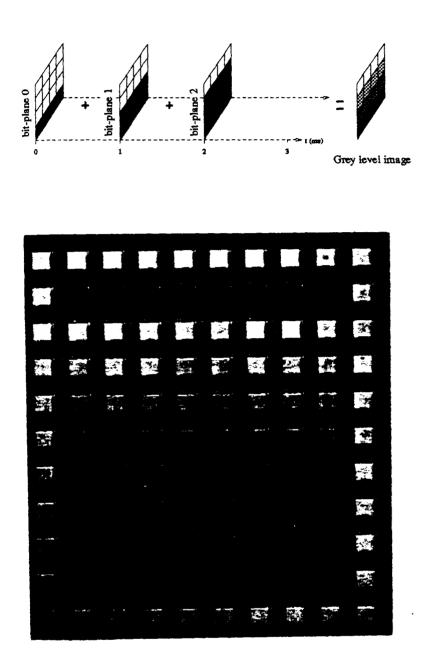

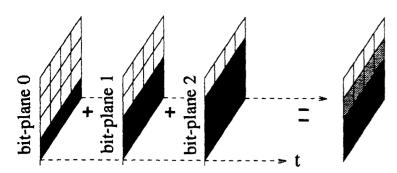

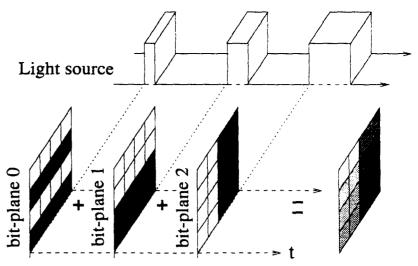

| 3–7    | Binary encoded bit-planes to generate eight grey levels             | 50 |

| 3–8    | The multi-layer perceptron.                                         | 51 |

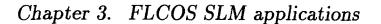

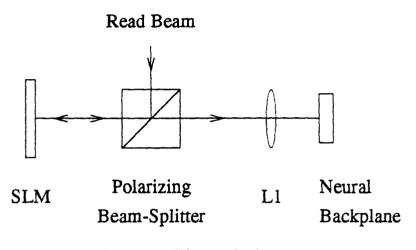

| 3–9    | A polarisation-based single layer perceptron system                 | 54 |

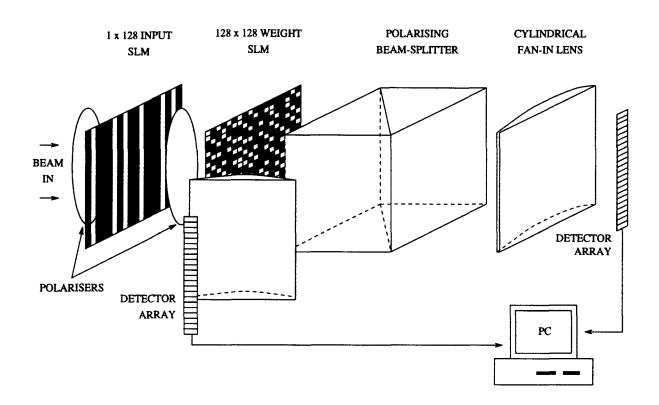

| 4–1    | Basic CMOS inverter and transient current behaviour.                | 61 |

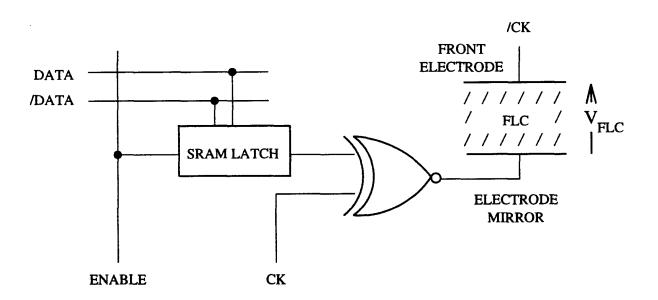

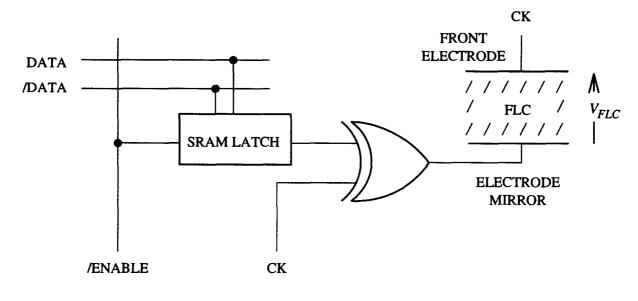

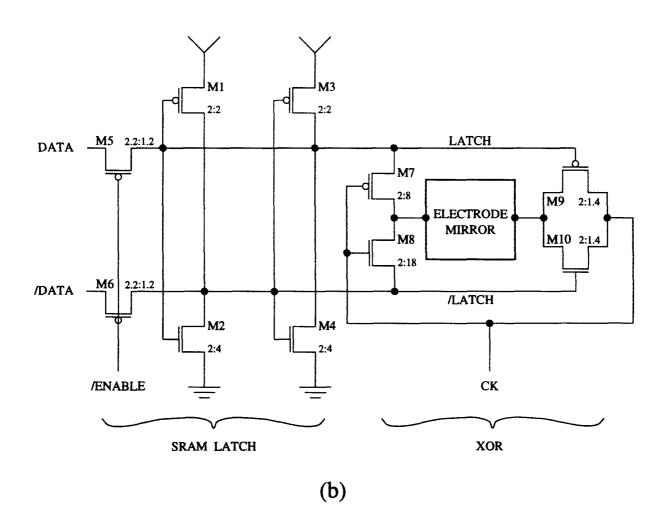

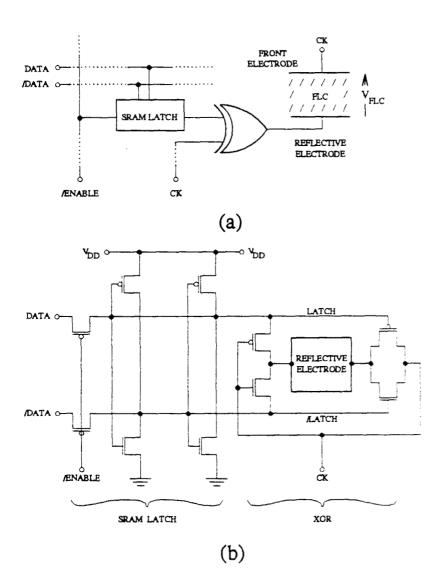

| 4–2    | The SRAM-XOR pixel                                                  | 64 |

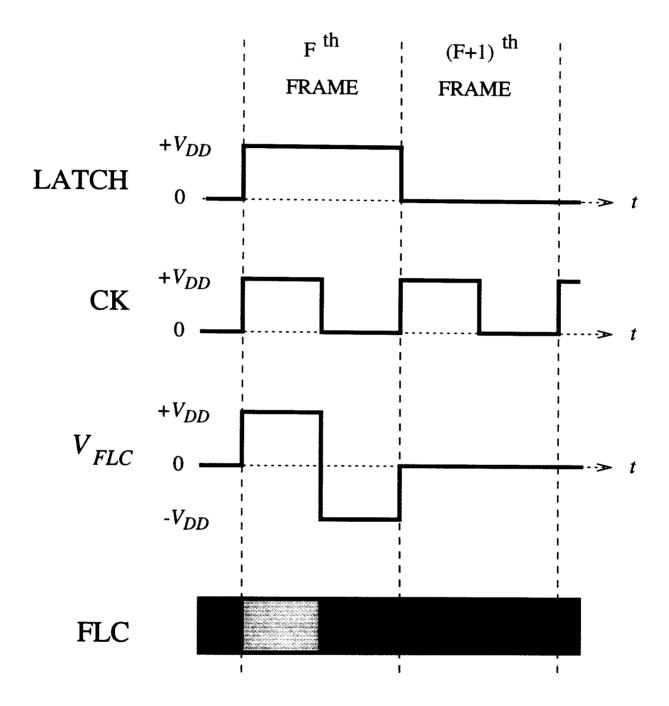

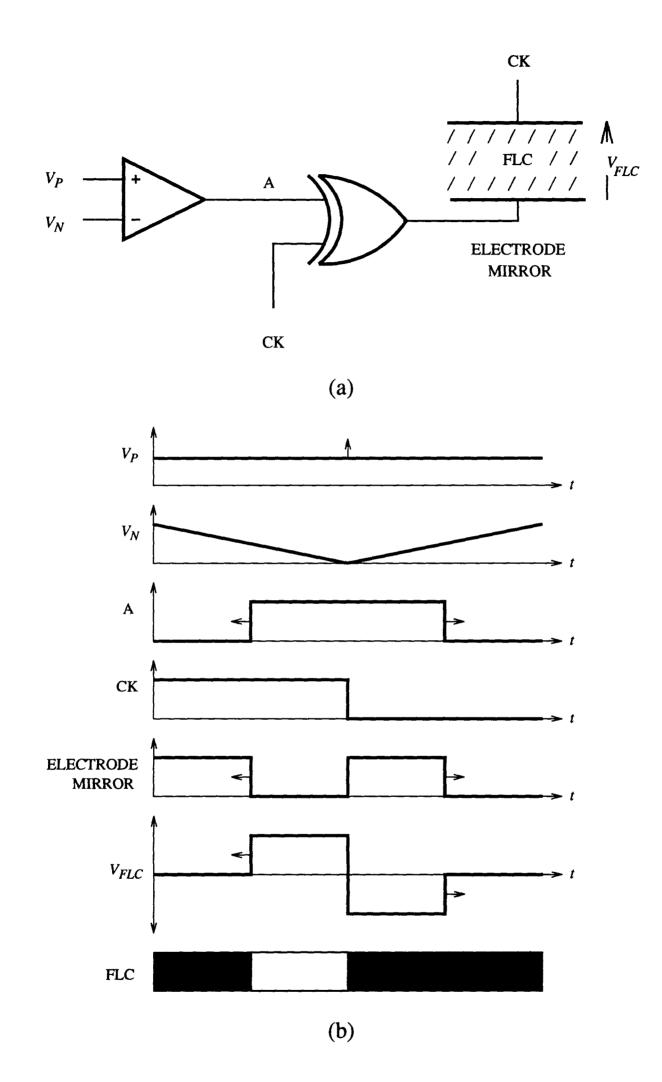

| 4-3    | Pixel drive scheme                                                  | 68 |

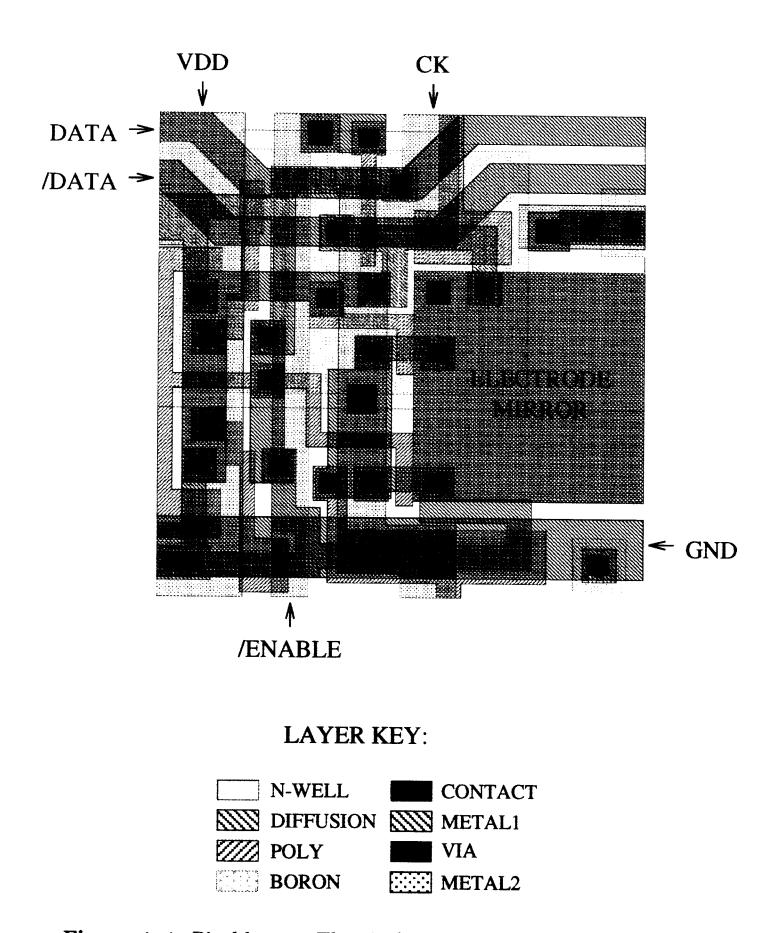

| 4-4    | Pixel layout                                                        | 70 |

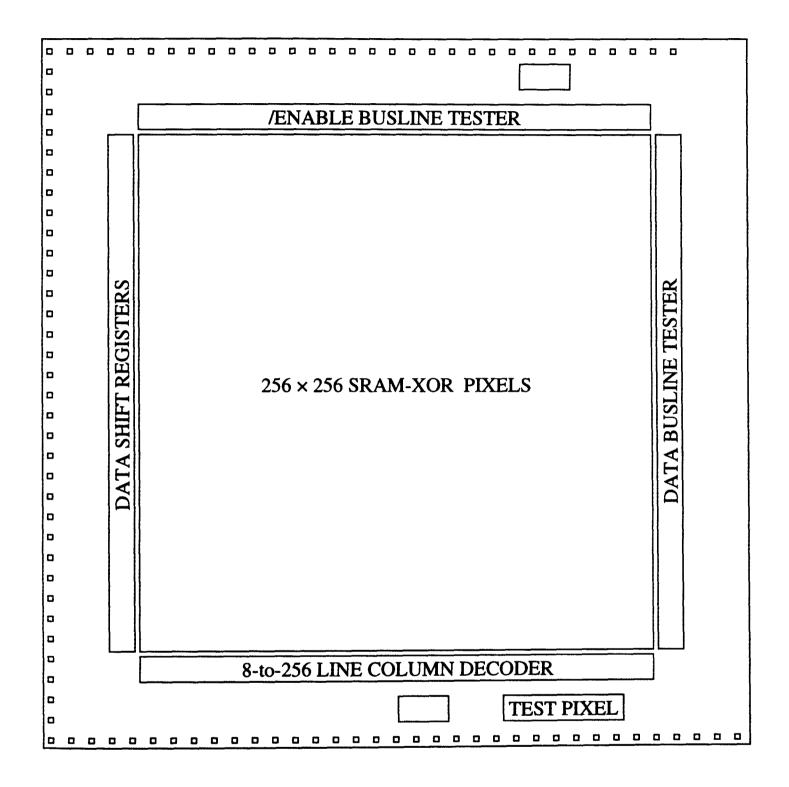

| 4–5    | Block diagram of the main functional units on the backplane         | 72 |

| 46     | Schematic of a single data shift register cell                      | 73 |

| List of Fig | gures |

|-------------|-------|

|-------------|-------|

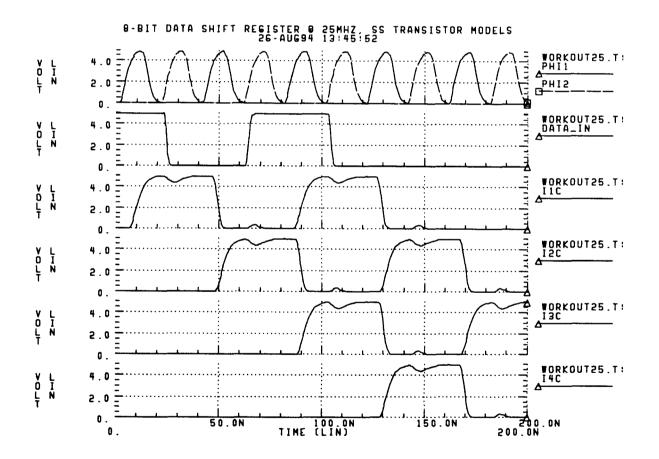

| 4–7    | HSPICE simulation of the data shift register operating at 25 MHz. | 74  |

|--------|-------------------------------------------------------------------|-----|

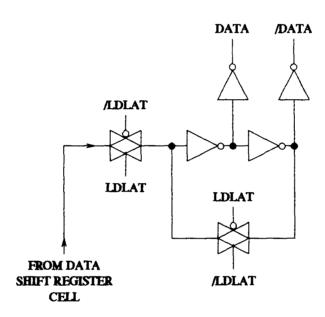

| 4-8    | Schematic of a single latch-buffer cell                           | 75  |

| 4–9    | Schematic of a single column decoder cell                         | 76  |

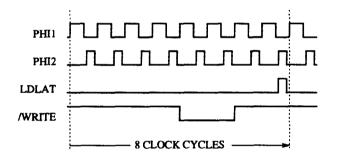

| 4–10   | Control signal timing sequence to load a single column            | 76  |

| 4–11   | Schematic of the split global clock signal                        | 77  |

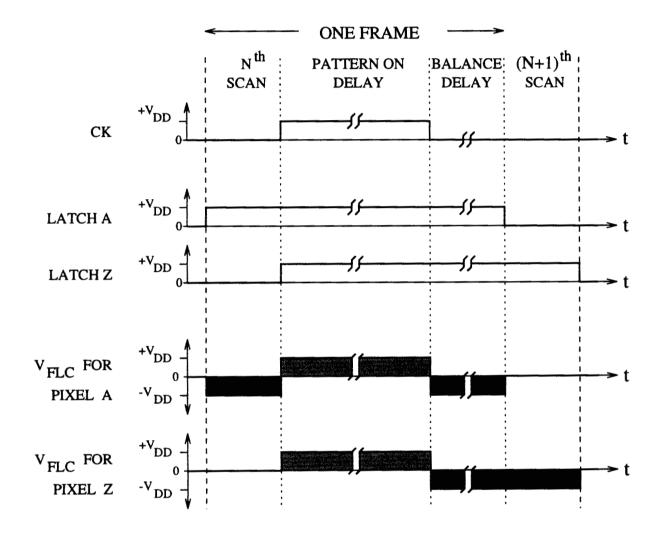

| 4-12   | Charge balanced SLM drive scheme                                  | 79  |

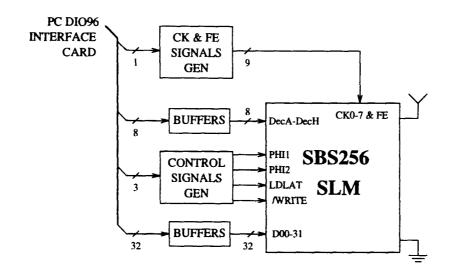

| 5–1    | Block diagram of the SimpleInt interface                          | 88  |

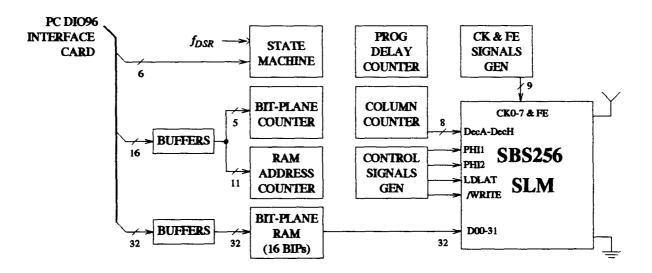

| 5 - 2  | Block diagram of the FastInt interface.                           | 89  |

| 5 - 3  | Experimental set-up to investigate transient current spikes       | 91  |

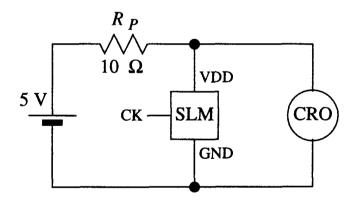

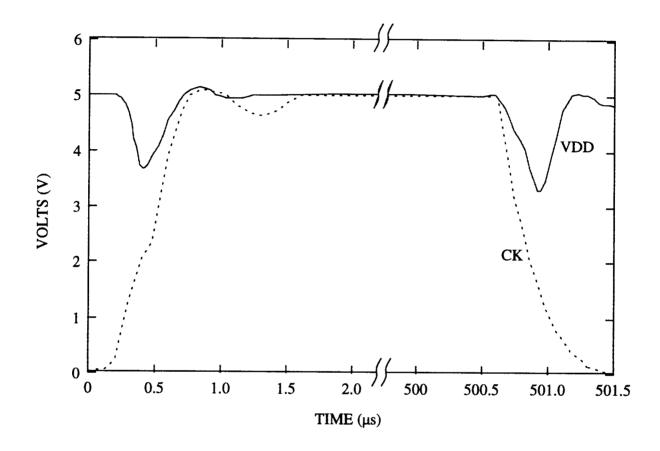

| 5 - 4  | Effect of the CK transient current spike on test resistor         | 93  |

| 5 - 5  | Oscilloscope trace of data shift register operating at 24 MHz     | 94  |

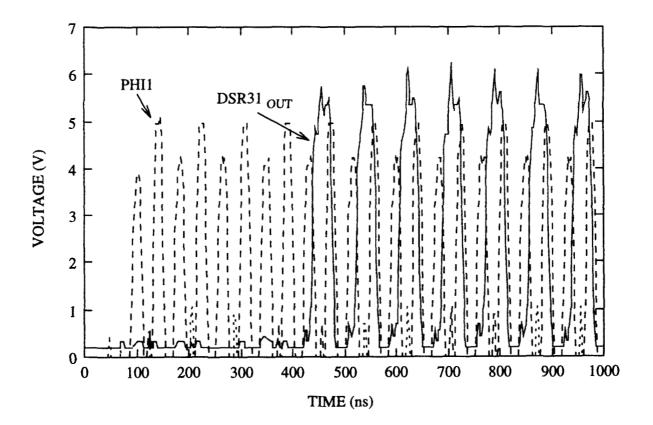

| 5–6    | Schematic of the DATA busline tester.                             | 96  |

| 5 - 7  | Oscilloscope traces from the busline tester circuits              | 97  |

| 5–8    | Probe test yield of wafer 1                                       | 101 |

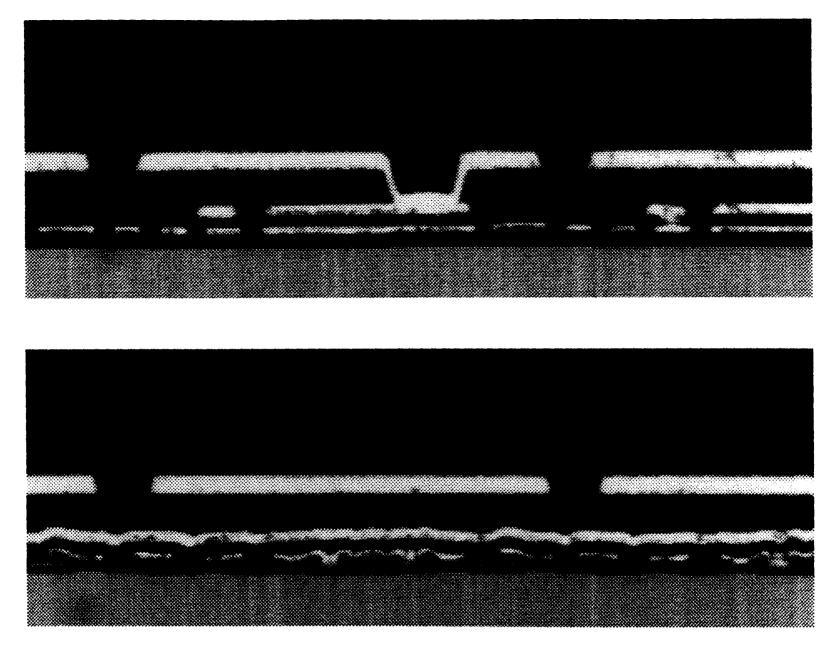

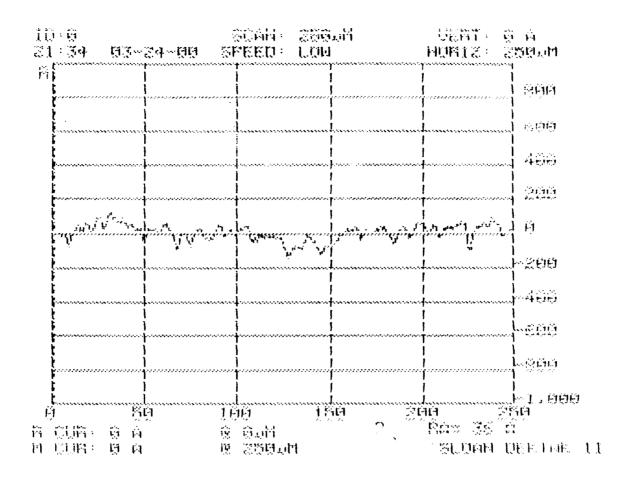

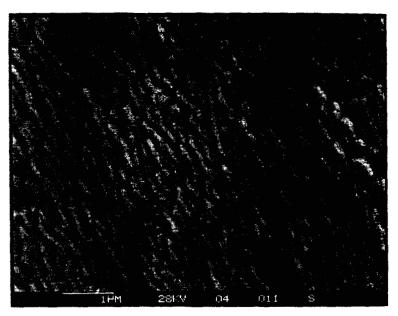

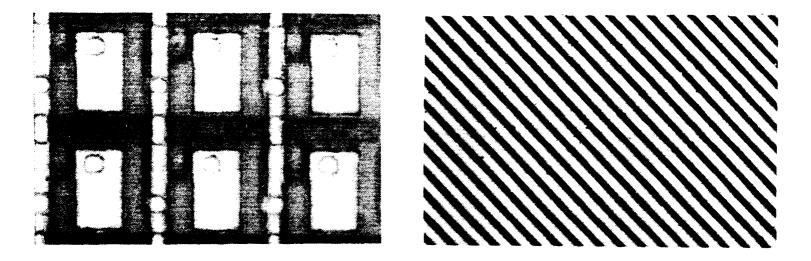

| 5–9    | Photomicrographs of unplanarised and planarised pixels            | 105 |

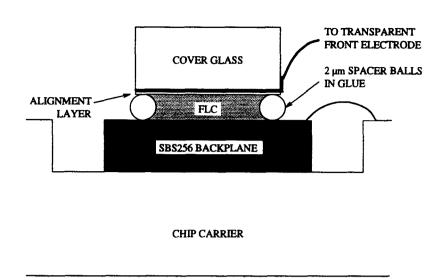

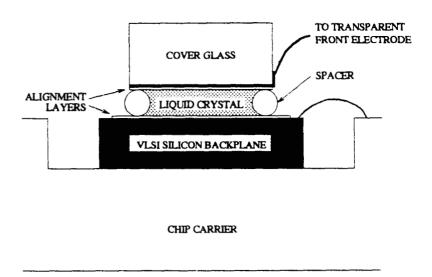

| 5–10   | Cross-section of the SBS256 SLM                                   | 106 |

| 5-11   | Two SLM viewing configurations.                                   | 107 |

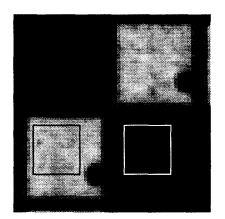

| 5-12   | Test pattern on a section of the SLM                              | 109 |

| 5-13   | A pattern with and without planarisation                          | 111 |

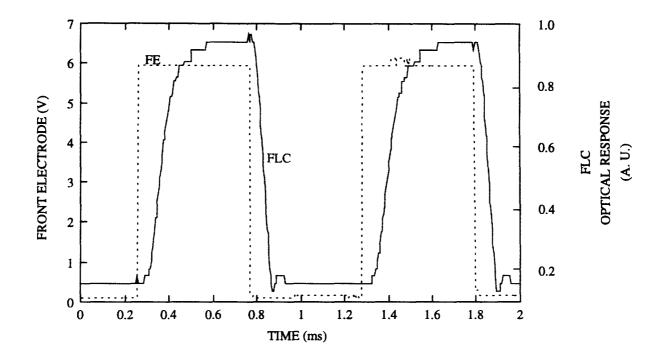

| 5–14   | Optical response of the FLC                                       | 112 |

| 5-15   | Estimating the pixel on/off contrast ratio.                       | 113 |

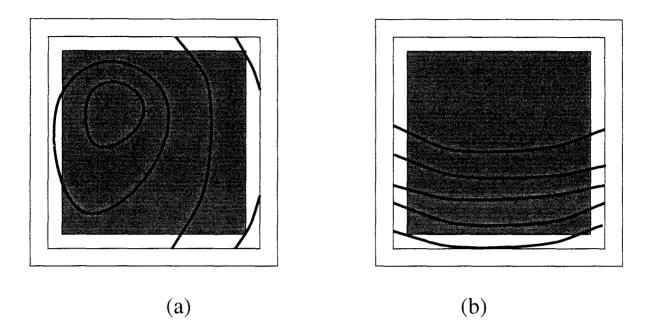

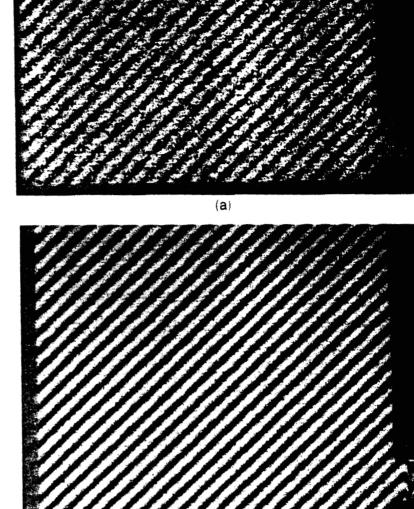

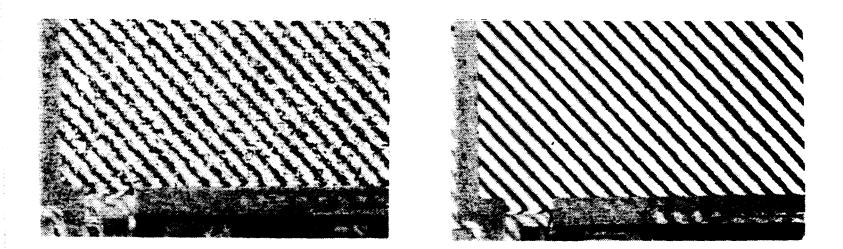

| 5 - 16 | Two typical fringe patterns present on fabricated SLMs            | 114 |

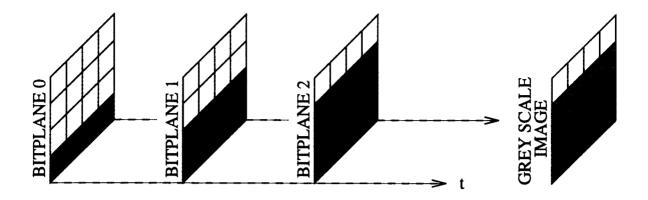

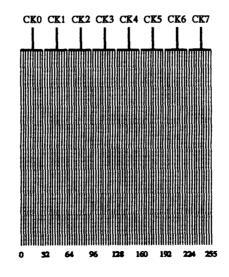

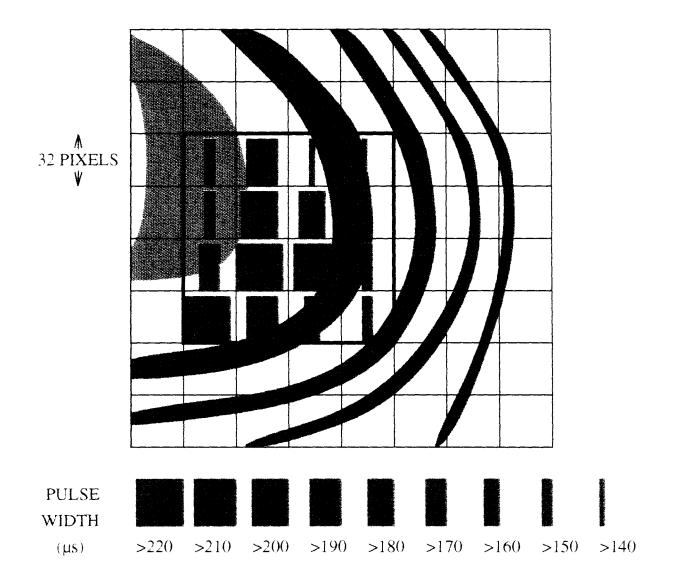

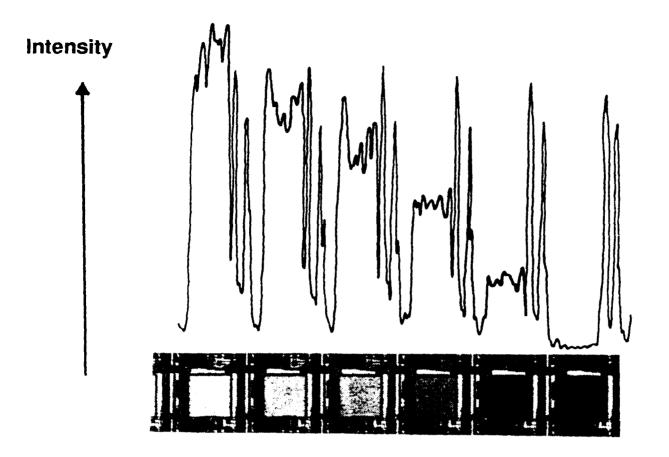

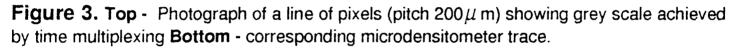

| 5 - 17 | Temporally multiplexed grey-scale on a planarised device          | 116 |

| 5 - 18 | 'Monalisa' test pattern on a section of the SLM                   | 117 |

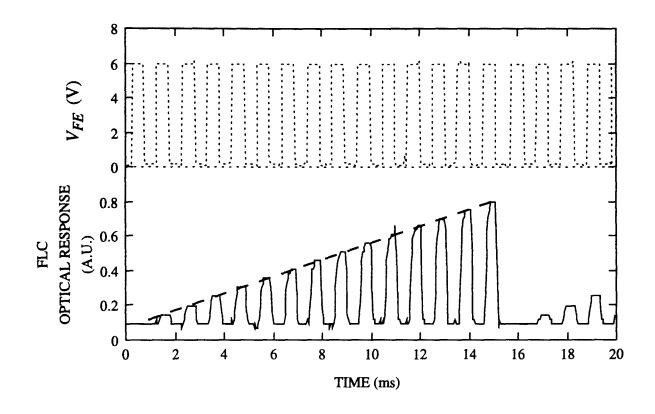

| 5–19   | Optical response of the FLC for a grey-scale test pattern         | 119 |

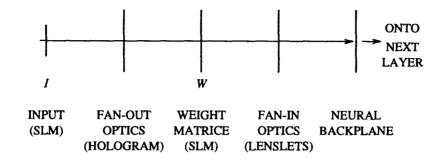

| 6-1    | Input-to-hidden layer section of an optoelectronic ANN            | 122 |

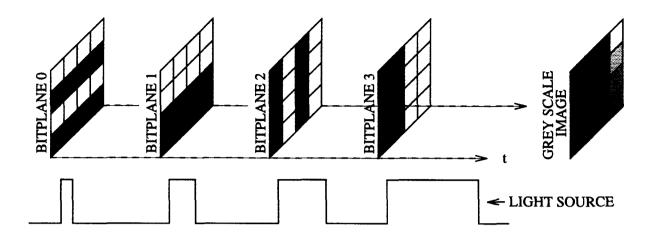

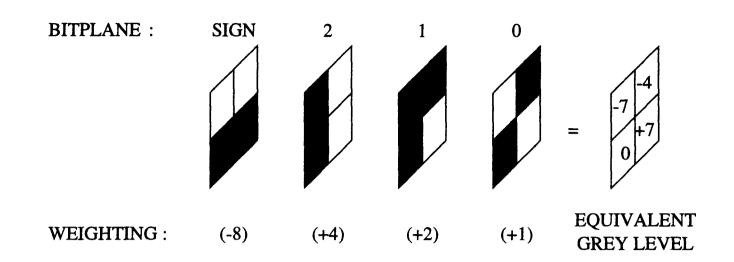

| 6-2    | Temporally multiplexed 2's complement grey-scale scheme           | 124 |

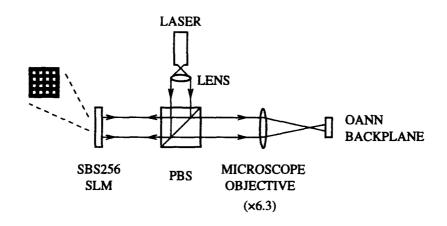

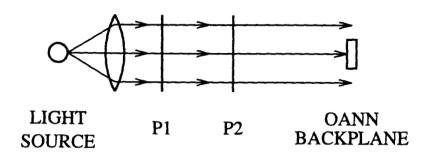

| 6-3    | A simplified optical system for backplane characterisation        | 126 |

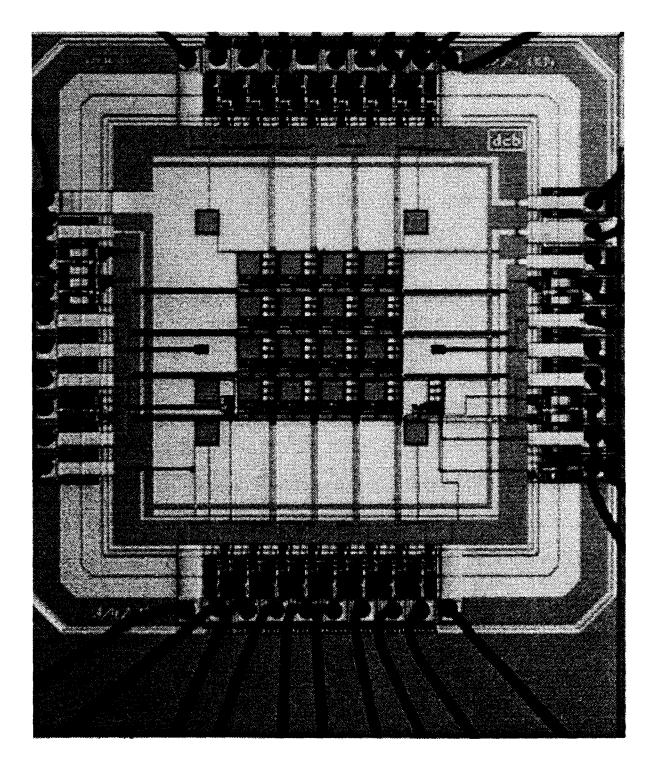

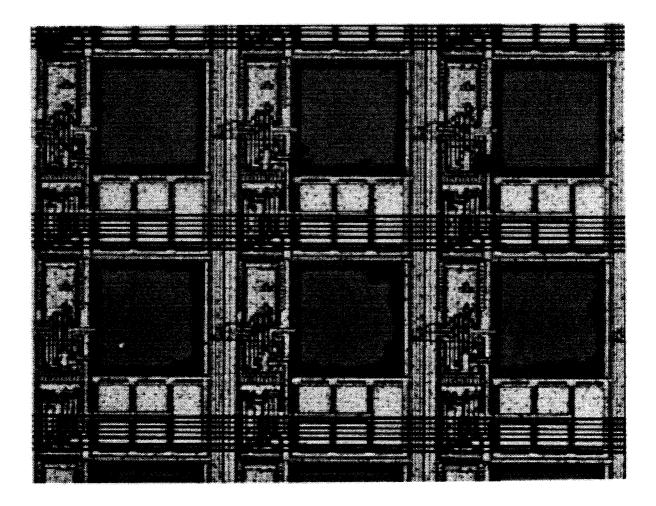

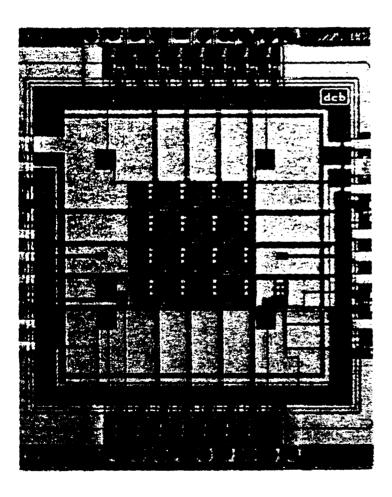

| 6-4    | Photomicrograph of the 4 $\times$ 4 neural-detector backplane     | 127 |

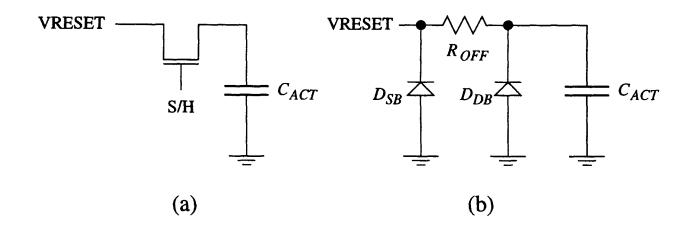

| 6-5    | Simple sample and hold circuit                                    | 128 |

| 6-6    | Charge storage n-well ring protection to reduce charge leakage    | 129 |

| 6–7    | Test circuit to measure charge leakage from $C_{ACT}$             | 130 |

| 6–8    | Charge leakage with and without n-well ring protection            | 131 |

| 6–9    | Schematic of a single neuron                                      | 131 |

viii

10

| LISE OF FIGURES | List | of | Figures |

|-----------------|------|----|---------|

|-----------------|------|----|---------|

| 6–10   | OANN control signals for the 2's complement drive scheme          | 133          |

|--------|-------------------------------------------------------------------|--------------|

| 6–11   | Transistor level diagram of the neuron back end                   | 134          |

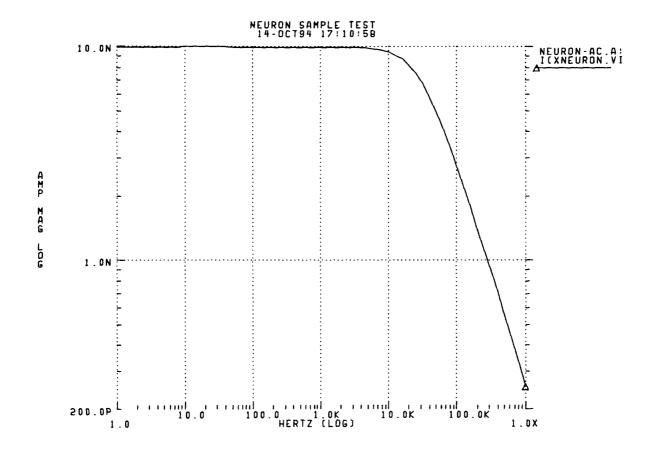

| 6–12   | HSPICE AC analysis simulation of neuron back-end                  | 137          |

| 6-13   | Transistor level diagram of the neuron front end                  | 1 <b>3</b> 8 |

| 6–14   | Layout of a single neuron.                                        | 140          |

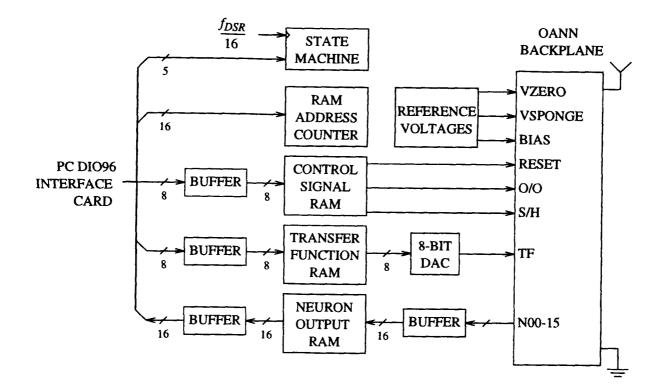

| 6 - 15 | Block diagram of the OANN interface.                              | 141          |

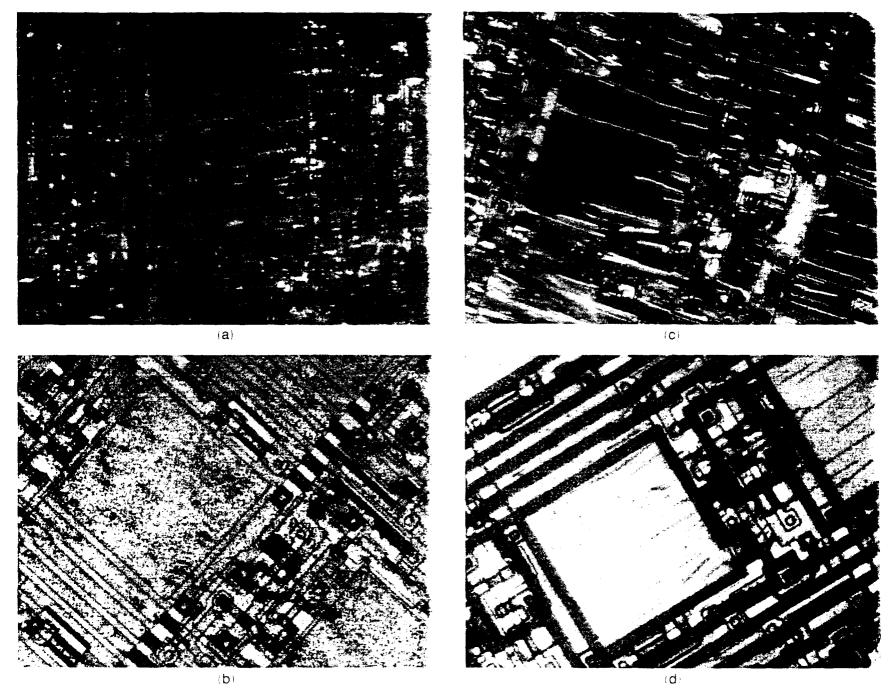

| 6-16   | Photomicrograph showing the residue on the photodiodes            | 143          |

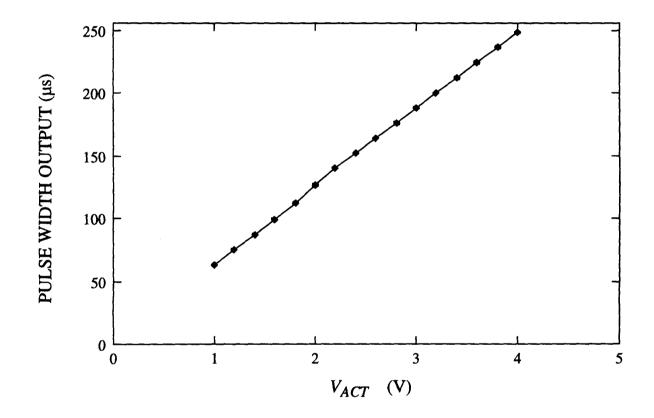

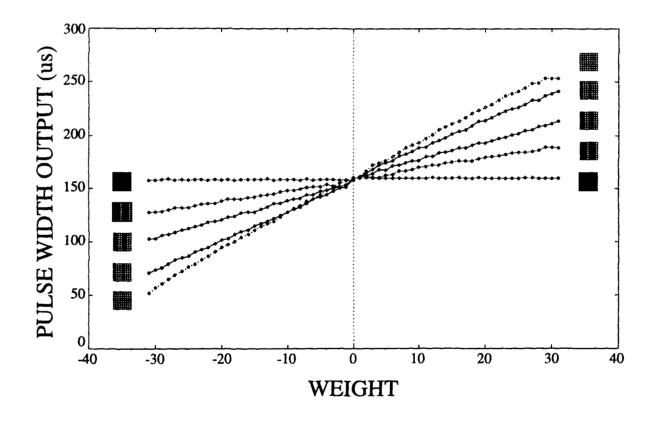

| 6-17   | Neuron pulse width output versus the activation voltage $V_{ACT}$ | 144          |

| 6–18   | Optical system to investigate the current-router functionality    | 145          |

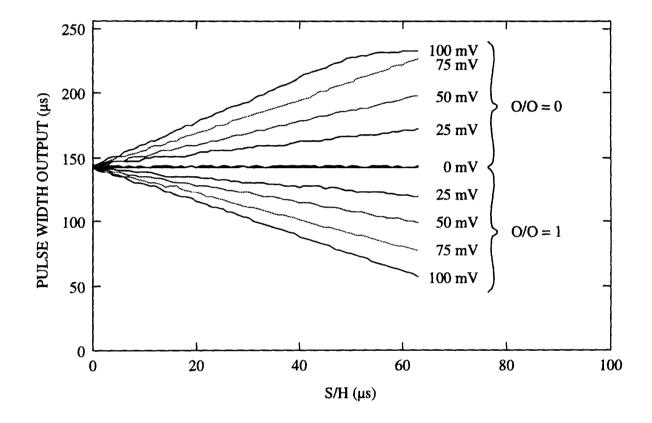

| 6-19   | Pulse width output versus S/H for several different intensities   | 146          |

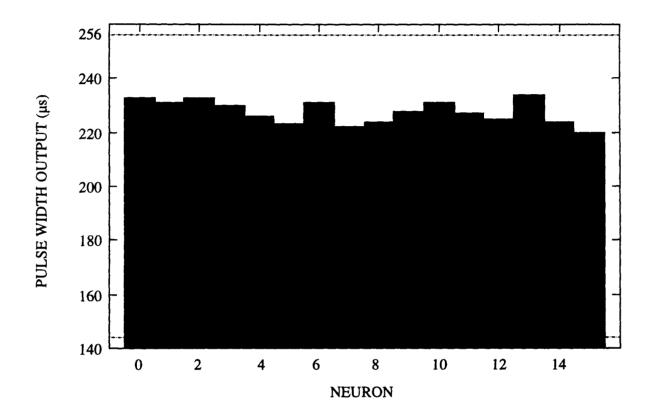

| 6-20   | Variation across the neuron array.                                | 147          |

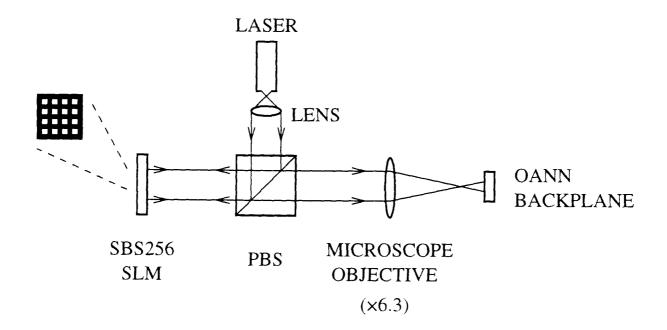

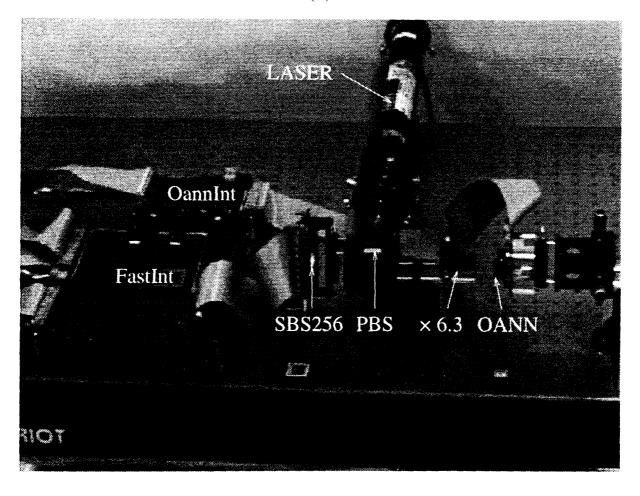

| 6-21   | The optical system and interfaces                                 | 148          |

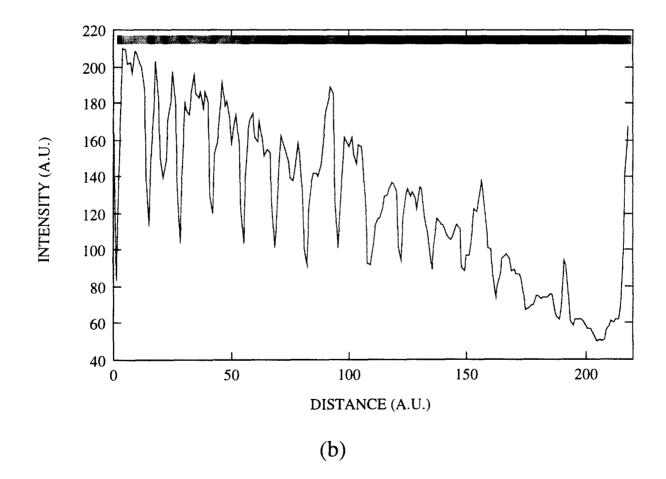

| 6-22   | Effects of SLM fringes on neuron outputs.                         | 149          |

| 6 - 23 | Neuron transfer characteristics using 6-bit weights               | 150          |

| 7–1    | The 'Quad' pixel layout.                                          | 156          |

| A-1    | Pulse width modulation test pixel.                                | 174          |

| A-2    | Optical response of the pixel.                                    | 175          |

| B-1    | "Applications abound for CRL's spatial light modulator"           | 177          |

| B-2    | "Breakthrough leads to fast image recognition".                   | 178          |

| B-3    | "Static memory may shrink imaging systems"                        | 179          |

| B-4    | "Compact SLM suits continuous illumination"                       | 180          |

ix

# List of Tables

| 2–1 | Examples from the literature of the development of one-transistor DRAM-type devices.                         | $2^{2}$ |

|-----|--------------------------------------------------------------------------------------------------------------|---------|

| 2-2 | Examples from the literature of the development of SRAM-type devices.                                        | 32      |

| 2-3 | Typical characteristics of the various SLM technologies described<br>in the chapter                          | 3       |

| 3–1 | Strengths of FLCOS SLM technology.                                                                           | 38      |

| 4–1 | A selection of CMOS processes from the AMS silicon foundry                                                   | 58      |

| 4–2 | Truth table and optical response of the FLC layer for the SRAM-<br>XOR pixel                                 | 60      |

| 4-3 | The effect of the various buslines on the overlying FLC                                                      | 7       |

| 44  | Estimated power dissipation in the pattern independent control signal buslines.                              | 82      |

| 4–5 | Estimated power dissipation for a selection of patterns                                                      | 8       |

| 5–1 | Comparison of the predicted and measured CK transition current spikes for a $64 \times 256$ block of pixels. | 92      |

| 5-2 | Wafer yield results from electrical probe testing                                                            | 99      |

| 5–3 | Yield results for wafer 2 before, and after, post-processing planar-<br>isation                              | 10      |

| 5-4 | SBS256 specifications.                                                                                       | 118     |

| 6–1 | Truth table for the current-routing circuitry control signals                                                | 13      |

to Gail

# Chapter 1

# Introduction

# 1.1 Background

Many optical processing architectures and systems require high performance, electrically addressed spatial light modulators (SLMs). The hybrid SLM technology of ferroelectric liquid crystal over silicon (FLCOS) is attractive because it combines two well matched technologies. Ferroelectric liquid crystals exhibit fast switching times coupled with low switching voltages, while very large-scale silicon integration permits the implementation of large active pixel arrays that can be addressed at high frame rates. These electrically addressed devices function as electronically-written, optically-read memory devices that are suitable for use in display applications, and as input or filter planes in optical systems.

Many of the medium-resolution FLCOS SLMs designed so far have been based on the one-transistor dynamic random access memory (DRAM) circuit. The DRAM-type circuit offers high pixel density but has some performance limitations, including photo-induced charge leakage and limited FLC drive capability. In this thesis, I present a general-purpose  $256 \times 256$  FLCOS device that incorporates a static-RAM latch and an XOR-gate at each pixel. The pixel circuit overcomes the limitations of the DRAM-type pixel at the expense of area and fill-factor. However, the high pixel count of this SRAM-type device raises many backplane design issues that are not as relevant to DRAM-type devices or smaller SRAM-type arrays. The device is particularly suitable for applications where the

#### Chapter 1. Introduction

read-beam is intense, say at the input stage of a cascaded SLM system, or in system where a pulsed light source cannot be used.

In recent years there has been a dramatic increase in research on artificial neural networks (ANNs). ANNs are useful tools for solving many classification, modelling, and prediction problems. They normally consist of parallel arrangements of many simple processing units (or neurons) connected together by variable strength connections (weights). Most work has centred on understanding the behaviour and limitations of many different network architectures and algorithms, through theoretical analysis and software simulation on digital processors. However, to realise the full potential of ANNs, efficient hardware implementations must be developed. Among other approaches, including VLSI neural chips, the optoelectronic approach is expected to play an important role in the implementation of medium-scale ANNs (100's-1000's of neurons). Optoelectronic implementations are especially attractive for classification applications where the input exists in the optical domain. FLCOS SLM technology can be used to implement the input, interconnection weights, and neuron functional blocks required by many optoelectronic ANN systems. Furthermore, if the image is converted to the coherent optical domain, powerful preprocessing functions can be performed on it 'for free' by using the techniques of Fourier optics.

## 1.2 Objectives

The objectives of my project were to:

- 1. Develop a general-purpose  $256 \times 256$  FLCOS SLM based on the static-RAM type pixel.

- 2. Demonstrate real-time temporally multiplexed grey-scale on such a device.

- 3. Develop a prototype neural-detector backplane capable of sampling the temporally multiplexed grey-scale generated by the SLM.

4. Optimise both devices for incorporation into a future optoelectronic ANN system.

# 1.3 Thesis outline

I begin Chapter 2 with an overview of some spatial light modulator technologies, and then introduce the technology of FLCOS. I then give a description of some pixel designs that have been incorporated into FLCOS SLM devices. These range from the single-transistor DRAM-type pixel, to so-called 'smart pixels' that can perform primitive processing functions.

In Chapter 3, I review some applications for which FLCOS SLMs are particularly suitable, including optical crossbar switching, and optical correlators. Then I consider some methods for generating grey-scale on FLCOS binary mode devices. The chapter closes with a review of some optoelectronic ANN implementations.

In Chapters 4 and 5, I present the SBS256 SLM – a  $256 \times 256$  pixel device that comprises a SRAM latch and an XOR-gate at each pixel. Chapter 4 concentrates on backplane design issues such as the pixel circuit, architecture, transient current spikes, and power dissipation. In Chapter 5, I present electrical and optical characterisation results. The electrical results include current spike measurements, operating frequency, backplane electrical yield, and the effects of post-processing planarisation. The optical characterisation results include contrast ratio, frame rate, temporally-multiplexed grey-scale, and uniformity.

Chapter 6 covers the development of OANN - a  $4 \times 4$  prototype neuraldetector backplane. The backplane is capable of sampling a 2's complement variant of the temporally multiplexed grey-scale generated by the SBS256. Photoinduced charge-leakage is identified as a potential problem for the neuron activity storage circuits. A simple technique is presented to significantly reduce this

## Chapter 1. Introduction

problem. Electrical and optical characterisation from the neuron circuits are also presented.

Finally in Chapter 7, I evaluate the performance of the two integrated circuit designs presented in earlier chapters and discuss possible improvements and future work using the devices.

# Chapter 2

# Spatial light modulators - an overview

The advantages gained from the inherent parallelism of many proposed optical processing and computing architectures rely critically on the availability of high performance two-dimensional spatial light modulators (SLMs). SLMs are used as data displays, spatial filters, incoherent to coherent image converters, twodimensional logic elements, and as routing elements. In this chapter I give an overview of some SLM technologies that have shown promise before focusing on the technology of ferroelectric liquid crystal over silicon (FLCOS).

## 2.1 Introduction

SLMs can modulate properties of an optical wavefront such as intensity, phase, or polarisation. Spatial light modulation can be accomplished via electrooptic, acoustooptic, magnetooptic, mechanical, photorefractive, or electroabsorptive effects in a variety of materials. There are two major classes of SLMs: optically and electrically addressed. There is such a wide variety of SLM technologies, that it is impractical to discuss all of them in detail (see SLM review papers [18,23, 74], or Applied Optics special issues on Information Processing for more recent

advances). In this chapter I will concentrate on electrically addressed devices, but will also consider optically addressed devices where appropriate.

The main advantage of electrically addressed devices is their ability to interface with both electrical and optical systems. The characteristics of electrically addressed SLMs are likely to define the performance of the systems they are used in. These characteristics include pixel count, frame rate, contrast ratio, physical size, cost, and power dissipation. I begin with an overview of the major SLM technologies.

# 2.2 Major SLM technologies

In this section, I consider three SLM technologies that have shown promise: digital micromirror devices, Si-PLZT devices, and self electrooptic effect devices.

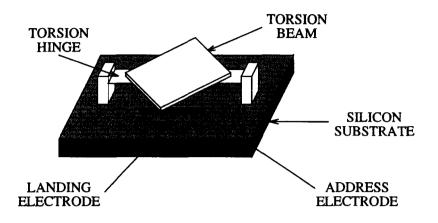

## 2.2.1 Digital micromirror devices

The digital micromirror device (DMD<sup>1</sup>), developed by Texas Instruments [84], is a monolithically fabricated SLM that employs electrostatically deflected mirrors as the light modulating elements. Each mirror is suspended by thin hinges over one or more address electrodes which are in contact with the underlying address circuitry. When an electrode is addressed, the overlying mirror, which is held at a fixed potential, is attracted to it. The mirror element design can be tailored to a particular application. For example, torsion beam DMDs are built to modulate amplitude, while flexure beam DMDs modulate mostly phase, and cantilever DMDs modulate amplitude and phase in a coupled fashion. The torsion-beam mirrors can be deflected in either of two directions about the axis defined by the support hinges (see Fig. 2–1). When a pixel mirror is tipped in one direction,

<sup>1</sup>DMD can also refer to deformable mirror devices, the forerunners to the digital micromirror technology

incident light is thrown out of the optical imaging system, so that the pixel appears dark. When it is tipped in the other direction, light passes through the imaging system so that the pixel appears bright.

**Figure 2–1:** Cross-section of a torsion-beam deformable mirror pixel. The mirror can be deflected in either of two directions about the support hinge axis by the underlying address electrodes.

DMDs have been addressed using charge coupled device (CCD) and static random access memory (SRAM) technologies. Boysel [9] developed a  $128 \times 128$ pixel virtual phase CCD-addressed device to establish an analogue charge image, which is then transferred to the overlying electrodes to deflect clover-leaf deformable mirrors. It accepts 16 analogue input signals at a clocking rate of up to 4 MHz. The underlying CCD array permits frame addressing so, unlike row addressed architectures, there is no skew, and a high 96% duty cycle. The contrast ratio of this device is approximately 2:1, as it was designed as a phase modulator. A 768  $\times$  576 pixel SRAM addressed DMD SLM with torsion-beam mirrors, has recently been developed by Texas Instruments capable of displaying PAL broadcast quality pictures for use in a projector display system [112]. Each frame of video is divided into three colour fields and grey scale is achieved by pulse width modulation within each colour field. Pixels can be switched in 10  $\mu$ s and exhibit a contrast ratio of 50:1. Texas Instruments are also fabricating a  $2048 \times 1152$  pixel device for a prototype high definition television display system [116]. The die will be 37 by 22 mm in size, and so is likely to suffer yield and reliability problems.

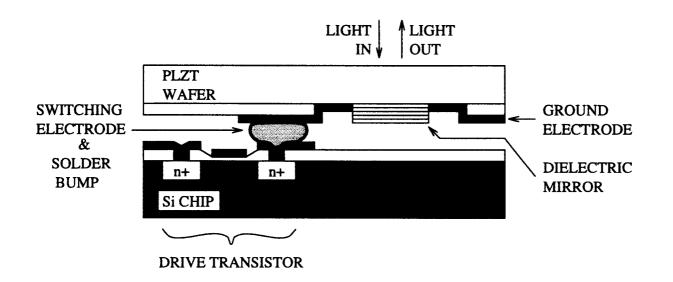

## 2.2.2 Si-PLZT devices

Si-PLZT devices combine mature silicon technology for processing and control, with the modulator material, lead lathanum zirconate titanate (PLZT). PLZT is a transparent, electrooptic, ferroelectric, ceramic material. It exhibits low switching times ( $\leq 100$  ns), high contrast ratios ( $\geq 500$ :1), and analogue modulation capability. However, it also requires high drive voltages (20–100 V) to give reasonable transmission through crossed polarisers.

The main technique used for combining Si and PLZT substrates involves flipchip bonding an Si chip (or chips) to a PLZT wafer – flip-chip bonding is widely used in the emerging technology of multi-chip-modules. Control and driver circuits are placed on the Si chip and connected to the PLZT modulator using metal solder bumps. The basic configuration of a unit cell is shown in Fig. 2–2. The drive transistor gate can be varied by electrically or optically addressed [20] control circuitry. The resulting electric field between the switching and ground electrodes, spaced 15–50  $\mu$ m apart, can vary the refractive index of the overlying PLZT material to phase modulate a read-beam. Amplitude modulation can be achieved by passing the read-beam through suitably oriented crossed polarisers. The output signal rise/fall times are limited by the drive circuitry. To give an idea of the transmission characteristics inherent with these devices, consider one of the prototype modulators fabricated by Jin *et al* [48] where an electrode spacing of 15  $\mu$ m was used. For an applied voltage of 0 V the transmission was ~ 0%, while for 40 V and 120 V it was ~ 4.5% and ~ 60% respectively.

With the flip-chip bonding approach, there is a voltage compatibility problem between the 20-100 V required for the modulator drive circuits (which may contain more than the single transistor illustrated in Fig. 2-2) and the control logic circuits operating at 5 V. Jin *et al* have also studied methods of bonding thin Si films with driver circuits directly onto bulk PLZT and then flip-chip bonding an Si chip containing the control circuitry. The low-voltage control signal is passed across the solder bump to control the high-voltage drive circuit. This will allow them to use high-density, foundry-processed VLSI chips with sophisticated

Figure 2-2: Cross section of a unit cell of a Si-PLZT SLM implemented using flip-chip bonding of the Si chip to the PLZT wafer. The electric field between the switching and ground electrodes varies the refractive index of the overlying PLZT material.

control circuits. Esener [19] reviews several other approaches used for combining the Si and PLZT substrates, each with their attendant advantages and disadvantages. He also describes a technique that incorporates self-tuned Fabry-Perot cavities into the modulator structures to reduce the required drive voltage by a factor of at least five. An optically recorded volume hologram is used as one of the highly reflective coatings of the Fabry-Perot cavity. It is recorded in place using interference between read-beam illumination and the reflected output. The phase angle of the resulting hologram automatically compensates for thickness variations across the modulator layer. This technique could also be applied to a wide variety of other SLM technologies where modulator uniformity is difficult to achieve over large arrays.

The large drive transistors required for high speed operation, coupled with the considerable power dissipation at high operating voltages, will probably limit this technology to relatively small, low fill-factor arrays. However, their analogue modulation capability makes them suitable for many optical processing and neural network applications.

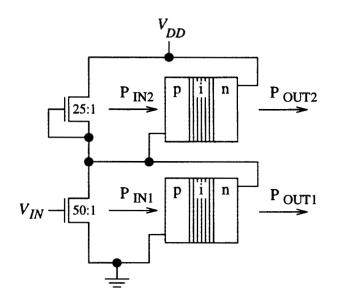

## 2.2.3 Self electrooptic effect devices

In the past few years several variants of the self electrooptic effect device (SEED) technology have been developed. SEEDs make use of the non-linear effect called the quantum confined Stark effect, which describes the changes in optical properties of quantum wells when an electric field is applied perpendicular to multiple quantum well (MQW) layers. Since the quantum confined Stark effect is an almost instantaneous process, the modulation frequency is limited only by the frequency with which the electric field can be modulated. Devices must be operated at a relatively narrow optical bandwidth, which is determined by the structure and properties of the MQW layers.

The MQW structure typically consists of 50–100 alternate layers of GaAs and  $Al_xGa_{1-x}As$ <sup>2</sup> grown by molecular beam epitaxy. In a SEED, a MQW is placed within a p-i-n diode structure, and can be configured as optical input and output devices [70]. When a SEED is connected to an external load, and is under strong optical illumination, the photocurrent generated in the SEED induces a large voltage drop across the load. The field across the MQW is reduced which, in turn, increases its absorption and photocurrent, so that by positive feedback, the transmittance of the device becomes significantly reduced. The modulation is fast, but the contrast ratio is low (2:1), and operation is restricted to a particular wavelength (typically 850 nm for GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As MQWs).

In symmetric-SEEDs (S-SEEDs), two SEEDs are connected back to back so that each acts as a light controlled load resistor for the other. The device can be switched between two stable states by momentarily changing the ratio of the two optical inputs. As switching is controlled by the ratio of two inputs rather than absolute intensities, device operation is more robust for real optical systems. The optical input and output power supply beams must be clocked, but this is not seen as a problem for most digital optical systems, where the architectures

<sup>2</sup>Where x is typically  $0.25 \le x \le 0.35$

and algorithms tend to be synchronous anyway. A  $256 \times 128$  optically addressed array and a  $16 \times 8$  electrically addressed array have been fabricated [11].

Figure 2-3: Cross section of a unit cell of an electrically addressed GaAs FET-SEED amplified differential modulator. implemented by Lentine *et al* [56]. Note that the drive transistors are wide compared to their length (W:L given in microns) to give high current sourcing capability for high frequency operation.

S-SEEDs have also been successfully integrated with various electronic technologies. When S-SEEDs are monolithically integrated with GaAs field effect transistors (FETs), very high speed, electrically addressed, differential modulator arrays can be implemented. A small  $6 \times 6$  [56] electrically addressed integrated array has been fabricated with a differential amplifier at each pixel (see Fig. 2-3). The input voltage swing to the differential amplifiers can be as small as a few hundred millivolts, while the voltage across the MQW modulators can be as high as 10 V. This permits the array to be interfaced to standard Si bipolar emittercoupled logic or GaAs FET electronic families that have typical voltage swings of less than 1 V. The device can operate at modulation frequencies of up to 2 GHz, limited only by the current sourcing capabilities of the drive transistors. Note that as with high speed Si-PLZT drive circuits, the transistors must be made wide to give high current sourcing capability for high frequency operation. They therefore take up significant area on the GaAs substrate which tends to limit pixel density, resolution and active area fill factor. GaAs circuits also use only n-channel transistors, so circuits such as inverters sink current in one of their states, and thus may be susceptible to overheating if care is not taken in their design.

Goodwill *et al* [30] have recently flip-chip bonded a  $16 \times 16$  array of S-SEEDs to a silicon driver backplane. Although inherently slower than GaAS FET technologies, silicon CMOS processes offer higher packing density, lower cost, higher yield and less overheating problems. The modulators are designed to work in the 1047–1064 nm region to match the high power available from diode pumped Nd:YLF and Nd:YAG lasers. They believe the device could work at up to 70 MHz with contrast ratios of 2–4:1.

S-SEED technology shows great potential for smart pixel and digital optical computing applications where very high frequency operation and low switching energies are more important than high contrast ratio and pixel resolution.

# 2.3 Liquid crystal devices

The design of electrically addressed FLCOS SLMs has been influenced by the liquid crystal display (LCD) industry. Many of the liquid crystal cell configurations and addressing schemes are similar, so before focusing on FLCOS SLMs, some configurations and schemes will be reviewed.

Liquid crystals (LCs) are attractive modulator materials for SLMs and displays as they have high birefringence, low switching energies, and low drive voltage requirements. LCs research and development has been driven by the displays industry as it attempts to challenge the cathode ray tube's dominance of the television monitor market with flat, light-weight, low-power devices. There can be major differences between the requirements of good SLMs and those for displays [15]. Displays typically have to operate with white light illumination, have a wide viewing angle, be shock resistant, and may have to withstand extremes of temperature. They usually only require 25–50 Hz frame rates, and contrast ratios of 5–10:1. SLMs, on the other hand, usually require high frame rates, high contrast ratios, and for coherently illuminated systems, phase flatness is also important.

LCs are a class of materials that possess properties intermediate of those of typical crystalline and liquid phases. LC molecules are mainly organic in nature with long, thin, rod-like structures formed by linking aromatic rings to hydrocarbon chains. Their anisotropic<sup>3</sup> structure can lead to anisotropy of certain bulk physical properties such as dielectric permittivity and refractive index. The combination of such anisotropy, characteristic of crystalline materials, with the flow properties of liquids make liquid crystals uniquely useful in a variety of applications.

Three classes of liquid crystal structures exist: nematic, cholesteric, and smectic phases, each with a characteristic crystalline structure. Commercially available nematic LCs appeared in the early 1970's and have been used extensively in the relatively mature LCD technology. However, nematic LCs exhibit relatively low contrast (5:1), and 10–100 ms switching times, restricting potential device frame rates to 10–50 Hz. Since the early 1980's, smectic phase ferroelectric liquid crystals (FLCs) have been investigated for use in high frame rate applications requiring much faster switching times (10–100  $\mu$ s), and higher contrast ratios.

#### 2.3.1 Smectic phase - the surface stabilised effect

In the smectic phase, the long axes of the molecules align themselves parallel to each other. Furthermore, the centres of gravity of these molecules exist in one plane and the planes, or layers, pile up on each other. However, there is no general regularity of spacing between the molecules in one layer. There is therefore a two-dimensional ordering in the position of the liquid crystal molecules.

<sup>3</sup>Anisotropic materials have different properties for different directions in the material.

Certain chiral<sup>4</sup> smectic liquid crystals exhibit ferroelectric properties, which can be utilised in electrooptic devices. Ferroelectric liquid crystals (FLCs) possess a permanent or spontaneous polarisation, and most of the commonly used ferroelectric phase is the chiral smectic C ( $S_C^*$ ) phase. In a bulk sample there is no net polarisation because the director n, spirals through the material from layer to layer. However, by use of suitable boundary conditions, the helical structure can be suppressed and thin layers of  $S_C^*$  can show a net polarisation.

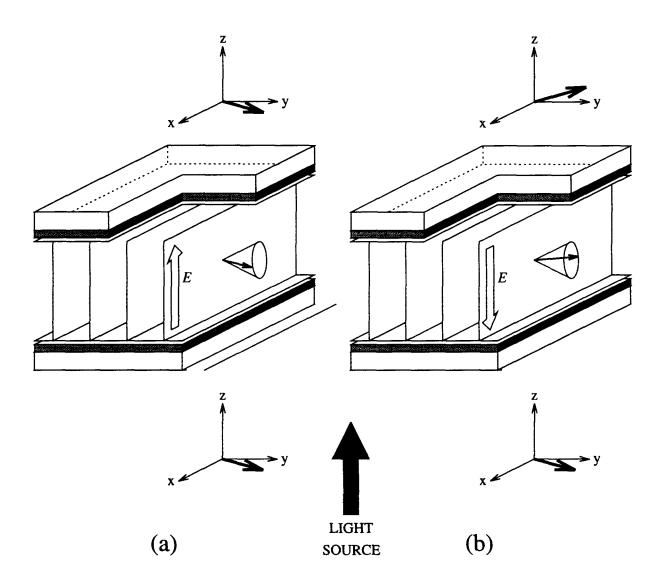

The most commonly used device geometry is the surface stabilised FLC (SS-FLC), first described by Clark and Lagerwell [13]. A transmissive SSFLC cell typically comprises a 2–3  $\mu$ m of FLC sandwiched between two glass substrates, each coated with a transparent electrode and a SiO<sub>x</sub> or rubbed polyamide alignment layer. The device is similar to a twisted nematic device [89] except that the cells are thinner and the alignment layers are parallel. In the idealised SSFLC configuration, the substrates are close enough to unwind the FLC's intrinsic helical structure permanently so that the molecular axes (or directors) can only exist in two energetically degenerate states oriented at  $\pm \phi$  to the layer normal, where  $\phi$  is the molecular tilt angle.  $\phi$ , is typically close to 22.5° over large temperature ranges, permitting the optic axis to be electronically rotated through approximately 45°, by an applied electric field of the appropriate sign. Both amplitude and phase modulation are possible.

#### Amplitude modulation

Amplitude modulation can be achieved by placing the cell between crossed polarisers (see Fig. 2-4). If the polarisation of normally incident light is chosen either parallel or perpendicular to one of the voltage selected optical axis states, it will be transmitted through the FLC unaffected. When the other optical state is selected by applying a field of the opposite sign, the optical axis is rotated to a 45°

<sup>4</sup>A chiral molecule cannot be superimposed upon its mirror image by translation, rotation, or reflection.

angle from the incident polarisation so that both the ordinary and extraordinary modes are excited. For the correct FLC layer thickness d, a total phase shift of  $\pi$  will accumulate between these two modes, and the incident light's polarisation will be rotated by 90°. The transmission I through the crossed-polarisers is given by:

$$I = I_0 \sin^2(4\phi) \sin^2(\frac{\Delta n d\pi}{\lambda})$$

(2.1)

where  $I_0$  is the input intensity,  $\Delta n$  is the FLC birefringence, and  $\lambda$  is the wavelength of the incoming light. The contrast ratio is theoretically infinite, but in real devices, it is limited by the uniformity of the director alignment and the quality of the polarisers. Gourlay [31] has measured contrast ratios of up to 500:1 for FLC test cells fabricated in-house in the Applied Optics Group facilities, at the University of Edinburgh.

#### Phase modulation

Two methods can be used to generate phase modulation. The first has one of the switchable optical axes parallel to the polarisation vector of the incoming light. When the FLC is switched to the other state, the phase of the light is changed by an amount dependent on both the FLC rotation angle and the birefringence. In the other method, the polarisation vector of the incident light and first polariser are set to bisect the FLC's two switchable optic axes. The propagation of light through the FLC produces elliptically polarised light from the incident linear polarisation. The sense of the polarisation depends on which side the FLC's director is switched to. The elliptically polarised light then passes through an analyser, orthogonal to the first polariser, which reduces the elliptical polarisation to linear polarisation exhibiting a 0 or  $\pi$  phase difference, independent of switching angle or optical path length. For 100% transmission,  $\phi$  must be 45°, rather than 22.5°.

÷

Chapter 2. Spatial light modulators - an overview

Figure 2-4: Ferroelectric liquid crystal operation. (a) FLC optic axis switched so that it is parallel to incident polarised light - no change in polarisation. (b) FLC optic axis at 45° to incident light - polarisation rotated by 90°.

#### Real devices – the chevron defect

The most common defect found in SSFLC  $S_C^*$  devices is the chevron defect [85, 54]. They are caused by the shrinking of the smectic layers during the final stages of cell fabrication, so that the layers are not normal to the bounding glass plates; zig-zag patterns can be observed when viewed through a polarising microscope. With devices in the chevron structure, the switched states are not fully bistable, and one of the states is usually preferred when the driving voltage is removed. Contrast ratios are also severely reduced. The chevron geometry can be changed to the more desirable bookshelf geometry by applying a low frequency alternating electric field across the FLC layer, typically 30 V/ $\mu$ m or more.

#### Switching time

To a first approximation the switching time  $\tau$  can be given by,

$$\tau = \frac{\eta}{P_S E} \tag{2.2}$$

where,  $\eta$  and  $P_S$  are the FLC material's viscosity and spontaneous polarisation, and E is the electric field applied across it. Clearly  $\tau$  is lower for low viscosities, high polarisation, and high electric fields.

#### Switching energy

In general, the power dissipated, P, in charging and discharging a capacitor from 0 to V and back to 0 again at frequency f is given by,

$$P = QVf \tag{2.3}$$

where Q is charge dumped onto the capacitor. For an area A of FLC material with spontaneous polarisation  $P_s$ , the charge Q associated with switching from one state to another is given by,

$$Q = 2 |P_S| A \tag{2.4}$$

so,

$$P_{FLC} = 2 \left| P_S \right| A V_{FLC} f \tag{2.5}$$

A rough calculation shows that  $P_{FLC}$  for a typical test cell filled with SCE13 FLC, is about 1 mW when the following values are used:

$$P_S = 26 \text{ nC/cm}^2 V_{FLC} = 10 \text{ V}$$

$A = 1 \text{ cm}^2 \qquad f = 2 \text{ kHz}.$

#### Charge balancing

In order to prevent chemical degradation in any liquid crystal device, care must be taken to ensure that over a period of time, the LC layer does not receive a net voltage or field across it. Practically, this means that if a positive voltage pulse is applied across the LC for a certain period of time, a negative pulse of equal duration should then be applied across it. The is usually referred to as the charge balancing requirement. The FLC layer in SSFLC devices responds to the *sign* of the electric field applied across the layer. Therefore because of charge balancing, the duty cycle of the device can be significantly affected as the FLC will be in its OFF state for 50% of the time. This is explained in more detail for specific device implementations in Section 2.4.

#### 2.3.2 Other FLC modes

SSFLC devices are inherently binary in nature, however, some FLC modes can have an analogue response.

#### **Electroclinic effect**

The smectic A  $(S_A)$  phase, used in the electroclinic or soft mode electrooptic effect [4,16], has attracted attention because of its analogue optical response and sub-microsecond switching times. In this phase, the directors are perpendicular

to the layers and the optic axis can be rotated in proportion to the applied field. Davey and Crossland [16] have built test cells capable of generating more than 50 grey levels. However, high electric fields are required, but, the main limitation of using the electroclinic effect to generate reproducible grey levels, is that the cell's temperature must be controlled to within a few hundredths of a degree. This could be a problem for addressing an array of pixels on a silicon backplane as there are likely to be variations in temperature across the array, because of power dissipated in switching transistor circuits.

#### **Distorted helix effect**

The distorted helix effect (DHE) also has a fast, analogue response [21]. The DHE device structure is similar to the SSFLC but the helical precession of the director from layer to layer is not suppressed. This can be achieved by using FLC mixtures that possess a short helix pitch. The application of an external field distorts the helix and thus changes the cell's birefringence. However, at present DHE device research is at an early stage of development and cells tend to suffer from alignment and scattering problems.

## 2.3.3 Addressing schemes

Liquid crystal devices can be addressed optically [32,71] or electrically. Electrical addressing of array LC devices can be performed by direct drive, passive, or active matrix addressing methods.

#### Direct drive addressing

In direct drive addressing, one wire is used to address each pixel. It is useful for arrays up to  $16 \times 16$ , but above this, the area required for interconnect would dominate the pixel array. The frame rate is potentially high as all the pixels can be addressed simultaneously, and good contrast ratio can be expected as pixels can be constantly driven.

#### Passive addressing

The simplest way to address a large array of pixels is to use matrix addressing techniques. Row and column electrodes are patterned onto the glass substrates and the pixels are defined where the electrodes overlap. Data is simultaneously presented to all columns, and one row at a time is selected by an appropriate voltage signal. This scheme results in error voltages which affect the unselected rows [3]. The size of the array is limited by the effects of the error voltages and the characteristics of the (typically nematic) liquid crystal. The frame time is proportional to the number of rows in the display as the signal has to be present on each row long enough for the liquid crystal to switch. This limits device to about 100 lines, which is acceptable for calculators, status display panels, etc.

Multiplexing capabilities are improved with supertwist nematics (STN), which provides higher contrast, sharper turn-on characteristics, and faster response. The fast switching times and bistability of FLCs can also improve the multiplexing capabilities of passively addressed devices: CRL Smectic Technology have developed several transmissive FLC devices, including a  $320 \times 320$  array [98], with a contrast ratio of at least 50:1.

#### Active matrix addressing

Active matrix addressing overcomes the problems associated with passive addressed nematic devices by including an active element in each pixel. The active element is usually a thin-film transistor (TFT), although two-terminal devices and diodes have also been used [44]. The TFT has the effect of sharpening the effective cell threshold by replacing the unfavourable switching characteristics of the TN cell with the favourable characteristics of a transistor. These TFTs serve to hold the desired voltage at each pixel, while subsequent rows are addressed with significantly reduced cross-talk.

With TFT displays, there is also the opportunity to integrate some of the drive circuitry onto the display, which can drastically reduce the number of external

connectors [24,63]. However, the presence of TFTs on the back glass plate limits both the resolution and the ability to miniaturise the displays. The opaque TFTs take up room and must be a certain physical size to attain the necessary drive. This can cut the display's light efficiency to less than 5%. The main disadvantage of TFT displays is their high cost. This is a direct consequence of the need to produce displays with a working TFT at each pixel. Defect densities of 0.01 defects/cm<sup>2</sup> lead to yields of only 10–20% for a 10 inch diagonal display. The defect density is much lower than that needed for Si memory chips. Faulttolerant architectures can improve yields [97], but they are still expensive.

Matsushita manufacture a 15 inch diagonal, full colour, display with a resolution of  $1152 \times 900$  pixels [109] is an example of a state-of-the-art active matrix device. This device is probably at the limits of what is economically feasible.

## 2.4 Ferroelectric liquid crystal over silicon

In recent years there has been an active interest in developing the hybrid technology of ferroelectric liquid crystal over silicon (FLCOS). The fast switching times and low switching energies of FLCs, coupled with the high addressing speeds of Si backplanes make FLCOS SLMs attractive components for compact optical systems. The Si and LC industries have each progressed rapidly over the last decade so that the performance capabilities of SLMs has increased and can be expected to continue as a consequence of improvements in the component technologies.

During the 1980's, complementary metal oxide semiconductor (CMOS) became the dominant technology for general-purpose integrated circuit (IC) applications. It has come to the forefront primarily due to low power consumption; aside from leakage currents, power is dissipated only during switching events and not when the circuit is in a stable (non-switching) state. This is a major improvement over what occurs in circuits based on bipolar and nMOS fabrication technologies. Similarly, circuits can be designed where small deviations in transistor characteristics do not perturb the operating point. Consequently, it has

proven to be a robust manufacturing technique that permits large quantities and varieties of ICs to be fabricated with high yield. The technology is very flexible - it is suitable for implementing digital logic, memory devices, photodetectors, signal processing, and various analogue applications.

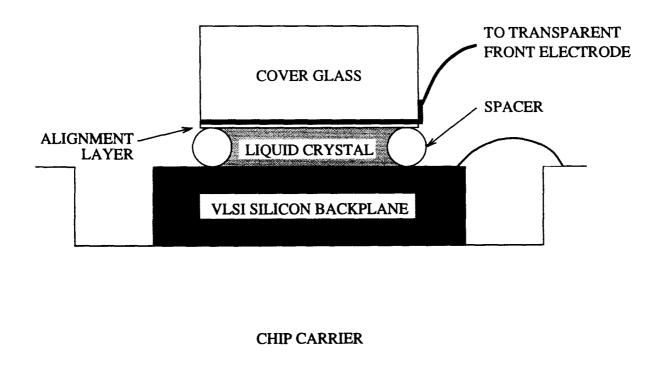

An FLCOS SLM is constructed by sandwiching a thin layer of FLC between a silicon backplane IC and a block of glass coated with a transparent front electrode (see Fig. 2–5). The backplane IC normally comprises an array of pixels, each with a memory circuit and an aluminium pad that doubles as an electrode and a mirror. Peripheral circuitry, such as shift registers and/or decoders, is usually included to address the array. The transparent front electrode is common to all pixels so the voltage applied across the FLC at each pixel is the difference between the front electrode voltage and that applied to the pixel electrode mirror. The device works in a reflective rather than transmissive mode but the principle of selectively rotating the polarisation of the read-beam is exactly the same (see Section 5.4).

Figure 2–5: Cross-section of a FLCOS SLM.

The remainder of this chapter reviews the various pixel designs that have been used in FLCOS SLM backplanes. These range from simple single transistor pixels to so-called 'smart pixels' that incorporate optical input with some primitive local

processing. I will discuss the single transistor pixel in some detail because the SBS256 device described in Chapters 4 and 5 was developed to overcome the short-comings inherent in the single transistor design.

## 2.4.1 DRAM-type devices

The main thrust of research into FLCOS SLMs has focused on new device designs with increased bandwidth. As with active-matrix displays, most designs utilise a pixel circuit based on the one-transistor cell of the dynamic random access memory (DRAM) to achieve a high pixel density (see Table 2–1).

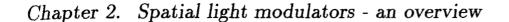

#### **One-transistor** pixel

The basic structure of the one-transistor pixel is shown in Fig. 2–6. The capacitor  $C_{FLC}$  represents the capacitance of the overlying FLC layer, while  $C_{MIRROR}$  is the storage capacitance associated with the electrode mirror. The transistor acts as a voltage controlled switch, that isolates the capacitors when open (ENABLE low), and permits the capacitors to charge to the DATA line potential when closed (ENABLE high).

The simplicity of the single transistor design offers small pixel size and thus high pixel density. However, it also has some important limitations:

- Can only provide a limited amount of charge to switch the overlying FLC.

- Suffers from photo-induced charge leakage.

- Limited FLC charge balancing capability requires a pattern/inverse-pattern drive scheme.

These will now be considered in turn.

To achieve short frame scan times, it is usual for the row address time (the time when each ENABLE is high) to be shorter than the FLC response time.

Chapter 2. Spatial light modulators - an overview

| Array              | Backplane              | Pixel Area (in $\mu$ m <sup>2</sup> ) | Frame      | Ref.                |

|--------------------|------------------------|---------------------------------------|------------|---------------------|

| Size               | Technology             | (Pitch in $\mu$ m)                    | Rate (kHz) | (Year)              |

| $240 \times 240^*$ | CMOS                   | $145 \times 200$                      | 0.06       | [114] (1982)        |

|                    |                        | $(165 \times 220)$                    |            |                     |

| $176 \times 176$   | $3~\mu{ m m}$ p-well   | $22 \times 14.5$                      | 1          | [106] $(1991)$      |

|                    | CMOS                   | (30)                                  |            |                     |

| 12 	imes 12        | CMOS                   | $70 \times 100$                       | •••        | [5] (1992)          |

|                    |                        | (110)                                 |            |                     |

| $128 \times 128$   | $2~\mu{ m m}$ n-well   | 22~	imes~22                           | 5**        | [49] (1993)         |

|                    | CMOS                   | (30)                                  |            |                     |

| 256~	imes~256      | $2~\mu{ m m}$ p-well   | $17 \times 17$                        | 4**        | $[36,\!35]\ (1993)$ |

|                    | CMOS                   | (20)                                  |            |                     |

| 256~	imes~256      | $1.2 \ \mu m$ p-well   | 28.4 	imes 28.4                       | 4**        | $[36,\!35]\ (1993)$ |

|                    | CMOS                   | (30)                                  |            |                     |

| 256~	imes~256      | $1.2~\mu{ m m}$ n-well | $17 \times 17$                        | 8.3**      | [66, 67] (1993)     |

|                    | CMOS                   | (21.6)                                |            |                     |

| $512 \times 512$   | $3.0 \ \mu m p$ -well  | $22 \times 14.5$                      | 0.4        | [10] (1994)         |

|                    | CMOS                   | (30)                                  |            | ······              |

\* This device has a nematic LC modulator layer.

\*\* These frame rates do not include charge balancing (divide by two).

Table 2-1: Examples from the literature of the development of one-transistor DRAM-type devices.

Figure 2–6: Schematic of the one-transistor DRAM-type pixel. It comprises a FET pass transistor addressed by ENABLE and DATA buslines, a charge storage capacitor, and an electrode mirror. FE denotes the transparent front electrode.

Therefore the pixel capacitors are charged and then left electrically isolated until they are readdressed in the next frame. The movement of the ferroelectric dipoles while switching the FLC results in a voltage drop  $\Delta V$  across the FLC layer given by,

$$\Delta V = \frac{2P_S A}{C} \tag{2.6}$$

where A is the pixel area, and C is the effective capacitance of the pixel. From Equation 2.2, shorter switching times can be achieved with higher  $P_S$  FLC materials but  $\Delta V$  would be also be larger (assuming A and C were not changed). If  $\Delta V$  approaches the voltage impressed by the DATA signal, only partial switching will occur. Each row of the array would then have to be addressed for a time approaching  $\tau$  so that more charge could flow onto the pixel as the FLC switches; the frame scan time would therefore be drastically increased. This may limit the FLCs used on one-transistor DRAM devices to those that possess a  $P_S$  of less than a few tens of nC/cm<sup>2</sup> [15].

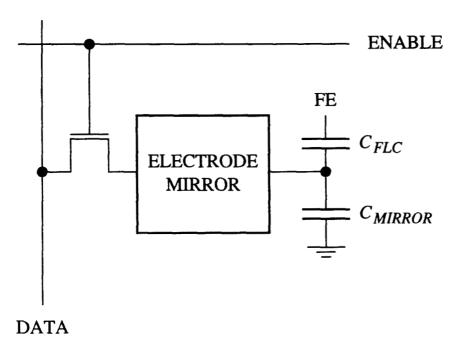

Photo-induced charge leakage is a problem inherent with DRAM-type pixels [35]. Once the pixel capacitor has been charged and isolated, the charge can leak away through the transistor channel resistance  $R_{OFF}$  (10<sup>12</sup>  $\Omega$ ), the liquid crystal resistance  $R_{FLC}$  (10<sup>11±1</sup>  $\Omega$ ), and the drain-substrate reverse-biased junction ( $D_{DB}$ ) of the pass transistor (see Fig. 2–7). When light falls onto the backplane sub-

Figure 2-7: Equivalent circuit of the one transistor DRAM-type pixel.

strate, the most significant leakage path is through  $D_{DB}$ . Light falling onto the substrate generates electron-hole pairs as it is absorbed near the surface. For a p-type substrate, the additional holes do not really affect the total majority hole population, however, the minority electron population is greatly increased. The electrons can exist in the substrate for 10–100  $\mu$ s, where they can travel for 100's of microns before they recombine with a hole. If some pass close to the reverse-biased diode they may be swept across its built-in electric field and so discharge the pixel capacitor. The photo-induced minority carrier population and thus the discharge rate is proportional to the light intensity. Handschy *et al* [35] measured a 50% erasure time of 100 ms with a light intensity of 10 mW/cm<sup>2</sup> for their second-generation 256 × 256 pixel device. To reduce the effects of charge leakage, the following steps can be taken:

- Make the pixel storage capacitor as large as possible.

- Shield as much of the substrate as possible from incident light.

- Refresh the pixel array at high frame rates.

- Use a low intensity read-beam.

- Pulse the read-beam on a low duty cycle.

It should be noted that if the FLC in FLCOS devices could be aligned into the fully bistable bookstack geometry, then charge leakage would only be significant if the capacitor discharged before the FLC had switched. However, the bookstack geometry is usually attained by treating the FLC layer with a high electric field  $(20-30 \text{ V}/\mu\text{m})$  – at the time of writing, this treatment has not been reported for a DRAM FLCOS device, probably because researchers do not want to risk damaging one of their limited supply of working devices.

The usual method of charge balancing the FLC layer on a one-transistor DRAM device, requires that after a pattern has been scanned onto the array and viewed, the inverse of the pattern must then be scanned on and held for the same duration. The pattern on the SLM is therefore discontinuous – it can only be interrogated for 50% of the time. Again, if the FLC layer had the bistable bookstack structure, the array would only need to be addressed when the pattern was to be altered, so a suitable drive scheme could be developed where the valid duty cycle was almost 100% (at the expense of frame rate).

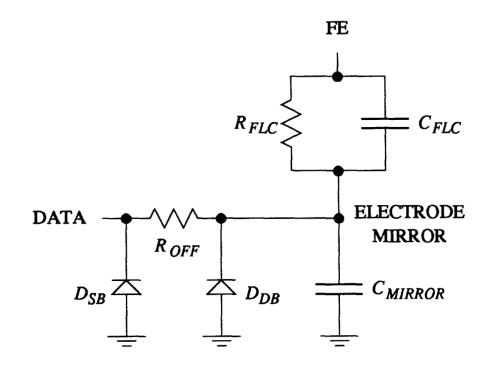

#### Three-transistor pixel

The three-transistor DRAM pixel design shown in Fig. 2–8, permits continuous interrogation of the overlying FLC layer whilst ensuring it is fully charge balanced.

The drive scheme for this type of pixel requires the following:

- The FLC layer must be fully bistable.

- The DATA line can be set to 0,  $V_{DD}/2$ , and  $V_{DD}$  voltage levels.

- The front electrode must be held at  $V_{DD}/2$ .

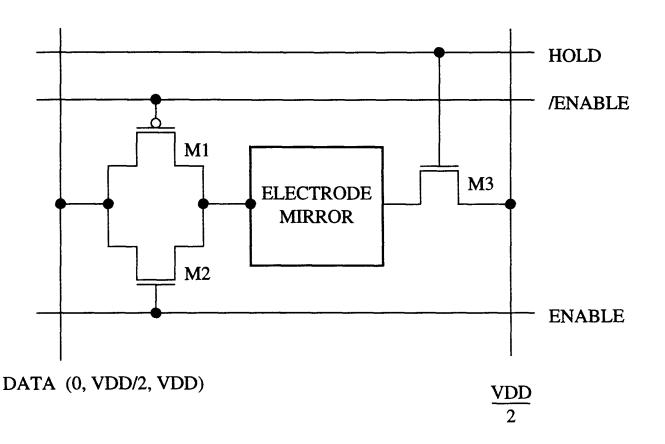

**Figure 2–8:** Schematic of the three-transistor DRAM-type pixel capable of providing almost continuously valid patterns. The two power rails, VDD and GND, which are required for substrate and well taps, are not shown.

Under normal conditions the pass transistor M3 is on so the electrode mirror is also held at  $V_{DD}/2$ ; as there is no voltage across the FLC layer, it remains in the state it was last driven to. Now assume the FLC is in its off state. It is switched to its on state by turning off the pass transistor, applying 0 V to the DATA line, and turning on the transmission gate M1 and M2. This results in a positive voltage (with respect to the mirror electrode) of  $V_{DD}/2$  across the FLC layer. After the FLC has switched, the transmission gate is turned off and the pass transistor is turned on again. To switch the FLC off again, the sequence is repeated with the DATA line set to  $V_{DD}$ , to generate a negative voltage across the FLC layer.

As row addressing is normally used to address pixel arrays, the DATA lines can be set to a third voltage level,  $V_{DD}/2$  to permit individual pixels to be changed by setting the appropriate DATA line to 0 or  $V_{DD}$  while setting all the others to  $V_{DD}/2$ . A 64 × 64 device using this type of pixel has been designed by Mike Snook in the Applied Optics Group at the University of Edinburgh [94]. It is

#### Chapter 2. Spatial light modulators - an overview

currently being fabricated using a high voltage (35 V) CMOS process that will permit both microsecond FLC switching times and high field treatment of the FLC layer to ensure bistability. It will be used in an efficient optical cross-bar routing network [72] (see Section 3.2.1).

#### Four-transistor pixel

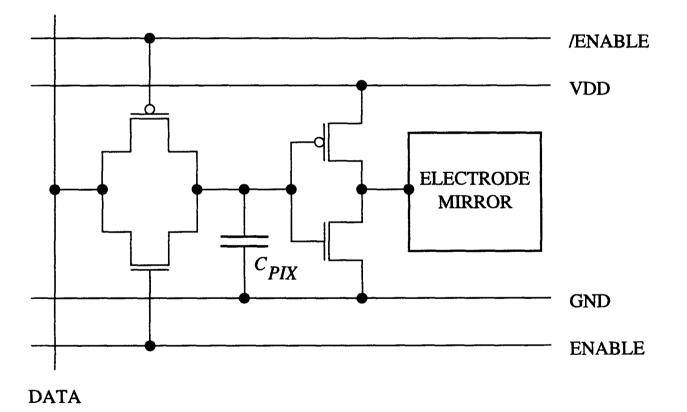

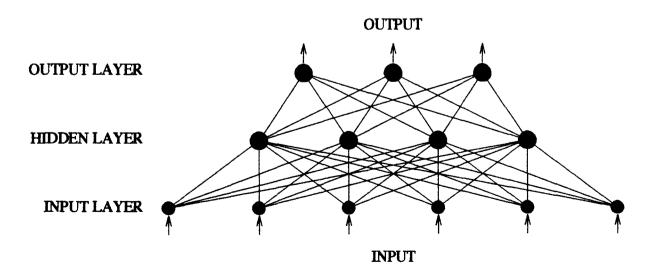

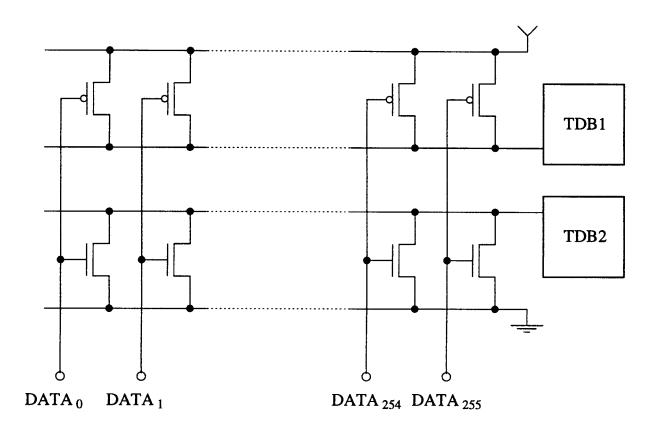

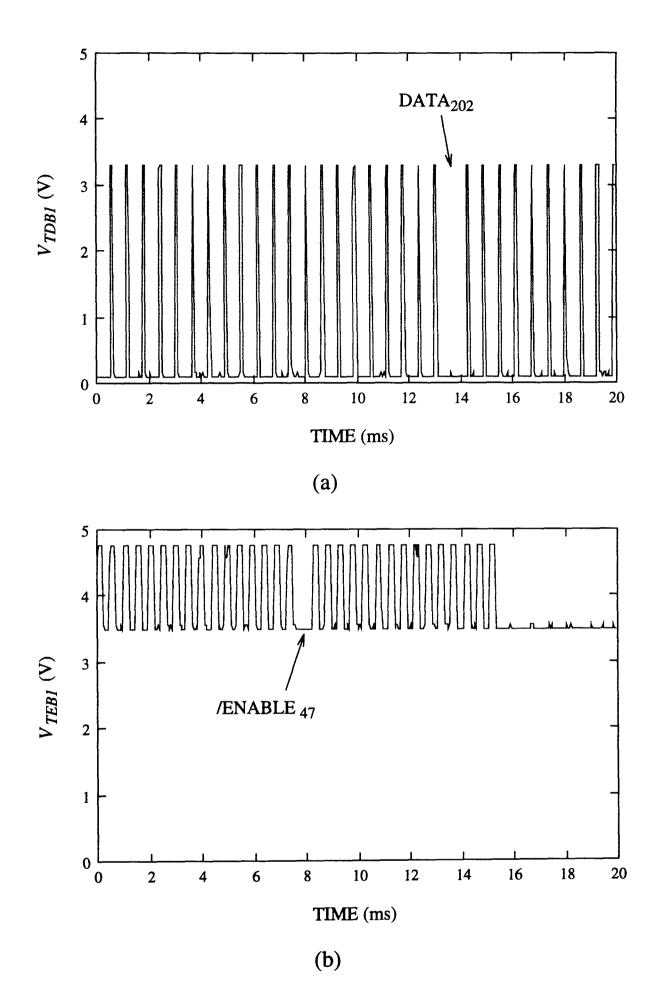

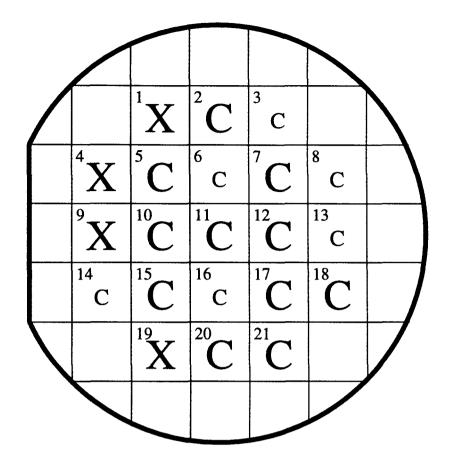

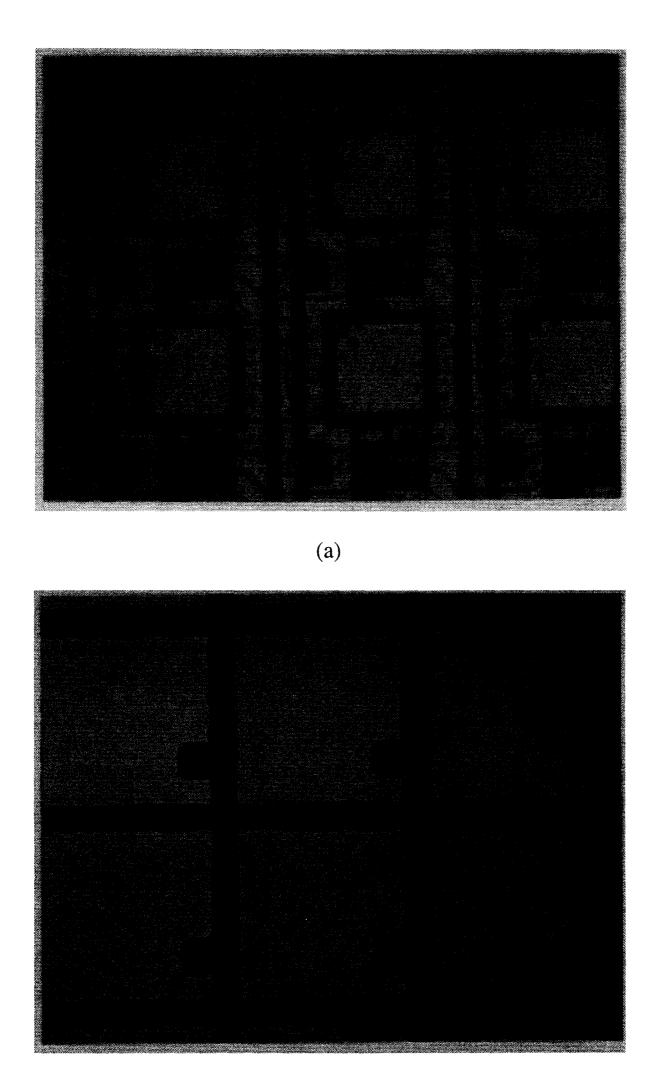

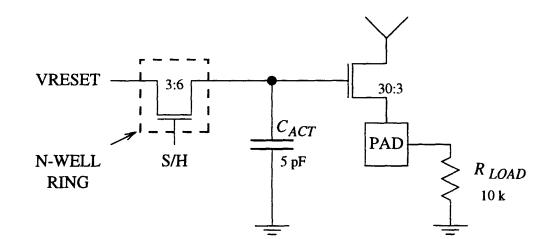

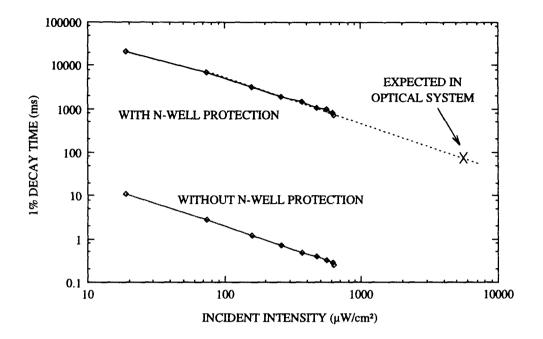

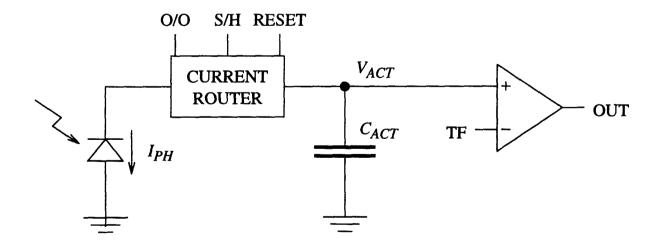

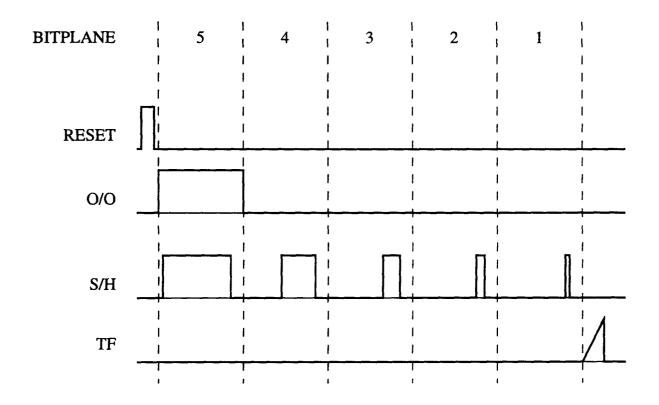

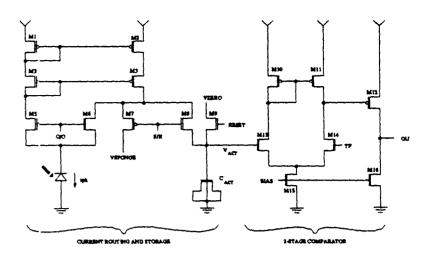

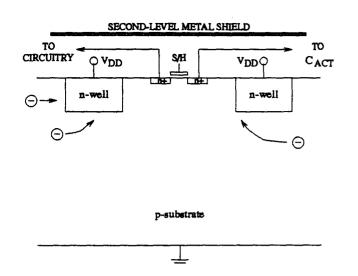

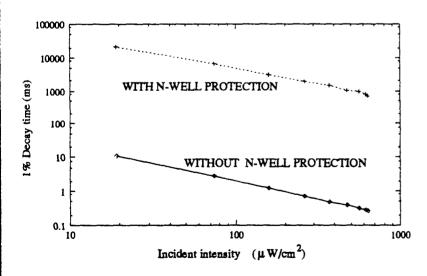

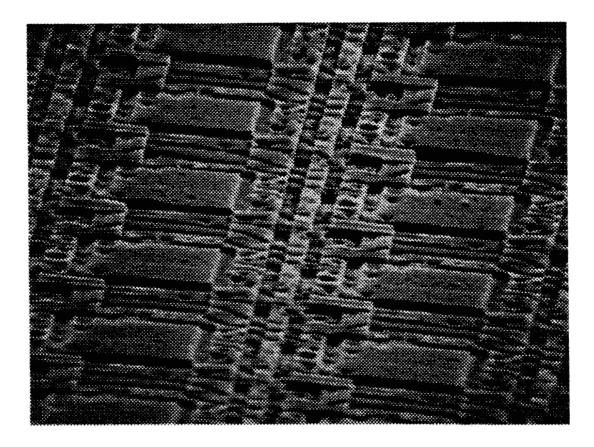

The four-transistor DRAM pixel implemented by Jared *et al* [46] is illustrated in Fig. 2–9. The inverter decouples the storage capacitor from the the pixel electrode mirror, and thus overcomes the  $P_S$  limitation of the single transistor design. However, the pixel still stores the state dynamically, and so suffers from light-induced charge leakage.