# Integrating CAM and Process Simulation to Enhance the Analysis and Control of IC Fabrication

Thesis submitted by

Angus Joseph MacDonald

for the degree of

Doctor of Philosophy

Edinburgh Microfabrication Facility

Department of Electrical Engineering

University of Edinburgh

United Kingdom

# **Declaration**

I declare that all the work done in this Thesis is entirely my own except where otherwise indicated.

This Thesis is the result of a CASE project with Plessey Semiconductors Ltd.

# **Contents**

| Abstract        |        |                                        |      |  |  |

|-----------------|--------|----------------------------------------|------|--|--|

| Pu              | blicat | ions                                   | viii |  |  |

| Acknowledgments |        |                                        |      |  |  |

| 1.              | Intro  | oduction                               | 1    |  |  |

|                 | 1.1    | IC Manufacturing                       | 2    |  |  |

|                 | 1.2    | Advanced Manufacturing Technology      | 4    |  |  |

|                 | 1.3    | Motivation                             | 8    |  |  |

|                 | 1.4    | Structure of Thesis                    | 9    |  |  |

|                 |        | References                             | 9    |  |  |

| 2.              | Spec   | eifying and Controlling IC Fabrication | 15   |  |  |

|                 | 2.1    | Introduction                           | 15   |  |  |

|                 | 2.2    | Wafer Fabrication                      | 16   |  |  |

|                 | 2.3    | Process Steps                          | 18   |  |  |

|                 |        | 2.3.1 Oxidation                        | 19   |  |  |

|                 |        | 2.3.2 Diffusion                        | 22   |  |  |

|                 |        | 2.3.3 Ion Implantation                 | 24   |  |  |

|                 |        | 2.3.4 Deposition                       | 26   |  |  |

|                 |        | 2.3.5 Etch                             | 28   |  |  |

|                 |        | 2.3.6 Photolithography                 | 30   |  |  |

|                 | 2.4    | Process Integration                    | 32   |  |  |

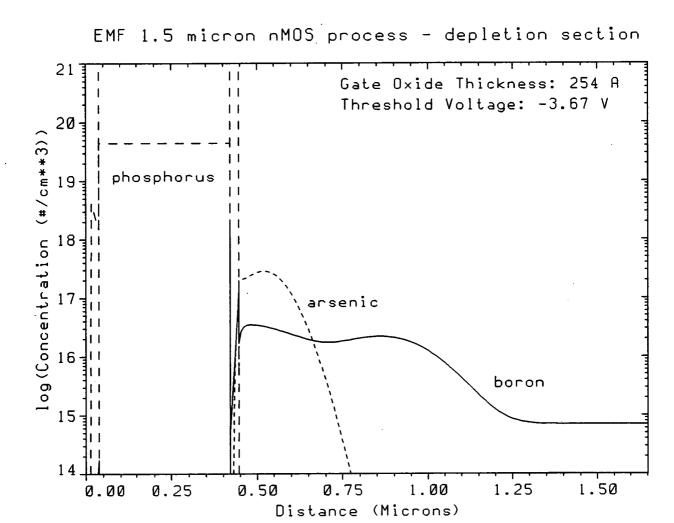

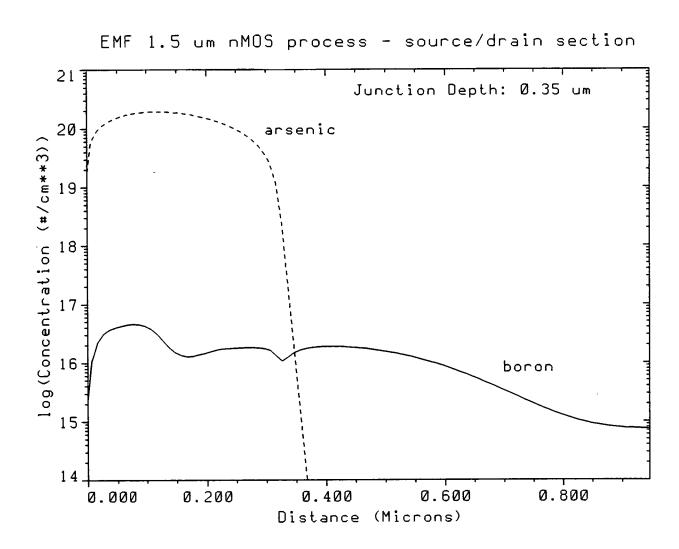

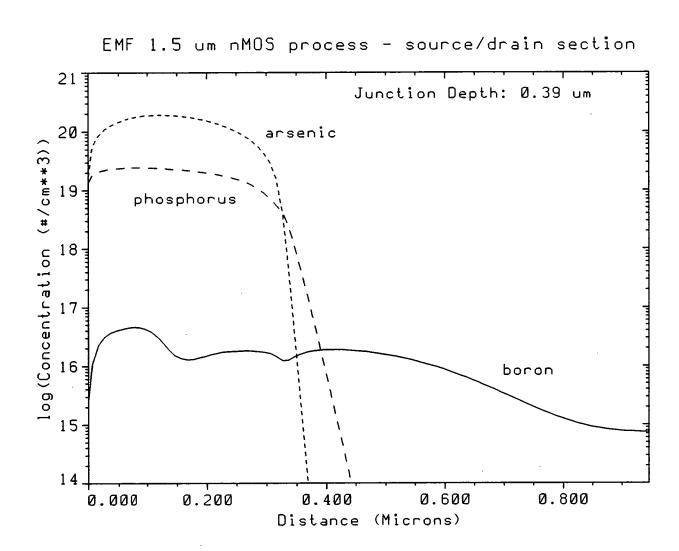

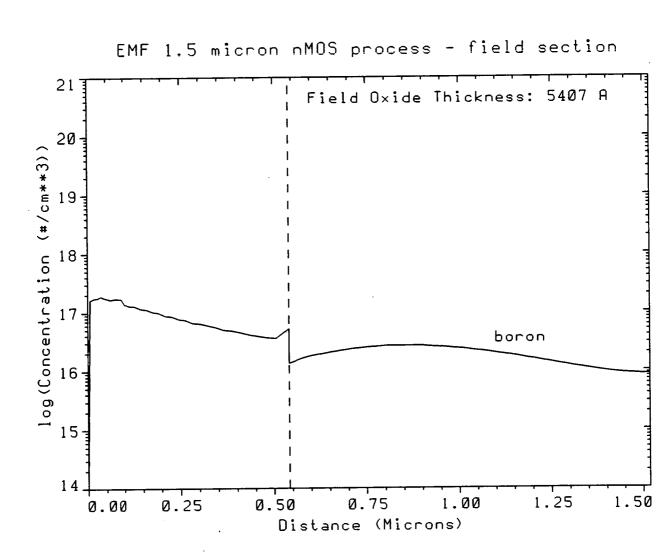

|                 |        | 2.4.1 The EMF 1.5 μm nMOS Process      | 34   |  |  |

|                 |        | 2.4.2 The Process Runsheet             | 37   |  |  |

|                 | 2.5    | Summary                                | 38   |  |  |

|                 |        | References                             | 40   |  |  |

| 3.              | Con    | nputer Aided Manufacturing             | 43   |  |  |

|                 | 3.1    | Introduction                           | 43   |  |  |

|                 | 3.2    | CAM for the Semiconductor Industry     | 44   |  |  |

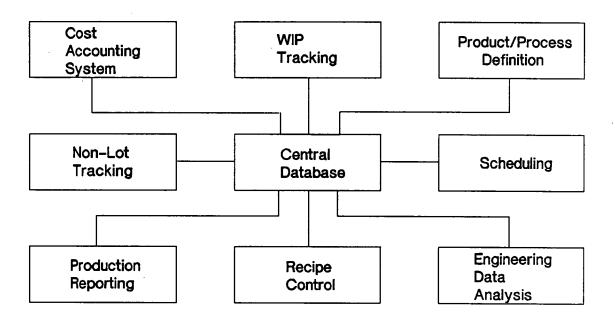

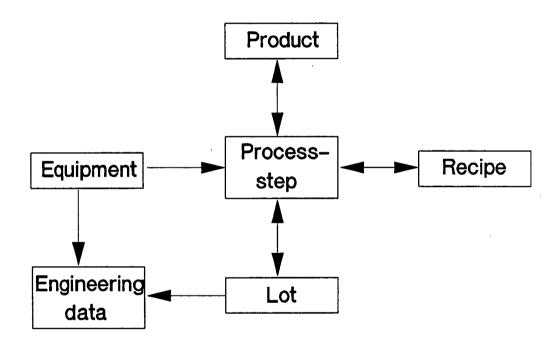

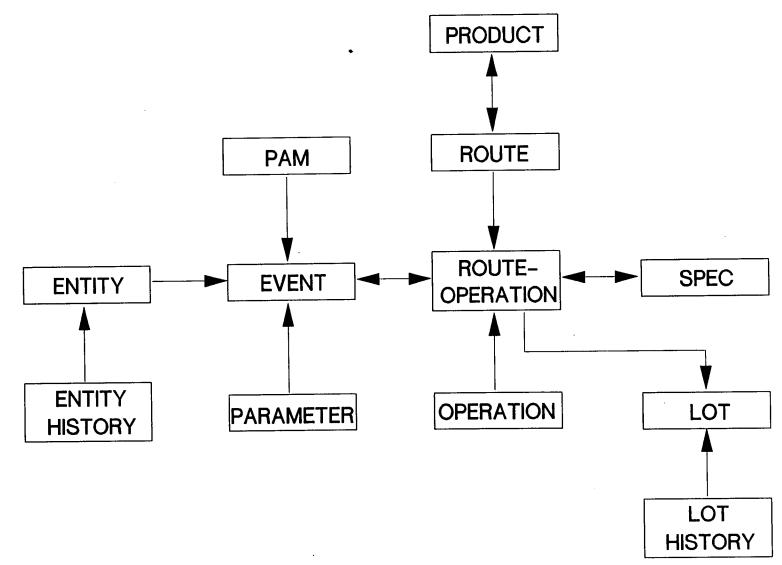

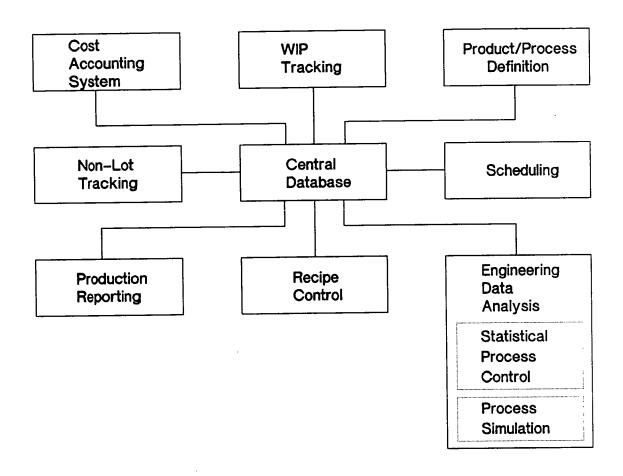

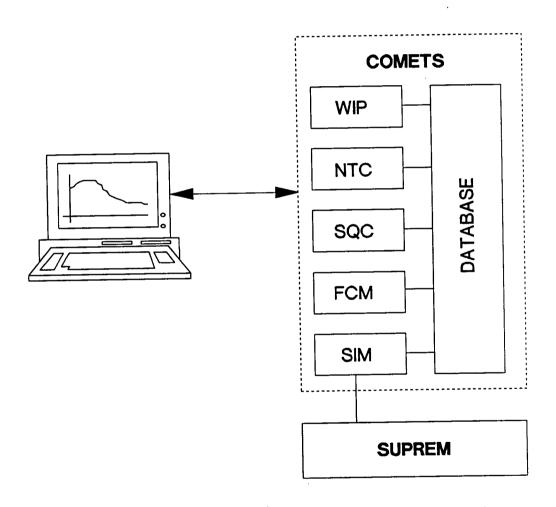

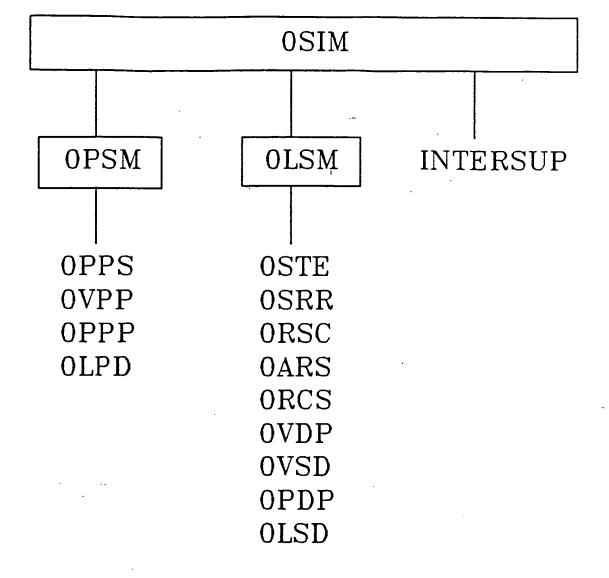

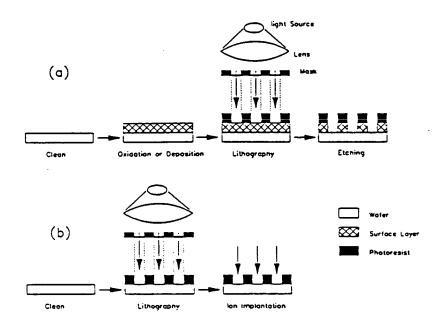

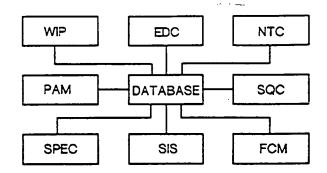

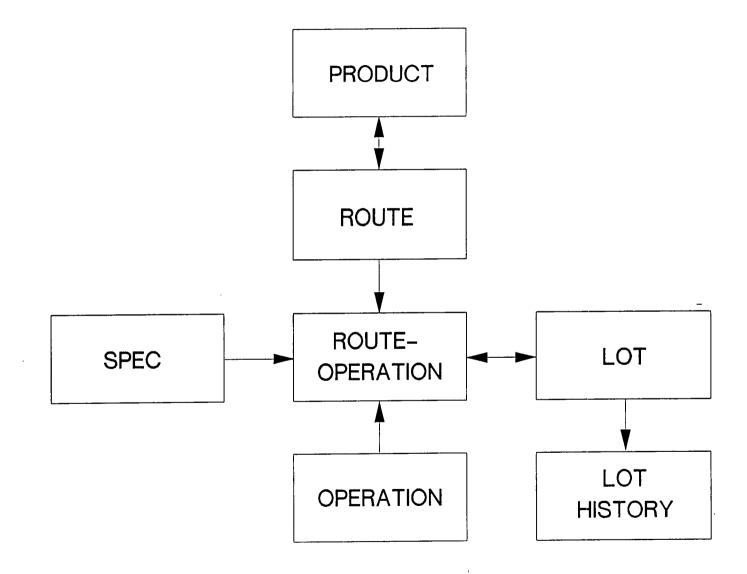

|                 | 3.3    | The COMETS CAM System                  | 49   |  |  |

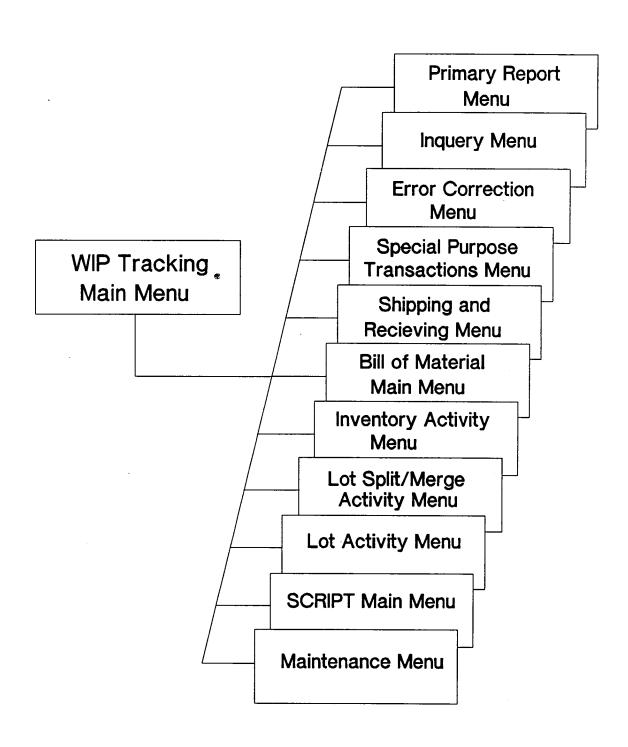

|                 |        | 3.3.1 WIP Tracking                     | 55   |  |  |

|                 |        | 3.3.2 Recipe Management                | 56   |  |  |

|                 |        | 3.3.3 Data Collection                  | 58   |  |  |

|                 |        | 3.3.4 Non-Lot Tracking                 | 58   |  |  |

|                 |        | 3.3.5 Process Automation               | 59   |  |  |

|                 | 3.4    |                                        | 60   |  |  |

|    | 3.5                          | Summary                                               | 62  |  |  |

|----|------------------------------|-------------------------------------------------------|-----|--|--|

|    |                              | References                                            | 63  |  |  |

| 4  | Process Simulation           |                                                       |     |  |  |

| •• | 4.1                          | Introduction                                          | 66  |  |  |

|    | 4.2                          | One-Dimensional Simulation                            | 67  |  |  |

|    | 1.2                          | 4.2.1 Oxidation                                       | 72  |  |  |

|    |                              | 4.2.2 Diffusion                                       | 73  |  |  |

|    |                              | 4.2.3 Ion Implantation                                | 74  |  |  |

|    |                              | 4.2.4 Deposition                                      | 75  |  |  |

|    |                              | 4.2.5 Etch                                            | 76  |  |  |

|    |                              | 4.2.6 Electrical                                      | 77  |  |  |

|    | 4.3                          | Two-Dimensional Simulation                            | 78  |  |  |

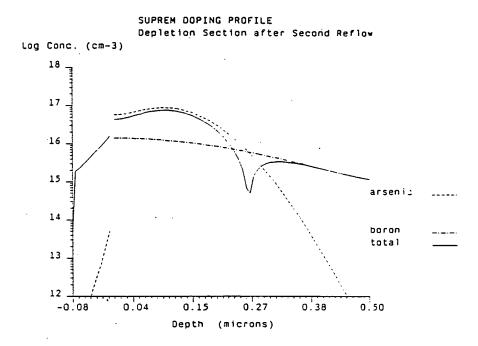

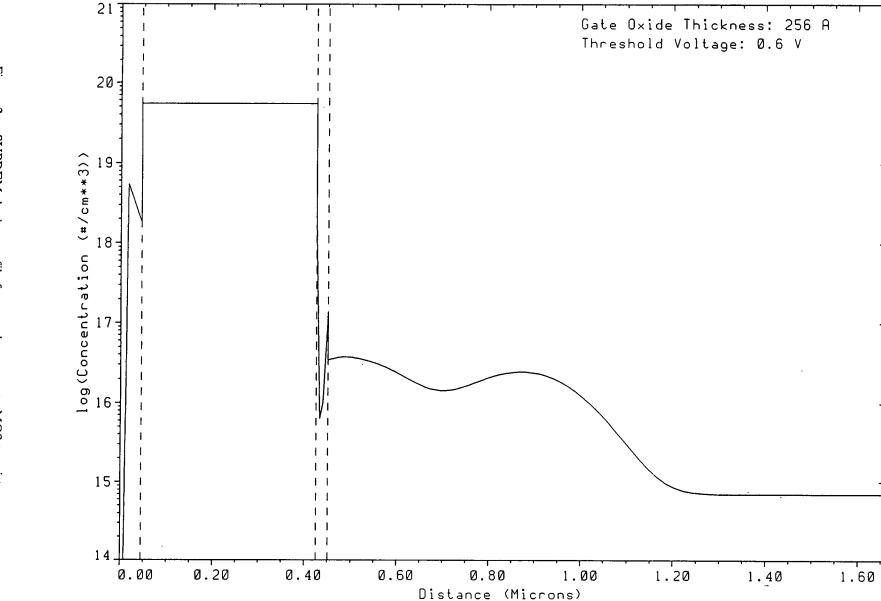

|    | 4.4                          | Simulating the EMF 1.5 µm nMOS Process                | 81  |  |  |

|    | 4.5                          | Summary                                               | 88  |  |  |

|    | 4.5                          | References                                            | 88  |  |  |

|    |                              | References                                            | 00  |  |  |

| 5. | Enh                          | ancing On-Line Analysis and Control of IC Fabrication | 95  |  |  |

|    | 5.1                          | Introduction                                          | 95  |  |  |

|    | 5.2                          | A New Method of Process Analysis                      | 95  |  |  |

|    | 5.3                          | Forming a Complete Process Definition                 | 104 |  |  |

|    | 5.3                          | Summary                                               | 111 |  |  |

|    |                              | References                                            | 111 |  |  |

| 6. | Inte                         | grating CAM and Process Simulation                    | 113 |  |  |

|    | 6.1                          | Introduction                                          | 113 |  |  |

|    | 6.2                          | Requirements and Constraints                          | 113 |  |  |

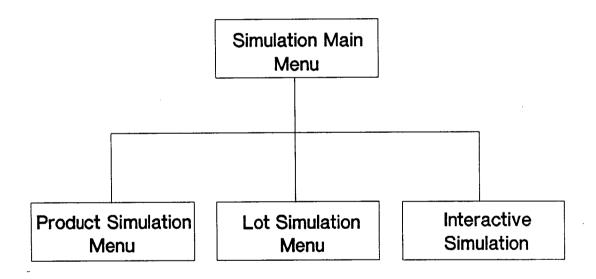

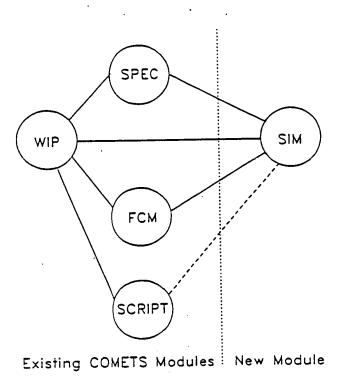

|    | 6.3                          | Developing the SIM Module                             | 115 |  |  |

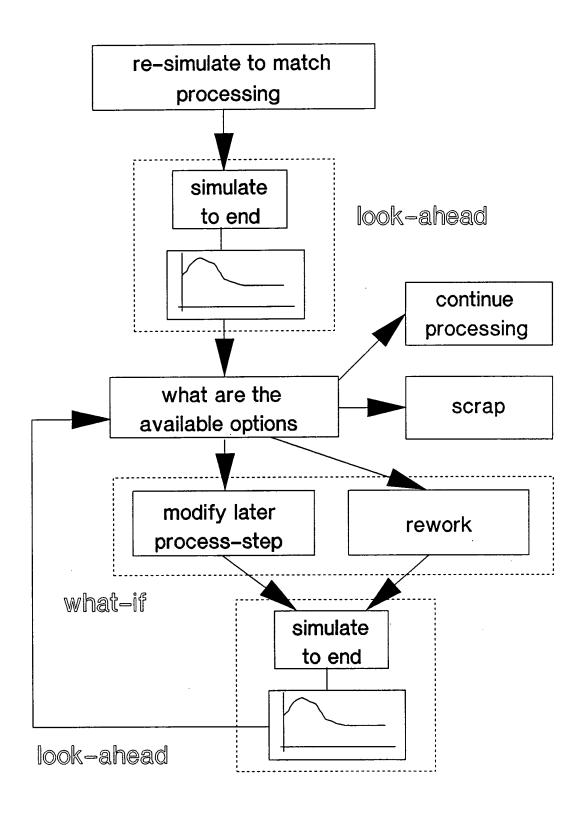

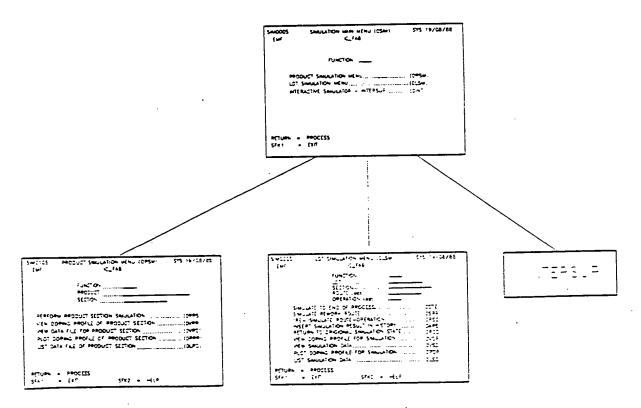

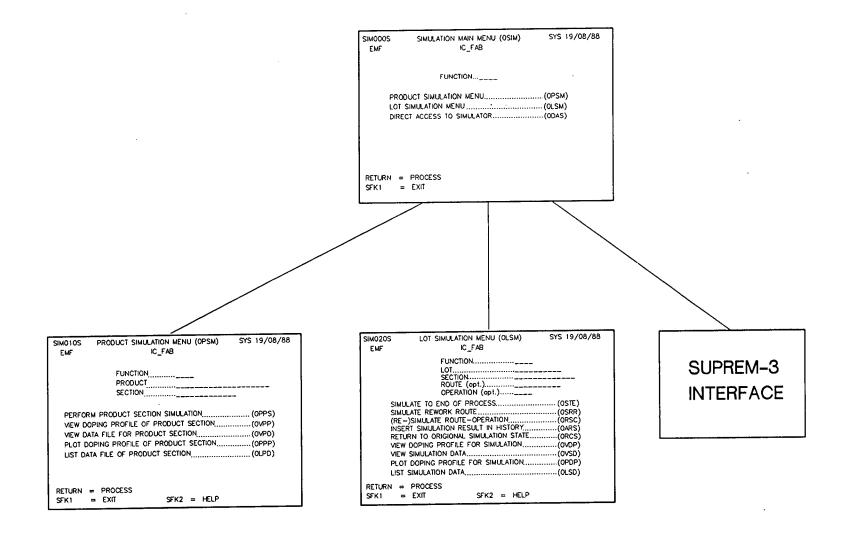

|    | 6.4                          | The SIM Menu Structure                                | 119 |  |  |

|    | 6.5                          | Further Developments                                  | 123 |  |  |

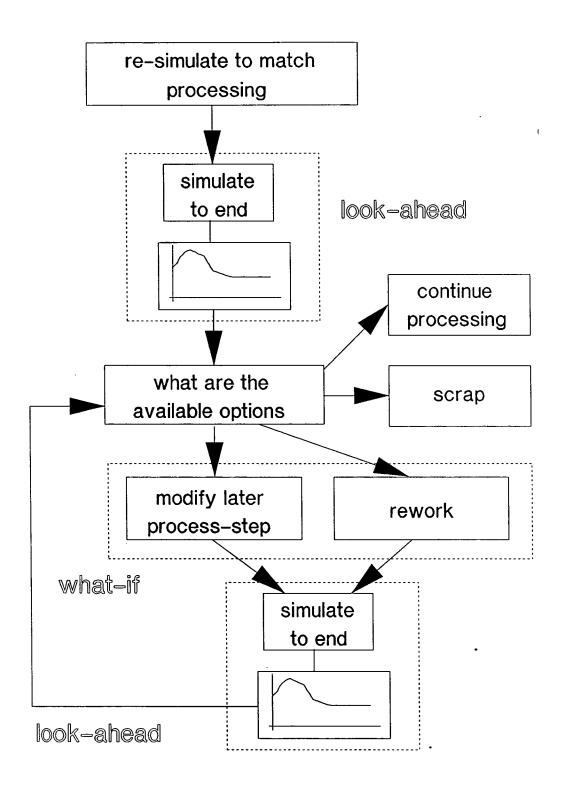

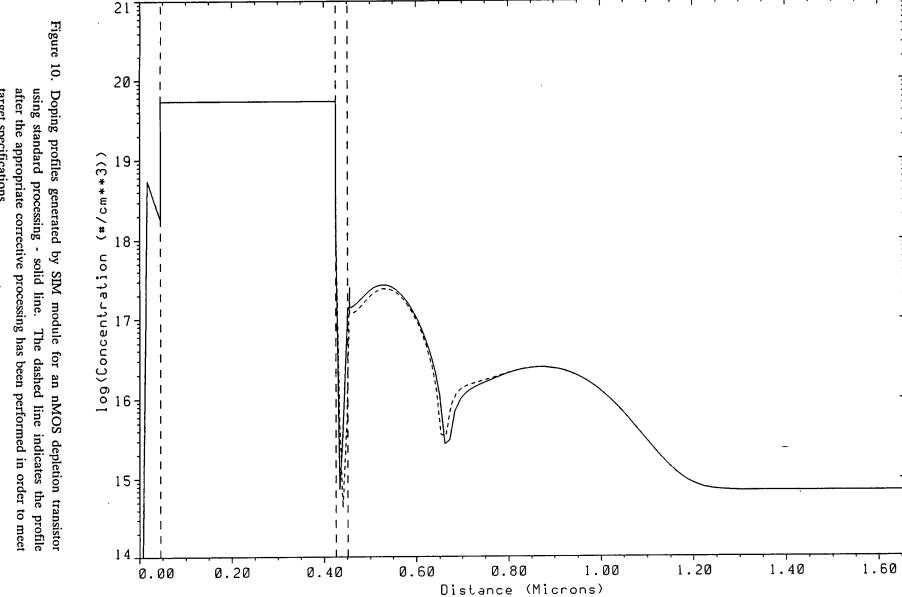

|    | 6.6                          | Applications and Results                              | 126 |  |  |

|    | 6.7                          | Summary                                               | 133 |  |  |

|    |                              | References                                            | 134 |  |  |

| 7. | 7. Recipe Management for CAM |                                                       |     |  |  |

|    | 7.1                          | Introduction                                          | 135 |  |  |

|    | 7.2                          | Specifying a Recipe Management System                 | 136 |  |  |

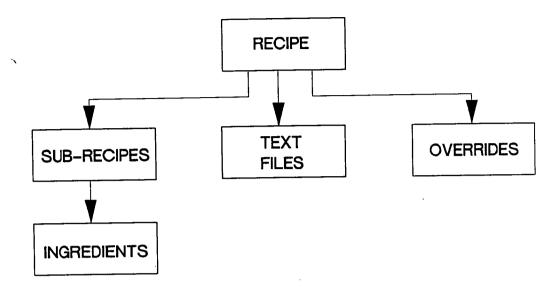

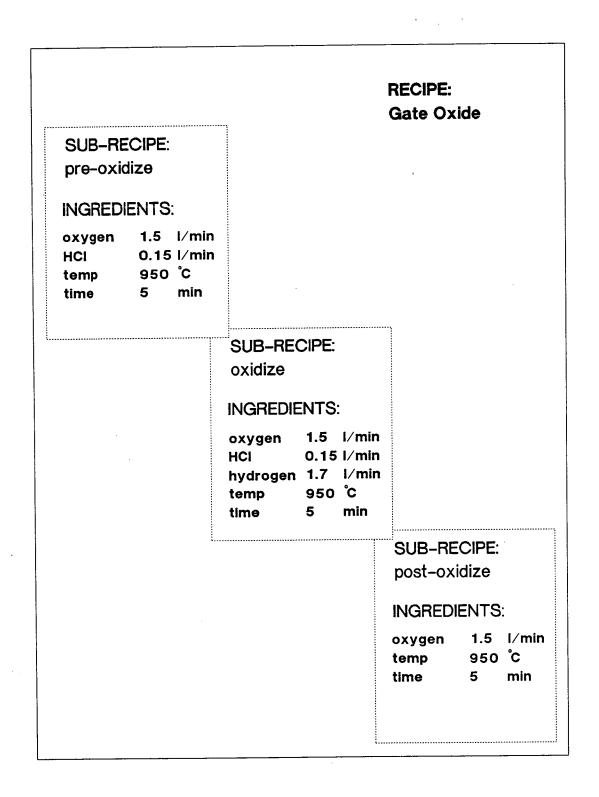

|    | 7.3                          | Recipe Data Structures                                | 140 |  |  |

|    | 7.4                          | On-line RCP                                           | 146 |  |  |

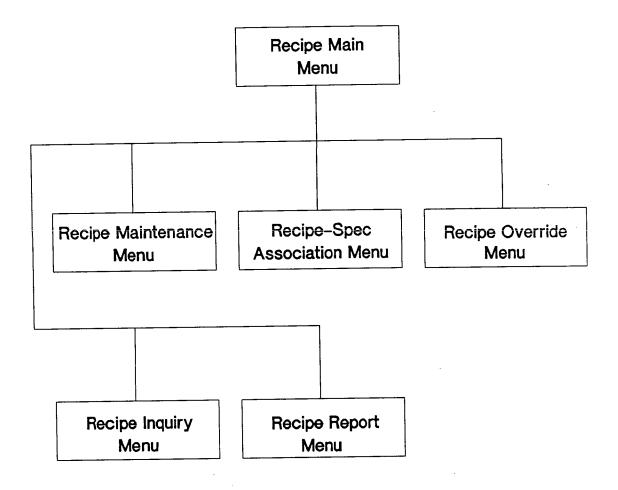

|    | 7.5                          | The RCP Menu Structures                               | 146 |  |  |

|    | 7.6                          | Performing Process Simulation using Process Recipes   | 152 |  |  |

|    | 7.7                          | Further Applications for Process Recipes              | 155 |  |  |

|    | 7.8                          | Summary                                               | 159 |  |  |

|    |                              | References                                            | 160 |  |  |

|    |                              |                                                       |     |  |  |

| 8. Conclusions                                              | 161 |

|-------------------------------------------------------------|-----|

| Appendix A: The EMF 1.5µm nMOS Process Runsheet             | 166 |

| Appendix B: nMOS Process ROUTES and OPERATIONS              | 182 |

| Appendix C: SUPREM-3 input files for the 1.5µm nMOS process | 188 |

| Appendix D: Data Definitions for COMETS Recipe Management   | 245 |

| Appendix E: Reprints of Published Papers                    | 261 |

•

## **Abstract**

The application of advanced manufacturing technology (AMT) to semiconductor manufacturing has made great improvements to the productivity and cost effectiveness of the industry. In particular, the application of computer aided manufacturing (CAM) to integrated circuit (IC) fabrication has helped to reduce costs, increase asset utilization and throughput, and improve yields. It is anticipated that market forces and technical constraints will bring about a more flexible approach to production that will depend heavily on manufacturing control systems. However, the current generation of CAM systems do not provide the level of analysis and control required by flexible manufacturing environments.

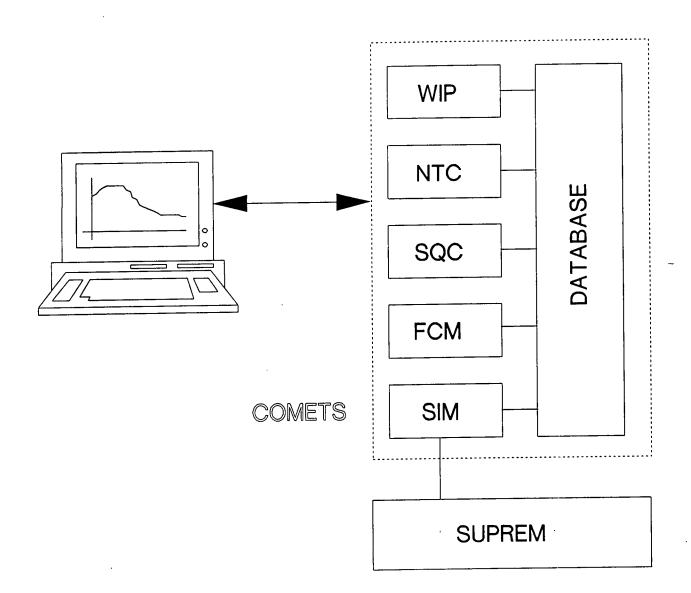

This Thesis introduces a method for integrating process simulation with a commercial CAM system to enhance the analysis and control of IC fabrication. A structured interface has been developed that will allow a process engineer to interactively use process simulation to verify past processing and estimate the effect of future operations. This results in a better understanding of the process within the manufacturing environment, the ability to analyse the fabrication sequence, and decision support for feed-forward control. The information used to control the simulations is held within the CAM system. The new system has been implemented using the CAM system COMETS and the process simulators SUPREM-II and SUPREM-3. It is believed that this is the first time that process simulation has been made available as a manufacturing tool.

To support the application of process simulation to manufacturing a specification control system has also been developed. This system adds recipe management to the COMETS CAM system by explicitly representing process information within its database. Apart from enhancing process analysis through process simulation, this system simplifies process maintenance, improves the integrity of process specifications, and allows effective on-line control of production.

In addition to these original contributions, this Thesis provides extensive reviews of fabrication specification and control, semiconductor CAM systems, and the application of process simulation to manufacturing processes.

## **Publications**

Publications by the author relevant to this work include:

- A.J. MacDonald, A.J. Walton, J.M. Robertson, *Integrating COMETS and Process Simulation*, COMETS International User Conference, Phoenix, Arizona, September 1988.

- A.J. MacDonald, A.J. Walton, J.M. Robertson, R.J. Holwill, Computer Aided Manufacturing in the Semiconductor Industry, Sunderland Advanced Manufacturing Technology Conference, Sunderland, UK, March 1989.

- A.J. MacDonald, A.J. Walton, J.M. Robertson, R.J. Holwill, *Integrating CAM and Process Simulation*, (invited paper), COMETS European User Conference, Hayes, UK, May/June 1989.

- A.J. MacDonald, A.J. Walton, J.M. Robertson, R.J. Holwill, Integrating Computer Aided Manufacturing and Process Simulation for the Production of ASICs, Microelectronics'89, Brisbane, Australia, July 1989.

- A.J. MacDonald, A.J. Walton, J.M. Robertson, R.J. Holwill, Integrating CAM and Process Simulation to Enhance On-Line Analysis and Control of IC Fabrication, To be published in IEEE Trans. on Semiconductor Manufacturing,

# Acknowledgments

I would like to thank all those who have contributed, wittingly or otherwise, to this Ph.D. The staff of the Edinburgh Microfabrication Facility have provided a tremendous source of knowledge on all aspects of wafer fabrication. However, I must acknowledge the particular efforts of my supervisors Dr. A.J. Walton and Prof. J.M. Robertson.

I am indebted to Mr. Alistair MacConnaill and Mrs. Jacqui James, of the Plessey CAM Group, for their practical advice on running and modifying the COMETS CAM system. The Plessey process engineers have also played an important role by suggesting real world applications for this project. Recognition must go to Consilium Inc. for providing the COMETS CAM system, and DEC for the supporting software and hardware.

Financial sponsorship of this project came from the Science and Engineering Research Council, and, in the form of a CASE award, from Plessey (née Ferranti) Semiconductors.

## Chapter 1

## Introduction

Over the last twenty years the semiconductor industry has come to play a major role in the world economy. Not only are integrated circuits (ICs) an internationally saleable commodity in themselves, but they also influence the market for many other products, such as computer and audio equipment. In turn the market for these products effects the value of ICs, often resulting in cyclical variations in demand. The major players in the production of ICs are the United States, Japan and Europe. These factors cause IC manufacture to be regarded as a strategic industry, which has led to the international market being distorted by political intervention. However, despite these influences companies are very aware of the need to remain competitive on price and quality and so share a common goal of achieving world-class manufacturing.

IC manufacture requires a tremendously high capital investment before production can begin [1], and yet more capital becomes tied up in the value of the work-in-progress once production is underway. The result is that it is essential to make the most efficient use of both time and equipment. Such economic constraints are paralleled by technical constraints. ICs are required to meet specifications which are at the edge of processing limits, and the task is complicated by the need to fabricate ever smaller features on increasingly large wafers.

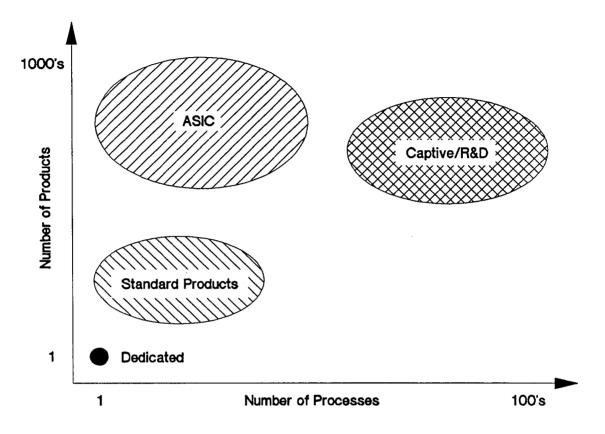

In response to the economic and technical constraints on IC manufacturing, the industry has largely polarised into commodity and application specific production. Figure 1.1 shows the spectrum of fabrication lines which exist to meet the needs of the market. Commodity-style manufacture seeks to achieve the lowest possible cost per unit and so tends towards producing high volumes of only a few products. For example, the fabrication of memory and microprocessor circuits in standard product or dedicated production facilities. Application specific-style manufacture aims for the more specialised end of the market where products can command higher selling prices. A consequence of this is that more products are made in lower volumes and so the facilities must be flexible enough to

make changes in product-mix very quickly. The range of production facilities that perform flexible manufacturing include application specific IC (ASIC), research and development, captive, and some standard product facilities.

Figure 1.1 The wafer fabrication line spectrum, after [1].

The search for more efficient production, and thence world-class manufacturing, has led companies from all sectors of the IC industry to begin adopting advanced manufacturing technology (AMT). This includes automated material flow, integrating computer systems, factory simulation, statistical quality control, and expert systems. The most widely applied technology, however, is computer aided manufacture (CAM). CAM systems provide tools to perform tracking of work-in-progress, planning of production, collection of engineering data and report generation. Where implemented they are reported to have improved cycle times, equipment utilization and yield [2].

#### 1.1. IC Manufacture

Integrated circuits are fabricated on wafers of semiconducting material, normally silicon, which are then cut-up into die, or chips, before being packaged and subjected to functional testing. Though only a simple outline, this description serves to highlight the major areas of IC manufacture. AMT has been applied, to some extent, in each of these areas but with the greatest effort being made in wafer fabrication. This is largely because during fabrication there is the greatest increase in the value of the products being manufactured.

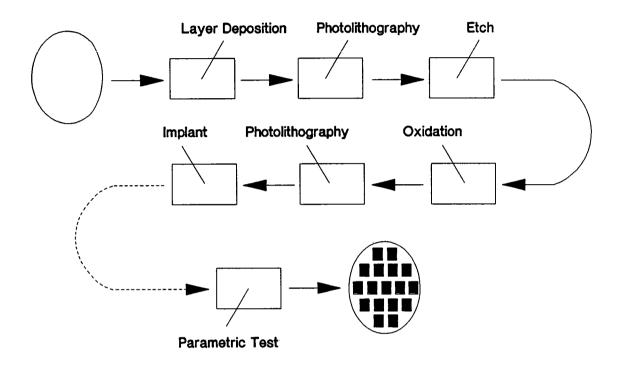

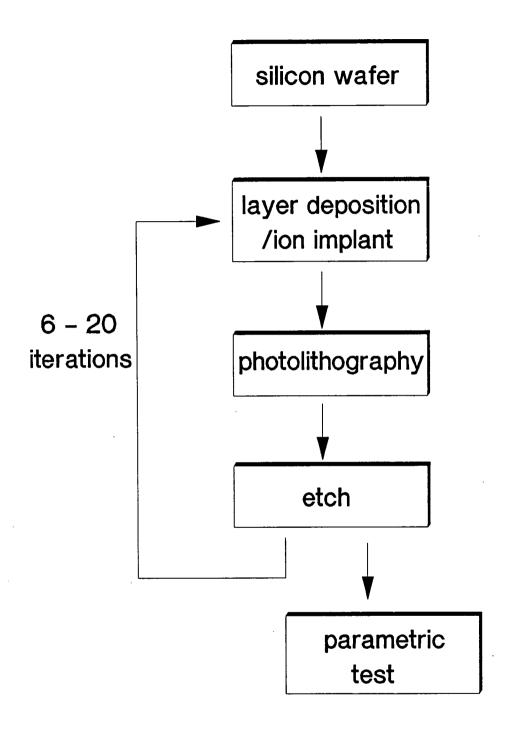

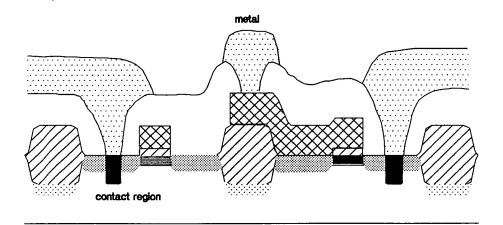

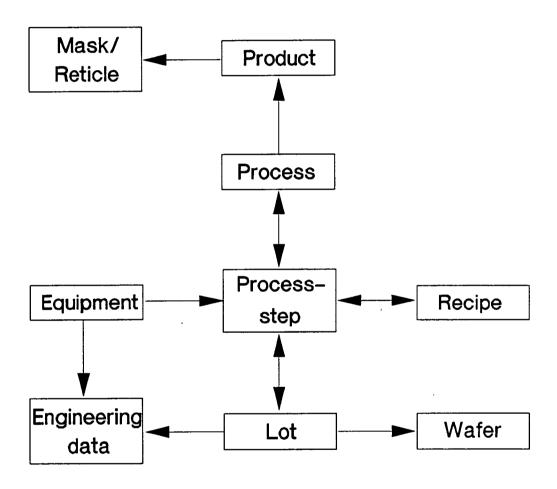

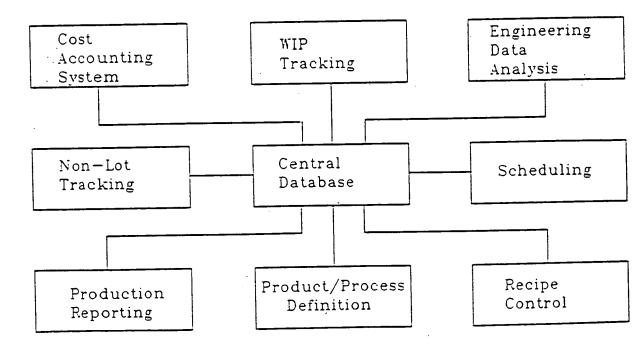

Figure 1.2 An MOS IC fabrication sequence.

A wafer fabrication process consists of many hundreds of individual steps. These are performed on batches of wafers which pass serially between the process steps; there being no sub-assemblies in wafer fabrication. As is apparent from figure 1.2 a process consists of a set of steps, many of which are repeated throughout the fabrication sequence. After certain process steps, measurements are made to verify part of the previous processing. Only a limited number of these tests can be made without damaging the wafers and so few test are performed in-line on product wafers. Consequently it is not known until the end of the process whether the devices being fabricated will have the desired electrical parameters. The yield of the process is dependent on both the control parameters for each operation, and the accuracy of the process equipment. The ensuing causal relationships are extremely complex. Achieving a satisfactory yield is further complicated by the fact that both the

operating ranges of the processing equipment, and the device geometries are approaching the physical limits of technology.

The goal of every manufacturing facility is to make the right products at the right time for the right cost [3]. As suggested earlier, the production methodologies used to achieve this objective range from commodity to application specific manufacture. Historically the dominant production philosophy has been stable commodity-style manufacture, but this is giving way to more flexible approaches to manufacturing [4]. This can be regarded as the movement from load-oriented systems, where product is 'pushed' through the line, to process-oriented systems, where market demand 'pulls' product through the line [5].

Commodity production is normally characterised by having a high volume throughput on a single process with large batch sizes and very few products. The goal is to achieve minimum time per operation with maximum output per unit of time, although this does result in long set-up times. Application specific production, in contrast, tends to have smaller batch sizes with many products each being fabricated in a comparatively low volume. There is also the potential for many processes being run at one time. Application specific manufacture generally seeks to achieve minimum time per order, maximum utilization of facilities per time period, and set-up times close to zero. Though the terms 'commodity' and 'application specific' are useful for characterizing fabrication facilities, instances do exist of facilities that have some of the characteristics of both types of manufacture. For example, a nominally ASIC gate array production facility can be based on very high volume with only a single product until just prior to metallization. After this the single product can become many hundreds of different products, each being fabricated in very low volume.

## 1.2. Advanced Manufacturing Technology

The objective of introducing advanced manufacturing technology (AMT) into IC production is to increase profitability. Therefore any new addition to the existing manufacturing tools could be described as AMT. However, the technologies that have received the most attention over the last few years have been factory automation and computer integrated manufacturing (CIM).

Factory automation is a broad term that has been used to describe the automation of processing equipment, the mechanization of the wafer transfer and handling equipment, and the computer networks required to track, control and distribute information around

an automated environment [6]. There have been many discussions on the use of robots, track systems and automated guided vehicles (AGV) [6,7,8,9,10,11] to achieve material transfer for semiconductor manufacturing. Automation is driven by technological needs: smaller device geometries; increasing wafer sizes; and cleaner fabrication environments [12].

However, there are very few cases of automated wafer transfer systems, perhaps because these systems will not fit into existing clean-rooms. Where factory automation has been implemented it has been either as full mechanization, or as more flexible *islands-of-automation*. Mechanization of wafer fabrication is an inflexible approach where machines are hard-wired together and wafer transport between processing stations is by fixed track systems. These systems are best suited for producing high volumes of only a few products on a single process; that is, commodity production. As a result they offer better turn-around-times, and improvements in process and defect control [3]. This approach to manufacturing has been favoured by the Japanese in the semiconductor and other industries [13]. Although normally there is very little published on Japanese methods of IC manufacture, the level of automation achieved by the company NMB has been well documented [9,14,15] and similar work by Mitsubishi has also been reported [16]. Published research in the USA, into fully mechanised systems, includes the automated IC packaging system Odyssey from National Semiconductor [7].

The idea of a 'clean-box' rather than a 'clean-room' has been employed with some success to reduce particle counts, and thereby defects, in automated environments [8, 17, 18, 19, 20]. The semiconductor manufacturing interface (SMIF) box is used to transfer wafers between pieces of automated processing equipment, thus reducing the amount of contact between operators and wafers.

As with many other industries, flexible manufacturing systems (FMS) have emerged as a manufacturing methodology that is capable of reacting quickly to the demands of the market. An FMS consists of equipment grouped into cells with control of equipment and material flow being performed by a distributed computer system [21]. Automated cells, or islands-of-automation, are of considerable individual value but may introduce problems because of the lack of communication between them [22]. Cells may be classed as either functional or sequential [23]. In a functional cell, the processing equipment runs the same type of process, such as dry etching. Equipment inside a sequential cell performs a logical sequence of process steps, for example, a photolithography sequence. A number of cell

implementations have been reported [3, 24, 25, 26].

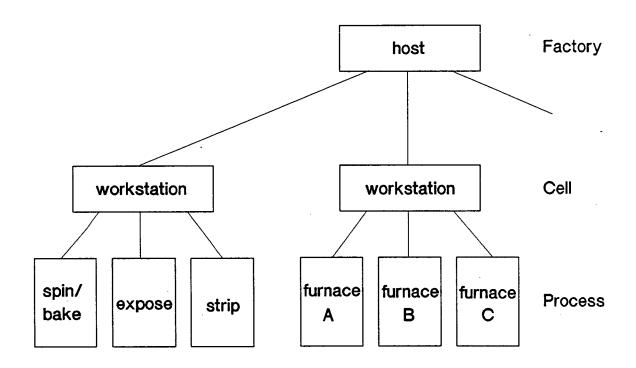

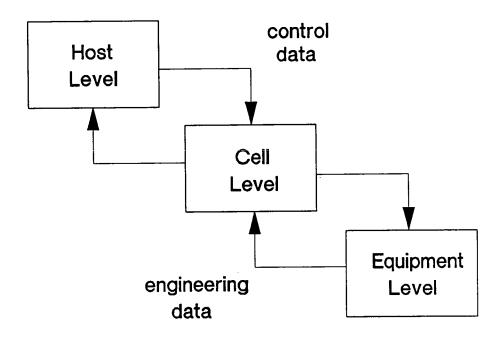

Various control hierarchies have been suggested for implementing automated IC fabrication [27, 28], these can be generalised to the form shown in figure 1.3. Such hierarchies are used in both commodity and application specific manufacturing environments as the levels of the hierarchy correspond to levels of management control rather than the distributed nature of wafer processing.

Figure 1.3 Generalised manufacturing control hierarchy

At the most basic level of figure 1.3 are dedicated microprocessors performing the real-time control of the processing equipment. They apply the control parameters to the equipment and collect raw data to be passed to the next level in the hierarchy. In many cases equipment controllers are being shipped with the processing equipment. The next level is that of the cell, which physically might be a workstation, performing a certain amount of data reduction and downloading recipes to equipment controllers. Further capabilities might be included at this level; including process monitoring and feedback control based on sensory data, scheduling, and expert systems. Information from the cell computer is then passed up to the host system. The host is normally a larger computer with extensive data storage capabilities, and supports a comprehensive computer aided

manufacturing (CAM) system [29, 30, 31, 32, 33]. These systems perform the overall work-in-progress tracking, capacity planning, scheduling of the movement of work between cells, and assorted data analysis functions. Though the hierarchy of systems has been described here as physically distributed over different computers, they could potentially all be implemented on one computer, assuming that it is capable of handling the data transactions within an acceptable amount of time.

The equipment to computer interfaces for semiconductor manufacturing play an important role in factory automation, for data collection and remote control. This has resulted in the development of the SEMI Equipment Communications Standard (SECS) [34]. The standard has been developed in two parts. SECS-II defines a set of data and messages types for communication between a host computer and semiconductor processing equipment. SECS-I describes the procedure to block these messages and transfer them to processing equipment. In time it is anticipated that these basic standards will be developed further [35,36]. Currently SECS is peculiar to the semiconductor industry, a review of other communications standards is given in [37].

The use of computers in this environment to integrate the control of processes, product handling, and information flow can lead to higher levels of process control, repeatability and equipment utilization; this is often referred to as computer integrated manufacturing (CIM) [3]. In the same way as automation is driven by technology concerns, CIM is driven by production concerns: better plant utilization; increased ability to manage complexity in a mixed processing environment; cost reductions; and improved customer satisfaction [38]. However, CIM is seen as more than simply advanced computerised manufacturing. CIM can also include computer aided design (CAD), CAM and management information systems (MIS) [5,25,37,38,39,40,41,42]. Thus a CIM system can allow data to be shared freely throughout a company.

The availability of information characterizing the shop-floor has encouraged the application of new management philosophies such as just-in-time (JIT) [43, 44]. For a review of production scheduling methodologies, including manufacturing resource planning (MRP) and JIT, see [45].

Although complete CIM is yet to be achieved, the spread of manufacturing control systems has led to the availability of previously unattainable data. Consequently many tools are being applied to the analysis of data in order to aid decision making.

Simulation tools have been developed to analyse the operation of semiconductor manufacturing facilities [46, 47, 48, 49]. These simulation techniques have led to enhancements in capacity planning, equipment maintenance management, production scheduling, the forecasting of product delivery, and resource requirements scheduling [50, 51, 52, 53].

Statistical process control (SPC) has recently emerged as a method of analysing the vast amounts of data which can be collected in an IC manufacturing facility [54, 55, 56, 57, 58, 59, 60]. In addition, expert systems have been investigated as a method for aiding decision making in the complex fabrication environment [61, 62, 63, 64].

#### 1.3. Motivation

This Ph.D. originally set out to investigate the application of CAM to IC fabrication. The motivation for this lay in the need to develop CAM systems that could meet the combined challenges of flexible manufacturing and increasingly complex processing. It became apparent during this investigation that there are very few tools available to enhancemanufacturing productivity. Therefore, particular emphasis has been given to considering what aids are required for the analysis and control of semiconductor processes.

Currently available tools, such as SPC, can be used for production analysis but provide no insight into how a process works. In order to understand a process it is necessary to model it. Process simulation is a method that can be used to explore the physical effects of process steps and their interaction in a complete process. This Thesis shows how process simulation can be integrated with CAM to perform process analysis and feed-forward control.

In implementing this system it was noted that the current generation of CAM systems do not provide an explicit description of processing. Therefore, this Thesis also demonstrates how specification control, or recipe management, can be implemented as part of a flexible manufacturing control system.

#### 1.4. Structure of Thesis

This chapter has presented a broad background to the application of computer aided manufacturing for the production of ICs. However, to fully appreciate the rationale behind the use of process simulation for the analysis and control of IC fabrication a more detailed discussion of the control of IC fabrication is presented in chapter 2. Chapter 3 presents the current state of CAM systems for the semiconductor industry and describes the implementation of the commercial system COMETS. A brief review of process

simulation is presented in chapter 4 along with examples of how both one- and twodimensional simulators can be calibrated to a manufacturing process. In chapter 5 these strands of information are brought together to describe the fundamental concepts of this Ph.D. and its contribution to the field of CAM for the production of ICs. Chapters 6 and 7 describe in detail the original work carried out as part of this Ph.D.: the integration of process simulation and CAM is described in chapter 6; and chapter 7 presents a new method for fully describing the manufacturing sequence using process recipes. Finally some conclusions are drawn on the work presented within this Thesis and some suggestion for further work are outlined.

#### References

- W.C. Holton, J. Dussault, D.A. Hodges, C.L. Liu, J.D. Plummer, D.E. Thomas, and P.F. Wu, Computer Integrated Manufacturing (CIM) and Computer Assisted Design (CAD) for the Semiconductor Industry in Japan, Japanese Technology Evaluation Program, National Science Foundation, Washington DC, USA, December 1988.

- 2. A. MacConnaill, "Experience with a Computerised Production Control System within the Semiconductor Industry," STEP/Europe, pp. 36-46, Edinburgh, UK, October 1986.

- 3. D.J. Miller and J.A. Fenimore, "The Application of Advanced Manufacturing Technology in Semiconductor Fabrication," *IEEE/CHMT Int. Electronics Manufacturing Technology Symposium*, Orlando, Florida, USA, 1988.

- 4. K. Shankar, "DRAMs and ASICs as Technology Drivers," *Solid State Technology*, pp. 51-52, Dataquest, September 1989.

- 5. W. Gutschke and K. Mertins, "CIM: Competitive Edge in Manufacturing," Robotics & Computer-Integrated Manufacturing, vol. 3, no. 1, pp. 77-87, 1987.

- 6. Y. Iwasawa and K. Yamamoto, "Development of an Automatic Wafer Transport System in the Semiconductor Industry," *Proc. 8th. Int. Conf. Automation in Warehousing*, pp. 271-282, Tokyo, Japan, October 1987.

- 7. H.E. Lehrheuer, "National Semiconductor's Odyssey A New Way of Manufacturing," Microelectronic Manufacturing and Testing, pp. 10-11, January 1988.

- 8. P.H. Singer, "Automating Inter-Equipment Transport," Semiconductor International,

- pp. 56-61, March 1985.

- 9. C. Murray, "Planning for Inter-Equipment Transport Automation," Semiconductor International, pp. 74-78, September 1986.

- 10. C.R. Deninger, "Specifying a Factory Automation System," Microelectronic Manufacturing and Testing, pp. 13-16, January 1986.

- 11. A. Chestnut, P.H. Singer, and K. Kearney, "Robotic Systems Enhance Manufacturing Efficiency," *Semiconductor International*, October 1988.

- 12. R.C. Dehmel and G.H. Parker, "Future VLSI Manufacturing Environment," Solid State Technology, pp. 115-121, May 1987.

- 13. R.J. Schonberger, Japanese Manufacturing Techniques, Collier Macmillan, 1982.

- 14. S. Shinoda, "Total Automation in Wafer Fabrication," *Semiconductor International*, pp. 86-88, September 1986.

- 15. L. Kehoe, "Where cleanliness is next to good chip yields," Financial Times, p. 20, Wednesday 14th December 1988.

- M.D. Arch, N. Chandler, A.J. Walton, T. Gordon, C. Hughes, and N.R. Stockham, "Automation and Quality Control," Electronic Packaging in Japan, pp. 130-149, The Welding Institute, Cambridge, UK, November 1987.

- 17. M. Parikh and A. Bonora, "SMIF Technology Reduces Clean Room Requirements," Semiconductor International, May 1985.

- 18. H. Harada and Y. Susuki, "SMIF System Performance at 0.22μm Particle Size," Solid State Technology, December 1986.

- 19. M. Parikh, R. Fried, and A. Bonora, "Assessing the Effectiveness of an Integrated SMIF System," *Microcontamination*, January 1986.

- G. Ortiz, "An Overview of Automated SMIF Facilities," 3rd Symposium on Automated IC Manufacturing, pp. 440-453, The Electrochemical Society, Honolulu, HI, USA, October 1987.

- 21. P.G. Ranky, *The Design and Operation of FMS*, IFS (Publications) Ltd., North Holland, 1983.

- 22. P.J. Russell, "Open Systems Architecture for CIM," Factory 2000, pp. 57-66, Cambridge, UK, September 1988.

- 23. E. Herrmann, "Standardization of Work Cell Software in a Hierarchical CAM System for VLSI Manufacturing," *Proc. of the 3rd Symposium on Automated Integrated Circuit Manufacturing*, pp. 385-397, The Electrochemical Society, Honolulu, HI, USA, October 1987.

- 24. E.C. Hume, R.P. Mueller, H. Schlick, and J. Conway, "Automated Cells for Submicron Lithography," 3rd Symposium on Automated IC Manufacturing, pp. 255-261, The Electrochemical Society, Honolulu, HI, USA, October 1987.

- 25. N. Hutchinson, "CIM, Electronics Manufacturing...and ATE," *IEEE International Test Conference*, Washington DC, USA, September 1988.

- T. Torii and Y. Yamamoto, "Shop Floor Control in Computer-Integrated Manufacturing for Large-Scale Integrated Wafer Fabrication Systems," Robotics & Computer-Integrated Manufacturing, vol. 3, no. 4, pp. 423-428, 1987.

- 27. R.A. Hughes and J.D. Shott, "The Future of Automation for High-Volume Wafer Fabrication and ASIC Manufacturing," *Proc. of the IEEE*, vol. 74, no. 12, pp. 1775-1793, December 1986.

- 28. C.R. McLean and P.F. Brown, "The Architecture of the NBS Factory Automation Research Testbed," 10th World Congress on Automated Control, vol. 4, pp. 141-146, Munich, FDR, July 1987.

- 29. P. Burggraaf, "CAM Software Part 1: Choices and Capabilities," Semiconductor International, pp. 56-61, June 1987.

- 30. P. Burggraaf, "CAM Software Part 2: Implementation and Expectations," Semiconductor International, pp. 63-65, July 1987.

- 31. W.A. Bosenberg, "A 'Structured' Approach to CAM," Semiconductor International, pp. 62-68, June 1987.

- 32. H.A. Watts, "CAM: Lot Tracking and More," Semiconductor International, pp. 66-68, July 1987.

- 33. P. Burggraaf, "CAM Software: It's Getting Better," Semiconductor International, May 1989.

- 34. "SEMI Equipment Communications Standard (SECS I & II)," in *Book of SEMI Standards*, vol. 2, Semiconductor Equipment and Materials Institute, Mountain View, CA, USA, 1987.

- 35. M.G. Middents, "Equipment Interfacing, Methods and Practice," *Proc. of the 3rd Symposium on Automated Integrated Circuit Manufacturing*, pp. 241-254, The Electrochemical Society, Honolulu, HI, 1987, October 1987.

- 36. SEMI SITF Generic Equipment Model for SECS Communications, Semiconductor Equipment and Materials International, Mountain View, CA, USA, December 1988.

Draft Version 1.7

- 37. R.H. Weston, J.D. Gascoine, A. Rui, A. Hodgson, C.M. Sumpter, and I. Coutts, "Steps Towards Information Integration in Manufacturing," *Int. J. Computer Integrated Manufacturing*, vol. 1, no. 3, pp. 140-153, 1988.

- 38. M.S. Ligeti, "Meeting the CIM Challenge in Semiconductor Manufacturing (Part 1)," Microelectronic Manufacturing and Testing, p. 11, June 1987.

- 39. M.S. Ligeti, "Meeting the CIM Challenge in Semiconductor Manufacturing (Part 2)," Microelectronic Manufacturing and Testing, pp. 11-12, July 1987.

- 40. G. Barbuscia and R. Traversini, "Process Integration Concept," *Microelectronics Engineering*, vol. 6, no. 1-4, pp. 3-13, 1987.

- 41. P. Ranky, "A Comparative Analysis of Tool Management System Architectures Designed for Flexible Machining and Assembly (FMS/FAS) Systems in CIM Environment," *IEEE 1988 Computer Integrated Manufacturing Conference*, pp. 36-43, Troy, NY, USA, May 1988.

- 42. A. Hultquist and G. Leighton, "How to Select and Implement a CIM Strategy," Proc. of the 3rd Symposium on Automated Integrated Circuit Manufacturing, pp. 408-417. The Electrochemical Society, Honolulu, HI, USA, October 1987.

- 43. L. Cory, "Just-In-Time Approach to IC Fabrication," Solid State Technology, pp. 177-179, May 1986.

- 44. L.A. Martin-Vega, M. Pippin, E. Gerdon, and R. Burcham, "Applying Just-In-Time in a Wafer Fab: A Case Study," *IEEE Trans. on Semiconductor Manufacturing*, vol. 2, no. 1, pp. 16-22, February 1989.

- 45. F.A. Rodammer and K.P. White, "A Recent Survey of Production Scheduling," *IEEE Trans. on Systems, Man, and Cybernetics*, vol. 18, no. 6, pp. 841-851, November/December 1988.

- 46. J.E. Dayhoff and R.W. Atherton, "Simulation of VLSI Manufacturing Areas," VLSI Design, pp. 84-91, December 1984.

- 47. D.Y. Burman, F.J. Gurrola-Gal, A. Nozari, S. Sathaye, and J.P. Sitarik, "Performance Analysis Techniques for IC Manufacturing Lines," AT & T Technical Journal, vol. 65, no. 4, pp. 46-57, July/August 1986.

- 48. J.E. Dayhoff and R.W. Atherton, "A Model for Wafer Fabrication Dynamics in Integrated Circuit Manufacturing," *IEEE Trans. on Systems, Man and Cybernetics*, vol. SMC-17, no. 1, pp. 91-100, January/February 1987.

- 49. S.T. Wang, "Animated Simulation of a Flexible Manufacturing System," Proc. of the 1986 Winter Simulation Conference, Orlando, Florida, USA, 1986.

- 50. A. Edwards, D. Felix, R. Holvey, R. Poulsen, and V. Sutcliffe, "A Versatile Simulator/Scheduler for Silicon IC Manufacture," *Third Symposium on Automated Integrated Circuits Manufacturing*, pp. 322-332, The Electrochemical Society, Honolulu, HI, USA, October 1987.

- 51. R.W. Atherton, "Factory Scheduling using Simulation Models," *Third Symposium on Automated Integrated Circuits Manufacturing*, pp. 333-339, The Electrochemical Society, Honolulu, HI, USA, October 1987.

- 52. L.M. Wein, "Scheduling Semiconductor Wafer Fabrication," IEEE Trans. on Semiconductor Manufacturing, vol. 1, no. 3, pp. 115-130, August 1988.

- 53. C.R. Glassey and M.G.C. Resende, "Closed-Loop Job Release Control for VLSI Circuit Manufacturing," *IEEE Trans. on Semiconductor Manufacturing*, vol. 1, no. 1, pp. 36-46, February 1988.

- 54. P.K. Mozumder, C.R. Shyamsundar, and A.J. Strojwas, "Statistical Control of VLSI Fabrication Processes," *American Control Conference*, Mineapolis, USA, June 1987.

- M.S. Phadke, R.N. Kackar, D.V. Speeney, and M.J. Grieco, "Off-Line Quality Control in Integrated Circuit Fabrication Using Experimental Design," The Bell Systems Technical Journal, pp. 1273-1309, May-June 1983.

- 56. M.A. Styblinski and L.J. Opalski, "Algorithms and Software Tools for IC Yield Optimization Based on Fundamental Fabrication Parameters," *IEEE Trans. on Computer-Aided Design*, vol. CAD-5, no. 1, pp. 79-89, January 1986.

- 57. L.B. Pritchard, "Statistical Process Control in Photolithography," Semiconductor International, pp. 164-167, May 1987.

- 58. P.K. Mozumder, C.R. Shyamsundar, and A.J. Strojwas, "Statistical Control of VLSI Fabrication Processes: A Framework," *IEEE Trans. on Semiconductor Manufacturing*, vol. 1, no. 2, pp. 62-71, May 1988.

- 59. C.R. Shyamsundar, P.K. Mozumder, and A.J. Strojwas, "Statistical Control of VLSI Fabrication Processes: A Software System," *IEEE Trans. on Semiconductor Manufacturing*, vol. 1, no. 2, pp. 72-82, May 1988.

- 60. K.M. Kearney, "SPC: Using Predictability to Conquer Variability," Semiconductor International, May 1989.

- 61. J.Y. Pan and J.M. Tenenbaum, "PIES: An Engineer's Do-It-Yourself Knowledge System for Interpretation of Parametric Test Data," *Proc. AAAI-86*, vol. 2, pp. 836-843, Philadelphia, USA, August 1986.

- 62. M.C. Murphy Hoye, "Artificial Intelligence in Semiconductor Manufacturing for Process Development, Functional Diagnostics, and Yield Crash Prevention," *IEEE International Test Conference*, Washington DC, 1986.

- 63. N.H. Chang, K.K. Lin, C.Y. Fu, and D.A. Hodges, "BIPS Application for LPCVD Polysilicon," *TI Technical Journal*, pp. 30-38, Winter 1987.

- 64. J.Y. Pan, J.M. Tenenbaum, and J. Glicksman, "A Framework for Knowledge Based Computer Integrated Manufacturing," *IEEE Trans. on Semiconductor Manufacturing*, vol. 2, no. 2, pp. 33-46, May 1989.

# Chapter 2

# Specifying and Controlling IC Fabrication

#### 2.1. Introduction

Since the development of the first integrated circuit (IC) by Kilby [1] in 1958 a massive industry has developed around producing ever faster and more functional ICs at lower cost. As the intricacy of these products has evolved so too has the complexity of the processes required to manufacture them. In response to this the semiconductor industry has polarized into commodity manufacturers producing standard products in high volume, eg. memory and microprocessors, and application specific integrated circuit (ASIC) manufacturers satisfying the demand for custom products in lower volumes. This has resulted in the availability of a wide range of production technologies and materials. Despite this the majority of ICs are still fabricated on silicon. Therefore in this chapter we will restrict our discussion of IC processing to silicon based technologies.

The manufacture of ICs is performed in a number of stages. During the first stage the wafers upon which the ICs are fabricated are sliced from specially grown single crystals of silicon. Current wafer diameters vary from three to circa eight inches in diameter, with some advanced fabrication facilities using even larger wafers. The second stage is wafer fabrication where each layer of the circuit design is applied to sites on the wafer surface. The whole fabrication process can take anything from three to ten weeks to complete, the cycle time being very dependent upon the layout and scheduling of the individual facility. Following from wafer fabrication is assembly where the circuits on the wafers are cut into separate die, or chips, and then packaged to form the saleable product. Finally, functional testing is performed to check that the packaged circuits will perform as designed and within specification.

When attempting to maximise the productivity of IC manufacturing emphasis must be placed on wafer fabrication. This is because, for most processing scenarios, wafer fabrication has the greatest impact on the cost per unit of the final product; which is evident when one considers that a raw wafer may only cost a few tens of dollars while the fully

processed wafer can be worth many thousands of dollars.

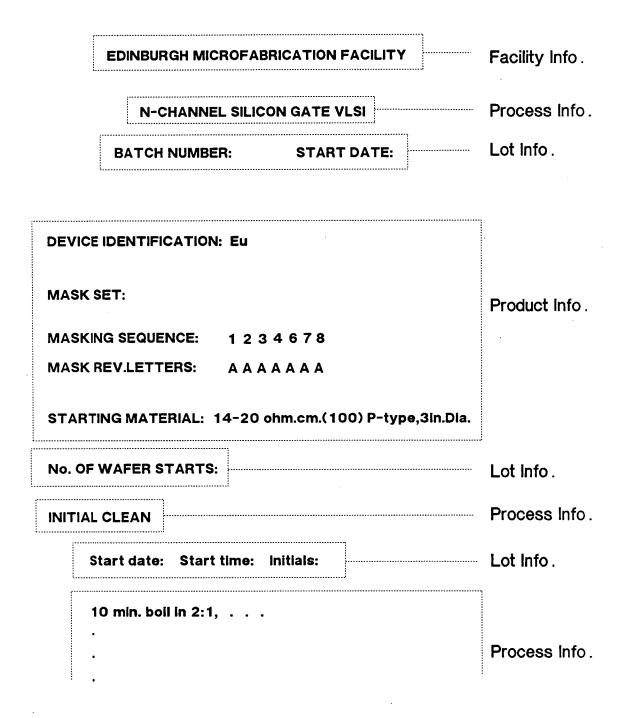

In this chapter an overview of wafer fabrication is presented. The steps which go to make up a fabrication process are then discussed, with emphasis on the parameters required to control these steps and the engineering data that can be collected to perform process monitoring and control. Finally the integration of these process steps is demonstrated using, as an example, the Edinburgh Microfabrication Facility (EMF) 1.5 micron nMOS process.

#### 2.2. Wafer Fabrication

The processes which are used to fabricate ICs are among the most complex performed today. This complexity is a function of the high number of steps which make up a process and the way that all of these steps are interrelated. Ultimately however all IC fabrication processes have the same objective: to produce a high yield of reliable ICs in the most cost effective manner.

Within any IC fabrication plant much time and effort is directed towards achieving a clean, vibration free, highly organised environment where temperature and humidity are tightly controlled. The objective being to maintain consistent processing, reduce the presence of particles, improve alignment accuracies during photolithographic process steps, and avoid the breakages and misprocessing that occurs. To appreciate why the manufacturing environment need be so well maintained one must look more closely at the generic characteristics of an IC process and come to understand the rationale behind the construction of the process.

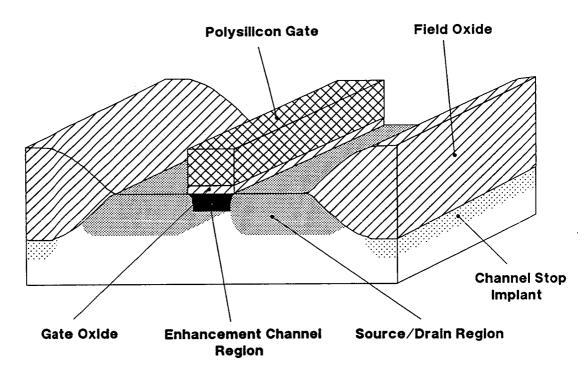

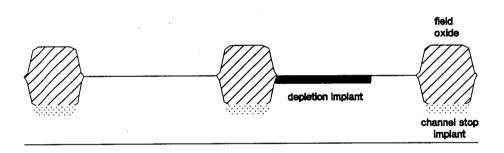

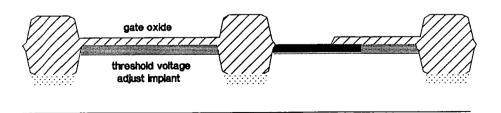

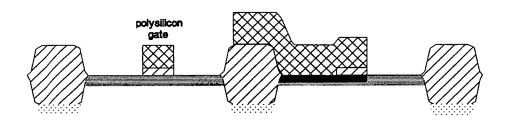

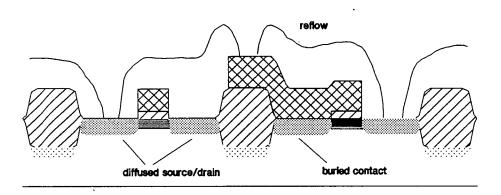

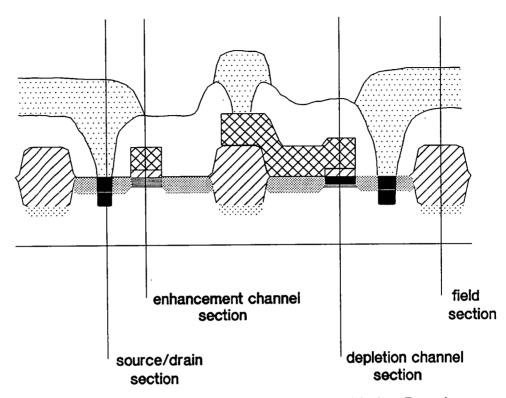

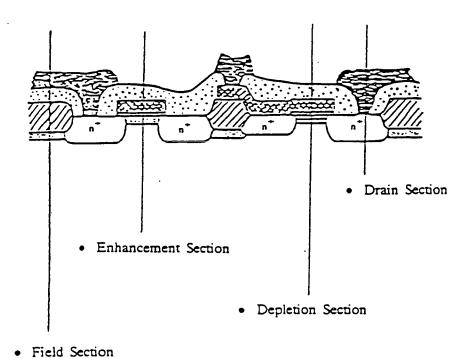

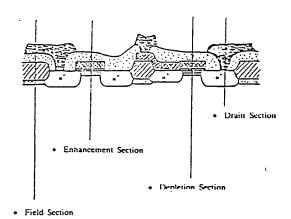

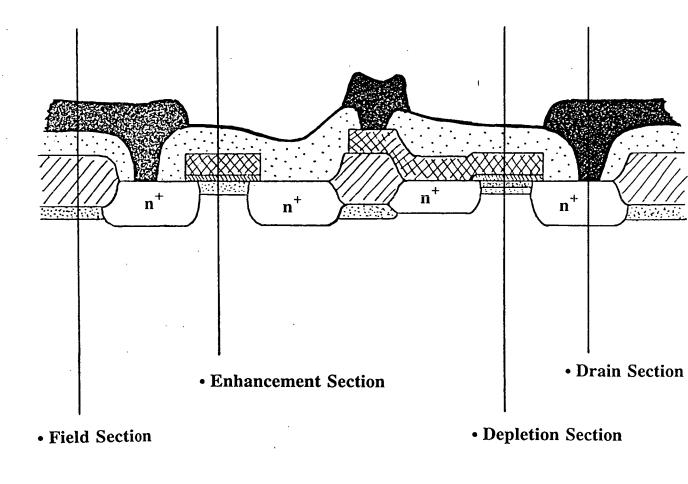

The objective of processing a wafer is to build electrical circuitry across its surface. Commonly this takes the form of many separate sites on the wafer surface, that may either be the same circuit replicated many times or a mixture of different circuit designs. Each circuit can be made up of transistors, resistors, capacitors and other electrical devices. These are fabricated as three-dimensional structures, a section through a typical structure is shown in figure 2.1. Note that this device is made up of layers, both above and below the surface of the wafer. Each layer is defined by a mask which corresponds to a level of the circuit design.

The mask is applied by spinning a photoresist onto the surface of a wafer and exposing the photoresist to light through the mask. When the resist is developed a pattern of exposed wafer surface results. Then the exposed material can be etched or doped and the

Figure 2.1 Section through an enhancement mode nMOS transistor.

remaining photoresist is stripped off.

The range of materials include conductors (eg. aluminium), semiconductors (eg. doped silicon), and insulators (eg. silicon dioxide). The level and type of doping of the semiconductors dictate their conductivity. Common dopants are boron (p-type), arsenic, antimony and phosphorus (all n-type). The level and type of doping through a wafer is termed its doping profile.

Two distinct types of IC fabrication processes have evolved: bipolar and Metal-Oxide-Semiconductor (MOS). Initially bipolar developed as the leading technology and spawned such device families as TTL, ECL and I<sup>2</sup>L, all of which are still used widely. The main characteristic of bipolar silicon circuits is their speed. However, they are also power hungry and generate a great deal of heat. The first MOS technology to emerge was p-type MOS (pMOS), but this was later superseded by n-type MOS (nMOS) which is faster, due to the higher mobility of electrons than holes, and offers greater packing densities. Then followed CMOS where both p- and n-type MOS devices are used. Although not inherently offering the same high packing densities as nMOS, CMOS requires very little power. For a full discussion of silicon IC technologies see Hillenius [2].

## 2.3. Process Steps

Wafer fabrication is a serial process. As each process step is performed it influences the other steps in the fabrication sequence. For example, when a process step includes a heat component it will cause some redistribution of the dopants introduced during previous process steps. Another example is the use of oxide layers as masks to prevent dopants being introduced to certain areas of a wafers surface. From these examples, it is evident that there is a strong interrelation between the steps of a process.

Though there are many ways in which ICs may be fabricated there are only a limited set of operations which can be performed. These range from oxidation to lithography, each requiring very different control parameters. For an operation to become a step in a manufacturing process the input parameters must be carefully considered so that the function performed plays its part in terms of the whole process. Engineering data can then be collected to verify that the intended processing has actually occurred.

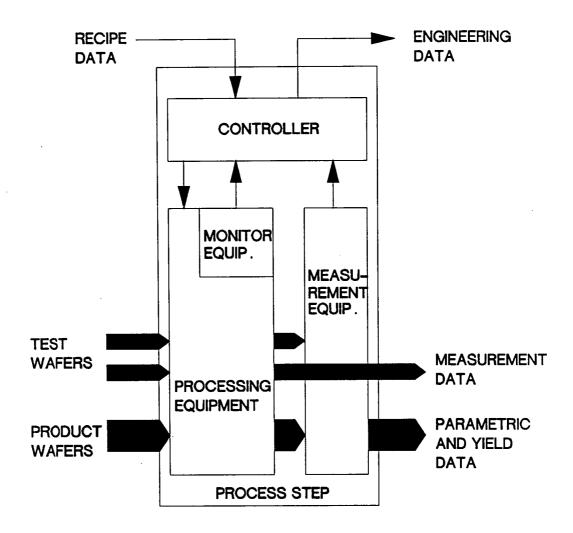

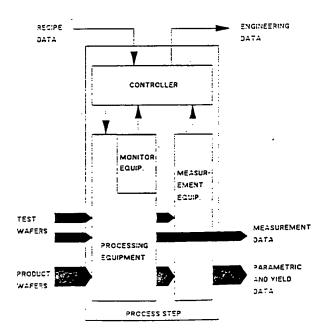

Figure 2.2 shows a generic process step in terms of the information required to control the step and the information which may be collected from this step. The input parameters can be passed as a complete recipe definition from a control system. The data collected from monitoring the processing equipment and from measurements made on the product and test wafers can be passed back to the control system so that process control may be performed. Where possible, in a production environment, process measurements are made on the product wafers, as test wafers take up space which otherwise would be used for product wafers. The data collected during the process is from physical measurements made on the surface of the wafer during or after each process step. Parametric data is also collected after metallization by measuring the electrical characteristics of test devices to produce engineering yield data. The test devices are often sited on process monitor chips (PMC) [3], which take up wafer sites normally used for product chips, or in the scribe lines between devices [4]. The uniformity of the collected physical and electrical parameters is often displayed to the process engineer as a wafer map [5]. In many cases it possible to collect parametric data using computer controlled equipment.

However, it is not always possible within a manufacturing environment to verify processing as it is performed. For example, when a gate oxide is grown during an MOS process one may wish to test the doping density at the surface of the wafer to find out how much dopant has been leached out of the silicon by the growth of the silicon dioxide. Unless a destructive test is performed at this point then it is necessary to wait until a later

Figure 2.2 Generic wafer fabrication process step

process step has exposed the wafer surface before the doping density can be established. Destructive testing is not generally desirable during manufacture as it is wasteful of both time and potential product.

From this we can see that our ability to track and control a process is dependent on the interrelation of the process steps. Thus we must consider the operations which can be performed, paying particular attention to why they are performed, how they are performed, the effect they have on previously defined layers, and how they are controlled and monitored.

#### 2.3.1. Oxidation

The oxidation of silicon is very important in semiconductor manufacturing as the

natural oxide of silicon is a key component in the structure of all devices. Indeed, planar processing technology derives much of its success from the properties of thermally grown silicon dioxide. These properties allow the oxide to be used for several purposes: as a masking layer against implanted ions and dopant diffusion; as a surface passivation layer; and as an isolation layer/region both between the conducting layers of a device and between devices. A common characteristic of all these oxides is that they must be of high quality and be produced in a controlled and repeatable manner.

Although thermal oxidation is the most prevalent technique for producing an oxide it is also possible, and sometimes necessary, to use other methods. These range from wet anodization through chemical vapour deposition (CVD) to plasma oxidation. For example, in laying down a passivation layer over metal the CVD method must be used.

Within thermal oxidation there are essentially two chemical mechanisms; as shown in equations 2.1 and 2.2.

$$Si(solid) + O_2 \rightarrow SiO_2(solid)$$

(2.1)

$$Si(solid) + 2H2O - SiO2(solid) + 2H2$$

(2.2)

For thin oxides dry oxidation (eqn. 2.1) is normally used while for thicker oxides the faster wet mechanism (eqn. 2.2) is preferred.

Both forms of thermal oxidation are performed in tube furnaces where gas flows, temperatures and sequencing are microprocessor controlled. In normal processing the wafers are loaded into the furnace at an idling temperature of 700-900°C before the temperature is ramped up for processing. After the oxidation the temperature is ramped down again. Ramping is employed to minimise wafer warpage.

Prior to oxidation it is necessary to clean the wafers. This removes any contaminants, arising from previous process steps or handling, that might degrade the electrical characteristics of devices or increase the defect density.

The dry oxidation of silicon requires only simple processing equipment and produces a slow growth of oxide at moderate temperatures (c. 950°C). Dopants in the silicon will also redistribute during oxidation as a result of the high temperature.

For dry oxidation the growth rate may be enhanced by modifying the recipe control parameters. For example, higher temperatures will result in a thicker oxide. Though this can also cause an extensive redistribution of dopants. Alternatively the pressure may be

increased to give a larger oxide but with little redistribution of dopants. However, to-date there has been limited development of high-pressure processing equipment [6]. Another approach is the introduction of HCl [7] which increases the oxidation rate and improves gettering.

The oxidation mechanism used during wet oxidation results in a higher oxide growth rate than can normally be achieved during dry oxidation. There are two commonly used methods for producing a wet ambient: steam oxidation and pyrogenic oxidation. In steam oxidation oxygen is bubbled through water before entering the furnace tube. This produces a large oxide at moderate temperatures and times. However, the bubbler system can easily become contaminated. These problems may be avoided by using pyrogenic oxidation. Here the water vapour is created in the furnace tube by direct combination of hydrogen and oxygen. It is also possible to perform wet oxidation with dry, or dry-HCl, oxidation in the same tube and thereby tailor the characteristics of the oxide. This is only achieved however at the expense of equipment complexity.

As with dry oxidation the increase of temperature will result in larger oxide growths. However, the presence of HCl will have little or no effect. When pressure is increased there is a subsequent rise in oxidation rate. Though maintaining a consistent pressure profile throughout a furnace and from run to run is very complex, and failing to do so can result in erratic oxide growth [8].

The trend towards smaller, faster devices has led to the increasing use of thin oxides in the range of 50-200 Å. This places additional restraints on the growth of the oxides as thinner oxides are more sensitive to fatal defects and are harder to grow uniformly. As with normal oxides there are a number of ways in which a thin oxide can be grown. However, for a dry oxidizing ambient there is an initial rapid oxide growth to around 200 Å making thin oxide growth difficult to control. Techniques using lower temperatures and reduced pressures have been developed to combat this problem [9, 10]. For wet oxidations a consistent low growth rate can be achieved in a high pressure steam ambient at lower temperatures than for normal oxides [11]. For a review of rapid thermal processing see Sedgwick [12].

Monitoring the thickness of a grown oxide and its uniformity across both wafer and batch can be achieved using reflective/refractive techniques such as spectrophotometry and ellipsometry on the product wafers [13]. This is important as, for example, variations in the gate oxide of an MOS device can cause substantial threshold voltage variations. To

obtain useful uniformity data it is important to make many thickness measurements across the surface of a wafer, so these measurements are normally performed using automated measurement equipment.

#### 2.3.2. Diffusion

The diffusion of dopants in silicon is a crucial mechanism in planar processing. Introducing a dopant and controlling its concentration can be used to alter both the type and the electrical conductivity of silicon. In MOS technology it is used to form source/drain regions, deep wells, and to dope polysilicon. To achieve devices with electrical characteristics which adhere to specification it is important that dopant diffusion is uniform and reproducible.

There are a number of ways in which a dopant can be introduced into the surface of a wafer: a chemical source in a vapour, deposition of a doped oxide source, and ion implantation. The method chosen for doping the wafers is dependent on the required doping profile and surface concentration. Heating the wafers to a high temperature in the presence of a chemical vapour for the whole of the diffusion will result in a complementary error function (erfc) distribution. Whereas if a pre-deposition of the dopant is performed at a lower temperature followed by a drive-in at a higher temperature a gaussian distribution can be obtained. High temperature diffusion is used not only to distribute the dopant but also to electrically activate the dopants; a technique called annealing. A similar effect to that of a pre-deposition step can be produced by using a doped oxide source. The introduction of impurities by ion implantation is considered separately in section 2.3.3.

Deposited dopant concentrations tend to be high which makes shallow abrupt junctions difficult to form. The high temperatures associated with diffusion cause lateral as well as vertical distribution of dopants. For a detailed study of the distribution of dopants in silicon at diffusion temperatures see Fair [14].

The diffusion of dopant through other materials than single crystal silicon is also of interest; particularly polysilicon and silicon dioxide.

Polysilicon is used both for self-aligned gates and as an intermediate semiconductor between two layers of a device. Boron, phosphorus and arsenic are often used to reduce the resistivity of polysilicon.

Silicon dioxide is commonly used as a masking layer to prevent the introduction of dopants into silicon over predefined areas of a wafer. Because of the slow diffusion of

most dopants through silicon dioxide it is convenient to make sure that the oxide is simply thick enough to act as a barrier to the dopants. However, it has been noted that during oxidation some dopants will diffuse further in the regions exposed to an oxidizing ambient [15].

So far consideration has been restricted to vertical diffusion, however in a three dimensional structure diffusion also occurs laterally. This effect is noticeable where an area of silicon has been masked off for pre-deposition such as during the formation of a source or drain region in an MOS device. Here we see that the junction formed by the lateral diffusion under the mask is at about 3/4 the distance from the mask edge as the vertical junction is from the surface. In fabricating a device with a short drain region it is essential that the source and drain regions do not meet otherwise the device will short circuit. This emphasises the importance of considering the two dimensional diffusion of dopants in small geometry VLSI devices.

The diffusion of dopants is performed in furnace tubes under similar control regimes to those of oxidation. For the deposition of dopants on the wafer surface liquid or solid sources are commonly used. When a liquid source is used oxygen can be introduced to form a doped oxide layer over the wafer surface during the diffusion rather than a chemical vapour. Phosphorus and boron may be also be deposited using this method. Wafers of boron nitride and phosphorus oxide are used as solid sources. They are interleaved with the product wafer to ensure a uniform distribution over the surface of the wafers. The deposition of arsenic is not normally performed in this way as it is too toxic, ion implantation is used instead.

Time, temperature and concentration have a first order effect on the deposition and diffusion of impurities in silicon. In a practical system the timing will be bracketed, as with oxidation, by temperature ramp-up and a ramp-down periods.

A diffusion operation may be monitored by measuring the junction depth and sheet resistance of the processed wafers. The junction depth can be measured by grinding a wedge shape in the wafer and staining the sample so that the junction between p- and n-type materials can be identified, this is called the bevel and stain technique. The sheet resistance of the surface of the wafer can be measured using a four-point probe or Van der Pauw technique [16]. These sheet resistance techniques can be used in-line on product wafers as they are non-destructive, quick and easy to automate. The measurement of the junction depth is slow and destructive, and must therefore be performed on a test wafer.

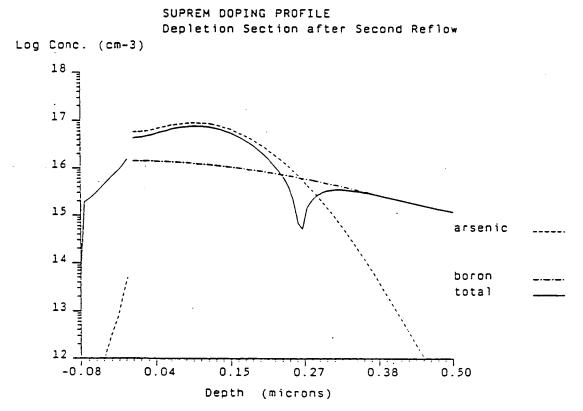

To obtain further information on the outcome of a diffusion it is necessary to establish the concentration profile of the dopants through the wafer. This may be measured using the spreading resistance technique [17], the Secondary Ion Mass Spectrometry (SIMS) [18], or the capacitance-voltage (C-V) technique [19]. The measurement of the doping profile is normally only used when characterizing or developing a process.

## 2.3.3. Ion Implantation

Since its inception in the 1960's ion implantation has played an increasingly important role in wafer fabrication, particularly for MOS structures. Implantation is achieved by sweeping an ion beam over the surface of a silicon wafer in high vacuum. The areas to be doped are defined using a masking layer which may be photoresist, oxide, nitride, or polysilicon. The ability of the ions to penetrate the masking layer is dependent on both the masking material and the thickness of the layer. Damage to the silicon lattice during this process can be repaired by a later anneal step.

Ion implantation provides an alternative to dopant diffusion techniques for introducing controlled amounts of impurities into a silicon wafer. As discussed in section 3.2.2 diffusion has a number of disadvantages which make well controlled, uniform and reproducible doping profiles difficult to achieve.

Using ion implantation doping levels can be accurately controlled and the impurity distribution profiles can be adjusted during the implantation process. Processing is performed at low temperatures which also results in little lateral spread of impurities. However, where diffusion may be performed on several hundred wafers at one time and thus has a very high throughput, ion implanters have a much smaller capacity and are comparatively slow to load. Because of their complexity ion implanters also tend to be unreliable and expensive.

For MOS processing ion implantation can be used to perform threshold adjustment, well implantation, and source and drain doping. When higher power implanters are used it is possible to form buried junctions.

Implantation is controlled to the first order by modifying beam-current and beamenergy [20]. The current of the ion beam is used to control the speed at which the wafers are implanted while the energy of the beam defines the depth of the implanted dopant in the wafer. During ion implantation wafers can suffer from a number of problems which will effect yield. These include surface damage and ion channelling. The former is caused by the impact of the dopant atoms on the wafer surface and is either annealed out or prevented by laying a thin layer of photoresist or oxide over the wafer and implanting through this. The latter occurs when a dopant ion travels between the rows of a crystal lattice deep into the substrate which could make a significant difference to the doping profile of a device. Channeling can also be reduced by growing a thin layer of amorphous material over the wafer surface prior to implantation to de-channel the incident ions.

In a production environment particle contamination, surface charging and wafer heating may be added to the list of potential problems. Particle contamination is the greatest problem as a particle on the surface of a wafer may prevent part of a device being implanted thereby directly effecting yield. Surface charging can occur because of the high electric field present when an ion beam sweeps over a wafer, this can cause non-uniform implantation or trapping of charges in the wafer. Finally wafer heating under the influence of an ion beam can cause warpage and parasitic thermal diffusion.

The implantation of a dopant into silicon is not enough to change its electrical characteristics, the dopant must also be electrically activated. This is achieved by annealing, which puts dopant atoms on substitutional sites and repairs any damage to the silicon lattice caused by implantation. Annealing is performed in a furnace tube, much as for diffusion, but in an inert ambient. Times are normally of the order of tens of minutes and temperatures in the 900-1000°C. Recently a technique called rapid thermal annealing (RTA) has emerged as an alternative to furnace annealing. Here a wafer is heated to a high temperature for a period of seconds by using a high-energy laser pulse. The result is that lattice damage is repaired and the dopant electrically activated with minimal diffusion. This feature is particularly attractive for shallow junction formation.

Many techniques can be used to evaluate the accuracy, uniformity and reproducibility of ion implantation [21]. Four point probing measures sheet resistance on test wafers after an anneal has been performed. Thermal wave analysis measures crystal damage, is non-contact, non-damaging and can be used directly after implantation. Ellipsometry uses optical means to measure the crystal damage caused by implantation. Capacitance-voltage (CV) analysis using test wafers is used to produce dopant concentration profiles.

Other techniques such as spreading resistance probing (SRP) are very useful for supporting development and process characterization.

As ion implantation is used for more and more applications it becomes increasingly important to control the implantations in real time and to increase the throughput of the implanters. The latter is being achieved by applying automation to the transport and loading of wafers. The former however is complicated by the need to integrate in-situ process monitoring data with data collected after the implant to provide feed-back control. This is also resulting in techniques such as thermal wave probing being preferred as an analysis technique because they do not diminish the implanters throughput.

#### 2.3.4. Deposition

The deposition of material films plays many important roles in wafer fabrication. Deposition is used to form layers of material such as silicon dioxide, silicon nitride, polysilicon and metals. Doped oxides can be used as diffusion sources as discussed in section 2.3.2. The method used for deposition varies, but may be classed as evaporation, sputtering or chemical vapour deposition (CVD). Each of these techniques must produce material layers which have good adhesion, are uniform, and have a constant film composition.

Thermal evaporation is the simplest technique for depositing a film. A source material, normally solid, is heated in a vacuum until it evaporates and then condenses on the wafers forming a film. Heating methods include a hot plate or filament and electron bombardment (e-beam). Evaporation is often used for laying down metallization layers which are then etched to become interconnect. The most common material for this purpose is aluminium, which evaporates at a low temperature. However, the uniformity, or step coverage, for thermal evaporation over an uneven surface topography is often unsatisfactory, particularly for the thin metal films required in VLSI applications. Despite this evaporation is still widely used because of its relatively low cost.

Sputtering is a development of the evaporation technique, replacing thermal heating of the source with bombardment by energetic ions. The ions can be generated in a number of ways but two popular methods are ion beam sputtering and magnetron sputtering. In the former an ion beam is directed at the source so that the sputtered material deposits in a controlled manner on the wafer surface. This method has the advantage of producing very pure films, but is slow and therefore has a low throughput. However, it is the second method which is most widely used. Here the atoms are charged to form a plasma glow in front of the target material. The argon ions are then accelerated towards the material which they strike causing sputtering of source atoms that are then directed

towards the target wafers. Magnetron sputtering provides good step coverage and can be controlled to achieve good reproducibility. It also provides a high throughput. Sputtering differs from thermal evaporation in that it can be used to perform well controlled deposition of all materials: metals, alloys, semiconductors and insulators. Damage to the wafer surface caused by sputtering can be removed by a low temperature anneal. For sputtering the deposition rate and final layer thickness can be accurately controlled by varying the substrate bias, the wafer temperature, the pressure inside the chamber and the time.

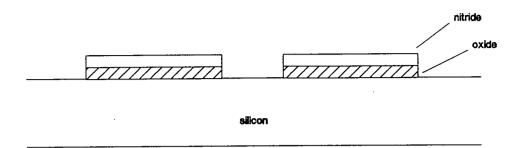

CVD is widely used for depositing silicon and its compounds on a wafer surface. Like evaporation and sputtering, CVD is performed in a chamber but the source of the deposited material is a gas above the surface of the wafers. The gas is heated so that a chemical reaction occurs depositing a film on the wafers. The most widely used materials for film deposition are single crystal silicon, polycrystalline silicon, silicon dioxide and silicon nitride. These materials can be doped during the deposition process by introducing dopants into the source gas. Some metals and metal silicides can also be deposited using CVD.

CVD can be divided into three basic categories: atmospheric deposition (APCVD); low pressure deposition (LPCVD); and deposition in the presence of a gas plasma (PECVD). High wafer throughputs can be achieved using all CVD techniques making them suitable for volume production.

APCVD is mostly used for the deposition of single crystal silicon, or epitaxial, layers with the same crystal orientation as the substrate. This process is important in bipolar processes but is rarely used in fabricating MOS structures. Epitaxial deposition is commonly performed at around 1200°C.

LPCVD is used to deposit polysilicon, silicon nitride and silicon dioxide. This is achieved at a lower temperature (c. 800°C) and with higher throughput than for APCVD, it also produces layers with better thickness and composition uniformity. The deposition of metals using LPCVD results in better step coverage than can be achieved using evaporation or sputtering and so is the preferred technique when forming multi-layer interconnect.

PECVD allows very low temperatures (c. 300°C) to be used in material deposition by reacting the source gases in a plasma. Silicon dioxide and silicon nitride are deposited using this technique. However, PECVD is a very complex process and therefore more difficult to control than other CVD methods.

Monitoring the growth of thin films during their deposition can be performed using a number of techniques. Quartz crystal microbalance (QCM) technology is often used for measuring deposition rate and film thickness in physical vapour deposition processes, ie. evaporation and sputtering. QCM also has the advantages of not requiring calibration and being inexpensive. Other methods, such as mass spectrometry, measure the partial pressure of the gas species being deposited and infer the thickness and deposition rate. Ellipsometry may also be used to measure the thickness and refractive index of some materials as they are deposited.

Techniques for measuring the thickness of films after their deposition may be classed into those which can be performed on product wafers and those for which a test wafer must be introduced into the process. The techniques used to measure film thicknesses on product wafers all depend on the reflective/refractive properties of the material. These include reflection spectrophotometry, which allows small areas of the wafer to be inspected very quickly but requires empirical calibration, and ellipsometry. Measurements which are normally made on test wafers include electrical techniques, such as four point probing, and destructive techniques.

The move towards sub-micron geometries places harsh restrictions on deposition techniques. For example, they must be low temperature, have uniform step coverage, few process-induced defects and a high throughput. Thus the use of evaporation and sputtering techniques is likely to diminish except where there comparative low cost over CVD systems makes them desirable. For MOS technologies emphasis is most likely to be placed on LPCVD and PECVD.

#### 2.3.5. Etch

Along with lithography (section 2.3.6) etching is used to define the structural elements of devices on a silicon wafer. Thus to fabricate an nMOS device of the type shown in figure 2.1 etching techniques must be used throughout the whole process to selectively remove areas of deposited/grown layers. Etching processes therefore exist to remove all the materials used in wafer fabrication. The method chosen for any particular etch is dependent on the desired shape of the resultant feature.

The most important properties of a feature formed by an etching process are size and profile (isotropic, anisotropic, etc.) but other properties are also important in determining the suitability of an etching operation. These include the uniformity of etch across the wafer, the ratio of the etch rate of the film to the etch rate of the substrate, called

selectivity, and the number of impurities and defects which the operation will introduce. For a production environment throughput is also of concern.

In an nMOS process, for example, etching is used for many purposes: to expose an area of the silicon wafer surface for following ion implantation and oxide growth steps during the formation of a field region; and to remove areas of polysilicon leaving only polysilicon gate regions. However, an etching process cannot be considered in isolation, it must be designed with an understanding of the topography formed by preceding steps and the requirements of the following steps. As an example, a material deposited over an abrupt edge can require over-etching before the process is complete. Alternatively, prior to interconnect metallization, the etch used to open up contact windows must not leave behind sharply defined window edges lest the metal deposited over these edges be prone to breakage.

There are essentially two types of etching used in semiconductor fabrication: wet and dry. Wet etching is the simplest mechanism, here the prepared wafer is dipped in an appropriate chemical solution and remains there until a sufficient amount of material has been removed. Such a process is isotropic and may only be controlled by varying the chemical concentration, the temperature and the time. The rate and uniformity of the etch is also influenced by agitation of the wafers while in the etchent. Chemical mixes have been devised for removing all the material commonly used during wafer fabrication, however care must be taken as some of the chemicals are highly toxic. Because of its simplicity wet etching can have a very high throughput making it an attractive option in a production environment. Careful choice of chemicals can also lead to highly selective etching, although monitoring the rate of etching and the time at which the etch is completed is very difficult. Wet etching may also be non-uniform across the surface of the wafer. As a consequence it may be necessary to routinely over-etch, which along with its isotropic nature makes wet etching unsuitable for defining very small features. However, for more tolerant features wet etching still remains a useful technique.

Dry etching is performed in a chamber where a relatively inert input gas is excited by a plasma discharge producing reactive species that combine with the exposed film to form volatile products which are vented from the chamber. The application of r.f. power to create the plasma also directs the reactive ions onto the surface of the wafer resulting in an highly anisotropic etch. This ability makes dry etching eminently suitable for defining critical VLSI device features such as MOS gates. Dry etching also offers lower chemical costs

and tends to introduce fewer defects than wet etching. However, the selectivity of dry etching is lower than wet etching as reactive ions tend not, for example, to differentiate between silicon and silicon dioxide. Dry etching also suffers from very high equipment costs, although these can be offset by automating the loading/unloading process and, in some cases, using fast single wafer processing to increase their throughput.

Dry etching is classed as either plasma etching or reactive ion etching (RIE). In both cases the wafers are laid out on an electrode with the plasma being generated immediately above their surfaces, they differ in the polarity of their electrodes. RIE etchers also have a lower operating pressure and higher energy ions and are therefore preferred in production environments because of their speed. The actual mechanisms involved in dry etching are complex and not well understood thus controlling the etch rate is very difficult. For both classes of etcher there are the following control parameters: r.f. frequency and power used to excite the input gas; flow rate of the gases (both input and output); and pressure inside the reaction chamber.

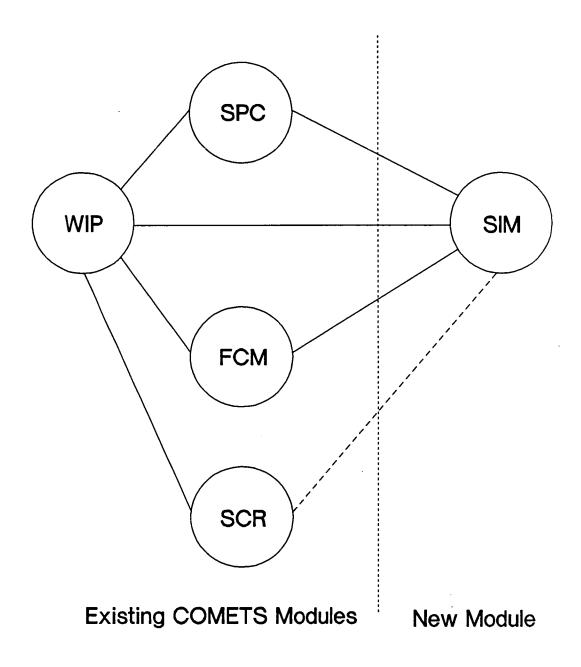

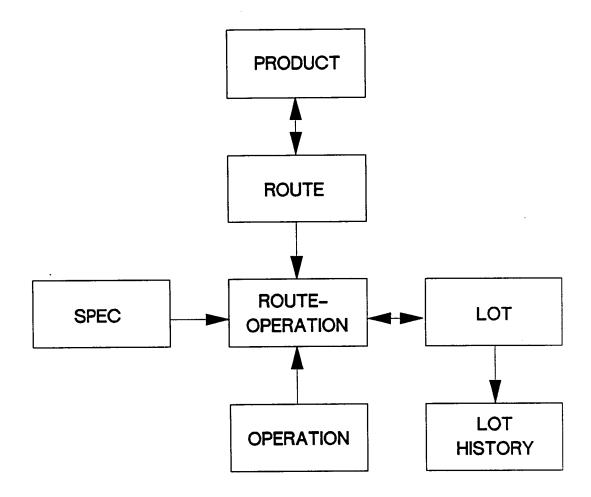

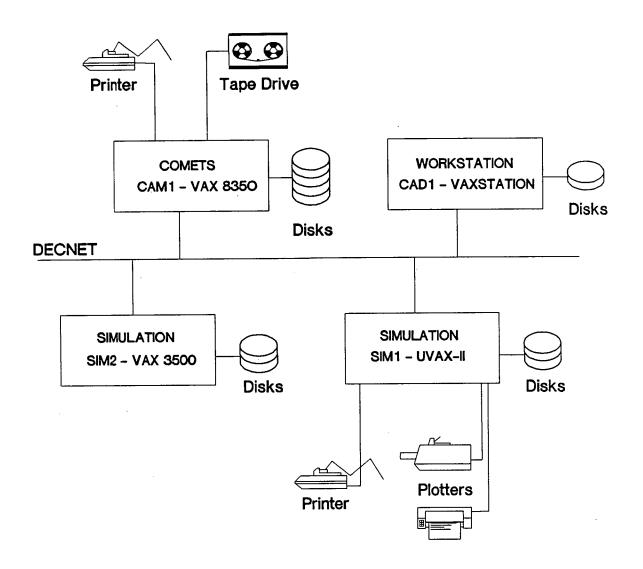

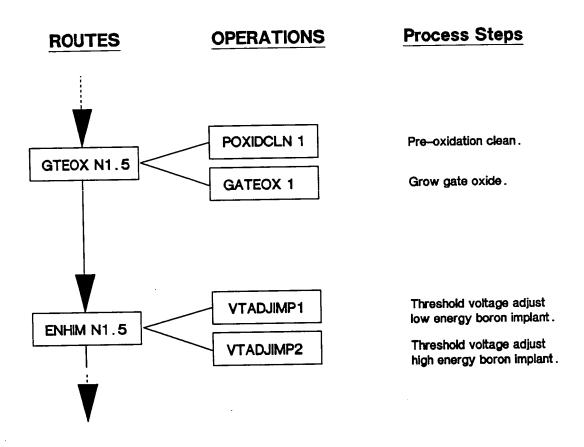

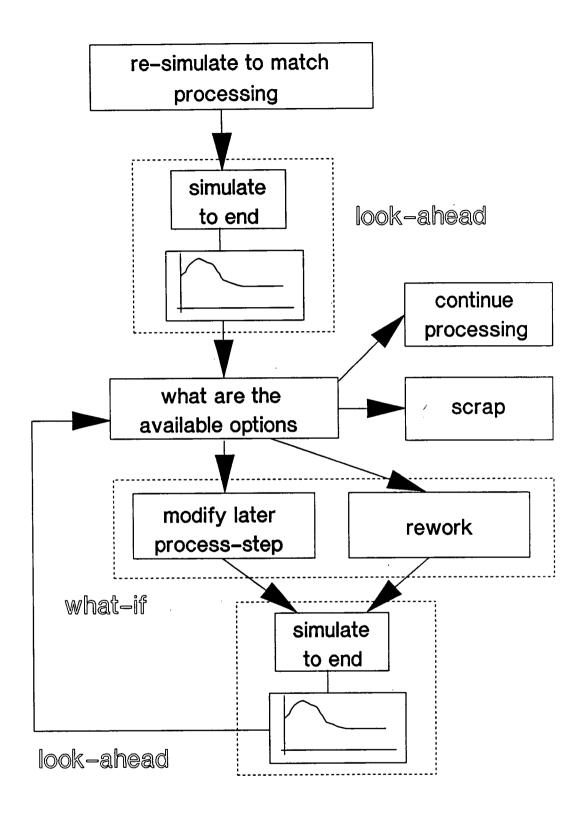

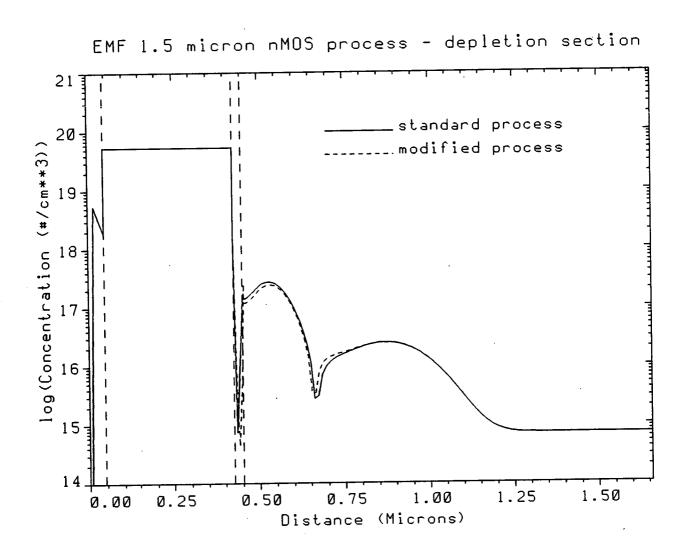

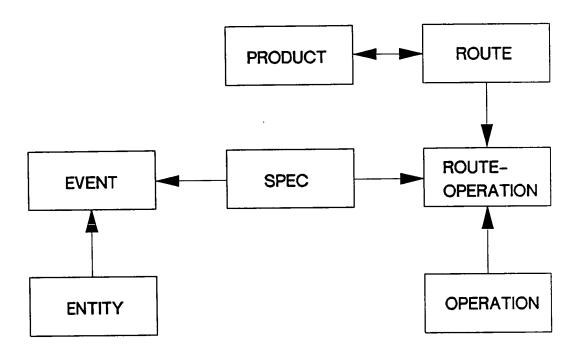

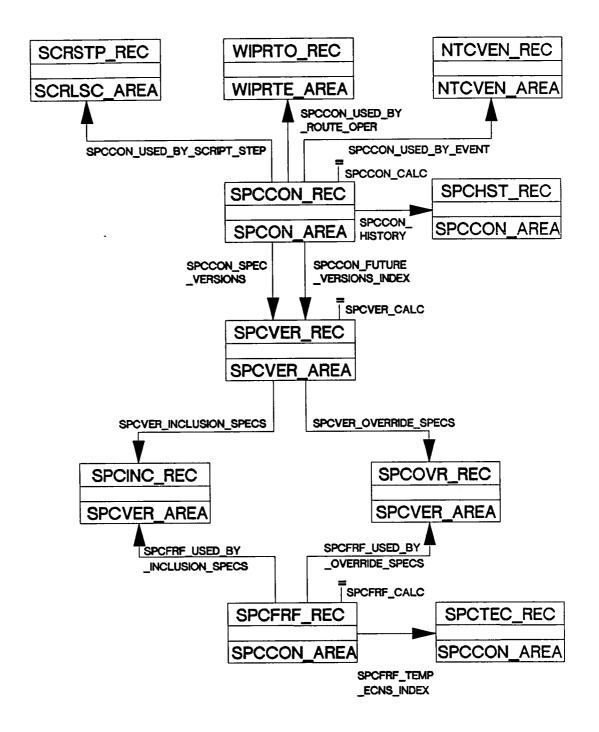

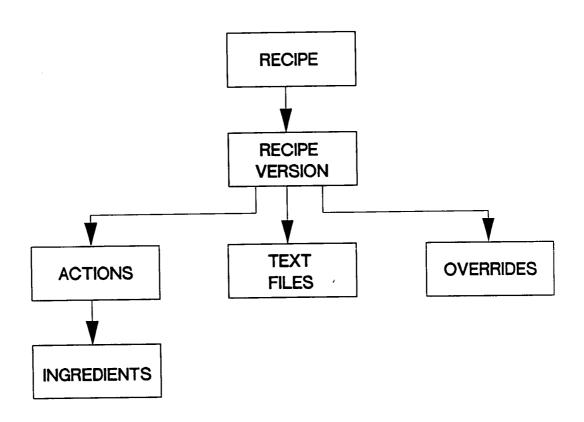

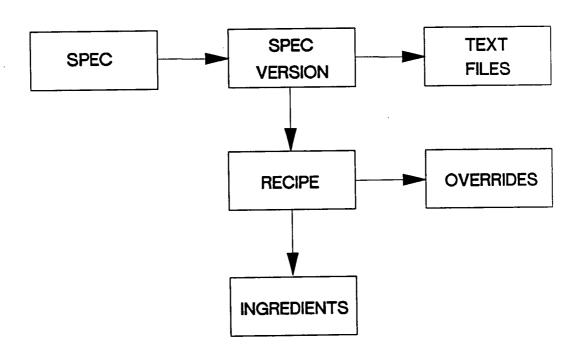

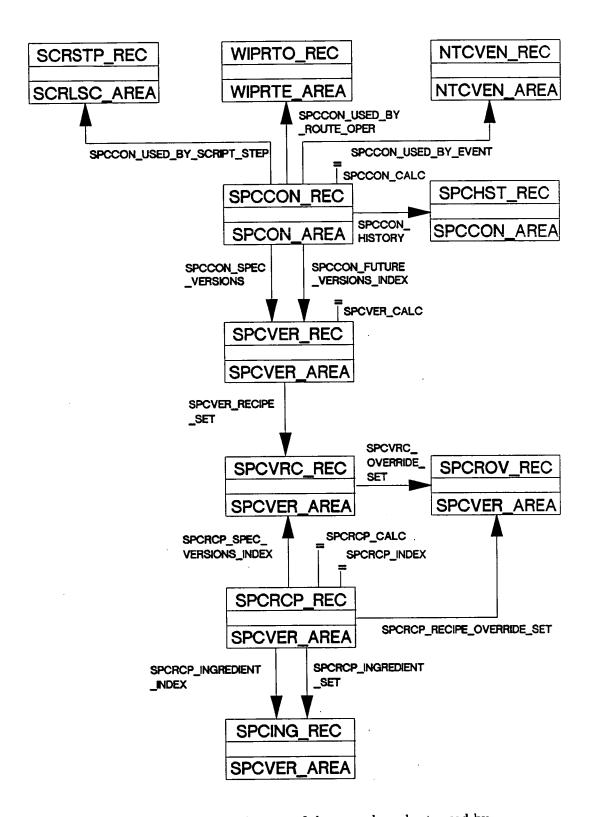

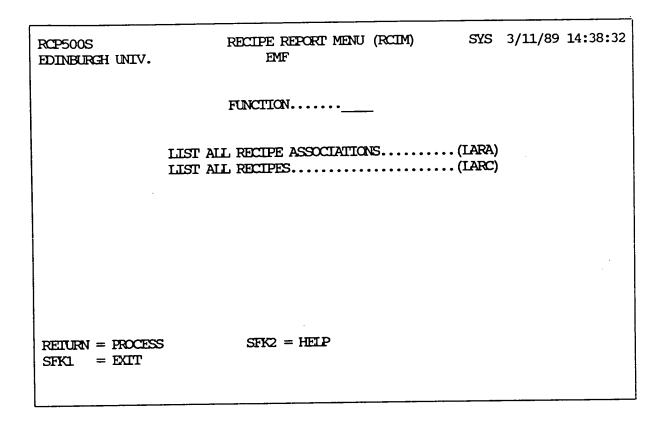

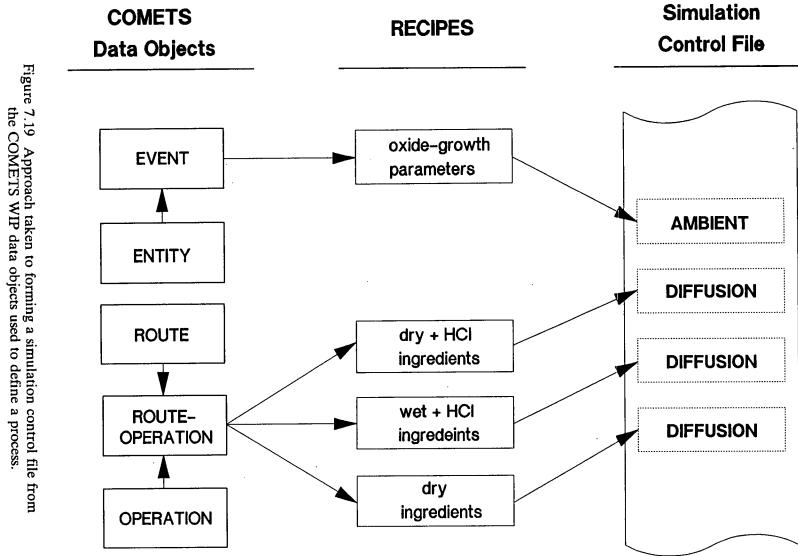

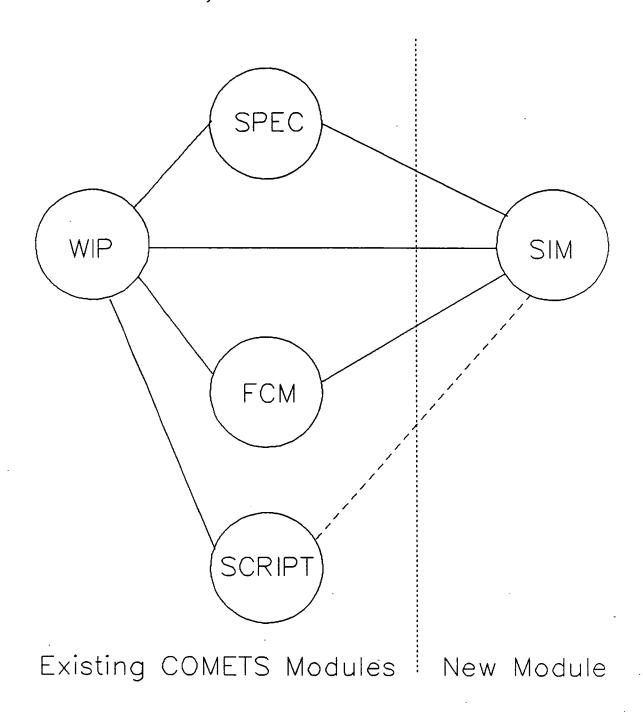

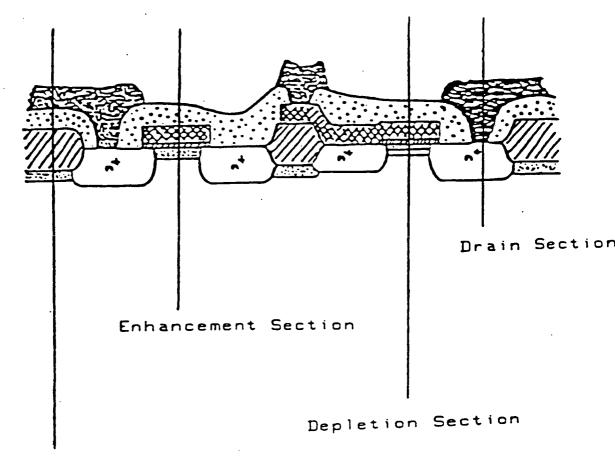

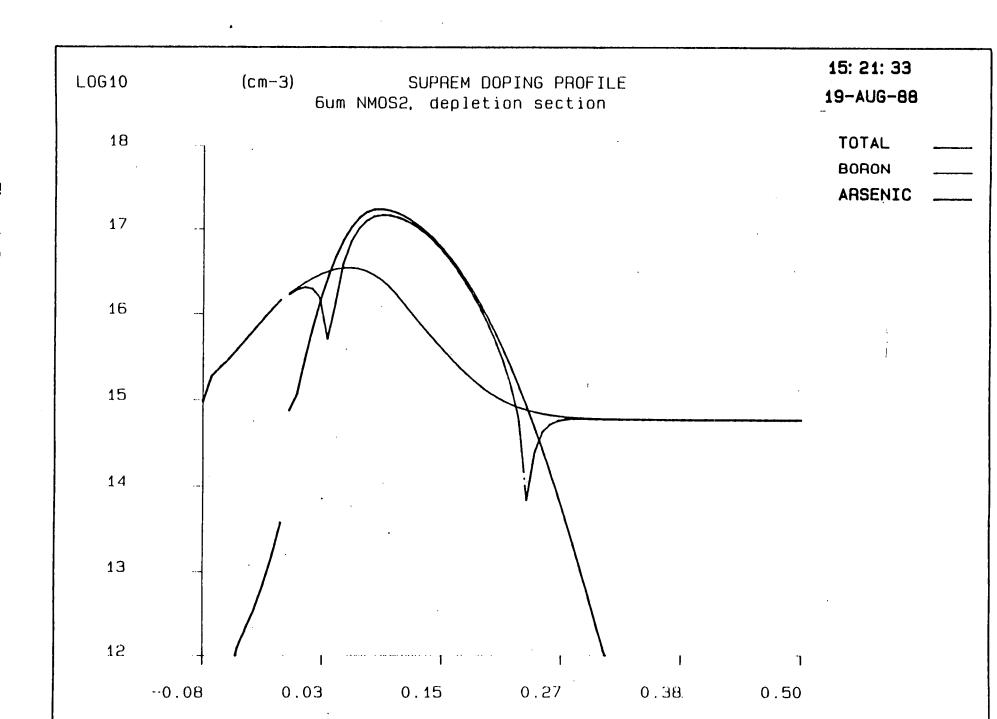

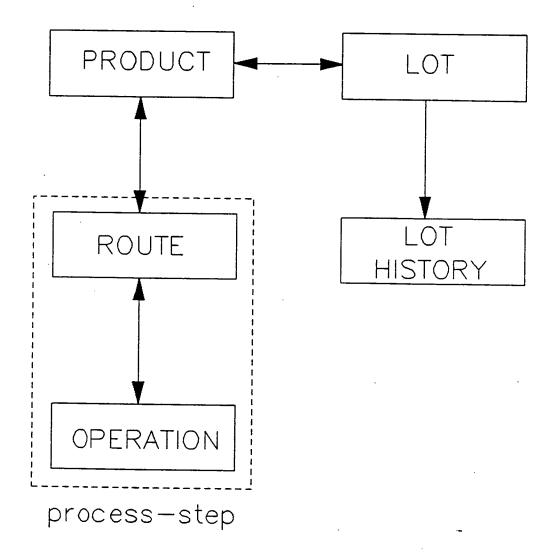

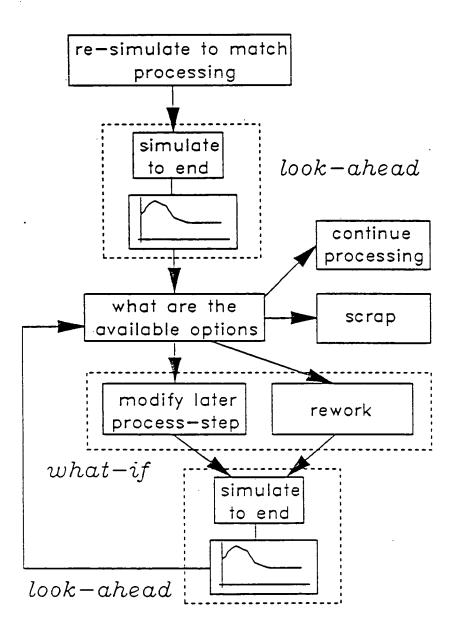

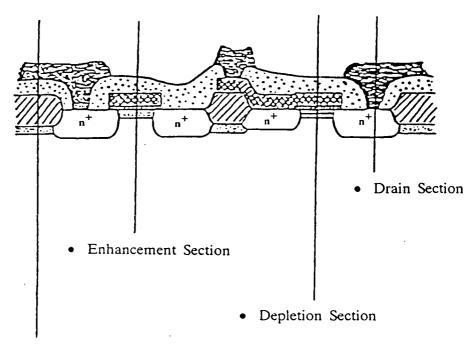

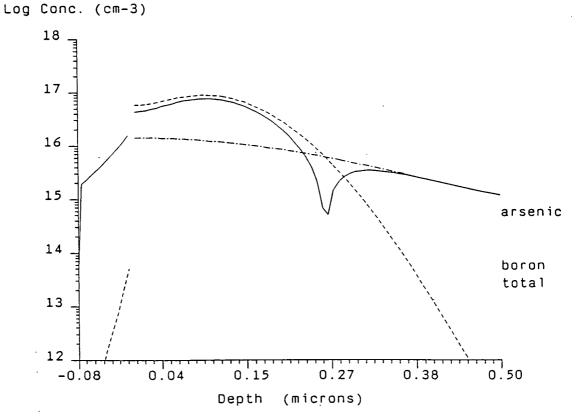

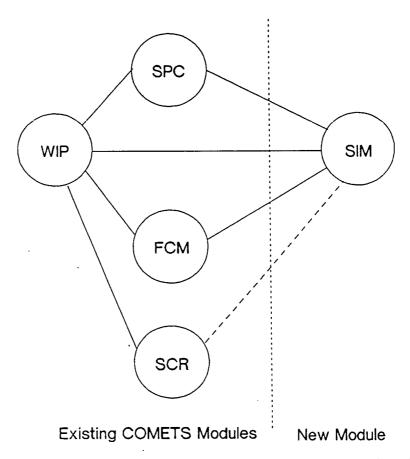

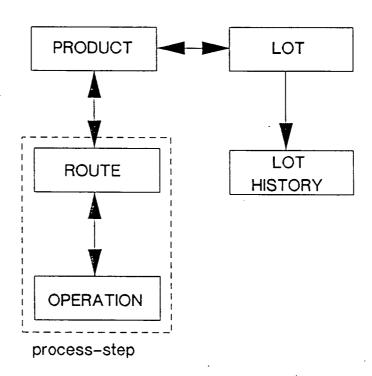

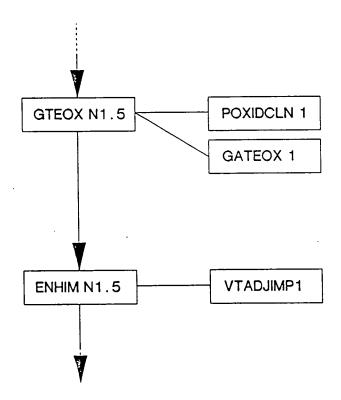

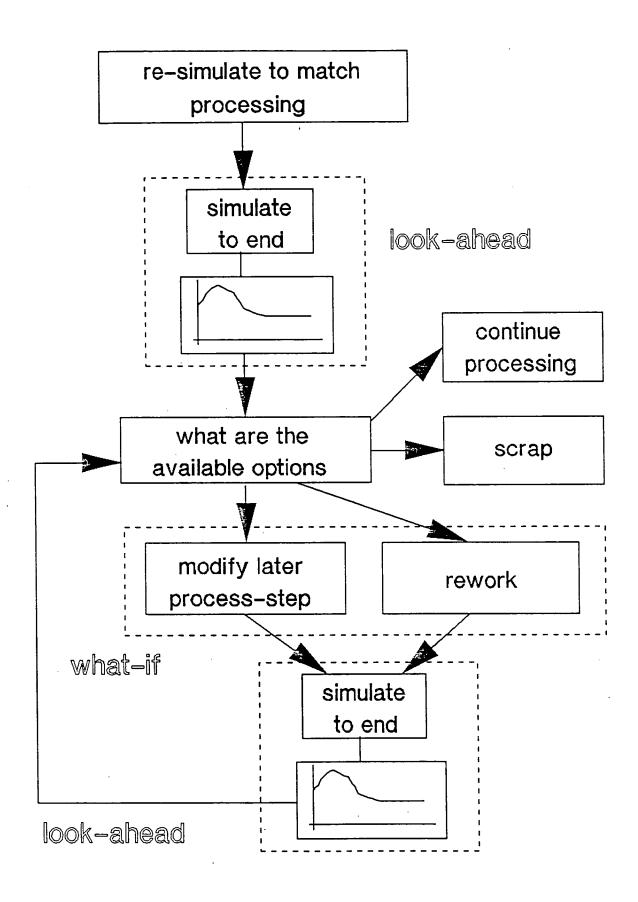

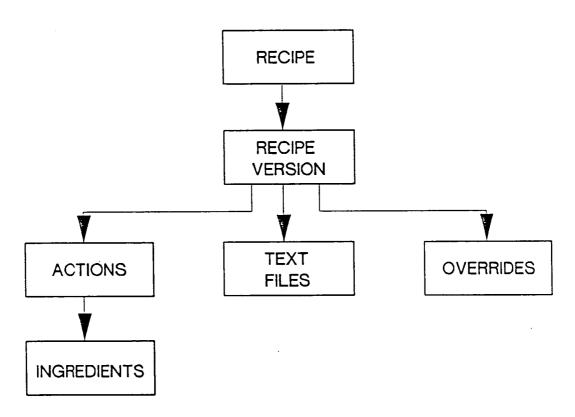

Monitoring of the etch rate for wet etching is not normally performed, the time spent by the wafers in the chemical being determined empirically. Visual inspection is then used to check whether the etch has completed over the whole surface of the wafer. In dry etching, however, the end-point of the etch can be monitored using optical emission spectroscopy or mass spectroscopy. These techniques provide information on the concentration of reactant and etch product which change when the film being etched is used up. Laser reflectance techniques can also be used to perform in-situ measurement of film thickness. The end-point detected using these techniques does not guarantee the removal of all the exposed film so it is necessary to add an over-etch period to remove any excess film; it is important that this period be minimised.