# Surface Topography of Silicon Microcircuits

Thesis submitted by

Martin Fallon

for the degree of

Doctor of Philosophy.

Edinburgh Microfabrication Facility

Edinburgh University

1992

## Table of Contents

| Abstract                   | ix  |

|----------------------------|-----|

| Declaration of Originality | x   |

| Acknowledgements           | xi  |

| Glossary                   | xii |

| 1 INTRODUCTION |  |

|----------------|--|

|----------------|--|

| 1.1 | HISTORICAL BACKGROUND         | 1  |

|-----|-------------------------------|----|

| 1.2 | THE TRANSISTOR                | 2  |

| 1.3 | MINIATURISATION               | 3  |

|     | 1.3.1 Motivation              | 3  |

|     | 1.3.2 Scaling                 | 6  |

|     | 1.3.3 Non-Scaleable Constants | 8  |

| 1.4 | THESIS OUTLINE                | 10 |

|     | 1.4.1 Thesis Motivation       | 10 |

|     | 1.4.2 Thesis Content          | 11 |

1

| REFERENCES | <br>12 |

|------------|--------|

|            |        |

| 2 ISOLATION PROCESSING        | 14 |

|-------------------------------|----|

| 2.1 INTRODUCTION              | 14 |

| 2.2 OXIDATION                 | 15 |

| 2.3 LOCOS                     | 17 |

| 2.3.1 White Ribbon            | 18 |

| 2.3.2 2-D Profiles            | 20 |

| 2.3.3 3-D Profiles            | 23 |

| 2.4 LOCOS ALTERNATIVES        | 24 |

| 2.4.1 General                 | 24 |

| 2.4.2 Silicon Etch Processes  | 25 |

| 2.4.3 Poly Buffered Processes | 27 |

| 2.4.4 Other Options           | 28 |

| 2.6 SUMMARY                   | 29 |

| REFERENCES                    | 30 |

| 3 DEVICE PHYSICS                      | 34 |

|---------------------------------------|----|

| 3.1 INTRODUCTION                      | 34 |

| 3.2 THE CRYSTAL LATTICE               | 34 |

| 3.2.1 The Fermi Energy                | 35 |

| 3.2.2 Energy Bands                    | 35 |

| 3.2.3 The Fermi Energy                | 36 |

| 3.2.3 Intrinsic Carrier Concentration | 37 |

| 3.2.4 Law Of Mass Action              | 38 |

| 3.2.5 Impurities                      | 40 |

| 3.2.6 Conduction                      | 43 |

| 3.2.6.1 Mobility and Drift Velocity   | 43 |

| 3.2.6.2 Diffusion Current             | 45 |

| 3.2.6.2 Minority Carrier Lifetime     | 46 |

| 3.3 THE PN JUNCTION DIODE             | 47 |

| 3.3.1 Reverse And Forward Bias        | 52 |

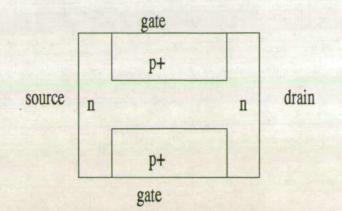

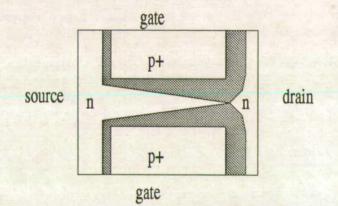

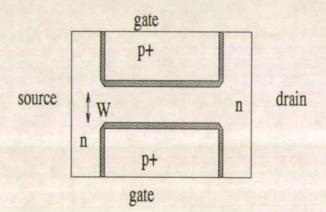

| 3.4 THE FET TRANSISTOR                | 54 |

| 3.4.1 The Junction FET                | 54 |

| 3.4.2 The IGFET                       | 56 |

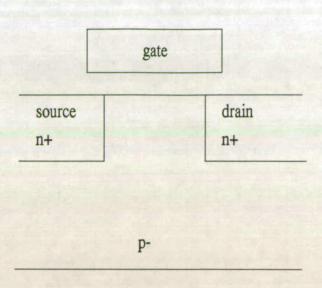

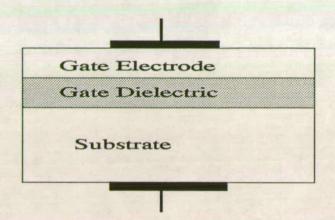

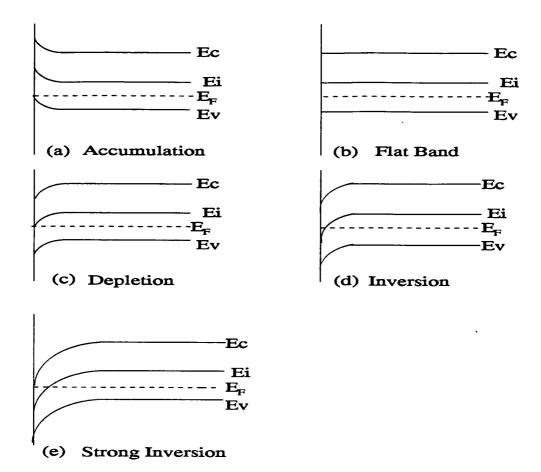

| 3.4.3 The 2 Terminal MOSFET                     | 57   |

|-------------------------------------------------|------|

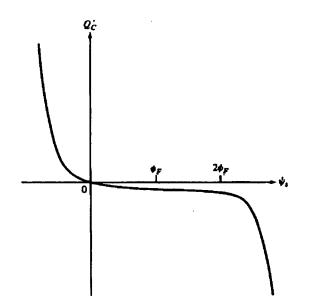

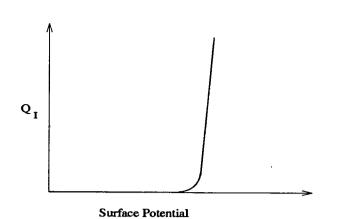

| 3.4.4 General Analysis Of The 2 Terminal MOSFET | 63   |

| 3.4.5 The Three Terminal Device                 | 72   |

| 3.4.5 The Four Terminal Device                  | 74   |

| 3.5 ION IMPLANTED CHANNELS                      | 77   |

| 3.6 SUMMARY                                     | 78   |

| REFERENCES                                      | 79   |

|                                                 |      |

| 4 DEVICE WIDTH                                  | 80   |

| 4.1 INTRODUCTION                                | 80   |

| 4.2 THRESHOLD VOLTAGE                           | 81   |

| 4.2.1 Width Dependence Of Threshold Voltage     | 82   |

| 4.2.2 The Parasitic Field Transistor            | · 85 |

| 4.3 DEVICE WIDTH                                | 87   |

| 4.3.1 The Series Resistance                     | 88   |

| 4.3.2 Mobility Modulation                       | 90   |

| 4.3.3 Width Definitions                         | 92   |

| 4.3.3 Electrical Extraction Techniques          | 94   |

.

| 4.3.4 Width Formulation | 104 |

|-------------------------|-----|

| 4.4 SUMMARY             | 111 |

| REFERENCES              | 112 |

###

.

| 5.1 | INTRODUCTION                 | 118 |

|-----|------------------------------|-----|

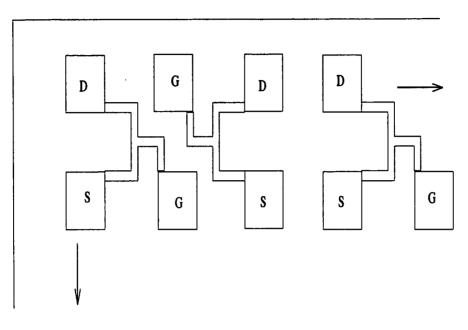

| 5.2 | FABRICATION                  | 118 |

|     | 5.2.1 The Process Variations | 121 |

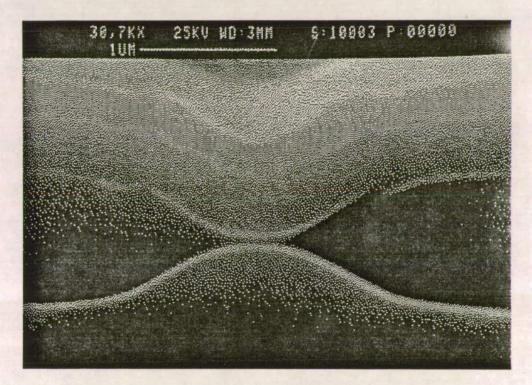

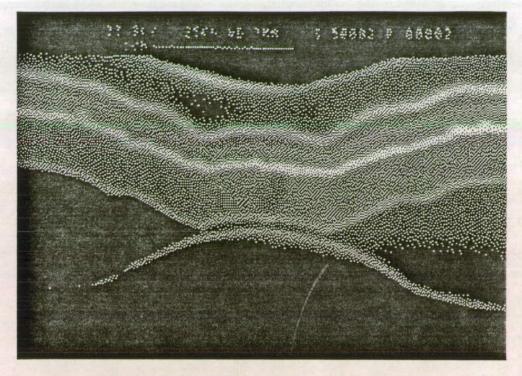

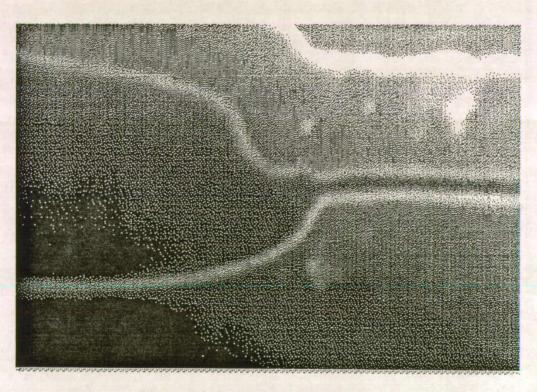

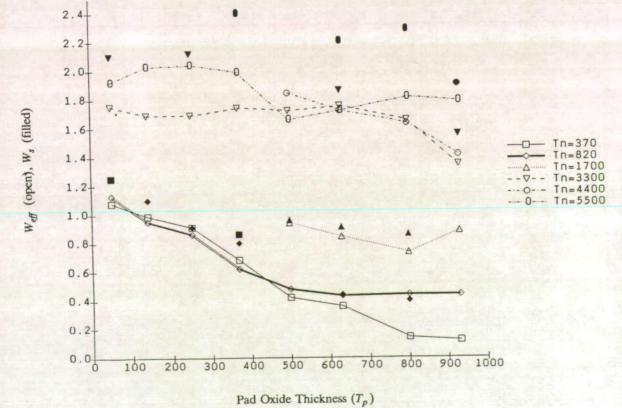

| 5.3 | RESULTS 1: TOPOGRAPHY        | 121 |

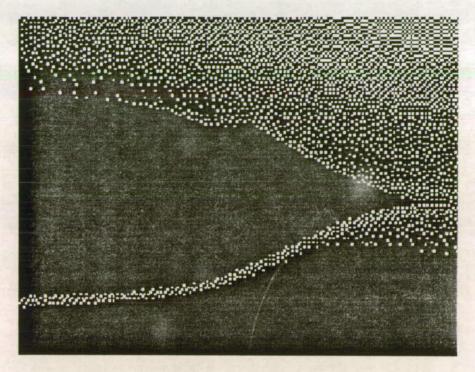

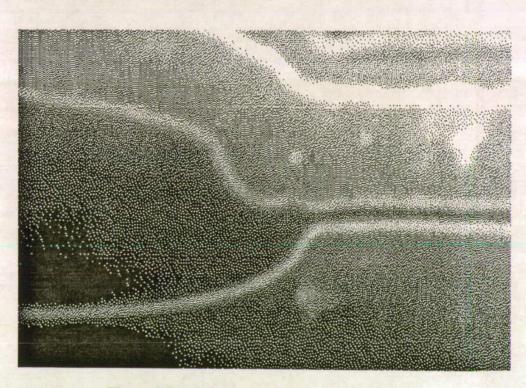

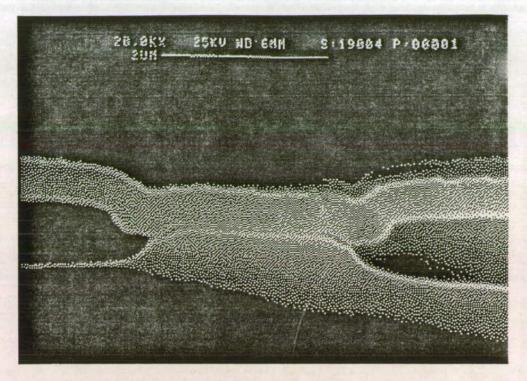

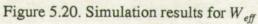

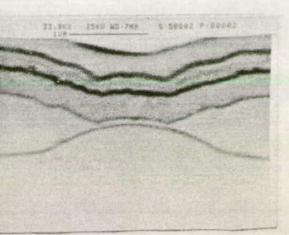

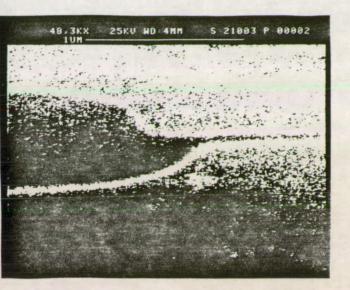

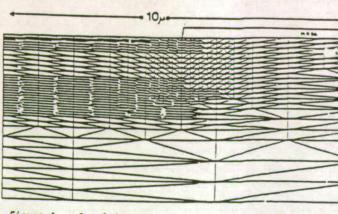

| ,   | 5.3.1 SEM Profiles           | 122 |

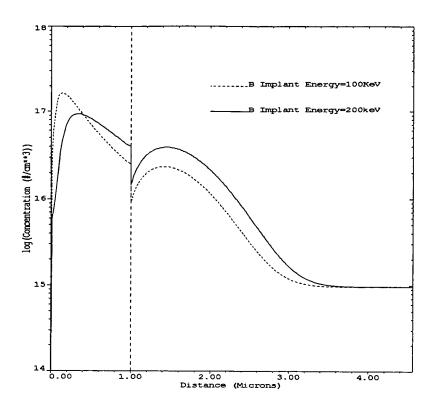

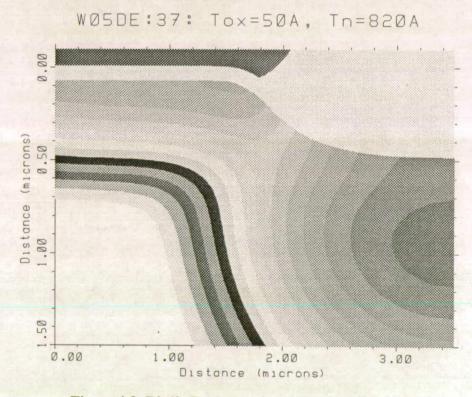

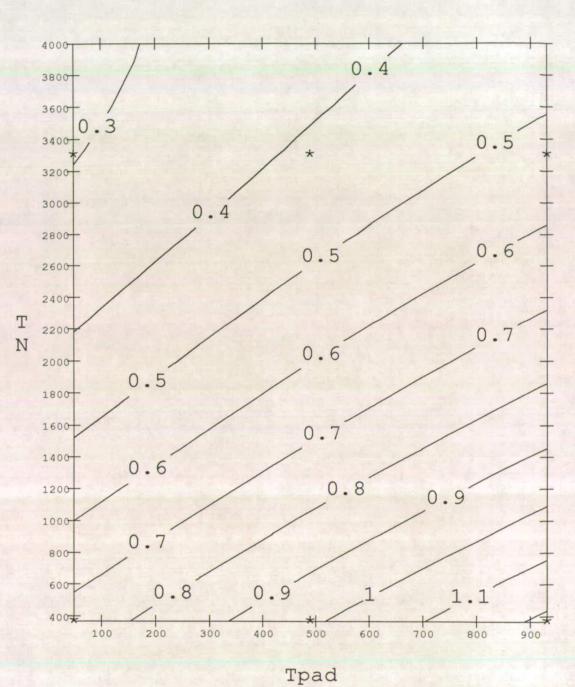

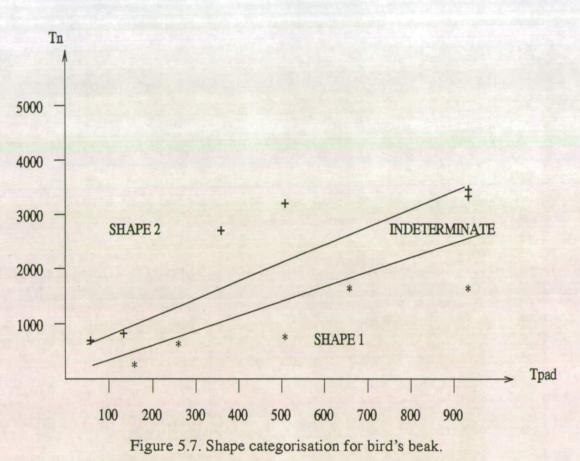

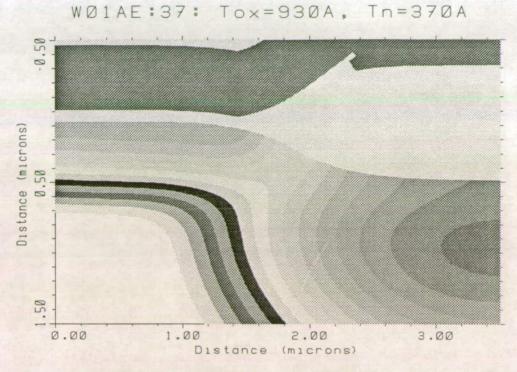

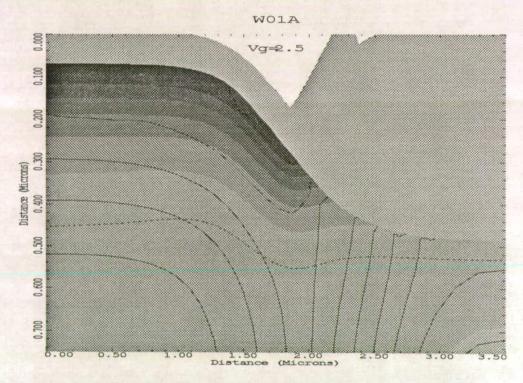

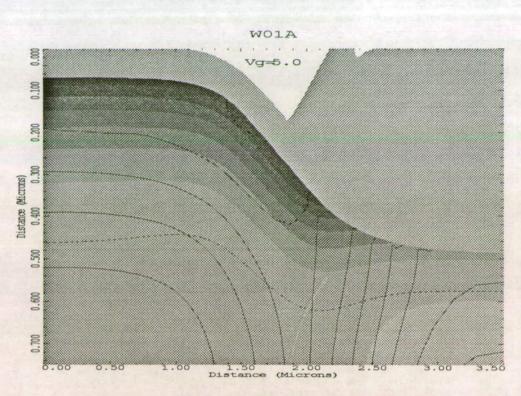

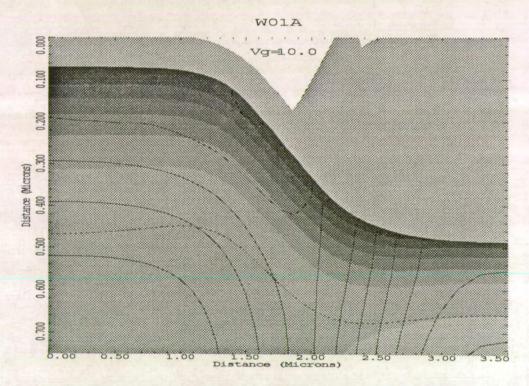

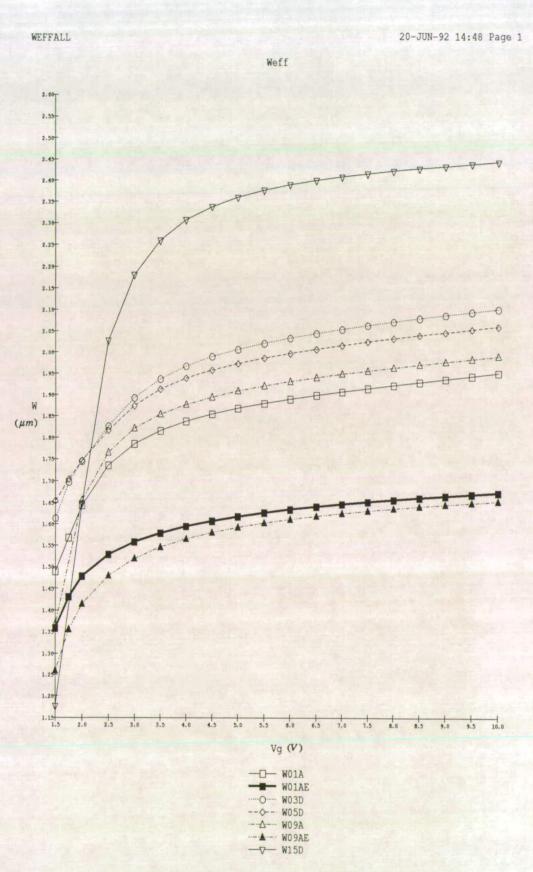

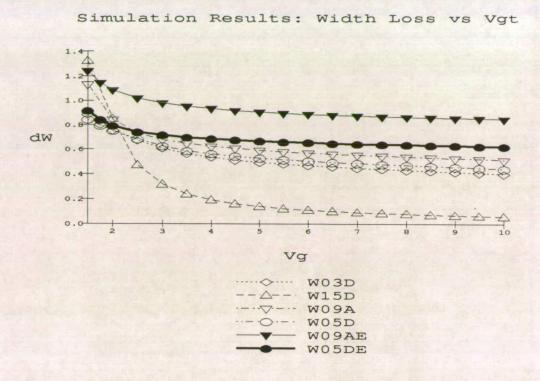

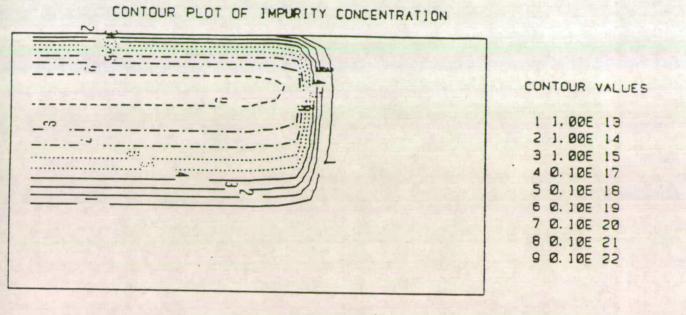

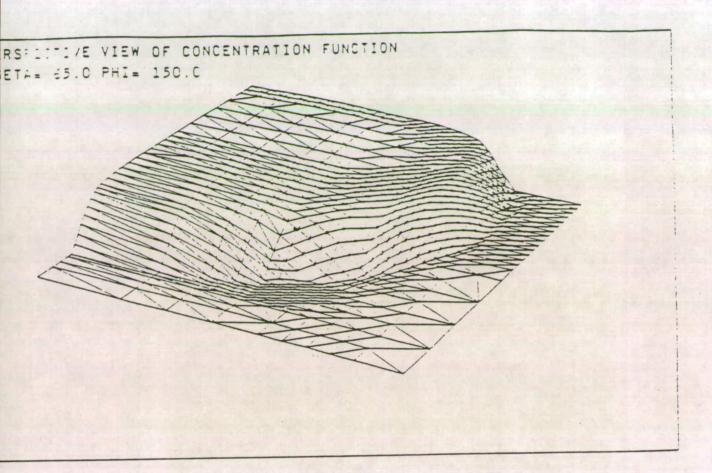

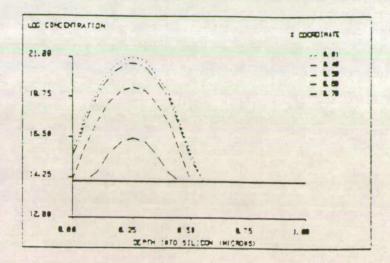

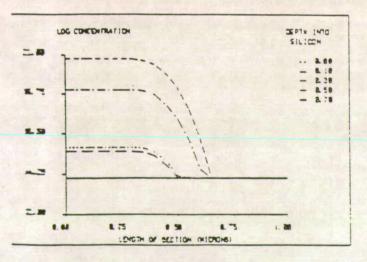

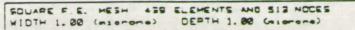

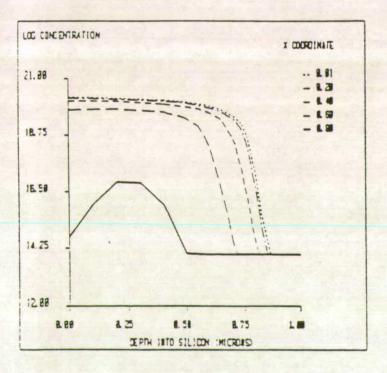

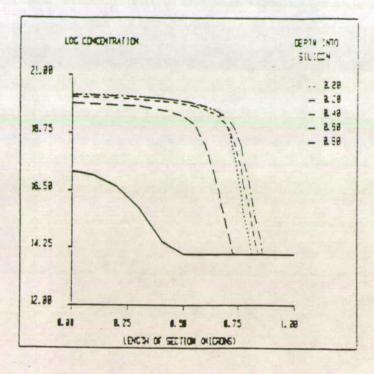

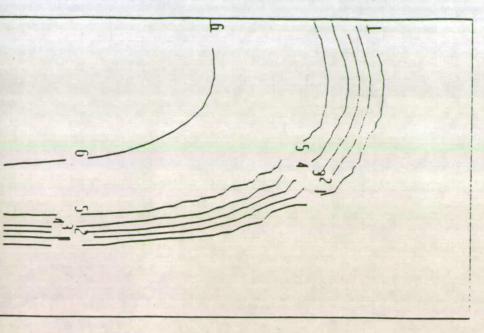

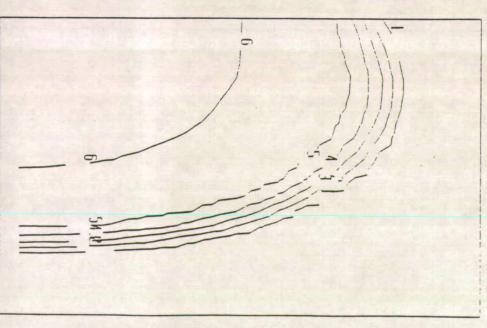

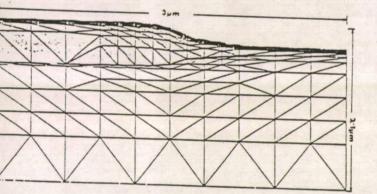

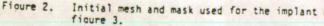

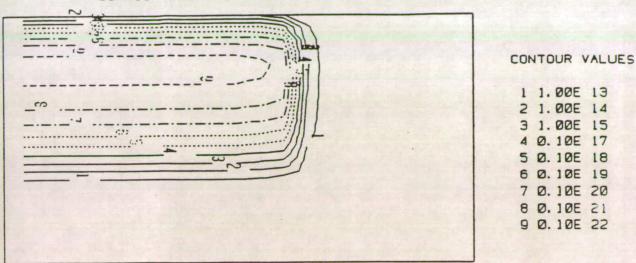

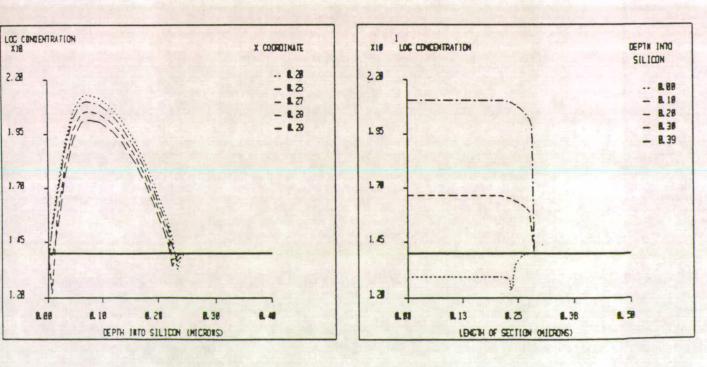

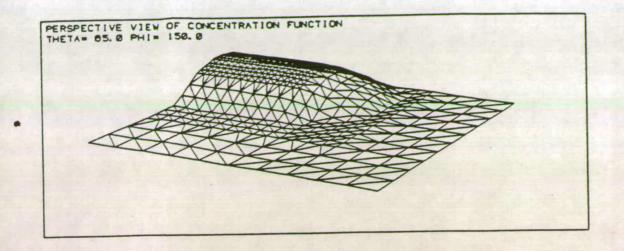

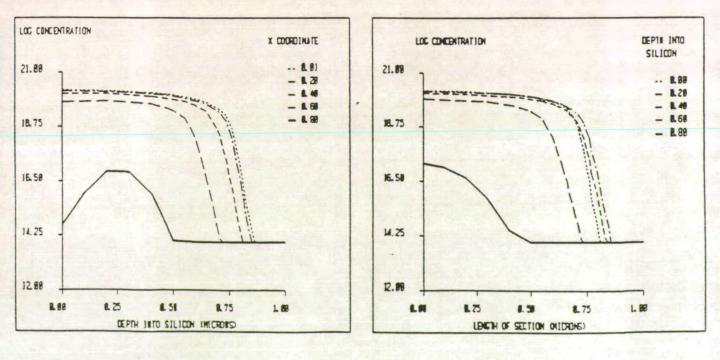

| 5.4 | RESULTS 2: SIMULATION        | 126 |

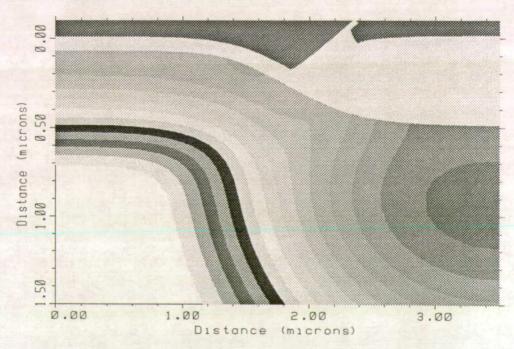

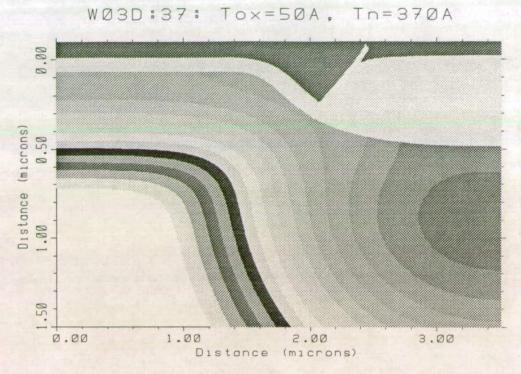

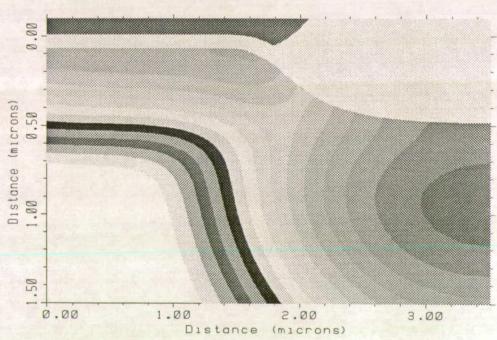

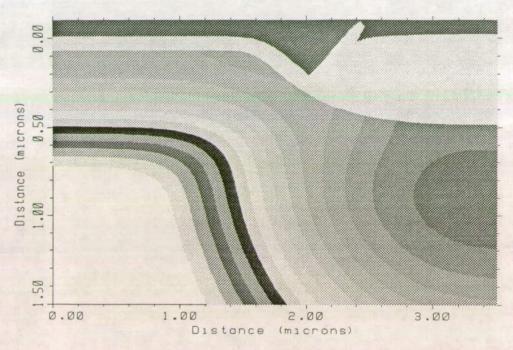

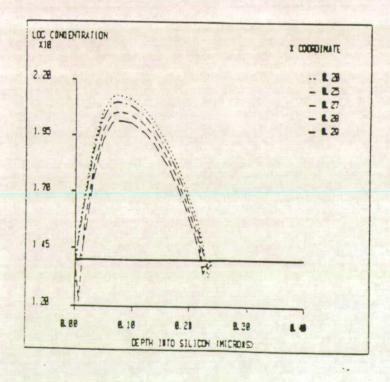

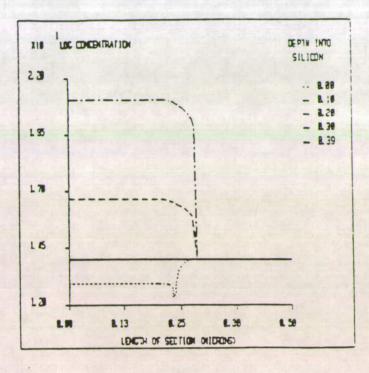

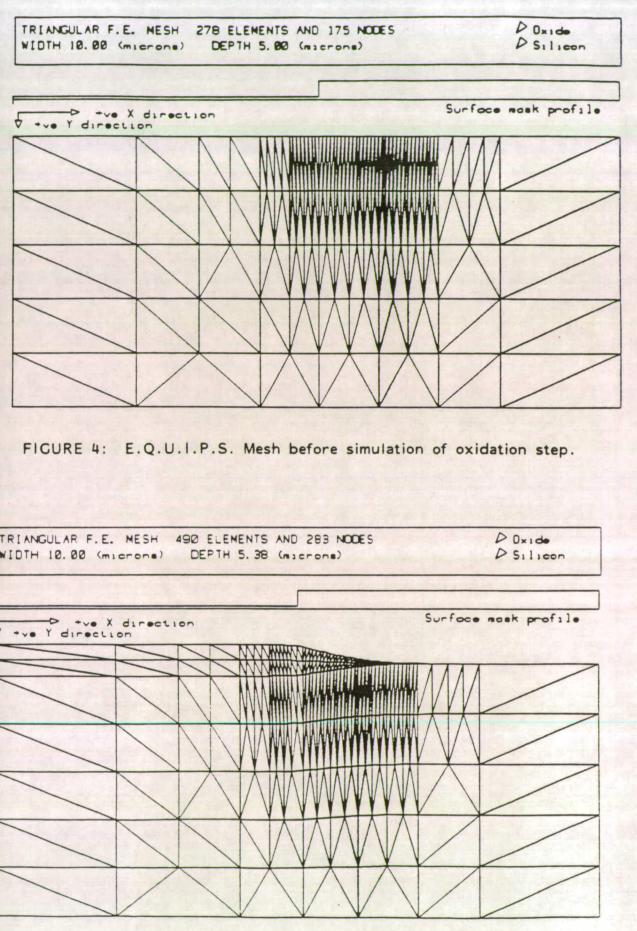

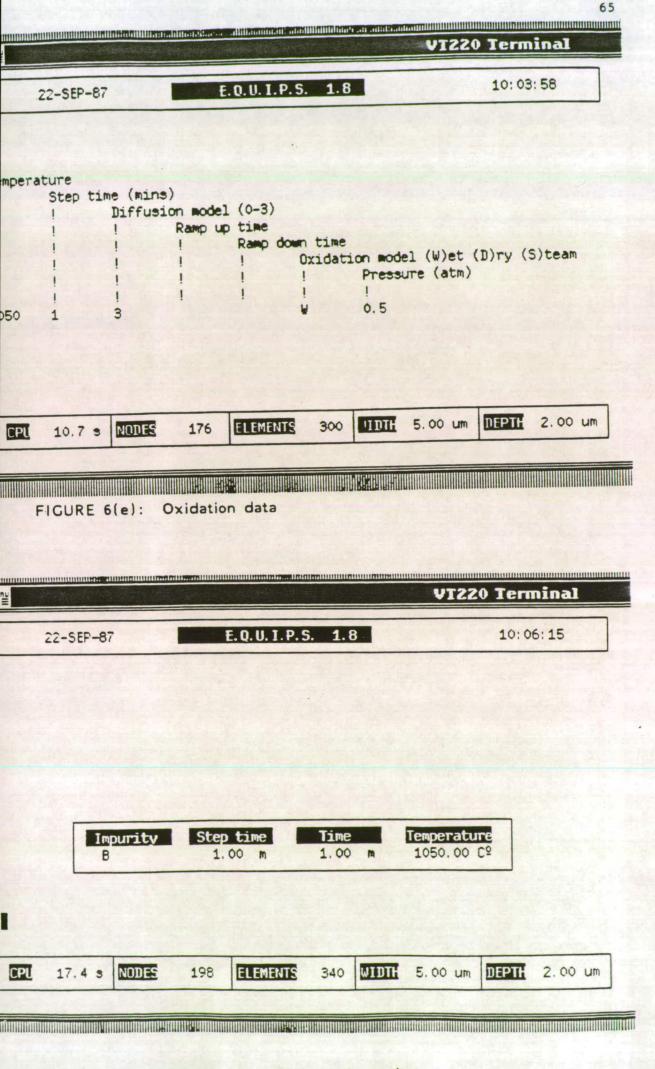

|     | 5.4.1 Process Modelling      | 127 |

|     | 5.4.2 Device Models          | 131 |

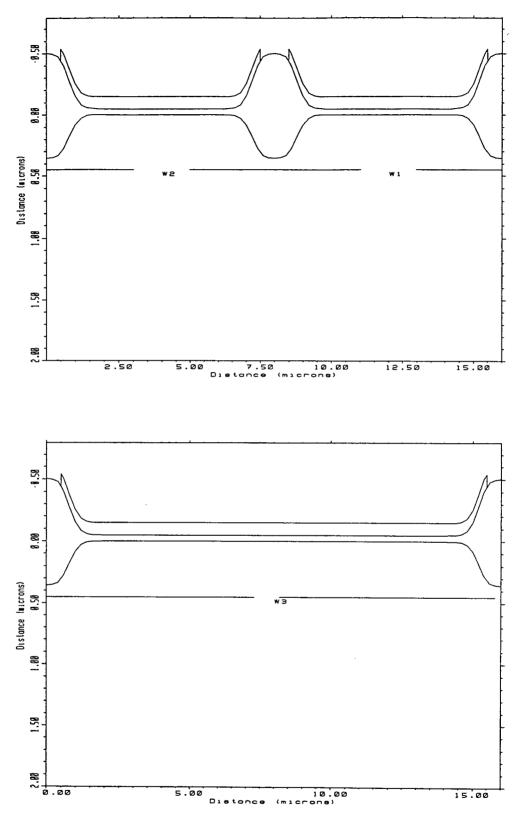

| 5.5 | NOVEL EXTRACTION STRATEGY    | 137 |

| 5.6 | SUMMARY                      | 140 |

| REF | ERENCES                      | 141 |

•

| 6 ELECTRICAL EXTRACTION                                 | 143 |

|---------------------------------------------------------|-----|

| 6.1 INTRODUCTION                                        | 143 |

| 6.2 SERIES RESISTANCE EXTRACTION                        | 143 |

| 6.3 WIDTH EXTRACTION I: $I_{edge} = 0$                  | 144 |

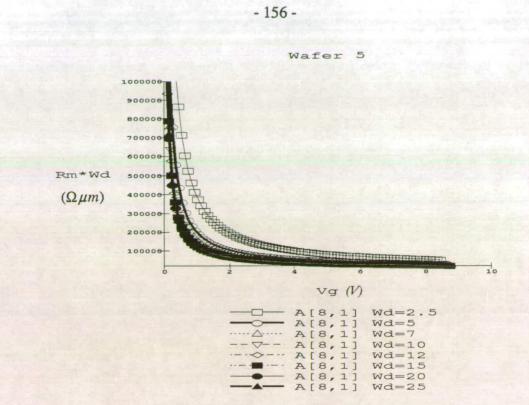

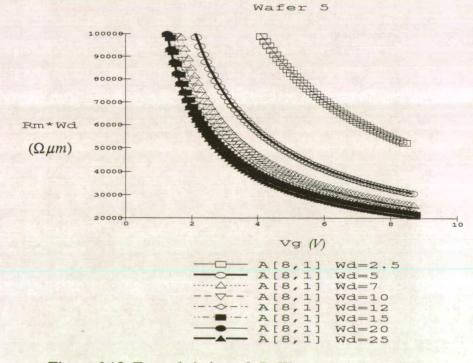

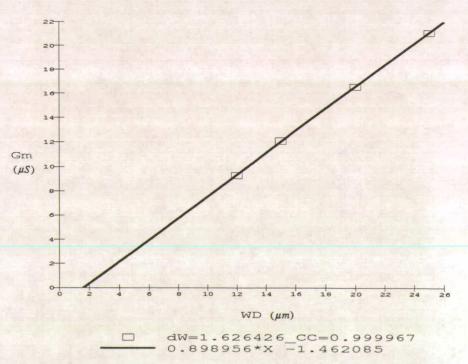

| 6.3.1 Channel Normalisation                             | 145 |

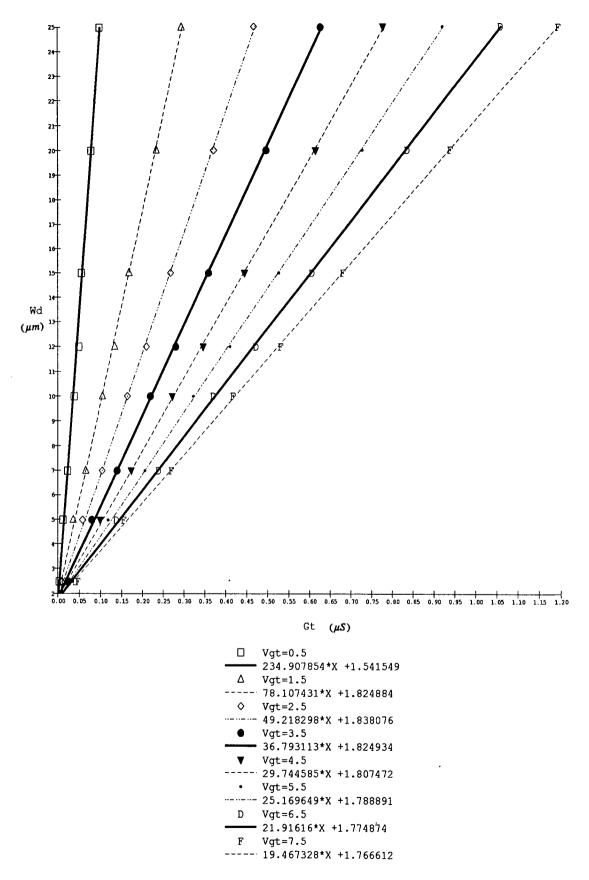

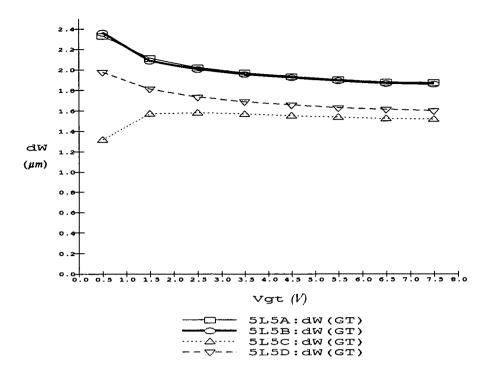

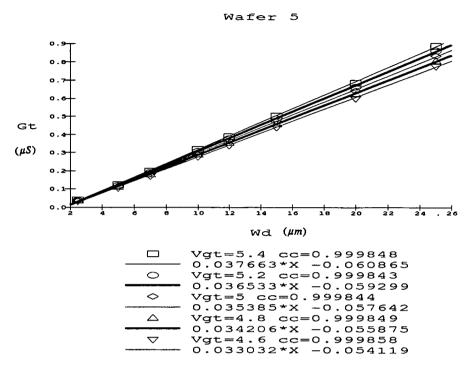

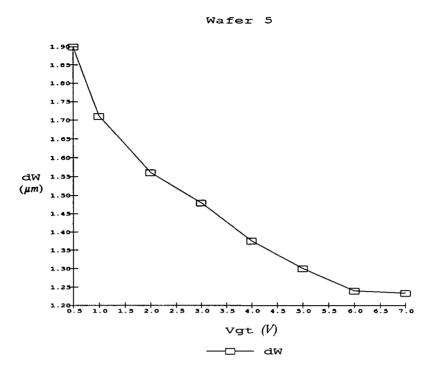

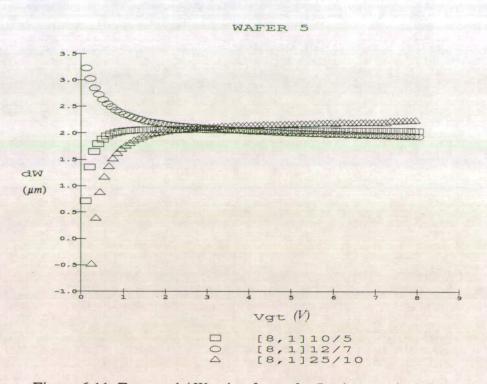

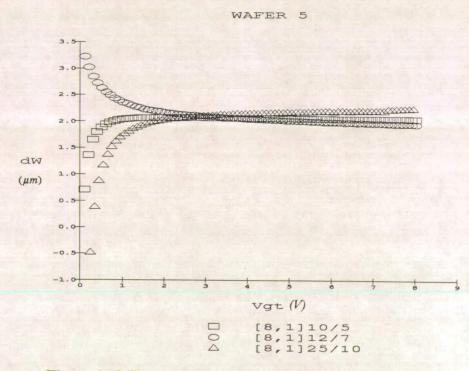

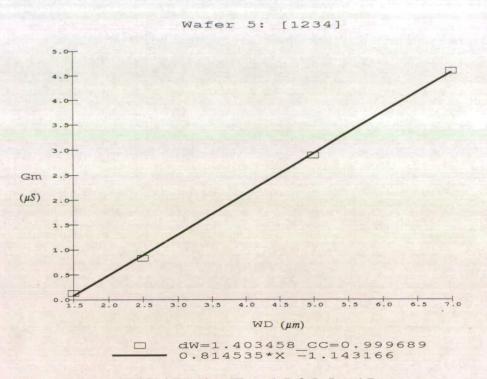

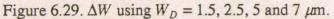

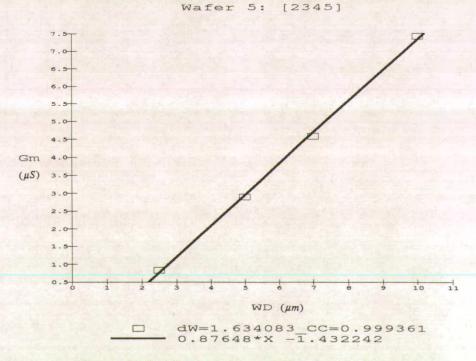

| 6.3.2 Channel Conductance Extrapolation                 | 148 |

| 6.4 WIDTH EXTRACTION I: $I_{edge} \neq 0$               | 151 |

| 6.5 ERRORS AND APPROXIMATIONS                           | 154 |

| 6.5.1 Channel Normalisation: Error In Series Resistance | 155 |

| 6.5.2 Channel Normalisation: Error In Threshold Voltage | 158 |

| 6.5.3 $G'_i$ Extrapolation: Errors In Series Resistance | 163 |

| 6.5.4 $G'_t$ Extrapolation: Errors In Threshold Voltage | 163 |

| 6.6 MEASUREMENT ANALYSIS                                |     |

| 6.6.1 Correlation Coefficient                           | 170 |

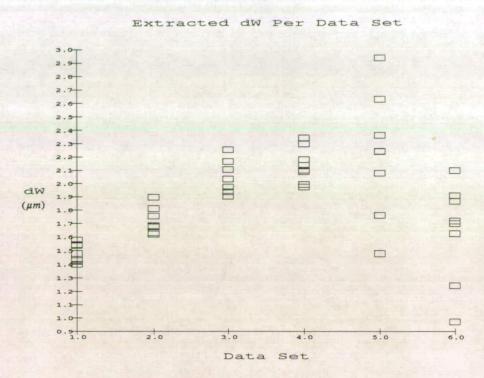

| 6.7 DATA SET SELECTION                                  | 171 |

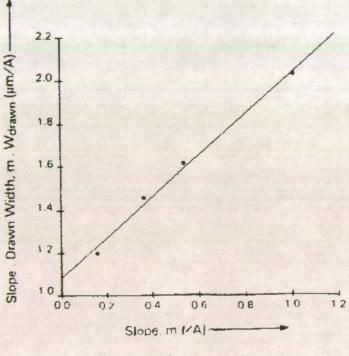

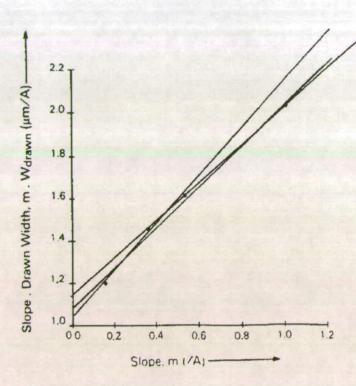

| 6.7.1 Extrapolation Using Two-Stage Processes           | 175 |

| 6.7.2 Data Set Optimisation                             |     |

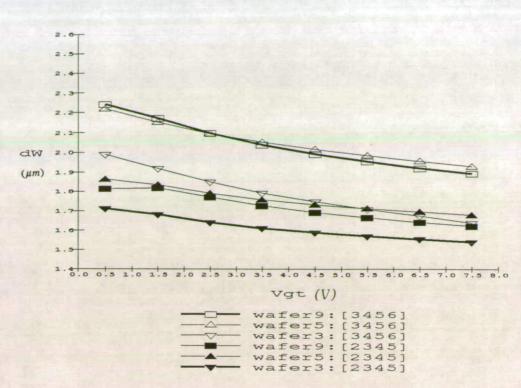

| 6.8 RESULTS                                             |     |

|   | 6.9 SUMMARY                         | 187 |

|---|-------------------------------------|-----|

|   | REFERENCES                          | 187 |

|   |                                     |     |

| _ |                                     |     |

| 7 | DISCUSSION AND CONCLUSIONS          | 189 |

|   | 7.1 INTRODUCTION                    | 189 |

|   |                                     |     |

|   | 7.2 RESULTS COMPARISION             | 189 |

|   | 7.3 REVIEW                          | 192 |

|   | 7.3.1 SEM                           | 192 |

|   | 7.3.2 Simulation                    | 193 |

|   | 7.3.3 Parameter Extraction          | 192 |

|   | 7.4 RECOMMENDATIONS AND FUTURE WORK | 194 |

|   | REFERENCES                          | 195 |

| APPENDIX | 196 |

|----------|-----|

|          |     |

•

| PUBLISHED PAPERS | PUBLISHED PAPERS |  | 217 |

|------------------|------------------|--|-----|

|------------------|------------------|--|-----|

Abstract

The shrinking dimensions of silicon microcircuits have reached the point where the vertical and lateral features are comparable in size. The consequence can be seen in each aspect of the manufacture of devices. The 2D layout of the physical routing becomes a convoluted maze when put into fabrication. The diminishing dimensions have focused greater attention on the edge effects since these play a proportionately greater role in the device performance. The consequences of the edge interactions can be categorised into two sections: those on the silicon surface and those on the subsequent layers.

The MOS transistor is directly impacted by the silicon surface profile. A fundamental parameter is the transistor width, which till recently has received little attention. This thesis correlates the different definitions commonly used, and investigates the impact of the individual processing parameters on the surface topography and consequently on the transistor width. Different measurement techniques are used and a novel extraction process is proposed.

The weakness of the current generic electrical extraction technique is exposed and recommendations made to overcome this. Further work on SEM sample preparation and processing is presented. -

I declare that all the work in this thesis is entirely my own unless otherwise indicated.

.

Martin Fallon

.

I would like to thank Dr A. J. Walton for his unstinting enthusiasm, A. M. Gundlach for his unfailing *joie-de-vivre*, R. J. Holwill for his good ear, and the staff of the EMF for their constant encouragement throughout.

I also wish to thank my wife, Susan, who has not known married life without the PhD.

Lastly I wish to thank big Sean for all his inspiration: And that's a fact

To my wife.

## Susan

.

'Writing a Ph.D. is easy - you just stare at a blank sheet of paper till drops of blood form on your forehead'

## List Of Symbols

| β                  | $q/k_BT$                          | $V^{-1}$                |

|--------------------|-----------------------------------|-------------------------|

| Ć <sub>ox</sub>    | oxide capacitance per unit area   | <i>Fm</i> <sup>-2</sup> |

| $C_{s}^{'}$        | silicon capacitance per unit area | $Fm^{-2}$               |

| $\Delta W$         | channel width reduction           | m                       |

| D                  | diffusion coefficient             | $m^2 s^{-1}$            |

| Ec                 | conduction band energy            | eV                      |

| E <sub>F</sub>     | Fermi energy                      | eV                      |

| Eg                 | band gap energy                   | eV                      |

| E <sub>v</sub>     | valence band energy               | eV                      |

| $\varepsilon_{ox}$ | permittivity of silicon dioxide   | $Fm^{-1}$               |

| E                  | electric field                    | $Vm^{-1}$               |

| G                  | conductance                       | $AV^{-1}$               |

| $G_P$              | parallel conductance              | $AV^{-1}$               |

| γ                  | body effect coefficient           | $V^{1/2}$               |

| I <sub>DS</sub>    | source-drain current              | A                       |

| I <sub>edge</sub>  | edge current                      | A                       |

| J                  | current density                   | $Am^{-2}$               |

| κ                  | scaling constant                  |                         |

| k <sub>B</sub>     | Boltzmann's constant              | <i>JK</i> <sup>-1</sup> |

| k <sub>s</sub>     | surface rate reaction constant    | $ms^{-1}$               |

| L                  | drawn channel length              | m                       |

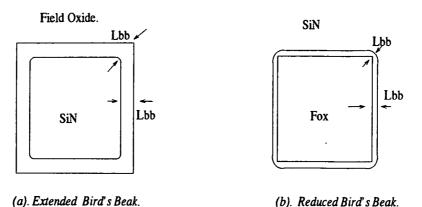

| L <sub>bb</sub>    | bird's beak length                | m                       |

| $L_{eff}$          | effective channel length          | m                       |

- xiv -

| μ                 | carrier mobility                          | $m^2 V^{-1} s^{-1}$     |

|-------------------|-------------------------------------------|-------------------------|

| $\mu_s$           | surface carrier mobility                  | $m^2 V^{-1} s^{-1}$     |

| $\mu_o$           | low field carrier mobility                | $m^2 V^{-1} s^{-1}$     |

| $\mu_c$           | chemical potential                        | V                       |

| n                 | n-carrier concentration                   | $m^{-3}$                |

| n <sub>i</sub>    | intrinsic carrier concentration           | m <sup>-3</sup>         |

| N <sub>A</sub>    | no. of acceptors per unit volume          | $m^{-3}$                |

| N <sub>D</sub>    | no. of donors per unit volume             | $m^{-3}$                |

| p                 | p-carrier concentration                   | m <sup>-3</sup>         |

| $\psi_s$          | surface potential                         | V                       |

| $\phi_{ms}$       | metal-semiconductor work function         | V                       |

| $\phi_F$          | Fermi potential                           | V                       |

| <i>q</i>          | electron charge                           | С                       |

| $Q_f$             | fixed oxide charge/ unit area             | $Cm^{-2}$               |

| Qot               | oxide trapped charge/ unit area           | Cm <sup>-2</sup>        |

| $Q_m$             | mobile oxide charge/ unit area            | Cm <sup>-2</sup>        |

| $Q_{it}$          | interface trapped oxide charge/ unit area | <i>Cm</i> <sup>-2</sup> |

| R <sub>P0</sub>   | width $\times$ resistance product         | $\Omega m$              |

| R <sub>chan</sub> | channel resistance                        | Ω                       |

| R <sub>x</sub>    | series resistance                         | Ω                       |

| ρ                 | charge density per unit volume            | <i>Cm</i> <sup>-3</sup> |

| T <sub>pad</sub>  | pad oxide thickness                       | т                       |

| $T_n$             | silicon nitride thickness                 | m                       |

| Τ                 | absolute temperature                      | К                       |

| τ                 | fitting factor                            | S                       |

| $	au_t$           | transit time                              | s <sup>-1</sup>         |

| $\tau_n$              | electron minority carrier lifetime | S               |

|-----------------------|------------------------------------|-----------------|

| $	au_p$               | hole minority carrier lifetime     | S               |

| θ                     | mobility modulation coefficient    | $V^{-1}$        |

| t <sub>ox</sub>       | oxide thickness                    | т               |

| U                     | recombination rate                 | s <sup>-1</sup> |

| v <sub>D</sub>        | drift velocity                     | $ms^{-1}$       |

| V <sub>DS</sub>       | drain to source voltage            | V               |

| V <sub>GS</sub>       | gate to source voltage             | V               |

| V <sub>t</sub>        | threshold voltage                  | V               |

| $V_{G_i}$             | voltage above threshold            | V               |

| W <sub>D</sub>        | drawn width                        | т               |

| W <sub>eff</sub>      | effective width                    | m               |

| <i>x</i> <sub>n</sub> | n region junction depth            | m               |

| <i>x</i> <sub>p</sub> | p region junction depth            | т               |

. •

.

•

### Chapter 1

# Introduction

#### 1.1. Historical Background

#### **The Computer**

As a calculating machine, the computer has existed for thousands of years. The fundamental principles upon which computers are based, are those of mathematics, whereby every complex computation can be reduced to addition and subtraction, and for that matter subtraction is nothing more than the opposite of addition. Thus it was the manual dexterity of the operator that limited the performance of the first computer, the abacus. It was not until 1822 with the realization of a proposal by the mathematician Charles Babbage, which produced a mechanical counting machine, that a new step had been taken in computer technology. His suggestion to mechanize the long, tedious calculations necessary to produce the nautical and astronomical charts of the day was embodied in "Babbage's Engine" [1] which successfully counted and carried by means of gearing. His failure to produce a universal machine rested on the intricate gearing necessary but unobtainable at that time.

In 1930, Vannevar Bush at MIT built a mechanical computer which was driven by electric motors. A World War II problem led to the first electronic computer. A means was sought to calculate quickly ballistic tables for a wide variety of shells. J. W. Mauchly and J. P. Eckbert at the University of Pennsylvania tackled the project. The result was the Electronic Numerical Integrator and Calculator, ENIAC [2]. ENIAC weighed over 30 tons, occupied  $150m^2$  of floor space, used 18,850 vacuum tubes and required 150 kW to keep it operating. The world's first electronic computer was completed in 1946.

On 23rd December 1947 at Bell Labs, John Bardeen and Walter H. Brattain demonstrated the transistor which sounded the death knell for the technology of ENIAC. Along with William B. Shockley, they were awarded the Nobel prize, for what is arguably the most significant technological development of this, or any other, century.

#### 1.2. The Transistor

.

The Field Effect Principle upon which this was based had been proposed as a means of producing amplifying devices as early as the 1926 by Lillenfield and 1938 by Heil[3]. In 1945 Shockley suggested making a semiconductor amplifier based on this principle. Early experiments failed, however, and it was Bardeen's suggestion of electron trapping in surface states and the possibility of an inversion layer which led to the publication by Bardeen and Brattain in 1947 of the point contact transistor [4].

The development of the transistor, *per se*, would not have been sufficient to produce the unheralded growth in the industry. The properties of semiconductors and pattern transfer were the key to the integration of discrete components. In 1958, J. S. Kilby of Texas Instruments produced the first I.C. using black wax to mask etching of mesas to produce the active elements [5]. The advantages of this technology over valves were enormous. Valves were costly, bulky and unreliable; of limited life and dissipated large amounts of power; they also had to be manually integrated by solder connections to other components. Interest in semiconductors proliferated. In 1960, Kahng and Atalla fabricated the first modern surface field effect transistor [6] and in 1961 P. K. Weimer presented the first evaporated thin film transistor [7]. Reference 7 is a collection of the early publications in this field.

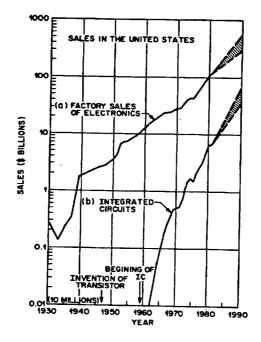

From a point start three decades ago, worldwide sales of I.C.s have risen to \$46.65billion in 1991 [8].

Figure 1.1 charts this growth.

Figure 1.1. Factory sales of I.C.s. [9]

The wide interest generated further technological advances which facilitated continued miniaturisation and integration. Table 1.1 highlights the process innovations, between conception and introduction into manufacturing.

#### **1.3.** Miniaturisation

#### 1.3.1. Motivation.

In any industry, technology change is motivated by cost. The continual change in the semiconductor industry is to reduce the size of the devices. In the early days of the industry the benefits of size reduction were evident. Communication electronics in the heavy bomber of the 1940s comprised 25% of the payload. Miniaturisation

| History Of Technology Discontinuities |                |                    |  |  |

|---------------------------------------|----------------|--------------------|--|--|

| Tool or Technology                    | Year Developed | Year in Production |  |  |

| Silicon Epitaxy                       | 1960-61        | 1964               |  |  |

| Atmospheric SiN                       | 1965           | 1967-68            |  |  |

| Ion Implant                           | 1969           | 1973               |  |  |

| TiW                                   | 1969           | 1973               |  |  |

| Schottky TTL                          | 1970           | 1974-7             |  |  |

| CCDs                                  | 1970           | 1981               |  |  |

| RIE                                   | 1975-76        | 1980               |  |  |

| Advanced Schottky                     | 1976           | 1980               |  |  |

| Polysilicon emitter                   | 1976           | 1984-85            |  |  |

| Refractory Gate                       | 1976           | 1983               |  |  |

| SOI - Ion Implant                     | 1978           | 1989               |  |  |

| Trench                                | 1979           | 1989               |  |  |

| Silicide                              | 1978           | 1985               |  |  |

| LDD                                   | 1980           | 1986               |  |  |

| TiN Local Strap                       | 1986           | 1988               |  |  |

Table 1.1. Technology Developments.[8]

was then an economic must. In the electronics of to-day's microchip, the economics are still the driving force but the reasons are more subtle.

The planar process which is used for I.C. fabrication produces uniform device features across a whole wafer. It is the most successful and least recognized example of automation ever produced. Because the devices are 'batch produced' on a single chip, the chips 'batch produced' on a single wafer, and the wafers batch produced in lots of 25 or 50, the cost of processing one device diminishes as the number of devices/wafer increases.

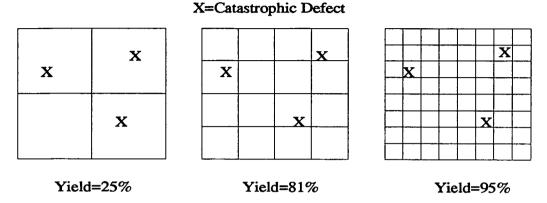

Another reason for this can be seen in Fig 1.2.

Figure 1.2. Chip size and yield.

A continual war is being fought in the fabrication line against particulate. When chip sizes are large, a larger proportion of chips are lost due to a fixed number of contaminant particles. Thus the yield can be increased dramatically as the device dimensions reduce. So it was that the industry saw the introduction of large scale integration (LSI), (>  $10^3$  components/chip), in the 1970s and VLSI (>  $10^4$  components/chip) in the late 1970's.

The benefits of 'downscaling' are seen as higher speed, increased functionality and lower cost. The DRAM production is the driving force in developing new technology to meet the requirements of the shrinking device. Every 3 years a new DRAM with a ×4 increase in bit density appears on the market as the previous generation begins to wane. At Texas Instruments in late 1990, the 256Mbit DRAM arrived at the research stage, the 64Mbit was in development, and the 16Mbit in product characterisation. The 4Mbit was then ramping up to full manufacture. These 4 phases comprise a 10 year cycle, when with the introduction of the 1024Mbit to the research stage, the sequence will shift down one step [10].

#### 1.3.2. Scaling.

The inexorable drive to smaller devices has continued towards the fundamental physical limits which must define an end point to the present basic structures. For example, as feature sizes become comparable to the wavelength of light, the seeming elasticity in the limits of optical lithography will mean that its domination over X-ray and e-beam systems must yield eventually. The study of size reduction has produced the principle of scaling whereby all lateral and vertical dimensions are reduced by a factor of  $\kappa$ . Beyond this, two options are open. These and their consequences are shown in Table 1.2.

In the first instance of 'constant voltage', all the physical dimensions within the circuit are scaled down by a factor of  $\kappa$ , but the supply and threshold voltages are kept constant. Substrate doping must be increased by a factor of  $\kappa^2$  also, to scale the depletion widths around the source and drain junctions. The constant supply voltage across a reduced gate length increases the power per gate by a factor of  $\kappa$ . Since the gate density increases by a factor of  $\kappa^2$ , the power density increases by a factor of  $\kappa^3$ . Applying these rules and projecting gate lengths down to 0.5  $\mu$ m, it would appear from geometric considerations, to be possible to put 800,000 gates on a  $6 \times 6mm^2$  chip. If this were done however, the power dissipation would be of the order of 1 kWatt.

The other option of constant field scaling overcomes this problem by maintaining a constant power density, but results in system-incompatible supply voltages and reduced noise margin in threshold voltages. In practice, a recipe for scaling is produced by some massaging of these two scaling principles. This however begs the question: how large can  $\kappa$  become? This is essentially asking what the minimum effective channel length can become. A rough approximation can be

| Paramater                  | Constant Voltage | Constant Field |

|----------------------------|------------------|----------------|

| Feature Size               | 1/κ              | 1/ <i>ĸ</i>    |

| Gate/Field Oxide Thickness | 1/ĸ              | 1/ <i>ĸ</i>    |

| Gate Capacitance           | 1/ <i>ĸ</i>      | 1/ <i>ĸ</i>    |

| Junction Depth             | 1/ĸ              | 1/ <i>ĸ</i>    |

| Substrate Doping Conc.     | $\kappa^2$       | κ              |

| Poly Sheet Res.            | ĸ                | ĸ              |

| Linewidth                  | 1/ <i>ĸ</i>      | 1/κ            |

| Transistor Gain            | ĸ                | ĸ              |

| Supply Voltage             | 1                | 1/κ            |

| Enhancement/Deplt $V_T$    | 1                | 1/κ            |

| Current/Gate               | к                | 1/κ            |

| Relative RC                | 1                | 1              |

| Power/Gate                 | 1/ <i>ĸ</i>      | $1/\kappa^2$   |

| Power Density              | $\kappa^{3}$     | 1              |

| Gate Density               | $\kappa^2$       | $\kappa^2$     |

| Gates for 1W               | 1/ <i>ĸ</i>      | 1              |

Table 1.2 Scaling Factors [11]

obtained by imposing 2 limitations on the MOSFET [10] :

1.  $L_{\min} > 2 \times$  drain depletion width

2.  $N_A$  must support the drain junction for the supply voltage.

For typical values

$$N_A = 1.5 \times 10^{17}, V_{DD} = 5V, L_{\min} = 0.18 \mu m$$

Other proposals have been suggested based on maintaining long channel characteristics. Ratnakumar and Meindl, [12] set the criterion that the change in threshold voltage be less than 10%, while Brews *et al* [13] set a 10% relative limit on increased drain current at  $V_G = V_T$ , as  $V_D$  is increased.

These approaches assume that the fundamental structures remain as they are. The expected limit beyond which radical change is necessary is the 1Gbit device whereupon physical limits and quantum mechanical effects will be significant.

#### **1.3.3.** Non-Scaleable Constants

Whilst scaling principles may be applied to devices, and judicious selections may provide an operating compromise, some features remain stubborn to miniaturization.

The increased complexity in topography has focused attention on interconnect. The maze of wiring can now surpass the chip area several times over. As shown in table 1.2, the *RC* time constant does not scale. Therefore, as chip sizes and layer numbers increase, the *RC* product becomes unacceptably large. This problem has been attacked through the use of alternative materials, most notably in the area of refractory metal silicides [14]. Accompanying this problem is the increase in the number of contacts and contact resistance, the latter increasing by  $\kappa^2$ . This again can be addressed by materials and process development in the first instance.

A common problem for interconnect and device scaling is that of edge-effects. As dimensions reduce and complexity increases, edge-effects play a significantly larger role in performance specification. There are two reasons for this.

(i) Firstly, an increase in the number of layers produces awkward topography, through which the interconnect tracks must route. This increases the unwanted parasitic capacitances. Also, since it may not be possible to reduce the thickness of the film due to step coverage constraints [15] and the length of interconnect may increase rather than decrease, the edge electric fields form a larger percentage of the total electric field. In this case thoughtful layout can improve device performance.

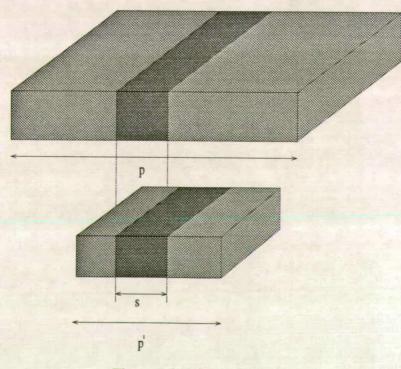

(ii) Secondly, as line/space pitch is reduced the transition or overlap between the two remains constant. The effect of scaling by  $\kappa$ , then, is to increase the region of transition by  $\kappa$  also.

This can be seen in figure 1.3 where the pitch, p, is scaled to p' by the scale factor  $\kappa$ . The transition region s does not scale and therefore, since,

$$p' = \kappa p$$

then

$s/p' = \kappa s/p$

Figure 1.3. Effect of Scaling.

At some point, this increase will become intolerable and a new technology will be

forced. In the MOS transistor structure, this effect is seen in two places. Firstly, the gate-drain overlap remains fixed for a geometric scaling. The theoretical reduction limit here is constrained by twice the depletion depth as discussed in section 1.2.2. Secondly, the active area-isolation transition also remains fixed. This region of the device defines the width of the MOSFET and has till recently been regarded as a second order effect compared to the gate length parameters. With the advent of VLSI this can no longer be the case and forms the subject matter for this thesis.

#### 1.4. Thesis Outline

#### **1.4.1.** Thesis Motivation

As the device dimensions have reduced, the feature sizes have become comparable with that layer thickness. This has had a three-fold impact on fabrication.

- (i) The complex topography now faces difficulties in processing, requiring planarization and edge tapering.

- (ii) The measurement of the feature size is difficult since the edge of the feature is no longer clearly defined.

- (iii) The steps and corners produced during fabrication can result in high electric fields as these points and edges mirror the lightning rod phenomena, acting as a focus for electric field lines.

The last of these three is perhaps the most subtle, since the effect cannot be seen till the process is complete. Since many features are now measured electrically, these edge effects must now also be examined. The surface topography examined herein is that produced at the initial stage of processing, impacting single transistor performance and defining the topography of the first layer. The process studied is the LOCOS process. This was invented in 1970 and despite a plethora of alternatives is still in use even at small geometries.

#### 1.4.2. Thesis Content

Chapter 2 reviews isolation technologies currently available and discusses the LOCOS processing parameters and their impact on the bird's beak profile.

Chapter 3 discusses the basic device physics, focusing on the parameters which are chosen to characterise a MOST.

Chapter 4 reviews state-of-the-art work in the area of width parameter extraction. The impact of the constituent process steps which define the device in cross section are also examined.

Chapter 5 describes the experiment and presents the topographic profiles obtained by SEM cross-section from actual devices. Both process simulation and device simulation results are presented. A novel electrical parameter extraction technique is proposed to permit direct comparison with the simulation results.

Chapter 6 contains the results of electrical measurement. The effective width of the MOSFET is examined with respect to processing parameters and its sensitivity to gate voltage. Detailed analysis of the electrical techniques is performed.

Chapter 7 is presents the conclusions and a final discussion of the results.

#### References

- 1. H.I. Sharlin, in *The Making Of The Electrical Age*, Aberlard-Schuman Press.

- 2. J. J. Staller and A. H. Wolfson, "Miniaturisation In Computers", in *Miniaturisation*, ed. H. D. Gilbert, Rienhold Publishing, New York.

- 3. J. Nishizawa, "The Transistor A Look Back And A Look Ahead", Solid State Technology, Dec 1987.

- 4. J. Bardeen, Solid State Technology, Dec 1987.

- J. S. Kilby, "The Invention of the Integrated Circuit", IEEE Trans. On Electron Devices, vol. Vol ED-23, no. 7, July 1976.

- D. Kahng, "A Historical Perspective On The Development Of MOS Transistors And Related Devices", *IEEE Trans. On Electron Devices*, vol. ED-23, no. 7, July 1976.

- 7. P. K. Wiemer, *The TFT A New Thin-Film Transistor*, Holt, Rheinhart and Winston Inc, New York. Reprinted in "Micro and Thin Film Electronics"

- 8. J. Handelman, Semiconductor International, Jan 1991.

- 9. S. M. Sze, in VLSI Technology, McGraw-Hill.

- J. Meindl, "Opportunities For Gigascale Integration.", Solid State Technology, Dec 1987.

- 11. "DRAM Manufacturing In The 90's", Semiconductor International, May 1991.

- K. N. Ratnakumar and J. D. Meindl, "Short Channel MOST Threshold Model", IEEE Journal of Solid State Circuits, vol. SC-17 (5), Oct 1982.

- W. Fichtner, E. H. Nicollian, S. M. Sze, and J. Brews, "Generalized Guide for MOSFET Miniaturization", *IEEE Electron Device Letters*, vol. EDL -1,2, 1980.

- 14. S. Murarka, in Silicides for VLSI Fabrication., Academic Press, New York.

- 15. R. T. Bate, "Nanoelectronics", Solid State Technology, Nov 1989.

### Chapter 2

## **Isolation Processing**

#### 2.1. Introduction

The isolation regions in any chip are essentially wasted space and it is therefore highly desirable to reduce these areas. The function of the isolation region is to prevent cross-talk between transistors. In practice however, the demands made on the technology are high. Ideally all of the following must be satisfied:

- (i) Negligible leakage current between active devices

- (ii) Minimal 'wasted' space

- (iii) Controllable process

- (iv) No impact on active device characteristics

- (v) Minimal mask offset.

- (vi) In some cases, temperature and radiation hard.

Traditionally, two approaches have been used. One of these uses junction isolation and the other oxide isolation. The former was favoured in bipolar technology and the latter in MOS. In MOS, the leakage paths are primarily localized at the semiconductor surface, so the oxide isolation is preferable. Combinations of these two techniques are increasingly used, in both bipolar and CMOS technology and with the advent of BiCMOS processes this trend has continued. There are basically two current approaches to VLSI isolation. One provides an oxide thick enough to prevent surface inversion and the other is trench isolation which is analogous to the junction isolation process, whereby deep trenches in the silicon are filled with a dielectric. This more recently developed process has, in solving some problems, introduced others of its own, particularly in reducing these leakage paths round the interface.

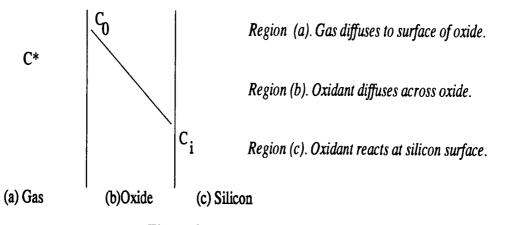

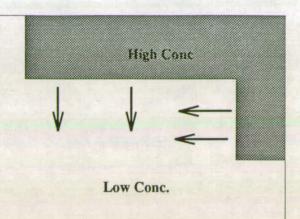

#### 2.2. Oxidation

Thermal oxidation of silicon was first proposed in 1959 by Atalla [1] for use as a gate dielectric, though it was 5 years later before the problematic ionic contaminants were identified and eliminated to establish the process as an industrial concern [2]. The mechanism of the oxidation process was examined by Deal & Grove [3]. They produced a model based on equating the three fluxes as shown in figure 2.1: the flux from the gas to the surface,  $F_1$ , the flux across the oxide  $F_2$ , and the flux corresponding to the reaction at the interface,  $F_3$ .

Three initial equations were used.

$$F_1 = h(C^* - C_0) \tag{2.1}$$

$$F_2 = -D_{eff}(\frac{dC}{dx}) \tag{2.2}$$

$$F_3 = k_s C_i$$

where

h is the gas-phase mass transfer coefficient

$C^*$  is the concentration of the oxidant in the gas

$C_0$  is the concentration of the oxidant in the outer surface of the oxide

$D_{eff}$  is the effective diffusion coefficient of the oxidant in the oxide.

$\frac{dC}{dx}$  is the concentration gradient of the oxidizing species in the oxide.

$C_i$  is the concentration of oxidant in the interface

$k_s$  is the surface rate reaction constant

Equating these fluxes produced the linear-parabolic oxidation law:

$$x_0 + Ax^2 = B(t + \tau)$$

(2.4)

where

$x_0$  is the oxide thickness grown

t is the time

$\tau$  is a fitting factor for thin oxides

B is the parabolic rate constant

B/A is the linear rate constant

B and B/A can be expressed in terms of the parameters in (2.1), (2.2) and (2.3)

This model works well for oxides down to about 25 nm and exponential terms have been added to extend this model for thinner oxides [4]. It is however a one dimensional model and as will be seen the 2D (and 3D) effects play a different but important role in the isolation process.

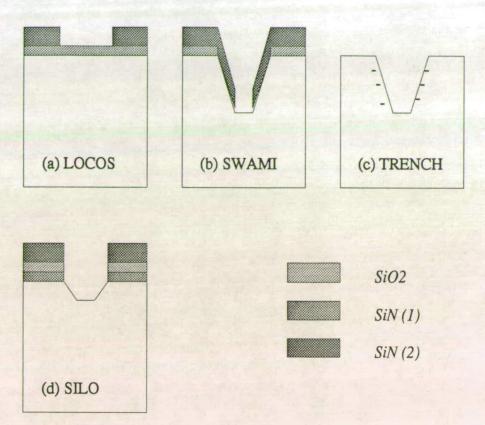

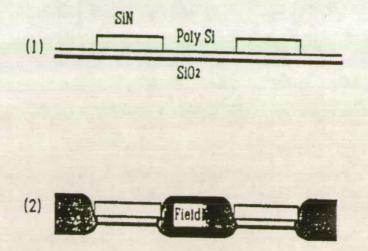

#### **2.3. LOCOS**

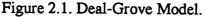

Early isolation techniques used a thick field oxide through which a window was cut for the active area, producing a steep transition between active area and field. This proved problematic later in the process, giving rise to weak spots in the metallization. In 1970, Philips Research Laboratories published a new oxide isolation process which took advantage of the difference in oxidation rates of silicon and silicon nitride. With a rate of oxidation approximately 2 orders of magnitude lower, silicon nitride proved to be an excellent oxidation mask. The process is outlined in Figure 2.2. This process for selective or local oxidation of the silicon regions was given the acronym LOCOS. - for *LOCal Oxidation of Silicon*. The advantages here are three-fold.

- (i) A better window definition is achieved.

- (ii) The field inversion implant is self-aligned to the isolation mask

- Because the oxide is semi-recessed, the thickness can be increased without step cover problems.

The process proved to be the workhorse for the industry, though with the advent of LSI, inherent problems became more apparent. The transition region between active area and field is not abrupt and is characterised by the 'bird's beak' profile. This arises from the diffusion of oxidant under the edge of the nitride mask and thence to the silicon substrate where oxidation takes place. The bird's beak feature is approximately the same dimension as the thickness of field oxide grown. The rigidity

Figure 2.2. The LOCOS process

of the nitride layer can lead to stacking faults in the silicon and enhanced diffusion can occur during the oxidation processes.

#### 2.3.1. White Ribbon

Another feature of the LOCOS process was the white ribbon. The term was used because through an optical microscope it looked like a white ribbon surrounding the isolation region, extending about 1  $\mu$ m into the active area [5]. In fact, it turned out to be a thinning of the oxide in the active area. The reduction of thickness of the gate oxide introduced a reliability problem, with this region susceptible to low breakdown.

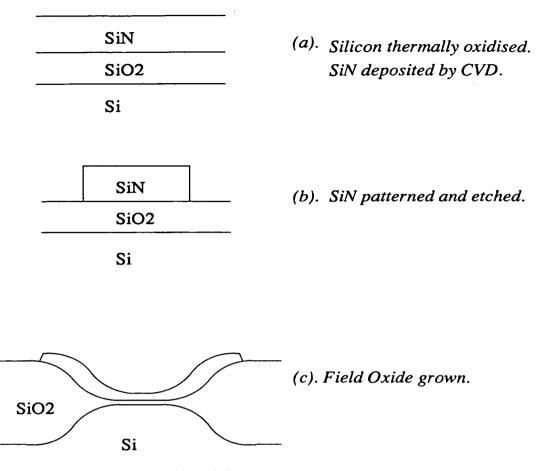

The mechanism for this phenomena is shown in figure 2.3.

$Si + H20 \rightarrow SiO2 + H2$

Figure 2.3. White Ribbon Formation.

Diffusion of OH or  $H_2O$  from the ambient to the underside of the SiN layer reacts to produce  $SiO_2$  and  $NH_3$ . Subsequent diffusion of the  $NH_3$  to the substrate enables the reaction with the silicon to occur and the formation of  $Si_3N_4$  and  $H_2O$ . The newly formed SiN at the substrate inhibits oxidation from occuring. Nakajima *et al* [6] showed a similar effect in the body of the active area, away from the bird's beak. Here the  $NH_3$  produced at the surface of the SiN layer was seen to diffuse through the nitride layer itself to produce defects in the substrate. This problem can be overcome in both instances by oxidising in a dry ambient. However, as the field oxide is the thickest thermal oxide grown during the process, the time factor is critical. SiN etching fails to remove this defect consistently and similar problems are seen when the SiN is crystalline as opposed to amorphous [7].

The solution to the problem is to use a second, wet, sacrificial oxidation performed prior to the gate oxidation [8].

#### 2.3.2. 2-D Profiles

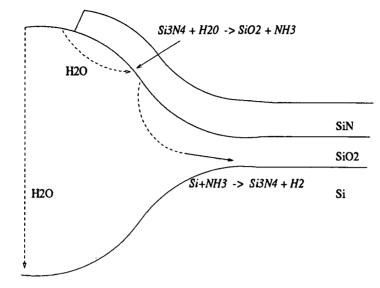

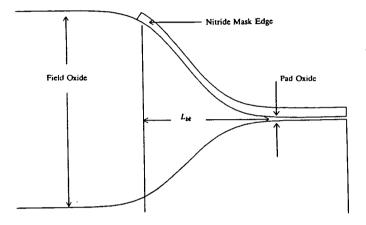

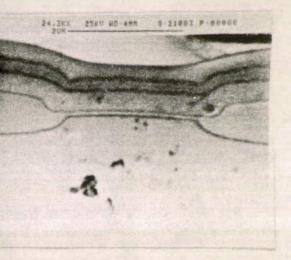

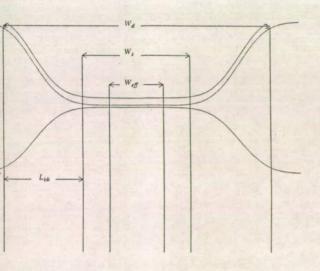

The importance of the bird's beak transition from active area to field increased as feature sizes became comparable to layer thicknesses. Using a similar approach to the Deal-Grove 1-D model, Wu *et al* [9] developed a 2-D equation relating processing parameters to the topographic profile of the bird's beak. Figure 2.4 shows the LOCOS profile with the parameter definitions.

Figure 2.4. LOCOS dimensional parameters -

Equation (2.5) shows an exponential decay of bird's beak height against distance into the active area. Five processing parameters can be examined as to their individual or combined impact on the profile.

$$\frac{R(y,t)}{R_o(t)} = \frac{C_s(t)}{C_i(t)} \left[ \frac{1}{\left(1 + T_{pad} \frac{k_s}{2D}\right)} \right] \exp\left(-\Gamma y\right)$$

(2.5)

where

$$\Gamma = \left[\frac{k_s}{T_{pad}D} \frac{1}{1 + \frac{T_{pad}k_s}{2D}}\right]^{1/2}$$

(2.6)

As can be seen, similar terms are present in this model as in the 1-D Deal-Grove model, with rate limiting terms such as surface rate reaction, diffusion coefficient and concentrations appearing. The left hand side relates the ratio of oxidation rate at a distance y along the surface of the silicon, under the nitride mask, to the oxidation of the unmasked region. The equation predicts an exponential decay of the growth rate under the nitride mask. This model proved successful but demonstrated the complexity of the processing conditions. An alternative approach was used by Guillemot et al [10] who began with experimentally determined profiles and fitted equations to these using empirical parameters. In so doing, another processing parameter was included: the thickness of the silicon nitride. The nitride film is usually a dense, rigid film. The expanding oxide under the delineated edges lifts the nitride resulting in the bird's beak. A thick nitride film will suppress this but too thick a film will crack. As may be expected with such a large number of process variables, trade-offs must be made. The nitride film must be thick enough to act as an oxidation barrier. Thick nitride also acts as a diffusion barrier to the  $NH_3$  responsible for the defects in the gate oxide [6] and further reduces the bird's beak.

Using this approach the experimentally observed "step" in the silicon surface as a result of the field oxidation could be included. These sharp corners could not be predicted from the initial analysis by Wu [9] since no nitride stress effects were included in the model. The topographic step, or kink, is seen according to the  $T_{pad}/T_n$ conditions and may impact the electrical performance of the device.<sup>†</sup>

Another subtle effect which may only be evident by its consequences on electrical characteristics is the stress in the nitride film which produces dislocations and defects in the silicon crystal. This is produced, not by the difference in thermal expansion of the silicon and silicon nitride, but by coulombic forces arising from the  $\frac{1}{7}$  Discussed in Chapter 4.

mismatch of the two layers at their interface [11]. This will impact dopant diffusion and consequently produce uncertainty in the final device performance. The presence of the intermediate pad oxide in the silicon - silicon nitride sandwich acts as a stress relief layer to alleviate this problem. Further, direct deposition of nitride onto silicon can result in doping of the surface with n-type material during the nitride removal in  $H_3PO_4$  [12].

Guillemot's motivation in this approach was to produce an analytical model for computer simulation. Thus a defined range of interest of input parameters was necessary to produce a look-up table. The sole advantage over the numerical models available is in the CPU time. However the disadvantages is in the limited range of usefulness. Current numerical simulation models incorporate stress effects of both nitride and oxide. The evaluation of stress in the nitride layer can be measured across the wafer according to the amount of wafer bending, but this value can increase dramatically when the wafer is patterned, resulting in different, localised stress values.

Oxide has till now been modelled as a non-viscous, incompressible material. However it has been recognised that the oxide may flow at temperatures around 950°C [13]. Viscous flow will relieve the stress in the oxide layer and reduce the number of point defects introduced into the substrate and the subsequent impurity diffusion. Point defect diffusion is orders of magnitude greater than substitutional diffusion and consequently must be minimised, to allow control at small geometries.

The number of input processing parameters which influence the bird's beak profile means that a lot of experimental work is necessary to produce a definitive calibration table. Table 2.1 shows the qualitative interactions between the major parameters

| Parameter               | $T_{pad}$ | $T_N \uparrow$ | k <sub>s</sub> ↑ | Temp ↑ | $F_{ox}\uparrow$ | Press ↑ |

|-------------------------|-----------|----------------|------------------|--------|------------------|---------|

| $\frac{L_{bb}}{F_{ox}}$ | ↓         | 1              | ↓                | Ļ      | ↓                | ſ       |

Table 2.1. Effect of process parameters on bird's beak.

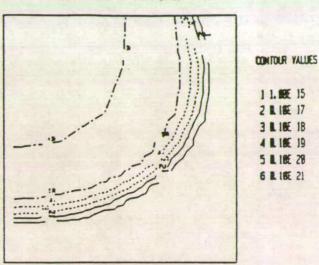

## 2.3.3. 3-D Profiles

The compressive pressure of the nitride mask, which causes the retardation of the oxide growth below the mask edge, can be seen to vary according to the pattern etched in the film. Van der Plas *et al* [14] demonstrated possible geometrical cases whereby the bird's beak profile will vary across the circuit. These are identified as

- (i) Convex corners where the oxidant can diffuse from a greater solid angle thus increasing the oxidation rate at this corner.

- (ii) Concave corners where the solid angle open to the oxidant is reduced causing a reduction in the bird's beak.

- (iii) Narrow mask features which are more resistant to bending thus reducing the beak length

- (iv) Narrow mask openings, which were also studied by Mizuno *et al* [15] and results in a field oxide thinning but maintains the length of the beak.

Hand-in-hand with the effect of reducing the solid angle open to the oxidant is an increased resistance of the mask to bending. These results are seen in the hole and island structures studied by [16] and are shown in figure 2.5. One consequence of this is that packing density will be severely impacted, since the extension of the bird's beak at the corner may be 2-3 times that of a long mask edge.

(b). Actual Dira

Figure 2.5. Geometry Dependent Bird's Beak

A final parameter impacting this feature is the etch back of the oxide after field oxidation. Since this is usually done with a wet isotropic etch, etching beyond the surface of the silicon can be rapid, and can have serious consequences on the electrical characteristics of the transistor. Thus a compromise must be reached, whereby the etch-back leaves a small bird's-beak in the wide openings to avoid overetching the narrow openings.

#### 2.4. LOCOS Alternatives.

## 2.4.1. General

The drive for alternatives was motivated by the length of the bird's beak. Since this feature was approximately  $1\mu m$ , the drawn active area size would of necessity, have to be larger to achieve the dimension on the wafer. i.e. incorporating  $1\mu m$  loss of feature size on either side of the active area, set a  $+2\mu m$  offset on the drawn dimension. Further, as shown by Mizuno [15] oxidation windows below  $1\mu m$  showed a sharp attenuation of field oxide thickness. Therefore, on purely topographical grounds the minimum pitch must be  $3\mu m$  greater than the desired final active area width. Since this  $3\mu m$  serves no other function than isolating active devices, it is seen as an undesirable overhead. Because of these limitations other approaches have been suggested. The option of producing a planar process was an attractive one, since the subsequent layer depositions would avoid step coverage problems, and eliminate potential weak spots. The alternatives can be classified into 2 main groups. The first of these consists of a silicon etch prior to field oxidation, whereas the second uses a polysilicon buffered layer which can be selectively oxidised to produce the field oxide.

## 2.4.2. Silicon Etch Processes

The option of etching the silicon prior to field oxidation to provide a more planar structure was presented by Appels et al in the original LOCOS paper [17]. This opened the possibility of creating mesas, either by silicon etching or by successive oxidation and oxide etching. Bassous et al [12] studied both recessed and semirecessed oxides with a view to planarising the surface and minimising the bird's beak. Optimum conditions were seen to be a 5 nm pad oxide and a 200 nm nitride film when using fully recessed oxide. The silicon etch process used KOH to anistropically etch the substrate to leave the sidewalls exposed to the field oxidation. Thus, although the bird's beak was minimised the characteristic profile remained. Chui et al [18] employed a similar approach, using plasma etching to recess the silicon substrate. The SideWall Masked Isolation technique[19] eliminated the white ribbon problem and produced a more planar surface. In this case the exposed silicon sidewalls are oxidised and coated with a second silicon nitride and planar etched to leave the pad oxide and nitride on the active areas and sidewalls before undergoing field oxidation. However this structure is susceptible to the dislocations symptomatic of the thick nitride structures previously discussed. Since the second nitride film coats the sidewall, the thickness of the film perpendicular to the substrate is equal to the size of the step ( $\approx 330$  nm). Volume expansion due to oxidation under these sidewalls encourages stress defects in the silicon substrate.

The problem was attacked by sloping the sidewalls, in a controlled etch process, thus reducing the effective thickness of the second nitride perpendicular to the oxide growth. However, by requiring a slope in the silicon prior to field oxidation, the minimum drawn isolation width will be constrained by the etched depth and the angle of the slope.

The Sealed Interface Local Oxidation, (SILO), tackles the bird's beak problem by depositing nitride directly onto the silicon surface before the pad oxide and masking nitride. Silicon etching recesses the substrate prior to field oxidation. Excellent planarity is achieved and the bird's beak is eliminated [20]. However, the stability of the active area has still to be proved.

In each of the above cases, the presence of SiN is required to eliminate the bird's beak. However, the nature of the film is conducive to stress dislocations in the substrate, which may increase greatly when patterned and etched [18, 21]. These defects give rise to

(i) Excessive junction leakage

(ii) Device degradation

## (iii) Reliability problems by providing deep recombination centres

Trench, or BOX, isolation uses the silicon etch but does not incorporate silicon nitride in the process. Here the isolation region is back filled once the exposed silicon surface has been sealed with a dielectric and the entire structure is etched back to from a planar surface [22]. This technique poses 2 major problems. One is in the stray leakage paths along the trench sidewalls. The other is in satisfactory planarising the range of topographic profiles which are present over the circuit.

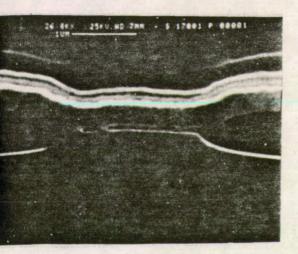

Figure 2.6 shows the 2-d profiles of these structures before field oxidation.

Figure 2.6. Isolation Profiles.

## 2.4.3. Poly Buffered Processes.

Using a nitride film to reduce the presence of the bird's beak produces stress along the perimeter of the active area possibly causing defects which may lead to junction leakage and/or low breakdown. The use of a polysilicon 'sandwich' layer between the silicon oxide and silicon nitride has been proposed as a way of minimising these effects [23]. Figure 2.7 shows the generic process for which there are two alternatives. In the first instance the polysilicon film is thick enough to provide the entire field oxide. This leaves a non-recessed oxide and corresponding large steps in the transition region. The stress effects of the nitride film are then absorbed in the oxidised polysilicon instead of the silicon substrate. Consequently a thicker nitride film can be used, to minimise the bird's beak. Alternatively, a thinner polysilicon film may be used and consequently a thinner nitride film, which recesses the field oxide but is more likely to suffer from the stress dislocations associated with

Figure 2.7. Poly Buffered Process.

conventional LOCOS. In neither case is any evidence of the white ribbon effect seen.

Optimised values of the three stack layers [24] suggest values for the pad oxide, polysilicon and nitride as 20 nm, 55 nm, 150 nm respectively, while compromising the restrictions due to stress dislocations arising from the thicker nitride films.

As with conventional LOCOS, the final topographic width is dependent on the etchback prior to gate oxidation. However the thinning of the field oxide must be compensated by a higher channel stop implant. This added etchback can extend the width of the active area by as much as 0.4  $\mu$ m over the conventional poly buffered process and has been successfully applied to the manufacture of 0.5 $\mu$ m CMOS technolology [25].

## 2.4.4. Other Options

Whilst the isolation technologies described above are the most commonly used, they are by no means complete. Oxynitrided layers act as oxidation inhibitors [21] but are prone to problems similar to the SILO structures. Epitaxial silicon has also been used [26] to form device islands in an approach similar to SOI [27]. Another area of isolation research is in implantation, whereby oxygen is implanted deep in the silicon by high energy implantation to provide an SOI structure [28].

The common disadvantage that these alternatives suffer is the increased complexity of processing, an option which does not sit well with high volume manufacture. This is reflected in the reluctance for volume manufacture to switch from the LOCOS process. Whilst other options have been presented, the viability of the original LOCOS process is demonstrated by current processes such as that of AT&T which operates a 1.5  $\mu$ m active area/isolation pitch.

#### 2.5. Summary

Chapter 2 has reviewed the more common isolation processes and highlighted some of the inherent difficulties. The range of options reflects the importance of the isolation process in the I.C. performance. This is of ever increasing relevance as geometries continue to shrink. One of the difficulties in assessing the strategies chosen is the large number of input parameters for any one option. A second problem is need for electrical testing. The effects of isolation technique on the electrical parameters may be difficult to interpret and of course can only be done at the end of process. Thus the process matrix to encompass even a few parameters involves a great deal of further work before devices are ready for electrical characterization. The most popular of the isolation processes, however, is the *LOCOS* process which will be used as the vehicle of study for this thesis.

#### References

- 1. M. M. Atalla, US Patent 3,206,670, 1960.

- 2. E. H. Snow, J. Appl. Physics, vol. 36, p. 1664, 1965.

- 3. B. E. Deal and A. S. Grove, "General Relationship for the Thermal Oxidation of Silicon", Journal of Applied Physics, vol. 36, no. 12, p. 3770, 3778, 1965.

- H. Z. Massoud, J. D. Plummer, and E. H. Irene, "Thermal Oxidation Of Silicon in Dry Oxygen - Growth Rate Enhancement in the Thin Regime", *Journal of the Electrochemical Society*, vol. 124, p. 2685, 1985.

- E. Kooi, J. G. Van Lierop, and J. A. Appels, "Formation Of Silicon Nitride at a Si-SiO2 Interface During Local Oxidation Of Silicon And During Heat-Treatment Of Oxidised Silicon In NH3 Gas", *Journal Of The Electrochemical Society: Solid State Science & Technology*, vol. 23, no. 7, July 1976.

- O. Nakajima, N. Shiono, S. Muramoto, and C. Hashimoto, "Defects In A Gate Oxide Grown After The LOCOS Process", Japanese Journal Of Applied Physics, vol. 18, no. 5, pp. 943-951, May 1979.

- H. Tompkins, M. Dydyk, and P.W. Deal, "Unintentional Formation Of Etch-Resistant Silicon", Journal Of The Electrochemical Society, vol. 137, no. 6, 1990.

- T. Shankoff, T. T. Sheng, R. B. Marcus, S. E. Haszko, and T. E. Smith, "Bird's Beak Configuration And ELimination Of Gate Oxide Thinning Produced During Selective Oxidation", *Electrochemical Society: Solid State Science And Technology*, pp. 216-222, 1980.

- T. C. Wu, W. T. Stacy, and K. N. Ritz, "The Influence Of The LOCOS processing Parameters On The Shape Of The Birds Beak Structure", *Journal Of The Electrochemical Society: Solid State Science & Technology*, vol. 130, no. 7, pp. 1563-1556, July 1983.

- N. Guillemot, G. Pananakakis, and P. Chenevier, "A New Analytical Model Of The Birds Beak", *IEEE Transactions On Electron Devices*, vol. ED-34, no. 5, pp. 1033-1038, May 1987.

- J. G. Dill, J. W. Barsten, R. D. J. Verhaar, and A. E. T. Kuiper, "LOCOS With Thick And Thin Nitride Masking", *Philips Journal Of Research*, vol. 40, no. 2, 1985.

- E. Bassous, H. N. Yu, and V. Maniscalco, "Topology Of Silicon Structures With Recessed SiO2", Journal Of The Electrochemical Society: Solid State Science & Technology, vol. 123, no. 11, Nov 1976.

- 13. Eernisse, Appl. Phys. Lett., vol. 30, p. 290, 1977.

- P. A. van der Plas, N. A. H. Wils, and R. de Werdt, "Geometry Dependent Birds Beak Formation For Submicron LOCOS Isolation", in *ESSDERC*, pp. 131-134, 1989.

- 15. T. Mizuno, S. Sawada, S. Maeda, and S. Shinozaki, Oxidation Rate Reduction In The Submicrometer LOCOS Process.

- H. Umimoto, S. Odanaka, I. Nakao, and H. Esaki, "Numerical Modelling Of Nonplanar Oxidation Coupled With Stress Effects", *IEEE Trans. Comp.-Aided* Des, vol. 8, no. 6, pp. 599-607, June 1989.

- J. A. Appels, E. Kooi, M. M. Paffen, J. J. H. Schatorje, and W. H. C. J. Verkuylen, "Local Oxidation Of Silicon And Its Application In Semiconductor Technology", *Philips Research Reports*, no. 25, pp. 118-132, 1970.

- R. C. Fang, K. Y. Chiu, and J. L. Moll, "Defect Characteristics And Generation Mechanism In A Birds Beak Free Structure By Sidewall Masked Technique", *Journal Of The Electrochemical Society: Solid State Science & Technology*, vol. 130, no. 1, Jan 1983.

- K. Y. Chui, J. L. Moll, and J. Manoliu, "A Birds Beak Free Local Oxidation Technology Feasible For VLSI Circuits Fabrication", *IEEE Transactions On Electron Devices*, vol. ED-29, no. 4, April 1982.

- V. K. Dwivedi, "A Birds Beak Free Sealed Interface Local Oxidation Technology For Submicron Ultra Large Scale Integrated Circuits", Journal Of The Electrochemical Society, vol. 137, no. 8, Aug 1990.

- H. H. Tsai, C. L. Yu, and C-Y Wu, "A Birds Beak Reduction Technique For LOCOS in VLSI Fabrication", *IEEE Transactions Electron Device Letters*, vol. EDL-7, pp. 122-123, Feb 1986.

- G. Zwicker, P. Lang, P. Staudt-Fishbach, and W. Windbracke, "Field Isolation Using Shallow Trenches For Submicron CMOS Technology", in *ESSDERC*, pp. 147-149, 1989.

- 23. N. Matsukawa, H. Nozawa, J. Matsunaga, and S. Kohyama, "Selective Polysilicon Technology for VLSI Isolation", *IEEE Transactions On Electron Devices*, vol. ED-29, no. 4, April 1982.

- M. Ghezzo, E. Kaminsky, Y. Nissan-Cohen, P. Frank, and R. Saia, "LOPOS: Advanced Device Isolation For A 0.08µm", Journal Of The Electrochemical Society, vol. 136, no. 7, July 1989.

- 25. J. Hayden, F. K. Baker, S. A. Ernst, R. E. Jones, J. Klein, M. Lein, T. F. McNelly, T. C. Mele, H. Mendez, B-Y. Nguyen, L. C. Parrilo, W. Paulson, J. R. Pfeister, F. Pintchovski, Y-C. See, R. Sivan, B. M. Somero, and E. O. Travis, "A High Performance Half Micrometer Generation CMOS Technology For Fast SRAMS", *IEEE Transactions Electron Device Letters*, vol. 38, no. 4, pp. 876-886, April 1991.

- 26. Y. C-S. Yu and A. Witkowski, "New Birds Beak Free Device Isolation Technology", Journal Of The Electrochemical Society: Solid State Science & Technology, vol. 135, no. 10, Oct 1988.

- 27. S. M. Sze, Physics Of Semiconductor Devices, Wiley & Sons, New York, 1981.

- K Yallup, "Oxygen Implantation For SOI Device Technology", in ESSDERC, p. 533, 1987.

## Chapter 3

# **Device Physics**

## 3.1. Introduction

The workings of semiconductor devices lie in the theories of solid state physics. The fundamental structures of solids determine their electrical properties. The transition from the good conductors (e.g. metals) to good insulators, is the realm of semiconductors. Their ability to conduct electricity to a varying but controllable degree, means that their potential as electronic components is vast. The techniques used in wafer fabrication allow very precise alteration of the semiconductor properties. Understanding the physics behind this necessitates an awareness of the quantised nature of the energy levels, or bands, in the semiconductor. For the duration of this discussion the semiconductor will be silicon, though the qualitative arguments are applicable to any semiconductor.

## **3.2.** The Crystal Lattice

At 0K the silicon substrate is an array of well-ordered silicon atoms, held together by valence electrons forming a pure covalent bond. The electrons are held firmly in place, and charge neutrality is observed. At temperatures greater than 0K, the lattice vibrates due to thermal energy and electrons 'shake' free. If the motions of the electrons can be coordinated, then a flow of current can be achieved.

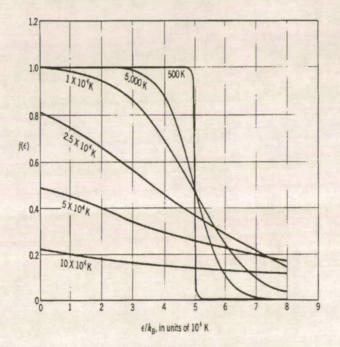

## 3.2.1. The Fermi Energy

Quantum physics tells us that the energy levels in an atom are discrete. Only specific energies are permitted within one atomic structure. At 0K the maximum energy of a ground state electron is given by  $E_F$ , called the Fermi energy. At temperatures greater than 0K, the energy distribution of electrons is given by the Fermi-Dirac distribution,

$$f(E) = \frac{1}{e^{(E-\mu_c)/k_BT} + 1}$$

(3.1)

This equation gives the probability that an orbital at energy E will be occupied. At absolute zero,  $\mu_c = E_F$ .

Figure 3.1. The Fermi-Dirac Function [1]

Figure 3.1 shows the Fermi-Dirac distribution function as a function of energy at different temperatures and to a first order in T, we may replace the chemical potential  $\mu_c$ , by the Fermi energy,  $E_F$ . The Fermi energy can be related to the electron

concentration by solving the Schroedinger equation for a fixed volume, V. This results in

$$E_F = \frac{\hbar^2}{2m} \left(\frac{3\pi^2 N}{V}\right)^{2/3} \tag{3.2}$$

which can be re-arranged to give the total number of orbitals of energy  $\leq E_F$ ,

$$N = \frac{V}{3\pi^2} \left(\frac{2mE_F}{\hbar^2}\right)^{3/2} \tag{3.3}$$

The number of orbitals per unit energy range is then given by dN/dE,

$$D(E) = \frac{V}{2\pi^2} \left(\frac{2m}{\hbar^2}\right)^{3/2} E^{1/2}$$

(3.4)

### **3.2.2. Energy Bands**

The concept of energy bands is an important tool in understanding the mechanisms of current transport in semiconductors.<sup>†</sup> In extending the above to a single crystal lattice, we see that standing waves are set up within the crystal wherein no solutions of the Schroedinger equation are found [1]. Thus forbidden regions or band gaps within the energy distribution are produced, leaving bands of permitted energies on either side. The nature of these energy bands dictates the properties of the material, categorising it into conductor, semiconductor or insulator. The crystal behaves as a metal if one or more of the bands is partly filled (10% - 90%), an insulator if the bands are entirely filled or entirely empty, and a semiconductor if all the bands are entirely filled except for one or two bands slightly filled or slightly empty. In silicon this band gap is 1.12eV.

<sup>†</sup> An alternative approach using contact potentials is given in reference 2.

## 3.2.3. Intrinsic Carrier Concentration

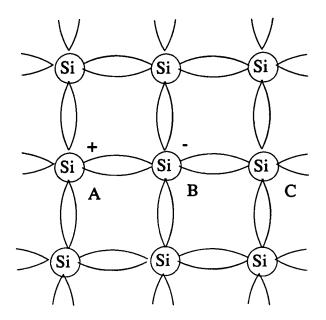

Consider figure 3.2, representing a silicon lattice.

Figure 3.2. The Silicon Lattice.

Each silicon atom is bonded to 4 other atoms, using valence electrons in a covalent bond. At 0K, there are no free electrons and the semiconductor is a perfect insulator. At temperatures above 0K, thermal vibration dislodges electrons which are free to roam throughout the lattice. Atom A is one such atom which has lost an electron. Therefore there is a positive charge associated with A. The vacancy created by the freed electron may now be filled by an electron from a neighbouring atom. This in turn leaves atom B with a net positive charge which may be neutralized by the same process whereby a neighbouring atom, C, donates an electron. Thus we can see that there are two mechanisms for transporting charge around the lattice.

- (i) The motion of free electrons, each carrying a single negative charge

- (ii) The motion of valence electrons in the opposite direction, from bond to bond, at each stage leaving behind a single positive charge.

It is convenient to think of this second mechanism as the motion of positively charged 'holes' in the opposite direction. (The commonly used analogy is that of bubbles in a liquid). If a hole and electron meet in a lattice then they undergo what is termed recombination, whereby they annihilate each other. In a pure, or *intrinsic*, lattice at room temperature, the concentration of these free carriers is  $\sim 1.45 \times 10^{10} cm^{-3}$ . The density of silicon is  $5 \times 10^{22}$  atoms  $cm^{-3}$ . Therefore only about 3 atoms in every  $10^{13}$  contribute an electron-hole pair. In the intrinsic semiconductor every electron which breaks free is matched by a hole. Let the concentration of electrons be n and the concentration of holes be p. Then since these occur in pairs,

$$n = p = n_i \tag{3.5}$$

where  $n_i$  is known as the intrinsic carrier concentration.

#### 3.2.4. Law Of Mass Action

It is convenient to calculate this parameter  $n_i$ , in terms of the energy levels,  $E_c$ ,  $E_V$  and  $\mu_c$ , the chemical potential. In semiconductor physics  $\mu_c$  is called the Fermi level,  $E_F$ . First we calculate the number of electrons per unit volume excited to the the conduction band. This is given by *n* where,

$$n = \int_{E_c}^{\infty} D(E) f(E) dE$$

(3.6)

D(E) is given from (3.4) and f(E) is the Fermi-Dirac distribution function (3.1). The integral therefore becomes

$$n = \int_{E_C}^{\infty} 4\pi \left[ \frac{2m_e}{h^2} \right]^{3/2} E^{1/2} \frac{1}{1 + e^{(E - E_F)/k_B T}} dE$$

(3.7)

where  $m_e$  is the effective mass of the electron.

At temperatures of interest, where  $E - E_F \gg k_B T$ , the Fermi-Dirac distribution

reduces to

$$f(E) \approx e^{-(E-E_F)/k_BT} \tag{3.8}$$

The integral is easily evaluated to

$$n = N_c e^{-(E_c - E_F)/(k_B T)}$$

(3.9)

where

$N_c$  is the effective density of states in the conduction band and

$$N_{C} = 2 \left[ \frac{2\pi m_{e} k_{B} T}{h^{2}} \right]^{3/2}$$

(3.10)

Because a hole is the absence of an electron, the distribution function for holes can be written as

$$f_h = 1 - \frac{1}{e^{(E_F - E_V)/k_B T} + 1}$$

(3.11)

Using a similar approach then, yields the hole concentration in the valence band

$$p = N_V e^{-(E_F - E_V)/(k_B T)}$$

(3.12)

where

$m_h$  is the effective mass of the hole

$N_V$  is the effective density of states in the conduction band

and

$$N_{V} = 2 \left[ \frac{2\pi m_{h} k_{B} T}{h^{2}} \right]^{3/2}$$

(3.13)

The product of (3.9) and (3.12) is known as the Law of Mass Action

$$np = 2 \left[ \frac{2\pi k_B T}{h^2} \right]^3 (m_e m_h)^{3/2} e^{-(E_C - E_V)/k_B T}$$

(3.14)

This is a useful expression since the result is independent of the presence of impurities. The only assumption is that the material is non-degenerate. viz. the Fermi level is  $> 3k_BT$  away from the edge of the conduction or valence band, within the band gap. From (3.5)

$$n = p = n_i$$

Therefore,

$$n_{i} = 2 \left[ \frac{2\pi k_{B}T}{h^{2}} \right]^{3/2} (m_{e}m_{h})^{3/4} e^{-(E_{C} - E_{V})/k_{B}T}$$

(3.15)

Thus the intrinsic carrier concentration depends exponentially on the temperature. Also since n = p, equating (3.9) and (3.12) for an intrinsic semiconductor gives

$$E_F = \frac{E_V + E_C}{2} + \frac{3}{4} k_B T \ln\left(\frac{m_e}{m_h}\right)$$

(3.16)

which places the Fermi level very close to the middle of the band gap for the intrinsic semiconductor.

## 3.2.5. Impurities

Because the product of electrons and holes is a constant, introducing added quantities of one must reduce the other. This simple observation has profound impact in practice. It possible then to enormously reduce a carrier concentration by addition of the opposite type. This phenomenon is known as **compensation**. Figure 3.3 demonstrates the mechanism of doping of a crystal lattice.

Figure 3.3(a) shows the pure silicon case. Figure 3.3(b) shows the presence of an atom (boron) from group III in the periodic table and 3.3(c) the presence of an atom (arsenic) from group V in the periodic table. Since silicon lies in group IV, in neither case will there be a complete matching of bonds. In the case of boron with 3 valence electrons, an extra electron is 'accepted' to form 4 covalent bonds around the

Figure 3.3. The Doped Lattice.

boron atom and a positively charged hole is created in the valence band. The silicon is then p-type because of the addition of a positively charged carrier and the boron is known as an acceptor. In the case of arsenic an electron is lost or 'donated' from the valence band to the conduction band. The silicon is then n-type because of the addition of a negatively charged carrier and the arsenic is known as a donor. Since at room temperature most donors and acceptors are ionised, charge neutrality can be expressed as

$$n + N_A = p + N_D \tag{3.17}$$

In an *n*-type semiconductor

$$n \approx N_D \tag{3.18}$$

and in a *p*-type semiconductor

$$p \approx N_A \tag{3.19}$$

Equations (3.9) and (3.12) can be re-arranged to provide the relations

$$E_C - E_F = k_B T \ln\left(\frac{N_C}{n}\right) \tag{3.20}$$

and

which using (3.18) and (3.19) become

$$E_F - E_V = k_B T \ln\left(\frac{N_V}{n}\right) \tag{3.21}$$

$$E_C - E_F = k_B T \ln\left(\frac{N_C}{N_D}\right) \tag{3.22}$$

and

$$E_F - E_V = k_B T \ln\left(\frac{N_V}{N_A}\right) \tag{3.23}$$

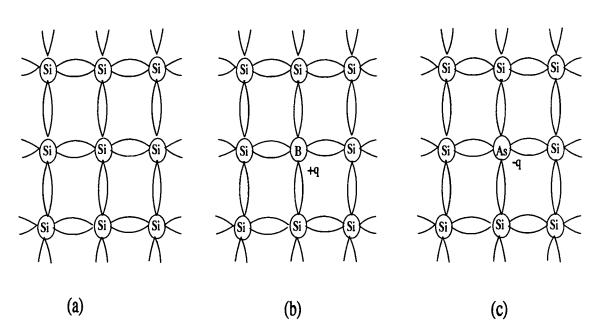

The conclusion of this is to shift the Fermi level *relative* to the conduction or valence bands according the to quantity of dopant introduced. Figure 3.4 shows the related energy band diagrams for the intrinsic, p-type and n-type cases.

n-typeintrinsicp-typeFigure 3.4. Energy Band Diagram for p - type, n - type and intrinsic silicon.

An alternative approach yields an equivalent expression whereby the concentrations are expressed in terms of the intrinsic carrier concentration and the intrinsic energy level

$$n = n_i e^{(E_F - E_i)/k_B T}$$

(3.24)

and

$$p = n_i e^{(E_i - E_F)/k_B T}$$

(3.25)

In the limiting case where the Fermi levels are shifted because of excessive carrier doping to a few ( $\approx 3k_BT$ ) of the conduction band, then these equations are no longer valid and the material is said to be **degenerate**.

## 3.2.6. Conduction

If the motion of the free carriers can be coordinated then a directional current can be achieved. The can be done by applying an electric field E. The motion of the carriers under these conditions is complicated because they accelerate, collide and accelerate again in discrete charge packets. Further, recombination will occur. Generally there are two mechanisms for current flow: drift current and diffusion current.

#### **3.2.6.1.** Mobility and Drift velocity

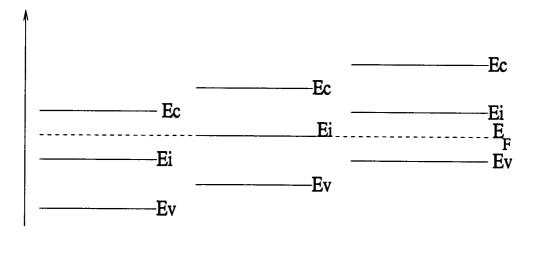

The following discussion assumes no recombination. Assume a current I, is flowing in the semiconductor shown in figure 3.5

Figure 3.5. Current Flow

The average time taken for a charge to cross the region is defined as  $\tau_i$ . The motion of the carriers caused by the *E* field is known as the drift velocity  $v_d$ . The value of this velocity depends on

(i) the type of semiconductor

(ii) the type of dopant

(iii) the type of carrier

(iv) the concentration of the carrier

(v) the temperature

When a carrier is accelerated through a high electric field, the subsequent loss of energy to the lattice becomes dominant and the velocity is said to *saturate*. Below this, the velocity is proportional to the electric field and the constant of proportionality is known as the mobility,  $\mu$ . For silicon a low electric field is < 0.3V/m for electrons, and < 0.6V/m for holes. In general  $\mu = aT^{-x}$ , where a and x are constants.[2]. Analytic models have been developed to express the reduction of the bulk mobility with the introduction of dopant [3, 4]. The introduction of dopant reduces the mobility according to [2] †

$$\mu = m^{1/2} N^{-1} T^{-3/2} \tag{3.26}$$

The transit time,  $\tau_t$ , then can be related to the drift velocity.

$$\tau_t = \frac{a}{|\nu_D|} \tag{3.27}$$

where a is the length of material through which the current flows.

<sup>†</sup>It should be noted that here we have discussed the bulk mobility,  $\mu_B$ , which is not equivalent to the surface mobility  $\mu_s$ .

,

Also

$$E = \frac{V}{a} \tag{3.28}$$

Therefore,

$$\tau_t = \frac{a}{\mu E} \tag{3.29}$$

and

.

$$\tau_t = \frac{a^2}{\mu V} \tag{3.30}$$

Therefore for a fixed voltage, V, and mobility  $\mu$ , the transit time,  $\tau_i$ , reduces as the length increases. The dependence is a square law, reflecting the two reasons for this.

(i) As a increases the carriers have further to travel

(ii) As a increases, E, (= V/a), reduces.

The current flowing through the bar is then given by

$$I = \frac{Q}{\tau_t} = nq \, \frac{abc}{\tau_t} \tag{3.31}$$

Applying (3.30)

$$I = nq\mu \frac{bc}{a}V \tag{3.32}$$

which is equivalent to Ohm's Law where  $\left[nq\mu \frac{bc}{a}\right]^{-1}$  is the resistance of the material.

## **3.2.6.2.** Diffusion Current

Where a non-uniform distribution of particles exists, then there occurs a phenomenon known as *diffusion*. i.e. wherever there exists a concentration gradient the motion of the thermally stimulated particles tends towards a uniform distribution over time. This is not due to electric fields. As may be expected, the higher the concentration gradient, the higher the diffusion current. In fact, it can be shown [2] that in the absence of an external electric field,

$$J_n = qD_n \frac{\partial n}{\partial x} \tag{3.33}$$

for electrons and

$$J_p = -qD_p \frac{\partial p}{\partial x} \tag{3.34}$$

where J is the current density, n and p refer to electron and hole concentrations and D is the diffusion coefficient. The total current density made up from the two mechanisms of drift and diffusion can be written as

$$J_n = q \,\mu_n E + q D \,\frac{\partial n}{\partial x} \tag{3.35}$$

and

$$J = J_n + J_p \tag{3.36}$$

The diffusion coefficient can be related to the mobility through the Einstein Relation [2]:

$$D_n = \frac{k_B T}{q} \mu_n \tag{3.37}$$

$$D_p = \frac{k_B T}{q} \mu_p \tag{3.38}$$

## 3.2.6.3. Minority Carrier Lifetime

If the equilibrium is disturbed such that  $n_i^2 \neq np$ , then the tendency is to return to the equilibrium. This can be seen in the case of an *n*-type semiconductor under illumination, whereby carriers are generated at a rate dp/dt, equal to the net generation minus the recombination. Recombination processes can be modelled by a parameter known as the minority carrier lifetime  $(\tau_n, \tau_p)$ . whereby the nett rate of recombination, U, is proportional to the number of carriers generated under illumination,  $p_n$ , minus the number of minority carriers in equilibrium,  $p_{no}$  [5]. The constant of proportionality is given by  $\tau_p$  such that

$$U = \frac{1}{\tau_p} (p_n - p_{no})$$

(3.39)

The processes for recombination are complex, either by direct band-to-band, when an electron in the conduction band recombines with a hole in the valence band, or by trapping between the bands, when an electron or hole capture by a suitable donor or acceptor occurs in the semiconductor. This term must be included however in the current continuity equations

$$\frac{\partial p}{\partial x} = \frac{1}{q} \nabla J_p - U_p \tag{3.40}$$

#### **3.3.** The P-N Junction Diode

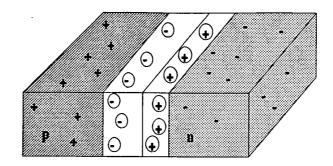

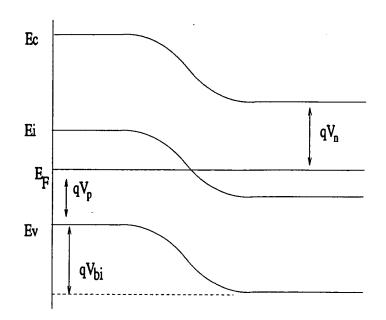

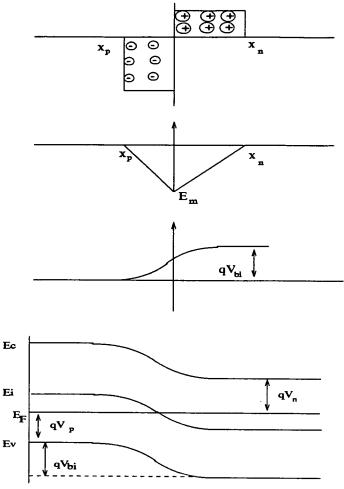

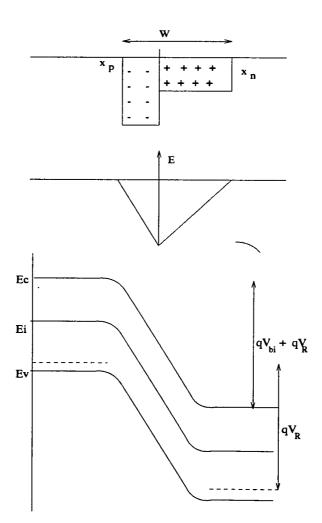

If a region of silicon is selectively doped with an n-type dopant, and an adjacent region doped with p-type dopant the resultant structure will produce what is known as a **pn junction**. Figure 3.6 shows the schematic.

Here we have assumed that the *n*-type region is more highly doped than the *p*-type, and that the transition from one to another is abrupt - the so-called **abrupt** or **step junction**. In this structure electrons will diffuse from the *n* side across the boundary to the *p* side. Similarly holes will diffuse from the *p* to the *n* region. In so

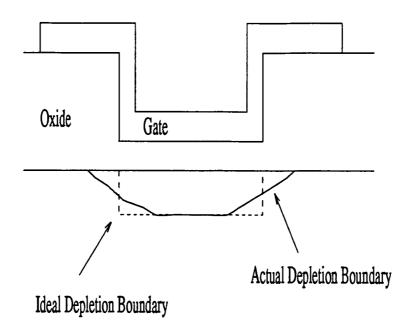

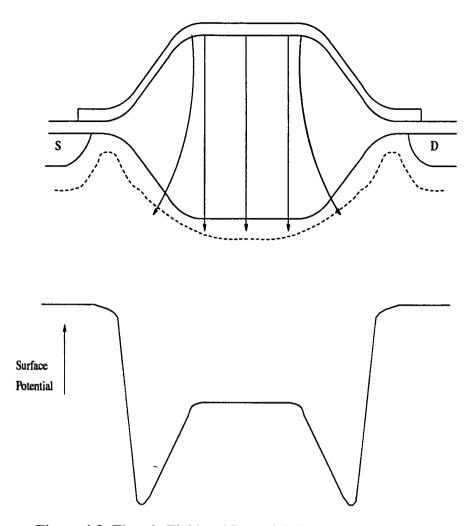

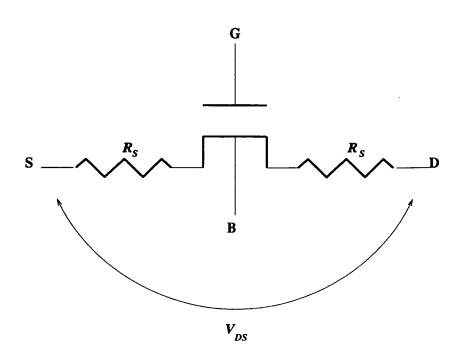

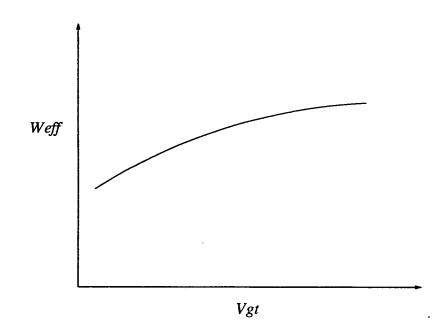

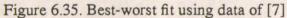

Figure 3.6. pn Junction Diode