## THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Impedance Matching and DC-DC Converter Designs for Tunable Radio Frequency Based Mobile Telecommunication Systems

Yan Chiew Wong

A thesis submitted for the Degree of Doctor of Philosophy The University of Edinburgh 2014

#### **Declaration**

I hereby declare that this thesis has been composed by myself and that except where stated, the work contained is my own. I also declare that the work contained in this thesis has not been submitted for any other degree or professional qualification except as specified.

\_\_\_\_\_

Yan Chiew Wong

March 2014

#### **Acknowledgements**

I wish to express my gratitude to my supervisors, Prof. Dr. Tughrul Arslan and Dr. Alister Hamilton for their invaluable support, constant encouragement and guidance throughout this study.

I wish also like to thank Dr. Ahmet T. Erdogan for his support and help during my PhD study.

I would like to thank Malaysia Ministry of Education and Universiti Teknikal Malaysia Melaka (UTeM) for financially supporting my study. I am particularly grateful to the management of UTeM for enabling me to further my study abroad.

I would also like to thank all my colleagues in the System Level Integration Research Group for their friendship and support.

My special thanks are due to my family and family-in-law for their understanding, patience and support during the research and the preparation of this thesis.

Finally and most importantly, I would like to thank my husband –Mr. Che Keong Yeoh – for his unceasing love, unreserved support and patience over the course of this research, and to my gorgeous daughter – Jen Xi Yeoh – for being a great inspiration and motivation along my PhD study. I hope I can repay their encouragement and love.

#### **Abstract**

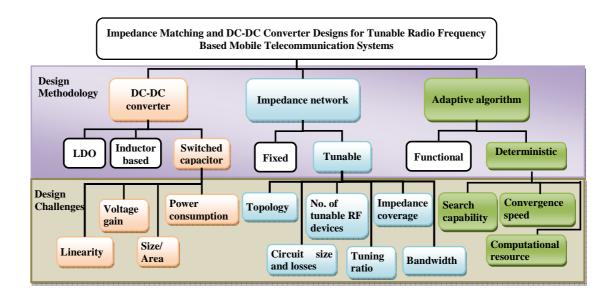

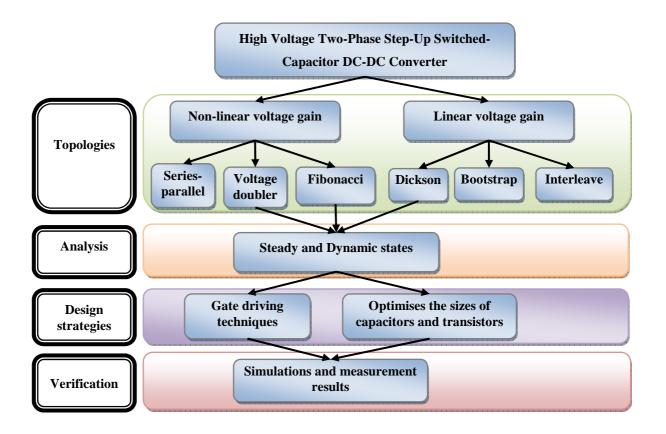

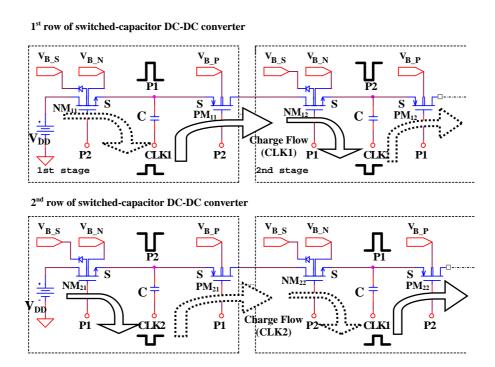

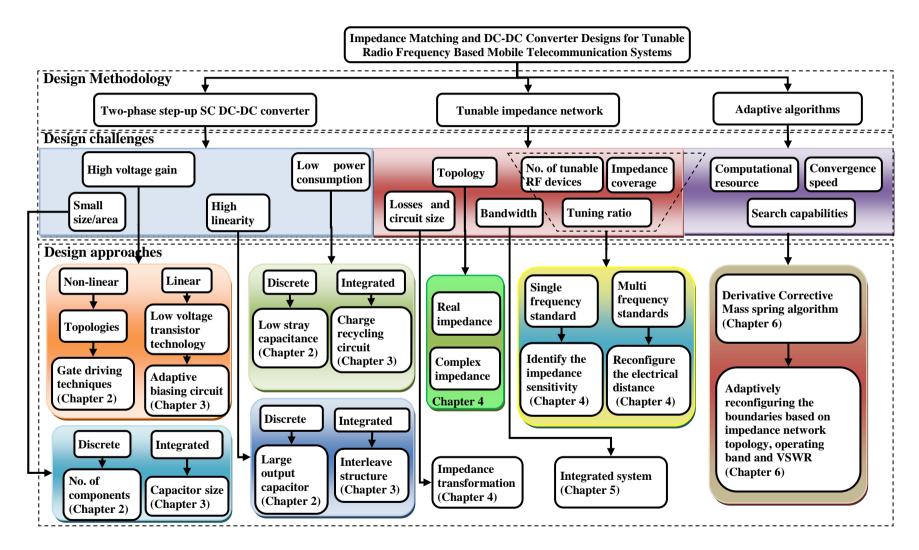

Tunability and adaptability for radio frequency (RF) front-ends are highly desirable because they not only enhance functionality and performance but also reduce the circuit size and cost. This thesis presents a number of novel design strategies in DC-DC converters, impedance networks and adaptive algorithms for tunable and adaptable RF based mobile telecommunication systems. Specifically, the studies are divided into three major directions: (a) high voltage switch controller based DC-DC converters for RF switch actuation; (b) impedance network designs for impedance transformation of RF switches; and (c) adaptive algorithms for determining the required impedance states at the RF switches.

In the first stage, two-phase step-up switched-capacitor (SC) DC-DC converters are explored. The SC converter has a simple control method and a reduced physical volume. The research investigations started with the linear and the non-linear voltage gain topologies. The non-linear voltage gain topology provides a higher voltage gain in a smaller number of stages compared to the linear voltage gain topology. Amongst the non-linear voltage gain topologies, a Fibonacci SC converter has been identified as having lower losses and a higher conversion ratio compared to other topologies. However, the implementation of a high voltage (HV) gain Fibonacci SC converter is complex due to the requirement of widely different gate voltages for the transistors in the Fibonacci converter. Gate driving strategies have been proposed that only require a few auxiliary transistors in order to provide the required boosted voltages for switching the transistors on and off. This technique reduces the design complexity and increases the reliability of the HV Fibonacci SC converter.

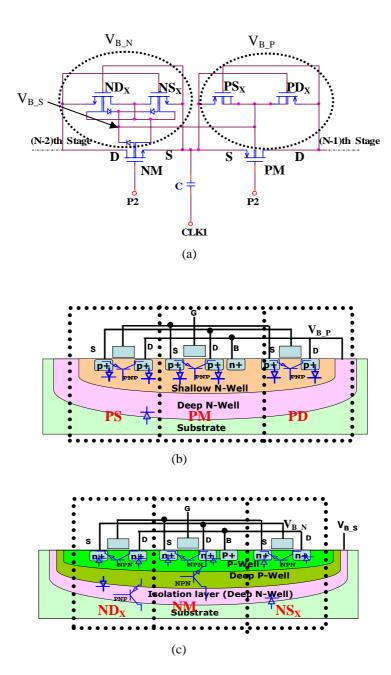

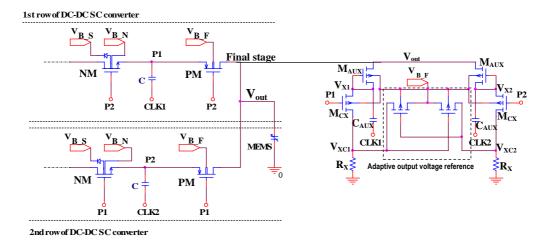

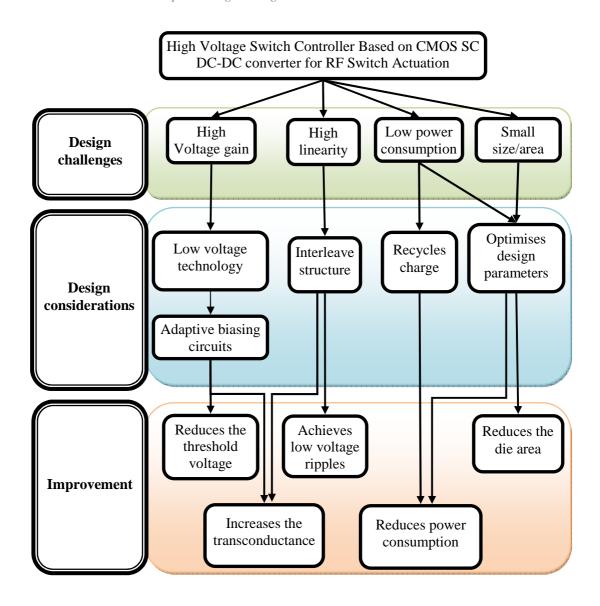

For the linear voltage gain topology, a high performance complementary-metal-oxide-semiconductor (CMOS) based SC DC-DC converter has been proposed in this work. The HV SC DC-DC converter has been designed in low voltage (LV) transistors technology in order to achieve higher voltage gain. Adaptive biasing circuits have been proposed to eliminate the leakage current, hence avoiding latch-up which normally occurs with low voltage transistors when they are used in a high voltage design. Thus, the SC DC-DC converter achieves more than 25% higher boosted voltage compared to converters that use HV transistors. The proposed design provides a 40% power reduction through the charge recycling circuit that reduces the effect of non-ideality in integrated HV capacitors. Moreover, the SC DC-DC converter achieves a 45% smaller area than the conventional converter through optimising the design parameters.

In the second stage, the impedance network designs for transforming the impedance of RF switches to the maximum achievable impedance tuning region are investigated. The maximum achievable tuning region is bounded by the fundamental properties of the selected impedance network topology and by the tunable values of the RF switches that are variable over a limited range. A novel design technique has been proposed in order to achieve the maximum impedance tuning region, through identifying the optimum electrical distance between the RF switches at the impedance network. By varying the electrical distance between the RF switches, high impedance tuning regions are achieved across multi frequency standards. This technique reduces the cost and the insertion loss of an impedance network as the required number of RF switches is reduced. The prototype demonstrates high impedance coverages at LTE (700MHz), GSM (900MHz) and GPS (1575MHz).

Integration of a tunable impedance network with an antenna for frequency-agility at the RF front-end has also been discussed in this work. The integrated system enlarges the bandwidth of a patch antenna by four times the original bandwidth and also improves the antenna return loss. The prototype achieves frequency-agility from 700MHz to 3GHz. This work demonstrates that a single transceiver with multi frequency standards can be realised by using a tunable impedance network.

In the final stage, improvement to an adaptive algorithm for determining the impedance states at the RF switches has been proposed. The work has resulted in one more novel design techniques which reduce the search time in the algorithm, thus minimising the risk of data loss during the impedance tuning process. The approach reduces the search time by more than an order of magnitude by exploiting the relationships among the mass spring's coefficient values derived from the impedance network parameters, thereby significantly reducing the convergence time of the algorithm. The algorithm with the proposed technique converges in less than half of the computational time compared to the conventional approach, hence significantly improving the search time of the algorithm.

The design strategies proposed in this work contribute towards the realisation of tunable and adaptable RF based mobile telecommunication systems.

#### **Table of Contents**

| Decla                 | ration                                  |                                                                                  | ii    |

|-----------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Ackno                 | owledgen                                | nents                                                                            | ii    |

| Abstr                 | act                                     |                                                                                  | iv    |

|                       |                                         | ents                                                                             |       |

|                       |                                         |                                                                                  |       |

| List of               | f Figures                               |                                                                                  | xii   |

| List o                | f Tables .                              |                                                                                  | xix   |

| List o                | f Acrony                                | ms and Abbreviations                                                             | XX    |

| Chant                 | ter 1· Int                              | roduction                                                                        | 1     |

| о <b>пар</b> .<br>1.1 |                                         | ation for the Tunable RF based Mobile Telecommunication Systems                  |       |

|                       | 1.1.1                                   | Multi Frequency Bands                                                            |       |

|                       | 1.1.2                                   | Variable Transmit Power Level                                                    |       |

|                       | 1.1.3                                   | Antenna in Mismatch Conditions                                                   | 3     |

|                       | 1.1.4                                   | Fluctuating Operating Environment                                                | 4     |

| 1.2                   | Resear                                  | ch Investigation                                                                 | 5     |

|                       | 1.2.1                                   | High Voltage Switch Controller based on DC-DC Converters for RF Switch Actuation |       |

|                       | 1.2.2                                   | Impedance Network Designs for Impedance Transformation of RF Switches            | 8     |

|                       |                                         | 1.2.2.1 Discrete Tuning                                                          | 9     |

|                       |                                         | 1.2.2.2 Continuous Tuning                                                        | 10    |

|                       | 1.2.3                                   | Adaptive Algorithms for Determining the Required Impedance State RF Switches     |       |

|                       |                                         | 1.2.3.1 Functional Approach                                                      | 11    |

|                       |                                         | 1.2.3.2 Deterministic Approach                                                   | 11    |

| 1.3                   | Overvi                                  | iew of Thesis                                                                    | 13    |

| 1.4                   | Publications Arising from This Research |                                                                                  |       |

| 1.5                   | Summary1                                |                                                                                  |       |

| Chant                 | ter 2: H                                | igh Voltage Switch Controller based Two-phase Step-up SC 1                       | DC-DC |

| _                     |                                         |                                                                                  |       |

| 2.1                   | Introdu                                 | uction                                                                           | 16    |

| 2.2                   | Topolo                                  | ogies of Two-phase Step-up SC DC-DC Converter                                    | 17    |

|                       | 2 2 1                                   | Linear Voltage Gain Topology                                                     | 17    |

|      |                                    | 2.2.1.1 The Dickson SC Converter                                | 17 |  |  |

|------|------------------------------------|-----------------------------------------------------------------|----|--|--|

|      |                                    | 2.2.1.2 The Bootstrap SC Converter                              | 18 |  |  |

|      |                                    | 2.2.1.3 The Interleave Structure SC Converter                   | 19 |  |  |

|      | 2.2.2                              | Nonlinear Voltage Gain Topology                                 | 20 |  |  |

|      |                                    | 2.2.2.1 The Series-Parallel SC Converter                        | 20 |  |  |

|      |                                    | 2.2.2.2 The Voltage Doubler SC Converter                        | 21 |  |  |

|      |                                    | 2.2.2.3 The Fibonnacci SC Converter                             | 22 |  |  |

| 2.3  | Evalua                             | tion of Key Components in the SC Converter                      | 23 |  |  |

|      | 2.3.1                              | Charge Storage Capacitors                                       | 23 |  |  |

|      | 2.3.2                              | Charge Transfer Transistors                                     | 24 |  |  |

| 2.4  | Analys                             | sis of the SC Converters                                        | 25 |  |  |

|      | 2.4.1                              | Steady State                                                    | 25 |  |  |

|      |                                    | 2.4.1.1 Simulation Results                                      | 27 |  |  |

|      | 2.4.2                              | Dynamic State                                                   | 30 |  |  |

|      |                                    | 2.4.2.1 Simulation Results                                      | 31 |  |  |

|      | 2.4.3                              | Comparisons                                                     | 31 |  |  |

| 2.5  | Transistor Gate Driving Techniques |                                                                 |    |  |  |

|      | 2.5.1                              | Optimisation of the Fibonacci Topology                          | 38 |  |  |

|      | 2.5.2                              | Simulation Results                                              | 39 |  |  |

|      | 2.5.3                              | Verification                                                    | 41 |  |  |

| 2.6  | Discus                             | sionsion                                                        | 42 |  |  |

| 2.7  | Summa                              | ary                                                             | 43 |  |  |

| Chap | ter 3: Hig                         | gh Voltage Switch Controller based CMOS SC DC-DC Converter      | 45 |  |  |

| 3.1  |                                    | action                                                          |    |  |  |

| 3.2  | High V                             | Voltage Switch Controller based CMOS SC DC-DC Converter         | 46 |  |  |

| 3.3  | Operat                             | ion of High Voltage SC DC-DC Converter                          | 46 |  |  |

| 3.4  | Design                             | of High Voltage SC DC-DC Converter                              | 48 |  |  |

|      | 3.4.1                              | Adaptive Bulk Biasing Circuit                                   | 48 |  |  |

|      | 3.4.2                              | Output Stage of the SC DC-DC Converter                          | 51 |  |  |

| 3.5  | Analys                             | sis of the Design Parameters of High Voltage SC DC-DC Converter |    |  |  |

|      | 3.5.1                              | Voltage Gain Efficiency                                         | 52 |  |  |

|      | 3.5.2                              | Power Consumption                                               | 53 |  |  |

|      | 3.5.3                              | SC DC-DC Converter with Losses                                  | 54 |  |  |

|      | 3.5.4                              | Optimisation of the Design Parameters                           | 54 |  |  |

|      | 3.5.5                              | Design Example                                                  | 56 |  |  |

| 3.6   | Improv   | vement to the Performance of High Voltage SC DC-DC Converter   | 57      |

|-------|----------|----------------------------------------------------------------|---------|

|       | 3.6.1    | Improving the Voltage Gain Efficiency                          | 57      |

|       |          | 3.6.1.1 Reducing the Threshold Voltage of the Transistors      | 57      |

|       |          | 3.6.1.2 Increasing the Transconductance of the Transistors     | 58      |

|       | 3.6.2    | Reducing the Power Consumption in Parasitic Capacitance        | 59      |

| 3.7   | Verific  | cation of the Improved Performance High Voltage SC DC-DC Conve | rter 61 |

| 3.8   | Implen   | mentations                                                     | 70      |

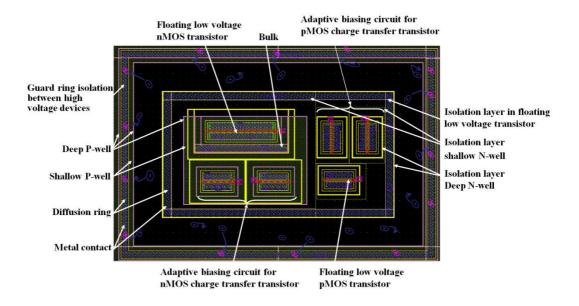

|       | 3.8.1    | Layout of Floating Low Voltage Transistors                     | 70      |

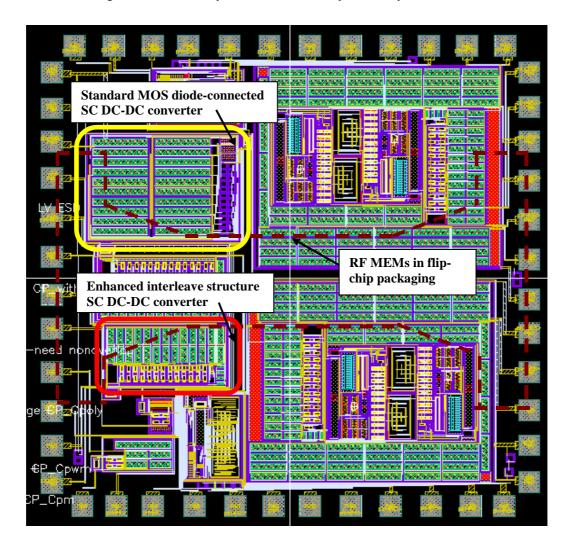

|       | 3.8.2    | Layout of SC DC-DC Converters                                  | 71      |

| 3.9   | Bench    | marking                                                        | 72      |

| 3.10  | Measu    | rement Results                                                 | 74      |

| 3.11  | Discus   | ssion                                                          | 77      |

| 3.12  | Summa    | ary                                                            | 77      |

| Chapt | ter 4: T | Tunable Impedance Network Designs for RF Switches Im           | pedance |

|       |          | on                                                             |         |

| 4.1   | Introdu  | uction                                                         | 79      |

| 4.2   | Impeda   | ance Network Topologies                                        | 80      |

|       | 4.2.1    | Real Impedance Matching                                        | 80      |

|       | 4.2.2    | Complex Impedance Matching                                     | 84      |

|       |          | 4.2.2.1 Matching Stub                                          | 84      |

|       |          | 4.2.2.2 Matching Lumped Elements                               | 84      |

| 4.3   | Optimi   | isation of Impedance Network Topologies                        | 86      |

|       | 4.3.1    | Techniques for Impedance Transformation                        | 86      |

| 4.4   | Tunab    | le Impedance Network                                           | 89      |

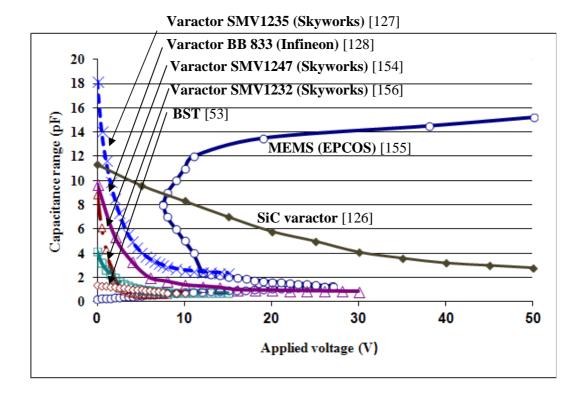

|       | 4.4.1    | Semiconductor                                                  | 89      |

|       |          | 4.4.1.1 Silicon                                                | 89      |

|       |          | 4.4.1.2 Gallium Arsenide                                       | 90      |

|       |          | 4.4.1.3 Performance                                            | 90      |

|       |          | 4.4.1.4 Availability                                           | 91      |

|       | 4.4.2    | Barium Strontium Titanate                                      | 91      |

|       |          | 4.4.2.1 Performance                                            | 92      |

|       |          | 4.4.2.2 Availability                                           | 92      |

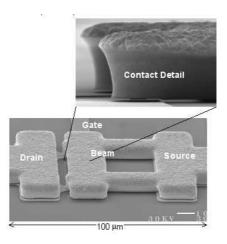

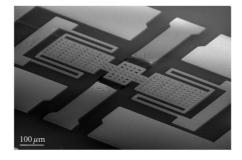

|       | 4.4.3    | Micro Electro-Mechanical Systems                               | 93      |

|       |          | 4.4.3.1 Performance                                            | 94      |

|       |          | 4.4.3.2 Availability                                           | 94      |

|      | 4.4.4     | Comparison                                                   | 95  |

|------|-----------|--------------------------------------------------------------|-----|

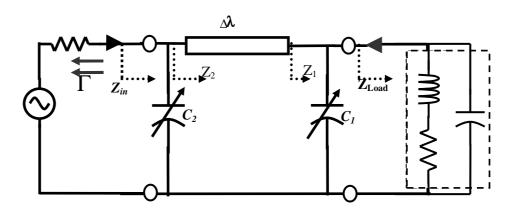

| 4.5  | Tunab     | le Impedance Networks with Wide Impedance Coverage           | 96  |

| 4.6  | Imped     | ance Network Design Technique                                | 97  |

|      | 4.6.1     | In Consideration of Topology                                 | 98  |

|      | 4.6.2     | In Consideration of Maximum Impedance Coverage               | 100 |

| 4.7  | Verific   | cations                                                      | 102 |

| 4.8  | Prototy   | yping                                                        | 103 |

| 4.9  | Discus    | ssions                                                       | 105 |

| 4.10 | Summ      | ary                                                          | 107 |

|      |           | unable Impedance Network Integrated with an Antenna for less |     |

| 5.1  | Introdu   | uction                                                       | 109 |

| 5.2  | Anteni    | nas for Multi-standard RF Front-end                          | 110 |

|      | 5.2.1     | Antenna in Mobile Devices                                    | 110 |

|      | 5.2.2     | Design of Wideband Antennas by using Switchable Impedance    |     |

| 5.3  | Design    | n of a Wide Bandwidth Frequency-Agility Impedance Network    | 115 |

|      | 5.3.1     | Multi-section Transmission Line                              | 115 |

|      | 5.3.2     | Radial Stub                                                  | 117 |

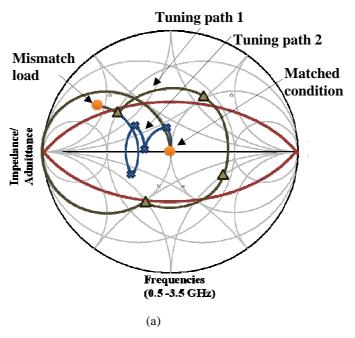

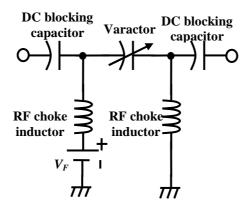

|      | 5.3.3     | Tuning Trajectory                                            | 119 |

| 5.4  | Optim     | ization and Implementation                                   | 120 |

|      | 5.4.1     | Layout of the Wideband Impedance Network                     | 120 |

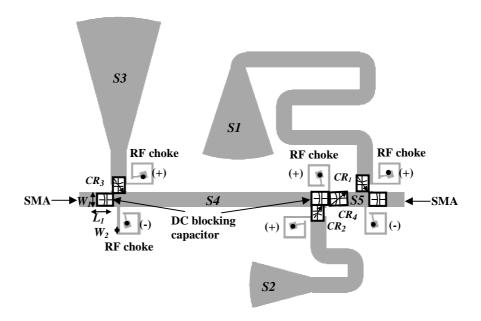

|      | 5.4.2     | Controlling the RF Switches                                  | 121 |

| 5.5  | Verific   | cation                                                       | 122 |

| 5.6  | Discus    | ssions                                                       | 126 |

| 5.7  | Summ      | ary                                                          | 127 |

| Chap | ter 6: Ad | aptive Algorithms for Tunable RF Impedance Networks          | 129 |

| 6.1  | Introdu   | uction                                                       | 129 |

| 6.2  | Adapti    | ive Algorithms                                               | 130 |

|      | 6.2.1     | Linear Correlation Method                                    | 130 |

|      |           | 6.2.1.1 Formation of the Susceptance Matrix                  | 130 |

|      |           | 6.2.1.2 The Process of LMS                                   | 132 |

|      |           | 6.2.1.3 Simulation Results                                   | 134 |

|      | 6.2.2     | Stochastic Method                                            | 136 |

|      |           | 6.2.2.1 Population                                           | 138 |

|      |            | 6.2.2.2    | Fitness   | Value                                                                               |

|------|------------|------------|-----------|-------------------------------------------------------------------------------------|

|      |            | 6.2.2.3    | GA's C    | Operators                                                                           |

|      |            | 6.2.2.4    | Simula    | tion Results140                                                                     |

|      | 6.2.3      | Derivat    | ive-Corr  | ective Mass Spring Algorithm143                                                     |

|      |            | 6.2.3.1    | Simula    | tion Results145                                                                     |

| 6.3  | Summa      | ary        |           |                                                                                     |

| Chap | ter 7: Coi | nclusions  | •••••     | 149                                                                                 |

| 7.1  | Summa      | ary and Co | onclusio  | ns149                                                                               |

| 7.2  | Summa      | ary of Co  | ntributio | ns                                                                                  |

|      | 7.2.1      | _          | _         | h Voltage Switch Controller based on SC DC-DC<br>RF Switch Actuation                |

|      |            | 7.2.1.1    | Non-lir   | near Voltage Gain SC Converter                                                      |

|      |            |            | a.        | Research investigation into the nonlinear voltage gain SC converters                |

|      |            |            | b.        | Design of gate driving techniques                                                   |

|      |            |            | c.        | Design optimisation and linearity improvement 153                                   |

|      |            |            | d.        | Implementation considerations for an HV switch controller using discrete technology |

|      |            | 7.2.1.2    | Linear    | Voltage Gain SC Converter                                                           |

|      |            |            | a.        | Research investigation into the linear voltage gain SC converters                   |

|      |            |            | b.        | Design optimisation and linearity improvement 154                                   |

|      |            |            | c.        | Design of adaptive bulk biasing techniques 154                                      |

|      |            |            | d.        | Implementation considerations for an HV switch controller in integrated technology  |

|      | 7.2.2      |            |           | work Designs for Impedance Transformation of RF                                     |

|      |            |            | a.        | Research investigation into the impedance network topologies                        |

|      |            |            | b.        | Optimises impedance network to reduce losses and circuit size                       |

|      |            |            | c.        | Research study on the technology of RF switches 155                                 |

|      |            |            | d.        | Design of high impedance coverage technique 156                                     |

|      |            | 7.2.2.1    | Integra   | ted System Designs for Multi Frequency Standards 156                                |

|      |            |            | a.        | Research study on the wide bandwidth impedance networks                             |

|      |            |            | b.        | Implementation considerations for an impedance network integrated with an antenna   |

|        | 7.2.3       | Adaptive Algorithm for Determining the Required Impedance States at the RF Switches  |

|--------|-------------|--------------------------------------------------------------------------------------|

|        |             | a. Research investigation into the linear correlation approach                       |

|        |             | b. Research investigation into the stochastic approach 157                           |

|        |             | c. The design of a speedy adaptive algorithm for mobile applications                 |

| 7.3    | Future      | Work                                                                                 |

|        | 7.3.1       | High Voltage Switch Controller based on SC DC-DC Converters for RF Switch Actuation  |

|        | 7.3.2       | Impedance Network Designs for Impedance Transformation of RF Switches                |

|        | 7.3.3       | Adaptive Algorithms for Determining the Required Impedance States at the RF Switches |

|        | 7.3.4       | Final Comments                                                                       |

| 7.4    | Conclu      | usion                                                                                |

| Appe   | ndix I:     |                                                                                      |

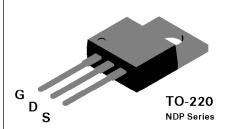

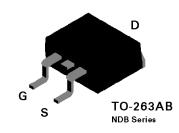

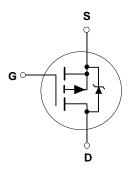

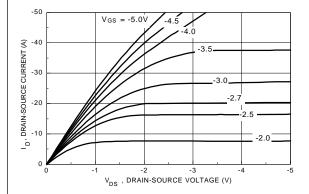

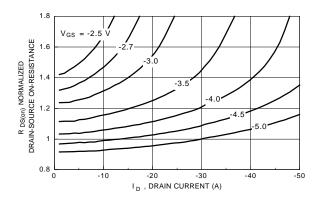

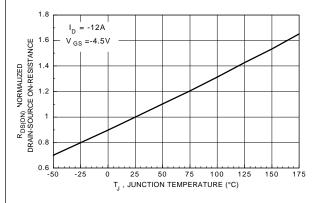

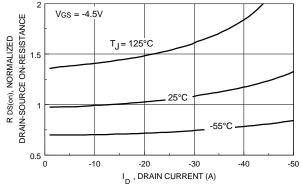

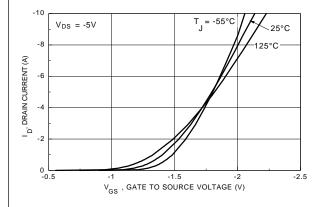

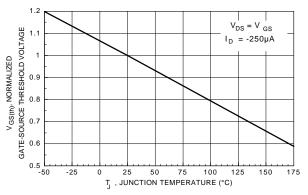

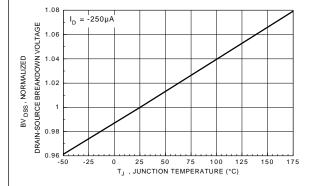

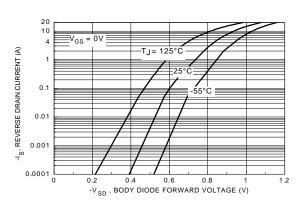

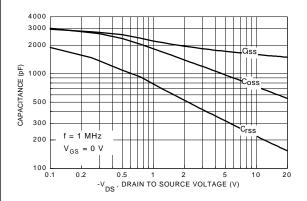

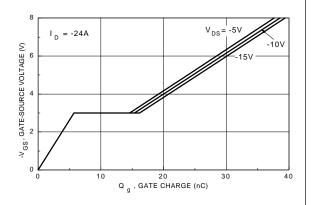

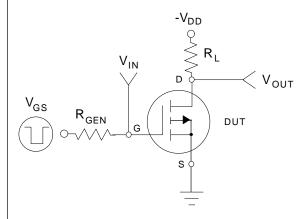

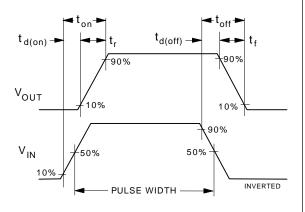

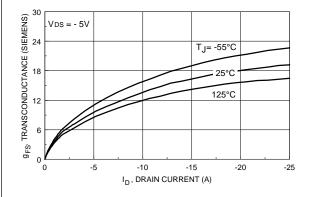

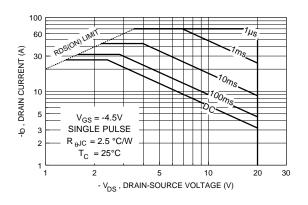

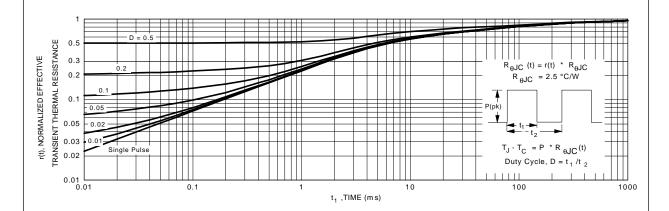

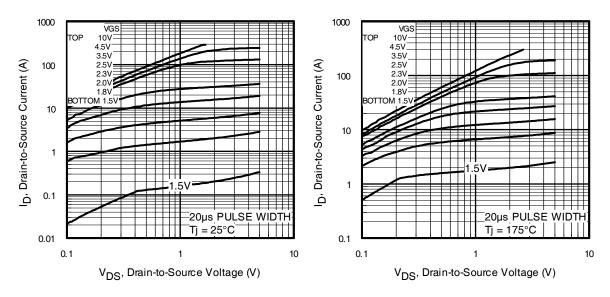

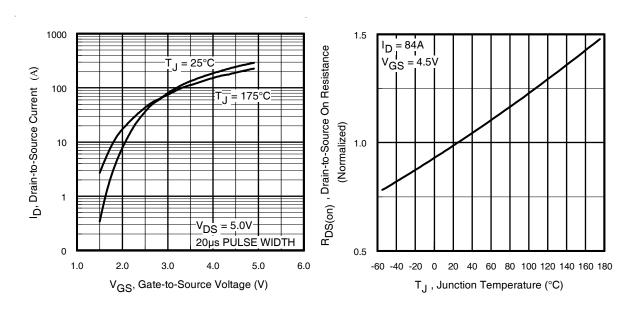

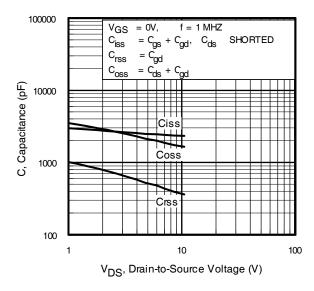

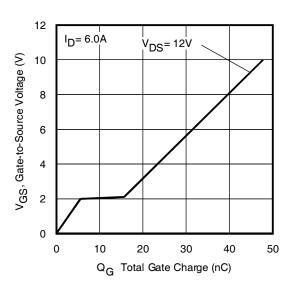

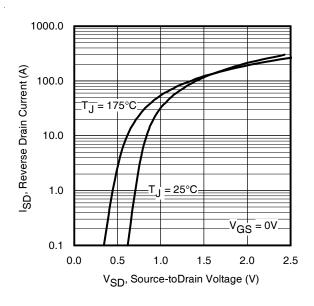

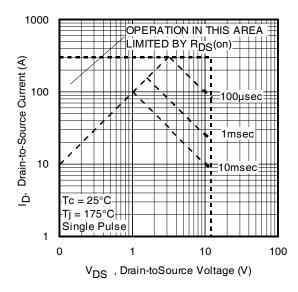

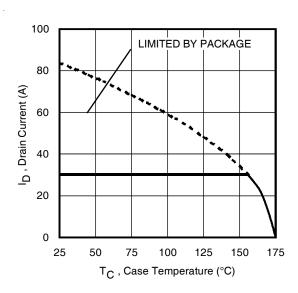

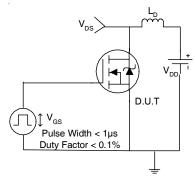

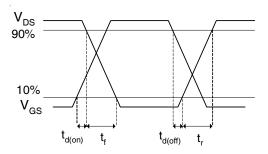

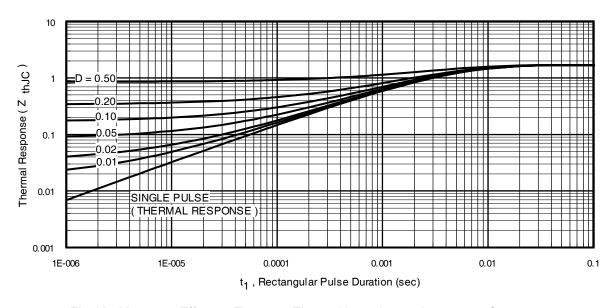

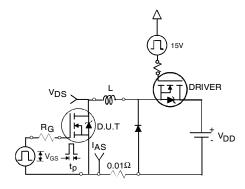

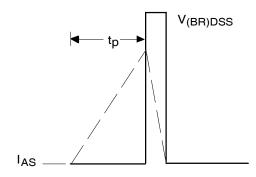

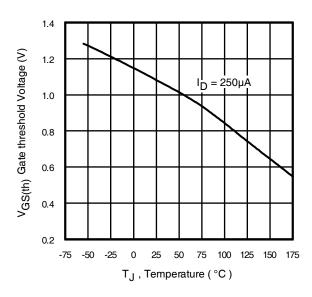

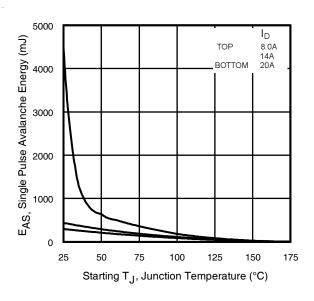

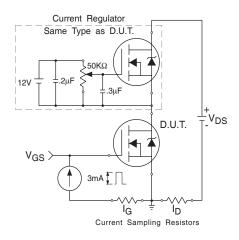

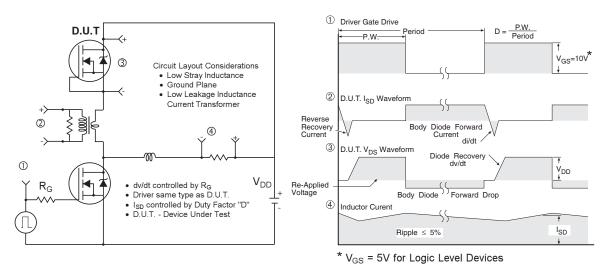

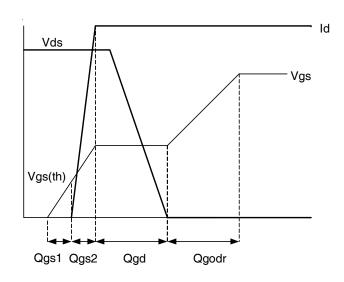

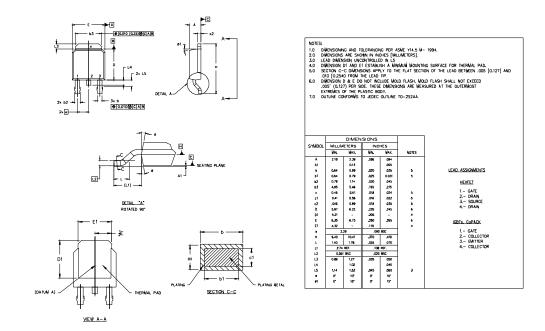

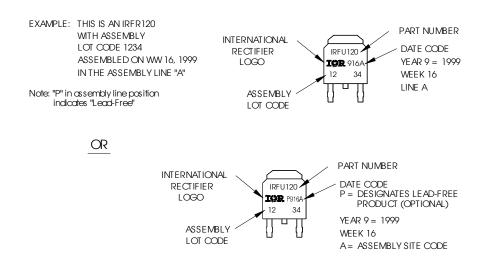

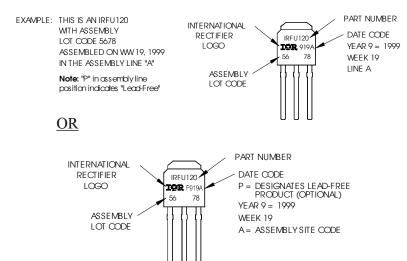

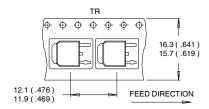

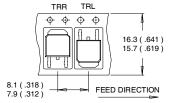

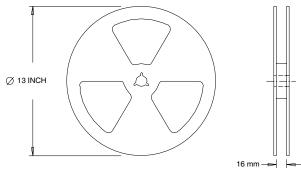

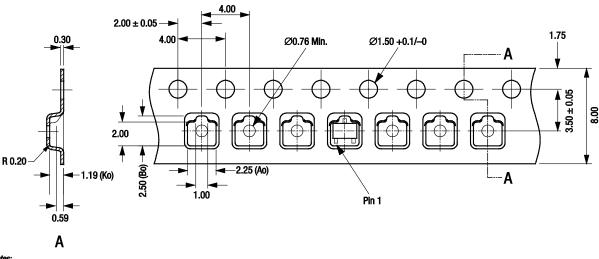

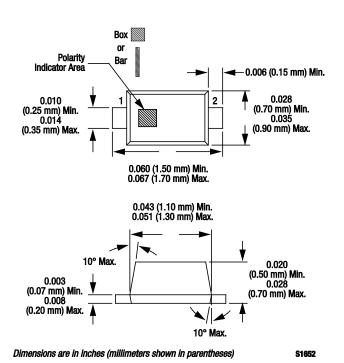

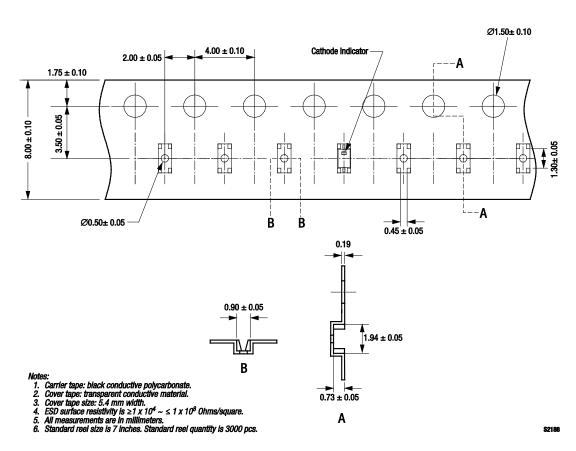

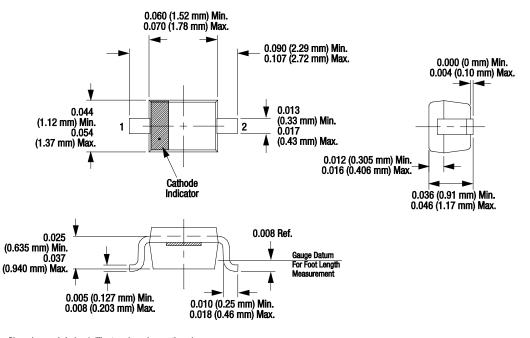

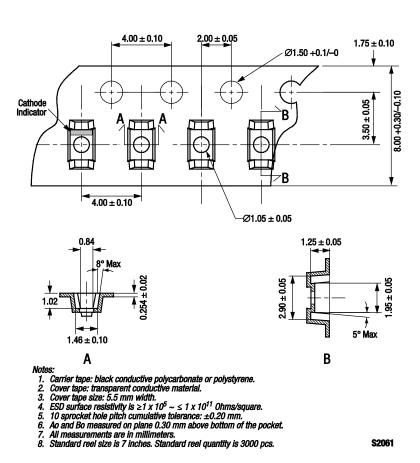

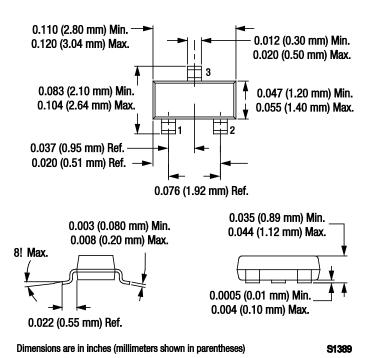

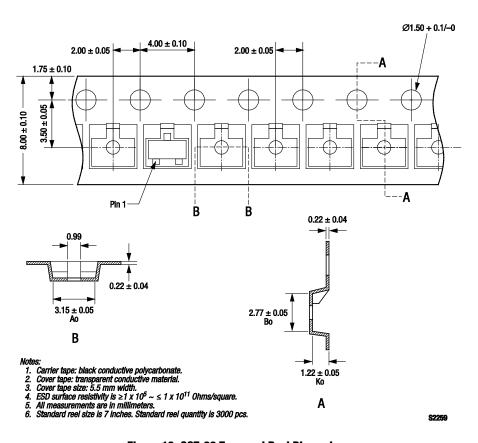

| Trans  | sistor Dev  | vice characteristics178                                                              |

| Appe   | ndix II:    |                                                                                      |

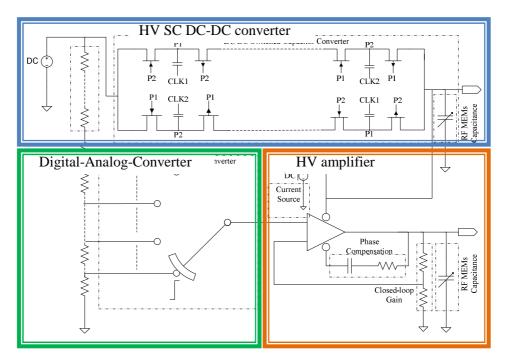

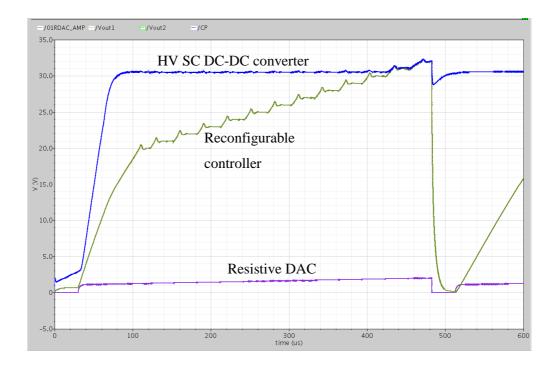

| Recor  | nfigurable  | e HV Controller based SC DC-DC Converter 196                                         |

| Appe   | ndix III:.  |                                                                                      |

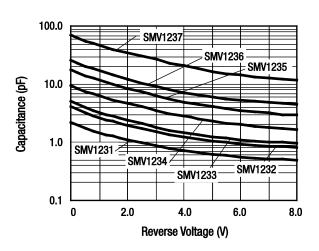

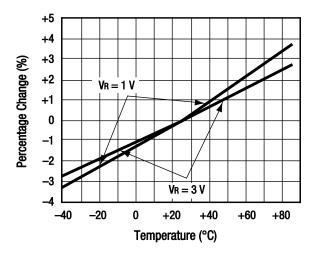

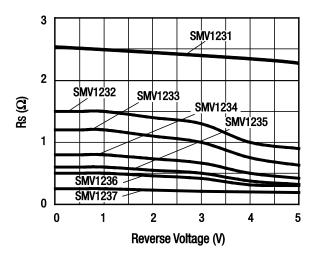

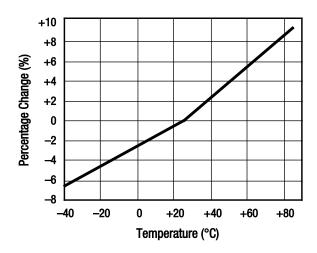

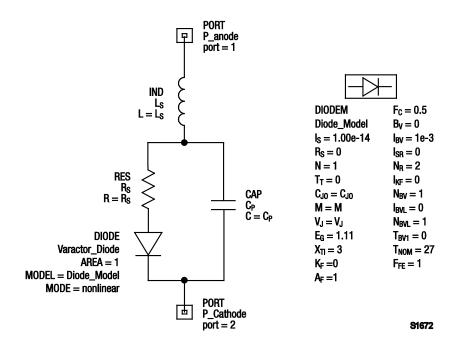

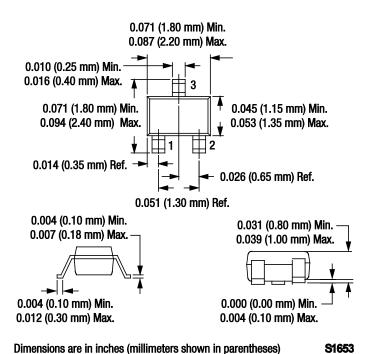

| Data   | sheet of s  | emiconductor hyper abrupt junction tuning varactors 199                              |

| Appe   | ndix IV:.   |                                                                                      |

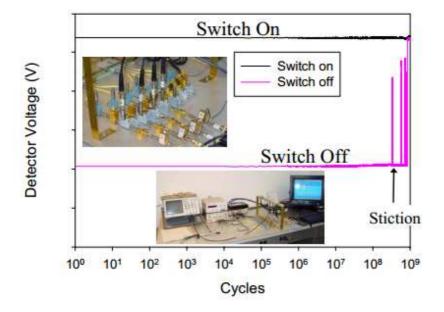

| RF lif | fe time tes | sting of RF MEMS switches211                                                         |

### **List of Figures**

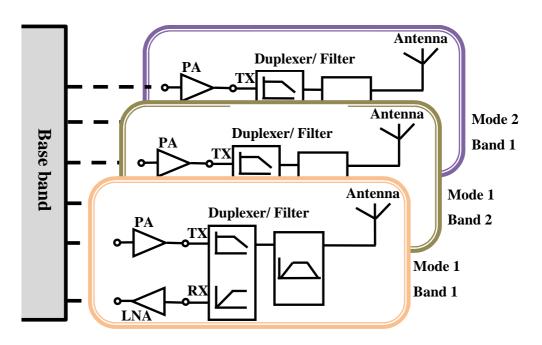

| Figure 1.1: | $\label{eq:multi-mode} \mbox{Multiple transceiver units employed for multi-mode and multi-band operations} \ . \ 2$                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

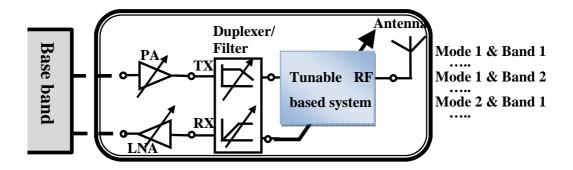

| Figure 1.2: | Tunable RF based system reduces the size of multi-mode and multi-band transceiver                                                       |

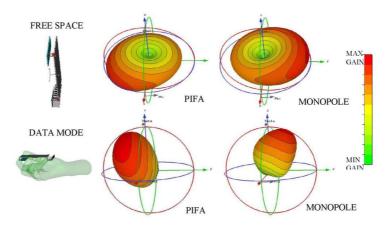

| Figure 1.3: | Effect of human hand (in data mode position) to the antenna gain patterns at 881.5MHz frequency [24]                                    |

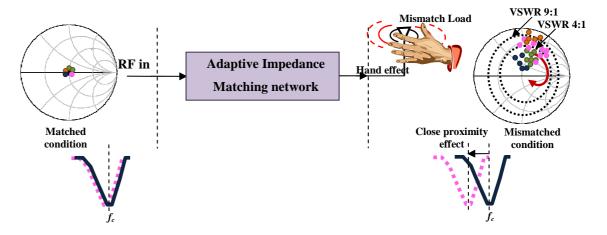

| Figure 1.4: | Adaptability in an RF circuit corrects the antenna impedance mismatch that is caused by the effect of close proximity with a human hand |

| Figure 1.5: | Research areas (in the dashed block) covered in this thesis                                                                             |

| Figure 1.6  | : Topologies of DC-DC converter (a) linear regulator (b) inductor based converter (c) switched capacitor converter                      |

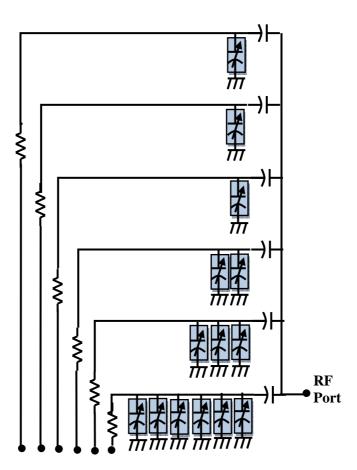

| Figure 1.7: | An example of discrete tuning approach which utilises a total of 14 RF switches in a 6-bit configuration                                |

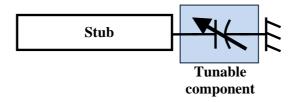

| Figure 1.8: | An example of continuous tuning approach which utilises an RF switch in a tunable matching stub                                         |

| Figure 1.9: | The overview of the research structure (the highlighted boxes are the research areas)                                                   |

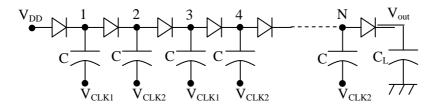

| Figure 2.1: | Dickson SC DC-DC converter with discrete diodes                                                                                         |

| Figure 2.2: | Dickson SC DC-DC converter with MOS diode connected                                                                                     |

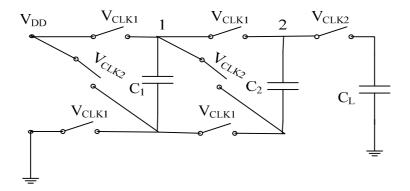

| Figure 2.3: | Bootstrap SC DC-DC converter                                                                                                            |

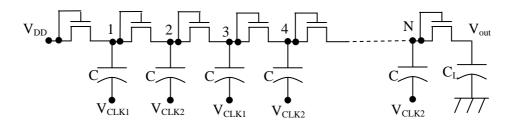

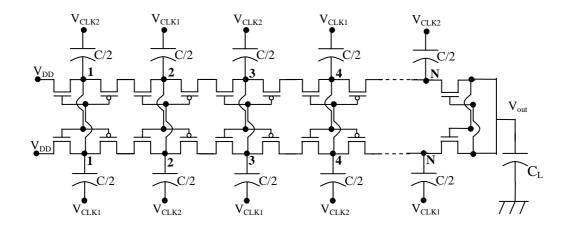

| Figure 2.4: | Interleave structure SC DC-DC converter                                                                                                 |

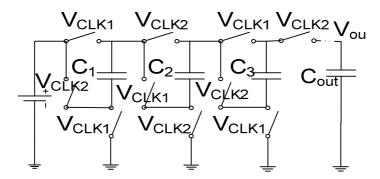

| Figure 2.5: | Series-parallel SC DC-DC converter                                                                                                      |

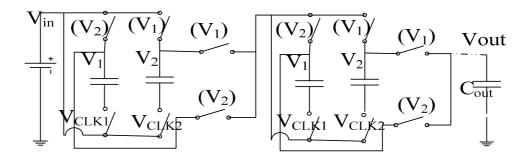

| Figure 2.6: | Voltage doubler SC DC-DC converter                                                                                                      |

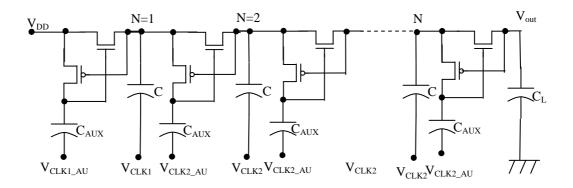

| Figure 2.7: | Fibonacci SC DC-DC converter                                                                                                            |

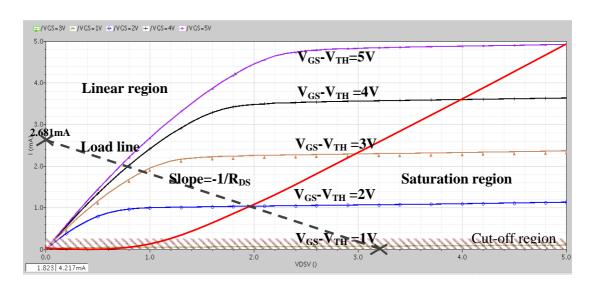

| Figure 2.8: | I-V characteristic curve of a transistor                                                                                                |

| Figure 2.9: Illustration of transistors in a Dickson SC DC-DC converter in a steady state                                                                                                                                                                          | 27 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.10: Illustration of transistors in a voltage doubler SC DC-DC converter in a stead state                                                                                                                                                                  | •  |

| Figure 2.11: Illustration of transistors in a Fibonacci SC DC-DC converter in a steady state                                                                                                                                                                       | 28 |

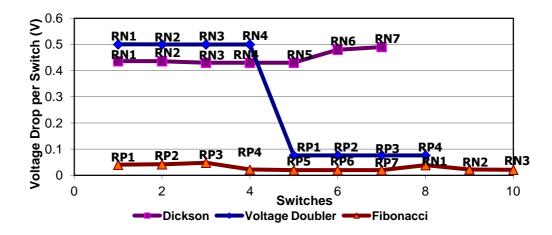

| Figure 2.12: Total resistive voltage drop in the SC DC-DC converters at a steady state                                                                                                                                                                             | 29 |

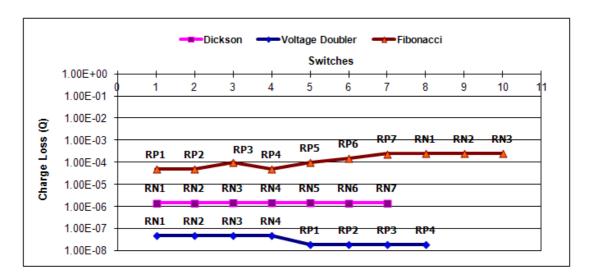

| Figure 2.13: Total charge loss in the SC DC-DC converters at a dynamic state                                                                                                                                                                                       | 31 |

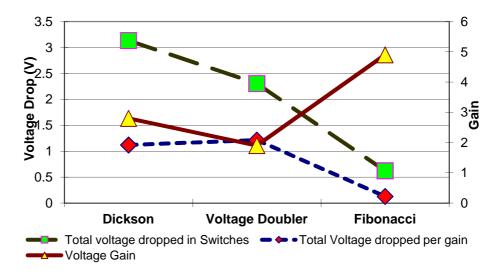

| Figure 2.14 Comparison of total voltage drop versus voltage conversion gain amongst the SDC-DC converters                                                                                                                                                          |    |

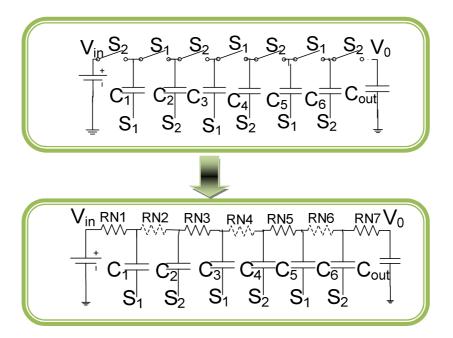

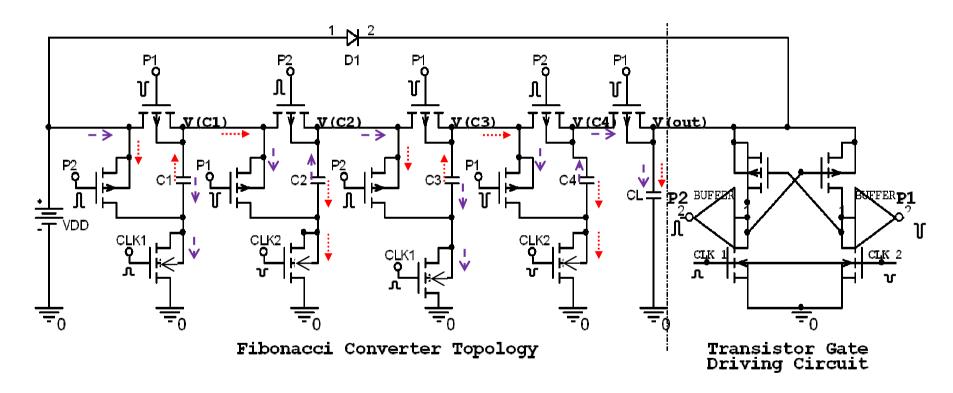

| Figure 2.15: Effective gate driving technique for a low to medium voltage conversion gain Fibonacci SC DC-DC converter                                                                                                                                             |    |

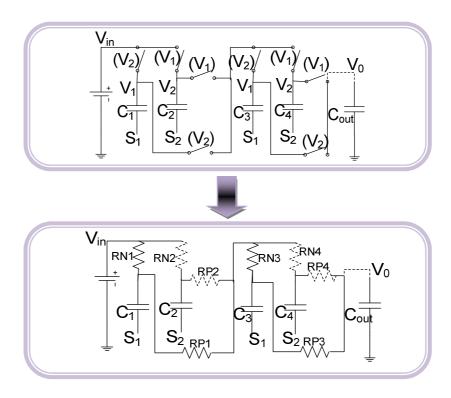

| Figure 2.16: Effective gate driving technique for a long cascaded high voltage conversion gain Fibonacci SC DC-DC converter                                                                                                                                        |    |

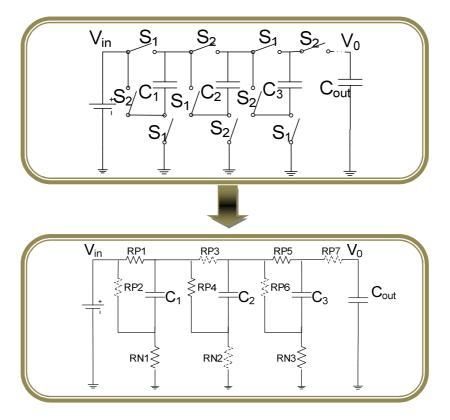

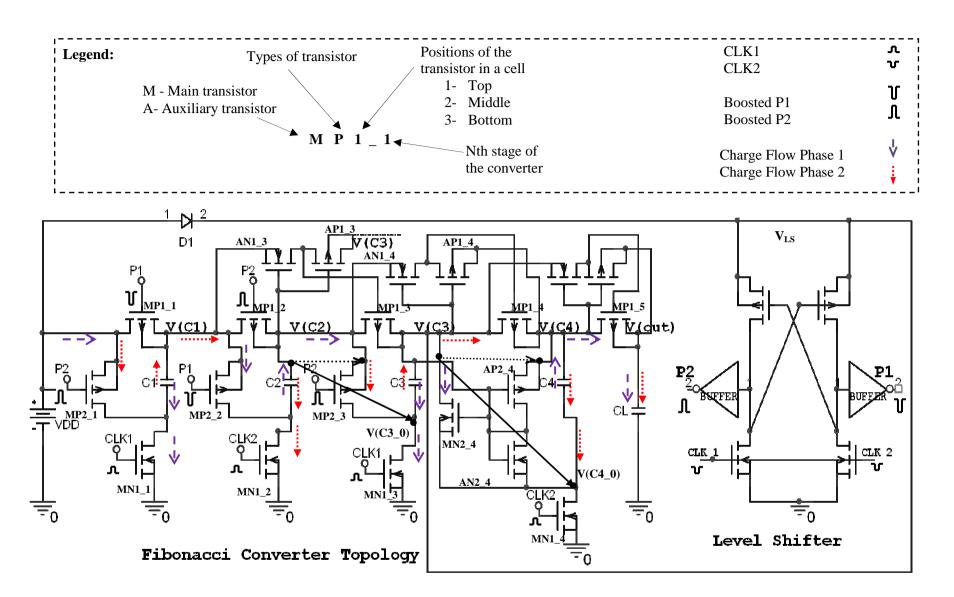

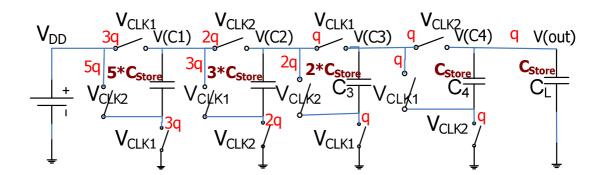

| Figure 2.17: Charge flow and optimisation in the Fibonacci SC DC-DC converter                                                                                                                                                                                      | 38 |

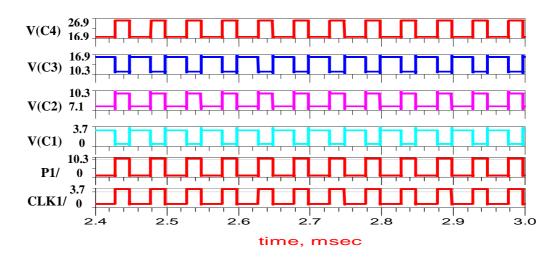

| Figure 2.18: The internal node voltage levels for the 8 <i>X</i> Fibonacci SC DC-DC converter                                                                                                                                                                      | 39 |

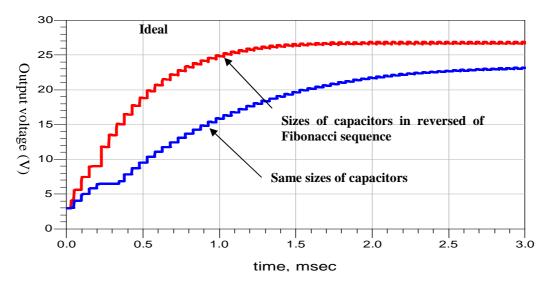

| Figure 2.19: The simulated output voltages for the 8X Fibonacci SC DC-DC converter                                                                                                                                                                                 | 40 |

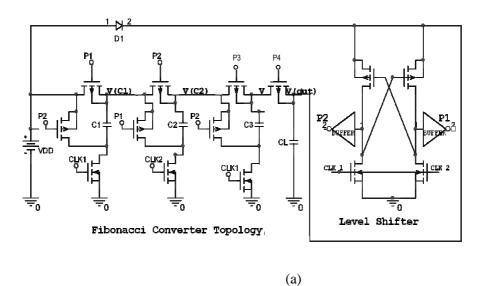

| Figure 2.20: The fabricated 5X Fibonacci SC DC-DC converter by discrete components (a circuit diagram (b) prototype                                                                                                                                                | -  |

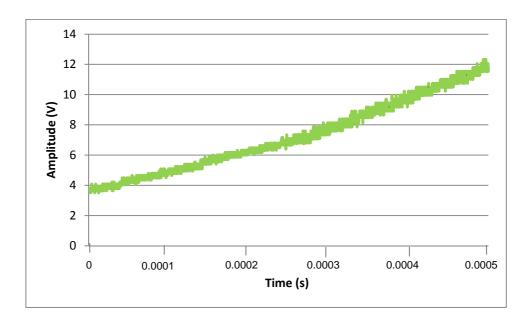

| Figure 2.21: Measurement result of the SC DC-DC converter                                                                                                                                                                                                          | 42 |

| Figure 2.22: Summary of the areas and the challenges addressed in Chapter 2                                                                                                                                                                                        | 44 |

| Figure 3.1: Interleave structure linear voltage gain SC DC-DC converter                                                                                                                                                                                            | 47 |

| Figure 3.2: Single stage of the SC DC-DC converter with adaptive bulk biasing circuit (a) schematic, (b) the equivalent cross-section in floating pMOS LV transistors, an (c) the equivalent cross-section in floating nMOS LV transistors with parasitic elements |    |

| Figure 3.3: Output stage of the SC DC-DC converter with an adaptive output stage biasing circuit                                                                                                                                                                   | -  |

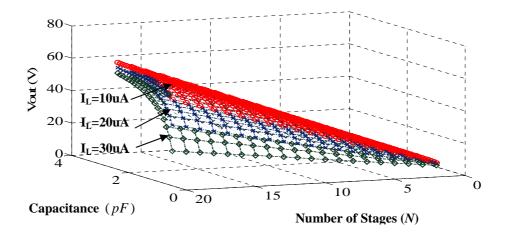

| Figure 3.4: Output voltage of an ideal SC converter (without loss) operating at 25MHz for to 20 number of stages ( $N$ ), and three different output currents ( $I_L$ )                                                                                            |    |

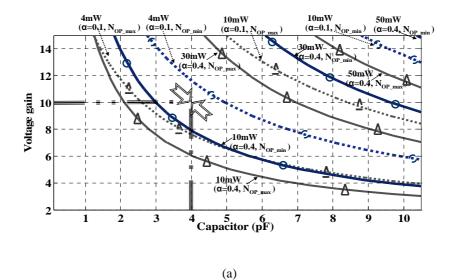

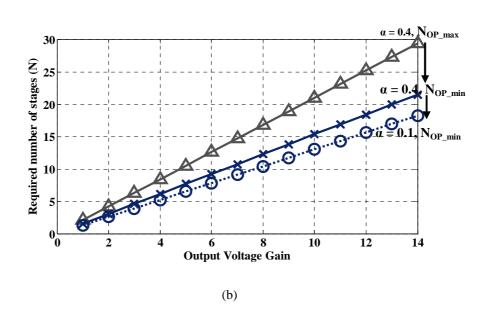

| Figure 3.5: | Comparison of power consumption and voltage gain by minimising $I_L$ (O) and maximising $I_L$ ( $\Delta$ ) design (a) Power consumption of an SC converter with parasitic capacitance losses of $\alpha = 0.1$ (dotted line) and $\alpha = 0.4$ (solid line) and $\beta = 0.05$ , threshold voltage $V_{TH} = 0.7V$ (b) Required number of stages based on different voltage gains                                            |

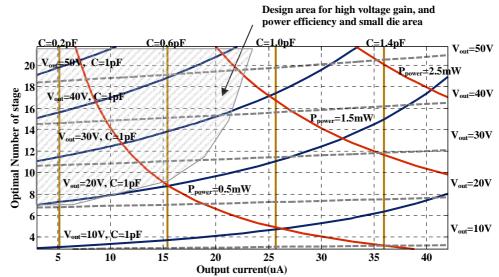

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.6: | Design area of an SC DC-DC converter with an operating frequency of $f$ = 25 MHz, with the assumption that parasitic capacitance loss of $\alpha$ =0.4, and a constant threshold voltage of 0.7V from the transistors                                                                                                                                                                                                         |

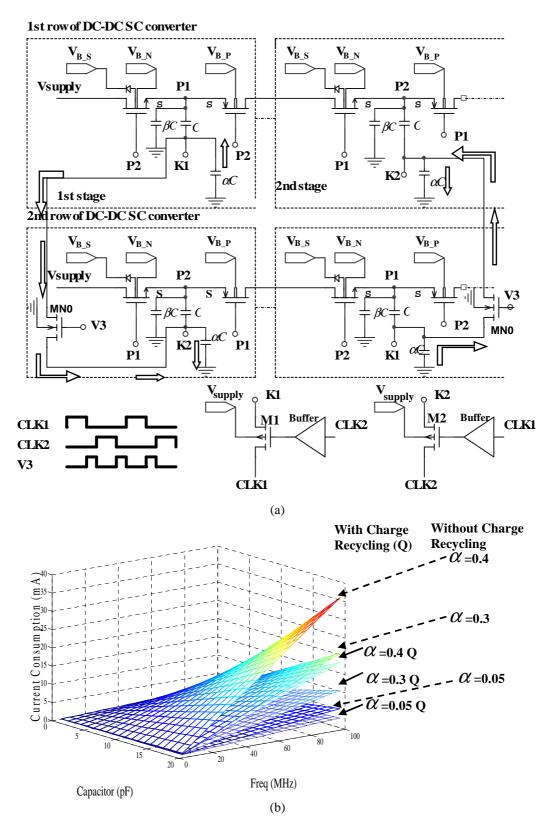

| Figure 3.7: | Charge recycling technique in the SC DC-DC converter (a) circuit diagram for the implementation (b) Comparison of the current consumption with and without the charge recycling technique                                                                                                                                                                                                                                     |

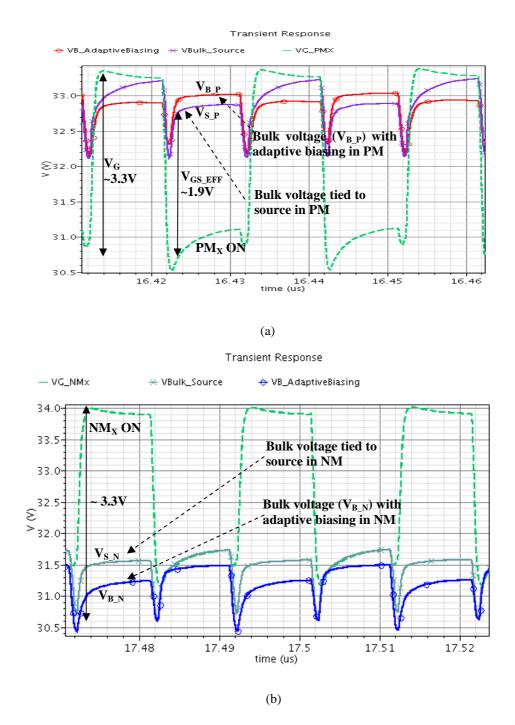

| Figure 3.8: | Simulation results of the proposed SC DC-DC converter show (a) bulk voltage in PM ( $V_{B\_P}$ ) that uses the inter stage adaptive biasing circuit is always higher than its source to switch off the vertical parasitic bipolar in PM, (b) bulk voltage in NM ( $V_{B\_N}$ ) that uses the inter stage adaptive biasing circuit is always lower than its source to switch off the vertical parasitic bipolar in NM          |

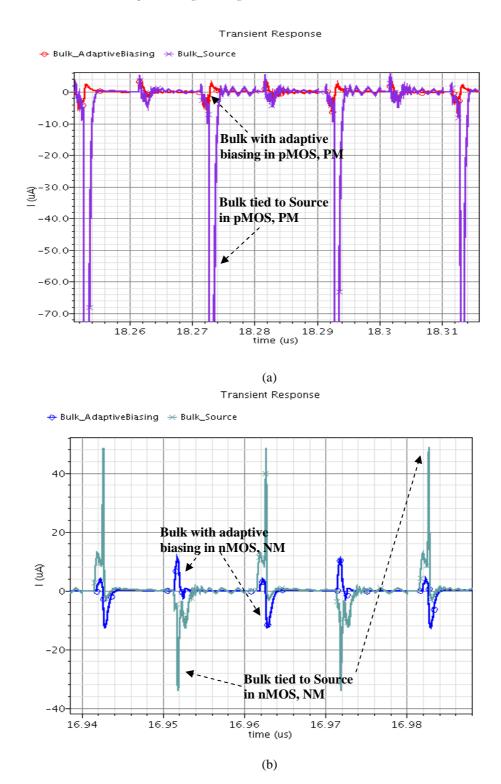

| Figure 3.9: | Simulation results of the proposed SC DC-DC converter show (a) no leakage current in PM that uses the adaptive biasing circuit compared to the PM's bulk tied to its source (which have very high current peaks flowing to the substrate) and, (b) no leakage current in NM that uses the adaptive biasing circuit compared to the NM's bulk tied to its source (which have very high current peaks flowing to the substrate) |

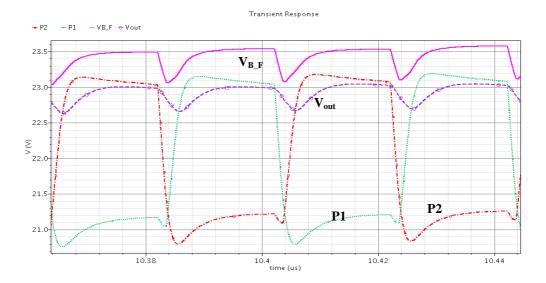

| Figure 3.10 | b: Bulk voltage at the output stage ( $V_{B_{\_F}}$ ) of the proposed SC DC-DC converter that uses the final stage adaptive biasing circuit is always higher than the output voltage, $P1$ and $P2$ to prevent the converter from latch-up                                                                                                                                                                                    |

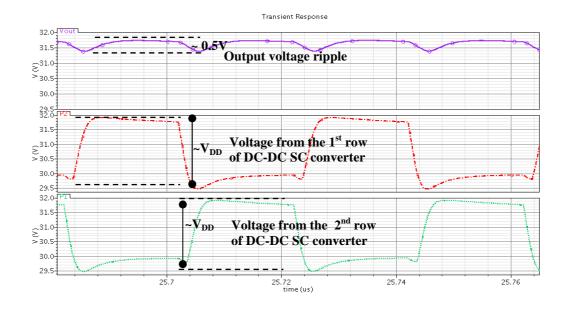

| Figure 3.11 | : The SC converter achieves small ripples at the output voltage through complementing the internal node voltages from the 1 <sup>st</sup> and the 2 <sup>nd</sup> rows of the SC DC-DC converter                                                                                                                                                                                                                              |

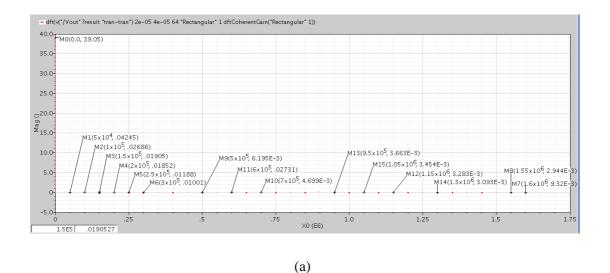

| Figure 3.12 | 2: The output voltage ripple and its harmonic in (a) magnitude and (b) dB10 65                                                                                                                                                                                                                                                                                                                                                |

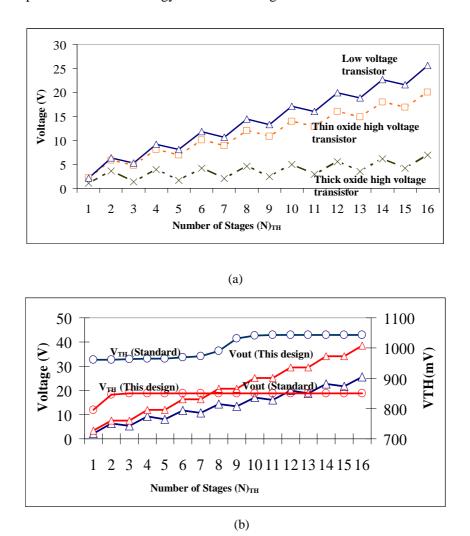

| Figure 3.13 | 8: Simulation results of the SC DC-DC converter with improved voltage gain through (a) LV transistors and (b) low V <sub>TH</sub> in transistors                                                                                                                                                                                                                                                                              |

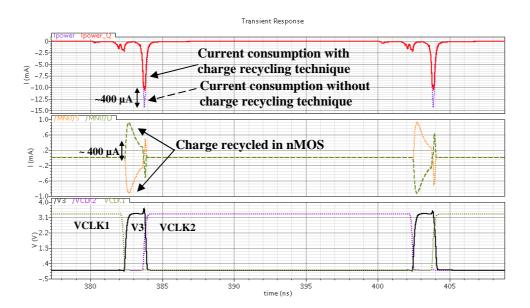

| Figure 3.14 | E: Charges in parasitic capacitors are recycled to reduce the current consumption, I <sub>power</sub> through an optimized nMOS, MN0 operating at period of V3                                                                                                                                                                                                                                                                |

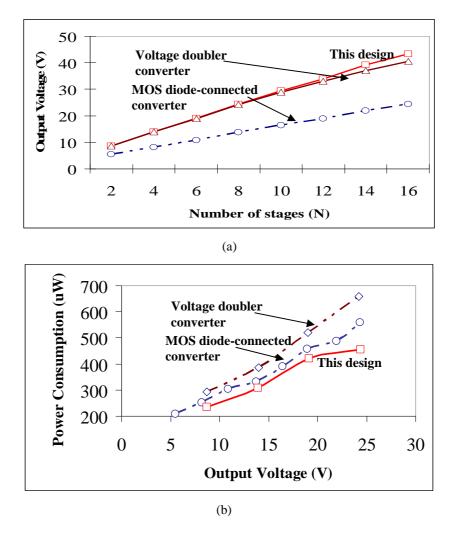

| Figure 3.15 | 5: Simulation results of the improved HV SC DC-DC converter compared with the standard MOS diode-connected converter and the voltage doubler converter, with 0.935pF per stage at 25MHz, in terms of a) output voltage and b) power consumption                                                                                                                                                                               |

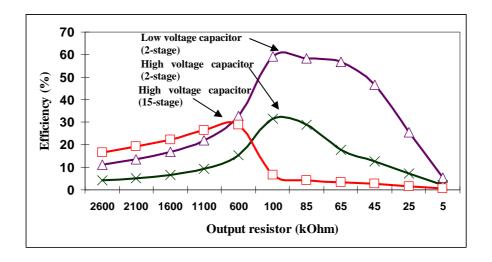

| Figure 3.16 | 6: A 2-stage and a 15-stage SC DC-DC converters using HV capacitors compare with a 2-stage SC converter using LV capacitors in terms of (a) efficiency and (b) output voltage                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.17 | 2: Layout of the enhanced interleave structure HV SC DC-DC converter in a single stage                                                                                                                                                                                                                                 |

| Ü           | 2: Layout of the enhanced interleave structure HV SC DC-DC converter in fabrication ready pad frame (with the effective area of 0.2176 mm² surrounded by the red colour line) compares with the standard MOS diode-connected converter that has the effective area of 0.3924mm² (surrounded by the yellow colour line) |

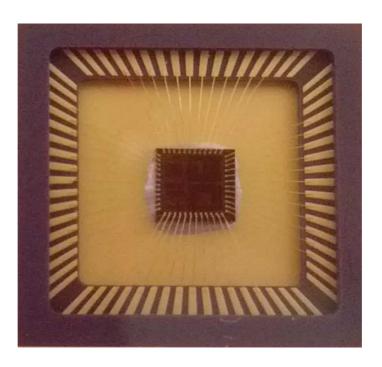

| Figure 3.19 | 2: The fabricated SC DC-DC converter on a die                                                                                                                                                                                                                                                                          |

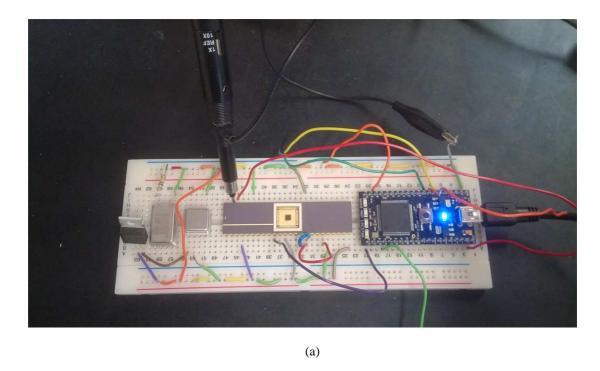

| Figure 3.20 | The fabricated SC DC-DC converter (a) in the testing set up environment and, (b) the generated 22MHz square ware clock signal by the ARM processor 75                                                                                                                                                                  |

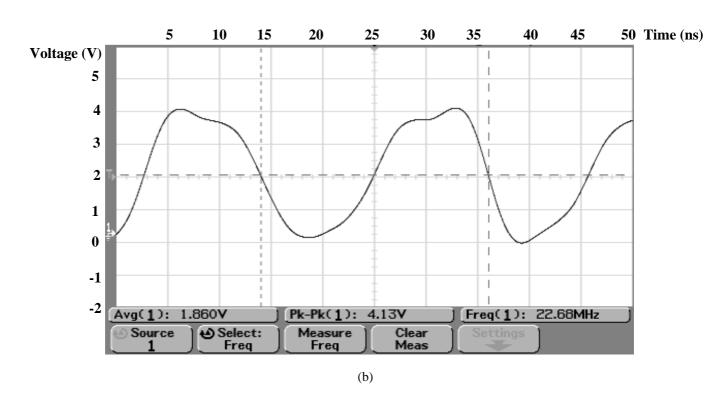

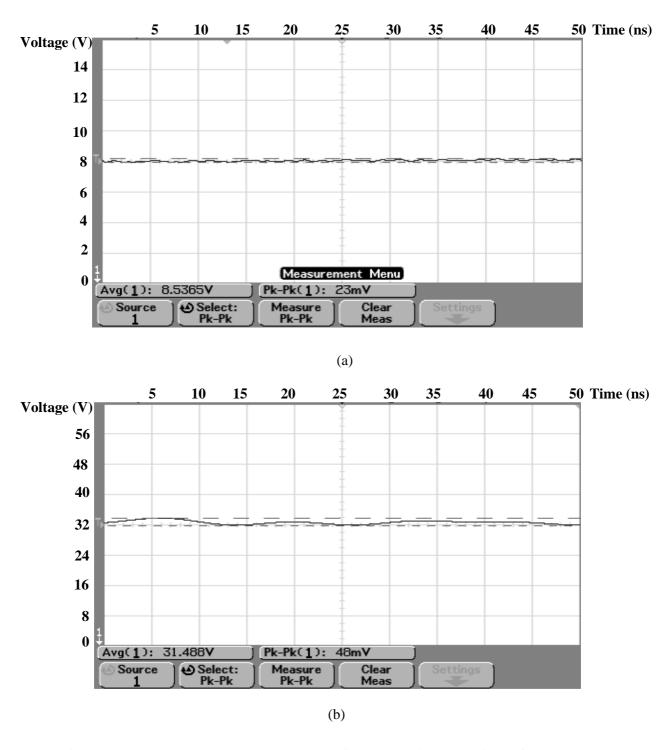

| C           | : Measured output voltages (a) at 8.53V for 2-stage (with voltage ripple of 23mV) and, (b) at 31.49V for 15-stage (with voltage ripple of 48mV) based on the 22MHz frequency                                                                                                                                           |

| Figure 3.22 | 2: Summary of the areas and the challenges addressed in Chapter 3                                                                                                                                                                                                                                                      |

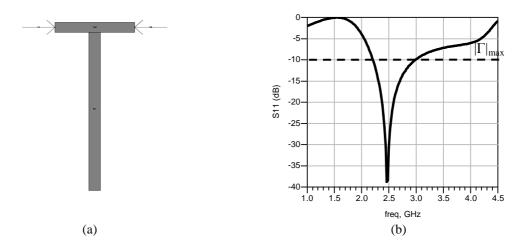

| Figure 4.1: | A quarter-wave impedance matching in (a) layout view and (b) its characteristic                                                                                                                                                                                                                                        |

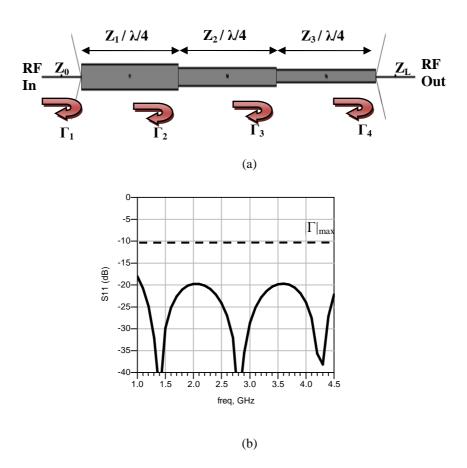

| Figure 4.2: | A multi-section impedance network in (a) layout view and (b) its characteristic 82                                                                                                                                                                                                                                     |

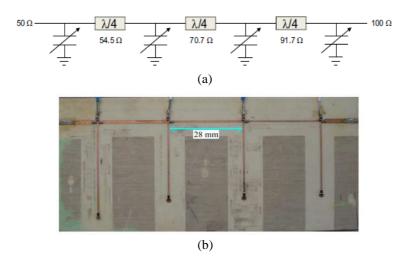

| •           | A Binomial multi-section impedance network to transform from 50 $\Omega$ and 100 $\Omega$ in (a) schematic view and (b) prototype [56]                                                                                                                                                                                 |

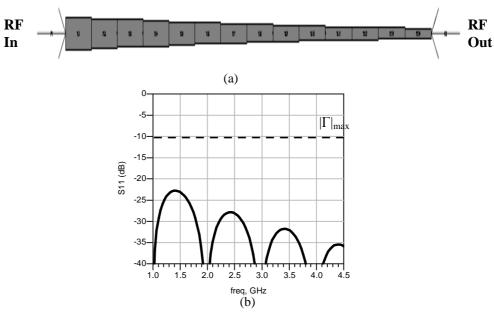

| Figure 4.4: | A continuous tapered line in (a) layout view and (b) its characteristic                                                                                                                                                                                                                                                |

| Figure 4.5: | Single matching stub in (a) layout view and (b) its characteristic                                                                                                                                                                                                                                                     |

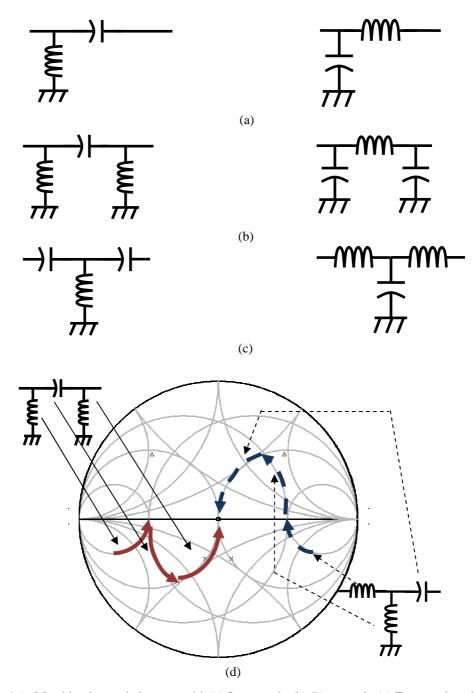

| Figure 4.6: | Matching lumped elements with (a) L-network, (b) <i>Pi</i> -network, (c) T-network and (d) the trajectories of series and parallel inductors and capacitors on the Smith chart                                                                                                                                         |

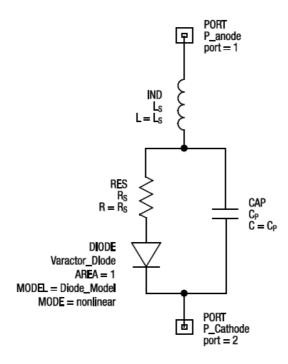

| Figure 4.7: | SPICE model of a varactor                                                                                                                                                                                                                                                                                              |

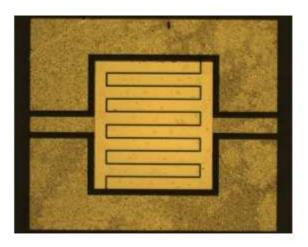

| Figure 4.8: | BST interdigital capacitive electrodes RF switches with five finger pairs [135] 92                                                                                                                                                                                                                                     |

| Figure 4.9: | Scanning Electron Microscope (SEM) micrograph of ohmic RF MEMS switching technologies for discrete tuning approach [140]                                                                                                                                                                                                                                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.10 | 2): SEM micrograph of capacitive RF MEMS switching technologies for continuous tuning approach [141]                                                                                                                                                                                                                                                                                                                                     |

| Figure 4.11 | : Comparison of capacitance-voltage (CV) curves for a selection of RF switches technologies                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.12 | 2: A <i>Pi</i> -network with related network parameters                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 4.13 | 3: Simulated impedance coverage (lossless) of a sample <i>Pi</i> -network. The arrows indicate the directions of increase for C <sub>1</sub> and C <sub>2</sub> from 1pF to 37pF98                                                                                                                                                                                                                                                       |

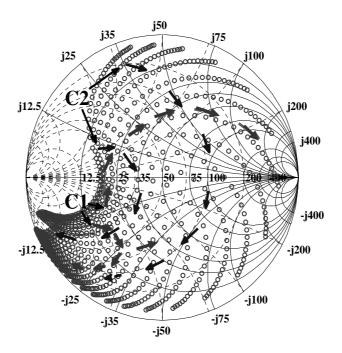

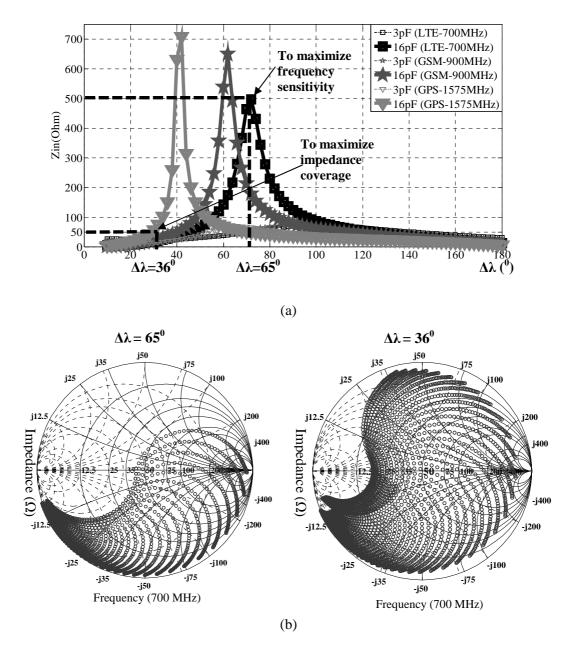

| Figure 4.14 | 4: Technique in choosing the electrical length of the series transmission line $(\Delta\lambda)$ based on tuning range and operating frequency. (a) Magnitude of the input impedances for different electrical length of the series transmission line using capacitor values of $C_1$ =[1pF, 37pF] and $C_2$ =[1pF, 37pF], and (b) the impedance coverage in the Smith chart at $\Delta\lambda$ =36° and $\Delta\lambda$ =65° (lossless) |

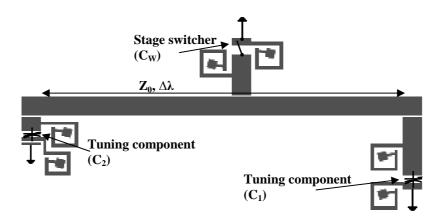

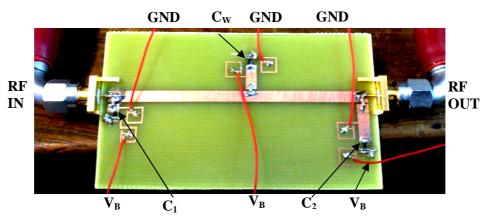

| Figure 4.15 | 5: Layout of the $\Delta\lambda$ reconfigurable <i>Pi</i> -network                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.16 | $\Delta \lambda$ reconfigurable <i>Pi</i> -network to achieve high impedance coverage at multi frequency standards                                                                                                                                                                                                                                                                                                                       |

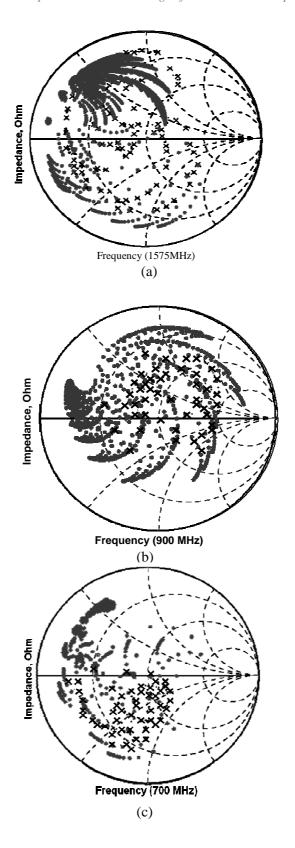

| Figure 4.17 | 7: Simulated (O) and measured (X) range of impedance coverage at (a) GPS (1575 MHz) (b) GSM (900 MHz), and (c) LTE (700 MHz)                                                                                                                                                                                                                                                                                                             |

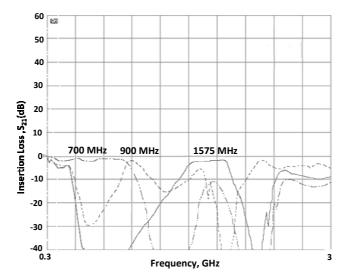

| Figure 4.18 | 3: Insertion loss of the <i>Pi</i> -network at 1575 MHz, 900 MHz and 700 MHz 105                                                                                                                                                                                                                                                                                                                                                         |

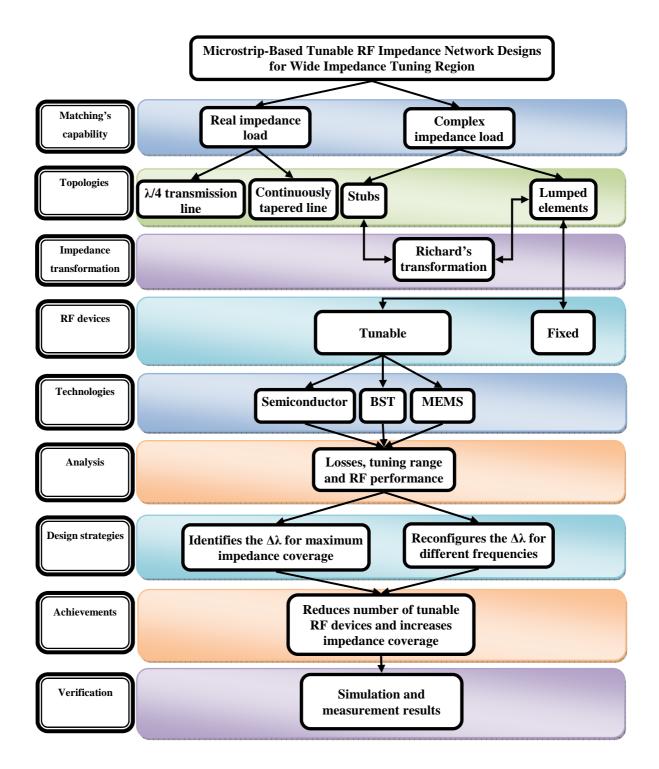

| Figure 4.19 | 9: Summary of the areas and the challenges addressed in Chapter 4 108                                                                                                                                                                                                                                                                                                                                                                    |

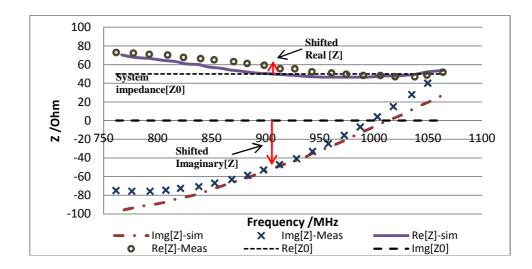

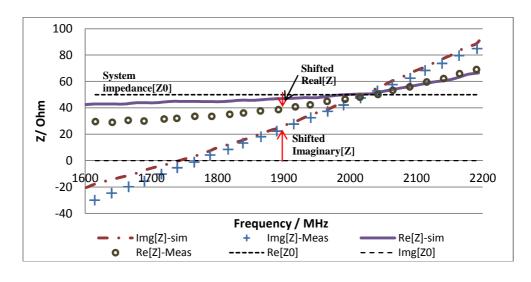

| Figure 5.1: | Effect on a $\lambda/4$ monopole antenna in close proximity to the user, causing a shift in the antenna input impedance from its nominal value ( $Z_0$ ) at (a) 914MHz and (b) 1890MHz operating frequencies [166]                                                                                                                                                                                                                       |

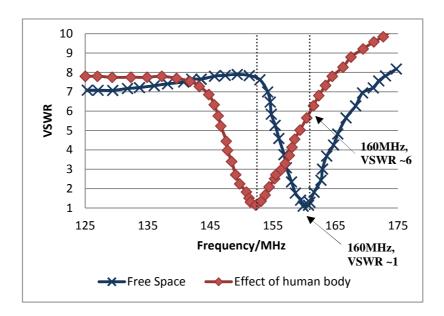

| Figure 5.2: | Effect of a monopole helical antenna in close proximity to the human body, causing a change in the resonant frequency of the antenna away from the desired frequency at 160MHz [68]                                                                                                                                                                                                                                                      |

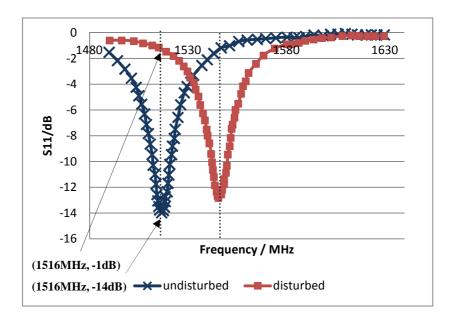

| Figure 5.3: | Effect of a microstrip patch antenna in close proximity with a metal sheet shifts the resonant frequency of the antenna and increases the reflected power [167]113                                                                                                                                                                                                                                                                       |

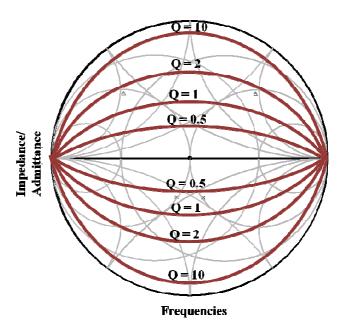

| Figure 5.4: | Bandwidth of the impedance network depends on the level of mismatch load and could be estimated by constant-Q lines on the Smith chart                                                                                                                                                                                                                                                                                                   |

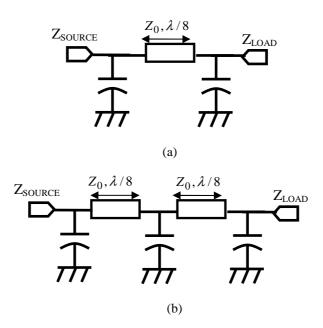

| Figure 5.5: | Impedance networks based on (a) a single <i>Pi</i> -network, and (b) two <i>Pi</i> -networks                                                                    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

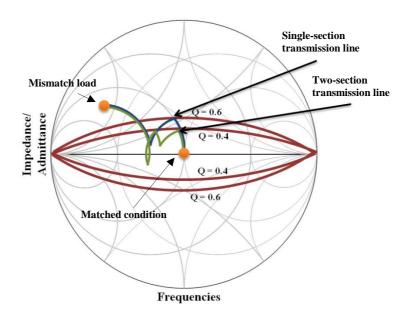

| Figure 5.6: | The impedance network based on two $Pi$ -networks achieves a smaller Q factor (Q = 0.4) compared to a single $Pi$ -network (Q = 0.6)                            |

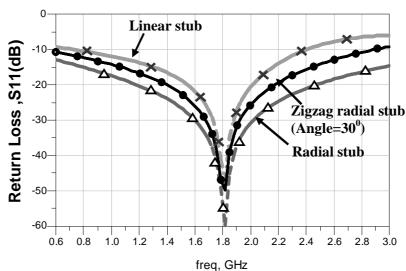

| Figure 5.7: | Bandwidths of linear open-circuited stub, radial stub (angle=90°) and zigzag radial stub (angle=30°)                                                            |

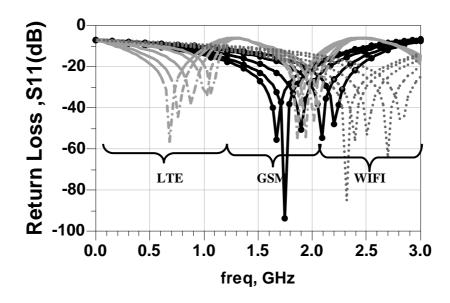

| Figure 5.8: | Frequency agility of the impedance network at LTE, GSM and WIFI 118                                                                                             |

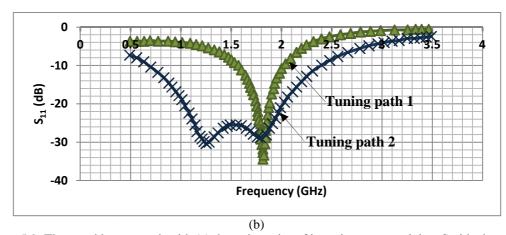

| Figure 5.9: | The matching network with (a) the trajectories of impedance network in a Smith chart and (b) the corresponding return loss                                      |

| Figure 5.10 | 2: Layout of the impedance network for LTE, GSM and WIFI operating standards                                                                                    |

| Figure 5.11 | : The configuration in semiconductor based varactor biasing circuit                                                                                             |

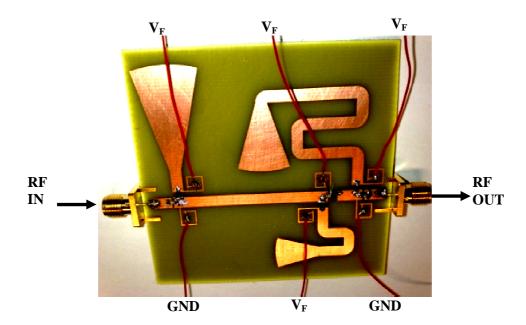

| Figure 5.12 | 2: Prototype of the impedance network with frequency-reconfigurable capability                                                                                  |

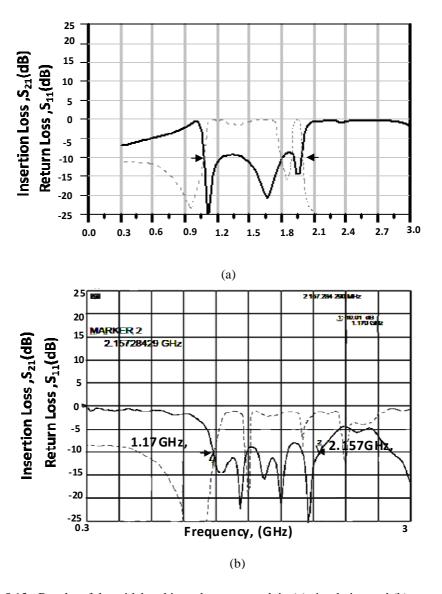

| Figure 5.13 | 3: Results of the wideband impedance network in (a) simulation and (b) measurement                                                                              |

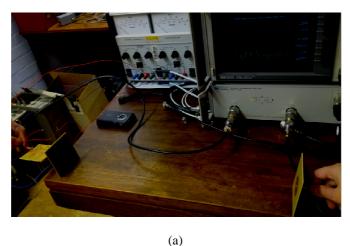

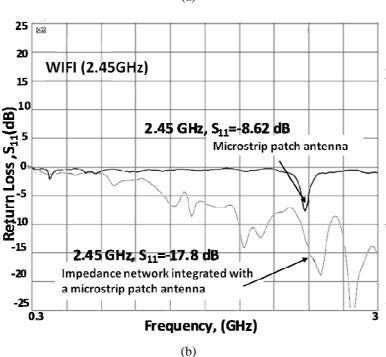

| Figure 5.14 | l: Integrated system of the impedance network with a simple microstrip antenna in (a) experimental setup and (b) measurement result at 2.45GHz                  |

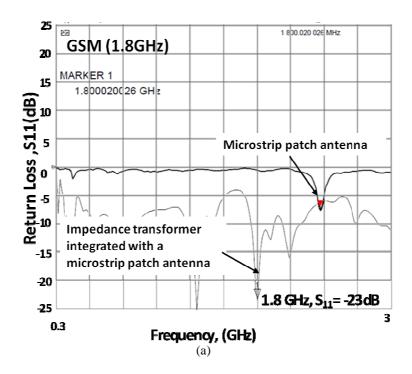

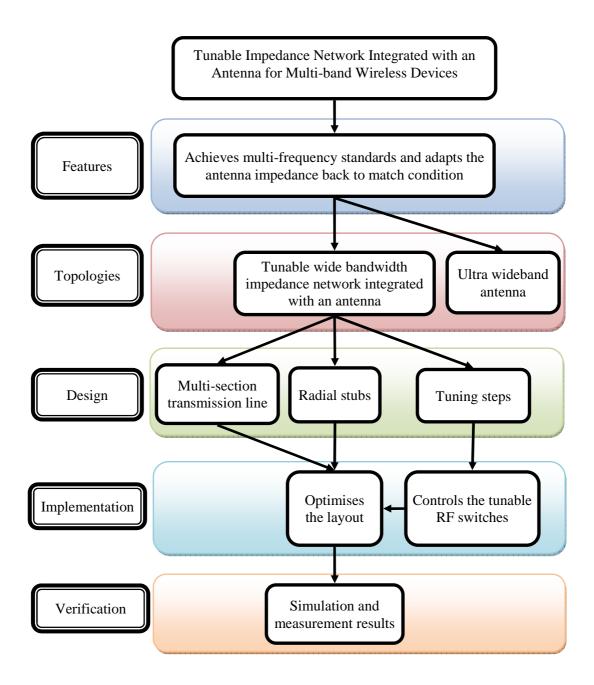

| Figure 5.15 | 5: Measured results of the integrated system at (a) 1.8GHz, and (b) 700 MHz . 125                                                                               |

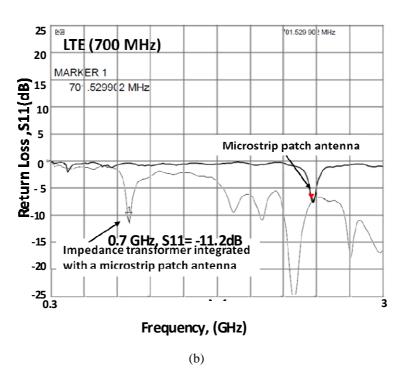

| Figure 5.16 | 5: Insertion loss of the antenna and the integrated system                                                                                                      |

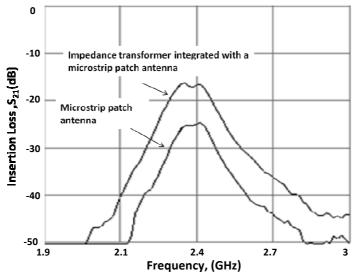

| Figure 5.17 | 7: Summary of the areas and the challenges addressed in Chapter 5                                                                                               |

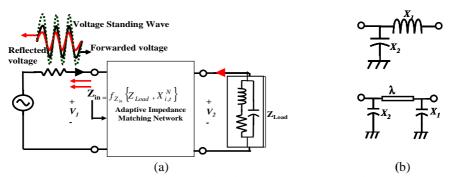

| Figure 6.1: | Block diagram of an adaptive impedance network (a) impedance network parameters (b) impedance network topologies: <i>LC</i> -network and <i>Pi</i> -network 130 |

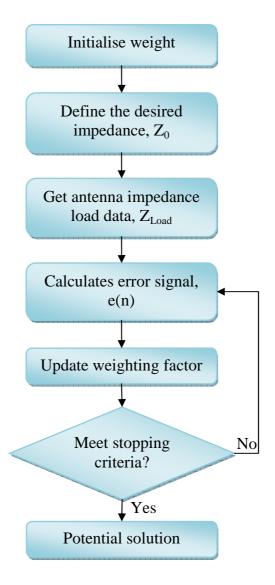

| Figure 6.2: | LMS process flow                                                                                                                                                |

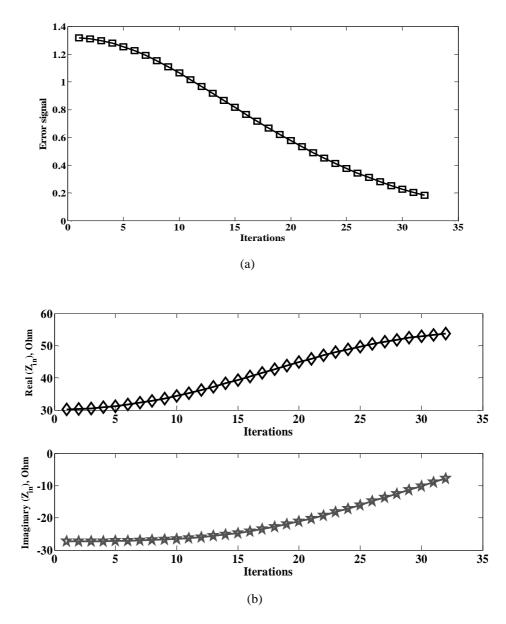

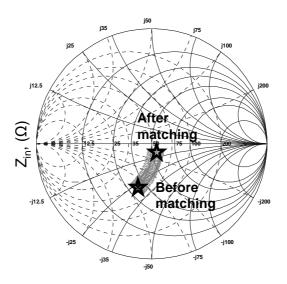

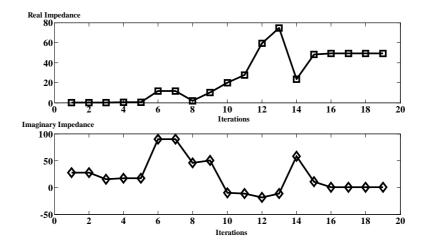

| Figure 6.3: | Convergence of LMS based on (a) error signals and (b) the real and imaginary of input impedances over number of iterations                                      |

| Figure 6.4: | Convergence of LMS based on complex impedances in a Smith chart 135                                                                                             |

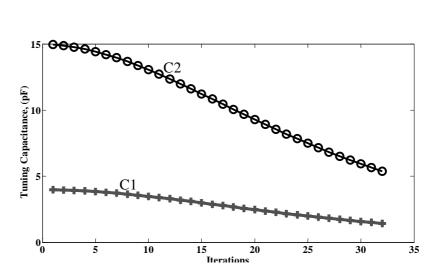

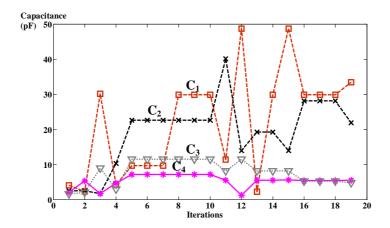

| Figure 6.5: | Tuning elements $C_1$ and $C_2$ over number of iterations                                                                                                       |

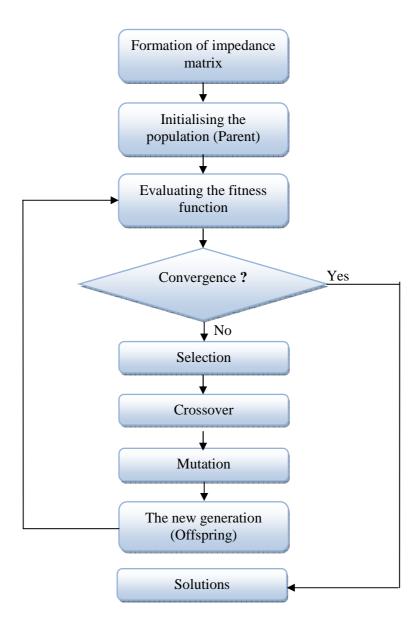

| Figure 6.6: | GA process flow                                                                                                                                                                                                         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

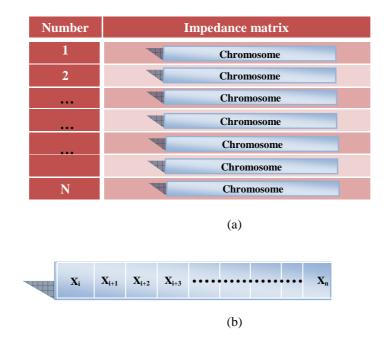

| Figure 6.7: | Population of the GA with (a) the formation of the impedance matrix and (b) the arrangement of RF switches in a chromosome structure                                                                                    |

| Figure 6.8: | Convergence of GA based on complex input impedances in the Smith chart 140                                                                                                                                              |

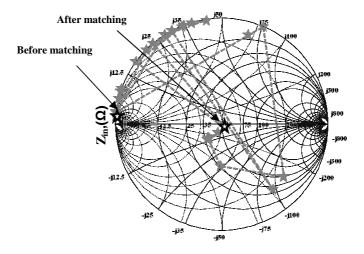

| Figure 6.9: | Convergence of the GA based on real and imaginary parts of input impedances over number of iterations                                                                                                                   |

| Figure 6.10 | ): Tuning elements $C_1$ , $C_2$ , $C_3$ and $C_4$ over number of iterations                                                                                                                                            |

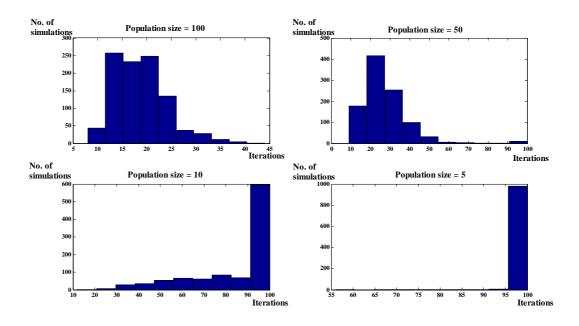

| Figure 6.11 | : The required number of iterations of a GA for population sizes of 5, 10, 50 and 100 in 1000 times Monte Carlo simulations in a four tunable elements impedance network                                                |

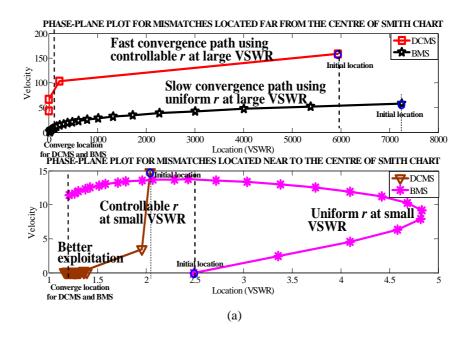

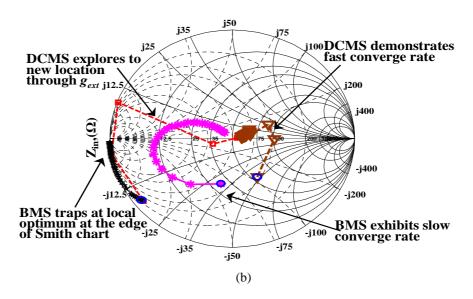

| Figure 6.12 | 2: Comparison of the proposed DCMS with BMS for different mismatches based on (a) velocities and current locations of the individuals in phase-plane plot, and (b) complex input impedances ( $Z_{in}$ ) in Smith chart |

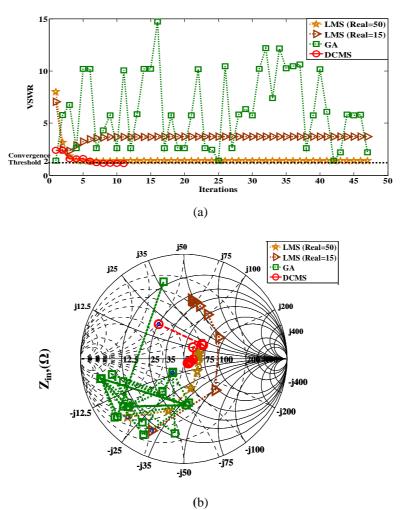

| Figure 6.13 | 8: Convergence of LMS, GA and DCMS based on (a) VSWR over number of iterations, and (b) complex input impedances ( $Z_{in}$ ) in a Smith chart                                                                          |

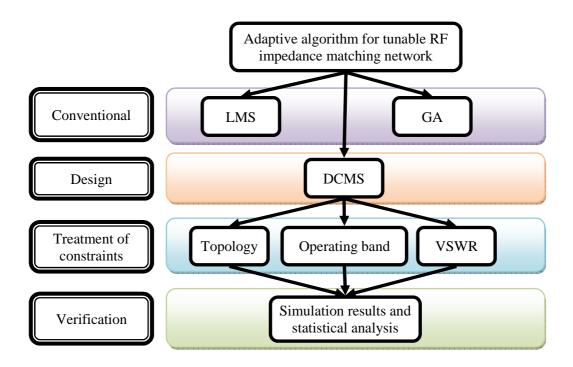

| Figure 6.14 | E: Summary of the areas and the challenges addressed in Chapter 6                                                                                                                                                       |

| Figure 7.1: | The areas and the challenges addressed in the thesis                                                                                                                                                                    |

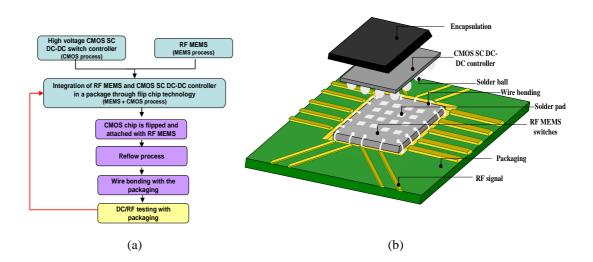

| Figure 7.2: | System integration between an RF MEMS switch and the CMOS SC DC-DC converter in (a) process flow and (b) package level integration through flip chip technology                                                         |

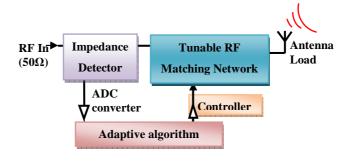

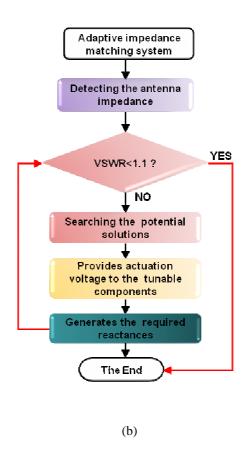

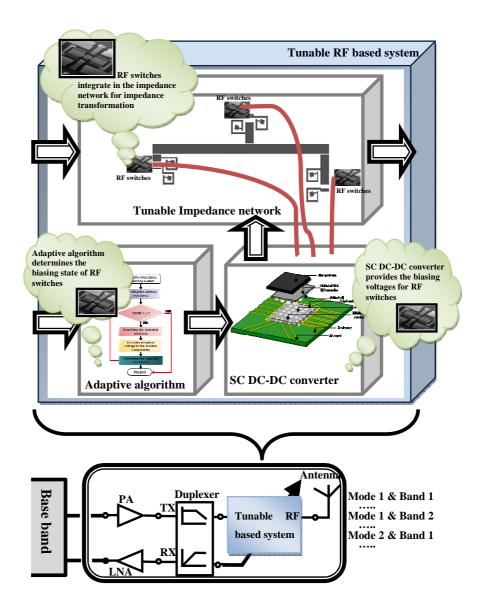

| Figure 7.3: | Integrating the adaptive algorithm to the tunable impedance matching system in (a) block diagram, and (b) flow chart                                                                                                    |

| Figure 7.4: | Contributions of the proposed functional blocks towards the realisation of tunable RF based mobile telecommunication systems, aimed at the realisation of high performance mobile telecommunication systems             |

#### **List of Tables**

| Table 2.1: T  | ypes of Capacitors                                                                                                                                                                                                                    | 24 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|               | ummary of the design parameters and merits of performance on two-phase SC                                                                                                                                                             |    |

| Ι             | OC-DC converter                                                                                                                                                                                                                       | 73 |

| Table 4.1: In | npedance transformation                                                                                                                                                                                                               | 87 |

| Table 4.2: Co | omparison of operating performances in RF switches technologies                                                                                                                                                                       | 95 |

| t             | alculation of the required susceptances for the stubs and equivalent capacitance of match the non $50\Omega$ impedance loads to $50\Omega$ with a $\Delta\lambda=36^0$ at different operating standards                               |    |

| C             | the average VSWR and CPU time for DCMS, LMS and GA in 1000 runs based on $LC$ - and $Pi$ - network for mismatches involving both real and imaginary part $Z_{Load}$ (15+i15.6) and solely the imaginary part of $Z_{Load}$ (50+i15.6) | of |

#### **List of Acronyms and Abbreviations**

AMS = AustriaMicroSystem

B = Susceptance

BMS = Basic mass spring

BST = Barium Strontium Titanate

C = Charge storage capacitor

$C_L$  = Output load capacitor

CMOS = Complementary metal-oxide-semiconductor

$C_P$  = Parasitic capacitance

CPM = POLY1-MET1-MET2-MET3

CPOLY = POLY1-POLY2

$C_{OX}$  = Gate oxide transistor

$C_{OUT}$  = Output capacitor

$C_{Store}$  = Charge storage capacitor

CV = Capacitance-voltage

CWPM = DNTUB-MET1-MET2-MET3

d(n) = Desired impedance

DC = Direct current

DCMS = Derivative-corrective mass spring

$D_{i,t+1}^{N}$  = Displacement of the spring

e(n) = Error signal

EMI = Electromagnetic interference

f = Clock frequency  $f_d$  = Design frequency

FET = Field-effect transistor

FOM = Overall antenna figure of merit

G = Antenna gain

GA = Genetic algorithm

GaAs = Gallium Arsenide

$g_{ext}$  = External random force

$G_L$  = Conductance

GPS = Global Positioning System

GSM = Global System for Mobile Communications

HV = High voltage

$egin{array}{lll} IC & = & & & & & & \\ I_D & = & & & & & \\ DC \ drain \ current \\ I_L & = & & & & \\ Output \ current \end{array}$

k = Stiffness of the spring

$K_{ox}$  = Relative permittivity of silicon dioxide

L = Length of the transistor LDO = Low-Dropout regulator

LV = Low voltage

MEMS = Miro-electro-mechannical-systems

MOS = Metal-oxide-semiconductor

MS = Mass spring

N = Number of stages

$N_A$  = Doping concentration

nMOS = N type metal-oxide-semiconductor

NPN = A bipolar transistor with a layer of P-doped between two N-doped

layers

PNP = A bipolar transistor with a layer of N-doped between two P-doped

layers

pMOS = P-type metal-oxide-semiconductor

q = Charge of an electron

Q-factor = Quality factor

RF = Radio frequency

SC = Switched- capacitor

SEM = Scanning electron microscope

SiC = Silicon Carbide

SMA = surface-mount assembly

SOI = Silicon-on-insulator SOS = Silicon-on-sapphire

SP = Series-parallel S/H = Sample and hold

T = Antenna noise temperature

$V_{B\ S}$  = Bulk to substrate voltage

VCLK1 = Voltage at clock 1 VCLK2 = Voltage at clock 2

$V_{DB\_MAX}$  = Maximum technology allowable drain to bulk voltage

VDD = Power supply

VDS = Drain to source voltage

$V_{DS\ MAX}$  = Maximum technology allowable drain to source voltage

$V_{GS\_eff}$  = Effective gate to source voltage

$V_{GS\ MAX}$  = Maximum technology allowable gate to source voltage

$V_{LS}$  = Voltage supply at the level shifter

VLSI = Very large scale or integration

$V_{i,t+1}^{N}$  = Next step velocity

$V_{out}$  = Output voltage

$V_{SB\_MAX}$  = Maximum technology allowable source to bulk voltage

VSWR = Voltage standing wave ratio

$V_{TH}$  = Threshold voltage  $V_{TH0}$  =  $V_{TH}$  with zero  $V_{SB}$

W = Width of the transistor

w(n) = Weighting factor

$Y_0$  = Nominal system admittance

$Z_{in}$  = Input impedance  $Z_{Load}$  = Load impedance

$Z_0$  = Nominal system impedance

$\alpha$  = Alpha  $\beta$  = Beta

$\varepsilon_{si}$  = Permittivity of silicon

$\varepsilon_{ox}$  = Oxide permittivity

$\Delta\lambda$  = Electrical distance between the RF switches

$g_m$  = Transconductance  $\lambda/4$  = Quarter wavelength

$\eta$  = Efficiency

r = Vicious damping coefficient  $r_{ds}$  = On-resistance in the transistor

$\Gamma$  = Reflection coefficient

$t_{ox}$  = Gate oxide thickness

$2\phi_F$  = Surface potential

$\mu_n$  = Mobility of electrons near the silicon surface

$\gamma$  = Body effect parameter

## Chapter 1: Introduction

#### 1.1 Motivation for the Tunable RF based Mobile Telecommunication Systems

Radio frequency (RF) circuits with tunable and adaptable functions propose a wide range of possibilities and attract significant interest especially in the field of mobile telecommunication systems. Tunable and adaptable RF based mobile telecommunication systems not only enhance their functionality and performance but also reduce the circuit size and cost. In general, RF front-end circuits can be designed to adapt to different types of operating conditions, such as multi frequency bands, variable transmit power levels, antennas in mismatch conditions and a fluctuating operating environment, which are discussed as follows.

#### 1.1.1 Multi Frequency Bands

Over the past 10 years, the mobile industry has evolved at a rapid pace, which increases both the requirements and the capabilities of the RF front-end in order to support a multi frequencies wireless connection. Wireless communication has expanded from a single mode, triple-band 2G system in the year 2000, to a triple-mode, 9-band high speed data capable system by the year 2010 [1]. The trend continues with the rapid deployment of 4G LTE

systems with new modes and operating bands. The operation of multi-mode and multi-band is usually supported by multiple stacked transceiver units [2], as shown in Figure 1.1. Each of units is optimised for a single frequency band. Employment of multiple transceiver units is costly due to component duplication and large components count, which are undesirable for mobile applications. For the front-end to be able to support the continuing evolution, tunable RF technology is one of the promising solutions [1, 2]. Figure 1.2 shows that the tunable RF system reconfigures for multi-mode standards in a single transceiver unit rather than duplicating mode-specific transceiver units for each new standard. In tunable RF system, RF main components such as filters or duplexers, power amplifiers and antenna impedance matching network have to be reconfigured to cater for multi-mode standard operating requirements [3]. For instance, tunability in filter provides spectral diversity and increases efficiency [4]; Tunability in duplexer improves adjustable isolation [5]; Tunability in power amplifiers provides variable transmit power levels for multi frequency operations [6]; Tunability in impedance matching network provides required susceptance for antenna to compensate for changes such as frequency and the detuning effects that occur due to the user's head and hand. As a result, the whole tunable RF system increases the reuse of components and lower material costs, resulting in space saving and cost efficiency.

Figure 1.1: Multiple transceiver units employed for multi-mode and multi-band operations

Figure 1.2: Tunable RF based system reduces the size of multi-mode and multi-band transceiver

#### 1.1.2 Variable Transmit Power Level

On the other hand, tunable RF technology also improves the power efficiency in RF front-ends. Transmit power levels in mobile devices depend on the distance to the communicating base stations. By adjusting the biasing voltage or current [7, 8] or load impedance [6, 9, 10] of the power amplifier at the RF front-ends, according to the optimum operating power level, overall power efficiency can be considerably improved.

#### 1.1.3 Antenna in Mismatch Conditions

Tunability for RF front-end helps in relaxing antenna design process. Antennas used in mobile devices are preferable small in size. However, most of the small size antennas are narrow bandwidth which is easily detuned by a slight handling error or a fluctuating operating environment. A detuned antenna will have an operating frequency that is shifted from its design frequency. This causes a high voltage standing wave ratio (VSWR) and a large power reflection. Some of the antennas for mobile devices are developed with a maximum VSWR of 3.5 which have an equivalent loss of 1.6 dB or 30 percent of the reflected power at the antenna [11]. Tunable RF circuits allow a considerable extension of the operational bandwidth of mobile device antennas [12, 13]. With tunable RF circuitries, the operational frequency [14-16] and radiation pattern [17] of an antenna can even be reconfigured. These significantly relax the tight constraints in designing the antennas.

#### 1.1.4 Fluctuating Operating Environment

Adaptability in RF front-end improves the link quality by maintaining low VSWR in operating environment through spontaneously tuning the impedance to counteract the sudden impedance change in a user fluctuating operating environment. This situation mostly occurs in the miniaturised antenna of a mobile terminal [18]. The impedance of miniaturised antennas tends to shift with simple human ergonomics in operating conditions [19, 20].

Previous researchers have analysed the performance of mobile antennas influenced by a user's head, hand and shoulder [21-25]. For example, how the phone is held by the hand can have an impact on antenna performance, as shown in Figure 1.3 [24]. Similarly, how the phone is stored (in a pocket or briefcase, for example) can also negatively impact the matching of the antenna impedance. Due to the fact that every model of a device is different, interference from the user's hand and head is undefined a priori. This creates a significant problem to mobile users such as phone call drop, bad link quality and fast drain off of battery power.

Figure 1.3: Effect of human hand (in data mode position) to the antenna gain patterns at 881.5MHz frequency [24]

For this reason, adaptability in the RF circuit is needed in order to improve the link quality by reducing the user's impact on antenna in mobile devices, as shown in Figure 1.4. The adaptive RF circuit corrects the impedance mismatch and preserves the maximum radiated power [7, 26-29]. By reducing the reflected power, the battery life of mobile devices is extended and the communication performance of mobile device is enhanced.

Figure 1.4: Adaptability in an RF circuit corrects the antenna impedance mismatch that is caused by the effect of close proximity with a human hand

#### 1.2 Research Investigation

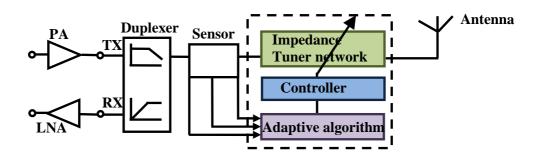

Introducing tunability or adaptability to the RF front-end provides great benefits but carries also losses and complexity by having additional functional blocks. Thus, research attentions are required to optimise these functional blocks in order to minimise the additional losses. Several key areas require research attentions such as RF switches design, controller, processor, impedance network designs and detector. Specifically, this thesis focuses on control circuitries, impedance network designs and adaptive algorithms for RF switches, aiming at the realisation of high performance mobile telecommunication systems. The study is divided into three distinct topics: (a) high voltage switch controller based on DC-DC converters for the RF switches actuation, (b) impedance network designs for impedance transformation of the RF switches, and (c) adaptive algorithms to determine the required impedance state at the RF switches for compensating the impedance variation of an antenna, as depicted in Figure 1.5.

Figure 1.5: Research areas (in the dashed block) covered in this thesis

## 1.2.1 High Voltage Switch Controller based on DC-DC Converters for RF Switch Actuation

In the first stage, high voltage (HV) switch controller for RF switches actuation will be explored. Most of the RF switches, in particular RF Micro-Electro-Mechanical-Systems (MEMS) devices, require biasing voltages which are significantly higher than the supply voltage. Thus, a DC-DC converter will be developed as an HV switch controller for biasing the RF switches. The DC-DC converter has to meet several specifications such as high output voltage, small size, low power consumption and linearity.

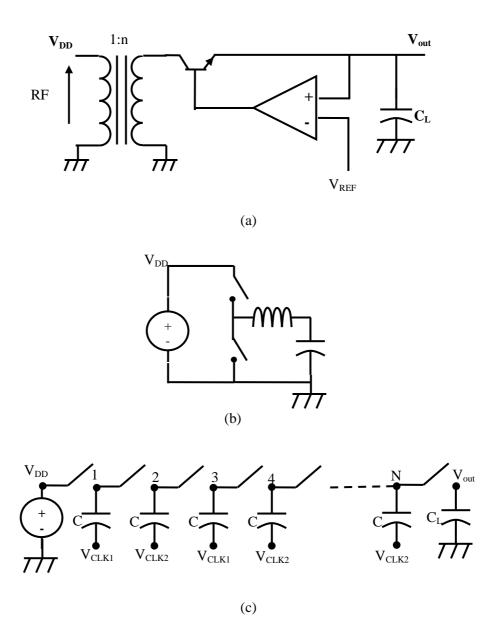

In general, three topologies can be implemented for the DC-DC converter. They are linear regulators, inductive based converters and switched-capacitor (SC) DC-DC converters, as shown in Figure 1.6 (a), (b) and (c) respectively.

Linear regulators or low-dropout regulators (LDO) are a mature technology but they are not preferable in scenarios where the dropout voltage between the input and output is very large. This will dramatically reduce the efficiency of the LDO [30].

The SC DC-DC converters have several advantageous properties, which include a simple control method and a reduced physical volume [31-34]. They also have less electromagnetic interference (EMI), low cost and high power density for the design. The SC converter output voltage is determined by the converter topology and has good no-load voltage regulation [35]. This is ideally suited for battery-operated applications with power management, where the converter must operate at an almost zero load.

Inductive based switching converters provide high efficiency and flexible power conversions. However, the inductive based converters require either technologically intensive integrated inductors (i.e. non- production CMOS) or bulky off-chip inductors, and suffer from severe electromagnetic interference noise [30, 36]. Furthermore, the switching components (i.e. transistors) in the inductive based converters have to sustain the full voltage difference and the peak current of the converter. This high voltage rating requirement is difficult to fulfil by current state of the art CMOS technology. In contrast, for a linear SC DC-DC converter, the required rating of the transistors is relatively small. Furthermore, the SC DC-DC converter requires only capacitors and switches. Thus, these make the SC DC-DC converter feasible for integration. Comparative analyses in [30, 37] conclude that the SC DC-DC converter has strong advantages with respect to both switch utilisation and high

energy densities of capacitors versus inductors. These show that the SC converter is evidently a promising candidate for this application.

Figure 1.6: Topologies of DC-DC converter (a) linear regulator (b) inductor based converter (c) switched capacitor converter