# Reconfiguration of Field Programmable Logic in Embedded Systems

Irwin O. Kennedy

Doctor of Philosophy

School of Informatics

University of Edinburgh

2005

#### **Abstract**

This thesis presents a set of techniques for evaluating and exploiting the programmability of a reconfigurable computing fabric in embedded systems. It concentrates specifically on the Field-Programmable Gate Array.

Reconfigurable logic promises a flexible computing fabric well suited to the low cost, low power, high performance and fast time to market now demanded of today's computing devices. Today, most reconfigurable systems are constructed using ad hoc techniques, making little use of previous designs and intellectual property (IP).

This thesis proposes a systematic approach to reconfigurable real-time system design. It exploits static and medium frequency reconfiguration by exploiting inter-task mutually exclusive resource usage. It exploits high frequency reconfiguration through data-folding specialisation techniques. A procedure for creating parameterised designs that approach minimal coverage of all possible system requirements is described. A runtime framework based upon a regularly occurring system-wide pause of execution is described.

A large case study of the design approach and runtime framework is presented and compared with the static equivalent. The case study system is a commercial Universal Mobile Telecommunications System (UMTS) physical layer processing engine. Equations describing the logic gate and memory requirements of the commercial ASIC design are extracted and used to estimate resource requirements of a low-medium frequency reconfigurable solution. A detailed investigation of very rapid reconfiguration is carried out on a large circuit block. Good logic and memory resource requirement reduction is shown to be possible.

A complementary FPGA reconfiguration architecture is presented. It provides the ability to tradeoff time and space according to the reconfiguration speed requirements of an application domain. A number of configuration compression schemes are investigated. In addition to an excellent compression ratio they are shown to be highly parallelisable and scalable, unlike previous approaches.

## **Acknowledgements**

I would like to thank my supervisor Murray Cole for his support and encouragement. Murray helped turn my work into the thesis presented. I am also very grateful to my previous supervisor Gordon Brebner for his guidance and constructive criticism and to Frank Mullany at Lucent Bell Labs for his excellent technical advice.

Others who were helpful to me include Michael Dales, André DeHon, John Gray, Tom Kean and Steve Trimberger.

This work was supported by an EPSRC CASE award in collaboration with Lucent Bell-Labs.

# Declaration

I declare that this thesis was composed by myself and that the work contained therein is my own, except where explicitly stated otherwise in the text. Some of the material in this thesis has already been published:

- G. Brebner and I. Kennedy, "Circlets: Circuitry over the Internet", Proceedings of 9th IEEE Symposium on Field-Programmable Custom Computing Machines, April, 2001.

- I. Kennedy and G. Brebner, "Novel Techniques to Enhance the use of Dynamic Reconfiguration in Fine Grain Field Programmable Logic", Proceedings 2nd U.K. ACM SIGDA Workshop on Electronic Design Automation, September, 2002.

- I. Kennedy, "Fast Reconfiguration Through Difference Compression", Proceedings of 11th IEEE Symposium on Field-Programmable Custom Computing Machines, pp. 265-266, April, 2003.

- I. Kennedy, "Exploiting Redundancy to Speedup Reconfiguration of an FPGA", Proceedings of 13th International Conference on Field Programmable Logic and Applications, Springer Lecture Notes in Computer Science 2778, pp. 262-271, September, 2003.

- I. Kennedy and F. Mullany, "Design of a Reconfigurable UMTS Channel Processing Engine", Proceedings IEEE Semiannual Vehicular Technology Conference, May, 2004.

- I. Kennedy, "A dynamically reconfigured UMTS multi-channel complex code matched filter", Proceedings IEEE International Conference on Field-Programmable Technology, December, 2005 (to appear).

(Irwin O. Kennedy)

# **Contents**

| 1 | Intr | duction                                  |

|---|------|------------------------------------------|

|   | 1.1  | Introduction                             |

|   | 1.2  | Just In Time Computing                   |

|   | 1.3  | Computing Fabrics                        |

|   |      | 1.3.1 Introduction                       |

|   |      | 1.3.2 Spatial versus Temporal            |

|   |      | 1.3.3 Computing Fabric Discussion        |

|   | 1.4  | Wireless Communications                  |

|   | 1.5  | Thesis Overview                          |

| 2 | Back | ground 10                                |

|   | 2.1  | Introduction                             |

|   | 2.2  | FPL                                      |

|   |      | 2.2.1 Overview                           |

|   |      | 2.2.2 Granularity                        |

|   |      | 2.2.3 FPGA                               |

|   | 2.3  | Runtime Reconfigurable FPL               |

|   |      | 2.3.1 Introduction                       |

|   |      | 2.3.2 Runtime Reconfigurable FPGA        |

|   |      | 2.3.3 DSP and Runtime Reconfigurable DSP |

|   |      | 2.3.4 Specialisation                     |

|   |      | 2.3.5 Hardware Software Co-design        |

|   | 2.4  | Platform based design                    |

|   |     | 2.4.1        | Introduction                                      | 17 |

|---|-----|--------------|---------------------------------------------------|----|

|   |     | 2.4.2        | What is a platform?                               | 17 |

|   |     | 2.4.3        | Flexibility                                       | 18 |

|   |     | 2.4.4        | Heterogeneity                                     | 19 |

|   |     | 2.4.5        | Scalability                                       | 20 |

|   |     | 2.4.6        | Productivity                                      | 20 |

|   |     | 2.4.7        | Abstraction                                       | 21 |

|   | 2.5 | Approa       | aches to harnessing a runtime reconfigurable FPGA | 22 |

|   |     | 2.5.1        | Introduction                                      | 22 |

|   |     | 2.5.2        | Multitasking Operating System                     | 23 |

|   |     | 2.5.3        | Temporal Pipelining                               | 24 |

|   |     | 2.5.4        | Data Folding                                      | 26 |

|   |     | 2.5.5        | Summary                                           | 27 |

|   | 2.6 | Resour       | ce Fragmentation and Interface Satisfaction       | 27 |

|   |     | 2.6.1        | Introduction                                      | 27 |

|   |     | 2.6.2        | Fragmentation                                     | 27 |

|   |     | 2.6.3        | Interface Satisfaction                            | 29 |

|   | 2.7 | Techni       | ques to Speedup reconfiguration                   | 31 |

|   |     | 2.7.1        | Introduction                                      | 31 |

|   |     | 2.7.2        | Summary                                           | 38 |

|   | 2.8 | Summa        | ary                                               | 39 |

| • | EDG | a w          |                                                   | 40 |

| 3 |     |              | nfiguration Architecture Design Space             | 40 |

|   | 3.1 |              | action to methods for FPGA fast reconfiguration   | 40 |

|   | 3.2 |              | Virtex Architecture                               | 42 |

|   | 3.3 |              | figuration Analysis                               | 43 |

|   |     | 3.3.1        | Introduction                                      | 43 |

|   |     | 3.3.2        | JBits API                                         | 44 |

|   |     | 3.3.3        | Circuits Used                                     | 44 |

|   | 3.4 | and the same | y Technique                                       | 45 |

|   |     | 3.4.1        | Overview                                          | 45 |

|   |     | 3.4.2        | Algorithm and Implementation                      | 45 |

|   |     | 3.4.3   | Results                                         | 48 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 3.4.4   | Summary                                         | 50 |

|   | 3.5 | Bit-Str | ream Redundancy Analysis                        | 50 |

|   |     | 3.5.1   | Overview                                        | 50 |

|   |     | 3.5.2   | Experiments                                     | 50 |

|   |     | 3.5.3   | Results                                         | 51 |

|   |     | 3.5.4   | Summary                                         | 53 |

|   | 3.6 | Chang   | es Compression                                  | 53 |

|   |     | 3.6.1   | Overview                                        | 53 |

|   |     | 3.6.2   | Targeted Compression Algorithms                 | 54 |

|   |     | 3.6.3   | Results                                         | 55 |

|   |     | 3.6.4   | Summary                                         | 56 |

|   | 3.7 | Virtex  | II and future platform FPGAs                    | 57 |

|   |     | 3.7.1   | Introduction                                    | 57 |

|   |     | 3.7.2   | Architectural Features                          | 57 |

|   |     | 3.7.3   | Off-chip Memory Bandwidth                       | 59 |

|   |     | 3.7.4   | Summary                                         | 61 |

|   | 3.8 | Summ    | ary                                             | 61 |

|   |     |         |                                                 |    |

| 4 | A D | 7.0     | ethodology for the Reconfigurable Platform FPGA | 62 |

|   | 4.1 | Introdu | action                                          | 62 |

|   | 4.2 | Applic  | ation Domain                                    | 63 |

|   |     | 4.2.1   | Introduction                                    | 63 |

|   |     | 4.2.2   | Static Application Domain                       | 63 |

|   |     | 4.2.3   | Model of computation                            | 65 |

|   |     | 4.2.4   | Summary                                         | 69 |

|   | 4.3 | Metho   | dology Overview                                 | 69 |

|   | 4.4 | Check   | point Framework                                 | 71 |

|   | 4.5 | Targeti | ng                                              | 74 |

|   |     | 4.5.1   | Introduction                                    | 74 |

|   |     | 4.5.2   | Reconfiguration Frequency                       | 74 |

|   |     | 4.5.3   | Reconfiguration Organisation                    | 75 |

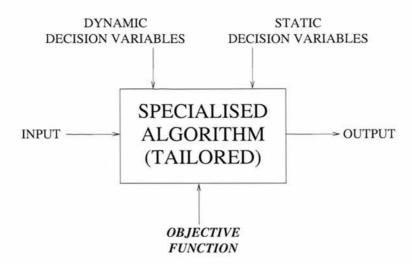

|   |      | 4.5.4   | Optimisation                                               | 76  |

|---|------|---------|------------------------------------------------------------|-----|

|   |      | 4.5.5   | Procedure                                                  | 78  |

|   | 4.6  | Discus  | ssion                                                      | 81  |

|   |      | 4.6.1   | Introduction                                               | 81  |

|   |      | 4.6.2   | Contributions                                              | 81  |

|   |      | 4.6.3   | Restricted Design Freedom                                  | 83  |

|   |      | 4.6.4   | Abstraction                                                | 84  |

|   | 4.7  | Summ    | ary                                                        | 85  |

| 5 | Case | Study   | : UMTS Physical Layer Processing                           | 87  |

|   | 5.1  | Introdu | action                                                     | 87  |

|   | 5.2  | UMTS    | SSOC Overview                                              | 87  |

|   | 5.3  | UMTS    | CE Outline                                                 | 89  |

|   | 5.4  | Metho   | dology Application                                         | 91  |

|   |      | 5.4.1   | Introduction                                               | 91  |

|   |      | 5.4.2   | Step 1: Capture system requirements                        | 93  |

|   |      | 5.4.3   | Step 2: Perform preliminary system design                  | 94  |

|   |      | 5.4.4   | Step 3: Extract decision variables                         | 96  |

|   |      | 5.4.5   | Step 4: Separate system into static products               | 97  |

|   |      | 5.4.6   | Step 5: Capture system constraints (inequalities)          | 98  |

|   |      | 5.4.7   | Step 6: Extract system cost function                       | 100 |

|   |      | 5.4.8   | Step 7: Minimise system cost function                      | 105 |

|   |      | 5.4.9   | Step 8: Direct intra-subsystem reconfiguration effort      | 109 |

|   |      | 5.4.10  | Algorithm Description                                      | 110 |

|   |      | 5.4.11  | Static Design                                              | 111 |

|   |      | 5.4.12  | Step 9: Advance implementation                             | 125 |

|   |      | 5.4.13  | Step 10: Generate checkpoint control unit                  | 125 |

|   | 5.5  | Xilinx  | Virtex Configuration architecture to support UMTSCE imple- |     |

|   |      | mentat  | ion using Checkpoint Framework                             | 125 |

|   |      | 5.5.1   | Overview                                                   | 125 |

|   |      | 5.5.2   | Requirements                                               | 126 |

|   |      | 553     | Change Memory Arrangements                                 | 127 |

|   |            | 5.5.4                                                                                     | Selected Memory Arrangement                   | 127                                                         |

|---|------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|

|   |            | 5.5.5                                                                                     | Decompression unit design                     | 128                                                         |

|   |            | 5.5.6                                                                                     | Implementation                                | 128                                                         |

|   | 5.6        | Assum                                                                                     | nptions                                       | 130                                                         |

|   | 5.7        | Result                                                                                    | s                                             | 131                                                         |

|   | 5.8        | Outcom                                                                                    | me                                            | 133                                                         |

| 6 | Con        | clusions                                                                                  | s                                             | 136                                                         |

|   | 6.1        | Summ                                                                                      | ary                                           | 136                                                         |

|   | 6.2        | Conclu                                                                                    | usions                                        | 137                                                         |

|   | 6.3        | Future                                                                                    | Work                                          | 138                                                         |

|   |            | 6.3.1                                                                                     | Overview                                      | 138                                                         |

|   |            | 6.3.2                                                                                     | Architectural Features to aid Reconfiguration | 139                                                         |

|   |            | 6.3.3                                                                                     | Off-chip Memory Feasibility Study             | 139                                                         |

|   |            | 6.3.4                                                                                     | Design with Reconfiguration                   | 143                                                         |

| A | Digi       | tal Com                                                                                   | nmunications                                  | 145                                                         |

|   | A.1        | Introdu                                                                                   | uction                                        | 145                                                         |

|   | A.2        |                                                                                           |                                               |                                                             |

|   |            | Digital                                                                                   | l Modulation                                  | 145                                                         |

|   | A.3        |                                                                                           | l Modulation                                  | 145<br>146                                                  |

|   | A.3<br>A.4 | Power                                                                                     |                                               |                                                             |

|   |            | Power<br>Conste                                                                           | Spectral Density                              | 146                                                         |

|   | A.4        | Power<br>Conste<br>Bandw                                                                  | Spectral Density                              | 146<br>147                                                  |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw                                                                  | Spectral Density                              | 146<br>147<br>149                                           |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula                                                       | Spectral Density                              | 146<br>147<br>149<br>150                                    |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula<br>A.6.1                                              | Spectral Density                              | 146<br>147<br>149<br>150<br>150                             |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula<br>A.6.1<br>A.6.2                                     | Spectral Density                              | 146<br>147<br>149<br>150<br>150                             |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula<br>A.6.1<br>A.6.2<br>A.6.3                            | Spectral Density                              | 146<br>147<br>149<br>150<br>150<br>151<br>152               |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula<br>A.6.1<br>A.6.2<br>A.6.3<br>A.6.4                   | Spectral Density                              | 146<br>147<br>149<br>150<br>150<br>151<br>152               |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula<br>A.6.1<br>A.6.2<br>A.6.3<br>A.6.4<br>A.6.5          | Spectral Density                              | 146<br>147<br>149<br>150<br>150<br>151<br>152<br>154<br>155 |

|   | A.4<br>A.5 | Power<br>Conste<br>Bandw<br>Cellula<br>A.6.1<br>A.6.2<br>A.6.3<br>A.6.4<br>A.6.5<br>A.6.6 | Spectral Density                              | 146<br>147<br>149<br>150<br>151<br>152<br>154<br>155<br>156 |

|   |         | A.6.10   | Correlation                                  | 158 |

|---|---------|----------|----------------------------------------------|-----|

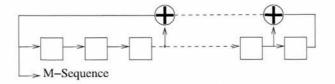

|   |         | A.6.11   | Code generation                              | 159 |

|   |         | A.6.12   | Gold Sequences                               | 160 |

|   |         | A.6.13   | Walsh Sequences                              | 160 |

|   |         | A.6.14   | Receiver                                     | 160 |

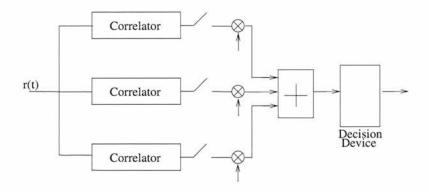

|   |         | A.6.15   | Single User RAKE                             | 161 |

|   |         | A.6.16   | Multi User Detection                         | 162 |

|   |         | A.6.17   | Joint Detection: Maximum Likelihood Sequence | 162 |

| n | TINE    | rc       |                                              | 164 |

| В | UM'     |          | CANAMO I : IA                                |     |

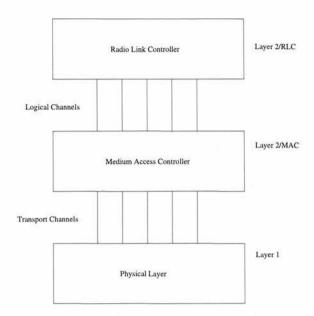

|   | B.1     |          | ew of UMTS physical Layer                    | 164 |

|   |         | B.1.1    | UMTS Introduction                            | 164 |

|   |         | B.1.2    | Air Interface Principles                     | 165 |

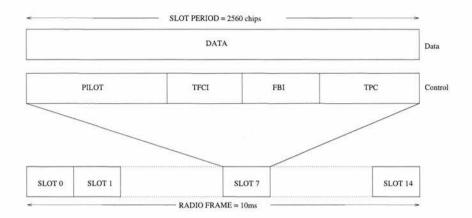

|   |         | B.1.3    | Uplink Physical Channels                     | 166 |

|   |         | B.1.4    | Downlink Physical Channels                   | 168 |

|   | B.2     | UMTS     | Partition Overview                           | 169 |

|   |         | B.2.1    | Preamble Detector                            | 169 |

|   |         | B.2.2    | Searcher                                     | 171 |

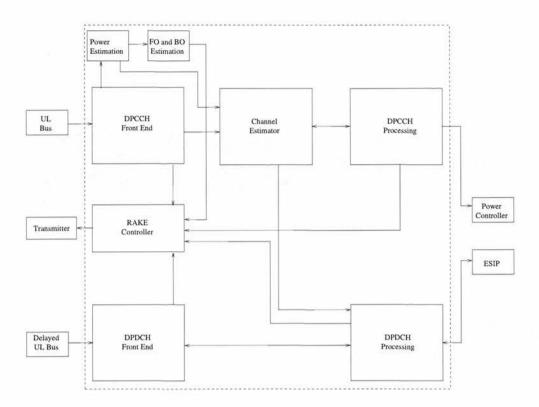

|   |         | B.2.3    | RAKE Receiver                                | 172 |

|   |         | B.2.4    | Power Controller                             | 174 |

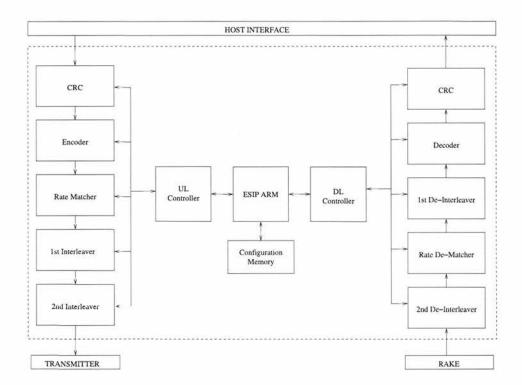

|   |         | B.2.5    | Transmitter                                  | 174 |

|   |         | B.2.6    | Extended Soft Information Processor (ESIP)   | 175 |

| ~ | Y 13 47 | DOOR D   |                                              | 150 |

| C |         |          | arameterisation                              | 178 |

|   | C.1     |          | eterisation                                  | 178 |

|   |         | C.1.1    | Introduction                                 | 178 |

|   |         | C.1.2    | Logic                                        | 179 |

|   |         | C.1.3    | Memory                                       | 186 |

| D | Revi    | ew of th | ne multiple-context FPGA                     | 195 |

|   | D.1     |          | ction                                        | 195 |

|   | D.2     |          | of operations                                | 195 |

|   | D.3     |          | e                                            | 196 |

|   |         |          |                                              |     |

| Bibliography |                                        | 201 |

|--------------|----------------------------------------|-----|

| D.3.5        | Power Consumption                      | 199 |

| D.3.4        | Finite State Machine                   | 198 |

| D.3.3        | Parasitic Effects of Multiple Contexts | 197 |

| D.3.2        | Re-timing                              | 196 |

| D.3.1        | Latency                                | 196 |

# **List of Figures**

| 1.1 | Just In Time (JIT) Tradeoff Space                                         | 2  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Computational Space Occupied by Reconfigurable Logic                      | 4  |

| 1.3 | Temporal versus Spatial Programming Space                                 | 5  |

| 2.1 | Generalised FPGA Architecture                                             | 12 |

| 2.2 | Xilinx Virtex CLB                                                         | 13 |

| 2.3 | Algorithm Implemented on a Reconfigurable FPL Fabric                      | 15 |

| 2.4 | Xilinx Virtex II Pro Block Diagram                                        | 19 |

| 3.1 | Xilinx Virtex Architecture                                                | 43 |

| 3.2 | The overlay technique configuration sequence                              | 46 |

| 3.3 | A netlist being trimmed                                                   | 48 |

| 3.4 | The advance and residual changes expressed as a percentage of the         |    |

|     | total number of changes required to configure the area of fabric occupied | 49 |

| 3.5 | The number of changed bits as a percentage of the actual number of        |    |

|     | bits required to configure the area of fabric occupied                    | 52 |

| 3.6 | The number of changed bits broken down by resource type and ex-           |    |

|     | pressed as a percentage of the total number of change bits required to    |    |

|     | configure the area of fabric occupied                                     | 52 |

| 3.7 | The compressed changes dataset size expressed as a percentage of the      |    |

|     | number of bits required to configure the area of fabric occupied          | 56 |

| 4.1 | Traditional Implementation versus Reconfigurable Implementation Ex-       |    |

|     | ploiting Inter-Subsystem Resource Sharing                                 | 72 |

|     |                                                                           |    |

| 4.2  | Illustration of timing relationships between checkpoints, computation |     |

|------|-----------------------------------------------------------------------|-----|

|      | and reconfiguration                                                   | 73  |

| 4.3  | Configuration instance specification process                          | 76  |

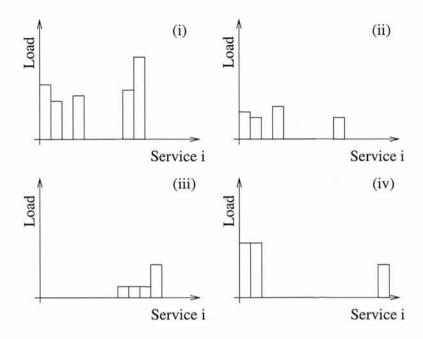

| 4.4  | Four examples of load distribution across the different service types | 77  |

| 4.5  | Implementation of a Reconfigurable Algorithm Enhanced by Knowl-       |     |

|      | edge of the Global Objective Function                                 | 82  |

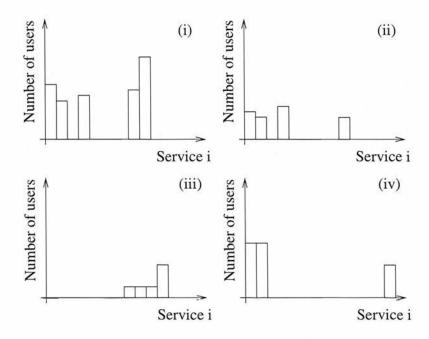

| 5.1  | Four examples of user distribution across the different service types | 102 |

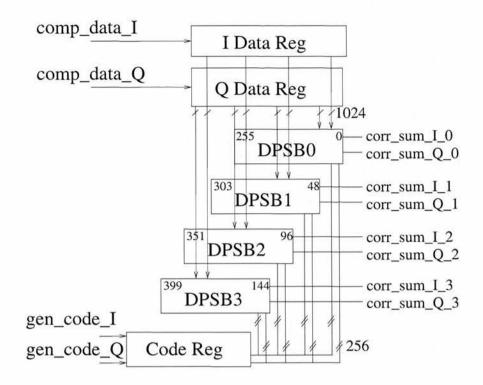

| 5.2  | CCMF Top Level Structure                                              | 111 |

| 5.3  | CCMF Dot Product Sub Block Cell                                       | 112 |

| 5.4  | CCMF Cell with multipliers replaced with negation units and multi-    |     |

|      | plexers                                                               | 113 |

| 5.5  | The VHDL interface description for the generator unit                 | 114 |

| 5.6  | Generator Unit Black Box                                              | 114 |

| 5.7  | CF Unit Black Box                                                     | 114 |

| 5.8  | DF Unit Black Box                                                     | 116 |

| 5.9  | Cell Reconfiguration Sequence                                         | 118 |

| 5.10 | Data-folded Implementation                                            | 119 |

| 5.11 | Structure of G4 unit                                                  | 120 |

| 5.12 | G4 unit CE timing diagram                                             | 121 |

| 5.13 | Configuration changes on-chip RAM arrangements                        | 126 |

| 5.14 | Block diagram of circuitry for decompression                          | 128 |

| A.1  | Constellation for QPSK modulation                                     | 147 |

| A.2  | Generic modulation architecture for digital signals                   | 149 |

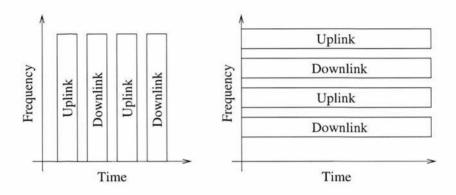

| A.3  | TDD and FDD techniques for separating the signals of transmit and     |     |

|      | receive                                                               | 150 |

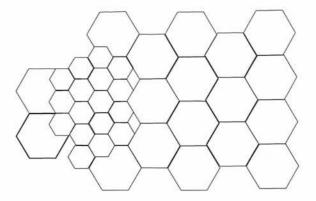

| A.4  | Hierarchical Cellular Plan                                            | 151 |

| A.5  | Diagram illustrating Time Division Multiple Access (TDMA)             | 152 |

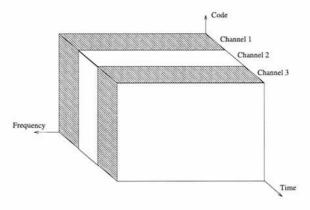

| A.6  | Diagram illustrating Frequency Division Multiple Access (FDMA)        | 152 |

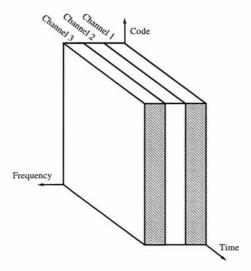

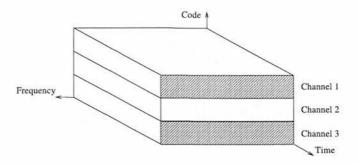

| A.7  | Diagram illustrating Code Division Multiple Access (CDMA)             | 153 |

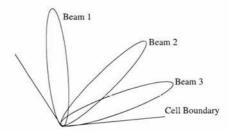

| A.8  | Diagram illustrating Space Division Multiple Access (SDMA)            | 153 |

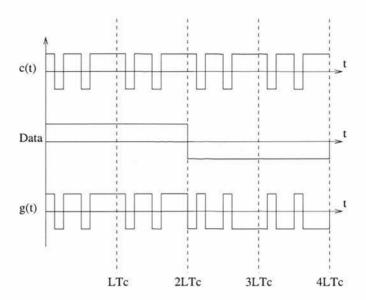

| A.9  | Direct Sequence Spread Spectrum System signals in time domain           | 15/ |

|------|-------------------------------------------------------------------------|-----|

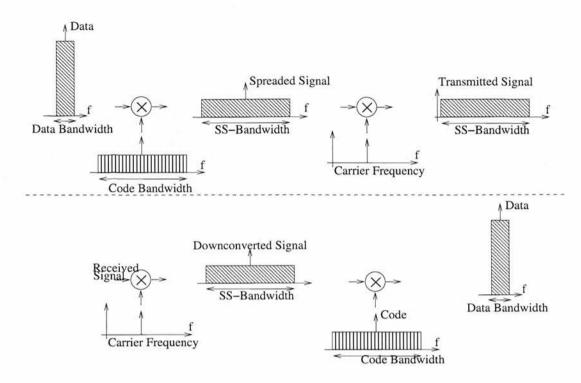

| A.10 | Direct Sequence Spread Spectrum System signals in frequency domain      | 158 |

| A.11 | Drawing of a code sequence generator                                    | 159 |

| A.12 | Maximum ratio combining RAKE receiver with 3 fingers                    | 162 |

| B.1  | Physical Layer Relation to Upper Layers                                 | 165 |

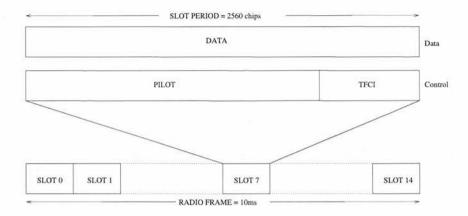

| B.2  | Radio Frame Structure UL DPDCH and UL DPCCH                             | 167 |

| B.3  | Radio Frame Structure RACH message                                      | 168 |

| B.4  | UMTSSOC: Preamble Detector Partition                                    | 170 |

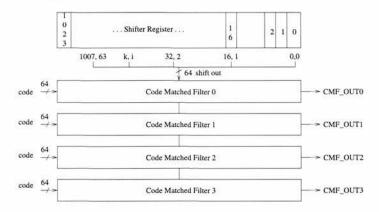

| B.5  | UMTSSOC: Preamble Detector CMF Block                                    | 170 |

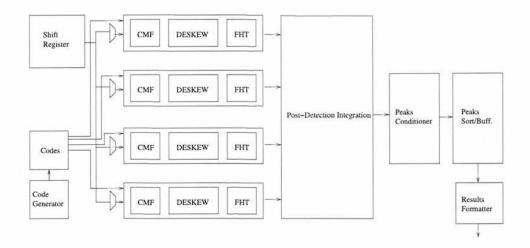

| B.6  | UMTSSOC: Searcher Partition                                             | 171 |

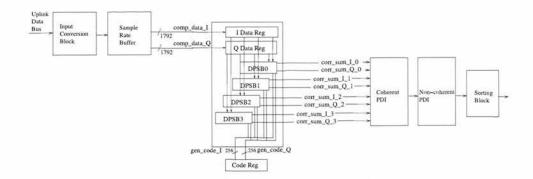

| B.7  | UMTSSOC: RAKE Partition                                                 | 173 |

| B.8  | UMTSSOC: ESIP Partition                                                 | 176 |

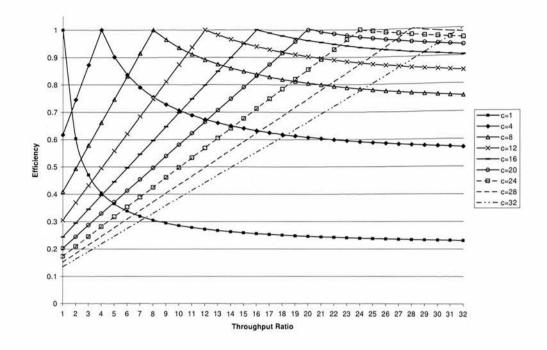

| D.1  | DPGA utilisation efficiency versus throughput ratio for various context |     |

|      | counts                                                                  | 199 |

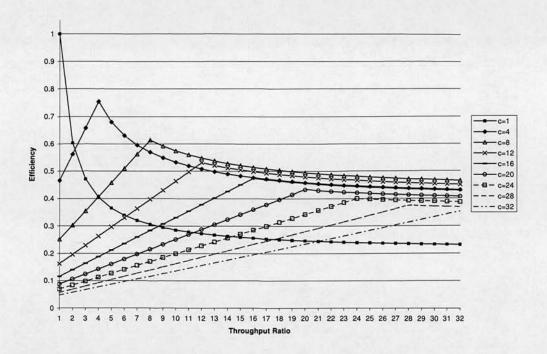

| D.2  | DPGA utilisation efficiency versus throughput ratio for various context |     |

|      | counts. Efficiency is adjusted for the worst case speed penalty caused  |     |

|      | by the addition of multiple context functionality.                      | 200 |

# **List of Tables**

| 3.1  | Selected data for the largest device in each Virtex series generation  | 57  |

|------|------------------------------------------------------------------------|-----|

| 3.2  | Percentage of configuration bitstream for logic-slice fabric           | 59  |

| 3.3  | User I/O pins for the largest device in each Virtex generation         | 60  |

| 4.1  | Suitability of selected reconfigurable FPGA models to the characteris- |     |

|      | tics of the static FPGA's application domains                          | 65  |

| 4.2  | Three strand approach to exploiting reconfiguration                    | 69  |

| 5.1  | UMTSCE ASIC Resource Requirements                                      | 89  |

| 5.2  | Connection parameters value ranges                                     | 96  |

| 5.3  | Static system variables                                                | 96  |

| 5.4  | List of Basestation Product Configurations                             | 98  |

| 5.5  | List of Dynamic Instances for Suburban Product Configuration           | 101 |

| 5.6  | List of Dynamic Instances for Rural Product Configuration              | 101 |

| 5.7  | Cost function parameters and their calculation dependencies            | 103 |

| 5.8  | Cost functions for logic blocks                                        | 104 |

| 5.9  | Cost functions for memory blocks                                       | 105 |

| 5.10 | LUT requirement breakdown for the CF cell                              | 114 |

| 5.11 | Generator Unit Costs: Gn is 1 Generator with 12n cells                 | 122 |

| 5.12 | Construction of CCMF from Gn units                                     | 122 |

| 5.13 | Results of reconfigurable CCMF implementation                          | 123 |

| 5.14 | Memory Requirements (in Bits) Normalised with respect to the ASIC      |     |

|      | Design Total                                                           | 133 |

| 5.15 | Logic Requirements (in Gates) Normalised with respect to the ASIC   |     |

|------|---------------------------------------------------------------------|-----|

|      | Design Total                                                        | 134 |

| 5.16 | Percentage Logic and Memory Savings Over the ASIC Design            | 135 |

| 6.1  | Largest UMTSCE memory block throughputs                             | 142 |

| A.1  | Theoretical Bandwidth Efficiency of Several Modulation Techniques . | 150 |

| C.1  | List of Parameters for UMTSCE Parameterised Design                  | 179 |

| C.2  | Percentage of UMTSCE logic described parametrically                 | 181 |

| C.3  | CE Memories Parameterised                                           | 187 |

## Glossary

Chip A chip is a binary digit at the physical link layer.

The redundancy introduced by Forward Error Correction, spreading etc.

results in one application layer bit being represented by many chips.

Finger A RAKE receiver exploits multiple versions of the same transmit stream

by descrambling and despreading several delay paths. The different paths

are then combined to maximise the received energy. A finger is one

correlator unit allocated to a particular delay path which is to be detected

and demodulated.

Handover or Hard Handover refers to the process of switching all

UMTS physical links from one NodeB to another NodeB.

Node B UMTS cellular basestation.

RAKE is the name of a receiver architecture for spread spectrum

communication systems.

Soft Handover In Soft Handover, the transfer of radio links is performed

gradually ensuring the UE always has at least one active radio link at all

times.

Softer Handover Softer Handover is a special form of soft handover in which

radio links are transferred within the same NodeB, for example, between

two sectors on the same base station.

## **Acronyms**

3GPP 3rd Generation Partnership Project

3G 3rd Generation Cellular Mobile Telecommunications

ACM Association for Computing Machinery

ADC Analogue to Digital Converter

ALAP As Late As Possible (Scheduling Algorithm)

ALU Arithmetic Logic Unit

AP Access Point

API Application Programming Interface

APS Application Profile Set

ASAP As Soon As Possible (Scheduling Algorithm)

ASIC Application Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BLER Block Error Rate

BPSK Binary Phase Shift Keying

BRAM Block Random Access Memory

BW Bandwidth

CAM Content Addressable Memory

CCMF Complex Code Matched Filter

CCPCH Common Control Physical Channel

CDFG Control Data Flow Graph

CDMA Code Division Multiple Access

CFG Control Flow Graph

CF Code Folded

CFC Code Folded Control

CLB Configurable Logic Block

CMF Code Matched Filter

CPCH Common Packet Channel

CPICH Common Pilot Channel

CPU Central Processing Unit

CRC Cyclic Redundancy Check

DAC Digital to Analogue Converter

DC Direct Current

DCH Dedicated Channel

DCT Discrete Cosine Transform

DDR Double Data Rate

DF Data Folded

DFC Data Folded Control

DIMM Dual In-line Memory Module

DLL Delay Locked Loop

DPCCH Dedicated Physical Control Channel

DPCH Downlink Dedicated Physical Channel

DPDCH Dedicated Physical Data Channel

DPGA Dynamically Programmable Gate Array

DPSB Dot Product Sub Block

DRAM Dynamic Random Access Memory

DS-CDMA Direct Sequence Code Division Multiple Access

DSP Digital Signal Processor

DSSS Direct Sequence Spread Spectrum

EMI Electro-Magnetic Interference

ESIP Extended Soft Information Processor

ETSI European Telecommunications Standards Institute

FACH Forward Access Channel

FBI Feed Back Information

FDMA Frequency Division Multiple Access

Frequency Division Duplex

FEC Forward Error Correction

FF Flip/Flop

FDD

FFT Fast Fourier Transform

FHT Fast Hadamard Transform

FIR Finite Impulse Response

FPFA Field Programmable Function Array

FPGA Field Programmable Gate Array

FPL Field Programmable Logic

FSM Finite State Machine

GPP General Purpose Processor

GSM Global System for Mobile Communications

HC Hardware Configuration

HCS Hardware Configuration Set

HDL Hardware Description Language

HSDPA High Speed Downlink Packet Access

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IIR Infinite Impulse Response Filter

IOB Input Output Buffer

IP Intellectual Property

I/Q In phase/Quadrature

JEDEC Joint Electron Device Engineering Council

JIT Just In Time

LLR Log Likelihood Ratio

LRU Least Recently Used

LUT Look Up Table

LZ Lempel Ziv

MAC Medium Access Controller

MAI Multiple Access Interference

MEMS Micro Electro-Mechanical Systems

MIMD Multiple Instruction Multiple Data

MMSE Minimum Mean Square Error

MPEG Moving Picture Expert Group

MUX Multiple xor

NRE Non Recurring Engineering

OFDM Orthogonal Frequency Division Modulation

OS Operating System

OSI Open Systems Interconnection Reference Model

OVSF Orthogonal Variable Spreading Factor

PAL Programmable Array Logic

PCH Physical Channel

PCPCH Physical Common Packet Channel

PD Preamble Detector

PDI Post Detection Integration

PDSCH Physical Downlink Shared Channel

PIP Programmable Interconnect Point

PLA Programmable Logic Array

PLD Programmable Logic Device

PRACH Physical Random Access Channel

QPSK Quadrature Phase Shift Keying

RACH Random Access Channel

RTL Register Transfer Language

SCH Shared Channel

SDMA Space Division Multiple Access

SDR Software Defined Radio

SDRAM Synchronous Dynamic Random Access Memory

SIA Semiconductor Industry Association

SIMD Single Instruction Multiple Data

SLU Swappable Logic Unit

SNR Signal to Noise Ratio

SOC System On Chip

SRB Sample Rate Buffer

SRL Shift Register LUT

TDD Time Division Duplex

TDMA Time Division Multiple Access

TFCI Transport Format Combination Indicator

TPC Transmit Power Control

TTI Transmission Time Interval

TX Transmit

UART Universal Asynchronous Receiver-Transmitter

UE User Equipment

UL Uplink

UMTS Universal Mobile Telecommunications System

UMTSCE UMTS Channel Element

UMTSSOC UMTS System On Chip

VHDL Very High Speed Integrated Circuit HDL

WCDMA Wideband Code Division Multiple Access

# Chapter 1

## Introduction

#### 1.1 Introduction

According to Semiconductor Industry Association (SIA) projections[144], the number of transistors per die and the local clock frequencies for high-performance designs will continue to grow exponentially over the next decade. By the year 2014, the SIA predicts that 20 billion transistors will be available per die. As a consequence of such massive transistor integration and the advent of Micro-Electro-Mechanical Systems (MEMS), new application spaces are envisaged as well as the growth of existing ones. For example it is predicted that smart devices woven into our environment will create a world of "ambient intelligence"[13]. An existing application space predicted to benefit from strong growth is wireless communications and the software defined radio (SDR)[140]. The ideal SDR consists of a small analogue stage with all other processing performed in software, although, it may be more appropriate to think of the implementation technology as soft-programmable, rather than a microprocessor. The flexibility enables standards changes to be implemented via a download over the air interface and the support of multiple standards by a single device.

Reconfigurable computing is a term which has emerged to describe a class of computing fabrics which may be reprogrammed electronically post-manufacture. As will be described in Section 1.3 they offer an alternative computing fabric to the system designer, combining the flexibility of the microprocessor and the spatial circuitry im-

plementation of the ASIC. The design of reconfigurable computing systems is the focus of this thesis, with particular attention given to platform Field-Programmable Gate Arrays (FPGAs). A large case study from the domain of wireless communications is used to demonstrate the design techniques proposed.

The introduction and background on reconfigurable computing is presented in Chapter 2. Here we introduce related areas necessary for the understanding of the thesis. The specific area of reconfigurable computing of interest is called Just-In-Time computing (JIT) and is introduced in Section 1.2. Section 1.3 describes the difference between spatial and temporal computing and introduces the main computational fabrics at a system architect's disposal. Section 1.4 provides a short introductory motivation for the choice of wireless communications as the major case study in the thesis. Finally, an overview of each chapter in the thesis is presented in Section 1.5.

#### 1.2 Just In Time Computing

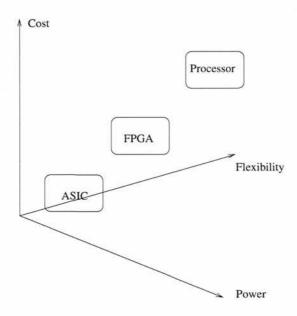

Figure 1.1: Just In Time (JIT) Tradeoff Space

Just In Time Computing refers to the design tradeoff space of embedded systems as described by Rabaey in [131]. As illustrated in Figure 1.1, cost, power and flexibility

are the three axes in the tradeoff space. Notably, performance is missing from the design space. This is a key difference between Just-In-Time computing and traditional, transformational general purpose computing. Rather than attempting to maximise performance, the functionality is known and simply becomes a design constraint. Embedded systems enjoy a well specified set of tasks at design time. This contrasts sharply with general purpose computing where the set of tasks to be performed is not known at design time. The term "Just-In-Time" captures an embedded system's requirement to simply match the system's performance criteria, rather than attempt to perform it as fast as possible.

The tradeoff between the cost, power and flexibility is obviously dependent on the system being designed. For example, power consumption is critical for battery powered devices, but is often only a concern from a heat dissipation perspective in mains powered devices such as television set-top boxes.

The cost tradeoff axis is the complete cost of the solution. For example, an ASIC's cost must include all Non-Recurring Engineering (NRE) charges, such as the mask set used in fabrication, functional verification and physical verification. The microprocessor and FPGA have no NRE costs when bought as a complete, packaged device, however they incur some NRE costs if they are incorporated into an ASIC System On Chip. For example, masks sets must be manufactured to describe the ASIC logic and the intellectual property of the FPGA fabric or processor on the same chip. Some of the verification cost may be reduced, since the intellectual property will be used across many designs, and hence may be partially amortised.

Flexibility is the third tradeoff axis in Figure 1.1. It refers to the level of programmability of the system post-manufacture. With time to market critical for many systems, the ability to apply bug fixes and incorporate changes to evolving standards late in the design process is desirable. The FPGA and the microprocessor are well suited to such requirements. An ASIC designed and optimised to a specific task has very poor flexibility since its functionality is fixed at manufacture. A two stage implementation strategy is adopted for some standards driven products in which an initial solution is rapidly produced using flexible fabrics to establish a market position, and then once the standard has stabilised, cost is reduced by creating an ASIC. Another ex-

ample is a system built for a family of products which may require a level of flexibility for integration purposes. Flexibility is discussed further in Section 2.4.

#### 1.3 Computing Fabrics

#### 1.3.1 Introduction

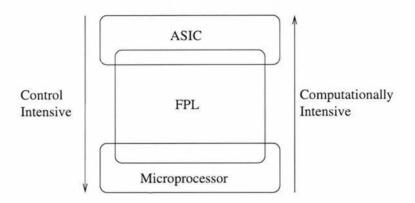

Figure 1.2: Computational Space Occupied by Reconfigurable Logic

There are three broad types of computing fabric - the Application Specific Integrated Circuit (ASIC), Field-Programmable Logic (FPL) and Microprocessor. Note that enhanced forms and hybrids of these basic fabrics also exist, like the digital signal processor (DSP). These are discussed in later sections. Figure 1.2 illustrates the relative suitability of the basic fabrics to control and compute intensive algorithms (arrows indicate increasing suitability). The ASIC is built using libraries of logic cells which define primitives such as logic gates, memories and adders. By connecting the cells circuitry can be described. When an ASIC design is complete, it is fabricated to perform the task exactly as explicitly defined by the cells and wires interconnecting them. FPL, for example the FPGA, is programmed electronically post manufacture by configuring specially designed logic blocks and routing resources. It is described in more detail in Section 2.2.

The Microprocessor and FPGA may be bought as standard devices (pre-manufactured) and hence are programmed to perform their task post-manufacture. This means they

may be used across many different systems, amortising much of the cost and risk associated with an ASIC. The level of abstraction for the processor and the FPGA is higher than that of the ASIC. Neither the FPGA nor ASIC fabric offers the same degree of control as the microprocessor, although the FPGA offers substantially more than the ASIC. As illustrated in Figure 1.2, to be better at control intensive tasks, a fabric trades off performance. This is due to the penalty paid for offering a high level of post-manufacture programmability.

In this section we will define spatial and temporal computation and then base a discussion of the three fabrics around Figure 1.2.

#### 1.3.2 Spatial versus Temporal

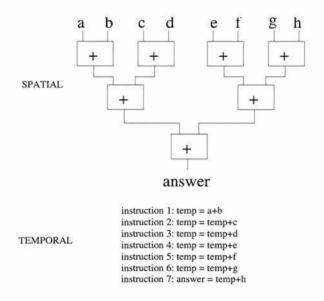

Figure 1.3: Temporal versus Spatial Programming Space

The von Neumann computing paradigm led to the microprocessor architecture. It consists of a fixed datapath and a dynamic set of instructions (program) which configure the datapath to perform a task by way of a number of steps. It provided a common architecture that could be used to perform many different tasks.

Rather than time-multiplexing a fixed data-path, it is possible to implement algorithms in space by constructing circuitry to perform them directly. This may be viewed

as the more natural candidate for implementation, since a microprocessor is effectively emulating hardware. Figure 1.3 illustrates the difference between temporal programming, as is done with a microprocessor and spatial programming, as is done with an ASIC or an FPGA. The temporal example performs the computation by time multiplexing a single adder. The fully spatial implementation uses 7 adders to perform the same computation.

It is possible to use a combination of spatial and temporal styles to tradeoff cost against time. For the sum example in Figure 1.3, the number of adders used is the cost and the time is the number of clock cycles required to perform the computation. An example combination of spatial and temporal techniques would be to use only 3 adders with some registers and control logic to perform the addition in a number of cycles. It should be noted that the brief overview of temporal versus spatial design given here is highly simplified. The ability of the FPGA or an ASIC to use a combination of both design styles means they can implement a microprocessor. However, neither would achieve as good a point in the JIT tradeoff space as a full custom implementation of the microprocessor. In this work we use the term ASIC and FPGA to refer to their classical use as fabrics for the construction of bespoke circuitry.

#### 1.3.3 Computing Fabric Discussion

The ASIC, FPL and microprocessor bring different qualities to the JIT computing tradeoff space. The ASIC may be designed to perform a specific task or set of tasks, hence its silicon area efficiency, speed and power consumption are excellent. It exhibits very little flexibility post-manufacture so if a chip's application space is not well defined at design time, a complete ASIC solution is not wise. FPL is programmed post-manufacture and hence offers flexibility, but this is paid for by being slower and less energy efficient than the ASIC. The FPL fabric design space is varied and the exact tradeoff is dependent on the match between the fabric and the application. Typically, the granularity of the computing elements making up an FPL fabric determines its speed/flexibility/energy tradeoff. This is discussed in Section 2.2.2. The microprocessor offers greatest flexibility, which has in part led to its success. In embedded systems, the high flexibility of the microprocessor is well suited to control flow tasks

such as a user interface.

Flexibility is also leading to the microprocessor's downfall as *the* computational fabric in the new era of computing dominated by just-in-time systems. Increasing clock rates and the exploitation of instruction level parallelism have provided diminishing returns on processor performance[90]. The once impressive scaling of the microprocessor's performance with Moore's law is no longer the case. Today, less than 10% of a modern microprocessor's die actually implements the datapath, with the majority of area taken by the cache to overcome the *memory wall*[174], and circuitry to inject instruction level parallelism. The modern high performance microprocessor's efficiency as measured by the percentage of transistors actively involved with performing computation is extremely low. It is well recognised in the literature that FPL provides a more energy and silicon efficient solution over the microprocessor for computationally intensive tasks such as DSP. For example, in [153] the authors observe energy savings in commercial devices of 89% when using FPL instead of an embedded microprocessor.

Changes have been made to the microprocessor's architecture to make it more suitable to data intensive processing, producing the digital signal processor. These are best characterised by the Harvard architecture, which effectively separates program bus and data bus. Parallelism is enhanced by overlapping data fetch, data operations and address calculations. Instruction set enhancements help minimise loop overheads and simplify the implementation of filters. A thorough summary of DSP architectures can be found in [84]. Despite the introduction of VLIW and multiple function units, the DSP is still fundamentally sequential, being based upon a serial instruction stream. In a move away from the serial instruction stream, the reconfigurable DSP has emerged, which we describe in background section 2.3.3.

#### 1.4 Wireless Communications

The rise of untethered computing devices is a major contributor to massive growth in wireless communications. It has been observed in [131] that the number of worldwide wireless subscribers each year grows as a Fibonacci series, and looks set to continue doing so in the near term. In [20] the authors predict that as the number of wireless

devices operated directly by humans saturates (e.g. cellphones), wirelessly connected machines will continue the growth trend.

Partly as a consequence of this growth in wireless communications, the efficient use of the electromagnetic spectrum enjoys very active research. The sophistication of the algorithms being developed to harness efficiently a given bandwidth is increasing rapidly. In [131] it is pointed out that the computational demands of these algorithms are growing much more quickly than the processor performance as predicted by Moore's law. Therefore, the software defined radio is, at least in the short term, likely to be a reality only in terms of the flexibility to use multiple air-interfaces. High layers in the communication protocol stack may be performed by software on a microprocessor, however lower level layers such as the MAC and Physical layer are too computationally intensive to be satisfied by a microprocessor. Instead, more specialised computational fabrics are required to meet the JIT requirements. These reasons, combined with the evolving nature of new communication standards, suggest that wireless communications is a good application area for reconfigurable computing. Therefore, the 3rd generation cellular standard called the Universal Telecommunications System (UMTS) is chosen for the case study in the thesis. Specifically, the physical layer processing engine of the base station is studied. Appendix A provides some fundamental wireless communications background and references for the interested reader.

#### 1.5 Thesis Overview

This thesis proposes an approach to the design of complex real-time embedded systems on programmable platforms. It offers a realistic approach to harnessing reconfiguration by acknowledging the increased design complexity of runtime reconfiguration. The word "realistic" is used here to differentiate the work from previous work on harnessing reconfiguration. The increased silicon area due to the configuration architecture, the disruption to the traditional design flow and the lack of tool support are considered in addition to the energy and resource savings achievable. It proposes a top-down approach to design, enabling a global optimisation effort rather than the local optimisation effort of the many previously proposed bottom-up approaches.

We use the physical layer processing engine of the Universal Mobile Telecommunication System (UMTS) as a case study throughout the thesis. It is a fully specified design for cellular basestations supporting up to 64 users.

In Chapter 2 we provide the reader with the required background for the understanding of the thesis including a detailed description of the Field Programmable Gate Array, fundamentals of hardware/software co-design, runtime reconfiguration and platform based design.

Chapter 3 explores the configuration architecture of an FPGA and proposes a design tradeoff space. Several techniques are investigated for speeding up reconfiguration and the corresponding required changes to the Xilinx Virtex configuration architecture are investigated.

Chapter 4 describes the proposed design methodology for targeting a reconfigurable fabric. The chapter begins by discussing the difference between transformational and reactive computing systems, and develops this difference to justify the proposed design framework for reconfigurable reactive systems. We then discuss the challenges of runtime reconfiguration and the opportunities of heterogeneous platform based design. The checkpoint based design framework is then proposed, together with its targeting approach.

In Chapter 5, the design of a commercial UMTS channel processing engine is used to apply the methodology in Chapter 4. This is done for all subsystems at a low-medium frequency of reconfiguration and for a single block of circuitry for high frequency reconfiguration.

# Chapter 2

# **Background**

#### 2.1 Introduction

This chapter presents essential background material for the understanding of the thesis. Field-Programmable Logic (FPL) is described in Section 2.2 with reconfigurable computing introduced in Section 2.3. Section 2.4 provides an overview of the emerging paradigm of platform based design. Previous approaches to harnessing a runtime reconfigurable Field Programmable Gate Array (FPGA) are outlined in Section 2.5. In Section 2.6 we summarise work in the literature on harnessing run-time reconfiguration. Section 2.7 summarises previous techniques developed for speeding up reconfiguration. Finally, Section 2.8 provides a summary of the chapter. Some fundamental principles of cellular wireless communications are provided in Appendix A.

#### 2.2 FPL

#### 2.2.1 Overview

Field-Programmable Logic, also known as reconfigurable logic, refers to a class of architectures in which the configuration bits are directly involved with controlling hardware and links; otherwise, the architecture is referred to as programmable. Most FPL architectures are a mixture of programmable and reconfigurable.

An FPL fabric performs computation spatially. Most commonly, it is composed

of a two-dimensional grid of computational elements which are connected together using some form of reconfigurable interconnect mesh. We note that other architectural compositions have been proposed, such as the linear array as in RaPiD[61] and PipeRench[138]. These architectures are aimed at highly regular pipelined computation-intensive tasks, and are therefore limited in application. In this section we will discuss the term granularity, describe in detail one particular type of FPL - the Field Programmable Gate Array (FPGA) and outline some previous work on hardware-software co-design.

#### 2.2.2 Granularity

The granularity of an FPL fabric refers to the width of the path between computation elements and the computation performed by an individual element. In [82] the authors look at mapping algorithms to a coarse grain fabric arranged as a two dimensional grid of N-bit ALUs. Another example is the FPGA such as the Xilinx Virtex [177] which uses lookup tables of 4-bit input, 1-bit output to perform computation at a much finer granularity. In general, coarse grain FPL is better suited to word-oriented computation such as multiplication and fine-grain FPL is better suited to bit oriented computation such as the permutation operations typical of encryption algorithms.

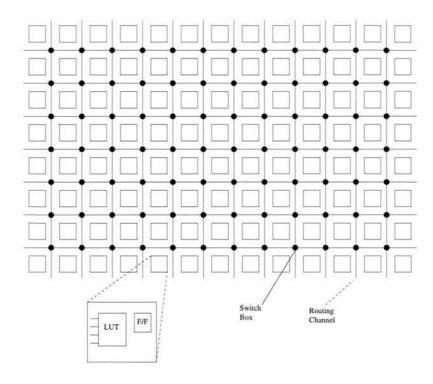

#### 2.2.3 FPGA

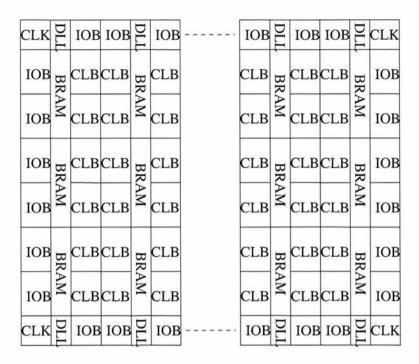

The Field Programmable Gate Array (FPGA) is a particular type of FPL architecture dating back to around 1989[71]. It consists of a 2 dimensional grid of look up tables and flip/flops connected by a hierarchical interconnect fabric. Through programming the contents of the LUTs and setting multiplexers within the interconnect to connect the LUTs together as required, circuitry is created. Most common is the 4-input, 1-output LUT. It consists of a 16-bit memory and is therefore capable of implementing any function of 4 inputs. Figure 2.1 is a diagram illustrating an FPGA's architecture. It is programmed (post manufacture) by loading a configuration bitstream into the device's highly distributed configuration RAM.

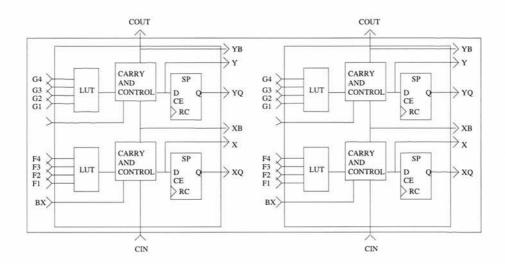

Figure 2.2 shows an example of a commercial architecture's logic block. It is the

Figure 2.1: Generalised FPGA Architecture

Xilinx Virtex Configurable Logic Block (CLB), containing two identical slices, each slice consisting of two LUT and flip/flop pairs. Rather than the simple single LUT and flip/flop as drawn in the diagram of Figure 2.1, the slices also contain circuitry to help with common arithmetic - for example the provision of a fast carry chain for adders.

### 2.3 Runtime Reconfigurable FPL

#### 2.3.1 Introduction

Runtime reconfiguration of FPL refers to changing the content of the configuration memory during computation. This enables the algorithm designer to allocate computational resources to match algorithm and data. Such architectures typically couple the FPL with a processor or sequencer to form a hybrid. The sequencer or processor's role is to manage configurations and perform control intensive tasks.

Figure 2.2: Xilinx Virtex CLB

Here we offer a brief overview of the runtime reconfigurable FPGA in section 2.3.2 and the runtime reconfigurable DSP in section 2.3.3. The concept of specialisation is introduced in section 2.3.4 and hardware-software co-design in the context of runtime reconfigurable FPL is described in section 2.3.5.

#### 2.3.2 Runtime Reconfigurable FPGA

Most hybrid processor-FPGA based systems reported in the literature are not runtime reconfigurable, but static. In these systems, the computationally intensive kernels of the application are implemented on the FPGA and the rest on a microprocessor. The FPGA's configuration is downloaded at the start of system execution and does not change during execution. PRISM[11], Splash[10], and the Programmable Active Memory (PAM) work at DEC-Paris labs[17] are frequently referenced examples of this system model.

Examples of runtime reconfigurable FPGA based systems include a reconfigurable compiler and FPGA architecture called WASMII[106], a self reconfiguration processor[64] and work on incremental run-time reconfiguration by Lysaght and Dunlop[109].

#### 2.3.3 DSP and Runtime Reconfigurable DSP

DSP processors are instruction-set programmable architectures specialised to digital signal processing problems[155]. This makes them well suited for repetitive numerical processing tasks such as arithmetic loop kernels, and less suitable for general purpose computing tasks. They benefit from architectural features such as single cycle multiply and accumulate (MAC) units, zero-overhead loop circuitry, address generation units and a throughput oriented memory architecture. An example of a DSP processor is the Texas Instruments TI6416 DSP[158].

The runtime reconfigurable DSP offers an alternative architecture to the traditional DSP. Reconfigurable captures their spatial processing ability and runtime captures its operation. A runtime reconfigurable DSP uses coarse grain processing elements and interconnect path-widths greater than one bit. This is because DSP benefits from modular arithmetic operators and it brings large area savings over the single bit CLB and interconnect offered by the FPGA. However, it should be noted that coarse-grained architectures are poor at bit-level manipulations found, for example, in many communications algorithms.

An example of a runtime reconfigurable DSP is MATRIX[118], based upon a MIMD grid of small 8 bit processors with near-neighbour and length-four connectivity. The REMARC[119] architecture was based upon a grid of 16-bit processors with nearest neighbour and full-length bus based communication, globally controlled with a SIMD-like instruction sequencer.

#### 2.3.4 Specialisation

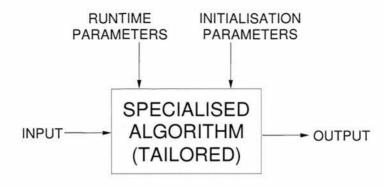

Specialisation refers to the ability of reconfigurable FPL to be tailored to more closely match its requirements. This is in contrast to an ASIC design which is fixed at manufacture and hence is generalised, satisfying all possible requirements including the "worst-case". Figure 2.3 illustrates this point by showing how a reconfigurable design may exploit better specified design time knowledge such as "initialisation parameters" together with "run-time parameters" to better match the exact requirements. This is often referred to as data-folding, or constant-propagation. The closer an algorithm's

Figure 2.3: Algorithm Implemented on a Reconfigurable FPL Fabric

implementation is to its actual use, the more data is available for specialisation and the less general purpose it becomes. In contrast, the ASIC must implement a "one-size fits all" design. FPL enjoys a continuum of specialisation from static through to very frequent dynamic reconfiguration. The frequency of reconfiguration is a subject of much interest in the literature and is discussed in this thesis. There are numerous examples of specialisation across a wide variety of application domains in the literature, from folding the key into an encryption algorithm[129], to creating a constant coefficient multiplier for a FIR filter[42].

#### 2.3.5 Hardware Software Co-design

#### 2.3.5.1 Overview

A large body of literature exists on the problem of hardware-software co-design. "Hardware" in this work primarily refers to the ASIC and "software" refers to computation performed by the microprocessor. FPL, particularly reconfigurable FPL, blurs the traditional boundary between hardware and software. The most common approach to harnessing FPL in the reconfigurable computing literature has been software centric, i.e. the FPL is treated as a slave to the microprocessor as discussed in Section 2.3.5.2. The other more recent approach is to elevate the FPL's importance from slave to master with logic centric design as discussed in Section 2.3.5.3.

#### 2.3.5.2 Software Centric

There are many projects in the literature which attempt to take a high-level description of a design (e.g. written in C) and automatically map it to a microprocessor and FPL. The architectural solutions differ primarily in the coupling between the microprocessor and the FPL. The coupling varies between including FPL as a reconfigurable function unit on the system bus, to placing it on the peripheral bus as a co-processor.

For example, the Proteus Architecture [48] is an ARM based implementation with a reconfigurable ALU consisting of multiple reconfigurable function units. Applications load custom instructions at run-time to speedup execution. The commercial Triscend A7 device [161] has an ARM processor loosely coupled to a large reconfigurable fabric to provide co-processor functionality. This approach requires a more traditional hardware-software co-design methodology.

The software centric approach usually involves profiling the application and applying the 90:10 rule of thumb, which states that 90% of software execution time is spent in 10% of the code. The kernels representing 10% of execution time are then considered for implementation on the FPL.

#### 2.3.5.3 Logic Centric

The dominance of the software centric approach to reconfigurable system design can in part be explained by the legacy of the general purpose microprocessor. However, it often fails to harness the massive parallelism possible with FPL since it centres around the serial instruction stream. Instead, it would seem more sensible to capture the design in a more logic-centric way, thus preserving its parallelism.

The logic-centric approach to system design elevates the FPL to be the primary vehicle of computation. In [27] Brebner describes a class of systems in which FPL is best suited to performing the computation with the microprocessor relegated to processing only exceptional cases. The illustrative example used is a gigabit IP router design in which line rate processing is performed by the FPL and only exceptional cases are handled by the microprocessor.

#### 2.3.5.4 Summary

It is likely that reconfigurable embedded systems will demand elements of both software and logic centric design approaches. It is important for the designer to appreciate the strengths of each fabric so a good mapping within the JIT trade-off space can be made.

## 2.4 Platform based design

#### 2.4.1 Introduction

The much heralded System on a Chip (SOC) design paradigm as originally conceived has largely failed due to problems with the integration of IP blocks[9][16]. Platform based design may provide an alternative route to SOC. Here we outline what a platform is and review some of the opportunities and challenges it brings to the embedded system designer. We structure the review using the headings: Flexibility, Heterogeneity, Scalability, Productivity and Abstraction.

#### 2.4.2 What is a platform?

We define the platform here as a standardised programmable architecture and its associated abstraction model. The term standardised describes the ability to target many applications, perhaps from a particular domain, at the architecture. The term programmable emphasises that a level of flexibility exists such that function blocks and the connections between them can be configured post-manufacture. Finally, the abstraction model provides a programmer's view of the architecture without unnecessary detail, but with enough visibility to allow fine-tuning. For example, the use of Matlab and Simulink in the Xilinx System Generator for DSP presents an alternative programming model for FPGAs from Hardware Description Languages (HDLs) such as Verilog. The platform we are interested in is the complete system platform - not simply the architectural design, but a full device manufactured as a standard part, or family of parts.

To further describe what is meant by the platform based approach to SOC design, it is useful to look at the environment in which it has been born. Two powerful forces are shaping the semiconductor industry today - the shrinking size of the time to market window and spiralling non-recurring engineering (NRE) costs. The gap between the level of chip integration possible and the productivity of a designer continues to grow. This results in it becoming increasingly difficult to meet the spike characteristic of market demand. For example in [151], Smith presents evidence that a 1 month lead in time to market can result in a 70% difference in revenue over an ASIC's lifetime. The second problem relates to the cost of manufacturing an ASIC. At each generation of Moore's law, the cost of creating the masks used in the manufacture of a chip grows exponentially. To justify this cost, the chip must be manufactured in large volumes. The way in which platform based design meets this challenge is by removing a lot of choice from the designer. Instead of starting with a blank piece of silicon, the designer is presented with a pre-designed flexible computing fabric to which he maps his system. The fabric is used across several different systems which both increases design reuse and amortises the NRE cost.

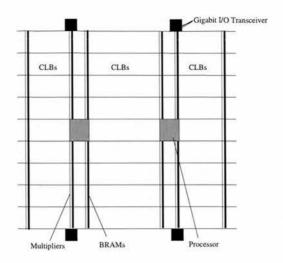

Many different platforms exist. Some are highly domain specific such as the Texas Instruments C64x DSP with its turbo decoder co-processor. Others, such as the Xilinx Virtex II FPGA family[180] are targeted more generally at networking and DSP applications. Figure 2.4 illustrates the high level of integration: microprocessors, multipliers, block RAM (BRAM) and giga-bit I/O transceivers within a 2-dimensional grid of LUTs and a rich interconnect fabric.

#### 2.4.3 Flexibility

As discussed in Section 1.1, flexibility is now viewed as a design attribute in computer architecture. It forms one of the three axes in the JIT computing tradeoff space. If a platform provides too much flexibility then it is cost and energy inefficient. If too little flexibility is provided then it is not possible to map the required system functionality.

To explore what the implications of flexibility are, it is useful to view it from two perspectives - design-time and run-time. It is of course true that design-time flexibility must incorporate the required level of runtime flexibility, but examining the two sep-

Figure 2.4: Xilinx Virtex II Pro Block Diagram

arately will help to shape this amorphous attribute. (It should be noted that a higher level of flexibility exists - portability between platforms. This is discussed under the heading of abstraction in Section 2.4.7.)

At design time, the prime focus is programming the platform to implement a system. The level of flexibility required is just enough to map the system to the platform, although the availability of extra flexibility eases the mapping as discussed by DeHon in [55]. At runtime, a level of flexibility must exist to satisfy the degree to which the system's functionality is runtime dependent. For example, the requirement to implement arbitrary algorithms demands high flexibility. A (design-time) well-specified data-independent system has a low demand for runtime flexibility.

#### 2.4.4 Heterogeneity

Given some form of application domain, the platform architect's challenge is to create a solution which satisfies the domain's performance requirement, trading off cost, flexibility and energy. This leads to a heterogeneous solution. At the architect's disposal are three broad sets of computational fabric - processor, FPGA and ASIC. Within each of these sets are many further choices. One which is particularly wide is the choice of ASIC elements to include, beyond the mixture of computational fabrics, memory,

interconnect and I/O demand further decisions.

The challenges faced by the system designer targeting a platform are different from those of the SoC designer. The design freedom offered by the SOC created the possibility of a near optimal solution. In terms of value, this often led to a disproportionate amount of effort spent on architecture design over system design. With platform based design, the designer is restricted to the task of mapping rather than creation. One interesting concept this brings to the fore is that of algorithm fluidity, i.e. functionality may be moved between computational fabrics. In [88] the authors coin the term "software decelerators" to refer to functionality implemented in an FPGA logic fabric being shifted to a microprocessor. For example, given a mapping problem where FPGA logic resources are in high demand and microprocessor resources are under utilised then exploitation of such fluidity is useful.

#### 2.4.5 Scalability

Scalability represents a highly prized but elusive goal of computing. The ability to scale a system through the addition of extra silicon resources with little additional design effort is very valuable. Its realisation is likely to run through the centre of a system from design capture right through to the implementation fabric. To be truly scalable (across fabrication process generations) the system description must be implementation independent.

A less demanding form of scalability is to confine its scope to a single process generation, for example, a system which ships in products of different configurations. If the platform targeted is offered as a family of device sizes, then it could be exploited with a scalable design, rather than a single large design which is capable of all product configurations.

#### 2.4.6 Productivity

Productivity is increased right across the design flow when targeting architectural platforms. The productivity gain of reduced designer freedom has already been mentioned. Platform based design increases productivity by allowing the designer to concentrate on system design rather than the details of the implementation fabric. The use of a common platform brings with it the opportunity for increased use of IP blocks. The central promise of the SOC design failed to reach potential - improved productivity through use of IP blocks. The problem was that design teams had to spend a great deal of time integrating IP blocks together. With a common platform architecture, the potential for straightforward integration exists, bringing with it the true potential of "plug and play" IP based design.

Perhaps the greatest productivity gain is reduced verification and test. With a standard platform architecture, the significant cost of physical test and verification is independent of the design and can therefore be amortised over all designs.

#### 2.4.7 Abstraction

As platform based design envelops more systems, domain specific platforms will be created to better match the requirements of a particular group of systems. Apart from the obvious benefits of increased competition, the availability of many platforms presents the system designer with choice. Traditional design methodologies assume knowledge of the target platform, so the decision must be made early in the design process. Such a methodology ties the system to a particular implementation target, bringing with it several undesirable consequences, two of which are a) the choice of target platform may have been incorrect, leading to a solution with a sub-optimal point in the cost-energy-flexibility tradeoff space and b) platform architectures will evolve to exploit increased chip-level integration, making IP blocks tied to a particular architecture obsolete.

These problems demand design abstraction from the implementation platform. This is an active subject of research in the literature incorporating the large subject area of hardware-software co-design. Platform based design brings its own challenges which are only beginning to be investigated. The level of design abstraction required is likely to be higher than that of hardware-software design due to the heterogeneity of platforms. In [26][31] the authors propose and investigate the idea of Circlets: a circuitry description independent of its implementation, allowing rapid mapping to a concrete fabric. The level of abstraction is low, around the level of the 4-input LUT,

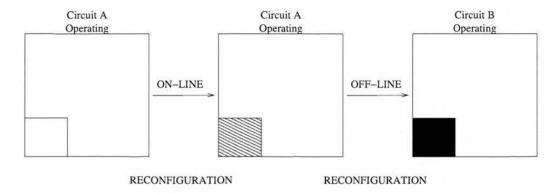

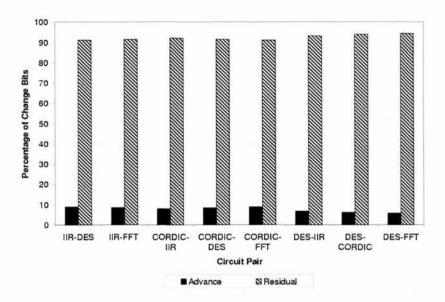

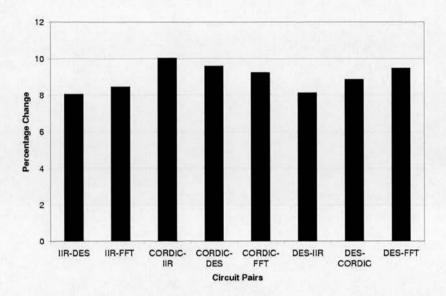

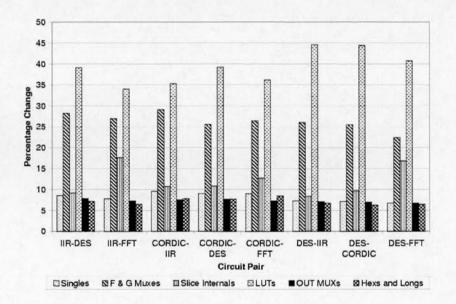

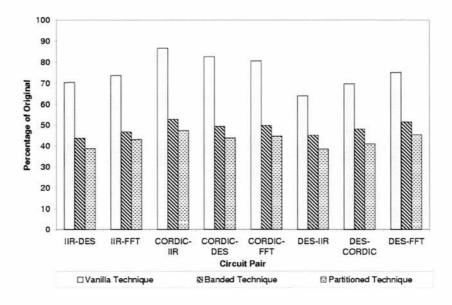

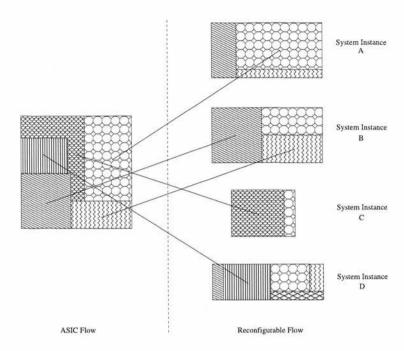

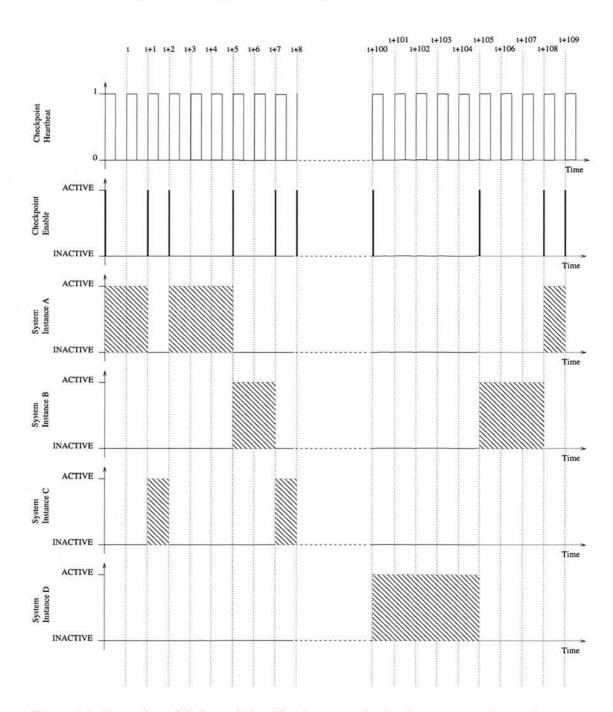

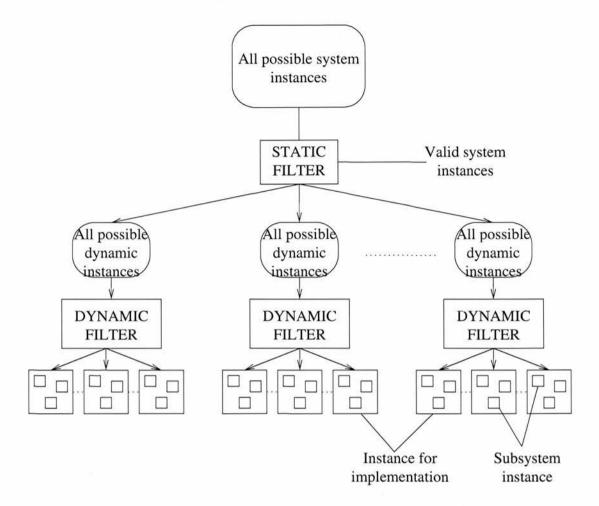

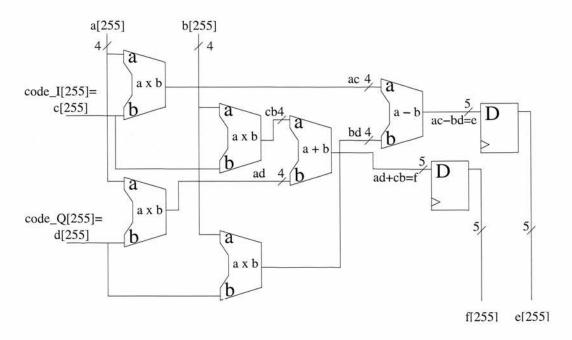

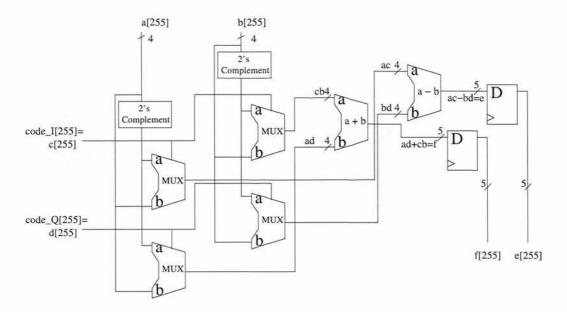

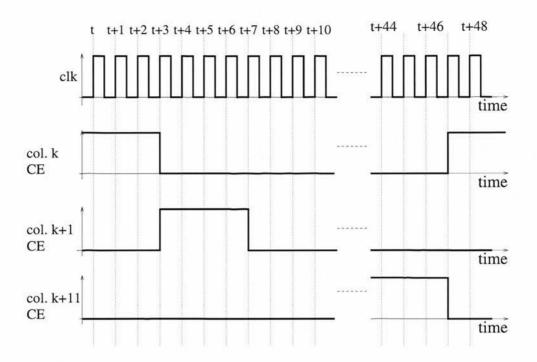

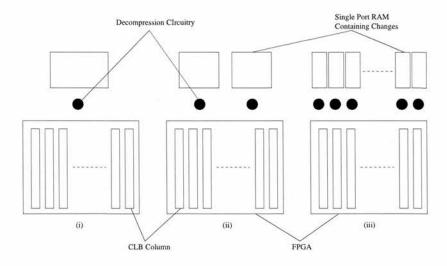

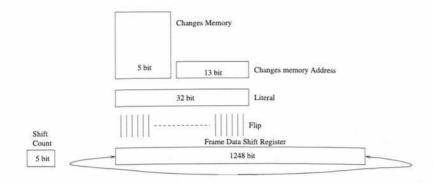

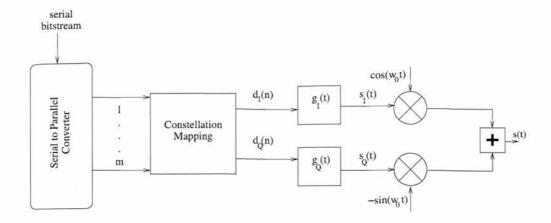

and is therefore limited in scope to homogeneous FPGA fabrics. It is possible to raise the level of abstraction, enabling the use of features such as hardwired multipliers, however the original aim of fast real-time mapping from the description to implementation may be lost. For example, in [74] the authors envisage the requirement for a system's design to remain platform independent during its entire life-cycle. Java byte code provides the processor abstraction and an RTL based byte-code[75] provides the circuitry abstraction. An interpreter at the client maps the RTL description onto the concrete FPGA fabric. The authors do not consider the (substantial) computation required to perform the mapping operation, although they do point out that it would be less than performing the full synthesis from a high-level VHDL description.