# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# MICROCOMPUTER BASED SIMULATION

by

Andrew Haining, B.Sc.

Doctor of Philosophy University of Edinburgh 1981

#### **ABSTRACT**

Digital simulation is a useful tool in many scientific areas.

Interactive simulation can provide the user with a better appreciation of a problem area. With the introduction of large scale integrated circuits and in particular the advent of the microprocessor, a large amount of computing power is available at low cost. The aim of this project therefore was to investigate the feasibility of producing a minimum cost, easy to use, interactive digital simulation system.

A hardware microcomputer system was constructed to test simulation program concepts and an interactive program was designed and developed for this system. By the use of a set of commands and subsequent interactive dialogue, the program allows the user to enter and perform simulation tasks. The simulation program is unusual in that it does not require a sophisticated operating system or other system programs such as compilers. The program does not require any backup memory devices such as magnetic disc or tape and indeed could be stored in The program is designed to be flexible and extendable and could be easily modified to run with a variety of hardware configurations. The highly interactive nature of the system means that its operation requires very little programming experience.

The microcomputer hardware system uses two microprocessors together with specially designed interfaces. One was dedicated to the implementation of the simulation equations, and the other provided an input/output capability including a low cost CRT display.

# <u>ACKNOWLEDGEMENTS</u>

I would like to thank my supervisor Dr. J.R. Jordan and everybody else from the Department of Electrical Engineering and the Institute of Terrestrial Ecology without whose help this project would not have been possible.

# CONTENTS

| Abstract         |     |   |                                     |     |  |  |

|------------------|-----|---|-------------------------------------|-----|--|--|

| Declaration      |     |   |                                     |     |  |  |

| Acknowledgements |     |   |                                     |     |  |  |

| Contents         |     |   |                                     |     |  |  |

| content          | 5   |   |                                     | (v) |  |  |

|                  |     |   |                                     |     |  |  |

| CHAPTER          | 1   | : | Introduction                        | 1   |  |  |

|                  | 1.1 | : | Motivation                          | 1   |  |  |

|                  | 1.2 | : | Microcomputer System                | 2   |  |  |

|                  | 1.3 | : | Natural Resource Applications       | 4   |  |  |

|                  | 1.4 | : | Engineering Applications            | 6   |  |  |

|                  | 1.5 | : | Numerical Integration               | 7   |  |  |

| CHAPTER          | 2   | : | Simulation                          | 13  |  |  |

|                  | 2.1 | : | Continuous Simulation               | 13  |  |  |

|                  | 2.2 | : | Simulation Problem Implementation   | 15  |  |  |

|                  | 2.3 | : | Microcomputer Considerations        | 24  |  |  |

|                  |     |   | 2.3.1 Man-Machine Interface         | 24  |  |  |

|                  |     |   | 2.3.2 Arithmetic                    | 26  |  |  |

|                  |     |   | 2.3.3 Languages                     | 28  |  |  |

|                  | 2.4 | : | Microcomputer System Implementation | 31  |  |  |

| CHAPTER          | 3   | : | Microcomputer System                | 35  |  |  |

|                  | 3.1 | : | System Requirements                 | 35  |  |  |

|                  |     |   | 3.1.1 Microprocessor                | 35  |  |  |

|                  |     |   | 3.1.2 Memory                        | 46  |  |  |

|                  |     |   | 3.1.3 Secondary Storage             | 49  |  |  |

|                  |     |   | 3.1.4 Input and Output Devices      | 50  |  |  |

|                  | 3.2 | : | System Hardware                     | 52  |  |  |

|                  |     |   | 3.2.1 General Description           | 52  |  |  |

|                  |     |   | 3.2.2 Microprocessors               | 56  |  |  |

|                  |     |   | 3.2.3 CMOS Memory                   | 60  |  |  |

|            |     |   |                                         | Page     |  |

|------------|-----|---|-----------------------------------------|----------|--|

|            |     |   | 3.2.4 Arithmetic Processor              | 63       |  |

|            |     |   | 3.2.5 Nascom-1 Extender                 | 65       |  |

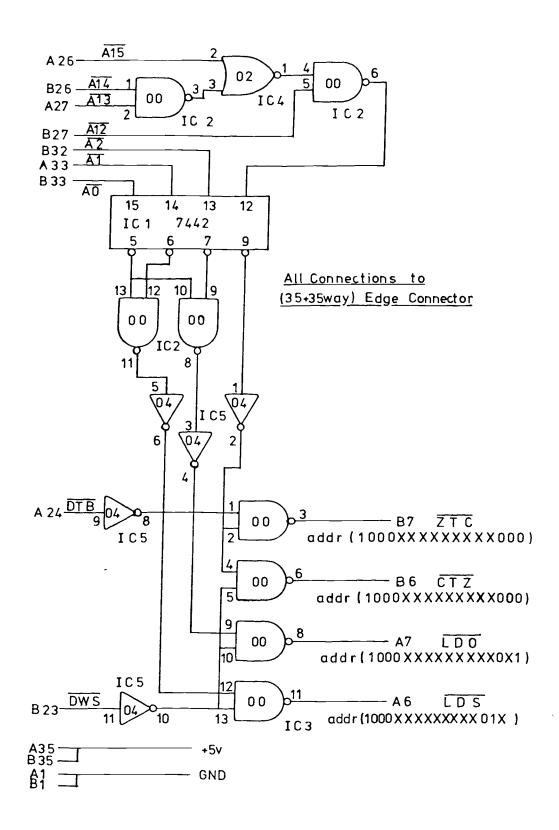

|            |     |   | 3.2.6 Link Circuit                      | 68       |  |

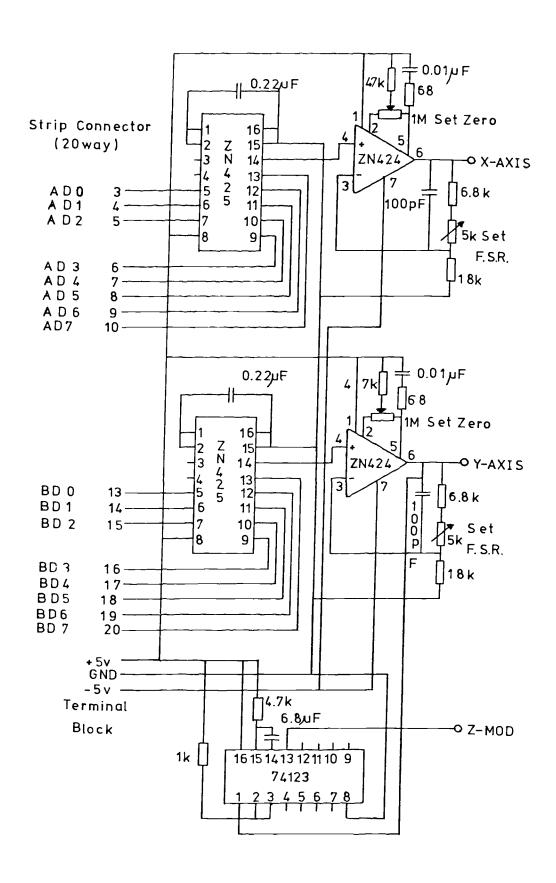

|            |     |   | 3.2.7 Analogue Output                   | 70       |  |

|            | 3.3 | : | System Software                         | 70       |  |

|            |     |   | 3.3.1 Program Development               | 70       |  |

|            |     |   | 3.3.2 Program Debugging Aids            | 77       |  |

|            |     |   | 3.3.3 Floating Point Package            | 80       |  |

| CHAPTER    | 4   | : | Microcomputer Simulation System Program | 82       |  |

|            | 4.1 | : | Overview                                | 82       |  |

|            | 4.2 | : | Command Level                           | 91       |  |

|            | 4.3 | : | Equation Entry                          | 91       |  |

|            | 4.4 | : | System Control                          | 104      |  |

|            | 4.5 | : | Running Equations                       | 114      |  |

|            | 4.6 | : | Displaying Results                      | 119      |  |

| CHAPTER    | 5   | : | Using the Simulation System             | 126      |  |

|            | 5.1 | : | Operational Details                     | 126      |  |

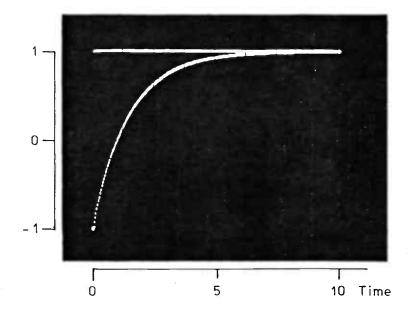

|            | 5.2 | : | First Order Step Response               | 132      |  |

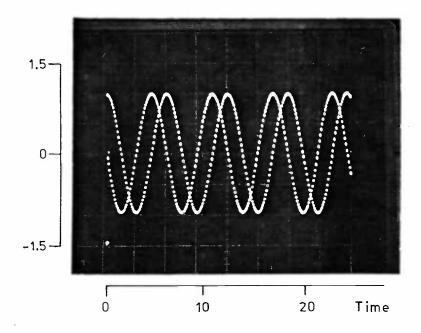

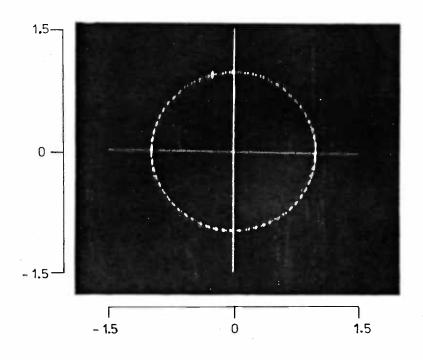

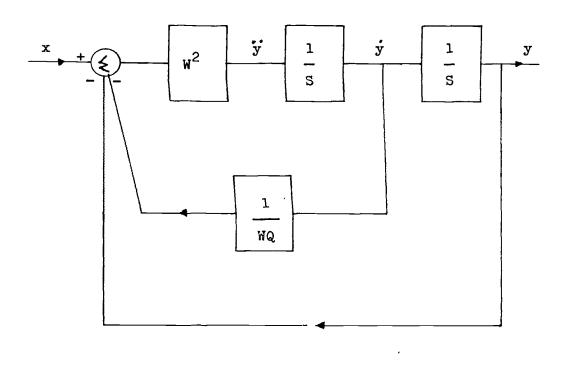

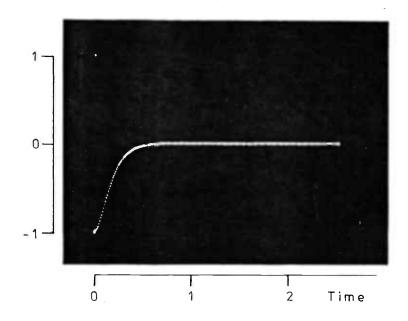

|            | 5.3 | : | Linear Oscillator                       | 139      |  |

|            | 5.4 | : | Other Test Results                      | 146<br>• |  |

| CHAPTER    | 6   | : | Conclusions                             | 160      |  |

|            | 6.1 | : | Present System                          | 160      |  |

|            | 6.2 | : | Future Developments                     | 166      |  |

| REFERENCES |     |   |                                         |          |  |

#### 1.1 Motivation

The advent of large scale integrated circuits and the development of microprocessors has meant that considerable computing power is now available at low cost and with small size. Simulation is a powerful tool used for investigation and prediction in a wide variety of fields including engineering and natural resources. Digital simulation of continuous systems has in the past been only available on large and expensive computer installations.

The aim of this project was therefore to investigate the possibilities of constructing a microprocessor based simulation system for the digital simulation of continuous systems. proposed system would provide a useful level of simulation facilities at low cost. A small single-user interactive system should enable a user with little or no programming experience to quickly develop and use simulation models. The original area for simulation problems whose consideration led to this project, was the natural resource field. A considerable number of problems in this field have a large number of relatively simple equations. This means that although the individual equations are quite easy to simulate, their large number combined with the long time scales generally found in these problems, require considerable computing With a conventional time sharing computer system these time. simulation models can be very expensive to develop and use, especially if an interactive system is used. An interactive simulation system greatly speeds the development of the required models by both providing the user with a feel or insight for the problem and enabling the user to terminate simulation runs when

the model is obviously producing erroneous results. A microprocessor based system offers the advantage of interactive use with low initial and running costs. The microprocessor will be much slower in computations than a mainframe computer, but the overall simulation system response time might not be significantly slower than a busy multi-access system, and has the advantage of being always available.

The simulation system developed and described in chapters three and four, allows a user with little computing experience to develop and use models in a highly interactive mode. Printed and graphic output is provided together with data input facilities. The size of the models usable is dependent on the amount of memory the system has, and is easily extendable.

#### .1.2 Microcomputer System

A microcomputer is just a very small computer which uses a microprocessor as its Central Processing Unit (CPU). The microprocessor performs arithmetic and logical functions, and controls the flow of data to and from the other components which make up the microcomputer. The most basic microcomputer system which could be used for even the simplest simulation tasks would require not only the microprocessor, but also sufficient memory to store the simulation program and its associated data together with a two way interface to allow the user to communicate with the simulation program.

The type and amount of memory required depends on the type of simulation system. There are two basic types of main memory, these are Read Only Memory (ROM) whose contents are permanently fixed and can therefore be used to hold important programs like

monitors and interpreters, and read write memory usually called Random Access Memory (RAM) which can be used to hold temporary programs All variables and results produced while a program is running must be stored in RAM and since microcomputers almost exclusively use semiconductor memory which is volatile, then they are lost if the power is switched off unless they are stored in secondary, or backup, memory. For simulation results this is generally quite acceptable, but for the programs themselves this can be very inconvenient as they have to be loaded up before each session. An alternative is to store the programs in some form of read only memory like Erasable Programmable Read Only Memory (EPROM) which can be wiped clean and reused. ROM and EPROM are fine providing the data need not be changed, so they are more suited to the systems programs and look-up data tables.

In order to get the microcomputer to do any useful work, the user must be able to interact with it, to tell it what to do and to follow its progress. The most common and indeed most flexible way for this is by using an alphanumeric keyboard and display. The display could be either a Visual Display Unit (VDU) or a printer. Alternative input and output devices, like joysticks and oscilloscopes, can be advantageous for some speciallized applications.

No present microprocessors can perform floating point arithmetic directly, and most cannot even perform integer multiplication and division. Therefore subroutines must be provided for the level of arithmetic required for any given application. Integer arithmetic can be used in multiples of the microprocessors word length to provide any accuracy, but for general purpose simulation

where a wide dynamic range is needed together with moderate accuracy, then integer arithmetic becomes very expensive in memory space and the more compact floating point can be used. Special purpose hardware can be used to relieve the arithmetic subroutines of some of their calculations.

To develop simulation programs of reasonable complexity, several development and debugging aids are necessary in order to ensure that the time and effort involved in producing the program is not out of all proportion to the benefits derived from it. Typical programs that may be required are monitors, editors, assemblers, interpreters and compilers. To enter the program into the microcomputer, either for development or use, some form of secondary storage is required with the appropriate loading facilities. Secondary storage methods commonly used are paper tape, and magnetic media such as cassettes and floppy discs.

## 1.3 Natural Resource Applications

The original motivation behind the microprocessor based simulation system arose from an examination of a simulation problem concerning the water flow in a forest. The problem concerned both the internal water flow pathways inside the forest, including the transport mechanisms within the tree itself, and the net effect of the forest on the surrounding area. The Institute of Terrestrial Ecology has been measuring the development and functioning of a plantation of sitka spruce, and among these measurements were some of the factors which affect the water balance of the forest. The accurate measurement of environmental

factors is difficult to achieve because of the extremes of weather and the long timescales over which the measurements are required. The measurement of physiological details of the trees themselves is even more difficult due to the small quantitative changes involved, and their long timescales. The initial need for simulation would be to allow the action of various theoretical models to be examined, so that scarce resources could be allocated to measuring the most useful parameters. The experimental results could then be used to generate new models, and the whole process would be repeated.

Another use of simulation would be to produce a model of the gross action of the forest, at all stages of development, so that its effect on possible planting sites could be examined. The changes in the water flows caused by the afforestation of a tract of land is very important because the sites suitable for the forest are often reservoir catchment areas.

Due perhaps to the difficulties of collecting accurate data, the model equations resulting from research are in themselves quite simple. However the large quantity of equations needed for an overall water flow simulation and the long timescales over which the model has to be run, combine to produce a simulation model which requires a lot of computing time. The cost of such computing time using a mainframe computer to organisations like the Institute of Terrestrial Ecology, which have very scare resources, means that such simulation models cannot be used to their maximum benefit. A microprocessor based simulation system would however have a very low running cost, and its interactive facilities would also help to reduce the effort and cost of developing the models

in the first place. The slower calculation speed of the microprocessor need not be a disadvantage since, after the user has checked to see that the model is functioning properly, the system could be left overnight to produce the results.

## 1.4 Engineering Applications

Simulation is a very useful tool in all fields of engineering but, because of the effort required to run a simulation, it has generally been reserved for problems which are difficult either to analyze or to test practically. Small systems, especially electrical and electronic analogue circuits, are quite often designed using a simplified theory and then modified to obtain the correct operation after being built and tested. Although inelegant, this method is often the cheapest and most cost effective. However if a cheap and easy to use simulation system was available, then simulation could be used effectively to reduce the required testing and modification stages, as well as allowing the designer to explore a greater variety of possible solutions. For most problems a graphic output would be preferable, with only a relatively low accuracy result being required.

Another area where simulation could be used profitably is in the teaching of engineering, and in particular analogue electronics. The conceptual difficulty in relating theory to experimental work hampers a student when the theory has to be applied to a real problem. The use of simulation to illustrate the theory could help to break down the conceptual difficulties and enable a student to accept the theory more easily. The need

here would be for graphic presentation of the simulation results which could easily be related to the oscilloscope waveforms encountered in the laboratory.

#### 1.5 Numerical Integration

The present version of the SIMUPROG simulation system program does not provide a built in integration routine, but instead allows the user to implement the most suitable method for the problem under consideration. While this does provide great flexibility, a built in integration method or methods could usefully be included in expanded versions of the system.

Considering a first order differential equation, the numerical integration methods suitable for solving the equation fall into two main categories. These are the single step methods, such as Euler and the Runge Kutta families, and the multistep methods like the Adams Bashforth predictors and Adams Moulton correctors. A full explanation of these and other methods has been given by Gear<sup>1</sup>.

Considering a discrete time step h, the value of the variable y at time t+h can be expressed in terms of the values of its derivatives at time t by the following Taylor Series expansion.

$$y(t+h) = y(t) + h*\dot{y}(t) + \frac{h^2}{2}*\ddot{y}(t) + \frac{h^3}{3}*\ddot{y}(t) + \dots$$

An integration method is said to be of order N if it produces component terms which match the first N+1 terms of the above series.

Higher order differential equations can either be broken down into a set of first order ones, or in some cases treated directly.

Gear<sup>1</sup> gives examples using the truncated Taylor Series expansion directly and also using the Nyström formula for special second order equations.

The accuracy of any simulation run is dependent on both the integration method and the accuracy of the arithmetic. arithmetic performed on the GIMINI microcomputer used 32 bit floating point representation, with 23 bits for the mantissa, 8 bits for the binary exponent and one sign bit. Since the results of a calculation are truncated to get them back to the 23 bits, the worst case error produced is  $2^{-23}$  times the exponent of This error is therefore between  $2^{-23}$  and  $2^{-22}$  times the result. the normalised result value. If it is assumed that the error is randomly distributed with a rectangular distribution, then the mean error will be  $2^{-24}$  to  $2^{-23}$  times the result value for each operation performed. For example after 10000 operations the truncation error could be expected to be between .0006 and .0012 times the result value. Another source of error is that the numbers entered into the system are only held with 23 bit significant Thus more cumulative errors may be introduced if, for example, a value like the step size is inaccurate. The result of these errors can be amplified if unsuitable equations are chosen, i.e. if a small variation in a large value number is critical.

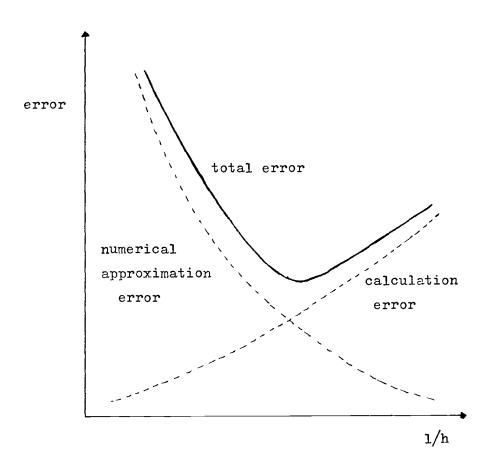

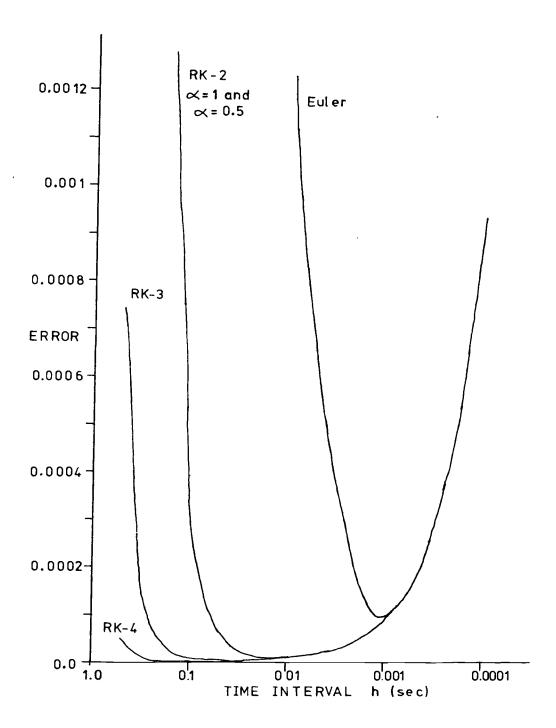

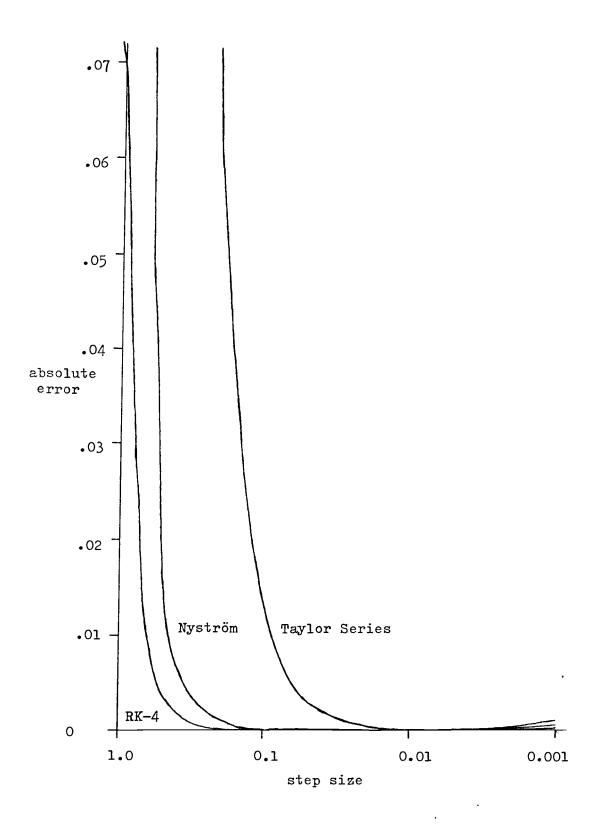

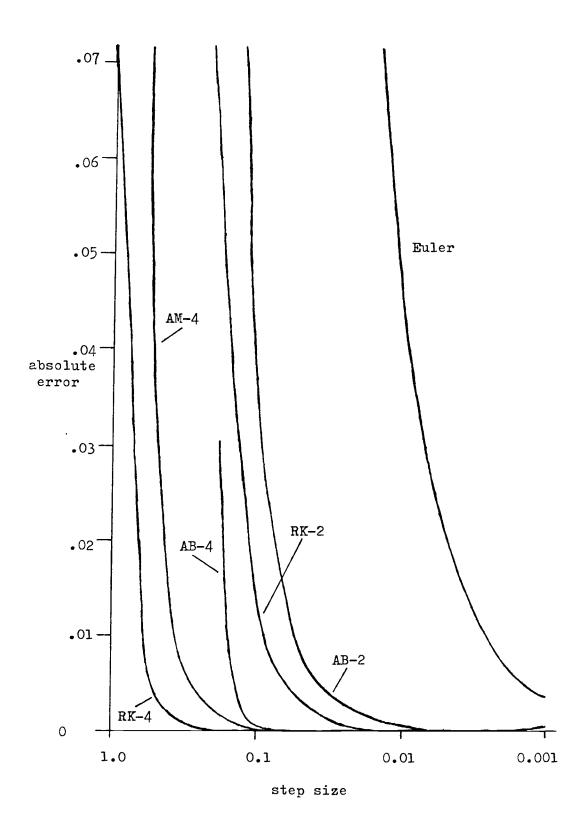

Ideally any integration method can be made more accurate by decreasing the step size, unfortunately, as the step size is decreased, the truncation errors become more significant until they are completely dominant. Each integration method will have its own error curve, and a typical example is shown in figure 1.1.

Figure 1.1 Integration Errors

The choice of integration method will depend on both the simulation equations and the accuracy of the results required. Euler integration is the simplest to implement, but being first order it is also the least accurate, so that a large number of steps using high accuracy arithmetic will be needed to produce a very accurate result. Also, because of the large number of steps, it may be slower to run. In spite of this, if a quick low accuracy solution is required, Euler may be very convenient. The one parameter family of second order Runge Kutta methods given by Benyon<sup>2</sup> can be rewritten as the predictor-corrector family given below.

$$y_{n+\alpha}^{p} = y_{n} + \alpha h \dot{y}_{n}$$

$$\dot{y}_{n+\alpha}^{p} = f(y_{n+\alpha}^{p}, t_{n+\alpha})$$

$$y_{n+1} = y_{n} + h((1 - \frac{1}{2\alpha})\dot{y}_{n} + \frac{1}{2\alpha}\dot{y}_{n+\alpha}^{p}$$

$$\dot{y}_{n+1} = f(y_{n+1}, t_{n+1})$$

When  $\alpha$  = 1 the above method is sometimes known as Heun's method or the Euler-trapezoidal method. The other second order Runge Kutta method tested in section 5 is obtained when  $\alpha$  = 0.5 and is sometimes known as the Improved Polygon method. These methods are quite easy to implement. Both require two derivative evaluations per step, but provide greater accuracy than Euler, since they are second order. James  $^3$  gives the third order Runge Kutta also used in section 5. The classical fourth order Runge Kutta, which is also used, is described by Gear  $^1$ .

Multistep integration methods are not as convenient to use as single step methods, because at the start of a simulation run they have to be provided with past values of variables. These values can be estimated before the run and provided as initial conditions, although this normally means estimating a new set for each step size used. Alternatively a single step method can be used to provide the first few values to start the multistep method, but this has the disadvantage of requiring two separate integration methods. The predictor correctors such as the Adams Moulton require twice as many derivative evaluations per step as the predictor only methods such as the Adams Bashforth methods, but should provide better stability.

A comparison of relative computation time per step for various methods is given by Benyon<sup>2</sup>, and although the arithmetic calculation times performed by the GIMINI software are not the same, the overall relationships appear roughly similar.

The use of an integration method with a variable step size could mean that less steps would be needed to attain a given accuracy, because the smaller step sizes would only need to be used for fast changing parts of the solution. Variable step size is difficult and not very satisfactory when used with predictor correctors, as pointed out by Martens<sup>4</sup>. Each time the step size is changed, the predictor corrector has to be restarted using a single step method. The Runge Kutta Merson fourth order method can generate an estimate of the integration error, sometimes called truncation error, for each step and so control the step size. For other methods, a possible way of generating an estimate of the error size is the

Richardson method explained by James<sup>3</sup>. In this method two solutions are generated at each step, one forthe full step size and the other using two half steps. The two values are then used to produce an error estimate. One disadvantage of using a variable step method apart from its complexity is that it is difficult to produce regular outputs of results.

Smith<sup>5</sup> describes the use of compensation to increase the accuracy of low order integrators. For a known result the compensation could be adjusted to reduce the error, but when the result is not known in advance, Smith does describe a variable phase integrator which applies the compensation as it proceeds.

#### 2. SIMULATION

#### 2.1 Continous Simulation

The simulation of continuous systems can be described as experimenting with mathematical models of a system instead of the system itself. Simulation can therefore be used both to predict the behaviour of a system and to aid the development of better system models. A continuous simulation problem generally involves the solution of a set of differential equations from initial conditions, and both analogue and digital methods can be used to perform these simulations.

When using an analogue computer an electronic circuit analogue of the required system is constructed from individual component circuit blocks. Parameters and initial conditions are set by potentiometers and the output is either on a Cathode Ray Oscilloscope (CRO) or x-y plotter. Analogue computers are fast, and the essential parallelism of their circuits means that their speed is more or less independent of the problem size, but they have a limited accuracy due to their components (0.01 to 0.05%<sup>6</sup>), and such high accuracy components are very expensive.

Simulation using a digital computer involves dividing the continuous solution into small discrete steps and using the values from the preceding steps to estimate the result of the present step. Digital simulation can be performed to a very high accuracy using a general purpose digital computer, however since each equation of a parallel system has to be evaluated sequentially the speed of operation suffers. Hybrid computers have been developed which combine the speed of the analogue computer with the ease

of setting up of the digital computer, but they are very expensive and the close interaction between the user and the analogue computer is normally lost.

Analogue computer problems have to be scaled because of the limited analogue voltage range. Digital computers do not require scaling if floating point arithmetic is used, but do if the faster fixed point arithmetic is used. Since the user can manually alter the values of the parameters and initial conditions of an analogue solution and immediately see their effect, the user can obtain an insight or 'feel' for the simulation problem. Most hybrid computers and batch processing digital computers lose this benefit.

Programs run on large mainframe computers are either batch processed or run interactively. Since most interactive programs only use the computers Central Processing Unit (CPU) a fraction of the time, several programs are usually time shared to provide a multi-access facility. Most medium and large minicomputers can also run in both interactive and batch modes and are cheaper but less powerful than mainframes. Small minicomputers and microcomputers are normally used interactively for just one user.

Simulations can be written in a general purpose high level computer language like FORTRAN<sup>7</sup> or BASIC<sup>8</sup>, but a low level assembly language would be considerably more difficult to use and to modify. Since most simulations have common features like integration and result output, a lot of programming time can be saved by using a simulation system which takes care of the repetitive functions. Such simulation systems fall into two categories, those which accept an explicit set of differential equations and those where the

model is entered by specifying the interconnections between functional blocks similar to those of an analogue computer. Both the equation oriented and block diagram systems can be used either interactively or in batch mode.

For a small digital system an interactive approach should be able to provide the analogue computer feel for the problem at a much lower cost than an analogue or hybrid computer. A batch processing system makes more efficient use of the computers central processing unit (CPU) than an interactive system since in the interactive mode the CPU will spend significant time waiting for the user to enter new commands. In a large computer system the CPU is an expensive part of the computer so time sharing is often used to cut this cost, but in a microcomputer system the CPU may only cost £10-£40 which is considerably less than most of the other system components. This means that the user's time is far more important than that of the CPU, therefore a microcomputer system is very suitable for interactive use with just one user.

#### 2.2 Simulation Problem Implementation

To perform a simulation task interactively on a microcomputer three main actions were required, firstly the initial model must be entered into the computer, next the model must be implemented and results produced, and finally the model can be edited prior to being run again. To implement a simulation problem either a special program can be written in a suitable general purpose language, or a more specialised simulation language or system may be used.

Using a general purpose language for each simulation problem encountered implies that the programmer must have a good knowledge of the programming language used, and also implies that a good deal of the programmers effort is wasted in rewriting almost similarly functioning sections like data input and result output. level languages offer the best approach for writing a special program as assembly languages require considerably more programming effort and greatly obscure the relationship between the program and the simulation problem. The high level program must be translated into the actions of the computer required to implement the specified task, and this may be performed either by a compiler or an interpreter. For interactive use on a small computer such as a microcomputer the interpreter approach is simpler, since it requires a smaller program than a compiler and does not need to store a machine code version of the program. On the other hand the compiler's machine code program is considerably faster in execution than the interpreter. While the high level compilers implemented on microcomputers are considerably more limited than those available on larger computers, they still require relatively sophisticated operating systems with secondary storage.

Several high level languages are available for microcomputer use, with BASIC being the most common. Most microcomputers have interpreted BASIC like the SWTP  $6800^8$  although some BASIC compilers have been produced. Various compilers using versions of IBM's PL/1 language have also been produced like PL/M $^9$  by Intel and the PLZ $^{10}$  family of languages produced by Zilog. The newer Pascal language  $^{11,12,13}$  is gaining in popularity and by using the

intermediate P-code, both compilers and interpreters have been produced <sup>14</sup>, and even a new microcomputer has been designed to operate on the P-code directly <sup>15</sup>.

Korn<sup>16</sup> proposed a block diagram language in which a sequence of prewritten subroutines are called to perform any required task. The inputs and outputs of each subroutine called would be specified as parameters with the program stored in an array as threaded code. Threaded code means that the program is represented by the addresses of the subroutines and variables and is implemented by indexed subroutine jumps and indexed data operations respectively. The language Forth 17 uses indirect threaded code with a dictionary of subroutine blocks to implement the program. unusual in that postfix or reverse Polish notation is used and that the user has full control of the stack. The threaded code operations refer to entries in the dictionary which contains the addresses and other details of the subroutines, this dictionary structure enables the programmer to define new operations using a combination of existing ones, and even other user defined operations. Forth is a very compact language, and with its reverse Polish notation and explicit processor operations including the use of assembly language it is obviously designed more for system use than general purpose programming.

Of the available high level languages BASIC is probably about the easiest to learn, but the more structured languages like Pascal allow the programmer to produce a program which is more closely related to the simulation problem and thus more comprehensible. The more complicated languages like FORTRAN<sup>7</sup> and the PL/1 variants

are more difficult to learn and are written to use quite a large microcomputer system with secondary storage. The reverse Polish notation and explicit stack manipulation could make Forth difficult to use for an inexperienced programmer. The main problem with using high level languages is that much of the programming effort is used in producing repeatedly used sections like result tabulation and integration. The presence of these sections in the users program also tends to obscure the simulation model. One solution to these problems could be to have prewritten sections or subroutines which perform the often used functions, but most functions like output and Runge Kutta integration cannot be performed by just one Therefore if simplified output and integration subroutine call. instructions are to be used, then the simulation program itself must be running under the control of another program which keeps track of the progress of the simulation problem and performs the Such a control actions required by the simplified instructions. Korn<sup>6</sup> program would form the basis of a simulation system. describes a package of FORTRAN subroutines which can be used on any computer with a suitable FORTRAN IV compiler. The model equations are written as a FORTRAN subroutine on punched cards and combined, with the required subroutines from the package, to form the simulation program which is then run in batch mode.

Since historically, digital simulation developed after analogue computer simulation was well established, many block diagram simulation systems have been written for mainframe computers which were designed to ape an analogue computer. DAS 18 and KALDAS 19 are examples of such systems which have attempted to produce a

digital version of the analogue computer, but since they are batch processed the analogue computer interaction or 'feel' is lost. PACTOLUS<sup>20</sup> is a similar block diagram system, but which can be operated interactively. These block diagram systems require that the mathematical models to be used are first rewritten as an appropriate block diagram, using analogue type components, before entering into the simulation system. The MARSYAS system<sup>21</sup> is a block diagram system designed for aerospace simulation on a large computer installation. The MARSYAS blocks can however be considerably more complicated than simple analogue computer blocks and can include high order transfer functions and complete subsystems which have been previously defined as block diagrams.

Equation oriented systems allow the simulation model to be entered algebraically in the form of differential equations. Most equation oriented systems conform roughly to the conventions of the Society for Computer Simulation's CSSL Committee  $^{22}$ . One such system is DARE P $^6$  which is an equation oriented system designed for batch processing and written in FORTRAN IV for portability.

Interactive operation of large computers is very expensive, so some systems have been written for minicomputers of various sizes. The DARE/ELEVEN system<sup>6</sup>, which was developed from earlier DARE systems at the University of Arizona to run interactively on a PDP-11/40 minicomputer, is unusual because it provides an equation oriented language together with a fast block diagram language. DARE/ELEVEN can accept an equation oriented CSSL type program which can be entered using an interactive editor. The system translates the simulation program into a FORTRAN program which is then compiled by the computers standard FORTRAN compiler to

produce an object code module. This module is then linked together with any required library routines to form the object program which is then run to produce the required results. The complete process is run under the control of the standard operating system on a PDP-11/40 with 28K of memory and a fast magnetic disc. memory is not big enough to hold all the programs required, overlay Memory overlay is the process of overwriting techniques are used. selected parts of the computers memory with new programs. The previous programs are lost, but copies of all the programs are held on the magnetic disc. The DARE/ELEVEN block diagram language uses fixed point arithmetic for speed, and can even be used in different parts of the same simulation as the equation oriented language. The block diagram is entered by specifying the required blocks together with their inputs and outputs. The DARE/ELEVEN system then orders the blocks in procedural order and uses the computers own macro assembler to produce the object code.

Micro-DARE BASIC/RT 11<sup>23</sup> is a block structured simulation language similar to that used in DARE/ELEVEN which can be used on a PDP-11 or LSI-11 with at least 16K of memory and the RT 11 operating system, but needs no system disc. Micro DARE BASIC/RT 11 uses a dialect of BASIC for initialisation and control of simulation runs, and a block diagram language with fixed point arithmetic for the integration loop. The block diagram language is compiled into a threaded subroutine structure and the BASIC statements are semicompiled on entry to compress them, with an expansion routine provided to facilitate editing.

$ISL-8^{24,25}$  is a block diagram language which runs on a PDP-8

minicomputer with as little as 4K words of memory. The fixed point arithmetic used in ISL-8 requires time and amplitude scaling. Newer versions of  ${\rm ISL}^{26}$  can be used with other minicomputers and for hybrid simulations.

BEDSOCS<sup>27</sup> is a CSSL specification equation language which uses BASIC instead of FORTRAN as its procedural language. By using interpreted BASIC the system is designed to run on a Hewlett-Packard 2100A minicomputer with 8K of core store.

Hay<sup>28</sup> describes three interactive simulation system implementations on a PDP-8 minicomputer with 28K words of fast memory, a magnetic disc and a floating point processor. All three implementations provide equation oriented simulation languages. One scheme makes extensive use of the PDP-8 system programs like editor, monitor and FORTRAN compiler. The simulation program is translated into FORTRAN statements to be compiled by the FORTRAN compiler into the required object code. The PDP-8 batch processor, under the control of a command file is used to provide the interactive facilities, and extensive overlaying is required. The other two approaches use self contained programs, one converts the simulation program into an intermediate code which is interpreted at run time, and the other has a further stage of compilation to produce a More recent versions of the interpreter machine code program. implementation called ISIS<sup>29,30</sup> are written in FORTRAN and can be used on a variety of computers. ISIS conforms to the CSSL specification but does not translate the simulation program into a procedural language like FORTRAN as most CSSL systems do, instead it checks and semicompiles each line as soon as it has been

entered. The semicompiled form is stored for later translation into its interpreter instruction code at the start of a run.

SIMEX<sup>31</sup> is an equation oriented language which was written for a PDP-9 minicomputer with 24K words of core memory and high speed bulk storage. Instead of compiling the complete simulation program just before it is run as most equation oriented systems do, SIMEX compiles each line separately as it is entered. The system provides for interactive editing by storing the source code on the bulk storage medium. To obtain a fast calculation speed fixed point arithmetic is used, and by restricting the time steps to powers of two, and using Euler integration, the system can perform the integration calculations using just shifts and additions. An automatic scaling system is implemented to relieve some of the burden of scaling the simulation problem, and this uses scale factors of powers of two so that only shifts are needed.

For a user inexperienced in computer programming, writing simulation programs in a purely high level language has two main The first is the need to learn the particular high drawbacks. level language used, and the second is the need to know the appropriate programming techniques required for result output and interactive control of the simulation. Using a simulation system relieves the second and most important drawback. Of the systems described only DARE/ELEVEN, BEDSOCS, ISIS and SIMEX provide high level type languages designed for simulation work. DARE/ELEVEN and ISIS provide FORTRAN features for more advanced simulation programs and BEDSOCS provides BASIC. Only BEDSOCS and SIMEX are core resident programs as the others require overlay techniques,

but SIMEX does require fast secondary storage for source programs.

Block diagram language systems are easier to implement on a small computer since the code to be executed is already written as blocks or subroutines and only the interconnections need be specified. This also means that no source programs need be stored for the execution phase. Micro-DARE/RT11 and ISL-8 provide block diagram languages which do not require fast secondary storage, and Micro-DARE/RT11 also provides BASIC statements for initialisation and control of simulation runs.

A problem with block diagram languages is that users unfamiliar with analogue computing have to learn to convert their problems from the familiar mathematical expressions to an unfamiliar block diagram representation of the problem. Therefore a simple microprocessor based system would preferably be of the equation oriented type.

The previously mentioned equation oriented systems all require the simulation problem defined as a program using the systems special language usually based on a high level programming language. This means that not only does the particular special language used have to be learnt, but the system has to store a copy of the source program for future interactive editing. If instead of this a highly interactive dialogue could be maintained between the computer and the user, then the simulation system could at least partly explain how to enter the required information. Auslander describes two implementations of a structured data simulation system. Both run on a PDP-7 minicomputer with 8K words of memory and instead of writing a special program the simulation model information is entered

using a series of commands. The two implementations differ in the data structure used to store the models, but both require that the model equations are entered in a very sty-lised format with nonlinear functions implemented as machine code subroutines. One implementation uses a linked data block structure with directories used to reference blocks of information about state variables. As well as the names and values of each variable, the blocks also contain a set of pointers to other variables which make up the stored equation. The other implementation uses a node incidence matrix to describe the topology of a directed linear graph. Each equation stored in this system can be represented by a simple directional graph, and the node incidence matrix contains the binary information about the presence or absence of each possible individual branch in the graph.

The command structure used by Auslander does not offer much dialogue so the user has to remember what information has to be entered. The entry format for the equations is awkward and involves extra user effort, with the resulting equations being rather restricted.

It was therefore decided to implement a microprocessor based system which was equation oriented and had the simulation problem held as recoverable data. The system should also have as much interactive dialogue as possible to guide the user in using the system.

# 2.3 Microcomputer Considerations

#### 2.3.1 Man-Machine Interface

The methods of communication which the user has with the simulation system are very important since the system has to be

easy to use for people with little experience of computers. The entry of data and control instructions should be straightforward, and the microcomputer should be able to output helpful guidance as well as results. An alphanumeric keyboard together with an alphanumeric printer or Visual Display Unit (VDU) is the most common and versatile method used to provide interactive control of a computer. Other input and output devices can provide very useful extra facilities, but they are not absolutely necessary. So that the minimum microcomputer system implementation can be usefully used, the simulation system program was designed so that the alphanumeric input and output devices could provide data input, result output and simulation control. Alternative data input and result output devices were also catered for, but the simulation system can still be used if they are not available.

Difficulties occuring in the communication between user and microcomputer program are caused by the organisation of the interactive dialogue and not by the hardware involved. The present simulation system uses a teleprinter as the main user interface. While the slow speed of 10 characters per second is fine for user input, it greatly limits the amount of text which can be printed out without the user becoming impatient. While an inexperienced user will tolerate lengthy printouts which provide helpful guidance, these printouts will become annoying and timewasting to a user who already knows how to operate the system. A way round this would be to switch between short rather cryptic dialogue and expanded explanatory dialogue depending on the users preference. Useful as this method could be, the memory limit in the present system prohibits its use.

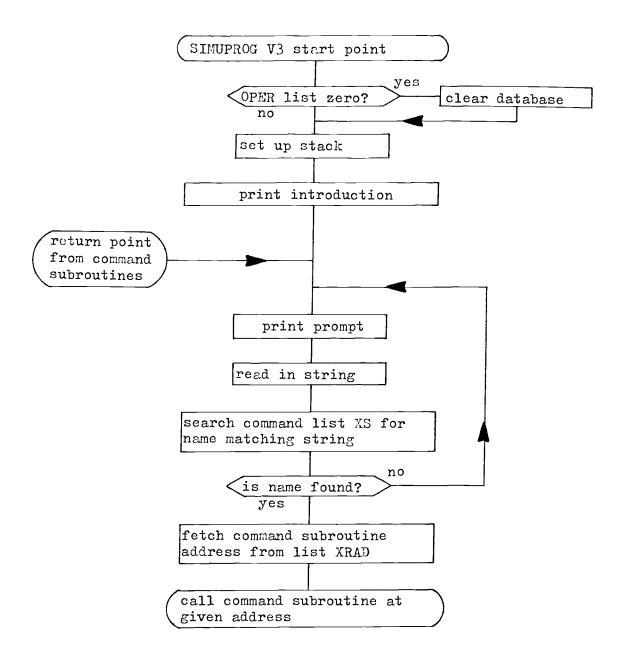

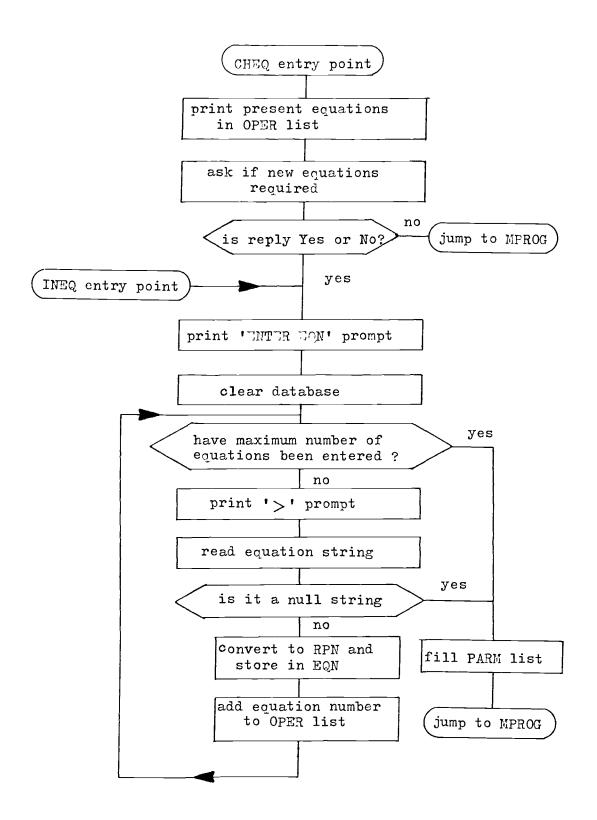

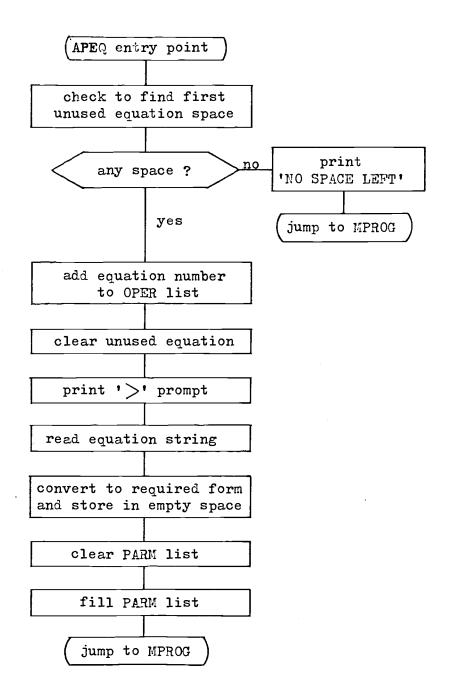

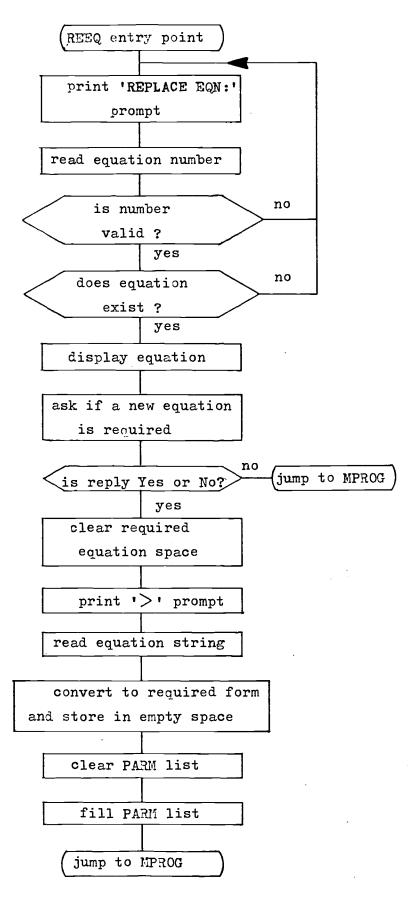

Therefore a compromise was reached for the present implementation so that only one set of dialogue was needed. The function of the simulation system was broken down into a selection of commands, the present version of the program has 20 and each consists of a name or a mnemonic up to 4 letters long. When a command has been activated, the required function is implemented using a controlled dialogue between the user and the program. The simulation model and control information is stored in a unified database and each command has independent access to the appropriate parts of the database. Several formats for the controlled dialogue were tried for different commands.

The use of a higher speed VDU for the text output would remove the speed limit from the size of the program messages, and would also allow alternative dialogue formats to be used. An example of this would be the use of a menu of the command names, a brief explanation of each command could also be included.

#### 2.3.2 Arithmetic

For general purpose use, the simulation system should be able to accept a wide range of input values so that the user does not need to spend extra time and effort scaling the simulation problem. This wide dynamic range must be combined with sufficient accuracy to ensure that the cumulative errors remain within the required limits, even after a large number of steps.

Integer arithmetic is the simplest to implement, but very long integers would be needed to cope with the wide dynamic range needed and this would require a large amount of storage, most of which would

be wasted since the great majority of the values would contain either leading zero's or else more bits of information than the initial accuracy of the variables could justify. Scaling techniques can be used to reduce the size of the integers required, Gakhal<sup>33</sup> describes some scaling methods for some discrete fourier transforms. However for the simulation system, the variety of types of equations that can enter means that an automatic scaling system would be very complex and difficult to implement. Errors in solving differential equations can be reduced by increasing the accuracy of the numerical integration calculations. This can be done by either holding the state variables with a higher precision, or else using residue retention as described by Baker<sup>34</sup>, however this would complicate the simulation system since the program would have to detect and keep track of variables being integrated.

Floating point arithmetic can provide both a wide dynamic range and sufficient accuracy for the simulation system. Floating point arithmetic software is slower and more complex than integer software, but is no more difficult to use once the software has been written. An alternative number system suggested by Edgar 35,36 called FOCUS uses a logarithmic representation which is claimed to be significantly faster than floating point for the same accuracy. While multiplication and division are easy in FOCUS, addition and subtaction are slower and more complex. The input and output conversion is also more complex and FOCUS would probably require more memory than floating point. For real time systems where speed is at a premium and calculation errors cease to become significant after

a relatively few number of steps, the FOCUS number system with input and output conversion hardware could be useful.

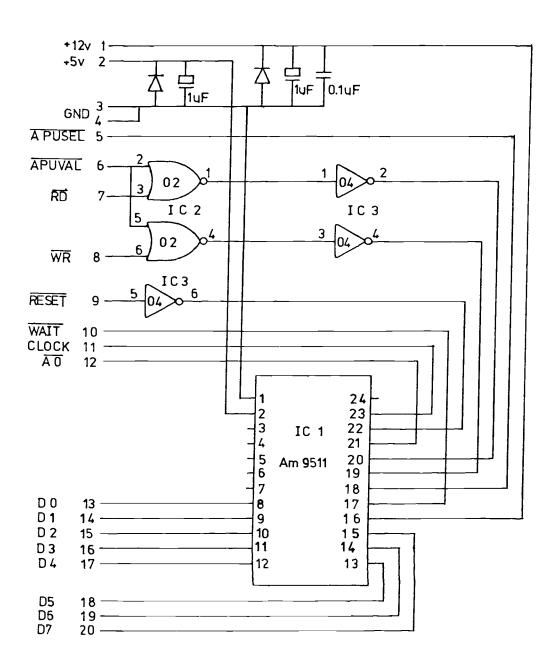

Arithmetic hardware can both reduce the amount of software and speed up the arithmetic operations. Integer multiplication and division can be used to speed up both integer and floating point arithmetic, and can use either Read Only Memories or digital The recent introduction of single chip floating point hardware. processors means that floating point arithmetic is much easier to The National Semiconductor 57109<sup>37</sup> can provide BCD implement. floating point arithmetic together with trigometric, logarithmic, and exponential functions. This device however uses PMOS technology and is actually significantly slower than the floating point software used with the CP 1600 microprocessor. The Advanced Micro Devices AM9511 arithmetic processing unit was only available at the end of this project, and can provide 16 and 32 bit integer arithmetic as well as floating point arithmetic including trigonometric, logarithmic and exponential functions. The Am9511 uses binary floating point and is faster than the CP 1600 binary floating point software which was actually used for the simulation system. The 32 bit floating point was felt to be the optimum for the simulation system as 16 bit floating point could not provide the accuracy and dynamic range needed, and both 48 and 64 bit floating point would have taken more storage and would also have slowed the simulation system down unnecessarily.

# 2.3.3 Languages

The choice of language used to write the simulation system program depended not only on the need to produce an efficient and

comprehensible program, but also depended on the physical limitations of the microcomputer system itself. While small programs can usefully be written directly in machine code, it is impractical to write and debug a large complex program without either assembly or high level language program aids.

Assembly language provides mnemonic representation of the microprocessors machine code instructions together with labels for program jumps and variable storage. Programs written in assembly language are much easier to understand than pure machine code because the mnemonic labels and instructions, together with the comment text, allow the program structure to be discerned more clearly. The assembly language program is translated into a machine code program which is then stored to be run later. Even though each assembly statement directly represents one machine code instruction, they cannot be translated in isolation because of references to labels appearing The assembler overcomes this by making two later in the program. or more passes through the program, the first pass builds up a table of the addresses of the labels used in the program and subsequent passes are used to generate the required machine code program.

High level languages are easier to understand than assembly language because each high level statement is the equivalent of several machine code instructions, and can therefore be designed to perform a function much closer to the programmers concept of the basic operations from which the program is constructed. The high level program can be translated into machine code by a compiler which, although more complex, operates in a similar manner to the assembler. An alternative method of implementing a high level

language is to use an interpreter. The interpreter does not produce machine code, but instead it examines each line of the program as it is being run and performs the same actions as the user's program would have if it had been compiled. An interpreted program is therefore considerably slower than a compiled one, but the interpreter does have the advantages that it is easier to use and does not need to store a machine code program. Therefore in programs involving lengthy loops, such as simulation programs, the calculation time taken by an interpreter could be at least an order of magnitude greater than a previously compiled program would take.

Assemblers and high level language compilers can be run either on the microcomputer itself or on another computer altogether. To run an assembler or compiler on the microcomputer itself requires secondary storage for the source and object programs since it would be prohibitive to hold them in main memory. If a cross-assembler or cross-compiler is run on another computer, the microcomputer only needs enough memory for the resulting machine code simulation system Compilers are more complex and require more memory than program. assemblers. At the start of this project very few high level languages were available for microprocessors, and even these required at least a floppy disc drive for secondary storage. By exploiting fully the architecture of the microprocessor, a program written in assembly language should be smaller and faster than the alternative high level program, but the programming effort needed to produce the assembly language program would be much greater. A way to combine the two approaches could be to use a high level language which allowed critical program segments to be written in assembly language,

however there still remains the problem of integrating the actions of the high and low level sections. The CP 1600 superassembly language, finally used to write the simulation system program, overcomes this problem by providing high level programming enhancements to an otherwise standard assembly language. Although the superassembly language is not as sophisticated as a true high level language, it makes it much easier to make full use of the architecture of the microprocessor with little more requirements than a standard assembler.

# 2.4 Microcomputer System Implementation

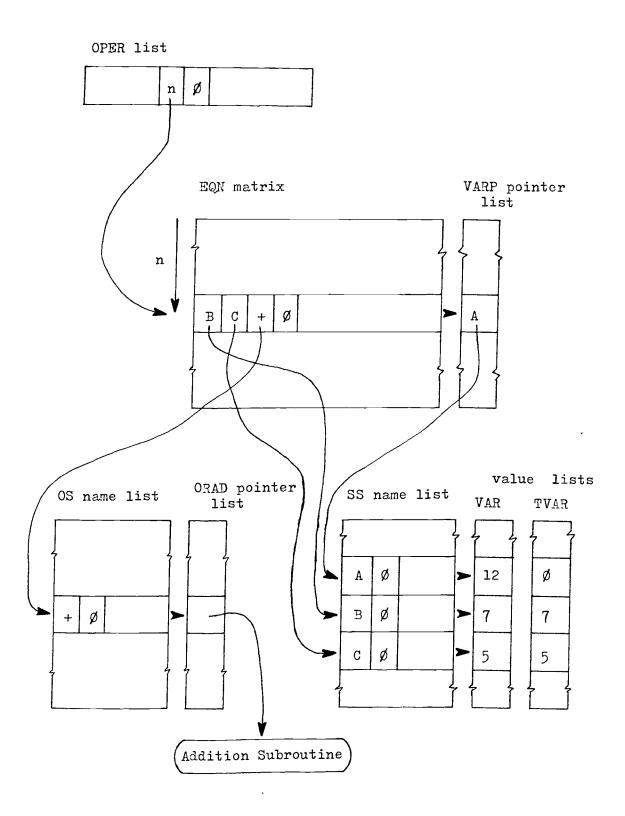

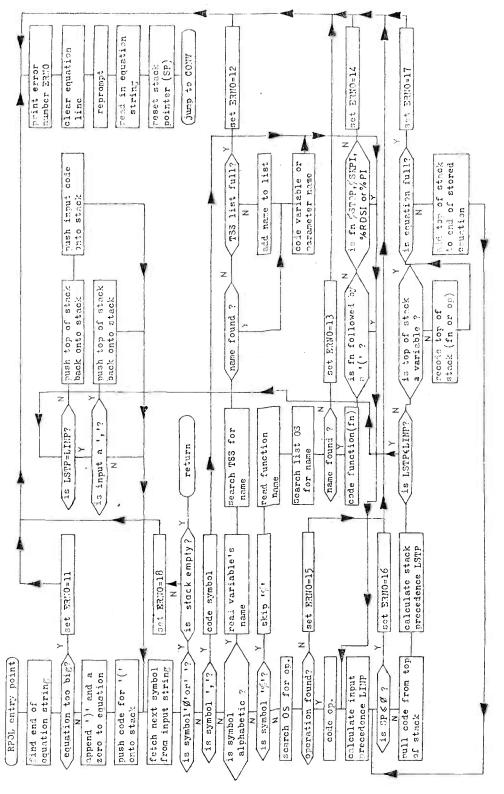

The limited memory size and relatively slow speed of the microprocessor based system envisaged means that the simulation model equations need to be stored in as compact a form as possible, without sacrificing execution speed. Since the equations which will be entered into the system do not have a fixed format and can make use of several layers of parenthesis, an equally flexible system is required to store the equations so that they form a suitable instruction stream for run time calculations. describes the main types of instruction streams which can be used. Polish notation is probably the most compact form of instruction stream, and since the stack operation times, using the microprocessor stack pointer, are very much less than floating point calculation times, there is very little loss in execution speed. The trailing operator or reverse Polish notation (RPN) form of instruction stream is the easiest to evaluate, and so was chosen for equation s. rage. To compress the equation further, the RPN instruction

stream was coded so that each entry consisted of a single 16 bit Equations entered into the simulation system can be word. represented as (variable)=(expression) where the '=' represents an assignment operation not an equality. An expression is coded using positive integers to represent variables whose values are to be pushed onto the stack, and negative integers to represent arithmetic operators and functions which operate on the stack. A positive integer refers to the position of the required variable in a list which, as well as containing the value of the variable, also contains its name so that stored equations can be printed The negative integer refers to the position of the starting out. address of the required arithmetic subroutine in a list which also contains the operator symbol or function name needed to print out the stored equation. The RPN expression is terminated by a zero entry and the variable to which the value of the expression, now held in the stack, is to be assigned is found in a separate list. The reason for this is twofold, firstly it simplifies the evaluation of the expression since it eliminates the need to enter the address of the unknown variable in the stored instruction stream, and secondly it allows for prewritten system functions and user entered functions to be implemented, in future versions, in the same way as model equations.

Since the entered equations are not of fixed length, the zero which terminates their equivalent stored instruction stream effectively terminates a variable length list. All the data specifying the simulation models is effectively held in lists, and this provides an effective method for storing variable amounts of data without

keeping track of separate pointers and counters. The set of model equations are themselves held in a list, in the order they were To increase flexibility of operation, the order of the list of equations does not determine the order of operation, and instead the order of operation is specified by a separate list. Not only does the operation list mean that the order of operation can easily be changed, but equations can be dropped from the list or even appear several times without disturbing the original set of The actual list of equations is held in a two equations. dimensional array or matrix. Alternative storage organisations could be implemented to make use of the space otherwise wasted by equations shorter than the maximum length. Storing the equations as linked lists could make use of the space but since the only replacement operations required would involve whole equations, the extra pointers required to implement linked lists would make the system very inefficient. The individual equations could also be stored as segments in a single data space with an array of pointers indicating the start of each equation. This system would make better use of the memory space than the matrix method, and should The only main drawback would be that replacement be just as fast. of individual equations would be more difficult. The main reason that the matrix method was used was that it was easier to implement and debug, the segmented method could then be introduced later and debugging would be much easier when the rest of the program was validated.

All the information needed to run the simulation is included in the database including run time controls and output lists.

This means that the simulation run information is independent of the program and can be stored and rerun at a later date. The size of the database, and hence the maximum size of a simulation model, is limited only by the memory size of the microcomputer and can easily be adjusted to suit the available memory.

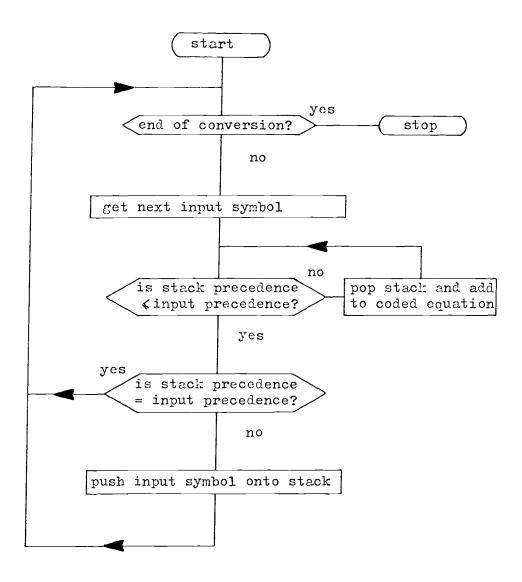

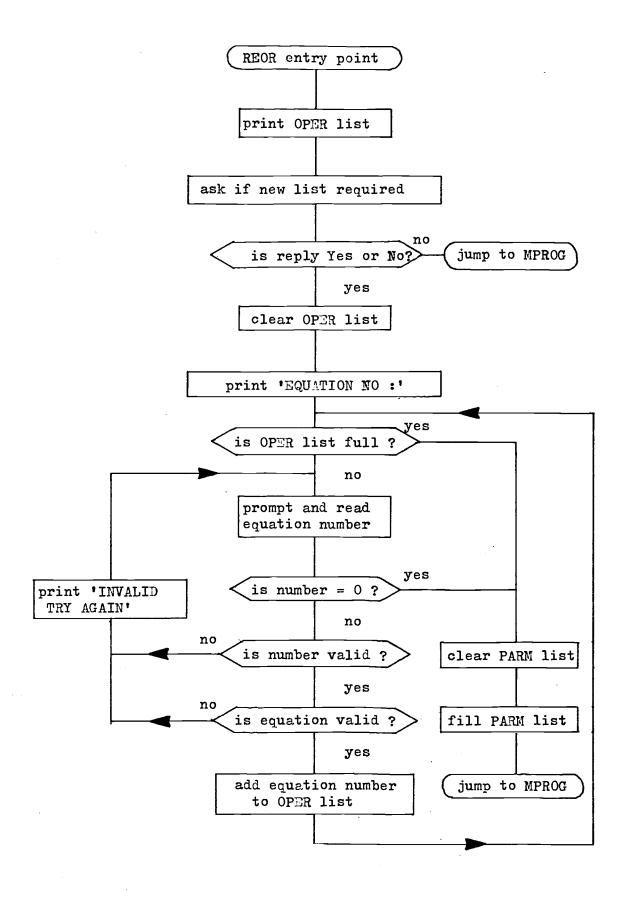

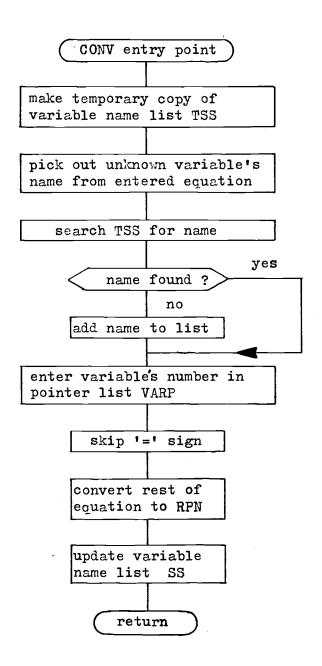

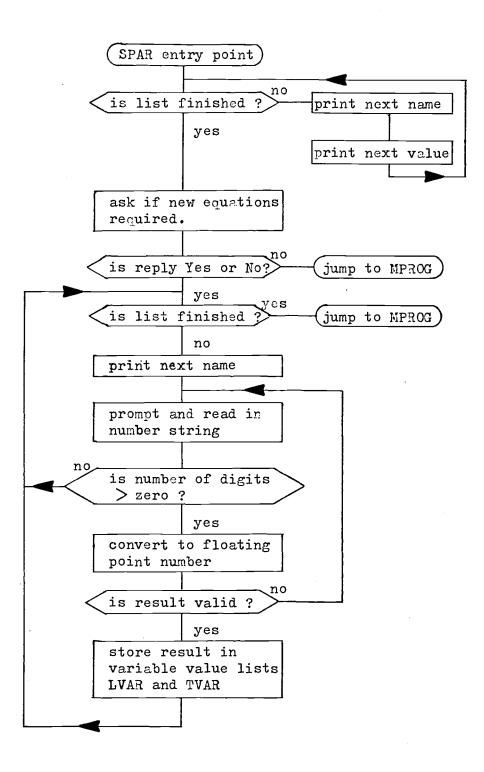

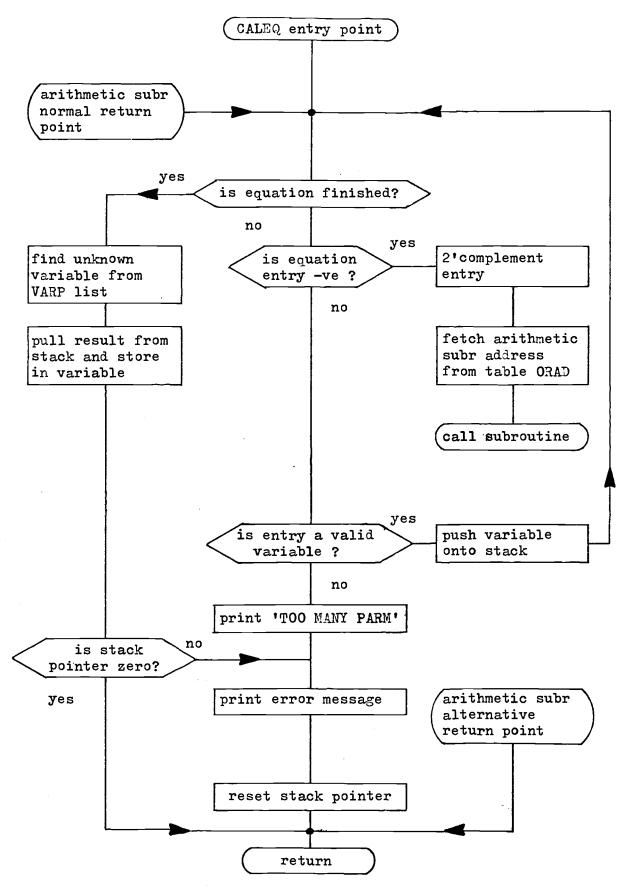

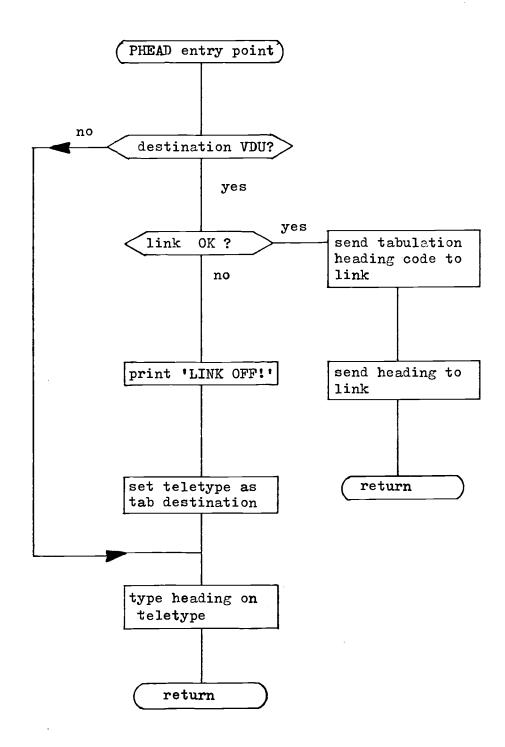

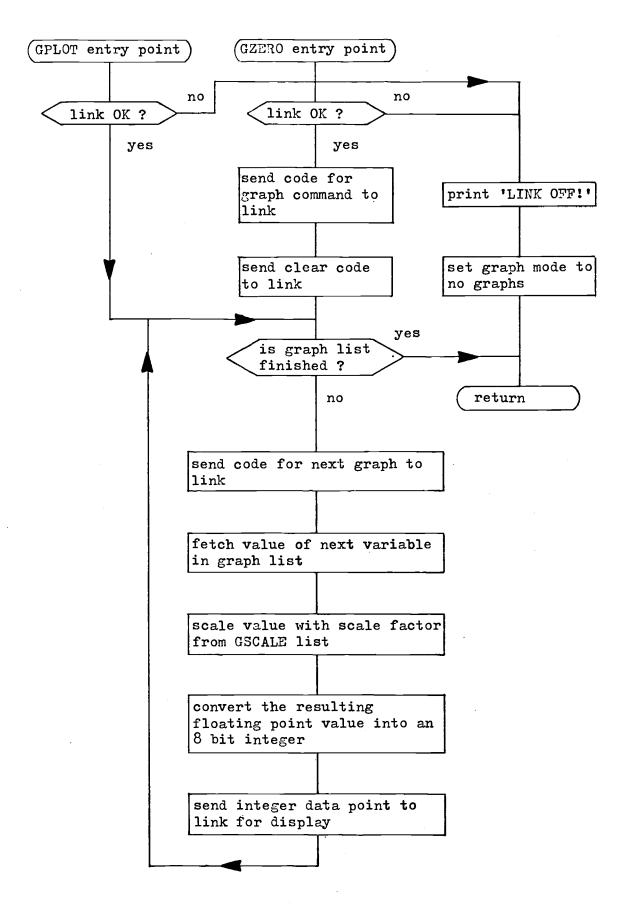

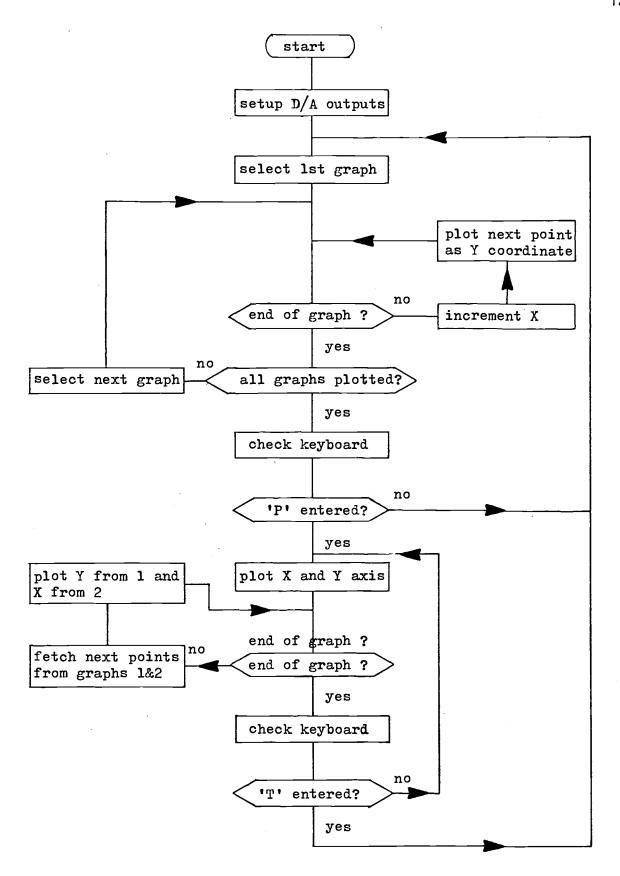

Each command used to control the simulation system is implemented as an independent subroutine so that commands can be added to or deleted from the system as required. Each command subroutine operates independently on the database although, to keep the program compact, several command subroutines may themselves make use of common Once a command has been initiated, the user is guided subroutines. through the command sequence by questions requiring yes or no answers and prompts for entering data. As well as a line editor for user entered input, the commands are designed with options so that an entry error by the user does not require too much effort to The equation entry subroutines accept equations in normal algebraic form, with parenthesis, and converts them to the required reverse Polish notation form. Some checks are also made as to the validity of the equations, and a limited error diagnosis is produced before the user is asked to enter the equation again.

It was not felt appropriate to include facilities for automatic sorting of equations or for dealing with implicit loops.

# 3. MICROCOMPUTER SYSTEM

### 3.1 System Requirements

# 3.1.1 Microprocessor

There is now a wide range of microprocessors available, with differing capabilities and designed to suit a variety of applications. Since the microprocessor performs the required calculations and controls the other system components, it is the main limiting factor determining a microcomputers capabilities. The usefulness of a particular microcomputer configuration for a given application is determined by a variety of factors. The principle factors are the speed of the microprocessor, its address range, its instruction set, the type and size of memory used, the hardware and software experience and backup available, and the hardware configuration.

The simulation program will require a considerable amount of calculation, and the programs themselves may be quite lengthy. The microprocessor should therefore be able to address sufficient memory to hold the largest program required, although the use of overlay techniques, with secondary memory, can reduce the requirement. While just about any microcomputer can perform floating point arithmetic if properly programmed, the instruction speed and the word length of the microprocessor, combined with the design of its instruction set and architecture, will determine how fast the calculations are performed.

The most suitable microprocessors are the more recent 'general purpose' 8 and 16 bit single chip microprocessors. The smaller 4 bit single chip microprocessors and microcomputers are designed

for smaller and less memory intensive systems, and their limited memory space combined with the more complicated programs required for calculation and data manipulation means that they are not suitable for the simulation system. Older general purpose microcomputers using PMOS (P-channel MOS) and the earlier NMOS (N-channel MOS) devices are slower, and most also have interfacing Other specialised microprocessors usually have disadvantages. disadvantages, bit slice microprocessors can generally achieve a far greater speed than single chip devices, but they introduce another level of complexity since the actual instruction set to be used in writing the simulation programs has first to be designed and This does not rule out their use, but it does mean that developed. the fast speed has to be balanced against the extra time, effort A possible use of bit slice machines and cost that they entail. would be in a multimicroprocessor system where they could perform a small repetative section of program at high speed. chip microcomputers have memory and input/output lines contained with the microprocessor in one integrated circuit. Those with ROM or PROM memory are designed for volume production, and even those with EPROM or only RAM usually have a limited address space and are not suitable.

Cost is a major factor in deciding on the hardware to be used, but the cost of the microprocessor itself is only a small part of the total hardware cost. Indeed when considering the development costs, unless for high volume production, the cost of the microprocessor itself is usually insignificant. The actual microprocessor used has however a large indirect effect on the costs, since it determines

the hardware needed for the system as well as the effort involved in developing the programs. The development costs can be divided into two main areas, hardware and software. Taking hardware first, the existence of compatable families of microcomputer components means that the construction of the required hardware configuration can be done without an extensive knowledge of digital hardware and computer techniques, providing that the constructor uses only the family components and that the documentation is adequate. Most. microcomputer families are incomplete, so that often components from other manufacturers and components not specifically designed for use with a particular microcomputer are needed to attain the required configuration. An alternative to building a microcomputer from scratch is to buy a commercially available microcomputer system. Most of these systems which range from simple single board computers with hexadecimal keyboards and light emitting diode (LED) displays, to sophisticated systems with a visual display unit (VDU) and magnetic disc storage, are designed for the hobbies or small business markets. The resulting high volumes of sales, especially of the single board computers, means that the finished product is very competitively priced compared to the cost of the hardware components, without even considering the development costs to build the hardware. Therefore for the development of a simulation system, the most cost effective approach would be to use an available microcomputer and extend its hardware as required. However if appreciable quantities of systems are to be produced then a microcomputer system can be designed to suit the application. Another advantage of using available microcomputer boards, apart

from not having to design and debug the hardware, is that many of them are supplied with monitor programs in ROM or EPROM. Some of the newer single board microcomputers even have BASIC interpreters in ROM. Most of these microcomputers also have libraries of software available either from the manufacturer or independent software companies.

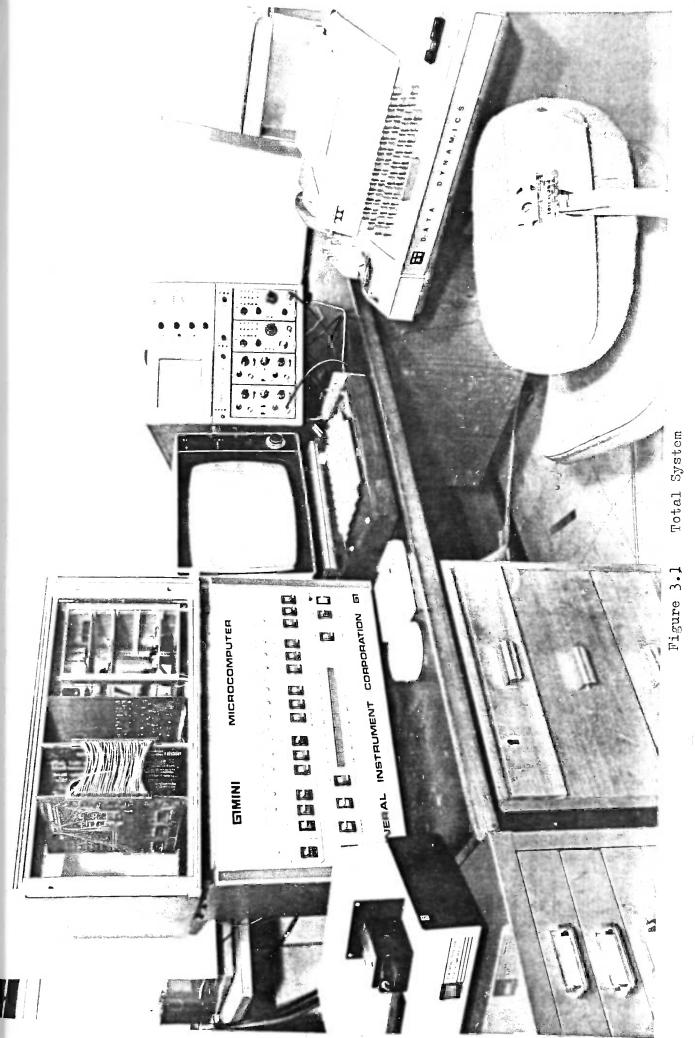

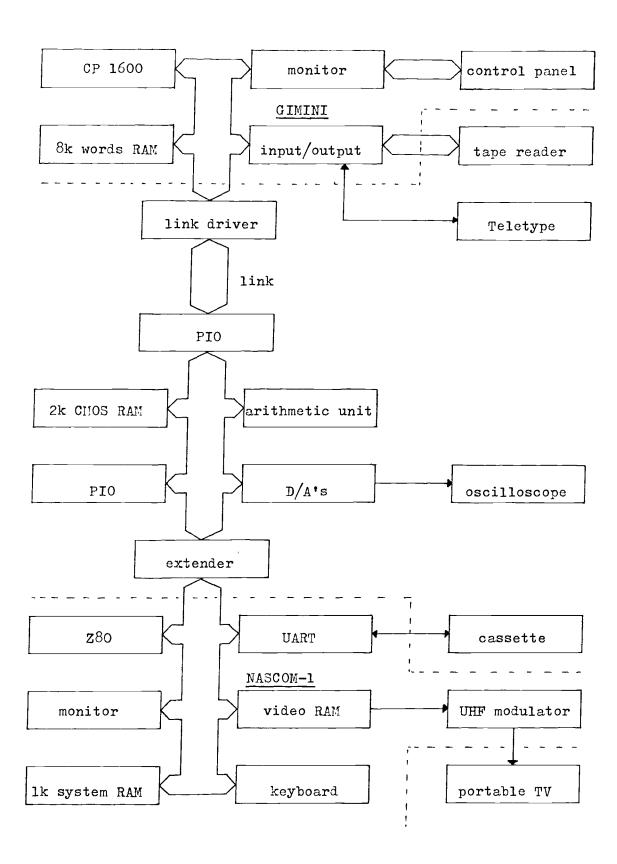

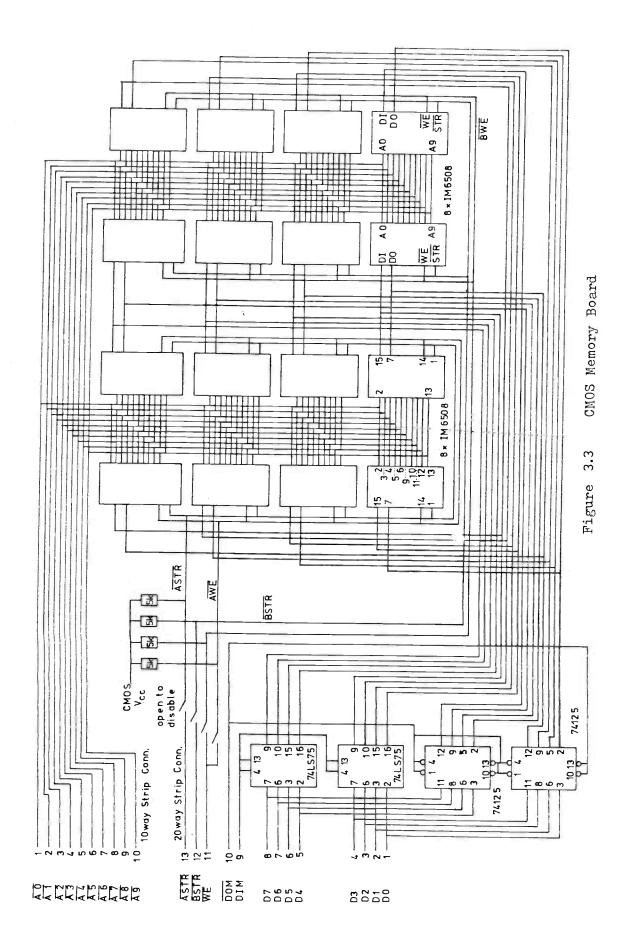

The main microcomputer used in the simulation system was the General Instrument Microelectronics CP-1600, which is a 16 bit single The CP-1600<sup>39</sup> described in more detail in chip microprocessor. section 3.2.2, was purchased as a complete GIMINI microcomputer The GIMINI microcomputer was chosen because it offered very good value for money at the time, when a limited budget was available. The GIMINI also has the advantages that all the system software was provided with the microcomputer, as well as local technical backup being available. The CP-1600 is an NMOS (N-channel MOS) single chip device and, with its regular architecture modelled on that of the PDP-11, its features were indicative of the trends in microprocessor evolution. Therefore the results and experience gained with the CP-1600 would be useful in considering future microprocessors. These trends have certainly continued with the introduction of the Z8000 and M68000 which employ very regular architectures with general purpose register sets. At the same time a smaller 8 bit microcomputer system was built to compare with the capabilities of the 16 bit machine. This microcomputer used a Motorola M6800 microprocessor and was based on their D1 development Later on in the project another small microcomputer was board. built, and this used the 8 bit Z-80. The later system was based

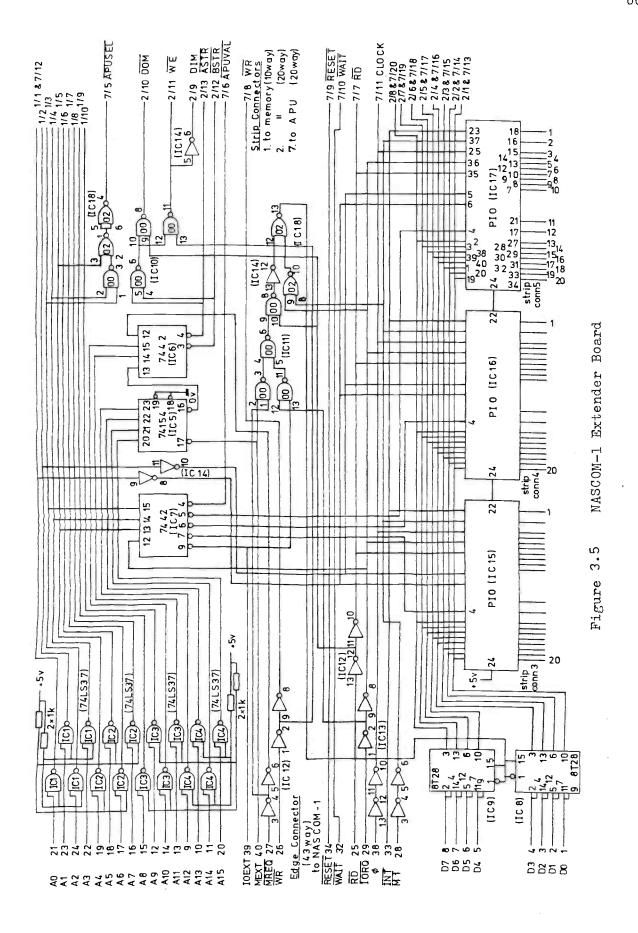

on the NASCOM-1 single board microcomputer which was designed for the hobbies market.

The tasks to be performed by a microprocessor in running a simulation system can often be reduced by extra hardware, such as a floating point processor, or additional microprocessors for input and output or parallel processing. If floating point hardware is used then a large portion of the arithmetic requirement is removed. Intelligent input/output devices and peripherals reduce the need for input and output lines from the main microprocessor as well as freeing it from most of the input and output control tasks, this results in a speeding up of the system's operation. interactive simulation system could be divided into the three main activity areas of, user interfacing, data handling for updating and using models, and calculations required for a simulation run. user interfacing the input/output mechanisms of a microprocessor can effect both the hardware complexity and the software overheads. All the currently available 8 and 16 bit microprocessors can handle the input and output requirements of the simulation system, but the interfacing hardware needs to be designed specifically for a microprocessor in order to achieve the best efficiency. handling is an important requirement for the simulation system because its structure involves lists and pointers in an address space which can be varied according to the complexity of simulation tasks to be handled. Therefore address handling with arithmetic operations on the addresses over the full address range is required together with the ability to indirectly address data from a previously calculated address for several levels. The address range required

is dependent on the size of data base used, but for the system envisaged the address size would preferably be 16 bits which is normally the maximum address space of current general purpose microprocessors. An efficient subroutine call and return structure is an advantage because the program can then easily be divided into modules which make it easier to write, change and debug, if the modules are suitably written. Floating point arithmetic is used by the simulation system, and since no present microprocessors can directly perform floating point arithmetic, then special software Recently hardware, in the form of an auxiliary has to be written. arithmetic processor, has become available for use with microprocessors, but is still relatively expensive. This processor would however relieve the microprocessor of the actual calaculations, as it would then only be required to transfer data to and from the auxiliary The simulation system implements its equations in processor. reverse Polish form, so therefore requires a separate arithmetic stack from that used to hold subroutine return addresses. This stack need not be physically separate from the normal stack as long as the program can distinguish which quantity is which. The extra computing required to disentangle arithmetic data from return addresses would however add to the size of the program as well as reducing calculation speed.

Considering first the 8 bit microprocessors suitable for a simulation system. The Intel 8080<sup>40</sup> was the first of the NMOS devices to achieve popularity, and was designed to provide software compatability with their preceding 8008. The Intel 8085<sup>41</sup> is basically an 8080 with hardware improvements including a single

supply rail and more interrupts. The Zilog Z-80<sup>42</sup> not only has software compatibility with the 8080, but also has additional registers, including two index registers, and extra instructions. The maintenance of upward compatibility from the 8008 has produced rather irregular instruction sets for the 8085 and Z-80. This together with the lack of certain instruction types, such as direct addition from memory to accumulator, means that they are more difficult to program than would otherwise be the case. The Zilog Z-80 with its much expanded instruction set and extra registers is more suitable for this application than either the 8080 or 8085.

The Motorola M6800<sup>43</sup> microprocessor has a more regular instruction set than the Z-80, including direct arithmetic operations, The 6800 also has the advantage so is therefore easier to program. of two accumulators, but does not have a set of general purpose registers like the 8085 and Z-80. The 6800, while lacking some of the Z-80's sophisticated instructions, has the ability to perform some operations directly on memory without requiring the use of the registers and this can often offset or even outweight the Z-80's extra registers. The Z-80 in common with the 8085 has separate memory and input/output buses, whereas the 6800 has a combined bus. This means that the 6800 performs input/ouput operations in an identical fashion to memory references, thus allowing the use of it's direct memroy operations. The 8085 does have some input/output devices designed to operate as memory, and the only disadvantage of this method is that, especially with partial address decoding, the maximum memory size is reduced, but with the smallish simulation systems envisaged this would not matter.

The MOS Technology 6502<sup>44</sup> microprocessor has a very similar instruction set to the 6800, but has only one accumulator together with extra addressing modes. Whereas the 6800, Z-80 and 8080 originally became popular through being provided as chip sets and sophisticated development systems, the 6502 has become well known because of it's use in built up microcomputers like the PET and the Superboard.

The Fairchild F8<sup>45</sup> seems to be designed primarily for control and other low memory requirement applications, as the lack of an on chip program counter complicates it's use in memory intensive situations. Although the 6800, Z-80, 6502, 8080 and 8085 are the most popular 8 bit microcomputers a variety of others are available. Some of these are slower like the Signetics 2650<sup>46</sup> and the General Instrument Microelectronics LP8000 whereas others have more limited instruction sets like National's SC/MP. This does not preclude their use but they may incur speed and programming penalties. RCA's COSMAC<sup>47</sup> microprocessor is unusual in that it's CMOS technology means a low power requirement, and it also has an unusual architecture with a set of sixteen 16 bit registers any one of which can be defined as a program counter and any other as a data pointer.

Some of the newer single chip microcomputers are being designed to cope with memory intensive applications, and although most are designed for high volume and use mask programmed ROM, some are also available as prototype versions with either EPROM or no ROM at all. If they are based on an existing microprocessor then there is unlikely to be any advantage.

Microprocessors like the Z-80 have some limited 16 bit data

handling capabilities which are designed primarily for address calculations. The Motorola 6809 is an attempt to bridge the gap between 8 and 16 bit microcomputers. The 6809<sup>48</sup> has the same architecture as the 6800 and shares its support devices, but has an extra index register and stack pointer together with more addressing modes and 16 bit arithmetic including multiplication.

Sixteen bit single chip microprocessors, because of their greater internal complexity, are more difficult to produce and consequentially have been slower to appear than the 8 bit machines. The General Instrument CP-1600 previously mentioned is modelled on the PDP-11 minicomputer but is not software compatable. The existence of large amounts of software written for minicomputers, and the increasing competition from the microprocessors produced by the semiconductor companies, has induced the minicomputer manufacturers to produce their own microprocessors which are software compatable with their minicomputers. The Texas Instruments  $9900^{49}$ , which has the same instruction set as their 990 minicomputer, has an unusual memory to memory architecture with a set of working registers being maintained in RAM memroy instead of in the processor itself. This means that interrupts can be handled very quickly by moving to a new section of memory, but has the disadvantage that computation speed is dependent on the speed of the memory which is usually slower than internal registers. Digital Equipment Corporations's LSI-11 is not a single chip microprocessor but a multiple chip set which can use a lot of the software produced for the PDP-11. Intersil  $IM6100^{50}$  is a CMOS microprocessor with a 12 bit word length and the instruction set of the PDP-8 minicomputer. This means that

PDP-8 software can be run on the IM6100, but the programmer is limited to the PDP-8's rather primitive instruction set and The instruction set of the Data General Nova architecture. minicomputer is used for their own Micro Nova as well as Fairchilds  $9400^{51}$  microprocessor. The Nova, although not as well known in this country as the PDP-11, also has a large software base. The use of an existing minicomputer instruction set limits the architecture and features which can be added to a new microprocessor, and since established minicomputers generally were designed to be implemented in either discrete components or small scale integrated circuits they are unlikely to make the most efficient use of current large scale integration technology. Most semicondcutor manufacturers who are not also in the minicomputer business, have opted to design their own architectures and instruction sets. Motorola and Zilog have made a complete break with their previous 8 bit microcomputers in attempts to produce architectures which will serve them for a future series of upward and downward compatable microprocessors.

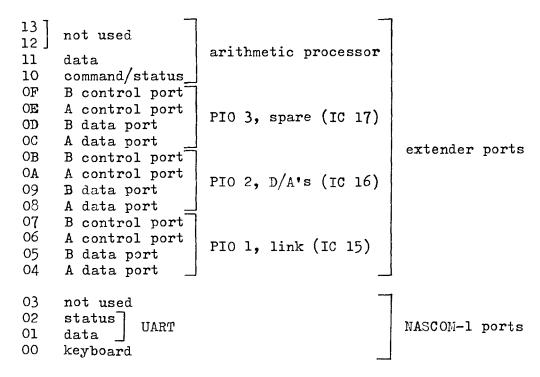

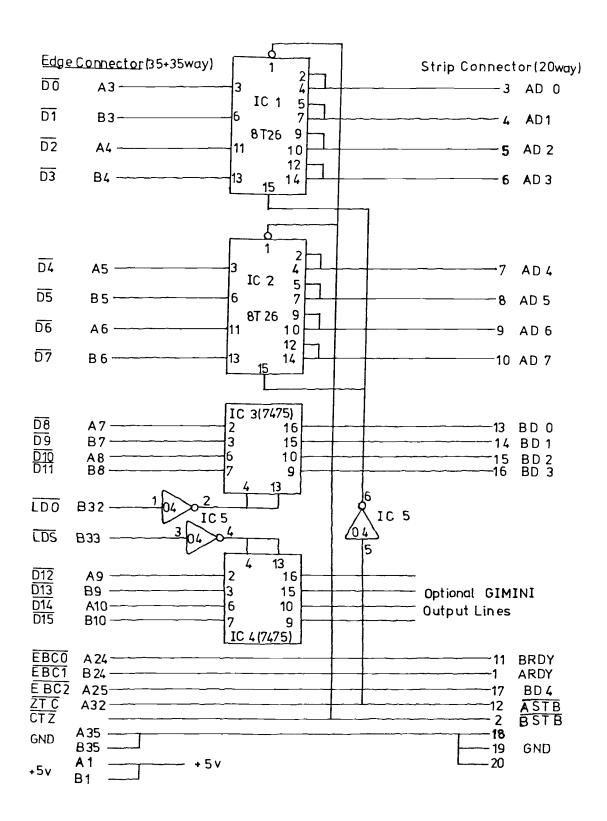

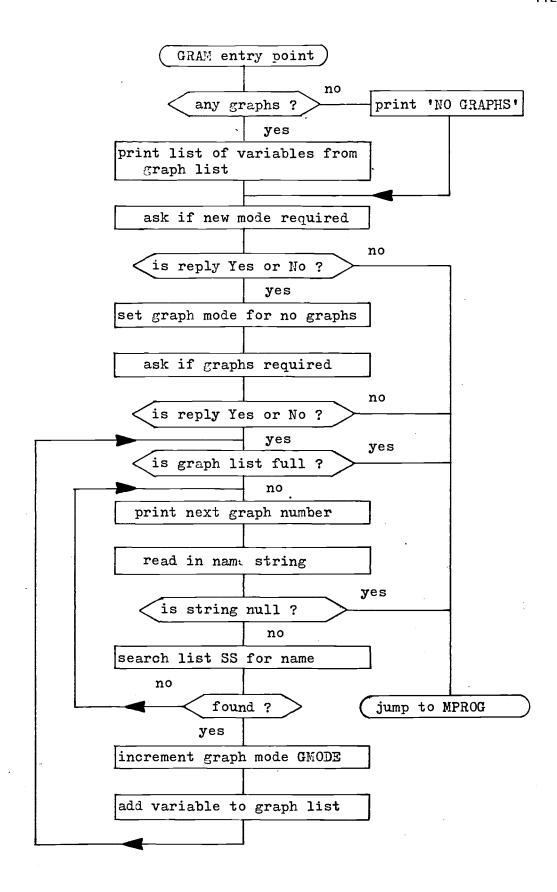

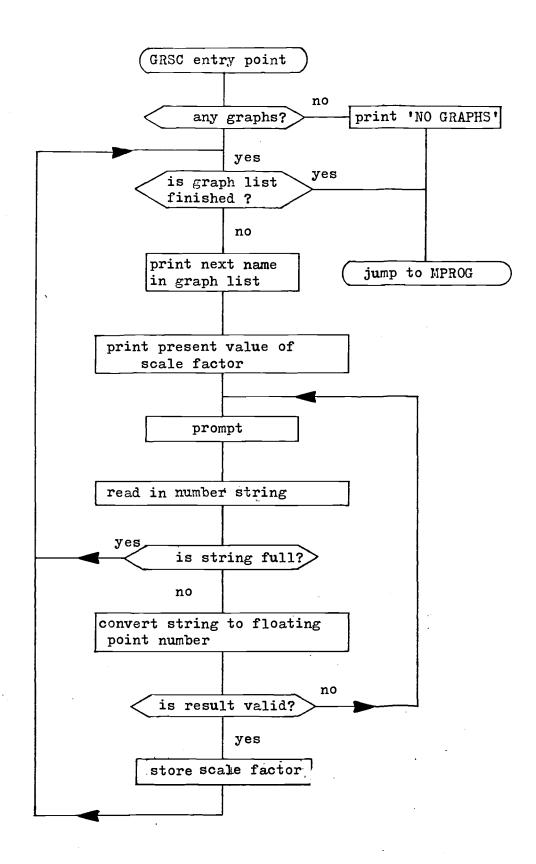

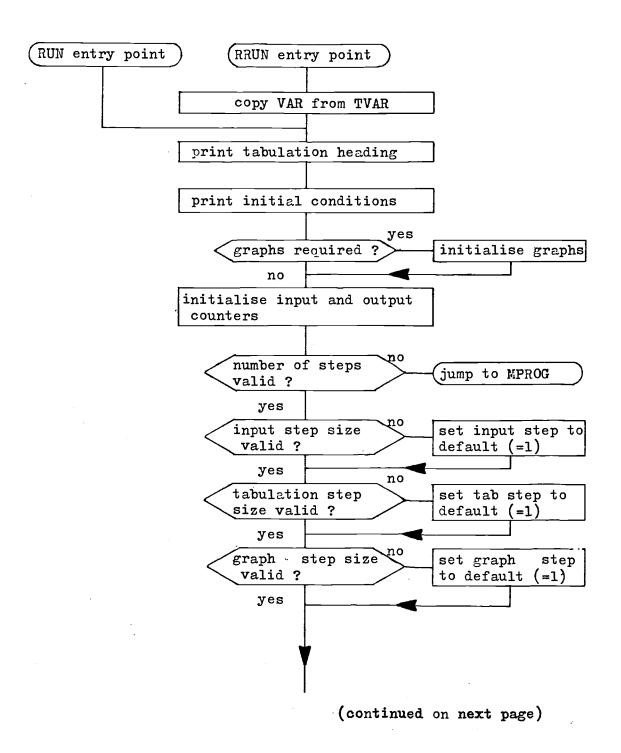

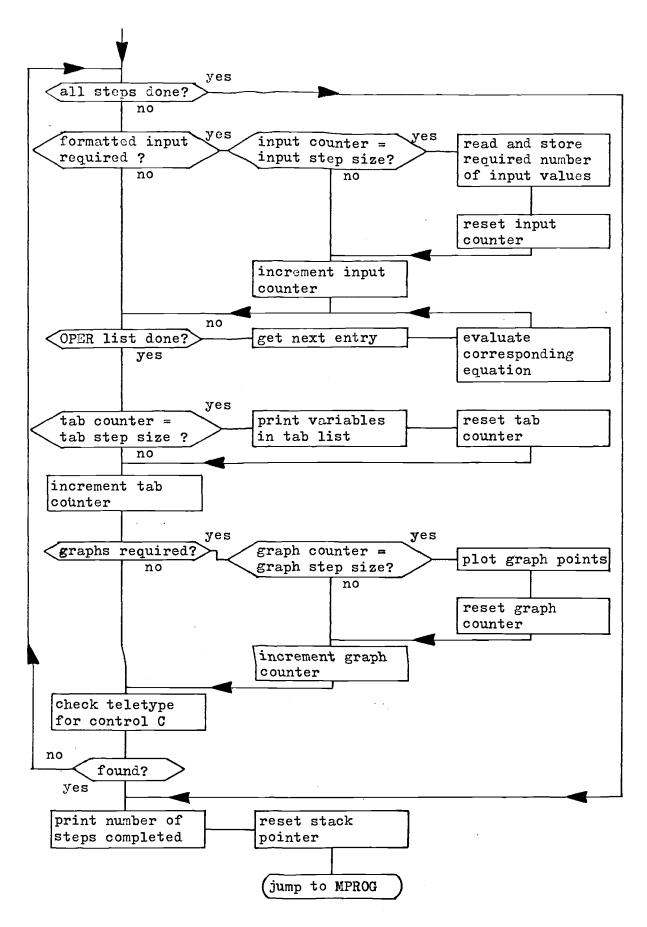

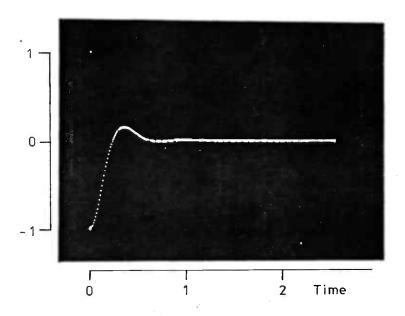

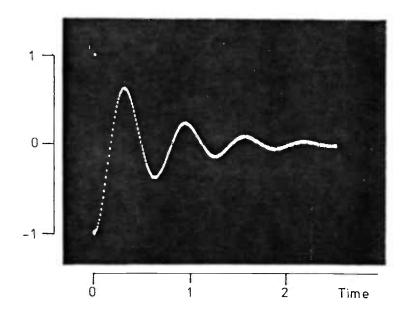

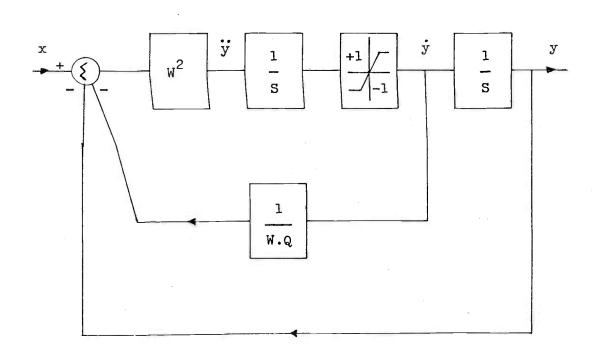

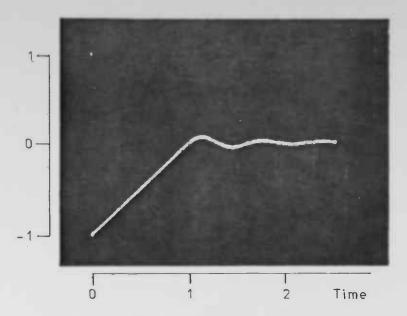

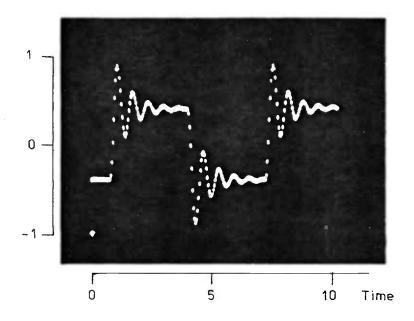

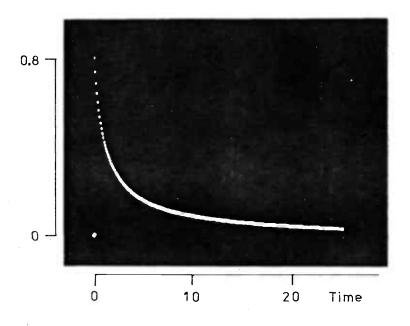

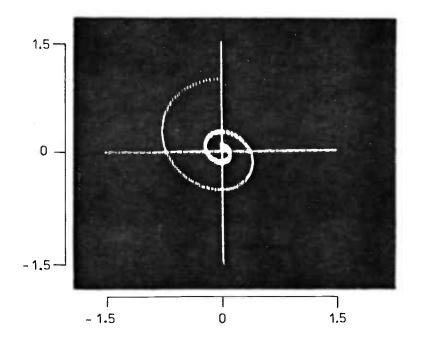

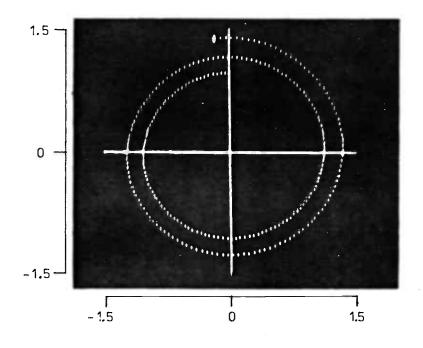

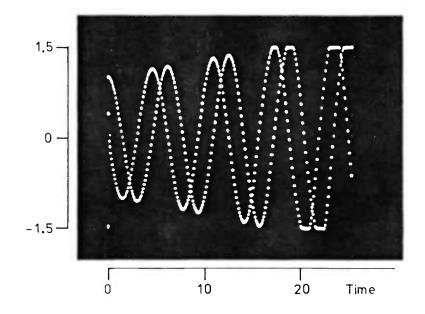

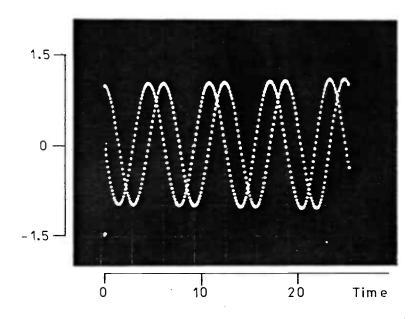

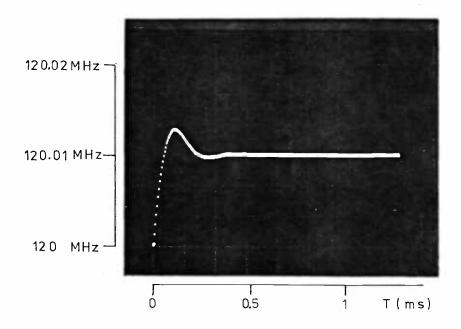

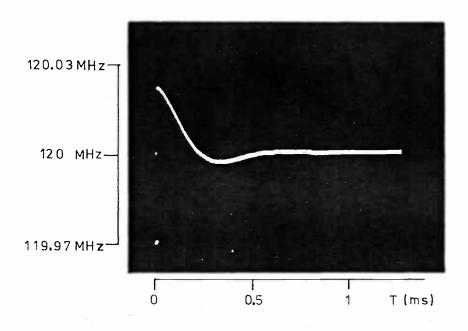

The Zilog Z8000<sup>52,53</sup> is a 16 bit microcomputer, in that its hardware handles sixteen bits in parallel, but it can handle data types of 8, 16, 32 and for some instructions even 64 bits as well as single bits. The Z8000 also has sixteen general purpose registers which can be used with most instructions as accumulators, data storage, index registers, or memory pointers. The Z8000 is available in two versions, one has a 40 pin package and can address 64 kilobytes of memory, and the other has a 48 pin package and provides for the use of 128 segments each of 64 k bytes to give a total memory space of 8 Me-gabytes. The Z8000 has two modes of