Université de Toulouse

# THÈSE

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

**Délivré par :** L'Université Paul Sabatier

## Présentée et soutenue par :

Florent Lopez

Le 11 décembre 2015

Titre :

Task-based multifrontal QR solver for heterogeneous architectures

Solveur multifrontal QR à base de tâches pour architectures hétérogènes

## Ecole doctorale et discipline ou spécialité :

ED MITT : Domaine STIC : Sûreté du logiciel et calcul haute performance

Unité de recherche : IRIT - UMR 5505

**Directeurs de Thèse :** Michel Daydé (ENSEEIHT-IRIT) Alfredo Buttari (CNRS-IRIT)

**Rapporteurs :** Timothy A. Davis (Texas A&M University) Pierre Manneback (Université de Mons)

## Autres membres du jury :

Frédéric Desprez (Inria Rhône-Alpes) Iain S. Duff (Rutherford Appleton Laboratory) Raymond Namyst (Inria Bordeaux Sud-Ouest)

# Résumé

Afin de s'adapter aux architectures multicoeurs et aux machines de plus en plus complexes, les modèles de programmations basés sur un parallélisme de tâche ont gagné en popularité dans la communauté du calcul scientifique haute performance. Les moteurs d'exécution fournissent une interface de programmation qui correspond à ce paradigme ainsi que des outils pour l'ordonnancement des tâches qui définissent l'application.

Dans cette étude, nous explorons la conception de solveurs directes creux à base de tâches, qui représentent une charge de travail extrêmement irrégulière, avec des tâches de granularités et de caractéristiques différentes ainsi qu'une consommation mémoire variable, au-dessus d'un moteur d'exécution. Dans le cadre du solveur qr\_mumps, nous montrons dans un premier temps la viabilité et l'efficacité de notre approche avec l'implémentation d'une méthode multifrontale pour la factorisation de matrices creuses, en se basant sur le modèle de programmation parallèle appelé "flux de tâches séquentielles" (Sequential Task Flow). Cette approche, nous a ensuite permis de développer des fonctionnalités telles que l'intégration de noyaux dense de factorisation de type "minimisation de communications" (Communication Avoiding) dans la méthode multifrontale, permettant d'améliorer considérablement la scalabilité du solveur par rapport a l'approche original utilisée dans mémoire au sein de notre solveur, exploitable dans le cas des architectures multicoeur, réduisant largement la consommation mémoire de la méthode multifrontale QR avec un impacte négligeable sur les performances.

En utilisant le modèle présenté ci-dessus, nous visons ensuite l'exploitation des architectures hétérogènes pour lesquelles la granularité des tâches ainsi les stratégies l'ordonnancement sont cruciales pour profiter de la puissance de ces architectures. Nous proposons, dans le cadre de la méthode multifrontale, un partitionnement hiérarchique des données ainsi qu'un algorithme d'ordonnancement capable d'exploiter l'hétérogénéité des ressources. Enfin, nous présentons une étude sur la reproductibilité de l'exécution parallèle de notre problème et nous montrons également l'utilisation d'un modèle de programmation alternatif pour l'implémentation de la méthode multifrontale.

L'ensemble des résultats expérimentaux présentés dans cette étude sont évalués avec une analyse détaillée des performance que nous proposons au début de cette étude. Cette analyse de performance permet de mesurer l'impacte de plusieurs effets identifiés sur la scalabilité et la performance de nos algorithmes et nous aide ainsi à comprendre pleinement les résultats obtenu lors des tests effectués avec notre solveur.

**Mots-clés :** méthodes directes de résolution de systèmes linéaires, méthode multifrontale, multicoeur, moteurs d'exécutions, ordonnancement, algorithmes d'ordonnancement sous contraintes mémoire, architectures hétérogènes, calcul haute performance, GPU

# Abstract

To face the advent of multicore processors and the ever increasing complexity of hardware architectures, programming models based on DAG parallelism regained popularity in the high performance, scientific computing community. Modern runtime systems offer a programming interface that complies with this paradigm and powerful engines for scheduling the tasks into which the application is decomposed. These tools have already proved their effectiveness on a number of dense linear algebra applications.

In this study we investigate the design of task-based sparse direct solvers which constitute extremely irregular workloads, with tasks of different granularities and characteristics with variable memory consumption on top of runtime systems. In the context of the qr\_mumps solver, we prove the usability and effectiveness of our approach with the implementation of a sparse matrix multifrontal factorization based on a Sequential Task Flow parallel programming model. Using this programming model, we developed features such as the integration of dense 2D Communication Avoiding algorithms in the multifrontal method allowing for better scalability compared to the original approach used in qr\_mumps. In addition we introduced a memory-aware algorithm to control the memory behaviour of our solver and show, in the context of multicore architectures, an important reduction of the memory footprint for the multifrontal QR factorization with a small impact on performance.

Following this approach, we move to heterogeneous architectures where task granularity and scheduling strategies are critical to achieve performance. We present, for the multifrontal method, a hierarchical strategy for data partitioning and a scheduling algorithm capable of handling the heterogeneity of resources. Finally we present a study on the reproducibility of executions and the use of alternative programming models for the implementation of the multifrontal method.

All the experimental results presented in this study are evaluated with a detailed performance analysis measuring the impact of several identified effects on the performance and scalability. Thanks to this original analysis, presented in the first part of this study, we are capable of fully understanding the results obtained with our solver.

**Keywords:** sparse direct solvers, multifrontal method, multicores, runtime systems, scheduling, memory-aware algorithms, heterogeneous architectures, high-performance computing, GPU

# Acknowledgements

I am extremely grateful to Alfredo Buttari for his excellent supervision and constant support throughout three years of intensive work. Without his efforts this thesis would not have been possible. Thanks also to my two co-advisors Emmanuel Agullo and Abdou Germouche for their fruitful collaborations and very interesting discussions. I also wish to thank Michel Daydé for his support during this thesis.

Thanks to Jack Dongarra and George Bosilca for their warm welcome at the University of Tennessee, Knoxville, during my six month scholar visit to the ICL Laboratory. Thanks to the Distributed Computing team for the great collaboration, valuable help and introducing me to the PaRSEC library.

I would like to thank all the members of the thesis committee for reviewing my dissertation and particularly the "Rapporteurs" Tim Davis and Pierre Manneback for the insightful reports they provided about this manuscript. Also a big thank you to Iain Duff for providing such a complete and detailed feedback on the dissertation.

Thanks to my colleagues and particularly my office mates who are now among my closest friends: François-Henry Rouet, Clement Weisbecker, Mohamed Zenadi, Clément Royet and Théo Mary. Thanks to them for the good moments we shared, and the advice and support I received from you.

Finally, I'm deeply grateful to my family for their love, support and encouragement during the production of this thesis.

# Contents

| Ack    | nowledgements                                                                                                                                                          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 ]    | Introduction                                                                                                                                                           |

| -      | .1 Architectures                                                                                                                                                       |

| -      | .2 Linear systems and direct methods                                                                                                                                   |

|        | 1.2.1 Problems/applications                                                                                                                                            |

|        | 1.2.2 QR decomposition                                                                                                                                                 |

|        | 1.2.3 Multifrontal QR methods                                                                                                                                          |

| -      | .3 Parallelization of the $QR$ factorization                                                                                                                           |

|        | 1.3.1 Dense $QR$ factorization $\ldots \ldots \ldots$  |

|        | 1.3.2 Sparse $QR$ factorization $\ldots \ldots \ldots$ |

| -      | .4 Programming models and runtime systems                                                                                                                              |

|        | 1.4.1 Programming models for task-based applications                                                                                                                   |

|        | 1.4.2 Task-based runtime systems for modern architectures $\ldots \ldots \ldots$                                                                                       |

|        | 1.4.2.1 The StarPU runtime system                                                                                                                                      |

|        | 1.4.2.2 The PaRSEC runtime system                                                                                                                                      |

| -      | 1.5 Related work on dense linear algebra                                                                                                                               |

|        | .6 Related work on sparse direct solvers                                                                                                                               |

| -      | .7 The qr_mumps solver                                                                                                                                                 |

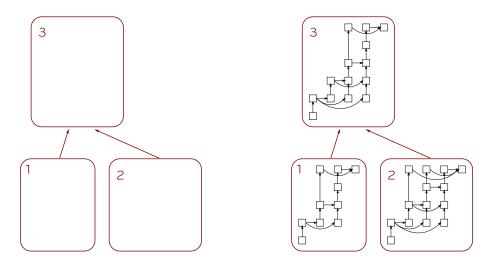

|        | 1.7.1 Fine-grained parallelism in qr_mumps                                                                                                                             |

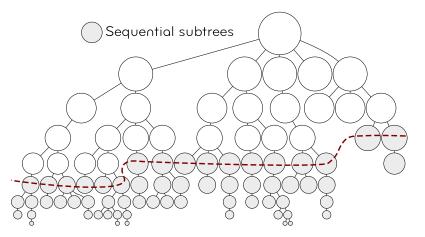

|        | 1.7.2 Tree pruning $\ldots$                                                                                                                                            |

|        | 1.7.3 Blocking of dense matrix operations                                                                                                                              |

|        | 1.7.4 The qr_mumps scheduler                                                                                                                                           |

| -      | 1.7.4.1 Scheduling policy                                                                                                                                              |

|        |                                                                                                                                                                        |

| -      | 1.9 Experimental settings                                                                                                                                              |

|        | 1.9.1         Machines                                                                                                                                                 |

|        | 1.9.2 I TODIEIIIS                                                                                                                                                      |

| 2      | Performance analysis approach                                                                                                                                          |

| 4      | 2.1 General analysis                                                                                                                                                   |

| 6<br>4 | 2.2 Discussion                                                                                                                                                         |

|          | 3.2                                                                                                                                          | StarPU-based multifrontal method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                                                  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

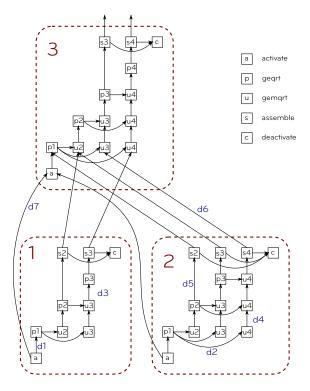

|          |                                                                                                                                              | 3.2.1 DAG construction in the runtime system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                                                                  |

|          |                                                                                                                                              | 3.2.2 Dynamic task scheduling and memory consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                  |

|          |                                                                                                                                              | 3.2.3 Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                                                                                                  |

|          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                     |

| 4        | $\mathbf{STI}$                                                                                                                               | -parallel multifrontal QR method on multicore architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                                                                                                  |

|          | 4.1                                                                                                                                          | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                                  |

|          |                                                                                                                                              | 4.1.1 STF-parallelization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                                  |

|          | 4.2                                                                                                                                          | STF multifrontal QR method 1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69                                                                                                  |

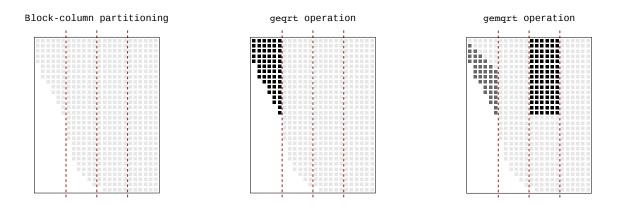

|          |                                                                                                                                              | 4.2.1 STF parallelization with block-column partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69                                                                                                  |

|          |                                                                                                                                              | 4.2.2 Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71                                                                                                  |

|          |                                                                                                                                              | 4.2.3 The effect of inter-level parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75                                                                                                  |

|          | 4.3                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76                                                                                                  |

|          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79                                                                                                  |

|          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83                                                                                                  |

|          | 4.4                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85                                                                                                  |

|          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                     |

| <b>5</b> | Me                                                                                                                                           | nory-aware multifrontal method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89                                                                                                  |

|          | 5.1                                                                                                                                          | Memory behavior of the multifrontal method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89                                                                                                  |

|          | 5.2                                                                                                                                          | Task scheduling under memory constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91                                                                                                  |

|          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91                                                                                                  |

|          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92                                                                                                  |

|          | 5.3                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93                                                                                                  |

|          | 5.4                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95                                                                                                  |

|          |                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                     |

| 6        | $\mathbf{STI}$                                                                                                                               | • 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 99                                                                                                  |

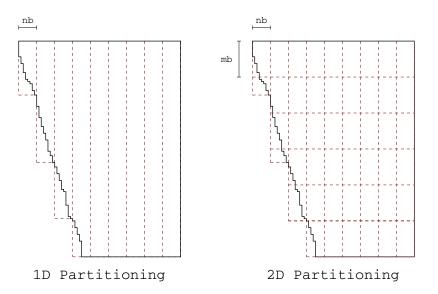

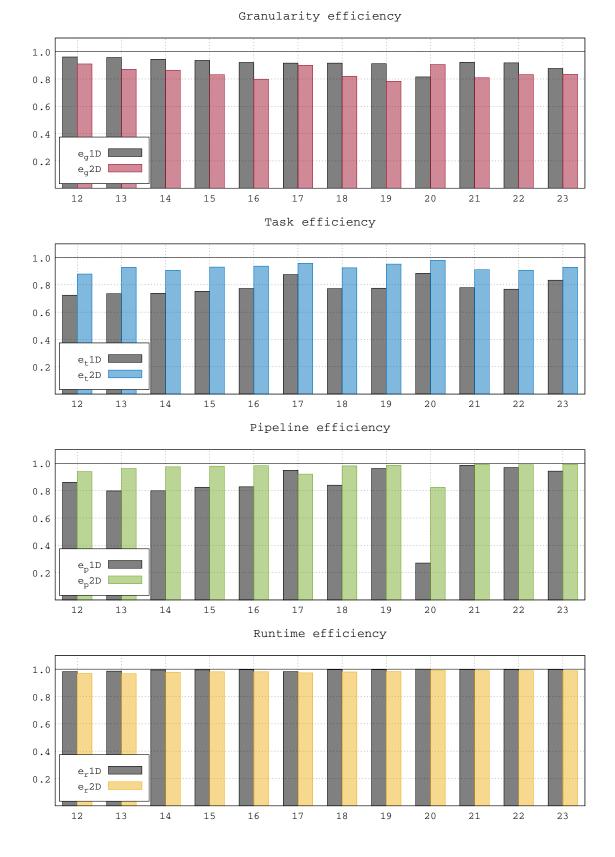

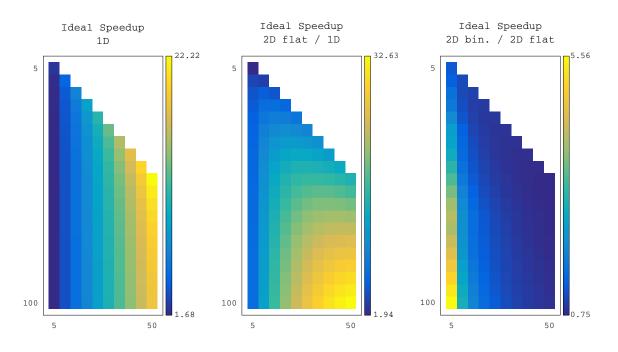

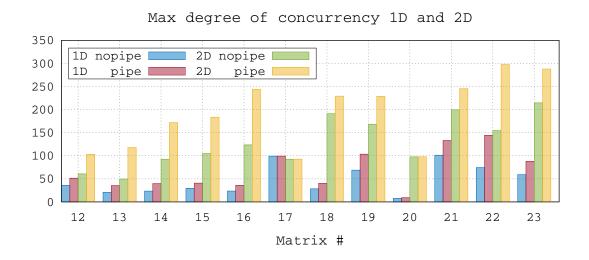

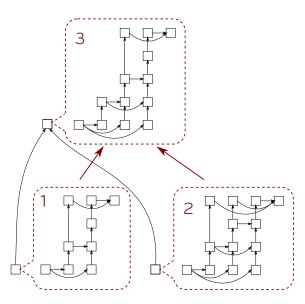

|          | 6.1                                                                                                                                          | Frontal matrices partitioning schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

|          | -                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99                                                                                                  |

|          | 6.2                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99<br>.02                                                                                           |

|          |                                                                                                                                              | Scheduling strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

|          | 6.2                                                                                                                                          | Scheduling strategies       1         Implementation details       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 02                                                                                                  |

|          | $\begin{array}{c} 6.2 \\ 6.3 \end{array}$                                                                                                    | Scheduling strategies       1         Implementation details       1         Experimental results       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .02<br>.05                                                                                          |

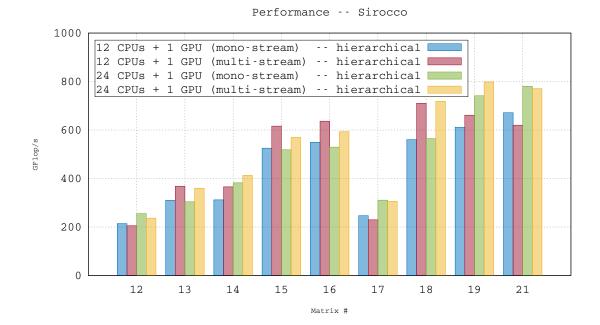

|          | $\begin{array}{c} 6.2 \\ 6.3 \end{array}$                                                                                                    | Scheduling strategies1Implementation details1Experimental results16.4.1Performance and analysis1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .02<br>.05<br>.06                                                                                   |

|          | $\begin{array}{c} 6.2 \\ 6.3 \end{array}$                                                                                                    | Scheduling strategies1Implementation details1Experimental results16.4.1Performance and analysis6.4.2Multi-streaming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .02<br>.05<br>.06                                                                                   |

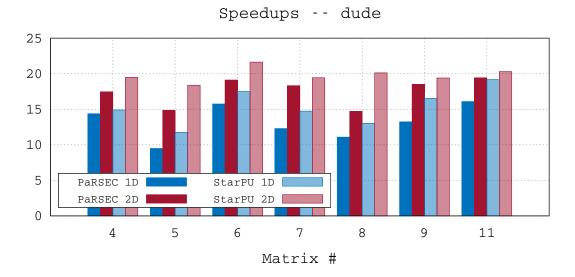

|          | $\begin{array}{c} 6.2 \\ 6.3 \end{array}$                                                                                                    | Scheduling strategies1Implementation details1Experimental results16.4.1Performance and analysis6.4.2Multi-streaming6.4.3Comparison with a state-of-the-art GPU solver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .02<br>.05<br>.06<br>.06<br>.10                                                                     |

|          | 6.2<br>6.3<br>6.4                                                                                                                            | Scheduling strategies1Implementation details1Experimental results16.4.1Performance and analysis6.4.2Multi-streaming6.4.3Comparison with a state-of-the-art GPU solver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .02<br>.05<br>.06<br>.06<br>.10                                                                     |

| 7        | <ul><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                                                                | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1       Performance and analysis       1         6.4.2       Multi-streaming       1         6.4.3       Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1                                                                                                                                                                                                                                                                                                                                                               | .02<br>.05<br>.06<br>.06<br>.10                                                                     |

| 7        | <ul><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                                                                | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1       Performance and analysis       1         6.4.2       Multi-streaming       1         6.4.3       Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         Deciated work       1                                                                                                                                                                                                                                                                                                                                 | .02<br>.05<br>.06<br>.06<br>.10<br>.12<br>.13                                                       |

| 7        | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> </ul>                                                                  | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         primeted work       1         PTG multifrontal QR method       1                                                                                                                                                                                                                                                                                                        | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br><b>15</b>                                                 |

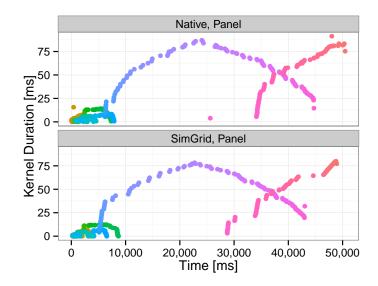

| 7        | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> </ul>                                                     | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1       Performance and analysis       1         6.4.2       Multi-streaming       1         6.4.3       Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         price work       1         PTG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1                                                                                                                                                                                                                            | .02<br>.05<br>.06<br>.06<br>.10<br>.12<br>.13<br>.13<br>.15                                         |

| 7        | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> </ul>                           | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         price       1         PTG multifrontal QR method       1         StarPU contexts in qrm_starpu       1                                                                                                                                                                                                                                                                  | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br><b>15</b><br>.20                                          |

| 7        | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>Cor</li> </ul>              | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         pointed work       1         PTG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1         StarPU contexts in qrm_starpu       1         Aclusion       1                                                                                                                                                                     | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br>.15<br>.20<br>.24<br><b>29</b>                            |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> </ul>                           | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         PrG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1         StarPU contexts in qrm_starpu       1         clusion       1         General conclusion       1                                                                                                                                                                | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br>.15<br>.20<br>.24<br><b>29</b><br>.29                     |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>Cor</li> </ul>              | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         PrG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1         StarPU contexts in qrm_starpu       1         clusion       1         General conclusion       1                                                                                                                                                                | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br>.15<br>.20<br>.24<br><b>29</b>                            |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>Cor</li> <li>8.1</li> </ul> | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         PrG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1         StarPU contexts in qrm_starpu       1         Perspectives and future work       1                                                                                                                                                                              | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br>.15<br>.20<br>.24<br><b>29</b><br>.29                     |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>Cor</li> <li>8.1</li> </ul> | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1 Performance and analysis       1         6.4.2 Multi-streaming       1         6.4.3 Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         pociated work       1         PTG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1         StarPU contexts in qrm_starpu       1         Perspectives and future work       1         Public articles       1                                                                                                                | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br>.15<br>.20<br>.24<br><b>29</b><br>.30                     |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>Cor</li> <li>8.1</li> </ul> | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1       Performance and analysis       1         6.4.2       Multi-streaming       1         6.4.3       Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         pociated work       1         PTG multifrontal QR method       1         Simulation of qrm_starpu with StarPU SimGrid       1         starPU contexts in qrm_starpu       1         Perspectives and future work       1         Public articles       1         Submitted articles       1         Conference proceedings       1                    | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br>.15<br>.20<br>.24<br><b>29</b><br>.30<br>.33              |

|          | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Ass</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>Cor</li> <li>8.1</li> </ul> | Scheduling strategies       1         Implementation details       1         Experimental results       1         6.4.1       Performance and analysis       1         6.4.2       Multi-streaming       1         6.4.3       Comparison with a state-of-the-art GPU solver       1         Possible minor, technical improvements       1         Possible minor, technical improvements       1         poster       1         PTG multifrontal QR method       1         Simulation of qrm_starpu       1         starPU contexts in qrm_starpu       1         clusion       1         General conclusion       1         Submitted articles       1         Posters       1         Posters       1 | .02<br>.05<br>.06<br>.10<br>.12<br>.13<br><b>15</b><br>.20<br>.24<br><b>29</b><br>.30<br>.33<br>.33 |

## References

# Chapter 1

# Introduction

## **1.1** Architectures

The world of computing, and particularly the world of High Performance Computing (HPC), have witnessed a substantial change at the beginning of the last decade as all the classic techniques used to improve the performance of microprocessors reached the point of diminishing returns [17]. These techniques, such as deep pipelining, speculative execution or superscalar execution, were mostly based on the use of Instruction Level Parallelism (ILP) and required higher and higher clock frequencies to the point where the processors power consumption, which grows as the cube of the clock frequency, became (or was about to become) unsustainable. This was not only true for large data or supercomputing centers but also, and even more so, for portable devices such as laptops, tablets and smartphones which have recently become very widespread. In order to address this issue, the microprocessor industry sharply turned towards a new design based on the use of Thread Level Parallelism (TLP) achieved by accommodating multiple processing units or *cores* on the same die. This led to the production of *multicore* processors that are nowadays ubiquitous. The main advantage over the previous design principles lies in the fact that the multicore design does not require an increase in the clock frequency but only implies an augmentation of the chip capacitance (i.e., the number of transistors) on which the power consumption only depends linearly. As a result, the multicore technology not only enables improvement in performance, but also reduces the power consumption: assuming a single-core processor with frequency f, a dual-core with frequency 0.75 \* f is 50% faster and consumes 15% less energy.

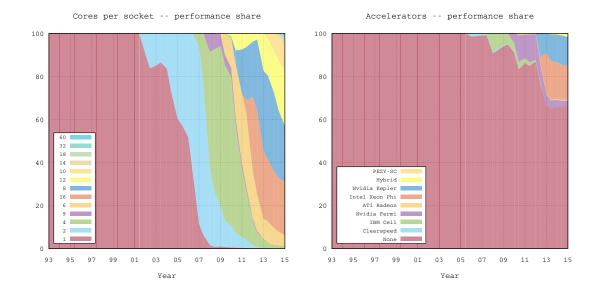

Since their introduction, multicore processors have become increasingly popular and can be found, nowadays, in almost any device that requires some computing power. Because they allow for running multiple processes simultaneously, the introduction of multicore in high throughput computing or in desktop computing was transparent and immediately beneficial. In HPC, though, the switch to the multicore technology lead to a sharp discontinuity with the past as methods and algorithms had to be rethought and codes rewritten in order to take advantage of the added computing power through the use of TLP. Nonetheless, multicore processors have quickly become dominant and are currently used in basically all supercomputers. Figure 1.1 (*left*) shows the performance share of multicore processors in the Top500<sup>1</sup> list (a list of the 500 most powerful supercomputers in the world, which is updated twice per year); the figure shows that after their first appearance in the list (May 2005) multicore has quickly become the predominant technology in the Top500 list and ramped up to nearly 100% of the share in only 5 years. The figure also

<sup>&</sup>lt;sup>1</sup>http://top500.org

Figure 1.1: Performance share of multicore processors (on the left) and accelerators (on the right) in the Top500 list.

shows that the number of cores per socket has grown steadily over the years: a typical modern processor features between 8 and 16 cores. In Section 1.9.1 we present the systems used for the experiments reported in this document. The most recent and powerful among these processors is the Xeon E5-2680 which hosts 12 cores; each of these cores has 256 bit AVX vector units with Fused Multiply-Add (FMA) capability which, with a clock frequency of 2.5 GHz make a peak performance of 40 Gflop/s per core and 480 Gflop/s on the whole processor for double-precision floating point operations.

Around the same period as the introduction of multicore processors, the use of ac*celerators* or *coprocessors* started gaining the interest of the HPC community. Although this idea was not new (for example FPGA boards were previously used as coprocessors), it was revamped thanks to the possibility of using extremely efficient commodity hardware for accelerating scientific applications. One such example is the Cell processor [65] produced by the STI consortium (formed by IBM, Toshiba and Sony) from 2005 to 2009. The Cell was used as an accelerator board on the Roadrunner supercomputer installed at the Los Alamos National Labrador (USA) which was ranked #1 in the Top500 list of November 2008. The use of accelerators for HPC scientific computing, however, gained a very widespread popularity with the advent of General Purpose GPU computing. Specifically designed for image processing operations, Graphical Processing Units (GPUs) offer a massive computing power which is easily accessible for highly data parallel applications (image processing often consists in repeating the same operation on a large number of pixels). This led researchers to think that these devices could be employed to accelerate scientific computing applications, especially those based on the use of operations with a very regular behaviour and data access pattern, such as dense linear algebra. In the last few years, GPGPU has become extremely popular in scientific computing and is employed in a very wide range of applications, not only dense linear algebra. This widespread use of GPU accelerators was also eased by the fact that GPUs, which were very limited in computing capabilities and difficult to program, have become, over the years, suited to a much wider range of applications and much easier to program thanks to the development of specific high-level programming languages and development kits. Figure 1.1 (*right*) shows the performance share of supercomputers equipped with accelerators. Although some GPU accelerators are also produced by AMD, currently the most widely used ones are produced by Nvidia. Figure 1.2 shows a block diagram of the architecture of a recent Nvidia GPU device, the K40m of the Kepler family. This board is equipped with 15 Streaming Multiprocessors (SMX), each containing 192 single precision cores and 64 double precision ones for a peak performance of 1.43 (4.29) Tflop/s for double (single) precision computations. The K40m also has a memory of 12 GB capable of streaming data at a speed of 288 GB/s.

More recently Intel has also started producing accelerators, namely the Xeon Phi boards. The currently distributed models of the Xeon Phi devices, the Knights Corner family, can host up to 61 cores connected with a bi-directional ring interconnect. Each core has a 512 bit wide vector unit with FMA capability and the clock frequency can be as high as 1.238 GHz which makes an overall maximum peak performance of 1208 Gflop/s for double-precision, floating point computation. On-board memory can be as big as 16 GB and transfer data at a speed of 352 GB/s. One outstanding advantage of the Xeon Phi devices is that the instruction set is fully x86 compliant which allows for using "traditional" multithreading programming technologies such as OpenMP.

Figure 1.2: Block diagram of the Kepler K40m GPU.

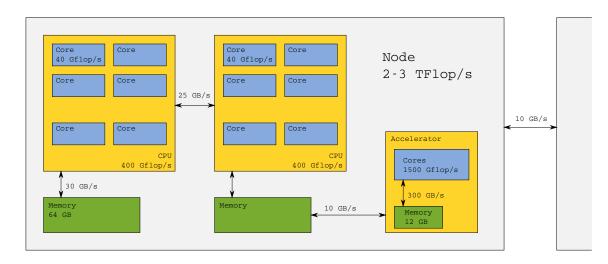

Figure 1.3 shows a typical configuration of a modern HPC computing platform. This is formed by multiple (up to thousands) nodes connected through a high-speed network; each node may include multiple processors, each connected with a NUMA memory module. A node may also be equipped with one or more accelerators. Please note that the figure reports indicative values for performance, bandwidths and memory capacities and do not refer to any specific device. The figure shows that modern HPC platforms are based on extremely heterogeneous architectures as they employ processing units with different performance, memories with different capacities and interconnects with different latencies and bandwidths.

Figure 1.3: Illustration of a typical HPC computing platform architecture.

## 1.2 Linear systems and direct methods

## 1.2.1 Problems/applications

This thesis deals with the efficient and scalable implementation of direct solvers for large scale, sparse linear systems of equations on modern architectures equipped with multicore processors and accelerators, such as GPU devices. Specifically, this work focuses on sparse multifrontal solvers based on the QR factorization of the system matrix. This method decomposes the input matrix  $A \in \mathbb{R}^{m \times n^2}$ , assumed to be of full rank, into the product of a square, orthogonal matrix  $Q \in \mathbb{R}^{m \times m}$  and an upper triangular matrix  $R \in \mathbb{R}^{n \times n}$ .

**Theorem 1.1** - Björck [23, Theorem 1.3.1]. Let  $A \in \mathbb{R}^{m \times n}$ ,  $m \ge n$ . Then there is an orthogonal matrix  $Q \in \mathbb{R}^{m \times m}$  such that

$$A = Q \begin{pmatrix} R \\ 0 \end{pmatrix}, \tag{1.1}$$

where R is upper triangular with nonnegative diagonal elements. The decomposition (1.1) is called the QR decomposition of A, and the matrix R will be called the R-factor of A.

The columns of the Q matrix can be split in two groups

$$Q = [Q_1 Q_2] \tag{1.2}$$

where  $Q_1 \in \mathbb{R}^{m \times n}$  is an orthogonal basis for the range of A,  $\mathcal{R}(A)$  and  $Q_2 \in \mathbb{R}^{m \times (m-n)}$  is an orthogonal basis for the kernel of  $A^T$ ,  $\mathcal{N}(A^T)$ .

The QR decomposition can be used to solve square linear system of equations

$$Ax = b$$

, with  $A \in \mathbb{R}^{n \times n}$ , (1.3)

$<sup>^{2}</sup>$ Without loss of generality here, and in the rest of this document, we will assume that the same algorithms and methods, programming techniques and experimental analysis can be generalized to the case of complex arithmetic.

as the solution x can be computed through the following three steps (where we use MATLAB notation)

$$\begin{cases} [QR] = qr(A) \\ z = Q^T b \\ x = R \backslash z \end{cases}$$

(1.4)

where, first, the QR decomposition is computed (e.g., using one of the methods described in the next section), an intermediate result is computed trough a simple matrix-vector product and, finally, solution x is computed through a triangular system solve. It must be noted that the second and the third steps are commonly much cheaper than the first and that the same QR decomposition can be used to solve matrix A against multiple right-hand sides b. If the right hand sides are available all together, then the second and third steps can each be applied at once to all of them. As we will explain the next two sections, the QR decomposition is commonly unattractive in practice for solving square systems mostly due to its excessive cost when compared to other available techniques, despite its desirable numerical properties.

The QR decomposition is instead much more commonly used for solving linear systems where A is overdetemined, i.e. where there are more equations than unknowns. In such cases, unless the right-hand side b is in the range of A, the system admits no solution; it is possible, though, to compute a vector x such that Ax is as close as possible to b, or, equivalently, such that the residual  $||Ax - b||_2$  is minimized:

$$\min_{x} \|Ax - b\|_2. \tag{1.5}$$

Such a problem is called a *least-squares* problem and commonly arises in a large variety of applications such as statistics, photogrammetry, geodetics and signal processing. One typical example is given by linear regression where a linear model, say f(x, y) = a + bx + cy has to be fit to a number of observations subject to errors  $(f_i, x_i, y_i)$ , i = 1, ..., m. This leads to the overdetermined system

$$\begin{bmatrix} 1 & x_1 & y_1 \\ 1 & x_2 & y_2 \\ \vdots & \vdots & \vdots \\ 1 & x_m & y_m \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix} = \begin{bmatrix} f_1 \\ f_2 \\ \vdots \\ f_m \end{bmatrix}$$

Assuming the QR decomposition of a in Equation (1.1) has been computed and

$$Q^T b = \left[ \begin{array}{c} Q_1^T \\ Q_2^T \end{array} \right] b = \left[ \begin{array}{c} c \\ d \end{array} \right]$$

we have

$$||Ax - b||_{2}^{2} = ||Q^{T}Ax - Q^{T}b||_{2}^{2} = ||Rx - c||_{2}^{2} + ||d||_{2}^{2}.$$

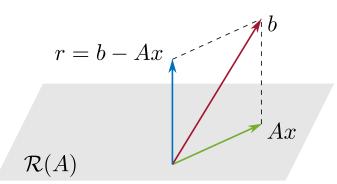

This quantity is minimized if Rx = c where x can be found with a simple triangular system solve. This is equivalent to saying that  $Ax = Q_1Q_1^Tb$  and thus solving Equation (1.5) amounts to finding the vector x such that Ax is the orthogonal projection of b over the range of A, as shown in Figure 1.4. Also note that  $r = Q_2Q_2^Tb$  and thus r is the projection of b on the null space of  $A^T$ ,  $\mathcal{N}(A)$ .

Another commonly used technique for the solution of the least-squares problem is the Normal Equations method. Because the residual r is in  $\mathcal{N}(A^T)$

$$A^T(Ax - b) = 0$$

Figure 1.4: Solution of a least-squares problem.

and, thus, the solution x to Equation (1.5) can be found solving the linear system  $A^T A x = A^T b$ . Because  $A^T A$  is Symmetric Positive Definite (assuming A has full rank), this can be achieved through the Cholesky factorization. Nonetheless, the method based on the QR factorization is often preferred because the conditioning of  $A^T A$  is equal to the square of the conditioning of A, which may lead to excessive error propagation.

The QR factorization is also commonly used to solve underdetermined systems, i.e., with more unknowns than equations, which admit infinite solutions. In such cases the desired solution is the one with minimum 2-norm:

$$\min \|x\|_2, \quad Ax = b. \tag{1.6}$$

The solution of this problem can be achieved computing the QR factorization of  $A^T$

$$[Q_1 Q_2] \left[ \begin{array}{c} R\\ 0 \end{array} \right] = A^T$$

where  $Q_1 \in \mathbb{R}n \times m$  and  $Q_2 \in \mathbb{R}n \times (n-m)$ . Then

$$Ax = R^T Q^T x = [R^T 0] \begin{bmatrix} z_1 \\ z_2 \end{bmatrix} = b$$

and the minimum 2-norm solution follows by setting  $z_2 = 0$ . Note that  $Q_2$  is an orthogonal basis for  $\mathcal{N}(A)$  and, thus, the minimum 2-norm solution is computed by removing for any admissible solution  $\tilde{x}$  all of its components in  $\mathcal{N}(A)$ .

For the sake of space and readability, we do not discuss here the use of iterative methods such as LSQR [91] or Craig [39] for the solution of problems (1.5) and (1.6) but we refer the reader to the book by Björck [23] which contains a thorough description of the classical methods used for solving least-squares and minimum 2-norm problems.

#### 1.2.2 QR decomposition

The QR decomposition of a matrix can be computed in different ways; the use of Givens Rotations [57], Householder reflections [69] or the Gram-Schmidt orthogonalization [100] are among the most commonly used and best known ones. We will not cover here the use of Givens Rotations, Gram-Schmidt orthogonalization and their variants and refer, instead, the reader to classic linear algebra textbooks such as Golub et al. [59] or Björck [23] for an exhaustive discussion of such methods. We focus, instead, on the QR factorization based on Householder reflections which has become the most commonly used method especially because of the availability of algorithms capable of achieving very high performance on processors equipped with memory hierarchies.

For a given a vector u, a Householder Reflection is defined as

$$H = I - 2\frac{uu^T}{u^T v} \tag{1.7}$$

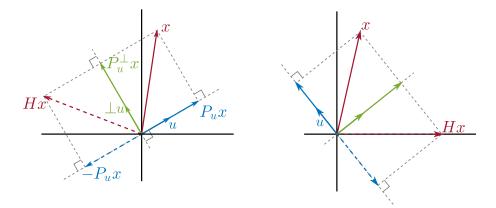

and u is commonly referred to as *Householder vector*. It is easy to verify that H is symmetric and orthogonal. Because  $P_u = \frac{uu^T}{u^T u}$  is a projector over the space of u, Hx can be regarded as the reflection of a vector x on the hyperplane that has normal vector u. This is depicted in Figure 1.5 (*left*).

Figure 1.5: Householder reflection

The Householder reflection can be defined in such a way that Hx has all zero coefficients except the first, which means to say that  $Hx = \pm ||x||_2 e_1$  where  $e_1$  is the first unit vector. This can be achieved if Hx is the reflection of x on the hyperplane that bisects the angle between x and  $\pm ||x||_2 e_1$ . This hyperplane is orthogonal to the difference of these two vectors  $x \mp ||x||_2 e_1$  which can thus be used to construct the vector

$$u = x \mp ||x||_2 e_1. \tag{1.8}$$

Note that, if, for example, x is close to a multiple of  $e_1$ , then  $||x||_2 \approx x(1)$  which may lead to a dangerous cancellation in Equation (1.8); to avoid this problem u is commonly chosen as

$$u = u + sign(x(1)) ||x||_2 e_1.$$

(1.9)

In practice, it is very convenient to scale u in such a way that its first coefficient is equal to 1 (more on this will be said later). Assuming v = u/u(1), through some simple manipulations, the Householder transformation H is defined as

$$H = I - \tau v v^{T}, \text{ where } \tau = \frac{sign(x(1))(x(1) - \|x\|_{2})}{\|x\|_{2}}.$$

(1.10)

Note that the matrix H is never explicitly built neither to store, nor to apply the Householder transformation; the storage is done implicitly by means of v and  $\tau$  and the transformation can be applied to an entire matrix  $A \in \mathbb{R}^{m \times n}$  in 4mn flops like this

$$HA = (I - \tau v v^T)A = A - \tau v (v^T A)$$

(1.11)

The Householder reflection can be computed and applied as described above using the \_larfg and \_larf routines in the LAPACK[15] library.

A sequence of Householder transformations can be used to zero-out all the coefficients below the diagonal of a dense matrix to compute its QR factorization:

$$H_n H_{n-1} \dots H_2 H_1 A = R$$

, where  $H_n H_{n-1} \dots H_2 H_1 = Q^T$ .

Each transformation  $H_k$  annihilates all the coefficients below the diagonal of column k and modifies all the coefficients in the trailing submatrix A(k:m, k+1:n). The total cost of this algorithm is  $2n^2(m-n/3)$ . The Q matrix is implicitly represented by means of the  $v_k$  vectors and the  $\tau_k$  coefficients. One extra array has to be allocated to store the  $\tau_k$  coefficients, whereas the  $v_k$  vectors can be stored inside matrix A in the same memory as the zeroed-out coefficients; this is possible because the  $v_k$  have been scaled as described above and thus the 1 coefficients along the diagonal must not be explicitly stored. The LAPACK \_geqr2 routine implements this algorithm.

**Theorem 1.2** - Björck [23, Remark 2.4.2].

Let R denote the computed R. It can be shown that there exists an exactly orthogonal matrix  $\overline{Q}$  (not the computed Q) such that

$$A + E = \bar{Q}\bar{R}, \ \|E\|_F \le c_1 u \|A\|_F,$$

where the error constant  $c_1 = c_1(m, n)$  is a polynomial in m and n,  $\|\cdot\|_F$  denotes the Frobenius norm and u the unit roundoff.

In other words, the Householder QR factorization is normwise backward stable.

The use of a QR factorization by mean of a sequence of orthogonal transformations to solve least-squares problems was introduced by Golub [58]; this method is also proven to be backward stable:

**Theorem 1.3** - Björck [23, Remark 2.4.8].

Golub's method for solving the standard least squares problem is normwise backward stable. The computed solution  $\hat{x}$  can be shown to be the exact solution of a slightly perturbed least squares problem

$$\min \|(A+\delta A)x - (b+\delta b)\|_2,$$

where the perturbations satisfy the bounds

$$\|\delta A\|_2 \le cun^{1/2} \|A\|_2, \|\delta b\|_2 \le cu\|b\|_2$$

and c = (6m - 3n + 41)n.

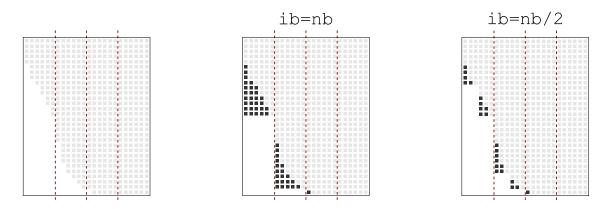

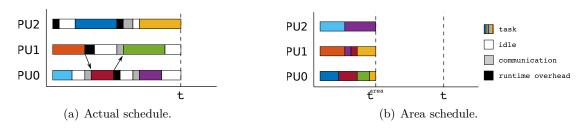

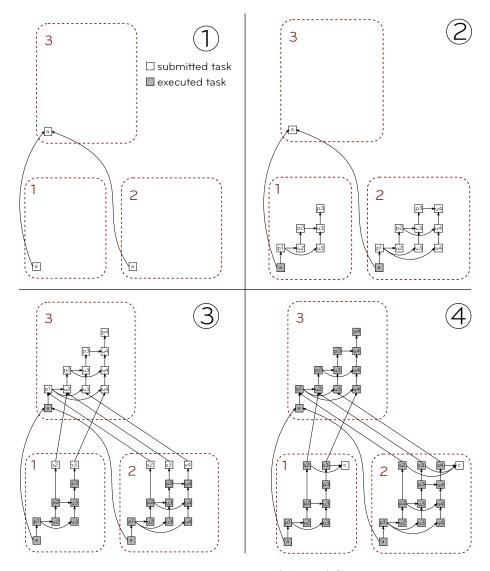

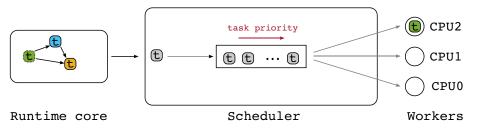

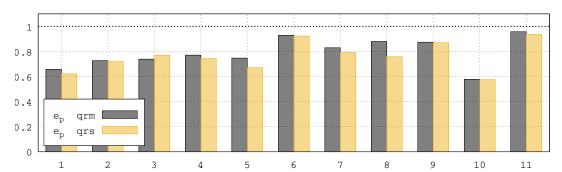

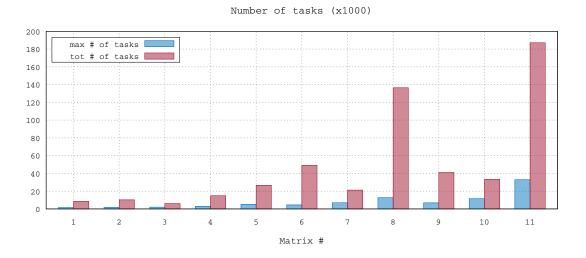

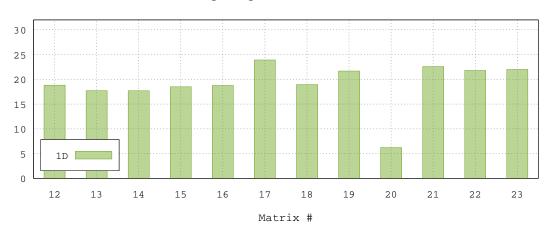

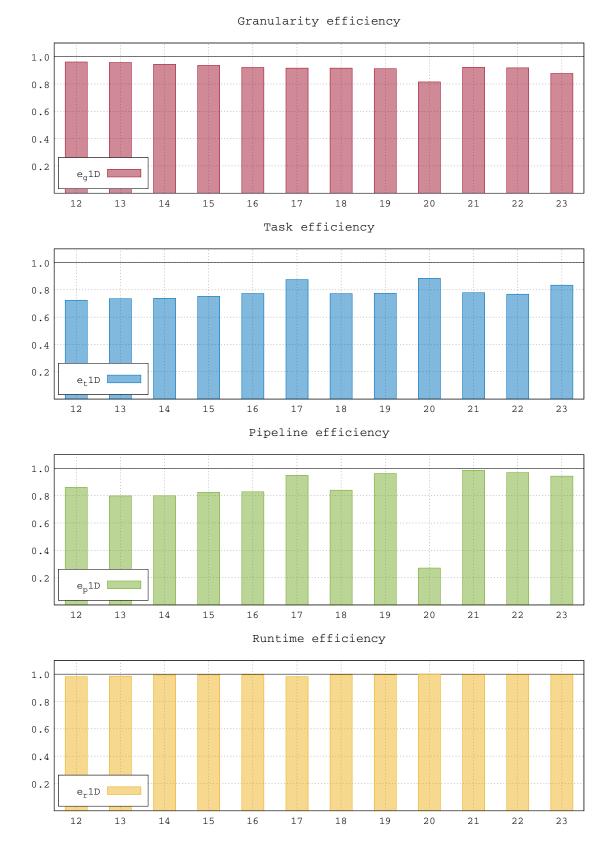

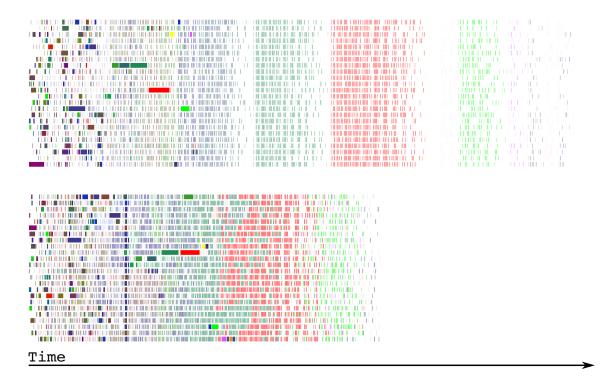

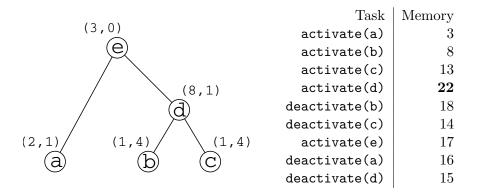

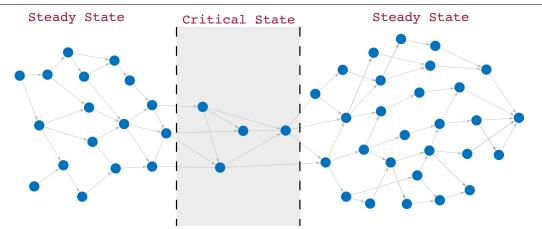

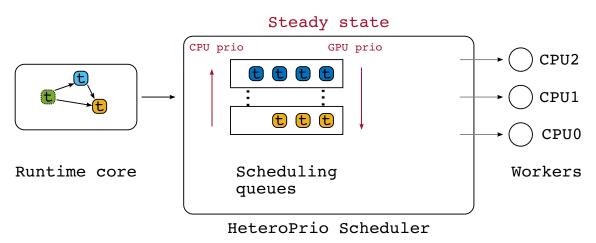

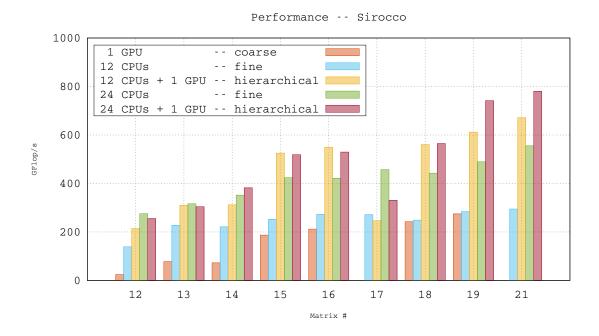

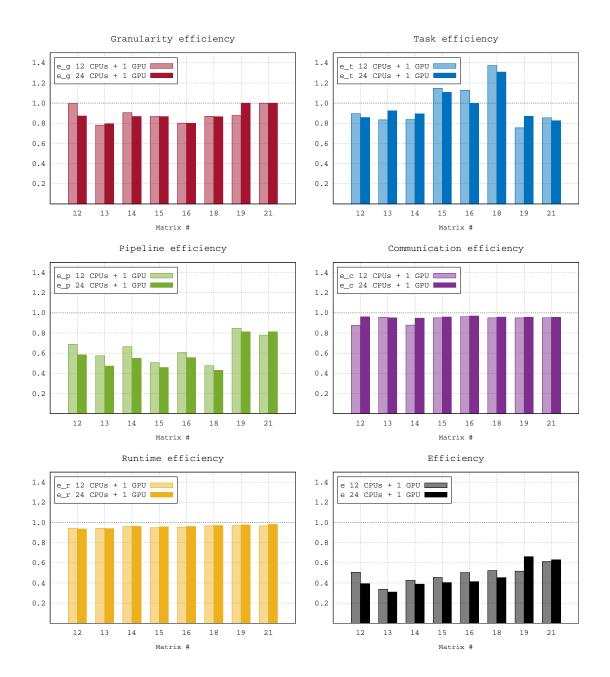

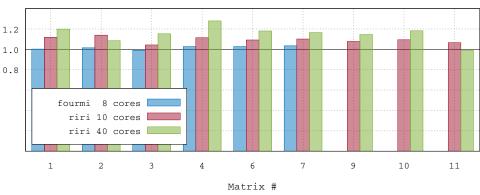

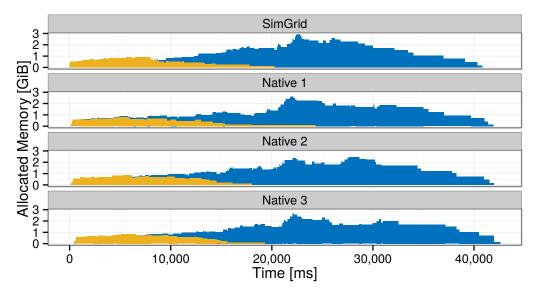

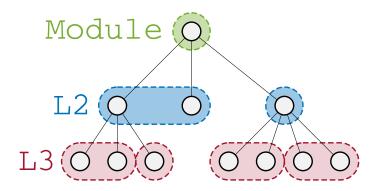

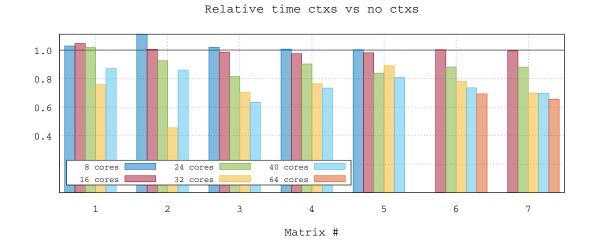

Despite these very favorable numerical properties, the QR factorization is rarely preferred to the Gaussian Elimination (or LU factorization) with Partial Pivoting (GEPP) for the solution of square systems because its cost is twice the cost of GEPP and because partial pivoting is considered stable in most practical cases.