Samuel Martins Simões Sistema Adaptativo para Pré-distorção de Amplificadores

Amplifier Predistortion Adaption System

Universidade de Aveiro 2021

### Samuel Martins Simões

### Sistema Adaptativo para Pré-distorção de Amplificadores

### **Amplifier Predistortion Adaptation System**

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Eletrónica e Telecomunicações, realizada sob a orientação científica de Doutor Telmo Reis Cunha, Professor Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro.

Dissertation presented to the University of Aveiro to fulfill the required to obtain the degree of Master in Electronics and Telecommunication Engineering, developed under the scientific guidance of Doctor Telmo Reis Cunha, Professor in the Department of Electronics, Telecommunications and Informatics of the University of Aveiro.

### o júri / the jury

| presidente / president                | <b>Professora Doutora Susana de Jesus Mota</b><br>Professora Auxiliar, Departamento de Eletrónica, Telecomunicações e Informática<br>da Universidade de Aveiro                                     |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| arguente Principal / main<br>examiner | <b>Professor Doutor Manuel Cândido Duarte dos Santos</b><br>Professor Auxiliar, Departamento de Engenharia Electrotécnica e de Computadores<br>da Faculdade de Engenharia da Universidade do Porto |

| orientador / advisor                  | <b>Professor Doutor Telmo Reis Cunha</b><br>Professor Associado, Departamento de Eletrónica, Telecomunicações e Informática<br>da Universidade de Aveiro                                           |

## agradecimentos / acknowledgements

Em primeiro lugar gostaria de agradecer ao meu orientador, Professor Telmo Reis Cunha pelo apoio científico prestado, por toda orientação, sugestões e esclarecimento de dúvidas disponibilizado.

Gostaria também de agradecer ao Instituto de Telecomunicações, pelo acesso às instalações, laboratório, equipamentos de medida e componentes. Um obrigado ao Paulo Gonçalves e ao Hugo Mostardinha pelo apoio técnico prestado pela simpatia, profissionalismo e disponibilidade demonstrada.

Agradeço à Universidade de Aveiro e ao Departamento de Eletrónica, Telecomunicações e Informática pelas oportunidades e todo o ensino de qualidade.

A todos os meus amigos, em especial ao Rui Carvalho pelo apoio e ajuda imensurável ao longo dos anos, ao Bruno Brandão pelo apoio e conhecimento partilhado durante o design deste projeto. Por último e não menos importante aos meus amigos Eduardo Fernandes, Joana Castro, Joaquim Melim, José Nogueira e Rafael Almeida, a todos um grande obrigado pelo companheirismo durante dias a fio e noites adentro ao qual tornaram esta viagem inesquecível.

Finalmente um grande obrigado à minha família, pai, mãe e irmã pelo apoio incondicional ao longo da minha vida, nomeadamente nestes últimos anos, por acreditarem e não me deixarem desistir, a eles um enorme obrigado pelo que sou e consegui atingir.

#### Palavras-chave

Resumo

Pré-distorção, Pré-distorção Analógica, Amplificador de Potência, Rádio Frequência.

No mundo de hoje, com as exigências necessárias para cumprir os requisitos para o 5G, é fundamental que os amplificadores de Rádio Frequência (RF) funcionem de uma forma cada vez mais eficiente. Para cumprir esse objetivo, uma das opções existentes foca-se no uso de técnicas de linearização para melhorar o seu desempenho na sua zona de saturação. Uma das técnicas que mais se destaca, quer seja pela sua eficiência ou pelo nível de linearização que proporciona, é aquela que consiste na aplicação de pré-distorsores. Estes podem ser utilizados com uma configuração pré-programada ou podem adaptar a sua resposta em tempo real, recorrendo à leitura do sinal existente na saída do amplificador de potência.

Este trabalho foca-se na construção de um sistema adaptativo para pré-distorção de amplificadores em tempo real. Este sistema realiza a medição espetral de um sinal de RF com o objetivo de no futuro ser usado para controlar um pré-distorsor.

Tendo em consideração um cenário de *Multiple-Input and Multiple-Output* (*MIMO*), onde um transmissor é construído através de vários amplificadores de baixa potência e com banda larga (em que cada um requer algum tipo de linearização), o sistema de medida espectral assume, desde o início, os requisitos de obter um produto de baixo custo e que exija o mínimo espaço possível.

Predistortion, Analog Predistotion, Power Amplifier, Radio Frequency

In today's world, with the demands needed to fulfil the challenges on 5G, it is important that Radio Frequency (RF) amplifiers work in a more efficient way. To meet this objective, one of the existing options focuses on the usage of linearization techniques to improve amplifier performance on its saturation zone. One relevant technique, which has great efficiency and linearization potential is the application of predistorters. They can be used with a pre-programed configuration or they may adapt their response in real-time, with the help of signal readings at the power amplifier's (PA) output.

This work focuses on the design and implementation of an amplifier predistortion real-time adaption system. This system measures the spectral power of an RF signal with the purpose of, in the future, incorporating a predistorter automatic adaption system.

Having the Multiple-Input and Multiple-Output (MIMO) transmitter scenario as background, where a single transmitter is built from several low-power and wideband amplifiers (each of which require linearization actions), the developed spectrum measurement system assumed, from the start, the requirements of achieving a very low cost and reduced space confinement.

Keywords

Abstract

# List of contents

| Li       | List of contents i |                        |                             |    |  |

|----------|--------------------|------------------------|-----------------------------|----|--|

| Li       | List of figures v  |                        |                             |    |  |

| Li       | st of              | tables                 |                             | ix |  |

| Li       | st of              | acrony                 | /ms                         | xi |  |

| 1        | Intr               | oducti                 | on                          | 1  |  |

|          | 1.1                | Motiva                 | tion and Context            | 1  |  |

|          | 1.2                | Object                 | ives                        | 2  |  |

|          | 1.3                | Outlin                 | e                           | 4  |  |

| <b>2</b> | Stat               | e Of T                 | The Art                     | 5  |  |

|          | 2.1                | Overvi                 | ew                          | 5  |  |

|          |                    | 2.1.1                  | Amplifier Efficiency        | 6  |  |

|          |                    | 2.1.2                  | Amplifier Nonlinearities    | 6  |  |

|          | 2.2                | Linear                 | ization Techniques          | 9  |  |

|          |                    | 2.2.1                  | Feedforward Linearization   | 10 |  |

|          |                    | 2.2.2                  | Predistortion Linearization | 10 |  |

|          | 2.3                | Spectr                 | um acquisition system       | 12 |  |

|          |                    | 2.3.1                  | Components                  | 12 |  |

| 3        | Spe                | $\operatorname{ctrum}$ | Acquisition System Design   | 15 |  |

|          | 3.1                | Electro                | onic Components             | 16 |  |

|          |                    | 3.1.1                  | SAW Filter                  | 16 |  |

|          |                    | 3.1.2                  | PLL                         | 18 |  |

|          |                    | 3.1.3                  | Mixer                       | 19 |  |

|          |                    | 3.1.4                  | RMS Power Detector          | 19 |  |

|          |                    | 3.1.5                  | VGA                         | 20 |  |

|          |                    | 3.1.6                  | Microcontroller             | 21 |  |

|   |      | 3.1.7  | Oscillators                               | 22       |

|---|------|--------|-------------------------------------------|----------|

|   |      | 3.1.8  | Other Components                          | 24       |

|   | 3.2  | Design | ned Circuits                              | 25       |

|   |      | 3.2.1  | PLL                                       | 25       |

|   |      | 3.2.2  | Mixer                                     | 30       |

|   |      | 3.2.3  | SAW Filter                                | 30       |

|   |      | 3.2.4  | VGA                                       | 30       |

|   |      | 3.2.5  | RMS Power Detector                        | 31       |

|   |      | 3.2.6  | Microcontroller                           | 32       |

|   | 3.3  | Match  | ing Networks                              | 33       |

|   |      | 3.3.1  | PLL to Mixer                              | 34       |

|   |      | 3.3.2  | Mixer to SAW Filter and SAW Filter to VGA | 34       |

|   |      | 3.3.3  | VGA to RMS Power Detector                 | 37       |

|   | 3.4  | Layou  | t                                         | 38       |

|   | 3.5  | Systen | n Specification                           | 40       |

|   |      | -      |                                           |          |

| 4 | Soft | ware I | Design                                    | 42       |

|   | 4.1  |        | controller Project                        |          |

|   | 4.2  | Firmw  | vare Code                                 |          |

|   |      | 4.2.1  | Harmony                                   |          |

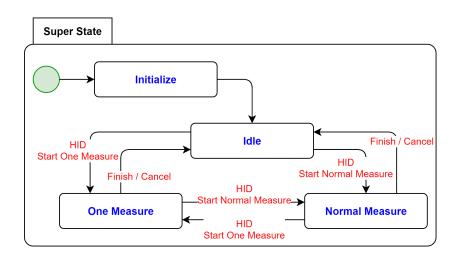

|   |      | 4.2.2  | System State Machine                      | 46       |

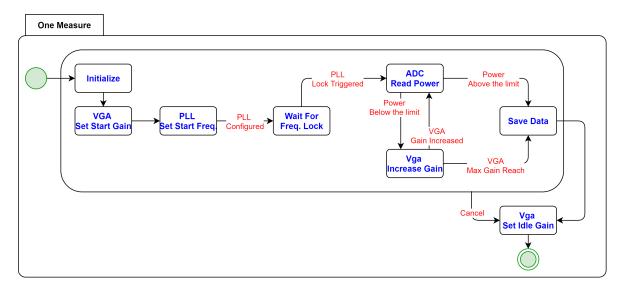

|   |      | 4.2.3  | One Measure State Machine                 | 46       |

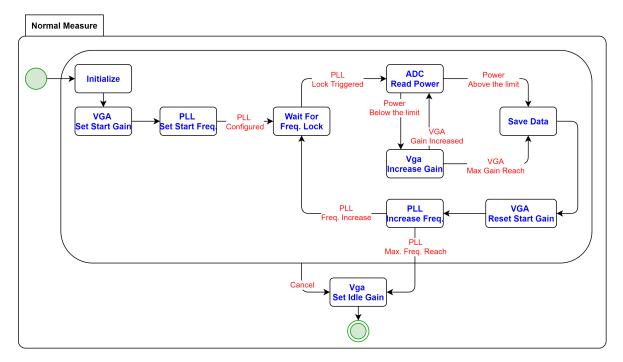

|   |      | 4.2.4  | Normal Measure State Machine              | 47       |

|   |      | 4.2.5  | Final State Machine                       | 48       |

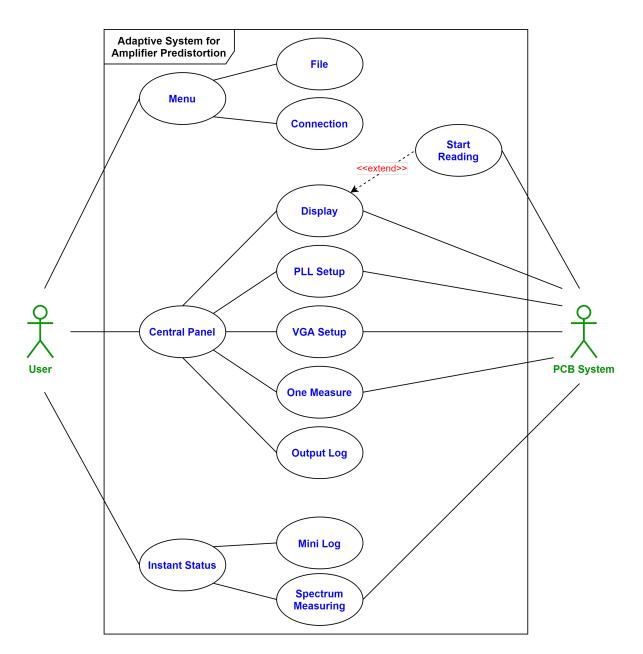

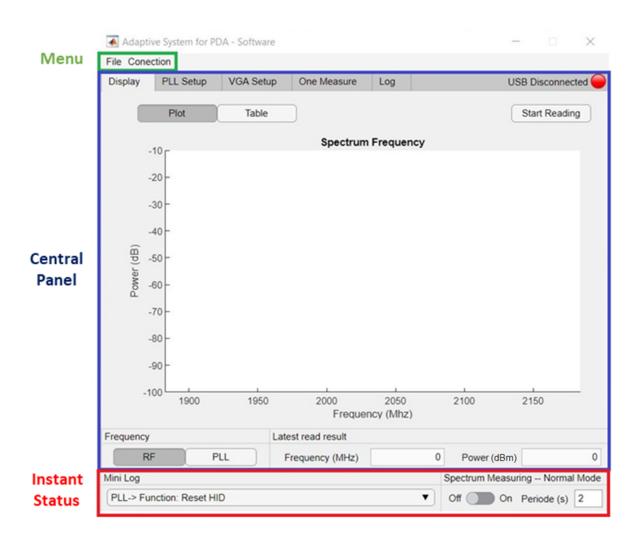

|   | 4.3  | Applic | cation Interface                          | 49       |

|   |      | 4.3.1  | Central Panel                             | 51       |

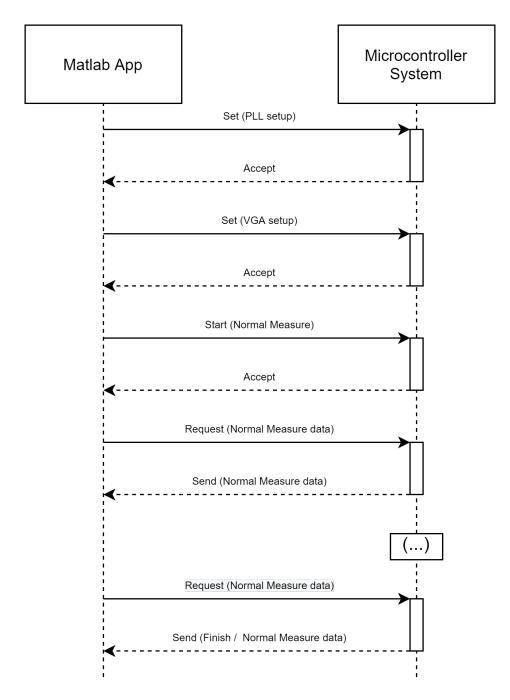

|   | 4.4  | Comm   | nunication                                | 56       |

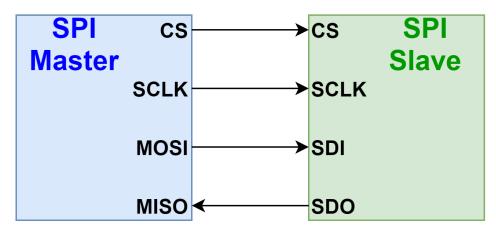

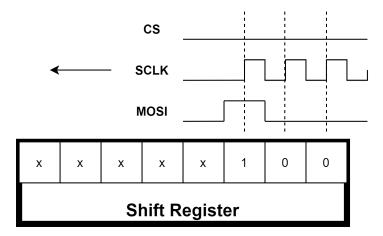

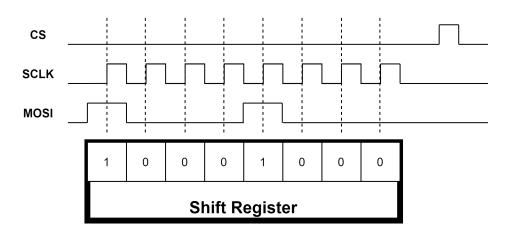

|   |      | 4.4.1  | SPI                                       | 56       |

|   |      | 4.4.2  | USB                                       | 59       |

| - | ът   |        |                                           | <u> </u> |

| 5 |      |        | nent Results                              | 62       |

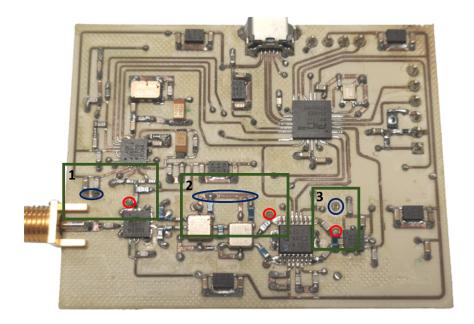

|   | 5.1  |        | Tests                                     | 62       |

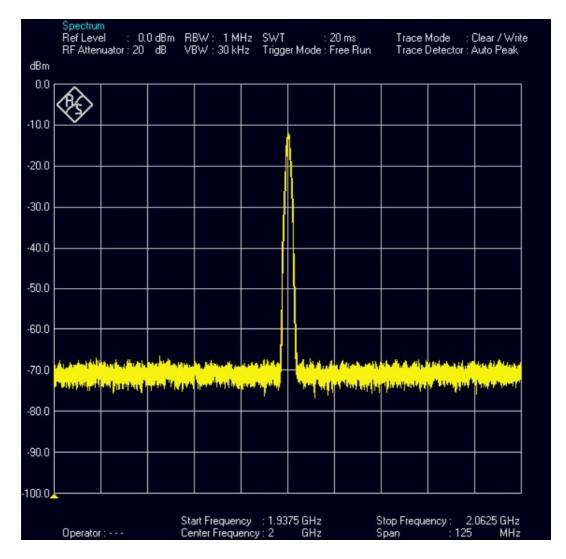

|   |      | 5.1.1  | PLL Frequency                             | 66       |

|   |      | 5.1.2  | SAW Filter                                | 68       |

|   | •    | 5.1.3  | VGA Gain                                  | 68       |

|   | 5.2  | v      | n Tests                                   | 70       |

|   |      | 5.2.1  | One Measurement                           | 72       |

|   |      | 5.2.2  | Normal Measurement                        | 73       |

|   |      | 5.2.3  | SAW Filter                                | 76       |

| 6  | Con             | clusive Remarks            | <b>7</b> 9 |

|----|-----------------|----------------------------|------------|

|    | 6.1             | Discussion and Conclusions | 79         |

|    | 6.2             | Future Work                | 80         |

| Re | e <b>fere</b> i | nces                       | 81         |

# List of figures

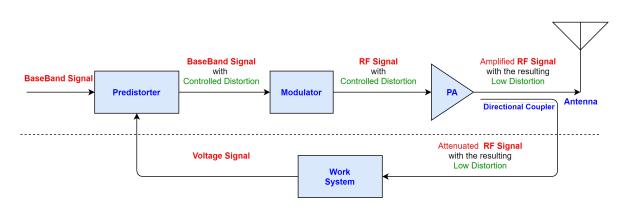

| 1.1  | Work system framed in RF transmitter chain diagram                                         | 3  |

|------|--------------------------------------------------------------------------------------------|----|

| 2.1  | Gain regions of a power amplifier                                                          | 5  |

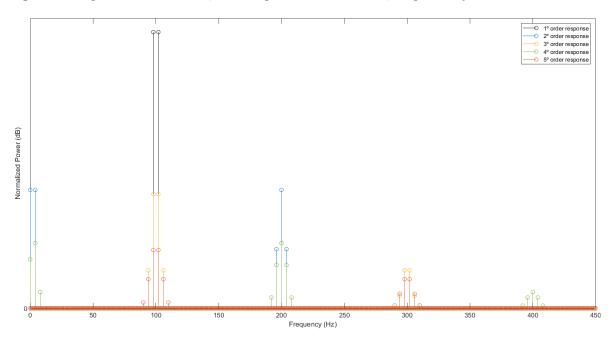

| 2.2  | Response of a 5th-order polynomial to a two tone excitation signal                         | 7  |

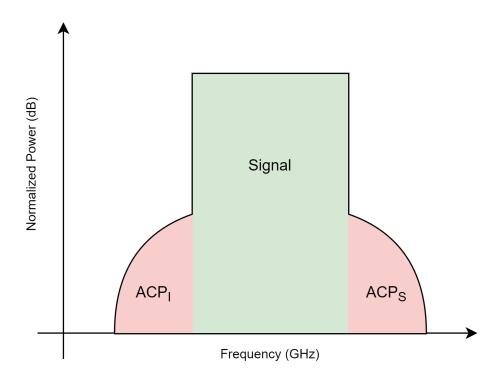

| 2.3  | Spectrum Signal with ACPR.                                                                 | 9  |

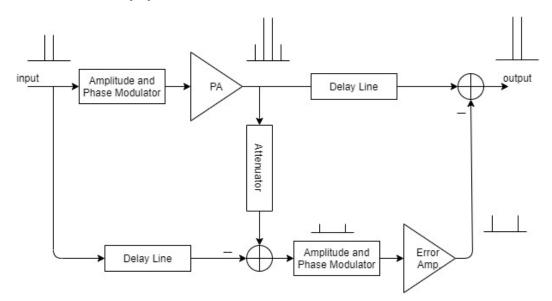

| 2.4  | Feedforward linearization block diagram                                                    | 10 |

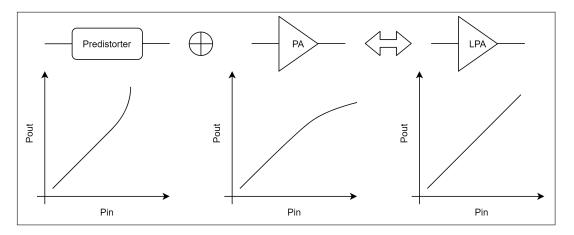

| 2.5  | Predistotion linearization technique.                                                      | 11 |

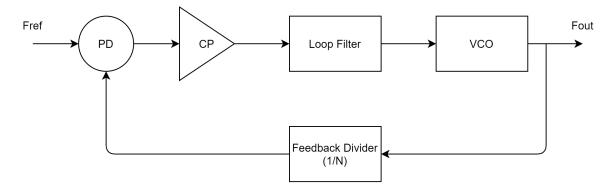

| 2.6  | PLL Core Block Diagram.                                                                    | 14 |

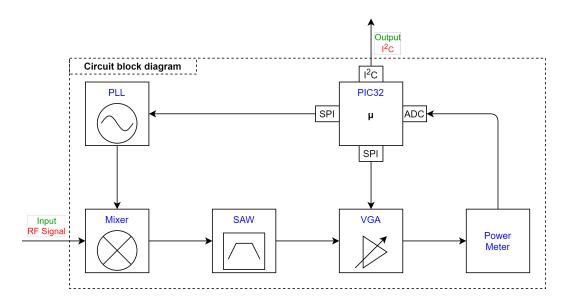

| 3.1  | System block diagram.                                                                      | 15 |

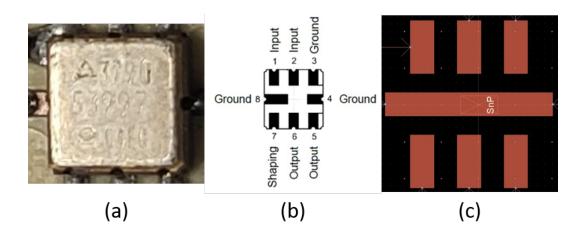

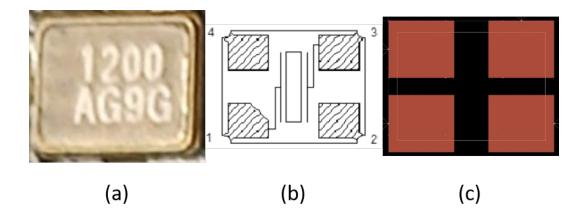

| 3.2  | The SAW filter used represented as: (a) real Image, (b) bottom view, and (c)               |    |

|      | the used layout                                                                            | 17 |

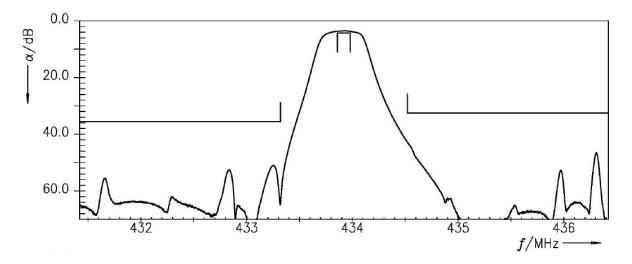

| 3.3  | Transmission coefficient of used SAW filter.                                               | 17 |

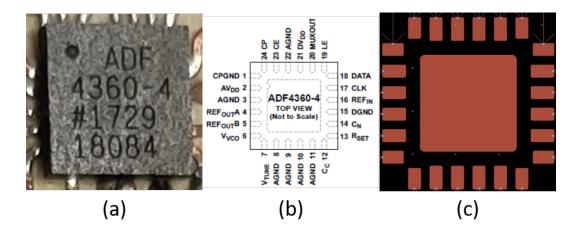

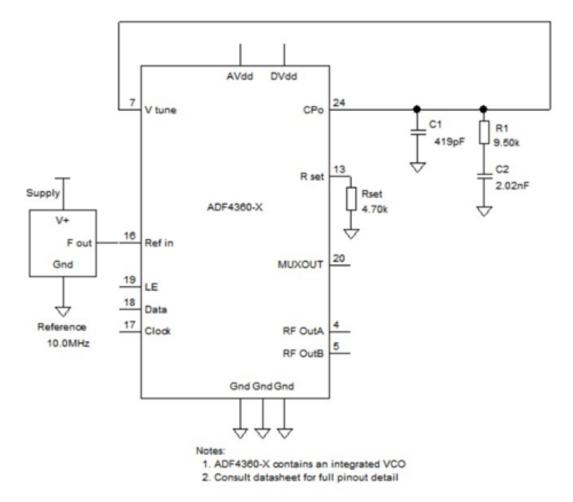

| 3.4  | The PLL used represented as: (a) real Image, (b) top view, and (c) the used                |    |

|      | layout                                                                                     | 18 |

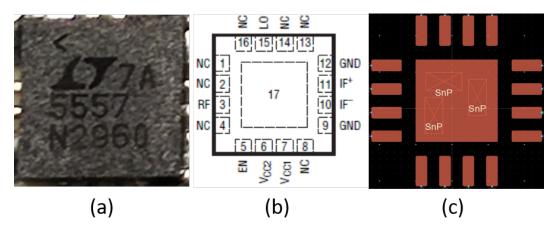

| 3.5  | The Mixer used represented as: (a) real Image, (b) top view , and (c) the used             |    |

|      | layout                                                                                     | 19 |

| 3.6  | The RMS Power Detector used represented as: (a) real Image, (b) top view,                  |    |

|      | and (c) the used layout. $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ . | 20 |

| 3.7  | The VGA used represented as: (a) real Image, (b) top view, and (c) the used                |    |

|      | layout                                                                                     | 20 |

| 3.8  | The microcontroller used represented as: (a) real Image, (b) bottom view, and              |    |

|      | (c) the used layout                                                                        | 21 |

| 3.9  | The PLL's oscillator used represented as: (a) real Image, (b) top view, and (c)            |    |

|      | the used layout                                                                            | 23 |

| 3.10 | The microcontroller's oscillator used represented as: (a) real Image, (b) top              |    |

|      | view, and (c) the used layout                                                              | 23 |

| 3.11 | PICkit 3                                                                                   | 25 |

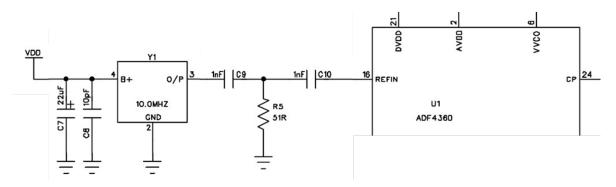

| 3.12 | Reference input circuit for the PLL                                                        | 26 |

| 3.13 | ADF4360-4 working frequency configuring on the ADIsimPLL.                                  | 27 |

| 3.14 | PLL loop filter generated by ADIsimPLL                                                           | 28 |

|------|--------------------------------------------------------------------------------------------------|----|

| 3.15 | PLL behaviour result from a simulation made on the ADIsimPLL. $\ldots$ .                         | 29 |

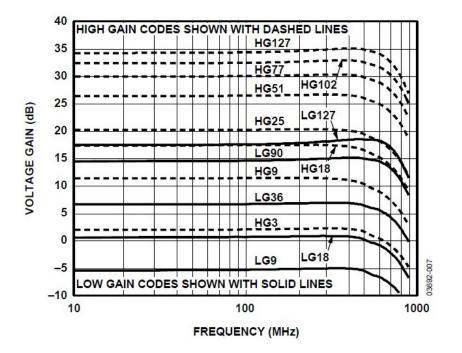

| 3.16 | VGA frequency response vs. gain code                                                             | 31 |

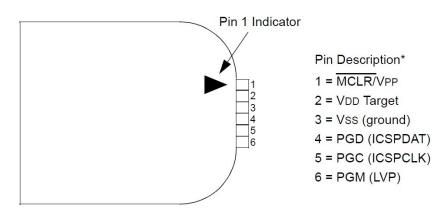

| 3.17 | PICkit 3 ports.                                                                                  | 32 |

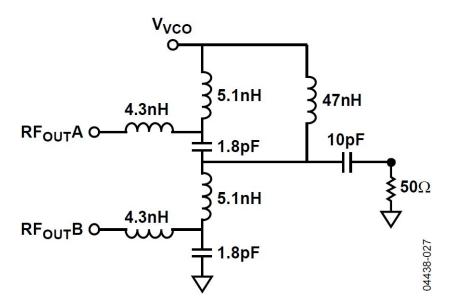

| 3.18 | LC balun used to match the PLL output. $\hdots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

| 3.19 | Matching network from mixer to first SAW filter Schematic                                        | 35 |

| 3.20 | Cascade filter Schematic                                                                         | 36 |

| 3.21 | Schematic used to create the matching network between the second SAW filter                      |    |

|      | and the VGA                                                                                      | 36 |

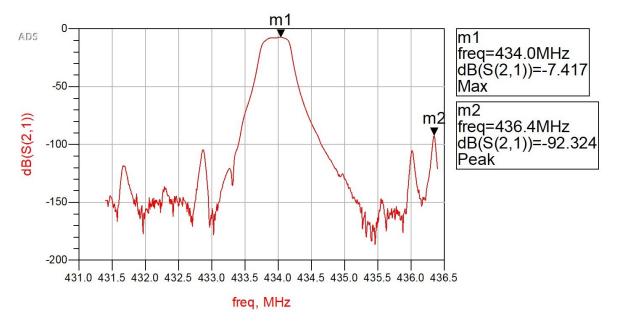

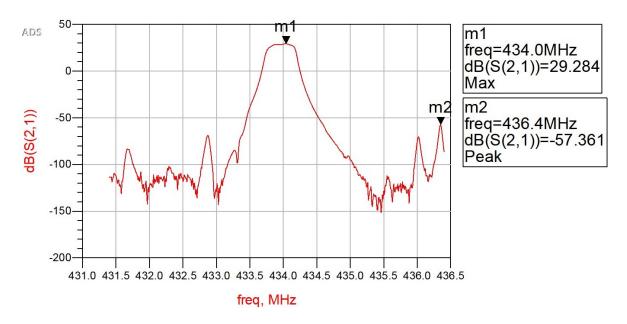

| 3.22 | S21 parameters of the filter (matching network between mixer and VGA)                            | 37 |

| 3.23 | S21 parameters system maximum gain                                                               | 38 |

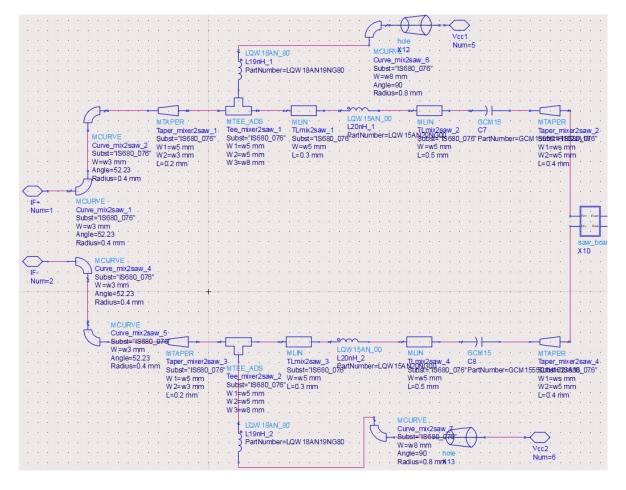

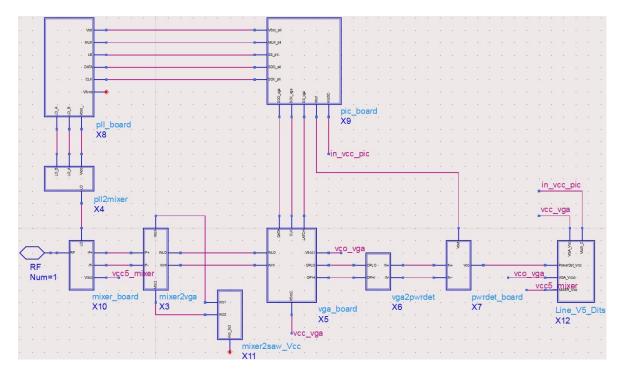

| 3.24 | System schematic with links create between the devices layouts                                   | 39 |

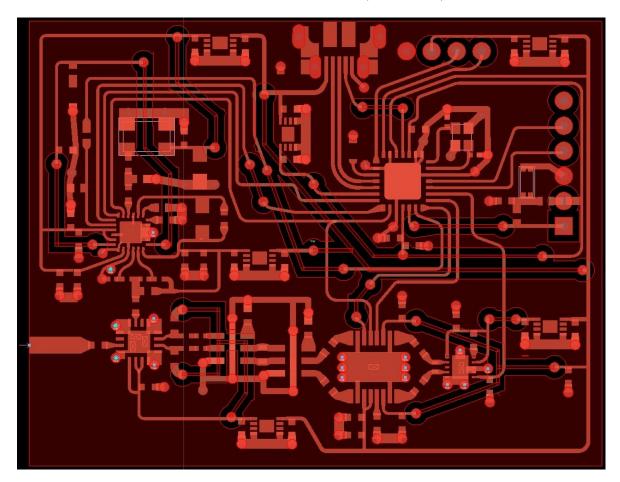

| 3.25 | System layout.                                                                                   | 40 |

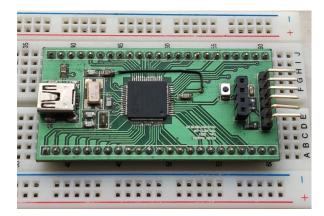

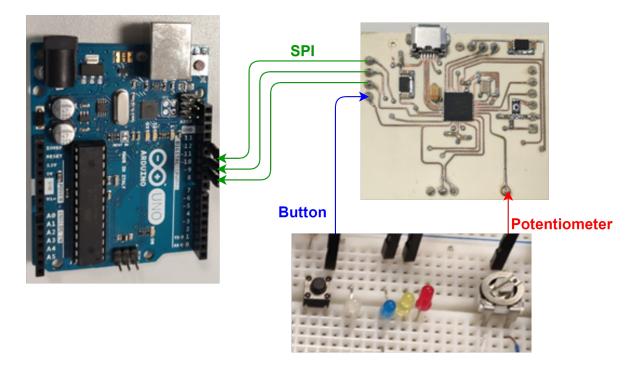

| 4.1  | PIC32MX755F512H used on the development testing.                                                 | 42 |

| 4.2  | Workbench diagram used during the development testing                                            | 43 |

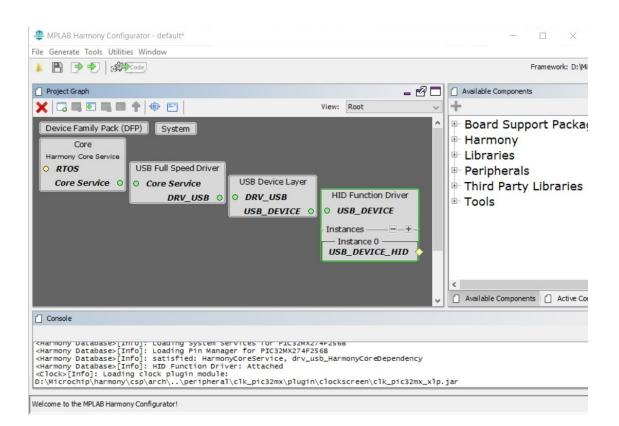

| 4.3  | Harmony Software, edited system clock configuration.                                             | 45 |

| 4.4  | Harmony Software, system libraries dependency                                                    | 46 |

| 4.5  | State diagram of the One Measure                                                                 | 47 |

| 4.6  | State diagram of the Normal Measure                                                              | 48 |

| 4.7  | State diagram of the application firmware                                                        | 49 |

| 4.8  | Use case diagram of the MATLAB application.                                                      | 50 |

| 4.9  | Display tab of the MATLAB aplication.                                                            | 51 |

| 4.10 | PLL Setup tab of the MATLAB application                                                          | 53 |

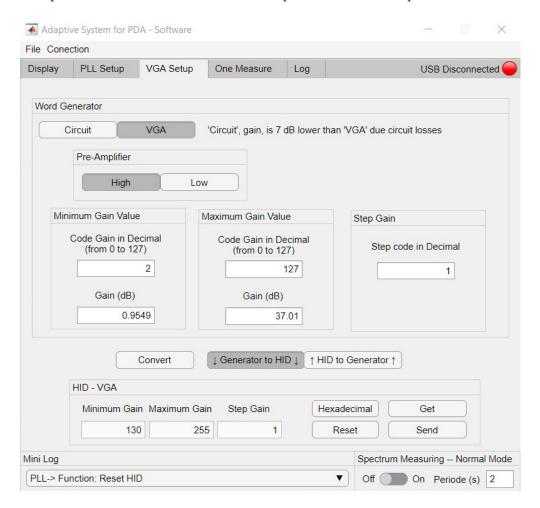

| 4.11 | VGA Setup tab of the MATLAB application.                                                         | 54 |

| 4.12 | One Measure tab of the MATLAB application.                                                       | 55 |

| 4.13 | Common SPI bus conection from master to a single slave. $\ldots$                                 | 56 |

| 4.14 | Running expample of a shift Register receiving a SPI word. $\ldots$                              | 57 |

| 4.15 | Complete SPI byte transmission to a shift Register                                               | 58 |

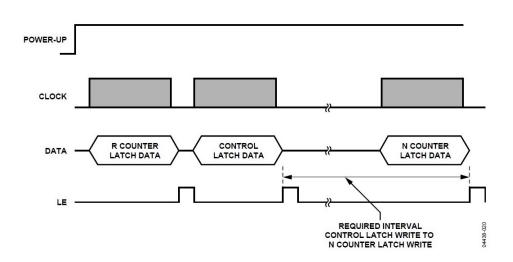

| 4.16 | ADF4360-4 Power-Up Timing.                                                                       | 59 |

| 4.17 | Interaction diagram to proceed a Normal Measure.                                                 | 61 |

| 5.1  | Workbench diagram.                                                                               | 63 |

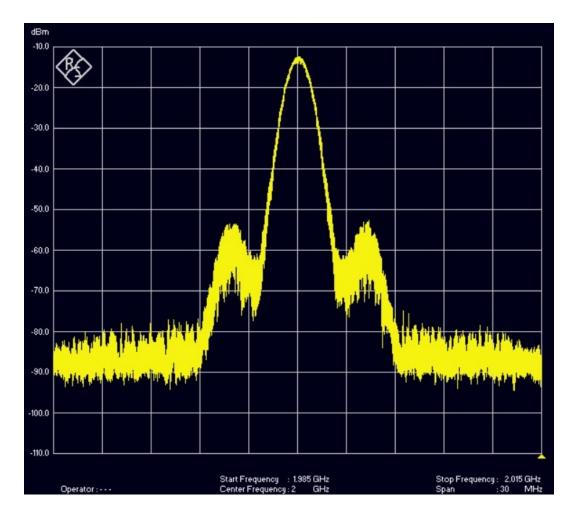

| 5.2  | Sine RF signal at 2 GHz generated by VGS, photo taken on the FSH4View. $\ .$ .                   | 63 |

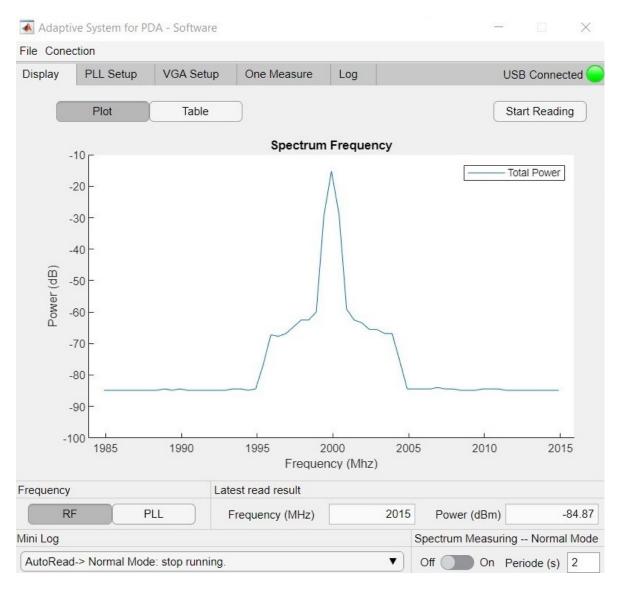

| 5.3  | Initial test with the sine signal at 2GHz on the One Measure tab of the                          |    |

|      | MATLAB application.                                                                              | 64 |

| 5.4  | Spectrum Analizer with a passive probe.                                                          | 65 |

| 5.5  | System testing points, (the reds circles represent the testing points and the          |    |

|------|----------------------------------------------------------------------------------------|----|

|      | blues the nearest grounds), to measure: 1- PLL output, 2- SAW filter output,           |    |

|      | 3- VGA output                                                                          | 66 |

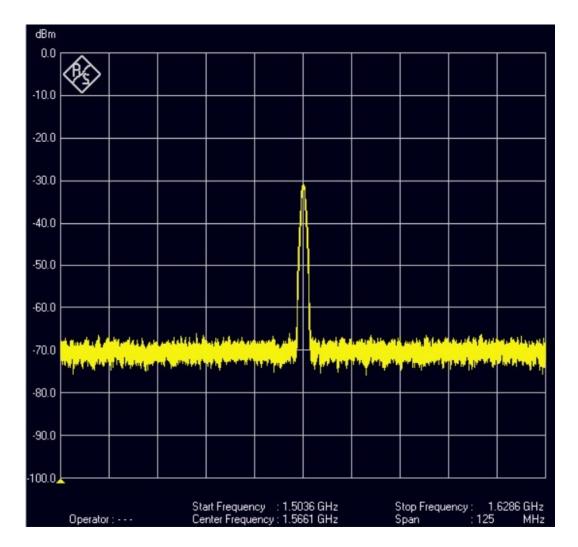

| 5.6  | PLL output frequency, photo taken on the FSH4View                                      | 67 |

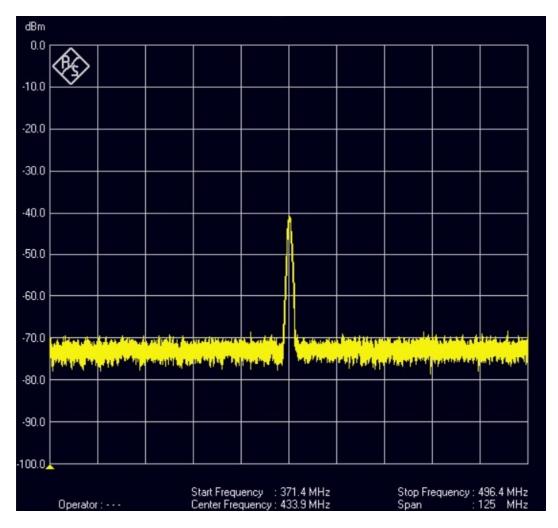

| 5.7  | SAW filter output frequency, photo taken on the FSH4View                               | 68 |

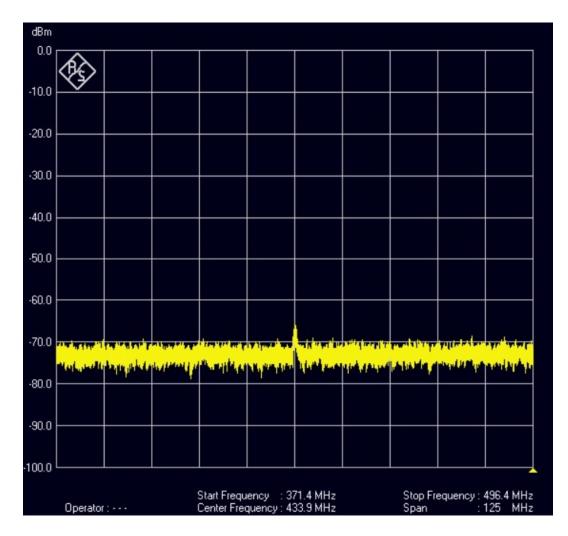

| 5.8  | VGA output frequency, photo taken on the FSH4View                                      | 69 |

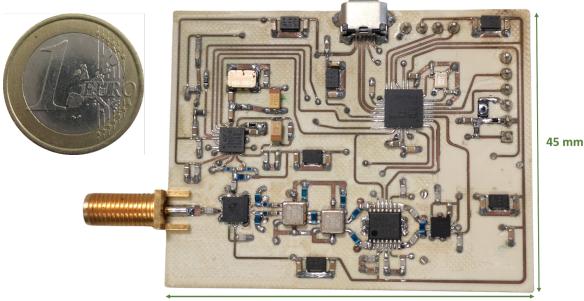

| 5.9  | Final system board.                                                                    | 70 |

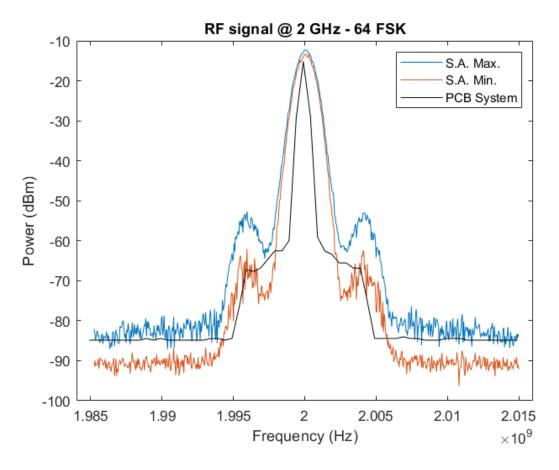

| 5.10 | $64~\mathrm{FSK}$ signal at 2 GHz generated by VGS, photo taken on the FSH4View. $~$ . | 71 |

| 5.11 | System test with the 64 FSK signal at 2GHz on the One Measure tab of the               |    |

|      | MATLAB application.                                                                    | 72 |

| 5.12 | PLL configuration used on the Normal Measure test                                      | 73 |

| 5.13 | VGA configuration used on the Normal Measure test                                      | 74 |

| 5.14 | Normal Measure result for the input 64 FSK signal on the Display the tab of            |    |

|      | the MATLAB application                                                                 | 75 |

| 5.15 | Overlap result for the input 64 FSK signal tests.                                      | 76 |

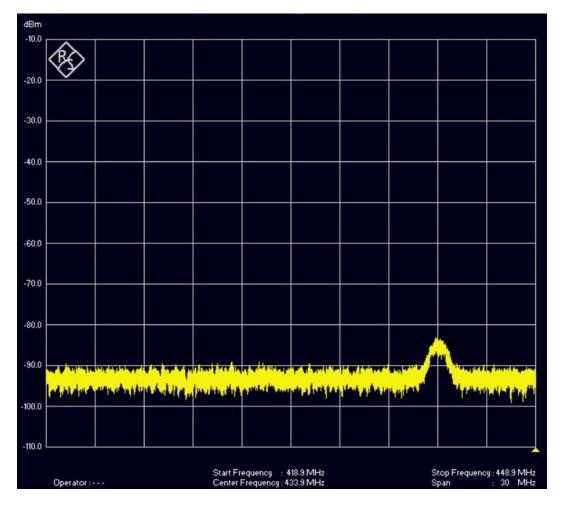

| 5.16 | SAW filter output with a central frequency of 1991 MHz, photo taken on the             |    |

|      | FSH4View.                                                                              | 77 |

| 5.17 | SAW filter test with the 64 FSK signal at 1991 MHz on the One Measure tab $$           |    |

|      | of the MATLAB application.                                                             | 78 |

# List of tables

| 2.1 | Polynimial Filter model response to a two-tone signal at frequencies w1 and |

|-----|-----------------------------------------------------------------------------|

|     | w2, and amplitudes A1 and A2                                                |

| 3.1 | System consumption current                                                  |

| 3.2 | System gain and noise figure                                                |

# List of acronyms

| $4\mathrm{G}$             | Fourth Generation                             |

|---------------------------|-----------------------------------------------|

| $5\mathrm{G}$             | Fifth Generation                              |

|                           |                                               |

| AC                        | Alternating Current                           |

| ACPR                      | Adjacent Channel Power Ratio                  |

| ADC                       | Analog-to-Digital Converter                   |

| ADS                       | Advanced Design System                        |

| AP                        | Access Point                                  |

| APD                       | Analog Predistorter                           |

| CCPR                      | Co-Channel Power Ratio                        |

| CP                        |                                               |

| CP                        | Charge Pump                                   |

| DAC                       | Digital-to-Analog Converter                   |

| DC                        | Direct Current                                |

| DPD                       | Digital Predistorter                          |

| ETSI                      | European Telecommunications Stander Institute |

| FCC                       | Federal Communications Commission             |

| FSK                       | Frequency-Shift Keying                        |

| HID                       | Human Interface Device                        |

| $\mathbf{I}^2 \mathbf{C}$ | Inter-Integrated Circuit                      |

| I/O                       | Input/Output                                  |

| IDE                       | Integrated Development Environment            |

| IF                        | Intermediate Frequency                        |

| IMD                       | Intermodulation Distortion                    |

| IoT                       | Internet of Things                            |

| IT                        | Institute of Telecommunications               |

|                           |                                               |

| LDO                       | Low-Dropout Regulator                                                                                                      |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| MIMO                      | Multiple-Input and Multiple-Output                                                                                         |  |

| MISO                      | Master In Slave Out                                                                                                        |  |

| MOSI                      | Master Out Slave In                                                                                                        |  |

| PA                        | Power Amplifier                                                                                                            |  |

| PC                        | Personal Computer                                                                                                          |  |

| PCB                       | Printed-Circuit Board                                                                                                      |  |

| PD                        | Phase Detector                                                                                                             |  |

| PEP                       | Peak Envelope Power                                                                                                        |  |

| PLL                       | Phase Lock Loop                                                                                                            |  |

| PPS                       | Peripheral Pin Select                                                                                                      |  |

| $\mathbf{RF}$             | Radio Frequency                                                                                                            |  |

|                           |                                                                                                                            |  |

| RMS                       | Root Mean Square                                                                                                           |  |

| RMS<br>SAW                | Root Mean Square<br>Surface Acoustic Wave                                                                                  |  |

|                           | -                                                                                                                          |  |

| SAW                       | Surface Acoustic Wave                                                                                                      |  |

| SAW<br>SPI                | Surface Acoustic Wave<br>Serial Peripheral Interface                                                                       |  |

| SAW<br>SPI<br>TCXO        | Surface Acoustic Wave<br>Serial Peripheral Interface<br>Temperature Compensated Crystal Oscillator                         |  |

| SAW<br>SPI<br>TCXO<br>USB | Surface Acoustic Wave<br>Serial Peripheral Interface<br>Temperature Compensated Crystal Oscillator<br>Universal Serial Bus |  |

## Chapter 1

## Introduction

#### 1.1 Motivation and Context

Nowadays, there is a steady increase on the number of equipment that require wireless communications. Not only there is a ubiquitous amount of the common cell phone, the Internet of Things (IoT) is having an explosive growth, which also will put an extra strain on the current infrastructure and some of the new technologies will have new requirements that are not possible with the current Fourth Generation (4G) cellular communication networks.

To solve this, the new wireless generation, the Fifth Generation, will need to address these issues, meaning that a 5G site will need not only to support a huge number of user equipment, but also be ready for any special constrains requested by them. Such common needs include very low latency, high data rate, reliability, security concerns and better costand energy-efficiency [1]. To achieve these obligations, the foundations of 5G will rely on edge technology that lay on millimetre waves, small cell, Multiple-Input and Multiple-Output (MIMO), beamforming, and full duplex. Millimetre waves refer to the usage of frequencies over 6 GHz allowing for wider channel bandwidths, small cells are used as Access Points (APs) used for extending coverage beyond regular base stations, massive MIMO allows the use of multiple transmitters to deliver a beam signal [2].

At the moment, the solutions used on 4G to obtain the aforementioned cost/energy-efficiency are not good enough for current stander because they use a higher efficiency Radio Frequency (RF) Power Amplifiers (PAs) that cause unacceptable distortion in form of Intermodulation Distortion (IMD), which produce Adjacent Channel Power Ratio (ACPR), Co-Channel Power Ratio (CCPR) [3][4]. These spurious frequencies outside of the desired bandwidth, need to be under the limitations impose by Federal Communications Commission (FCC) and European Telecommunications Stander Institute (ETSI).

To remedy this fault, a predistorter could be added to the transmitter chain to correct the signal. While this is a valid answer for the days before 5G, the components used for the predistorter are usually very expensive and use too much power [5]. This is a new problem caused by the use of millimetres waves and the surge of cell availability with its reliance on MIMO technology, which requires a massive number of transmitters, and a high number of low-power amplifiers per transmitter.

A predistorter is a device that modifies the input signal of the PA in a way that cancels the distortions introduced by the PA. There are two types of predistorters, the Digital Predistorter (DPD) and the Analog Predistorter (APD).

The APD uses an analog circuit, that relies on a predetermined open loop to cancel the distortion.

The DPD functions as an algorithm on a digital processor. Some of them use the output PA signal read through an Analog-to-Digital Converter (ADC) and is analysed in real time determine the distortion caused by the PA and corrects the input signal. The main drawback of this solution is that the processor used must have a high clock rate to be able to sample the signal, especially when operating in wideband applications.

In summary, the DPD is a better approach to obtain a higher quality signal, however the processor/ADC combination used is not as cost/energy efficient as an APD.

The target of this work is to develop a prototype of a simple (and low cost) circuit which measures the spectrum of the output signal of a PA, gathering the spectrum in a low grade microcontroller for further using such information to tune the parameters of the predistorter that compensates the PA. This prototype will not be based on a very fast sampler, but will consider a very sharp band-pass filter (followed by a power meter) through which the spectrum of the PA output signal is slided.

#### 1.2 Objectives

The scope of this work was the development of a hardware platform that provided an adapting mechanism to a predistorter. This hardware should be capable of measuring an output signal from a PA, then it should calculate the distortion of the PA's output. With the calculation of the distortion completed, its value is used to act over a predistorter. This back-loop system optimizes the predistorter, improving its capability to reduce the distortion at the PA signal output. Figure 1.1 frames the created system on a transmitter chain.

Figure 1.1: Work system framed in RF transmitter chain diagram.

The implementation of this adaptative system should be done using low complexity components and low complexity processing units (e.g. a microprocessor), both with a low rate of energy consumption.

Some of the most important requirements for these system's performance are as follow:

- Input Central Frequency of 2 GHz: The circuit must be capable of measuring signals with a central frequency around 2 GHz, for which some amplifiers available at the RF Laboratory at the Institute of Telecommunications (IT) were designed.

- Input bandwidth of 20 MHz: The input signal should have a bandwidth up to 20 MHz, which is a bandwidth already used in some mobile application.

- Input power level of -10 dBm: The PA signal output, which is the input signal of the designed adaptative system, would be acquired through a directional coupler, allowing a reliable copy of the signal without damaging the power of the original output signal. The signal obtained by the directional coupler is then much lower than the transmitting signal, with a level around -10 dBm.

- Power range of 90 dB: This value covers the regulation set by the entities such as FCC and ETSI, which state that for some mobile application, the adjacent channel power needs to be 65 dB lower than the transmitting signal [6].

- Output: The output of this system should be sampled by Digital-to-Analog Converters (DACs) and generate the necessary voltage signal to control the APD (predistorter).

Succinctly, the specifications and requirements of this system were set taking in consideration the state of the art for 5G technologies, but also the possibility of creating a prototype with the tools provided by IT.

#### 1.3 Outline

The rest of this document is structured as follows:

Chapter 2: This chapter overviews the most important points relative to the objective of this work. The chapter begins explaining the reason why PAs suffer from signal distortion and the problems associated with it. Subsequently, some solutions to the distortion problem are presented. This chapter ends with the introduction of the proposed adaptive method to optimize a predistorter.

Chapter 3: In this chapter, it is explained the thought behind every component that was chosen, followed by a description of the design process considered for the implementation of the prototype circuit and sub-circuits. Afterwards, the Matching Networks between devices are presented and finally it is analysed the layout of the entire system.

Chapter 4: This chapter is focused on the software produced for this project. It begins with the introduction of the firmware developed to control the microcontroller, followed by the presentation of the user application to control the system over a Personal Computer (PC). This chapter ends with the overview of the Serial Peripheral Interface (SPI) communication used to control the devices, and communication between both software.

Chapter 5: This chapter contains the test and the results of the developed system. The final modifications on the Printed-Circuit Board (PCB), which led to the final working system discussed here. It also describes some tests focused on the crucial parts of the system.

Chapter 6: The last chapter presents the conclusions and ends with some suggestions for future work.

## Chapter 2

## State Of The Art

This chapter shows some of the existing technologies and techniques that are used in this work, along with some potential alternative examples.

#### 2.1 Overview

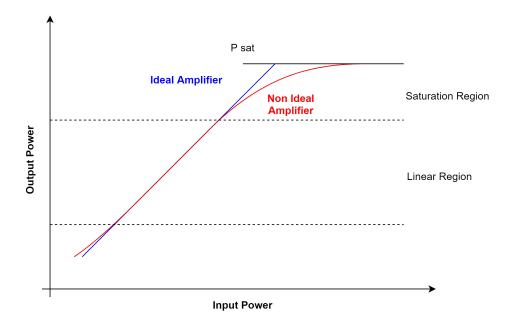

A power amplifier is a circuit that converts a Direct Current (DC) power supply into an amplified Alternating Current (AC) output signal, whose main components are RF transistors, but since in the real world there are no perfect components, the amplifier is not linear in all of its conductive zone presenting, therefore, a nonlinear behavior [7]. In Figure 2.1 it can be seen a sketch of the gain of a regular power amplifier.

Figure 2.1: Gain regions of a Power Amplifier.

#### 2.1.1 Amplifier Efficiency

The efficiency of a PA is determined by its output power divided by the power supplied to the PA (from the DC supply and from the input signal generator) Equation (2.1), therefore, since the output power achieves its maximum value on saturation zone and the DC power spent does not scale linearly, it can be concluded that this is the region where the PA has the most efficiency. Since this is out of the linear zone, it demonstrates that there is a trade-off between linearity and the PA efficiency, which is known as the power-spectrum efficiency trade-off [7].

$$\eta_t = \frac{P_{out}}{P_{dc} + P_{in}}.$$

(2.1)

There are multiple choices for the design of a PA. Each design will have a different impact on its efficiency and linearity, being the bias point of the transistors determinant for the overall behavior [8].

The PA bias defines the conduction period of the output current and will dictate the class of operation of the PA. Therefore, the bias point has direct impact on the PA efficiency, on its linearity, and also on the maximum output power [9]. The class A, whose bias allows the RF transistor to have a conduction angle of the output current of 360 °. This class is inherently the most linear but also the least efficient, with a maximum theoretical efficiency of 50 %, but due to real-world constraints, most applications usually cannot reach more than 25 % of efficiency [9].

There are other amplifier classes of operation, where their bias point is set to conduct on a lower conduction angle, as a result it is possible to achieve much better efficiency with a cost of lowering the linearity mainly due to the insertion of distortion on the signal [9]. Nowadays, these classes are a better choice than the class A, because there are techniques that can be used to easily remove the added harmonics and they keep the advantage of greater efficiency [4]. In the end, the root cause of the distortion seen on the output wave is the clipped signal caused by the saturation zone of the PA.

#### 2.1.2 Amplifier Nonlinearities

The nonlinearity of the system comes mostly from the compression behaviour of the amplifier, meaning that the output power can no longer maintain the gain as the input power increases [9]. These nonlinearities cause Intermodulation Distortion (IMD) and Harmonic Distortion, producing a spectral transformation [7]. With this in mind, the PA has to be designed with a trade-off between power efficiency and spectral efficiency.

To illustrate the impact of nonlinearity on the signals frequency content, Figure 2.2 presents the response of a 5th-order polynomial to a two tone excitation signal (of frequency close to 100 Hz), and in Table 2.1 are represented the components for the distinct frequencies generated by a Polynomial Filter model, whose pth-order kernel is  $H_p(.)$ , when excited with a two-tone

signal at frequencies  $\omega_1$  and  $\omega_2$ , and amplitudes  $A_1$  and  $A_2$ , respectively.

Figure 2.2: Response of a 5th-order polynomial to a two tone excitation signal.

In Figure 2.2 it can be seen that distortion appears at frequency bands distinct from the fundamental one (these can be removed by filtering), but distortion terms are also present within the fundamental band (these cannot be removed by a simple linear filter). One thing to note is that the even orders of the system response do not appear near the original frequencies so they are an issue easy to solve.

The odd order terms cause an increase both on the CCPR and on the ACPR, described in Equation (2.2) and represented in Figure 2.3 [7].

$$ACPR = \frac{IntegratedChannelSignalPower}{IntegratedAdjacent - ChanelPower_{I,S}}.$$

(2.2)

| Response Frequency $(-\omega_m)$  | Response Amplitude                                                                           | Response Type        |

|-----------------------------------|----------------------------------------------------------------------------------------------|----------------------|

| 1st Order or Linear Response      |                                                                                              |                      |

| $-\omega_1$                       | $^{1/\!2}\cdot A_2^{st}\cdot H_1(-\omega_2)$                                                 |                      |

| $-\omega_2$                       | $1/2 \cdot A_1^{\overline{*}} \cdot H_1(-\omega_1)$                                          | Lincon Desmanas      |

| $\omega_1$                        | $1/2 \cdot A_1^* \cdot H_1(\omega_1)$                                                        | Linear Response      |

| $\omega_2$                        | $1/2 \cdot A_2^* \cdot H_1(\omega_2)$                                                        |                      |

| 2nd Order Response                |                                                                                              |                      |

| $-2\omega_2$                      | $^{1/\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$               | 2nd Order            |

| $-2\omega_1$                      | $^{1/\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$               | Harmonic             |

| $2\omega_1$                       | $^{1/4}\cdot A_1^{st 2}\cdot H_2(\omega_1,\omega_1)$                                         | Distortion           |

| $2\omega_2$                       | $1/4 \cdot A_2^{*2} \cdot H_2(\omega_2, \omega_2)$                                           | Distortion           |

| $\omega_1 - \omega_2$             | $1/2 \cdot A_1 \cdot A_2^* \cdot H_2(\omega_1, -\omega_2)$                                   | 2nd Order            |

| $\omega_2 - \omega_1$             | $^{1/2}\cdot A_{1}^{st}\cdot A_{2}\cdot H_{2}(-\omega_{1},\omega_{2})$                       | Intermodulation      |

| $\omega_1 + \omega_2$             | $1/2 \cdot A_1 \cdot A_2 \cdot H_2(\omega_1, \omega_2)$                                      | Distortion           |

| $-\omega_1 - \omega_2$            | $^{1/2} \cdot A_{1}^{*} \cdot A_{2}^{*} \cdot H_{2}(-\omega_{1},-\omega_{2})$                |                      |

| $\omega_1 - \omega_1$             | $1/2 \cdot  A_1 ^2 \cdot A_2 \cdot H_2(-\omega_1,\omega_1)$                                  | Bias Point           |

| $\omega_2 - \omega_2$             | $1/2 \cdot A_1 \cdot  A_2 ^2 \cdot H_2(-\omega_2,\omega_2)$                                  | Shift                |

| 3rd Order Response                |                                                                                              |                      |

| $-3\omega_2$                      | $1/8 \cdot A_2^{*3} \cdot H_3(-\omega_2, -\omega_2, -\omega_2)$                              | 3rd Order            |

| $-3\omega_1$                      | $1/8 \cdot A_1^{*3} \cdot H_3(-\omega_1, -\omega_1, -\omega_1)$                              | Harmonic             |

| $3\omega_1$                       | $1/8 \cdot A_{1}^{*3} \cdot H_3(\omega_1, \omega_1, \omega_1)$                               | Distortion           |

| $3\omega_2$                       | $1/\!\!8\cdot A_2^{*3}\cdot H_3(\omega_2,\omega_2,\omega_2)$                                 |                      |

| $-2\omega_2-\omega_1$             | $^{3/8} \cdot A_{1}^{*} \cdot A_{2}^{*2} \cdot H_{3}(-\omega_{2}, -\omega_{2}, -\omega_{1})$ |                      |

| $2\omega_2 + \omega_1$            | $3/8 \cdot A_1 \cdot A_2^2 \cdot H_3(\omega_1, \omega_2, \omega_2)$                          |                      |

| $2\omega_1 + \omega_2$            | $3/8 \cdot A_1^2 \cdot A_2 \cdot H_3(\omega_1, \omega_1, \omega_2)$                          | 3rd Order            |

| $2\omega_1 - \omega_2$            | $^{3/8} \cdot A_{1}^{*2} \cdot A_{2}^{*} \cdot H_{3}(-\omega_{2}, -\omega_{1}, -\omega_{1})$ | Intermodulation      |

| $-2\omega_2 + \omega_1$           | $^{3/8} \cdot A_{1} \cdot A_{2}^{*2} \cdot H_{3}(-\omega_{2}, -\omega_{2}, \omega_{1})$      | Distortion           |

| $-2\omega_1 + \omega_2$           | $\frac{3}{8} \cdot A_1^{*2} \cdot A_2 \cdot H_3(-\omega_1, -\omega_1, \omega_2)$             |                      |

| $2\omega_1 - \omega_2$            | $\frac{3}{8} \cdot A_1^2 \cdot A_2^* \cdot H_3(-\omega_2,\omega_1,\omega_1)$                 |                      |

| $2\omega_2 - \omega_1$            | $\frac{3}{8} \cdot A_1^* \cdot A_2^2 \cdot H_3(-\omega_1, \omega_2, \omega_2)$               |                      |

| $-\omega_2$                       | $\frac{3}{8} \cdot A_2^* \cdot  A_2 ^2 \cdot H_3(-\omega_2, -\omega_2, \omega_2)$            | AM/AM Conversion     |

| $\omega_2$                        | $\frac{3}{8} \cdot A_2 \cdot  A_2 ^2 \cdot H_3(-\omega_2, \omega_2, \omega_2)$               | (Gain Compression)   |

| $\omega_1$                        | $\frac{3}{8} \cdot A_1 \cdot  A_1 ^2 \cdot H_3(-\omega_1, \omega_1, \omega_1)$               | and AM/PM Conversion |

| $-\omega_1$                       | $\frac{3}{8} \cdot A_1^* \cdot  A_1 ^2 \cdot H_3(-\omega_1, -\omega_1, \omega_1)$            | (Phase Shift)        |

| $\omega_1 + \omega_2 - \omega_2$  | $\frac{3}{4} \cdot A_1^* \cdot  A_2 ^2 \cdot H_3(-\omega_2, \omega_1, \omega_2)$             | Response             |

| $-\omega_1 + \omega_2 - \omega_2$ | $^{3/4} \cdot A_{1}^{*} \cdot  A_{2} ^{2} \cdot H_{3}(-\omega_{2}, -\omega_{1}, \omega_{2})$ | Sensitivity          |

| $-\omega_2 + \omega_1 - \omega_1$ | $\frac{3}{4} \cdot A_2^* \cdot  A_1 ^2 \cdot H_3(-\omega_2, -\omega_1, \omega_1)$            | Loss                 |

| $\omega_2 + \omega_1 - \omega_1$  | ${}^{3/\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$             | 2000                 |

Table 2.1: Polynimial Filter model response to a two-tone signal at frequencies  $\omega_1$  and  $\omega_2$ , and amplitudes  $A_1$  and  $A_2$ .[7].

Figure 2.3: Spectrum Signal with ACPR.

Looking into the future, the 5G requirements will impose a high level of efficiency, and to achieve this the RF power transistor will have to operate in such a way that will inevitably create significant distortion [4].

There are techniques that can improve the overall performance of the PA. One well known is the linearization technique, as the name implies it uses elements that leads a PA to have a more linear behaviour. The main objective is to reduce the amplifier distortion to acceptable levels by adding low power consuming components, so that improving the linearity of the system does not cost too much of its efficiency.

#### 2.2 Linearization Techniques

A simple way to linearize a PA is "backing off" the output power, but as this compromises the efficiency, it is not the most suitable technique to linearize the PA [4]. For that purpose, there are better linearization techniques, which can achieve a better spectral efficiency without losing too much power efficiency.

There are several linearization techniques, each with different approaches on how to linearize the PA, the three most common techniques are the Feedforward Linearization, the Analog Predistortion Linearization, and the Digital Baseband Predistortion Linearization.[9]

#### 2.2.1 Feedforward Linearization

The feed-forward technique uses two amplifiers. The first to be considered, is the main amplifier where it creates an output signal composed by the amplified frequencies and the added distortion product obtained from the PA nonlinearity.

The second amplifier, the error amplifier, uses as input signal the distortions produced by the main PA. This correction signal is then used to cancel the distortions introduced by the previous PA. Theoretically, this approach allows the acquisition of a more precise output amplified signal and a simple design representation of this approach can be seen in Figure 2.6 [9].

Feedforward linearizers can achieve very high linearity and can support a wide bandwidth. However, it has a major drawback, since the error amplifier needs to be perfectly linear, it cannot operate with a high efficiency, leading to a significant decrease of the overall efficiency of the overall amplifier [10].

Figure 2.4: Feedforward linearization block diagram.

#### 2.2.2 Predistortion Linearization

The predistortion can be performed either in analog or digital domain, and can operate at baseband, Intermediate Frequency (IF) or RF frequency. This technique produces a calculated distortion on the input signal, therefore, when the signal is amplified in the main amplifier, a clean output will be provided. This is possible because the non-linearity of the PA is cancelled by the distortion added by the predistorter. An illustrative example is presented in Figure 2.5 [9].

Figure 2.5: Predistotion linearization technique.

#### Analog Predistorter

The Analog Predistorter (APD) can be used in both RF frequencies and Baseband frequencies. Nowadays, this type of predistorters is mostly used for high power applications with bandwidths on the higher end of GHz [10].

A use case of APD is to split the input signal into a distortion path and a linear path. The signal on the distortion path is run through a "distortion creator" which will introduce a similar error as the main amplifier would create. The objective is that when later combining these two paths, they would cancel each other and provide an output signal without the usual distortion created by a standard PA [9].

The APD has low implementation cost, typically has high efficiency, and can perform on wide bandwidth signals, but lacks linearity performance when compared with other options [10].

#### **Digital Predistortion Linearization**

The Digital Predistorter (DPD) is based on processing the signal digitally, at baseband frequencies. The predistortion is done digitally by using the inverse characteristic of the transfer function of the PA [9].

This predistorter can be designed with either a close loop or an open loop, and some of the better options is to use a Lookup Table (LUT). A Lookup Table can be obtained through constellation mapping, signal mapping and the complex gain system of the amplifier. With it, the errors created by the PA can be considered beforehand and will be cancelled on the output signal [9].

A DPD has excellent linearity, typically good power efficiency, but falls a bit short on the bandwidth it can cover [10].

For the current state of technologies available, the preferable solution would be to have

a predistorter capable of handling wide bandwidth signals, with the highest linearization performance possible, an additional feedback loop so that it could correct any environmental changes, low implementation costs and high efficiency.

#### 2.3 Spectrum acquisition system

This section will expose two different approaches to measure the spectrum power of the signal, being the first approach to read the power at baseband frequencies, while the second approach at an IF frequency.

For the baseband method, the RF input signal passes through an envelope detector, resulting in its baseband signal, with this output signal being subsequently filtered by a variable band-pass filter. With this filter, it is possible to go through all of the bandwidth of the signal with the purpose of measuring the resulting power and, as a result, the power spectrum of the signal can be determined.

This method relies on an envelope detector and a filter. Even though an envelope detector was a device already used on IT, with good results, choosing a suitable filtering method is a problem, as the baseband working frequencies are from 0 MHz to 20 MHz, and finding components that allow a precise variable band-pass filter with high bandwidth at low frequencies is a difficult task.

The second method uses a down-converting mixer, this would convert the RF input signal to an IF signal where this can be filtered and then have its power measured. The quality of this system relies mainly in two components. First, it is required a frequency generator with the ability to provide frequencies with good precision and stability. The mixer will then use this frequency to shift the RF signal to IF frequencies. A Phase Lock Loop (PLL) is an example of a device that fills these two requisites. The second component, responsible to filter the signal on these new IF frequencies, is a Surface Acoustic Wave (SAW) filter, the reason for this choice was due to its great Q factor as it will provide a higher resolution in the spectrum measurement.

This last method has the advantage of being able to measure a larger bandwidth signal and having better accuracy, at the cost of having a slight increase in power consumption.

#### 2.3.1 Components

• Mixer:

A mixer is a non-linear circuit that multiplies two input signals that may be from different frequencies to produce a new signal, which has the sum and difference of the starting frequencies (Equation (2.3)). This component's main use is to shift an input signal into a new central frequency, this process is called heterodyning.

$$\cos(2\pi \cdot f_1 \cdot t) \cdot \cos(2\pi \cdot f_2 \cdot t) = = \frac{1}{2}\cos(2\pi \cdot (f_1 - f_2) \cdot t) + \frac{1}{2}\cos(2\pi \cdot (f_1 + f_2) \cdot t)$$

(2.3)

A down-converting mixer can be used to shift the input RF signal into a new IF frequency which is easier to work on with filters. This can be accomplished with the help of a PLL which provides the needed local oscillator to make this shift possible.

In the end, the resulting frequency from the mixer is  $f_{RF} - f_{PLL} = F_{SAW}$ , meaning that it will have to match the SAW filter's frequency.

• SAW Filter:

A SAW filter is a type of a band-pass filter and can be used to eliminate the unneeded products of a mixer and provides the filtering quality required to isolate the frequency where the power of a signal has to be measured.

An important feature of a SAW filter is the Q factor. The Q factor is defined by the ratio between the central frequency of the filter and its bandwidth. The SAW filter is an adequate band-pass filter, it is cheap, small, has low power consumption, and fulfils the requirement of a high Q factor.

• VGA:

A Variable Gain Amplifier (VGA), as the name implies, is an amplifier where its gain can be controlled with an external input which allows the gain to be decided in real time, based on the working conditions necessities.

Some applications require a high range of power readings, but for some of the values at the lower end of the scale, a normal power detector would be unable to detect them. Therefore, a VGA is a viable option when it is necessary to boost the signal to a level where it could be read.

• Power Detector:

The power detector in this system takes the output signal from the VGA and calculates the Root Mean Square (RMS) power value, so it can be read through a microcontroller's ADC.

• PLL:

A Phase Lock Loop (PLL) is a control device that generates a precise frequency. As represented in Figure 2.6, the PLL is based on a Voltage Controlled Oscillator (VCO), that generates the desired frequency based on an input voltage, at the cost of being inaccurate. To combat this, a feedback divider matches the output frequency (Fout) into the reference frequency (Fref), so that when closing the control loop to a Phase Detector (PD), the signals can be compared and therefore provide the error between the current output and the desired frequency. Then, this output signal error is amplified to the corresponding VCO's needed voltage through the Charge Pump (CP). Lastly, it has a Loop Filter so that sudden changes to the signal do not create massive ripples on the frequency, thus helping the VCO to converge to the desired frequency in a smoother way [11].

Figure 2.6: PLL Core Block Diagram.

• Microcontroller:

A microcontroller can be used as the brain of any system. It has modules that can communicate with external devices and, using as examples the components discussed in this section, it can control both a VGA's gain and a PLL's frequency. Moreover, with the help of an ADC, a microcontroller can read measurements such as ones given by a power detector. This means that a microcontroller is able to adjust the control values as a system evolves over time.

# Chapter 3

# Spectrum Acquisition System Design

In this chapter, it will be presented the choices done during the conception of the design system and also the directives that led to purchase suitable components.

To obtain the final system, it was necessary to take into account the boundaries established beforehand: The end result has to be a working prototype, with the theoretical characteristics discussed on the state of art and needs to work with the constraints imposed by the equipment available on the IT.

Since the main objective of this work is to have a functional prototype, of the two methods discussed in the state of the art chapter, the one that used a down-converting mixer was followed, as it had the best chance of having results from a first research.

This system is based on a mixer, a PLL and SAW filters. To make it, it was also necessary to add a VGA, a power detector, and a microcontroller. A block diagram of the designed system can be consulted on Figure 3.1.

Figure 3.1: System block diagram.

# **3.1** Electronic Components

The main limitation related to the construction is imposed by the ability of the hardware machine(CNC) to make a PCB, as the actual technology on IT allows only the production of a PCB with two layers, the top and bottom layer. This constrain mainly impacts the design of the layout because all the components should have a good path placement so that no lane will overlap with each other during the implementation.

It is also a target trying to achieve the smallest prototype possible, as it will translate into less waste of substrate and so a cheaper product. However, this cannot conflict with the cleanliness and reliability of it.

Other constraints include the minimum size of the CNC's drill, 2mm, therefore the layout design must have, at least, the same distance between two copper lanes. One of the main drawbacks of this is that any device used must have at least two millimetres between the pads.

There are other limitation less relevant than the above mentioned, such as the soldering, this has to be done by the technician of IT, and therefore the components cannot be very small, or it will be very difficult to solder them by hand.

For the circuit elements properties, it should be taken into account their power consumptions, the signal power that they can handle and their noise figure, as these directly compromise the quality of the final product.

The last criterion was the price, the cheapest components were selected, and bought on a store approved by IT.

With the above requirements met, it was chose a component that could suit the theoretical and practical constrains.

For reason mentioned above, the circuit elements chosen were:

#### 3.1.1 SAW Filter

The first element picked was the filter, as it is a central part of system circuit, that because this element dictates the quality of the measured signal, furthermore its central frequency will impose the other components frequencies.

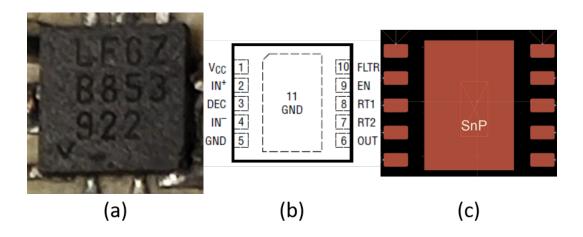

Figure 3.2 presents the chosen SAW filter, the B39431B3790Z810 [12] from B3790 series made by RF360. As it can be seen in Figure 3.3, this filter has a theoretical centre frequency of 433,92 MHz, with a minimum insertion attenuation of 3,6 dB between 433,86 MHz and 433,98 MHz, which means it has a band-pass bandwidth of 0,12 MHz. Among the other seen filters, this filter was the one with the best Q factor at that moment.

Figure 3.2: The SAW filter used represented as: (a) real Image, (b) bottom view [12], and (c) the used layout.

Another key factor for the filter choice was having a good attenuation along the band-stop, this important characteristic was not found on other available filters.

To achieve a better filter, it was considered the use of two different filters in cascade where one would have an excellent Q factor and the other would have very good attenuation on the band-stop, but no combinations were found that could be better than the B39431B3790Z810.

Furthermore, the filter alone cannot achieve the desired characteristics, as the signal should be 90dB below the transmitting signal, it is desired that the system should be able to measure a dynamic power range of 90dB, which for this case, the filter has to have the stopband with 90dB lower than the band-pass and to achieve that, two filters were used. In this case it was used the same filter two times in a cascade.

Figure 3.3: Transmission coefficient of used SAW filter [12].

# 3.1.2 PLL

The Phase Lock Loop generates the frequencies responsible to shift the RF signal into the frequencies that the system circuit works, which in this case is 434 MHz, since this is the central frequency of the SAW filter. Therefore, the PLL needs to generate frequencies around the 2000 MHz minus the 434 MHz, what resulting frequencies around the 1566 MHz.

The other requisite the PLL is also responsible for, is the ability to reach the 20 MHz bandwidth with a maximum step of 1 MHz between two frequencies.

With the feature mentioned above the PLL that suited better was the ADF4360-4 from Analog Devices, it is composed by an Integrated Synthesizer and an internal VCO, meaning that it just needs an external oscillator to work properly.

The ADF4360 series is composed by four devices, with each one operating in different frequencies. Among them, there is the ADF4360-4 [13] represented in Figure 3.4, with an output frequency range from 1450 MHz to 1750 MHz, which includes the desired frequencies around the 1566 MHz and more than the 20 MHz of bandwidth, furthermore this PLL can achieve a channel spacing with less than 1 MHz as it is able to get steps smaller than 0.1 MHz, this was the feature that led this PLL to be chosen among those available.

The ADF4360 series have similar characteristics, which is interesting for future projects, since the defining difference between them is the output frequency range of the PLL, the system could measure higher RF input frequencies with minimal changes to the whole system.

One last attribute to be mentioned is the PLL control's communication, the ADF4360-4 uses a compatible SPI communication, this is an advantage as it uses less lines when compared with other devices that use parallel communication.

Figure 3.4: The PLL used represented as: (a) real Image, (b) top view [13], and (c) the used layout.

## 3.1.3 Mixer

The mixer is responsible to shift the input RF signal to the pretended 434 MHz. Its characteristics are predetermined by the PLL output signal, the RF signal that needs to be analysed and the SAW filter frequency.

By taking the above features into account, the mixer LT5557 [14] was chosen, made by Linear Technology.

This mixer is optimized for high linear down-conversion and depending on the output matching it can be capable of achieving a gain of 3 dB from RF input to IF output, furthermore it is already partially matched for frequencies up to 600 MHz (which includes the intended frequency of 434 MHz).

The datasheet proposes a few options for matching networks, with one of those being a perfect fit with all of the presented requirement above met. Thanks to this, the LT5557 was considered the best available choice.

Figure 3.5 presents the chosen mixer:

Figure 3.5: The Mixer used represented as: (a) real Image, (b) top view [14], and (c) the used layout.

## 3.1.4 RMS Power Detector

The LTC5582 [15] presented in Figure 3.6 is an RMS power detector, from Analog Devices, since the most important feature on the power meter is the dynamic range that can be measured, LTC5582 presents a theoretical range from -60 dBm to 2 dBm.

Another relevant feature of this power detector was its output, the LTC5582 generates an output between 0.5 V and 2.5 V, whose values are inside the ADC range of the microcontroller. Furthermore, it generates a linear output, which facilitates the conversion from voltage read on the ADC to the corresponding power measured, allowing less processing power usage during the conversion.

Figure 3.6: The RMS Power Detector used represented as: (a) real Image, (b) top view [15], and (c) the used layout.

# 3.1.5 VGA

The VGA has a great impact on the dynamic range of the system, therefore the main feature needed is the maximum gain at the intended frequency of 434 MHz. Most of the VGAs had a low-pass behaviour, so it was important to not only see the gain values presented on the datasheet, but also the gain response along frequencies.

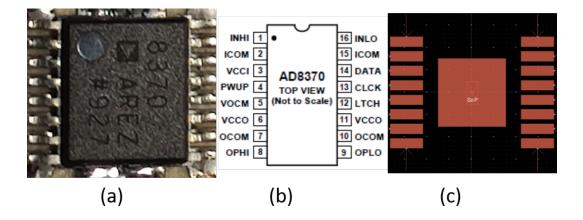

The VGA chosen was the AD8370 [16] from Analog Devices, with a theoretical dynamic gain range from -11 dB to 37 dB, and a theoretical bandwidth of 750 MHz. An image of this VGA is presented in Figure 3.7.

Figure 3.7: The VGA used represented as: (a) real Image, (b) top view [16], and (c) the used layout.

#### 3.1.6 Microcontroller

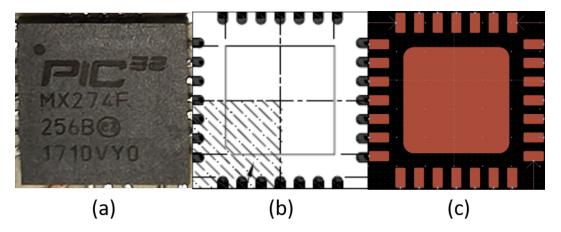

The Figure 3.8 presents the microcontroller used, a PIC32MX274F256B [17] from Microchip. The Microchip microcontroller was chosen mainly because it was used previously in other projects, therefore it is a known microcontroller leading to an easy learning curve. This microcontroller requires another device to flash the program, but there was already a PICkit 3 [18] available, so it did not pose any problem. Among the Microchip controllers available, it was selected a microcontroller with a SPI, Universal Serial Bus (USB) and I<sup>2</sup>C interfaces and that also respects the constrains referred at the beginning of this chapter. This microcontroller has the Peripheral Pin Select (PPS) technology on its most of Input/Output (I/O) pins, which allows configuration of digital peripherals to any I/O pin and also enables routing a peripheral to multiple pins, thus facilitating the layout. At last, it was decided to use a high-performance microcontroller, to guarantee that performance is not an issue on this prototype.

Figure 3.8: The microcontroller used represented as: (a) real Image, (b) bottom view [17], and (c) the used layout.

The PIC32MX274F256B has integrated interfaces and modules, for this thesis the relevant are the following:

• SPI:

The SPI interface is used to communicate with PLL and VGA, the communication is done in parallel, with the device being selected through two pins, each one functioning as a chip select for the respective device. Furthermore, it was used only one pin port to source the clock signal (CKL) for the both devices, while for the output data signal (SDO) it was used two separates pins, this being possible by configuring the two pins as the same internal port through the PPS [19].

•  $I^2C$ :

The  $I^2C$  interface is used as an output communication, its objective is to use it to control a predistorter's DACs. This communication requires two pins, one for a clock signal (SCL) and another for the data signal (SDA), both pins were selected through PPS.

So that the system would have reliable communication it was added to the layout one ground pin and one 3.3 voltage pin, this can supply the DACs if needed and the ground pin can be used as a reference, ensuring the adequate voltage needed for the communication.

• USB:

The USB was the communication opted to send the prototype results to the PC, in this way an application can easily send control commands to the microcontroller, and also receive a visual output.

For the USB communications it was added a micro-USB port, this port not only allows communication but also it is used to power the entire system.

### 3.1.7 Oscillators

In this system there are two devices that require oscillators, the PLL and the microcontroller. They need different types of oscillators since they have different ways to attach to them. The first oscillator will generate the "base" signal for the PLL and it will need an external power supply. Also, this oscillator's goal is to aid the PLL in generating frequencies that are at GHz level, as these frequencies impact the accuracy of the system, this oscillator must be as precise as possible and with a low drift.

For that reason, it was selected the XNCLH10M000CHJA2P0 [20] from Murata, it is a precision Temperature Compensated Crystal Oscillator (TCXO), with a temperature compensated circuit, also has the pretended specifications, it has an operating temperature range from -40 °C to 85 °C, a frequency shift by temperature of 0.28 ppm, and a frequency aging of 0.28 ppm/year.

The XNCLH10M000CHJA2P0 oscillator, represented on Figure 3.9, needs a supply of 3.3 V and works at a frequency of 10 MHz.

Figure 3.9: The PLL's oscillator used represented as: (a) real Image, (b) top view [20], and (c) the used layout.

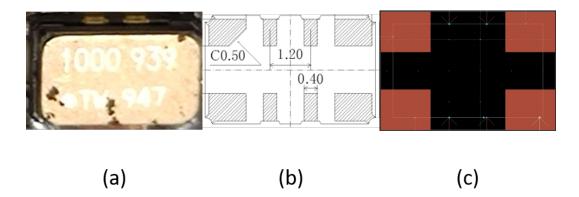

In Figure 3.10 the second oscillator can be seen, this one is used to supply the microcontroller's clock, unlike the oscillator used on PLL, the power to supply this oscillator it is given by the microcontroller itself. Moreover, the main reason to use an oscillator attached to the microcontroller is to generate the clock for the USB communication, the USB communication uses a clock in the MHz order, so the oscillator does not need to be so good as the PLL clock.

The oscillator chosen is a ABM10-166-12.00MHz [21], which is a cheaper choice when compared with the PLL's oscillator. This oscillator, as the name implies, operates at a frequency of 12 MHz, and have a load capacitance of 8 pF.

Figure 3.10: The microcontroller's oscillator used represented as: (a) real Image, (b) top view [21], and (c) the used layout.

### 3.1.8 Other Components

There were other components used to materialize a functional system, the most common were the capacitors, inductors, and resistances.

Beyond these there were other components worth to be mentioned:

• Headers / I/O Connectors:

The headers pins were used to provide the  $I^2C$  communication with the external DAC's, and another group of I/O pins to attached to the programmer.

• USB Connector:

For the USB connector, it was employed an USB type B inverted, the choice fell on an inverted connector because it facilitates the connection between the D+ and D- pins of the microcontroller and the connector, so that the lines do not cross over each other.

• SMA Connector:

The SMA Connector is the physical port where the RF signal enters the system, this connector is matched to 50  $\Omega$  and works with frequencies around the 2 GHz.

• LDO:

The Low-Dropout Regulator (LDO) ensures a stable voltage of 3.3 V converted from the 5 V provide by the USB. Several LDOs were used, one for each device, to ensure proper regulated voltage and a better isolation between the devices.

• Button:

A small button was implemented to permit a physical reset on the microchip.

• PICkit 3 [18]:

Figure 3.11 shows the used PICkit 3. As mentioned above, the PICkit 3 is an in-circuit Programmer and a Debugger, it was chosen to program the microcontroller.

It is simple to integrate on the system, its software is already integrated on the microchip Integrated Development Environment (IDE) (MPLAB), with drivers automatically installed on Windows. As for the hardware required, a few copper lines and header pins were added to the prototype board so that the PICkit 3 can be easily connected to the microcontroller. A simple mini-USB type B cable is then used to connect to the computer to upload the code.

Figure 3.11: PICkit 3.

# **3.2 Designed Circuits**

For a working system, the devices need an appropriate circuit design. The way to achieve that, it was by starting to follow the datasheet recommendations and when it was available, follow the schematics guidelines, always considering the differences between the presented projects and this thesis project.

Most of the devices used, have the enable chip feature, which can be controlled through an I/O pin, this would be preferable to use so that it could be controlled by the microcontroller, but due to constrains imposed by the two layers of the substrate, it was decided to not use it. Instead, the solution was to leave these pins be connect to 3.3 V turning its always on.

Another problem arose in some passive components, as the sought impedance, capacitance and inductance values were not always available to purchase. Usually, these values have a normalized reference value so, the solution was to trace the two nearest available components values and go for the one that had closest results.

Hereupon, it will follow specific for each device:

### 3.2.1 PLL

For the ADF4360-4, the Analog Devices provides, along with the datasheet [13], an evaluation board user guide [22], and a software, named ADIsimPLL, where a PLL loop filter can be simulated. The evaluation board user guide contains information about how to use their board and how to control the evaluation board through their software, moreover, another important factor is that it also contains a schematic of the evaluation board, which it was used to guide this thesis design.

To describe the decisions made during this circuit design, the approach will be to divide it into four separates parts, being the first the supplier circuits, the second is the input circuit composed by the oscillator, the third part is the PLL loop filter, and finally the fourth part, the output matching, which will be discussed in the next section.

The supplier circuits were designed by using a LDO to convert the 5V into to the required 3.3V, this LDO can supply a stable 3.3 V and can handle the maximum current of the PLL

of 47.5 mA, furthermore, by following the datasheet [13] recommendations it was used two LDOs, one to power the PLL through its VDD pin, and another to supply the VCO through the VVCO pin and with the addition of two capacitors, one of 100nF and another with 10 pF, a reliable power supply was created with a good filter to prevent the non-wanted signal.

For the oscillator circuit, as the chosen oscillator has characteristics similar to the used on their evaluation board, the schematic proposed in the evaluation board user guide was used [22]. The important part of this schematic was edited and presented in Figure 3.12.

Figure 3.12: Reference input circuit for the PLL [22].

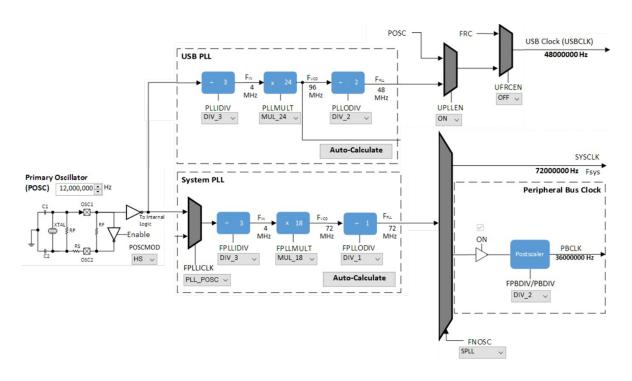

Finally, for the loop filter, it was used the ADIsimPLL software.

The ADIsimPLL was set with the predetermined PLL parameters, working with a central frequency of 1566 MHZ and 20 MHz of bandwidth, additionally as the Phase Detector Freq. parameter decides the channel spacing of the PLL, it was settled for 0.5 MHz, this value is well below 1 MHz which is the maximum spacing requirement for this thesis. If needed, the spacing can also be later changed through software to an even lower number as the PLL can support spacing lower than 0.1 MHz. The last parameter is the oscillator frequency which is 10 MHz.

The configurations mentioned above were set in the ADIsimPLL software and they can be seen in the following Figure 3.13.

| Output Frequency Requirements                                                                                                                                              | $\times$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Specify the Output Frequency requirements for your PLL synthesizer                                                                                                         |          |

| Minimum Frequency 1.556GHz                                                                                                                                                 |          |

| Maximum Frequency 1.576GHz                                                                                                                                                 |          |

| Phase Detector Freq 500kHz                                                                                                                                                 |          |

| Channel Spacing equals the Phase Detector Frequency for<br>Integer-N PLL's unless an external prescaler is used.                                                           |          |

| If you have a given reference frequency that you must use then<br>check the box below and enter the frequency. Otherwise the<br>reference frequency can be selected later. |          |

| Use Reference Frequency of: 10.0MHz                                                                                                                                        |          |

| All frequencies are entered in Hz. To enter 10MHz<br>simply type "10M" or "10e6", to enter 22.5kHz type<br>"22.5k" or "22.5e3" and so on.                                  |          |

| < Back Next > Cancel He                                                                                                                                                    | lp       |

Figure 3.13: ADF4360-4 working frequency configuring on the ADIsimPLL.

As a result, the software generates a schematic of the loop filter as seen in Figure 3.14, on another tab it shows a simulation of the noise and gain, and in the last tab a report is created, where it shows other characteristics of the generated sine signal, such as the noise present and the time needed to lock on the frequency.