# STARS

University of Central Florida

STARS

Electronic Theses and Dissertations, 2020-

2021

# Improving Performance and Flexibility of Fabric-Attached Memory Systems

Vamsee Reddy Kommareddy University of Central Florida

Part of the Data Storage Systems Commons Find similar works at: https://stars.library.ucf.edu/etd2020 University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Kommareddy, Vamsee Reddy, "Improving Performance and Flexibility of Fabric-Attached Memory Systems" (2021). *Electronic Theses and Dissertations, 2020*-. 518. https://stars.library.ucf.edu/etd2020/518

## IMPROVING PERFORMANCE AND FLEXIBILITY OF FABRIC-ATTACHED MEMORY SYSTEMS

by

## VAMSEE REDDY KOMMAREDDY M.S. University of Central Florida, 2018

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Spring Term 2021

Major Professor: Amro Awad

© 2021 Vamsee Reddy Kommareddy

## ABSTRACT

As demands for memory-intensive applications continue to grow, the memory capacity of each computing node is expected to grow at a similar pace. In high-performance computing (HPC) systems, the memory capacity per compute node is decided upon the most demanding application that would likely run on such a system, and hence the average capacity per node in future HPC systems is expected to grow significantly. However, diverse applications run on HPC systems with different memory requirements and memory utilization can fluctuate widely from one application to another. Since memory modules are private for a corresponding computing node, a large percentage of the overall memory capacity will likely be underutilized, especially when there are many jobs with small memory footprints. Thus, as HPC systems are moving towards the exascale era, better utilization of memory is strongly desired. Moreover, as new memory technologies come on the market, the flexibility of upgrading memory and system updates becomes a major concern since memory modules are tightly coupled with the computing nodes.

To address these issues, vendors are exploring fabric-attached memories (FAM) systems. In this type of system, resources are decoupled and are maintained independently. Such a design has driven technology providers to develop new protocols, such as cache-coherent interconnects and memory semantic fabrics, to connect various discrete resources and help users leverage advances in-memory technologies to satisfy growing memory and storage demands. Using these new protocols, FAM can be directly attached to a system interconnect and be easily integrated with a variety of processing elements (PEs). Moreover, systems that support FAM can be smoothly upgraded and allow multiple PEs to share the FAM memory pools using well-defined protocols. The sharing of FAM between PEs allows efficient data sharing, improves memory utilization, reduces cost by allowing flexible integration of different PEs and memory modules from several vendors, and makes it easier to upgrade the system.

However, adopting FAM in HPC systems brings in new challenges. Since memory is disaggregated and is accessed through fabric networks, latency in accessing memory (efficiency) is a crucial concern. In addition, quality of service, security from neighbor nodes, coherency, and address translation overhead to access FAM are some of the problems that require rethinking for FAM systems. To this end, we study and discuss various challenges that need to be addressed in FAM systems. Firstly, we developed a simulating environment to mimic and analyze FAM systems. Further, we showcase our work in addressing the challenges to improve the performance and increase the feasibility of such systems; enforcing quality of service, providing page migration support, and enhancing security from malicious neighbor nodes.

# ACKNOWLEDGMENTS

I have received immense support and assistance to pursue the degree and throughout this dissertation.

I thank my advisor, Dr. Amro Awad, for his immense belief and trust in me. Your guidance and expertise were precious in addressing and formulating various research questions and solving them. Your support and feedback motivated and drove me in improving my ability to think and solve critical problems.

I would also like to thank Dr. Clayton Hughes and Dr. Simon David Hammond from Sandia-National Laboratories for their collaboration and guidance. I thank my committee members, Dr. Rickard Ewetz, Dr. Zhishan Guo, Dr. Paul Gazzillo, and Dr. Clayton Hughes for serving in my defense panel.

Finally, I would like to thank my family and friends for their constant support and motivation.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                  | xi |

|----------------------------------------------------------------------------------|----|

| LIST OF TABLES                                                                   | XV |

| CHAPTER 1: INTRODUCTION                                                          | 1  |

| 1.1 Fabric-Attached Memory Simulation Setup                                      | 7  |

| 1.2 Investigating Performance by Enforcing Fairness with Hierarchical Priority   | 8  |

| 1.3 Page Migration Support                                                       | 8  |

| 1.4 Architecture-Aware Virtual Memory Support For Fabric Attached Memory Systems | 10 |

| CHAPTER 2: FABRIC-ATTACHED MEMORY SIMULATION                                     | 13 |

| 2.1 Background                                                                   | 13 |

| 2.2 Opal: A Centralized Memory Manager                                           | 14 |

| 2.2.0.1 Exposing External Memory Directly to Local Nodes                         | 18 |

| 2.2.0.2 Virtualizing External Memory                                             | 19 |

| 2.2.1 Opal Configuration                                                         | 19 |

| 2.2.2 Memory Allocation Policies                                                 | 22 |

|       |         | 2.2.2.1     | Local Memory First Policy:                   | 22 |

|-------|---------|-------------|----------------------------------------------|----|

|       |         | 2.2.2.2     | Alternate Memory Allocation Policy:          | 22 |

|       |         | 2.2.2.3     | Round Robin Memory Allocation Policy:        | 23 |

|       |         | 2.2.2.4     | Proportional Memory Allocation Policy:       | 23 |

|       | 2.2.3   | Commun      | ication Between Nodes                        | 24 |

| 2.3   | Evalua  | tion        |                                              | 24 |

|       | 2.3.1   | Opal Me     | mory Allocation Policies                     | 26 |

|       |         | 2.3.1.1     | Local Memory First (LMF) Policy:             | 27 |

|       |         | 2.3.1.2     | Alternate (ALT) Policy:                      | 27 |

|       |         | 2.3.1.3     | Round Robin (RR) Policy:                     | 28 |

|       |         | 2.3.1.4     | Proportional (PROP) Policy:                  | 29 |

| 2.4   | Conclu  | ision       |                                              | 30 |

| CHAP' | TER 3:  | INVESTI     | GATING PERFORMANCE IMPROVEMENTS BY ENFORCING |    |

|       | ]       | FAIRNESS    | S IN FABRIC-ATTACHED MEMORY SYSTEMS          | 31 |

| 3.1   | Quality | y of Servic | e                                            | 32 |

| 3.2   | Fairnes | ss in Fabri | c-Attached Memory Systems                    | 33 |

|       | 3.2.1   | Hierarch    | ical Priority                                | 33 |

|      |        | 3.2.1.1 Static Priority                                       | 33  |

|------|--------|---------------------------------------------------------------|-----|

|      |        | 3.2.1.2 Dynamic Priority                                      | 35  |

|      | 3.2.2  | Splitting Shared Memory                                       | 37  |

| 3.3  | Evalua | ation                                                         | 38  |

|      | 3.3.1  | The Impact of Number of Shared Memory Pools                   | 41  |

|      | 3.3.2  | QoS using Hierarchical Priority                               | 42  |

| 3.4  | Conclu | usion                                                         | 45  |

| CHAP |        | PAGE MIGRATION SUPPORT FOR FABRIC-ATTACHED MEMORY SYS-        | 1.0 |

|      |        | TEMS                                                          | 46  |

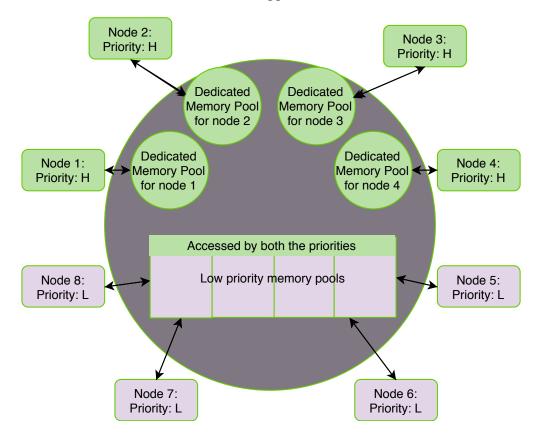

| 4.1  | Motiva | ation: Impact of Number of Nodes Accessing FAM on Performance | 46  |

| 4.2  | Page N | Aigration                                                     | 47  |

|      | 4.2.1  | Translation Look-Aside Buffer (TLB) Shootdown:                | 48  |

|      | 4.2.2  | Literature                                                    | 49  |

| 4.3  | Page N | Migration in FAM systems                                      | 51  |

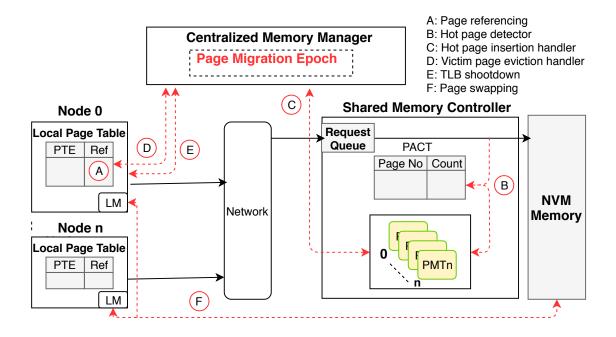

|      | 4.3.1  | Detecting Hot and Victim Pages                                | 51  |

|      | 4.3.2  | Performing Page Migration                                     | 53  |

|      | 4.3.3  | Sequence of Events                                            | 55  |

|       | 4.3.4  | Overheads                                                                        | 56 |

|-------|--------|----------------------------------------------------------------------------------|----|

| 4.4   | Evalua | ation                                                                            | 57 |

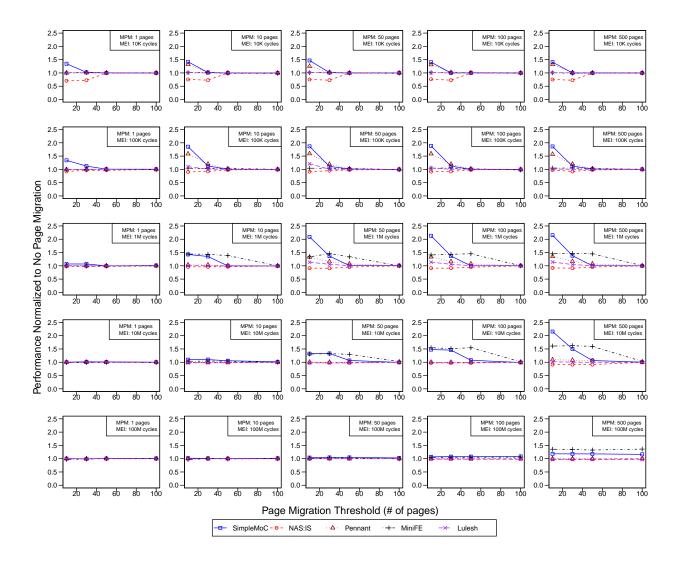

|       | 4.4.1  | Effect of Page Migration Parameters                                              | 60 |

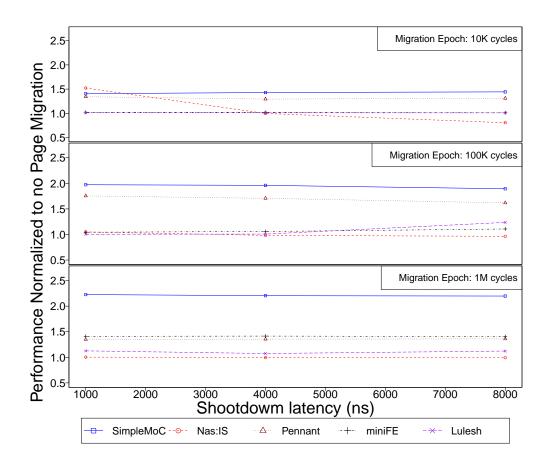

|       | 4.4.2  | Page Migrations Costs                                                            | 62 |

|       | 4.4.3  | Sensitivity to NVM's Read/Write Latency                                          | 65 |

| 4.5   | Conclu | usion                                                                            | 67 |

| CHAPT |        | ARCHITECTURE-AWARE VIRTUAL MEMORY SUPPORT FOR FABRIC-<br>ATTACHED MEMORY SYSTEMS |    |

| 5.1   | FAM N  | Management Approaches                                                            | 68 |

|       | 5.1.1  | Exposed FAM (E-FAM)                                                              | 68 |

|       | 5.1.2  | Indirect Access to FAM (I-FAM)                                                   | 69 |

| 5.2   | Hierar | chical Page Tables                                                               | 70 |

|       | 5.2.1  | Exposed FAM vs Indirect Access to FAM                                            | 72 |

|       | 5.2.2  | Threat Model                                                                     | 72 |

| 5.3   | Decou  | pled Access Control and Address Translation (DeACT) Scheme                       | 74 |

|       | 5.3.1  | Overview                                                                         | 75 |

|       | 5.3.2  | System Overview                                                                  | 78 |

|        | 5.3.3   | FAM Translator                           |

|--------|---------|------------------------------------------|

|        | 5.3.4   | FAM Access Verification                  |

| 5.4    | Metho   | dology and Results                       |

|        | 5.4.1   | FAM Address Translation Hit Rate         |

|        | 5.4.2   | Address Translation Requests at FAM      |

|        | 5.4.3   | Impact of DeACT on Performance    89     |

|        | 5.4.4   | Sensitivity Analysis                     |

|        |         | 5.4.4.1 STU Cache Size and Associativity |

|        |         | 5.4.4.2 Access Control Metadata Size     |

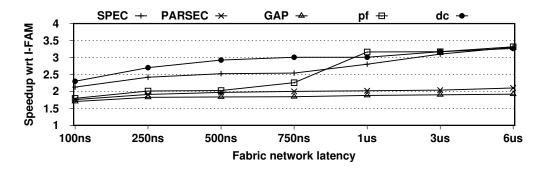

|        |         | 5.4.4.3 Fabric Latency                   |

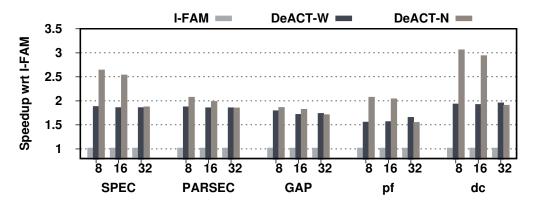

|        |         | 5.4.4.4 Number of Nodes                  |

| 5.5    | Relate  | d Work                                   |

| 5.6    | Conclu  | usion                                    |

| LIST C | )F REFI | ERENCES                                  |

# **LIST OF FIGURES**

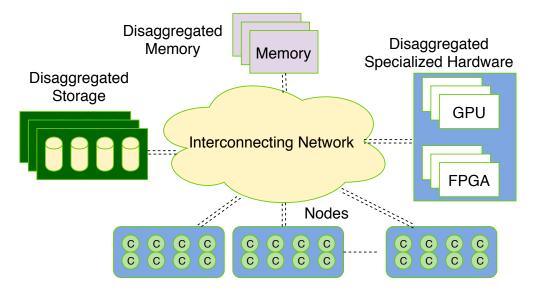

| Figure 1.1: Disaggregated memory system                                                                                                                                                                                                                                         | 3  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

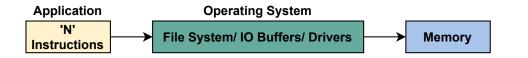

| Figure 1.2: Memory access approach in FAM and tranditional memory                                                                                                                                                                                                               | 5  |

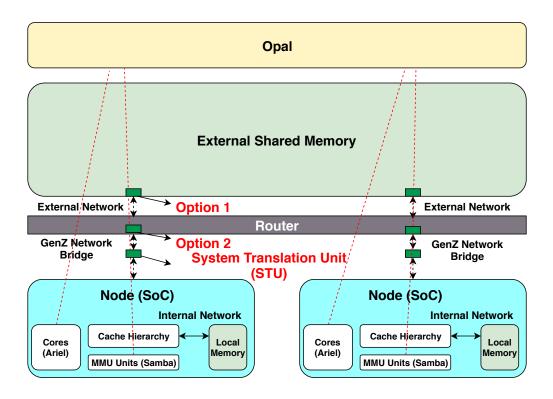

| Figure 2.1: A simulated system that uses Opal for centralized memory management                                                                                                                                                                                                 | 17 |

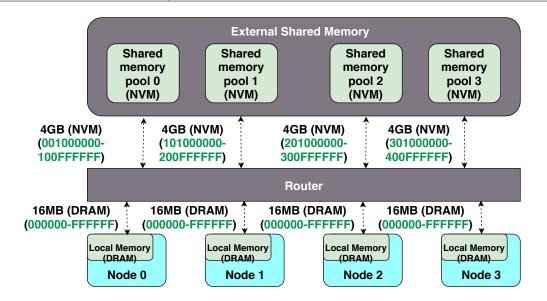

| Figure 2.2: Example configuration                                                                                                                                                                                                                                               | 21 |

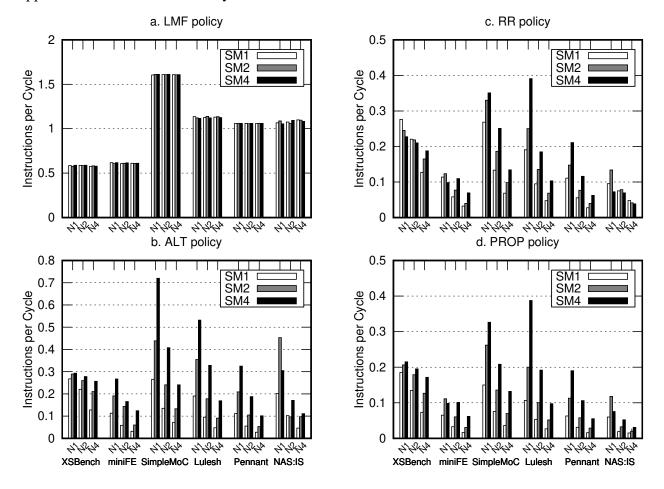

| Figure 2.3: Performance in instructions per cycle of disaggregated memory system with different memory allocation policies. <i>N</i> indicates number of nodes. <i>SM</i> indicates number of shared memory pools. <i>LMF</i> , <i>ALT</i> , <i>RR</i> and <i>PROP</i> indicate |    |

| local memory first, alternate memory, round robin and proportional memory allocation policies.                                                                                                                                                                                  | 26 |

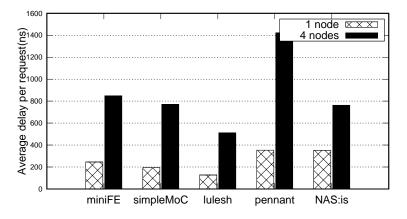

| Figure 3.1: Average memory access delay per request observed by the core in dedicated single node FAM system (FAM is accessed by only one node) and shared four node FAM system (FAM is shared by four nodes).                                                                  | 31 |

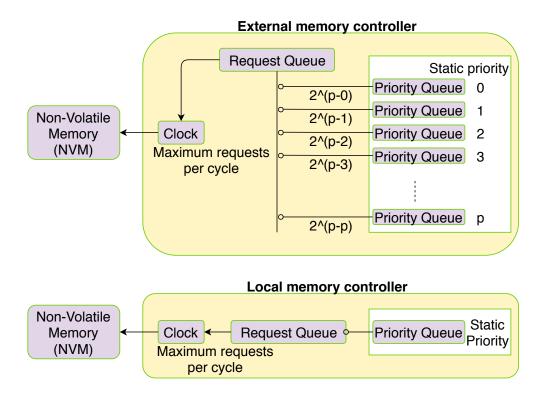

| Figure 3.2: Hierarchical priority based QoS implementation in Local and External mem-<br>ory controllers                                                                                                                                                                        |    |

| Figure 3.3: Dedicating shared memory pools for high priority nodes                                                                                                                                                                                                              | 38 |

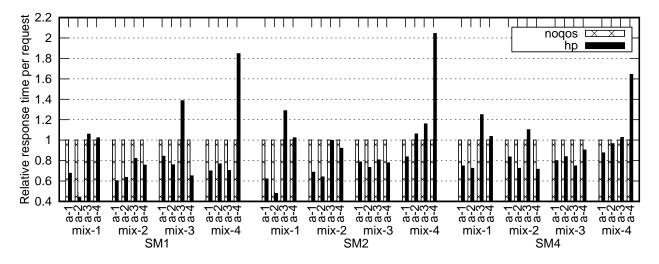

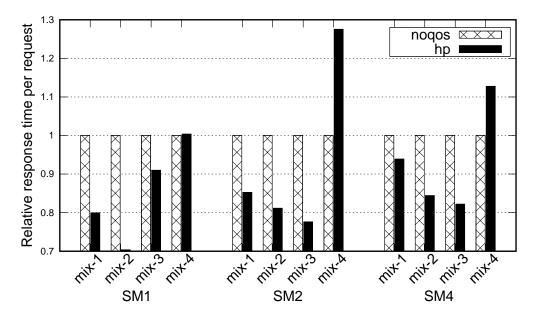

| Figure 3.4: Relative response time per memory request of disaggregated memory system model.                                                                                                                                                                                     | 42 |

| Figure 3.5: R | Relative response time per request wherein global memory is divided into    |    |

|---------------|-----------------------------------------------------------------------------|----|

| sl            | hared memory pools in disaggregated memory system                           | 43 |

| Figure 3.6: C | Overall relative response time per request of disaggregated memory system   |    |

| u             | sing no QoS and hierarchical priority based QoS                             | 44 |

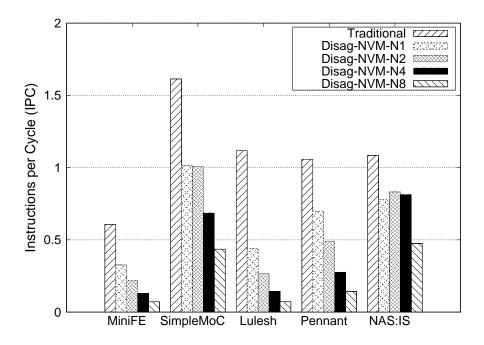

| Figure 4.1: A | Average performance of traditional (non-FAM) memory system and disag-       |    |

| g             | regated memory systems with one to eight nodes accessing a single FAM       |    |

| n             | nodule                                                                      | 47 |

| Figure 4.2: T | LB shootdown process                                                        | 48 |

| Figure 4.3: P | Page migration in disaggregated memory systems. LM: Local Memory, PMTn:     |    |

| Р             | Pages to Migrate Table per node, PACT: Page Access Count Table              | 54 |

| Figure 4.4: P | Performance improvement (normalized to no page migration) in disaggre-      |    |

| g             | ated memory system when page migration parameters migration epoch length,   |    |

| n             | umber of pages to migrate and page migration threshold are varied. Shoot-   |    |

| d             | own latency is maintained at 8us and per page migration delay(cost) is 1us. |    |

| Ν             | IPM indicates Maximum pages to Migrate per epoch. MEI indicates Mi-         |    |

| g             | ration Epoch Interval                                                       | 59 |

| Figure 4.5: P | Performance improvement (normalized to no page migration) in disaggre-      |    |

| g             | ated memory system with best possible cases. Migration epoch interval is    |    |

| 1             | 0K, 100K and 1M cycles with PMT of 10 accesses, 8us TLB shootdown           |    |

| la            | atency, a maximum of 50 pages to migrate per epoch and per page migration   |    |

| d             | elay(cost) of 1us per page                                                  | 63 |

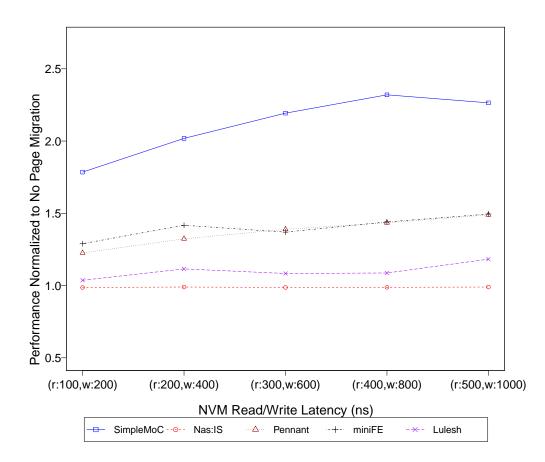

| Figure 4.6: Performance improvement in disaggregated memory system with respect to     |    |

|----------------------------------------------------------------------------------------|----|

| conventional memory system with different NVM read/write latency. PMT is               |    |

| 10 accesses with a maximum of 50 pages to migrate, TLB shootdown latency               |    |

| of 8us and per page migration delay(cost) is 1us per page. Page migration is           |    |

| performed for every 1M cycles                                                          | 65 |

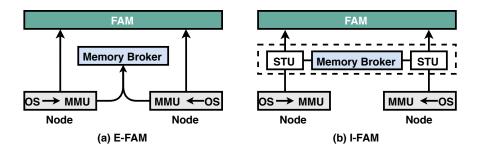

| Figure 5.1: Two ways of managing memory in FAM systems                                 | 70 |

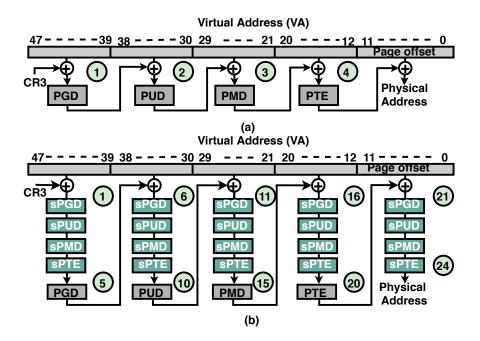

| Figure 5.2: Page table walking in (a) x86 and (b) virtualized systems                  | 71 |

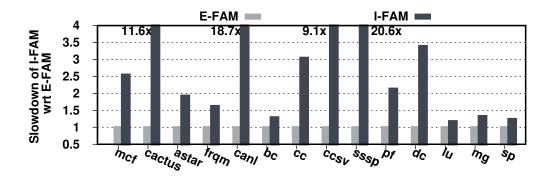

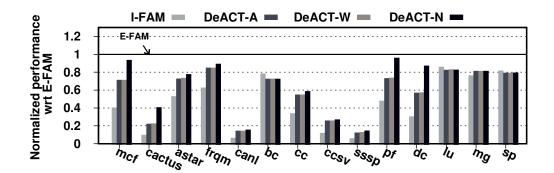

| Figure 5.3: Normalized performance with respect to E-FAM.                              | 73 |

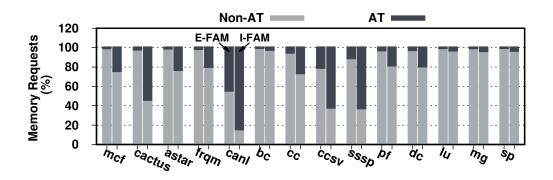

| Figure 5.4: Breakdown of percentage of address translation (AT) and non address trans- |    |

| lation (Non-AT) requests observed at FAM in I-FAM and E-FAM systems                    | 73 |

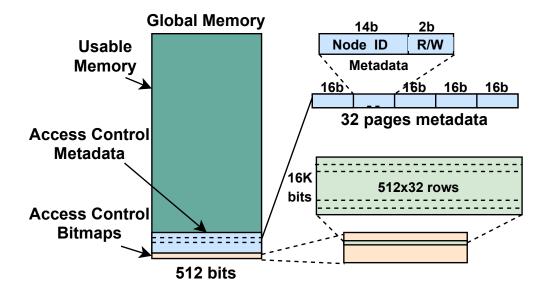

| Figure 5.5: Page access control metadata and bitmaps in FAM                            | 77 |

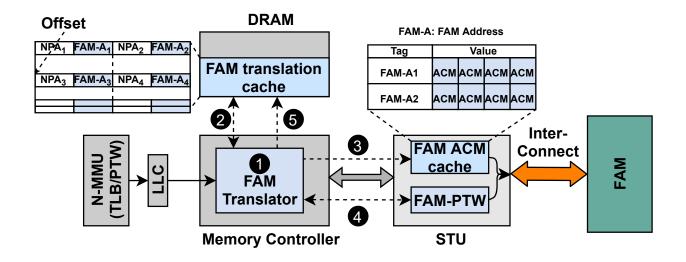

| Figure 5.6: DeACT FAM schematic.                                                       | 79 |

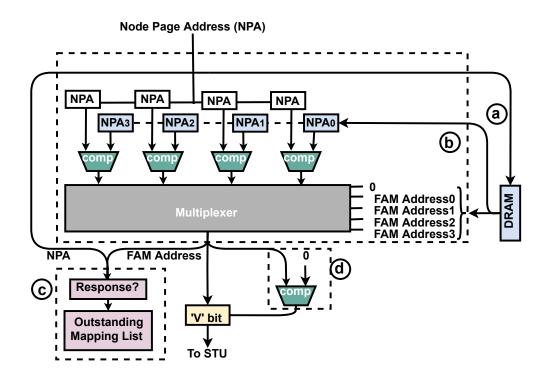

| Figure 5.7: FAM translator.                                                            | 81 |

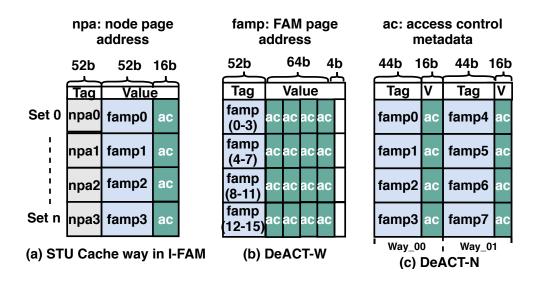

| Figure 5.8: ACM organization in STU cache way in (a) I-FAM and (b,c) DeACT             | 83 |

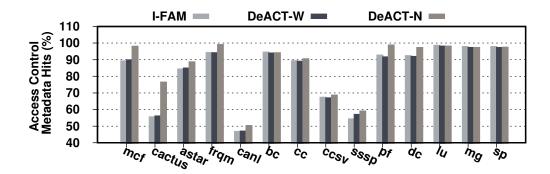

| Figure 5.9: Access control metadata hit rate.                                          | 84 |

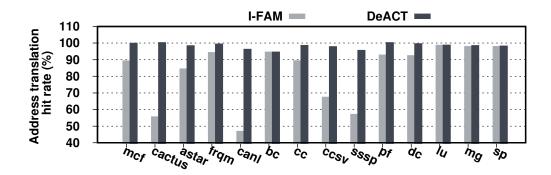

| Figure 5.10Address translation hit rate in I-FAM and DeACT                             | 89 |

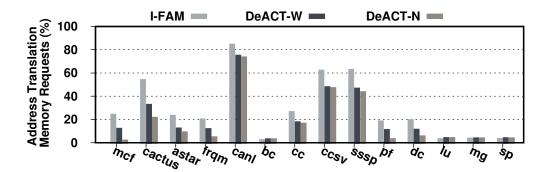

| Figure 5.11Percentage of address translation requests at FAM.                          | 90 |

| Figure 5.12Normalized performance with respect to E-FAM.                               | 91 |

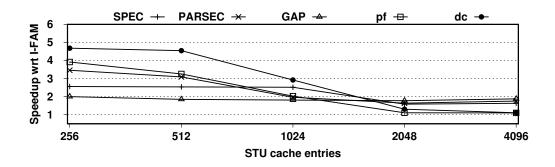

| Figure 5.13Performance improvement wrt STU cache size.                                 | 93 |

| Figure 5.14Metadata size effect on performance.                    | 94 |

|--------------------------------------------------------------------|----|

| Figure 5.15The impact of fabric latency on performance.            | 95 |

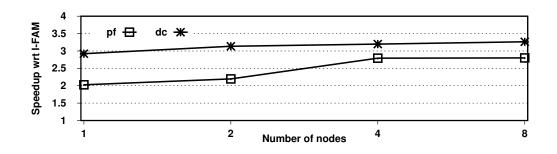

| Figure 5.16Impact of increasing the number of nodes on performance | 96 |

# LIST OF TABLES

| Table 2.1: | Opal Parameters                                                                         | 20 |

|------------|-----------------------------------------------------------------------------------------|----|

| Table 2.2: | Memory Pool Parameters                                                                  | 21 |

| Table 2.3: | Exploring Allocation Policies Simulation Parameters                                     | 25 |

| Table 2.4: | Applications used to Exploring Allocation Policies                                      | 25 |

| Table 3.1: | System Simulation Parameters used to Examine Hierarchical Priority Approach             | 39 |

| Table 3.2: | Applications-Mixes used to Examine Hierarchical Priority Approach                       | 41 |

| Table 4.1: | System Simulation Parameters to Analyse Page Migration Support for FAM<br>Architectures | 57 |

| Table 4.2: | Applications used Analyse Page Migration Support for FAM Architectures                  | 57 |

| Table 5.1: | FAM Architectures Comparison.                                                           | 75 |

| Table 5.2: | System Configuration                                                                    | 86 |

| Table 5.3: | Applications                                                                            | 88 |

# **CHAPTER 1: INTRODUCTION**

This chapter discusses the drawbacks of HPC systems with tightly coupled in-node memories (resources) and emphasizes on the need for fabric-attached memory (FAM) systems for HPC workloads.

With the ever increasing demand for larger memory capacities, many high-performance computing (HPC) systems nowadays have their nodes equipped with hundreds of gigabytes of memories. For instance, Oak Ridge National Lab's Summit supercomputer has 512GB of DRAM and 96GB of HBM2 per compute node. The catalyst for increased memory capacity needs per compute node is increasing memory requirements for current new age and emerging workloads like data analytics, graph analytics, machine learning, artificial intelligence et al. However, maintaining such huge memory within a node leads to following drawbacks. Most HPC systems typically run many different applications from a variety of domains, each of which will have its own unique resource requirements; some applications may use the whole memory in the node while others may only use a few gigabytes. Nevertheless, most current HPC schedulers allocate resources at the node granularity, and applications with extremely low memory demands can end up reserving nodes with large memories. Unfortunately, the current approach to choose the size of memory per node is based on the maximum footprint (per node) of the applications of interest, which can lead to significant under-utilization of the memory system. Perhaps more importantly, because the memory subsystem is typically constructed with DRAM, each node can incur very high cooling costs in addition to significant power consumption [1, 2, 3, 4, 5, 6, 7, 8]. A recent study shows that about 80% of the jobs on HPC systems overestimate their memory requirements [9]; thus, HPC systems under-utilize memory slots by dedicating them to specific jobs. Moreover, applications that are not able to fit their memory needs into one node incur additional communication overhead because their computation must be split across nodes. Ideally, compute nodes should have

direct access to memories that meet their demands without the need to incur expensive software stack overhead due to message passing libraries. As asserted since memory subsystem is mostly constructed with DRAM, considering its fast access rates, power consumption is high. In addition to the under-utilization and sharing overheads of the systems that couple memory with computing nodes, upgrading memory can be challenging. To take advantage of the fast-evolving memories and adapt to the new requirements of applications, system memory should have the ability to be augmented with evolving memory technologies. In systems that deploy petabytes of storage, it is important to be able to flexibly extend the data stores and ensure their robustness. Further, migrating jobs is one of the crucial requirements for hybrid cloud systems [10] and with the existing memory arrangement it is complicated since the data pertaining to the job, which is to be migrated to the target system (node), has to be moved completely.

The emergence of workloads that process huge shared files or large graphs makes private memory for a node less attractive. These workloads are expected to become more common in the future, [11, 12], pushing future computing systems to become *memory-centric*. Hence, to mitigate the scalability challenges and data sharing complexities of coupled memory systems, a new memory design direction, decoupled memory systems in which memory is decoupled from the compute engines, is evolving as a result of memory-driven applications [13]. To support such systems, recent standards (consortium's), such as Gen-Z[14], Compute Express Lanes (CXL)[15] and Cache Coherent Interconnect for Accelerators (CCIX)[16], define protocols and interface requirements for accessing memory modules attached to the fast system interconnect. Memory modules that implement memory-semantic protocols and can be readily integrated with the system fabric are typically referred to as FAMs. Protocols defining how to integrate FAMs are being developed through a consortium of major vendors, such as Intel, HPE, AMD, IBM, Lenovo, and VMware[15, 14, 16]. FAMs promise a new HPC architecture where compute nodes can potentially access shared physical memory pools through fast interconnects. In particular, there has been recent industrial interest

in architectures where memory modules can be disaggregated from compute nodes, and hence, allows nodes to scale up its memory allocation to the requirements of the workloads run on the node. Such architectures are typically referred to as *memory-centric architectures*. Memory-centric architectures leverage memory semantic protocols to communicate with FAM pools over high-speed interconnects. Owing to memory disaggregation, they promise efficiency, flexibility, and reduced costs. Examples of architectures that resemble memory-centric systems include Facebook's Disaggregated Rack[17], HPE Labs' *The Machine*[13], and Intel's Rack Scale Architecture[18].

Figure 1.1: Disaggregated memory system

As shown in Figure 1.1, FAM decouples memory from computing nodes (FPGAs, GPUs or systemon-chips (SoCs)). In such systems, the applications can use traditional shared memory interfaces to operate on shared data by utilizing the large shared memory space. Most importantly, the shared memory space can be accessed by traditional load/store operations instead of explicitly communicating between computing nodes. Moreover, applications that access shared large files or data-sets concurrently can benefit from having these files resident in the globally accessible shared memory. Such a trend becomes more compelling with emerging Non-volatile memories (NVM) [19, 20]. NVMs, e.g., Intel's and Micron's 3D XPoint[21, 22, 23] are considered among the best candidates for building FAM systems for several reasons. First, with NVMs expected to have capacities in terabytes per processor socket [24, 25, 26, 27], the under-utilization problem becomes more severe if a processor-centric approach is adopted. Second, NVMs can be used to host directly-accessible filesystems, e.g., Linux's Direct Access for Files (DAX) support [28]. Having NVM modules shared across computing units allows for more efficient operation on shared files. Third, due to the slow and limited endurance of NVM writes, they are expected to be used as an additional layer in the memory hierarchy; having small DRAM-based local memory within nodes while NVM used as a lower-tier memory/storage, attached over fabrics, is a more natural design point [29]. Fourth, when scaling up the total memory capacity of data centers to petabytes, idle power becomes a major concern, and thus DRAM becomes a less practical solution given its significant refresh power and hence high cooling and operational costs.

Memory is maintained in a rack-scaled manner and can be accessed by scores of the compute nodes. Several nodes are connected to the shared memory through a high speed interconnect fabric, e.g., Gen-Z, CXL, and CCIX, [30, 31, 15, 32], are key enablers for disaggregated memory systems, in addition to scalable, dense and ultra-low power memory devices such as emerging NVMs. For instance, Gen-Z[30], is a new interconnect standard that defines a new memory semantic where memory units are directly attached to a system interconnect. In such design, memory becomes the center of the system, where other components, such as accelerators, processor nodes, and SoCs are integrated into the system by interfacing them with a shared interconnect that is attached to the memory.

While accessing memory traditionally, data is copied at multiple locations before storing in memory. For instance, as shown in Figure 1.2(a) data is copied at three places; file system, input output buffers and drivers. Such data copies are not necessary while accessing FAM. This is due to the direct connection between compute nodes to storage class memory with universal memory controllers. This saves both power and also time while maintaining data at multiple locations. Further, with the intervention of software stack in traditional memory access approach, the number of instructions issued by applications is significantly greater than the actual (useful) instructions. Since, PEs can be directly connected to the storage class memory, the number of instructions that are required to access memory now is drastically reduced to only useful instructions [33]. Although, PEs can access memory directly, to connect to the fabric network, PEs, currently, need to understand the underlying protocols provided by the fabric providers to access fabric attached storage class memory. To make PEs or applications oblivious of the underlying protocols, Symmetrical Hierarchical Memory (SHMEM), a PGAS library is used. SHMEM is a point-to-point, one-sided communicative library. Sandia OpenSHMEM (SOS) [34], OpenSHMEM [35] and CraySHMEM [36] are different implementations of SHMEM to communicate with the underlying communicative primitives. OpenFabrics Interfaces (OFI) [37] is a framework which is aimed at exporting fabric communication services or primitives to the upper layers (applications) through SHMEM interface. Libfabric [38] and unified communication X (UCX) [39] are two different framework variants of OFI. These frameworks export user-space application interfaces of the fabric interface to connect to the fabric provider hardware unit.

a. Traditional Memory Access Software Stack

b. Fabric Attached Memory Access Software Stack

Figure 1.2: Memory access approach in FAM and tranditional memory

Such memory-centric systems promise scalable shared memory applications and significantly reduce communication overhead by relying on shared memory and accessing memory directly with almost zero data copies instead of message passing interfaces between compute nodes and multiple data copies with interference from software stack as discussed. Moreover, disaggregated memory enables fluid division of the shared memory resource among all nodes resulting in a highly scalable system, yet cost efficient. Finally, upgrading and migrating the memory system would require much less efforts. Considering the advantages, many major vendors are considering system designs that utilize FAM, which can be accessed by a large number of processing nodes.

While FAM systems are a promising direction for designing future computing systems, adopting such systems requires rethinking to address various challenges raised with such systems. The drawbacks or challenges while adopting FAM systems are

- *High memory access latency*: Memory is accessed via fabric network interface and hence, memory access latency also includes fabric network latency apart from latency due to various memory types (DRAM or NVM).

- *Security*: FAM (centralized memory) is accessed by number of nodes and without proper memory protection mechanisms, data can be leaked to the neighbour nodes.

- *Fairness*: FAMs are expected to be used in multi-tenant environments and hence, multiple applications from different nodes access FAM. To this end, critical applications need to be prioritized to avoid starvation from applications running in the neighbour nodes .

- *Data coherency*: FAM allows for data sharing between the nodes and hence, data needs to be synchronized between the nodes. Data coherency should be scaled at node-level to achieve data synchronized between the nodes.

- Memory management: Remote FAM pages are allocated with the help of global memory

manager[40]. The global memory manager keeps track of the status of the remote memory, for instance, free and allocated pages. However, accessing remote memory manager require modifications to the operating systems (OSes).

**Thesis statement:** Our thesis thrives to study a promising use-case for FAMs, which is adopting FAMs in High-Performance Compute (HPC) systems, where the underutilization of memory is a major challenge. For such a use-case, drawbacks like increased memory access latency and security from the neighbour nodes should be addressed. Hence, we address these drawbacks and provide solutions to improve the performance and feasibility of adopting FAMs in HPC systems.

The summary of our contributions are as follows:

#### 1.1 Fabric-Attached Memory Simulation Setup

To study the impact of decoupling memory and maintaining centralized memory we need a proper simulating environment. FAM system is explored using QEMU [41] by HP laboratories [42]. However, scaling the simulation setup to study number of nodes accessing FAM with QEMU is not practical or takes non-realistic time. Hence, first we design a simulation model for evaluating disaggregated memory architectures using a publicly available simulator, Structural Simulation Toolkit (SST). SST is a cycle-level architectural simulator that is widely used, based on opensource licensing and is publicly available. SST has been proven to be one of the most reliable simulators for large-scale systems due to the scalability and modular design of its components. This makes SST the perfect candidate for simulating disaggregated memory systems at scale. To this end, we developed a new evaluating platform to explore FAM architectures and we explored various memory allocation policies for FAMs. Further details are explained in detailed in chapter

#### 1.2 Investigating Performance by Enforcing Fairness with Hierarchical Priority

As asserted, FAMs are expected to be used in multi-tenant environments, e.g., cloud systems or data centers. Contention can become a significant problem due to competition for the shared global (centralized) memory. As the number of compute nodes that share the global FAM increase, the more likely the average global memory access time will increase. Additionally, the worst-case access latency becomes much higher and mainly depends on the access patterns of other nodes and their memory intensity. This potential slowdown can certainly affect the adoption of such systems in environments where users and applications are guaranteed some level of quality assurance through Service-Level Agreements (SLAs), such as in cloud systems. To this end, ensuring *Quality-of-Service (QoS)*, is essential for designing and using FAMs.

We investigate the impact of QoS on application performance when running on FAM architectures. Specifically, we propose a hierarchical dynamic priority-based approach to support QoS in disaggregated NVM systems. Two levels of priorities are maintained - static and dynamic. Static priority is fixed at run-time. Dynamic priority is adjusted over the lifetime of the application. We divide the shared memory into memory pools to improve performance and study the effect of our approach. To the best of our knowledge, our work is the first to investigate QoS on DMS and to propose novel solutions to ensure QoS is enforced. Our simulation results show that by employing proposed hierarchical priority based QoS techniques, a speed up of 55% in accessing FAM is achieved. Hierarchical priority approach and necessary optimizations are discussed in chapter 3

#### 1.3 Page Migration Support

For disaggregated memory systems, it is expected that each computing node would have a small local memory that is based on either HBM or DRAM, whereas a large shared NVM memory would

be accessible by all nodes [29]. However, given the contention that results from memory sharing among nodes, proper management of the shared memory resource is a key design requirement. Managing such systems with global and local memory requires a novel hardware/software co-design.

Because off-node memory accesses are expensive, page migration will become a frequent operation on heterogeneous and disaggregated memory systems [43, 44]. During page swapping, physical addresses assigned to the virtual addresses can change, hence page table entry (PTE) update is required. The core initiating a PTE update needs to send Inter-Processor Interrupt (IPI) to other cores to force them to invalidate any copies from the updated PTE on their Translation Lookaside Buffers (TLBs). This process is called TLB shootdown [45]. To reduce the costs of such an interruption, several TLB shootdown optimization algorithms have been proposed [46, 44] Before these systems can be deployed, it will be important to analyze the impact the page migration will have on disaggregated memories. To this extent we provide a detailed page migration support to initiate page migration between global and local memory to maximize performance while enabling access to huge shared memory. Further we investigate such memory management aspects and the major system-level aspects that can affect design decisions in disaggregated NVM systems. Hence, monitoring memory accesses at the shared memory level would require careful design and implementation due to its direct impact on overall system performance. Triggering page migrations between shared memory and local memory would require special handling to ensure invalidating the affected and possibly cached memory mappings on each node. Moreover, identifying when and how often to migrate pages from global memory to local memory is challenging due to many aspects: temporal reuse of page, cost of page migration, network latency and shared memory latency. All of these aspects together should be considered to determine if page migration is useful or not for FAM architectures.

Hence we systematically analyze the impact of various memory management aspects including

TLB shootdowns, page migration latencies, page migration frequency and initiation mechanisms, and global memory latency, on the overall system performance for several applications. Counterintuitively, we observe that for some applications, accessing remote memory instead of migrating pages to local memory would lead to a better performance. We identify what system configurations and parameters would make page migration more useful. Finally, we propose a novel page migration mechanism that relies on minimal hardware changes to track hot pages at the global memory, where such information can be periodically accessed by system software to initiate page migrations at defined epoch boundaries.

Our evaluation results reveal that for a system with unoptimized TLB shootdown costs, page migration latency, and memory-centric latency, applications do not benefits from page migration, since migrating pages to the relatively fast local memories is amortized by the costs of page migration and TLB shootdown. To mitigate this, we first investigate the impact of optimized TLB shootdown latency to understand to what level TLB shootdown cost is acceptable in disaggregated memory systems, i.e., the point on which such migrations no longer burden memory management. Later, we vary page migration latency and global memory latency to understand their impact on the effectiveness of memory management. Based on these investigations, we propose a novel mechanism that removes much of these overheads from the critical path. Chapter 4 provides a detailed analysis about page migration support in FAM systems.

#### 1.4 Architecture-Aware Virtual Memory Support For Fabric Attached Memory Systems

Since memory-centric architectures leverage FAMs as physically shared memory pools, multiple compute nodes, potentially running applications from different users, can access pages in the same FAM memory modules. This access model is different from conventional HPC architectures where each compute node has its own memory modules and applications' memory accesses are limited to

its own nodes, unless explicitly requested from other nodes through software interface. Therefore, a new question arises: who is responsible for access control of FAMs? Without strict access control mechanisms, malicious OSes, applications, and PEs can potentially compromise the entire system by accessing the data of other users in the shared FAMs. Note that in this system architecture, there could be compute nodes containing PEs from different vendors. Even if not malicious, these PEs could contain bugs in their internal virtual memory implementation, which can compromise the whole system. Obviously, with such a wide attack surface, accesses to shared FAM modules need to be vetted externally, at the system-level, and not rely solely on internal access control within PEs. Pages in shared FAM pools can be managed in two different ways. The first approach is through transparently allocating FAM pages to nodes on-demand, i.e., each compute node has the illusion that it has a contiguous large physical space [47]. Such an approach is similar in spirit to how hypervisors give virtual machines (VMs) the illusion that each VM has a contiguous guest physical memory, which eventually gets translated into the real system physical address through the hypervisor. In this case, a memory broker node is dedicated to set up such translations for each node at the system level. The second approach is to expose each node to the real physical addresses (FAM addresses) and modify the OS kernel running on each node to communicate with the external memory broker to allocate FAM pages [47, 48].

Transparent management of FAMs' pages eliminates the need to modify the OS kernel and, most importantly, allows system-level vetting of accesses to FAMs through a second level of memory translation, from the node guest address to the FAM physical address. However, while this is similar to two-level translation in virtualized environments, flexibility, transparency, and security come at the cost of significant performance overheads due to the additional level of translation. In conventional x86 systems, each memory access can require up to four memory accesses for translation, however, when a second level is added, the number of memory accesses can be up to 24 [49]. We observe that significant performance overheads can be incurred when naively implement-

ing state-of-the-art implementations of two-level translation in the context of FAM architectures. Hence, in this paper, we focus on optimizing the implementation of virtual memory support for memory-centric systems.

To minimize the performance overheads of transparent access control and management support for shared FAM pools, we propose an efficient and secure architecture aware virtual memory management support for FAM systems. Chapter 5 studies the existing memory management schemes and discusses out proposed novel memory management approach for FAM systems.

## **CHAPTER 2: FABRIC-ATTACHED MEMORY SIMULATION**

In this chapter, we discuss the implementation of FAM simulation setup in SST. A FAM manager is developed which maintains the status of the global FAM. This FAM manager is used to connect multiple nodes to the global memory.

#### 2.1 Background

Disaggregated memory performance can be emulated on the real systems using device drivers and dividing physical memory to evaluate the remote memory [50, 51, 52]. In this setup, remote memory latency is emulated through a device driver. Unfortunately, relying on real-system emulation restricts the design space exploration to a narrow space that is constrained by the real-system configurations. Trace-driven simulations [53, 54] oversimplify the impact of system-level operations and the out-of-order nature of processing cores and memory systems. They are rarely scalable beyond a few cores, even with very simple memory and processor models. Moreover, it is difficult to model disaggregated memory as it requires multiple nodes to be simulated at the same time. Real-system prototyping takes a significant amount of time and limits the conclusions to the available hardware and software stack, which reduces the flexibility of design exploration. FAM system is explored using QEMU [41] by HP laboratories [42]. However, scaling the simulation setup to study number of nodes accessing FAM with QEMU is not practical (simple) or takes non-realistic time. To the best of our knowledge there is currently no simulation platform that can properly simulate and model disaggregated memory systems. Thus, to facilitate research efforts in disaggregated memory systems, we develop a disaggregated memory emulation environment that takes into consideration many important system-level aspects.

We choose SST to implement FAM system since, SST [55] has been proven to be one of the most reliable simulators for large-scale systems due to the scalability and modular design of its components. Further, SST is a discrete-event simulation model that is modular and easy to customize. This makes SST the perfect candidate for simulating disaggregated memory systems at scale. Implementing a disaggregated memory system design in SST opens up opportunities to explore and examine many challenges. One of the current limitations of SST is the lack of a centralized memory management entity that correctly models page faults and requests for physical frames from the simulated machine. Such a limitation becomes more relevant when there are a large number of shared resources (pools). Thus as an initial step we implemented a centralized memory management entity for disaggregated memory, Opal [56]. Opal is developed to investigate memory allocation policies, page placement, page migration, the impact of TLB shootdown, and other important aspects that are related to managing disaggregated memory systems.

#### 2.2 Opal: A Centralized Memory Manager

Disaggregated memory systems require global memory managers to handle the system shared memory, initiate and broadcast TLB shootdown requests, implement page migration and allow for sharing memory between nodes. To model these aspects of the system, we propose Opal, a centralized memory manager that is implemented as a part of SST to help researchers in studying the functionalities, bottlenecks and optimizations for managing disaggregated memory systems. For the rest of this section, we describe the Opal framework and how it can be utilized to investigate disaggregated memory systems.

Opal can be thought of as the OS memory manager and, in the case of a disaggregated memory system, the system memory allocator/manager. In conventional systems with a single level memory, once a process tries to access a virtual address, a translation is triggered to map the virtual

address to a physical address. If a translation is not found, and the hardware realizes that either there is no mapping to that virtual address or the access permissions would be violated, it triggers a page fault that is handled by the OS. The page fault handler maps the virtual page to a physical page that is chosen from a list of free frames (physical pages). Once a physical page is selected, its address is inserted in the page table along with the corresponding access permissions. Any successive accesses to that virtual address will result in a translation process that concludes with obtaining the physical address of the selected page. Since SST aims for fast simulation of HPC systems, it does not model the OS aspects of this sequence of events. However, the memory allocation process will have a major impact on performance for heterogeneous memory systems and disaggregated memory, simply because of the many allocation policies that an OS can select from. Moreover, allocation policies are not well understood on disaggregated memory systems, making it important to investigate them to discover the best algorithm or heuristics to be employed for both performance and energy efficiency. Opal is proposed to fill this role; facilitating fast investigation and exploration of allocation policies in heterogeneous and disaggregated memory systems.

Each component in SST typically represents a subsystem in a real system. SST models a wide range of components such as cores, MMU units, memory hierarchy, routers, and different memory models like DRAM and NVM. Components are ticked according to the component clock frequency set up during configuration. Links are used to communicate between components. Each link can be configured with a latency. We used the Ariel, Samba [57], Messier [58] and Merlin components in SST to simulate CPU cores, MMU unit, NVM memory and network respectively to implement disaggregated memory system design with the help of Opal component.

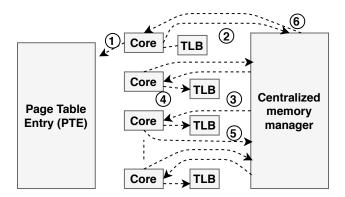

As shown in Figure 2.1, Opal and the external memory are maintained remotely and each node is connected to Opal and external memory through external links. Processing cores and memory management units are connected to global memory manager, Opal. In our design, we maintained an internal router that helps in communicating between cache and memory components. Likewise, an external router is maintained to connect the internal router with external memory through a network bridge that has its latency modelled after GenZ [30]. This way, communication between nodes and external memory takes place though internal and external routers. To make it realistic, links to external memory is configured with high latency and links to internal memory is configured with high latency and links to internal memory is configured with low latency.

Processing cores are connected to Opal to pass hints about memory allocations. For instance, calls to malloc or mmap do not immediately allocate physical pages, but are allocated at the time of mapping, during a page fault. Opal can use hints sent from cores to decide where to allocate the physical page. This is similar to libNUMA malloc hints, which will be recorded and used later by the kernel at the time of on-demand paging. CPU cores can trigger TLB shootdown events to all the other cores, including cores on other nodes. It is cumbersome to create links between each core to send events like TLB shootdown. Hence, we facilitate a communication medium between nodes through Opal. CPU cores communicate with Opal, sending TLB shootdowns events, using a core to Opal link.

The hardware MMU units have links to Opal, so that once a TLB miss and page table walk conclude with a page fault request (unmapped virtual address), a request for physical frame allocation is sent to Opal. Allocation requests come from the page table walker when the accessed virtual page has never been mapped, which resembles the minor page fault and on-demand paging on the first access to virtual pages in real systems. Opal searches for any hints associated with the page fault. If the hints are available, memory is allocated according to the hints from a specific memory region, if not, Opal checks for free frames according to the allocation policies, described in Section 2.2.2, and allocates a frame to the corresponding memory request. Apart from this, during TLB shootdown, Opal sends invalid addresses to all the MMU's through the MMU unit to Opal link and the MMU unit responds with an acknowledge event to Opal after invalidating the addresses.

Figure 2.1: A simulated system that uses Opal for centralized memory management.

Hence, Opal must be connected to both a MMU unit, such as Samba, for receiving page fault requests and a processing element, such as Ariel. To allow this, Ariel cores and Samba units should connect to their respective ports in Opal, *coreLink\_n* and *mmuLink\_n*. For example, *coreLink\_0* port of Opal can be connected to the *opal\_link\_0* port of an Ariel core and *mmuLink\_0* port of Opal can be connected to the *ptw\_to\_opal0* port of Samba.

Before diving into the details of Opal, we will start with discussing different ways of managing disaggregated memory systems:

#### 2.2.0.1 Exposing External Memory Directly to Local Nodes

In this approach a local node OS (or Virtual Machine) sees both the local memory and external memory, however, it needs to request physical frames from a central memory manager to be able to access external memory legitimately. To enforce access permission, and to achieve isolation between data belonging to different nodes/users, the system must provide a mechanism to validate the mappings and the validity of physical addresses being accessed by each node. To better understand the challenges of this scheme, Figure 2.1 depicts different options to implement access control on shared resources in such management scheme.

As shown in the Figure 2.1, Option 1 would be to check if the requesting node is eligible to access the requested address at the memory module level. This implementation requires a bookkeeping mechanism at the memory module level (or in the memory blade) to check the permission of every access. If the access is valid, then the request will be forwarded to the memory, otherwise either random data is returned or an error packet (access violation) is sent back to the requesting core. Since the external memory is shared between nodes, the system memory manager must have a consistent view of allocated pages and their owning nodes. One way to implement this is through a device driver (part of the local nodes' OS) that can be used to communicate, either through the network or predefined memory regions, with the external memory manager. Option 2 is similar but instead of relegating the permission check to the memory module, the router will have mechanisms to check if the accessed physical addresses are granted to the requesting node. In both options, nodes will not have direct access or modification privileges for permission tables, only the system memory manager will have such access. Such a guarantee can be implemented by encrypting requests with some integrity and freshness verification mechanisms. There are many benefits of these schemes, such as: page table walking process is not modified and it is much faster than virtualized environments (4 steps vs. 26 steps). Also, node-level memory manager optimizations

and page migrations are feasible (unlike virtualized environments). But the operating system must be patched with a device driver to communicate with external memory manager and the centralized memory manager becomes a bottleneck if not scalable.

#### 2.2.0.2 Virtualizing External Memory

In this approach, each node has an illusion that it owns all of the system memory. In fact, in this scheme, the OS does not need to be aware of the current state of the actual system physical memory. Figure 2.1 depicts the virtualized system memory scheme.

As shown in Figure 2.1, the system translation unit (STU) must be added to support translation from the *node physical address* to the *system physical address*. The STU can be implemented as an ASIC-based or FPGA-based unit that takes a physical address from the node and translate it into the corresponding system physical address. In case the address has never been accessed, an on-demand request mechanism is initiated by the STU to request system physical page. The STU might need to do a full system page table walk to obtain the node to system translation. Most importantly, the STU can be updated only through the system memory manager. This scheme is better if OS does not need to be changed. But the STU will need to walk the system level page table in addition to walking the node's page table at the node level. Also, there is no guarantee of where the system physical pages that back up the node physical pages exist.

#### 2.2.1 Opal Configuration

Opal should be configured with the component-specific, node-specific and shared memory-specific information as shown in Table 2.1. Component-specific information includes clock frequency, maximum instructions per cycle, etc. Node-specific information includes number of nodes, num-

ber of cores per node, clock frequency per node, per node network latency to access the Opal component, node memory allocation policy as explained in section 2.2.2 and local memory information. Shared memory-specific information includes the number of memory pools that shared memory is divided into and the respective memory pool parameters. Both per-node local memory and per-shared memory pool parameters are related to memory and they are explained separately in Table 2.2. Each of these parameters should be appended with memory related parameters as shown in Table 2.1. Table 2.2 describes the memory pool-specific parameters. Each memory pool, whether shared or local, needs a starting address, pool size, frame or page size, and memory technology.

| Parameter                | Description                                                                                                                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| clock                    | frequency of Opal component                                                                                                    |

| max_inst                 | maximum instructions processed in a cycle.                                                                                     |

| num_nodes                | number of nodes.                                                                                                               |

| node_i_cores             | number of cores per node.                                                                                                      |

| node_i_clock             | frequency of each node.                                                                                                        |

| node_i_latency           | latency to access Opal component per node.                                                                                     |

| node_i_allocation_policy | memory allocation policy per node.                                                                                             |

| node_i_memory.           | local memory-specific information per node. These come<br>under memory parameters and are shown in Table 2.2                   |

| shared_mempools          | number of shared memory pools to maintain shared mem-<br>ory.                                                                  |

| shared_mem.mempool_i.    | global memory-specific information per shared memory<br>pool. These come under memory parameters and are shown<br>in Table 2.2 |

We show a basic configuration used to test a disaggregated memory system with Opal in Figure 2.2. According to the example configuration, the system has 4 nodes ("*num\_nodes*" : 4) with a private memory each and shared global memory is divided into 4 memory pools ("*shared\_mempools*" : 4). The private memory uses *DRAM* ("*node0.memory.mem\_tech*" : 0) technology with a size of

Table 2.2: Memory Pool Parameters

| Parameter  | Description                                                                       |

|------------|-----------------------------------------------------------------------------------|

| start      | starting address of the memory pool.                                              |

| size       | size of the memory pool in KB's.                                                  |

| frame_size | frame size of each frame in memory pool in KB's. This is equivalent to page size. |

| mem_tech   | memory pool technology (0 : DRAM, 1 : NVM).                                       |

Figure 2.2: Example configuration

16MB ("node0.memory.size" : 16384), a starting address of 0 ("node0.memory.start" : 0). The total global or shared memory is 16GB, which is divided into 4 memory pools each of 4GB ("shared\_mem.memp ool0.size" : 4194304). The starting address of shared memory pool 0 is 001000000 ("shared\_mem.mempool0.start" : 001000000) which is equivalent to local memory (16MB) + 1; the starting address of memory pool 1 is 101000000 ("shared\_mem.mempool1.start" : 101000000, which is equal to the starting address of shared memory pool 0 + shared memory pool 0 is 0 size. Figure 2.2 shows the starting address of each memory pool, from which the size of each

memory pool can be deduced. Each shared memory pool is of *NVM* type ("*shared\_mem.mempool*0 .*mem\_type*": 1). Frame size or page size in both DRAM and NVM is 4*KB* ("*node*0.*memory.frame\_size*": 4 "*shared\_mem.mempool*0.*frame\_size*": 4). Memory allocation policy can be configured using "*node*0.*allocation\_policy*" parameter, which is explained in the Section 2.2.2. The network latency to communicate with Opal can be configured with "*node*3.*latency*" parameter. In our case we used 2 micro seconds latency to communicate with Opal.

#### 2.2.2 Memory Allocation Policies

Multiple memory allocation policies are implemented in our design, which are described below.

# 2.2.2.1 Local Memory First Policy:

Local memory is given more priority than shared memory, that is, memory is searched in local memory and if local memory is full then shared memory is searched for memory. If shared memory is spread into different memory pools, then a shared memory pool is chosen randomly among different memory pools until some space is found. If none of the memory pools are available, that is total memory is full, then an error message is thrown. This memory allocation policy can be chosen by setting "*allocation\_policy*" parameter of a node to 0.

# 2.2.2.2 Alternate Memory Allocation Policy:

For every two memory requests, one frame is allocated from local memory and the other from shared memory. For example, if two shared memory pools are maintained, first page is allocated from the local memory, second page is allocated from shared memory pool one, third page is allocated from the local memory, fourth page is allocated from the shared memory pool two and so on. This memory allocation policy can be chosen by setting "*allocation\_policy*" parameter of a node to one.

## 2.2.2.3 Round Robin Memory Allocation Policy:

Memory frames are scheduled to be allocated from shared and local memory based on the total number of memory pools, which includes local memory pool of a node and total shared memory pools in a round robin fashion. If two shared memory pools are maintained, then for the 1st memory request, memory is allocated from local memory, for the 2nd memory request, memory is allocated from shared memory pool 1, for the 3rd memory request, memory is allocated from shared memory and so on. This memory allocation policy can be chosen by setting "*allocation\_policy*" parameter of a node to 2.

#### 2.2.2.4 Proportional Memory Allocation Policy:

The proportion at which memory frames are allocated from shared and local memory is based on the fraction of local memory size to total shared memory size. For example, if the local memory size is 2GB and shared memory size is of 16GB, then, for the 1st memory allocation request, memory is allocated from local memory while the next 8 memory requests are allocated from shared memory in sequential order. For the next memory request, which is the 10th memory request, memory is allocated from local memory and so forth. This memory allocation policy can be chosen by setting "*allocation\_policy*" parameter of a node to 3.

#### 2.2.3 Communication Between Nodes

Opal also allows nodes to communicate directly with one another by sending hints with the same *fileID* to Opal using Ariel *ariel\_mmap\_mlm* and *ariel\_mlm\_malloc* calls. Opal checks if the received *fileID* is registered with any memory. If it is, then the specific page index is sent to the requesting node. If the *fileID* is not registered with any memory page, then memory is allocated based on the requested size. The allocated memory region is now registered with the requester *fileID*. Nodes can share information just by writing information to the specific pages. This reduces costly OpenMPI calls to share information between nodes.

# 2.3 Evaluation

We validated our design by calculating the performance of the system in-terms of instructions per cycle (IPC). We vary the number of nodes, number of shared memory pools and memory allocation policies. The average number of instructions per cycle is taken into consideration. Simulation parameters and applications that we used along with application parameters are shown in Tables 5.2 and 2.4 respectively.

Table 5.2 depicts simulation parameters for our experiments. According to this, each node has 8 cores and each core can serve up to 2 instructions per cycle. The clock frequency of the cores is 2GHz. Each core is configured to service up to 100 million instructions. Three levels of cache are used, L1, L2, and L3, with sizes of 32KB, 256KB and 16MB respectively and each are of non-inclusive type. Local memory size is 2GB and is of DRAM type. External memory is of NVM type with 16GB size. Network latency is critical in disaggregated memory system. For the external network latency, we use 20*ns* for input and 20*ns* for output buffer latency (in total 40ns latency) which has been modelled after the GenZ network latency.

| Element                  | Parameters                                                |

|--------------------------|-----------------------------------------------------------|

| CPU                      | 8 Out-of-Order cores, 2GHz, 2 issues/cycles, 32 max. out- |

|                          | standing requests                                         |

| L1                       | private, 64B blocks, 32KB, LRU                            |

| L2                       | private, 64B blocks, 256KB, LRU                           |

| L3                       | shared, 64B blocks ,16MB, LRU                             |

| Local memory             | 2GB, DDR4-based DRAM                                      |

| Global memory            | 16GB, NVM-based DIMM (PCM), 128 max. outstanding          |

|                          | requests, 16 banks                                        |

|                          | 300ns Read Latency, 1000ns Write Latency                  |

| External network latency | 20ns input and 20ns output latency[59]                    |

Table 2.3: Exploring Allocation Policies Simulation Parameters

Table 2.4: Applications used to Exploring Allocation Policies

| Application     | Value                   |

|-----------------|-------------------------|

| XSBench [60]    | -s large -t 8           |

| Lulesh [61]     | -s 120                  |

| SimpleMoC [62]  | -t 8 -s                 |

| Pennant [63]    | leblancbig.pnt          |

| miniFE [64]     | -nx 140 -ny 140 -nz 140 |

| NAS:IS [65, 66] | class C                 |

Since our focus is on HPC applications we evaluated our design using 6 HPC mini applications. XSBench [60], a mini-app representing a key computational kernel of the Monte Carlo neutronics application, OpenMC. Lulesh [61], a mini-app for hydrodynamics. Pennant [63] is an unstructured mesh physics mini-app designed for advanced architecture research. SimpleMOC [62], mini-app is to demonstrate the performance characteristics and viability of the Method of Characteristics (MOC) for 3D neutron transport calculations in the context of full scale light water reactor simulation. NASA IS [65, 66] mimics the computation and data movement characteristics of large scale computational fluid dynamics (CFD) applications; IS is an integer sort kernel which performs a sorting operation. MiniFE [64] is a proxy application for unstructured implicit finite element

codes. Applications and their parameters are shown in Table 2.4. We decided upon these specific applications as these are memory intensive.

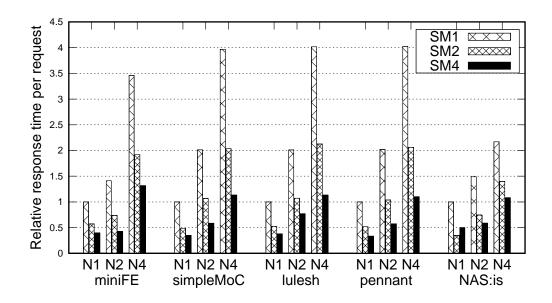

Figure 2.3: Performance in instructions per cycle of disaggregated memory system with different memory allocation policies. *N* indicates number of nodes. *SM* indicates number of shared memory pools. *LMF*, *ALT*, *RR* and *PROP* indicate local memory first, alternate memory, round robin and proportional memory allocation policies.

# 2.3.1 Opal Memory Allocation Policies

If more memory is allocated from shared memory, the performance of the system worsens as the delay in accessing shared memory is high. Memory allocation policies, explained in section 2.2.2, control allocation of local and shared memory. Contention at shared memory is one of the key factors that contributes to the performance in disaggregated memory systems. The more the contention at the memory, the more will be the delay in accessing memory. Contention at memory is higher if more nodes are accessing memory at a given time. Accordingly, we observed the following traits for each memory allocation policy.

#### 2.3.1.1 Local Memory First (LMF) Policy:

According to the local memory first allocation policy, memory is allocated in private memory first and if there is no space in private memory then memory is allocated from global memory. The benchmark applications that we used occupy a maximum of approximately 500MB of memory to generate 100 million instructions. Because each node has its private memory of 2GB, all of the memory pages should be allocated form local memory and the performance of the nodes should be same as there is no contention at local memory due to other nodes. Our results in Figure 2.3(a) reflect this. Irrespective of the number of nodes and number of shared memory pools the performance of each node, i.e., number of instructions per cycle is equal. We show this to understand the memory intensity of the benchmarks. According to Figure 2.3(a), the IPC of XSBench and MiniFE is around 0.6. Lulesh, Pennant and NAS:IS have an IPC of around 1.1. Wherein the IPC of SimpleMoC is 1.6. From this it can be understood that XSBench and MiniFE are more memory intensive, SimpleMoC is less memory intensive, and Lulesh and Pennant are moderately memory intensive among the set of benchmarks that we experimented with.

### 2.3.1.2 Alternate (ALT) Policy:

In this memory allocation policy, for every other page fault, a page is allocated from the shared memory. Accordingly, almost half of the pages are from the shared memory, i.e., among 500MB of

memory that the applications use, 230MB of memory is from shared memory. From Figure 2.3(a) the IPC of Lulesh is 1.1 while Figure 2.3(b) shows an IPC of 0.2. The performance decreases by 81% when shared memory is used. It further decreases if there are a greater number of nodes accessing the shared memory. For the same benchmark, the IPC is 0.05 when 4 nodes share the external memory. As the number of nodes making use of the shared memory increases, contention at the shared memory increases and the individual node performance decreases. Contention can be reduced by dividing the shared memory into number of memory pools and hence the performance of the system increases. From Figure 2.3(b) it can be seen that for Pennant, the IPC is 0.12 and 0.34 with 1 node when shared memory is maintained in 1 shared memory pool and 4 shared memory pools respectively. With 4 nodes, the IPC is 0.1 when shared memory is maintained in 4 shared memory pools, which is almost equivalent to the performance of the system with 1 node when shared memory 1 shared memory pool.

# 2.3.1.3 Round Robin (RR) Policy:

Memory is allocated based on the number of shared and local memory pools. The more the number of shared memory pools, the more memory addresses are allocated from the shared memory and the performance decreases. Figure 2.3 shows that, for the 4 node SimpleMoC benchmark with 4 shared memory pools, the IPC is 0.15 for the RR policy and 0.25 for the ALT policy. This is due to more memory is allocated from shared memory in the RR memory allocation policy with 4 shared memory pools. When shared memory is maintained only in 1 memory pool, RR memory allocation policy is same as ALT memory allocation policy. From Figure 2.3(c) it can also be observed that, for some applications, when shared memory is maintained in more shared memory pools, the performance decreases due to more memory being allocated from shared memory. For instance, the IPC of XSBench drops from 0.28 to 0.23 when shared memory is divided into 4 shared memory pools compared to when shared memory is maintained in 1 shared memory pool.

# 2.3.1.4 Proportional (PROP) Policy:

Memory allocation in based on the proportion of local and shared memory. From the configuration that we used, 16GB of shared memory and 2GB local memory, the proportion at which shared and local memory are allocated is 8:1, i.e., for every 9 memory allocations 8 memory allocations are from shared memory and 1 memory allocation is from local memory. According to this, more memory is allocated from shared memory in comparison with RR and ALT allocation policies. From Figure 2.3(d) it can be clearly observed that, for miniFE, the IPC is 0.06 with 1 node and when shared memory is maintained in only 1 shared memory pool. This is less than the IPC of ALT memory allocation policy and RR memory allocation policy which is around 0.11 each, from Figures 2.3(b) and 2.3(c). As the nodes increased from 1 to 4, the IPC of the system further decreased from 0.06 to 0.02. When shared memory is divided into 4 shared memory pools the IPC of the system increased to 0.06.

We observe that dividing shared memory into more shared memory pools does not always improve the performance of the system. The performance depends on the application characteristics as wellFrom Figure 2.3 it can be seen that for NAS:IS benchmark, for several memory allocation policies, the IPC, when shared memory is maintained in 2 shared memory pools, is more when compared with IPC of the system when shared memory is maintained in 4 shared memory pools with 1 node in the system. We suspect that NAS:IS is latency sensitive and performs better when local memory is used even though it has limited memory-level parallelism. When shared memory is divided into 2 shared memory pools, this can lead to a increase in the number of memory accesses serviced by global memory as in round-robin allocation policy, however, this can also improve the bandwidth and memory-level parallelism. Meanwhile, increasing the number of pools to 4 can lead to performance degradation as the increase in memory access latency due to accessing global memory is no longer amortized by the increase in bandwidth.

# 2.4 Conclusion

While FAM systems are a useful system design, before fully adopting such architectures, there are a lot of challenging design parameters that must be fully understood such as latency, memory management policies, virtual to physical address translation, page migration, and quality of service. To this end, we proposed a new FAM system simulating model to examine and explore various aspects related to such an architecture. Specifically, we implemented a centralized memory manager in SST which has capability to manage memory in disaggregated memory systems.

# CHAPTER 3: INVESTIGATING PERFORMANCE IMPROVEMENTS BY ENFORCING FAIRNESS IN FABRIC-ATTACHED MEMORY SYSTEMS

FAM systems opens a path for designing future computing systems. However, as asserted, memory access latency is a concern in such systems. One of the reasons for the latency is, the global memory is accessed by various applications from a number of nodes. This leads to contention at the global memory not just from the applications from within the node, but from applications from a number of nodes accessing FAM. Using the FAM simulation setup that is explained in chapter 2, Figure 3.1 shows the delay (observed by the core) in accessing memory per request in disaggregated memory systems when the FAM is dedicated to a single node and is shared between four nodes. These results are with respect to system configuration shown in Table 3.1. More details about the methodology and benchmarks are discussed in section 3.3 in detail.

Figure 3.1: Average memory access delay per request observed by the core in dedicated single node FAM system (FAM is accessed by only one node) and shared four node FAM system (FAM is shared by four nodes).