# Leveraging Non-Volatile Memory in Modern Storage Management Architectures

## Dissertation

zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

> vorgelegt an der Technischen Universität Dresden Fakultät Informatik

> > eingereicht von Lucas Lersch, M.Sc.

geboren am 6. November 1990 in Porto Alegre, Brasilien

Gutachter: Prof. Dr.-Ing. Wolfgang Lehner

Technische Universität Dresden

Fakultät Informatik

Institut für Systemarchitektur Lehrstuhl für Datenbanken

01062 Dresden

**Prof. Dr.-Ing. Dr. h. c. Theo Härder** Technische Universität Kaiserslautern

Fachbereich Informatik

Lehrgebiet Informationssysteme

AG Datenbanken und Informationssysteme

67653 Kaiserslautern

Tag der Verteidigung: 30. Oktober 2020

Dresden, den 30. Oktober 2020

# **ABSTRACT**

Non-volatile memory technologies (NVM) introduce a novel class of devices that combine characteristics of both storage and main memory. Like storage, NVM is not only persistent, but also denser and cheaper than DRAM. Like DRAM, NVM is byte-addressable and has lower access latency. In recent years, NVM has gained a lot of attention both in academia and in the data management industry, with views ranging from skepticism to over excitement. Some critics claim that NVM is not cheap enough to replace flash-based SSDs nor is it fast enough to replace DRAM, while others see it simply as a storage device. Supporters of NVM have observed that its low latency and byte-addressability requires radical changes and a complete rewrite of storage management architectures.

This thesis takes a moderate stance between these two views. We consider that, while NVM might not replace flash-based SSD or DRAM in the near future, it has the potential to reduce the gap between them. Furthermore, treating NVM as a regular storage media does not fully leverage its byte-addressability and low latency. On the other hand, completely redesigning systems to be NVM-centric is impractical. Proposals that attempt to leverage NVM to simplify storage management result in completely new architectures that face the same challenges that are already well-understood and addressed by the traditional architectures. Therefore, we take three common storage management architectures as a starting point, and propose incremental changes to enable them to better leverage NVM. First, in the context of log-structured merge-trees, we investigate the impact of storing data in NVM, and devise methods to enable small granularity accesses and NVM-aware caching policies. Second, in the context of B+Trees, we propose to extend the buffer pool and describe a technique based on the concept of optimistic consistency to handle corrupted pages in NVM. Third, we employ NVM to enable larger capacity and reduced costs in a index+log key-value store, and combine it with other techniques to build a system that achieves low tail latency. This thesis aims to describe and evaluate these techniques in order to enable storage management architectures to leverage NVM and achieve increased performance and lower costs, without major architectural changes.

# **ACKNOWLEDGMENTS**

While this thesis carries a single name as its author, it is actually the result of the contributions and support of many people during the years that led to it.

First and foremost, it has been a privilege to be mentored and supervised by Prof. Dr.-Ing. Wolfgang Lehner. Not only has Wolfgang contributed significantly to my professional growth, but he has also been incredibly supportive on a personal level helping me to face the challenges and get through the obstacles I have faced along the way. Furthermore, it is truly inspiring to witness the positive impact that Wolfgang has in the life of its students.

Second, I would like to thank Prof. Dr.-Ing. Dr. h. c Theo Härder for reviewing this thesis. Prof. Härder was one of the people who inspired me to pursue a PhD degree, by granting me the opportunity to participate in his research group through an exchange program in 2012 during my bachelor's and later master's degree programs.

I am also immensely grateful for the opportunity to conduct this work in close collaboration with SAP, as part of the SAP HANA Database Campus. Ivan Schreter had a major role in supervising my work and teaching me a lot about software development. Arne Schwarz has been fundamental in leading the SAP HANA Database Campus and ensuring that the other students and I had the necessary tools, equipment, and environment required for us to focus on our research work. I would like to extend my gratitude to Alexander Böhm and Norman May for helping making the goals of SAP HANA Database Campus a reality. I would also like to thank the Intel colleagues Thomas Willhalm, Roman Dementiev, Otto Bruggeman and Heinrich Teiken for all of the support they provided me while I was conducting my research.

I would specially like to express my gratitude to two colleagues whom I also have the privilege of calling friends. First, it was while working with Caetano Sauer during my master's degree program that I was inspired to pursue a PhD degree. Not only has he graced me many times with insightful technical discussions, but Caetano has also been there to offer his support during my most difficult of times, to which I am most grateful. My gratitude to Caetano is also extended to his wife Irina and daughter Aria, for always being so kind and welcoming. Second, I would like to thank Ismail Oukid for enabling me to do my PhD as part of the SAP HANA Database Campus. Once I was given the opportunity, he continued to guide my work, even through our occasional heated debates. I look forward to working with Ismail again in the future.

I am also grateful to my colleagues at SAP, who have not only taught me a lot on a professional level, but also made my PhD years a lot more fun. Although I have shared

a limited time with Iraklis, Marcus, Michael R., Robert, David, and Elena, they all served as role models for ideal PhD candidates. I was privileged to start my PhD journey with Georgios, who always contributed to the socialization of the group, and Frank, who always was willing to help me by sharing his deep technical knowledge. Florian has shown me how important it is to insist on high standards. Matthias amazed me with his incredible broad knowledge of things. Thomas has supported me immensely not only on a professional level, but also personal one through engaging discussions. Stefan has been my favorite person to share both my frustrations and achievements during our daily afternoon breaks. Robin has made otherwise stressful days brighter with his sense of humor, good music taste, and by surprising me on how much denial a person can sustain about "The Last Jedi" being a horrible movie and a mistake in the "Star Wars" sequel trilogy. I also had the privilege to witness Tiemo and Michael B. transition from master's students to PhD candidates, and I look forward to seeing them achieve great things. It was also a pleasure to have met Mehdi and Jonas in the final months of my PhD and I wish them success.

On a personal level, I would like to thank my friends, both near and far, who have supported me and gave me the strength to endure this journey. As a representative of these friends, Gilson was a always close and supportive one. In supply-chain management, it is often said that the last mile is the most difficult one when delivering products. This seems to also have been the case of my PhD time, not only due to its own challenges, but also due to external events. I am grateful to Diana for having made this last mile a lot easier. Finally, I would like to thank all my family members who have supported me unconditionally throughout my whole life. I feel truly privileged to have had all the aforementioned people offering their support and encouragement, not only while I conducted my research and wrote this dissertation, but in my personal life as well.

# **CONTENTS**

| 1 | INT | RODUCTION                              | 13             |

|---|-----|----------------------------------------|----------------|

|   | 1.1 | Non-Volatile Memory                    | 14             |

|   | 1.2 | Challenges                             | 15             |

|   | 1.3 | Non-Volatile Memory & Database Systems | 16             |

|   | 1.4 | Contributions and Outline              | 17             |

| 2 | Вас | CKGROUND                               | 19             |

|   | 2.1 | Non-Volatile Memory                    | 19<br>21<br>22 |

|   | 2.2 | Related Work                           | 25             |

|   | 2.3 | Case Study: Persistent Tree Structures | 31             |

| 3 | Loc | G-STRUCTURED MERGE-TREES               | 45             |

|   | 3.1 | LSM and NVM                            | 45             |

|   | 3.2 | LSM Architecture                       |                |

|   | 3.3 | Persistent Memory Environment          | 49             |

|   | 3.4 | 2Q Cache Policy for NVM                | 51             |

|   | 3.5 | Evaluation                             | 53<br>54       |

|   | 3.6 | Additional Case Study: RocksDB         |                |

| 4 | B+1 | TREES                                                                                                                                                   | 61              |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|   | 4.1 | B+Tree and NVM                                                                                                                                          | 62<br>63        |

|   | 4.2 | Persistent Buffer Pool with Optimistic Consistency                                                                                                      | 65              |

|   | 4.3 | Detecting Corruptions                                                                                                                                   |                 |

|   | 4.4 | Repairing Corruptions                                                                                                                                   | 73              |

|   | 4.5 | Performance Evaluation and Expectations                                                                                                                 | 76              |

|   | 4.6 | Discussion                                                                                                                                              | 80              |

| 5 | IND | EX+LOG KEY-VALUE STORES                                                                                                                                 | 83              |

|   | 5.1 | The Case for Tail Latency                                                                                                                               | 84              |

|   | 5.2 | Goals and Overview                                                                                                                                      | 85              |

|   | 5.3 | Execution Model                                                                                                                                         | 85<br>86        |

|   | 5.4 | Log-Structured Storage                                                                                                                                  | 89              |

|   | 5.5 | Networking                                                                                                                                              | 90              |

|   | 5.6 | Implementation Details  5.6.1 NVM Allocation on RStore  5.6.2 Log-Structured Storage and Indexing  5.6.3 Garbage Collection  5.6.4 Logging and Recovery | 91<br>92<br>94  |

|   | 5.7 | System Operations                                                                                                                                       | 98              |

|   | 5.8 | Evaluation  5.8.1 Methodology  5.8.2 Environment  5.8.3 Other Systems  5.8.4 Throughput Scalability                                                     | 99<br>99<br>100 |

|    | ;     | 5.8.5  | Tail Later | тсу   |       |      | <br> |  | <br> | <br> |  | <br> |  | 103 |

|----|-------|--------|------------|-------|-------|------|------|--|------|------|--|------|--|-----|

|    | ;     | 5.8.6  | Scans .    |       |       |      | <br> |  | <br> | <br> |  | <br> |  | 104 |

|    | ;     | 5.8.7  | Memory     | Consu | ımpti | on . | <br> |  | <br> | <br> |  | <br> |  | 106 |

|    | 5.9   | Relate | ed Work    |       |       |      | <br> |  | <br> | <br> |  | <br> |  | 107 |

| 6  | Con   | ICLUS  | ION        |       |       |      |      |  |      |      |  |      |  | 109 |

| Bı | BLIOG | RAPH   | łΥ         |       |       |      |      |  |      |      |  |      |  | 113 |

| Α  | PiBE  | NCH    |            |       |       |      |      |  |      |      |  |      |  | 125 |

# INTRODUCTION

Storage managers are in the core of database systems. They are critical for achieving high performance in the overall system by enabling efficient access to slower storage devices which usually become the bottleneck. Furthermore, storage managers are also responsible for providing the A (atomicity) and D (durability) of the ACID properties [HR83], thus preventing data loss and corruption. As a consequence of being so critical, storage management has to be constantly revisited in order to properly leverage modern hardware and keep the pace with the ever growing data processing demands.

A good example of this constant revisit is the The Five-Minute Rule series, which surveys once per decade the advances in modern hardware and their implications in database systems. In the original paper from 1987 [GP87], Jim Gray and Gianfranco Putzolu considered metrics of DRAM and HDD, such as latency, bandwidth, and cost, to calculate the break-even point at which the cost of keeping a page in memory matches the cost of doing I/O to read the page from HDD. They introduced the rule of thumb that named the series: "Pages referenced every five minutes should be memory resident". In 1997, Jim Gray and Goetz Graefe revisited the work in view of technological improvements of HDDs: ten-fold increase in access speeds, hundred-fold increase in capacity, and ten-thousand-fold decrease in costs [GG97]. In 2007, Goetz Graefe investigated the impact of a novel technology by the time: flash [Gra07]. While it was still in its early stages and many questions were still open, it was a promising technology. The main take-away was the prediction that flash would be used to fill the gap between DRAM and HDD, which has since been proven correct. More recently, in 2017, Appuswamy et. al. revisited the discussion in view of now well-established NAND flash-based solid-state storage devices (SSD) [ABGA17]. The initial challenges imposed by flash in 2007, namely reduced lifetime and higher costs, are long gone and, as a consequence, SSDs became the main storage device, thus relegating HDDs to a high-density storage medium for infrequently accessed data. The performance gap between DRAM and SSDs is reduced even further with the advent of PCIe NVMe SSDs, also referred to as enterprise SSDs. The work also scratches the surface of a novel storage technology rising on the horizon: non-volatile memory (NVM).

It is still too early to revisit the series in view of NVM. Even if the technology is currently available, it is not yet as established as DRAM, SSDs, or HDDs. Many works are exploring ways to properly leverage NVM in the context of database systems and answering open questions. The advancements made by these works will pave the way to the next chapter in the *The Five-Minute Rule* series. This dissertation aspires to be one of these works.

### 1.1 NON-VOLATILE MEMORY

Many different underlying technologies (PCM [PSU+70], carbon nanotubes [DVTBH13], ReRAM [Chu19], STT-MRAM [HYY+05, H+08], battery-backed DRAM) and names (nonvolatile memory, NVRAM, storage class memory, persistent memory) belong to a novel class of storage devices and are often used interchangeably. Although they might have different properties, they all refer to byte-addressable persistent media that blurs the boundary between main memory and storage. This is the main reason why history will not simply repeat itself with a faster media, as it was the case with flash-based SSDs. NVM has a higher potential of disrupting modern software stacks.

Works dating from as early as the 1980s entertained the idea of such a technology and its impacts in system architectures [Zak81, Cha78, Wri83, DGS80]. However, the assumption was mostly theoretical [Chu71] or unpractical due to technological limitations or prohibitive costs, existing only in the form of niche accelerators [Mic17, Tec18]. Recent technological advancements made this technology real and more accessible. More prominent is the 3D XPoint technology<sup>2</sup>, developed by Intel and Micron [Mic20, Eva15]. Intel currently commercializes 3D XPoint both as regular Optane PCle NVMe SSD [Int20b] and Optane DC Persistent Memory Modules (DCPMM for short) [Int20c]. The latter is the one we focus on in this work. As a result, there is renewed attention to this area of research as it promises to deliver the long-awaited features required to blur the boundaries between memory and storage. But how are these boundaries blurred? Or in other words, what does byte-addressable really mean? Since this term is often used with different meanings, it is appropriate to discuss and make explicit the definition used in this work.

Common consensus usually defines main memory (DRAM) as byte-addressable and storage (HDD and SSD) as block-addressable. This definition is often based on the fact that the programmer can access a single byte in DRAM. However, from this point of view, common file system interfaces also allow the programmer to read a single byte from a file. It is true that the underlying file system is actually reading a whole block (usually 4 kB) from storage into memory in order to provide access to that single byte, but that is also the case in modern CPU architectures, in which a block (usually much smaller and referred to as cache line) is read from memory into the CPU caches. In other words, conceptually there is no difference, as in both cases data is always transferred at larger granularities, be it a block, page, or cache line. Therefore, this definition is too loose and considered inadequate to define byte-addressability. Our definition focus more on the access path rather than on the access granularity. Whenever we refer to byte-addressability, we mean that NVM is attached directly to the same bus as regular DRAM and therefore it is also accessed through the CPU caches and shares the same virtual memory space.

In addition to byte-addressability, NVM also introduces other attractive characteristics. In comparison to modern DRAM, 3D XPoint is cheaper [Aco19] and prices are expected to drop within the next years. It is also denser, in the sense that the largest DRAM module commercially available is 128 GB while Intel has already announced a single DCPMM of up to 1TB. The latency is higher than that of DRAM, but within the same order magnitude and, therefore, lower than NAND flash. The bandwidth, is better than NAND flash, but still far from that of DRAM. Finally, 3D XPoint also has a higher write endurance than modern NAND flash. All these advantages, however, come at a cost.

<sup>&</sup>lt;sup>1</sup>In this work we opted for using the term *non-volatile memory*, or NVM for short.

$<sup>^2</sup>$ An analysis has shown that 3D XPoint is based on *phase-change memory* (PCM) [Cho17].

# 1.2 CHALLENGES

The opportunities mentioned also entail challenges, following the "no free lunch" conjecture. In the case of NVM, it is beneficial to consider the challenges under two different scopes: reading from NVM and writing to NVM.

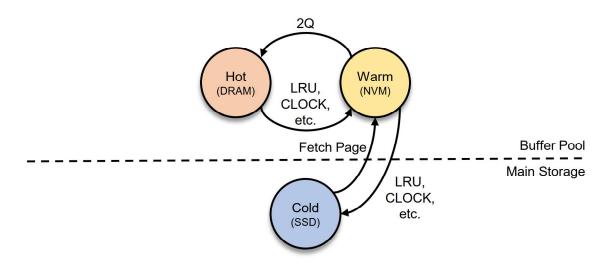

In terms of reading, the challenge lies in investigating NVM performance characteristics in order to properly fit it into the storage hierarchy. For years, similar questions have being investigated by many works in the context of tape, HDDs, SSDs, and DRAM. In the case of byte-addressable NVM, these works only cover part of the problem. In the example of the The Five Minute Rule mentioned previously, the rule only dictates which pages should be evicted from DRAM, but it does not focus so much on which pages should be moved to DRAM. Fair enough, before NVM this was never really a concern, since there was no choice, as a page always had to be read from persistent storage to DRAM in order to be accessed. Even if a decision was made to evict a page immediately after reading it from storage, the high I/O cost was already paid. In the case of NVM, pages can be directly accessed without any additional I/O. Therefore, NVM introduces a new dimension that should be considered when optimizing data placement and buffer policies.

Writing directly to NVM is hard. Database systems rely on persistent data to always be consistent in some way. To achieve a desired degree of consistency, it is required full control of what and when is made persistent. For example, transactional recovery algorithms require log records to be persisted prior to the updated page (a.k.a. write-ahead logging). The challenge comes from the fact that, while systems have full control over data movement between memory and traditional storage, this is not the case with NVM. Since NVM can be accessed directly by the CPU, corruption and data loss may occur for many different reasons, such as updated data staying in the CPU cache and being lost at a power failure, or the CPU arbitrarily evicting (and therefore persisting) cache lines in the wrong order. In other words, as opposed to the traditional memory-storage interaction, there is no way of pinning a cache line to prevent it from being evicted by the CPU.

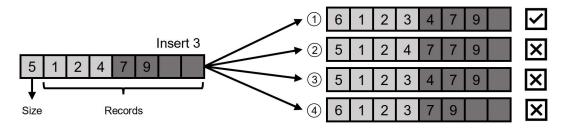

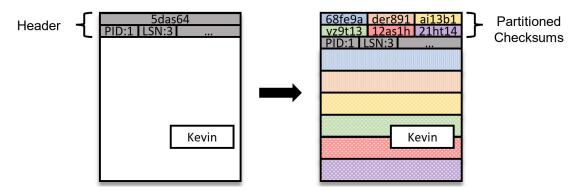

Figure 1.1 better illustrates the challenge with an example. The left-hand side shows the memory layout of a sorted array in NVM that spans two cache lines (indicated by the different shades of gray). The first position of the array indicates the current size, while each remaining record is represented by an integer. Three steps are required for inserting a new record 3: move records 4-9 one position to the right in order to make space, insert record 3 in the appropriate position, increment the size from 5 to 6. A failure might occur at any intermediate state of this operation and upon restart the sorted array may be found in one of different states illustrated on the right-hand side. In state (1), the operation completed successfully before the failure and the array is found in a consistent state. All the other states are inconsistent. In 2, the records 9 and 7 were moved one position to the right, the CPU arbitrarily evicted the second cache line, and the failure occurred. In ③, the insertion completed, but the cache lines were evicted and the power failure occurred before the size was updated. Finally, in 4, the insertion completed, the size was updated, but only the first cache line was evicted before the failure, while the second portion of the array remained in its original state. The example shows how such a simple and fundamental operation can easily lead to data being corrupted when NVM is used as persistent storage. To a certain extent, addressing this challenge is in the core of many modern works that propose architectures, data structures and algorithms in the context of NVM.

**Figure 1.1:** Possible states if a failure occurs while inserting a record in a sorted array in NVM (figure inspired by [CJ15]).

### 1.3 NON-VOLATILE MEMORY & DATABASE SYSTEMS

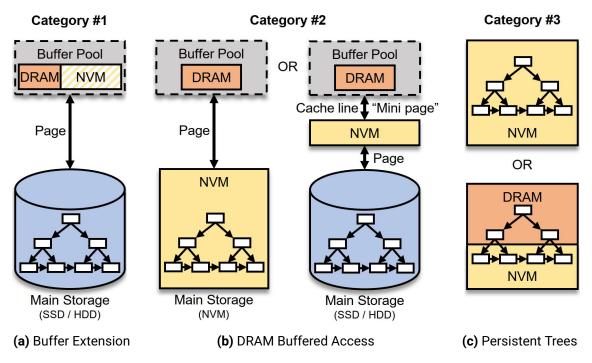

Many works investigate NVM in the context of databases. They either focus on individual components of the system, such as data structures [CJ15, OLN+16, ALML18], memory allocators [CCA+11, BCB16, OBL+17], logging schemes [HSQ14, WJ14, APP16], or on the database architecture as a whole. These works can also be categorized based on their initial assumptions and expectations regarding NVM. In this dimension, we observe that two categories can be identified: a *conservative* approach and a more *radical* approach.

Conservative approaches simply treat NVM as a faster SSD by accessing it through regular file system interfaces [GXH+11, PWGB13, EGA+18]. These approaches are commonly seen in industry, under the consideration that NVM is not well-established enough to justify expensive re-architecting efforts. The main advantage is that NVM is used transparently as a caching layer between DRAM and SSD, thus leveraging all devices in the modern storage hierarchy and avoiding the previously mentioned challenge of directly writing to NVM. Therefore, these systems are *NVM-agnostic*, as they behave exactly the same way, from an architectural point of view, both in the presence and absence of NVM.

On the other hand, **radical approaches** are *NVM-centric*, in the sense that they propose novel techniques with the goal of fully leveraging NVM characteristics to achieve higher performance. Recent works in the research community proposing novel database architectures fall in this category [Kim15, OBL<sup>+</sup>14, PAA<sup>+</sup>17]. Furthermore, an extreme assumption is that NVM performance and cost will lead to the extinction of modern DRAM and storage technologies, and drive the adoption of what is known as *single-level systems*. The notion of single-level systems is not new [KELS62] and refers to the idea of having no separation between volatile data and persistent data. While this assumption is far-fetched, it is made by many works [YWC<sup>+</sup>15, CJ15, WLL18, ALML18], as it opens interesting research questions. However, both conservative and radical approaches have drawbacks.

Conservative approaches have two main disadvantages. First, the lower latency, one of the major selling points of NVM, might not be observed, as access to persistent media may be dominated by kernel and file system operations, which become relatively more expensive when compared to I/O costs on modern SSDs. Second, it does not leverage byte-addressability and still imposes unnecessary data movement between DRAM and NVM. In the case of radical approaches, the main disadvantage comes from the fact that they are too optimistic regarding a quick and wide adoption of NVM and therefore the proposed architectures are very different from traditional systems. As a consequence, there is no

obvious way to migrate from a well-established traditional architecture to NVM-centric approaches, since they do not consider the modern storage hierarchy comprised of DRAM, SSD, HDD, and even tape. This becomes an issue since we consider that, as the time of writing and for the near future, NVM will not replace either DRAM or SSD, and therefore it must coexist harmonically with these other devices. Furthermore, the alternative of developing a complete new system from scratch is often unfeasible in practice due to high development costs. Therefore, we argue that moderate approaches are required.

Two principles should guide moderate approaches. First, they should focus on transforming systems designed for traditional devices (DRAM, SSD, HDD) into systems that leverage all aspects of NVM, mainly the byte-addressability and persistency. This is done to a certain extend by hybrid data-structures [OLN+16, XJXS17], which integrate NVM into regular memory data structures in order to make them persistent. While these data structures are often used as containers and building blocks, it is important to also look at this principle from the perspective of a more complete system. Second, the changes required should not be so disruptive that the architectural behavior of the system is completely changed. In other words, the architecture should not become dependant on the presence of NVM.

# 1.4 CONTRIBUTIONS AND OUTLINE

As mentioned in the beginning of this chapter, storage management in database systems is likely to be the area most impacted by the advent of NVM. Following the previously mentioned moderate approach, we investigate the impact of NVM in the three most common modern architectures for storage management: LSM, B+Tree and index+log [IC20]. For each one of them, we take the current state-of-the-art architecture as a starting point and explore potential use-cases, trade-offs, opportunities, and challenges in view of NVM. The goal is to leverage NVM as more than simply faster storage, while avoiding the, at times prohibitive, effort to design and implement a completely new architecture. In the following, we provide an overview of the organization of this dissertation by giving an overview of each chapter and their respective contributions<sup>3</sup>:

- Chapter 2 lays the general technical background on NVM required for the understating of the next chapters. We also cover related work and conclude with our case study on persistent data structures [LHO+19], in which we revisit persistent tree structures proposed by prior work. Since these persistent trees were originally evaluated on emulation platforms, we re-implement and re-evaluate them on real NVM hardware as a way of setting the expecations of its real performance and behavior. The required background specific to each following chapter is introduced in the chapter itself.

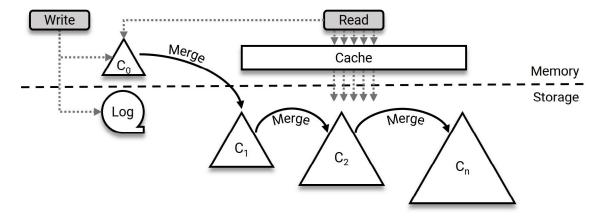

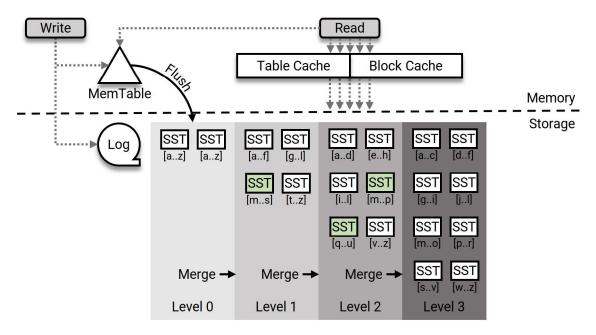

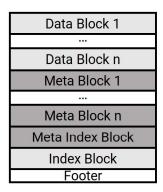

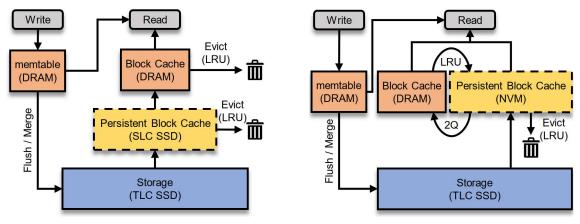

- Chapter 3 explores the synergy between NVM and log-structured merge-tree (LSM) systems [LOLS17, LOSL17]. We take LevelDB as a first case study and propose a persistent memory environment, Pmemenv, that enables LevelDB to directly access NVM. We also analyze the caching behavior and propose a 2Q Cache Policy for NVM to better leverage the byte-addressability. Finally we complement with a more recent case study on RocksDB (a more modern system) and on real DCPMM.

<sup>&</sup>lt;sup>3</sup>Many of the contributions have been peer-reviewed and published in the referenced papers.

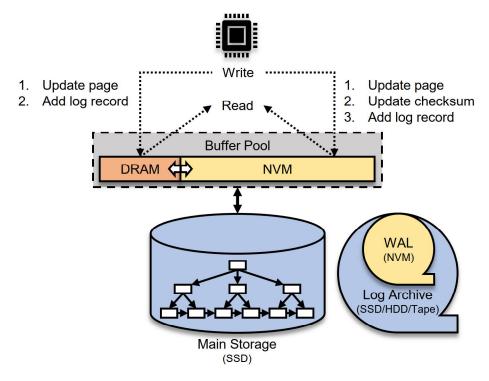

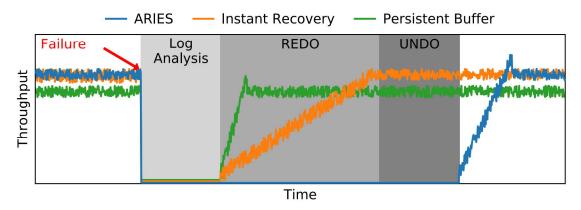

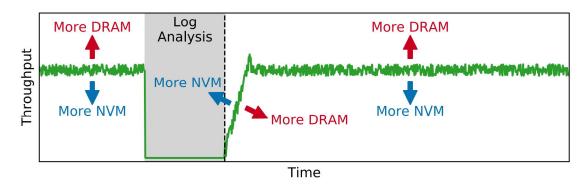

- Chapter 4 investigates opportunities in the context of B+Tree architectures. We propose an extended buffer pool with an optimistic consistency model [LL019]. The optimistic consistency model relies on a checksum algorithm and recovery infrastructure common to most database systems, therefore requiring minor architectural modifications. This introduces a knob that enables the system to choose a trade-off between more NVM (lower costs and faster recovery) or more DRAM (faster performance). We present our algorithm and discuss all possible corner cases, as well as empirically evaluate the overhead and discuss end-to-end performance expectations.

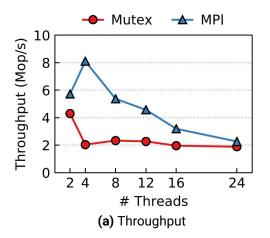

- · Chapter 5 presents RStore, a multicore key-value store with an index+log architecture [LSOL20]. RStore focus on use-cases requiring low tail-latency, such as web caching, real-time systems, and metadata management. We introduce the building blocks of RStore and how to integrate NVM in order to enable high performance and lower costs. We show results of isolated evaluations to back our design decisions, as well as an end-to-end evaluation and comparison with similar modern systems.

- · Chapter 6 concludes our work by summarizing the key findings of each chapter and providing directions for future work.

The author of this thesis is responsible for the conception, implementation, evaluation, analysis, and the interpretation of the results for each of the contributions presented. The author is also the main author of the works upon which this dissertation is based on. Nevertheless, the author is thankful to all co-authors that contributed substantially to these works. Many of the ideas proposed had constant feedback and input through discussions with Wolfgang Lehner, Ivan Schreter, and Ismail Oukid. Xiangpeng Hao and Tianzheng Wang contributed with the full implementation of BzTree and with partial implementation of the framework used for the persistent trees evaluation discussed in Section 2.3. Thomas Willhalm contributed with suggestions and analysis of the results collected through hardware counters. Caetano Sauer contributed with clarifications about transactional recovery in the context of the buffer pool with optimistic consistency model in Chapter 4. Thomas Bach contributed with discussions about the probability of data loss due to checksum collisions, on that same chapter. The RStore system in Chapter 5 was built by the author on top of the Reflex project at SAP, idealized and implemented by Ivan Schreter. Reflex provides the following building blocks: message-passing communication, cooperative multitasking, memory management, and networking. The author contribution lies on the design, implementation, and evaluation of NVM in that system.

# BACKGROUND

In this chapter, we cover the background on NVM required for the understanding of the following chapters. We also survey related work that has explored opportunities to leverage NVM in the context of database systems and storage management. Finally, we conclude with an empirical analysis of persistent data structures in order to better exemplify the challenges of NVM and solutions proposed, as well as to set realistic expectations of the performance of NVM.

# 2.1 NON-VOLATILE MEMORY

Non-volatile memory (NVM)<sup>1</sup> is a novel class of technologies that has been regarded as the next evolution step for persistent storage. The technologies in this class exhibit characteristics of both storage and main memory. More precisely, they provide persistency and high density while also being byte-addressable and offering a latency much closer to that of modern DRAM (albeit often higher). While these characteristics are common to most types of NVM technologies, they might vary slightly between them.

### 2.1.1 Types of NVM

There are two main groups of NVM technologies. The first group refers to technologies based on flash memory, commonly known as *NVDIMMs*. These devices are motivated by the observation that the recent improvements in throughput and capacity of modern NAND-flash SSDs have shifted the bottleneck from the storage device itself to the PCIe bus. Therefore, to avoid the high latency (tens of µs) and limited bandwidth (tens of GBps) of PCIe, these devices are interfaced via the same memory bus used for DRAM modules. The *Storage Networking Industry Association* (SNIA) currently standardize two types of NVDIMM. The *NVDIMM-F* type defines a flash-only DIMM, similar to regular PCIe SSDs, but connected to the memory bus. The access latency of devices of this type is lower

<sup>&</sup>lt;sup>1</sup>Also referred to as non-volatile RAM (NVRAM), storage class memory (SCM), or persistent memory (PM).

than that of PCIe NAND-flash SSDs, but still much higher that that of DRAM. They also present capacity and cost similar to those of modern SSDs. The main disadvantage is that NVDIMM-F devices are block-addressable rather than byte-addressable, which is one of the main advantages of other NVM devices. The second type is NVDIMM-N, which combines both DRAM and flash storage in a single module. Only the DRAM can be accessed during normal operation. With the aid of an on-chip battery or capacitor, the DRAM content is written to flash during a power failure, and restored during restart. NVDIMM-N devices have the advantage of achieving a performance similar to that of DRAM and of being byte-addressable, but have small capacities (in the tens of GB range) and high costs. Examples of these devices are the ones commercialized by Viking Technology [Tec18] and Micron [Mic18]. In general, NVDIMMs today are considered niche accelerators when compared to PCIe NAND-flash SSDs.

The second group of NVM includes devices based on materials other than NAND-flash, with the most prominent being phase-change memory (PCM) [LZY+10, PSU+70], spintorque transfer magnetic RAM (STT-MRAM) [DWS $^+$ 08, HYY $^+$ 05, H $^+$ 08], and resistive RAM (ReRAM) [GKC+11, SSSW08, Chu11]. PCM has its roots in research conducted in the 1960s [Ovs68] and is based on the property of certain materials, such as germanium, antimony and tellurium, to persist a phase change when the right current is applied to them. In industry, PCM has been researched by IBM, HGST, Micron, and Intel. STT-MRAM makes use of the spin property of electrons, as opposed to conventional semiconductor electronics that make use of the charge property. It relies on the magnetic retention property of certain materials to store information. Reads rely on sensing the resistant difference between two states of this material, while writes are based on the spin-torque transfer effect to change the orientation of the magnetization. Companies like Samsung, Qualcomm, Crocus Technology, Everspin, and Intel have demonstrated works on STT-MRAM technologies. Finally, ReRAM relies on applying high enough voltage to materials that do not conduct electric current. This will force a phenomen called dielectric breakdown, which damages the material. In certain materials, this damage is reversible and the controlled defects caused can be used to represent bits in a binary system. HP Labs is the main company researching ReRAM. Table 2.1 compares the performance characteristics of single-level cell flash, DRAM, and the NVM technologies discussed<sup>2</sup>.

Recent technological advancements lead by Intel and Micron resulted in the development of 3D XPoint<sup>3</sup> [Mic20]. 3D XPoint is based on PCM [Cho17] and is currently considered the NVM technology with the most potential to succeed and to be widely adopted. Intel commercializes 3D XPoint under the market name of Optane. Two lines of Optane products exist. First, Optane is sold in PCIe SSD format, similar to the NAND-flash variant, but offer latencies an order of magnitude lower. Second, Optane DC Persistent Memory Modules (DCPMM) are dual in-line memory modules (DIMMs) like DRAM, and thus are connected directly to the memory bus. While Optane SSDs offer a much lower latency than NANDflash SSDs, they are still interfaced with PCIe and are block-addressable, while DCPMMs are byte-addressable. Furthermore, DCPMM is the NVM technology more accessible in the market and has received support both in Windows [Tob16] and Linux [Lin15] systems. For these reasons, in this work we focus on DCPMM and often use the more general term "NVM" to refer to it. Nevertheless, our findings are not specific to DCPMM and can be applied to other NVM technologies that exhibit access modes.

<sup>&</sup>lt;sup>2</sup>In the real world, certain reported numbers might vary due format-specific functionalities, such as wearleveling techniques employed in SSDs.

<sup>&</sup>lt;sup>3</sup>Pronounced "three dee cross point".

| Parameter        | SLC Flash     | DRAM        | PCM           | STT-MRAM          | ReRAM             |

|------------------|---------------|-------------|---------------|-------------------|-------------------|

| Read Latency     | 25 µs         | 50 ns       | 50 ns         | 10 ns             | 10 ns             |

| Write Latency    | 500 µs        | 50 ns       | 500 ns        | 50 ns             | 50 ns             |

| Byte-addressable | No            | Yes         | Yes           | Yes               | Yes               |

| Endurance        | $10^4 - 10^5$ | $> 10^{15}$ | $10^8 - 10^9$ | >10 <sup>15</sup> | >10 <sup>11</sup> |

| Density          | High          | Low         | Medium        | Low               | High              |

| Cost             | \$            | \$\$\$\$    | \$\$          | \$\$\$            | \$\$\$\$          |

**Table 2.1:** Comparison of flash, DRAM, and modern NVM technologies.

### 2.1.2 Access Modes

Enabling modern systems to access NVM requires changes at different levels. At the hardware level, Intel introduced support for DCPMM in the Cascade Lake processor family. The DCPMM can be exposed in two different modes. In the memory mode, DCPMM is treated as volatile memory. This mode has the benefit of significantly increasing the perceived amount of memory available, while being completely transparent to the operating system and applications. To amortize memory accesses due to the higher latency of DCPMM, the DRAM present in the system is used as a cache. Therefore, NVM is not treated as byte-addressable media as its contents must always be cached in DRAM instead of being directly accessed by the CPU. Furthermore, in memory mode, data on DCPMM becomes inaccessible after a restart, thus not leveraging the persistency of NVM.

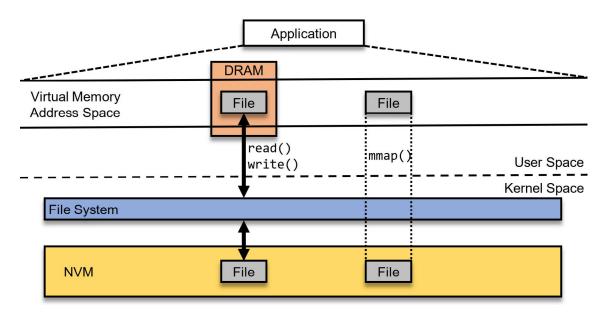

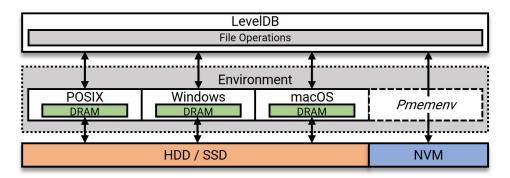

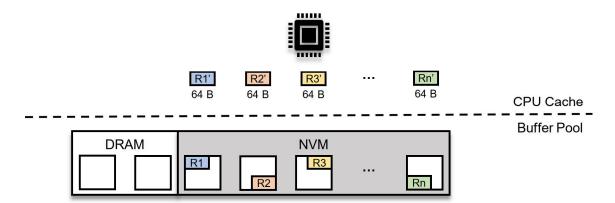

In the app direct mode, DCPMM is exposed as a device, similar to a HDD or SSD. It then can be formatted and mounted with a file system. At the software level, applications have two ways of interacting with this file system. First, as shown on the left-hand side of Figure 2.1, applications can manage files through the regular file system interfaces, such as read() and write(). In this case, DCPMM is treated as a very fast block device and has the advantage that no modifications to the software are required. Like other storage devices, operations to files on DCPMM are done at a page granularity (usually 4kB) and buffered in DRAM. The second way is shown on the right-hand side of Figure 2.1. If the file system is mounted with the special DAX flag, the application might map the file to its virtual memory address space with mmap(). The DAX flag indicates that the DCPMM is directly accessed and prevents intermediate buffering, such as the operating system page cache. As a consequence, load and store instructions done to the mapped address space are reflected directly to the DCPMM device. This has the advantages of avoiding expensive system calls, of reducing the transfer granularity from pages to cache lines (64B), and of requiring only a single copy of the data, since it is not buffered in DRAM. It is worth noting that, while both DRAM and NVM share the same virtual memory address space, the application can distinguish their respective memory regions, and therefore control where to place data. Finally, while accessing persistent media through load and store instructions introduce challenges that require the software to be properly adapted, we consider this to be the only way to fully leverage NVM and achieve optimal performance. Therefore, in this thesis we only assume the scenario in which DCPMM is configured in app direct mode and files are mapped to the virtual memory address space of applications.

Figure 2.1: NVM Access.

### 2.1.3 Byte-addressability and Persistency

As previously mentioned, when configuring the DCPMM in the app direct mode and managing it through a file system with the DAX flag enabled, applications are able to directly map files in NVM to the virtual memory address space and access them through load and store operations. The DAX flag guarantees that the operating system or file system will not employ any intermediate buffering, thus ensuring that operations are always persisted in NVM. While the DAX flag removes the volatility from the access chain at the software level, there is still volatility to be considered at the hardware level, as the path from CPU registers to NVM is long and mostly volatile.

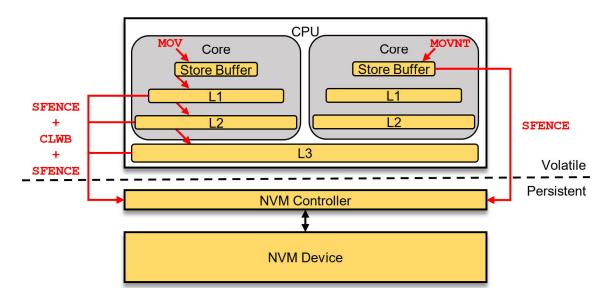

As shown in Figure 2.2, Intel CPUs employ store buffers and three levels of caches to hide the latency of memory accesses. Each physical core has its own L1 and L2 caches, while the L3 cache is shared between all the cores. Accessing NVM through load and store operations implies that data in NVM is transferred to the CPU caches, just like DRAM. This traffic happens in cache lines of 64 B. This leads to three problems. First, the CPU caches are volatile and therefore store operations are not quaranteed to be persistent after they were executed. Second, since most CPUs employ out-of-order execution, store operations might be reordered. Third, from the software point of view, cache lines are arbitrarily evicted and, therefore, persisted back to NVM. Traditionally the software has little control over the CPU caches, and, in such scenario, it is impossible to enforce store ordering and data durability, which are the main requirements to ensure consistency.

To aid software developers, Intel has introduced the hardware instructions CLFLUSHOPT and CLWB, which, when combined with SFENCE, can provide memory ordering and durability. While it is not possible to prevent a cache line from being evicted from the CPU cache, the CLFLUSHOPT and CLWB instructions eagerly force cache lines to be flushed and, therefore, persisted. While both instructions are used to flush cache lines, the only difference is that CLFLUSHOPT will also evict it from the CPU cache and CLWB will retain the cache line in the CPU cache. The SFENCE instruction is a memory barrier that serializes all pending

Figure 2.2: The volatility chain from the CPU to NVM.

stores, thus preventing undesired reordering. Therefore, as seen in the left-hand side of Figure 2.2, a typical pattern for persisting a store operation to NVM (represented by the MOV instruction) is to explicitly follow it by three instructions: SFENCE, CLFLUSHOPT or CLWB, and another SFENCE. The first SFENCE ensures that the stores completed, the CLFLUSHOPT or CLWB will trigger a cache line flush to persist the store, and the last SFENCE will ensure the previous CLFLUSHOPT or CLWB completed before resuming. In addition to these instructions, non-temporal stores (MOVNT) can also be used to bypass the cache by writing to a special buffer, which is evicted either when it is full, or when an SFENCE is issued. This is shown in the right-hand side of Figure 2.2. Non-temporal stores are useful when the CPU is simply writing to a new memory location without previously reading the data and loading its cache lines, such as when streaming data in a log-structured manner.

Finally, it is worth noting that, while cache line transfers between CPU caches and NVM happen in a granularity of 64 B and are atomic, current x86 CPUs only guarantee that 8 B stores are atomic, i.e., complete within a single CPU cycle<sup>4</sup>. While it is unlikely that a cache line will be evicted during a store operation larger than 8 B, algorithms and data structures should take that into consideration to avoid partial writes and guarantee correctness. This is usually achieved by atomically updating an 8 B variable to reflect larger stores, such as a pointer (in the case of shadowing) or the tail of a log. In the context of NVM, this 8 B unit is commonly referred to as *p-atomic*.

### 2.1.4 **Performance**

In order to give a good overview of the performance characteristics of DCPMM, we have measured its latency and bandwidth using Intel Memory Latency Checker (v3.9) [VKW+13]. The hardware used for the measurements is shown in Table 2.2. We first compare the latency of DCPMM to the latency of CPU caches and DRAM. The processor has 24 physical

<sup>&</sup>lt;sup>4</sup>Not to be confused with atomic visibility, which can be achieved at larger sizes by the cache-coherency protocol when using hardware instructions such as compare-and-swap(CMPXCHG16B).

| Processor        | Intel Xeon Platinum 8260L CPU @2.40 GHz                  |

|------------------|----------------------------------------------------------|

| Main Memory      | 96 GiB DDR4 @2666 MHz ( $6 \times 16$ GiB modules)       |

| NVM              | Intel Optane DCPMM 1.5 TiB ( $6 \times 256$ GiB modules) |

| Operating System | Linux 5.3.4-3                                            |

**Table 2.2:** Hardware used for measuring DCPMM performance characteristics.

| Level | Sequential Access | Random Access |  |  |

|-------|-------------------|---------------|--|--|

| L1    | 1ns               | 1ns           |  |  |

| L2    | 7 ns              | 7 ns          |  |  |

| L3    | 20 ns             | 20 ns         |  |  |

| DRAM  | 75 ns             | 85 ns         |  |  |

| DCPMM | 175 ns            | 300 ns        |  |  |

**Table 2.3:** Latency for accessing different levels of the memory hierarchy.

cores and 48 logical cores. The L1 caches are divided in instruction cache and data cache, each one having a capacity of 32 kB. Each L2 cache has a capacity of 1024 kB and the shared L3 cache has a capacity of 36 608 kB. The access latencies are shown in Table 2.3. The main observation is that DCPMM not only has higher latencies, but they differ significantly between sequential and random accesses. This is explained by buffering being employed internally in the DCPMM device, as reported by Intel [Int20d]. While traffic between CPU caches and DCPMM happens in a 64 B granularity, just like DRAM, internally the DCPMM employs buffering at a 256 B granularity. In other words, it is beneficial to collocate data on DCPMM in units of 256 B to explore spatial locality. It is also worth mentioning that the reported DCPMM latency refer to read operations. As previous studies have also noted [IYZ+19], precisely measuring the write latency of DCPMM is difficult. For supporting DCPMM, Intel CPUs rely on a feature called asynchronous DRAM refresh (ADR). The ADR triggers a hardware interrupt to the memory controller to flush write-protected data buffers in the case of a power failure. While stores that linger in the ADR domain are "safe", currently there is no way to detect when they physically reach the DCPMM itself.

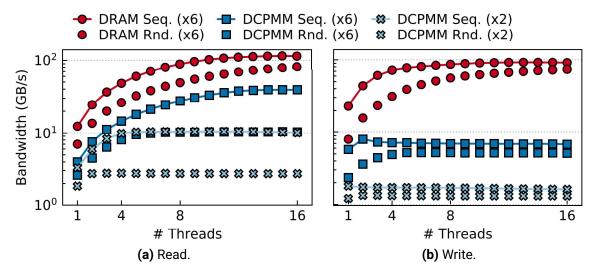

Figure 2.3 compares the bandwidth under two and six DCPMMs with a varying number of threads. The CPU supports six channels, each of which has two slots, one for DRAM and one for NVM. Therefore, the number of DCPMMs also indicates the number of memory channels. Similar to DRAM, adding more DCPMMs significantly increases the read bandwidth, while the impact for write bandwidth is relatively smaller. It is worth noting that in most cases using two threads is enough to saturate the DCPMM write bandwidth. Nevertheless, having as many DCPMMs as possible is not always better, as the optimal setup highly depends on the use-case. As an example, one might benefit from less DCP-MMs in favor of more DRAM modules, since the amount of available memory slots is limited per CPU. In such case, this would imply trading the lower costs and increase in bandwidth of DCPMM for a more expensive setup and larger DRAM capacity, benefiting from its lower latency access. DCPMM exhibits peak sequential read and write bandwidth of 40 GB/s and 10 GB/s, respectively. These are respectively  $\sim 3 \times$  and  $\sim 11 \times$  times lower than those of DRAM. This gap widens even more for random read and write bandwidth to respectively  $\sim 8 \times$  (7.4 or 7.4 GB/s) and  $\sim 14 \times$  (5.3 GB/s) lower bandwidth than DRAM. Given the performance gap between DRAM and DCPMM, it becomes more important to leverage more memory channels (i.e., equip more DCPMMs) to reach the peak bandwidth.

Figure 2.3: DRAM and Optane DCPMM bandwidth when a server is fully ( $\times$  6 modules) and partially ( $\times$  2 modules) populated.

### **RELATED WORK** 2.2

The advances in the recent years raised the interest in NVM technologies both in academia and industry. Many interesting works proposed data structures, algorithms, and architectures in different contexts. While most of the contributions and the concepts explored can be used as building blocks for more complex systems, in this section, we limit to review the related work of more complete storage management systems in the context of NVM.

### Storage Management in the NVRAM Era

Pelley et al. [PWGB13] explore the impact of NVM (referred to as NVRAM) in traditional database architecture. Rather than leveraging NVM in the context of the modern storage hierarchy comprised of DRAM, SSD, HDD, and even tape, the work assume that NVM will replace all existing persistent storage devices. Therefore, as a starting point, they use NVM as a drop-in replacement for disk and analyze how it impacts the database architecture. The first dimension considered refers to reading from NVM. Even if the performance of NVM is higher than that of other storage media, the authors assume that caching is still required due to its higher latency. Three alternatives are proposed: Software Buffer, Hardware Buffer, and DRAM Replication. The Software Buffer approach relies on caching hot pages in DRAM through a buffer manager, as in conventional databases. The **Hardware** Buffer alternative involves removing the buffer manager and rely solely on CPU caches to hide the higher latency of NVM. Finally, the **DRAM Replication** also relies on removing buffer management by having a complete replica of the database in DRAM to serve read requests. Like the authors, we consider that, while Hardware Buffer and DRAM Replication strategies can simplify the software stack my removing buffer management, they are impractical in most scenarios due to the limited capacity of CPU caches and to the large DRAM requirements, respectively. Therefore, having a portion of DRAM managed by a Software Buffer to cache hot pages is still the best strategy.

Since a Software Buffer in DRAM is used to read and modify pages, the second dimension considered by the authors refers to writing the pages back to NVM. The strategies considered are: Traditional WAL/ARIES, In-Place Updates, and NVRAM Group Commit. To enable Traditional WAL/ARIES, the authors introduce two operations, persist\_wal() and persistent\_page(), to enable atomic propagation of log records and pages to NVM, respectively. The authors note that, while it is a simple approach, the software overhead of logging and page flushing becomes the bottleneck if NVM is used as the main storage device. As an alternative, the In-Place Update strategy is proposed. It eliminates redo logging by employing a force strategy (i.e., flushing all updated pages at commit). Transactions employ private undo log records, which are persisted to NVM until the transaction commits, thus enabling the transaction to roll back after a failure. Finally, the authors also propose the NVRAM Group Commit strategy, which extends the In-Place Update by batching multiple transactions and applying their updates at once to a copy of the whole database. The authors consider NVRAM Group Commit to be the best strategy, as it amortizes the overhead associated with committing single transactions.

While we agree with the authors that Software Buffer is a good strategy, we make a few observations regarding writing to NVM. In the Traditional WAL/ARIES approach, the authors argue that logging and the asynchronous page flushing are the main source of overhead. We point out that, while the authors assume that shadow paging is used to atomically flush pages to NVM, this is not required, since the WAL suffices to guarantee the consistency of the database and recover pages in case of partial writes. The overhead of WAL can also be significantly reduced with better logging protocols, as discussed later in this section. Furthermore, the In-Place Update and NVRAM Group Commit are proposed to eliminate redo logging. However, both strategies employ shadow paging during commit time, which was previously pointed out as a main overhead in the context of asynchronous page flushing. Removing the redo log also implies lack of support for media recovery. Therefore, we consider that a well-implemented Traditional WAL/ARIES approach can reduce the mentioned overheads and perform better than the proposed alternatives.

## Managing Non-Volatile Memory in Database Systems

Similar to the *Software Buffer* strategy discussed previously, van Renen et al. [vRLK<sup>+</sup>18] propose a buffer manager to leverage the benefits of NVM. The authors point that DRAM is still required to hide the higher latencies of NVM but that page-based DRAM caching leads to unnecessary memory traffic. Therefore, unlike Pelley et al. [PWGB13], they propose to leverage NVM in the context of a more complete storage hierarchy comprised of DRAM and SSD, and to reduce the traffic between DRAM and NVM from pages to smaller granularities, such as cache lines or "mini pages". The authors also employ many state-of-the-art techniques, such as pointer-swizziling [GVK+14], and further discuss replacement strategies. The main advantages of the proposed buffer manager are its simplicity, which makes it easy to be integrated into existing systems, and its capacity to leverage other storage devices. Nevertheless, while the unnecessary traffic between DRAM and NVM is reduced, it is not completely eliminated, as NVM is never directly accessed by the CPU.

### **FOEDUS**

The FOEDUS is a transactional system [Kim15] designed to leverage many-core servers and NVM. Like Pelley et al. [PWGB13], the author assumes a scenario in which NVM completely replaces other storage devices and coexists solely with DRAM. It proposes a B+Tree variation called Master Tree and relies on the concept of dual pages. Each page has two copies: a read-only state in NVM and a volatile state in DRAM. This technique resembles shadow paging, but it stores the address of both versions of a page in the incoming page pointers, rather than in a separate mapping data structure. FOEDUS employs a redo-only distributed logging scheme [TZK+13, ZTKL14]. A "log gleaner" process propagates the updates to the NVM pages by asynchronously replaying the log records. While FOEDUS employs many state-of-the-art techniques, the author assumes that NVM is accessed through the regular file system interface, thus not leveraging its byte-addressability and being the main drawback of the proposed architecture.

### Write-Behind Logging

Motivated by the observation that write-ahead logging becomes the main bottleneck in many scenarios, Arulraj et al. propose an NVM-aware commit protocol called write-behind logging (WBL) [APP16]. They assume a database system consisting of only DRAM and NVM and multi-version concurrency control (MVCC) [LBD+11, KR79]. During transaction execution, changes are written to a DRAM copy of the database. At commit, dirty records are flushed individually to NVM, following a force strategy. Since MVCC is used, records are always written to a new location in NVM. Nevertheless, uncommitted updates might be propagated to NVM if a failure occurs during commit. To determine loser transactions, a group-commit interval is defined by two timestamps  $(c_p, c_d)$ , such that all transactions with timestamp lower than  $\emph{c}_\emph{p}$  have successfully committed, and no transactions with timestamp higher than  $c_d$  have executed yet. These timestamps are written to a log after all the changes older than  $c_p$  have been propagated to NVM, hence "write-behind". The recovery consists of reading the log to determine the  $(c_p,c_d)$  intervals that define the loser transactions. Following MVCC, records modified by loser transactions are then ignored by new transactions, later being removed by a garbage collection process.

The authors show benefits over write-ahead logging (WAL) in terms of memory consumption and reduced traffic to NVM. However, we note that WAL is a protocol for update-in-place strategies, which is not the case of MVCC. In other words, the multiple copies of a record stored in a MVCC system already resemble the before- and after-images stored in log records in WAL. Furthermore, while WAL can be eliminated in MVCC systems by using WBL, we point that WAL is often leveraged to enable other functionalities, such as remote replication, database auditing, and partial transaction rollback. Therefore, in addition to being limited to MVCC, WBL makes the support of these functionalities more cumbersome.

### **SAP HANA**

SAP HANA [FML+12] is a modern database system that targets hybrid enterprise applications consisting of both transactional and analytical workloads. It follows an in-memory column-store architecture and exploits modern hardware, such as multiple cores, SIMD instructions, and large main memory and CPU caches. In order to store all database contents in memory, SAP HANA relies heavily on data compression. To enable a high compression rate, data has to be often coalesced and organized in efficient formats. Therefore, SAP HANA employs a delta-main approach: a small delta component ingests new records and updates and is periodically merged to a larger and read-only main component, which stores data in a compressed format. Durability is guaranteed through command logging [MWMS14] and transaction-oriented checkpoints [HR83]. SAP HANA can also leverage NVM to extend the capacity of the main component [ALR+17]. This is a natural fit, as the main component is read-only and, therefore, NVM can be accessed directly by the CPU just like DRAM. Not only DCPMMs are larger than DRAM modules, but they are also cheaper, leading to lower costs. While runtime performance is impacted by the higher NVM latency, the startup is significantly faster, as the main component of NVM is persisted across restarts, thus avoiding large load times from the storage device to memory.

### Hyrise-NV

Hyrise-NV [SKD+16] is an NVM-aware version of the Hyrise in-memory database system [GKP+10]. Similar to SAP HANA, Hyrise is tailored to hybrid transaction and analytical workloads and employs the delta-main architecture. In addition to the main component, Hyrise-NV also persists other data structures, such as the proposed nvBTree, used as secondary indexes. Hyrise-NV relies on append-only strategies and multi-version storage to update data transactionally and guarantee consistency. Furthermore, since write-ahead logging is not employed, metadata of currently running transactions is persisted to enable undo in case of failure.

## SOFORT

SOFORT [OBL+14, Ouk18] is a database system developed from scratch to leverage a hybrid DRAM-NVM environment. Similar to SAP HANA and Hyrise-NV, SOFORT is an in-memory column-store targeting both transactional and analytical workloads, also following the delta-main architecture. Differently than other systems that leverage traditional storage devices, SOFORT relies purely on DRAM and NVM and, therefore, is able to employ a single-level architecture. In other words, SOFORT only manages persistent objects in the virtual memory address space, rather than files in a file system. Primary data is stored in NVM and written/read directly by the CPU. Auxiliary data, such as secondary indexes, can be placed either in DRAM or in NVM, thus allowing the system to be configured either for high performance or for lower costs and faster restart.

SOFORT also supports ACID transactions through multi-version concurrency control (MVCC) [LBD+11, KR79]. Unlike other approaches that propose to eliminate logging but

still employ it in a smaller granularity, SOFORT is able to achieve that goal by employing a force strategy and storing the transaction table in a persistent data structure. Therefore, "transaction objects" are persisted and are used to discard operations tagged with the MVCC timestamps of transactions that were in-flight when the failure occurred.

The main limitation of SOFORT is the lack of support for other storage devices (HDD and SSD) in a more complete storage hierarchy. While the proposed architecture may have benefits in a future where NVM will replace other storage technologies, for the time being, modern storage technologies, such as SSDs, still have to be considered for most use-cases. Finally, as also noted by the authors, it is unpractical to adapt existing systems to follow the same architecture, at it would require heavy software rewrite and architectural changes

### Logging

Many of the works discussed so far make the observation that, when leveraging NVM as the main storage device in a database, logging (typically WAL) becomes the main bottleneck. Therefore, these works employ different flavors of force strategies with the goal to completely eliminate logging from the critical path of transactions [PWGB13, APP16, SKD<sup>+</sup>16, OBL<sup>+</sup>14, Ouk18]. Other works go in the different direction of leveraging NVM to reduce the overhead of logging, rather than eliminating it [CKKS89, AJ89, FHH+11, GXH+11, HSQ14, WJ14]. We focus on two of these works.

Huang et al. [HSQ14] make the observation that NVM is more expensive than other storage devices (HDD and SSD) and, therefore, restricting the use of NVM to improve logging performance yields a higher ratio of transactions per dollar than simply replacing all storage with NVM. The authors propose NV-Logging to improve the traditional ARIES logging protocol [MHL+92]. The main idea is to reduce the software overhead associated with centralized log buffers by introducing decentralized transaction-private log buffers. During transaction processing, log records are created in private DRAM buffers. Upon commit, the transaction flushes the log records to arbitrary locations in NVM in the form of "log objects". To enforce the global LSN order, pointers to these "log objects" are then appended to a "log entry index" implemented as a circular buffer. While the "log entry index" still acts as a contention point, its critical-section is much shorter, since only fixed-length pointers have to be appended, rather than arbitrarily large log records.

Unlike NV-Logging, Wang et al. [WJ14] propose fully-distributed logging for multi-core multisocket environments. They note that, while distributed logging reduces the overhead of logging by spreading log records across multiple physical logs, they are prohibitive due to the overhead introduced by dependency tracking and additional I/O required to guarantee global order of log records. Fortunately, NVM can be leveraged to significantly reduce these I/O costs and enable distributed logging. The authors investigate both page-level and transaction-level log space partitioning and employ a global sequence number based on a logical clock [Lam78] to uniquely identify log records. The empirical evaluation shows that transaction-level partitioning is more favorable, as it avoids cross-socket communications.

We agree that leveraging NVM to improve the logging infrastructure will be mandatory for database systems, and that completely replacing all storage by NVM is currently unfeasible

in most scenarios due to its higher cost when compared to SSD and HDD. We also note that, this approach not only is more cost effective, but it also limits the changes in the code base to the log manager, thus not requiring drastic changes in the whole database architecture. Nevertheless, we consider that there are other opportunities to leverage NVM in database systems, such as NVM-aware buffer management policies.

### **NOVA**

While the works previously discussed were mostly in the context of database systems, NOVA [XS16] explores NVM in the context of file systems. The goal of NOVA is to enable efficient access to NVM through the abstraction of regular file system interfaces. The main motivation is to enable applications to leverage NVM without any changes, rather than specifically tailoring them to manage NVM through the virtual memory space. NOVA is a file system in the user-space that follows a hybrid DRAM-NVM architecture and relies on log-structured writes to provide strong consistency guarantees. The authors claim that it is able to achieve 22% to 216× throughput improvement compared to state-of-the-art file systems, and  $3.1\times$  to  $13.5\times$  improvement compared to file systems that provide equally strong data consistency guarantees. We consider that, while specialized applications such as database systems can benefit more from directly managing NVM, other applications that do not require high performance can easily leverage some of the performance benefits of NVM through file systems like NOVA.

### 2.3 CASE STUDY: PERSISTENT TREE STRUCTURES

Perhaps one of the most prolific categories of works in the context of NVM is comprised of persistent data structures, such as persistent hash tables [LHWL20, DHK+15, NCC+19, NIK+17, SDUP15, ZH18, ZHW18] and persistent trees [ALML18, CGN11, CJ15, HKWN18, LLS+17, OLN+16, VTRC11, YWC+15, LXCW19]. Works in this category take as a starting point volatile memory data structures common in existing programming languages (such as std::map in C++). NVM is leveraged to make these data structures persistent, but still maintaining a similar behavior to their volatile counterparts. Therefore, persistent data structures are simpler when compared to the architecture of storage management system that employs concepts such as buffer management, ACID transactions, and garbage collection. While they may be inappropriate as a standalone storage manager, they are still relevant as building blocks for more complex systems. As an example, one could use a persistent hash table to implement a persistent version of a lock manager in a relational database system. The techniques employed by these persistent data structures can be generalized and applied in other scenarios. Therefore, we consider that looking at their design decisions can aid the reader in better understanding the challenges of NVM.

|                 | Architecture                             | Node structure                                | Concurrency                   |  |  |

|-----------------|------------------------------------------|-----------------------------------------------|-------------------------------|--|--|

| wBTree NVM-only |                                          | Unsorted                                      | Single-threaded               |  |  |

| NV-Tree         | NVM-only<br>(optionally hybrid)          | Unsorted leaf nodes; inconsistent inner nodes | Locking                       |  |  |

| BzTree          | NVM-only                                 | Partially unsorted leaf; sorted inner nodes   | Lock-free<br>(PMwCAS [WLL18]) |  |  |

| FPTree          | DRAM (inner nodes)<br>+ NVM (leaf nodes) | Unsorted leaf nodes                           | Selective<br>(HTM + locking)  |  |  |

**Table 2.4:** Comparison of key design decisions of the persistent tree structures analyzed.

### 2.3.1 **Persistent Trees**

We limit the scope of persistent data structures to persistent tree variants, since these are the most commonly used ones in database systems. We pick four candidates considered to cover a good portion of the design space: wBTree [CJ15], NV-Tree [YWC+15], **BzTree** [ALML18], and **FPTree** [OLN<sup>+</sup>16]. In the following, we give an overview of each one of these persistent tree data structures. Table 2.4 summarizes their key design decisions.

### Write-Atomic B+Tree (wBTree)

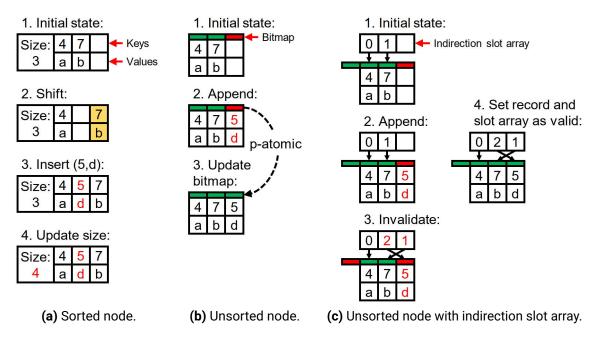

wBTree [CJ15] is a persistent, single-threaded B+Tree that achieves high performance by reducing cache line flushes and writes to NVM. Traditional B+Tree nodes are sorted for faster binary search. However, as Figure 2.4a shows, keeping a node sorted requires a shift of data to make place for the new key, which might leave the node in an inconsistent state upon crashes, and incurs more (expensive) NVM writes. wBTree solves this problem with unsorted nodes proposed in prior work [CGN11]. Figure 2.4b illustrates the idea. A bitmap is used to indicate if each slot contains a valid (green box in the figure) record or not (red box). The new record is inserted into a free slot (out-of-place), and the bitmap is atomically modified using 8 B writes to set the validity of the inserted record. Using unsorted nodes reduces the number of NVM writes and eases implementation, but requires linear search for lookups, which might be more expensive than a binary search. Nevertheless, as we will see later, the use of unsorted nodes is a common and effective design in NVM trees.

To enable binary search (thus reducing NVM accesses), wBTree uses an indirection slot array in each node, as shown in Figure 2.4c. Each entry of the array records the index position of the corresponding key in sorted order, i.e., the n-th array element will "point" to the n-th smallest key by recording the key's index into the key-value slots. In the example, after inserting key 5, in step 3 the bitmap needs to be modified so that the third element records the position of key 7, which is stored as the second element (index 1) in the key-value storage area. One bit (left-most box in the figure) in the bitmap is reserved to indicate the validity of the array. wBTree relies on the atomic update of the bitmap to achieve consistency, and on logging for more complex operations such as node splits. After inserting the record out-of-place in a free slot, the indirection slot array is flagged as invalid and updated, as shown in step 3 of Figure 2.4c. In case of a failure, the indirection

Figure 2.4: Comparison of inserting key 5 with value d. Unsorted node reduces writes but requires linear search for lookup, which can be avoided by using an indirection slot array.

slot array will be detected as invalid and reconstructed upon recovery. Finally, the bitmap is atomically updated to set both the indirection slot array and the new record as valid. This last step imposes that the bitmap is not larger than 8 B, the p-atomic unit. When the indirection slot array is smaller than 8 B, the bitmap could be removed as the indirection slot array can be atomically updated and serve as the validity flag.

## **NV-Tree**

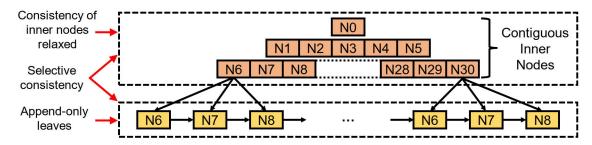

NV-Tree [YWC+15] proposes the concept of selective consistency, which, as shown in Figure 2.5, enforces the consistency of leaf nodes and relaxes that of inner nodes. This design simplifies implementation and reduces consistency costs by avoiding cache line flushes. Inner nodes, however, have to be rebuilt upon restart, since the copy in NVM might be inconsistent and unable to guide lookups correctly. We note that inner nodes could also be placed in DRAM since their consistency is not enforced. Similar to the wBTree, NV-Tree also uses unsorted leaf nodes with an append-only strategy to achieve fail-atomicity. Figure 2.6 shows an example of an insertion in an NV-Tree leaf node. The record is directly appended with a positive flag (or a negative flag in case of a deletion) regardless of whether the key exists or not. Then, the leaf counter is atomically incremented to reflect the insertion. To lookup a key, the leaf node is scanned backwards to find the latest version of the key: if its flag is positive, then the key exists and is visible; otherwise, the key has been deleted. The inner nodes are stored contiguously to abstract away pointers and improve cache efficiency. However, this implies the need for costly rebuilds when a parent-to-leaf node needs to be split. To avoid frequent rebuilds, inner nodes are rebuilt in a sparse way, which may lead to high memory footprint. As inner nodes are immutable (except parent-to-leaf nodes) once they are built, threads can access them without locking and only need to take locks at the leaf and their parents level when traversing the tree.

Figure 2.5: NV-Tree overview.

Figure 2.6: Insertion of a record in an NV-Tree node.

### **BzTree**

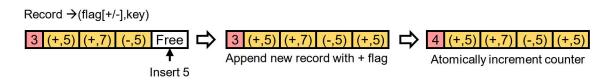

BzTree [ALML18] is a lock-free B+Tree for NVM that uses persistent multi-word compareand-swap (PMwCAS) [WLL18] to handle concurrency and ease implementation. PMwCAS is a general-purpose primitive that allows atomically changing multiple arbitrary 8 B NVM words in a lock-free manner with crash consistency. To achieve this, PMwCAS uses a two-phase approach. In Phase 1, it uses a descriptor d to collect the "expected" and "new" values for each target word, persist the descriptor, and atomically installs (using singleword CAS) a pointer to the descriptor on each word. If Phase 1 succeeded, Phase 2 will install the new values; otherwise the operation is aborted with all changes rolled back.

BzTree uses PMwCAS for insert, delete, search, scan, and structural modification operations which may need to change multiple NVM words. Because of the use of PMwCAS, while being lock-free, BzTree implementation is easier to understand than typical lock-free code. PMwCAS ensures that any multi-word changes are done atomically and recovery is transparent to BzTree, removing the need for customized logic for logging and recovery.

As Figure 2.7a shows, BzTree stores both inner and leaf nodes in NVM. Inner nodes are immutable (copy-on-write) except for updates to existing child pointers; leaf nodes can accommodate inserts and updates. Figure 2.7b shows the situation in which a node L splits and a new pointer must be inserted in the parent node P. Inserting to a parent node causes it to be replaced with a new one that contains the new key (P'). Then, an update in the grandparent node G is conducted to point to the new parent node P'. Splits can propagate up to the root and grow the tree. Records in inner nodes are always sorted, while records in leaf nodes are not. Initially, records are inserted to the free space serially. Periodically leaf nodes get consolidated (sorted) and subsequent inserts may continue to insert into the free space serially. After searching the sorted area (using binary search), the tree must linearly search the unsorted area to get a correct result. The design rationale is that inner nodes are not updated as often as leaf nodes and should be search-optimized; leaf nodes, however, need to be write-optimized.

Figure 2.7: BzTree overview.

Figure 2.8: FPTree overview.

### Fingerprinting Persistent Tree (FPTree)

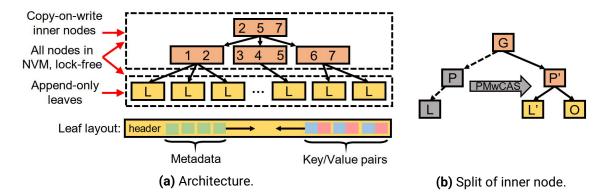

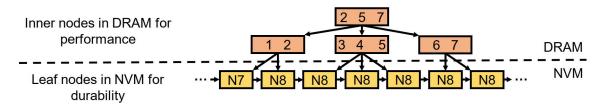

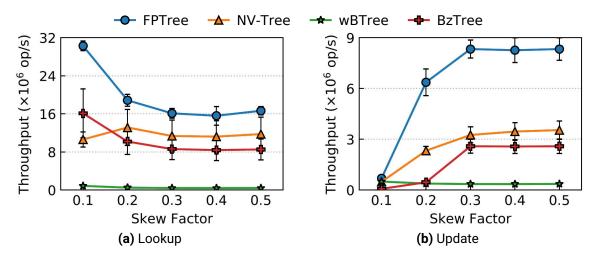

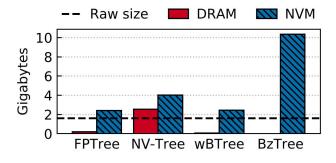

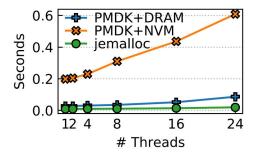

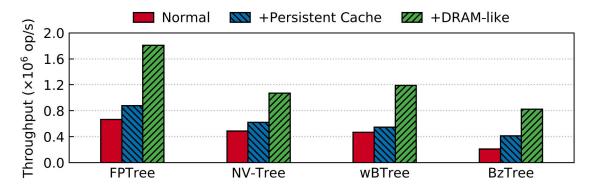

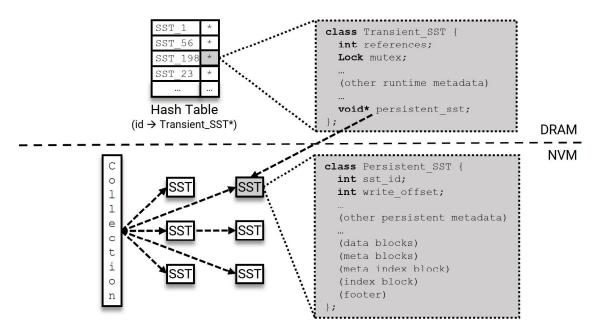

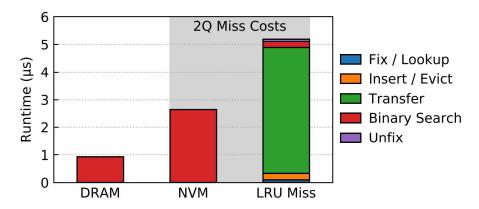

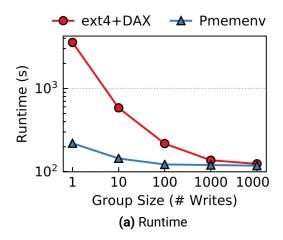

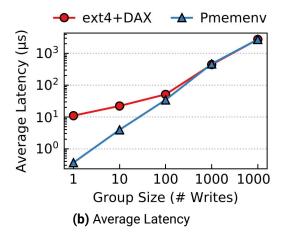

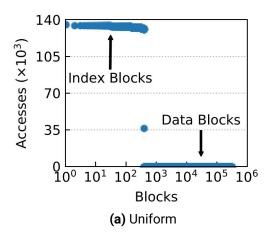

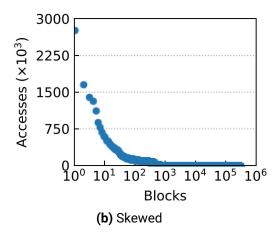

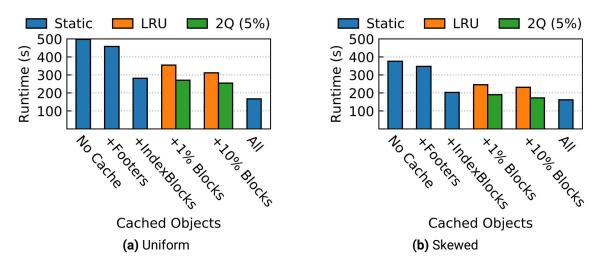

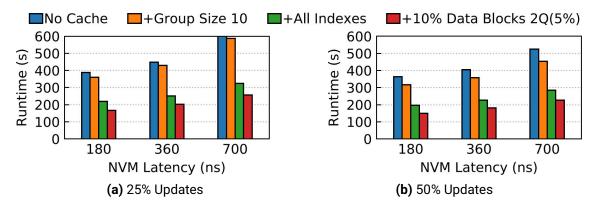

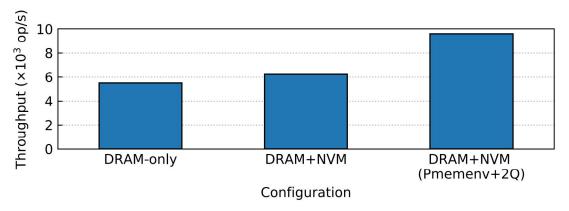

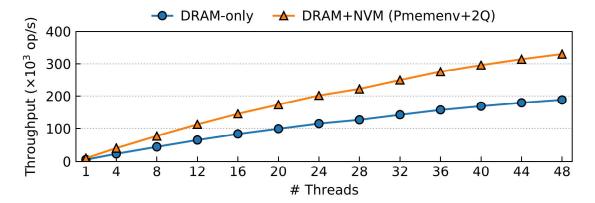

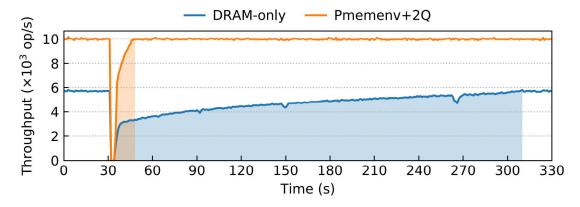

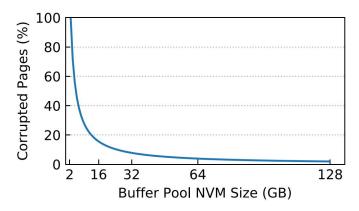

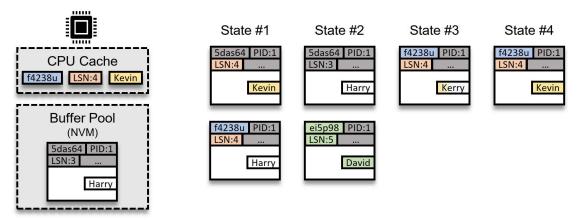

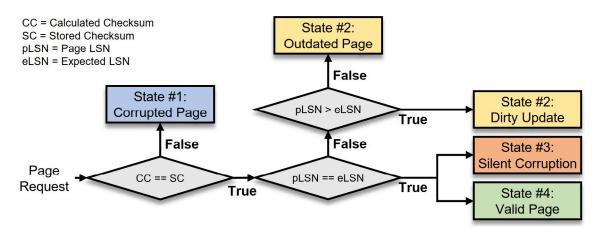

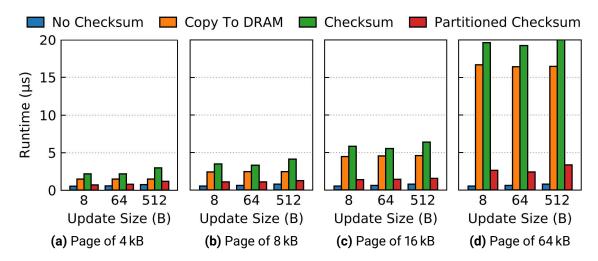

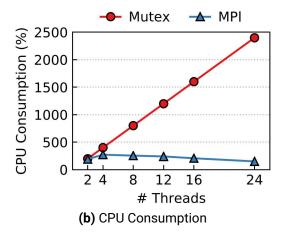

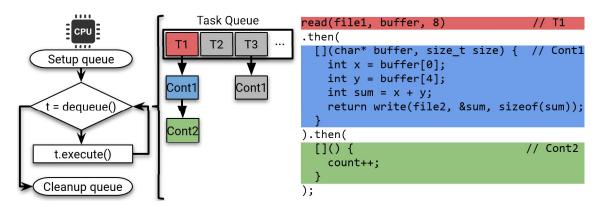

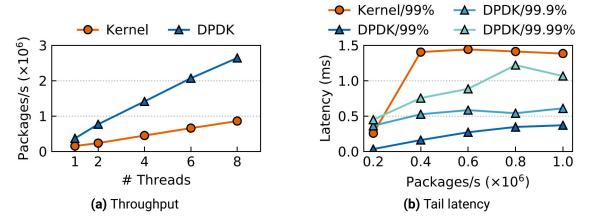

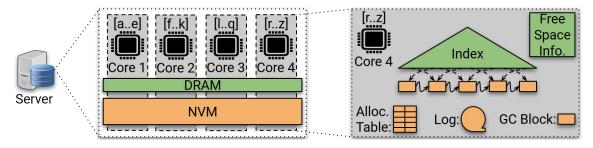

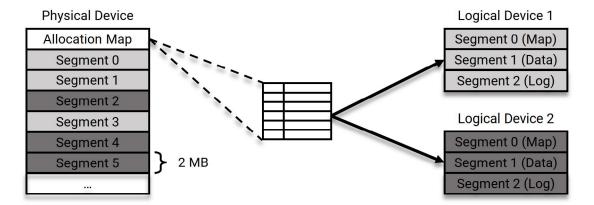

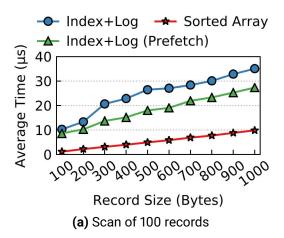

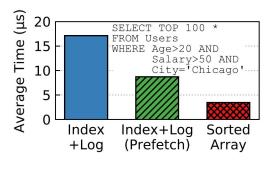

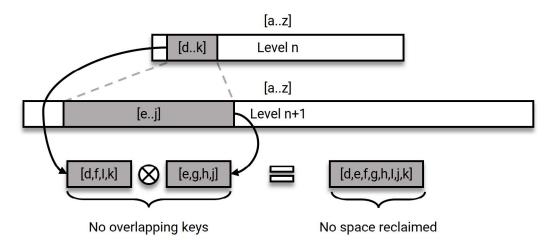

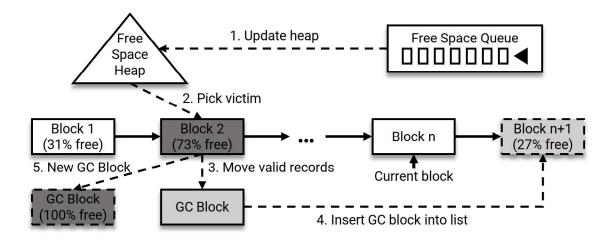

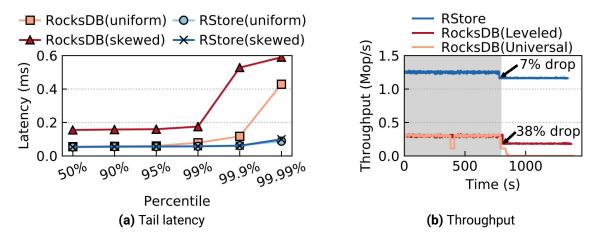

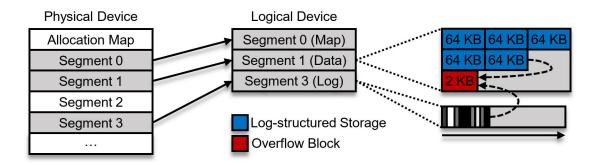

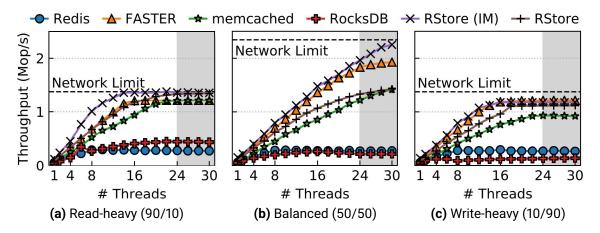

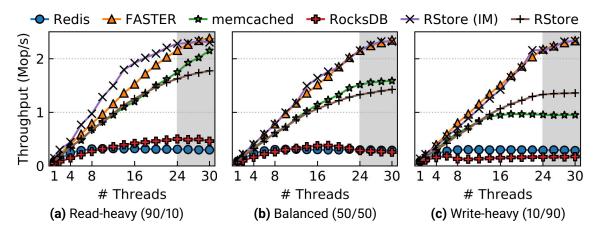

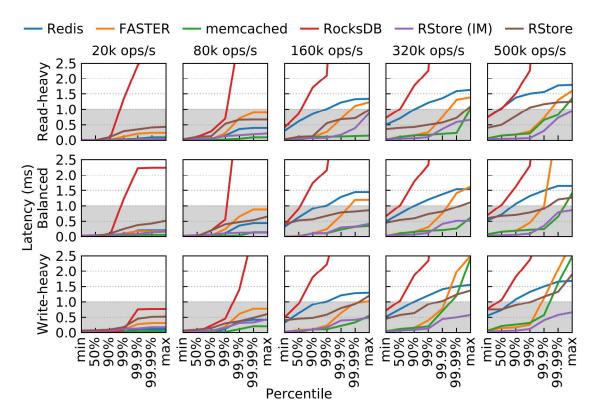

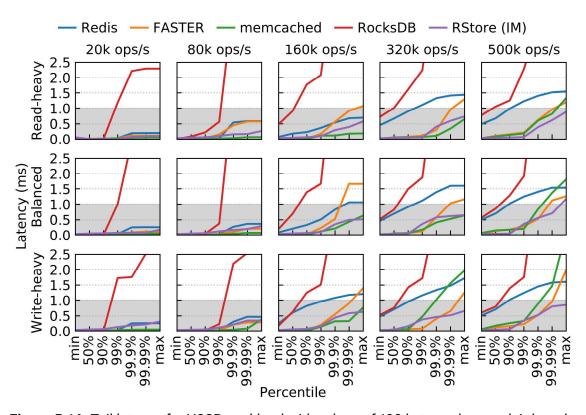

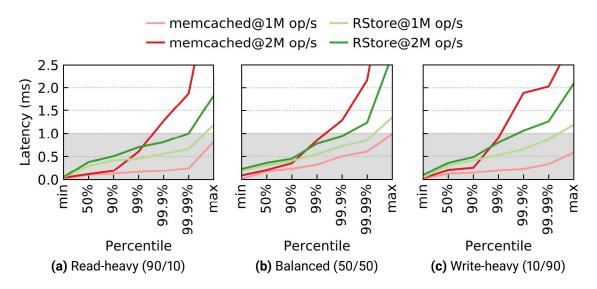

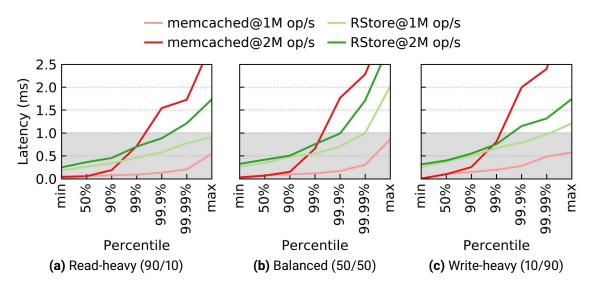

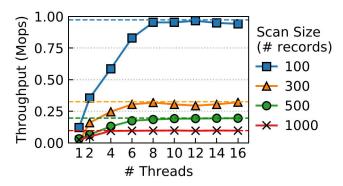

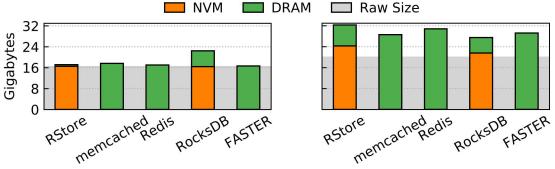

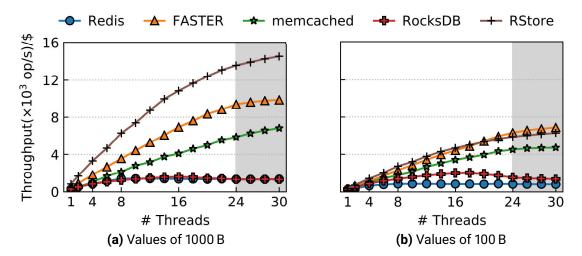

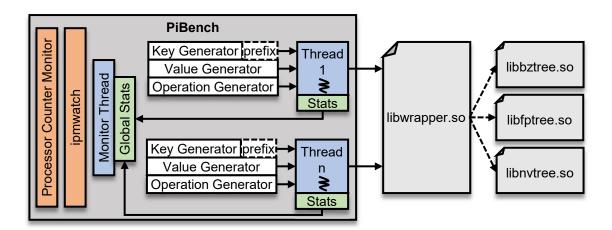

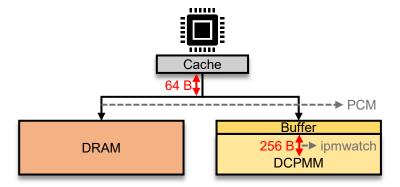

Unlike the other trees being evaluated, FPTree [OLN+16] uses both DRAM and NVM to achieve near-DRAM performance. As Figure 2.8 shows, it stores inner nodes in DRAM, and leaf nodes in NVM. This way, FPTree accelerates lookup performance while maintaining persistence of primary data (leaf nodes), as only leaf accesses are more expensive during a tree traversal compared to a fully transient counterpart. The rationale behind is that while losing leaf nodes leads to an irreversible loss of data, inner nodes can always be rebuilt from leaf nodes. Since the inner nodes must be rebuilt upon recovery, FPTree trades recovery time for higher runtime performance.