# CNTFET-BASED TERNARY LOGIC DESIGN AND ARITHMETIC CIRCUIT SIMULATION USING HSPICE

EE POEY GUAN

UNIVERSITI TEKNOLOGI MALAYSIA

# CNTFET-BASED DESIGN TERNARY LOGIC DESIGN AND ARITHMETIC CIRCUIT SIMULATION USING HSPICE

### EE POEY GUAN

A project report submitted in partial fulfilment of the requirements for the award of the degree of

Master of Engineering (Electrical - Computer and Microelectronic System)

Faculty of Electrical Engineering

Universiti Teknologi Malaysia

JANUARY 2015

Specially dedicated to my beloved family, lecturers and friends

For the guidance, encouragement and inspiration

Throughout my journey of education

### **ACKNOWLEDGEMENT**

First, I would like to take this opportunity to express my deepest gratitude to my project supervisor Ir. Dr. Michael Tan Loong Peng, for his supports and supervision. He has been very helpful with the installation of circuit simulator, and has been guiding me to the right path ever since. I sincerely thank him for his supports.

In addition, I wish to thank my postgraduate course-mates for their cooperation and information sharing in completing this project. Yet, not to forget my fellow friends for their care and moral support when it was most required.

Furthermore, I would like to thank my friends for their encouragement and supports. They had gave me useful opinion and assistance. Last but not the least, I am very thankful for my family members for their spiritual and financial supports.

### **ABSTRACT**

This project report focuses on the multiple-value logic (MVL) or commonly known as ternary logic gates by using carbon nanotube (CNT) FETs devices (CNTFETs). It is shown ternary logic has promising future in CNTFETs when compare to conventional binary logic design, due to its simplicity and energy efficiency in digital design reduced circuit overhead such as chip area and interconnection. In this research, existing CNTFET-based binary inverter and standard ternary inverter with resistive-load (STI-R) for comparison with the other three types of inverter are proposed - Complementary Standard Ternary Inverter (CSTI); Standard Ternary Inverter with 1 resistor and 3 NCNTFET (NSTI-R); Standard Ternary Inverter with 1 resistor and 3 PCNTFET (PSTI-R) to analysis the performance, structure design and application. In addition, the research covers all the basic logic Ternary NAND gate and Ternary NOR gate for further benchmarking. All simulation results using SPICE are obtained and analyzed in the Direct Current (DC) setting and verifed using half adder. Further study behavior of ternary logic includes the implementation of partial binary design into the ternary design and performance benchmarking. The result shows the CSTI have advantage on low power design with low leakage while NSTI-R has advantage on high-speed design inverter. In addition, partial binary design in the arithmetic circuit ternary design with CSTI shows added advantage in a low power design.

#### **ABSTRAK**

Projek ini berfokus multi nilai logik atau dikenal pasti sebagai gate logik pertigaan dengan menggunakan "tiub nano karbon peranti kesan sirip transistor (CNTFETs)" logik pertigaan telah menunjukkan masa depan yang cerah dan menyakinkan dari segi permudahan and penjimatan tenaga dari kajian apabila dibandingkan dengan logik binari dari segi penggunaan jumlah kawasan chip dan hubungan antara transistor. Pada kajian ini, CNTFET-based binari penyongsang dan ternari penyongsang jenis beban resistor akan dibanding dengan tiga jenis invertor yang dicadangkan - Pelengkap Standard pertigaan Penyongsang (CSTI); Standard pertigaan penyongsang dengan 1 perintang dan tiga NCNTFET (NSTI-R); Standard pertigaan penyongsang dengan 1 perintang dan tiga PCNTFET (PSTI-R) untuk mengkaji prestasi, stuktur bina dan penggunaan. Semua keputusan simulasi dikaji dengan menggunakan SPICE untuk menentu prestasi arus terus dengan pengesahan penggunaan litar aritmatik panambah separuh untuk mengenalpasti prestasi logik pertigaan. Kajian mengenalkan sebahagian reka binari digunakan ke atas rekaan logik pertigaan dengan memerhatikan prestasiny. Keseluruhanya, CSTI menunjukkan kelebihan dalam litar kuasa rendah dengan kebocoran tenaga rendah dan NSTI-R menunjukan pantasannya pada litar laju. Manakala, pengenalan reka binary ke dalam litar aritmetik ternari dengan menggunakan CSTI lagi menunjukkan kelebiahan pada litar kuasa rendah.

## TABLE OF CONTENTS

| CHAPTER | TITLE                                    | PAGE |

|---------|------------------------------------------|------|

|         | DECLARATION                              | ii   |

|         | DEDICATION                               | iii  |

|         | ACKNOWLEDGEMENT                          | iiv  |

|         | ABSTRACT                                 | v    |

|         | ABSTRAK                                  | vi   |

|         | TABLE OF CONTENTS                        | vii  |

|         | LIST OF TABLES                           | ix   |

|         | LIST OF FIGURES                          | X    |

|         | LIST OF ABBREVIATIONS                    | xiii |

|         | LIST OF APPENDICES                       | XV   |

| 1       | INTRODUCTION                             | 1    |

|         | 1.1 History of Transistor                | 1    |

|         | 1.2 Problem Statements                   | 5    |

|         | 1.3 Objectives                           | 5    |

|         | 1.4 Scope of Work                        | 6    |

|         | 1.4 Signigicance of Study                | 6    |

| 2       | LITERATURE REVIEW                        | 7    |

|         | 2.1 Review of Ternary Logic.             | 7    |

|         | 2.2 Carbon Nanotube (CNT)                | 10   |

|         | 2.3 Carbon Nano Tube FET                 | 12   |

|         | 2.4 CNTFET-Based Ternary Inverter design | 14   |

|         | 2.5 Ternary Arithmetric                  | 18   |

| 3            | RES          | EARCH METHODOLOGY                                | 19 |

|--------------|--------------|--------------------------------------------------|----|

|              | 3.1          | Introduction                                     | 19 |

|              | 3.2          | Stanford University CNFET Model                  | 20 |

|              | 3.3          | HSPICE                                           | 21 |

|              | 3.4          | CosmosScope                                      | 21 |

|              | 3.5          | Gantt Chart                                      | 22 |

|              | 3.6          | CNTFET Schematic                                 | 23 |

|              | 3.7          | Ternary K-Map and Arithmetic Design              | 24 |

|              | 3.8          | Ideal & Non-Ideal input for Ternary Design       | 25 |

| 4            | RES          | ULTS AND DISCUSSION                              | 26 |

|              | 4.1          | Inverter                                         | 26 |

|              |              | 4.1.1 Proposed 2 new type of STI for the circuit | 26 |

|              |              | 4.1.2 Ternary Resistive Load                     | 28 |

|              |              | 4.1.3 Ternary CSTI                               | 30 |

|              |              | 4.1.4 PSTI-R and NSTI-R Simulation result        | 32 |

|              |              | 4.1.4 Inverter result                            | 32 |

|              | 4.2          | T-NAND Gate and T-NOR Gate                       | 37 |

|              | 4.3          | Tenary Half Adder (T-HA)                         | 40 |

| 5            | CON          | ICLUSION AND FUTURE WORK                         | 46 |

|              | 5.1          | Conclusion                                       | 46 |

|              | 5.2          | Future Work                                      | 48 |

| REFERENC     | ES           |                                                  | 49 |

| Appendices A | <b>A</b> – E |                                                  | 52 |

## LIST OF TABLES

| TABLE NO. | TITLE                                                            | PAGE |

|-----------|------------------------------------------------------------------|------|

| 1.1       | Technology node versus gate length                               | 3    |

| 1.2       | Samsung Unveil SSD using its new 3-bit V-NAND Storage Technology | 4    |

| 2.1       | Ternary inverter logic                                           | 8    |

| 2.2       | Truth Table of STI, PTI and NTI.                                 | 9    |

| 2.3       | Truth Table of T-NAND gate and T-NOR gate.                       | 9    |

| 2.4       | Ternary addition rules                                           | 18   |

| 3.1       | Gantt chart for first semester                                   | 22   |

| 3.2       | Gantt chart for second semester                                  | 22   |

| 4.1       | Summation K-Map from HA                                          | 40   |

| 4.2       | Carry K-Map from HA                                              | 40   |

## LIST OF FIGURES

| FIGURE NO. | TITLE                                                                      | PAGE |

|------------|----------------------------------------------------------------------------|------|

| 1.1        | Moore's Law                                                                | 1    |

| 2.1        | Single-wall carbon nanotubes (SWCNT)                                       | 10   |

| 2.2        | Multi-wall carbon nanotubes (MWCNT) with three shells                      | 10   |

| 2.3        | Number of articles which contain the phrase 'CNT'                          | 11   |

| 2.4        | Number of issues and applications that contain the phrase 'CNT'            | 11   |

| 2.5        | Cross sectional view Schematic diagram of a CNT transistor                 | 12   |

| 2.6        | Top view of Schematic diagram of a CNT transistor                          | 13   |

| 2.7        | Threshold voltage of CNTFETs versus $n$ (for $m = 0$ )                     | 14   |

| 2.8        | Schematic diagram of resistive load CNTFET-based STI proposed in.          | 15   |

| 2.9        | Proposed III.  Proposed CNTFET-based STI design complementary style (CSTI) | 26   |

| 2.10       | Schematic diagram of (a) NTI and (b) PTI                                   | 17   |

| 2.11       | Symbols of (a) STI, (b) NTI, and (c) PTI                                   | 17   |

| 3.1        | Research methodology flowchart                                             | 20   |

| 3.2        | Proposed new way of sketching the CNT in diagram                           | 23   |

| 3.3  | 2 variable K-Map                                  | 24 |

|------|---------------------------------------------------|----|

| 4.1  | N-type ternary with only one resistor (NSTI-R)    | 27 |

| 4.2  | P-type ternary with only one resistor (PSTI-R)    | 28 |

| 4.3  | STI-R Simulation on R1 versus R2                  | 29 |

| 4.4  | Delay of the STI-R                                | 29 |

| 4.5  | CSTI VTC curve                                    | 30 |

| 4.6  | CSTI transient response                           | 30 |

| 4.7  | CSTI with different configuration tube            | 31 |

| 4.8  | PSTI-R VTC curve                                  | 32 |

| 4.9  | PSTI-R transient response                         | 32 |

| 4.10 | NSTI-R VTC curve                                  | 33 |

| 4.11 | NSTI-R transient response                         | 33 |

| 4.12 | Transient response on all TIs and binary inverter | 34 |

| 4.13 | PDP for TI and Binary CNTFET inverter             | 35 |

| 4.14 | EDP for CSTI and Binary CNTFET inverter           | 35 |

| 4.15 | EDP for PSTI-R, NSTI-R & STI-R                    | 36 |

| 4.16 | Output result for T-NAND                          | 37 |

| 4.17 | Transient response for T-NAND                     | 37 |

| 4.18 | Output result for T-NOR                           | 38 |

| 4.19 | Transient response for T-NOR                      | 38 |

| 4.20 | PDP for T-NAND & T-NOR                               | 39 |

|------|------------------------------------------------------|----|

| 4.21 | EDP for T-NAND & T-NOR                               | 39 |

| 4.22 | RT buffer                                            | 41 |

| 4.23 | Unary decoder                                        | 41 |

| 4.24 | Output Unary decoder                                 | 42 |

| 4.25 | Ternary Half adder circuit                           | 42 |

| 4.26 | Ternary HA result with ideal input                   | 43 |

| 4.27 | Ternary Half adder circuit with Binary Logic mixture | 43 |

| 4.28 | Transient response of different HA                   | 44 |

| 4.29 | PDP of different HA                                  | 44 |

| 4.30 | EDP of different HA                                  | 45 |

| 5.1  | Binary versus ternary data handling in bits          | 47 |

| 5.2  | Proposed ternary ALU                                 | 48 |

### LIST OF ABBREVIATIONS

CMOS - Complementary Metal-Oxide-Semiconductor

MOSFET - Metal-Oxide-Semiconductor Field-Effect Transistor

R - Resistor

L - Inductor

C - Capacitor

W - Width

L - Length

NMOS - N-channel Metal-Oxide-Semiconductor

PMOS - P-channel Metal-Oxide-Semiconductor

FET - Field Effect Transistor

CNTFET - Carbon Nano Tube Field Effect Transistor

NCNTFET - N-type Carbon Nano Tube Field Effect Transistor

PCNTFET - N-type Carbon Nano Tube Field Effect Transistor

V<sub>th</sub> - Threshold Voltage

STI - Standard Ternary Inverter

PTI - Positive Ternary Inverter

NTI - Negative Ternary Inverter

STI-R - Standard Ternary Inverter With resistor load

NSTI-R - Standard Ternary Inverter with 1 resistor and 3 NCNTFET

PSTI-R - Standard Ternary Inverter with 1 resistor and 3 PCNTFET

CSTI - Complimentary Standard Ternary Inverter

TI - Ternary Inverter

T-NAND - Ternary NAND Gate Logic

T-NOR - Ternary NOR Gate Logic

CT-NAND - Complimentary Ternary NAND Gate Logic

NT-NAND-R - Ternary NAND Gate Logic with NSTI-R inserted

T-HA - Ternary Half Adder

SOC - System on Chip

SSD - Solid State Devices

SWNT - Single Wall Nano Tube

MWNT - Multi Wall Nano Tube

VLSI - Very Large Scale Integration

VTC - Voltage Transfer Curve

DC - Direct Current

SPICE - Simulation Program with Integrated Circuit Emphasis

PDP - Power Delay Product

EDP - Energy Delay Product

## LIST OF APPENDICES

| APPENDIX | TITLE                                            | PAGE |

|----------|--------------------------------------------------|------|

| A        | CNTFET HSPICE Netlist Model                      | 52   |

| В        | Binary CNTFET HSPICE Netlist                     | 53   |

| C        | Ternary CNTFET HSPICE Netlist                    | 54   |

| D        | Ternary CNTFET Arithmetic Circuit HSPICE Netlist | 56   |

| Е        | Binary CNTFET Results                            | 58   |

### **CHAPTER 1**

### **INTRODUCTION**

### 1.1 History of Transistor

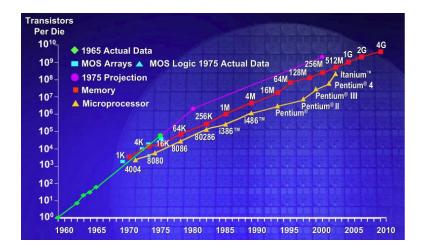

According to the popular Moore's Law, the number of transistors that can be placed on a single die doubled every two years [1]. Based on this assumption, it is predicted that in 2018, the end of complementary metal-oxide semiconductor (CMOS) era is immiment. Thus, new material and technique of fabrication or design system have been proposed and tested in many of the semiconductors manufacturing industries.

Figure 1.1 Moore's Law [2]

This is very promising when the number of transistors is increasing that allow more features in a system-on-chip (SOC) and more transistor in the same die size. Technology node and their respective physical gate length from 2007 to 2014 is tabulated in Table 1.1

**Table 1.1:** Technology node versus gate length [3]

| Year      | Technology node | Physical gate length |

|-----------|-----------------|----------------------|

|           | (nm)            | (nm)                 |

| 2007      | 45              | 32/29                |

| 2009      | 32              | 27/24                |

| 2011-2012 | 22              | 22/20                |

| 2013-2014 | 16              | 18/16                |

When downscaling is done to increase the gate count and high switching rate, it introduces a high leakage current ratio due to the limitation of conventional CMOS. Thus, new materials such as carbon nanotube, silicon nanowire and graphene are introduced to overcome this problem. In this research, carbon nanotube FET (CNTFET) in digital circuit simulation is explored. In other words, this project is focused on the simulation of Carbon Nanotube Field-Effect Transistors (CNTFET) with the ternary design and benchmark with binary design. Ternary logic design later to be verified the performance and correctness using arithmetic circuit.

Since digital logic is introduced, digital computation is only performed on two-valued logic (0 or 1, TRUE or FALSE) in the Boolean space. Multiple-valued logic (MVL) replaces the classical Boolean characterization of variables with either finitely or infinitely many values such as ternary logic [4] or fuzzy logic [5]. Ternary logic (or three-valued logic) has attracted considerable interests due to its potential advantages over binary logic for designing digital systems. For example, it is possible for ternary logic to achieve simplicity and energy efficiency in digital design since the logic reduces the complexity of interconnects and chip area. Furthermore, serial and serial-parallel arithmetic operations can be faster if the ternary logic is employed. Besides

resistive load design, ternary logic using CMOS can be found in the technical literature [6-7]. Chip area and power dissipation is reduced by more than 50 percent using an efficient MVL implementation for a signed 32-bits multiplier compared to its fastest binary counterpart [8]. MVL modules have been inserted into binary logic ICs to enhance the performance of CMOS technologies [9].

There are two kinds of MVL circuits based on MOS technology, namely the current-mode MVL circuits and the voltage mode MVL circuits. Voltage-mode MVL circuits have been achieved in multithreshold CMOS design [10]. The carbon nanotube (CNT) FET (CNTFET) is a promising alternative to the bulk silicon transistor for lowpower and high-performance design due to its ballistic transport and low OFF-current properties [11-15]. A multithreshold CMOS design relies on body effects using different bias voltages to the base or the bulk terminal of the transistors. In a CNTFET, the threshold voltage of the transistor is determined by the diameter of the CNT. Therefore, a multithreshold design can be accomplished by employing CNTs with different diameters (and, therefore, chirality) in the CNTFETs. A resistive-load CNTFET-based ternary logic design has been proposed in Ref. [8]. However, in this configuration, large OFF-chip resistors (of at least  $100M\Omega$  values) are needed due to the current requirement of the CNTFETs. The design technique proposed in this paper base on Ref. [16] to eliminate the large resistors by employing active load with p-type CNTFETs in the ternary logic gates. In this paper, the multivalued logic design based on multithreshold CNTFETs is assessed and compared with existing multivalued logic designs based on CNTFETs.

In this research, designs of basic ternary gates/operators inverter is described in details namely ternary inverters (TI), ternary NAND (T-NAND), and ternary NOR (T-NOR). Beside resistive load inverter, another three type of inverter is used to benchmark performance. Ternary half adder (T-HA) is used for the reference to verify and analysis are presented as examples of the application of these ternary gates design technique.

For the arithmetic circuit design, a modified ternary logic circuit design technique is used to speed up and reduce power consumption of the circuits. The modified ternary logic design uses both ternary logic gates and binary logic gates based on the previous ternary logic design structures to take advantage of the two logic design styles' merits. The ternary logic gates are a good candidate for decoding block since it requires less number of gates while binary logic gates are a good candidate for fast computation. In this report, the modified ternary logic design method is proposed to achieve gate count reduction. Figure 1.2 is another solid proof that at CMOS design, Samsung already produce Solid State Device using 3-Bit V-NAND Technology and it proof the ternary can be very useful to handle the massive data. System on Chip (SOC) become main stream design, data handling become more heavy and most probably ternary design can be the replace binary design in some application .

# Samsung Unveils Solid State Drives Using Its New 3-Bit V-NAND Storage Technology

BY FARHAN · 2 DAYS AGO · 4 COMMENTS · 2.1K VIEWS

Figure 1.2 Samsung unveil SSD using its new 3-bit V-NAND storage technology

[17]

### 1.2 Problem Statements

Silicon (Si) MOSFET has reached its limits as the technology is scaling down. Unlike Si MOSFET, CNTFET is favorable [8] due to its ballistic transport and low OFF current properties. This research addressed the following issues: How many type of Ternary inverter can be proposed for CNTFET-based design? What type of application can be applied on these few type of ternary inverter? What is the performance of ternary logic in CNTFET versus Binary logic in CNTFET? What is the maximum number of CNT can be placed in the channel to obtain the optimum performance of the device? How to model the 3 bits input for the ternary design using HSPICE?

### 1.3 Objectives

Since the Silicon based MOSFET is reaching the end of roadmap, this project is based on SPICE circuit-simulation of a type of multi-level logic gate design using Carbon Nanotube Field Effect Transistor (CNTFET). The objectives are:

- To compare CNTFET-based binary inverter and standard ternary inverter with resistive-load (STI-R) with other three type of inverter is proposed Complementary Standard Ternary Inverter (CSTI); Standard Ternary Inverter with 1 resistor and 3 NCNTFET (NSTI-R); Standard Ternary Inverter with 1 resistor and 3 PCNTFET (PSTI-R) to analysis the performance

- 2. To extend the ternary logic design to arithmetic ternary design and analyze the performance.

- 3. To study the combination of ternary design and binary design hence benchmark it performance.

### 1.4 Scope of Work

The main scope of this project is to study and simulate four types of inverter ternary design using CNTFET where the SPICE model is obtained from Stanford University. Four types ternary Inverter design is further analysis and benchmarks with Binary design to evaluate the performance. Arithmetic circuit used to verify the correctness from the ternary design. In addition, combination of ternary design and binary design in the ternary arithmetic is studied and simulated to improve the performance. HSPICE is used alongside Cosmoscope to perform digital circuit simulation. 3 bits input from the HSPICE model is introduced for ternary design and used for all ternary design simulation. Arithmetic circuit is used to simulate and study the energy efficiency and benchmarked with binary logic CNTFET design.

### 1.5 Significance of Study

This project has several important outcomes, which are

- 1. A new design of inverter is propose into the ternary design and identify the performance in several application.

- 2. Ternary design shown is state of art at the future to handle massive data processing and storage.

- 3. Tolerance of ternary input is identify with imperfect three levels (logic 0, 1 and 2) of square wave.

### REFERENCES

- 1. Hassan S. and Asghar M., Limitation of Silicon Based Computation and FutureProspects, in *Communication Software and Networks*, 2010. ICCSN'10. Second International Conference on, 2010, pp. 559-561.

- 2. Gunther. N. J. (2007). Moore's Law: More or Less? Available website: <a href="http://www.cmg.org/measureit/issues/mit41/m\_41\_2.html">http://www.cmg.org/measureit/issues/mit41/m\_41\_2.html</a>

- 3. Iwai. H, "Roadmap for 22&10nm and beyond (Invited Paper)," *Microelectronic Engineering*, vol. 86, pp. 1520-1528, 2009.

- 4. Mukaidono. M, Regular ternary logic functions—Ternary logic functions suitable for treating ambiguity, *IEEE Trans. Comput.*, vol. C-35, no. 2, pp. 179–183, Feb. 1986.

- 5. Araki T., Tatsumi H., Mukaidono M., and Yamamoto F., Minimization of incompletely specified regular ternary logic functions and its application to fuzzy switching functions, in *Proc. IEEE Int. Symp*. Multiple-Valued Logic, May, 1998, pp. 289–296.

- 6. Balla. P. C. and Antoniou. A., Low power dissipation MOS ternary logicfamily, *IEEE J. Solid-State Circuits*, vol. 19, no. 5, pp. 739–749, Oct. 1984.

- 7. Raychowdhury and Roy K., Carbon-nanotube-based voltage-mode multiple-valued logic design, *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 168–179, Mar. 2005.

- 8. Rich. D. A., A survey of multivalued memories, IEEE Trans. Comput., vol. 35, no. 2, pp. 99–106, Feb. 1986.

- 9. Yasuda.Y., Tokuda Y., Taima S., Pak K., Nakamura T, and Yoshida A., Realization of quaternary logic circuits by n-channel MOS devices, *IEEE J. Solid-State Circuits*, vol. 21, no. 1, pp. 162–168, Feb. 1986.

- 10. Appenzeller J, Carbon nanotubes for high-performance electronics—Progress and prospect, *Proc. IEEE*, vol. 96, no. 2, pp. 201–211, Feb. 2008.

- 11. Rahman, Guo J., Datta S., and Lundstrom M. S., Theory of ballistic nanotransistors, *IEEE Trans. Electron Device*, vol. 50, no. 10, pp. 1853–1864, Sep. 2003.

- 12. Akturk, Pennington G., Goldsman N., and Wickenden A., Electron transport and velocity oscillations in a carbon nanotube, *IEEE Trans. Nanotechnol.*, vol. 6, no. 4, pp. 469–474, Jul. 2007.

- 13. Hashempour H. and Lombardi F., Device model for ballistic CNFETs using the first conducting band, *IEEE Des. Test. Computer*, vol. 25, no. 2, pp. 178–186, Mar./Apr. 2008.

- 14. Lin Y., Appenzeller J., Knoch J., and Avouris P, High-performance carbon nanotube field-effect transistor with tunable polarities, *IEEE Trans. Nanotechnol.*, vol. 4, no. 5, pp. 481–489, Sep. 2005.

- 15. Kleene S. C., Introduction to Metamathematics. Amsterdam, The Netherlands: North-Holland, 1952, pp. 332–340.

- 16. Lin S., Kim. Y.-B., and Lombardi F., A novel CNTFET-based ternary logic gate design, in *Proc. IEEE Int. Midwest Symp. Circuits Syst.*, Aug. 2009, pp. 435–438

- 17. Website: <a href="http://www.lowyat.net/2014/12/samsung-unveils-solid-state-drives-using-its-new-3-bit-v-nand-storage-technology/">http://www.lowyat.net/2014/12/samsung-unveils-solid-state-drives-using-its-new-3-bit-v-nand-storage-technology/</a> Dec 2014

- 18. Lucasiewicz, Jan O Logice Tr´ojwarkoscioewj English translation: *On three valued logic*, in L. Borkowski (ed.), Selected works by Jan Lukasiewicz, North Holland, Ams-terdam, 1970, pp. 87-88

- 19. Balla P. C. and Antoniou A., Low power dissipation MOS ternary logic family, IEEE J. *Solid-State Circuits*, vol. 19, no. 5, pp. 739–749, Oct.1984.

- 20. Raychowdhury A. and Roy K., Carbon-nanotube-based voltage-mode multiple-valued logic design," *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 168–179, Mar. 2005

- 21. Shande A. P, Ingole V T, Ghiye V R, Ternary digital system, consepts and applications Oct 2014 page 15

- 22. Park. J. Y, Band Structure and Electron Transport Physicsof One Dimensional SWNTs, in *Carbon Nanotube Electronics*, A. Javey, Kong, J., Ed., ed New York, USA: Springer Science+Business Media, 2009

- 23. Deji A., Wong, P.H.S., Carbon Nanotube and Graphene Device Physics. United States of America: Cambridge University Press, New York, 2011.

- 24. Appenzeller J., "Carbon nanotubes for high-performance electronics—Progress and prospect," Proc. IEEE, vol. 96, no. 2, pp. 201–211, Feb. 2008

- 25. (2008). Stanford University CNFET model Website. Stanford University, Stanford, CA [Online]. Available website: <a href="http://nano.stanford.edu/model.php?id=23">http://nano.stanford.edu/model.php?id=23</a>

- 26. Deng J. and Wong, H.-S. P, A compact SPICE model for carbon nanotube field-effect transistors including nonidealities and its application—Part I: Model of the intrinsic channel region, *IEEE Trans. Electron Device*, vol. 54, no. 12, pp. 3186–3194, Dec. 2007

- 27. Deng J. and Wong, H.-S. P, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part II: Full device model and circuit performance benchmarking, *IEEE Trans. Electron Device*, vol. 54, no. 12, pp. 3195–3205, Dec. 2007

- 28. Wang B., Poa P., Wei L., Li.P., Yang Y., and Y. Chen, (n,m) Selectivity of single-walled carbon nanotubes by different carbon precursors on Co–Mo catalysts, J. Amer. Chem. Soc., vol. 129, no. 9, pp. 9014–9019, 2007

- 29. Balla. P. C. and Antoniou A, Low power dissipation MOS ternary logic family, *IEEE J. Solid-State Circuits*, vol. 19, no. 5, pp. 739–749, Oct. 1984

- 30. Sheng Lin CNTFET-Based Design of Ternary Logic Gatesand Arithmetic Circuits, *IEEE TRANSACTIONS ON NANOTECHNOLOGY*, VOL. 10, NO. 2, MARCH 2011 217

- 31. Shande. A. P, Ingole V. T., V R Ghiye, Ternary digital system, consepts and applications Oct 2014 page 4