#### SPECULATIVE TECHNIQUES FOR MEMORY HIERARCHY MANAGEMENT

#### A Dissertation

by

#### LAITH MOHAMMAD ALBARAKAT

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Paul V. Gratz

Committee Members, Daniel A. Jiménez

Samuel Palermo

I-Hong Hou

Head of Department, Miroslav M. Begovic

May 2021

Major Subject: Computer Engineering

Copyright 2021 Laith Mohammad AlBarakat

#### ABSTRACT

The "Memory Wall" [1], is the gap in performance between the processor and the main memory. Over the last 30 years computer architects have added multiple levels of cache to fill this gap, cache levels that are closer to the processors are smaller and faster. On the other hand, the levels that are far from the processors are bigger and slower. However the processors are still exposed to the latency of DRAM on misses. Therefore, speculative memory management techniques such as prefetching are used in modern microprocessors to bridge this gap in performance.

First, we propose Synchronization-aware Hardware Prefetching for Chip Multiprocessors, a novel hardware data prefetching scheme designed for prefetching shared-memory, multi-threaded workloads. This is the first work we are aware of to characterize the causes of poor prefetching performance in shared-memory multi-threaded applications. These are the inability to prefetch beyond synchronization points and tendency to prefetch shared data before it has been written. SB-Fetch, a low-complexity, low-overhead prefetcher design that addresses both issues.

Second, we propose a new prefetching algorithm, Set-Level Adaptive Prefetching for Compressed Caches (SLAP-CC), which seeks to address this problem by varying the prefetching aggressiveness based on how much effective capacity is available in each set. The ontributions of this work is characterize the increase and per-set variability of cache efficiency which typical cache compression schemes create, and propose a new prefetching scheme, SLAP-CC, designed to leverage this cache efficiency variability.

Third, we propose a new scheduling mechanism that predicts hard-to-prefetch loads at issue time and preemptively schedule them for execution as soon as they are ready, to allow the cache hierarchy to start the mishandling mechanism sooner. Such scheduling mechanism reduces the miss penalty on the dependent instructions after a hard-to-prefetch loads.

#### ACKNOWLEDGMENTS

I would like to thank my advisor Dr. Paul V. Gratz for the opportunity to participate in research with the Computer Architecture, Memory Systems and Interconnection Networks(CAMSIN) research group. His advice and feedback that made this work successful.

I would also like to express my gratitude to my advisory committee members, Dr. Daniel A. Jiménez, Dr. I-Hong Hou and Dr. Samuel Palermo for their time and effort reviewing this work.

Finally, I would like to thank all my family for their love, encouragement, and support.

## CONTRIBUTORS AND FUNDING SOURCES

## Contributors

This work was supported by a dissertation committee consisting of Dr. Paul V. Gratz, Dr. I-Hong Hou, Dr. Samuel Palermo of the Department of Computer and Electrical Engineering and Dr. Daniel A. Jimenez of the Department of Computer Science and Engineering.

All other work conducted for the dissertation was completed by the student independently.

# **Funding Sources**

There are no outside funding contributions to acknowledge related to the research and compilation of this document.

# TABLE OF CONTENTS

|    |              |                                                               | P                                                               | age      |

|----|--------------|---------------------------------------------------------------|-----------------------------------------------------------------|----------|

| ΑF | BSTR         | ACT                                                           |                                                                 | ii       |

| A( | CKNC         | OWLED                                                         | GMENTS                                                          | iii      |

| CO | ONTF         | RIBUTO                                                        | ORS AND FUNDING SOURCES                                         | iv       |

| TA | BLE          | OF CO                                                         | ONTENTS                                                         | v        |

|    |              |                                                               | JRES                                                            |          |

|    |              |                                                               | LES                                                             |          |

| LI | 31 U         | r iadi                                                        |                                                                 | Х        |

| 1. | INT          | RODUG                                                         | CTION                                                           | 1        |

|    | 1.1          | _                                                             | ative Techniques for Memory Hierarchy                           |          |

|    | 1.2          |                                                               | tation Statement                                                |          |

|    | 1.3          | Dissert                                                       | tation Organization                                             | 4        |

| 2. | BAC          | CKGRO                                                         | UND AND RELATED WORK                                            | 5        |

|    | 2.1          | Data I                                                        | Prefetching                                                     | 5        |

|    | 2.2          |                                                               | Compression                                                     |          |

|    | 2.3          | Load (                                                        | Criticality                                                     | 8        |

| 3. | Syno         | chroniza                                                      | tion-Aware Hardware Prefetching for Chip Multiprocessors        | 9        |

|    | 3.1          | Introd                                                        | uction                                                          | 10       |

|    | $3.1 \\ 3.2$ |                                                               | ation and Background                                            |          |

|    | 9.2          | 3.2.1                                                         | Data Prefetching                                                |          |

|    |              | 0.2.1                                                         | 3.2.1.1 B-Fetch Microarchitecture                               |          |

|    |              | 3.2.2                                                         | The Shared Memory Model                                         |          |

|    |              |                                                               | 3.2.2.1 Shared Memory Synchronization                           | 17       |

|    |              |                                                               | 3.2.2.2 Architectural Support for Shared Memory Synchronization | 18       |

|    |              | 3.2.3                                                         | Cache Coherence                                                 | 19       |

|    |              |                                                               | 3.2.3.1 Prefetching in Multithreaded Workloads                  | 21       |

|    | 3.3          | _                                                             | sed Design                                                      | 23       |

|    |              | 3.3.1                                                         | Overview                                                        | 23       |

|    |              | 3.3.2                                                         | System Components                                               | 24       |

|    | 3.4          | 3.3.3<br>Evalua                                               | Hardware Cost                                                   | 26<br>27 |

|    | 0.4          | $-\mathbf{r}_{I}\mathbf{v}\mathbf{a}_{I}\mathbf{m}\mathbf{a}$ | MIOH                                                            | 21       |

|    |                                                 | 3.4.1                                                | Methodology                                      | 27 |  |  |  |

|----|-------------------------------------------------|------------------------------------------------------|--------------------------------------------------|----|--|--|--|

|    |                                                 | 3.4.2                                                | Results                                          | 28 |  |  |  |

|    |                                                 |                                                      | 3.4.2.1 Performance                              |    |  |  |  |

|    |                                                 |                                                      | 3.4.2.2 Coverage and Accuracy Analysis           | 30 |  |  |  |

|    |                                                 |                                                      | 3.4.2.3 Sensitivity Analysis                     | 32 |  |  |  |

|    |                                                 |                                                      | 3.4.2.3.1 Invalidation Filter Size               | 32 |  |  |  |

|    |                                                 |                                                      | 3.4.2.3.2 Synchronization Primitives Trace Cache | 33 |  |  |  |

|    |                                                 |                                                      | 3.4.2.3.3 Branch Confidence                      | 33 |  |  |  |

|    |                                                 |                                                      | 3.4.2.3.4 Scalability                            |    |  |  |  |

| 4. | SET                                             | SET-LEVEL ADAPTIVE PREFETCHING FOR COMPRESSED CACHES |                                                  |    |  |  |  |

|    | 4.1                                             | Introd                                               | uction                                           | 36 |  |  |  |

|    | 4.2                                             | Backg                                                | round and Motivation                             | 41 |  |  |  |

|    |                                                 | 4.2.1                                                | Cache Compression                                | 42 |  |  |  |

|    |                                                 | 4.2.2                                                | Compressed Cache Layout                          | 43 |  |  |  |

|    |                                                 | 4.2.3                                                | Dead Block Prediction and Replacement            |    |  |  |  |

|    |                                                 | 4.2.4                                                | Data Prefetching                                 |    |  |  |  |

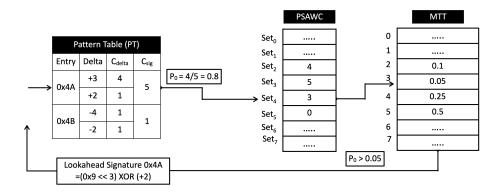

|    |                                                 |                                                      | 4.2.4.1 Signature Pattern Prefetcher (SPP)       |    |  |  |  |

|    |                                                 | 4.2.5                                                | Compression and Prefetching Interactions         |    |  |  |  |

|    | 4.3                                             |                                                      | l                                                |    |  |  |  |

|    |                                                 | 4.3.1                                                | Design Overview                                  |    |  |  |  |

|    |                                                 | 4.3.2                                                | SLAP-CC Cache Compression.                       | 51 |  |  |  |

|    |                                                 | 4.3.3                                                | <u>-</u>                                         |    |  |  |  |

|    | 4.4                                             |                                                      | -CC Implementation                               | 54 |  |  |  |

|    | 4.5                                             |                                                      | ation                                            | 55 |  |  |  |

|    | 4.0                                             | 4.5.1                                                | Methodology                                      | 55 |  |  |  |

|    |                                                 | 4.5.2                                                | 30                                               | 57 |  |  |  |

|    | 16                                              | _                                                    | v                                                |    |  |  |  |

|    | 4.6                                             | Concu                                                | usion                                            | 61 |  |  |  |

| 5. | SCHEDULING MECHANISM FOR HARD TO PREFETCH LOADS |                                                      |                                                  |    |  |  |  |

|    | 5.1                                             |                                                      |                                                  | 62 |  |  |  |

|    | 5.2                                             | _                                                    | round and Motivation                             | 65 |  |  |  |

|    |                                                 | 5.2.1                                                | Instruction Criticality                          | 65 |  |  |  |

|    |                                                 | 5.2.2                                                | Latency Prediction                               | 66 |  |  |  |

|    |                                                 | 5.2.3                                                | Data Prefetching                                 | 67 |  |  |  |

|    | 5.3                                             | Hard-t                                               | to-Prefetch Loads Scheduling                     | 68 |  |  |  |

|    |                                                 | 5.3.1                                                | Identifying Hard Loads                           | 68 |  |  |  |

|    |                                                 | 5.3.2                                                | Scheduler Design                                 | 70 |  |  |  |

|    | 5.4                                             | Evalua                                               | ation                                            | 70 |  |  |  |

|    |                                                 | 5.4.1                                                | Methodology                                      | 70 |  |  |  |

|    |                                                 | 5.4.2                                                | Performance Analysis                             | 71 |  |  |  |

|    | 5.5                                             | Conclu                                               | ·                                                | 71 |  |  |  |

| 6  | CON                                             | VCLUS                                                | ION                                              | 73 |  |  |  |

| REFERENCES | <br> | <br> | 74 |

|------------|------|------|----|

|            |      |      |    |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                            |      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Memory access latency                                                                                                                                                                                      | . 2  |

| 3.1    | Speedup of Parsec [36], Rodinia [37], and Parboil [38] workloads with <i>B-Fetch</i> [12, 13], normalized against a no-prefetching baseline                                                                | . 11 |

| 3.2    | Data Access and Control Flow.                                                                                                                                                                              | . 13 |

| 3.3    | B-Fetch microarchitecture.                                                                                                                                                                                 | . 14 |

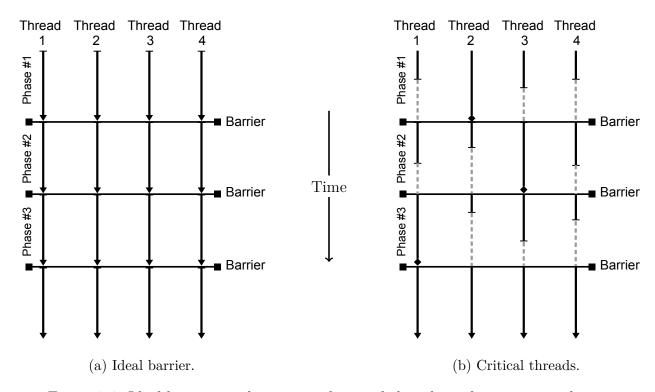

| 3.4    | Ideal barrier synchronizes and critical threads in the execution phases                                                                                                                                    | . 17 |

| 3.5    | Cache coherence and prefetching                                                                                                                                                                            | . 20 |

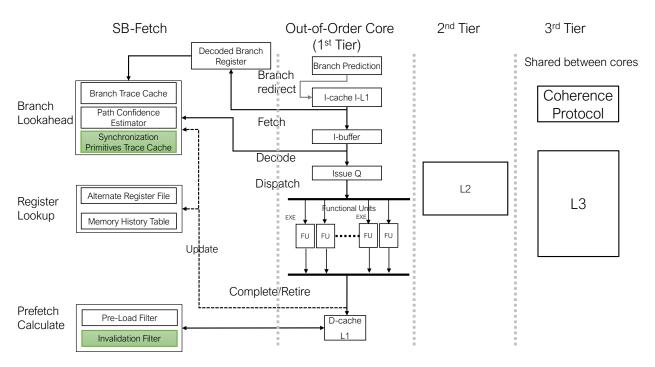

| 3.6    | SB-Fetch microarchitecture. Additional components beyond B-Fetch high-lighted in green.                                                                                                                    | . 25 |

| 3.7    | Single Synchronization Primitives Trace Cache (SPTC) entry                                                                                                                                                 | . 25 |

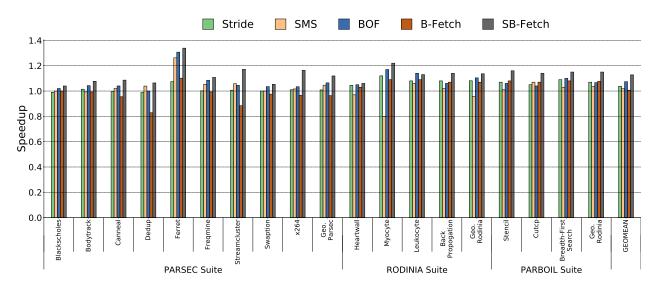

| 3.8    | Multi-threaded workload speedups                                                                                                                                                                           | . 29 |

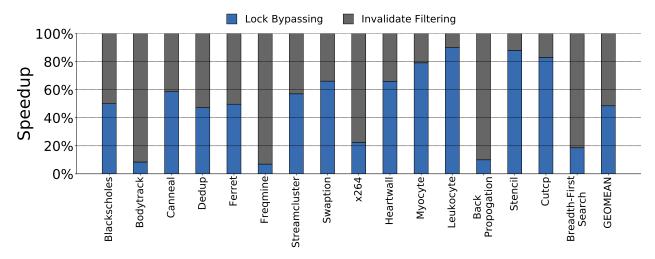

| 3.9    | SB-Fetch speedup breakdown by mechanism                                                                                                                                                                    | . 30 |

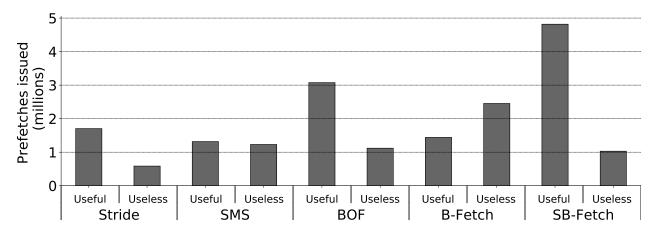

| 3.10   | Useful and useless prefetches issued, averaged across all benchmarks for each prefetcher.                                                                                                                  | . 31 |

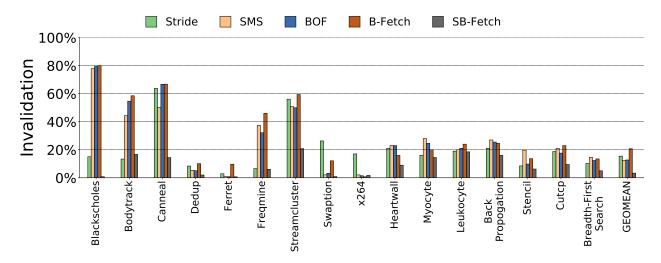

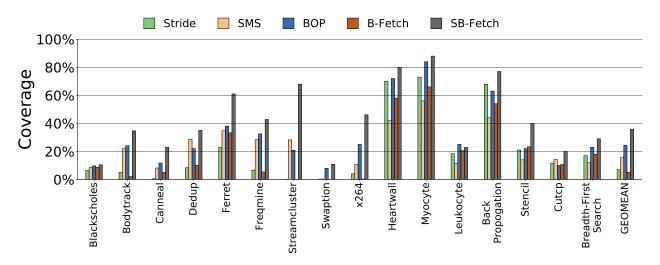

| 3.11   | Invalidated prefetches for each prefetcher across all benchmarks                                                                                                                                           | . 32 |

| 3.12   | Coverage for each prefetcher across all benchmarks.                                                                                                                                                        | . 32 |

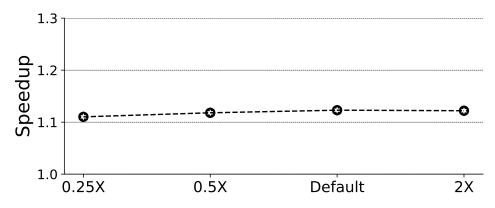

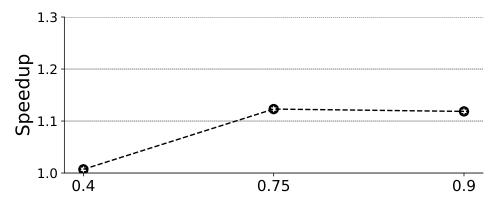

| 3.13   | Invalidation Filter size sensitivity.                                                                                                                                                                      | . 33 |

| 3.14   | Synchronization Primitives Trace Cache sensitivity.                                                                                                                                                        | . 33 |

| 3.15   | Branch confidence sensitivity.                                                                                                                                                                             | . 34 |

| 3.16   | SB-Fetch speedup comparison for 4- and 8-core CMPs normalized to the baseline.                                                                                                                             | . 34 |

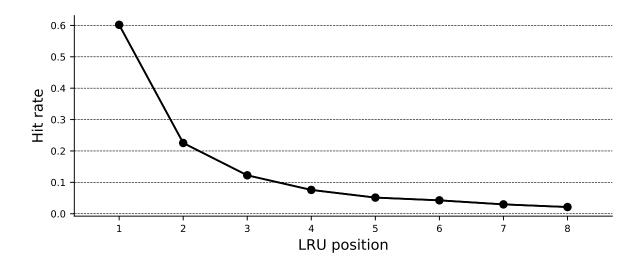

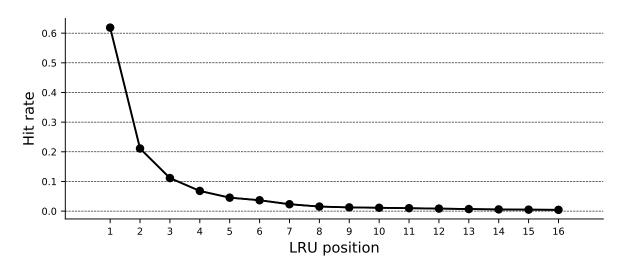

| 4.1    | Mean L2 hitrate per way under SPEC CPU2017 benchmarks, sorted into an LRU stack for a 256KB L2 cache of 8-ways - representing baseline; and a 512KB L2 cache of 16-ways - representing perfect compression | . 39 |

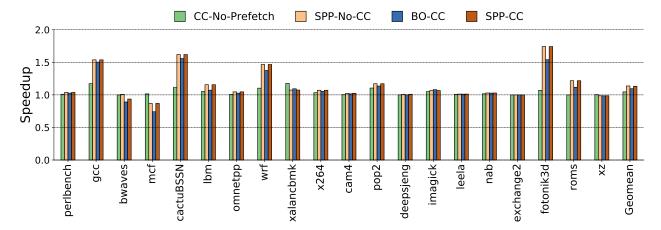

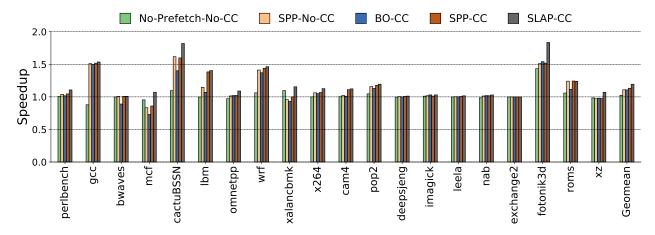

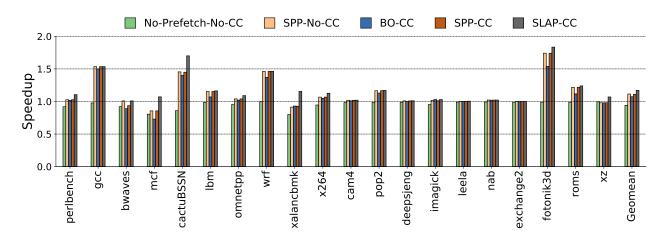

| 4.2  | SPEC CPU 2017 Single-Core IPC Speedup with and without BΔI [26] cache compression (CC), the SPP [68] prefetcher and Best Offeset (BO) [69] prefetcher all normalized against no prefetching/no CC in the L2 cache. | 40 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3  | $B\Delta I$ compression using one base value                                                                                                                                                                       | 43 |

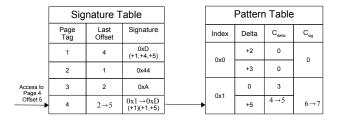

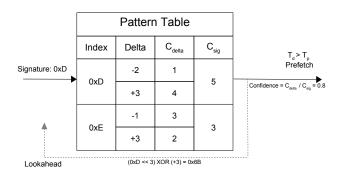

| 4.4  | SPP Data-path Flow                                                                                                                                                                                                 | 46 |

| 4.5  | SPP lookahead prefetching.                                                                                                                                                                                         | 46 |

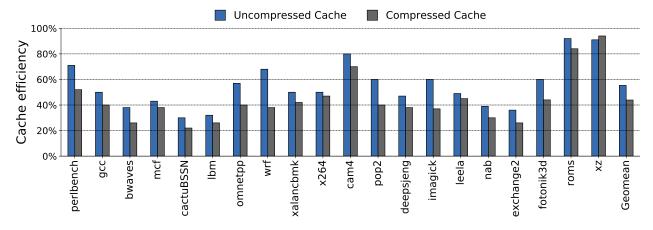

| 4.6  | Cache efficiency.                                                                                                                                                                                                  | 48 |

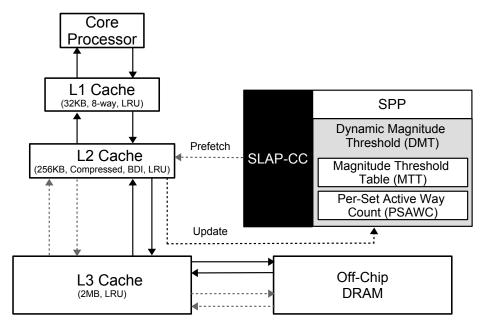

| 4.7  | SLAP-CC Design Overview.                                                                                                                                                                                           | 51 |

| 4.8  | Dynamic Magnitude Threshold                                                                                                                                                                                        | 54 |

| 4.9  | SPEC CPU 2017 Single-Core IPC Speedup, normalized against a system with a B $\Delta$ I compressed L2 and no prefetching                                                                                            | 57 |

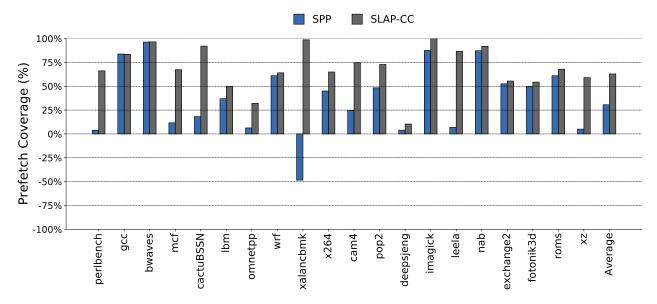

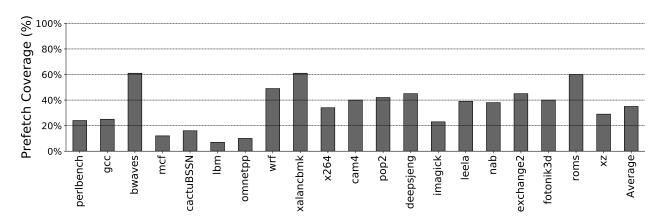

| 4.10 | Prefetching coverage.                                                                                                                                                                                              | 58 |

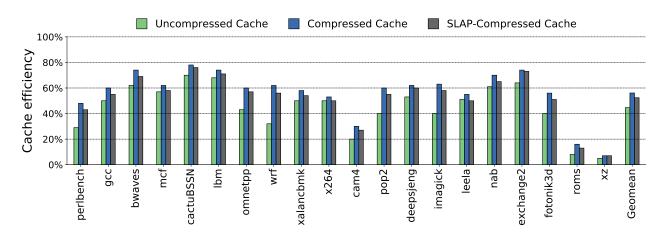

| 4.11 | Cache efficiency.                                                                                                                                                                                                  | 58 |

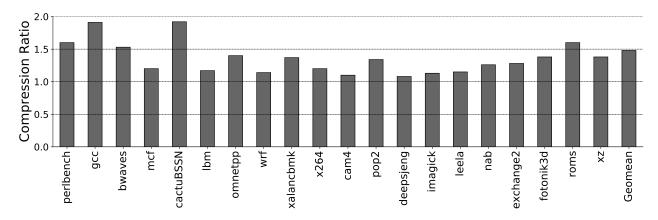

| 4.12 | Compression Ratio.                                                                                                                                                                                                 | 59 |

| 4.13 | Speedups for a baseline system with a faster LLC access time                                                                                                                                                       | 59 |

| 5.1  | Prefetch Coverage of SPP.                                                                                                                                                                                          | 63 |

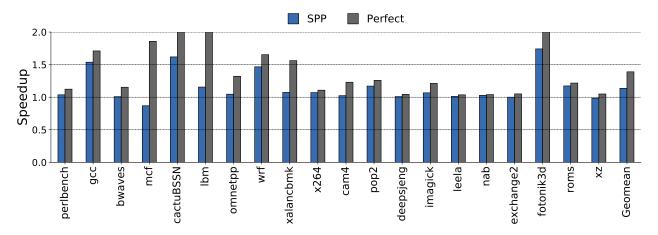

| 5.2  | Speedup with SPP and Perfect Prefetcher                                                                                                                                                                            | 64 |

| 5.3  | Dataflow graph.                                                                                                                                                                                                    | 66 |

| 5.4  | HLS Design Overview                                                                                                                                                                                                | 69 |

| 5.5  | SPEC CPU 2017 Single-Core IPC Speedup                                                                                                                                                                              | 72 |

# LIST OF TABLES

| TABLE      |                                 | Page |

|------------|---------------------------------|------|

|            | Hardware storage overhead in KB |      |

| 4.1<br>4.2 | Hardware storage overhead in KB |      |

| 5.1        | Simulation Parameters.          | . 71 |

## 1. INTRODUCTION

Big Data has revolutionized many areas of scientific research, science and technology. For the last decade, computer scientists developed tools to mine, structure, and visualize data in ways never before possible. As we move to the future to welcome the "Insight Era.", where machine learning and artificial intelligence are refined to facilitate data-driven decision-making. Our ability to perform computation on massive data sets is expected to increase.

Data-intensive computation forms significant challenges for computer architects. In particular, the volume and movement of large data sets generate significant stress on the memory hierarchy, leading to performance bottleneck.

#### 1.1 Speculative Techniques for Memory Hierarchy

The memory hierarchy has been a determining factor of overall system performance. Access to off-chip memory costs many cycles and consumes more energy. Therefore, designing efficient memory hierarchy requires low access latencies and maximizes the hit rates.

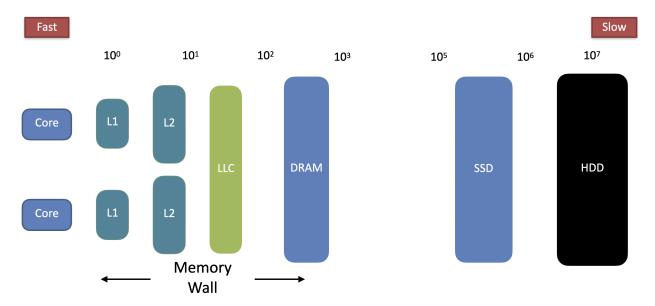

Figure 1.1 outlines a typical cache hierarchy in a modern system. The "Memory Wall" [1], is the gap in performance between the processor and the main memory. Over the last 30 years computer architects have added multiple levels of cache to fill this gap, cache levels that are closer to the processors are smaller and faster. On the other hand, the levels that are far from the processors are bigger and slower. The goal of the this hierarchy is to improve average memory access time by frequently handling the demand requests at the cache, and avoiding the long access latency of DRAM. Despite this hierarchy the processors are still exposed to the latency of DRAM on misses. Cache size is a key design parameter that impacts performance, die area, and power consumption. With the end of Dennard scaling [2], growing cache size comes at an increasingly high cost in terms of power and energy consumption.

Figure 1.1: Memory access latency.

To hide memory access latency, computer architects have focused on speculative memory management techniques such as data prefetching; cache replacement policies; and reuse prediction.

Data prefetching in particular gained a lot of interest in the computer architect community and has been deeply studied. In addition to that, hardware prefetchers have been deployed in modern microprocessor design. Prefetching is predicting a subsequent memory access and fetching the required values ahead of the memory access to hide any potential long memory latency. To be effective, prefetching must be timely, accurate and introduce low hardware overhead. Ideally, a perfect prefetcher could make all memory accesses hit in the level one cache. However, in practice prefetchers may not be timely or accurate. Despite the fact that hardware prefetchers have an impressive impact on instructions per cycle by reducing the number of cache misses, the processor is still exposed to the memory wall on a cache miss due to Hard-to-Prefetch loads.

Another cache optimization technique that interacts positively with data prefetching is cache compression. Cache compression has the potential to increase the effective capacity of the cache with extra area overhead. Compressed caches can achieve the benefits of larger caches without making the cache physically larger by fitting more cache blocks in the same cache space. Building a compressed cache centered around two main components: a compression algorithm that maps the data to a compressed format with fewer bits, and cache layout to fit compressed blocks in the cache [3]. To be effective, cache compression must be fast, simple, and effective in saving storage space. Therefore, the compression ratio should be large and the hardware complexity of implementing the scheme should be low in terms of area and power. The biggest challenge to build a compressed cache in modern microprocessors is the decompression latency. Unlike compression latency, which can take place off the critical path, decompression is on the critical path and increases the cache access time.

#### 1.2 Dissertation Statement

In this dissertation, we aim to develop a new set of speculative techniques for modern memory hierarchies, resulting in performance improvements and attractive to be implemented in future systems.

To this end, we first characterize the causes of poor prefetching performance in shared-memory multi-threaded applications. These are the inability to prefetch beyond synchronization points and tendency to prefetch shared data before it has been written. Building upon this characterization, we propose SB-Fetch, a low-complexity, low-overhead prefetcher design that addresses both issues.

Second, we propose a new prefetching algorithm, Set-Level Adaptive Prefetching for Compressed Caches (SLAP-CC), which seeks to address this problem by varying the prefetching aggressiveness based on how much effective capacity is available in each set. The contributions of this work is characterize the increase and per-set variability of cache efficiency which typical cache compression schemes create, and propose a new prefetching scheme, SLAP-CC, designed to leverage this cache efficiency variability.

Third, we propose a new scheduling mechanism that predicts hard-to-prefetch loads at issue time and preemptively schedule them for execution as soon as they are ready, to allow

the cache hierarchy to start the mishandling mechanism sooner. Such scheduling mechanism reduces the miss penalty on the dependent instructions after a hard-to-prefetch loads.

Each speculative technique is designed to have low hardware complexity so that it can be easily implemented in future systems.

## 1.3 Dissertation Organization

In the following chapters, each speculative technique is first introduced with the main research motivations that lead up to this work, followed by detailed design implementation, then followed by evaluation methodology and results obtained. To put our work into perspective, Chapter 2 introduces a background and some of the most relevant related work. Chapter 3 discusses the synchronization-aware hardware prefetching for chip multiprocessors. Chapter 4 introduces set-level adaptive prefetching for compressed caches. In Chapter 5 we present our new scheduling mechanism for hard to prefetch loads. Finally, Chapter 6 concludes this dissertation.

#### 2. BACKGROUND AND RELATED WORK

Our work builds on the contributions of many other researchers to the field. To place our work in the context of other research, we now review some of the most recent related work.

#### 2.1 Data Prefetching

Data prefetching is a well known technique in which the cache is pre-filled with useful data ahead of an actual demand load request coming from the processor. Several hardware prefetchers with diverse prefetching strategies have been proposed in the literature.

History-based prefetching is the most commonly used among hardware prefetching strategies, where a prefetch engine uses the history of memory references to predict future references and generate prefetch requests. Spatial Memory Streaming (SMS) prefetcher is one of the current top-performing, light-weight, history based prefetchers [4, 5]. SMS predicts the future access pattern within a spatial region around a miss, based on a history of access patterns initiated by that missing instruction [4]. SMS uses the concept of a spatial region which begins with the first demand miss to a region and ends with the eviction or invalidation of any block from that region [4]. Spatial prefetchers are ineffective for pointer-based data structures with arbitrary memory layouts and have shown limited effectiveness for some workloads with many pointer-chasing access patterns [4, 6, 7, 5].

Runahead-based prefetching uses the execution core to pre-execute a set of instructions speculatively instead of stalling the resources on a long latency cache miss that goes all the way to memory [8, 9, 10]. Run-ahead was originally proposed in the context of in-order cores by Dundas and Mudge [11]. Mutlu et al. proposed an implementation to support runahead execution in out-of-order processors [8], in the implementation, when a memory operation misses in the second-level cache, the processor enters runahead mode and speculatively pre-executed future instructions to initiate prefetching. The drawback with using runahead prefetchers, there is a large overhead to recover from the runahead mode and restart normal

execution. Also, because of this overhead, the effectiveness of this mechanism to handle shorter latencies like the first-level cache miss latencies is reduced [12, 13, 6, 5, 8, 9, 10].

Branch-predictor-directed prefetchers reuse existing branch predictors to explore future control flow. These techniques use the branch predictor to recursively make future predictions to find instruction-block addresses for prefetch. Because branch predictors are decoupled from the rest of the pipeline, predictors can theoretically advance ahead of execution to an arbitrary extent to predict future control flow. Liu at el. [14, 12, 13, 6, 5] proposed branch-based data prefetching, which associated the history of data references to the previous branch instructions in the Branch Target Buffer (BTB). The BTB is then used to issue prefetches for load instructions following the branch instruction in the program flow. Pinter at el. proposed Tango prefetcher for superscalar implementations, to further improve the quality of stride-based reference prediction table approach proposed by Chen at el. [15]. Some prefetchers, such as B-Fetch [12, 13, 6, 5], are triggered by the fetch of a branch instruction by the processor, making them more suitable for prefetching beyond synchronization points as we will discuss. B-Fetch is a data cache prefetcher that employs two speculative components. It speculates on the expected path through future basic blocks, using a lookahead mechanism that relies on branch prediction to predict that execution path, and a scheme to predict the effective addresses of load instructions along that path based on the register file transformations per-basic block [12, 13, 6, 5]. B-Fetch records the variation of register contents at earlier branch instructions and uses this knowledge to predict the effective address. B-Fetch is a light-weight and very accurate prefetcher, but it requires a very complex hardware and a lot of hooks to the microarchitecture [12, 13, 6, 5].

Sequential Pattern Prefetchers are limited to waiting until a cache miss occurs, and then reading either a set of lines sequentially following the current miss [16], a set of lines following a strided pattern with respect to the current miss [17], or a set of blocks spatially around the miss [4, 5]. More recent prefetchers attempt to predict complex, irregular access patterns [4, 18, 19, 20, 21, 22, 6]. While these methods show significant benefit, they are

inherently reactive, waiting until a cache miss occurs before they initiate prefetches down the speculated path.

Some recent prior work has examined the case of prefetching in specialized multi-threaded environments. In particular Lee *et al* examine prefetching mechanisms for GPGPUs [23] and Izraelevitz *et al* discuss how a policy of "always-abort" can improve performance for hardware transactional memory [24]. While these a works have a similar intent to the work presented here the specialized domains of GPUs and HTM respectively make their solutions hard to generalize to traditional shared memory CPUs.

#### 2.2 Cache Compression

Cache compression has the potential to increase the effective capacity of the cache with extra area overhead [25]. Compressed caches can achieve the benefits of larger caches without making the cache physically larger by keeping more cache lines in the same cache space. Designing a compressed cache includes a compression algorithm and compressed cache layout. The compression algorithm represents a cache block with fewer bits, while a compaction mechanism determines how to read/write a compressed cache block to the cache [26, 27, 28, 29, 30].

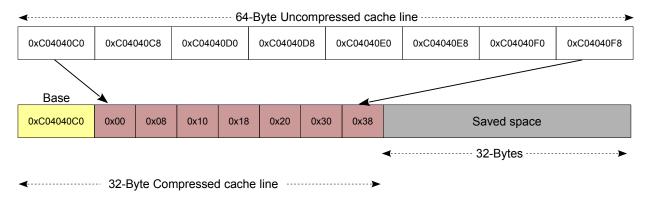

Zero-value algorithms are limited to zero cache lines with low latency. Zero-Content Augmented cache design uses auxiliary cache to represent zero cache lines [31]. Frequent Value Compression (FVC) encodes frequent values present in cache lines with fewer bits [29, 28]. The downside of FVC, it only compress frequent values and cannot exploit other commonly found patterns [29, 28, 26]. Pattern-Based Compression [32, 33, 3] exploits the fact that many values are narrow (e.g., small integers) and can be represented using a small number (e.g., 4-8) of bits, but are normally stored in full 32-bit or 64-bit words. Base-Delta-Immediate (BDI) compression exploits spatial value locality, i.e., the observation that values that are spatially close in memory also tend to have small differences in their values [26]. BDI represents a block using one or more base values and an array of differences from the base values [26].

Typical cache stores one tag address to track a fixed-size cache block. The corresponding tag is used to perform hit detect for the cache block. In order to track more blocks, compressed caches are required to store more tags, which result in more area, power. Simple cache design double the number of tags (i.e., 2x Block Tags), allowing them to track up to twice as many cache blocks in the cache [32]. Decoupled Compressed Cache (DCC) [21, 22] and Skewed Compressed Cache (SCC) [25, 34] use more complex designs to reduce the number of extra tags, by exploiting spatial locality and use super-block tags to track more blocks and reduce the extra tag overhead.

#### 2.3 Load Criticality

Cache optimization techniques such as data prefetching and cache compression cache have an impressive impact on performance and effectively minimize the impact of the performance gap between the execution core and memory subsystem. Even though the processor is still exposed to the memory wall on a cache miss due to hard to prefetch loads. Modern Out-of-Order microprocessors employ large instruction queue to exploit instruction-level parallelism. Program criticality can be described using a data-dependency graph; there exists one or more paths through the graph with a maximum length; such a path is called a critical path [35]. Instruction along that path called criticality instructions. A critical load is a load instruction that is on the critical path. Due to variable latency when executing load instruction based on the cache level that is responsible to source the target data, non critical load instructions have a big impact on the execution time when cache misses take place. In a system with data prefetcher, these loads expose the processor to long latency because they hard-to-prefetch.

# 3. SYNCHRONIZATION-AWARE HARDWARE PREFETCHING FOR CHIP MULTIPROCESSORS \*

Shared-memory, multi-threaded applications often require programmers to insert thread synchronization primitives (*i.e.* locks, barriers, and condition variables) in critical sections to synchronize data access between processes. Scaling performance requires balanced perthread workloads with little time spent in critical sections. In practice, however, threads often waste time waiting to acquire locks/barriers, leading to thread imbalance and poor performance scaling. Moreover, critical sections often stall data prefetchers that mitigate the effects of waiting by ensuring data is preloaded in core caches when the critical section is done.

This chapter introduces a pure hardware technique to enable safe data prefetching beyond synchronization points in chip multiprocessors (CMPs). We show that successful prefetching beyond synchronization points requires overcoming two significant challenges in existing techniques. First, typical prefetchers are designed to trigger prefetches based on current misses. Unlike cores in single-threaded applications, a multi-threaded core stall on a synchronization point does not produce new references to trigger a prefetcher. Second, even if a prefetch were correctly directed to read beyond a synchronization point, it will likely prefetch shared data from another core before this data has been written. This prefetch would be considered "accurate" but highly undesirable because it would lead to three extra "ping-pong" movements due to coherence, costing more latency and energy than without prefetching. We develop a new data prefetcher, Synchronization-aware B-Fetch (SB-Fetch), built as an extension to a previous single-threaded data prefetcher. SB-Fetch addresses both issues for shared memory multi-threaded workloads. The novelty in SB-Fetch is that it explicitly issues prefetches for data beyond synchronization points and it distinguishes between data likely

<sup>\*</sup>Reprinted with permission from "SB-Fetch: Synchronization aware hardware prefetching for chip multiprocessors" by L. M. AlBarakat, P. V. Gratz, and D. A. Jimenez 2020. Proceedings of the 34th ACM International Conference on Supercomputing, Copyright 2020 by Association for Computing Machinery.

and unlikely to incur cache coherence overhead. These two features are directly synergistic since blindly prefetching beyond synchronization is likely to incur coherence penalties. No prior work includes both features.

SB-Fetch is evaluated using a representative set of benchmarks from Parsec [36], Rodinia [37], and Parboil [38]. SB-Fetch improves execution time by 12.3% over baseline and 4% over best of class prefetching.

#### 3.1 Introduction

The scaling of computer systems through the final CMOS process technology generations poses a grand challenge for the computing industry. Despite increasing transistor density, performance and power gains that traditionally accompanied process scaling have largely ceased. This trend has manifested in the current proliferation of chip-multiprocessors (CMPs) replacing single core processors as the dominant processor design, due to their lower power consumption for similar performance, however, blithely scaling core counts with future process technologies will quickly lead to diminishing returns, particularly for shared-memory, multi-threaded applications. In these applications, core and thread-count scaling often leads to performance destroying workload imbalances [39, 40]. One of the major causes of these thread-level workload imbalances, as well as degrading performance in general, is memory latency.

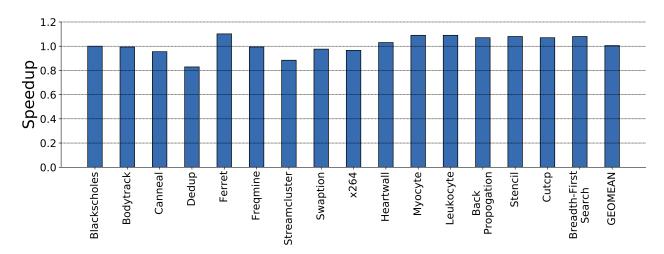

Prefetching is a well-studied technique to reduce the impact of memory latency. Prior work has shown that prefetching produces substantial performance gains on typical single-threaded and multi-application workloads [4, 41, 13, 22]. Unfortunately, multi-threaded applications typically see little to no performance benefit from existing prefetching schemes. Figure 3.1 shows the speedup of multi-threaded applications under a previously proposed prefetching scheme [12, 13]. The figure shows that, at best, the performance improvement of the previous scheme is marginally positive, and at worst performance is significantly degraded despite evidence that several are memory bound [40, 36]<sup>2</sup>. There are two main

<sup>&</sup>lt;sup>2</sup>On single-threaded, multi-programmed workloads, B-Fetch sees an average gain of 31%[13].

Figure 3.1: Speedup of Parsec [36], Rodinia [37], and Parboil [38] workloads with B-Fetch [12, 13], normalized against a no-prefetching baseline.

reasons for the poor performance of traditional prefetching techniques on these workloads: First, most prefetchers only issue a prefetch when a cache miss occurs in that core. In multi-threaded applications, the ideal time to pre-load the cache is while a given thread is waiting on thread synchronization. This represents a significant wasted opportunity because thread synchronization primitives contain no (relevant) cache misses.

Second, for those few prefetchers that issue prefetches without a triggering miss (e.g. B-Fetch [12, 13]), prefetching shared data, even with perfect accuracy, might incur excess invalidations in the event that the prefetched data is read before it is written in the producing core. This is the primary cause of B-Fetch's performance loss in the figure. No prior work we are aware of has identified and addressed these two issues in prefetching for multi-threaded applications.

Here, we present Synchronization-aware B-Fetch (SB-Fetch), a data prefetching scheme designed for prefetching shared-memory, multi-threaded workloads. This work makes the following contributions:

• This is the first work we are aware of to characterize the causes of poor prefetching performance in shared-memory multi-threaded applications. These are the inability to prefetch beyond synchronization points and tendency to prefetch shared data before it has been written.

- Building upon this characterization, we propose SB-Fetch, a low-complexity, low-overhead prefetcher design that addresses both issues.

- We show that SB-Fetch provides a speedup of 12.3% over baseline and 4% over best of class prefetching [4, 21].

#### 3.2 Motivation and Background

#### 3.2.1 Data Prefetching

Data prefetching is a well known technique in which the cache is pre-filled with useful data ahead of an actual demand load request coming from the processor. Typically, the prefetching opportunity is limited to waiting until a cache miss occurs, and then reading either a set of lines sequentially following the current miss [16], a set of lines following a strided pattern with respect to the current miss [17], or a set of blocks spatially around the miss [4]. More recent prefetchers attempt to predict complex, irregular access patterns [4, 18, 19, 20, 21, 22]. While these methods show significant benefit, they are inherently reactive, waiting until a cache miss occurs before they initiate prefetches down the speculated path.

Some prefetchers, such as B-Fetch [12, 13], are triggered by the fetch of a branch instruction by the processor, making them more suitable for prefetching beyond synchronization points as we will discuss. B-Fetch is a data cache prefetcher that employs two speculative components. It speculates on the expected path through future basic blocks, using a lookahead mechanism that relies on branch prediction to predict that execution path, and a scheme to predict the effective addresses of load instructions along that path based on the register file transformations per-basic block. B-Fetch records the variation of register contents at earlier branch instructions and uses this knowledge to predict the effective address.

Some recent prior work has examined the case of prefetching in specialized multi-threaded environments. In particular Lee *et al* examine prefetching mechanisms for GPGPUs [23] and Izraelevitz *et al* discuss how a policy of "always-abort" can improve performance for hardware

transactional memory [24]. While these a works have a similar intent to the work presented here the specialized domains of GPUs and HTM respectively make their solutions hard to generalize to traditional shared memory CPUs.

#### 3.2.1.1 B-Fetch Microarchitecture

Since B-Fetch is one of the few prefetchers that explicitly speculates down a future path of execution and that does not wait for a memory reference to miss before it starts prefetching, we will use it as a basis for the work in this chapter. Thus we here present a recap of the B-Fetch microarchitecture as originally published [13, 12].

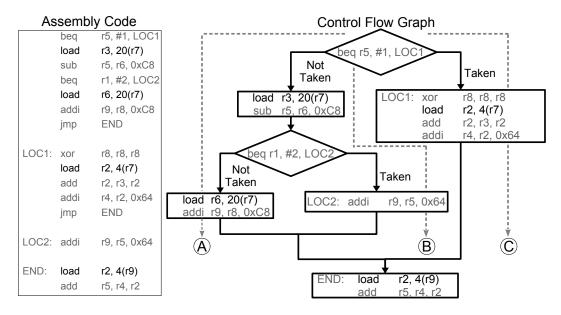

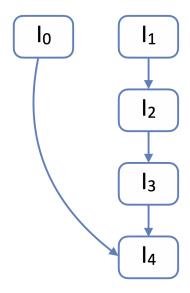

Program construction can be mapped into a control flow graph as shown in Figure 3.2. As shown in the figure, the outcome of each branch determines which basic blocks will ultimately be executed. In the figure, there are three possible such paths, highlighted as (A), (B) and (C). In each case, which loads are issued is directly dependent upon the path taken through the code as shown. Further, the particular effective addresses themselves are dependent upon the path taken through the code, as each basic block causes transformations to the data in the register file as execution continues.

Figure 3.2: Data Access and Control Flow.

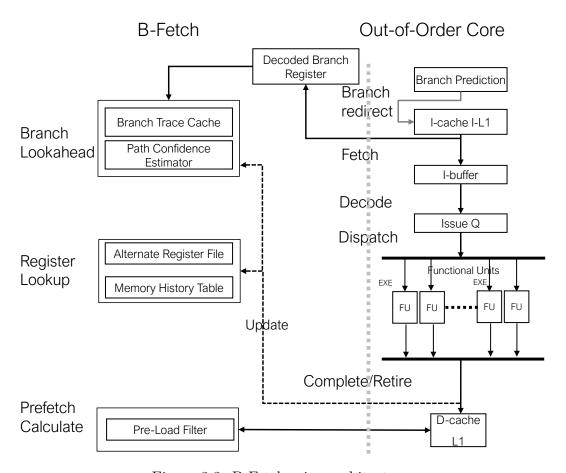

B-Fetch uses a lookahead mechanism that predicts the likely path of execution starting from the current non-speculative branch and issues prefetches for the memory references down that path. B-Fetch relies on the idea that register values at the time of effective address generation are correlated in a predictable way from their corresponding values at a time when their preceding branch instructions were executed and the transformations that occur to them over the course of the blocks to that point. Figure 3.3 shows the overall system architecture of a B-Fetch together with an out-of-order processor core. It shows the main core execution pipeline and the auxiliary hardware for B-Fetch preftecher.

Figure 3.3: B-Fetch microarchitecture.

B-Fetch is composed of a 3-stage pipeline that runs parallel to the core pipeline. The

Decoded Branch Register (DBR) connects B-Fetch to the cores's Fetch stage. When a branch instruction is decoded in the main execution pipeline, the PC of the branch instruction is added to the DBR. This branch PC and target address starts the prediction of the future execution path, memory instructions, and their effective addresses.

Here we describe each of the major microarchitectural components of B-Fetch and their purpose.

Branch Lookahead Stage: This stage is similar to the fetch stage in the main pipeline. The duty of this stage is to generate the speculative exception path from the currently decoded branch. This stage includes two main components. First, the *Branch Trace Cache* that traces the branch instructions in the dynamic instruction stream. This is used to create set of pointers in the program control flow marked by branch instructions, allowing the prefetcher to skip the branch instructions in between. By doing so, the branch trace cache help guide the lookahead stage forward and the branch predictor and target buffer to help maneuver it in the right direction. The second component is *Path Confidence Estimator* that is used to throttle speculation in the event that the cumulative branch predictions to this point are not confident. This component prevents the issuing of useless prefetches and cache pollution.

Register Lookup Stage: This stage retains information about the registers which produce loads in each basic block to generate effective addresses for the given block. This stage includes two main components. First, the Alternate Register File (ARF) maintains a copy of the register file contents for use in generating predicted prefetch effective addresses. To ensure timely updates to the ARF, a copy of execution stage generated register values is used to perform updates. The second component is the Memory History Table (MHT) that maintains source register indices, current register values, and offset values to calculate effective addresses for prefetch candidates.

**Prefetch Calculate Stage:** This stage is responsible for generating the prefetch addresses that are issued to the prefetch queue. It synthesizes the data from the MHT and ARF to

produce a stream of predicted future memory references. This stream is then passed through the *pre-load filter* that keeps track of the issued but useless prefetches on a per-load basis. Loads found to typically produce useless prefetches are prohibited from producing a prefetch.

We note that it is beyond the scope of the current work to discuss the full details of the previously published B-Fetch microarchitecture, for that we point the reader towards the prior work [13, 12]. That said, we would like to point out that B-Fetch requires relatively little state (~12KB) and relatively low hardware complexity (a handful of tables and some adders) to achieve accurate and high coverage on traditional workloads. Importantly, unlike other prefetching techniques, B-Fetch provides a direct mechanism for speculating upon the future path of the program and leveraging that speculation to issue prefetches, without the overhead of running the full core ahead, as in runahead execution [9]. Thus, we feel that B-Fetch makes an ideal starting point for attempting to efficiently issue prefetches beyond synchronization points.

#### 3.2.2 The Shared Memory Model

With growing core counts, fully exploiting the underlying microarchitecture and achieving scaling performance of single applications requires dividing that application into independent threads that can run simultaneously across the cores within a system and take advantage of thread-level parallelism (TLP). The dominant programming model for this form of TLP is shared memory multi-threading. In this programming model, an application is broken into independent threads that share a single, coherent view of memory. Typically, these independent threads share some data to complete the task. In this model, programmers insert explicit thread synchronization primitives (*i.e.* locks, barriers, and condition variables) to coordinate data sharing between threads, ensuring that data produced by one thread is not read by a consuming thread before it is written and so forth.

### 3.2.2.1 Shared Memory Synchronization

Synchronization is a central operation in parallel applications. The two major forms of explicit synchronization operations in shared memory multiprocessors are barriers and locks. A barrier used to ensure no process within a group cooperating processes can move beyond a certain point in the execution before all processes have reached the barrier. Barriers are commonly used to enforce such waiting.

Figure 3.4a illustrates how a barrier works. A task executes its code until it reaches a barrier. Then it waits until all other tasks have reached that barrier before proceeding. Ideally, all tasks start at the same time and reach the barrier at the same time, then start new phase of execution.

Figure 3.4: Ideal barrier synchronizes and critical threads in the execution phases.

A thread is critical if its progress determines the progress of the whole application and

forces other threads to wait for it. Due to load imbalance between threads, different threads can be critical during execution. As Figure 3.4b shows other threads need to wait untill the critical thread get to the barrier before resume execution. A synchronization barrier can lead to performance degradation. The slowest thread prevents forward progress of other threads and forces other threads to wait on the barrier. The performance of synchronization barriers in shared memory is often unpredictable and a performance bottleneck.

#### 3.2.2.2 Architectural Support for Shared Memory Synchronization

To facilitate the construction of synchronization primitives, most architectures provide some form of read-modify-write instructions that are capable of updating (*i.e.*, reading and writing) a memory location as an atomic operation. For example, RISC style ISAs, such as Arm and ALPHA, support Load Linked (LL) and Store Conditional (SC) instructions to implement synchronization primitives [42, 43]. In this scheme, the LL instruction loads a block of data into the cache and marks this cache line for tracking. The following SC instruction attempts to write a new value to the same block. This write succeeds only if the block has not been referenced since the preceding LL. Any memory reference to the block from another processor between the LL and SC pair causes the SC to fail. Upon failure, the locking thread will typically retry the full LL/SC pair until atomic read/modify/write success is achieved.

For a thread to acquire the lock, it needs to load the lock and check if no other thread is holding the lock. After that it needs to own the lock. If the thread fails to acquire the lock, it will stay in a spin loop until it successfully acquires it. Once a thread acquires the lock it is safe to execute the critical section. Upon entering the critical section, only then is it "safe" to write or update data shared between threads because only one thread may enter the critical section to modify that data at any given time. Once this shared data is written, the thread then releases the lock to allow other threads to execute the critical section, and modify the shared data as well. Acquiring and releasing a lock involves executing primitive instructions.

We note that CISC ISAs typically employ single read/modify/write atomic instructions that produce similar behavior in implementing shared memory synchronization semantics. For the purpose of discussion we focus on the LL/SC but our approach can be easily applied to CISC ISAs. In Section 3.3.2 we briefly discus the changes required to support CISC ISAs.

## 3.2.3 Cache Coherence

Cache coherence is the hardware mechanism by which shared data in different cores' private caches are kept coherent. Many coherence schemes have been proposed [44, 45, 46, 47, 48, 49]. One commonly used approach is a directory based cache coherence scheme. In this scheme, a directory, typically co-located with the shared, last-level cache, maintains the sharing state of all the cache lines in the individual cores' private caches. In such a scheme, when a core issues a request to acquire or change the state of a cache line in its private cache it must send a message to the directory. The directory then may need to send messages to the other cores' private caches, waiting for their acknowledgment before finally replying back to the requesting core. This transaction incurs a significant latency [50, 51, 52, 53].

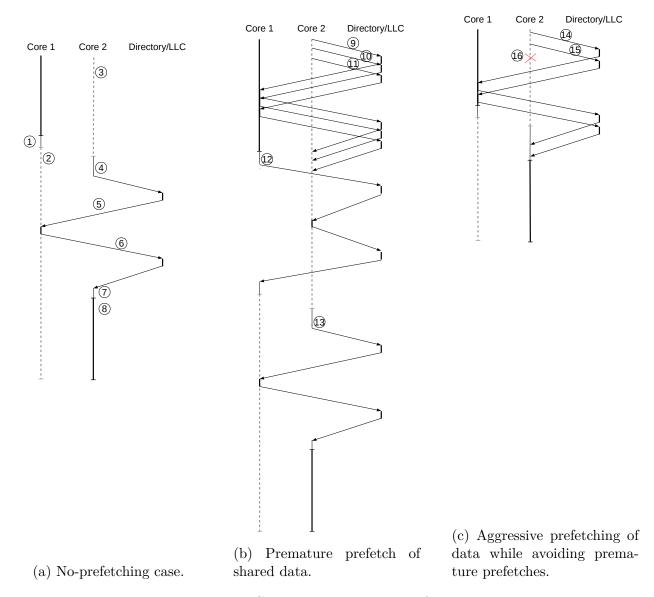

Figure 3.5a illustrates the typical case for the sharing of data in a cache coherent shared memory system. The figure shows two threads communicating through shared data, synchronized by a lock. In the figure, core 1 first enters its critical section (①). In this case the cache line containing the shared data with the lock variable happens to be in the local private cache and the critical section finishes quickly. Note that, at ② and beyond, the cache line containing the lock variable will remain in the private cache of core 1, while core 2 executes, prior to its critical section. Here, at ③, core 2 is spinning, waiting for the write of this shared data. Once core 1 has completed its critical section, core 2 is free to enter the critical section and access the data in question. Since this data is on a cache line in core 1's private cache, a request is made to the directory for a shared copy, ④. At ⑤, this request leads to a writeback request to core 1. At ⑥, core 1's private cache issues a writeback to the LLC of the line containing the shared data. Finally, at ⑦, this line is then forwarded to core 2 and core 2's critical section can proceed (⑧). All of this back and forth between

the caches, directory and LLC, can incur hundreds of cycles of overhead at exactly the most critical time in the execution of a multi-threaded application.

Figure 3.5: Cache coherence and prefetching.

#### 3.2.3.1 Prefetching in Multithreaded Workloads

Multithreaded applications are just as likely to experience lost performance due to longlatency memory accesses as traditional, single threaded applications. Thus, prefetching should be a good way to improve performance. As discussed in the previous section, prefetching for multi-threaded applications produces unique challenges, in that threads waiting on synchronization typically do not induce prefetches for data beyond those synchronization points. Moreover, reckless prefetching of data beyond synchronization points could hurt performance due to premature prefetching of shared data before it has been written.

In the first case, where prefetching does not occur past synchronization points, there is a great lost opportunity for performance gain. As we see in Figure 3.5a, at point ③, core 2 is effectively idle waiting for core 1 to finish its critical section. If prefetching of data that core 2 will need after this synchronization point could be performed, it would be a great opportunity to leverage available, unused memory bandwidth in core 2. However, if core 2 is overly aggressive and prefetches shared data before it is written, the performance impact could be greater than the benefit of correct, on-time prefetches.

Figure 3.5b illustrates the danger of overly aggressive prefetching in this case. Here again, at the beginning of execution, the cache line containing shared data to be written by core 1 is currently residing in core 1's private cache, along with several other cache blocks that core 2 will need, but will not be written in core 1's critical section. At the beginning of the trace, while core 2 is idling, the prefetcher in core 2's private caches issues three prefetches, (9)-(11). While two of these prefetches, (9) and (10), are to data that ultimately will not be re-written in core 1, one prefetch, (11), has not yet seen its final write in core 1. Later, core 1 enters its critical section to write shared data to one of the cache line that was already prefetched (at (11)), inducing another coherence transaction at (12) to retrieve ownership of the shared cache line core 2 just prefetched. Once the cache line has been retrieved from core 2, core 1 can safely write the new data and release its lock, at which point core 2 can enter the critical section, (13), and attempt to read the shared data core 1 just wrote. This incurs yet another

coherence transaction pulling this data back to core 2 again. As the figure illustrates, here prefetching actually incurs a large negative performance impact versus a baseline case where prefetching does not occur.

This resultant cache block transitioning back and forth between the cores due to overly aggressive prefetching has a much worse impact on multi-threaded applications than traditional single-threaded applications. In particular, while the impact of a bad prefetch on a single threaded application implies some wasted bandwidth, energy and some cache pollution; in multi-threaded applications, this extra latency often occurs exactly when the threads in question are literally "critical" to performance, in that they are the only threads executing during a mutex in their critical sections. Slowing down these critical sections has a significantly outsized influence on application performance. We empirically determined that these extra writebacks and invalidations account for the performance loss shown for several benchmarks using B-Fetch in Figure 3.1.

As shown in Figure 3.5c, ideally, one would like the idle cores to aggressively prefetch data while spinning on a lock, leveraging the available time and bandwidth, and yet avoid prefetching specifically only that data that will eventually be written by other cores. In the figure we see that the two useful prefetches, 14 and 15 are allowed to proceed while prefetch 16 is squashed before issuing because 16 is predicted to be invalidated by a future write in core 1. As we see, accurate prefetching beyond synchronization primatives can lead to significant performance increases while preventing performance regression due to premature prefetching. This is the goal of SB-Fetch.

Prior works address prefetching for multi-threaded workloads. Jerger et al., [54] presents a taxonomy that classifies the effects of multiprocessor prefetches. While this work suggests invalidation filtering schemes could improve performance, it provides no practical mechanism for such a scheme, nor does it discuss explicitly prefetching beyond synchronization points as SB-Fetch does. They show that, without explicitly prefetching beyond synchronization points, the benefit of invalidation filtering is marginal. Liu et al., [55] and Panda et al., [56]

both present schemes that attempt to tune prefetch aggressiveness depending upon the criticality of the thread (among other things). This interesting approach is somewhat orthogonal to SB-Fetch and likely could be used in combination with SB-Fetch. Preliminary work by Panda et.al, [57] proposes a hardware prefetching framework that studies and classifies L1 misses across all threads to generate L2 cache prefetches. In our preliminary work [58], we initially examined the feasibility of prefetching for multithreaded workloads. Here we expand upon this prior work.

#### 3.3 Proposed Design

SB-Fetch addresses the two issues with prefetching for multi-threaded workloads. It must continue prefetching beyond the synchronization semantic while the thread itself is busy waiting. It must also avoid issuing prefetches for shared data before it has been written.

The insight behind SB-Fetch is to use the decode stage in the actual processor pipeline to dynamically track the synchronization primitives and identify when a thread is spinning on a lock. For a thread to acquire a lock, it must load the lock and check that no other thread is currently holding the lock. Then it must own the lock. If the thread fails in acquiring the lock, it will stay in a spin loop until it successfully acquires it. Once a thread acquires the lock it is safe to execute the critical section. The thread needs to release the lock to allow other threads to execute the critical section as well. Acquiring and releasing a lock involves executing the synchronization primitive instructions LL and SC described in Section 4.1.

#### 3.3.1 Overview

SB-Fetch is an extension to the prior work B-Fetch prefetcher described in Section 3.2. To address prefetching beyond synchronization points, we must detect when a thread is trying to acquire and release a lock in the instruction stream, then feed the first branch instruction after releasing the lock to the B-Fetch engine to start prefetching. To this end, SB-Fetch monitors the synchronization primitive instructions, LL/SC, in the dynamic instruction stream. The prefetcher identifies when a thread is spin waiting by the decoding of LL instructions. It

then learns the backward branches following the LL instruction that are part of the spin once the LL/SC pair are successful and records these. Later, when this synchronization point is encountered again, the prefetcher will ignore the "correct" backward branch prediction to skip ahead of the synchronization point, allowing prefetch to continue in the region beyond the critical section.

To solve the second issue, prefetch invalidation due to premature prefetching, SB-Fetch keeps track of prefetches that are invalidated via the cache coherence mechanism prior to their use. This information is used to filter these "unsafe" prefetches, prohibiting them from being prefetched in the future.

Figure 3.6 illustrates the overall system architecture of a system incorporating *B-Fetch* together with the additional components needed to implement SB-Fetch. The figure shows the main CPU execution pipeline and the additional hardware for the *B-Fetch* prefetcher. We note that, in code that does not have synchronization, SB-Fetch will perform identically to B-Fetch, already one of the top performing prefetchers for single-threaded code [13, 12].

#### 3.3.2 System Components

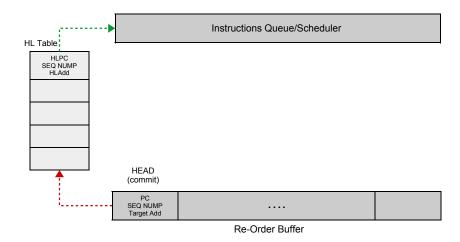

As previously described, Figure 3.6 shows the *SB-Fetch* microarchitecture. In particular two components, the Synchronization Primitives Trace Cache (SPTC) and Invalidation Filter are added to the original B-Fetch microarchitecture. Here we describe each.

Synchronization Primitives Trace Cache (SPTC): The SPTC dynamically captures the atomic primitives that were used to implement synchronization semantics. Each entry acts as a state machine to indicate the beginning and ending of each critical section encountered. Here, an LL instruction followed by a SC to the same effective address, indicates the beginning of a critical section. Once a second SC is detected, it indicates the end of a critical section. In SB-Fetch, the SPTC receives information from the decode stage in the Out-of-Order pipeline. Figure 3.7 shows an entry in SPTC. Each entry in the SPTC includes the lower 32 bits of the effective address and 2 state bits. An entry is installed in SPTC on the beginning of a critical section, then the entry becomes valid once a second SC is

Figure 3.6: SB-Fetch microarchitecture. Additional components beyond B-Fetch highlighted in green.

detected, which indicates the end of the critical section. Then the first branch address after the critical section will be passed to branch lookahead component of the B-Fetch pipeline, so B-Fetch can predict the execution path starting from the current branch in order to prefetch data in the next basic block after the end of the synchronization semantic. The structures in B-Fetch/SB-Fetch pipeline are squashed and updated on commits.

Figure 3.7: Single Synchronization Primitives Trace Cache (SPTC) entry.

We note, as the SPTC is a multi-entry cache, it is possible to track many synchronization primitives at once, thus complex, multi-lock synchronization structures can be easily handled by this structure. We also note that while the above discussion revolves around the semantics of LL/SC based synchronization, it would be actually somewhat easier to adapt the proposed mechanism to CISC ISAs that contain atomic read/modify/write mechanisms. In particular, instead of requiring monitoring for the sequence of an LL instruction followed by an SC, SB-Fetch would only need to monitor for the single atomic read/modify/write instruction itself.

Invalidation Filter: To prevent useless prefetches wasting time, bandwidth and energy, it is crucial to reduce the number of invalidations of data prefetched but never used in the local core. The Invalidation Filter tracks data recently prefetched from another core's private caches. In the event that a cache line prefetched from another core is invalidated prior to its use by the local core, the filter notes the associated load that caused the prefetch. Future prefetches associated with that load in that basic block will be dropped before issuing under the assumption that this load is likely to lead to a premature prefetch.

The invalidation filter consists of a table that keeps track of the prefetched cache block that was invalidated by the coherence protocol. The invalidation filter is indexed by a 10-bit hash of the load PC for the prefetch address. The invalidation filter has precedence over the branch confidence and per-load filter. That is, regardless of current branch confidence and per-load confidence, if a prefetch results in invalidation, we stop prefetching for the load PC that prefetch is predicted for.

The Invalidation filter by default will never un-learn that a given location is unsafe for prefetching. To allow for more adaptive behavior, we employ a simple, counter-based, random clear mechanism. The counter counts cycles up to a definable maximum,  $C_m$ . When this maximum is reached a single entry in the table is chosen to be cleared. Thus, the entire table is cleared every  $C_m * k$  cycles where k is the size of the table.

#### 3.3.3 Hardware Cost

The additional hardware storage requirements for SB-Fetch, B-Fetch, BOP and SMS are summarized in Table 3.1. Two additional components have been added to B-Fetch. In term of hardware budget Synchronization Primitives Trace Cache (SPTC) is 0.53125KB and the Invalidation Filter is 4.0KB. To optimize the performance of SMS, we used the configuration

Table 3.1: Hardware storage overhead in KB

| Prefetcher | Component                 | # Entries | Size (KB) |

|------------|---------------------------|-----------|-----------|

|            | Branch Trace Cache        | 256       | 2.06      |

|            | Memory History Table      | 128       | 4.5       |

|            | Alternate Register File   | 32        | 0.156     |

| B-Fetch    | Per-Load Prefetch Filter  | 2048      | 2.25      |

| D-retch    | Additional Cache bits     | -         | 1.37      |

|            | Prefetch Queue            | 100       | 0.51      |

|            | Path Confidence Estimator | 2048      | 2         |

|            | TOTAL SIZE :              |           | 12.84     |

| SB-Fetch   | B-Fetch                   | _         | 12.84     |

|            | Primitives Trace Cache    | 128       | 0.53      |

|            | Invalidation Filter       | 1024      | 4         |

|            | TOTAL SIZE :              |           | 17.37     |

| ВОР        | Recent Requests Table     | 256       | 6         |

|            | Additional Cache bits     | -         | 4         |

|            | BO prefetcher state       | -         | 0.8       |

|            | TOTAL SIZE: 10.8          |           | 10.8      |

| SMS        | Active Generation Table   | 64        | 0.57      |

|            | Pattern History Table     | 16k       | 36        |

|            | TOTAL SIZE :              |           | 36.57     |

used by Somogyi, et al. [41] and 2KB spatial regions, a 64-entry accumulation table, and a 16K-entry pattern history table. Thus, SB-Fetch incurs a small, 4.53125KB overhead over B-Fetch, which is still significantly less hardware state than SMS requires.

### 3.4 Evaluation

# 3.4.1 Methodology

We used gem5 [59], a cycle accurate simulator, to evaluate SB-Fetch. The baseline configuration is summarized in Table 3.2. We used a set of nine multi-threaded programs from PARSEC benchmark suite [60], four applications from the Rodinia benchmark suite [37], and three benchmarks from the Parboil benchmark suite [38]. These benchmark applications represent widely used shared memory applications that use the P-threads library to handle synchronization. The benchmark applications are cross-compiled for the ALPHA ISA and run on gem5 configured with the O3CPU CPU model (Out-of-Order) and the detailed

(classic) memory model. The benchmarks were run in Full System (FS) mode.

The baseline hardware is a 4-core CMP machine with three level cache hierarchy as specified in Table 3.2. Each core's private cache is split into I-cache (32KB) and D-cache(32KB), 256KB second level cache and 1024KB per core third level shared cache.

Table 3.2: Target Microarchitecture Parameters

| Simulator       | Gem5 Simulator, ALPHA ISA, Full System Simulation |

|-----------------|---------------------------------------------------|

| Architecture    | O3 processor, 4-wide, 192-entry ROB               |

| ICache / DCache | 32KB, 8-way set-associative                       |

| L2Cache         | 256KB, 8-way set-associative                      |

| Shared L3Cache  | 1024KB per core, 16-way set-associative           |

| Memory          | DDR3-1600 x64 channel, Micron MT41J512M8          |

SB-Fetch results are compared against four light-weight prefetcher designs: Stride, SMS, BOP and the original B-Fetch. In the cases of SMS and BOP, the code for these prefetchers as well as their configuration was directly adapted from their respective submissions to the First [61], and Second [62] Data Prefetching Competitions. We note that BOP was the winner of the Second Data Prefetching competition. The Stride prefetcher was configured as in prior work [13].

#### 3.4.2 Results

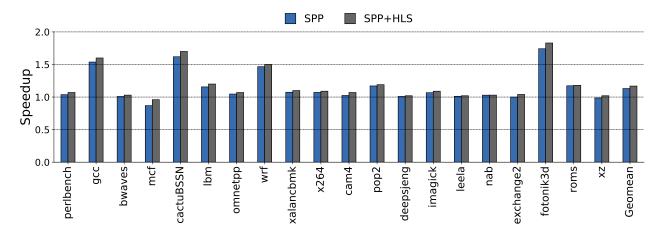

### 3.4.2.1 Performance

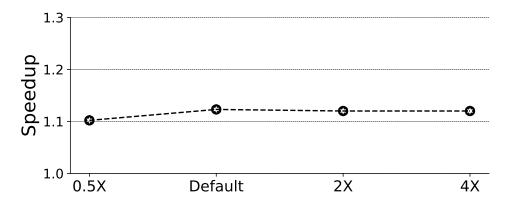

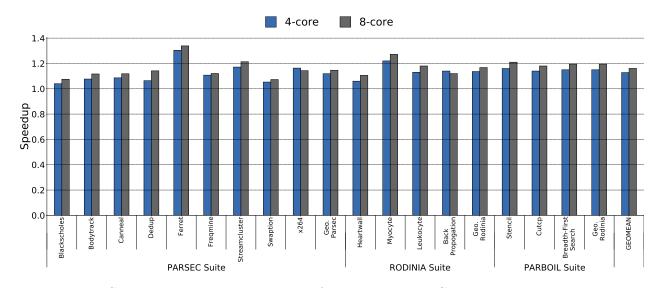

Figure 3.8 shows the performance of each of the five prefetcher designs as the speedup compared to the baseline no-prefetching configuration. For all results, the execution time is the time spent in the region of interest (ROI). In the figure we see that SB-Fetch provides a significant performance increase across all benchmarks of 12.3% versus the baseline, beating the performance of the closest competitor, BOP 8.1%. Moreover, where the original B-Fetch showed performance regressions versus a non-prefetching baseline, SB-Fetch improves performance for every benchmark. Interestingly, SB-Fetch sees some of its biggest performance

gains for applications where the original B-Fetch saw significant performance losses. Given the speedup and the cost of storage overhead together, SB-Fetch presents a better solution for data prefetching in multi-threaded workloads. We also see that for each suite individually, SB-Fetch outperforms each of the competing techniques, largely by similar margins. This highlights the robustness of SB-Fetch's gains.

Figure 3.8: Multi-threaded workload speedups.