#### University of Arkansas, Fayetteville

## ScholarWorks@UARK

Theses and Dissertations

12-2020

## Developing A Medium-Voltage Three-Phase Current Compensator **Using Modular Switching Positions**

Vinson Jones University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### Citation

Jones, V. (2020). Developing A Medium-Voltage Three-Phase Current Compensator Using Modular Switching Positions. Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/3941

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

# Developing A Medium-Voltage Three-Phase Current Compensator Using Modular Switching Positions

## A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Vinson Jones University of Arkansas Bachelor of Science in Electrical Engineering, 2014 University of Arkansas Masters of Science in Electrical Engineering, 2016

## December 2020 University of Arkansas

| This dissertation is approved for reco         | mmendation to the Graduate Council. |  |

|------------------------------------------------|-------------------------------------|--|

| Juan Carlos Balda, Ph.D. Dissertation Director |                                     |  |

| Alan Mantooth, Ph.D. Committee Member          | Roy McCann, Ph.D. Committee Member  |  |

| David Andrews, Ph.D.                           |                                     |  |

#### **ABSTRACT**

The objective of this thesis is to present the context, application, theory, design, construction, and testing of a proposed solution to unbalanced current loading on three-phase four-wire systems. This solution, known as the Medium-Voltage Unbalanced Current Static Compensator or MV-UCSC, is designed to recirculate currents between the three phases of a distribution system. Through this redistribution of the currents negative- and zero-sequence current components are eliminated and a balanced load is seen upstream from the point of installation. The MV-UCSC as it operates in the distribution system is presented followed by its effect on traditional compensation equipment. The construction of the MV-UCSC as well as 13.8 kV simulations are then shown. Development of the switching positions required by the MV-UCSC is then given followed by a variation on this switching position with the intent to reduce part count. Finally, the testing the 13.8 kV three-phase four-wire, neutral-point-clamped, elevenlevel, flying-capacitor-based MV-UCSC connected directly to the grid is presented.

### **ACKNOWLEDGEMENTS**

Thank you to Dr. Balda for the opportunity to further my knowledge in Electrical Engineering as well as the support and advice on this project. And to all of my colleagues for their help along the way.

I would also like to thank the staff at NCREPT. The support provided by Chris Farnell and Justin Jackson was indispensable to this project and thus, my sanity.

## **TABLE OF CONTENTS**

## CHAPTER 1

| INTRODUCT | TION                                                                    | 1   |

|-----------|-------------------------------------------------------------------------|-----|

| 1.1       | Unbalanced Currents in Distribution Systems: The Problem and Motivation | n 1 |

| 1.2       | Existing Current Compensation Solutions                                 | 2   |

| 1.2.1     | Passive Solutions                                                       | 2   |

| 1.2.2     | Active Solutions                                                        | 3   |

| 1.3       | Challenges of Multilevel Converters                                     | 8   |

| 1.4       | Proposed Solution for Unbalanced Current Static Compensation            | 10  |

| 1.5       | Objectives of the Dissertation                                          | 12  |

| 1.6       | Organization of the Dissertation                                        | 12  |

| 1.7       | Major Contributions of this Research                                    | 13  |

| 1.8       | References                                                              | 14  |

| CHAPTER 2 |                                                                         |     |

| CURRENT C | OMPENSATORS FOR UNBALANCED ELECTRIC DISTRIBUTION                        |     |

| SYSTEMS   |                                                                         | 20  |

| 2.1       | Abstract                                                                | 20  |

| 2.2       | Introduction                                                            | 20  |

| 2.3       | Primary Applications of a Shunt Compensator                             | 22  |

| 2.3.1     | Current Balancing                                                       | 23  |

| 2.3.2     | Power Factor Regulation                                                 | 24  |

| 2.3.3     | Harmonic Compensation                                                   | 25  |

| 2.4       | Secondary Applications of a Shunt Compensator                           | 25  |

| 2.4.1      | Complements Load Redistribution Practices    | 26 |

|------------|----------------------------------------------|----|

| 2.4.2      | Inter-feeder Current Sharing                 |    |

| 2.4.3      | Microgrid Augmentation                       | 27 |

| 2.4.4      | Compact Installation                         | 28 |

| 2.4.5      | Energy Storage and Delivery                  | 28 |

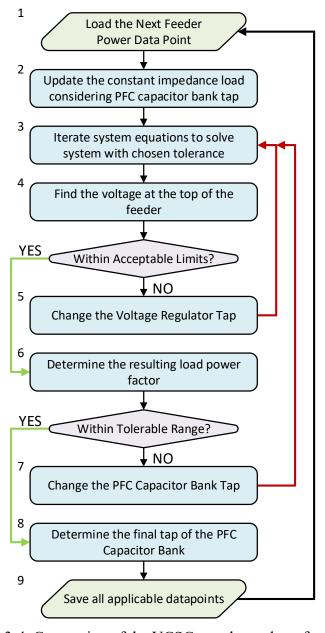

| 2.5        | UCSC Simulation Results                      | 28 |

| 2.6        | UCSC Technical Challenges                    | 31 |

| 2.6.1      | Over-Voltage Events                          | 32 |

| 2.6.2      | Internal Faults                              | 33 |

| 2.6.3      | Converter Start-up                           | 34 |

| 2.7        | Conclusions                                  | 35 |

| 2.8        | Acknowledgments                              | 35 |

| 2.9        | References                                   | 36 |

| CHAPTER 3  |                                              |    |

| THE IMPACT | OF A CURRENT IMBALANCE COMPENSATOR ON FEEDER |    |

| COMPENSAT  | TION EQUIPMENT OPERATION                     | 40 |

| 3.1        | Abstract                                     | 40 |

| 3.2        | Introduction                                 | 40 |

| 3.3        | Conventional Regulating Equipment            | 42 |

| 3.3.1      | Uncompensated System                         | 44 |

| 3.3.2      | System with Traditional Compensation         | 46 |

| 3.4        | Effect of Adding the UCSC                    | 49 |

| 3.4.1      | Placement of the UCSC                        | 49 |

| 3.4.2     | Effect of the UCSC                                  | 51 |

|-----------|-----------------------------------------------------|----|

| 3.4.3     | Effect on the Power Transformer                     | 56 |

| 3.5       | Conclusions                                         | 57 |

| 3.6       | References                                          | 58 |

| CHAPTER 4 |                                                     |    |

| CONSTRUC  | TION AND SIMULATION OF THE MV-UCSC PROTOTYPE        | 60 |

| 4.1       | MV-UCSC Prototype Design                            | 60 |

| 4.1.1     | The 3.3 kV Switching Position                       | 61 |

| 4.1.2     | Flying and DC-Bus Capacitors                        | 62 |

| 4.1.3     | Converter Output Filter                             | 65 |

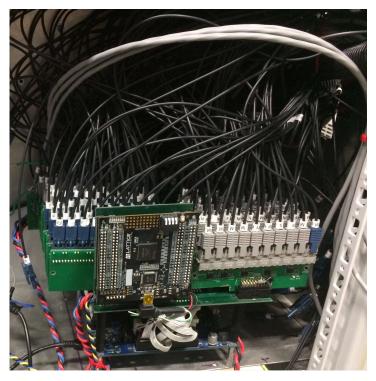

| 4.2       | MV-UCSC Prototype Construction                      | 67 |

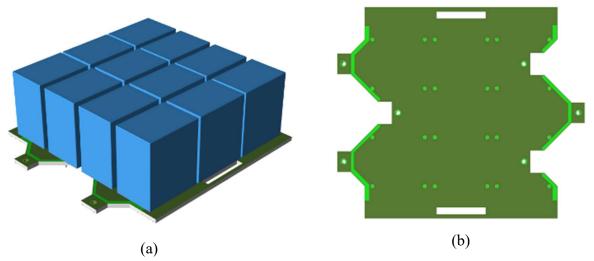

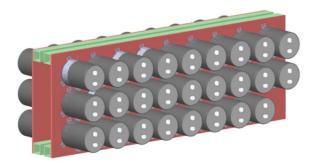

| 4.2.1     | Submodule Capacitors                                | 67 |

| 4.2.2     | DC-Link Capacitors                                  | 69 |

| 4.2.3     | Filter Capacitors                                   | 70 |

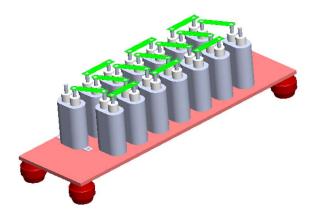

| 4.2.4     | Filter Inductors                                    | 71 |

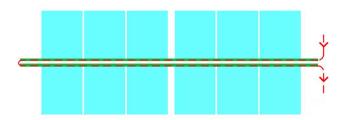

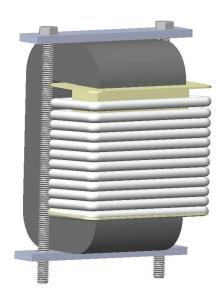

| 4.2.5     | Creepage and Clearance Requirements                 | 76 |

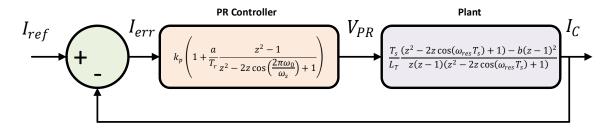

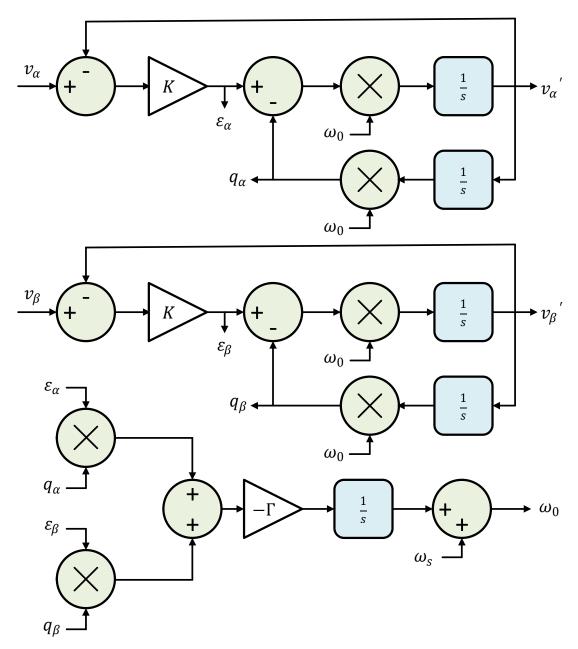

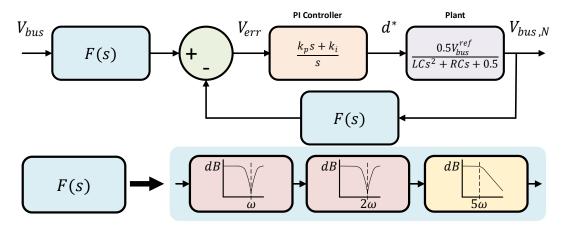

| 4.3       | MV-UCSC Controller Design                           | 79 |

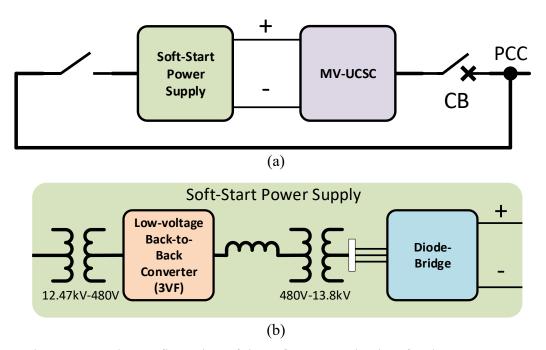

| 4.3.1     | Converter Start-up                                  | 79 |

| 4.3.2     | Steady-state Operation of the MV-UCSC               | 81 |

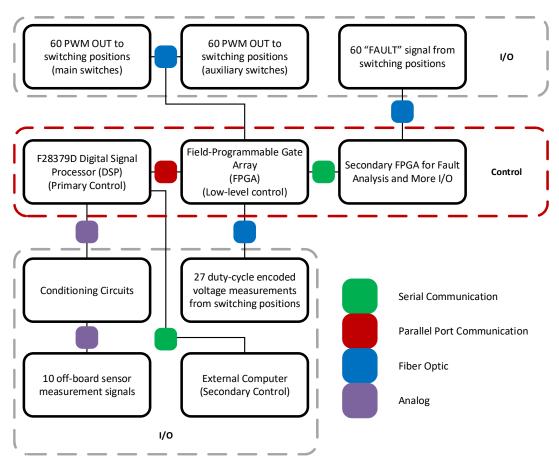

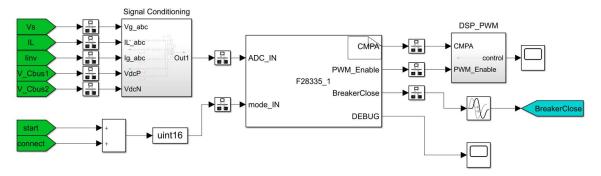

| 4.3.3     | The Control Module                                  | 86 |

| 4.4       | Grid-Connected Simulations of the MV-UCSC Prototype | 88 |

| 4.5       | Concluding Remarks                                  | 95 |

| 4.6       | References                                          | 95 |

## CHAPTER 5

| ٨ | MODIII AD | CWITCHING | DOCITION WITH | VOLTACE DAL | ANCING AND SELF- |

|---|-----------|-----------|---------------|-------------|------------------|

| Α | MUDDULAR  | SWILCHING | POSITION WITH | VOLTAGE-BAL | ANCING AND SELF- |

| P | OWERING I | FOR SERIES DEVICE CONNECTION                             | 98  |

|---|-----------|----------------------------------------------------------|-----|

|   | 5.1       | Abstract                                                 | 98  |

|   | 5.2       | Introduction                                             | 98  |

|   | 5.3       | The Proposed Modular Switching Position                  | 102 |

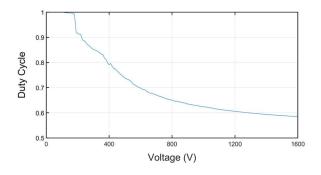

|   | 5.4       | Design Methodology for the Voltage-Balancing Circuitry   | 104 |

|   | 5.4.1     | Resistive Loading Conditions                             | 107 |

|   | 5.4.2     | Current Source Loading Conditions                        | 112 |

|   | 5.4.3     | Voltage-Balancing Modification for Half-Bridge Operation | 115 |

|   | 5.5       | Design of the Self-Powered Circuitry                     | 117 |

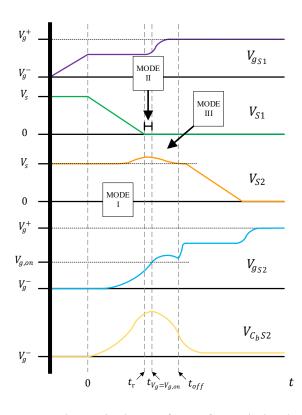

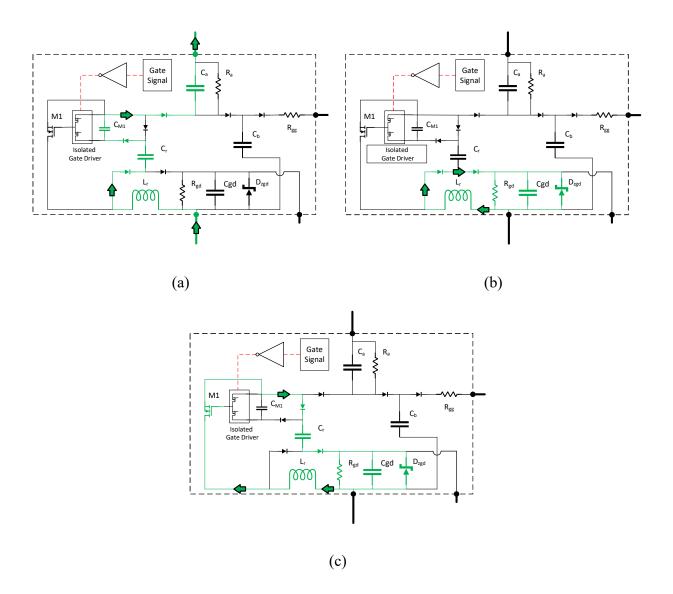

|   | 5.6       | Start-Up of the Switching Position                       | 120 |

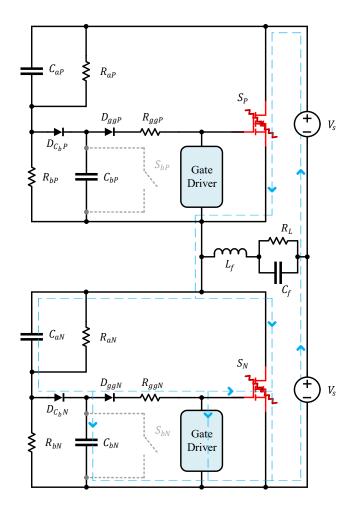

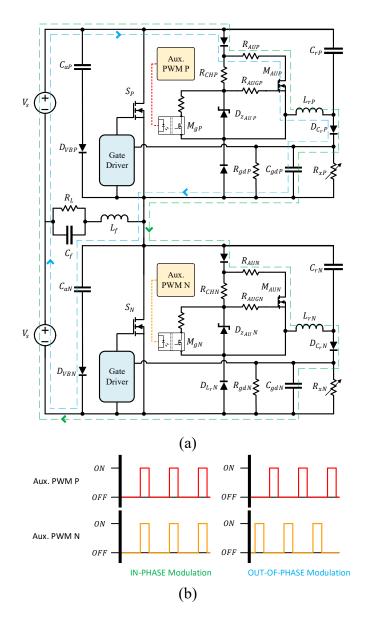

|   | 5.6.1     | Overview                                                 | 120 |

|   | 5.6.2     | Half-Bridge Operation                                    | 123 |

|   | 5.7       | Circuit Simulation Results                               | 126 |

|   | 5.7.1     | Voltage Balancing Circuit                                | 126 |

|   | 5.7.2     | Self-Power Circuit                                       | 128 |

|   | 5.8       | Circuit Experimental Results                             | 130 |

|   | 5.8.1     | Voltage-Balancing Circuit                                | 131 |

|   | 5.8.2     | Self-Powered Circuit                                     | 133 |

|   | 5.8.3     | Start-Up for a Half-Bridge Application                   | 135 |

|   | 5.9       | Protection Concerns                                      | 136 |

|   | 5.10      | Conclusions                                              | 138 |

| 5.11        | Appendix                                                                 | . 138 |

|-------------|--------------------------------------------------------------------------|-------|

| 5.12        | Acknowledgments                                                          | . 141 |

| 5.13        | References                                                               | . 141 |

| CHAPTER 6   |                                                                          |       |

| A HYBRID SN | NUBBER FOR VOLTAGE-BALANCING AND SELF-POWERING OF                        |       |

| SERIES-CON  | NECTED DEVICES                                                           | . 145 |

| 6.1         | Abstract                                                                 | . 145 |

| 6.2         | Introduction                                                             | . 145 |

| 6.3         | Design of the Voltage Balancing Circuit                                  | . 146 |

| 6.4         | Design of the Self-Powered Circuit                                       | . 149 |

| 6.5         | Snubber Simulation Results                                               | . 151 |

| 6.6         | Snubber Experimental Results                                             | . 153 |

| 6.7         | Conclusions                                                              | . 156 |

| 6.8         | Acknowledgments                                                          | . 157 |

| 6.9         | References                                                               | . 158 |

| CHAPTER 7   |                                                                          |       |

| TESTING RES | SULTS OF THE MV-UCSC PROTOTYPE                                           | . 160 |

| 7.1         | Experimental Setup for the MV-UCSC Prototype                             | . 160 |

| 7.2         | Start-Up Using the Modular Switching Positions                           | . 161 |

| 7.3         | Testing of the MV-UCSC with 11-Levels and 1.8 kV AC Grid                 | . 162 |

| 7.4         | Testing of the MV-UCSC with 5-Levels and 4.16 kV AC Grid                 | . 168 |

| 7.5         | Performance of the Voltage Balancing Circuit within the 3.3 kV Switching |       |

|             | Position                                                                 | . 174 |

| 7.6        | References                      | 175 |

|------------|---------------------------------|-----|

| CHAPTER 8  | 3                               | 176 |

| 8.1        | Conclusions                     | 176 |

| 8.2        | Recommendations for Future Work | 179 |

| 8.2.1      | Reliability                     | 179 |

| 8.2.2      | Applications                    | 180 |

| 8.2.3      | Efficiency                      | 181 |

| 8.3        | References                      | 182 |

| APPENDICE  | ES                              | 184 |

| APPENDIX . | A                               |     |

| TESTING SI | ETUP FOR THE MV-UCSC PROTOTYPE  | 184 |

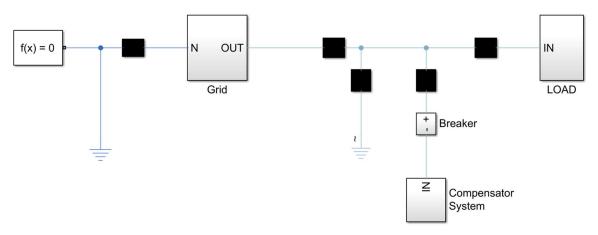

| A.1        | Introduction                    | 184 |

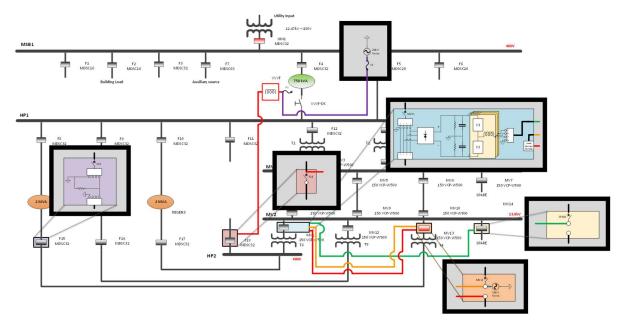

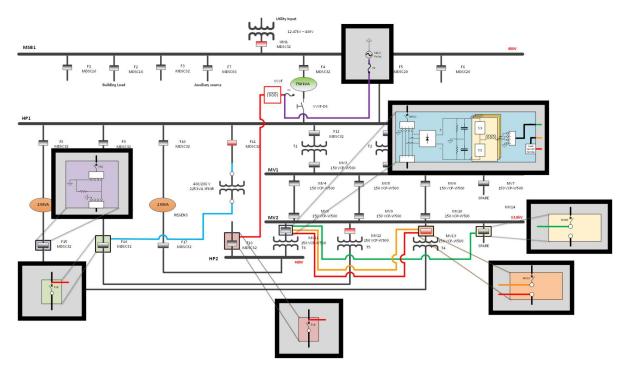

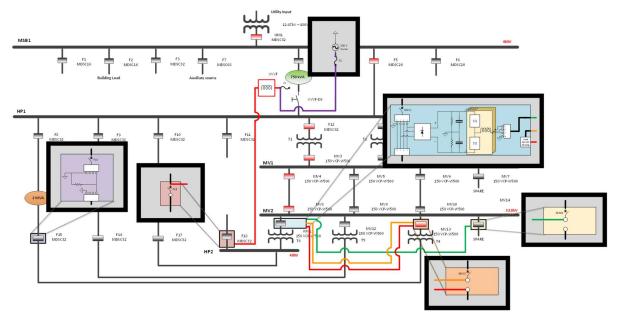

| A.2        | Test Setup                      | 184 |

| A.2.1      | 208 V & 480 V AC Grids          | 184 |

| A.2.2      | 1.8 kV & 6 kV AC Grids          | 185 |

| A.2.1      | 4.16 kV & 13.8 kV AC Grids      | 186 |

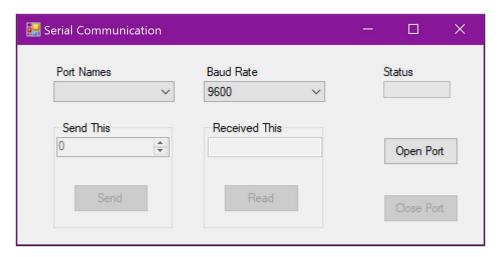

| A.3        | Communication and Control       | 186 |

| A.4        | Test Procedure                  | 187 |

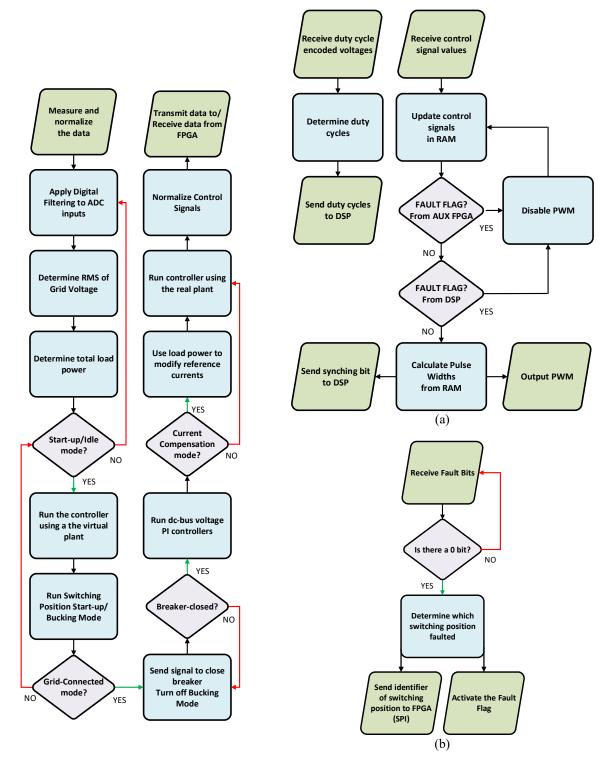

| A.4.1      | DSP Modes of Operation          | 188 |

| A.4.2      | Start-up Procedure              | 188 |

| A.4.3      | Steady-State Operation          | 189 |

| A.4.4      | Shutdown Procedure                       | 189 |

|------------|------------------------------------------|-----|

| A.5        | Referenced Equipment                     | 189 |

| A.6        | Instrumentation Used for MV-UCSC Testing | 199 |

| APPENDIX B |                                          |     |

| EMBEDDED   | SYSTEM CODE                              | 200 |

| B.1        | Introduction                             | 200 |

| B.2        | The Digital Signal Processor (DSP)       | 200 |

| B.2.1      | Interrupt service routines               | 200 |

| B.2.2      | The Mode Functions                       | 205 |

| B.2.3      | Compensator Functions                    | 213 |

| B.3        | The Field Programmable Gate Array (FPGA) | 214 |

## LIST OF FIGURES

| Figure 1-1. Thyristor-switched inductor and capacitor bank                                  |

|---------------------------------------------------------------------------------------------|

| Figure 1-2. Three-phase three-wire converter                                                |

| Figure 1-3. Three single-phase converters.                                                  |

| Figure 1-4. Three-phase four-wire (a) neutral point clamped (b) four-leg converter 6        |

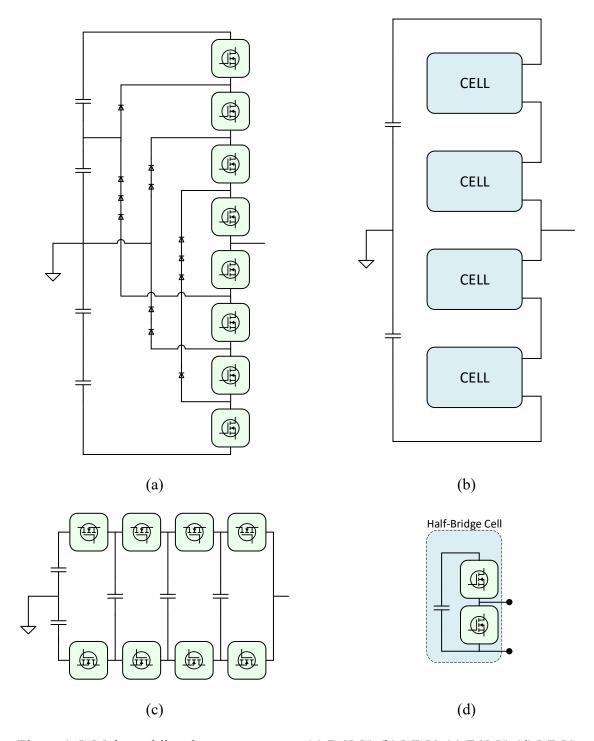

| Figure 1-5. Main multilevel converter types: (a) DCMC (b) MMC (c) FCMC (d) MMC cell 9       |

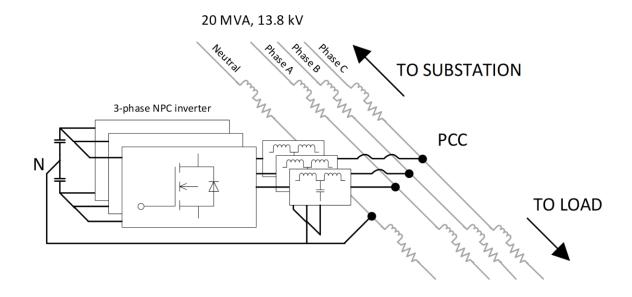

| Figure 2-1. Connection of the UCSC to a three-phase feeder                                  |

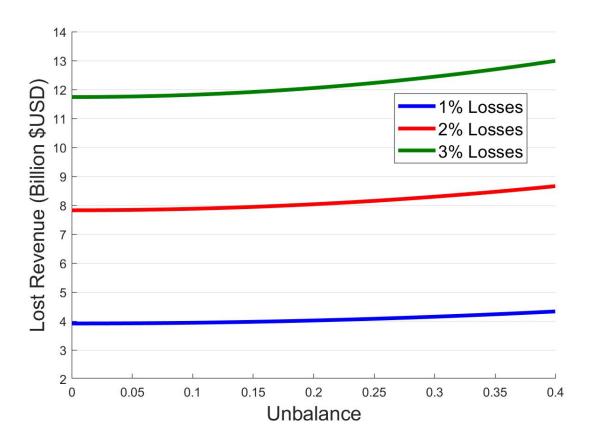

| Figure 2-2. Lost revenue due to unbalances.                                                 |

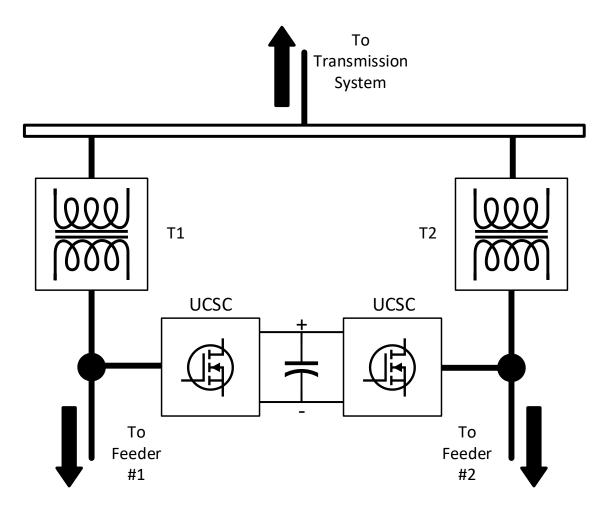

| Figure 2-3. DC-link sharing between UCSC on adjacent feeders                                |

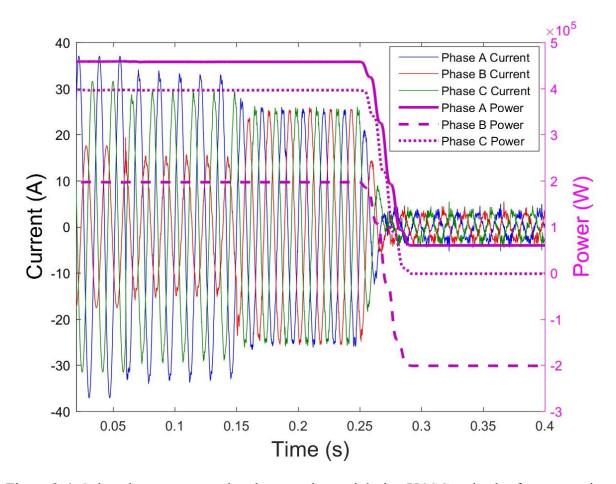

| Figure 2-4. Substation currents and real power demand during UCSC and solar farm operation. |

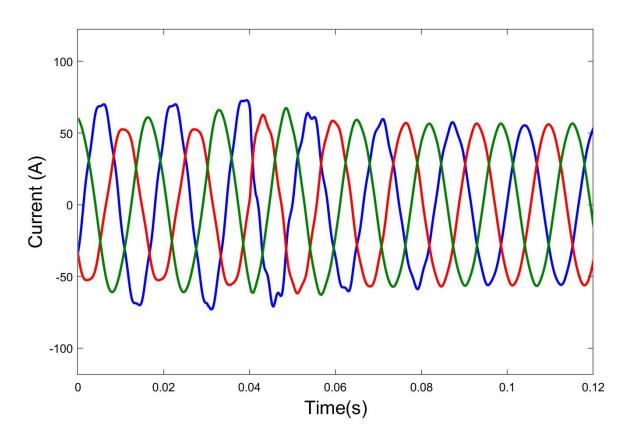

| Figure 2-5. Substation currents before and after harmonic compensation                      |

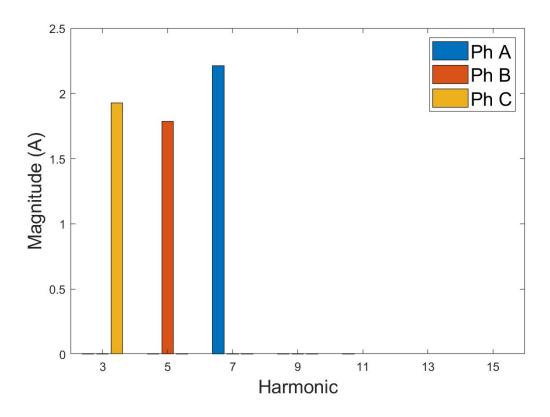

| Figure 2-6. Substation harmonics before compensation                                        |

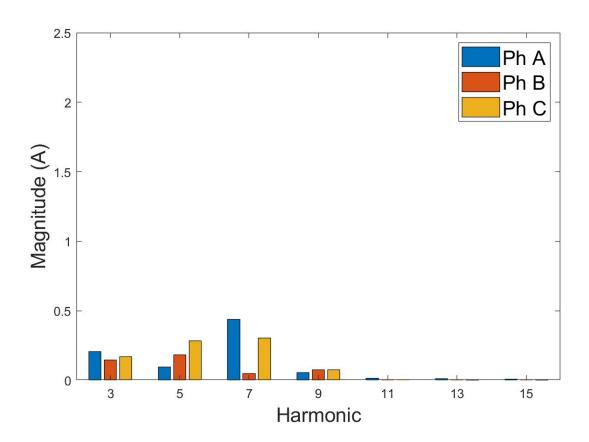

| Figure 2-7. Substation harmonics after compensation                                         |

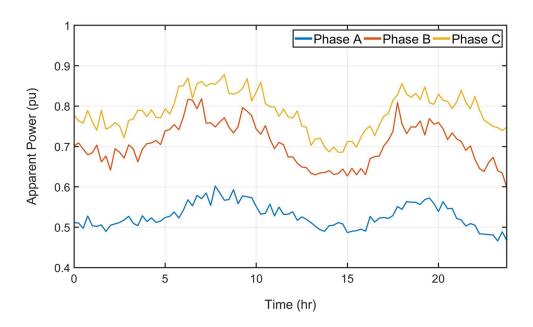

| Figure 3-1. Feeder apparent power over a 24 hr period                                       |

| Figure 3-2. Voltage drop at the head of the feeder over a 24 hr period                      |

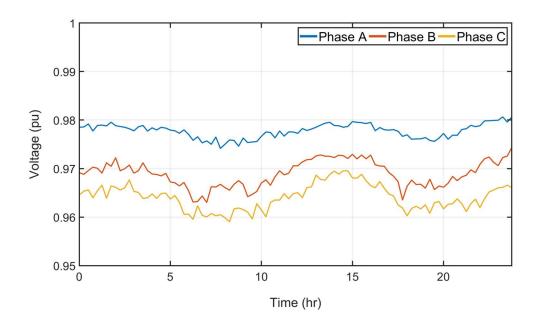

| Figure 3-3. Connection of the UCSC to a three-phase feeder                                  |

| Figure 3-4. Connection of the UCSC to a three-phase feeder                                  |

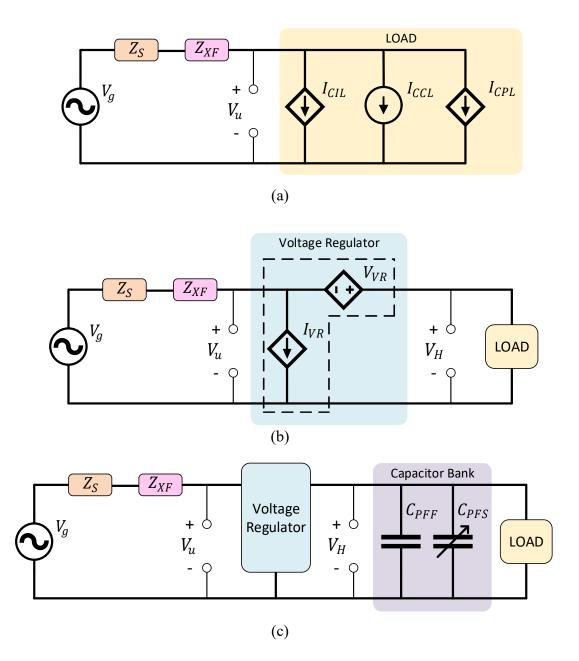

| Figure 3-5. UCSC placement for Configuration 1 with current sensor locations 50             |

| Figure 3-6. UCSC placement for Configuration 2 with current sensor locations 50             |

| Figure 3-7. UCSC current sensor reconfiguration. 52                                         |

| Figure 4-1. Connection of the MV-UCSC to a three-phase feeder                               |

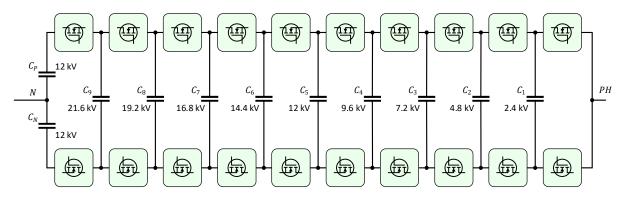

| Figure 4-2. The topology for one phase of the MV-UCSC                                       |

| Figure 4-3. The switching position placement in a converter phase                           |

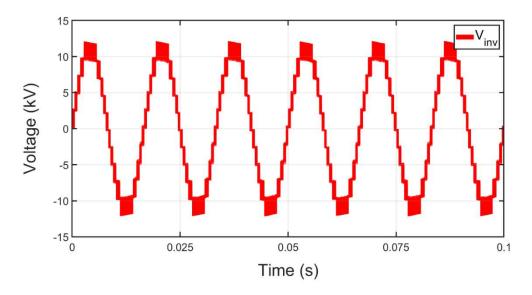

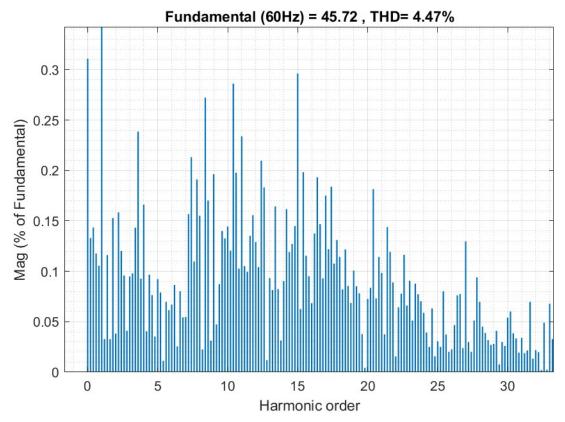

| Figure 4-27. FFT of the steady-state converter current                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

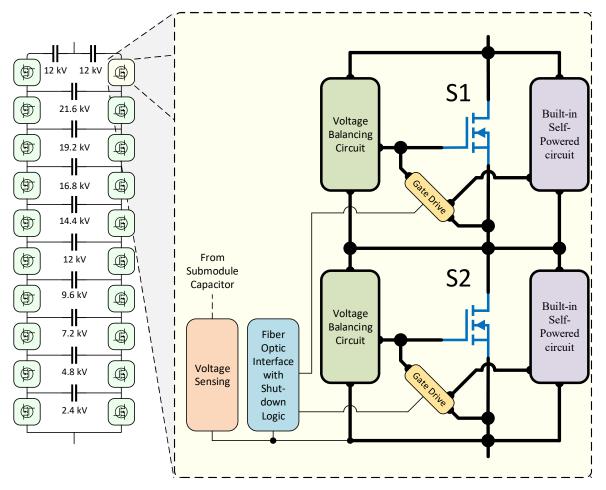

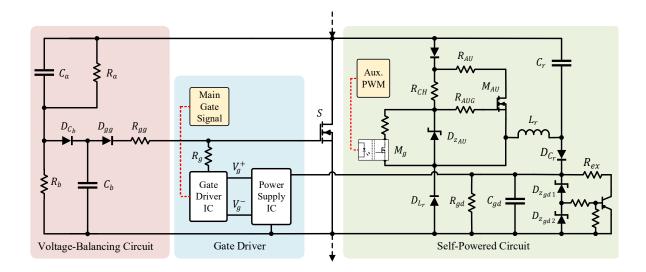

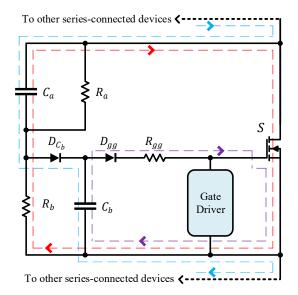

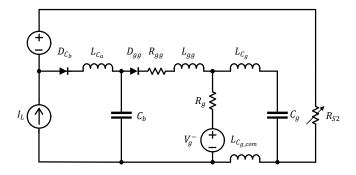

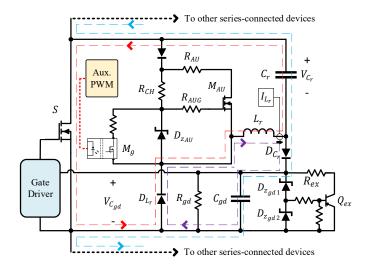

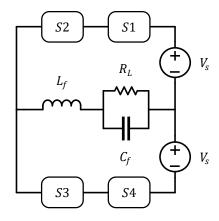

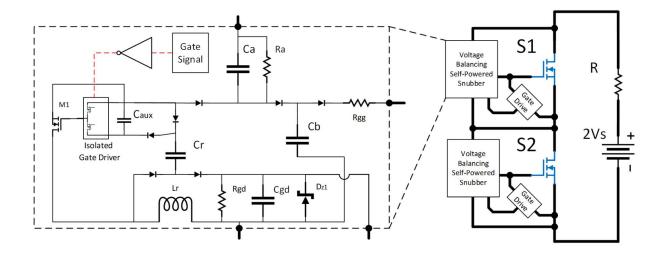

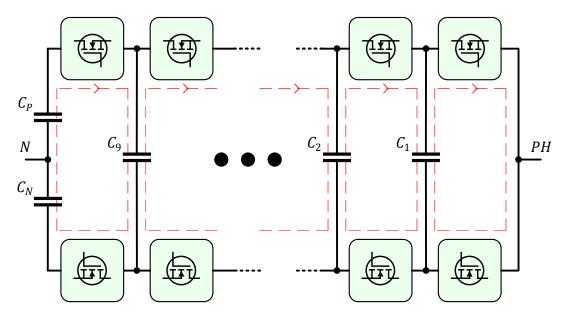

| Figure 5-1. The proposed modular switching position                                                                                                                           |

| Figure 5-2. The voltage-balancing circuit across a power device                                                                                                               |

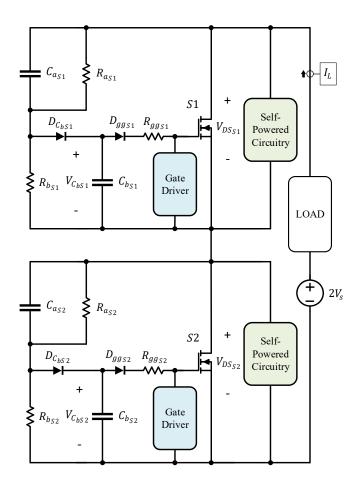

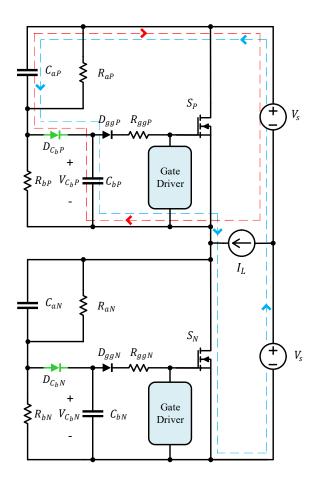

| Figure 5-3. A series connection of two modular switching positions                                                                                                            |

| Figure 5-4. Equivalent circuit for voltage-balancing action with resistive load                                                                                               |

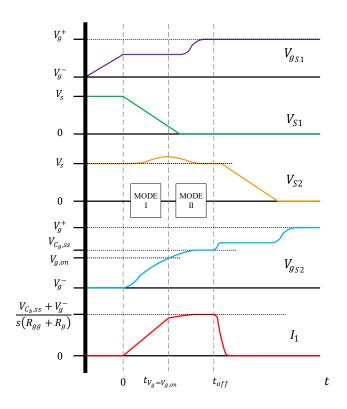

| Figure 5-5. Theoretical waveforms for resistive loading                                                                                                                       |

| Figure 5-6. Equivalent circuit for the voltage-balancing action with a current-source load 113                                                                                |

| Figure 5-7. Theoretical waveforms for a current-source load                                                                                                                   |

| Figure 5-8. The voltage-balancing circuit used in a half-bridge application                                                                                                   |

| Figure 5-9. Current commutations during the ON- and OFF-times of the power MOSFET 117                                                                                         |

| Figure 5-10. Proposed modified self-powered circuit with start-up circuitry                                                                                                   |

| Figure 5-11. Proposed modified self-powered circuit with start-up circuitry                                                                                                   |

| Figure 5-12. Proposed modified self-powered circuit with start-up circuitry                                                                                                   |

| Figure 5-13. (a) Start-up currents with in-phase and out-of-phase bucking pulses. (b) The in-phase and out-of-phase modulation pulses                                         |

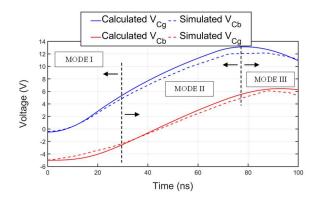

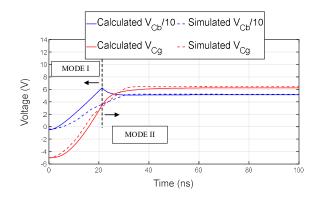

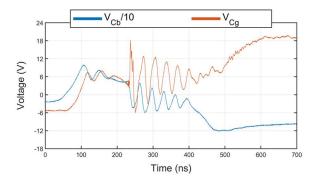

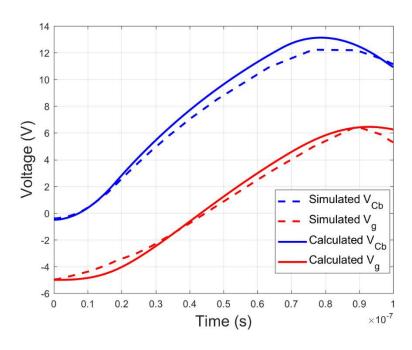

| Figure 5-14. Calculated vs simulation values of $V_{Cb}/10$ and $V_g$ for a resistive load                                                                                    |

| Figure 5-15. Calculated vs simulation values of $VCb/10$ and $Vg$ for a current-source load 127                                                                               |

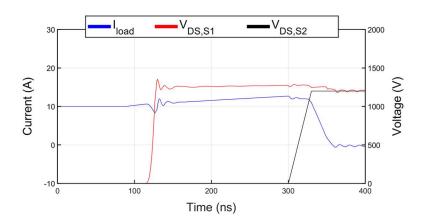

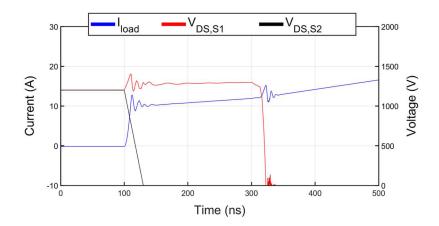

| Figure 5-16. Simulation results of <i>VDS</i> , <i>S</i> 1 and <i>VDS</i> , <i>S</i> 2 during turn-OFF with a 200 ns delay in offset time with a current-source load          |

| Figure 5-17. Simulation results of <i>VDS</i> , <i>S</i> 1 and <i>VDS</i> , <i>S</i> 2 during turn-ON with a 200 ns delay in offset time with a current-source load           |

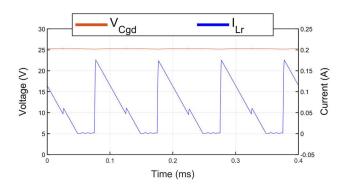

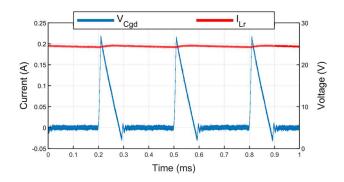

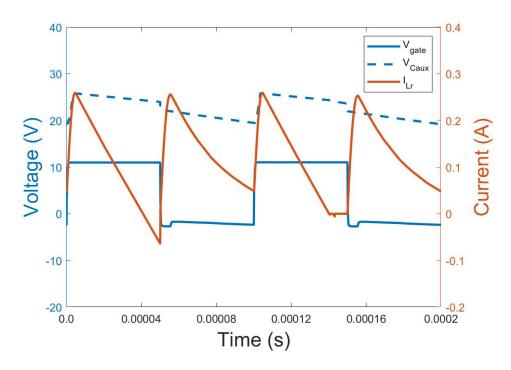

| Figure 5-18. $ILr$ , and $V_{Cgd}$ during turn ON and turn OFF of $S2$ .                                                                                                      |

| Figure 5-19. Photograph of 3.3 kV switching position prototype                                                                                                                |

| Figure 5-20. Experimental results of $V_{Cb}/10$ and $V_g$ with S2 delayed by 220ns                                                                                           |

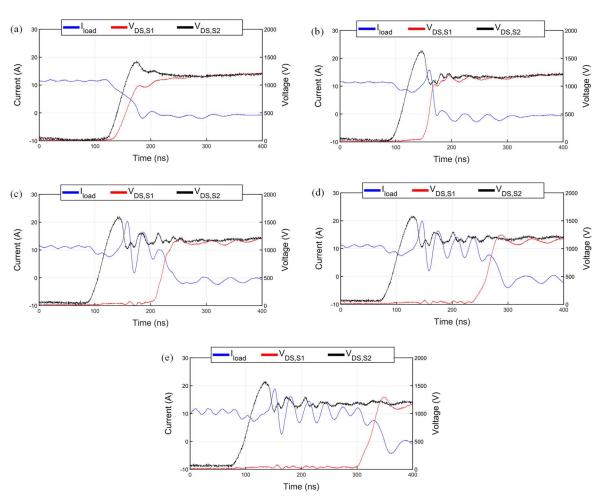

| Figure 5-21. Experimental results of <i>VDS</i> , <i>S</i> 1 and <i>VDS</i> , <i>S</i> 2 during turn-OFF for (a) 10 ns (b) 50 ns (c) 100 ns (d) 150 ns (e) 200 ns offset time |

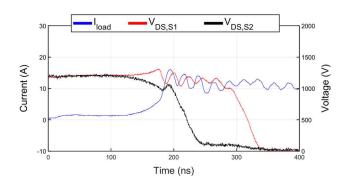

| Figure 5-22. Experimental results of <i>VDS</i> , <i>S</i> 1 and <i>VDS</i> , <i>S</i> 2 during turn-ON with a 200 ns delay in offset time.              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-23. Experimental waveforms of <i>ILr</i> and <i>VCgd</i> during bucking start-up operation 134                                                  |

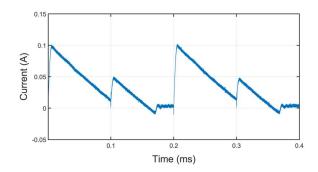

| Figure 5-24. Experimental waveforms of <i>ILr</i> where <i>Lr</i> operating in continuous conduction mode                                                |

| Figure 5-25. Half-bridge testing configuration                                                                                                           |

| Figure 5-26. Voltage-balancing circuit capacitor voltage and self-power inductor current with inphase start-up modulation                                |

| Figure 5-27. Voltage-balancing circuit capacitor voltage and self-power inductor current with inphase start-up modulation                                |

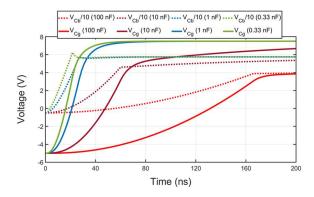

| Figure 5-28. VCg and VCb/10 for different values of Cb                                                                                                   |

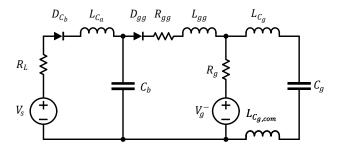

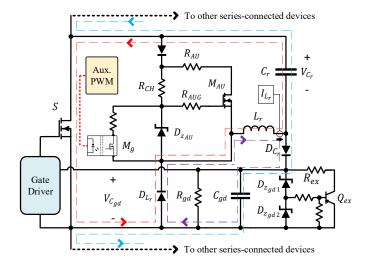

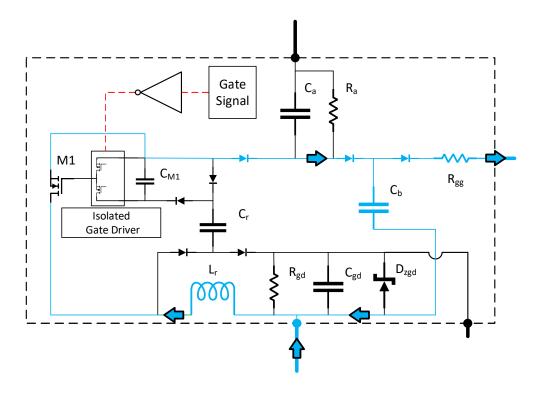

| Figure 6-1. Proposed voltage balancing self-powered gate driver                                                                                          |

| Figure 6-2. Current commutations during the on- and off-times of S2                                                                                      |

| Figure 6-3. Calculated vs simulation values of $V_{cb}/10$ and $V_g$                                                                                     |

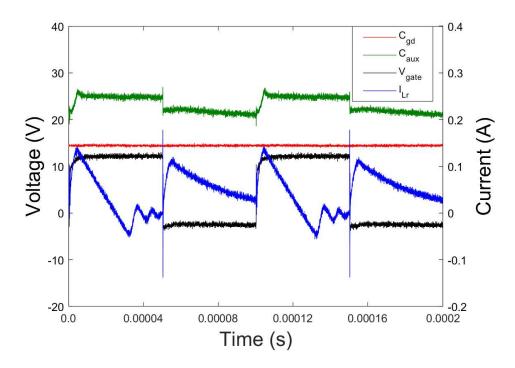

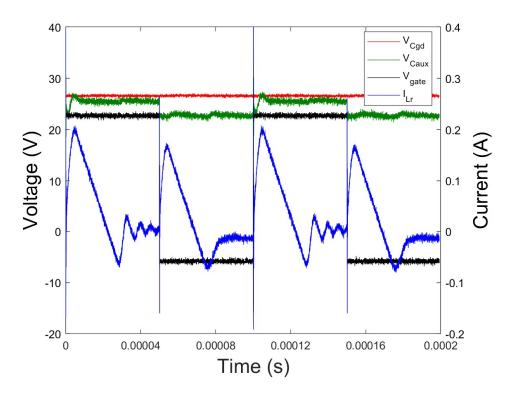

| Figure 6-4. V <sub>gate</sub> , V <sub>Caux</sub> , and I <sub>Lr</sub> during turn on and turn-off of S2                                                |

| Figure 6-5. Additional current paths during the off-time of S2                                                                                           |

| Figure 6-6. $V_{gate}$ , $V_{Caux}$ , and $I_{Lr}$ during turn on and turn-off of S2                                                                     |

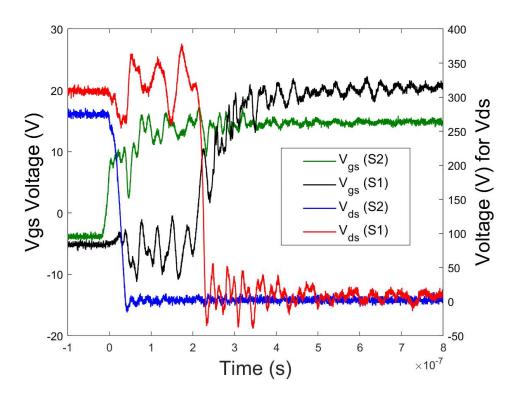

| Figure 6-7. $V_{ds}$ and $V_{gs}$ for S1 and S2 during a turn-on event                                                                                   |

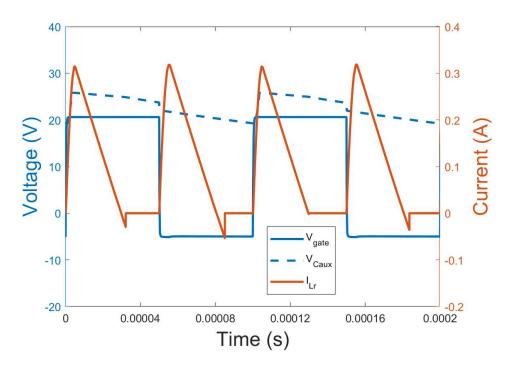

| Figure 6-8. $V_{gate}$ , $V_{Caux}$ , and $I_{Lr}$ during turn on and turn-off of S2                                                                     |

| Figure 6-9. $V_{gate}$ , $V_{Caux}$ , and $I_{Lr}$ during turn on and turn-off of S2 with large $R_{gg}$                                                 |

| Figure 7-1. MV-UCSC start-up current paths                                                                                                               |

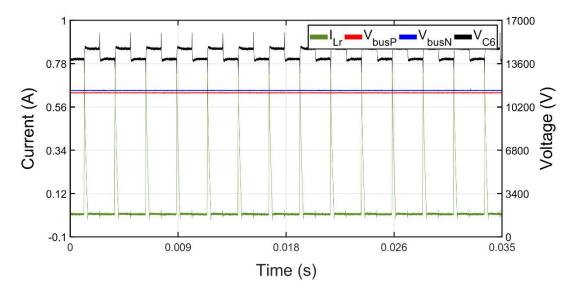

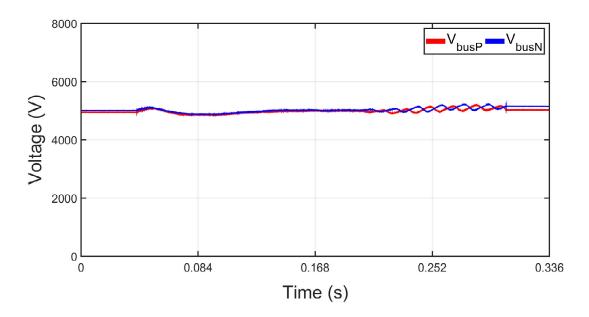

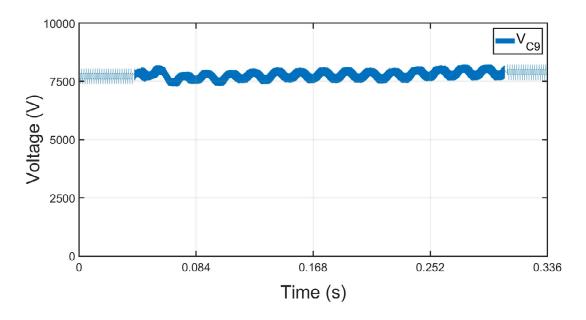

| Figure 7-2. DC-bus voltages, resonant inductor current, and flying capacitor voltage during the 2start-up interval of the 11-level MV-UCSC at ±12 kV bus |

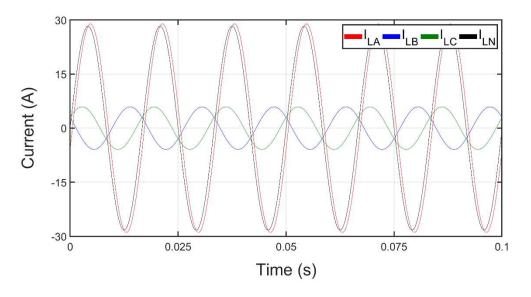

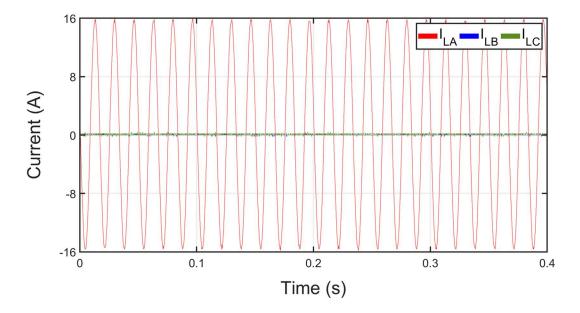

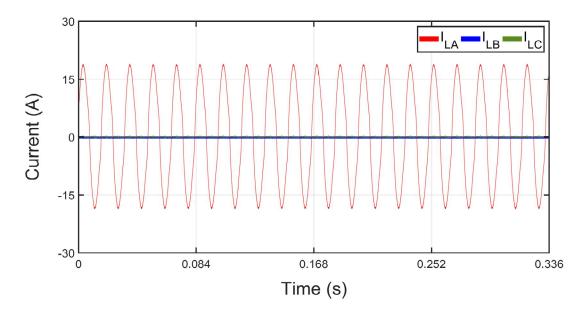

| Figure 7-3. Three-phase unbalanced load currents; only phase A has a load                                                                                |

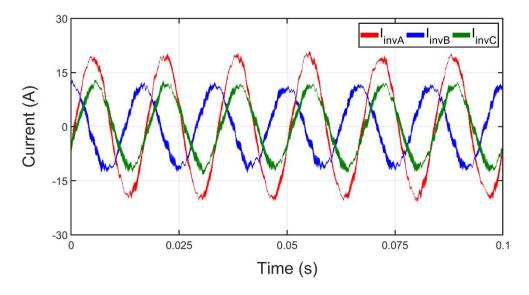

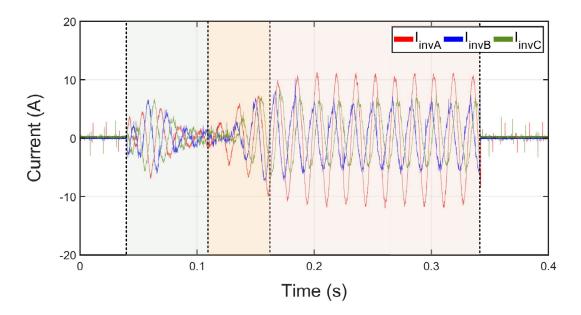

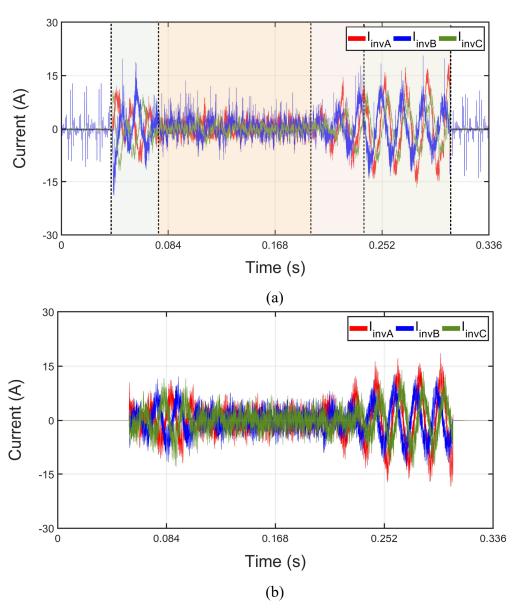

| Figure 7-4. MV-UCSC experimental output currents with the 1.8 kV ac grid                                                                                 |

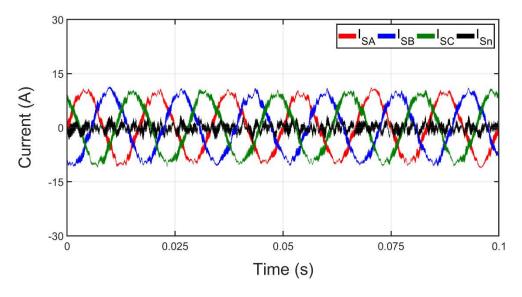

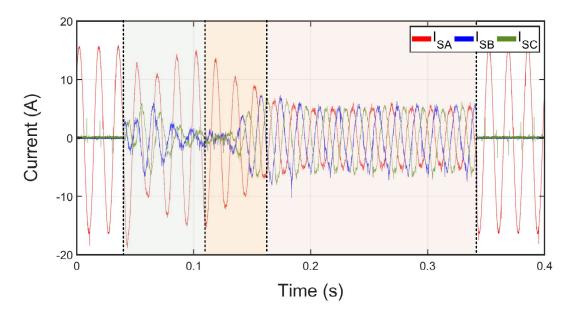

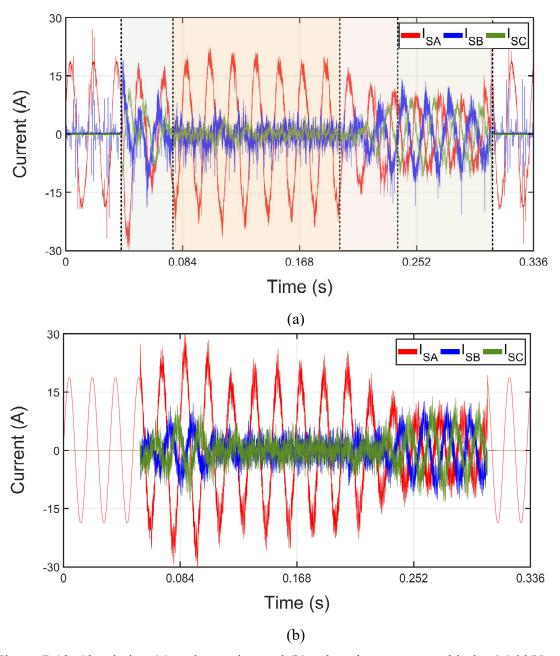

| Figure 7-5. Experimental substation currents with the 1.8 kV ac grid                                                                                     |

| Figure 7-6. Experimental substation currents separated by phase with the 1.8 kV ac grid 166                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------|

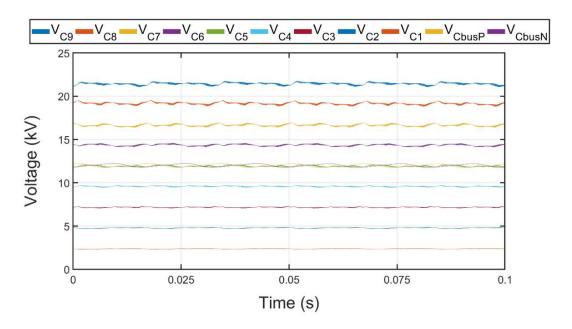

| Figure 7-7. MV-UCSC experimental dc-bus capacitance voltages with the 1.8 kV ac grid 167                                                |

| Figure 7-8. MV-UCSC experimental flying capacitor voltage with the 1.8 kV ac grid 167                                                   |

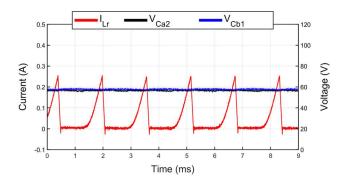

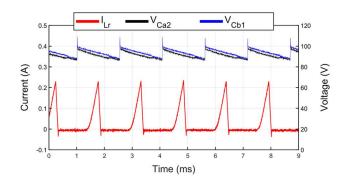

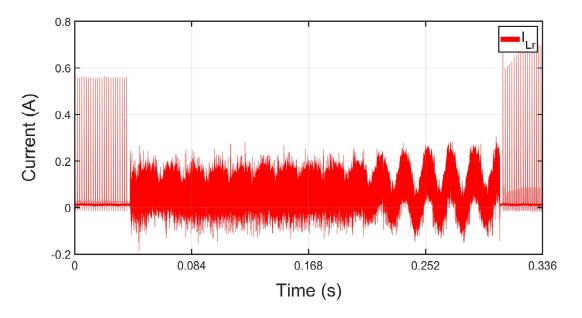

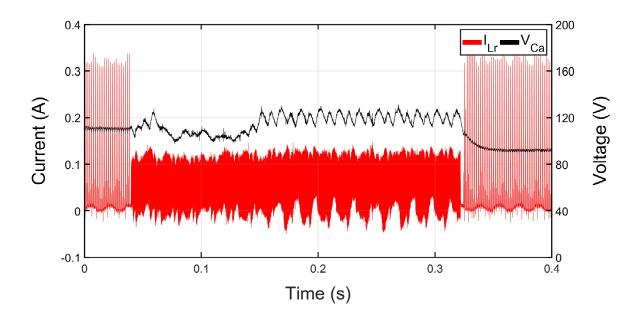

| Figure 7-9. Experimental resonant inductor current and output capacitor voltage within the self-powered circuit with the 1.8 kV ac grid |

| Figure 7-10. Experimental unbalanced load currents with the 4.16 kV ac grid                                                             |

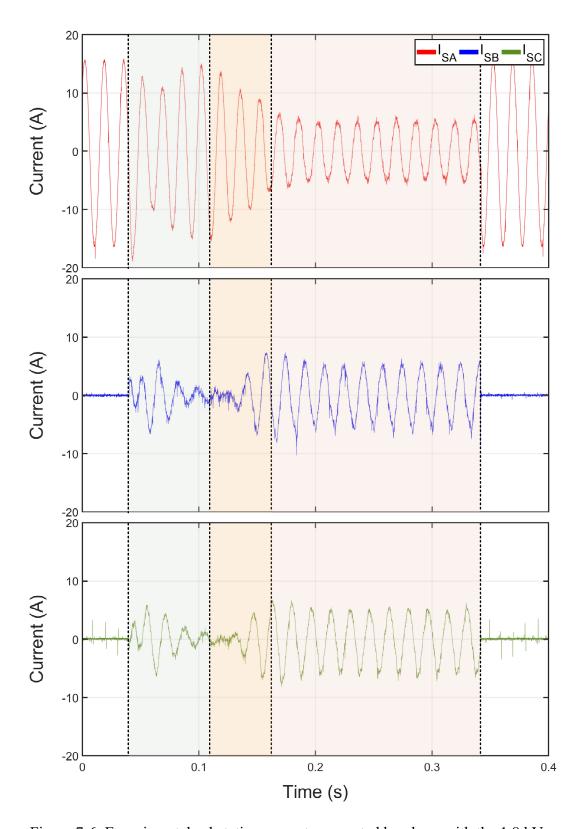

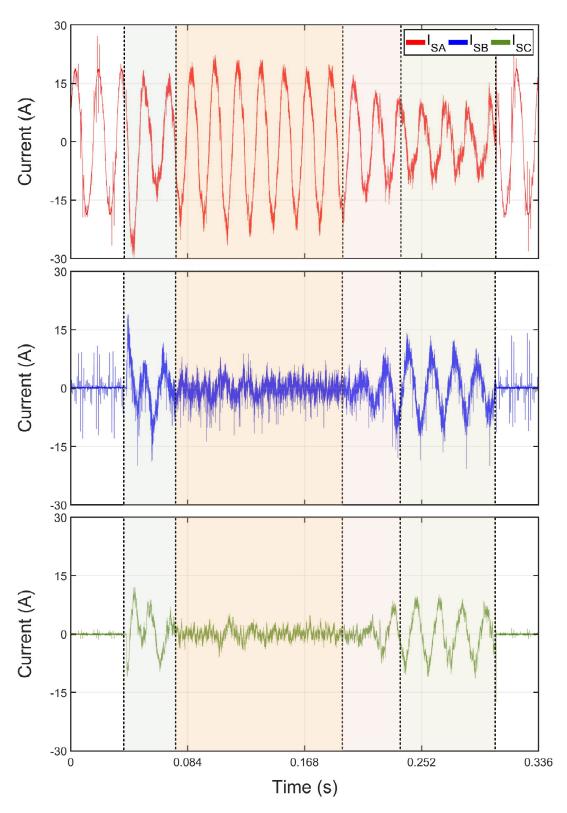

| Figure 7-11. MV-UCSC experimental (a) and simulation (b) output currents with the 4.16 kV ac grid                                       |

| Figure 7-12. Simulation (a) and experimental (b) substation currents with the 4.16 kV ac grid.                                          |

| Figure 7-13. Experimental substation currents separated by phase with the 4.16 kV ac grid 172                                           |

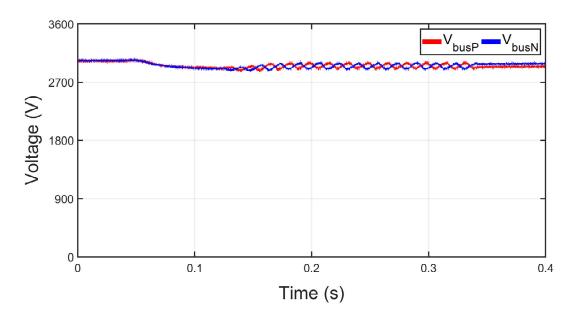

| Figure 7-14. MV-UCSC experimental dc-bus capacitance voltages with the 4.16 kV ac grid 173                                              |

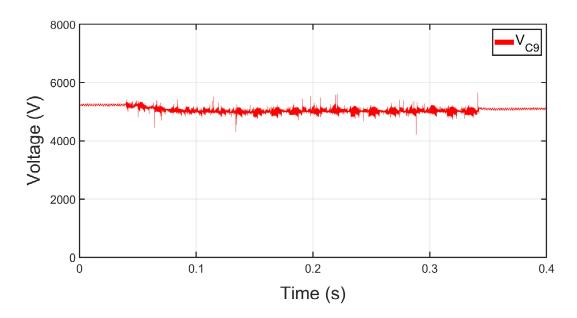

| Figure 7-15. MV-UCSC experimental flying capacitor voltage with the 4.16 kV ac grid 173                                                 |

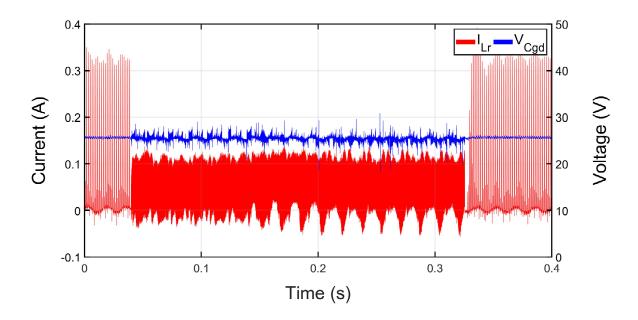

| Figure 7-16. Experiment resonant inductor current with the 4.16 kV ac grid                                                              |

| Figure 7-17. Experimental resonant inductor current and voltage-balancing capacitor voltage at a dc-bus voltage ±1 kV                   |

| Figure A-1. Test setup for ≤ 480 V ac grid                                                                                              |

| Figure A-2. Test setup for 1800 V & 6000 V ac grid                                                                                      |

| Figure A-3. Test setup for 4160 V & 13800 V ac grid                                                                                     |

| Figure A-4. Serial Interface from laptop to the DSP                                                                                     |

| Figure A-5. 0-560 V variac                                                                                                              |

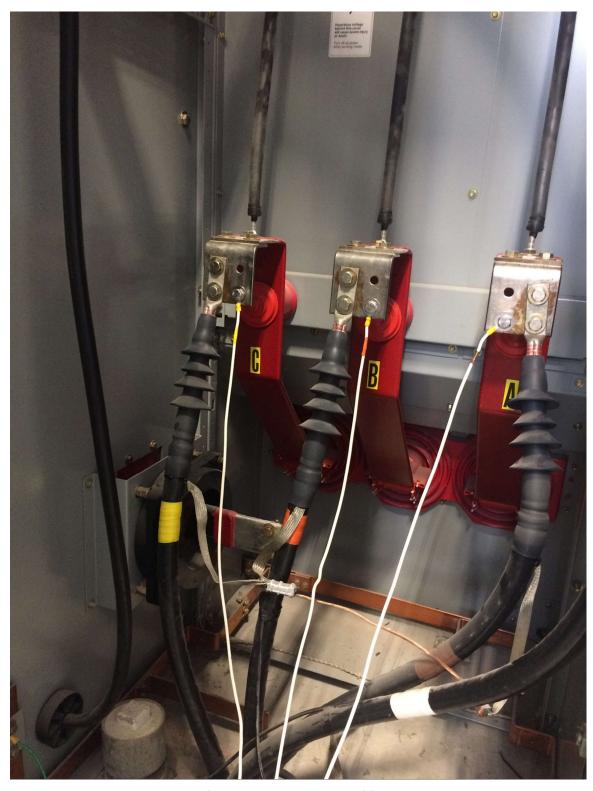

| Figure A-6. CB MV13 cabinet                                                                                                             |

| Figure A-7. CB MV14 cabinet                                                                                                             |

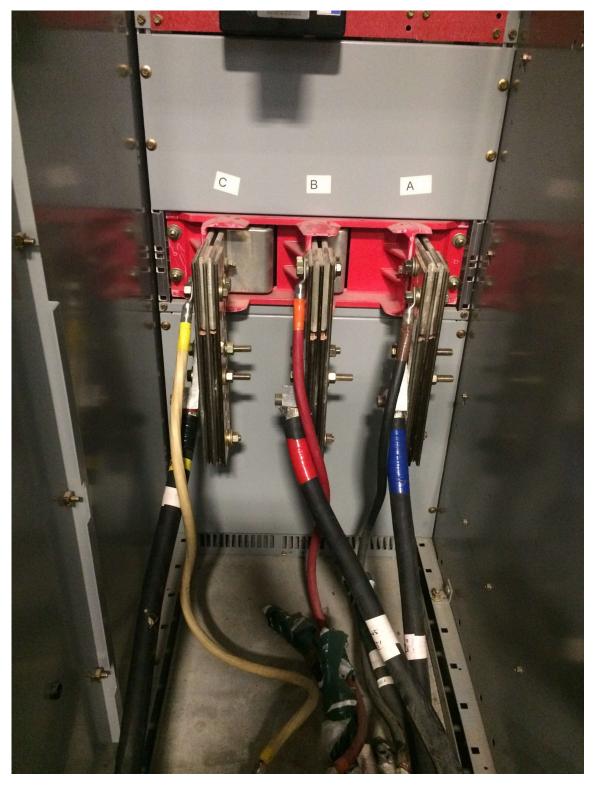

| Figure A-8. CB MV11 cabinet                                                                                                             |

| Figure A-9. CB F15 cabinet.                                                                                                             |

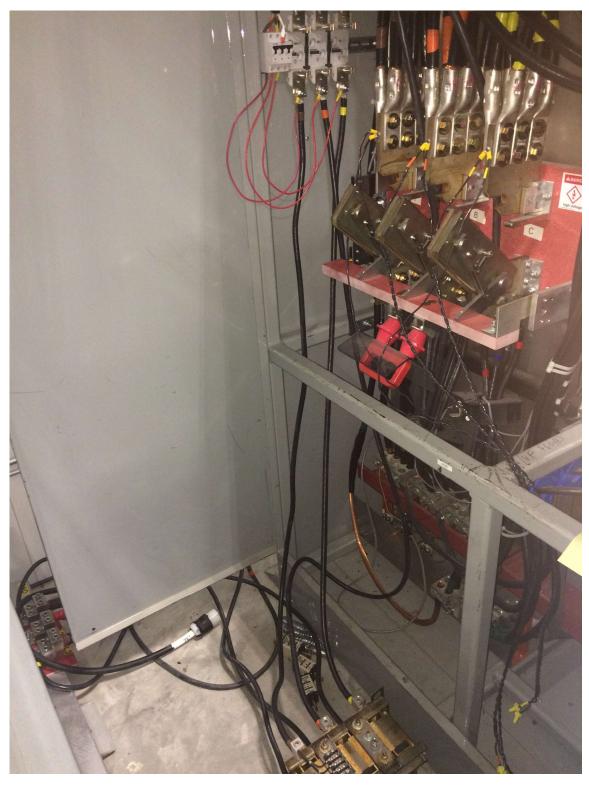

| Figure A-10. CB F18 cabinet.                                                                                                            |

| Figure A-11. The 3VF cabinet.                              | 197 |

|------------------------------------------------------------|-----|

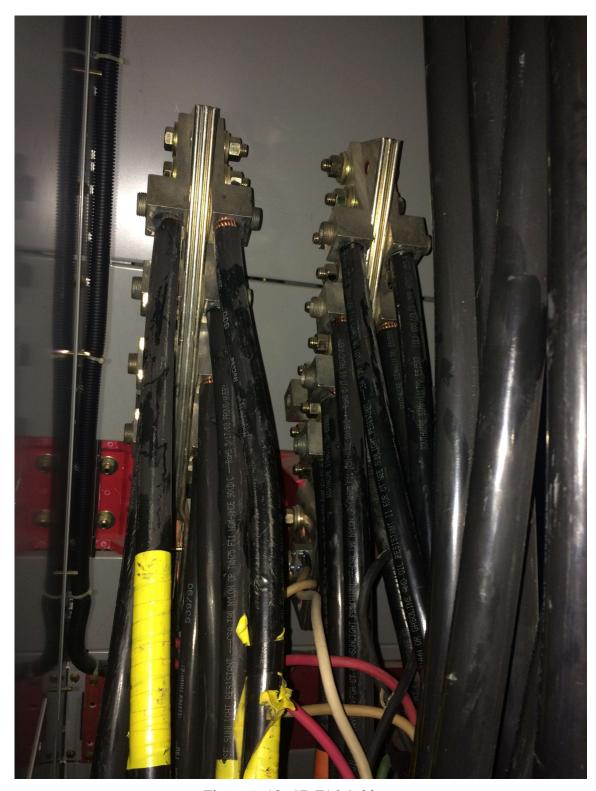

| Figure A-11. CB F16 Cabinet.                               | 198 |

| Figure B-1. Reading the ADC data                           | 200 |

| Figure B-2. Inverse function calls to remove phase delays. | 201 |

| Figure B-3. Parallel port function call.                   | 201 |

| Figure B-4. Phase-Lock Loop function call.                 | 201 |

| Figure B-5. Sine-wave RMS function call.                   | 202 |

| Figure B-6. Normalized voltage vector generation.          | 202 |

| Figure B-7. Dc-bus measurement filtering.                  | 202 |

| Figure B-8. Virtual plant function call.                   | 203 |

| Figure B-9. Overvoltage and overcurrent tripping.          | 203 |

| Figure B-10. Mode function pointer call.                   | 203 |

| Figure B-11. Register loading.                             | 203 |

| Figure B-12. Phase-Lock Loop function call.                | 204 |

| Figure B-13. SCI Port ISR code.                            | 204 |

| Figure B-14. Mode 1 code.                                  | 205 |

| Figure B-15. Mode 2 code.                                  | 206 |

| Figure B-16. Mode 3 code.                                  | 207 |

| Figure B-17. Mode 4 code.                                  | 210 |

| Figure B-18. Mode 5 code.                                  | 212 |

| Figure B-19. Mode 5 code (Continued).                      | 213 |

| Figure B-20. Mode 5 code (Continued).                      | 213 |

| Figure B-21. Current controller function code.             | 214 |

| Figure B-22. The compensator function code   | 214 |

|----------------------------------------------|-----|

| Figure B-23. Internal oscillator component.  | 215 |

| Figure B-24. Phase-Lock Loop component.      | 215 |

| Figure B-25. Data bus manager component.     | 215 |

| Figure B-26. High-level ePWM component.      | 216 |

| Figure B-27. Custom parallel port component. | 216 |

## LIST OF TABLES

| Table 1-1. Summary of common current compensation solutions                       | 6   |

|-----------------------------------------------------------------------------------|-----|

| Table 1-2 Commercially available power supplies                                   | 10  |

| Table 1-3 Contributions of this research                                          | 14  |

| Table 3-1 Feeder characteristics                                                  | 43  |

| Table 3-2 Scenario descriptions                                                   | 52  |

| Table 3-3 Scenario 1                                                              | 53  |

| Table 3-4 Scenario 2                                                              | 53  |

| Table 3-5 Scenario 3                                                              | 53  |

| Table 3-6 Scenario 4                                                              | 54  |

| Table 3-7 Scenario 5                                                              | 54  |

| Table 3-8 Scenario 6                                                              | 54  |

| Table 3-9 Scenario 7                                                              | 56  |

| Table 3-10 Scenario 8                                                             | 56  |

| Table 4-1. MV-UCSC design specifications                                          | 61  |

| Table 4-2. MV-UCSC components and values                                          | 63  |

| Table 4-3 Clearance distances versus voltage (kV)                                 | 77  |

| Table 4-4. Creepage distance versus voltage                                       | 77  |

| Table 5-1. Values of $V(s)$ and $I(s)$ during each mode                           | 110 |

| Table 5-2. Circuit Parameters                                                     | 126 |

| Table 6-1. Values of $V(s)$ during each period of the turn-on compensation action | 148 |

| Table 6-2. Snubber Parameters                                                     | 151 |

| Table A-1. Instrumentation used for this dissertation                             | 199 |

#### LIST OF PUBLICATIONS

- Chapter 2 V. Jones, J. C. Balda, and R. Adapa, "Current Compensators for Unbalanced Electric Distribution Systems," in 2018 IEEE Electronic Power Grid (eGrid), 2018, pp. 1-6. (Published)

- Chapter 3 V. Jones and J. C. Balda, "The Impact of a Current Imbalance Compensator on Feeder Compensation Equipment Operation," in 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), 2020, pp. 463-469.

(Published)

- Chapter 5 V. Jones, R. A. Fantino, and J. C. Balda, "A Modular Switching Position with Voltage-Balancing and Self-Powering for Series Device Connection," IEEE Journal of Emerging and Selected Topics in Power Electronics, pp. 1-1, 2020. (Published)

- Chapter 6 V. Jones, J. C. Balda, and R. Adapu, "A Hybrid Snubber for Voltage-Balancing and Self-Powering of Series-Connected Devices," presented at the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, 2019. (Published)

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Unbalanced Currents in Distribution Systems: The Problem and Motivation

An electric power transmission system normally consists of three phases and three-wires or conductors, but it becomes a four-wire one in the United States once the voltage is stepped down to voltages at the distribution system level. Though some of the customers in distribution systems utilize three-phase power, this is not economical for the vast majority of a given utility's service area. As a result single-phase feeders are used to service residential areas [1]. Single-phase loading leads to an inherent imbalance in the three-phase currents. The imbalances can cause several issues including overheating of neutral conductors, increased losses in generators, torque ripples in electric machines and excessive losses in the holding tank for ungrounded wye-connected transformers [2-7]. The entire system may also see a drop in efficiency [8, 9].

Recently, the use of rooftop solar panels in some areas has exacerbated current imbalances [10, 11].

Traditionally, utilities use balanced three-phase fixed and switched capacitor banks to compensate for this. These capacitor banks are sold in standard reactive power units normally 50 or 100 producing kVAR increments per phase for the distribution system. Imbalances can also make compensating for the power factor at the head of a feeder more difficult since not all phases would have the same power factor. Thus, the ability of the utility to adjust unbalanced reactive currents more closely and thus achieve an appropriate power factor is reduced.

The seasonality of loads can also play a role in this. For example, a tourist location supplied with a largely underground distribution feeder could experience overcompensation of the power factor in the off-season due to the increased capacitances of underground systems.

Overcompensation to a leading power factor can cause over-voltages on the distribution feeder.

The utility then might have to also install shunt reactors seasonally to fix this issue [1].

Additionally, the use of non-linear power-electronics-based front-end converters on many loads can contribute to harmonic distortion in the currents drawn from the grid [10]. These currents drawn through the upstream impedances cause harmonic voltage distortions along the feeder, contribute to additional losses, and can cause overheating of fixed and switched capacitor banks because of their relatively low impedance at the harmonic frequencies.

Hence major problems associated with distribution feeders described above are:

- Load current imbalances,

- Voltage Regulation,

- Power factor correction, and

- Current harmonics.

#### 1.2 Existing Current Compensation Solutions

The predominant distribution system configuration in the United States, the region of interest, is a three-phase four-wire system, so the focus of the considered solutions are for such a system. Existing solutions and their benefits are presented next.

#### 1.2.1 Passive Solutions

Passives are cheap and simple to use relative to active solutions. As mentioned above, capacitor banks can correct for lagging power factors and adjust to increases in load or undervoltage conditions, but they are limited by the coarse nature of their taps. They also provide some decoupling of the upstream system from the downstream load harmonics; however, they

are normally not designed for this function. Additionally, these may induce additional system resonances and do not compensate for load imbalances [1].

Among passive solutions that compensate for unbalanced currents is the zig-zag transformer [12]. Through a modified winding configuration, this three-phase transformer is connected between each of the phases and the neutral wire. This transformer presents high-impedance to differential phase currents but presents very little impedance to common-mode currents. In the context of three-phase current component theory, the common-mode currents are equivalent to the zero-sequence currents or the currents in the neutral conductor. By providing a low-impedance current path for the zero-sequence components the magnitude of these currents seen upstream from the zig-zag transformer is reduced. This can reduce the imbalances seen at the head of the feeder. The drawbacks with this method are the need for another large, and potentially custom, line-frequency transformer and the need to be installed near the load, reducing the amount of load for which any one zig-zag transformer can compensate.

#### 1.2.2 Active Solutions

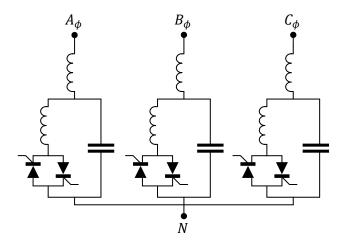

Active solutions based on power electronics and closed-loop control tend to be more expensive and more complex, but these solutions provide improved performance and functionality over the passives-based solutions. A first step towards an active solution would be thyristor-switched reactor and capacitor banks [13]. By controlling the firing angle of a thyristor, the current through a shunt-connected network of reactive components can be controlled and the equivalent power factor of the load can be compensated. The control for this type of compensator is relatively simple and it can be effective, but it also can produce significant harmonic currents and does not compensate for unbalanced currents. An example of this converter is in Figure 1-1.

Figure 1-1. Thyristor-switched inductor and capacitor bank.

#### Voltage-Source Converters (VSCs)

Three-phase, three-leg converters can compensate for power factor, negative-sequence current, and non-zero-sequence harmonics [14]. These can be used to keep the power factor at a desired value under any loading (within their power rating). This allows the converter to act as a switched capacitor bank with very small kVAr steps. However, the disadvantage with this topology is the inability to compensate for zero-sequence currents and thus cannot compensate for all the load current imbalances. A diagram of the converter is displayed in Figure 1-2.

Three single-phase converters that share the same dc bus can be used to compensate for all the above problems. This setup requires the use of a full-bridge converter for each phase. The drawback with this topology is the requirement of single-phase transformers for interfacing with the load due to the need for three separate neutral wire connections. This converter is given in Figure 1-3.

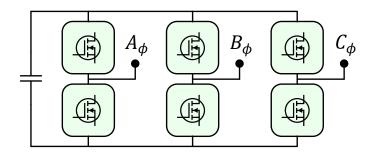

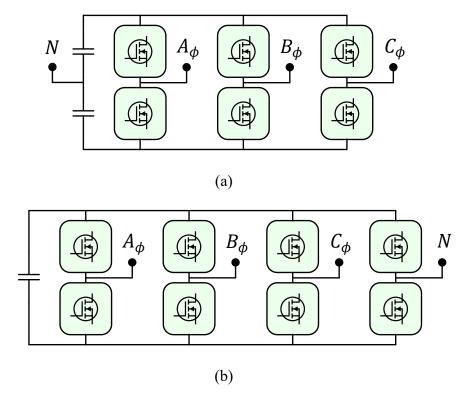

A three-phase four-wire converter with a neutral point clamped (NPC) dc bus can compensate for all unbalanced load currents, power factor, and all harmonics [15]. However, the dc-bus voltage for this converter is 15% higher than those for three-phase three-wire and three

Figure 1-2. Three-phase three-wire converter

Figure 1-3. Three single-phase converters

single-phase converters for the same grid voltage, and thus it may require higher rated semiconductor devices. There is the potential to reduce the required dc-bus voltage by utilizing more complex modulation techniques and a four-leg variant of this converter. Though the voltage stress may be reduced, this variant requires more semiconductor devices. Both converter types are shown in Figure 1-4. A summary of all the above solutions is given in Table 1-1.

#### **Direct Connection to Distribution Systems**

Usually a shunt active compensator at distribution system level voltages would be rated for lower voltages (e.g., 480 V) and a step-up transformer would interface with the feeder [16-18]. This requirement remains a barrier for the use of these converters because of their ease-of-use can be diminished by the need for a transformer. Also, though relatively uncostly, line-frequency transformers require a significant amount of space, which can affect the deployment of these equipment along the distribution feeder. Active compensators connected directly to

Figure 1-4. Three-phase four-wire (a) neutral point clamped (b) four-leg converter.

Table 1-1. Summary of common current compensation solutions

| Solution            | Power Factor<br>Compensation | Negative-<br>Sequence<br>Current<br>Compensation | Zero-Sequence<br>Current<br>Compensation | Harmonic<br>Current<br>Compensation |

|---------------------|------------------------------|--------------------------------------------------|------------------------------------------|-------------------------------------|

|                     |                              | Passive Solutions                                |                                          |                                     |

| Shunt Capacitors    | ✓                            | ×                                                | ×                                        | <b>√</b> 1                          |

| Zig-zag Transformer | *                            | ×                                                | ✓                                        | <b>√</b> <sup>2</sup>               |

|                     |                              | Active Solutions                                 |                                          |                                     |

| Thyristor Switched  |                              |                                                  |                                          |                                     |

| Inductor and        | ✓                            | ×                                                | ×                                        | ×                                   |

| Capacitor           |                              |                                                  |                                          |                                     |

| 3-leg VSC           | $\checkmark$                 | ✓                                                | ×                                        | $\checkmark$                        |

| 6-leg VSC           | $\checkmark$                 | $\checkmark$                                     | ✓                                        | $\checkmark$                        |

| 3-leg NPC VSC       | $\checkmark$                 | ✓                                                | ✓                                        | $\checkmark$                        |

| 4-leg VSC           | $\checkmark$                 | $\checkmark$                                     | $\checkmark$                             | $\checkmark$                        |

<sup>✓</sup> indicates that the solution has the ability

\* indicates that the solution does not have the ability

¹ not normally intended for this purpose

<sup>&</sup>lt;sup>2</sup> can only compensate zero-sequence harmonic components

medium voltages have the potential to occupy less space and distribution system planners may use them more easily as with other equipment (e.g., shunt capacitors, voltage regulators).

#### **Multilevel Converters**

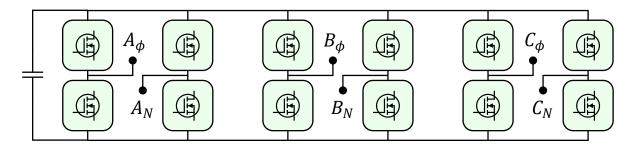

Multilevel converters have been suggested to achieve higher effective output voltages from the use of relatively low-voltage rated devices [19]. The breakdown voltages of semiconductor devices for high-voltage applications are reaching near 15 kV but the commercially available devices remain under 3.3 kV. Through special configurations of the low-voltage devices, these converters can achieve higher voltages by stacking these devices to form different "levels." There are many topologies available for active power exchange with the grid [19]. The three main topologies to consider are: The Diode-Clamped Multilevel Converter (DCMC), the Modular Multilevel Converter (MMC), and the Flying-Capacitor Multilevel Converter (FCMC).

The DCMC has the main advantage over the other two in that it does not require additional passives when adding levels to the converter. The main disadvantage is that the number of diodes increases exponentially with the number of required levels and the conduction losses can increase drastically as a result [20].

The MMC's main advantage is its modularity, lending itself to greater serviceability of the converter and can increase its reliability [21]. The main disadvantages are the number and size of the required capacitive components [22].

The FCMC has the main advantage of size reduction since the required capacitive energy storage is inversely proportional to the switching frequency [23, 24]. When compared to the MMC, which has a required energy storage inversely proportional to the line frequency, the FCMC has an obvious advantage. Like the MMC, this converter does not require the use of any

additional semiconductor devices and does not require any additional inductors. The main disadvantage of the FCMC is the complexity. The levels of the flying capacitor are not completely modular and balancing of the different capacitor levels may require additional control [25-33]. Five-level examples of these three converters in NPC configurations are shown in Figure 1-5.

#### 1.3 Challenges of Multilevel Converters

As the voltage produced by the converter increases some challenges can arise such as an increase in isolation and dv/dt immunity requirements [34-36]. When employing higher voltages in a converter, clearance and creepage distances must be increased at all levels of the design [37]. These issues together can increase the size of the converter. The use of isolation materials with high-voltage withstand capability must be used. This leads to the second potential result of these challenges, higher cost. In addition to the higher price of high-performance materials, custom power supply circuit configurations that can withstand the required voltage ratings in addition to the required dv/dt's must be used, which increases the cost. Even with the choice of more robust materials and topologies, the dv/dt experienced across an isolation barrier can still contribute to the degradation of the isolating material, resulting in a third challenge, reliability of the converter.

One area of particular concern where all these challenges converge are the power supplies for supplying power to the converter switching positions. Parasitic currents due to the switching behavior of the power semiconductor devices can, unless mitigated, flow through the parasitic capacitances of the power supply, gate driver ICs, and other isolating chips. These current transients have the ability to degrade the small digital-level signals and cause false

Figure 1-5. Main multilevel converter types: (a) DCMC (b) MMC (c) FCMC (d) MMC cell triggering of digital logic or corruption of analog measurements [34]. These issues can lead to unwanted turn-ON of power semiconductor devices or drive undesired controller behavior in the converter. For the voltage isolation requirement of  $\pm 12~\rm kV_{dc}$  and 7.9 kV<sub>ac</sub> and a dv/dt withstand

requirement of  $100-150 \text{ kV/}\mu\text{s}$  required by this project commercially available "off-the-shelf" power supplies are often not available. Table 1-2 shows some commercially available supplies that target high-voltage applications.

As previously mentioned, the commercial availability of semiconductor devices with appropriate breakdown voltage ratings decreases as the required breakdown voltage increases. Equipment manufacturers then assume a much larger risk in their supply chain when attempting to use higher voltage rating devices. A solution is using several low-voltage semiconductor devices connected in series to form a switching position with a higher effective breakdown voltage [38-40]. This type of scheme increases the complexity of each switching position in the converter but decreases the complexity of the converter topology [38-51].

#### 1.4 Proposed Solution for Unbalanced Current Static Compensation

A current compensator is suggested in this dissertation in the interest of alleviating the current imbalances experienced on distribution feeders. The following logic is used to derive an appropriate solution:

Table 1-2 Commercially available power supplies

| Part Number/Series | Manufacturer           | Isolation Voltage<br>Rating                 | Coupling<br>Capacitance |

|--------------------|------------------------|---------------------------------------------|-------------------------|

| RHV3               | Recom                  | 12.5 kV <sub>ac</sub> , 20 kV <sub>dc</sub> | 3.5 pF (4.0 pF max.)    |

| ISO5125I-120       | Power Integrations     | $12.5 \text{ kV}_{pk}$                      | 4.0 pF                  |

| REC6               | Recom                  | $5~kV_{ac},10~kV_{dc}$                      | 20.0 pF                 |

| DCHBA1-XXXXH8      | Wall Industries, Inc   | $8~\mathrm{kV_{dc}}$                        | 10.0 pF                 |

| 30EFL              | HVP                    | $30 \; kV_{dc}$                             | 40.0 pF max.            |

| PWR                | Murata                 | $4 \text{ kV}_{dc}, 8 \text{ kV}_{pk}$      | 10.0 pF                 |

| XE1000             | AEB Sapphire           | $15~kV_{dc},10~kV_{ac}$                     | -                       |

| SW25-25G           | Siebel Elektronik GmbH | $25 \mathrm{kV}_{\mathrm{ac}}$              | 10 pF                   |

- An active solution utilizing high-speed power semiconductor devices must be chosen for current compensation due to the enhanced functions and versatility compared to passive or hybrid solutions.

- A three-phase four-wire converter is required because of the applicability to unbalanced distribution systems in the United States.

- Eliminate the use of a step-up transformer to reduce a barrier to adoption by the electric utilities. Thus, connecting directly to the distribution system voltages requires the use of a multilevel converter.

- Solve the set of challenges, particularly with the availability of high-voltage semiconductor devices and the power supplies that can be used to drive them, that come with multilevel converters based on fast-switching semiconductor devices.

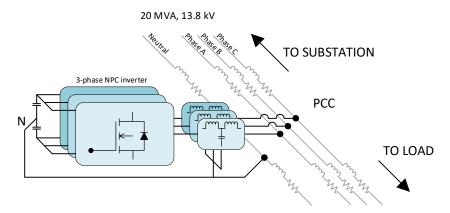

With all of this in mind, the solution chosen for this paper is a Medium-Voltage Unbalanced Current Static Compensator (MV-UCSC) that consists of a 13.8 kV three-phase four-wire, neutral-point-clamped, eleven-level, flying-capacitor converter.

In [52] and [53], FCCs with a high number of levels have been demonstrated at low voltages to produce efficient and compact designs. The use of the flying capacitor converter at medium-voltages has not been shown. Overall, there are very few experimental examples of multilevel medium-voltage converters of any kind in the literature [54, 55].

The MV-UCSC is made from 3.3 kV switching positions by utilizing two modular stackable 1.7 kV switching positions connected in series. These switching positions have self-powering ability, which allows them to provide on-board power to themselves for the gate drives and other auxiliary circuitry from the voltage across the switching position in the OFF state [56-58]. This eliminates the need for an external isolated power supply meeting the isolation and

dv/dt requirements. They also utilize voltage-balancing circuits that allows for series-connection of an arbitrary number of these switching positions to form an effectively higher voltage switching position.

#### 1.5 Objectives of the Dissertation

The objectives of the dissertation are as follows:

- 1. Provide an overview of the primary functions of the proposed MV-UCSC,

- 2. Show the effects of adding the MV-UCSC to existing conventional regulating equipment,

- 3. Describe the construction of the MV-UCSC and its the control algorithms,

- 4. Present the modular stackable switching positions used in the MV-UCSC,

- 5. Introduce an enhanced variant of the modular switching position, and

- 6. Lay out the final testing results from operation of the constructed MV-UCSC prototype at the NCREPT test facility.

#### 1.6 Organization of the Dissertation

The structure of this dissertation comes in three major tiers. The first one addresses the MV-UCSC functionality at the distribution system level. The operation of the MV-UCSC along with some non-obvious applications are provided in Chapter 2. The consequence of a MV-UCSC installation with respect to the function of traditional compensation equipment that is installed at the substation is demonstrated in Chapter 3.

The second tier narrows the focus onto the converter itself as reflected in Chapter 4 where the construction and simulation of the MV-UCSC as a non-ideal system are presented.

The third tier narrows the focus even further to the development of a modular stackable switching position for use within the MV-UCSC. The design theory, simulation, and testing of this modular stackable switching position as well as modification required for its use in half-bridge configurations are presented in Chapter 5. The switching position concept and variation of the switching position in Chapter 5 are given in Chapter 6. All these analyses are experimentally verified in Chapter 7 where the testing results of the proposed MV-UCSC as a grid-connected current compensator utilizing the switching positions from Chapter 5 are shown.

Finally, major conclusions from this work along with suggestions for future work are provided in Chapter 8. Appendices have been included to enable easier recreation of the work described in this dissertation.

#### 1.7 Major Contributions of this Research

The major contributions are the development of a modular stackable switching position and the design and implementation of this modular switching position within a medium-voltage converter. Table 1-3 summarizes the details of each of these contributions.

#### **Modular Switching Position**

- Improved a voltage balancing circuit such that it is suitable for half-bridge operation [59].

- Provided a previously non-existent quantitative design methodology for choosing component values for the voltage balancing circuit of series-connected devices [59].

- Reconfigured an existing self-powered circuit to allow for self-powering at any voltage and thus a soft-starting mechanism using a simplified implementation [59].

- Developed a start-up routine for a half-bridge configuration of the modular stackable switching positions by leveraging the proposed soft-start mechanism of the switching position [59].

#### **MV-UCSC** with the Switching Position

- Designed and built a 13.8 kV, 11-level NPC FCC (Chapter 4).

- Combined two instances of the 1.7 kV switching position in series to form an effective 3.3 kV switching position [59].

- Demonstrated the use of a modular stackable switching positions within a half-bridge configuration (Chapter 7).

- Confirmed the operation of custom ridethrough, voltage regulating and fault handling of the switching position with the MV-UCSC (Chapter 7).

- Connected the MV-UCSC directly to a medium-voltage system with unbalanced loading and confirmed upstream current balancing (Chapter 7).

#### 1.8 References

- [1] T. Gonen, Electric Power Distribution Engineering, Third Edition. CRC Press, 2015.

- [2] A. P. S. Meliopoulos, J. Kennedy, C. A. Nucci, A. Borghetti, and G. Contaxis, "Power distribution practices in USA and Europe: impact on power quality," in 8th International Conference on Harmonics and Quality of Power. Proceedings (Cat. No.98EX227), 1998, vol. 1, pp. 24-29 vol.1.

- [3] R. G. Harley, E. B. Makram, and E. G. Duran, "The effects of unbalanced networks on synchronous and asynchronous machine transient stability," *Electric Power System Research*,

- [4] W. J. Lee, T. Y. Ho, J. P. Liu, and Y. H. Liu, "Negative sequence current reduction for generator/turbine protection," in *Conference Record of the 1993 IEEE Industry Applications Conference Twenty-Eighth IAS Annual Meeting*, 1993, pp. 1428-1433 vol.2.

- [5] R. H. Salim, R. A. Ramos, and N. G. Bretas, "Analysis of the small signal dynamic performance of synchronous generators under unbalanced operating conditions," in *IEEE PES General Meeting*, 2010, pp. 1-6.

- [6] B. N. Gafford, W. C. Duesterhoeft, and C. C. Mosher, "Heating of Induction Motors on Unbalanced Voltages," *Transactions of the American Institute of Electrical Engineers. Part III: Power Apparatus and Systems*, vol. 78, no. 3, pp. 282-286, 1959.

- [7] T. A. Short, *Electrical Power Distribution Handbook*. Boca Raton, FL: CRC Press Taylor & Taylor Group, 2004.

- [8] R. M. C. L.F. Ochoa, A. Padilha-Feltrin, G.P. Harrison, "Evaluation of distribution system losses due to load unbalance," presented at the 15th Power Systems Computation Conference PSCC 2005, Liège, Belgium, 2005-08-22, 2005.

- [9] T. H. Chen, "Evaluation of line loss under load unbalance using the complex unbalance factor," *IEE Proceedings Generation, Transmission and Distribution*, vol. 142, no. 2, pp. 173-178, 1995.

- [10] G. Chicco, F. Corona, R. Porumb, and F. Spertino, "Experimental Indicators of Current Unbalance in Building-Integrated Photovoltaic Systems," *IEEE Journal of Photovoltaics*, vol. 4, no. 3, pp. 924-934, 2014.

- [11] R. Yan and T. K. Saha, "Voltage Variation Sensitivity Analysis for Unbalanced Distribution Networks Due to Photovoltaic Power Fluctuations," *IEEE Transactions on Power Systems*, vol. 27, no. 2, pp. 1078-1089, 2012.

- [12] J. Hurng-Liahng, W. Jinn-Chang, W. Kuen-Der, C. Wen-Jung, and C. Yi-Hsun, "Analysis of zig-zag transformer applying in the three-phase four-wire distribution power system," *IEEE Transactions on Power Delivery*, vol. 20, no. 2, pp. 1168-1173, 2005.

- [13] L. Wang, C. S. Lam, and M. C. Wong, "Selective Compensation of Distortion, Unbalanced and Reactive Power of a Thyristor-Controlled LC -Coupling Hybrid Active Power Filter (TCLC-HAPF)," *IEEE Transactions on Power Electronics*, vol. 32, no. 12, pp. 9065-9077, 2017.

- [14] M. V. M. Kumar and M. K. Mishra, "Dual distribution static compensator for three-phase four-wire distribution system," *IET Generation, Transmission & Distribution*, vol. 10, no. 2, pp. 399-411, 2016.

- [15] D. Ning-Yi, W. Man-Chung, and H. Ying-Duo, "Application of a three-level NPC inverter as a three-phase four-wire power quality compensator by generalized 3DSVM," *IEEE Transactions on Power Electronics*, vol. 21, no. 2, pp. 440-449, 2006.

- [16] V. Jones, "Correcting Current Imbalances in Three-Phase Four-Wire Distribution Systems," MSEE Masters, Electrical Engineering, University of Arkansas, University of Arkansas, 2016.

- [17] V. Jones, J. C. Balda, and R. Adapa, "Analysis of a Grid-Connected Shoot-Through Current Immune Three-Phase Converter Topoloy under Unbalanced Loading Conditions," in 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), 2018, pp. 1-7.

- [18] V. Jones and J. C. Balda, "Correcting current imbalances in three-phase four-wire distribution systems," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), 2016, pp. 1387-1391.

- [19] M. Vijeh, M. Rezanejad, E. Samadaei, and K. Bertilsson, "A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View," *IEEE Transactions on Power Electronics*, vol. 34, no. 10, pp. 9479-9502, 2019.

- [20] J. Rodriguez, L. Jih-Sheng, and P. Fang Zheng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 724-738, 2002.

- [21] D. Cottet *et al.*, "Integration technologies for a medium voltage modular multi-level converter with hot swap capability," in *2015 IEEE Energy Conversion Congress and Exposition (ECCE)*, 2015, pp. 4502-4509.

- [22] M. Merlin and T. Green, "Cell capacitor sizing in multilevel converters: Cases of the modular multilevel converter and alternate arm converter," *IET Power Electronics*, vol. 8, pp. 350-360, 03/01 2015.

- [23] Y. Sato, M. Iimura, Y. Dodo, and H. Obara, "A study on minimum required capacitance in flying capacitor multilevel converters for grid-connected applications," in *2015 IEEE Energy Conversion Congress and Exposition (ECCE)*, 2015, pp. 3502-3507.

- [24] D. Jiao, Q. Huang, and A. Q. Huang, "Evaluation of Medium Voltage SiC Flying Capacitor Converter and Modular Multilevel Converter," in *2020 IEEE Energy Conversion Congress and Exposition (ECCE)*, 2020, pp. 4386-4392.

- [25] J. Amini, "An Effortless Space-Vector-Based Modulation for N-level Flying Capacitor Multilevel Inverter With Capacitor Voltage Balancing Capability," *IEEE Transactions on Power Electronics*, vol. 29, no. 11, pp. 6188-6195, 2014.

- [26] J. Amini, A. H. Viki, A. Radan, and M. Moallem, "A General Active Capacitor Voltage Regulating Method for L-Level M-Cell N-Phase Flying Capacitor Multilevel Inverter With Arbitrary DC Voltage Distribution," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 5, pp. 2659-2668, 2016.

- [27] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Improved Natural Balancing With Modified Phase-Shifted PWM for Single-Leg Five-Level Flying-Capacitor Converters," *IEEE Transactions on Power Electronics*, vol. 27, no. 4, pp. 1658-1667, 2012.

- [28] T. A. Meynard, M. Fadel, and N. Aouda, "Modeling of multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 44, no. 3, pp. 356-364, 1997.

- [29] C. Feng, J. Liang, and V. G. Agelidis, "Modified Phase-Shifted PWM Control for Flying Capacitor Multilevel Converters," *IEEE Transactions on Power Electronics*, vol. 22, no. 1, pp. 178-185, 2007.

- [30] R. H. Wilkinson, "Natural Balancing of Multicell Converters," Dissertation, Electrical Engineering, University of Stellenbosch, University of Stellenbosch, 2004.

- [31] B. P. McGrath, T. Meynard, G. Gateau, and D. G. Holmes, "Optimal Modulation of Flying Capacitor and Stacked Multicell Converters Using a State Machine Decoder," *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 508-516, 2007.

- [32] K. Dae-Wook, L. Byoung-Kuk, J. Jae-Hyun, K. Tae-Jin, and H. Dong-Seok, "A symmetric carrier technique of CRPWM for voltage balance method of flying-capacitor multilevel inverter," *IEEE Transactions on Industrial Electronics*, vol. 52, no. 3, pp. 879-888, 2005.

- [33] P. Papamanolis, D. Neumayr, and J. W. Kolar, "Behavior of the flying capacitor converter under critical operating conditions," in 2017 IEEE 26th International Symposium on Industrial Electronics (ISIE), 2017, pp. 628-635.

- [34] V.-S. Nguyen, L. Kerachev, P. Lefranc, and J.-C. Crebier, "Characterization and Analysis of an Innovative Gate Driver and Power Supplies Architecture for HF Power Devices With High dv/dt," *IEEE Transactions on Power Electronics*, vol. 32, no. 8, pp. 6079-6090, 2017.

- [35] V. S. Nguyen, P. Lefranc, and J. C. Crebier, "Gate driver supply architectures for common mode conducted EMI reduction in series connection of multiple power devices," *IEEE Transactions on Power Electronics*, pp. 1-1, 2018.

- [36] B. Sarrazin, R. Hanna, P. Lefranc, S. Am, F. Dumas, and J. P. Lavieville, "Insulated power supply for gate drivers up to 40kV for medium-voltage direct current applications," *IET Power Electronics*, vol. 10, no. 15, pp. 2143-2148, 2017.

- [37] Insulation coordination for equipment within low-voltage systems IEC/CEI 60664-1:2007 2007.

- [38] H. Wang, A. Q. Huang, and F. Wang, "Development of a Scalable Power Semiconductor Switch (SPSS)," *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 364-373, 2007.

- [39] K. Vechalapu, S. Hazra, U. Raheja, A. Negi, and S. Bhattacharya, "High-speed medium voltage (MV) drive applications enabled by series connection of 1.7 kV SiC MOSFET devices," in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), 2017, pp. 808-815.

- [40] K. Sasagawa, Y. Abe, and K. Matsuse, "Voltage-balancing method for IGBTs connected in series," *IEEE Transactions on Industry Applications*, vol. 40, no. 4, pp. 1025-1030, 2004.

- [41] F. Zhang, X. Yang, Y. Ren, L. Feng, W. Chen, and Y. Pei, "A Hybrid Active Gate Drive for Switching Loss Reduction and Voltage Balancing of Series-Connected IGBTs," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7469-7481, 2017.

- [42] L. Shu, J. Zhang, F. Peng, and Z. Chen, "Active Current Source IGBT Gate Drive With Closed-Loop di/dt and dv/dt Control," *IEEE Transactions on Power Electronics*, vol. 32, no. 5, pp. 3787-3796, 2017.

- [43] G. Busatto, B. Cascone, L. Fratelli, and A. Luciano, "Series connection of IGBTs in hard-switching applications," in *Conference Record of 1998 IEEE Industry Applications Conference. Thirty-Third IAS Annual Meeting (Cat. No.98CH36242)*, 1998, vol. 2, pp. 825-830 vol.2.

- [44] B. Ju Won, Y. Dong-Wook, and K. Heung-Geun, "High-voltage switch using series-connected IGBTs with simple auxiliary circuit," *IEEE Transactions on Industry Applications*, vol. 37, no. 6, pp. 1832-1839, 2001.

- [45] J. Saiz, M. Mermet, D. Frey, P. O. Jeannin, J. L. Schanen, and P. Muszicki, "Optimisation and integration of an active clamping circuit for IGBT series association,"

- in Conference Record of the 2001 IEEE Industry Applications Conference. 36th IAS Annual Meeting (Cat. No.01CH37248), 2001, vol. 2, pp. 1046-1051 vol.2.

- [46] N. Teerakawanich and C. M. Johnson, "Design Optimization of Quasi-Active Gate Control for Series-Connected Power Devices," *IEEE Transactions on Power Electronics*, vol. 29, no. 6, pp. 2705-2714, 2014.

- [47] J. Biela, D. Aggeler, D. Bortis, and J. W. Kolar, "Balancing Circuit for a 5-kV/50-ns Pulsed-Power Switch Based on SiC-JFET Super Cascode," *IEEE Transactions on Plasma Science*, vol. 40, no. 10, pp. 2554-2560, 2012.

- [48] L. Zhang, S. Sen, and A. Q. Huang, "7.2-kV/60-A Austin SuperMOS: An Intelligent Medium-Voltage SiC Power Switch," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 8, no. 1, pp. 6-15, 2020.

- [49] Y. Ren *et al.*, "A Compact Gate Control and Voltage-Balancing Circuit for Series-Connected SiC MOSFETs and Its Application in a DC Breaker," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 10, pp. 8299-8309, 2017.

- [50] C. Yang *et al.*, "A Gate Drive Circuit and Dynamic Voltage Balancing Control Method Suitable for Series-Connected SiC mosfets," *IEEE Transactions on Power Electronics*, vol. 35, no. 6, pp. 6625-6635, 2020.

- [51] A. F. Guerrero-Guerrero, A. J. Ustariz-Farfan, H. E. Tacca, and E. A. Cano-Plata, "IGBT Series Connection With Soft Switching and Power Recovery in Driver Power Supply," *IEEE Transactions on Power Electronics*, vol. 34, no. 12, pp. 11679-11691, 2019.

- [52] T. Modeer, N. Pallo, T. Foulkes, C. B. Barth, and R. C. N. Pilawa-Podgurski, "Design of a GaN-Based Interleaved Nine-Level Flying Capacitor Multilevel Inverter for Electric Aircraft Applications," *IEEE Transactions on Power Electronics*, vol. 35, no. 11, pp. 12153-12165, 2020.

- [53] N. Pallo, S. Coday, J. Schaadt, P. Assem, and R. C. N. Pilawa-Podgurski, "A 10-Level Flying Capacitor Multi-Level Dual-Interleaved Power Module for Scalable and Power-Dense Electric Drives," in 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 893-898.

- [54] S. Madhusoodhanan *et al.*, "Harmonic Analysis and Controller Design of 15 kV SiC IGBT-Based Medium-Voltage Grid-Connected Three-Phase Three-Level NPC Converter," *IEEE Transactions on Power Electronics*, vol. 32, no. 5, pp. 3355-3369, 2017.

- [55] S. Madhusoodhanan *et al.*, "Solid-State Transformer and MV Grid Tie Applications Enabled by 15 kV SiC IGBTs and 10 kV SiC MOSFETs Based Multilevel Converters," *IEEE Transactions on Industry Applications*, vol. 51, no. 4, pp. 3343-3360, 2015.

- [56] W. Hongfang and F. Wang, "A self-powered resonant gate driver for high power MOSFET modules," in *Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, 2006. APEC '06.*, 2006, p. 6 pp.

- [57] J. C. Crebier and N. Rouger, "Loss Free Gate Driver Unipolar Power Supply for High Side Power Transistors," *IEEE Transactions on Power Electronics*, vol. 23, no. 3, pp. 1565-1573, 2008.

- [58] S. Busquets-Monge, D. Boroyevich, R. Burgos, and Z. Chen, "Performance analysis and design optimization of a self-powered gate-driver supply circuit," in *2010 IEEE International Symposium on Industrial Electronics*, 2010, pp. 979-985.

- [59] V. Jones, R. A. Fantino, and J. C. Balda, "A Modular Switching Position with Voltage-Balancing and Self-Powering for Series Device Connection," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, pp. 1-1, 2020.

#### **CHAPTER 2**

# CURRENT COMPENSATORS FOR UNBALANCED ELECTRIC DISTRIBUTION SYSTEMS

V. Jones, J. C. Balda and R. Adapa, "Current Compensators for Unbalanced Electric Distribution Systems," *2018 IEEE Electronic Power Grid (eGrid)*, Charleston, SC, 2018, pp. 1-6.

#### 2.1 Abstract

Inherent current imbalances are often present in electric distribution systems due to the increase of single-phase generation in the form of renewables and the existence of single-phase loads. The continued expansion of non-linear load usage is also increasing the levels of harmonics through the power transformers servicing these distribution systems. The issues that arise from these operating conditions are widely known and standard solutions used by utilities are as well. However, they are often bulky and do not provide a level of control or versatility appropriate for these challenges. This paper gives an overview of many of the problems that are faced on distribution systems and how an active shunt compensator may be used to mitigate or eliminate them.

#### 2.2 Introduction

Distribution systems normally operate under certain amount of unbalanced loading, especially for residential systems, due to single-phase loads. The issue is exacerbated by single-phase generation in the form of rooftop solar which has seen significant increase in certain areas. Though large-scale three-phase solar generation remains by and large the majority of solar generation this does not eliminate the unbalanced nature of the loading. The issues associated with the negative- and zero-sequence current resulting from unbalanced loads are well documented [1-6]. For example: overheating of a generator, improper sizing of neutral

conductors, MMF ripples inside the generator due to negative-sequence MMFs and overheating of the holding tank for ungrounded wye-connected transformers. Efficiency of the total system is also adversely affected [7, 8].

One of the most prominent issues is the voltage profile along the feeder. Utilities use load rebalancing, load-tap changers, and reactive FACTS devices to meet voltage standards. At the three-phase feeder level, there is extensive research into techniques that can be used to optimize tap scheduling and the allocation of load among the available feeders, many of which are summarized in [9]. These algorithms are used to optimize a set of variables, not just load distribution, and many do not consider the effects of load imbalance which can greatly affect the analysis [10]. They also rely heavily on the prediction of the loading curve. This can be difficult when trying to design for new load centers, especially in rural areas [11, 12].

FACTS devices are currently used to augment the existing transmission systems; however, the use of power-electronics-based FACTS at the distribution level is still in its infancy. In this paper, the application of a shunt "unbalanced current static compensator" (UCSC) will be evaluated with respect to (1) the issues mentioned above, (2) a modernizing grid with increasing distributed generation, and (3) an expanding interest in a microgrid-based distribution system.

The remainder of this paper is organized as follows: the main and secondary applications of a shunt compensator are presented in sections 2.3 and 2.4, respectively. Simulation results and main implementation challenges for the proposed compensator are given in sections 2.5 and 2.6. Last thoughts are given in section 2.7.

# 2.3 Primary Applications of a Shunt Compensator

Reliability of service is a crucial criterion because customers expect consistent and limitless power availability. This requires a certain amount of margin between the nominal load and maximum feeder ratings at any given time to allow for contingencies. Unbalanced load currents add another level of complexity to the problem because any optimization effort needs to consider each phase of the feeder separately to achieve the true system-level optimal.

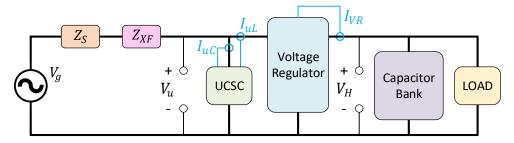

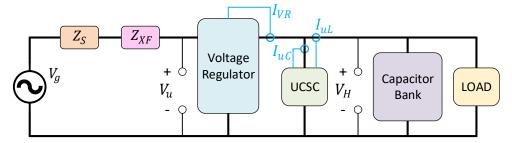

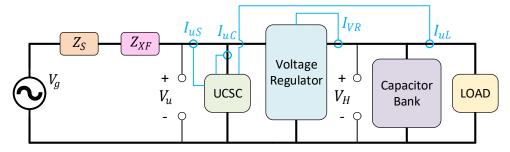

An UCSC installed near a distribution substation is shown in Figure 2-1. In this configuration on a traditional feeder, a shunt compensator can balance the currents seen by the substation, bring unity power factor (leveraging existing shunt capacitor banks), potentially dampen power oscillations during transient events, and compensate for harmonic currents that are produced by non-linear loads [13, 14].

Figure 2-1. Connection of the UCSC to a three-phase feeder.

#### 2.3.1 Current Balancing

When each phase of the feeder is carrying different and varying currents the UCSC can draw additional current from the less loaded phases and circulate that current onto phases that are more heavily loaded. This forces the current seen upstream to the average of the three phases, helping to eliminate any upstream fundamental frequency neutral current. This improves the efficiency of electric machines connected to the grid, can improve the efficiency of the system, and can improve the voltage balance at the point of common coupling by balancing the voltage drop across the upstream impedance [4].

Around 7.7% of billable energy was lost in transmission and distribution systems in the United States in 2016 [15]. Using the average retail price that implies approximately \$31.5 billion dollars in lost revenue. Taking a transmission line with equal line resistance and an average current unbalance term,  $\gamma$ , the three-phase currents can be defined as:

$$I_{abc,rms} = \begin{bmatrix} I_{avg}(1+\gamma) \\ I_{avg}(1-\gamma) \\ I_{avg} \end{bmatrix} , \quad 0 \le \gamma \le 1$$

(1)

where Iavg is the average RMS current of the phases. The proportional energy loss in the transmission line can be expressed as:

$$E_{3\phi} \propto I_{avg}^2(2\gamma^2 + 3) \tag{2}$$

In Figure 2-2 the lost revenue due to transmission losses is plotted against varying  $\gamma$  for the cases in which transmission line losses amount to 1%, 2%, and 3% of the total billable energy. For the sake of argument, transmission lines were assumed to be operating at a  $\gamma$  of 0.25 for the 7.7% losses quoted above.

Figure 2-2. Lost revenue due to unbalances.

These calculations are simple averages that do not reflect the varying nature of loading or \$\footnote{MWh}\$ for the electric power grid, but they do reflect the potential savings for utilities that experience unbalanced loading conditions.

## 2.3.2 Power Factor Regulation

Regulating the power factor to unity helps to improve the total system efficiency by reducing losses accrued in the upstream transmission lines through reactive current reduction.

When used in conjunction with relatively cheap and well-known switched shunt capacitor banks the rating of the UCSC can be significantly reduced. While the shunt capacitor banks compensate for most of the reactive power they can only be switched in units of around 50

kVAR per phase [16]. The UCSC can provide nearly infinite steps of reactive power within a smaller range. This

- maintains unity power factor at all operating points,

- reduces potentially the number of operations for the switched capacitor bank and thus, reduces the number transient events from the changing taps in a capacitor bank, and