# A 10GB/S FULL ON-CHIP BANG-BANG CLOCK AND DATA RECOVERY SYSTEM USING AN ADAPTIVE LOOP BANDWIDTH STRATEGY

A Thesis

by

### HYUNG-JOON JEON

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

August 2009

Major Subject: Electrical Engineering

### A 10GB/S FULL ON-CHIP

## BANG-BANG CLOCK AND DATA RECOVERY SYSTEM USING AN ADAPTIVE LOOP BANDWIDTH STRATEGY

A Thesis

by

### HYUNG-JOON JEON

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved by:

| Chair of Committee, | Jose Silva-Martinez    |

|---------------------|------------------------|

| Committee Members,  | Edgar Sanchez-Sinencio |

|                     | Peng Li                |

|                     | Alexander Parlos       |

| Head of Department, | Costas N. Georghiades  |

August 2009

Major Subject: Electrical Engineering

#### ABSTRACT

A 10Gb/s Full On-chip Bang-Bang Clock and Data Recovery System Using an Adaptive Loop Bandwidth Strategy.

(August 2009)

Hyung-Joon Jeon,

B.S., Seoul National University

Chair of Advisory Committee: Dr. Jose Silva-Martinez

As demand for higher bandwidth I/O grows, the front end design of serial link becomes significant to overcome stringent timing requirements on noisy and bandwidthlimited channels. As a clock reconstructing module in a receiver, the recovered clock quality of Clock and Data Recovery is the main issue of the receiver performance. However, from unknown incoming jitter, it is difficult to optimize loop dynamics to minimize steady-state and dynamic jitter.

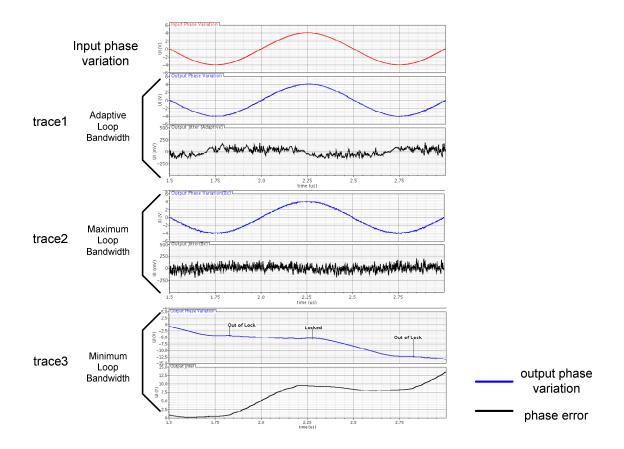

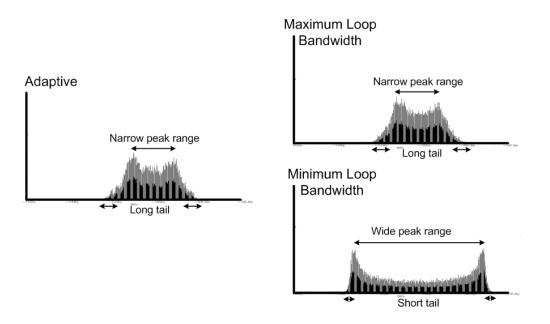

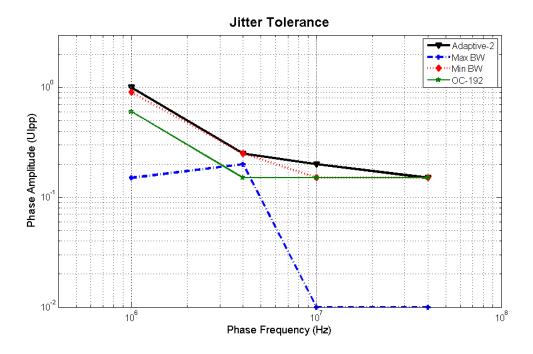

In this thesis a 10 Gb/s adaptive loop bandwidth clock and data recovery circuit with on-chip loop filter is presented. The proposed system optimizes the loop bandwidth adaptively to minimize jitter so that it leads to an improved jitter tolerance performance. This architecture tunes the loop bandwidth by a factor of eight based on the phase information of incoming data. The resulting architecture performs as good as a maximum fixed loop bandwidth CDR while tracking high speed input jitter and as good as a minimum fixed bandwidth CDR while suppressing wide bandwidth steady-state jitter. By employing a mixed mode predictor, high updating rate loop bandwidth adaptation is achieved with low power consumption. Another relevant feature is that it integrates a typically large off-chip filter using a capacitance multiplication technique that employs dual charge pumps.

The functionality of the proposed architecture has been verified through schematic and behavioral model simulations. In the simulation, the performance of jitter tolerance is confirmed that the proposed solution provides improved results and robustness to the variation of jitter profile. Its applicability to industrial standards is also verified by the jitter tolerance passing SONET OC-192 successfully.

To my parents and sister

#### ACKNOWLEDGEMENTS

Since the summer of 2006, I have enjoyed studying in the AMSC group. One of my best moments in the past three years was when I began to work with my advisor, Dr. J.Silva-martinez. His advice enriched my academic knowledge and his support encouraged me to focus on what I really love to study. Thanks to him, I now see myself much better than when I started my degree.

I would like to thank my committee members, Dr. E.Sanchez-Sinencio, Dr. Peng Li and Dr.Alexander Parlos, for their time and their valuable and important suggestions.

Working with my teammates, Ragahvendra, Jusung and Yung-Chung, always stimulated my academic passion through discussions and cooperation. I am grateful for their help and friendship. I would also like to thank all my other friends in AMSC, in particular, Joungwon, Seokmin, Younghoon, Marcos, Mohan, Barry, Charles, CJ, Salvador and Saikrishna for the happy times we shared.

Last but not least, I would like to thank all who prayed for me. I couldn't do anything if it weren't for you.

### TABLE OF CONTENTS

| ABSTRACT       |                                                                                                                                                                                                  | iii            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| DEDICATION     |                                                                                                                                                                                                  | v              |

| ACKNOWI        | LEDGEMENTS                                                                                                                                                                                       | vi             |

| TABLE OF       | CONTENTS                                                                                                                                                                                         | vii            |

| LIST OF FI     | GURES                                                                                                                                                                                            | ix             |

| LIST OF TABLES |                                                                                                                                                                                                  | xii            |

| CHAPTER        |                                                                                                                                                                                                  |                |

| Ι              | INTRODUCTION                                                                                                                                                                                     | 1              |

|                | <ul><li>1.Overview of Clock and Data Recovery in Serial Link</li><li>2.Topologies of Clock and Data Recovery</li><li>3.Organization</li></ul>                                                    | 1<br>4<br>8    |

| II             | ANALYSIS OF ANALOG BANG-BANG PHASE LOCKED LOOP<br>FOR CLOCK AND DATA RECOVERY APPLICATION                                                                                                        | 10             |

|                | <ol> <li>Background of Analog Bang-Bang PLL</li> <li>The Jitter Specifications in Bang-Bang Clock and Data Recovery</li> <li>Jitter Tolerance Improvement of Bang-Bang Clock and Data</li> </ol> | 10<br>20       |

|                | Recovery                                                                                                                                                                                         | 29<br>33       |

| III            | ADAPTIVE LOOP BANDWIDTH CLOCK AND DATA<br>RECOVERY                                                                                                                                               | 34             |

|                | 1.Loop Bandwidth Adaptation<br>1.1 Loop Bandwidth Adjustment with Charge Pump Current                                                                                                            | 34             |

|                | Control<br>1.2 Prediction with Mixed Mode Piece-wise Integration<br>2.System Overview                                                                                                            | 34<br>38<br>45 |

|                | 3.Predictor Design                                                                                                                                                                               | 43<br>47       |

|         | 4.Dual Variable Charge Pump Design                        | 56  |

|---------|-----------------------------------------------------------|-----|

|         | 5.Half-rate Phase Detector Design                         | 60  |

|         | 6. Analysis of Adaptive Bang-Bang Clock and Data Recovery | 65  |

|         | 6.1 Stability Characteristics                             | 65  |

|         | 6.2 The Decision of the Predictor Parameters              | 72  |

|         | 7.Summary                                                 | 78  |

| IV      | SIMULATION RESULT                                         | 80  |

|         | 1.Loop Bandwidth Control Dynamics                         | 80  |

|         | 2. Jitter Histogram                                       | 82  |

|         | 3. Jitter Tolerance                                       | 87  |

|         | 4.Design Summary                                          | 95  |

| V       | CONCLUSION                                                | 96  |

| REFEREN | CES                                                       | 98  |

| VITA    |                                                           | 102 |

Page

### LIST OF FIGURES

| FIGURE |                                                                                 |    |

|--------|---------------------------------------------------------------------------------|----|

| 1.1    | Front end in serial link application                                            | 2  |

| 1.2    | Analog PLL based CDR                                                            | 5  |

| 1.3    | Digital PLL based CDR                                                           | 6  |

| 1.4    | Semi-digital type CDR                                                           | 6  |

| 2.1    | The conceptual model of analog PLL (a) Linear PLL<br>(b) Bang-Bang PLL          | 11 |

| 2.2    | (a) Phase offset issue of Hogge Detector (b) Alexander PD                       | 12 |

| 2.3    | Slope overloaded output in BBPLL                                                | 13 |

| 2.4    | Transfer curve variation of BBPD                                                | 17 |

| 2.5    | Measurement of jitter transfer                                                  | 20 |

| 2.6    | Jitter transfer curve of BBPLL                                                  | 21 |

| 2.7    | Measurement of jitter generation                                                | 23 |

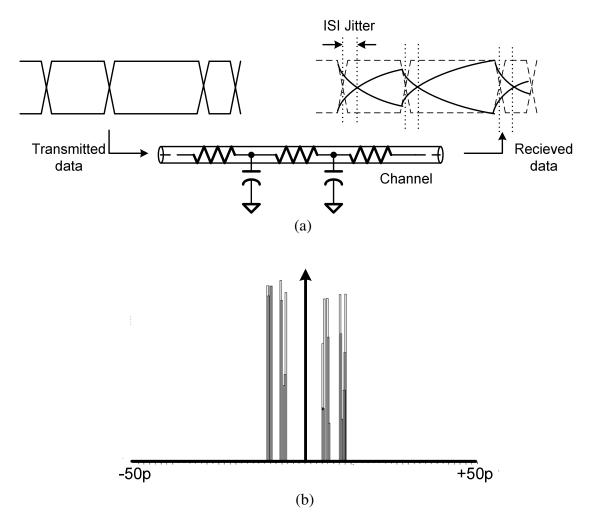

| 2.8    | (a) Generation of ISI and (b) its PDF                                           | 24 |

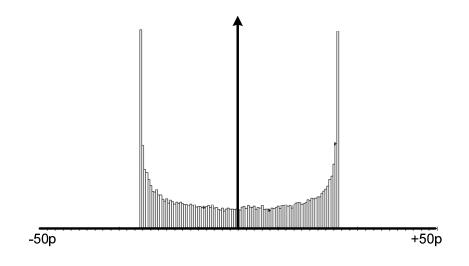

| 2.9    | PDF of sinusoidal jitter                                                        | 25 |

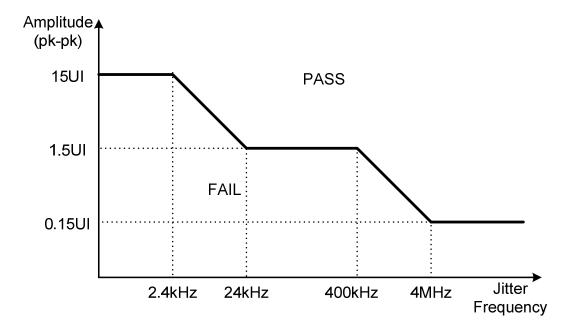

| 2.10   | SONET OC-192 jitter tolerance mask                                              | 26 |

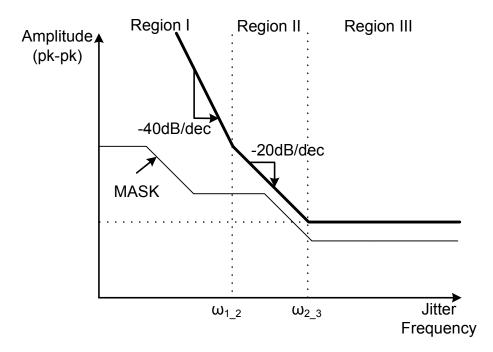

| 2.11   | Jitter tolerance of BBCDR                                                       | 27 |

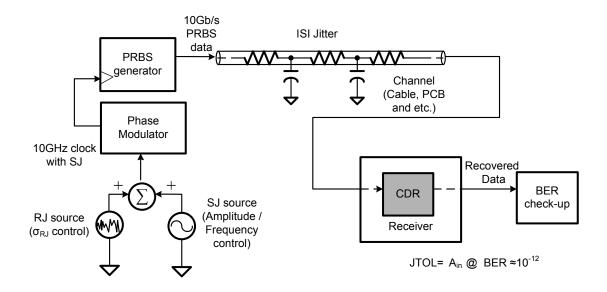

| 2.12   | Measurement of jitter tolerance                                                 | 29 |

| 2.13   | The characteristics of (a) narrow loop bandwidth and (b) wide loop bandwidth    | 30 |

| 3.1    | Jitter tolerance variation with (a) CP current control and (b) resistor control | 35 |

| FIGURE |                                                                                                      |    |

|--------|------------------------------------------------------------------------------------------------------|----|

| 3.2    | The example of resistor controlled scheme                                                            | 38 |

| 3.3    | The conceptual diagram of adaptive delta-sigma modulator                                             | 40 |

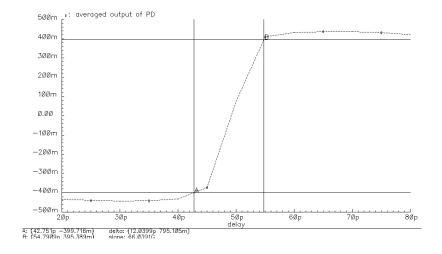

| 3.4    | The effect of BBPD on the integration                                                                | 41 |

| 3.5    | The conceptual diagram of the predictor                                                              | 42 |

| 3.6    | The effect of loop bandwidth updating rate                                                           | 44 |

| 3.7    | The architecture of proposed adaptive loop bandwidth BBCDR                                           | 45 |

| 3.8    | The architecture of the predictor                                                                    | 47 |

| 3.9    | Piece-wise integration with switched capacitor network                                               | 48 |

| 3.1    | 0 The schematic of analog front end of piece-wise integrator                                         | 49 |

| 3.1    | 1 The architecture of absolute A/D converter                                                         | 51 |

| 3.1    | 2 The timing diagram of the predictor operation                                                      | 52 |

| 3.1    | 3 The comparator schematic of A/D converter                                                          | 53 |

| 3.1    | 4 The state diagram of digital counter                                                               | 53 |

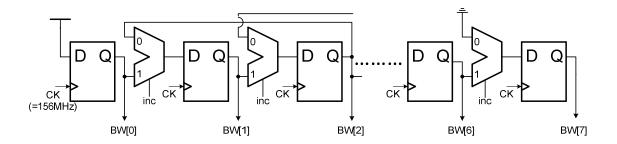

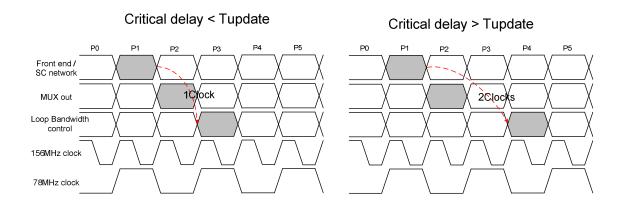

| 3.1    | 5 The implementation of bi-directional shift registers for digital counter                           | 54 |

| 3.1    | 6 The effect of logic delay on the loop bandwidth updating time                                      | 55 |

| 3.1    | 7 Implementations of variable current charge pump (a) binary control and<br>(b) thermo-meter control | 56 |

| 3.1    | 8 Capacitor multiplication in high speed application                                                 | 59 |

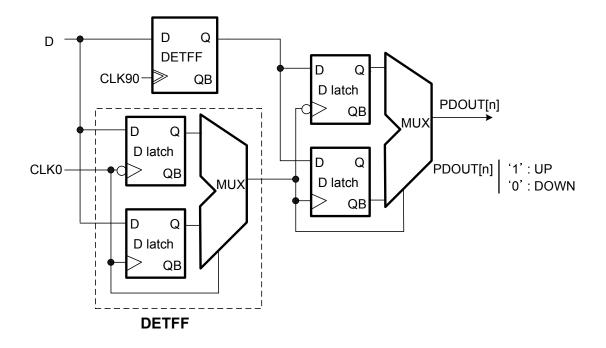

| 3.1    | 9 A half-rate Bang-Bang phase detector                                                               | 61 |

| 3.2    | 0 The timing diagram of the half-rate BBPD                                                           | 61 |

| 3.2    | 1 Current mode logic family for the BBPD                                                             | 62 |

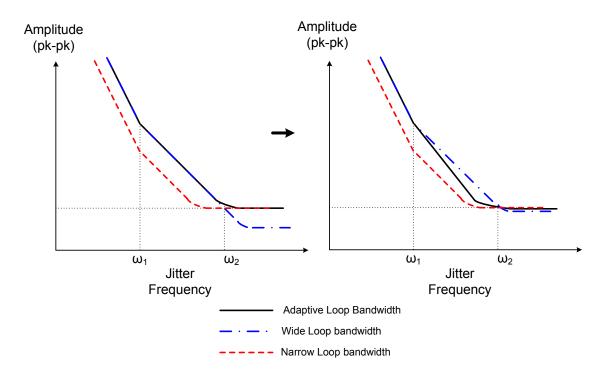

| 3.2    | 2 Jitter tolerance improvement with adaptive loop bandwidth                                          | 66 |

| JURE |                                                                                                                                                               | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

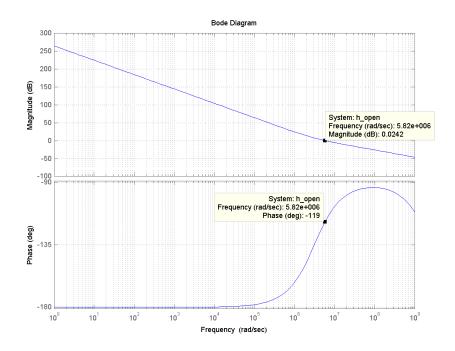

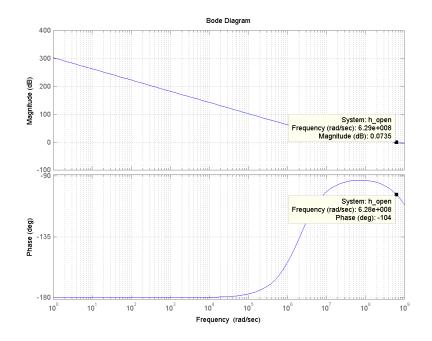

| 3.23 | Bode plot of the minimum bandwidth setup                                                                                                                      | 70   |

| 3.24 | Transfer function of BBPD                                                                                                                                     | 71   |

| 3.25 | Bode plot of the maximum bandwidth setup                                                                                                                      | 71   |

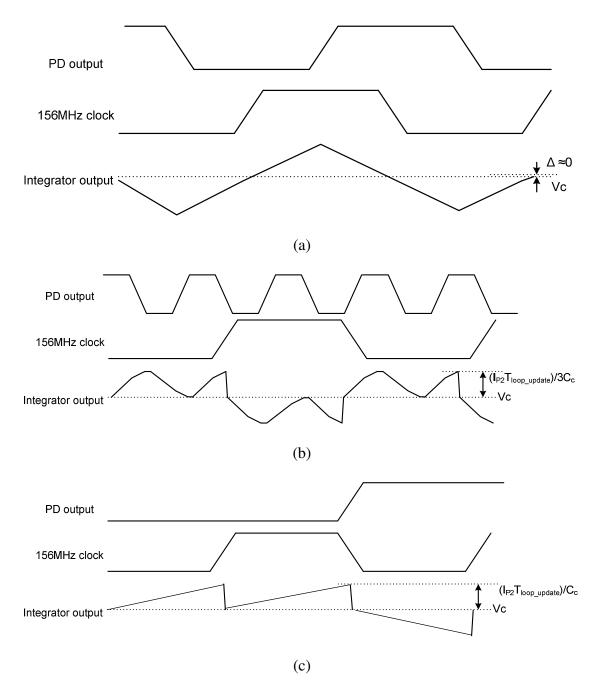

| 3.26 | Maximum integrator output if (a) limit cycle period = updating period<br>(b) limit cycle period < updating period (c) limit cycle period > updating<br>period | 76   |

| 3.27 | The effect of the updating rate on the loop bandwidth control                                                                                                 | 77   |

| 3.28 | The effect of the threshold points of A/D conversion on the loop bandwidth control                                                                            | 78   |

| 4.1  | Current and loop bandwidth control of proposed solution                                                                                                       | 80   |

| 4.2  | The comparison of jitter performance                                                                                                                          | 82   |

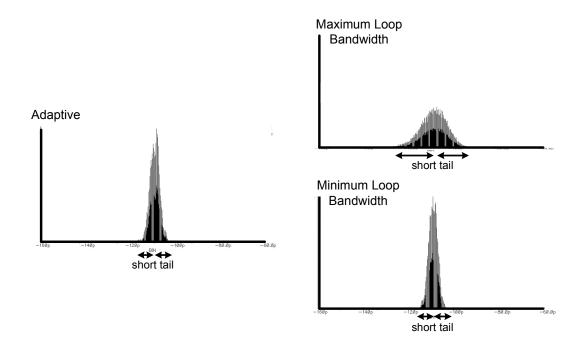

| 4.3  | Jitter histogram comparison : JHISTO-1                                                                                                                        | 84   |

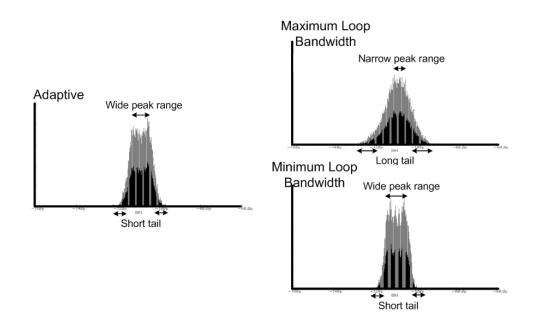

| 4.4  | Jitter histogram comparison : JHISTO-2                                                                                                                        | 84   |

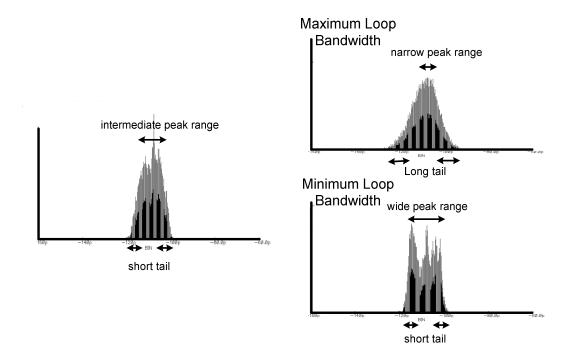

| 4.5  | Jitter histogram comparison : JHISTO-3                                                                                                                        | 85   |

| 4.6  | Jitter histogram comparison : JHISTO-4                                                                                                                        | 86   |

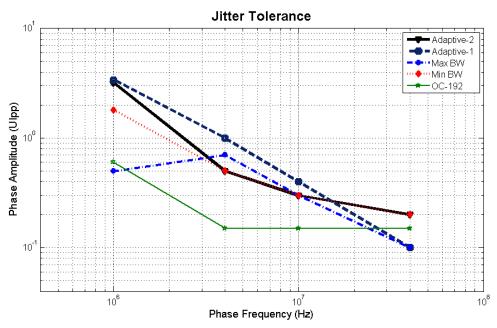

| 4.7  | Jitter tolerance of behavioral mode with condition JTOL-1                                                                                                     | 90   |

| 4.8  | Jitter tolerance of behavioral model with condition JTOL-2                                                                                                    | 90   |

| 4.9  | The effect on the low power wide bandwidth jitter profile                                                                                                     | 91   |

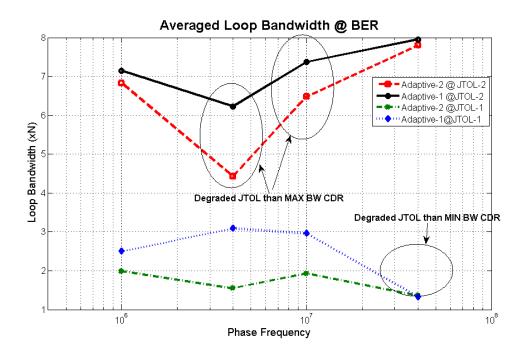

| 4.10 | Average loop bandwidth in the presence of bit error                                                                                                           | 92   |

| 4.11 | Potential threshold point control scheme                                                                                                                      | 93   |

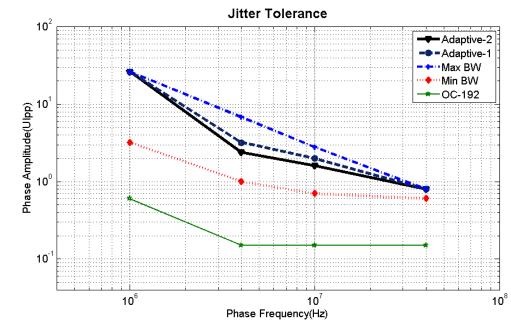

| 4.12 | Jitter tolerance of schematic level with condition JTOL-1                                                                                                     | 94   |

### LIST OF TABLES

| TABLE |     | Page                                                                     |    |

|-------|-----|--------------------------------------------------------------------------|----|

|       | 3.1 | The loop parameters of the proposed CDR                                  | 69 |

|       | 4.1 | The condition of input jitter for the simulation of the jitter histogram | 83 |

|       | 4.2 | Jitter profile for the JTOL measurement                                  | 88 |

|       | 4.3 | The design summary of the adaptive loop bandwidth CDR                    | 95 |

#### CHAPTER I

#### INTRODUCTION

#### **1.** Overview of Clock and Data Recovery in Serial Link

As demand on technology becomes higher in the every part of life, the volume of information to be processed by computing devices also increases. Communication and network industry has confronted wide bandwidth requirement for supporting people to enjoy the advanced computing technology without the limitation of time and places. Those trends also have driven the wide bandwidth technology for hardware-to-hardware communication such as video network, device I/O network and chip-to-chip network.

As the requirement is becoming more stringent, the front end of wireline communication applications must enable high data rate transportation between the devices along the channel with finite bandwidth. Although employing multiple channels might be able to simply increase the bandwidth requirement, it will drastically draw high cost for the hardware implementation as data rate increases. Serial link has been spotlighted as a solution because it saves the implementation cost. With low swing-high data rate signaling by multiplexing, the serial link requires fewer number of the channel material.

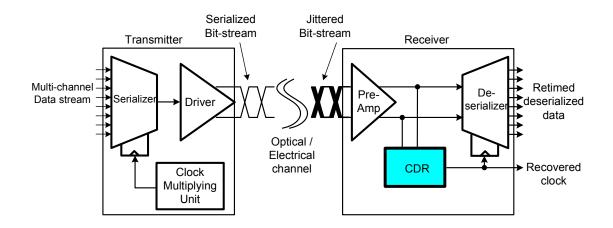

Figure 1.1 shows the general example of the front end in the serial link application.

This thesis follows the style of IEEE Journal of Solid-State Circuits.

Figure 1. 1 Front end in serial link application

A serializer generates high speed digital data stream by multiplexing with Clock Multiplying Unit (CMU). The serialized data stream is attenuated at the end of the channel after delivered by output driver in a transmitter. The data is regenerated to certain level after pre-amplifier stages. Since the data is transported in the absence of a clock, a receiver should recover the clock to retime the data at the right instant. Synchronized by the recovered clock, a de-serializer parallelizes the input data stream to several slow rate data streams into digital computing systems.

Low pass characteristic of the channel not only attenuates the amplitude of the signal but also distorts the shape of data transition. Noise also reduces timing margin from various sources. Supply noise and thermal noise from the transmitter, and cross-talk between the channels affects the shape of the data transition. The distorted data transition reduces timing margin to make a correct data level decision. The loss of timing margin is called *jitter* which is defined as *the timing variation of digital signal from its ideal points* in[1].

While the attenuated data amplitude can be easily recovered by using a comparator, the jitter is hardly corrected by a simple circuitry because the exact time deviation needs to be compensated. Therefore, a special module is required to recover the clock from timing distortion.

Clock and data recovery (CDR) circuits are the clock reconstructing module of a receiver. It extracts the clock at the optimal point from the random input data stream in spite of the presence of jitter. As the data rate increases up to more than 10Gb/s on single channel, the tolerable timing jitter decreases to maintain bit-error rate below certain level that the data level decision on the incoming data is more sensitive to the quality of the recovered clock. Thus, CDR becomes a crucial component for the overall receiver performance.

High quality recovered clock and data is the primary goal of CDR. CDR should recover the clock in the presence of frequency offset, jitter and the randomness of data pattern. The clock frequency offset will be presented between devices if the frequency of CMU in a transmitter is slightly different from the recovered clock of a receiver. CDR should detect the offset and adjust the frequency of the recovered clock as early as possible. As afore-mentioned, jitter is the main issue of recovering clock and data. CDR needs to filter the jitter to increase timing margin. The CDR recovers the clock from non-periodic random data. Due to the absence of frequency information in the random data, the CDR must equip special frequency and phase extraction scheme [2].

Cost optimization for implementation is another goal of CDR design. Industry faces the design trend of low power and low area. However, due to high speed operation,

most of CDR consumes high power more than 100mW for multi-Gb/s applications in >0.18um CMOS technology [3-6]. Moreover, for jitter filtering, large passive elements are required for narrow bandwidth implementation with the high data rate operation. Thus, the power and area need to be optimized for the CDR design as it can be a bottle neck of the overall receiver implementation.

#### 2. Topologies of Clock and Data Recovery

To recover the high quality clock with less implementation cost, various approaches have been proposed for CDR applications. Most of previously proposed CDRs can be classified into open loop type CDR and feedback type CDR [7]. The open loop CDR is a very attractive solution for burst mode data communication because this type of CDR can achieve fast locking and high stability due to its open loop architecture. Phase oversampling[8], gated VCO and high Q band-pass filter have been adopted to implement the open loop CDR. Limited frequency tracking is the common drawback of this open loop CDR because frequency extraction is generally hard to be accomplished without a feedback. The other problems of the open loop type CDR are low jitter suppression (Gated VCO) and high implementation cost (high Q band-pass filter). The feedback type CDRs are based on Phase-Locked Loop (PLL) or Delay-Locked Loop (DLL) structures. Many different types of topology have been suggested by means of phase interpolator [9], injection locking scheme, and the combination of PLL and DLL [10, 11]. Long lock time and stability have been pointed as the inherent problems of this type of CDR. Nevertheless, the feedback type CDR is most widely used because it demonstrates superior performance for bit-rate variation, frequency offset and jitter suppression.

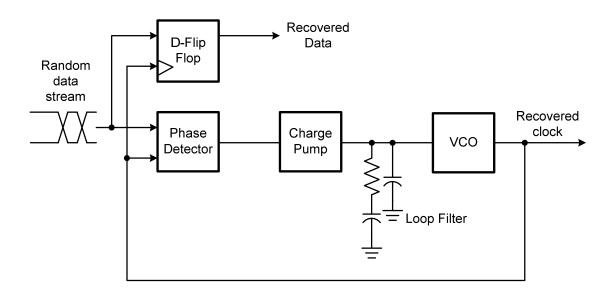

The feedback type CDR is divided into three different types of topology, analog based PLL[3, 5, 6], digital based PLL[12] and semi-digital based PLL/DLL[9, 13, 14], according to the implementation. Analog PLL based CDR transfers all information as continuous analog form of time, voltage and current between the building blocks. As shown in figure 1.2, PD, CP and analog loop filter generate the continuous control voltage of VCO in order to adjust the phase and frequency of recovered clock. The advantage of this topology is high speed implementation in limited technology. However, it generally experiences the leakage in the loop filter and is susceptible to supply noise.

Figure 1. 2 Analog PLL based CDR

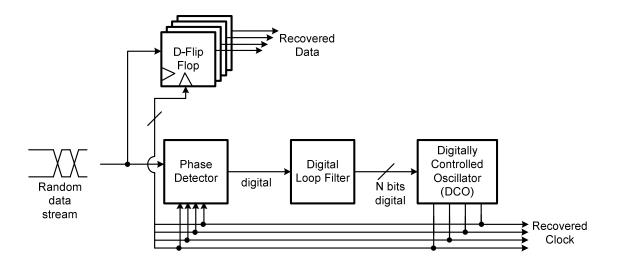

Figure 1. 3 Digital PLL based CDR

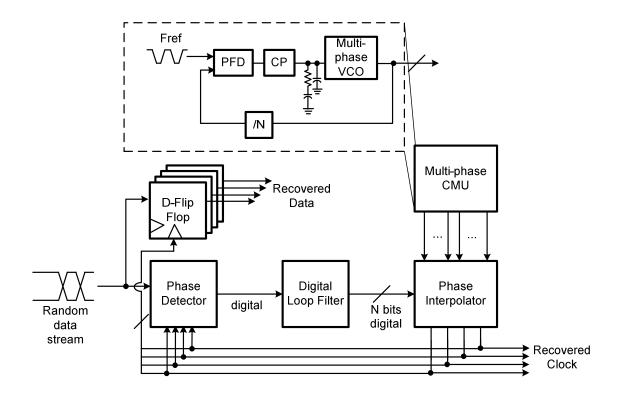

Figure 1. 4 Semi-digital type CDR

In the digital PLL based CDR in figure 1.3, the most of building blocks utilize digital I/Os to control loop dynamics while it still presents the behavior of general PLL [12, 15]. This type of system provides the flexibility of the design because it can be implemented with automatic design procedure as general digital system. This topology, however, is hard to be implemented in high speed application due to the timing requirement of CMOS logic design. The semi-digital PLL/DLL based CDR is implemented with the combination of both types [9, 13]. Generally, main signal path is built with digital components from PD to control voltage while multi-phase generating components are implemented with analog circuitry as shown in figure 1.4. The semi-digital topology provides more design flexibility than the digital based PLL in high speed applications. Nevertheless, the speed limitation of digital circuitry still results in degraded performance in >10Gb/s applications.

Despite of its limitation, the analog PLL is still widely preferred to implement high speed clock and data recovery over the digital or semi-digital topologies. The main reason is that analog loop filter implementation is not limited by input data rate due to its passive-only elements while a digital loop filter implementation is dependent on input data rate. It is necessary to implement high depth digital logic for the digital loop filter in order to recover a clock with high resolution phase step. Since more timing margin is required for higher logic depth, the limit of clock frequency of the filter is determined by the requirement of the clock phase step resolution and  $f_i$  of its technology. Since the maximum updating rate of overall PLL loop is limited by loop filter frequency, the ratio of input data rate to loop-updating rate increases for very high data rate application in low  $f_t$  technology. Then, additional timing jitter is introduced associated with an inherent digital feedback system behavior, *limit cycle*. The limit cycle will be discussed in the chapter II. To minimize the jitter from the limit cycle, the digital loop filter should be functional at even more than 1GHz clock for >10Gb/s applications. Due to the limited  $f_t$  in 0.18um CMOS technology, it is hard to implement 1GHz high depth digital filter with general CMOS logic design. Although CML design may achieve high speed requirement, it is not appropriate for high depth logic design due to its excessive power consumption. Pipe-lined design approach may be able to realize a high speed-high depth digital loop filter. However, it also increases loop delay that the effect of limit cycle will be seriously magnified. As it is free from the afore-mentioned issues of loop filter implementation, an analog PLL based CDR will be considered as the best topology for high input data rate application in low  $f_t$  CMOS technology.

### 3. Organization

This thesis is composed of 5 separate chapters to discuss the motivation, implementation and verification of proposed novel clock ad data recovery.

This chapter introduces the overall architecture of a serial link transceiver and various CDR topologies.

Chapter II reviews the property of Bang-Bang CDR and its jitter performance. Identifying the problem of conventional structures, the trade-off in jitter tolerance will be discussed for loop bandwidth setup. With the comparison of previous solutions, it is justified the necessity of novel CDR In Chapter III, the proposed solution will be described. The main idea will be discussed and relevant issues will be verified by graphical and mathematical analysis. Describing the implementation in detail, overall design procedure will be discussed.

The proposed solution will be verified by performing Cadence simulation in chapter IV. After summarizing all the features, conclusion is made in chapter V.

#### CHAPTER II

## ANALYSIS OF ANALOG BANG-BANG PHASE LOCKED LOOP FOR CLOCK AND DATA RECOVERY APPLICATION

#### **1. Background of Analog Bang-Bang PLL**

As previously shown in figure 1.2, the conventional analog PLL is generally composed of phase detector (PD), charge pump (CP), loop filter and voltage-controlled oscillator (VCO). PD detects phase difference between input data and recovered clock, and produces the corresponding information. CP simply carries out the conversion of the information from PD to be appropriate to the loop filter. The VCO transforms the information to the form of phase. Other components can be required for interfaces, noise immunity and other improvement.

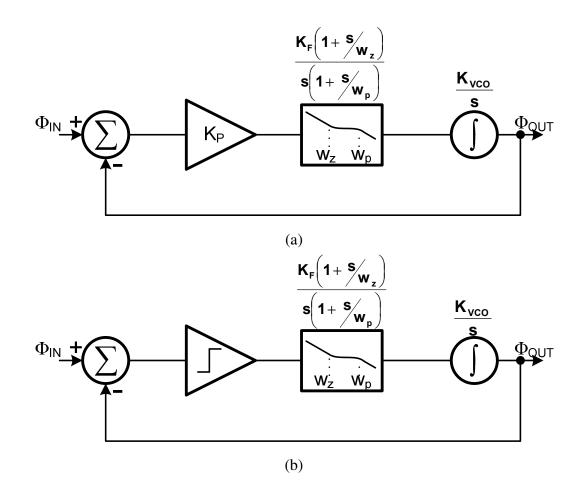

Analog PLLs are categorized by the type of PD. A linear PLL is simply represented as a linear feedback system with a linear type PD. On the other hand, a binary or Bang-Bang PLL exhibits similar behavior to digital system by utilizing a binary type PD (or Bang-Bang PD). The conceptual illustration of the analog PLL is shown in figure 2.1. Note that other components are simply represented as gain (CP), poles/zeros (loop filter) and integrator (VCO), respectively.

While the linear PD produces its output proportional to the phase error, Bang-Bang PD (BBPD) returns its output from the polarity of the phase error. BBPD generates additional timing jitter due to quantization error. Despite of the disadvantage, BBPD is more advantageous than linear PD for high-speed application because of following reasons. Firstly, BBPD effectively produces the output even with very small phase error. Since the PD generally presents the phase error as output pulse width, the linear PD must generate very small pulse width when the PLL is locked and the phase error is very small. On the other hand, BBPD holds the output for one clock period irrespective of the size of phase error due to its binary nature. Higher  $f_t$  is generally required for linear PD than Bang-Bang PD. Thus, BBPD is power efficient over the linear PD in high speed applications.

Figure 2. 1 The conceptual model of analog PLL (a) Linear PLL (b) Bang-Bang PLL

(a)

Figure 2. 2 (a) Phase offset issue of Hogge Detector (b) Alexander PD

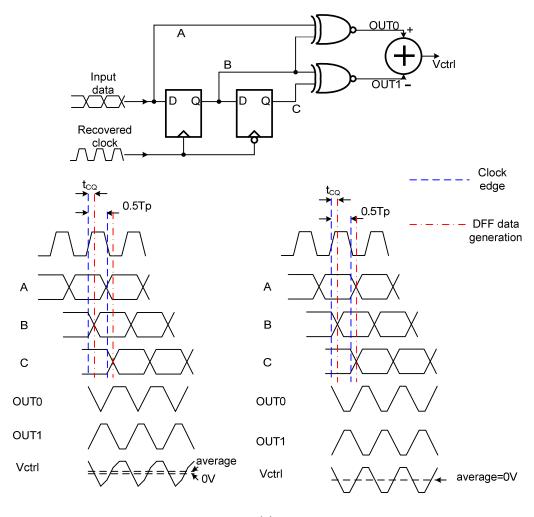

Secondly, BBPD is robust to delay issue. Hogge detector, the most commonly used linear PD in CDR application, generates output with XORs and flip-flops as shown in figure 2.2(a). It introduces certain phase offset because there is a finite timing skew between input data and re-sampled data due to clock-to-data delay ( $t_{CQ}$ ) of flip flop. As shown in the left timing diagram in figure 2.2(a), the output of control voltage will not be locked even if the clock ideally samples data at exact middle point of a bit period. When the clock samples data with phase offset, which is equal to ( $t_{CQ}$ ), the control voltage presents zero averaged output, and then CDR will be locked at this steady-state. However, BBPD never experiences this problem because all combinational logics are preceded by filp-flop. As an example, Alexander PD, the commonly used topology, is shown in figure 2.2(b). Offset is eliminated since all inputs of XOR are synchronized at the same instant.

Figure 2. 3 Slope overloaded output in BBPLL

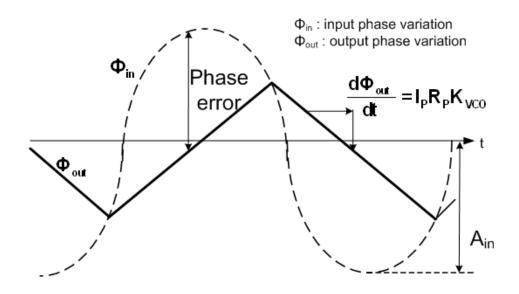

Modeling BBPD as a one-bit quantizer, the overall BBPLL can be represented as a delta-modulator, a well-known modulation scheme in the communications field. The difference is that the second or higher order loop filter adds more complexity to the first order delta-modulator. Based on the delta-modulator model, it can be shown that the loop bandwidth of the BBPLL is nondeterministic. While the loop bandwidth<sup>1</sup> of linear PLL is determined by internal design parameters, the loop bandwidth of BBPLL is dependent on the attribute of input phase perturbation. The characteristic originates from the slope-overloaded behavior of delta-modulator. If the instantaneous slope of input signal exceeds the step size of the delta-modulator, distortion will be generated between input signal and the output of the modulator in experiencing tracking incapability. In equivalent phase model the PLL enters slope-overloaded regime if instantaneous input phase variation or instantaneous input frequency exceeds the phase step of BBPLL as shown in figure 2.3. Phase-slewing is the slope-overloaded phenomenon of BBPLL. In order not to experience phase-slewing, loop parameters should satisfy the following condition [16].

$$I_P R_P K_{VCO} \ge max(\varphi(t)/dt) \tag{2.1}$$

where  $I_P$ ,  $R_P$  and  $K_{VCO}$  represent the pumping current of CP, resistor in the loop filter and the gain of VCO, respectively.  $\varphi(t)$  denotes input phase variation. In case the  $\varphi(t)$  is a

<sup>&</sup>lt;sup>1</sup> Here, loop bandwidth is defined as unity gain frequency of the open loop system

sinusoidal signal, equation (2.1) can be represented by the following equation with input phase amplitude,  $A_{in}$  and its frequency,  $\omega_{in}$ .

$$I_{P}R_{P}K_{VCO} > max(dA_{in} sin(\omega_{in}t)/dt)$$

= max(A<sub>in</sub>\omega\_{in} cos(t))

= A\_{in}\omega\_{in} (2.2)

Equation (2.2) implies large amplitude may cause phase-slewing as well as high frequency, and then attenuation ratio output versus input at certain frequency depends on input amplitude. This property leads to the consequence that the -3dB bandwidth of BBPLL is the function of  $A_{in}$ . The detailed expression of -3dB bandwidth of BBPLL is derived as equation (2.3) in [17].

$$\omega_{-3dB} = \frac{\pi I_P R_P K_{VCO}}{2A_{in}}$$

(2.3)

Since loop bandwidth is approximately equivalent to the -3dB bandwidth of closed loop, it is concluded from equation (2.2) and (2.3) firstly, wide loop bandwidth is required to avoid phase-slewing and secondly, loop bandwidth is inversely proportional to the amplitude of input phase variation.

Input phase perturbation also affects the transfer curve of PD. The perturbation discussed so far is mainly deterministic with phase amplitude and frequency. Random

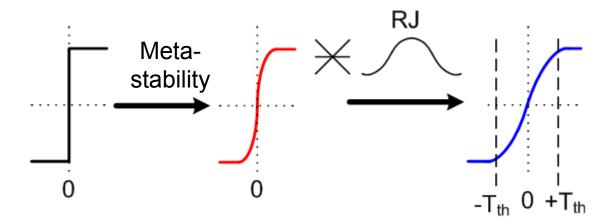

jitter (RJ), one of unpredictable perturbations, affects loop characteristics by changing the transfer curve of PD. RJ originates from thermal noise in electrical circuits and the composition of any uncorrelated noise sources [18]. The internal random noise of PD and CP can be also referred to the input as the form of additional RJ. Because of its unpredicted manner, RJ can be analyzed only using statistic methods. Since it is difficult to apply the probability model to deterministic analysis directly, we can re-define the transfer curve of PD associated with RJ by using its probability density function (PDF). The re-defined transfer curve of PD is represented as the convolution of ideal transfer curve of BBPD and PDF of RJ as shown in equation (2.4) [17].

$$\overline{V_{new}}(\Delta T) = \int_{-\infty}^{+\infty} \overline{V_{ideal}}(\Delta T - x)p(x)dx$$

(2.4)

where  $\overline{V_{new}}$  and  $\overline{V_{ideal}}$  are the transfer function of PD with and without RJ, respectively.  $\Delta T$  is timing error applied at the input of PD, and p(x) is the PDF of random jitter.

The transfer curve of PD is determined by the meta-stability of a flip-flop as well. So far, we have assumed that transfer curve displays extremely steep slope of transition around zero phase error point unless random noise is presented at the input. The assumption, in practice, does not hold because the flip-flop is not able to reach full swing level with very small phase error. A flip-flop is generally composed of two cascaded Dlatches. The D-latch samples data by pre-amplification and regenerates it with a positive feedback. The speed limitation of circuit may fail the D-latch to pre-amplify or to regenerate output voltage to valid level if allowed time or applied input voltage level is not enough. Therefore, smooth transition will be shown around zero phase error in the transfer curve.

Due to the RJ and meta-stability, PD presents linear-shaped transfer curve around the zero phase error region. Thus, it is possible to analyze BBPLL as a piece-wise linear model if the PLL is locked that phase error is close to zero. Figure 2.4 shows how PD transfer curve changes due to RJ, meta-stability and the combined. The linear region, where is between  $V_{thn}$  and  $V_{thp}$ , is widened as the PD experiences more meta-stability and random jitter. Since the linear gain is inversely proportional to the width of the region, it is concluded that the loop gain of piecewise-linear modeled BBPLL is dependent on random jitter and process variation.

Figure 2. 4 Transfer curve variation of BBPD

The binary characteristic of BBPD also affects the steady-state behavior of PLL. A digital feedback system is not able to converge to a single state due to the discontinuity of quantization process even if the difference of input and output is close to zero. In steady-state, digital feedback system exhibits bounded periodic oscillations at the output in the manner of dithering the quantized output to be close to desired finite value [19]. The periodic oscillation, which is called *limit cycle*, is presented in the BBPLL due to its digital property with BBPD. The quantization error with the limit cycle effect causes timing misalignment. The inherent timing jitter of BBPLL is called *hunting jitter* or *dithering jitter*. The peak-to-peak hunting jitter,  $\Delta t_{p,p}$ , is computed as the equation (2.5) and (2.6) according to [20]. Here,  $\tau = (T_{delay}/T_b)$ .

$$\Delta t_{p \ p} = I_{P} R_{P} K_{VCO} \cdot N \cdot (2(1+D) + (1+D)\tau + (1+D)^{3}\tau^{2} + O(\tau^{3})) T_{b}^{2}$$

$$= (I_{P} R_{P} K_{VCO} \cdot N \cdot T_{delay}) T_{b}$$

(2.5)

or

$$\frac{\Delta t_{p-p}}{T_o} = I_p R_p K_{VCO} \cdot N \cdot T_{delay}$$

(2.6)

where D,  $T_b$  and  $T_{delay}$  are the normalized loop delay, bit period and effective loop delay, respectively. N denotes the division ratio of the frequency divider or the decimation ratio of digital loop filter. It is typically unity for the analog PLL based CDR. As can be seen in equation (2.6), the normalized hunting jitter is proportional to N and  $T_{delay}$ . This correlation implies the limitation of digital or semi-digital topologies as previously discussed in chapter I. The equation (2.5) and (2.6) are derived based on the assumption that input RJ is much smaller than hunting jitter. With the presence of input RJ, [21] reported the empirical output jitter with respect to loop parameters as following<sup>2</sup>.

$$\sigma_{OUT} = 0.7 \sqrt{\theta_{bb}} \sigma_{IN}$$

=  $0.7 \sqrt{I_P R_P K_{VCO} T_{update}} \sigma_{IN}$  (2.7)

where  $\sigma_{OUT}$  and  $\sigma_{IN}$  represent standard deviation of output jitter and input jitter, respectively.  $T_{update}$  denotes the loop updating time. From the equation (2.3), (2.6) and (2.7), it is observed that wide loop bandwidth increases steady-state output jitter.

The pattern of input data stream is another important element affecting loop characteristics, especially on CDR applications. Unlike a normal PLL, CDR receives non-periodic random data. Since PLL detects and tracks phase error in the vicinity of data transition, the PLL can track faster the phase error as data transition occurs more frequently. Thus, loop bandwidth is also proportional to the rate of data transition, *data density*, which is defined as:

$$D = \#(data \ transition) / \#(bits \ of \ data \ stream)$$

(2.8)

Loop bandwidth of CDR is subsequently represented by:

$<sup>^{2}</sup>$  Note that (2.7) is valid only with moderate power of input jitter and large the stability factor (>100).

$$\omega_{loop\_CDR} = D \times \omega_{loop\_BBPLL}$$

$$= \frac{\pi D I_P R_P K_{VCO}}{2A_{in}}$$

$$(2.9)$$

### 2. The Jitter Specifications in Bang-Bang Clock and Data Recovery

n

In high-speed wire-line communication standard, the system is required to pass different types of jitter specification. Jitter transfer (JTRAN), jitter generation (JGEN) and jitter tolerance (JTOL) are essential jitter specifications widely referred in the industry.

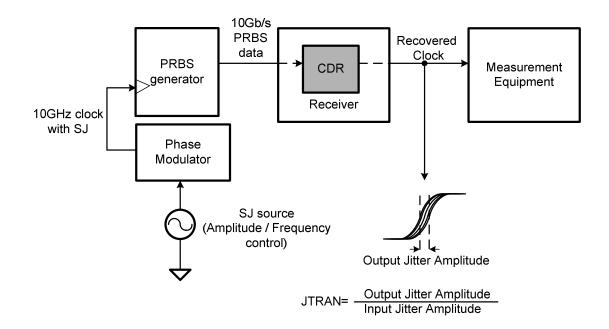

Figure 2. 5 Measurement of jitter transfer

JTRAN is defined as the output jitter suppression of the system to the input jitter. Wire-line communication network generally requires repeater in the middle of media for the long distance communication. If the jitter is not filtered out by each repeater, the jitter is accumulated and the receiver at the final destination experiences excessive jitter which leads to the degradation of overall bit-error-rate (BER). To avoid the phenomenon, JTRAN suggests the jitter suppression standard. JTRAN is generally the specification relevant to the transmitter because the transmitter generates final output of repeater to the following system. Nevertheless, JTRAN is still the specification related to CDR applications because the jitter of recovered clock and data affects the performance of following components between digital core and receiver front-end.

As illustrated in figure 2.5, JTRAN is represented by the relative output jitter corresponding to the input SJ amplitude at certain frequency. JTRAN, therefore, is generally equivalent to the system transfer function. To satisfy the JTRAN specification, BBCDR must follow low pass characteristic as corresponding to the characteristics of the general PLL.

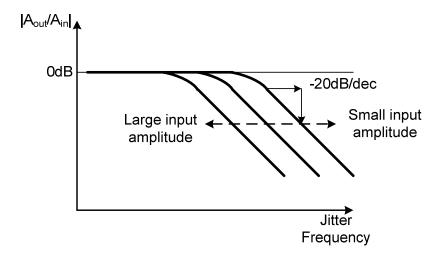

Figure 2. 6 Jitter transfer curve of BBPLL

The important factors of JTRAN are maximum gain peaking and corner frequency. Maximum gain peaking denotes the upper limit of allowable jitter amplification. Corner frequency specifies the upper limit of allowable frequency of transferred output jitter. Concerning the factors, BBCDR presents noticeable properties. First, as illustrated in figure 2.6, corner frequency is the function of input SJ amplitude since it is equivalent to -3dB frequency in equation (2.3). Second, BBCDR exhibits small gain peaking [17]. It is because high gain of PD in linear regime increases the distance between zero frequency and unity gain frequency.

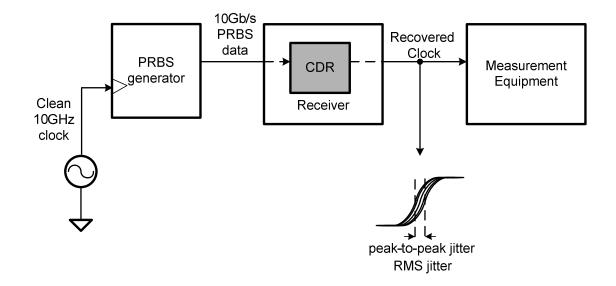

JGEN is the self-generated jitter of the system with the absence of input jitter. JGEN is also the specification relevant to transmitter. Nevertheless, JGEN is still important specification for CDR as an indicator of internal jitter contribution. Figure 2.7 shows the example of JGEN measurement setup. RMS jitter and peak-to-peak jitter should be reported to represent the specification. Generally, the VCO phase noise and hunting jitter are considered as the main contributors of JGEN. Due to its high pass property VCO phase noise is suppressed by wide loop bandwidth. On the other hand, hunting jitter increases for wide loop bandwidth according to the equation (2.6). The loop bandwidth of BBCDR should be selected carefully to minimize jitters from both effects. The optimal loop bandwidth setup can be different according to the VCO topology. For example, with ring VCO, wide loop bandwidth is required to mitigate the significant VCO phase noise. On the other hand, narrow loop bandwidth can be allowed for the implementation with LC VCO because of its superior noise performance over ring VCO

Figure 2. 7 Measurement of jitter generation

JTOL is defined as the maximum amplitude of input phase variation at the specified frequency where receiver maintains BER below the certain value. To satisfy the specification, CDR should regenerate the clock with maximal timing with the presence of jitter. Since many different jitter sources are involved in reality, it is necessary to define the various types of jitter and their characteristics in detail in order to analyze JTOL of BBCDR.

Jitter is generally categorized into two different types, random jitter (RJ) and deterministic jitter (DJ). RJ exhibits unbounded limit range while DJ varies within the certain boundary. DJ is also divided into particular subgroups. Inter-symbol interference (ISI), duty-cycle distortion (DCD) and periodic jitter (PJ) are the typical DJs as main interests in serial link. Due to its natural randomness and unbounded limit, it is hard to predict the behavior of RJ. On the other hand, there exists distinctive behavior of each DJ. ISI results from the bandwidth limitation of the channel and digital circuitry. When high rate random data are applied at the bandwidth-limited channel and circuitry, output signal may or may not reach full swing depending on the data pattern. The effect draws different delay time for each transition, and accordingly contributes additional timing jitter. Its peak value is deterministic and bounded as shown in figure 2.8.

Figure 2. 8 (a) Generation of ISI and (b) its PDF

ISI is basically wide bandwidth jitter because it changes from peak to peak even in 1-bit transition. DCD is generated by the unbalanced rising and falling time of input data. Due to the offsets and mismatches of transmitter side, input data may present asymmetrical transition. It may also result from the different decision thresholds between transmitter and receiver. DCD, however, is not serious issue because it can be easily alleviated with fully differential signaling. PJ is the jitter generated by any periodic disturbances. Switching power supply noise, EMI and RF coupling are the wellknown sources of PJ. While ISI and DCD are dependent on the data pattern, PJ is generally uncorrelated with input data pattern. The sinusoidal jitter (SJ) in figure 2.5 is special type of PJ. Due to its sinusoidal behavior, the peak value of SJ is bounded and its PDF exhibits high probability at the both extremes as shown in figure 2.9.

Figure 2. 9 PDF of sinusoidal jitter

To measure JTOL, input SJ is applied to the input of the system. Sweeping the SJ amplitude at the specified frequency, the maximum amplitude can be measured where the BER is beyond the certain level (typically  $<10^{-12}$ ). After collecting these points at different frequencies, JTOL will be plotted on the frequency-amplitude plane. This curve is required to be higher than the suggested mask by industrial standard. For example, the JTOL mask of SONET-OC192 is shown in figure 2.10. Due to the low pass characteristics of CDR, JTOL mask suggests smaller amplitude as frequency increases. If the frequency is beyond the certain frequency, the tolerable amplitude becomes flat because CDR cannot track the high frequency phase variation.

Figure 2. 10 SONET OC-192 jitter tolerance mask

Figure 2. 11 Jitter Tolerance of BBCDR

The JTOL of BBCDR has been studied by [17]. Based on the noise-free 2<sup>nd</sup>-order BBPLL, JTOL exhibits three distinctive regions, -40dB/dec slope (region I), -20dB/dec slope (region II) and flat range (region III) as illustrated in figure. 2.11. The corner frequency between each region is expressed as:

$$\omega_{I_2} = 0.63 \frac{\pi}{R_P C_P}$$

(2.10)

$$\omega_{2_{3}} = \frac{I_{P}R_{P}K_{VCO}}{2}$$

(2.11)

where  $\omega_{1_2}$  is the corner frequency between region I and II, and  $\omega_{2_3}$  is between –region II and III, respectively. Equation (2.10) implies that the integral gain with mainly

contributes phase tracking of PLL in region I. Equation (2.11) shows that phase tracking controlled by the proportional gain in region II. At the frequency beyond  $\omega_{2_3}$ , the loop cannot track phase variation that the JTOL will be flat. The tolerable amplitude of the flat range is ideally 0.5UIpp in noise free system. In practice, however, the system should pass JTOL with the presence of unpredictable wide bandwidth jitter such as RJ and ISI as depicted in figure 2.12. The practical JTOL in the region III is computed as:

$$JTOL = JTOL_{ideal} - RJ_{pp} - ISI_{pp} - CDR_{pp}$$

(2.12)

where  $JTOL_{ideal}$  is JTOL in noise free case.  $RJ_{pp}$  and  $ISI_{pp}$  are peak-to-peak value of input RJ and input ISI, respectively.  $CDR_{pp}$  represents transferred or self-generated output jitter. For the 10<sup>-12</sup> of BER, the peak-to-peak RJ,  $RJ_{pp}$ , is represented by equation (2.13) [22].

$$RJ_{pp} = 7\sigma_{RJ} \tag{2.13}$$

where  $\sigma_{RJ}$  is the RMS value of RJ. As shown in equation (2.13), the JTOL is degraded by transferred or self-generated output jitter. Therefore, it is the critical design issue to pass the high frequency JTOL mask.

Figure 2. 12 Measurement of jitter tolerance

### **3** Jitter Tolerance Improvement of Bang-Bang Clock and Data Recovery

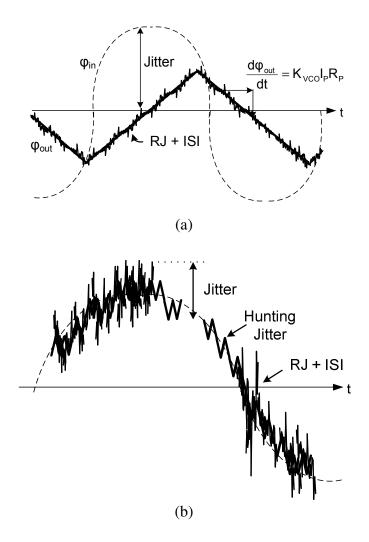

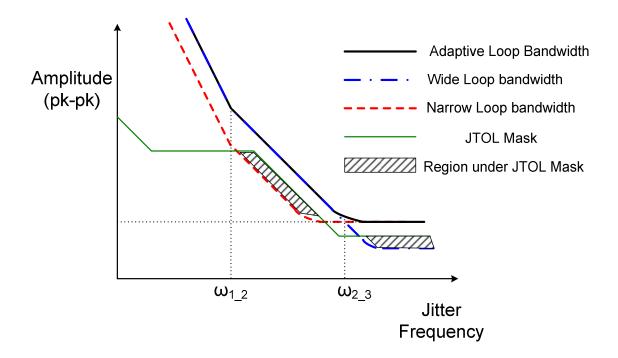

As a clock reconstructing module of the receiver, the improvement of JTOL is the primary goal of the CDR design. To guarantee more timing margin for JTOL, optimization of loop bandwidth is important issue among many considerations of CDR design. As discussed so far, wide loop bandwidth is generally advantageous to track the input SJ. In addition, VCO phase noise is highly suppressed by wide loop bandwidth feedback. The wide loop bandwidth setup, however, is not optimal with considerable RJ and ISI. As can be seen in equation (2.6) and (2.7), wide loop bandwidth magnifies wide bandwidth steady-state output jitter associated with RJ, ISI and hunting jitter. Thus, the BBCDR demonstrates degraded JTOL. On the other hand, narrow loop bandwidth of severe phase-slewing and VCO phase noise that JTOL will be degraded. The opposing characteristics of BBCDR with the different loop bandwidth are illustrated in figure 2.13.

Figure 2. 13 The characteristics of (a) narrow loop bandwidth and (b) wide loop bandwidth

As a result, JTOL will be displayed according to the loop bandwidth setup as:

1) Wide loop bandwidth CDR extends region II due to its high tracking capability. However, JTOL will be degraded in region III because CDR transfers more of wide bandwidth steady-state jitter. 2) Narrow loop bandwidth CDR suppress wide bandwidth jitter effectively so that it maintain relatively high JTOL in region III. Nevertheless, the corner frequency,  $\omega_{2,3}$ , is much decreased due to inability of phase tracking.

From the observations so far, it can be found that there exists optimal loop bandwidth to maximize timing margin for JTOL improvement. The optimal loop bandwidth should be wide enough to track input phase variation without phase-slewing. The optimal loop bandwidth is also forced to produce only moderate wide bandwidth steady-state jitter. Unfortunately, the optimal bandwidth is not a deterministic value because the input jitter profile is not predictable. The narrow loop bandwidth is optimal to the case with low frequency / small amplitude input SJ in experiencing harsh RJ and ISI. In contrast, wide loop bandwidth is superior for the high frequency / large amplitude input SJ with gentle RJ and ISI.

To improve JTOL to unknown jitter profile, automatic loop bandwidth optimization schemes have been suggested by previously proposed solutions.

[23] proposes the all digital CDR with automatic loop bandwidth control. After phase error is detected by multi-phase clock, CDR selects loop bandwidth setup to track the phase error without excessive hunting jitter. Basically, [23] achieved an improved corner frequency  $\omega_{2,3}$  between region II and III. The all-digital structure provides the high integration, low power and robustness to PVT variation. Nevertheless, in high frequency region III, it exhibits more degraded JTOL than the conventional topology. This mainly results from that the CDR adjusts the loop bandwidth according to the *instantaneous* phase error. This topology not only tracks input SJ but also transfers RJ and ISI. As a result, transferred jitter degrades JTOL according to equation (2.12). The poor phase noise of multi-phase ring VCO also worsens jitter performance. Ring VCO typically demonstrates inferior phase noise performance than LC VCO. Thus, when the narrow loop bandwidth is selected, the CDR will experience serious jitter injection by VCO phase noise.

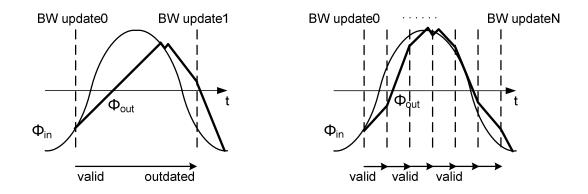

Semi-digital PLL/DLL based CDR is also proposed with the adaptive loop bandwidth approach by [24]. With digital piece-wise integration, the logic integrates the phase detector output during some cycles. If the absolute value of integrated sum is over the threshold, the loop bandwidth is increased. Conversely, the loop bandwidth is decreased in case the integrated sum is below the threshold. This approach provides the advantage of detecting relative power between wide bandwidth jitter (RJ, ISI) and phaseslewing. It improves JTOL in region III while maintaining tracking capability in region I and II. Additionally, the semi-digital structure presents good integration and moderate power consumption. However, some limitations still exist for the >10Gb/s application. First, the digital loop filter implementation is limited for the high speed application as afore-mentioned. Second, the loop bandwidth updating rate is quite slow. Due to slow updating rate of loop filter, the loop bandwidth updating process takes place every 320bits. The adaptation is not effective if the input SJ frequency is comparable to or faster than the updating rate because the adjusted loop bandwidth is outdated for the current phase variation.

In chapter III, the novel loop adaptation strategy will be discussed to optimize loop bandwidth for improved JTOL while alleviating the problems of previous solutions.

# 4. Summary

Bang-Bang PLL based CDR shows unique features of its input-dependent transfer function and steady-state limit cycle. The unique features results in the trade-off of loop bandwidth setup for jitter optimization and Jitter Tolerance improvement. Wide loop bandwidth setup introduces excessive wide bandwidth jitter while it demonstrates good tracking capability to eliminate phase-slewing. Narrow loop bandwidth experiences serious phase error due to inability of phase tracking although steady-state wide bandwidth jitter is highly suppressed. For loop bandwidth optimization, previously reported solutions suggest loop automatic loop bandwidth adjustment with digital or semi-digital implementation. Nevertheless, they present the limitations for high frequency jitter tolerance and high input data rate implementation.

#### CHAPTER III

#### ADAPTIVE LOOP BANDWIDTH CLOCK AND DATA RECOVERY

#### **1.** Loop Bandwidth Adaptation

#### **1.1. Loop Bandwidth Adjustment with Charge Pump Current Control**

To control loop bandwidth, there exist three adjustable design parameters, CP current, loop filter resistor and VCO gain (KVCO) according to equation (2.3). The KVCO, however, is not an effective option in analog type PLL applications because of its inaccurate control. While CP current and loop filter resistor are likely to be constant, it is hard to maintain constant KVCO due to its non-linear characteristic and the PVT variation.

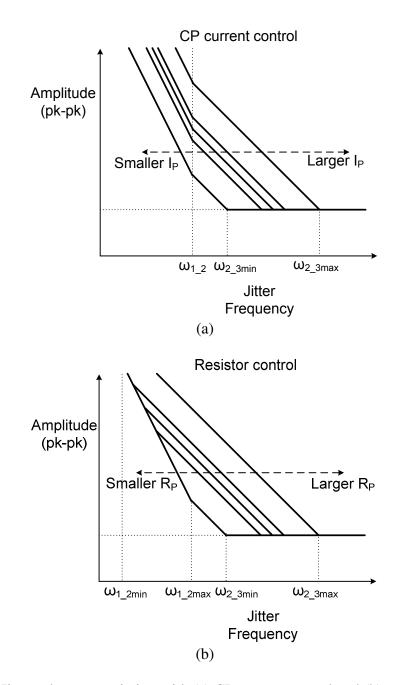

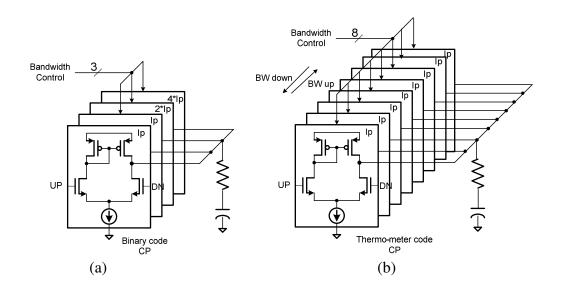

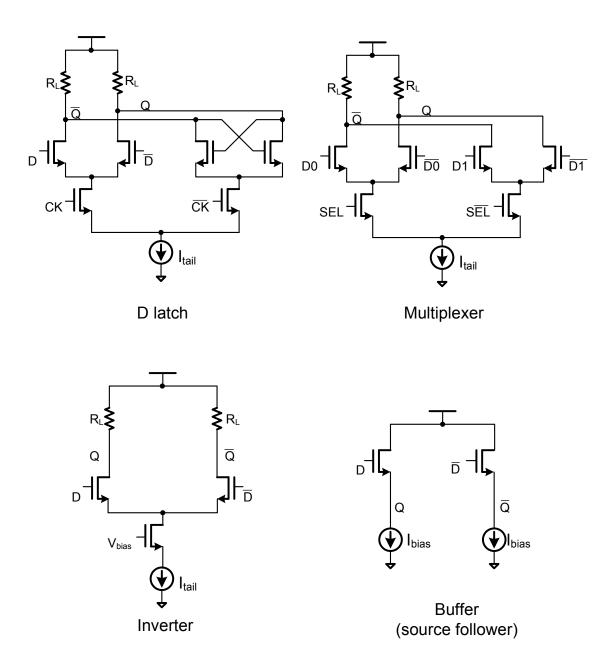

To compare the effect between CP current control and loop filter resistor control, the JTOL variations are illustrated in figure 3.1(a) and (b). Here,  $\omega_{1,2}$  is the corner frequency between region I (-40dB/dec region) and region II (-20dB/dec regions) and  $\omega_{2,3}$  is the corner frequency between region II and region III (flat regions). From equation (2.10) and (2.11), it can be seen that  $\omega_{1,2}$  is inversely proportional to the resistance in contrast to linear correlation of the  $\omega_{2,3}$  with resistance. On the other hand, the CP current control changes only  $\omega_{2,3}$  proportionally while it maintains  $\omega_{1,2}$  constant. Thus, as depicted in figure 3.1(a), the criteria of region I and II is never affected as region II can be extended or narrowed down by CP current control. Although both approaches control loop bandwidth accurately, in this thesis, CP current control strategy is suggested because of its superiority of the stability and circuit implementation.

Figure 3. 1 Jitter tolerance variation with (a) CP current control and (b) resistor control

Stability factor of 2<sup>nd</sup> order BBPLL is suggested by [21]. It is represented as the ratio of proportional phase gain and integral phase gain. Therefore:

$$\xi = \frac{P_{prop}}{P_{int}} = \frac{I_P R_P K_{VCO} T_{update}}{I_P K_{VCO} T^2_{update} / (2C_P)} = \frac{2R_P C_P}{T_{update}}$$

(3.10)

According to the equation, the stability factor is determined by the time constant of loop filter and loop updating time,  $T_{update}$ . Assuming constant loop delay and capacitance, the stability factor is only affected by loop filter resistance. Thus, resistor control results in time-variant stability factor. If loop bandwidth changes by eight times, the stability factor variation is also eight times. Unexpectedly decreased stability factor introduces additional timing error since it boosts peaking in the transfer function. To guarantee the stability in any loop bandwidth setup, loop filter capacitor will be much lager than conventional fixed loop bandwidth CDR. In contrast, CP current control realizes independent correlation between the stability factor and loop bandwidth variation. Since the CP current is not a relevant term of the stability factor in equation (3.10), the CP current control maintains constant stability factor regardless of loop bandwidth control range.

The analogy of conventional analysis on linear PLL helps shed light on the advantage of CP control. In linear PLL analysis, phase margin is the quantitative indicator of stability. In the 2<sup>nd</sup> order PLL, the phase margin is determined by the distance between zero ( $\omega_z$ ) and unit gain frequency<sup>3</sup> ( $\omega_c$ ).  $\omega_z$  and  $\omega_c$  are represented by:

<sup>&</sup>lt;sup>3</sup> Note that unit gain frequency is equivalent to loop bandwidth as defined in chapter II.

$$\omega_z = \frac{1}{R_P C_P} \tag{3.11}$$

$$\omega_c = \frac{I_P R_P K_{VCO}}{2\pi} \tag{3.12}$$

Accordingly, the phase margin of  $2^{nd}$  order linear PLL will be shown as:

$$PM = \arctan\left(\frac{\omega_c}{\omega_z}\right) = \arctan\left(\frac{I_P R_P^2 C_P K_{VCO}}{2\pi}\right)$$

(3.13)

As can be seen in the equation (3.13), the distance between  $\omega_z$  and  $\omega_c$  varies linearly to the CP current variation while quadratically to the resistance variation. As a result, phase margin variation is well-controlled by CP current than resistor. It can be deduced, therefore, that CP current control provides superior stability control. Note that this analysis provides only indirect insight to understand the stability of BBCDR by using analogy of linear system. It may be inadequate to apply directly the linear system theory to the BBCDR.

The CP current control also provides advantage of circuit implementation. Generally, CP current control can be accomplished by adjusting tail current of CP. The abrupt glitches in changing loop bandwidth can be absorbed by parasitics on the path from the tail current to the loop filter. On the other hand, the resistor control brings potential problem in its implementation. One example of resistor control method is shown in figure 3.2 To control the resistance of the loop filter, switches need to be turned on and off in connecting and disconnecting the parallel resistors. Since the source of current or charge glitches are directly connected to the loop filter without filtering, the control voltage of VCO will be very noise. In addition, large size of switches can cause additional phase error. The switch size should be large to minimize its resistance in order to control loop bandwidth accurately. However, induced by large sized switches, charge injection introduces the frequency offset then causes serious the phase error.

Figure 3. 2 The example of resistor controlled scheme

# 1.2. Prediction with Mixed Mode Piece-wise Integration

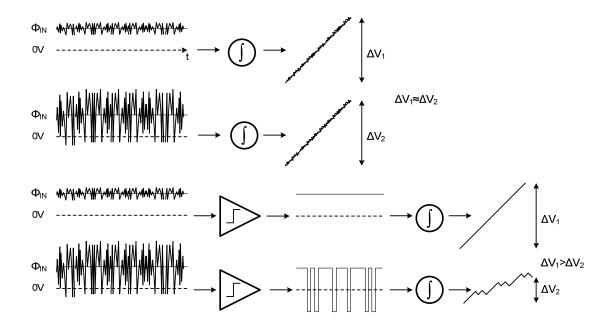

To optimize the loop bandwidth for >10Gb/s applications, a novel adaptive loop bandwidth BBCDR is proposed in this thesis. This technique employs a mixed mode piece-wise integration method. The overall system is conceptually based on the adaptive delta modulator. As shown in figure 3.3, the loop bandwidth is adjusted according to the binary output information of BBPD as a one-bit quantizer. The predictor interprets the binary information and controls loop bandwidth to minimize timing error under the presence of input SJ, hunting jitter, RJ and ISI.

The predictor detects current jitter profile by integrating the PD output. The effect of the integration on CDR performance is based on two assumptions. First, the hunting jitter, RJ and ISI are wider bandwidth jitter than SJ. Second, the mean value of them is zero. To distinguish the power of wide bandwidth jitter from the phase-slewing, integration will be the solution because it filters most power of zero-mean value jitters. However, direct integration of phase error obtains only the power of phase-slewing jitter because the information of zero mean wide bandwidth jitter, w(t), is vanished after integration time,  $t_0$  as shown in equation (3.1).

$$\int_{0}^{t_{0}} \left[ p(t) + w(t) \right] dt = \int_{0}^{t_{0}} p(t) dt + \int_{0}^{t_{0}} w(t) dt \cong \int_{0}^{t_{0}} p(t) dt \qquad (t_{0} \gg \tau_{w})$$

(3.1)

where p(t) is the timing jitter from phase-slewing. The parameter,  $\tau_w$ , is the inverse of the bandwidth of w(t). To optimize the loop bandwidth, however, the relative power between p(t) and w(t) is more useful information.

Figure 3. 3 The conceptual diagram of adaptive delta-sigma modulator

If BBPD precedes the integrator, the integrator output will reflect the relative power between phase-slewing jitter and wide bandwidth jitters. As the wide bandwidth jitter becomes more dominant than phase slewing, the averaged value of integrator will decrease. The averaged output will increase for dominant phase slewing as shown in figure 3.4. The equation (3.2) describes it as:

$$\int_{0}^{t_{0}} q[p(t) + w(t)] dt \cong \begin{cases} \int_{0}^{t_{0}} q(p(t)) dt \cong t_{0} \text{ or } - t_{0}, \ (\sigma_{p} \gg \sigma_{w}) \\ \\ \int_{0}^{t_{0}} q(w(t)) dt \cong 0, \qquad (\sigma_{p} \ll \sigma_{w}) \end{cases} \quad (\tau_{p} \gg t_{0} \gg \tau_{w}) \quad (3.2)$$

Here,  $\sigma_p$  and  $\sigma_w$  are power of phase-slewing and wide bandwidth jitter, respectively. The parameter,  $\tau_w$  and  $\tau_p$  are the inverse of the bandwidth of w(t) and p(t), respectively.

q(x) is the quantization function as represented in following equation (3.3).

$$q(x) = \begin{cases} +1, & (x > 0) \\ 0, & (x = 0) \\ -1 & (x < 0) \end{cases}$$

(3.3)

Basically, the information of BBPD output is already integrated in the capacitor of the loop filter. However, it is hard to detect the instantaneous input phase and frequency variation from the voltage of that capacitor. The reason is because the voltage variation is very small in a short period due to the large capacitance value. Also, the voltage across the capacitor is not instantaneous but long term frequency information.

Figure 3. 4 The effect of BBPD on the integration

Figure 3. 5 The conceptual diagram of the predictor

Thus, short period piece-wise integration will be the appropriate solution to detect the instantaneous input frequency variation.

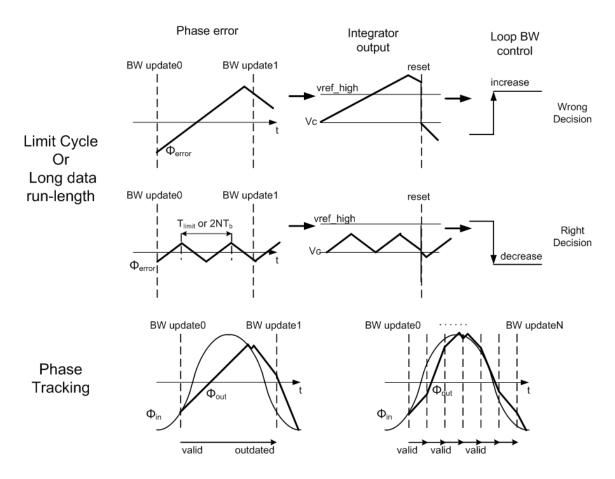

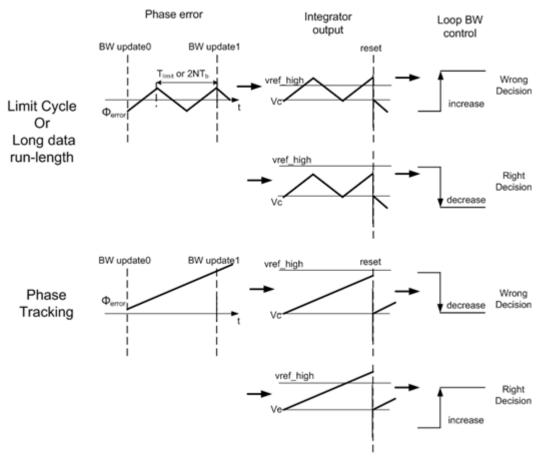

A novel predictor shown in figure 3.5 with mixed mode piece-wise integration is proposed. The analog front-end integrates binary output of BBPD, followed by one-bit absolute analog-to-digital (A/D) conversion. The output of absolute A/D conversion determines the increment or decrement of the loop bandwidth. The A/D conversion refers the absolute value of integrator output. For example, if either 'up' or 'down' is dominant than the other during the integration, the loop bandwidth will increase. Loop bandwidth will decrease if the numbers of 'up' and 'down' are comparable. Therefore, loop bandwidth should be increase (decrease) when the absolute value of average PD output is larger (smaller) than the threshold point. The absolute A/D conversion can be described as equation (3.4).

$$f(x) = \begin{cases} 1, & (x \ge X_{th\_high} \text{ or } x < X_{th\_low}) \\ 0 & (X_{th\_high} > x > X_{th\_low}) \end{cases}$$

(3.4)

Here,  $X_{th\_high}$  and  $X_{th\_low}$  are the upper and lower threshold points. From (3.2) to (3.4), it can be described how to decide the increment / decrement of loop bandwidth from the PD output as shown in equation (3.5).

$$f\left[\alpha\int_{0}^{t_{0}}q[p(t)+w(t)]dt+\beta\right]$$

$$\approx \begin{cases} f\left[\alpha\int_{0}^{t_{0}}q(p(t))dt+\beta\right] \cong f(\alpha t_{0}+\beta) \text{ or } f(-\alpha t_{0}+\beta)=1 \qquad (\sigma_{p} \gg \sigma_{w}) \\ f\left[\alpha\int_{0}^{t_{0}}q(w(t))dt+\beta\right] \cong f(\beta)=0 \qquad (\sigma_{p} \ll \sigma_{w}) \end{cases}$$

(3.5)

where  $\alpha$  and  $\beta$  are fitting factors for practical implementation.  $\beta$  must be selected between  $X_{th_high}$  and  $X_{th_how}$ . After absolute A/D conversion, a fully digital controller generates the loop bandwidth control signals according to the current and previous increment / decrement output of absolute A/D converter.

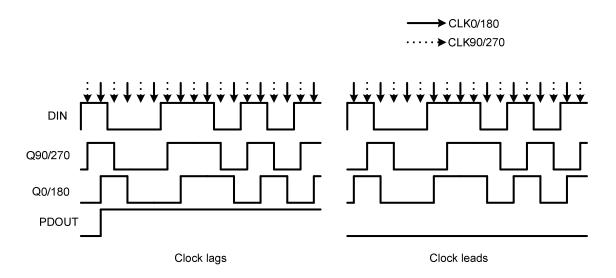

The proposed predictor brings apparent advantages compared to the previous solutions. First of all, current mode analog integrator relieves speed limitation. For 10Gb/s input data rate, the digital integrator should operate around 1GHz clock to maintain de-serialized ratio of 1:10. This requires high  $f_t$  technology or power hungry CML implementation. On the other hand, current mode analog integrator does not require high  $f_t$ . It leads significantly low power consumption for the integration. Second,

this approach maintains high speed loop bandwidth updating rate. The loop bandwidth updating rate is significant for the high frequency input SJ. As shown in figure 3.6, if the rate is quite slower, the updated loop is not valid because it is based on the past information. As afore-mentioned, previous solution [24] takes 320bits for the integration due to the speed limitation of loop filter. On the other hand, the proposed mixed-mode integration takes only 32 bits to update the loop bandwidth since analog loop filter does not involve decimation. Third, the proposed solution still takes advantage of the versatility of digital control. The information is processed in digital after the absolute A/D conversion. Since the required clock frequency of controller is moderate (from 166MHz to 333MHz for 30 to 60 cycle integration), it is possible to implement the required digital logic in 0.18um CMOS technology. Therefore, it can provide the design flexibility to realize various digital control schemes.

Figure 3. 6 The effect of loop bandwidth updating rate

# 2. System Overview

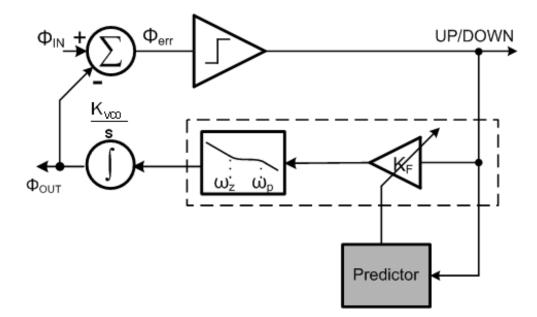

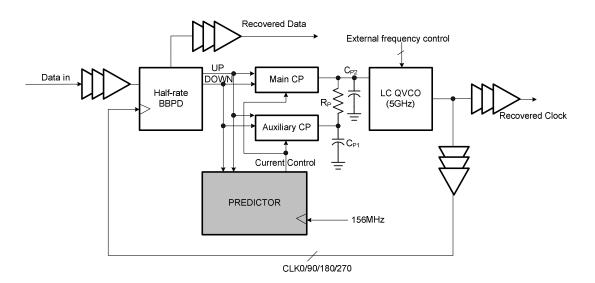

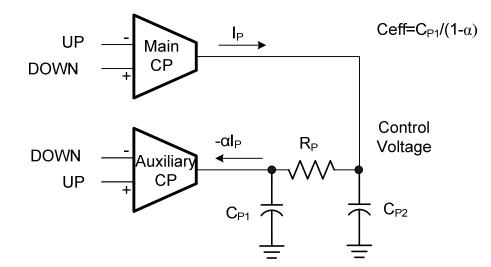

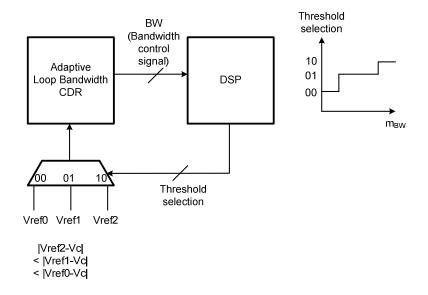

The overview of system diagram is shown in figure 3.7. The architecture is based on  $3^{rd}$  order BBPLL. Since the parallel capacitor ( $C_{P2}$ ) is relatively smaller than series capacitor ( $C_{P1}$ ), analysis of  $2^{nd}$  order BBPLL model is still valid. Combined with predictor, the BBPLL performs adaptive delta modulation.

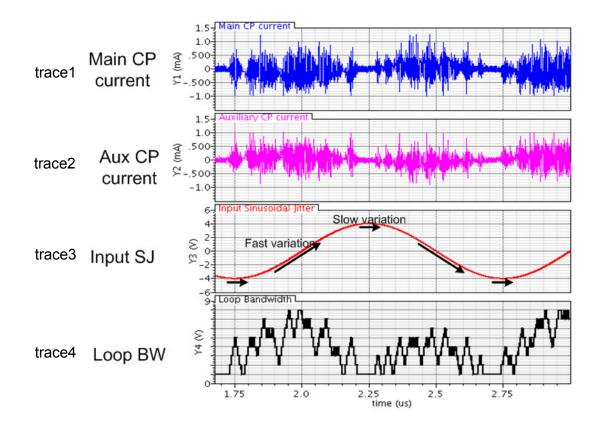

As discussed so far, the predictor is connected in parallel to the signal path from BBPD to CP. From the PD output, it detects jitter profile and updates the loop bandwidth by controlling CP current. The digital controller inside predictor is operating at 156MHz. This clock can be easily provided by sharing the frequency divider output in DeSerializer<sup>4</sup>.

Figure 3. 7 The architecture of proposed adaptive loop bandwidth BBCDR

<sup>&</sup>lt;sup>4</sup> It is out of the scope in this thesis

The proposed architecture adopts half-rate BBPD for the power and speed issue. For the 10Gb/s application, the full rate PD requires D flip flops updating the input data to the output within 100ps that requires significant power consumption. Moreover, with low  $f_t$  technology it may not be possible to realize full-rate operation even with high power consumption. Therefore, the half-rate structure relieves the speed and power requirement even with limited  $f_t$  technologies.

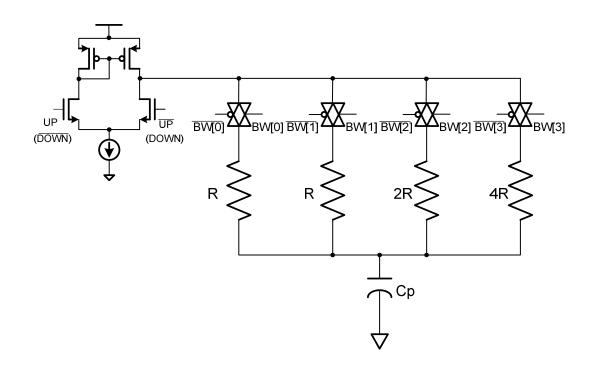

Dual variable CP is employed to realize the loop bandwidth control as well as a capacitor multiplication technique for on-chip integration. The current of CP is adjusted by three-bit digital control signal from the predictor. Dual CP structure provides the capacitor multiplication. The capacitor multiplication factor determines the current ratio of main and auxiliary CP. With the capacitor multiplication, required capacitor is reduced from one nF to 250pF in 200x200um<sup>2</sup>, which is on-chip implementable value.

Although out of the scope of this thesis, the effect of VCO needs to be considered thoroughly. The phase noise of VCO is especially critical issue in proposed solution. The proposed solution changes the loop bandwidth in real-time. If the loop bandwidth is set to the minimum, the phase noise of VCO may be magnified by the loop and accordingly the output jitter will be increased. Therefore, quadrature LC type VCO is regarded as the possible structure since its phase noise performance is superior than ring VCO. The behavioral model is built based on [25-27] and, for the verification, simulation has been performed with reasonable phase noise specification of typical LC VCO.

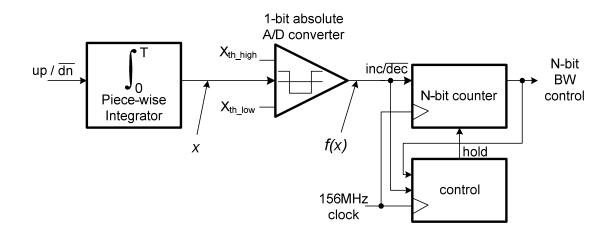

# **3. Predictor Design**

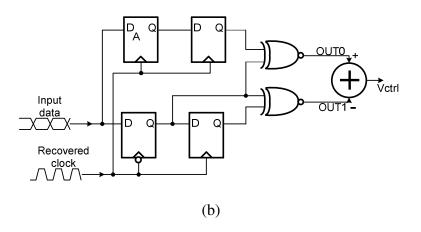

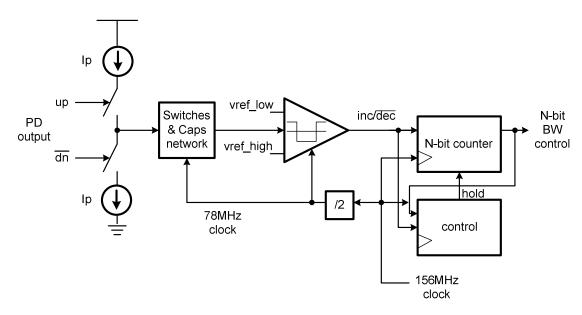

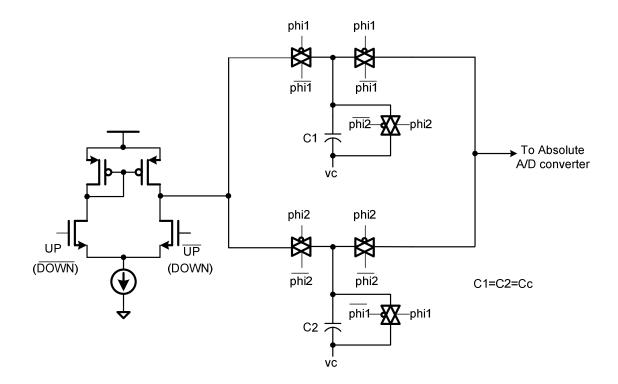

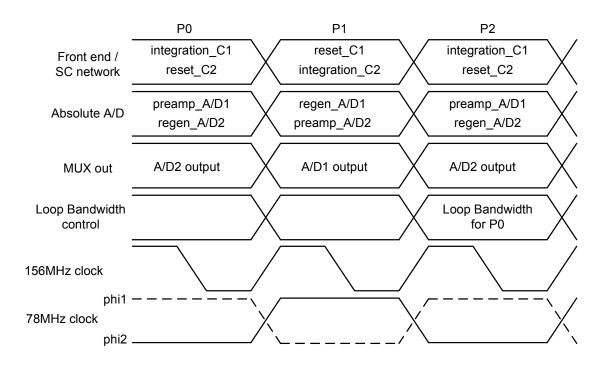

As shown in figure 3.8, the predictor consists of a charge pump, a switched capacitor network, absolute A/D converter and digital logic circuitry. Note that charge pump in the predictor is different components from the one connected to loop filter. This integrating charge pump (ICP) performs the mixed mode piece-wise integration with switched capacitor. The ICP generates the current corresponding to the BBPD output. The generated current will be integrated by the capacitor. In order to perform *piece-wise* integration, the charge on the capacitor should be reset periodically, otherwise, the past information will affect the future loop bandwidth decision because charge remains in the capacitor.

Figure 3. 8 The architecture of the predictor

Figure 3. 9 Piece-wise integration with switched capacitor network

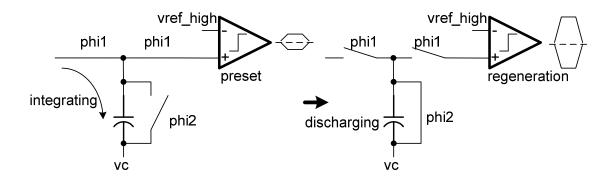

The operation is illustrated in figure 3.9 in detail. While the phil is on, the ICP current is integrated into the capacitor. When there is a transition of clock (from phil to phi2), integrated information is dumped to the A/D conversion stage. Now, while the phi2 is on, the capacitor starts being discharged by turning on the switch across the capacitor while the information of PD output is decoupled with the capacitor. This implies that loop bandwidth is evaluated during phil only. To make the system more efficient, dual path integration is required. One ICP and two switched capacitor network operates with complementary clock cycle. One path integrates PD output into the first capacitor while another path discharges the second capacitor. The dual path structure provides better jitter performance because it enables continuous adaptation.

The schematic of analog front end is illustrated in figure 3.10. A differential pair is employed to implement ICP. The switched capacitor network is composed of three CMOS transmission gate and one capacitor. In order to perform effective integration, the output pole of ICP is required to be far below than loop updating frequency because the most current of ICP needs to be injected to the capacitor without loss of charge by parallel resistance. Therefore, the output resistance of ICP should be much higher than the impedance of capacitor at the loop bandwidth updating frequency rate as:.

$$r_{dsp} // r_{dsn} \gg \frac{1}{2\pi f_{loop\_update} C_C}$$

(3.6)

Figure 3. 10 The schematic of analog front end of piece-wise integrator

where  $r_{dsp}$  and  $r_{dsn}$  denote small signal resistance of PMOS and NMOS, respectively. C<sub>C</sub> is the capacitance of piece-wise integrator.  $f_{loop\_update}$  is the updating frequency of loop bandwidth control. The effect of switch resistance is neglected in equation (3.6).

For a complete analysis, the effect of switch resistance needs to be considered because the size of switch may affect the performance of integrator. To hold the equation (3.6) valid, the parallel resistance of switch should be smaller than the impedance of capacitor. Thus, the following relations will hold as:

$$r_{on} \ll \frac{1}{2\pi f_{loop\_update} C_C}$$

(3.7)

$$\alpha_n \frac{W_n}{L} (V_{DD} - V_O - V_{tn}) + \alpha_p \frac{W_p}{L} (V_O - V_{tp}) >> 2\pi f_{update} C_C$$

(3.8)

where  $\alpha_n = \mu_n C_{ox}$  and  $\alpha_p = \mu_p C_{ox}$ , respectively.  $V_0$  is the output voltage of the integrator, and  $V_{tn}$  and  $V_{tp}$  are the threshold voltage of NMOS and PMOS, respectively. According to (3.8), the large transistor width is desirable to reduce the switch resistance. In practice, however, the switch size is limited by non-ideal effects such as charge injection and clock feed-through. The size of transistor is required to be optimized to minimize the effects while the equation (3.8) still holds. Although both conditions can be satisfied with the large Cc, it requires extra silicon area. Moreover, the voltage difference on large Cc will be too small to be detected after the integration.

The analog front end is followed by the one-bit absolute A/D converter. Composed of comparators and combinational digital logic, the absolute A/D converter samples the integrator output and regenerates it to digital domain for the versatility of digital controller.

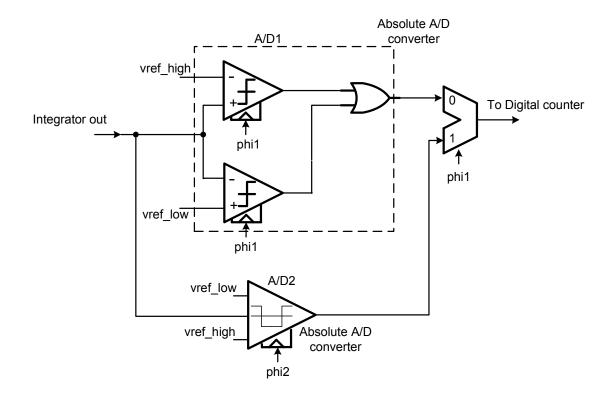

Figure 3. 11 The architecture of absolute A/D converter

The schematic of the converter is shown in figure 3.11 with preceding output of integrator. Two converters are implemented for both paths integrator outputs. Each converter returns its output in complementary phases. By multiplexing the two outputs, the predictor can provide the information to digital controller continuously. The detailed timing dynamics are depicted in figure 3.12.

Each A/D converter consists of two comparators with different threshold point. If the final integrator output either exceeds the high threshold or goes the below low threshold, either of comparators regenerates output to VDD. By or-gating the two comparator outputs, the absolute A/D conversion defined in equation (3.4) is realized.

Figure 3. 12 The timing diagram of the predictor operation

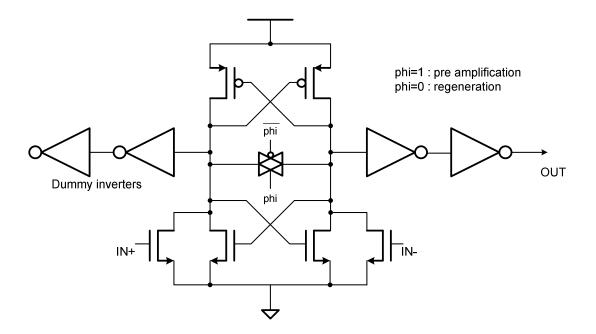

As shown in figure 3.13, static type comparator is implemented using a high sensitivity stage and rail-to-rail output. The output of the switched capacitor circuit may exhibit voltage around the threshold points if the wide bandwidth jitter is comparable to jitter by phase-slewing. High input sensitivity reduces the ambiguity of loop adjustment decision for the small input offset. Not limited by bias current, the pseudo differential topology regenerates output fast. The comparator is followed by minimum size inverters to help the output driving capability. Dummy inverters are added to match load condition of differential output.

Figure 3. 13 The comparator schematic of A/D converter

The absolute A/D converter returns high for the phase-slewing dominant jitter profile and returns low for the RJ and ISI dominant jitter.

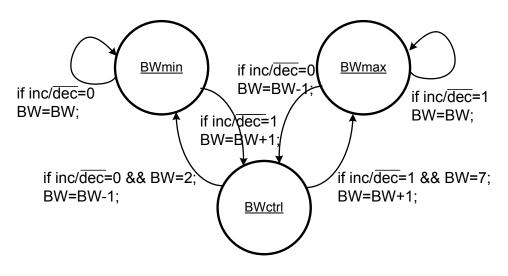

Figure 3. 14 The state diagram of digital counter

Figure 3. 15 The implementation of bi-directional shift registers for digital counter

According to this, the digital controller adjusts the loop bandwidth. As the bidirectional counter, the digital controller increases one step of loop bandwidth if the converter output is high. It also decreases one step if output is low. Once the loop bandwidth reaches to the maximum (or minimum) setup, the controller maintains the maximum (or minimum) loop bandwidth code until the decrement (or increment) is requested by the A/D converter. The loop bandwidth ranges from one to eight times the basic loop bandwidth. The state diagram of the digital controller is illustrated in figure 3.14. In this work, the digital controller is described with behavioral model for the simulation. One possible implementation is suggested in figure 3.15. Eight bit bidirectional shift register provides control signal to tune the loop bandwidth by a factor of eight. Only eight D flip flop and eight MUXes are required for the implementation.

In order to realize immediate loop bandwidth update, it is still required to minimize the critical delay from the analog front end to the input of digital controller. The updating procedure of predictor may not be accomplished within one clock period due to the excessive delay of comparator and logic. If additional clock cycles are required to complete the process, consequent latency of updating loop bandwidth results in outdated loop bandwidth setup for the input jitter profile as shown in figure 3.16. It potentially leads degradation on loop bandwidth optimization. The timing requirement, therefore, needs to guarantee the instantaneous loop bandwidth update. To update the loop bandwidth within one clock cycle, the following timing condition must be satisfied.

$$T_{clk} > t_{comp} + 2 \quad t_{inv} + t_{or} + t_{mux\_AD} + t_{mux\_ctrl} + t_{setup}$$

(3.9)

where  $T_{clk}$  is the predictor clock period (6.4ns for 156MHz).  $t_{comp}$ ,  $t_{inv}$ ,  $t_{or}$  and  $t_{mux\_AD}$  are the time delay of comparator, inverter and MUX, respectively.  $t_{mux\_ctrl}$  is the delay of MUX in digital counter and  $t_{setup}$  is the setup time of D flip-flop. Regarding the trade-off between dynamic power and speed, all dimensions of comparators and logic gates need to be carefully determined.

Figure 3. 16 The effect of logic delay on the loop bandwidth updating time

## 4. Dual Variable Charge Pump Design